半導体装置及びその製造方法

【課題】さらなる微細化に対しても適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現する。

【解決手段】ゲート電極120bは、第1の仕事関数を有する第1の金属含有膜114bと、第1の金属含有膜114b上に形成されており且つ第2の仕事関数を有する第2の金属含有膜117bとを含む。ゲート電極120aは、第1の金属含有膜114を含まないと共に第2の金属含有膜117aを含む。ゲート電極120bにおける第1の金属含有膜114bと第2の金属含有膜117bとの間に拡散防止層115bが形成されている。

【解決手段】ゲート電極120bは、第1の仕事関数を有する第1の金属含有膜114bと、第1の金属含有膜114b上に形成されており且つ第2の仕事関数を有する第2の金属含有膜117bとを含む。ゲート電極120aは、第1の金属含有膜114を含まないと共に第2の金属含有膜117aを含む。ゲート電極120bにおける第1の金属含有膜114bと第2の金属含有膜117bとの間に拡散防止層115bが形成されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、金属含有膜を含むゲート電極を有する半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、半導体集積回路装置の高集積化、高機能化及び高速化に伴って、金属−絶縁物−半導体電界効果トランジスタ(MISFET(Metal-Insulator-Semiconductor Field-Effect Transistor ))の微細化が進められている。

【0003】

一方、MISFETの微細化に伴い、ゲート絶縁膜の薄膜化を進めると、トンネル現象に起因するゲートリーク電流の増大、又はポリシリコンゲート電極の空乏化等の影響が顕著になり、オン電流の確保、ひいてはMISFETの動作速度の維持又は向上が難しくなってくる。

【0004】

この問題を解決するために、ゲート絶縁膜として、従来のシリコン酸化膜に代えて、ハフニウム酸化膜(HfO2 )等のより誘電率が高い絶縁膜(高誘電率絶縁膜(high-k膜))を用いると共に、ゲート電極における少なくともゲート絶縁膜と接する部分の材料をポリシリコンから金属含有材料に置き換えることが検討されている。これにより、ゲート絶縁膜の物理的な厚さを大きくしながら、酸化膜換算膜厚(EOT(Equivalent Oxide Thickness)を低減すること、及び、ゲート電極の空乏化を抑えて反転層厚さ(Tinv)を低減すること等が期待される。すなわち、ゲート絶縁膜の電気的な厚さを薄くすることが期待される。ここで、酸化膜換算膜厚EOTとは、酸化シリコンと異なる比誘電率を持つ誘電体膜の膜厚を酸化シリコンの比誘電率で換算した膜厚値をいう。

【0005】

前述の高誘電率ゲート絶縁膜及び金属含有ゲート電極を用いたトランジスタの実現において最も重要な課題の1つは適正な閾値電圧Vtを得ることである。そのためには、pチャネルMISFETのゲート電極構造においてはSiの価電子帯(5.15eV)に近い仕事関数を有するpチャネル用金属含有膜を用いると共にnチャネルMISFETのゲート電極構造においてはSiの伝導帯(4.05eV)に近い仕事関数を有するnチャネル用金属含有膜を用いた構造、つまり、デュアルメタルゲート構造を実現する必要がある。

【0006】

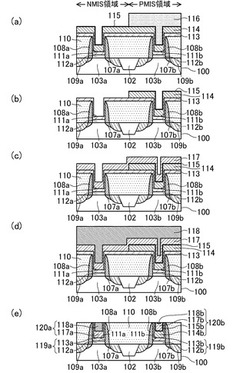

以下、従来のデュアルメタルゲート構造の一例として、特許文献1に開示されている構造について説明する。図7(a)〜(e)及び図8(a)〜(c)は、特許文献1に開示されている従来の半導体装置の製造方法の各工程を示す図である。

【0007】

まず、図7(a)に示すように、シリコン(Si)からなる半導体基板1の上部に、シャロウトレンチ分離(STI)からなる素子分離領域2を選択的に形成する。続いて、イオン注入法により、nチャネルMISFETの形成領域(以下、NMIS領域という)にはp型ウェル領域3aを形成し、pチャネルMISFETの形成領域(以下、PMIS領域という)にはn型ウェル領域3bを形成する。続いて、半導体基板1の表面上に下地膜4を介して高誘電率絶縁膜5を形成した後、高誘電率絶縁膜5上にpチャネル用金属含有膜6を形成する。

【0008】

次に、図7(b)に示すように、PMIS領域を覆うマスクパターン7を形成した後、マスクパターン7を用いて、図7(c)に示すように、NMIS領域に位置する部分のpチャネル用金属含有膜6をエッチバックして除去し、その後、マスクパターン7を除去する。次に、図7(d)に示すように、NMIS領域に位置する部分の高誘電率絶縁膜5上、及びPMIS領域に残存するpチャネル用金属含有膜6上に、nチャネル用金属含有膜8を形成する。

【0009】

次に、図7(e)に示すように、nチャネル用金属含有膜8上に導電膜9を形成した後、NMIS領域及びPMIS領域それぞれのゲート電極形成領域を覆うマスクパターン10を形成する。次に、マスクパターン10を用いたドライエッチングによって、図8(a)に示すように、導電膜9、nチャネル用金属含有膜8及びpチャネル用金属含有膜6を順次パターニングした後、マスクパターン10を除去する。これにより、NMIS領域には、nチャネル用金属含有膜8a及び導電膜9aからなるnチャネル用ゲート電極12aが形成されると共に、PMIS領域には、pチャネル用金属含有膜6b、nチャネル用金属含有膜8b及び導電膜9bからなるpチャネル用ゲート電極12bが形成される。このとき、nチャネル用ゲート電極12a及びpチャネル用ゲート電極12bのそれぞれの外側に位置する部分の下地膜4及び高誘電率絶縁膜5が除去されて、半導体基板1とnチャネル用ゲート電極12aとの間に、下地膜4a及び高誘電率絶縁膜5aからなるゲート絶縁膜11aが形成されると共に、半導体基板1とpチャネル用ゲート電極12bとの間に、下地膜4b及び高誘電率絶縁膜5bからなるゲート絶縁膜11bが形成される。

【0010】

次に、図8(b)に示すように、イオン注入法により、半導体基板1におけるnチャネル用ゲート電極12aの両側にn型エクステンション領域13aを形成し、半導体基板1におけるpチャネル用ゲート電極12bの両側にp型エクステンション領域13bを形成する。次に、図8(c)に示すように、nチャネル用ゲート電極12a及びpチャネル用ゲート電極12bのそれぞれの側面上に、絶縁性サイドウォールスペーサ14a及び14bを形成した後、イオン注入法により、半導体基板1におけるnチャネル用ゲート電極12a及び絶縁性サイドウォールスペーサ14aの両側にn型ソース/ドレイン領域15aを形成し、半導体基板1におけるpチャネル用ゲート電極12b及び絶縁性サイドウォールスペーサ14bの両側にp型ソース/ドレイン領域15bを形成する。

【0011】

以上に説明したように、従来のデュアルメタルゲート構造を有する半導体装置によると、NMIS領域においては高誘電率ゲート絶縁膜上にnチャネル用金属含有膜を有するゲート電極が形成されており、PMIS領域においては高誘電率ゲート絶縁膜上にpチャネル用金属含有膜を有するゲート電極が形成されている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】米国特許第7625791号明細書

【特許文献2】米国特許第6794234号明細書

【非特許文献】

【0013】

【非特許文献1】K.Mistry他、A 45nm Logic Technology with High-k+Metal gate Transitors,Strained Silicon,9 Cu Interconnect Layers,193nm Dry Patterning,and 100% Pb-free Packaging、IEDM2007、p.247-250

【発明の概要】

【発明が解決しようとする課題】

【0014】

しかしながら、従来のデュアルメタルゲート構造を有する半導体装置においては、微細化に伴い、適正な閾値電圧Vtが得られなくなるという問題が生じる。

【0015】

前記に鑑み、本発明は、さらなる微細化に対しても適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現することを目的とする。

【課題を解決するための手段】

【0016】

前述の目的を達成するために、本願発明者が、従来のデュアルメタルゲート構造において微細化に伴って適正な閾値電圧Vtが得られなくなる原因について検討したところ、以下のような知見を得た。

【0017】

図7(a)〜(e)及び図8(a)〜(c)に示す従来技術によると、PMISFETのゲート電極用金属含有膜(pチャネル用金属含有膜6)については、ゲートパターニング前に、NMIS領域に形成されている部分をエッチバックにより除去している。それに対して、NMISFETのゲート電極用金属含有膜(nチャネル用金属含有膜8)については、プロセスダメージの軽減やプロセスの簡便化等を目的として、ゲートパターニングまで、PMIS領域に形成されている部分を残存させている。従って、PMISFETのゲート電極(pチャネル用ゲート電極12b)は、pチャネル用金属含有膜6bと、nチャネル用金属含有膜8bとの積層構造を有することになる。ここで、前述の従来技術においては、pチャネル用ゲート電極12bの実効仕事関数が、ゲート絶縁膜11bのより近くに位置しているpチャネル用金属含有膜6bによって実質的に決定されること、言い換えると、pチャネル用ゲート電極12bの実効仕事関数に対して、ゲート絶縁膜11bから離れて位置しているnチャネル用金属含有膜8bが実質的な影響を及ぼさないことを前提としている。尚、「実効仕事関数」とは、MISFETの電気特性から求められる仕事関数であって、真空準位と金属のエネルギー準位との差を示す物性的な仕事関数に絶縁膜中の準位などの影響を加味したものを意味する。

【0018】

しかしながら、実際には、例えばゲートパターニング後における不純物(ソース/ドレイン領域に含まれる不純物)の活性化熱処理等の工程においてゲート電極構造が1000℃以上の高温プロセスに曝される。その結果、図9に示すように、pチャネル用ゲート電極12bにおいて、pチャネル用金属含有膜6bとnチャネル用金属含有膜8bとの積層構造中で界面反応が生じて合金化層(合金化層20)が形成されてしまう恐れがある。この合金化層の生成の程度によっては、下層に位置するゲート電極用金属含有膜(pチャネル用金属含有膜6b)の実効仕事関数が所望値から外れてしまう。その結果、従来のデュアルメタルゲート構造を有する半導体装置において、適正な閾値電圧Vtが得られなくなってしまう。

【0019】

尚、図7(a)〜(e)及び図8(a)〜(c)に示す従来技術においては、pチャネル用金属含有膜6bの厚さを十分に大きくすれば、前述の合金化層(合金化層20)の影響を抑制できるものの、この場合には、pチャネル用金属含有膜6bの選択的エッチバック及びゲートパターニングにおけるプロセス負荷が増大するという別の問題が生じる。

【0020】

また、特許文献2には、特許文献1に類似した異種のゲート電極用金属含有膜の積層構造における界面合金化反応を利用して、合金化反応後の仕事関数を利用する構成が提案されている。しかしながら、特許文献2に開示されている技術においては、合金化反応後の仕事関数を利用できる金属材料の選択肢が少ないという実用上の問題がある上に、合金化反応自体の制御が困難であるために、特許文献1と同様の問題を生じる恐れがある。

【0021】

また、非特許文献1には、特許文献1及び2のようなゲートファースト法に代えて、ゲートラスト法を用いたデュアルメタルゲート構造形成が開示されている。ゲートラスト法を用いた場合、ゲート電極の形成前にソース/ドレイン領域を形成できるため、ゲート電極形成後の工程における主な熱負荷は、420〜430℃程度のシンタの熱負荷位になるので、特許文献1及び2のようにゲートファースト法を用いた場合と比較して、異種のゲート電極用金属含有膜の積層構造における望ましくない合金化反応を抑制できる可能性がある。しかしながら、例えばアルミニウム等の金属材料を用いた場合には、シンタの熱負荷であっても金属拡散及び合金化が生じてしまう。また、ゲートラスト法においては、ポリシリコン等からなるダミーゲート電極の除去により形成されるリセス内に、異種の金属含有膜の積層構造が埋め込まれるが、微細化に伴って当該リセスの寸法(例えばゲート電極高さとなるリセス深さ)が小さくなるので、仕事関数を決定する各ゲート電極用金属含有膜の厚さを例えば10nm程度以下に薄くする必要がある。その結果、異種のゲート電極用金属含有膜の積層構造における界面合金化反応を十分に抑制できないと、合金化層の形成に起因して下層のゲート電極用金属含有膜の厚さが例えば5nm程度以下になってしまい、所望の仕事関数を得ることができなくなる。

【0022】

以上に述べたように、本発明の目的を達成するためには、つまり、さらなる微細化に対しても適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現するためには、ゲートファースト法及びゲートラスト法のいずれを用いた場合においても、仕事関数を決定する異種のゲート電極用金属含有膜の積層構造(pチャネル用金属含有膜とnチャネル用金属含有膜との積層構造)における界面合金化反応を極力抑えることが極めて重要な課題となる。

【0023】

本発明は、以上の知見に基づきなされたものであって、その要旨は、仕事関数を決定する異種のゲート電極用金属含有膜の積層構造(pチャネル用金属含有膜とnチャネル用金属含有膜との積層構造)における当該各金属含有膜同士の間に、金属拡散を防止するための拡散防止層を形成することである。これにより、さらなる微細化に対しても、異種のゲート電極用金属含有膜の積層構造における界面合金化反応を抑制して所望の仕事関数を得ることができるので、適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現することができる。尚、拡散防止層の形成に際しては、特に、プロセスの複雑化を避けるために、また、拡散防止層そのものを新たに挿入形成することに起因するゲート電極の厚さの増大や仕事関数に対する影響等を極力抑えるために、下層のゲート電極用金属含有膜の表面改質、又は異種のゲート電極用金属含有膜同士の界面の改質を行うことが好ましい。また、改質手段としては、膜堆積の他、例えば、熱処理、プラズマ処理又はイオン注入等を用いることができる。また、有効な拡散防止層材料としては、例えば、金属酸化物、金属窒化物又は金属酸窒化物等を用いることができる。

【0024】

具体的には、本発明に係る半導体装置は、第1のゲート電極を有する第1導電型MISFETと、第2のゲート電極を有する第2導電型MISFETとを半導体基板上に備えた半導体装置であって、前記第1のゲート電極は、第1の仕事関数を有する第1の金属含有膜と、前記第1の金属含有膜上に形成されており且つ第2の仕事関数を有する第2の金属含有膜とを含み、前記第2のゲート電極は、前記第1の金属含有膜を含まないと共に前記第2の金属含有膜を含み、前記第1のゲート電極における前記第1の金属含有膜と前記第2の金属含有膜との間に拡散防止層が形成されている。

【0025】

尚、前記拡散防止層は、ゲート電極の抵抗低減の観点からは、導電層であることが好ましいが、トンネル効果を生じる極薄(例えば2nm程度以下)の絶縁層であってもよい。また、前記拡散防止層が導電層であっても、微細化の観点(特にゲートラスト法を用いる場合)からは、前記拡散防止層の厚さは5nm程度以下であることが好ましく、ゲート電極の抵抗低減の観点からは、前記拡散防止層の厚さは2nm程度以下であることがより好ましい。

【0026】

本発明に係る半導体装置において、前記拡散防止層は、前記第1の金属含有膜を構成する材料の酸化物、窒化物又は酸窒化物から構成されていてもよい。

【0027】

本発明に係る半導体装置において、前記第1導電型MISFETはpチャネルMISFETであり、前記第2導電型MISFETはnチャネルMISFETであり、前記第1の金属含有膜は、Ti、Ta、W若しくはNiを含む金属窒化物、又は貴金属から構成されており、前記第2の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物から構成されていてもよい。ここで、前記拡散防止層は、Ti又はTaを含む酸化物から構成されていてもよい。また、前記第1の金属含有膜は、W若しくはNiを含む金属窒化物、又は貴金属から構成されており、前記拡散防止層は、Ti又はTaを含む金属窒化物から構成されていてもよい。また、前記第1の金属含有膜は、貴金属から構成されており、前記拡散防止層は、貴金属の酸化物、窒化物又は酸窒化物から構成されていてもよい。また、前記第1の金属含有膜は、Ti、Ta、W又はNiを含む金属窒化物から構成されており、前記拡散防止層は、Ti、Ta、W又はNiを含む金属酸窒化物から構成されていてもよい。

【0028】

本発明に係る半導体装置において、前記第1導電型MISFETはnチャネルMISFETであり、前記第2導電型MISFETはpチャネルMISFETであり、前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物から構成されており、前記第2の金属含有膜は、Ti、Ta、W若しくはNiを含む金属窒化物、又は貴金属から構成されていてもよい。ここで、前記拡散防止層は、Ti又はTaを含む酸化物から構成されていてもよい。また、前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物(但しTi又はTaの窒化物を除く)若しくは炭化物から構成されており、前記拡散防止層は、Ti又はTaを含む金属窒化物から構成されていてもよい。また、前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の炭化物から構成されており、前記拡散防止層は、前記第1の金属含有膜を構成する材料の酸化物、窒化物又は酸窒化物から構成されていてもよい。また、前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属の窒化物、又は前記金属群の中から選ばれた2つ以上の金属の合金の窒化物から構成されており、前記拡散防止層は、前記第1の金属含有膜を構成する材料の酸化物から構成されていてもよい。

【0029】

本発明に係る半導体装置において、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの下に、高誘電率絶縁膜を含むゲート絶縁膜が形成されていてもよい。ここで、前記ゲート絶縁膜は、前記高誘電率絶縁膜の下に形成されており且つシリコン酸化膜からなる下地膜を含んでいてもよい。

【0030】

本発明に係る半導体装置において、前記第1のゲート電極及び前記第2のゲート電極はそれぞれ、前記第2の金属含有膜上に形成された導電膜を含んでいてもよい。

【0031】

また、本発明に係る半導体装置の製造方法は、第1のゲート電極を有する第1導電型MISFETと、第2のゲート電極を有する第2導電型MISFETとを半導体基板上に備えた半導体装置の製造方法であって、前記半導体基板における前記第1導電型MISFETの形成領域の上に、第1の仕事関数を有する第1の金属含有膜を形成する工程(a)と、前記工程(a)よりも後に、前記第1の金属含有膜の上、及び前記半導体基板における前記第2導電型MISFETの形成領域の上に、第2の仕事関数を有する第2の金属含有膜を形成する工程(b)と、前記工程(b)よりも後に、前記第1の金属含有膜及び前記第2の金属含有膜をパターニングして、前記第1の金属含有膜及び前記第2の金属含有膜を含む前記第1のゲート電極と、前記第1の金属含有膜を含まないと共に前記第2の金属含有膜を含む前記第2のゲート電極とを形成する工程(c)とを備え、前記工程(a)と前記工程(c)との間に、前記第1のゲート電極における前記第1の金属含有膜と前記第2の金属含有膜との間に介在する拡散防止層を形成する工程(d)をさらに備えている。

【0032】

本発明に係る半導体装置の製造方法において、前記工程(d)において、前記第1の金属含有膜の表面部を改質することによって前記拡散防止層を形成してもよい。ここで、前記工程(d)は、前記工程(b)よりも前に実施され、前記工程(d)において、酸素及び窒素の少なくとも一方を含む雰囲気中での熱処理又はプラズマ処理によって、前記第1の金属含有膜の表面部を改質してもよい。また、前記工程(a)は、前記半導体基板における前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に、前記第1の金属含有膜を形成する工程(a1)と、前記工程(a1)よりも後に、前記第2導電型MISFETの形成領域の上に形成された部分の前記第1の金属含有膜を選択的に除去する工程(a2)とを含み、前記工程(d)は、前記工程(a1)と前記工程(a2)との間に実施され、前記工程(d)において、前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に形成された前記第1の金属含有膜の表面部を改質することによって前記拡散防止層を形成し、前記工程(a2)において、前記第2導電型MISFETの形成領域の上に形成された部分の前記拡散防止層を選択的に除去してもよい。或いは、前記工程(d)は、前記工程(b)よりも後に実施され、前記工程(d)において、酸素及び窒素の少なくとも一方のイオン注入によって、前記第1の金属含有膜の表面部を改質してもよい。

【0033】

本発明に係る半導体装置の製造方法において、前記工程(d)は、前記工程(b)よりも前に実施され、前記工程(d)において、前記第1の金属含有膜の上に前記拡散防止層を成膜してもよい。ここで、前記工程(a)は、前記半導体基板における前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に、前記第1の金属含有膜を形成する工程(a1)と、前記工程(a1)よりも後に、前記第2導電型MISFETの形成領域の上に形成された部分の前記第1の金属含有膜を選択的に除去する工程(a2)とを含み、前記工程(d)は、前記工程(a1)と前記工程(a2)との間に実施され、前記工程(d)において、前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に形成された前記第1の金属含有膜の上に前記拡散防止層を成膜し、前記工程(a2)において、前記第2導電型MISFETの形成領域の上に形成された部分の前記拡散防止層を選択的に除去してもよい。尚、前記拡散防止層を成膜により形成する場合、ピンホールの発生を防止する観点から、前記拡散防止層の厚さは1nm程度以上であることが好ましい。

【0034】

本発明に係る半導体装置の製造方法において、前記第1のゲート電極及び前記第2のゲート電極をゲートラスト法を用いて形成してもよい。

【発明の効果】

【0035】

本発明によると、さらなる微細化に対しても適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現することができる。

【図面の簡単な説明】

【0036】

【図1】図1(a)〜(f)は、第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図2】図2(a)〜(e)は、第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図3】図3(a)〜(c)は、第1の実施形態の変形例に係る半導体装置の製造方法の各工程を示す断面図である。

【図4】図4(a)〜(e)は、第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図5】図5(a)〜(d)は、第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図6】図6(a)〜(d)は、第2の実施形態の変形例に係る半導体装置の製造方法の各工程を示す断面図である。

【図7】図7(a)〜(e)は、従来の半導体装置の製造方法の各工程を説明する図である。

【図8】図8(a)〜(c)は、従来の半導体装置の製造方法の各工程を説明する図である。

【図9】図9は、従来の半導体装置の問題点を説明する図である。

【発明を実施するための形態】

【0037】

(第1の実施形態)

以下、本発明の第1の実施形態に係る半導体装置及びその製造方法について、図面を参照しながら説明する。図1(a)〜(f)及び図2(a)〜(e)は、第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【0038】

まず、図1(a)に示すように、例えばシリコン(Si)からなる基板100の上部に、例えばシャロウトレンチ分離(STI)構造を有する素子分離領域102を選択的に形成することにより、nチャネルMISFETの形成領域(以下、NMIS領域という)とpチャネルMISFETの形成領域(以下、PMIS領域という)とを区画する。続いて、例えばイオン注入法により、NMIS領域の基板100にp型ウェル領域103aを形成し、PMIS領域の基板100にn型ウェル領域103bを形成する。続いて、基板100の表面に対して、例えば公知の標準RCA洗浄及び希釈フッ酸(HF)洗浄を順次行った後、当該表面が清浄化された基板100に対して、例えば温度が600℃〜1000℃程度の酸素雰囲気で熱処理を行う。これにより、NMIS領域及びPMIS領域(つまりCMIS(Complementary Metal-Insulator-Semiconductor)デバイス形成領域)の基板100の上に、例えばシリコン酸化膜(SiO2 膜)からなる厚さ1〜3nm程度の絶縁膜104が形成される。ここで、例えばウェット処理を用いて、例えばケミカルシリコン酸化膜やISSG(In Situ Steam Generation)膜からなる絶縁膜104を形成してもよい。次に、絶縁膜104上に、所望のゲート電極高さに相当する例えば60〜80nm程度の厚さを持つ例えばアモルファスシリコンからなるダミーゲート電極膜105を堆積する。続いて、ダミーゲート電極膜105上に、リソグラフィ技術を用いて、例えばハードマスク材料やレジスト材料からなり且つNMIS領域及びPMIS領域それぞれのゲート電極形成領域を覆うマスクパターン106を形成する。

【0039】

次に、マスクパターン106を用いて、例えば塩素(Cl2 )ガス等によるドライエッチング又はウェットエッチングを行うことによって、図1(b)に示すように、ダミーゲート電極膜105をパターニングした後、マスクパターン106を除去する。これにより、NMIS領域には、nチャネル用ダミーゲート電極105aが形成されると共に、PMIS領域には、pチャネル用ダミーゲート電極105bが形成される。このとき、nチャネル用ダミーゲート電極105a及びpチャネル用ダミーゲート電極105bのそれぞれの外側に位置する部分の絶縁膜104が除去されて、基板100とnチャネル用ダミーゲート電極105aとの間にダミーゲート絶縁膜104aが形成されると共に、基板100とpチャネル用ダミーゲート電極105bとの間にダミーゲート絶縁膜104bが形成される。

【0040】

次に、nチャネル用ダミーゲート電極105a及びpチャネル用ダミーゲート電極105bのそれぞれの側面上にオフセットスペーサ(図示省略)を形成した後、図1(c)に示すように、例えばイオン注入法により、基板100の上部におけるnチャネル用ダミーゲート電極105aの両側にn型エクステンション領域107aを形成し、基板100の上部におけるpチャネル用ダミーゲート電極105bの両側にp型エクステンション領域107bを形成する。

【0041】

次に、図1(d)に示すように、nチャネル用ダミーゲート電極105a及びpチャネル用ダミーゲート電極105bのそれぞれの側面上に、前述のオフセットスペーサを介して、例えば窒化シリコンからなる絶縁性サイドウォールスペーサ108a及び108bを形成する。その後、例えばイオン注入法により、基板100の上部におけるnチャネル用ダミーゲート電極105a及び絶縁性サイドウォールスペーサ108aの両側にn型ソース/ドレイン領域109aを形成し、基板100の上部におけるpチャネル用ダミーゲート電極105b及び絶縁性サイドウォールスペーサ108bの両側にp型ソース/ドレイン領域109bを形成する。その後、例えば1000℃以上の温度で、n型エクステンション領域107a及びp型エクステンション領域107b並びにn型ソース/ドレイン領域109a及びp型ソース/ドレイン領域109bのそれぞれに注入された不純物に対して活性化アニールを行う。これにより、ダミーゲートトランジスタ構造が完成する。

【0042】

その後、図示は省略しているが、n型ソース/ドレイン領域109a及びp型ソース/ドレイン領域109bのそれぞれの表面部をシリサイド化した後、図1(e)に示すように、例えばプラズマCVD(Chemical Vapor Deposition )法により、基板100上の全面に亘って、例えば酸化シリコンを主成分とする層間絶縁膜110を堆積する。続いて、例えばCMP(Chemical Mechanical Polishing )法やドライエッチ法により、堆積した層間絶縁膜110に対して平坦化やエッチバックを行って、nチャネル用ダミーゲート電極105a及びpチャネル用ダミーゲート電極105bのそれぞれの上面を露出させる。

【0043】

次に、図1(f)に示すように、例えば塩素(Cl2 )ガスを主成分とるエッチングガスを用いたドライエッチング、又は例えばテトラエチル水酸化アンモニウム(TMAH)を用いたウェットエッチングにより、nチャネル用ダミーゲート電極105a及びpチャネル用ダミーゲート電極105bを除去する。続いて、例えばフッ酸(HF)を用いたウェットエッチングにより、シリコン酸化膜(SiO2 )からなるダミーゲート絶縁膜104a及び104bを除去する。これにより、ダミーゲート構造が除去されて、絶縁性サイドウォールスペーサ108aを側壁面とし且つ基板100を底面とするリセス111aが形成されると共に絶縁性サイドウォールスペーサ108bを側壁面とし且つ基板100を底面とするリセス111bが形成される。

【0044】

次に、図2(a)に示すように、例えばオゾン酸化を用いたウェット処理を行うことによって、リセス111a及び111bそれぞれの底面となる基板100上に、例えばシリコン酸化膜(SiO2 )からなる厚さ1nm程度の下地膜112a及び112bを形成する。ここで、例えば熱処理を用いて、例えばシリコン熱酸化膜やISSG膜からなる下地膜112a及び112bを形成してもよいが、下地膜112a及び112bの形成工程は前述のシリサイド化工程後に行われるので、熱処理温度は最大でも600℃を超えないようにする必要がある。次に、リセス111a及び111bそれぞれの底面上に形成された下地膜112a及び112bの上を含む基板100上の全面に、例えばALD(Atomic Layer Deposition ;原子層堆積)法を用いて、例えば絶縁性金属酸化物からなる厚さ3nm程度の高誘電率絶縁膜113を成膜する。具体的には、高誘電率絶縁膜113として、例えばHfO2 膜を成膜する場合、Hf原料としてHfCl4 を、酸化材としてH2 Oを用いると共に成膜温度を200〜400℃に設定し、HfCl4 の供給、パージ、H2 Oの供給及びパージのサイクルを繰り返し行うことによって、HfO2 を原子層レベルで成長させて、所望の厚さを持つHfO2 膜からなる高誘電率絶縁膜113を得ることができる。

【0045】

CMISトランジスタを構成するには、高誘電率絶縁膜113の形成後、PMIS領域及びNMIS領域のそれぞれにおいて、バンドエッジ(価電子帯及び伝導帯)付近の好適な仕事関数を持った異種のゲート電極用金属含有膜(pチャネル用金属含有膜及びnチャネル用金属含有膜)を形成する必要がある。ここで、pチャネル用金属含有膜及びnチャネル用金属含有膜のいずれを先に形成するかは、各ゲート電極材料の加工時の選択性等を考慮して決定すべきことであるが、以下、本実施形態では、pチャネル用金属含有膜を先に形成する場合を例として説明する。

【0046】

高誘電率絶縁膜113の形成後、図2(a)に示すように、高誘電率絶縁膜113上に、PMISFETに好適な仕事関数を持った材料、例えば、Pt、Pd若しくはRu等の貴金属、又はTi、Ta、W若しくはNiを含む金属窒化物からなる厚さ数nm〜十数nm程度のpチャネル用金属含有膜114を形成する。リセス111a及び111bが高アスペクト比を有する場合には、pチャネル用金属含有膜114の形成方法としては、例えば、コンフォーマルな堆積が可能なALD法若しくはCVD法、又はボトムカバレッジのよい(つまり高指向性の)PVD(Physical Vapor Deposition )法等を用いてもよい。

【0047】

続いて、図2(a)に示すように、pチャネル用金属含有膜114と、後述するnチャネル用金属含有膜117(図2(c)参照)との間の合金化反応を抑制するために、例えばpチャネル用金属含有膜114の表面部に対して改質処理を実施して拡散防止層115を形成する。拡散防止層115については後で詳細に述べる。その後、拡散防止層115上に、PMIS領域を覆うマスクパターン116を形成する。

【0048】

次に、マスクパターン116を用いて、図2(b)に示すように、NMIS領域に位置する部分のpチャネル用金属含有膜114及び拡散防止層115をエッチバックして除去し、その後、マスクパターン116を除去する。次に、図2(c)に示すように、NMIS領域に位置する部分の高誘電率絶縁膜113上、及びPMIS領域に残存する拡散防止層115上に、NMISFETに好適な仕事関数を持った材料、例えば、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなる厚さ数nm〜十数nm程度のnチャネル用金属含有膜117を形成する。リセス111a及び111bが高アスペクト比を有する場合には、nチャネル用金属含有膜117の形成方法としては、例えば、コンフォーマルな堆積が可能なALD法若しくはCVD法、又はボトムカバレッジのよい(つまり高指向性の)PVD法等を用いてもよい。

【0049】

次に、図2(d)に示すように、リセス111a及び111bの空隙部分が完全に埋まるように、nチャネル用金属含有膜117上に、例えばAl、Ti、W又はCu等の低抵抗の金属からなる導電膜118を形成する。

【0050】

最後に、図2(e)に示すように、リセス111a及び111bからはみ出た部分の導電膜118、nチャネル用金属含有膜117、拡散防止層115、pチャネル用金属含有膜114及び高誘電率絶縁膜113を、例えばCMP法による平坦化又はドライエッチング法によるエッチバックによって除去する。これにより、NMIS領域においては、下地膜112a及び高誘電率絶縁膜113aからなるゲート絶縁膜119aを挟んでリセス111aに埋め込まれており且つnチャネル用金属含有膜117a及び導電膜118aからなるnチャネル用ゲート電極120aが形成される。また、PMIS領域においては、下地膜112b及び高誘電率絶縁膜113bからなるゲート絶縁膜119bを挟んでリセス111bに埋め込まれており且つpチャネル用金属含有膜114b、拡散防止層115b、nチャネル用金属含有膜117b及び導電膜118bからなるpチャネル用ゲート電極120bが形成される。すなわち、ゲートラスト型トランジスタの基本構造が完成する。

【0051】

以上に説明したように、本実施形態によると、pチャネル用ゲート電極120bにおけるpチャネル用金属含有膜114bとnチャネル用金属含有膜117bとの間に拡散防止層115bが形成されている。このため、ゲート電極形成後のシンタ等の工程において熱負荷が加えられたとしても、pチャネル用金属含有膜114bとnチャネル用金属含有膜117bとの間の合金化反応を抑制して所望の仕事関数を得ることができるので、適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現できる。また、本実施形態ではゲートラスト法を用いているため、ソース/ドレイン領域形成に伴う不純物活性化熱処理をゲート電極形成前に実施できるので、ゲート電極形成後の工程における熱負荷を低減でき、それによって、前述の合金化反応をより一層抑制することができる。

【0052】

尚、本実施形態において、拡散防止層115は、ゲート電極抵抗の低減の観点からは、導電層であることが好ましいが、トンネル効果を生じる極薄(例えば2nm程度以下)の絶縁層であってもよい。また、拡散防止層115が導電層であっても、微細化の観点(特に本実施形態のようにゲートラスト法を用いる場合)からは、拡散防止層115の厚さは5nm程度以下であることが好ましく、ゲート電極抵抗の低減の観点からは、拡散防止層115の厚さは2nm程度以下であることがより好ましい。特に、20nm世代以降を想定した場合、拡散防止層115の厚さのみならず、実効仕事関数を決定するpチャネル用金属含有膜114及びnチャネル用金属含有膜117の厚さについても、数nm以下程度に抑制することが望ましい。

【0053】

また、本実施形態のように、pチャネル用金属含有膜114がPt、Pd若しくはRu等の貴金属、又はTi、Ta、W若しくはNiを含む金属窒化物からなり、nチャネル用金属含有膜117がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなる場合、拡散防止層115は、例えばTi又はTaを含む酸化物から構成されていてもよい。或いは、pチャネル用金属含有膜114がPt、Pd若しくはRu等の貴金属、又はW若しくはNiを含む金属窒化物からなる場合、拡散防止層115は、例えばTi又はTaを含む金属窒化物から構成されていてもよい。或いは、pチャネル用金属含有膜114がPt、Pd若しくはRu等の貴金属からなる場合、拡散防止層115は、Pt、Pd若しくはRu等の貴金属の酸化物、窒化物又は酸窒化物から構成されていてもよい。或いは、pチャネル用金属含有膜114がTi、Ta、W又はNiを含む金属窒化物からなる場合、拡散防止層115は、Ti、Ta、W又はNiを含む金属酸窒化物から構成されていてもよい。

【0054】

また、本実施形態において、拡散防止層115を形成するために、例えばpチャネル用金属含有膜114の表面改質を行ってもよい。表面改質の具体的方法としては、簡単には、拡散防止効果のある元素、例えば窒素及び酸素の少なくとも一方を含む雰囲気中で熱処理を行う方法がある。このような方法を用いると、pチャネル用金属含有膜114を構成する材料の酸化物、窒化物又は酸窒化物からなる拡散防止層115が形成される。尚、窒素及び酸素の少なくとも一方を含む雰囲気中での熱処理に代えて、例えば窒素及び酸素の少なくとも一方を含むガスからなるプラズマにpチャネル用金属含有膜114の表面を曝してもよい。このようなプラズマ処理を行う場合、処理深さの点で、図2(c)に示すnチャネル用金属含有膜117の形成前に行うのが効果的である。

【0055】

また、本実施形態において、pチャネル用金属含有膜114の表面改質を用いずに、pチャネル用金属含有膜114上に拡散防止層115を成膜してもよい。例えばTi又はTa等からなる高融点金属ターゲットを用いて、窒素及び酸素の少なくとも一方を含む雰囲気中で反応性スパッタを行うことによって、拡散防止層115を成膜してもよい。拡散防止層115を成膜する場合、ピンホールの発生を防止する観点から、拡散防止層115の厚さは1nm程度以上であることが好ましい。

【0056】

また、本実施形態においては、図2(c)に示すnチャネル用金属含有膜117の形成前に拡散防止層115を形成したが、これに代えて、nチャネル用金属含有膜117の形成後に、例えば窒素及び酸素の少なくとも一方のイオン注入を行うことにより、pチャネル用金属含有膜114とnチャネル用金属含有膜117との積層界面近傍を改質して拡散防止層115を形成してもよい。この場合、pチャネル用金属含有膜114の上面近傍(つまり表面部)のみならず、nチャネル用金属含有膜117の下面近傍にも拡散防止層115を形成することができるので、拡散防止効果を高めるのに効果的である。

【0057】

また、本実施形態においては、図2(a)〜(c)に示すように、CMISデバイス形成領域全体にpチャネル用金属含有膜114を形成した後、pチャネル用金属含有膜114上に拡散防止層115を形成し、その後、NMIS領域に位置する部分のpチャネル用金属含有膜114及び拡散防止層115をエッチバックして選択的に除去した。しかし、これに代えて、図3(a)〜(c)に示すように、CMISデバイス形成領域全体にpチャネル用金属含有膜114を形成した後、PMIS領域を覆うマスクパターン116を用いて、NMIS領域に位置する部分のpチャネル用金属含有膜114をエッチバックして選択的に除去し、その後、残存するpチャネル用金属含有膜114上に拡散防止層115を形成してもよい。尚、pチャネル用金属含有膜114の選択的除去と拡散防止層115の形成との前後関係については、各ゲート電極材料の組み合わせによって決まる選択性等に応じて最適のシーケンスを選択すればよい。具体的には、図2(a)〜(c)に示すシーケンスの場合、pチャネル用金属含有膜114及び拡散防止層115のエッチングは複雑になるものの、NMIS領域に位置する部分の高誘電率絶縁膜113に対するダメージは、pチャネル用金属含有膜114及び拡散防止層115のエッチングによる1回だけ生じる。一方、図3(a)〜(c)に示すシーケンスの場合、pチャネル用金属含有膜114のエッチングは簡単になるものの、NMIS領域に位置する部分の高誘電率絶縁膜113に対するダメージは、pチャネル用金属含有膜114のエッチング、及び拡散防止層115の形成による2回生じる。

【0058】

また、本実施形態においては、pチャネル用金属含有膜114を先に形成したため、pチャネル用ゲート電極120bが、pチャネル用金属含有膜114bとnチャネル用金属含有膜117bとの積層構造を持つので、pチャネル用ゲート電極120bにおけるpチャネル用金属含有膜114bとnチャネル用金属含有膜117bとの間に拡散防止層115bを形成した。しかし、これに代えて、nチャネル用金属含有膜を先に形成することにより、nチャネル用ゲート電極が、nチャネル用金属含有膜とpチャネル用金属含有膜との積層構造を持ち、それに対応して、nチャネル用ゲート電極におけるnチャネル用金属含有膜とpチャネル用金属含有膜との間に拡散防止層を形成してもよい。このとき、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなり、pチャネル用金属含有膜がPt、Pd若しくはRu等の貴金属、又はTi、Ta、W若しくはNiを含む金属窒化物からなる場合、拡散防止層は、例えばTi又はTaを含む酸化物から構成されていてもよい。或いは、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物(但しTi又はTaの窒化物を除く)若しくは炭化物からなる場合、拡散防止層は、例えばTi又はTaを含む金属窒化物から構成されていてもよい。或いは、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の炭化物からなる場合、拡散防止層は、nチャネル用金属含有膜を構成する材料の酸化物、窒化物又は酸窒化物から構成されていてもよい。或いは、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属の窒化物、又は前記金属群の中から選ばれた2つ以上の金属の合金の窒化物からなる場合、拡散防止層は、nチャネル用金属含有膜を構成する材料の酸化物から構成されていてもよい。

【0059】

また、本実施形態において、pチャネル用金属含有膜114及びnチャネル用金属含有膜117はそれぞれ仕事関数調整層を含んでいても良い。また、本実施形態において、nチャネル用ゲート電極120aをnチャネル用金属含有膜117a及び導電膜118aから構成し、pチャネル用ゲート電極120bをpチャネル用金属含有膜114b、拡散防止層115b、nチャネル用金属含有膜117b及び導電膜118bから構成したが、リセス111a及び111bの寸法によっては、少なくともpチャネル用ゲート電極120bが導電膜118を含まない場合もあり得る。

【0060】

また、本実施形態において、pチャネル用ゲート電極120bにおけるpチャネル用金属含有膜114bとnチャネル用金属含有膜117bとの間の合金化反応を防止するために、pチャネル用金属含有膜114bとnチャネル用金属含有膜117bとの間に拡散防止層115bを形成した。しかし、nチャネル用ゲート電極120aにおけるnチャネル用金属含有膜117aと導電膜118aとの間でも合金化反応が生じる恐れがある場合には、nチャネル用金属含有膜117aと導電膜118aとの間に拡散防止層を形成してもよいことは言うまでもない。

【0061】

(第2の実施形態)

以下、本発明の第2の実施形態に係る半導体装置及びその製造方法について、図面を参照しながら説明する。尚、第1の実施形態1ではゲートラスト法を用いてMISFET形成を行ったのに対して、本実施形態ではゲートファースト法を用いてMISFET形成を行う。

【0062】

図4(a)〜(e)及び図5(a)〜(d)は、第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【0063】

まず、図4(a)に示すように、例えばシリコン(Si)からなる基板200の上部に、例えばシャロウトレンチ分離(STI)構造を有する素子分離領域201を選択的に形成することにより、nチャネルMISFETの形成領域(以下、NMIS領域という)とpチャネルMISFETの形成領域(以下、PMIS領域という)とを区画する。続いて、例えばイオン注入法により、NMIS領域の基板200にp型ウェル領域202aを形成し、PMIS領域の基板200にn型ウェル領域202bを形成する。続いて、基板200の表面に対して、例えば公知の標準RCA洗浄及び希釈フッ酸(HF)洗浄を順次行った後、当該表面が清浄化された基板200に対して、例えば温度が600℃〜1000℃程度の酸素雰囲気で熱処理を行う。これにより、NMIS領域及びPMIS領域(つまりCMISデバイス形成領域)の基板200の上に、例えばシリコン酸化膜(SiO2 膜)からなる厚さ1nm程度の下地膜203が形成される。ここで、例えばウェット処理を用いて、例えばケミカルシリコン酸化膜やISSG膜からなる下地膜203を形成してもよい。次に、下地膜203上に、例えばALD法を用いて、例えば絶縁性金属酸化物からなる厚さ3nm程度の高誘電率絶縁膜204を成膜する。具体的には、高誘電率絶縁膜204として、例えばHfO2 膜を成膜する場合、Hf原料としてHfCl4 を、酸化材としてH2 Oを用いると共に成膜温度を200〜400℃に設定し、HfCl4 の供給、パージ、H2 Oの供給及びパージのサイクルを繰り返し行うことによって、HfO2 を原子層レベルで成長させて、所望の厚さを持つHfO2 膜からなる高誘電率絶縁膜204を得ることができる。

【0064】

CMISトランジスタを構成するには、高誘電率絶縁膜204の形成後、PMIS領域及びNMIS領域のそれぞれにおいて、バンドエッジ(価電子帯及び伝導帯)付近の好適な仕事関数を持った異種のゲート電極用金属含有膜(pチャネル用金属含有膜及びnチャネル用金属含有膜)を形成する必要がある。ここで、pチャネル用金属含有膜及びnチャネル用金属含有膜のいずれを先に形成するかは、各ゲート電極材料の加工時の選択性等を考慮して決定すべきことであるが、以下、本実施形態では、pチャネル用金属含有膜を先に形成する場合を例として説明する。

【0065】

高誘電率絶縁膜204の形成後、図4(a)に示すように、高誘電率絶縁膜204上に、PMISFETに好適な仕事関数を持った材料、例えば、Pt、Pd若しくはRu等の貴金属、又はTi、Ta、W若しくはNiを含む金属窒化物からなる厚さ数nm〜十数nm程度のpチャネル用金属含有膜205を形成する。

【0066】

次に、図4(b)に示すように、pチャネル用金属含有膜205上に、PMIS領域を覆うマスクパターン206を形成した後、当該マスクパターン206を用いて、図4(c)に示すように、NMIS領域に位置する部分のpチャネル用金属含有膜205をエッチバックして除去し、その後、マスクパターン206を除去する。

【0067】

続いて、図4(d)に示すように、pチャネル用金属含有膜205と、後述するnチャネル用金属含有膜208(図4(e)参照)との間の合金化反応(特に後述するソース/ドレイン領域形成に伴う不純物活性化熱処理等の高温プロセスに起因する合金化反応)を抑制するために、例えばpチャネル用金属含有膜205の表面部に対して改質処理を実施して拡散防止層207を形成する。拡散防止層207については後で詳細に述べる。

【0068】

次に、図4(e)に示すように、NMIS領域に位置する部分の高誘電率絶縁膜204上、及びPMIS領域に位置する拡散防止層207上に、NMISFETに好適な仕事関数を持った材料、例えば、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなる厚さ数nm〜十数nm程度のnチャネル用金属含有膜208を形成する。

【0069】

次に、ゲート電極抵抗値を所望の値に下げるために、図5(a)に示すように、nチャネル用金属含有膜208上に、例えば、導電性ポリシリコン、又はTi、Ta、W若しくはNi等の金属若しくは当該金属の窒化物等からなる厚さ数十nm程度の導電膜209を形成する。続いて、例えばリソグラフィ技術により、導電膜209上に、NMIS領域及びPMIS領域それぞれのゲート電極形成領域を覆うマスクパターン210を形成する。

【0070】

次に、マスクパターン210を用いて、例えば塩素(Cl2 )ガスを主成分とするエッチングガス等によるドライエッチング又はウェットエッチングを行うことによって、図5(b)に示すように、導電膜209、nチャネル用金属含有膜208、拡散防止層207及びpチャネル用金属含有膜205を順次パターニングした後、マスクパターン210を除去する。これにより、NMIS領域においては、nチャネル用金属含有膜208a及び導電膜209aからなるnチャネル用ゲート電極212aが形成されると共に、PMIS領域においては、pチャネル用金属含有膜205b、拡散防止層207b、nチャネル用金属含有膜208b及び導電膜209bからなるpチャネル用ゲート電極212bが形成される。このとき、nチャネル用ゲート電極212a及びpチャネル用ゲート電極212bのそれぞれの外側に位置する部分の下地膜203及び高誘電率絶縁膜204が除去されて、基板200とnチャネル用ゲート電極212aとの間に、下地膜203a及び高誘電率絶縁膜204aからなるゲート絶縁膜211aが形成されると共に、基板200とpチャネル用ゲート電極212bとの間に、下地膜203b及び高誘電率絶縁膜204bからなるゲート絶縁膜211bが形成される。

【0071】

尚、図5(b)に示すゲートパターニング工程における加工性及び選択性を良好に保つためには、pチャネル用金属含有膜205、拡散防止層207及びnチャネル用金属含有膜208のそれぞれの厚さを、所望の実効仕事関数を実現できる最低限の厚さに抑えることが望ましい。特に、20nm世代以降を想定した場合、実効仕事関数を決定するpチャネル用金属含有膜205、拡散防止層207及びnチャネル用金属含有膜208のそれぞれの厚さを数nm以下程度に抑制することが望ましい。

【0072】

次に、nチャネル用ゲート電極212a及びpチャネル用ゲート電極212bのそれぞれの側面上にオフセットスペーサ(図示省略)を形成した後、図5(c)に示すように、例えばイオン注入法により、基板200の上部におけるnチャネル用ゲート電極212aの両側にn型エクステンション領域213aを形成し、基板200の上部におけるpチャネル用ゲート電極212bの両側にp型エクステンション領域213bを形成する。

【0073】

次に、図5(d)に示すように、nチャネル用ゲート電極212a及びpチャネル用ゲート電極212bのそれぞれの側面上に、前述のオフセットスペーサを介して、例えば窒化シリコンからなる絶縁性サイドウォールスペーサ214a及び214bを形成する。その後、例えばイオン注入法により、基板200の上部におけるnチャネル用ゲート電極212a及び絶縁性サイドウォールスペーサ214aの両側にn型ソース/ドレイン領域215aを形成し、基板200の上部におけるpチャネル用ゲート電極212b及び絶縁性サイドウォールスペーサ214bの両側にp型ソース/ドレイン領域215bを形成する。その後、例えば1000℃以上の温度で、n型エクステンション領域213a及びp型エクステンション領域213b並びにn型ソース/ドレイン領域215a及びp型ソース/ドレイン領域215bのそれぞれに注入された不純物に対して活性化アニールを行う。

【0074】

その後、図示は省略しているが、n型ソース/ドレイン領域215a及びp型ソース/ドレイン領域215bのそれぞれの表面部をシリサイド化することによって、ゲートファースト型トランジスタの基本構造が完成する。

【0075】

以上に説明したように、本実施形態によると、pチャネル用ゲート電極212bにおけるpチャネル用金属含有膜205bとnチャネル用金属含有膜208bとの間に拡散防止層207bが形成されている。このため、ゲート電極形成後のソース/ドレイン領域形成に伴う不純物活性化熱処理等の工程において例えば1000℃以上の熱負荷が加えられたとしても、pチャネル用金属含有膜205bとnチャネル用金属含有膜208bとの間の合金化反応を抑制して所望の仕事関数を得ることができるので、適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現できる。

【0076】

尚、本実施形態において、拡散防止層207は、ゲート電極抵抗の低減の観点からは、導電層であることが好ましいが、トンネル効果を生じる極薄(例えば2nm程度以下)の絶縁層であってもよい。また、拡散防止層207が導電層であっても、微細化の観点からは、拡散防止層207の厚さは5nm程度以下であることが好ましく、ゲート電極抵抗の低減の観点からは、拡散防止層207の厚さは2nm程度以下であることがより好ましい。特に、20nm世代以降を想定した場合、拡散防止層207の厚さのみならず、実効仕事関数を決定するpチャネル用金属含有膜205及びnチャネル用金属含有膜208の厚さについても、数nm以下程度に抑制することが望ましい。

【0077】

また、本実施形態のように、pチャネル用金属含有膜205がPt、Pd若しくはRu等の貴金属、又はTi、Ta、W若しくはNiを含む金属窒化物からなり、nチャネル用金属含有膜208がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなる場合、拡散防止層207は、例えばTi又はTaを含む酸化物から構成されていてもよい。或いは、pチャネル用金属含有膜205がPt、Pd若しくはRu等の貴金属、又はW若しくはNiを含む金属窒化物からなる場合、拡散防止層207は、例えばTi又はTaを含む金属窒化物から構成されていてもよい。或いは、pチャネル用金属含有膜205がPt、Pd若しくはRu等の貴金属からなる場合、拡散防止層207は、Pt、Pd若しくはRu等の貴金属の酸化物、窒化物又は酸窒化物から構成されていてもよい。或いは、pチャネル用金属含有膜205がTi、Ta、W又はNiを含む金属窒化物からなる場合、拡散防止層207は、Ti、Ta、W又はNiを含む金属酸窒化物から構成されていてもよい。

【0078】

また、本実施形態において、拡散防止層207を形成するために、例えばpチャネル用金属含有膜205の表面改質を行ってもよい。表面改質の具体的方法としては、簡単には、拡散防止効果のある元素、例えば窒素及び酸素の少なくとも一方を含む雰囲気中で熱処理を行う方法がある。このような方法を用いると、pチャネル用金属含有膜205を構成する材料の酸化物、窒化物又は酸窒化物からなる拡散防止層207が形成される。尚、窒素及び酸素の少なくとも一方を含む雰囲気中での熱処理に代えて、例えば窒素及び酸素の少なくとも一方を含むガスからなるプラズマにpチャネル用金属含有膜205の表面を曝してもよい。このようなプラズマ処理を行う場合、処理深さの点で、図4(e)に示すnチャネル用金属含有膜208の形成前に行うのが効果的である。

【0079】

また、本実施形態において、pチャネル用金属含有膜205の表面改質を用いずに、pチャネル用金属含有膜205上に拡散防止層207を成膜してもよい。例えばTi又はTa等からなる高融点金属ターゲットを用いて、窒素及び酸素の少なくとも一方を含む雰囲気中で反応性スパッタを行うことによって、拡散防止層207を成膜してもよい。拡散防止層207を成膜する場合、ピンホールの発生を防止する観点から、拡散防止層207の厚さは1nm程度以上であることが好ましい。

【0080】

また、本実施形態においては、図4(e)に示すnチャネル用金属含有膜208の形成前に拡散防止層207を形成したが、これに代えて、nチャネル用金属含有膜208の形成後に、例えば窒素及び酸素の少なくとも一方のイオン注入を行うことにより、pチャネル用金属含有膜205とnチャネル用金属含有膜208との積層界面近傍を改質して拡散防止層207を形成してもよい。この場合、pチャネル用金属含有膜205の上面近傍(つまり表面部)のみならず、nチャネル用金属含有膜208の下面近傍にも拡散防止層207を形成することができるので、拡散防止効果を高めるのに効果的である。

【0081】

また、本実施形態においては、図4(a)〜(d)に示すように、CMISデバイス形成領域全体にpチャネル用金属含有膜205を形成した後、PMIS領域を覆うマスクパターン206を用いて、NMIS領域に位置する部分のpチャネル用金属含有膜205をエッチバックして選択的に除去し、その後、残存するpチャネル用金属含有膜205上に拡散防止層207を形成した。しかし、これに代えて、図6(a)〜(d)に示すように、CMISデバイス形成領域全体にpチャネル用金属含有膜205を形成した後、pチャネル用金属含有膜205上に拡散防止層207を形成し、その後、NMIS領域に位置する部分のpチャネル用金属含有膜205及び拡散防止層207をエッチバックして選択的に除去してもよい。尚、pチャネル用金属含有膜205の選択的除去と拡散防止層207の形成との前後関係については、各ゲート電極材料の組み合わせによって決まる選択性等に応じて最適のシーケンスを選択すればよい。具体的には、図4(a)〜(d)に示すシーケンスの場合、pチャネル用金属含有膜205のエッチングは簡単になるものの、NMIS領域に位置する部分の高誘電率絶縁膜204に対するダメージは、pチャネル用金属含有膜205のエッチング、及び拡散防止層207の形成による2回生じる。一方、図6(a)〜(d)に示すシーケンスの場合、pチャネル用金属含有膜205及び拡散防止層207のエッチングは複雑になるものの、NMIS領域に位置する部分の高誘電率絶縁膜204に対するダメージは、pチャネル用金属含有膜205及び拡散防止層207のエッチングによる1回だけ生じる。

【0082】

また、本実施形態においては、pチャネル用金属含有膜205を先に形成したため、pチャネル用ゲート電極212bが、pチャネル用金属含有膜205bとnチャネル用金属含有膜208bとの積層構造を持つので、pチャネル用ゲート電極212bにおけるpチャネル用金属含有膜205bとnチャネル用金属含有膜208bとの間に拡散防止層207bを形成した。しかし、これに代えて、nチャネル用金属含有膜を先に形成することにより、nチャネル用ゲート電極が、nチャネル用金属含有膜とpチャネル用金属含有膜との積層構造を持ち、それに対応して、nチャネル用ゲート電極におけるnチャネル用金属含有膜とpチャネル用金属含有膜との間に拡散防止層を形成してもよい。このとき、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなり、pチャネル用金属含有膜がPt、Pd若しくはRu等の貴金属、又はTi、Ta、W若しくはNiを含む金属窒化物からなる場合、拡散防止層は、例えばTi又はTaを含む酸化物から構成されていてもよい。或いは、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物(但しTi又はTaの窒化物を除く)若しくは炭化物からなる場合、拡散防止層は、例えばTi又はTaを含む金属窒化物から構成されていてもよい。或いは、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の炭化物からなる場合、拡散防止層は、nチャネル用金属含有膜を構成する材料の酸化物、窒化物又は酸窒化物から構成されていてもよい。或いは、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属の窒化物、又は前記金属群の中から選ばれた2つ以上の金属の合金の窒化物からなる場合、拡散防止層は、nチャネル用金属含有膜を構成する材料の酸化物から構成されていてもよい。

【0083】

また、本実施形態において、pチャネル用金属含有膜205及びnチャネル用金属含有膜208はそれぞれ仕事関数調整層を含んでいても良い。また、本実施形態において、nチャネル用ゲート電極212aをnチャネル用金属含有膜208a及び導電膜209aから構成し、pチャネル用ゲート電極212bをpチャネル用金属含有膜205b、拡散防止層207b、nチャネル用金属含有膜208b及び導電膜209bから構成したが、少なくともpチャネル用ゲート電極212bが導電膜209を含まない場合もあり得る。

【0084】

また、本実施形態において、pチャネル用ゲート電極212bにおけるpチャネル用金属含有膜205bとnチャネル用金属含有膜208bとの間の合金化反応を防止するために、pチャネル用金属含有膜205bとnチャネル用金属含有膜207bとの間に拡散防止層207bを形成した。しかし、nチャネル用ゲート電極212aにおけるnチャネル用金属含有膜208aと導電膜209aとの間でも合金化反応が生じる恐れがある場合には、nチャネル用金属含有膜208aと導電膜209aとの間に拡散防止層を形成してもよいことは言うまでもない。

【産業上の利用可能性】

【0085】

本発明は、仕事関数を決定する金属含有膜を含むゲート電極を有する半導体装置において、異種のゲート電極用金属含有膜の積層構造における界面合金化反応を抑制して所望の仕事関数を得ることを可能とするものであり、適切な閾値電圧を有するCMIS型の半導体装置等の実現に有用である。

【符号の説明】

【0086】

100 基板

102 素子分離領域

103a p型ウェル領域

103b n型ウェル領域

104 絶縁膜

104a、104b ダミーゲート絶縁膜

105 ダミーゲート電極膜

105a nチャネル用ダミーゲート電極

105b pチャネル用ダミーゲート電極

106 マスクパターン

107a n型エクステンション領域

107b p型エクステンション領域

108a、108b 絶縁性サイドウォールスペーサ

109a n型ソース/ドレイン領域

109b p型ソース/ドレイン領域

110 層間絶縁膜

111a、111b リセス

112a、112b 下地膜

113、113a、113b 高誘電率絶縁膜

114、114b pチャネル用金属含有膜

115、115b 拡散防止層

116 マスクパターン

117、117a、117b nチャネル用金属含有膜

118、118a、118b 導電膜

119a、119b ゲート絶縁膜

120a nチャネル用ゲート電極

120b pチャネル用ゲート電極

200 基板

201 素子分離領域

202a p型ウェル領域

202b n型ウェル領域

203、203a、203b 下地膜

204、204a、204b 高誘電率絶縁膜

205、205b pチャネル用金属含有膜

206 マスクパターン

207、207b 拡散防止層

208、208a、208b nチャネル用金属含有膜

209、209a、209b 導電膜

210 マスクパターン

211a、211b ゲート絶縁膜

212a nチャネル用ゲート電極

212b pチャネル用ゲート電極

213a n型エクステンション領域

213b p型エクステンション領域

214a、214b 絶縁性サイドウォールスペーサ

215a n型ソース/ドレイン領域

215b p型ソース/ドレイン領域

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、金属含有膜を含むゲート電極を有する半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、半導体集積回路装置の高集積化、高機能化及び高速化に伴って、金属−絶縁物−半導体電界効果トランジスタ(MISFET(Metal-Insulator-Semiconductor Field-Effect Transistor ))の微細化が進められている。

【0003】

一方、MISFETの微細化に伴い、ゲート絶縁膜の薄膜化を進めると、トンネル現象に起因するゲートリーク電流の増大、又はポリシリコンゲート電極の空乏化等の影響が顕著になり、オン電流の確保、ひいてはMISFETの動作速度の維持又は向上が難しくなってくる。

【0004】

この問題を解決するために、ゲート絶縁膜として、従来のシリコン酸化膜に代えて、ハフニウム酸化膜(HfO2 )等のより誘電率が高い絶縁膜(高誘電率絶縁膜(high-k膜))を用いると共に、ゲート電極における少なくともゲート絶縁膜と接する部分の材料をポリシリコンから金属含有材料に置き換えることが検討されている。これにより、ゲート絶縁膜の物理的な厚さを大きくしながら、酸化膜換算膜厚(EOT(Equivalent Oxide Thickness)を低減すること、及び、ゲート電極の空乏化を抑えて反転層厚さ(Tinv)を低減すること等が期待される。すなわち、ゲート絶縁膜の電気的な厚さを薄くすることが期待される。ここで、酸化膜換算膜厚EOTとは、酸化シリコンと異なる比誘電率を持つ誘電体膜の膜厚を酸化シリコンの比誘電率で換算した膜厚値をいう。

【0005】

前述の高誘電率ゲート絶縁膜及び金属含有ゲート電極を用いたトランジスタの実現において最も重要な課題の1つは適正な閾値電圧Vtを得ることである。そのためには、pチャネルMISFETのゲート電極構造においてはSiの価電子帯(5.15eV)に近い仕事関数を有するpチャネル用金属含有膜を用いると共にnチャネルMISFETのゲート電極構造においてはSiの伝導帯(4.05eV)に近い仕事関数を有するnチャネル用金属含有膜を用いた構造、つまり、デュアルメタルゲート構造を実現する必要がある。

【0006】

以下、従来のデュアルメタルゲート構造の一例として、特許文献1に開示されている構造について説明する。図7(a)〜(e)及び図8(a)〜(c)は、特許文献1に開示されている従来の半導体装置の製造方法の各工程を示す図である。

【0007】

まず、図7(a)に示すように、シリコン(Si)からなる半導体基板1の上部に、シャロウトレンチ分離(STI)からなる素子分離領域2を選択的に形成する。続いて、イオン注入法により、nチャネルMISFETの形成領域(以下、NMIS領域という)にはp型ウェル領域3aを形成し、pチャネルMISFETの形成領域(以下、PMIS領域という)にはn型ウェル領域3bを形成する。続いて、半導体基板1の表面上に下地膜4を介して高誘電率絶縁膜5を形成した後、高誘電率絶縁膜5上にpチャネル用金属含有膜6を形成する。

【0008】

次に、図7(b)に示すように、PMIS領域を覆うマスクパターン7を形成した後、マスクパターン7を用いて、図7(c)に示すように、NMIS領域に位置する部分のpチャネル用金属含有膜6をエッチバックして除去し、その後、マスクパターン7を除去する。次に、図7(d)に示すように、NMIS領域に位置する部分の高誘電率絶縁膜5上、及びPMIS領域に残存するpチャネル用金属含有膜6上に、nチャネル用金属含有膜8を形成する。

【0009】

次に、図7(e)に示すように、nチャネル用金属含有膜8上に導電膜9を形成した後、NMIS領域及びPMIS領域それぞれのゲート電極形成領域を覆うマスクパターン10を形成する。次に、マスクパターン10を用いたドライエッチングによって、図8(a)に示すように、導電膜9、nチャネル用金属含有膜8及びpチャネル用金属含有膜6を順次パターニングした後、マスクパターン10を除去する。これにより、NMIS領域には、nチャネル用金属含有膜8a及び導電膜9aからなるnチャネル用ゲート電極12aが形成されると共に、PMIS領域には、pチャネル用金属含有膜6b、nチャネル用金属含有膜8b及び導電膜9bからなるpチャネル用ゲート電極12bが形成される。このとき、nチャネル用ゲート電極12a及びpチャネル用ゲート電極12bのそれぞれの外側に位置する部分の下地膜4及び高誘電率絶縁膜5が除去されて、半導体基板1とnチャネル用ゲート電極12aとの間に、下地膜4a及び高誘電率絶縁膜5aからなるゲート絶縁膜11aが形成されると共に、半導体基板1とpチャネル用ゲート電極12bとの間に、下地膜4b及び高誘電率絶縁膜5bからなるゲート絶縁膜11bが形成される。

【0010】

次に、図8(b)に示すように、イオン注入法により、半導体基板1におけるnチャネル用ゲート電極12aの両側にn型エクステンション領域13aを形成し、半導体基板1におけるpチャネル用ゲート電極12bの両側にp型エクステンション領域13bを形成する。次に、図8(c)に示すように、nチャネル用ゲート電極12a及びpチャネル用ゲート電極12bのそれぞれの側面上に、絶縁性サイドウォールスペーサ14a及び14bを形成した後、イオン注入法により、半導体基板1におけるnチャネル用ゲート電極12a及び絶縁性サイドウォールスペーサ14aの両側にn型ソース/ドレイン領域15aを形成し、半導体基板1におけるpチャネル用ゲート電極12b及び絶縁性サイドウォールスペーサ14bの両側にp型ソース/ドレイン領域15bを形成する。

【0011】

以上に説明したように、従来のデュアルメタルゲート構造を有する半導体装置によると、NMIS領域においては高誘電率ゲート絶縁膜上にnチャネル用金属含有膜を有するゲート電極が形成されており、PMIS領域においては高誘電率ゲート絶縁膜上にpチャネル用金属含有膜を有するゲート電極が形成されている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】米国特許第7625791号明細書

【特許文献2】米国特許第6794234号明細書

【非特許文献】

【0013】

【非特許文献1】K.Mistry他、A 45nm Logic Technology with High-k+Metal gate Transitors,Strained Silicon,9 Cu Interconnect Layers,193nm Dry Patterning,and 100% Pb-free Packaging、IEDM2007、p.247-250

【発明の概要】

【発明が解決しようとする課題】

【0014】

しかしながら、従来のデュアルメタルゲート構造を有する半導体装置においては、微細化に伴い、適正な閾値電圧Vtが得られなくなるという問題が生じる。

【0015】

前記に鑑み、本発明は、さらなる微細化に対しても適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現することを目的とする。

【課題を解決するための手段】

【0016】

前述の目的を達成するために、本願発明者が、従来のデュアルメタルゲート構造において微細化に伴って適正な閾値電圧Vtが得られなくなる原因について検討したところ、以下のような知見を得た。

【0017】

図7(a)〜(e)及び図8(a)〜(c)に示す従来技術によると、PMISFETのゲート電極用金属含有膜(pチャネル用金属含有膜6)については、ゲートパターニング前に、NMIS領域に形成されている部分をエッチバックにより除去している。それに対して、NMISFETのゲート電極用金属含有膜(nチャネル用金属含有膜8)については、プロセスダメージの軽減やプロセスの簡便化等を目的として、ゲートパターニングまで、PMIS領域に形成されている部分を残存させている。従って、PMISFETのゲート電極(pチャネル用ゲート電極12b)は、pチャネル用金属含有膜6bと、nチャネル用金属含有膜8bとの積層構造を有することになる。ここで、前述の従来技術においては、pチャネル用ゲート電極12bの実効仕事関数が、ゲート絶縁膜11bのより近くに位置しているpチャネル用金属含有膜6bによって実質的に決定されること、言い換えると、pチャネル用ゲート電極12bの実効仕事関数に対して、ゲート絶縁膜11bから離れて位置しているnチャネル用金属含有膜8bが実質的な影響を及ぼさないことを前提としている。尚、「実効仕事関数」とは、MISFETの電気特性から求められる仕事関数であって、真空準位と金属のエネルギー準位との差を示す物性的な仕事関数に絶縁膜中の準位などの影響を加味したものを意味する。

【0018】

しかしながら、実際には、例えばゲートパターニング後における不純物(ソース/ドレイン領域に含まれる不純物)の活性化熱処理等の工程においてゲート電極構造が1000℃以上の高温プロセスに曝される。その結果、図9に示すように、pチャネル用ゲート電極12bにおいて、pチャネル用金属含有膜6bとnチャネル用金属含有膜8bとの積層構造中で界面反応が生じて合金化層(合金化層20)が形成されてしまう恐れがある。この合金化層の生成の程度によっては、下層に位置するゲート電極用金属含有膜(pチャネル用金属含有膜6b)の実効仕事関数が所望値から外れてしまう。その結果、従来のデュアルメタルゲート構造を有する半導体装置において、適正な閾値電圧Vtが得られなくなってしまう。

【0019】

尚、図7(a)〜(e)及び図8(a)〜(c)に示す従来技術においては、pチャネル用金属含有膜6bの厚さを十分に大きくすれば、前述の合金化層(合金化層20)の影響を抑制できるものの、この場合には、pチャネル用金属含有膜6bの選択的エッチバック及びゲートパターニングにおけるプロセス負荷が増大するという別の問題が生じる。

【0020】

また、特許文献2には、特許文献1に類似した異種のゲート電極用金属含有膜の積層構造における界面合金化反応を利用して、合金化反応後の仕事関数を利用する構成が提案されている。しかしながら、特許文献2に開示されている技術においては、合金化反応後の仕事関数を利用できる金属材料の選択肢が少ないという実用上の問題がある上に、合金化反応自体の制御が困難であるために、特許文献1と同様の問題を生じる恐れがある。

【0021】

また、非特許文献1には、特許文献1及び2のようなゲートファースト法に代えて、ゲートラスト法を用いたデュアルメタルゲート構造形成が開示されている。ゲートラスト法を用いた場合、ゲート電極の形成前にソース/ドレイン領域を形成できるため、ゲート電極形成後の工程における主な熱負荷は、420〜430℃程度のシンタの熱負荷位になるので、特許文献1及び2のようにゲートファースト法を用いた場合と比較して、異種のゲート電極用金属含有膜の積層構造における望ましくない合金化反応を抑制できる可能性がある。しかしながら、例えばアルミニウム等の金属材料を用いた場合には、シンタの熱負荷であっても金属拡散及び合金化が生じてしまう。また、ゲートラスト法においては、ポリシリコン等からなるダミーゲート電極の除去により形成されるリセス内に、異種の金属含有膜の積層構造が埋め込まれるが、微細化に伴って当該リセスの寸法(例えばゲート電極高さとなるリセス深さ)が小さくなるので、仕事関数を決定する各ゲート電極用金属含有膜の厚さを例えば10nm程度以下に薄くする必要がある。その結果、異種のゲート電極用金属含有膜の積層構造における界面合金化反応を十分に抑制できないと、合金化層の形成に起因して下層のゲート電極用金属含有膜の厚さが例えば5nm程度以下になってしまい、所望の仕事関数を得ることができなくなる。

【0022】

以上に述べたように、本発明の目的を達成するためには、つまり、さらなる微細化に対しても適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現するためには、ゲートファースト法及びゲートラスト法のいずれを用いた場合においても、仕事関数を決定する異種のゲート電極用金属含有膜の積層構造(pチャネル用金属含有膜とnチャネル用金属含有膜との積層構造)における界面合金化反応を極力抑えることが極めて重要な課題となる。

【0023】

本発明は、以上の知見に基づきなされたものであって、その要旨は、仕事関数を決定する異種のゲート電極用金属含有膜の積層構造(pチャネル用金属含有膜とnチャネル用金属含有膜との積層構造)における当該各金属含有膜同士の間に、金属拡散を防止するための拡散防止層を形成することである。これにより、さらなる微細化に対しても、異種のゲート電極用金属含有膜の積層構造における界面合金化反応を抑制して所望の仕事関数を得ることができるので、適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現することができる。尚、拡散防止層の形成に際しては、特に、プロセスの複雑化を避けるために、また、拡散防止層そのものを新たに挿入形成することに起因するゲート電極の厚さの増大や仕事関数に対する影響等を極力抑えるために、下層のゲート電極用金属含有膜の表面改質、又は異種のゲート電極用金属含有膜同士の界面の改質を行うことが好ましい。また、改質手段としては、膜堆積の他、例えば、熱処理、プラズマ処理又はイオン注入等を用いることができる。また、有効な拡散防止層材料としては、例えば、金属酸化物、金属窒化物又は金属酸窒化物等を用いることができる。

【0024】

具体的には、本発明に係る半導体装置は、第1のゲート電極を有する第1導電型MISFETと、第2のゲート電極を有する第2導電型MISFETとを半導体基板上に備えた半導体装置であって、前記第1のゲート電極は、第1の仕事関数を有する第1の金属含有膜と、前記第1の金属含有膜上に形成されており且つ第2の仕事関数を有する第2の金属含有膜とを含み、前記第2のゲート電極は、前記第1の金属含有膜を含まないと共に前記第2の金属含有膜を含み、前記第1のゲート電極における前記第1の金属含有膜と前記第2の金属含有膜との間に拡散防止層が形成されている。

【0025】

尚、前記拡散防止層は、ゲート電極の抵抗低減の観点からは、導電層であることが好ましいが、トンネル効果を生じる極薄(例えば2nm程度以下)の絶縁層であってもよい。また、前記拡散防止層が導電層であっても、微細化の観点(特にゲートラスト法を用いる場合)からは、前記拡散防止層の厚さは5nm程度以下であることが好ましく、ゲート電極の抵抗低減の観点からは、前記拡散防止層の厚さは2nm程度以下であることがより好ましい。

【0026】

本発明に係る半導体装置において、前記拡散防止層は、前記第1の金属含有膜を構成する材料の酸化物、窒化物又は酸窒化物から構成されていてもよい。

【0027】

本発明に係る半導体装置において、前記第1導電型MISFETはpチャネルMISFETであり、前記第2導電型MISFETはnチャネルMISFETであり、前記第1の金属含有膜は、Ti、Ta、W若しくはNiを含む金属窒化物、又は貴金属から構成されており、前記第2の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物から構成されていてもよい。ここで、前記拡散防止層は、Ti又はTaを含む酸化物から構成されていてもよい。また、前記第1の金属含有膜は、W若しくはNiを含む金属窒化物、又は貴金属から構成されており、前記拡散防止層は、Ti又はTaを含む金属窒化物から構成されていてもよい。また、前記第1の金属含有膜は、貴金属から構成されており、前記拡散防止層は、貴金属の酸化物、窒化物又は酸窒化物から構成されていてもよい。また、前記第1の金属含有膜は、Ti、Ta、W又はNiを含む金属窒化物から構成されており、前記拡散防止層は、Ti、Ta、W又はNiを含む金属酸窒化物から構成されていてもよい。

【0028】

本発明に係る半導体装置において、前記第1導電型MISFETはnチャネルMISFETであり、前記第2導電型MISFETはpチャネルMISFETであり、前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物から構成されており、前記第2の金属含有膜は、Ti、Ta、W若しくはNiを含む金属窒化物、又は貴金属から構成されていてもよい。ここで、前記拡散防止層は、Ti又はTaを含む酸化物から構成されていてもよい。また、前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物(但しTi又はTaの窒化物を除く)若しくは炭化物から構成されており、前記拡散防止層は、Ti又はTaを含む金属窒化物から構成されていてもよい。また、前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の炭化物から構成されており、前記拡散防止層は、前記第1の金属含有膜を構成する材料の酸化物、窒化物又は酸窒化物から構成されていてもよい。また、前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属の窒化物、又は前記金属群の中から選ばれた2つ以上の金属の合金の窒化物から構成されており、前記拡散防止層は、前記第1の金属含有膜を構成する材料の酸化物から構成されていてもよい。

【0029】

本発明に係る半導体装置において、前記第1のゲート電極及び前記第2のゲート電極のそれぞれの下に、高誘電率絶縁膜を含むゲート絶縁膜が形成されていてもよい。ここで、前記ゲート絶縁膜は、前記高誘電率絶縁膜の下に形成されており且つシリコン酸化膜からなる下地膜を含んでいてもよい。

【0030】

本発明に係る半導体装置において、前記第1のゲート電極及び前記第2のゲート電極はそれぞれ、前記第2の金属含有膜上に形成された導電膜を含んでいてもよい。

【0031】

また、本発明に係る半導体装置の製造方法は、第1のゲート電極を有する第1導電型MISFETと、第2のゲート電極を有する第2導電型MISFETとを半導体基板上に備えた半導体装置の製造方法であって、前記半導体基板における前記第1導電型MISFETの形成領域の上に、第1の仕事関数を有する第1の金属含有膜を形成する工程(a)と、前記工程(a)よりも後に、前記第1の金属含有膜の上、及び前記半導体基板における前記第2導電型MISFETの形成領域の上に、第2の仕事関数を有する第2の金属含有膜を形成する工程(b)と、前記工程(b)よりも後に、前記第1の金属含有膜及び前記第2の金属含有膜をパターニングして、前記第1の金属含有膜及び前記第2の金属含有膜を含む前記第1のゲート電極と、前記第1の金属含有膜を含まないと共に前記第2の金属含有膜を含む前記第2のゲート電極とを形成する工程(c)とを備え、前記工程(a)と前記工程(c)との間に、前記第1のゲート電極における前記第1の金属含有膜と前記第2の金属含有膜との間に介在する拡散防止層を形成する工程(d)をさらに備えている。

【0032】

本発明に係る半導体装置の製造方法において、前記工程(d)において、前記第1の金属含有膜の表面部を改質することによって前記拡散防止層を形成してもよい。ここで、前記工程(d)は、前記工程(b)よりも前に実施され、前記工程(d)において、酸素及び窒素の少なくとも一方を含む雰囲気中での熱処理又はプラズマ処理によって、前記第1の金属含有膜の表面部を改質してもよい。また、前記工程(a)は、前記半導体基板における前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に、前記第1の金属含有膜を形成する工程(a1)と、前記工程(a1)よりも後に、前記第2導電型MISFETの形成領域の上に形成された部分の前記第1の金属含有膜を選択的に除去する工程(a2)とを含み、前記工程(d)は、前記工程(a1)と前記工程(a2)との間に実施され、前記工程(d)において、前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に形成された前記第1の金属含有膜の表面部を改質することによって前記拡散防止層を形成し、前記工程(a2)において、前記第2導電型MISFETの形成領域の上に形成された部分の前記拡散防止層を選択的に除去してもよい。或いは、前記工程(d)は、前記工程(b)よりも後に実施され、前記工程(d)において、酸素及び窒素の少なくとも一方のイオン注入によって、前記第1の金属含有膜の表面部を改質してもよい。

【0033】

本発明に係る半導体装置の製造方法において、前記工程(d)は、前記工程(b)よりも前に実施され、前記工程(d)において、前記第1の金属含有膜の上に前記拡散防止層を成膜してもよい。ここで、前記工程(a)は、前記半導体基板における前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に、前記第1の金属含有膜を形成する工程(a1)と、前記工程(a1)よりも後に、前記第2導電型MISFETの形成領域の上に形成された部分の前記第1の金属含有膜を選択的に除去する工程(a2)とを含み、前記工程(d)は、前記工程(a1)と前記工程(a2)との間に実施され、前記工程(d)において、前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に形成された前記第1の金属含有膜の上に前記拡散防止層を成膜し、前記工程(a2)において、前記第2導電型MISFETの形成領域の上に形成された部分の前記拡散防止層を選択的に除去してもよい。尚、前記拡散防止層を成膜により形成する場合、ピンホールの発生を防止する観点から、前記拡散防止層の厚さは1nm程度以上であることが好ましい。

【0034】

本発明に係る半導体装置の製造方法において、前記第1のゲート電極及び前記第2のゲート電極をゲートラスト法を用いて形成してもよい。

【発明の効果】

【0035】

本発明によると、さらなる微細化に対しても適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現することができる。

【図面の簡単な説明】

【0036】

【図1】図1(a)〜(f)は、第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図2】図2(a)〜(e)は、第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図3】図3(a)〜(c)は、第1の実施形態の変形例に係る半導体装置の製造方法の各工程を示す断面図である。

【図4】図4(a)〜(e)は、第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図5】図5(a)〜(d)は、第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【図6】図6(a)〜(d)は、第2の実施形態の変形例に係る半導体装置の製造方法の各工程を示す断面図である。

【図7】図7(a)〜(e)は、従来の半導体装置の製造方法の各工程を説明する図である。

【図8】図8(a)〜(c)は、従来の半導体装置の製造方法の各工程を説明する図である。

【図9】図9は、従来の半導体装置の問題点を説明する図である。

【発明を実施するための形態】

【0037】

(第1の実施形態)

以下、本発明の第1の実施形態に係る半導体装置及びその製造方法について、図面を参照しながら説明する。図1(a)〜(f)及び図2(a)〜(e)は、第1の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【0038】

まず、図1(a)に示すように、例えばシリコン(Si)からなる基板100の上部に、例えばシャロウトレンチ分離(STI)構造を有する素子分離領域102を選択的に形成することにより、nチャネルMISFETの形成領域(以下、NMIS領域という)とpチャネルMISFETの形成領域(以下、PMIS領域という)とを区画する。続いて、例えばイオン注入法により、NMIS領域の基板100にp型ウェル領域103aを形成し、PMIS領域の基板100にn型ウェル領域103bを形成する。続いて、基板100の表面に対して、例えば公知の標準RCA洗浄及び希釈フッ酸(HF)洗浄を順次行った後、当該表面が清浄化された基板100に対して、例えば温度が600℃〜1000℃程度の酸素雰囲気で熱処理を行う。これにより、NMIS領域及びPMIS領域(つまりCMIS(Complementary Metal-Insulator-Semiconductor)デバイス形成領域)の基板100の上に、例えばシリコン酸化膜(SiO2 膜)からなる厚さ1〜3nm程度の絶縁膜104が形成される。ここで、例えばウェット処理を用いて、例えばケミカルシリコン酸化膜やISSG(In Situ Steam Generation)膜からなる絶縁膜104を形成してもよい。次に、絶縁膜104上に、所望のゲート電極高さに相当する例えば60〜80nm程度の厚さを持つ例えばアモルファスシリコンからなるダミーゲート電極膜105を堆積する。続いて、ダミーゲート電極膜105上に、リソグラフィ技術を用いて、例えばハードマスク材料やレジスト材料からなり且つNMIS領域及びPMIS領域それぞれのゲート電極形成領域を覆うマスクパターン106を形成する。

【0039】

次に、マスクパターン106を用いて、例えば塩素(Cl2 )ガス等によるドライエッチング又はウェットエッチングを行うことによって、図1(b)に示すように、ダミーゲート電極膜105をパターニングした後、マスクパターン106を除去する。これにより、NMIS領域には、nチャネル用ダミーゲート電極105aが形成されると共に、PMIS領域には、pチャネル用ダミーゲート電極105bが形成される。このとき、nチャネル用ダミーゲート電極105a及びpチャネル用ダミーゲート電極105bのそれぞれの外側に位置する部分の絶縁膜104が除去されて、基板100とnチャネル用ダミーゲート電極105aとの間にダミーゲート絶縁膜104aが形成されると共に、基板100とpチャネル用ダミーゲート電極105bとの間にダミーゲート絶縁膜104bが形成される。

【0040】

次に、nチャネル用ダミーゲート電極105a及びpチャネル用ダミーゲート電極105bのそれぞれの側面上にオフセットスペーサ(図示省略)を形成した後、図1(c)に示すように、例えばイオン注入法により、基板100の上部におけるnチャネル用ダミーゲート電極105aの両側にn型エクステンション領域107aを形成し、基板100の上部におけるpチャネル用ダミーゲート電極105bの両側にp型エクステンション領域107bを形成する。

【0041】

次に、図1(d)に示すように、nチャネル用ダミーゲート電極105a及びpチャネル用ダミーゲート電極105bのそれぞれの側面上に、前述のオフセットスペーサを介して、例えば窒化シリコンからなる絶縁性サイドウォールスペーサ108a及び108bを形成する。その後、例えばイオン注入法により、基板100の上部におけるnチャネル用ダミーゲート電極105a及び絶縁性サイドウォールスペーサ108aの両側にn型ソース/ドレイン領域109aを形成し、基板100の上部におけるpチャネル用ダミーゲート電極105b及び絶縁性サイドウォールスペーサ108bの両側にp型ソース/ドレイン領域109bを形成する。その後、例えば1000℃以上の温度で、n型エクステンション領域107a及びp型エクステンション領域107b並びにn型ソース/ドレイン領域109a及びp型ソース/ドレイン領域109bのそれぞれに注入された不純物に対して活性化アニールを行う。これにより、ダミーゲートトランジスタ構造が完成する。

【0042】

その後、図示は省略しているが、n型ソース/ドレイン領域109a及びp型ソース/ドレイン領域109bのそれぞれの表面部をシリサイド化した後、図1(e)に示すように、例えばプラズマCVD(Chemical Vapor Deposition )法により、基板100上の全面に亘って、例えば酸化シリコンを主成分とする層間絶縁膜110を堆積する。続いて、例えばCMP(Chemical Mechanical Polishing )法やドライエッチ法により、堆積した層間絶縁膜110に対して平坦化やエッチバックを行って、nチャネル用ダミーゲート電極105a及びpチャネル用ダミーゲート電極105bのそれぞれの上面を露出させる。

【0043】

次に、図1(f)に示すように、例えば塩素(Cl2 )ガスを主成分とるエッチングガスを用いたドライエッチング、又は例えばテトラエチル水酸化アンモニウム(TMAH)を用いたウェットエッチングにより、nチャネル用ダミーゲート電極105a及びpチャネル用ダミーゲート電極105bを除去する。続いて、例えばフッ酸(HF)を用いたウェットエッチングにより、シリコン酸化膜(SiO2 )からなるダミーゲート絶縁膜104a及び104bを除去する。これにより、ダミーゲート構造が除去されて、絶縁性サイドウォールスペーサ108aを側壁面とし且つ基板100を底面とするリセス111aが形成されると共に絶縁性サイドウォールスペーサ108bを側壁面とし且つ基板100を底面とするリセス111bが形成される。

【0044】

次に、図2(a)に示すように、例えばオゾン酸化を用いたウェット処理を行うことによって、リセス111a及び111bそれぞれの底面となる基板100上に、例えばシリコン酸化膜(SiO2 )からなる厚さ1nm程度の下地膜112a及び112bを形成する。ここで、例えば熱処理を用いて、例えばシリコン熱酸化膜やISSG膜からなる下地膜112a及び112bを形成してもよいが、下地膜112a及び112bの形成工程は前述のシリサイド化工程後に行われるので、熱処理温度は最大でも600℃を超えないようにする必要がある。次に、リセス111a及び111bそれぞれの底面上に形成された下地膜112a及び112bの上を含む基板100上の全面に、例えばALD(Atomic Layer Deposition ;原子層堆積)法を用いて、例えば絶縁性金属酸化物からなる厚さ3nm程度の高誘電率絶縁膜113を成膜する。具体的には、高誘電率絶縁膜113として、例えばHfO2 膜を成膜する場合、Hf原料としてHfCl4 を、酸化材としてH2 Oを用いると共に成膜温度を200〜400℃に設定し、HfCl4 の供給、パージ、H2 Oの供給及びパージのサイクルを繰り返し行うことによって、HfO2 を原子層レベルで成長させて、所望の厚さを持つHfO2 膜からなる高誘電率絶縁膜113を得ることができる。

【0045】

CMISトランジスタを構成するには、高誘電率絶縁膜113の形成後、PMIS領域及びNMIS領域のそれぞれにおいて、バンドエッジ(価電子帯及び伝導帯)付近の好適な仕事関数を持った異種のゲート電極用金属含有膜(pチャネル用金属含有膜及びnチャネル用金属含有膜)を形成する必要がある。ここで、pチャネル用金属含有膜及びnチャネル用金属含有膜のいずれを先に形成するかは、各ゲート電極材料の加工時の選択性等を考慮して決定すべきことであるが、以下、本実施形態では、pチャネル用金属含有膜を先に形成する場合を例として説明する。

【0046】

高誘電率絶縁膜113の形成後、図2(a)に示すように、高誘電率絶縁膜113上に、PMISFETに好適な仕事関数を持った材料、例えば、Pt、Pd若しくはRu等の貴金属、又はTi、Ta、W若しくはNiを含む金属窒化物からなる厚さ数nm〜十数nm程度のpチャネル用金属含有膜114を形成する。リセス111a及び111bが高アスペクト比を有する場合には、pチャネル用金属含有膜114の形成方法としては、例えば、コンフォーマルな堆積が可能なALD法若しくはCVD法、又はボトムカバレッジのよい(つまり高指向性の)PVD(Physical Vapor Deposition )法等を用いてもよい。

【0047】

続いて、図2(a)に示すように、pチャネル用金属含有膜114と、後述するnチャネル用金属含有膜117(図2(c)参照)との間の合金化反応を抑制するために、例えばpチャネル用金属含有膜114の表面部に対して改質処理を実施して拡散防止層115を形成する。拡散防止層115については後で詳細に述べる。その後、拡散防止層115上に、PMIS領域を覆うマスクパターン116を形成する。

【0048】

次に、マスクパターン116を用いて、図2(b)に示すように、NMIS領域に位置する部分のpチャネル用金属含有膜114及び拡散防止層115をエッチバックして除去し、その後、マスクパターン116を除去する。次に、図2(c)に示すように、NMIS領域に位置する部分の高誘電率絶縁膜113上、及びPMIS領域に残存する拡散防止層115上に、NMISFETに好適な仕事関数を持った材料、例えば、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなる厚さ数nm〜十数nm程度のnチャネル用金属含有膜117を形成する。リセス111a及び111bが高アスペクト比を有する場合には、nチャネル用金属含有膜117の形成方法としては、例えば、コンフォーマルな堆積が可能なALD法若しくはCVD法、又はボトムカバレッジのよい(つまり高指向性の)PVD法等を用いてもよい。

【0049】

次に、図2(d)に示すように、リセス111a及び111bの空隙部分が完全に埋まるように、nチャネル用金属含有膜117上に、例えばAl、Ti、W又はCu等の低抵抗の金属からなる導電膜118を形成する。

【0050】

最後に、図2(e)に示すように、リセス111a及び111bからはみ出た部分の導電膜118、nチャネル用金属含有膜117、拡散防止層115、pチャネル用金属含有膜114及び高誘電率絶縁膜113を、例えばCMP法による平坦化又はドライエッチング法によるエッチバックによって除去する。これにより、NMIS領域においては、下地膜112a及び高誘電率絶縁膜113aからなるゲート絶縁膜119aを挟んでリセス111aに埋め込まれており且つnチャネル用金属含有膜117a及び導電膜118aからなるnチャネル用ゲート電極120aが形成される。また、PMIS領域においては、下地膜112b及び高誘電率絶縁膜113bからなるゲート絶縁膜119bを挟んでリセス111bに埋め込まれており且つpチャネル用金属含有膜114b、拡散防止層115b、nチャネル用金属含有膜117b及び導電膜118bからなるpチャネル用ゲート電極120bが形成される。すなわち、ゲートラスト型トランジスタの基本構造が完成する。

【0051】

以上に説明したように、本実施形態によると、pチャネル用ゲート電極120bにおけるpチャネル用金属含有膜114bとnチャネル用金属含有膜117bとの間に拡散防止層115bが形成されている。このため、ゲート電極形成後のシンタ等の工程において熱負荷が加えられたとしても、pチャネル用金属含有膜114bとnチャネル用金属含有膜117bとの間の合金化反応を抑制して所望の仕事関数を得ることができるので、適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現できる。また、本実施形態ではゲートラスト法を用いているため、ソース/ドレイン領域形成に伴う不純物活性化熱処理をゲート電極形成前に実施できるので、ゲート電極形成後の工程における熱負荷を低減でき、それによって、前述の合金化反応をより一層抑制することができる。

【0052】

尚、本実施形態において、拡散防止層115は、ゲート電極抵抗の低減の観点からは、導電層であることが好ましいが、トンネル効果を生じる極薄(例えば2nm程度以下)の絶縁層であってもよい。また、拡散防止層115が導電層であっても、微細化の観点(特に本実施形態のようにゲートラスト法を用いる場合)からは、拡散防止層115の厚さは5nm程度以下であることが好ましく、ゲート電極抵抗の低減の観点からは、拡散防止層115の厚さは2nm程度以下であることがより好ましい。特に、20nm世代以降を想定した場合、拡散防止層115の厚さのみならず、実効仕事関数を決定するpチャネル用金属含有膜114及びnチャネル用金属含有膜117の厚さについても、数nm以下程度に抑制することが望ましい。

【0053】

また、本実施形態のように、pチャネル用金属含有膜114がPt、Pd若しくはRu等の貴金属、又はTi、Ta、W若しくはNiを含む金属窒化物からなり、nチャネル用金属含有膜117がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなる場合、拡散防止層115は、例えばTi又はTaを含む酸化物から構成されていてもよい。或いは、pチャネル用金属含有膜114がPt、Pd若しくはRu等の貴金属、又はW若しくはNiを含む金属窒化物からなる場合、拡散防止層115は、例えばTi又はTaを含む金属窒化物から構成されていてもよい。或いは、pチャネル用金属含有膜114がPt、Pd若しくはRu等の貴金属からなる場合、拡散防止層115は、Pt、Pd若しくはRu等の貴金属の酸化物、窒化物又は酸窒化物から構成されていてもよい。或いは、pチャネル用金属含有膜114がTi、Ta、W又はNiを含む金属窒化物からなる場合、拡散防止層115は、Ti、Ta、W又はNiを含む金属酸窒化物から構成されていてもよい。

【0054】

また、本実施形態において、拡散防止層115を形成するために、例えばpチャネル用金属含有膜114の表面改質を行ってもよい。表面改質の具体的方法としては、簡単には、拡散防止効果のある元素、例えば窒素及び酸素の少なくとも一方を含む雰囲気中で熱処理を行う方法がある。このような方法を用いると、pチャネル用金属含有膜114を構成する材料の酸化物、窒化物又は酸窒化物からなる拡散防止層115が形成される。尚、窒素及び酸素の少なくとも一方を含む雰囲気中での熱処理に代えて、例えば窒素及び酸素の少なくとも一方を含むガスからなるプラズマにpチャネル用金属含有膜114の表面を曝してもよい。このようなプラズマ処理を行う場合、処理深さの点で、図2(c)に示すnチャネル用金属含有膜117の形成前に行うのが効果的である。

【0055】

また、本実施形態において、pチャネル用金属含有膜114の表面改質を用いずに、pチャネル用金属含有膜114上に拡散防止層115を成膜してもよい。例えばTi又はTa等からなる高融点金属ターゲットを用いて、窒素及び酸素の少なくとも一方を含む雰囲気中で反応性スパッタを行うことによって、拡散防止層115を成膜してもよい。拡散防止層115を成膜する場合、ピンホールの発生を防止する観点から、拡散防止層115の厚さは1nm程度以上であることが好ましい。

【0056】

また、本実施形態においては、図2(c)に示すnチャネル用金属含有膜117の形成前に拡散防止層115を形成したが、これに代えて、nチャネル用金属含有膜117の形成後に、例えば窒素及び酸素の少なくとも一方のイオン注入を行うことにより、pチャネル用金属含有膜114とnチャネル用金属含有膜117との積層界面近傍を改質して拡散防止層115を形成してもよい。この場合、pチャネル用金属含有膜114の上面近傍(つまり表面部)のみならず、nチャネル用金属含有膜117の下面近傍にも拡散防止層115を形成することができるので、拡散防止効果を高めるのに効果的である。

【0057】

また、本実施形態においては、図2(a)〜(c)に示すように、CMISデバイス形成領域全体にpチャネル用金属含有膜114を形成した後、pチャネル用金属含有膜114上に拡散防止層115を形成し、その後、NMIS領域に位置する部分のpチャネル用金属含有膜114及び拡散防止層115をエッチバックして選択的に除去した。しかし、これに代えて、図3(a)〜(c)に示すように、CMISデバイス形成領域全体にpチャネル用金属含有膜114を形成した後、PMIS領域を覆うマスクパターン116を用いて、NMIS領域に位置する部分のpチャネル用金属含有膜114をエッチバックして選択的に除去し、その後、残存するpチャネル用金属含有膜114上に拡散防止層115を形成してもよい。尚、pチャネル用金属含有膜114の選択的除去と拡散防止層115の形成との前後関係については、各ゲート電極材料の組み合わせによって決まる選択性等に応じて最適のシーケンスを選択すればよい。具体的には、図2(a)〜(c)に示すシーケンスの場合、pチャネル用金属含有膜114及び拡散防止層115のエッチングは複雑になるものの、NMIS領域に位置する部分の高誘電率絶縁膜113に対するダメージは、pチャネル用金属含有膜114及び拡散防止層115のエッチングによる1回だけ生じる。一方、図3(a)〜(c)に示すシーケンスの場合、pチャネル用金属含有膜114のエッチングは簡単になるものの、NMIS領域に位置する部分の高誘電率絶縁膜113に対するダメージは、pチャネル用金属含有膜114のエッチング、及び拡散防止層115の形成による2回生じる。

【0058】

また、本実施形態においては、pチャネル用金属含有膜114を先に形成したため、pチャネル用ゲート電極120bが、pチャネル用金属含有膜114bとnチャネル用金属含有膜117bとの積層構造を持つので、pチャネル用ゲート電極120bにおけるpチャネル用金属含有膜114bとnチャネル用金属含有膜117bとの間に拡散防止層115bを形成した。しかし、これに代えて、nチャネル用金属含有膜を先に形成することにより、nチャネル用ゲート電極が、nチャネル用金属含有膜とpチャネル用金属含有膜との積層構造を持ち、それに対応して、nチャネル用ゲート電極におけるnチャネル用金属含有膜とpチャネル用金属含有膜との間に拡散防止層を形成してもよい。このとき、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなり、pチャネル用金属含有膜がPt、Pd若しくはRu等の貴金属、又はTi、Ta、W若しくはNiを含む金属窒化物からなる場合、拡散防止層は、例えばTi又はTaを含む酸化物から構成されていてもよい。或いは、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物(但しTi又はTaの窒化物を除く)若しくは炭化物からなる場合、拡散防止層は、例えばTi又はTaを含む金属窒化物から構成されていてもよい。或いは、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の炭化物からなる場合、拡散防止層は、nチャネル用金属含有膜を構成する材料の酸化物、窒化物又は酸窒化物から構成されていてもよい。或いは、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属の窒化物、又は前記金属群の中から選ばれた2つ以上の金属の合金の窒化物からなる場合、拡散防止層は、nチャネル用金属含有膜を構成する材料の酸化物から構成されていてもよい。

【0059】

また、本実施形態において、pチャネル用金属含有膜114及びnチャネル用金属含有膜117はそれぞれ仕事関数調整層を含んでいても良い。また、本実施形態において、nチャネル用ゲート電極120aをnチャネル用金属含有膜117a及び導電膜118aから構成し、pチャネル用ゲート電極120bをpチャネル用金属含有膜114b、拡散防止層115b、nチャネル用金属含有膜117b及び導電膜118bから構成したが、リセス111a及び111bの寸法によっては、少なくともpチャネル用ゲート電極120bが導電膜118を含まない場合もあり得る。

【0060】

また、本実施形態において、pチャネル用ゲート電極120bにおけるpチャネル用金属含有膜114bとnチャネル用金属含有膜117bとの間の合金化反応を防止するために、pチャネル用金属含有膜114bとnチャネル用金属含有膜117bとの間に拡散防止層115bを形成した。しかし、nチャネル用ゲート電極120aにおけるnチャネル用金属含有膜117aと導電膜118aとの間でも合金化反応が生じる恐れがある場合には、nチャネル用金属含有膜117aと導電膜118aとの間に拡散防止層を形成してもよいことは言うまでもない。

【0061】

(第2の実施形態)

以下、本発明の第2の実施形態に係る半導体装置及びその製造方法について、図面を参照しながら説明する。尚、第1の実施形態1ではゲートラスト法を用いてMISFET形成を行ったのに対して、本実施形態ではゲートファースト法を用いてMISFET形成を行う。

【0062】

図4(a)〜(e)及び図5(a)〜(d)は、第2の実施形態に係る半導体装置の製造方法の各工程を示す断面図である。

【0063】

まず、図4(a)に示すように、例えばシリコン(Si)からなる基板200の上部に、例えばシャロウトレンチ分離(STI)構造を有する素子分離領域201を選択的に形成することにより、nチャネルMISFETの形成領域(以下、NMIS領域という)とpチャネルMISFETの形成領域(以下、PMIS領域という)とを区画する。続いて、例えばイオン注入法により、NMIS領域の基板200にp型ウェル領域202aを形成し、PMIS領域の基板200にn型ウェル領域202bを形成する。続いて、基板200の表面に対して、例えば公知の標準RCA洗浄及び希釈フッ酸(HF)洗浄を順次行った後、当該表面が清浄化された基板200に対して、例えば温度が600℃〜1000℃程度の酸素雰囲気で熱処理を行う。これにより、NMIS領域及びPMIS領域(つまりCMISデバイス形成領域)の基板200の上に、例えばシリコン酸化膜(SiO2 膜)からなる厚さ1nm程度の下地膜203が形成される。ここで、例えばウェット処理を用いて、例えばケミカルシリコン酸化膜やISSG膜からなる下地膜203を形成してもよい。次に、下地膜203上に、例えばALD法を用いて、例えば絶縁性金属酸化物からなる厚さ3nm程度の高誘電率絶縁膜204を成膜する。具体的には、高誘電率絶縁膜204として、例えばHfO2 膜を成膜する場合、Hf原料としてHfCl4 を、酸化材としてH2 Oを用いると共に成膜温度を200〜400℃に設定し、HfCl4 の供給、パージ、H2 Oの供給及びパージのサイクルを繰り返し行うことによって、HfO2 を原子層レベルで成長させて、所望の厚さを持つHfO2 膜からなる高誘電率絶縁膜204を得ることができる。

【0064】

CMISトランジスタを構成するには、高誘電率絶縁膜204の形成後、PMIS領域及びNMIS領域のそれぞれにおいて、バンドエッジ(価電子帯及び伝導帯)付近の好適な仕事関数を持った異種のゲート電極用金属含有膜(pチャネル用金属含有膜及びnチャネル用金属含有膜)を形成する必要がある。ここで、pチャネル用金属含有膜及びnチャネル用金属含有膜のいずれを先に形成するかは、各ゲート電極材料の加工時の選択性等を考慮して決定すべきことであるが、以下、本実施形態では、pチャネル用金属含有膜を先に形成する場合を例として説明する。

【0065】

高誘電率絶縁膜204の形成後、図4(a)に示すように、高誘電率絶縁膜204上に、PMISFETに好適な仕事関数を持った材料、例えば、Pt、Pd若しくはRu等の貴金属、又はTi、Ta、W若しくはNiを含む金属窒化物からなる厚さ数nm〜十数nm程度のpチャネル用金属含有膜205を形成する。

【0066】

次に、図4(b)に示すように、pチャネル用金属含有膜205上に、PMIS領域を覆うマスクパターン206を形成した後、当該マスクパターン206を用いて、図4(c)に示すように、NMIS領域に位置する部分のpチャネル用金属含有膜205をエッチバックして除去し、その後、マスクパターン206を除去する。

【0067】

続いて、図4(d)に示すように、pチャネル用金属含有膜205と、後述するnチャネル用金属含有膜208(図4(e)参照)との間の合金化反応(特に後述するソース/ドレイン領域形成に伴う不純物活性化熱処理等の高温プロセスに起因する合金化反応)を抑制するために、例えばpチャネル用金属含有膜205の表面部に対して改質処理を実施して拡散防止層207を形成する。拡散防止層207については後で詳細に述べる。

【0068】

次に、図4(e)に示すように、NMIS領域に位置する部分の高誘電率絶縁膜204上、及びPMIS領域に位置する拡散防止層207上に、NMISFETに好適な仕事関数を持った材料、例えば、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなる厚さ数nm〜十数nm程度のnチャネル用金属含有膜208を形成する。

【0069】

次に、ゲート電極抵抗値を所望の値に下げるために、図5(a)に示すように、nチャネル用金属含有膜208上に、例えば、導電性ポリシリコン、又はTi、Ta、W若しくはNi等の金属若しくは当該金属の窒化物等からなる厚さ数十nm程度の導電膜209を形成する。続いて、例えばリソグラフィ技術により、導電膜209上に、NMIS領域及びPMIS領域それぞれのゲート電極形成領域を覆うマスクパターン210を形成する。

【0070】

次に、マスクパターン210を用いて、例えば塩素(Cl2 )ガスを主成分とするエッチングガス等によるドライエッチング又はウェットエッチングを行うことによって、図5(b)に示すように、導電膜209、nチャネル用金属含有膜208、拡散防止層207及びpチャネル用金属含有膜205を順次パターニングした後、マスクパターン210を除去する。これにより、NMIS領域においては、nチャネル用金属含有膜208a及び導電膜209aからなるnチャネル用ゲート電極212aが形成されると共に、PMIS領域においては、pチャネル用金属含有膜205b、拡散防止層207b、nチャネル用金属含有膜208b及び導電膜209bからなるpチャネル用ゲート電極212bが形成される。このとき、nチャネル用ゲート電極212a及びpチャネル用ゲート電極212bのそれぞれの外側に位置する部分の下地膜203及び高誘電率絶縁膜204が除去されて、基板200とnチャネル用ゲート電極212aとの間に、下地膜203a及び高誘電率絶縁膜204aからなるゲート絶縁膜211aが形成されると共に、基板200とpチャネル用ゲート電極212bとの間に、下地膜203b及び高誘電率絶縁膜204bからなるゲート絶縁膜211bが形成される。

【0071】

尚、図5(b)に示すゲートパターニング工程における加工性及び選択性を良好に保つためには、pチャネル用金属含有膜205、拡散防止層207及びnチャネル用金属含有膜208のそれぞれの厚さを、所望の実効仕事関数を実現できる最低限の厚さに抑えることが望ましい。特に、20nm世代以降を想定した場合、実効仕事関数を決定するpチャネル用金属含有膜205、拡散防止層207及びnチャネル用金属含有膜208のそれぞれの厚さを数nm以下程度に抑制することが望ましい。

【0072】

次に、nチャネル用ゲート電極212a及びpチャネル用ゲート電極212bのそれぞれの側面上にオフセットスペーサ(図示省略)を形成した後、図5(c)に示すように、例えばイオン注入法により、基板200の上部におけるnチャネル用ゲート電極212aの両側にn型エクステンション領域213aを形成し、基板200の上部におけるpチャネル用ゲート電極212bの両側にp型エクステンション領域213bを形成する。

【0073】

次に、図5(d)に示すように、nチャネル用ゲート電極212a及びpチャネル用ゲート電極212bのそれぞれの側面上に、前述のオフセットスペーサを介して、例えば窒化シリコンからなる絶縁性サイドウォールスペーサ214a及び214bを形成する。その後、例えばイオン注入法により、基板200の上部におけるnチャネル用ゲート電極212a及び絶縁性サイドウォールスペーサ214aの両側にn型ソース/ドレイン領域215aを形成し、基板200の上部におけるpチャネル用ゲート電極212b及び絶縁性サイドウォールスペーサ214bの両側にp型ソース/ドレイン領域215bを形成する。その後、例えば1000℃以上の温度で、n型エクステンション領域213a及びp型エクステンション領域213b並びにn型ソース/ドレイン領域215a及びp型ソース/ドレイン領域215bのそれぞれに注入された不純物に対して活性化アニールを行う。

【0074】

その後、図示は省略しているが、n型ソース/ドレイン領域215a及びp型ソース/ドレイン領域215bのそれぞれの表面部をシリサイド化することによって、ゲートファースト型トランジスタの基本構造が完成する。

【0075】

以上に説明したように、本実施形態によると、pチャネル用ゲート電極212bにおけるpチャネル用金属含有膜205bとnチャネル用金属含有膜208bとの間に拡散防止層207bが形成されている。このため、ゲート電極形成後のソース/ドレイン領域形成に伴う不純物活性化熱処理等の工程において例えば1000℃以上の熱負荷が加えられたとしても、pチャネル用金属含有膜205bとnチャネル用金属含有膜208bとの間の合金化反応を抑制して所望の仕事関数を得ることができるので、適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現できる。

【0076】

尚、本実施形態において、拡散防止層207は、ゲート電極抵抗の低減の観点からは、導電層であることが好ましいが、トンネル効果を生じる極薄(例えば2nm程度以下)の絶縁層であってもよい。また、拡散防止層207が導電層であっても、微細化の観点からは、拡散防止層207の厚さは5nm程度以下であることが好ましく、ゲート電極抵抗の低減の観点からは、拡散防止層207の厚さは2nm程度以下であることがより好ましい。特に、20nm世代以降を想定した場合、拡散防止層207の厚さのみならず、実効仕事関数を決定するpチャネル用金属含有膜205及びnチャネル用金属含有膜208の厚さについても、数nm以下程度に抑制することが望ましい。

【0077】

また、本実施形態のように、pチャネル用金属含有膜205がPt、Pd若しくはRu等の貴金属、又はTi、Ta、W若しくはNiを含む金属窒化物からなり、nチャネル用金属含有膜208がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなる場合、拡散防止層207は、例えばTi又はTaを含む酸化物から構成されていてもよい。或いは、pチャネル用金属含有膜205がPt、Pd若しくはRu等の貴金属、又はW若しくはNiを含む金属窒化物からなる場合、拡散防止層207は、例えばTi又はTaを含む金属窒化物から構成されていてもよい。或いは、pチャネル用金属含有膜205がPt、Pd若しくはRu等の貴金属からなる場合、拡散防止層207は、Pt、Pd若しくはRu等の貴金属の酸化物、窒化物又は酸窒化物から構成されていてもよい。或いは、pチャネル用金属含有膜205がTi、Ta、W又はNiを含む金属窒化物からなる場合、拡散防止層207は、Ti、Ta、W又はNiを含む金属酸窒化物から構成されていてもよい。

【0078】

また、本実施形態において、拡散防止層207を形成するために、例えばpチャネル用金属含有膜205の表面改質を行ってもよい。表面改質の具体的方法としては、簡単には、拡散防止効果のある元素、例えば窒素及び酸素の少なくとも一方を含む雰囲気中で熱処理を行う方法がある。このような方法を用いると、pチャネル用金属含有膜205を構成する材料の酸化物、窒化物又は酸窒化物からなる拡散防止層207が形成される。尚、窒素及び酸素の少なくとも一方を含む雰囲気中での熱処理に代えて、例えば窒素及び酸素の少なくとも一方を含むガスからなるプラズマにpチャネル用金属含有膜205の表面を曝してもよい。このようなプラズマ処理を行う場合、処理深さの点で、図4(e)に示すnチャネル用金属含有膜208の形成前に行うのが効果的である。

【0079】

また、本実施形態において、pチャネル用金属含有膜205の表面改質を用いずに、pチャネル用金属含有膜205上に拡散防止層207を成膜してもよい。例えばTi又はTa等からなる高融点金属ターゲットを用いて、窒素及び酸素の少なくとも一方を含む雰囲気中で反応性スパッタを行うことによって、拡散防止層207を成膜してもよい。拡散防止層207を成膜する場合、ピンホールの発生を防止する観点から、拡散防止層207の厚さは1nm程度以上であることが好ましい。

【0080】

また、本実施形態においては、図4(e)に示すnチャネル用金属含有膜208の形成前に拡散防止層207を形成したが、これに代えて、nチャネル用金属含有膜208の形成後に、例えば窒素及び酸素の少なくとも一方のイオン注入を行うことにより、pチャネル用金属含有膜205とnチャネル用金属含有膜208との積層界面近傍を改質して拡散防止層207を形成してもよい。この場合、pチャネル用金属含有膜205の上面近傍(つまり表面部)のみならず、nチャネル用金属含有膜208の下面近傍にも拡散防止層207を形成することができるので、拡散防止効果を高めるのに効果的である。

【0081】

また、本実施形態においては、図4(a)〜(d)に示すように、CMISデバイス形成領域全体にpチャネル用金属含有膜205を形成した後、PMIS領域を覆うマスクパターン206を用いて、NMIS領域に位置する部分のpチャネル用金属含有膜205をエッチバックして選択的に除去し、その後、残存するpチャネル用金属含有膜205上に拡散防止層207を形成した。しかし、これに代えて、図6(a)〜(d)に示すように、CMISデバイス形成領域全体にpチャネル用金属含有膜205を形成した後、pチャネル用金属含有膜205上に拡散防止層207を形成し、その後、NMIS領域に位置する部分のpチャネル用金属含有膜205及び拡散防止層207をエッチバックして選択的に除去してもよい。尚、pチャネル用金属含有膜205の選択的除去と拡散防止層207の形成との前後関係については、各ゲート電極材料の組み合わせによって決まる選択性等に応じて最適のシーケンスを選択すればよい。具体的には、図4(a)〜(d)に示すシーケンスの場合、pチャネル用金属含有膜205のエッチングは簡単になるものの、NMIS領域に位置する部分の高誘電率絶縁膜204に対するダメージは、pチャネル用金属含有膜205のエッチング、及び拡散防止層207の形成による2回生じる。一方、図6(a)〜(d)に示すシーケンスの場合、pチャネル用金属含有膜205及び拡散防止層207のエッチングは複雑になるものの、NMIS領域に位置する部分の高誘電率絶縁膜204に対するダメージは、pチャネル用金属含有膜205及び拡散防止層207のエッチングによる1回だけ生じる。

【0082】

また、本実施形態においては、pチャネル用金属含有膜205を先に形成したため、pチャネル用ゲート電極212bが、pチャネル用金属含有膜205bとnチャネル用金属含有膜208bとの積層構造を持つので、pチャネル用ゲート電極212bにおけるpチャネル用金属含有膜205bとnチャネル用金属含有膜208bとの間に拡散防止層207bを形成した。しかし、これに代えて、nチャネル用金属含有膜を先に形成することにより、nチャネル用ゲート電極が、nチャネル用金属含有膜とpチャネル用金属含有膜との積層構造を持ち、それに対応して、nチャネル用ゲート電極におけるnチャネル用金属含有膜とpチャネル用金属含有膜との間に拡散防止層を形成してもよい。このとき、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなり、pチャネル用金属含有膜がPt、Pd若しくはRu等の貴金属、又はTi、Ta、W若しくはNiを含む金属窒化物からなる場合、拡散防止層は、例えばTi又はTaを含む酸化物から構成されていてもよい。或いは、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物(但しTi又はTaの窒化物を除く)若しくは炭化物からなる場合、拡散防止層は、例えばTi又はTaを含む金属窒化物から構成されていてもよい。或いは、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の炭化物からなる場合、拡散防止層は、nチャネル用金属含有膜を構成する材料の酸化物、窒化物又は酸窒化物から構成されていてもよい。或いは、nチャネル用金属含有膜がHf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属の窒化物、又は前記金属群の中から選ばれた2つ以上の金属の合金の窒化物からなる場合、拡散防止層は、nチャネル用金属含有膜を構成する材料の酸化物から構成されていてもよい。

【0083】

また、本実施形態において、pチャネル用金属含有膜205及びnチャネル用金属含有膜208はそれぞれ仕事関数調整層を含んでいても良い。また、本実施形態において、nチャネル用ゲート電極212aをnチャネル用金属含有膜208a及び導電膜209aから構成し、pチャネル用ゲート電極212bをpチャネル用金属含有膜205b、拡散防止層207b、nチャネル用金属含有膜208b及び導電膜209bから構成したが、少なくともpチャネル用ゲート電極212bが導電膜209を含まない場合もあり得る。

【0084】

また、本実施形態において、pチャネル用ゲート電極212bにおけるpチャネル用金属含有膜205bとnチャネル用金属含有膜208bとの間の合金化反応を防止するために、pチャネル用金属含有膜205bとnチャネル用金属含有膜207bとの間に拡散防止層207bを形成した。しかし、nチャネル用ゲート電極212aにおけるnチャネル用金属含有膜208aと導電膜209aとの間でも合金化反応が生じる恐れがある場合には、nチャネル用金属含有膜208aと導電膜209aとの間に拡散防止層を形成してもよいことは言うまでもない。

【産業上の利用可能性】

【0085】

本発明は、仕事関数を決定する金属含有膜を含むゲート電極を有する半導体装置において、異種のゲート電極用金属含有膜の積層構造における界面合金化反応を抑制して所望の仕事関数を得ることを可能とするものであり、適切な閾値電圧を有するCMIS型の半導体装置等の実現に有用である。

【符号の説明】

【0086】

100 基板

102 素子分離領域

103a p型ウェル領域

103b n型ウェル領域

104 絶縁膜

104a、104b ダミーゲート絶縁膜

105 ダミーゲート電極膜

105a nチャネル用ダミーゲート電極

105b pチャネル用ダミーゲート電極

106 マスクパターン

107a n型エクステンション領域

107b p型エクステンション領域

108a、108b 絶縁性サイドウォールスペーサ

109a n型ソース/ドレイン領域

109b p型ソース/ドレイン領域

110 層間絶縁膜

111a、111b リセス

112a、112b 下地膜

113、113a、113b 高誘電率絶縁膜

114、114b pチャネル用金属含有膜

115、115b 拡散防止層

116 マスクパターン

117、117a、117b nチャネル用金属含有膜

118、118a、118b 導電膜

119a、119b ゲート絶縁膜

120a nチャネル用ゲート電極

120b pチャネル用ゲート電極

200 基板

201 素子分離領域

202a p型ウェル領域

202b n型ウェル領域

203、203a、203b 下地膜

204、204a、204b 高誘電率絶縁膜

205、205b pチャネル用金属含有膜

206 マスクパターン

207、207b 拡散防止層

208、208a、208b nチャネル用金属含有膜

209、209a、209b 導電膜

210 マスクパターン

211a、211b ゲート絶縁膜

212a nチャネル用ゲート電極

212b pチャネル用ゲート電極

213a n型エクステンション領域

213b p型エクステンション領域

214a、214b 絶縁性サイドウォールスペーサ

215a n型ソース/ドレイン領域

215b p型ソース/ドレイン領域

【特許請求の範囲】

【請求項1】

第1のゲート電極を有する第1導電型MISFETと、第2のゲート電極を有する第2導電型MISFETとを半導体基板上に備えた半導体装置であって、

前記第1のゲート電極は、第1の仕事関数を有する第1の金属含有膜と、前記第1の金属含有膜上に形成されており且つ第2の仕事関数を有する第2の金属含有膜とを含み、

前記第2のゲート電極は、前記第1の金属含有膜を含まないと共に前記第2の金属含有膜を含み、

前記第1のゲート電極における前記第1の金属含有膜と前記第2の金属含有膜との間に拡散防止層が形成されていることを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記拡散防止層は、前記第1の金属含有膜を構成する材料の酸化物、窒化物又は酸窒化物からなることを特徴とする半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、

前記第1導電型MISFETはpチャネルMISFETであり、

前記第2導電型MISFETはnチャネルMISFETであり、

前記第1の金属含有膜は、Ti、Ta、W若しくはNiを含む金属窒化物、又は貴金属からなり、

前記第2の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなることを特徴とする半導体装置。

【請求項4】

請求項3に記載の半導体装置において、

前記拡散防止層は、Ti又はTaを含む酸化物からなることを特徴とする半導体装置。

【請求項5】

請求項3に記載の半導体装置において、

前記第1の金属含有膜は、W若しくはNiを含む金属窒化物、又は貴金属からなり、

前記拡散防止層は、Ti又はTaを含む金属窒化物からなることを特徴とする半導体装置。

【請求項6】

請求項3に記載の半導体装置において、

前記第1の金属含有膜は、貴金属からなり、

前記拡散防止層は、貴金属の酸化物、窒化物又は酸窒化物からなることを特徴とする半導体装置。

【請求項7】

請求項3に記載の半導体装置において、

前記第1の金属含有膜は、Ti、Ta、W又はNiを含む金属窒化物からなり、

前記拡散防止層は、Ti、Ta、W又はNiを含む金属酸窒化物からなることを特徴とする半導体装置。

【請求項8】

請求項1又は2に記載の半導体装置において、

前記第1導電型MISFETはnチャネルMISFETであり、

前記第2導電型MISFETはpチャネルMISFETであり、

前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなり、

前記第2の金属含有膜は、Ti、Ta、W若しくはNiを含む金属窒化物、又は貴金属からなることを特徴とする半導体装置。

【請求項9】

請求項8に記載の半導体装置において、

前記拡散防止層は、Ti又はTaを含む酸化物からなることを特徴とする半導体装置。

【請求項10】

請求項8に記載の半導体装置において、

前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物(但しTi又はTaの窒化物を除く)若しくは炭化物からなり、

前記拡散防止層は、Ti又はTaを含む金属窒化物からなることを特徴とする半導体装置。

【請求項11】

請求項8に記載の半導体装置において、

前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の炭化物からなり、

前記拡散防止層は、前記第1の金属含有膜を構成する材料の酸化物、窒化物又は酸窒化物からなることを特徴とする半導体装置。

【請求項12】

請求項8に記載の半導体装置において、

前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属の窒化物、又は前記金属群の中から選ばれた2つ以上の金属の合金の窒化物からなり、

前記拡散防止層は、前記第1の金属含有膜を構成する材料の酸化物からなることを特徴とする半導体装置。

【請求項13】

請求項1〜12のいずれか1項に記載の半導体装置において、

前記第1のゲート電極及び前記第2のゲート電極のそれぞれの下に、高誘電率絶縁膜を含むゲート絶縁膜が形成されていることを特徴とする半導体装置。

【請求項14】

請求項13に記載の半導体装置において、

前記ゲート絶縁膜は、前記高誘電率絶縁膜の下に形成されており且つシリコン酸化膜からなる下地膜を含むことを特徴とする半導体装置。

【請求項15】

請求項1〜14のいずれか1項に記載の半導体装置において、

前記第1のゲート電極及び前記第2のゲート電極はそれぞれ、前記第2の金属含有膜上に形成された導電膜を含むことを特徴とする半導体装置。

【請求項16】

第1のゲート電極を有する第1導電型MISFETと、第2のゲート電極を有する第2導電型MISFETとを半導体基板上に備えた半導体装置の製造方法であって、

前記半導体基板における前記第1導電型MISFETの形成領域の上に、第1の仕事関数を有する第1の金属含有膜を形成する工程(a)と、

前記工程(a)よりも後に、前記第1の金属含有膜の上、及び前記半導体基板における前記第2導電型MISFETの形成領域の上に、第2の仕事関数を有する第2の金属含有膜を形成する工程(b)と、

前記工程(b)よりも後に、前記第1の金属含有膜及び前記第2の金属含有膜をパターニングして、前記第1の金属含有膜及び前記第2の金属含有膜を含む前記第1のゲート電極と、前記第1の金属含有膜を含まないと共に前記第2の金属含有膜を含む前記第2のゲート電極とを形成する工程(c)とを備え、

前記工程(a)と前記工程(c)との間に、前記第1のゲート電極における前記第1の金属含有膜と前記第2の金属含有膜との間に介在する拡散防止層を形成する工程(d)をさらに備えていることを特徴とする半導体装置の製造方法。

【請求項17】

請求項16に記載の半導体装置の製造方法において、

前記工程(d)において、前記第1の金属含有膜の表面部を改質することによって前記拡散防止層を形成することを特徴とする半導体装置の製造方法。

【請求項18】

請求項17に記載の半導体装置の製造方法において、

前記工程(d)は、前記工程(b)よりも前に実施され、

前記工程(d)において、酸素及び窒素の少なくとも一方を含む雰囲気中での熱処理又はプラズマ処理によって、前記第1の金属含有膜の表面部を改質することを特徴とする半導体装置の製造方法。

【請求項19】

請求項18に記載の半導体装置の製造方法において、

前記工程(a)は、前記半導体基板における前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に、前記第1の金属含有膜を形成する工程(a1)と、前記工程(a1)よりも後に、前記第2導電型MISFETの形成領域の上に形成された部分の前記第1の金属含有膜を選択的に除去する工程(a2)とを含み、

前記工程(d)は、前記工程(a1)と前記工程(a2)との間に実施され、

前記工程(d)において、前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に形成された前記第1の金属含有膜の表面部を改質することによって前記拡散防止層を形成し、

前記工程(a2)において、前記第2導電型MISFETの形成領域の上に形成された部分の前記拡散防止層を選択的に除去することを特徴とする半導体装置の製造方法。

【請求項20】

請求項17に記載の半導体装置の製造方法において、

前記工程(d)は、前記工程(b)よりも後に実施され、

前記工程(d)において、酸素及び窒素の少なくとも一方のイオン注入によって、前記第1の金属含有膜の表面部を改質することを特徴とする半導体装置の製造方法。

【請求項21】

請求項16に記載の半導体装置の製造方法において、

前記工程(d)は、前記工程(b)よりも前に実施され、

前記工程(d)において、前記第1の金属含有膜の上に前記拡散防止層を成膜することを特徴とする半導体装置の製造方法。

【請求項22】

請求項21に記載の半導体装置の製造方法において、

前記工程(a)は、前記半導体基板における前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に、前記第1の金属含有膜を形成する工程(a1)と、前記工程(a1)よりも後に、前記第2導電型MISFETの形成領域の上に形成された部分の前記第1の金属含有膜を選択的に除去する工程(a2)とを含み、

前記工程(d)は、前記工程(a1)と前記工程(a2)との間に実施され、

前記工程(d)において、前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に形成された前記第1の金属含有膜の上に前記拡散防止層を成膜し、

前記工程(a2)において、前記第2導電型MISFETの形成領域の上に形成された部分の前記拡散防止層を選択的に除去することを特徴とする半導体装置の製造方法。

【請求項23】

請求項16〜22のいずれか1項に記載の半導体装置の製造方法において、

前記第1のゲート電極及び前記第2のゲート電極をゲートラスト法を用いて形成することを特徴とする半導体装置の製造方法。

【請求項1】

第1のゲート電極を有する第1導電型MISFETと、第2のゲート電極を有する第2導電型MISFETとを半導体基板上に備えた半導体装置であって、

前記第1のゲート電極は、第1の仕事関数を有する第1の金属含有膜と、前記第1の金属含有膜上に形成されており且つ第2の仕事関数を有する第2の金属含有膜とを含み、

前記第2のゲート電極は、前記第1の金属含有膜を含まないと共に前記第2の金属含有膜を含み、

前記第1のゲート電極における前記第1の金属含有膜と前記第2の金属含有膜との間に拡散防止層が形成されていることを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記拡散防止層は、前記第1の金属含有膜を構成する材料の酸化物、窒化物又は酸窒化物からなることを特徴とする半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、

前記第1導電型MISFETはpチャネルMISFETであり、

前記第2導電型MISFETはnチャネルMISFETであり、

前記第1の金属含有膜は、Ti、Ta、W若しくはNiを含む金属窒化物、又は貴金属からなり、

前記第2の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなることを特徴とする半導体装置。

【請求項4】

請求項3に記載の半導体装置において、

前記拡散防止層は、Ti又はTaを含む酸化物からなることを特徴とする半導体装置。

【請求項5】

請求項3に記載の半導体装置において、

前記第1の金属含有膜は、W若しくはNiを含む金属窒化物、又は貴金属からなり、

前記拡散防止層は、Ti又はTaを含む金属窒化物からなることを特徴とする半導体装置。

【請求項6】

請求項3に記載の半導体装置において、

前記第1の金属含有膜は、貴金属からなり、

前記拡散防止層は、貴金属の酸化物、窒化物又は酸窒化物からなることを特徴とする半導体装置。

【請求項7】

請求項3に記載の半導体装置において、

前記第1の金属含有膜は、Ti、Ta、W又はNiを含む金属窒化物からなり、

前記拡散防止層は、Ti、Ta、W又はNiを含む金属酸窒化物からなることを特徴とする半導体装置。

【請求項8】

請求項1又は2に記載の半導体装置において、

前記第1導電型MISFETはnチャネルMISFETであり、

前記第2導電型MISFETはpチャネルMISFETであり、

前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物若しくは炭化物からなり、

前記第2の金属含有膜は、Ti、Ta、W若しくはNiを含む金属窒化物、又は貴金属からなることを特徴とする半導体装置。

【請求項9】

請求項8に記載の半導体装置において、

前記拡散防止層は、Ti又はTaを含む酸化物からなることを特徴とする半導体装置。

【請求項10】

請求項8に記載の半導体装置において、

前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の窒化物(但しTi又はTaの窒化物を除く)若しくは炭化物からなり、

前記拡散防止層は、Ti又はTaを含む金属窒化物からなることを特徴とする半導体装置。

【請求項11】

請求項8に記載の半導体装置において、

前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属、前記金属群の中から選ばれた2つ以上の金属の合金、又は前記1つの金属若しくは前記合金の炭化物からなり、

前記拡散防止層は、前記第1の金属含有膜を構成する材料の酸化物、窒化物又は酸窒化物からなることを特徴とする半導体装置。

【請求項12】

請求項8に記載の半導体装置において、

前記第1の金属含有膜は、Hf、Zr、Ti、Ta及びAlを包含する金属群の中から選ばれた1つの金属の窒化物、又は前記金属群の中から選ばれた2つ以上の金属の合金の窒化物からなり、

前記拡散防止層は、前記第1の金属含有膜を構成する材料の酸化物からなることを特徴とする半導体装置。

【請求項13】

請求項1〜12のいずれか1項に記載の半導体装置において、

前記第1のゲート電極及び前記第2のゲート電極のそれぞれの下に、高誘電率絶縁膜を含むゲート絶縁膜が形成されていることを特徴とする半導体装置。

【請求項14】

請求項13に記載の半導体装置において、

前記ゲート絶縁膜は、前記高誘電率絶縁膜の下に形成されており且つシリコン酸化膜からなる下地膜を含むことを特徴とする半導体装置。

【請求項15】

請求項1〜14のいずれか1項に記載の半導体装置において、

前記第1のゲート電極及び前記第2のゲート電極はそれぞれ、前記第2の金属含有膜上に形成された導電膜を含むことを特徴とする半導体装置。

【請求項16】

第1のゲート電極を有する第1導電型MISFETと、第2のゲート電極を有する第2導電型MISFETとを半導体基板上に備えた半導体装置の製造方法であって、

前記半導体基板における前記第1導電型MISFETの形成領域の上に、第1の仕事関数を有する第1の金属含有膜を形成する工程(a)と、

前記工程(a)よりも後に、前記第1の金属含有膜の上、及び前記半導体基板における前記第2導電型MISFETの形成領域の上に、第2の仕事関数を有する第2の金属含有膜を形成する工程(b)と、

前記工程(b)よりも後に、前記第1の金属含有膜及び前記第2の金属含有膜をパターニングして、前記第1の金属含有膜及び前記第2の金属含有膜を含む前記第1のゲート電極と、前記第1の金属含有膜を含まないと共に前記第2の金属含有膜を含む前記第2のゲート電極とを形成する工程(c)とを備え、

前記工程(a)と前記工程(c)との間に、前記第1のゲート電極における前記第1の金属含有膜と前記第2の金属含有膜との間に介在する拡散防止層を形成する工程(d)をさらに備えていることを特徴とする半導体装置の製造方法。

【請求項17】

請求項16に記載の半導体装置の製造方法において、

前記工程(d)において、前記第1の金属含有膜の表面部を改質することによって前記拡散防止層を形成することを特徴とする半導体装置の製造方法。

【請求項18】

請求項17に記載の半導体装置の製造方法において、

前記工程(d)は、前記工程(b)よりも前に実施され、

前記工程(d)において、酸素及び窒素の少なくとも一方を含む雰囲気中での熱処理又はプラズマ処理によって、前記第1の金属含有膜の表面部を改質することを特徴とする半導体装置の製造方法。

【請求項19】

請求項18に記載の半導体装置の製造方法において、

前記工程(a)は、前記半導体基板における前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に、前記第1の金属含有膜を形成する工程(a1)と、前記工程(a1)よりも後に、前記第2導電型MISFETの形成領域の上に形成された部分の前記第1の金属含有膜を選択的に除去する工程(a2)とを含み、

前記工程(d)は、前記工程(a1)と前記工程(a2)との間に実施され、

前記工程(d)において、前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に形成された前記第1の金属含有膜の表面部を改質することによって前記拡散防止層を形成し、

前記工程(a2)において、前記第2導電型MISFETの形成領域の上に形成された部分の前記拡散防止層を選択的に除去することを特徴とする半導体装置の製造方法。

【請求項20】

請求項17に記載の半導体装置の製造方法において、

前記工程(d)は、前記工程(b)よりも後に実施され、

前記工程(d)において、酸素及び窒素の少なくとも一方のイオン注入によって、前記第1の金属含有膜の表面部を改質することを特徴とする半導体装置の製造方法。

【請求項21】

請求項16に記載の半導体装置の製造方法において、

前記工程(d)は、前記工程(b)よりも前に実施され、

前記工程(d)において、前記第1の金属含有膜の上に前記拡散防止層を成膜することを特徴とする半導体装置の製造方法。

【請求項22】

請求項21に記載の半導体装置の製造方法において、

前記工程(a)は、前記半導体基板における前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に、前記第1の金属含有膜を形成する工程(a1)と、前記工程(a1)よりも後に、前記第2導電型MISFETの形成領域の上に形成された部分の前記第1の金属含有膜を選択的に除去する工程(a2)とを含み、

前記工程(d)は、前記工程(a1)と前記工程(a2)との間に実施され、

前記工程(d)において、前記第1導電型MISFET及び前記第2導電型MISFETのそれぞれの形成領域の上に形成された前記第1の金属含有膜の上に前記拡散防止層を成膜し、

前記工程(a2)において、前記第2導電型MISFETの形成領域の上に形成された部分の前記拡散防止層を選択的に除去することを特徴とする半導体装置の製造方法。

【請求項23】

請求項16〜22のいずれか1項に記載の半導体装置の製造方法において、

前記第1のゲート電極及び前記第2のゲート電極をゲートラスト法を用いて形成することを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2012−231071(P2012−231071A)

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願番号】特願2011−99578(P2011−99578)

【出願日】平成23年4月27日(2011.4.27)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願日】平成23年4月27日(2011.4.27)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]