半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体装置の製造工程では、ドライエッチング装置や成膜装置などの製造装置において発生するチャージに半導体基板が曝され、製造過程の素子がダメージを受けることがある。半導体装置の高集積化に伴う素子の微細化により、半導体装置の製造過程で生じるチャージダメージ耐性もますます厳しくなっている。

【0003】

このようなチャージダメージを回避する手段として、半導体装置のデバイス機能素子以外にチャージ蓄積用の容量素子を設け、製造装置で発生したチャージを蓄積する方法が提案されている。また、半導体装置の製造後にヒューズを切断してチャージ蓄積用の容量素子を切り離し、容量素子からチャージが放電されてデバイス機能素子に影響を与えることを防止する方法が提案されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003−347303号公報

【特許文献2】特開2007−194424号公報

【特許文献3】特開2009−076777号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、ヒューズを切断してチャージ蓄積用の容量素子を切り離す方法は、ヒューズを切断する工程を別途設ける必要があり、製造工程が追加し、ひいては製造コストが増大することがあった。

【0006】

本発明の目的は、半導体装置の製造過程におけるチャージダメージを防止するとともに、半導体装置の製造後におけるチャージの放電を防止しうる半導体装置及びその製造方法を提供することにある。

【課題を解決するための手段】

【0007】

実施形態の一観点によれば、半導体基板上に形成されたデバイス機能素子と、前記半導体基板上に形成されたチャージ蓄積用素子と、前記半導体基板上に形成され、前記デバイス機能素子と前記チャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する半導体装置が提供される。

【0008】

また、実施形態の他の観点によれば、半導体基板上に、デバイス機能素子を形成する工程と、前記半導体基板上に、チャージ蓄積用素子を形成する工程と、前記半導体基板上に、前記デバイス機能素子と前記チャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子を形成する工程と、前記分離用素子にオフ状態を書き込み、前記デバイス機能素子と前記チャージ蓄積用素子とを電気的に分離する工程とを有する半導体装置の製造方法が提供される。

【発明の効果】

【0009】

開示の半導体装置及びその製造方法によれば、デバイス機能素子とチャージ蓄積用素子との間に電気的に書き換え可能な不揮発性メモリトランジスタの分離用素子を設けるので、デバイス機能素子とチャージ蓄積用素子とを容易に分離することができる。また、分離用素子はメモリトランジスタと同時に形成することができ、また、分離用素子の書き込みはメモリトランジスタの機能試験時に行うことができるため、製造工程を増加することなくデバイス機能素子とチャージ蓄積用素子とを確実に分離することができる。

【図面の簡単な説明】

【0010】

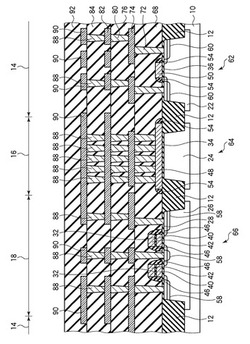

【図1】図1は、第1実施形態による半導体装置の構造を示す概略断面図である。

【図2】図2は、第1実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図3】図3は、第1実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図4】図4は、第1実施形態による半導体装置の製造方法を示す工程断面図(その3)である。

【図5】図5は、第1実施形態による半導体装置の製造方法を示す工程断面図(その4)である。

【図6】図6は、第1実施形態による半導体装置の製造方法を示す工程断面図(その5)である。

【図7】図7は、第1実施形態による半導体装置の製造方法を示す工程断面図(その6)である。

【図8】図8は、第1実施形態による半導体装置の製造方法を示す工程断面図(その7)である。

【図9】図9は、第1実施形態による半導体装置の製造方法を示す工程断面図(その8)である。

【図10】図10は、第1実施形態による半導体装置の製造方法を示す工程断面図(その9)である。

【図11】図11は、第1実施形態による半導体装置の製造方法を示す工程断面図(その10)である。

【図12】図12は、第1実施形態による半導体装置の製造方法を示す工程断面図(その11)である。

【図13】図13は、第1実施形態による半導体装置の製造方法を示す工程断面図(その12)である。

【図14】図14は、第1実施形態による半導体装置の製造方法を示す工程断面図(その13)である。

【図15】図15は、第2実施形態による半導体装置の構造を示す概略断面図である。

【図16】図16は、第2実施形態による半導体装置のチャージ蓄積用素子の構造を示す斜視図である。

【発明を実施するための形態】

【0011】

[第1実施形態]

第1実施形態による半導体装置及びその製造方法について図1乃至図14を用いて説明する。

【0012】

図1は、本実施形態による半導体装置の構造を示す概略断面図である。図2乃至図14は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0013】

はじめに、本実施形態による半導体装置の構造について図1を用いて説明する。

【0014】

シリコン基板10には、活性領域を画定する素子分離絶縁膜12が形成されている。図1において各活性領域は、図面右側から順に、デバイス機能素子形成領域14、チャージ蓄積用素子形成領域16、及び分離用素子形成領域18を表している。デバイス機能素子形成領域14は、メモリセルや周辺回路などの半導体装置の実質的な役割を担う素子が設けられる領域である。チャージ蓄積用素子形成領域16は、製造過程で発生するチャージを蓄積するチャージ蓄積用素子が形成される領域である。分離用素子形成領域18は、デバイス機能素子とチャージ蓄積用素子とを分離するための分離用素子が形成される領域である。

【0015】

デバイス機能素子形成領域14には、メモリセルや周辺回路などの機能素子が形成されるが、ここでは一例としてN型の周辺トランジスタ62が形成されているものとして説明する。

【0016】

デバイス機能素子形成領域14のシリコン基板10内には、Pウェル22が形成されている。Pウェル22が形成されたシリコン基板10上には、ゲート絶縁膜36を介してゲート電極50が形成されている。ゲート電極50の両側のシリコン基板10内には、ソース/ドレイン領域60が形成されている。こうして、デバイス機能素子形成領域14には、ゲート電極50及びソース/ドレイン領域60を有する周辺トランジスタ62が形成されている。

【0017】

チャージ蓄積用素子形成領域16のシリコン基板10内には、Pウェル24が形成されている。Pウェル24が形成されたシリコン基板10上は、キャパシタ誘電体膜34を介してプレート電極48が形成されている。こうして、チャージ蓄積用素子形成領域16には、下部電極としてのPウェル24と、キャパシタ誘電体膜34と、上部電極としてのプレート電極48とを有するMISキャパシタ構造のチャージ蓄積用素子64が形成されている。

【0018】

分離用素子形成領域18のシリコン基板10内には、Pウェル26が形成されている。Pウェル26が形成されたシリコン基板10上には、トンネルゲート絶縁膜28と、フローティングゲート40と、ONO膜32と、コントロールゲート42とが順次積層されたスタックゲートが形成されている。スタックゲートの両側のシリコン基板10内には、ソース/ドレイン領域58が形成されている。こうして、分離用素子形成領域18には、スタックゲート及びソース/ドレイン領域58を有する分離用素子66が形成されている。分離用素子66は、デバイス機能素子とチャージ蓄積用素子との間に接続して形成されている。分離用素子66は、図示しないメモリセル領域に形成されるメモリトランジスタと同様の構造及び機能を有しており、メモリトランジスタと同様に書き込み動作を行うことができるものである。

【0019】

周辺トランジスタ62、チャージ蓄積用素子64、分離用素子66が形成されたシリコン基板10上には、層間絶縁膜68が形成されている。層間絶縁膜68には、プレート電極48、ソース/ドレイン領域58,60等に接続されたコンタクトプラグ72が埋め込まれている。コンタクトプラグ72が埋め込まれた層間絶縁膜68上には、コンタクトプラグ72に接続された配線層74が形成されている。

【0020】

配線層74が形成された層間絶縁膜68上には、層間絶縁膜76が形成されている。層間絶縁膜76には、配線層74に接続されたコンタクトプラグ80が埋め込まれている。コンタクトプラグ80が埋め込まれた層間絶縁膜76上には、コンタクトプラグ80に接続された配線層82が形成されている。

【0021】

配線層82が形成された層間絶縁膜76上には、層間絶縁膜84が形成されている。層間絶縁膜84には、配線層82に接続されたコンタクトプラグ88が埋め込まれている。コンタクトプラグ88が埋め込まれた層間絶縁膜84上には、コンタクトプラグ88に接続された配線層90が形成されている。

【0022】

配線層90が形成された層間絶縁膜84上には、パッシベーション膜92が形成されている。

【0023】

チャージ蓄積用素子64のプレート電極48と分離用素子66のソース/ドレイン領域58の一方とは、コンタクトプラグ72,80,88、配線層74,82,90を介して電気的に接続されている。

【0024】

チャージ蓄積用素子64に接続される配線層74,82,90と、分離用素子66のソース/ドレイン領域58の他方及び周辺トランジスタ62に接続される配線層74,82,90とは、一定以上の間隔を空けて配置されている。これは、チャージ蓄積用素子64に蓄積されたチャージが、隣接するデバイス機能素子形成領域14の配線層74,82,90に放電され、デバイス機能素子にチャージダメージを与えるのを防止するためである。チャージの放電を防止するに好適な配線層74,82,90の間隔は、配線層の設計ルールや層間絶縁膜材料等に応じて変化するため一概に規定することはできないが、例えば、各配線層に許される最小ピッチの2倍以上の間隔等と規定することができる。

【0025】

チャージ蓄積用素子64は、製造過程において発生するチャージを蓄積するためのものであり、できるかぎり大容量とすることが望ましい。

【0026】

また、チャージ蓄積用素子64に接続される配線は、各製造過程においてチャージを取り込みやすいパターンとされている。具体的には、チャージ蓄積用素子64に接続されるコンタクトプラグ72,80,88、配線層74,82,90のそれぞれは、デバイス機能素子に接続されるコンタクトプラグ72,80,88、配線層74,82,90よりもアンテナ比が大きくなるように形成されている。アンテナ比とは、プラズマプロセス中にチャージされる配線層やコンタクトプラグなどの表面積と、それに接続されるゲート電極の面積との比である。

【0027】

すなわち、チャージ蓄積用素子に接続されるコンタクトプラグ72のチャージ蓄積用素子64に対するアンテナ比は、デバイス機能素子に接続されるコンタクトプラグ72のデバイス機能素子に対するアンテナ比よりも大きくなっている。また、チャージ蓄積用素子に接続されるコンタクトプラグ80のチャージ蓄積用素子64に対するアンテナ比は、デバイス機能素子に接続されるコンタクトプラグ80のデバイス機能素子に対するアンテナ比よりも大きくなっている。また、チャージ蓄積用素子に接続されるコンタクトプラグ88のチャージ蓄積用素子64に対するアンテナ比は、デバイス機能素子に接続されるコンタクトプラグ88のデバイス機能素子に対するアンテナ比よりも大きくなっている。

【0028】

同様に、チャージ蓄積用素子に接続される配線層74のチャージ蓄積用素子64に対するアンテナ比は、デバイス機能素子に接続される配線層74のデバイス機能素子に対するアンテナ比よりも大きくなっている。また、チャージ蓄積用素子に接続される配線層82のチャージ蓄積用素子64に対するアンテナ比は、デバイス機能素子に接続される配線層82のデバイス機能素子に対するアンテナ比よりも大きくなっている。また、チャージ蓄積用素子に接続される配線層90のチャージ蓄積用素子64に対するアンテナ比は、デバイス機能素子に接続される配線層90のデバイス機能素子に対するアンテナ比よりも大きくなっている。

【0029】

チャージ蓄積用素子64に接続されるコンタクトプラグ72,80,88、配線層74,82,90のアンテナ比を大きくすることにより、チャージ蓄積用素子64により多くのチャージが引き寄せられる。これにより、デバイス機能素子に接続されるコンタクトプラグ72,80,88、配線層74,82,90に引き寄せられるチャージを減らすことができ、デバイス機能素子のチャージダメージを低減することができる。

【0030】

また、チャージ蓄積用素子64のプレート電極48には、分離用素子66が接続されている。半導体装置の完成後に分離用素子66の書き込みを行いオフ状態(高閾値電圧状態)にしておくことにより、チャージ蓄積用素子64をデバイス機能素子から電気的に分離することができる。これにより、チャージ蓄積用素子64に蓄積されたチャージが放電されてデバイス機能素子にダメージを与えることを防止することができる。特に、分離用素子66としてフラッシュメモリのような電気的に書き換え可能な不揮発メモリトランジスタを用いることにより、ヒューズの切断によって素子間を分離する場合よりも容易に素子間を分離することができる。

【0031】

次に、本実施形態による半導体装置の製造方法について図2乃至図14を用いて説明する。

【0032】

まず、例えばP型のシリコン基板10に、例えばSTI法により、活性領域を画定する素子分離絶縁膜12を形成する。ここでは、素子分離絶縁膜12により、デバイス機能素子形成領域14、チャージ蓄積用素子形成領域16、分離用素子形成領域18を画定するものとする。

【0033】

なお、メモリセル領域に形成されるメモリトランジスタの製造方法は、分離用素子形成領域18に形成される分離用素子66の製造方法と基本的に同じであるため、ここでは説明を省略する。以下の製造方法の説明において、デバイス機能素子形成領域14は、周辺回路領域を表すものとし、メモリセル領域が含まれないものとする。

【0034】

次いで、例えば熱酸化法により、素子分離絶縁膜12により画定されたシリコン基板10の活性領域にシリコン酸化膜を形成し、シリコン酸化膜の保護絶縁膜20を形成する(図2)。

【0035】

次いで、フォトリソグラフィ及びイオン注入により、各活性領域に所定のウェルを形成する。例えば、デバイス機能素子形成領域14のシリコン基板10内にPウェル22を形成し、チャージ蓄積用素子形成領域16のシリコン基板10内にPウェル24を形成し、分離用素子形成領域18のシリコン基板10内にPウェル26を形成する(図3)。

【0036】

なお、Pウェル22,24,26を形成する際には、閾値電圧制御用のチャネル不純物層等の必要な不純物層も形成する。Pウェル26は、Nウェル(図示せず)で囲まれた二重ウェルとしてもよい。

【0037】

次いで、例えば弗酸水溶液を用いたウェットエッチングにより、保護絶縁膜20を除去する。

【0038】

次いで、例えば熱酸化法により、素子分離絶縁膜12により画定されたシリコン基板10の表面にシリコン酸化膜を形成し、シリコン酸化膜のトンネルゲート絶縁膜28を形成する。

【0039】

次いで、全面に、例えばCVD法により、フローティングゲート40となるポリシリコン膜30を堆積する。

【0040】

次いで、フォトリソグラフィ及びドライエッチングにより、ポリシリコン膜30をパターニングし、チャージ蓄積用素子形成領域16及びデバイス機能素子形成領域14のポリシリコン膜30を除去する(図4)。この際、分離用素子形成領域18では、コントロールゲート(ワード線)42の延在する方向にポリシリコン膜30を分離しておくなど、ポリシリコン膜30を所定の形状にパターニングする。

【0041】

次いで、全面に、例えばCVD法によりシリコン酸化膜を、例えばCVD法により膜厚シリコン窒化膜を、例えば熱酸化法によりシリコン酸化膜を、順次形成する。これにより、シリコン酸化膜/シリコン窒化膜/シリコン酸化膜構造のONO膜32を形成する。

【0042】

次いで、フォトリソグラフィ及びドライエッチングにより、ONO膜32をパターニングし、チャージ蓄積用素子形成領域16及びデバイス機能素子形成領域14のONO膜32を除去する(図5)。なお、Pウェル22,24は、本工程の後に形成するようにしてもよい。

【0043】

次いで、例えば弗酸水溶液を用いたウェットエッチングにより、チャージ蓄積用素子形成領域16及びデバイス機能素子形成領域14のトンネルゲート絶縁膜28を除去する。

【0044】

次いで、例えば熱酸化法により、シリコン基板10の表面にシリコン酸化膜を形成し、チャージ蓄積用素子形成領域16にキャパシタ誘電体膜34を形成し、デバイス機能素子形成領域14に周辺トランジスタ62のゲート絶縁膜36を形成する。

【0045】

次いで、全面に、例えばCVD法により、分離用素子66のコントロールゲート42、チャージ蓄積用素子64のプレート電極48、周辺トランジスタ62のゲート電極50となるポリシリコン膜38を堆積する(図6)。

【0046】

次いで、フォトリソグラフィ及びドライエッチングにより、分離用素子形成領域18のポリシリコン膜38、ONO膜32、ポリシリコン膜30をパターニングする。これにより、ポリシリコン膜30により形成されたフローティングゲート40とポリシリコン膜38により形成されたコントロールゲート42とを有する分離用素子66のスタックゲートを形成する(図7)。

【0047】

次いで、分離用素子形成領域18に、スタックゲートをマスクとしてイオン注入を行い、スタックゲートの両側のシリコン基板10内に、不純物拡散領域44を形成する。

【0048】

次いで、例えばCVD法によりシリコン窒化膜を堆積した後、このシリコン窒化膜をエッチバックし、スタックゲートの側壁部分に、シリコン窒化膜のサイドウォールスペーサ46を形成する(図8)。

【0049】

次いで、フォトリソグラフィ及びドライエッチングにより、チャージ蓄積用素子形成領域16及びデバイス機能素子形成領域14のポリシリコン膜38をパターニングし、チャージ蓄積用素子64のプレート電極48及び周辺トランジスタのゲート電極50を形成する。

【0050】

次いで、デバイス機能素子形成領域14に、ゲート電極50をマスクとしてイオン注入を行い、ゲート電極50の両側のシリコン基板10内に、不純物拡散領域52を形成する(図9)。

【0051】

次いで、例えばCVD法によりシリコン窒化膜を堆積した後、このシリコン窒化膜をエッチバックし、スタックゲートの側壁部分に、シリコン窒化膜のサイドウォールスペーサ54を形成する。

【0052】

次いで、分離用素子形成領域18にスタックゲートをマスクとして、デバイス機能素子形成領域14にゲート電極50をマスクとして、それぞれイオン注入を行い、スタックゲート及びゲート電極50の両側のシリコン基板10内に、不純物拡散領域56を形成する。

【0053】

これにより、分離用素子形成領域18に、不純物拡散領域44,56により、分離用素子66のソース/ドレイン領域58を形成する。また、デバイス機能素子形成領域14に、不純物拡散領域52,56により、周辺トランジスタ62のソース/ドレイン領域60を形成する。

【0054】

こうして、デバイス機能素子形成領域14に、ゲート電極50及びソース/ドレイン領域60を含む周辺トランジスタ62を形成する。また、チャージ蓄積用素子形成領域16に、キャパシタ誘電体膜34を挟んで形成されたPウェル24及びプレート電極48を下部電極及び上部電極とするMOSキャパシタ構造のチャージ蓄積用素子64を形成する。また、分離用素子形成領域18に、フローティングゲート40及びコントロールゲート42を有するスタックゲートとソース/ドレイン領域58とを含む分離用素子66を形成する(図10)。

【0055】

次いで、これら素子が形成されたシリコン基板10上に、例えばCVD法によりシリコン窒化膜及びシリコン酸化膜を堆積した後、例えばCMP法によりシリコン酸化膜の表面を平坦化し、シリコン酸化膜/シリコン窒化膜構造の層間絶縁膜68を形成する。

【0056】

次いで、フォトリソグラフィ及びドライエッチングにより、層間絶縁膜68に、プレート電極48、ソース/ドレイン領域58,60等に達するコンタクトホール70を形成する。

【0057】

次いで、全面にバリアメタル及びタングステン膜を堆積後、これら導電膜をエッチバックし、コンタクトホール70内に埋め込まれたコンタクトプラグ72を形成する。

【0058】

この際、チャージ蓄積用素子形成領域16に形成されたコンタクトプラグ72のアンテナ比が、デバイス機能素子形成領域14に形成されたコンタクトプラグ72のアンテナ比よりも大きくなるようにする。例えば、チャージ蓄積用素子形成領域16に形成されたコンタクトプラグ72の平面密度が、デバイス機能素子形成領域14に形成されたコンタクトプラグ72の平面密度よりも大きくなるようにする。

【0059】

次いで、例えばスパッタ法等により導電膜を堆積後、フォトリソグラフィ及びドライエッチングによりこの導電膜をパターニングし、コンタクトプラグ72に接続された配線層74を形成する(図11)。

【0060】

この際、チャージ蓄積用素子形成領域16に形成された配線層74のアンテナ比が、デバイス機能素子形成領域14に形成された配線層74のアンテナ比よりも大きくなるようにする。例えば、チャージ蓄積用素子形成領域16に形成された配線層74の配線幅や平面密度が、デバイス機能素子形成領域14に形成された配線層74の配線幅や平面密度よりも大きくなるようにする。また、チャージ蓄積用素子形成領域16に形成される配線層74と、デバイス機能素子形成領域14に形成される配線層74とは、上述の所定値以上の間隔を空けて配置する。

【0061】

配線形成工程では、プラズマCVD、スパッタリング、プラズマエッチング等のプラズマプロセスが用いられる。これら工程の処理中にコンタクトプラグ72や配線層74がプラズマに曝されると、これら導電体がアンテナとなり、コンタクトプラグ72や配線層74内にチャージが誘起される。基板に電気的に接続されていないフローティング状態のコンタクトプラグ72や配線層74では、チャージの抜け道が存在しないため電荷が蓄積され、チャージアップが生じる。

【0062】

例えば、プラズマに曝されたコンタクトプラグ72や配線層74には、プラスのチャージが誘起される。そしてこれに伴い、絶縁膜を介してこれらコンタクトプラグ72や配線層74に接続された電極(ゲート電極、プレート電極等)に対向するシリコン基板10表面には、マイナスのチャージが誘起される。

【0063】

このとき、デバイス機能素子形成領域14に形成されたコンタクトプラグ72又は配線層74のアンテナ比よりも大きいアンテナ比を有するコンタクトプラグ72又は配線層74がチャージ蓄積用素子形成領域16に形成されていると、容量の大きいチャージ蓄積用素子64に多くのチャージが引き寄せられる。これにより、デバイス機能素子に引き寄せられるチャージを減らすことができ、デバイス機能素子のチャージダメージを低減することができる。

【0064】

次いで、配線層74が形成された層間絶縁膜68上に、例えばCVD法によりシリコン窒化膜及びシリコン酸化膜を堆積した後、例えばCMP法によりシリコン酸化膜の表面を平坦化し、シリコン酸化膜/シリコン窒化膜構造の層間絶縁膜76を形成する。

【0065】

次いで、フォトリソグラフィ及びドライエッチングにより、層間絶縁膜76に、配線層74に達するコンタクトホール78を形成する。

【0066】

次いで、全面にバリアメタル及びタングステン膜を堆積後、これら導電膜をエッチバックし、コンタクトホール78内に埋め込まれたコンタクトプラグ80を形成する。

【0067】

この際、チャージ蓄積用素子形成領域16に形成されたコンタクトプラグ80のアンテナ比が、デバイス機能素子形成領域14に形成されたコンタクトプラグ80のアンテナ比よりも大きくなるようにする。

【0068】

次いで、例えばスパッタ法等により導電膜を堆積後、フォトリソグラフィ及びドライエッチングによりこの導電膜をパターニングし、コンタクトプラグ80に接続された配線層82を形成する(図12)。

【0069】

この際、チャージ蓄積用素子形成領域16に形成された配線層82のアンテナ比が、デバイス機能素子形成領域14に形成された配線層82のアンテナ比よりも大きくなるようにする。また、チャージ蓄積用素子形成領域16に形成される配線層82と、デバイス機能素子形成領域14に形成される配線層82とは、上述の所定値以上の間隔を空けて配置する。

【0070】

デバイス機能素子形成領域14に形成されたコンタクトプラグ80又は配線層82のアンテナ比よりも大きいアンテナ比を有するコンタクトプラグ80又は配線層82がチャージ蓄積用素子形成領域16に形成しておくことにより、容量の大きいチャージ蓄積用素子64に多くのチャージが引き寄せられる。これにより、デバイス機能素子に引き寄せられるチャージを減らすことができ、デバイス機能素子のチャージダメージを低減することができる。

【0071】

次いで、配線層82が形成された層間絶縁膜76上に、例えばCVD法によりシリコン窒化膜及びシリコン酸化膜を堆積した後、例えばCMP法によりシリコン酸化膜の表面を平坦化し、シリコン酸化膜/シリコン窒化膜構造の層間絶縁膜84を形成する。

【0072】

次いで、フォトリソグラフィ及びドライエッチングにより、層間絶縁膜84に、配線層82に達するコンタクトホール86を形成する。

【0073】

次いで、全面にバリアメタル及びタングステン膜を堆積後、これら導電膜をエッチバックし、コンタクトホール86内に埋め込まれたコンタクトプラグ88を形成する。

【0074】

この際、チャージ蓄積用素子形成領域16に形成されたコンタクトプラグ88のアンテナ比が、デバイス機能素子形成領域14に形成されたコンタクトプラグ88のアンテナ比よりも大きくなるようにする。

【0075】

次いで、例えばスパッタ法等により導電膜を堆積後、フォトリソグラフィ及びドライエッチングによりこの導電膜をパターニングし、コンタクトプラグ88に接続された配線層90を形成する(図13)。

【0076】

この際、チャージ蓄積用素子形成領域16に形成された配線層90のアンテナ比が、デバイス機能素子形成領域14に形成された配線層90のアンテナ比よりも大きくなるようにする。また、チャージ蓄積用素子形成領域16に形成される配線層90と、デバイス機能素子形成領域14に形成される配線層90とは、上述の所定値以上の間隔を空けて配置する。

【0077】

デバイス機能素子形成領域14に形成されたコンタクトプラグ88又は配線層90のアンテナ比よりも大きいアンテナ比を有するコンタクトプラグ88又は配線層90がチャージ蓄積用素子形成領域16に形成しておくことにより、容量の大きいチャージ蓄積用素子64に多くのチャージが引き寄せられる。これにより、デバイス機能素子に引き寄せられるチャージを減らすことができ、デバイス機能素子のチャージダメージを低減することができる。

【0078】

次いで、全面に、例えばCVD法により、シリコン酸化膜とシリコン窒化膜とを堆積し、シリコン窒化膜/シリコン酸化膜構造のパッシベーション膜92を形成し、本実施形態による半導体装置を完成する(図14)。

【0079】

この後、メモリトランジスタの機能試験等の工程において、フラッシュメモリの書き込み手法と同様にして、分離用素子66のフローティングゲート40に電子を注入し、分離用素子66にオフ状態を書き込む。これにより、チャージ蓄積用素子64をデバイス機能素子から分離することができ、チャージ蓄積用素子64に蓄積されたチャージが放電されてデバイス機能素子にダメージを与えることを防止することができる。

【0080】

分離用素子66への書き込みは、メモリトランジスタの機能試験等の工程において行うことができるため、チャージ蓄積用素子64を分離するための特別な工程を追加する必要はない。

【0081】

また、チャージ蓄積用素子形成領域16に形成された配線層74,82,90は、デバイス機能素子形成領域14に形成された配線層74,82,90から所定値以上の間隔を空けて配置している。これにより、チャージ蓄積用素子形成領域16に蓄積されたチャージがデバイス機能素子形成領域14方向に放電されてデバイス機能素子にチャージダメージを与えるのを防止することができる。

【0082】

このように、本実施形態によれば、デバイス機能素子とチャージ蓄積用素子との間に電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子を設けるので、デバイス機能素子とチャージ蓄積用素子とを容易に分離することができる。また、分離用素子はメモリトランジスタと同時に形成することができ、分離用素子の書き込みはメモリトランジスタの機能試験時に行うことができるため、製造工程を増加することも防止することができる。

【0083】

[第2実施形態]

第2実施形態による半導体装置及びその製造方法について図15及び図16を用いて説明する。図1乃至図14に示す第1実施形態による半導体装置及びその製造方法と同一の構成要素には同一の符号を付し説明を省略し又は簡潔にする。

【0084】

図15は、本実施形態による半導体装置の構造を示す概略断面図である。図16は、本実施形態による半導体装置のチャージ蓄積用素子の構造を示す斜視図である。

【0085】

本実施形態による半導体装置は、図15に示すように、配線層74,82,90及びコンタクトプラグ80,88により形成されたMIM(Metal-Insulator-Metal)キャパシタ構造のチャージ蓄積用素子64を有している。

【0086】

チャージ蓄積用素子形成領域16に形成された配線層74は、例えば図16に示すように、櫛歯型を有し互いに噛み合うように配置された2つの電極パターン74A,74Bを有している。同様に、チャージ蓄積用素子形成領域16に形成された配線層82は、櫛歯型を有し互いに噛み合うように配置された2つの電極パターン82A,82Bを有している。電極パターン74Aと電極パターン82Aとは、コンタクトプラグ80によって接続されている。同様に、電極パターン74Bと電極パターン82Bとは、コンタクトプラグ80によって接続されている。

【0087】

図16には示していないが、チャージ蓄積用素子形成領域16に形成された配線層90も配線層74,82と同様のパターンを有しており、コンタクトプラグによって配線層82に接続されている。

【0088】

こうして、電極パターン72A,80A,…及びこれらを接続するコンタクトプラグ80,82を一方の電極とし、電極パターン72B,80B,…及びこれらを接続するコンタクトプラグ80,82を他方の電極とし、層間絶縁膜76,84をキャパシタ誘電体膜とするチャージ蓄積用素子64が形成されている。

【0089】

チャージ蓄積用素子64は、第1実施形態による半導体装置と同様、分離用素子66に接続されている。チャージ蓄積用素子64は、少なくとも一方の電極を分離用素子66に接続する。他方の電極は、前記一方の電極に接続された分離用素子66とは別の分離用素子66に接続してもよいし、シリコン基板10に接続してもよいし、フローティング状態としてもよい。

【0090】

チャージ蓄積用素子64をMIM構造のキャパシタにより形成することによっても、第1実施形態と同様の効果を得ることができる。

【0091】

本実施形態による半導体装置の製造方法は、配線層72,80,88等のパターンが異なるほかは、第1実施形態による半導体装置の製造方法と同様である。

【0092】

このように、本実施形態によれば、デバイス機能素子とチャージ蓄積用素子との間に電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子を設けるので、デバイス機能素子とチャージ蓄積用素子とを容易に分離することができる。また、分離用素子はメモリトランジスタと同時に形成することができ、分離用素子の書き込みはメモリトランジスタの機能試験時に行うことができるため、製造工程を増加することも防止することができる。

【0093】

[変形実施形態]

上記実施形態に限らず種々の変形が可能である。

【0094】

例えば、上記実施形態では、分離用素子66としてスタックゲート構造の不揮発メモリトランジスタを示したが、分離用素子66はこれに限定されるものではない。分離用素子66は、電気的に書き換え可能な不揮発性メモリトランジスタであればよく、例えば、SONOS型の不揮発性メモリトランジスタを用いるようにしてもよい。

【0095】

また、上記実施形態では、3層の配線層により半導体装置を製造する場合を示したが、配線層の層数は3層に限定されるものではなく、適宜増減することができる。

【0096】

また、上記第1実施形態では、MISキャパシタの基板側の導電型をP型(Pウェル24)としたが、N型としてもよい。

【0097】

また、上記第2実施形態では、櫛歯型の電極パターンを有するMIMキャパシタを形成したが、電極パターンはこれに限定されるものではない。

【0098】

また、上記実施形態では、分離用素子形成領域18の活性領域内に分離用素子66を設けているが、デバイス機能素子形成領域14内の一部に分離用素子66を設けるようにしてもよい。例えば、メモリセルトランジスタのアレイの端部に、分離用素子66を設けるようにしてもよい。

【0099】

また、上記実施形態では、分離用素子形成領域18に、直列接続した2つの分離用素子66を設けた場合を示したが、分離用素子66は必ずしも2つである必要はない。分離用素子形成領域18に設ける分離用素子66は、1つでもよいし、3つ以上直列接続してもよい。

【0100】

また、上記実施形態に記載した半導体装置の構造、構成材料、製造条件等は、一例を示したものにすぎず、当業者の技術常識等に応じて適宜修正や変更が可能である。

【0101】

以上の実施形態に関し、更に以下の付記を開示する。

【0102】

(付記1) 半導体基板上に形成されたデバイス機能素子と、

前記半導体基板上に形成されたチャージ蓄積用素子と、

前記半導体基板上に形成され、前記デバイス機能素子と前記チャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子と

を有することを特徴とする半導体装置。

【0103】

(付記2) 付記1記載の半導体装置において、

前記デバイス機能素子に接続され、前記デバイス機能素子に対して第1のアンテナ比を有する第1の配線と、

前記チャージ蓄積用素子に接続され、前記チャージ蓄積用素子に対して前記第1のアンテナ比よりも大きい第2のアンテナ比を有する第2の配線と

を更に有することを特徴とする半導体装置。

【0104】

(付記3) 付記2記載の半導体装置において、

前記第1の配線層と前記第2の配線層とは、前記第1の配線層及び前記第2の配線層に許容される最小間隔の2倍以上離間している

ことを特徴とする半導体装置。

【0105】

(付記4) 付記1乃至3のいずれか1項に記載の半導体装置において、

前記チャージ蓄積用素子は、前記半導体基板上に形成された誘電体膜と、前記誘電体膜上に形成されたプレート電極とを含むMISキャパシタである

ことを特徴とする半導体装置。

【0106】

(付記5) 付記1乃至3のいずれか1項に記載の半導体装置において、

前記チャージ蓄積用素子は、前記半導体基板上に形成された絶縁膜に埋め込まれた配線層により形成されたMIMキャパシタである

ことを特徴とする半導体装置。

【0107】

(付記6) 半導体基板上に、デバイス機能素子を形成する工程と、

前記半導体基板上に、チャージ蓄積用素子を形成する工程と、

前記半導体基板上に、前記デバイス機能素子と前記チャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子を形成する工程と

を有することを特徴とする半導体装置の製造方法。

【0108】

(付記7) 付記6記載の半導体装置の製造方法において、

前記デバイス機能素子に接続され、前記デバイス機能素子に対して第1のアンテナ比を有する第1の配線と、前記チャージ蓄積用素子に接続され、前記チャージ蓄積用素子に対して前記第1のアンテナ比よりも大きい第2のアンテナ比を有する第2の配線とを形成する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【0109】

(付記8) 付記6記載の半導体装置の製造方法において、

前記分離用素子にオフ状態を書き込み、前記デバイス機能素子と前記チャージ蓄積用素子とを電気的に分離する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【符号の説明】

【0110】

10…シリコン基板

12…素子分離絶縁膜

14…デバイス機能素子形成領域

16…チャージ蓄積用素子形成領域

18…分離用素子形成領域

20…保護絶縁膜

22,24,26…Pウェル

28…トンネルゲート絶縁膜

30,38…ポリシリコン膜

32…ONO膜

34…キャパシタ誘電体膜

36…ゲート絶縁膜

40…フローティングゲート

42…コントロールゲート

44,52,56…不純物拡散領域

46,54…サイドウォールスペーサ

48…プレート電極

50…ゲート電極

58,60…ソース/ドレイン領域

62…周辺トランジスタ

64…チャージ蓄積用素子

66…分離用素子

68,76,84…層間絶縁膜

70,78,86…コンタクトホール

72,80,88…コンタクトプラグ

74,82,90…配線層

92…パッシベーション膜

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体装置の製造工程では、ドライエッチング装置や成膜装置などの製造装置において発生するチャージに半導体基板が曝され、製造過程の素子がダメージを受けることがある。半導体装置の高集積化に伴う素子の微細化により、半導体装置の製造過程で生じるチャージダメージ耐性もますます厳しくなっている。

【0003】

このようなチャージダメージを回避する手段として、半導体装置のデバイス機能素子以外にチャージ蓄積用の容量素子を設け、製造装置で発生したチャージを蓄積する方法が提案されている。また、半導体装置の製造後にヒューズを切断してチャージ蓄積用の容量素子を切り離し、容量素子からチャージが放電されてデバイス機能素子に影響を与えることを防止する方法が提案されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003−347303号公報

【特許文献2】特開2007−194424号公報

【特許文献3】特開2009−076777号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、ヒューズを切断してチャージ蓄積用の容量素子を切り離す方法は、ヒューズを切断する工程を別途設ける必要があり、製造工程が追加し、ひいては製造コストが増大することがあった。

【0006】

本発明の目的は、半導体装置の製造過程におけるチャージダメージを防止するとともに、半導体装置の製造後におけるチャージの放電を防止しうる半導体装置及びその製造方法を提供することにある。

【課題を解決するための手段】

【0007】

実施形態の一観点によれば、半導体基板上に形成されたデバイス機能素子と、前記半導体基板上に形成されたチャージ蓄積用素子と、前記半導体基板上に形成され、前記デバイス機能素子と前記チャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する半導体装置が提供される。

【0008】

また、実施形態の他の観点によれば、半導体基板上に、デバイス機能素子を形成する工程と、前記半導体基板上に、チャージ蓄積用素子を形成する工程と、前記半導体基板上に、前記デバイス機能素子と前記チャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子を形成する工程と、前記分離用素子にオフ状態を書き込み、前記デバイス機能素子と前記チャージ蓄積用素子とを電気的に分離する工程とを有する半導体装置の製造方法が提供される。

【発明の効果】

【0009】

開示の半導体装置及びその製造方法によれば、デバイス機能素子とチャージ蓄積用素子との間に電気的に書き換え可能な不揮発性メモリトランジスタの分離用素子を設けるので、デバイス機能素子とチャージ蓄積用素子とを容易に分離することができる。また、分離用素子はメモリトランジスタと同時に形成することができ、また、分離用素子の書き込みはメモリトランジスタの機能試験時に行うことができるため、製造工程を増加することなくデバイス機能素子とチャージ蓄積用素子とを確実に分離することができる。

【図面の簡単な説明】

【0010】

【図1】図1は、第1実施形態による半導体装置の構造を示す概略断面図である。

【図2】図2は、第1実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

【図3】図3は、第1実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

【図4】図4は、第1実施形態による半導体装置の製造方法を示す工程断面図(その3)である。

【図5】図5は、第1実施形態による半導体装置の製造方法を示す工程断面図(その4)である。

【図6】図6は、第1実施形態による半導体装置の製造方法を示す工程断面図(その5)である。

【図7】図7は、第1実施形態による半導体装置の製造方法を示す工程断面図(その6)である。

【図8】図8は、第1実施形態による半導体装置の製造方法を示す工程断面図(その7)である。

【図9】図9は、第1実施形態による半導体装置の製造方法を示す工程断面図(その8)である。

【図10】図10は、第1実施形態による半導体装置の製造方法を示す工程断面図(その9)である。

【図11】図11は、第1実施形態による半導体装置の製造方法を示す工程断面図(その10)である。

【図12】図12は、第1実施形態による半導体装置の製造方法を示す工程断面図(その11)である。

【図13】図13は、第1実施形態による半導体装置の製造方法を示す工程断面図(その12)である。

【図14】図14は、第1実施形態による半導体装置の製造方法を示す工程断面図(その13)である。

【図15】図15は、第2実施形態による半導体装置の構造を示す概略断面図である。

【図16】図16は、第2実施形態による半導体装置のチャージ蓄積用素子の構造を示す斜視図である。

【発明を実施するための形態】

【0011】

[第1実施形態]

第1実施形態による半導体装置及びその製造方法について図1乃至図14を用いて説明する。

【0012】

図1は、本実施形態による半導体装置の構造を示す概略断面図である。図2乃至図14は、本実施形態による半導体装置の製造方法を示す工程断面図である。

【0013】

はじめに、本実施形態による半導体装置の構造について図1を用いて説明する。

【0014】

シリコン基板10には、活性領域を画定する素子分離絶縁膜12が形成されている。図1において各活性領域は、図面右側から順に、デバイス機能素子形成領域14、チャージ蓄積用素子形成領域16、及び分離用素子形成領域18を表している。デバイス機能素子形成領域14は、メモリセルや周辺回路などの半導体装置の実質的な役割を担う素子が設けられる領域である。チャージ蓄積用素子形成領域16は、製造過程で発生するチャージを蓄積するチャージ蓄積用素子が形成される領域である。分離用素子形成領域18は、デバイス機能素子とチャージ蓄積用素子とを分離するための分離用素子が形成される領域である。

【0015】

デバイス機能素子形成領域14には、メモリセルや周辺回路などの機能素子が形成されるが、ここでは一例としてN型の周辺トランジスタ62が形成されているものとして説明する。

【0016】

デバイス機能素子形成領域14のシリコン基板10内には、Pウェル22が形成されている。Pウェル22が形成されたシリコン基板10上には、ゲート絶縁膜36を介してゲート電極50が形成されている。ゲート電極50の両側のシリコン基板10内には、ソース/ドレイン領域60が形成されている。こうして、デバイス機能素子形成領域14には、ゲート電極50及びソース/ドレイン領域60を有する周辺トランジスタ62が形成されている。

【0017】

チャージ蓄積用素子形成領域16のシリコン基板10内には、Pウェル24が形成されている。Pウェル24が形成されたシリコン基板10上は、キャパシタ誘電体膜34を介してプレート電極48が形成されている。こうして、チャージ蓄積用素子形成領域16には、下部電極としてのPウェル24と、キャパシタ誘電体膜34と、上部電極としてのプレート電極48とを有するMISキャパシタ構造のチャージ蓄積用素子64が形成されている。

【0018】

分離用素子形成領域18のシリコン基板10内には、Pウェル26が形成されている。Pウェル26が形成されたシリコン基板10上には、トンネルゲート絶縁膜28と、フローティングゲート40と、ONO膜32と、コントロールゲート42とが順次積層されたスタックゲートが形成されている。スタックゲートの両側のシリコン基板10内には、ソース/ドレイン領域58が形成されている。こうして、分離用素子形成領域18には、スタックゲート及びソース/ドレイン領域58を有する分離用素子66が形成されている。分離用素子66は、デバイス機能素子とチャージ蓄積用素子との間に接続して形成されている。分離用素子66は、図示しないメモリセル領域に形成されるメモリトランジスタと同様の構造及び機能を有しており、メモリトランジスタと同様に書き込み動作を行うことができるものである。

【0019】

周辺トランジスタ62、チャージ蓄積用素子64、分離用素子66が形成されたシリコン基板10上には、層間絶縁膜68が形成されている。層間絶縁膜68には、プレート電極48、ソース/ドレイン領域58,60等に接続されたコンタクトプラグ72が埋め込まれている。コンタクトプラグ72が埋め込まれた層間絶縁膜68上には、コンタクトプラグ72に接続された配線層74が形成されている。

【0020】

配線層74が形成された層間絶縁膜68上には、層間絶縁膜76が形成されている。層間絶縁膜76には、配線層74に接続されたコンタクトプラグ80が埋め込まれている。コンタクトプラグ80が埋め込まれた層間絶縁膜76上には、コンタクトプラグ80に接続された配線層82が形成されている。

【0021】

配線層82が形成された層間絶縁膜76上には、層間絶縁膜84が形成されている。層間絶縁膜84には、配線層82に接続されたコンタクトプラグ88が埋め込まれている。コンタクトプラグ88が埋め込まれた層間絶縁膜84上には、コンタクトプラグ88に接続された配線層90が形成されている。

【0022】

配線層90が形成された層間絶縁膜84上には、パッシベーション膜92が形成されている。

【0023】

チャージ蓄積用素子64のプレート電極48と分離用素子66のソース/ドレイン領域58の一方とは、コンタクトプラグ72,80,88、配線層74,82,90を介して電気的に接続されている。

【0024】

チャージ蓄積用素子64に接続される配線層74,82,90と、分離用素子66のソース/ドレイン領域58の他方及び周辺トランジスタ62に接続される配線層74,82,90とは、一定以上の間隔を空けて配置されている。これは、チャージ蓄積用素子64に蓄積されたチャージが、隣接するデバイス機能素子形成領域14の配線層74,82,90に放電され、デバイス機能素子にチャージダメージを与えるのを防止するためである。チャージの放電を防止するに好適な配線層74,82,90の間隔は、配線層の設計ルールや層間絶縁膜材料等に応じて変化するため一概に規定することはできないが、例えば、各配線層に許される最小ピッチの2倍以上の間隔等と規定することができる。

【0025】

チャージ蓄積用素子64は、製造過程において発生するチャージを蓄積するためのものであり、できるかぎり大容量とすることが望ましい。

【0026】

また、チャージ蓄積用素子64に接続される配線は、各製造過程においてチャージを取り込みやすいパターンとされている。具体的には、チャージ蓄積用素子64に接続されるコンタクトプラグ72,80,88、配線層74,82,90のそれぞれは、デバイス機能素子に接続されるコンタクトプラグ72,80,88、配線層74,82,90よりもアンテナ比が大きくなるように形成されている。アンテナ比とは、プラズマプロセス中にチャージされる配線層やコンタクトプラグなどの表面積と、それに接続されるゲート電極の面積との比である。

【0027】

すなわち、チャージ蓄積用素子に接続されるコンタクトプラグ72のチャージ蓄積用素子64に対するアンテナ比は、デバイス機能素子に接続されるコンタクトプラグ72のデバイス機能素子に対するアンテナ比よりも大きくなっている。また、チャージ蓄積用素子に接続されるコンタクトプラグ80のチャージ蓄積用素子64に対するアンテナ比は、デバイス機能素子に接続されるコンタクトプラグ80のデバイス機能素子に対するアンテナ比よりも大きくなっている。また、チャージ蓄積用素子に接続されるコンタクトプラグ88のチャージ蓄積用素子64に対するアンテナ比は、デバイス機能素子に接続されるコンタクトプラグ88のデバイス機能素子に対するアンテナ比よりも大きくなっている。

【0028】

同様に、チャージ蓄積用素子に接続される配線層74のチャージ蓄積用素子64に対するアンテナ比は、デバイス機能素子に接続される配線層74のデバイス機能素子に対するアンテナ比よりも大きくなっている。また、チャージ蓄積用素子に接続される配線層82のチャージ蓄積用素子64に対するアンテナ比は、デバイス機能素子に接続される配線層82のデバイス機能素子に対するアンテナ比よりも大きくなっている。また、チャージ蓄積用素子に接続される配線層90のチャージ蓄積用素子64に対するアンテナ比は、デバイス機能素子に接続される配線層90のデバイス機能素子に対するアンテナ比よりも大きくなっている。

【0029】

チャージ蓄積用素子64に接続されるコンタクトプラグ72,80,88、配線層74,82,90のアンテナ比を大きくすることにより、チャージ蓄積用素子64により多くのチャージが引き寄せられる。これにより、デバイス機能素子に接続されるコンタクトプラグ72,80,88、配線層74,82,90に引き寄せられるチャージを減らすことができ、デバイス機能素子のチャージダメージを低減することができる。

【0030】

また、チャージ蓄積用素子64のプレート電極48には、分離用素子66が接続されている。半導体装置の完成後に分離用素子66の書き込みを行いオフ状態(高閾値電圧状態)にしておくことにより、チャージ蓄積用素子64をデバイス機能素子から電気的に分離することができる。これにより、チャージ蓄積用素子64に蓄積されたチャージが放電されてデバイス機能素子にダメージを与えることを防止することができる。特に、分離用素子66としてフラッシュメモリのような電気的に書き換え可能な不揮発メモリトランジスタを用いることにより、ヒューズの切断によって素子間を分離する場合よりも容易に素子間を分離することができる。

【0031】

次に、本実施形態による半導体装置の製造方法について図2乃至図14を用いて説明する。

【0032】

まず、例えばP型のシリコン基板10に、例えばSTI法により、活性領域を画定する素子分離絶縁膜12を形成する。ここでは、素子分離絶縁膜12により、デバイス機能素子形成領域14、チャージ蓄積用素子形成領域16、分離用素子形成領域18を画定するものとする。

【0033】

なお、メモリセル領域に形成されるメモリトランジスタの製造方法は、分離用素子形成領域18に形成される分離用素子66の製造方法と基本的に同じであるため、ここでは説明を省略する。以下の製造方法の説明において、デバイス機能素子形成領域14は、周辺回路領域を表すものとし、メモリセル領域が含まれないものとする。

【0034】

次いで、例えば熱酸化法により、素子分離絶縁膜12により画定されたシリコン基板10の活性領域にシリコン酸化膜を形成し、シリコン酸化膜の保護絶縁膜20を形成する(図2)。

【0035】

次いで、フォトリソグラフィ及びイオン注入により、各活性領域に所定のウェルを形成する。例えば、デバイス機能素子形成領域14のシリコン基板10内にPウェル22を形成し、チャージ蓄積用素子形成領域16のシリコン基板10内にPウェル24を形成し、分離用素子形成領域18のシリコン基板10内にPウェル26を形成する(図3)。

【0036】

なお、Pウェル22,24,26を形成する際には、閾値電圧制御用のチャネル不純物層等の必要な不純物層も形成する。Pウェル26は、Nウェル(図示せず)で囲まれた二重ウェルとしてもよい。

【0037】

次いで、例えば弗酸水溶液を用いたウェットエッチングにより、保護絶縁膜20を除去する。

【0038】

次いで、例えば熱酸化法により、素子分離絶縁膜12により画定されたシリコン基板10の表面にシリコン酸化膜を形成し、シリコン酸化膜のトンネルゲート絶縁膜28を形成する。

【0039】

次いで、全面に、例えばCVD法により、フローティングゲート40となるポリシリコン膜30を堆積する。

【0040】

次いで、フォトリソグラフィ及びドライエッチングにより、ポリシリコン膜30をパターニングし、チャージ蓄積用素子形成領域16及びデバイス機能素子形成領域14のポリシリコン膜30を除去する(図4)。この際、分離用素子形成領域18では、コントロールゲート(ワード線)42の延在する方向にポリシリコン膜30を分離しておくなど、ポリシリコン膜30を所定の形状にパターニングする。

【0041】

次いで、全面に、例えばCVD法によりシリコン酸化膜を、例えばCVD法により膜厚シリコン窒化膜を、例えば熱酸化法によりシリコン酸化膜を、順次形成する。これにより、シリコン酸化膜/シリコン窒化膜/シリコン酸化膜構造のONO膜32を形成する。

【0042】

次いで、フォトリソグラフィ及びドライエッチングにより、ONO膜32をパターニングし、チャージ蓄積用素子形成領域16及びデバイス機能素子形成領域14のONO膜32を除去する(図5)。なお、Pウェル22,24は、本工程の後に形成するようにしてもよい。

【0043】

次いで、例えば弗酸水溶液を用いたウェットエッチングにより、チャージ蓄積用素子形成領域16及びデバイス機能素子形成領域14のトンネルゲート絶縁膜28を除去する。

【0044】

次いで、例えば熱酸化法により、シリコン基板10の表面にシリコン酸化膜を形成し、チャージ蓄積用素子形成領域16にキャパシタ誘電体膜34を形成し、デバイス機能素子形成領域14に周辺トランジスタ62のゲート絶縁膜36を形成する。

【0045】

次いで、全面に、例えばCVD法により、分離用素子66のコントロールゲート42、チャージ蓄積用素子64のプレート電極48、周辺トランジスタ62のゲート電極50となるポリシリコン膜38を堆積する(図6)。

【0046】

次いで、フォトリソグラフィ及びドライエッチングにより、分離用素子形成領域18のポリシリコン膜38、ONO膜32、ポリシリコン膜30をパターニングする。これにより、ポリシリコン膜30により形成されたフローティングゲート40とポリシリコン膜38により形成されたコントロールゲート42とを有する分離用素子66のスタックゲートを形成する(図7)。

【0047】

次いで、分離用素子形成領域18に、スタックゲートをマスクとしてイオン注入を行い、スタックゲートの両側のシリコン基板10内に、不純物拡散領域44を形成する。

【0048】

次いで、例えばCVD法によりシリコン窒化膜を堆積した後、このシリコン窒化膜をエッチバックし、スタックゲートの側壁部分に、シリコン窒化膜のサイドウォールスペーサ46を形成する(図8)。

【0049】

次いで、フォトリソグラフィ及びドライエッチングにより、チャージ蓄積用素子形成領域16及びデバイス機能素子形成領域14のポリシリコン膜38をパターニングし、チャージ蓄積用素子64のプレート電極48及び周辺トランジスタのゲート電極50を形成する。

【0050】

次いで、デバイス機能素子形成領域14に、ゲート電極50をマスクとしてイオン注入を行い、ゲート電極50の両側のシリコン基板10内に、不純物拡散領域52を形成する(図9)。

【0051】

次いで、例えばCVD法によりシリコン窒化膜を堆積した後、このシリコン窒化膜をエッチバックし、スタックゲートの側壁部分に、シリコン窒化膜のサイドウォールスペーサ54を形成する。

【0052】

次いで、分離用素子形成領域18にスタックゲートをマスクとして、デバイス機能素子形成領域14にゲート電極50をマスクとして、それぞれイオン注入を行い、スタックゲート及びゲート電極50の両側のシリコン基板10内に、不純物拡散領域56を形成する。

【0053】

これにより、分離用素子形成領域18に、不純物拡散領域44,56により、分離用素子66のソース/ドレイン領域58を形成する。また、デバイス機能素子形成領域14に、不純物拡散領域52,56により、周辺トランジスタ62のソース/ドレイン領域60を形成する。

【0054】

こうして、デバイス機能素子形成領域14に、ゲート電極50及びソース/ドレイン領域60を含む周辺トランジスタ62を形成する。また、チャージ蓄積用素子形成領域16に、キャパシタ誘電体膜34を挟んで形成されたPウェル24及びプレート電極48を下部電極及び上部電極とするMOSキャパシタ構造のチャージ蓄積用素子64を形成する。また、分離用素子形成領域18に、フローティングゲート40及びコントロールゲート42を有するスタックゲートとソース/ドレイン領域58とを含む分離用素子66を形成する(図10)。

【0055】

次いで、これら素子が形成されたシリコン基板10上に、例えばCVD法によりシリコン窒化膜及びシリコン酸化膜を堆積した後、例えばCMP法によりシリコン酸化膜の表面を平坦化し、シリコン酸化膜/シリコン窒化膜構造の層間絶縁膜68を形成する。

【0056】

次いで、フォトリソグラフィ及びドライエッチングにより、層間絶縁膜68に、プレート電極48、ソース/ドレイン領域58,60等に達するコンタクトホール70を形成する。

【0057】

次いで、全面にバリアメタル及びタングステン膜を堆積後、これら導電膜をエッチバックし、コンタクトホール70内に埋め込まれたコンタクトプラグ72を形成する。

【0058】

この際、チャージ蓄積用素子形成領域16に形成されたコンタクトプラグ72のアンテナ比が、デバイス機能素子形成領域14に形成されたコンタクトプラグ72のアンテナ比よりも大きくなるようにする。例えば、チャージ蓄積用素子形成領域16に形成されたコンタクトプラグ72の平面密度が、デバイス機能素子形成領域14に形成されたコンタクトプラグ72の平面密度よりも大きくなるようにする。

【0059】

次いで、例えばスパッタ法等により導電膜を堆積後、フォトリソグラフィ及びドライエッチングによりこの導電膜をパターニングし、コンタクトプラグ72に接続された配線層74を形成する(図11)。

【0060】

この際、チャージ蓄積用素子形成領域16に形成された配線層74のアンテナ比が、デバイス機能素子形成領域14に形成された配線層74のアンテナ比よりも大きくなるようにする。例えば、チャージ蓄積用素子形成領域16に形成された配線層74の配線幅や平面密度が、デバイス機能素子形成領域14に形成された配線層74の配線幅や平面密度よりも大きくなるようにする。また、チャージ蓄積用素子形成領域16に形成される配線層74と、デバイス機能素子形成領域14に形成される配線層74とは、上述の所定値以上の間隔を空けて配置する。

【0061】

配線形成工程では、プラズマCVD、スパッタリング、プラズマエッチング等のプラズマプロセスが用いられる。これら工程の処理中にコンタクトプラグ72や配線層74がプラズマに曝されると、これら導電体がアンテナとなり、コンタクトプラグ72や配線層74内にチャージが誘起される。基板に電気的に接続されていないフローティング状態のコンタクトプラグ72や配線層74では、チャージの抜け道が存在しないため電荷が蓄積され、チャージアップが生じる。

【0062】

例えば、プラズマに曝されたコンタクトプラグ72や配線層74には、プラスのチャージが誘起される。そしてこれに伴い、絶縁膜を介してこれらコンタクトプラグ72や配線層74に接続された電極(ゲート電極、プレート電極等)に対向するシリコン基板10表面には、マイナスのチャージが誘起される。

【0063】

このとき、デバイス機能素子形成領域14に形成されたコンタクトプラグ72又は配線層74のアンテナ比よりも大きいアンテナ比を有するコンタクトプラグ72又は配線層74がチャージ蓄積用素子形成領域16に形成されていると、容量の大きいチャージ蓄積用素子64に多くのチャージが引き寄せられる。これにより、デバイス機能素子に引き寄せられるチャージを減らすことができ、デバイス機能素子のチャージダメージを低減することができる。

【0064】

次いで、配線層74が形成された層間絶縁膜68上に、例えばCVD法によりシリコン窒化膜及びシリコン酸化膜を堆積した後、例えばCMP法によりシリコン酸化膜の表面を平坦化し、シリコン酸化膜/シリコン窒化膜構造の層間絶縁膜76を形成する。

【0065】

次いで、フォトリソグラフィ及びドライエッチングにより、層間絶縁膜76に、配線層74に達するコンタクトホール78を形成する。

【0066】

次いで、全面にバリアメタル及びタングステン膜を堆積後、これら導電膜をエッチバックし、コンタクトホール78内に埋め込まれたコンタクトプラグ80を形成する。

【0067】

この際、チャージ蓄積用素子形成領域16に形成されたコンタクトプラグ80のアンテナ比が、デバイス機能素子形成領域14に形成されたコンタクトプラグ80のアンテナ比よりも大きくなるようにする。

【0068】

次いで、例えばスパッタ法等により導電膜を堆積後、フォトリソグラフィ及びドライエッチングによりこの導電膜をパターニングし、コンタクトプラグ80に接続された配線層82を形成する(図12)。

【0069】

この際、チャージ蓄積用素子形成領域16に形成された配線層82のアンテナ比が、デバイス機能素子形成領域14に形成された配線層82のアンテナ比よりも大きくなるようにする。また、チャージ蓄積用素子形成領域16に形成される配線層82と、デバイス機能素子形成領域14に形成される配線層82とは、上述の所定値以上の間隔を空けて配置する。

【0070】

デバイス機能素子形成領域14に形成されたコンタクトプラグ80又は配線層82のアンテナ比よりも大きいアンテナ比を有するコンタクトプラグ80又は配線層82がチャージ蓄積用素子形成領域16に形成しておくことにより、容量の大きいチャージ蓄積用素子64に多くのチャージが引き寄せられる。これにより、デバイス機能素子に引き寄せられるチャージを減らすことができ、デバイス機能素子のチャージダメージを低減することができる。

【0071】

次いで、配線層82が形成された層間絶縁膜76上に、例えばCVD法によりシリコン窒化膜及びシリコン酸化膜を堆積した後、例えばCMP法によりシリコン酸化膜の表面を平坦化し、シリコン酸化膜/シリコン窒化膜構造の層間絶縁膜84を形成する。

【0072】

次いで、フォトリソグラフィ及びドライエッチングにより、層間絶縁膜84に、配線層82に達するコンタクトホール86を形成する。

【0073】

次いで、全面にバリアメタル及びタングステン膜を堆積後、これら導電膜をエッチバックし、コンタクトホール86内に埋め込まれたコンタクトプラグ88を形成する。

【0074】

この際、チャージ蓄積用素子形成領域16に形成されたコンタクトプラグ88のアンテナ比が、デバイス機能素子形成領域14に形成されたコンタクトプラグ88のアンテナ比よりも大きくなるようにする。

【0075】

次いで、例えばスパッタ法等により導電膜を堆積後、フォトリソグラフィ及びドライエッチングによりこの導電膜をパターニングし、コンタクトプラグ88に接続された配線層90を形成する(図13)。

【0076】

この際、チャージ蓄積用素子形成領域16に形成された配線層90のアンテナ比が、デバイス機能素子形成領域14に形成された配線層90のアンテナ比よりも大きくなるようにする。また、チャージ蓄積用素子形成領域16に形成される配線層90と、デバイス機能素子形成領域14に形成される配線層90とは、上述の所定値以上の間隔を空けて配置する。

【0077】

デバイス機能素子形成領域14に形成されたコンタクトプラグ88又は配線層90のアンテナ比よりも大きいアンテナ比を有するコンタクトプラグ88又は配線層90がチャージ蓄積用素子形成領域16に形成しておくことにより、容量の大きいチャージ蓄積用素子64に多くのチャージが引き寄せられる。これにより、デバイス機能素子に引き寄せられるチャージを減らすことができ、デバイス機能素子のチャージダメージを低減することができる。

【0078】

次いで、全面に、例えばCVD法により、シリコン酸化膜とシリコン窒化膜とを堆積し、シリコン窒化膜/シリコン酸化膜構造のパッシベーション膜92を形成し、本実施形態による半導体装置を完成する(図14)。

【0079】

この後、メモリトランジスタの機能試験等の工程において、フラッシュメモリの書き込み手法と同様にして、分離用素子66のフローティングゲート40に電子を注入し、分離用素子66にオフ状態を書き込む。これにより、チャージ蓄積用素子64をデバイス機能素子から分離することができ、チャージ蓄積用素子64に蓄積されたチャージが放電されてデバイス機能素子にダメージを与えることを防止することができる。

【0080】

分離用素子66への書き込みは、メモリトランジスタの機能試験等の工程において行うことができるため、チャージ蓄積用素子64を分離するための特別な工程を追加する必要はない。

【0081】

また、チャージ蓄積用素子形成領域16に形成された配線層74,82,90は、デバイス機能素子形成領域14に形成された配線層74,82,90から所定値以上の間隔を空けて配置している。これにより、チャージ蓄積用素子形成領域16に蓄積されたチャージがデバイス機能素子形成領域14方向に放電されてデバイス機能素子にチャージダメージを与えるのを防止することができる。

【0082】

このように、本実施形態によれば、デバイス機能素子とチャージ蓄積用素子との間に電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子を設けるので、デバイス機能素子とチャージ蓄積用素子とを容易に分離することができる。また、分離用素子はメモリトランジスタと同時に形成することができ、分離用素子の書き込みはメモリトランジスタの機能試験時に行うことができるため、製造工程を増加することも防止することができる。

【0083】

[第2実施形態]

第2実施形態による半導体装置及びその製造方法について図15及び図16を用いて説明する。図1乃至図14に示す第1実施形態による半導体装置及びその製造方法と同一の構成要素には同一の符号を付し説明を省略し又は簡潔にする。

【0084】

図15は、本実施形態による半導体装置の構造を示す概略断面図である。図16は、本実施形態による半導体装置のチャージ蓄積用素子の構造を示す斜視図である。

【0085】

本実施形態による半導体装置は、図15に示すように、配線層74,82,90及びコンタクトプラグ80,88により形成されたMIM(Metal-Insulator-Metal)キャパシタ構造のチャージ蓄積用素子64を有している。

【0086】

チャージ蓄積用素子形成領域16に形成された配線層74は、例えば図16に示すように、櫛歯型を有し互いに噛み合うように配置された2つの電極パターン74A,74Bを有している。同様に、チャージ蓄積用素子形成領域16に形成された配線層82は、櫛歯型を有し互いに噛み合うように配置された2つの電極パターン82A,82Bを有している。電極パターン74Aと電極パターン82Aとは、コンタクトプラグ80によって接続されている。同様に、電極パターン74Bと電極パターン82Bとは、コンタクトプラグ80によって接続されている。

【0087】

図16には示していないが、チャージ蓄積用素子形成領域16に形成された配線層90も配線層74,82と同様のパターンを有しており、コンタクトプラグによって配線層82に接続されている。

【0088】

こうして、電極パターン72A,80A,…及びこれらを接続するコンタクトプラグ80,82を一方の電極とし、電極パターン72B,80B,…及びこれらを接続するコンタクトプラグ80,82を他方の電極とし、層間絶縁膜76,84をキャパシタ誘電体膜とするチャージ蓄積用素子64が形成されている。

【0089】

チャージ蓄積用素子64は、第1実施形態による半導体装置と同様、分離用素子66に接続されている。チャージ蓄積用素子64は、少なくとも一方の電極を分離用素子66に接続する。他方の電極は、前記一方の電極に接続された分離用素子66とは別の分離用素子66に接続してもよいし、シリコン基板10に接続してもよいし、フローティング状態としてもよい。

【0090】

チャージ蓄積用素子64をMIM構造のキャパシタにより形成することによっても、第1実施形態と同様の効果を得ることができる。

【0091】

本実施形態による半導体装置の製造方法は、配線層72,80,88等のパターンが異なるほかは、第1実施形態による半導体装置の製造方法と同様である。

【0092】

このように、本実施形態によれば、デバイス機能素子とチャージ蓄積用素子との間に電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子を設けるので、デバイス機能素子とチャージ蓄積用素子とを容易に分離することができる。また、分離用素子はメモリトランジスタと同時に形成することができ、分離用素子の書き込みはメモリトランジスタの機能試験時に行うことができるため、製造工程を増加することも防止することができる。

【0093】

[変形実施形態]

上記実施形態に限らず種々の変形が可能である。

【0094】

例えば、上記実施形態では、分離用素子66としてスタックゲート構造の不揮発メモリトランジスタを示したが、分離用素子66はこれに限定されるものではない。分離用素子66は、電気的に書き換え可能な不揮発性メモリトランジスタであればよく、例えば、SONOS型の不揮発性メモリトランジスタを用いるようにしてもよい。

【0095】

また、上記実施形態では、3層の配線層により半導体装置を製造する場合を示したが、配線層の層数は3層に限定されるものではなく、適宜増減することができる。

【0096】

また、上記第1実施形態では、MISキャパシタの基板側の導電型をP型(Pウェル24)としたが、N型としてもよい。

【0097】

また、上記第2実施形態では、櫛歯型の電極パターンを有するMIMキャパシタを形成したが、電極パターンはこれに限定されるものではない。

【0098】

また、上記実施形態では、分離用素子形成領域18の活性領域内に分離用素子66を設けているが、デバイス機能素子形成領域14内の一部に分離用素子66を設けるようにしてもよい。例えば、メモリセルトランジスタのアレイの端部に、分離用素子66を設けるようにしてもよい。

【0099】

また、上記実施形態では、分離用素子形成領域18に、直列接続した2つの分離用素子66を設けた場合を示したが、分離用素子66は必ずしも2つである必要はない。分離用素子形成領域18に設ける分離用素子66は、1つでもよいし、3つ以上直列接続してもよい。

【0100】

また、上記実施形態に記載した半導体装置の構造、構成材料、製造条件等は、一例を示したものにすぎず、当業者の技術常識等に応じて適宜修正や変更が可能である。

【0101】

以上の実施形態に関し、更に以下の付記を開示する。

【0102】

(付記1) 半導体基板上に形成されたデバイス機能素子と、

前記半導体基板上に形成されたチャージ蓄積用素子と、

前記半導体基板上に形成され、前記デバイス機能素子と前記チャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子と

を有することを特徴とする半導体装置。

【0103】

(付記2) 付記1記載の半導体装置において、

前記デバイス機能素子に接続され、前記デバイス機能素子に対して第1のアンテナ比を有する第1の配線と、

前記チャージ蓄積用素子に接続され、前記チャージ蓄積用素子に対して前記第1のアンテナ比よりも大きい第2のアンテナ比を有する第2の配線と

を更に有することを特徴とする半導体装置。

【0104】

(付記3) 付記2記載の半導体装置において、

前記第1の配線層と前記第2の配線層とは、前記第1の配線層及び前記第2の配線層に許容される最小間隔の2倍以上離間している

ことを特徴とする半導体装置。

【0105】

(付記4) 付記1乃至3のいずれか1項に記載の半導体装置において、

前記チャージ蓄積用素子は、前記半導体基板上に形成された誘電体膜と、前記誘電体膜上に形成されたプレート電極とを含むMISキャパシタである

ことを特徴とする半導体装置。

【0106】

(付記5) 付記1乃至3のいずれか1項に記載の半導体装置において、

前記チャージ蓄積用素子は、前記半導体基板上に形成された絶縁膜に埋め込まれた配線層により形成されたMIMキャパシタである

ことを特徴とする半導体装置。

【0107】

(付記6) 半導体基板上に、デバイス機能素子を形成する工程と、

前記半導体基板上に、チャージ蓄積用素子を形成する工程と、

前記半導体基板上に、前記デバイス機能素子と前記チャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子を形成する工程と

を有することを特徴とする半導体装置の製造方法。

【0108】

(付記7) 付記6記載の半導体装置の製造方法において、

前記デバイス機能素子に接続され、前記デバイス機能素子に対して第1のアンテナ比を有する第1の配線と、前記チャージ蓄積用素子に接続され、前記チャージ蓄積用素子に対して前記第1のアンテナ比よりも大きい第2のアンテナ比を有する第2の配線とを形成する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【0109】

(付記8) 付記6記載の半導体装置の製造方法において、

前記分離用素子にオフ状態を書き込み、前記デバイス機能素子と前記チャージ蓄積用素子とを電気的に分離する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【符号の説明】

【0110】

10…シリコン基板

12…素子分離絶縁膜

14…デバイス機能素子形成領域

16…チャージ蓄積用素子形成領域

18…分離用素子形成領域

20…保護絶縁膜

22,24,26…Pウェル

28…トンネルゲート絶縁膜

30,38…ポリシリコン膜

32…ONO膜

34…キャパシタ誘電体膜

36…ゲート絶縁膜

40…フローティングゲート

42…コントロールゲート

44,52,56…不純物拡散領域

46,54…サイドウォールスペーサ

48…プレート電極

50…ゲート電極

58,60…ソース/ドレイン領域

62…周辺トランジスタ

64…チャージ蓄積用素子

66…分離用素子

68,76,84…層間絶縁膜

70,78,86…コンタクトホール

72,80,88…コンタクトプラグ

74,82,90…配線層

92…パッシベーション膜

【特許請求の範囲】

【請求項1】

半導体基板上に形成されたデバイス機能素子と、

前記半導体基板上に形成されたチャージ蓄積用素子と、

前記半導体基板上に形成され、前記デバイス機能素子と前記チャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子と

を有することを特徴とする半導体装置。

【請求項2】

請求項1記載の半導体装置において、

前記デバイス機能素子に接続され、前記デバイス機能素子に対して第1のアンテナ比を有する第1の配線と、

前記チャージ蓄積用素子に接続され、前記チャージ蓄積用素子に対して前記第1のアンテナ比よりも大きい第2のアンテナ比を有する第2の配線と

を更に有することを特徴とする半導体装置。

【請求項3】

請求項2記載の半導体装置において、

前記第1の配線層と前記第2の配線層とは、前記第1の配線層及び前記第2の配線層に許容される最小間隔の2倍以上離間している

ことを特徴とする半導体装置。

【請求項4】

半導体基板上に、デバイス機能素子を形成する工程と、

前記半導体基板上に、チャージ蓄積用素子を形成する工程と、

前記半導体基板上に、前記デバイス機能素子と前記チャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子を形成する工程と

を有することを特徴とする半導体装置の製造方法。

【請求項5】

請求項4記載の半導体装置の製造方法において、

前記デバイス機能素子に接続され、前記デバイス機能素子に対して第1のアンテナ比を有する第1の配線と、前記チャージ蓄積用素子に接続され、前記チャージ蓄積用素子に対して前記第1のアンテナ比よりも大きい第2のアンテナ比を有する第2の配線とを形成する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【請求項6】

請求項4記載の半導体装置の製造方法において、

前記分離用素子にオフ状態を書き込み、前記デバイス機能素子と前記チャージ蓄積用素子とを電気的に分離する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【請求項1】

半導体基板上に形成されたデバイス機能素子と、

前記半導体基板上に形成されたチャージ蓄積用素子と、

前記半導体基板上に形成され、前記デバイス機能素子と前記チャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子と

を有することを特徴とする半導体装置。

【請求項2】

請求項1記載の半導体装置において、

前記デバイス機能素子に接続され、前記デバイス機能素子に対して第1のアンテナ比を有する第1の配線と、

前記チャージ蓄積用素子に接続され、前記チャージ蓄積用素子に対して前記第1のアンテナ比よりも大きい第2のアンテナ比を有する第2の配線と

を更に有することを特徴とする半導体装置。

【請求項3】

請求項2記載の半導体装置において、

前記第1の配線層と前記第2の配線層とは、前記第1の配線層及び前記第2の配線層に許容される最小間隔の2倍以上離間している

ことを特徴とする半導体装置。

【請求項4】

半導体基板上に、デバイス機能素子を形成する工程と、

前記半導体基板上に、チャージ蓄積用素子を形成する工程と、

前記半導体基板上に、前記デバイス機能素子と前記チャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子を形成する工程と

を有することを特徴とする半導体装置の製造方法。

【請求項5】

請求項4記載の半導体装置の製造方法において、

前記デバイス機能素子に接続され、前記デバイス機能素子に対して第1のアンテナ比を有する第1の配線と、前記チャージ蓄積用素子に接続され、前記チャージ蓄積用素子に対して前記第1のアンテナ比よりも大きい第2のアンテナ比を有する第2の配線とを形成する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【請求項6】

請求項4記載の半導体装置の製造方法において、

前記分離用素子にオフ状態を書き込み、前記デバイス機能素子と前記チャージ蓄積用素子とを電気的に分離する工程を更に有する

ことを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2012−244046(P2012−244046A)

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願番号】特願2011−114672(P2011−114672)

【出願日】平成23年5月23日(2011.5.23)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願日】平成23年5月23日(2011.5.23)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]