半導体装置及びその製造方法

【課題】配線の低抵抗化を図る。

【解決手段】本実施形態の半導体装置は、半導体基板10を覆う第1の層間絶縁膜上に設けられる配線60と、配線60の上面上に設けられるキャップ層68と、配線60と第2の層間絶縁膜との間に設けられるバリア膜62と、を含む。配線60は高融点導電層を含み、配線60の配線幅W1は、キャップ層68の幅W2よりも小さい。バリア膜62は、高融点導電層60が含む元素の化合物からなり、配線60を覆う層間絶縁膜69,70に起因する不純物が配線60内に拡散するのを抑制する。

【解決手段】本実施形態の半導体装置は、半導体基板10を覆う第1の層間絶縁膜上に設けられる配線60と、配線60の上面上に設けられるキャップ層68と、配線60と第2の層間絶縁膜との間に設けられるバリア膜62と、を含む。配線60は高融点導電層を含み、配線60の配線幅W1は、キャップ層68の幅W2よりも小さい。バリア膜62は、高融点導電層60が含む元素の化合物からなり、配線60を覆う層間絶縁膜69,70に起因する不純物が配線60内に拡散するのを抑制する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体装置の配線において、銅(Cu)が、配線及びビアを形成するための低抵抗配線材料として、主に用いられている。

【0003】

最先端の半導体装置に用いられる配線構造において、配線及びビアの微細化が進んでいる。微細化の結果として、電子の界面非弾性散乱による抵抗率の上昇や、電流密度の増加、ストレスマイグレーション又はエレクトロマイグレーションによる信頼性の劣化が、配線構造の問題として、顕在化している。

【0004】

さらに、微細化が進むにつれて、上記の問題に加え、Cuのように長い平均自由工程を有する低抵抗配線材料は、電気抵抗のサイズ依存性が微細化によって顕著になる。

【0005】

また、Cuを用いた配線は、ダマシン構造を有するため、配線材としてのCuに加えて、バリアメタル膜が、配線材が埋め込まれる配線溝(ダマシン溝)内に形成される。そのため、形成された配線溝の寸法に対して、配線の電気伝導に寄与する実効的な配線の断面寸法(断面積)は、減少する。

【0006】

また、DRAM、フラッシュメモリ、或いは、クロスポイント構造のメモリにおいて、それらの製造プロセスの観点から、トランジスタのゲート電極及び配線は、高融点かつ低抵抗の材料が用いられることが好ましい場合がある。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2005−236330号公報

【特許文献2】特開2009−267296号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

配線の低抵抗化を図る技術を提案する。

【課題を解決するための手段】

【0009】

本実施形態の半導体装置は、素子が形成された半導体基板を覆う第1の層間絶縁膜上に設けられた配線と、前記配線の上面上に設けられるキャップ層と、前記配線と前記配線を覆う第2の層間絶縁膜との間に設けられるバリア膜と、を具備し、前記配線は、高融点導電層を含み、前記配線の配線幅は、前記キャップ層の幅よりも小さく、前記バリア膜は、前記高融点導電層が含む元素の化合物から構成され、前記第2の層間絶縁膜に起因する不純物が前記配線内に拡散するのを抑制する。

【図面の簡単な説明】

【0010】

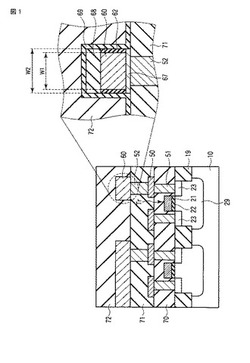

【図1】本実施形態の半導体装置の構成を説明するための図。

【図2】本実施形態の半導体装置の形成条件を説明するための図。

【図3】本実施形態の半導体装置の形成条件を説明するための図。

【図4】本実施形態の半導体装置の形成条件を説明するための図。

【図5】本実施形態の半導体装置の形成条件を説明するための図。

【図6】本実施形態の半導体装置の形成条件を説明するための図。

【図7】本実施形態の半導体装置の形成条件を説明するための図。

【図8】本実施形態の半導体装置の形成条件を説明するための図。

【図9】本実施形態の半導体装置の形成条件を説明するための図。

【図10】本実施形態の半導体装置の形成条件を説明するための図。

【図11】本実施形態の半導体装置の形成条件を説明するための図。

【図12】本実施形態の半導体装置の形成条件を説明するための図。

【図13】本実施形態の半導体装置の形成条件を説明するための図。

【図14】本実施形態の半導体装置の変形例を示す図。

【図15】本実施形態の半導体装置の変形例を示す図。

【図16】本実施形態の半導体装置の変形例を示す図。

【図17】本実施形態の半導体装置の応用例を示す図。

【図18】本実施形態の半導体装置の応用例を示す図。

【図19】本実施形態の半導体装置の応用例を示す図。

【図20】本実施形態の半導体装置の応用例を示す図。

【図21】本実施形態の半導体装置の製造方法1の一工程を示す断面工程図。

【図22】本実施形態の半導体装置の製造方法1の一工程を示す断面工程図。

【図23】本実施形態の半導体装置の製造方法1の一工程を示す断面工程図。

【図24】本実施形態の半導体装置の製造方法1の一工程を示す断面工程図。

【図25】本実施形態の半導体装置の製造方法1の一工程を示す断面工程図。

【図26】本実施形態の半導体装置の製造方法2の一工程を示す断面工程図。

【図27】本実施形態の半導体装置の製造方法2の一工程を示す断面工程図。

【図28】本実施形態の半導体装置の製造方法2の一工程を示す断面工程図。

【図29】本実施形態の半導体装置の製造方法2の一工程を示す断面工程図。

【図30】本実施形態の半導体装置の製造方法2の一工程を示す断面工程図。

【発明を実施するための形態】

【0011】

[実施形態]

以下、図1乃至図30を参照しながら、本実施形態について詳細に説明する。以下の説明において、同一の機能及び構成を有する要素については、同一符号を付し、重複する説明は必要に応じて行う。

【0012】

(1) 構成

図1を参照して、本実施形態の半導体装置の構成について、説明する。図1は、本実施形態の半導装置の構成を模式的に示す断面図である。

【0013】

半導体装置及び半導体装置が含む回路を形成する素子Trが、半導体基板10上に、設けられている。

【0014】

図1において、電界効果トランジスタTrが、半導体装置を形成する素子Trとして、図示されている。電界効果トランジスタは、例えば、MOSトランジスタである。

【0015】

トランジスタTrは、半導体基板10内の素子形成領域(アクティブ領域)29内に、設けられている。素子形成領域は、素子分離領域によって、定義されている。素子形成領域29内には、p型又はn型のウェル領域が設けられている。素子分離領域内に形成されたトレンチ内には、STI(Shallow Trench Isolation)構造の絶縁膜19が、埋め込まれている。

【0016】

トランジスタTrのゲート電極21は、ゲート絶縁膜22を介して、素子形成領域29の表面上に設けられている。素子形成領域29内には、トランジスタTrのソース/ドレインとしての2つの拡散層23が設けられている。素子形成領域29内における2つの拡散層23間の領域が、トランジスタTrのチャネル領域となる。ゲート電極21に所定の電圧が印加されることによって、チャネル領域の表層部(ゲート絶縁膜22の下方)に、チャネル(反転層)が形成される。

【0017】

尚、半導体装置が、抵抗素子、容量素子又はメモリ素子など、電界効果トランジスタ以外の素子を含んでいるのは、もちろんである。

【0018】

第1の層間絶縁膜70が、トランジスタTrを覆うように、半導体基板10上に設けられている。コンタクトプラグ51が、拡散層23に接続されるように、層間絶縁膜70内に形成されたコンタクトホール内に埋め込まれている。尚、ゲート電極21に接続されるコンタクトプラグも、層間絶縁膜70内に形成されている。

【0019】

第1の配線50が、コンタクトプラグ51に接続されるように、層間絶縁膜70上に設けられている。第1の配線50は、半導体基板10の表面からの高さ(半導体基板10の表面に対して垂直方向の位置)を基準として、第1の配線レベル内に設けられている。

【0020】

第2の層間絶縁膜71が、配線50上及び第1の層間絶縁膜70上に設けられている。ビアプラグ52が、第2の層間絶縁膜71内に形成されたコンタクトホール(ビアホール)内に、設けられている。

【0021】

第2の配線60が、ビアプラグ52に接続されるように、第2の層間絶縁膜71上に設けられている。第2の配線60は、第2の配線レベルに設けられている。

第3の層間絶縁膜72が、配線60及び層間絶縁膜71上に、設けられている。

【0022】

ここで、第2の配線60を用いて、本実施形態の半導体装置に用いられる配線の構造について、より具体的に説明する。

【0023】

本実施形態の半導体装置において、配線60は、高融点導電体を含む導電層を用いて、形成される。本実施形態における高融点導電体とは、融解温度(融点)TMが、1000℃以上、より好ましくは、1100℃より高い金属又は金属化合物のことである。高融点導電体は、AlやCuに比較して、配線の微細化の影響を受けにくい。

【0024】

密着層67は、配線60と層間絶縁膜71との間、及び、配線60とビアプラグ52との間に、設けられている。密着層67は、配線60と他の部材との密着性を確保するために設けられ、密着層67は、配線60が層間絶縁膜71及びプラグ52から剥離するのを防止する。また、密着層67は、例えば、バリアメタルとしての機能を有し、配線60と層間絶縁膜71との間に生じる不純物の拡散、及び、配線60とプラグ52との間に生じる不純物の拡散を、防止する。

例えば、密着層67には、窒化チタン(TiN)が用いられる。但し、密着層67の材料は、配線60の材料に応じて、適宜変更されてもよい。例えば、配線がMoによって形成される場合には、窒化モリブデン(MoN)が、密着層67として用いられる。

【0025】

例えば、配線60の上部(上面)上には、絶縁膜68が設けられている。絶縁膜68は、配線60を加工するためのマスクの一部として用いられる。以下では、絶縁膜68のことを、キャップ層とよぶ。配線60と上層の配線レベルの配線とを接続されるビアプラグの形成位置において、キャップ層68は、配線60の上面から除去されている。尚、キャップ層68は、配線60上に残存させなくともよく、キャップ層68は、配線60が加工された後に、除去されてもよい。

【0026】

パッシベーション膜(スペーサ膜ともよばれる)としての絶縁膜69は、メタル層61を覆っている。以下では、キャップ層68及びパッシベーション膜69のことを、層間絶縁膜として説明する場合がある。

【0027】

拡散防止膜62は、導電層60の外周に沿って、形成されている。図1に示される配線の構造において、拡散防止膜62は、導電層60の側部(側面)上に設けられている。図1において、拡散防止膜62は、導電層60とパッシベーション膜69との間に介在している。拡散防止膜62は、パッシベーション膜69や層間絶縁膜72を形成する際の酸化種又は窒化種が導電層60内に拡散するのを、抑制する。以下では、導電層60に対する不純物の拡散を抑制する膜62のことを、バリア膜62とよぶ。

バリア膜62は、導電層60を形成する材料(配線材)の酸化物又は窒化物である。例えば、配線60がMoを用いて形成された場合、バリア膜62は、二酸化モリブデン(MoO2)を含む。尚、バリア膜62は、酸窒化膜又は炭化膜でもよい。

【0028】

例えば、バリア膜62が、導電層60に対する酸化処理または窒化処理によって導電層60の側面上に形成された場合、導電層60の幅W1は、キャップ層68の幅W2よりも小さくなっている。

【0029】

例えば、配線としての高融点導電層60の配線幅W1は、半導体装置の配線パターン及び配線レベルに応じて、30nm以上、500nm以下の範囲で設定される。尚、配線60の配線幅W1は、500nmより大きい値に設定される場合もある。また、配線60の配線幅W1は、側壁転写技術などの微細加工技術を用いて、露光による解像度の限界より小さい寸法(例えば、20nm以下)に設定される場合もある。

【0030】

本実施形態の半導体装置において、配線60は、高融点導電体を含む導電層から構成される。本実施形態において、配線60を形成するための高融点導電体の具体例については、後述する。

【0031】

そして、後述の条件で、高融点導電体を含む配線(高融点導電層)60が形成されることによって、配線60が含む高融点導電体の結晶粒のサイズが大きくなる。この結果として、所定の面積(或いは単位体積)内における結晶粒界が減少し、高融点導電層60内における結晶粒界に起因する電子の散乱が減少する。それゆえ、高融点導電体を含む配線60の抵抗値は、減少する。

【0032】

高融点導電体が配線60に用いられる場合、高融点導電層が、エッチングによって所定のパターンに加工される。配線60の加工後に、配線60としての高融点導電層の側面が露出し、高融点導電層の露出した面が、層間絶縁膜(又はパッシベーション膜)の形成するための酸化雰囲気又は窒化雰囲気にさらされる。それゆえ、層間絶縁膜が、高融点導電層上に、直接形成された場合、層間絶縁膜の形成に起因した導電体層の過剰な酸化又は窒化に起因して、配線の電気抵抗が上昇することが懸念される。

これに対して、本実施形態の半導体装置の配線構造のように、配線60と層間絶縁膜との間に、バリア膜(拡散防止膜)62が設けられることによって、配線60を形成するための高融点導電層の酸化又は窒化が防止され、層間絶縁膜の形成に起因した配線60の抵抗の上昇が抑制される。

【0033】

また、バリア膜62が高融点導電層60に対する酸化処理又は窒化処理によって形成されることによって、高融点導電層60とバリア膜62とを含む配線構造の配線幅は、ほとんど増大しないため、微細化な配線構造を形成できる。

【0034】

したがって、本実施形態の半導体装置によれば、配線の低抵抗化を図ることができる。

【0035】

(2) 配線の材料及び配線構造の形成条件

図2乃至図13を参照して、本実施形態の半導体装置が含む配線60の材料及び配線構造の形成条件について、説明する。

【0036】

(a) 材料

図1を用いて説明したように、本実施形態の半導体装置において、高融点導電体(高融点導電層)が、配線60を形成するための材料(配線材)として、用いられている。

【0037】

本実施形態において、配線材としての高融点導電体は、モリブデン(Mo)、タングステン(W)、ルテニウム(Ru)、タンタル(Ta)、コバルト(Co)及びニッケル(Ni)を含むグループから選択される少なくとも1つの材料(元素)が、用いられる。これらの金属は、1000℃以上の融解温度TMを有する。これらの金属のことを、以下では、高融点金属とよぶ。尚、配線材としての高融点金属は、1000℃以上、より好ましくは1100℃より高い融解温度を有していれば、上記の金属に限定されない。また、1000℃以上の融解温度であれば、上記の高融点金属を含む合金でもよい。

【0038】

配線60を構成する高融点導電体は、1000℃以上の融解温度であれば、例えば、金属化合物でもよい。例えば、高融点導電体としての金属化合物(以下では、高融点金属化合物ともよぶ)には、上記の高融点金属の化合物、より具体的な例としては、モリブデンシリサイド(MoSi)、タングステンシリサイド(WSi)、ニッケルシリサイド(NiSi)、コバルトシリサイド(CoSi)などのシリサイドが、用いられてもよい。

【0039】

さらに、配線60としての高融点導電体は、上記の高融点金属及び高融点金属化合物のうち、再結晶化温度TRが1000℃以下の材料が用いられることが好ましい。Wの再結晶化温度は、1200℃以下である。Taの再結晶化温度は1000℃以下であり、Moの再結晶化温度は、900℃以下であり、Ruの再結晶化温度は900℃以下である。それゆえ、本実施形態において、上述の高融点金属のうち、Mo、Ru又はTaが、配線に用いられることがさらに好ましい。

【0040】

再結晶化温度が1000℃以下の高融点金属が、配線60に用いられることよって、比較的低い加熱温度で、高融点導電層から構成される配線60の結晶性の改善(結晶の大粒径化)を図ることができる。

【0041】

また、配線60だけでなく、図1のビアプラグ52に、上記に高融点導電体が用いられてもよい。

【0042】

半導体装置の製造プロセスは、温度条件が1000℃から1100℃程度又はこの温度以下のプロセスを含む。本実施形態のように、融解温度TMが1000℃以上の高融点導電体が、半導体基板10上の素子間を接続する配線60に用いられることによって、CuやAlなどの融解温度TMが比較的低い金属材料に比較して、過大な熱に起因した配線の劣化を抑制できる。

【0043】

また、再結晶化温度TRが1000℃以下の高融点導電体が、配線60に用いられた場合、上記の温度条件における製造プロセスにおいて、配線の結晶性の改善(結晶の大粒径化)を図ることができ、配線を低抵抗化できる。

【0044】

尚、配線を形成するための高融点導電体は、上述の金属及び金属化合物に限定されず、例えば、Tiのように、上述の融解温度及び再結晶化温度の条件を満たす金属又は金属化合物が、本実施形態の半導体装置の配線に用いられてもよい。

【0045】

(b) 形成条件

図2乃至図5を用いて、本実施形態の半導体装置が含む配線の形成条件について、説明する。

図2は、配線としての高融点導電層の堆積時における基板の加熱温度(以下、成膜温度とよぶ)と高融点導電層の電気的特性との関係を示すグラフである。

【0046】

図2において、グラフの横軸は、成膜温度を示している。図2において、グラフの縦軸は、成膜温度に対する配線の抵抗率の減少率(単位:[%])を示している。図2において、Mo又はWから構成される高融点導電層の電気的特性の変化が示されている。Mo層及びW層は、PVD(Physical Vapor Deposition)法によって、それぞれ形成される。

【0047】

図2において、配線の抵抗率の減少率は、基板の加熱無しに、室温(25℃〜30℃)で形成されたMo層又はW層の抵抗率を基準(参照値)として求められている。図2に示される例において、Mo層の成膜時に150℃、300℃、400℃及び500℃の基板加熱処理がそれぞれ施された場合における、Mo層の抵抗率の減少率が示されている。また、図2に示される例において、W層の成膜時に400℃の基板加熱処理が施された場合における、W層の抵抗率の減少率が示されている。

【0048】

図2に示されるように、配線を構成する導電層(ここでは、Mo層又はW層)が加熱された基板上に堆積されることによって、Mo層及びW層の抵抗率は、減少する。

図2に示される例において、W層の抵抗率は、400℃の成膜温度において、室温で形成されたW層に対して、30%程度、減少する。

また、図2に示される例において、150℃の成膜温度で形成されたMo層の抵抗率は、室温で形成されたMo層の抵抗率に比較して、20%程度低下し、成膜温度が高くなるにつれて、Mo層の抵抗率の減少率は大きくなる。500℃の成膜温度で形成されたMo層の抵抗率は、室温で形成されたMo層の抵抗率に比較して、60%から70%程度、減少する。

【0049】

室温の成膜温度で形成されたMo層及びW層の抵抗率は、所定の寸法(配線幅)において、例えば、15μΩ・cmから16μΩ・cm程度の大きさを有する。成膜時における400℃程度の基板加熱処理によって、W層の抵抗率は、11μΩ・cm程度の大きさを示す。

【0050】

成膜時に150℃程度の基板加熱処理が施されることよって、Mo層の抵抗率は、16μΩ・cm程度の大きさを示し、成膜時に500℃程度の基板加熱処理が施されることよって、Mo層の抵抗率は、8μΩ・cm程度の大きさを示す。

【0051】

このように、Mo層及びW層の抵抗率は、Mo層及びW層の成膜温度の上昇とともに、減少する。さらに、成膜時の加熱処理において、Moの再結晶化温度がWの再結晶化温度より低いため、Mo層の抵抗率の減少率は、W層の抵抗率の減少率より大きい。

【0052】

図3は、堆積後の配線に対して加熱処理(以下、ポストアニール処理とよぶ)が施された場合における加熱処理温度と配線(ここでは、Mo層及びW層)の電気的特性との関係を示すグラフである。

図3において、グラフの横軸は、ポストアニール処理の加熱温度を示している。加熱温度は、400℃から800℃程度に設定されている。図3において、グラフの縦軸は、ポストアニール処理を施した導電層の抵抗率の減少率(単位:[%])を示している。ここでは、室温(25℃〜30℃)の成膜温度で導電層が形成され、かつ、ポストアニール処理が施されていない導電層の抵抗率が、基準(参照値)とされている。

【0053】

図3に示される例において、400℃、600℃及び750℃のポストアニール処理が、室温で堆積されたMo層にそれぞれ施された場合における、Mo層の抵抗率の減少率が示されている。また、400℃及び750℃のポストアニール処理が室温で堆積されたW層に対してそれぞれ施された場合における、W層の抵抗率の減少率が示されている。尚、図2に示される例と同様に、Mo層及びW層は、PVD法によって、基板上に堆積されている。

【0054】

図3に示されるように、堆積された層に対してポストアニール処理が施されることによって、Mo層及びW層の抵抗率は、減少する。

W層の抵抗率は、400℃から750℃の範囲内のポストアニール処理によって、ポストアニール処理なしのW層に比較して、4%から10%程度の範囲内で、減少する。例えば、400℃から750℃の範囲においてポストアニール処理されたW層の抵抗率は、11μΩ・cmから12μΩ・cm程度の大きさを示す。

【0055】

Mo層の抵抗率は、400℃のポストアニール処理によって、10%程度減少し、600℃のポストアニール処理によって、15%程度減少する。また、750℃のポストアニール処理が施された場合、Mo層の抵抗率は、ポストアニール処理なしのMo層に比較して、27%程度減少する。例えば、400℃から750℃の範囲においてポストアニール処理されたMo層の抵抗率は、8μΩ・cmから10μΩ・cm程度の大きさを示す。上述のように、Moの再結晶化温度が比較的低いため、Mo層が含む結晶の大粒経化が促進され、Mo層の抵抗率の減少率が、W層の抵抗率の減少率よりも大きくなる。

【0056】

このように、成膜後のポストアニール処理によっても、成膜時の基板加熱と同様に、高融点導電層の抵抗率を低減できる。

【0057】

図4及び図5を用いて、PVD法を用いた場合における高融点導電層から構成される配線の成膜条件について説明する。図4及び図5において、スパッタ法が高融点導電層の成膜に用いられた場合の条件が示されている。

図4は、高融点導電層の堆積時における封入ガスのガス圧と高融点導電層の抵抗率との関係を示すグラフである。図4において、グラフの横軸は、スパッタガスのガス圧が示されている。図4において、グラフの縦軸は、各ガス圧で形成された導電層(ここでは、W層)の抵抗率が示されている。図4では、アルゴン(Ar)が、スパッタガスに用いられている。図4に示されるArガスのガス圧は、0.08Paから0.8Pa程度の範囲内にそれぞれに設定されている。また、図4では、放電電圧を変化させて、ガス圧に対する配線の抵抗率の変化が、測定されている。尚、図4において、3つの放電電圧A,B,Cのうち、放電電圧Cが最も大きく、放電電圧Aが最も小さく、放電電圧Bが、放電電圧Aと放電電圧Cとの間の大きさに設定されている。

【0058】

図5は、高融点導電層の堆積時における放電電圧と高融点導電層の抵抗率との関係を示すグラフである。図5において、グラフの横軸は、高融点導電層(ここでは、W層)の成膜のための放電電圧を示している。図5において、グラフの縦軸は、高融点導電層の抵抗率を示している。図5において、放電電圧は、250Wから600Wの範囲内にそれぞれ設定されて、導電層が堆積されている。図5において、スパッタガスとしてのArガスのガス圧が、0.08Pa、0.2Pa、0.6Pa及び0.8Paにそれぞれ設定された場合における放電電圧に対する高融点導電層の抵抗率の変化が示されている。

【0059】

図4に示されるように、各放電電圧で形成された高融点導電層において、スパッタ時におけるArのガス圧が低くなると、その導電層の抵抗率は低減する。このように、成膜時のスパッタガス圧が低くなると導電層の抵抗率が減少するのは、導電層内に取り込まれるガス成分が減少するためである。また、ガス圧が低減されることによって、スパッタリングのための放電電圧を高くできる。それゆえ、配線としての高融点導電層がスパッタ法によって堆積される場合、成膜時のチャンバ内のガス圧が小さくされることが、配線の抵抗率の低減に有効である。

【0060】

図5に示されるように、スパッタリングのための放電電圧が300Vより小さい場合、高融点導電層の抵抗率に対する放電電圧の依存性が大きくなる。これに対して、放電電圧が300V以上である場合、導電層の抵抗率の変化は、飽和した傾向を示す。また、導電層が300V以上の放電電圧を用いて堆積されることによって、300Vより小さい放電電圧で形成された導電層に比較して、配線の抵抗率を低減できる。

それゆえ、配線としての高融点導電層がスパッタ法によって堆積される場合、放電電圧が300V以上に設定されることが、その配線の抵抗率の低減に有効である。

【0061】

尚、図4及び図5において、W層が配線を形成するための導電層として例示されているが、Moや他の高融点金属がスパッタ法によって堆積される場合においても、実質的に同じ傾向を示す。

【0062】

図4及び図5に示されるように、スパッタ法によって配線を形成するための高融点導電層が堆積される場合、スパッタガスの圧力及びスパッタリングのための放電電圧を考慮することが、配線の低抵抗化のために好ましい。

【0063】

また、上記の形成条件及び形成工程に加えて、加工後の高融点導電層に対して、自然酸化膜を除去するための還元処理が施されることが好ましい。これによって、配線幅の減少を防止でき、配線の低抵抗化を図ることができる。還元処理は、高融点導電層に対するポストアニール処理と共通化できる。

【0064】

以上のように、本実施形態の半導体装置は、高融点導電体から構成される配線60を有している。

【0065】

図2及び図3に示されるように、高融点導電体を用いて形成される配線(ここでは、Mo層及びW層)60は、成膜時の基板加熱処理又は成膜後のポストアニール処理のように、高融点導電層60に熱を与えることによって、高融点導電層60の抵抗率が低減する。

【0066】

導電層に対する加熱処理によって、高融点導電層の結晶粒は、与えられた熱によって結晶成長し、結晶粒のサイズ(粒経)が大きくなり、高融点導電層内の粒界が減少する。その結果として、微細な配線内において、配線の表面や結晶粒界で生じる電子の散乱が減少し、高融点導電層の抵抗率(抵抗値)が低減する。

【0067】

また、加熱によるMo層の抵抗率の減少率は、W層の抵抗率の減少率よりも、大きい。これは、Moの再結晶化温度(1000℃程度)が、Wの再結晶化温度(1200℃程度)より低いため、Moの結晶核の生成及び結晶成長がWよりも促進されやすく、MoがWよりも大粒径化しやすいためである。それゆえ、配線に用いられる高融点導電体は、再結晶化温度が、1000℃以下であることが好ましい。

【0068】

このように、高融点導電層の成膜時又は成膜後に熱を与えることによって、高融点導電体から構成される配線が含む結晶粒を大きくでき、配線を低抵抗化できる。

【0069】

また、上述のように、高融点導電体から構成される配線が、スパッタ法を用いて形成される場合、ガス圧や放電電圧などの条件を適正な値に設定することで、配線の電気抵抗を低減できる。

【0070】

尚、図2乃至図5において、Mo又はWが配線を形成するための高融点導電体として用いられた場合について述べたが、RuやTaの高融点金属またはシリサイドが用いられた場合においても、上述の製造プロセス及び形成条件が適用可能な範囲において、実質的に同じ効果が得られる。

【0071】

以上のように、本実施形態の半導体装置によれば、配線を低抵抗化できる。

【0072】

(c) 層間絶縁膜の形成条件

図6及び図7を用いて、本実施形態の半導体装置における層間絶縁膜の形成条件について、説明する。

【0073】

層間絶縁膜が形成されるとき、加工された配線の露出面は、層間絶縁膜を形成するための原料ガス、ガス雰囲気及び温度条件にさらされる。そのため、層間絶縁膜の形成条件下において、配線の露出面の酸化又は窒化などの化学反応が生じ、配線の表面に絶縁膜が形成される場合がある。配線が過剰に酸化又は窒化されると、導電性に寄与する配線の配線幅は縮小し、配線の抵抗値の上昇が顕著になる。層間絶縁膜の形成に起因する配線抵抗の上昇を抑制するために、配線が酸化又は窒化しにくい条件下で、層間絶縁膜が形成されることが好ましい。

【0074】

図6は、高融点導電体の酸化速度を説明するための2次元マップである。図6の(a)は、Moの酸化速度(酸化レート)を示している。図6の(b)は、Wの酸化速度を示している。図6の(a)及び(b)において、グラフの横軸は酸素(O2)ガス圧(単位:[Pa])を示し、グラフの縦軸は加熱温度(単位:[℃])を示している。Mo及びWの酸化速度は、Mo酸化膜又はW酸化膜の形成速度に実質的に相当する。

【0075】

図7は、高融点導電体の酸化速度と加熱温度(アニール温度)との関係を示すグラフである。図7の(a)は、O2ガス圧が60Paに設定された場合におけるMo及びWの酸化速度と加熱温度との関係を示している。図7の(b)は、O2ガス圧が300Paに設定された場合におけるMo及びWの酸化速度と加熱温度との関係を示している。図7の(a)及び(b)において、グラフの横軸は加熱温度を示し、グラフの縦軸は酸化速度を示している。

【0076】

図6及び図7に示されるように、Mo層及びW層に関して、酸化雰囲気下における加熱温度が高くなると、酸化速度の増大が顕著になる。また、図6及び図7に示されるように、Mo層及びW層に関して、酸化処理に用いるO2ガス圧が高くなると、Mo層及びW層の酸化が促進される傾向を示している。そして、図6及び図7に示されるように、Wは、Moに比較して、酸化されやすい。

【0077】

図6の(a)及び図7の(a)に示されるように、60PaのO2ガス圧中において600℃の加熱処理が、Mo層に対して施された場合、0.15nm/sec以上の酸化速度を示す。その酸化速度に応じてMo層の表面(露出面)に、Mo酸化膜が形成される。また、図6の(a)及び図7の(b)に示されるように、300PaのO2ガス圧中において600℃の加熱処理が、Mo層に対して施された場合において、0.15nm/sec以上の酸化速度を示し、その速度に応じてMo酸化膜が形成される。

【0078】

この一方、図6の(a)及び図7の(a)及び(b)に示されるように、Mo層に対して450℃程度の加熱処理が施された場合、O2ガス圧が60Paから300Paの範囲内において、0.01〜0.03nm/sec程度の酸化速度を示す。

さらに、Mo層に対して400℃程度の加熱処理が施された場合、O2のガス圧にほとんど依存せずに、Moの酸化速度はほぼ0nm/sec程度となり、Mo層の表面上に、Mo酸化膜はほとんど形成されなくなる。

【0079】

図6の(b)及び図7の(a)に示されるように、60PaのO2ガス圧中において450℃以上の加熱処理が、W層に対して施された場合、0.10nm/sec以上の酸化速度を示し、その酸化速度に応じて、W層の表面(露出面)に、W酸化膜が形成される。これと同様に、図6の(a)及び図7の(b)に示されるように、W層が形成された基板に対して300PaのO2ガス圧中においても450℃以上の加熱処理が施された場合において、0.10nm/sec以上の酸化速度で、W酸化膜が形成される。そして、400℃程度の加熱処理が、W層が形成された基板に対して施された場合において、0.05nm/sec以下になる。加熱処理の温度が320℃以下で、Wの酸化速度は、実質的に0nm/sec程度になる。このように、図6及び図7に示される条件において、Wは、Moに比較して、酸化され易い傾向を示す。

【0080】

配線の線幅が酸化によって縮小すると、配線の抵抗値は増大する。そのため、層間絶縁膜の形成時における酸化雰囲気によって、配線が酸化されないことが好ましい。それゆえ、例えば、配線としての高融点導電層が、Mo層である場合、層間絶縁膜を形成するための温度は、400℃以下であることが好ましい。Mo層を覆う層間絶縁膜を形成するためのO2ガス圧(全圧又は分圧)は、60Pa以下であることが好ましい。また、配線としての高融点導電層が、W層である場合、層間絶縁膜を形成するための温度は、330℃以下であることが好ましい。W層を覆う層間絶縁膜を形成するためのO2ガス圧(全圧又は分圧)は、60Pa以下であることが好ましい。

【0081】

尚、ここでは、層間絶縁膜が酸化雰囲気中で形成される場合について述べたが、例えば、層間絶縁膜(キャップ層又はパッシベーション膜)が窒化雰囲気中で形成される場合においても、高融点導電体の窒化速度を考慮して、層間絶縁膜の形成温度(基板の加熱温度)及びN2ガス圧が適宜設定されることが好ましい。

【0082】

但し、層間絶縁膜の形成温度は、少なくとも層間絶縁膜の形成の初期段階において、例えば、層間絶縁膜の形成が開始されてから層間絶縁膜が高融点導電層(例えば、Mo層)から構成される配線を覆うまでの期間において、400℃以下であればよい。それゆえ、層間絶縁膜の形成工程を2段階に分け、400℃以下の温度条件下において薄い層間絶縁膜が配線上に形成された後、400℃より高い温度条件下において厚い層間絶縁膜が配線上に形成されてもよい。これによって、製造期間の長期化を回避して、配線の低抵抗化ができる。

【0083】

ここでは、Mo及びWが配線としての高融点導電層に用いられる場合について述べた。但し、高融点導電層が、Ru、Ta、又は、シリサイドなどから形成される場合においても、それらの導電層の酸化及び窒化反応、より具体的には、それらの導電層の酸化速度又は窒化速度を考慮して、層間絶縁膜の形成温度やガス圧が、それらの酸化又は窒化を抑制する条件に適宜設定すればよい。これによって、Mo及びW以外の高融点導電体を用いて配線が形成される場合であっても、層間絶縁膜の形成に起因した配線の抵抗値の上昇を抑制できる。

【0084】

尚、層間絶縁膜は、SiN、SiO2、SiOC又はSiCNなどが、配線間に生じる容量の設計に応じて、適宜選択される。層間絶縁膜が窒素又は炭素を含む場合、高融点導電層層の窒化速度又は炭化速度を考慮して、高融点導電層の窒化又は炭化が抑制される条件の層間絶縁膜の形成温度やガス圧が適宜設定すればよい。

【0085】

以上のように、層間絶縁膜を形成するためのガスと高融点導電層との反応速度を考慮して、層間絶縁膜の形成条件を設定することによって、配線としての高融点導電層の抵抗値の増加を抑制でき、配線の低抵抗化に貢献できる。

【0086】

(d) バリア膜及びその形成条件

図8乃至図13を参照して、配線としての高融点導電層上に設けられるバリア膜及びその形成条件について、説明する。

【0087】

図1に示されるように、半導体装置において、配線(高融点導電層)60が形成された後、窒化膜や酸化膜を含む層間絶縁膜68,69,71が、配線60を覆うように形成される。上述のように、層間絶縁膜68,69,71の形成時における酸化雰囲気中や窒化雰囲気中に、加工された配線60の露出面がさらされ、配線60の露出部分が酸化又は窒化される場合がある。図1に示されるように、配線としての高融点導電体層60の側面上に、バリア膜(拡散防止膜)62が設けられることによって、層間絶縁膜の形成時における配線に対する酸化種及び窒化種の拡散を抑制できる。バリア膜62は、例えば、酸化膜、窒化膜又は酸窒化膜から構成される。

【0088】

図8は、バリア膜を形成するための処理時間と高融点導電層の抵抗値の変化との関係を示すグラフである。図8のグラフの横軸は、バリア膜の形成時間(単位:[sec])を示している。図8のグラフの縦軸は、メタル層のシート抵抗(単位:[Ω/□])を示している。バリア膜は、高融点導電層の露出面に対する化学処理(ここでは、酸化処理)によって形成される。酸化処理によってバリア膜が形成される場合、バリア膜の形成時間と形成されるバリア膜の膜厚との間に相関関係が生じる。バリア膜の形成時間が長くなると、バリア膜の膜厚が厚くなる。

【0089】

尚、図8に示される例では、10sec、60sec、120secの処理時間でバリア膜が高融点導電層に形成される場合、及び、高融点導電層にバリア膜が形成されない場合(すなわち、バリア膜の形成時間がゼロ)における、高融点導電層のシート抵抗の変化が、それぞれ示されている。

図8の各サンプルにおいて、各形成時間によってバリア膜が形成された後に、高融点導電層上に、5nm程度の膜厚を有するシリコン窒化膜が形成される。図8において、高融点導電層には、50nm程度の膜厚を有するMo層が用いられている。

【0090】

図8に示されるように、バリア膜が形成された高融点導電層(Mo層)のシート抵抗は、バリア膜が形成されない高融点導電層のシート抵抗に比較して、低減する。これは、バリア膜が、シリコン窒化膜が形成される際の窒化種が高融点導電層に拡散するのを抑制するためである。それゆえ、高融点導電層と層間絶縁膜との間にバリア膜が設けられることによって、高融点導電層内に対する窒素(N)の拡散に起因した高融点導電層の抵抗値の上昇が、抑制される。

【0091】

このように、バリア膜62が、配線としての高融点導電層60の外周(例えば、側面)を覆うように、高融点導電層60と層間絶縁膜との間に形成されることによって、層間絶縁膜に起因する不純物が高融点導電層60内に拡散するのを防止でき、高融点導電層60の電気的特性の劣化を防止できる。

【0092】

例えば、Moのように、窒素の拡散により劣化しやすい高融点導電体が配線に用いられる場合、本実施形態のように、酸化膜からなるバリア膜が高融点導電層(配線)上に形成されることによって、キャップ層(ハードマスク)やパッシベーション膜に起因する窒素がMo層内に拡散するのを抑制することは、有効である。尚、酸素により劣化しやすい高融点導電体が配線に用いられる場合、窒化膜からなるバリア膜が、導電層と酸化膜からなる層間絶縁膜との間に設けられることが好ましい。

【0093】

バリア膜62が、高融点導電層60に対する酸化処理によって形成される酸化膜である場合、高融点導電層60とバリア膜(酸化膜)62との界面に、酸素が存在する。そして、高融点導電層60及びバリア膜62を含む配線構造において、その配線構造内の酸素濃度は、高融点導電層60とバリア膜62との界面(バリア膜側)から高融点導電層60の中央部に向かって、低くなる。これと同様に、バリア膜62が高融点導電層60に対する窒化処理によって形成される窒化膜である場合、高融点導電層60とバリア膜(窒化膜)62との界面に、窒素が存在する。高融点導電層60及びバリア膜62を含む配線構造内における窒素濃度は、高融点導電層60とバリア膜62との界面から高融点導電層60の中央部に向かって、低くなる。

【0094】

このように、バリア膜側から高融点導電層の中央部側に向かって、酸素又は窒素が濃度勾配を有することによって、酸素濃度又は窒素濃度の高いバリア膜側では、バリア膜としての機能を向上でき、酸素濃度又は窒素濃度の低い高融点導電層(配線)の中央部では、電気伝導率が向上する。

【0095】

例えば、高融点導電層60とバリア膜62との界面に、酸素又は窒素が存在する場合、高融点導電層(例えば、Mo層)の界面(表面)が、酸素又は窒素によって終端されている。

【0096】

バリア膜62を形成するための酸化処理(又は窒化処理)の時間が長くなると、高融点導電層60が過剰に酸化され、導電層60の配線幅(断面積)が縮小されるため、導電層60の抵抗値が増加する可能性がある。それゆえ、高融点導電層60に対する不純物の拡散の抑制と配線幅の縮小との関係を考慮して、バリア膜を形成するための酸化処理(又は窒化処理)の時間及びバリア膜の膜厚が、配線材の種類や配線の寸法に応じて、適宜設定されることが好ましい。

【0097】

図8に示される例において、Moが配線材に用いられた場合、Mo層の配線幅及び膜厚の縮小に起因する抵抗値の上昇を抑制するために、30secから130secの範囲内の酸化処理が実行されることが好ましい。但し、Moを用いて形成された配線の寸法に応じて、酸化処理の時間を調整してもよいのは、もちろんである。

【0098】

図6、図7及び図9を用いて、バリア膜の形成条件について、より具体的に説明する。ここでは、Mo及びWからなる高融点導電層を例示して、それらの導電層(Mo層及びW層)上に設けられるバリア膜について、説明する。ここでは、バリア膜がMo層及びW層に対する酸化処理によって形成される場合について述べる。

【0099】

上述のように、図6及び図7は、Mo及びWの酸化速度を示す図である。

図9は、高融点導電体の気化速度を説明するためのグラフである。図9の(a)は、酸素雰囲気中におけるMoの気化速度(気化レート)の2次元マップが示されている。図9の(a)において、グラフの横軸はO2ガス圧(単位:[Pa])を示し、グラフの縦軸は加熱温度を示している。図9の(b)は、O2ガス圧が60Paに設定された場合における、Mo及びWの気化速度と加熱温度との関係を一例として示している。図9の(b)において、グラフの横軸は加熱温度を示し、グラフの縦軸は気化速度を示している。

【0100】

バリア膜がMo層又はW層からなる配線の表面上に形成される場合、バリア膜の形成に起因して配線の抵抗値が上昇するのを抑制するために、導電体の過剰酸化、及び、導電体及び導電体の酸化物の気化(昇華)を考慮して、バリア膜の形成条件が設定されることが好ましい。

【0101】

図9の(a)及び(b)に示されるように、例えば、O2のガス圧が60Paに設定された場合、Moの気化速度は、450℃以下のMo層に対する加熱温度において、ほぼ0nm/sec程度になる。図6及び図7を用いて説明したように、O2ガス圧が60Paに設定された酸化雰囲気中において、Moの酸化速度は、加熱温度が400℃から450℃程度の範囲に設定された場合、0.02nm/secから0.03nm/sec程度になる。また、Mo層に対する加熱温度が500℃以上に設定された場合、Moの気化速度は0.04nm/sec以上になり、Moの酸化速度は0.05nm/sec以上になる。

【0102】

図9の(b)に示されるように、Wの気化速度は、O2のガス圧が60Paに設定された場合において、300℃から700℃の加熱温度の範囲内では、ほぼ0nm/secを示している。そして、図9の(b)に示される例に限らず、60Paから300PaのO2ガス圧の範囲、及び、300℃から700℃の範囲内において、Wは、ほぼ0nm/secの気化速度を示し、ほとんど気化(昇華)しない。このように、Wの気化レートは、Moの気化レートに比較して十分小さい。

【0103】

図6、図7及び図9に示されるように、Mo層がO2のガス圧が60Paの酸化雰囲気中において加熱処理された場合、酸化雰囲気中における500℃以上の加熱温度の条件下では、Moは気化する。そして、その条件下において、Mo(Mo酸化物)の気化速度及びMoの酸化速度は大きくなる。それゆえ、500℃以上の加熱温度において、バリア膜の形成時におけるMo層の過剰酸化やMo(又はMo酸化物)の気化に起因して、配線の導電性に寄与するMo層の寸法(断面積)が減少し、配線の抵抗値が大きくなる可能性がある。

【0104】

したがって、酸化処理によってMo層の側面(露出面)上にバリア膜が形成される場合、Moの気化を防ぐために、Mo層の側面が徐々に(ゆっくりと)酸化され、且つ、Mo(及びMo酸化物)がほとんど気化しない加熱温度及びO2ガス圧が設定されることが好ましい。例えば、Mo層上に酸化膜からなるバリア膜が形成される場合、バリア膜を形成するための酸化雰囲気中におけるMo層に対する加熱温度は、500℃より低い加熱温度、より好ましくは、400℃から450℃の温度範囲に設定される。また、導電体の過剰酸化を抑制するために、導電体の酸化速度は遅いほうが好ましい。それゆえ、Mo層に対する加熱温度が400℃から450℃に設定される場合、バリア膜を形成するためのO2のガス圧は、60Pa程度に設定されることが好ましい。

【0105】

また、Wが配線に用いられた場合、Wはほとんど気化しないので、Wが過剰酸化されないように、Wの酸化速度を考慮して、バリア膜を形成するためのO2のガス圧及び加熱温度が適宜設定される。

【0106】

以上のように、高融点導電体の気化速度が、高融点導電体の酸化速度より小さくなる条件で、バリア膜が高融点金属の配線上に形成されることが好ましい。このようなバリア膜の形成条件が設定されることによって、配線を構成する高融点導電体の気化や過剰酸化による配線の線幅及び膜厚の縮小や、バリア膜の昇華を防止できる。

これによって、バリア膜の形成が原因で配線の抵抗値が上昇するのを、防止できる。

【0107】

Moが配線に用いられた場合におけるバリア膜の形成条件例として、例えば、O2ガス圧が60Paに設定され、400℃から450℃の範囲に加熱温度が設定されることによって、Moの気化速度が、Moの酸化速度より小さくなる。

【0108】

上述のバリア膜の形成条件において、配線としてのMo層に対する酸化処理によって、バリア膜が形成される場合、Mo酸化物が、Mo層上に形成される。図10は、酸化処理によって形成されたMo酸化物の組成の一例のXRDプロファイルを示している。図10におけるXRDプロファイルは、2θ−θ法(粉末法)による測定結果が示されており、グラフの横軸は2θ(単位:[°])を示し、グラフの縦軸は回折強度(単位:[a.u])を示している。

【0109】

図10に示されるように、2θ=26°においてMoO2(11−1)の回折ピーク、2θ=37°においてMoO2(111)の回折ピーク、また、2θ=53.4°においてMoO2(211)の回折ピークが検出されている。

このXRDによる解析結果は、二酸化モリブデン(MoO2)の回折ピークを示している。

【0110】

このように、上記の条件によってMo層上に形成されるバリア膜(Mo酸化物)は、主に、MoO2を含んでいる。尚、Mo層上に形成されるMoの自然酸化膜は、例えば、三酸化モリブデン(MoO3)である。

【0111】

例えば、配線の膜厚が50nm程度である場合、バリア膜としてのMoO2膜の膜厚は、1nmから3nm程度の厚さであることが好ましい。MoO2膜の膜厚が、1nmから3nm程度であれば、配線(高融点導電層)に対する反応種(N)の拡散を抑制でき、かつ、バリア膜の形成による配線幅の縮小に起因した配線の抵抗値の上昇を抑制できる。但し、バリア膜の膜厚は、配線の寸法(膜厚又は幅)に応じて、適宜調整されるのはもちろんである。

【0112】

尚、Mo層上のバリア膜(Mo酸化膜)は、MoO2とMoO3とを両方含む膜でもよい。また、バリア膜は、高融点導電体が含む元素以外に、層間絶縁膜を形成するための元素を含んでいてもよい。例えば、バリア膜(例えば、MoO2を含むMo酸化膜)内に、Si、H、N又はCが、含まれる場合もある。配線としての高融点導電層60がMo層である場合、そのMo層上に形成されるバリア膜は、Mo窒化膜(MoN膜)でもよいのは、もちろんである。

【0113】

ここでは、配線材としてMo及びWが用いられた例について説明したが、導電体の酸化速度及び気化速度を考慮することによって、上述のTa、Ru又はシリサイドなど他の高融点導電体に、バリア膜を形成することができるのはもちろんである。

【0114】

尚、バリア膜としての酸化膜又は窒化膜が、酸化処理又は窒化処理によって形成される場合、酸化種又は窒化種が高融点金属層60の内部に拡散するとともに、酸化膜又は窒化膜の形成による体積の膨張が生じる場合がある。そのため、バリア膜が厚い場合、基板表面に対して水平方向において、バリア膜62の側面が、キャップ層68の側面よりも突出する可能性がある。この場合、配線の幅方向における高融点金属層60とバリア膜62とを含む寸法は、キャップ層69の幅W2よりも大きくなり、キャップ層68とバリア膜62との間に、段差が形成される。それゆえ、バリア膜の膜厚は、1〜3nm程度であることが好ましい。

【0115】

<セルフパッシベーションによるバリア膜の形成>

高融点導電層60上のバリア膜62は、金属のセルフパッシベーション(自己不動態化)によって、形成されてもよい。この場合、配線材として高融点導電体に、配線材として選択された高融点金属以外の元素(例えば、金属元素)が添加される。以下では、高融点導電層に添加される元素(金属元素)のことを、添加元素又は添加金属とよぶ。

【0116】

添加金属は、高融点導電体と添加金属との化合物によって、配線の抵抗値を上昇させない材料から選択されて、高融点導電層60内に添加される(ドーピングされる)ことが好ましい。高融点導電層60内における拡散速度が比較的速い金属が、高融点導電層60内に添加されることが好ましい。さらに、配線材に添加される材料(元素)の融点は、配線材(高融点導電体)の融点より低いことが好ましい。

【0117】

添加金属を含む高融点導電層60に対して酸化雰囲気中又は窒化雰囲気中における加熱処理が施されることによって、高融点導電層60内の添加金属が、高融点導電層の側面(露出面)に析出し、その析出した金属の酸化膜又は窒化膜が、高融点導電層の側面に沿って形成される。

【0118】

本実施形態において、金属のセルフパッシベーションによって形成されたバリア膜のことを、セルフパッシベーション膜とよぶ。

【0119】

図11は、金属の酸化物標準生成エネルギー(酸化物生成エネルギーともよばれる)を示す図である。図11の縦軸は各金属の酸化物の生成エネルギーを示し、図11の横軸は生成される酸化物を示している。

【0120】

例えば、配線としての高融点導電層にMo層又はW層が用いられている場合、Mo又はWの酸化物の酸化物標準生成エネルギー以下の金属元素(材料)が、配線材としてのMo層又はW層に添加されていることが、セルフパッシベーション膜を形成するために、好ましい。Mo酸化物(ここでは、MoO3)及びW酸化物(ここでは、WO2)の生成エネルギーは、450kJ/mol程度である。それゆえ、Mo層又はW層に対する酸化処理によって添加金属のセルフパッシベーション膜がバリア膜として形成される場合において、Mo層又はW層内に添加される金属の酸化物標準生成エネルギーは、450kJ/mol以下であることが好ましい。

また、添加された金属の酸化物が、Mo酸化物又はW酸化物に比較して、化学的に安定な材料であることが好ましい。

【0121】

これを鑑みて、Mo又はWを用いた配線60に対して酸化物からなるセルフパッシベーション膜が形成される場合、アルミニウム(Al)やジルコニウム(Zr)が、Mo層やW層に添加されることが好ましい。Alが、Mo又はW層内に形成された場合、酸化アルミニウム(AlxOy)膜が、Mo層又はW層の側面(露出面)上に形成される。また、ZrがMo又はW層内に形成された場合、酸化ジルコニウム(ZrOy)膜が、Mo層又はW層の側面上に形成される。バナジウム(V)やチタン(Ti)が、Mo層又はW層に添加されてもよい。尚、組成式中のx及びyの値(元素の組成比)は、化学量論的組成(ストキオメトリ)を満たすことが好ましいが、形成条件に応じて、組成のずれを含む場合がある。

【0122】

図12は、金属の窒化物標準生成エネルギー(窒化物生成エネルギーともよばれる)を示す図である。図12の縦軸は各金属の窒化物の生成エネルギーを示し、図12の横軸は生成される金属窒化物を示している。

【0123】

添加された金属元素の窒化物によって、セルフパッシベーション膜が形成される場合においても、添加される金属元素の窒化物生成エネルギーが、配線材としての高融点導電体の窒化物生成エネルギー以下であり、形成された窒化物が高融点導電体の窒化物よりも化学的に安定な材料であることが好ましい。Mo窒化物(ここでは、Mo2N)の生成エネルギーは、例えば、100kJ/mol程度である。例えば、Mo層に対する窒化処理によって添加金属のセルフパッシベーション膜が形成される場合、Mo層に添加される金属の窒化物生成エネルギーは100kJ/mol以下であることが好ましい。

【0124】

例えば、Moを用いて配線60が形成される場合、AlやZrが添加金属として用いられることが好ましい。AlがMo層内に添加された場合、AlxNy膜がMo層の外周(露出面)に沿って形成され、ZrがMo層内に添加された場合、ZrxNy膜がMo層の外周(露出面)に沿って形成される。

【0125】

ここで、図13を用いて、セルフパッシベーション膜の形成方法について、説明する。図13の(a)乃至(c)は、セルフパッシベーション膜の形成方法を説明するための模式図である。

【0126】

例えば、図13の(a)に示されるように、所定の濃度の添加金属81を含む高融点導電層60Xが、基板89上に堆積される。高融点導電層60Xの堆積時において、添加金属81は、高融点導電層60X内において、実質的に均一に分散している。

【0127】

尚、基板(例えば、SiO2層)上に、例えば、窒化モリブデンや窒化チタンなどの密着層(図示せず)が、形成され、その密着層上に、高融点導電層60Xが堆積されてもよい。

【0128】

添加金属81を含む高融点導電層(高融点金属層)60Xは、所定の組成比に設定された添加金属81と高融点金属とを含む合金ターゲットを用いたスパッタ法によって形成されてもよいし、添加金属81の金属ターゲットと高融点導電体のターゲットとを用いたスパッタ法によって形成されてもよい。また、高融点導電層が基板68上に堆積された後に、所定の金属元素がイオン注入によって高融点導電層に添加されてもよい。尚、高融点導電層に対する金属元素の添加は、ここで例示した方法に限定されない。

【0129】

そして、高融点導電層60X上に、マスク層(キャップ層)68が堆積される。

【0130】

図13の(b)に示されるように、パターニングされたマスク層68をマスクにして、添加金属81を含む高融点導電層60が、所定の配線パターンを有するように、加工される。加工された高融点導電60に対して、バリア膜を形成するために、例えば、酸素雰囲気中におけるアニール処理が、実行される。この際、高融点導電層60の露出面(ここでは、側面)から酸素が注入されるとともに、添加金属81が高融点導電層60の露出面側に向かって拡散し、添加金属81が高融点導電層60の露出面側において析出する。このように、添加金属81が高融点導電層60の露出面側へ析出させるために、添加金属81の拡散速度が、高融点導電体の拡散速度より速いことが好ましい。

【0131】

これによって、図13の(c)に示されるように、高融点導電層60の露出面上に、バリア膜としてのセルフパッシベーション膜62Aが、形成される。上述のように、添加金属81の酸化物生成エネルギーが、高融点導電体の酸化物生成エネルギーよりも小さい場合、主に、添加金属81が酸素と反応し、添加金属81の金属酸化膜が、高融点導電層60の露出面(側面)上に、形成される。但し、セルフパッシベーション膜62Aは、添加金属からなる金属酸化物と高融点導電体(高融点金属)からなる酸化物とを含んでいてもよい。

【0132】

添加金属81が高融点導電層60の露出面側に析出し、セルフパッシベーション膜62Aが高融点導電層60の露出面上に形成される結果として、高融点導電層60の中央部(内部)における添加金属81の元素濃度は、高融点導電層60の側面側(外周部)における添加金属81の元素濃度より低くなる。但し、高融点導電層60の中央部における添加金属81の元素濃度が、高融点導電層60の側面側における添加金属81の元素濃度と同程度となる場合もある。

【0133】

セルフパッシベーション膜62Aが形成された後、層間絶縁膜(図示せず)が、高融点導電層60及びセルフパッシベーション膜62Aを覆うように、基板89上に、堆積される。

【0134】

図13の(a)乃至(c)に示されるように、高融点導電層60,60X内に添加された金属81のセルフパッシベーションによって、配線としての導電層60,60Xの側面上に、バリア膜としてのセルフパッシベーション膜82Aが形成される。

【0135】

尚、バリア膜62が添加金属のセルフパッシベーションによって形成される場合においても、セルフパッシベーション膜が酸化膜か窒化膜かに応じて、高融点導電層60とセルフパッシベーション膜62との界面に、酸素又は窒素が存在する。高融点導電層60とセルフパッシベーション膜62とを含む配線構造内における酸素濃度又は窒素濃度は、高融点導電層60とセルフパッシベーション膜62との界面から高融点導電層60の中央部に向かって、低くなる。

【0136】

以上のように、配線の側面にセルフパッシベーション膜62Aが形成されることによって、層間絶縁膜の形成時に生じる酸化種又は窒化種が高融点金属層60内に拡散するのを低減でき、配線の電気的特性の劣化(例えば、抵抗値の上昇)を抑制できる。

【0137】

但し、酸化種/窒化種の拡散を防止できる膜厚のバリア膜が配線の微細化によって形成できない場合や、プロセスの整合性の観点からバリア膜(又はセルフパッシベーション膜)が形成できない場合がある。所定の膜厚のバリア膜が形成された後に、層間絶縁膜が形成されることによって、バリア膜の膜厚が増大し、配線の線幅が縮小する場合がある。或いは、バリア膜内への酸素又は窒素の拡散によって、バリア膜の特性が劣化する場合がある。そのため、バリア膜が形成された場合においても、バリア膜及び配線が劣化しないように、上述のように層間絶縁膜の形成条件を考慮することが好ましい。

【0138】

尚、高融点導電層60の露出面に対する化学反応処理によって形成されるバリア膜69及びセルフパッシベーション膜69は、高融点導電層60上において、不完全な酸化膜又は窒化膜でもよい。不完全な酸化膜又は窒化膜がバリア膜62として高融点導電層60上に設けられた場合においても、そのバリア膜62と高融点導電層60との界面に、酸素又は窒素が存在すればよい。バリア膜62と高融点導電層60との界面に、酸素又は窒素が存在する場合、不完全な酸化膜又は窒化膜は、高融点導電層60とバリア膜との界面において、高融点導電層(例えば、Mo層)の界面(表面)が酸素によって終端されている状態又は窒素によって終端されている状態を、有している。例えば、酸化膜から構成されるバリア膜62は、化学量論的組成に対して酸素欠損を含む膜でよいし、窒化膜から構成されるバリア膜62は、化学量論的組成に対して窒素欠損を含む膜でよい。

【0139】

(e) まとめ

本実施形態の半導体装置は、高融点導電体から構成される配線60を含む。

【0140】

配線60を形成するための高融点導電体は、1000℃以上の融解温度を有している。これによって、半導体装置の製造プロセスの温度条件(1100℃以下)において、融解温度の比較的低い材料(Cu又はAl)に比較して、高温に起因する配線の劣化を抑制できる。

【0141】

例えば、高融点導電体としての金属(高融点金属)には、Mo、W、Ru、Ta、Ni、Coなどが用いられる。高融点導電体としての金属化合物(高融点金属化合物)には、MoSi、WSi、NiSi、CoSiなどのシリサイドなどが用いられる。本実施形態の半導体装置において、これらの高融点金属及び高融点金属化合物のグループから選択される1つの導電体を用いて、配線60が形成される。

【0142】

これらの高融点導電体を用いて配線60が形成されることによって、配線60が含む高融点導電体の結晶粒を大きくでき、配線の抵抗率(抵抗値)を低減できる。

【0143】

配線60を構成する高融点導電体の結晶粒を大きくするために、例えば、高融点導電層60の堆積時における基板加熱処理や高融点導電層の堆積後のポストアニール処理が、高融点導電層60に対して施される。このような高融点導電層60に対する加熱処理によって、高融点導電層60の結晶性が改善され、配線としての高融点導電層60が含む結晶粒が大きくなる。

【0144】

尚、加熱処理による高融点導電層の結晶粒の大粒径化のため、1000℃以下の再結晶化温度を有する高融点導電体が用いられることが好ましい。高融点導電体の再結晶化温度を考慮した場合、配線を構成する高融点導電体には、例えば、Mo、Ru又はTaが用いられる。これによって、半導体装置の製造プロセスが含む温度条件において、配線としての高融点導電層の結晶性の改善(結晶の大粒径化)を、図ることができる。

【0145】

また、加工後の高融点導電層に対して、窒化雰囲気中における還元処理を施すことが好ましい。これによって、配線としての高融点導電層の露出面が還元され、配線の寸法の縮小を抑制でき、配線の抵抗値の上昇を抑制できる。

【0146】

例えば、配線60を覆う層間絶縁膜の形成時において、層間絶縁膜を形成するための条件に起因して、高融点導電体からなる配線の電気的特性が劣化しないように、層間絶縁膜の形成条件が設定される。

【0147】

例えば、層間絶縁膜の形成時、少なくとも層間絶縁膜の成膜時の初期段階において、400℃以下の温度条件下で、酸化物からなる層間絶縁膜が形成されることが好ましい。また、例えば、酸化物から構成される層間絶縁膜を形成するためのO2のガス圧は、60Pa以下であることが好ましい。

【0148】

このように、層間絶縁膜の形成条件を考慮することによって、高融点導電体(例えば、Mo)の過剰な酸化又は窒化が抑制され、導電層の酸化又は窒化に起因した配線幅及び膜厚の縮小が低減される。その結果として、高融点導電体から構成される配線の抵抗値の上昇を、防止できる。

【0149】

例えば、高融点導電体から構成される配線60の側面上に、バリア膜62が設けられる。バリア膜62が、高融点導電層60と層間絶縁膜との間に設けられることによって、層間絶縁膜に起因する不純物が、高融点導電層60内に拡散するのを抑制でき、配線の抵抗の上昇を抑制できる。

【0150】

バリア膜62は、例えば、酸化膜、窒化膜又は酸窒化膜から構成される。例えば、バリア膜62が、配線としての高融点導電層60に対する酸化処理又は窒化処理によって、高融点導電層60の側面上に形成される場合、図1又は図13に示されるように、高融点導電層60の配線幅W1は、高融点導電層60を加工するためのキャップ層(ハードマスク)の幅W2よりも小さくなる。この場合、バリア膜62の側面は、キャップ層68の側面よりも基板表面に対して水平方向にほとんど突出しないので、バリア膜62が交通店導電層60の側面上に形成されたとしても、高融点導電層60とバリア膜62とを含む配線構造の配線幅は拡大しない。また、互いに隣接する配線間の間隔が、バリア膜62の形成によって縮小することもほとんど無い。それゆえ、本実施形態における配線構造は、微細な配線パターンを、比較的容易に形成できる。

【0151】

また、バリア膜62が高融点導電層60に対する酸化処理又は窒化処理によって形成されている場合、キャップ層68の側面とバリア膜62との側面に段差が生じにくい。そのため、バリア膜62を含む配線構造を覆う層間絶縁膜(SiN膜)69の密着性及び被覆性が、改善される。

【0152】

配線の配線幅及び膜厚の縮小を抑制するために、バリア膜62は、高融点導電体の酸化物又は窒化物が形成される条件下において、高融点導電体が徐々に酸化又は窒化され、高融点導電体がほとんど気化しない条件で、形成される好ましい。例えば、Moを用いて形成された配線の側面上に、Mo酸化物を含むバリア膜が形成される場合、O2ガス圧が60Paに設定され、加熱温度が400℃から450℃の範囲に設定された形成条件で、バリア膜(この場合、MoO2を含む膜)が形成されることが好ましい。例えば、バリア膜としてのMoO2膜の膜厚は、1nmから3nm程度であることが好ましい。

【0153】

また、高融点金属60に添加された添加金属のセルフパッシベーションによって、バリア膜62が形成されてもよい。バリア膜62としてのセルフパッシベーション膜が酸化膜である場合、高融点金属に添加される金属には、添加金属の酸化物標準生成エネルギーが高融点金属の酸化物標準生成エネルギー以下の材料が用いられる。セルフパッシベーション膜が窒化膜である場合、添加金属の窒化物標準生成エネルギーが高融点金属の窒化物標準生成エネルギー以下の材料が、添加金属として用いられる。

【0154】

添加金属と高融点導電体との間に高抵抗な化合物を形成しない材料が、添加金属に用いられることが好ましい。拡散速度が高融点金属の拡散速度よりも速い材料が、添加金属に用いられることが好ましい。さらには、化学的に安定な酸化物又は窒化物が形成される材料が、添加金属に用いられることが好ましい。例えば、高融点金属にMo又はWが用いられる場合、例えば、Al又はZrが添加金属として、Mo層又はW層内に添加される。

【0155】

尚、バリア膜としてのセルフパッシベーション膜が形成された場合、配線内における添加金属の濃度プロファイルは、配線の側面側(バリア膜側)における濃度が、配線の中央部における濃度よりも高くなる。

【0156】

このような、高融点導電体に対する酸化/窒化処理又は添加金属のセルフパッシベーションによって形成されたバリア膜が、配線としての高融点導電層の側面上に設けられることによって、高融点導電層の寸法縮小や不純物拡散に起因した配線の抵抗の上昇を、抑制できる。

【0157】

以上のように、本実施形態の半導体装置によれば、半導体装置が含む配線の低抵抗化を図ることができる。

【0158】

(3) 変形例

以下、図14乃至図16を用いて、本実施形態の半導体装置の変形例について説明する。

【0159】

図14に示されるように、配線60Aの構造は、2つの導電体の積層構造でもよい。例えば、ポリメタル構造の配線60Aは、高融点導電層(例えば、Mo層)61が、ポリシリコン層63上に積層されている。ポリシリコン層63は、バリアメタル膜上に設けられてもよいし、層間絶縁膜75上に直接設けられてもよい。

【0160】

配線60Aを覆うバリア膜が、酸化処理によって形成される場合、高融点導電層61の側面上に、高融点導電体の酸化膜が設けられるとともに、ポリシリコン層63の側面上に、酸化シリコン膜が設けられている。また、バリア膜62,64が窒化処理によって形成されてもよい。この場合、高融点導電体の窒化膜が高融点導電層61の側面上に形成されるとともに、窒化シリコン膜64が、ポリシリコン層63の側面上に設けられる。

【0161】

尚、高融点導電体がシリサイドから構成される場合、配線60Aは、ポリシリコンとシリサイドとの積層構造(ポリサイド構造)を有する。

【0162】

図15に示されるように、配線としての高融点導電層60の上面上に、キャップ層は、設けられていなくてもよい。この場合、例えば、高融点導電層60の上面上に、バリア膜(又はセルフパッシベーション膜)62が設けられる。高融点導電層60の上面及び側面を覆うバリア膜62は、キャップ層が除去された後に、形成される。

【0163】

図16に示されるように、隣接する配線(高融点導電層)間の領域は、層間絶縁膜によって埋め込まれなくともよい。この場合、隣接する配線60間に、エアギャップAGが設けられている。エアギャップAGは、空気又は真空の空間である。

【0164】

エアギャップAGは、配線60間の間隔を小さくしたり、埋め込み性の悪い層間絶縁膜75Bを意図的に用いたりすることによって、形成できる。

【0165】

尚、層間絶縁膜が配線60間に埋め込まれていない場合であっても、配線60の上面を覆う層間絶縁膜75Bが形成されている期間において、配線としての高融点導電層60の側面が、酸化雰囲気中に又は窒化雰囲気中にさらされる。それゆえ、エアギャップAGが配線60に隣接する場合であっても、酸化雰囲気中における層間絶縁膜の形成温度が400℃以下に設定される、又は、バリア膜(又はセルフパッシベーション膜)62が高融点導電層60の側面上に設けられることが好ましい。

【0166】

図14乃至図16に示される本実施形態の半導体装置の変形例においても、上述の例と同様に、配線としての高融点導電層が含む結晶の大粒径化及び配線に対する不純物の拡散の抑制によって、配線を低抵抗化できる。

【0167】

(4) 応用例

以下、図17乃至図20を用いて、本実施形態の半導体装置の応用例について、説明する。

【0168】

<例1:電界効果トランジスタ>

本実施形態で述べた高融点導電体から構成される配線は、例えば、電界効果トランジスタ(FET:Field Effect Transistor)に用いることができる。

【0169】

図17は、電界効果トランジスタTrの断面構造の一例を示している。図22は、電界効果トランジスタのチャネル長方向の断面構造を示している。

【0170】

例えば、多層配線構造に用いられる配線60に高融点導電体が用いられるだけでなく、電界効果トランジスタTrのゲート電極21に、上述の高融点導電体が用いられてもよい。

【0171】

電界効果トランジスタTrは、半導体基板10内の素子形成領域(アクティブ領域)内に設けられている。素子形成領域は、素子分離領域内の素子分離絶縁膜19によって、区画されている。素子形成領域内には、P型又はN型のウェル領域(図示せず)が設けられる。

【0172】

ウェル領域内には、2つの拡散層23Aが設けられている。拡散層23は、トランジスタTrのソース/ドレインとして用いられる。例えば、拡散層23Aの表面には、ソース/ドレイン電極23Bが設けられている。

【0173】

2つの拡散層23A間のウェル領域表面には、ゲート絶縁膜22が設けられる。ゲート絶縁膜22は、酸化シリコン膜、酸窒化シリコン膜、高誘電率膜(high−k膜)またはこれらの積層膜うち、いずれか1つから形成される。

【0174】

トランジスタTrのゲート電極21は、ゲート絶縁膜22上に設けられる。ゲート電極21の側面上には、側壁絶縁膜18が設けられている。

【0175】

ゲート電極21上及びソース/ドレイン電極25上には、コンタクトCPがそれぞれ設けられている。各電極21,25は、コンタクトCPを経由して、配線60に接続される。

【0176】

コンタクトCP及び配線60は、層間絶縁膜70,71内に設けられている。

【0177】

配線60は、上述の高融点導電体(例えば、Mo)からなる。

【0178】

トランジスタTrのゲート電極21は、配線60と同様の高融点導電層61を含むゲート構造60Bを有していてもよい。トランジスタTrのゲート電極21が、高融点金属の単層構造である場合、メタルゲート構造の電界効果トランジスタが形成される。尚、トランジスタTrのゲート電極21は、高融点導電体としてのシリサイドの単層構造によって形成されてもよい。ゲート電極21としての高融点導電体は、高融点導電体の仕事関数を考慮して、トランジスタTrの特性及びゲート絶縁膜22の材料に応じて上述の複数の金属及び金属化合物の中から適宜選択される。

【0179】

図17に示されるように、トランジスタTrのゲート電極21は、高融点導電層とポリシリコンとの積層構造(ポリメタル構造又はポリサイド構造)でもよい。但し、高融点金属層とポリシリコン層との間に、高融点金属層とポリシリコン層との化合物層(シリサイド層)が形成される場合がある。

【0180】

また、ソース/ドレイン電極23Bに、高融点導電体(金属層又はシリサイド層)が用いられてもよい。

【0181】

ゲート電極21が含む高融点導電層61と側壁絶縁膜18との間に、バリア膜62が設けられてもよい。また、高融点導電層61は、高融点導電体以外の金属元素が添加されていてもよく、添加された金属元素の化合物膜(例えば、酸化膜又は窒化膜)からなるセルフパッシベーション膜が、バリア膜62として、ゲート電極21の側面上に形成されてもよい。バリア膜62が高融点金属層61の側面上に設けられている場合、側壁絶縁膜18は、設けられなくともよい。なお、ゲート電極21が、ポリメタル構造又はポリサイド構造を有する場合、ポリシリコン層63の側面上のバリア膜62は、酸化シリコン膜又は窒化シリコン膜から構成される。

【0182】

このように、図1乃至図16を用いて説明された配線としての高融点導電体を、電界効果トランジスタTrに適用することができる。

【0183】

<例2:フラッシュメモリ>

図18を用いて、本実施形態の半導体装置の応用例2について、説明する。

【0184】

本実施形態で述べた高融点導電体から構成される配線は、例えば、フラッシュメモリに用いることができる。

【0185】

図18は、NAND型フラッシュメモリが含む1つのメモリセルユニットの断面構造を示している。図18は、カラム方向(ビット線の延在方向)に沿うメモリセルユニットの断面構造を示している。

【0186】

1つのメモリセルユニットは、NANDストリングとNANDストリングの一端及び他端に接続されたセレクトトランジスタSTとから構成される。NANDストリングは、複数のメモリセルMC(例えば、n個)の電流経路(チャネル領域)が直列接続されることによって、形成されている。

【0187】

図18に示されるように、メモリセルユニットは、半導体基板10内の素子形成領域に配置される。ロウ方向(ワード線の延在方向)に互いに隣接する素子形成領域は、素子分離絶縁膜(図示せず)によって互いに電気的に分離されている。

【0188】

メモリセルMCは、例えば、電荷蓄積層24上にコントロールゲート電極25が積層されたゲート構造を有する電界効果トランジスタである。メモリセルMCのゲート構造は、電荷蓄積層24にフローティングゲート電極を用いたスタックゲート構造でもよいし、電荷蓄積層24にトラップ準位を含む絶縁膜(例えば、窒化シリコン膜)を用いたMONOS構造でもよい。図18には、フローティングゲート電極が電荷蓄積層24に用いられた例が示されている。

【0189】

電荷蓄積層24としてのフローティングゲート電極(ポリシリコン層)は、半導体基板1表面に形成されたゲート絶縁膜(トンネル絶縁膜)22A上に設けられる。

【0190】

コントロールゲート電極26は、フローティングゲート電極24上のゲート間絶縁膜25を介して、フローティングゲート電極24上に積層されている。

【0191】

コントロールゲート電極26は、ロウ方向に延在し、ロウ方向に隣接する複数のメモリセルMCで共有される。コントロールゲート線26は、ワード線WLとして用いられる。

【0192】

コントロールゲート電極26は、高融点導電層(例えば、Mo層)60を含む。コントロールゲート電極26は、高融点金属層(例えば、Mo層)60の単層構造でもよいし、高融点金属層60を含むポリメタル構造でもよい。また、コントロールゲート電極26は、高融点導電体としてのシリサイドの単層構造でもよいし、高融点金属層とシリサイド層とのポリサイド構造でもよい。

【0193】

カラム方向に隣接する複数のメモリセルMCは、ソース/ドレインを共有する。これによって、複数のメモリセルMCの電流経路が直列接続される。例えば、メモリセルMCのソース/ドレインとして、拡散層23Aが半導体基板10内に設けられている。但し、拡散層23Aは、形成されなくともよい。

【0194】

NANDストリングの一端(ドレイン側)及び他端(ソース側)には、セレクトトランジスタSTがそれぞれ設けられる。セレクトトランジスタSTの電流経路の一端は、拡散層23Aを介して、隣接するメモリセルMCにそれぞれ接続されている。

【0195】

セレクトトランジスタSTは、メモリセルMCとほぼ同時の工程で形成される。セレクトトランジスタSTのゲート電極29の下部電極層は、フローティングゲート電極24と同時に形成される。セレクトトランジスタSTのゲート電極29の上部電極層は、コントロールゲート電極と同時に形成される。セレクトトランジスタSTにおいて、上部電極層は、上部電極層と下部電極層との間の絶縁膜(ゲート間絶縁膜)に形成された開口部を介して、下部電極層に電気的に接続している。

【0196】

セレクトトランジスタの上部電極層は、コントロールゲート電極26と同様に、高融点導電体を含んでいる。セレクトトランジスタSTの上部電極層は、ロウ方向に隣接する複数のセレクトトランジスタで共有される。セレクトトランジスタSTのゲート電極29は、セレクトゲート線として用いられる。

【0197】

メモリセルユニットのドレイン側のセレクトトランジスタSTの電流経路の他端(ドレイン)23は、ビット線コンタクトBC、中間配線M0及びビアプラグV1を経由して、ビット線BLに接続される。メモリセルユニットのソース側のセレクトトランジスタSTの電流経路の他端(ソース)23は、ソース線コンタクトSCを経由して、ソース線SLに接続される。

【0198】

各コンタクトBC,SC,V1及び配線M0,BL,SLは、層間絶縁膜70,71内に形成されている。

【0199】

例えば、ビット線BL、ソース線SL及び中間配線M0は、上述の高融点導電体(例えば、Mo)を含んでいる。ビアプラグV1が、高融点導電体から形成されてもよい。

【0200】

このように、図1乃至図16を用いて説明された配線としての高融点導電体を、フラッシュメモリに適用することができる。

【0201】

<例3:抵抗変化型メモリ>

図19及び図20を用いて、本実施形態の半導体装置の応用例3について、説明する。

本実施形態で述べた高融点導電体から構成される配線は、例えば、抵抗変化型メモリに用いることができる。

【0202】

図19は、抵抗変化型メモリの断面構造を示している。

図19に示されるように、抵抗変化型メモリは、クロスポイント型メモリセルアレイ1を有している。クロスポイント型メモリセルアレイ1は、例えば、半導体基板10上に積層された層間絶縁膜70,71,72上に設けられている。この場合、半導体基板10上の層間絶縁膜が、クロスポイント型メモリセルアレイ1を形成するための基板として、用いられる。

【0203】

クロスポイント型メモリセルアレイ1は、複数のセルユニットCUを含んでいる。セルユニットCUは、ロウ方向に延在するワード線(第1制御線)WLとカラム方向に延在するビット線(第2の制御線)BLとの間に、設けられている。

【0204】

図20は、セルユニットCUの構造を模式的に示す鳥瞰図である。

【0205】

抵抗変化型メモリにおいて、メモリ素子30は、例えば、可変抵抗素子又は相変化素子である。

【0206】

メモリ素子30としての可変抵抗素子は、金属酸化物からなる膜31を含んでいる。これらの金属酸化物の薄膜31に所定の電圧(又は電流)が印加された場合、その膜31の抵抗値が印加された電圧に応じて可逆的に変化する。可変抵抗素子3の抵抗値が変化した状態は、所定の電圧が印加されるまで、ほぼ不揮発に維持される。このような金属酸化膜31の特性を利用して、可変抵抗素子を用いたメモリ素子3が、形成される。可変抵抗素子3が含む抵抗状態が変化する膜31のことを、抵抗変化膜31とよぶ。抵抗変化膜31は、酸化チタン(TiOx)又は酸化ハフニウム(HfOx)などの遷移金属の酸化物から形成される。

【0207】

金属酸化膜からなる抵抗変化膜31における抵抗状態の変化のメカニズムの一例として、抵抗変化膜31内における微細な電気経路(以下、フィラメントとよぶ)の形成及び消失に起因する抵抗変化が、挙げられる。フィラメントは、局所的な絶縁破壊や金属原子の偏析によって形成される。また、抵抗変化膜31内における金属イオン又は酸素イオンの移動によって、抵抗変化膜31の抵抗状態が変化する場合もある。

【0208】

メモリ素子としての相変化素子は、例えば、与えられた熱によって膜の結晶状態(相)が変化する膜(以下、相変化膜とよぶ)31を含んでいる。相変化膜31は、例えば、GeSbTe(GST)やInSbTe(IST)などの化合物から形成される。

【0209】

例えば、メモリ素子3としての相変化素子3に印加された電圧又は電流によって生じた熱によって、相変化膜31の結晶の配向状態が変化する。この結果として、相変化素子の抵抗値が変化する。

【0210】

抵抗変化膜(又は相変化膜)31は、2つの電極層32A,32Bに挟まれている。例えば、電極層32A,32Bの材料は、抵抗変化膜31の材料に応じて、適宜選択されることが好ましい。尚、メモリ素子30が相変化素子である場合、相変化膜31と一方の電極層との間に、ヒータ層が設けられてもよい。

【0211】

尚、MTJ(Magnetic Tunnel Junction)素子がメモリ素子30に用いられてもよい。

【0212】

セルユニットCUは、動作の対象となったメモリ素子と動作の対象となっていないメモリ素子との相互干渉を抑制するために、選択素子として含んでいる。選択素子として、例えば、ダイオードがセルユニットCU内に設けられている。クロスポイント型メモリセルアレイにおいて、セルユニットCUは、メモリ素子3とダイオード35との積層構造を有する。図20に示される例では、メモリ素子3が、ダイオード35上に積層されている。但し、ダイオード35が、メモリ素子3上に積層されてもよい。セルユニットCU内において、ダイオード35は、メモリ素子3に直列に接続されている。尚、ダイオード35の代わりに、キャパシタが、セルユニットCU内に設けられてもよい。

【0213】

ビット線BL及びワード線WLは、上述の高融点導電層(例えば、Mo)を用いて、形成されている。例えば、ビット線BL又はワード線WLとしての高融点導電層60の側面上に、バリア膜(又はセルフパッシベーション膜)62が、設けられている。

【0214】

本実施形態において、クロスポイント型メモリセルアレイ1より下層の半導体基板10上において、メモリセルアレイの動作を制御するための回路(以下、周辺回路とよぶ)が設けられている。周辺回路が設けられる領域を、周辺領域9とよぶ。周辺回路は、その構成素子として、電界効果トランジスタTr、抵抗素子、キャパシタなどを含んでいる。抵抗変化型メモリの周辺回路を形成する電界効果トランジスタTrは、図17に示されるように、高融点導電体からなるゲート電極又はソース/ドレイン電極を含んでもよい。

【0215】

半導体基板10表面に対して水平方向において、クロスポイント型メモリセルアレイ1に隣接するように、フックアップ領域(引き出し領域ともよばれる)7が、層間絶縁膜72上に設けられる。

【0216】

ビット線BL及びワード線WLは、クロスポイント型メモリセルアレイ1内からフックアップ領域7内に引き出される。フックアップ領域7内において、ビット線BL及びワード線WLの配線幅、隣接する配線間の配線ピッチ、及び、配線レイアウトが変換される。フックアップ領域7において、ビット線BL及びワード線WLは、コンタクトプラグZCを介して、下層又は上層の配線(高融点導電層)60に接続されている。メモリセルアレイ1を覆う層間絶縁膜73,74内において、コンタクトプラグZCは、例えば、複数の配線レベルにまたがって設けられる。

【0217】

半導体基板10上に形成された素子Trは、フックアップ領域7内の配線60及びコンタクトプラグZCを経由して、メモリセルアレイ1に、接続される。

【0218】

図19において、クロスポイント型メモリセルアレイ1に対してロウ方向に隣接するフックアップ領域のみが図示されているが、クロスポイント型メモリセルアレイ1に対してカラム方向に隣接するフックアップ領域が、層間絶縁膜(基板)72上に設けられているのはもちろんである。

【0219】

尚、抵抗変化型メモリの配線レイアウトに応じて、ビット線と同じ配線レベルの配線が、メモリセルアレイ1のロウ方向に隣接するフックアップ領域7内に、引き出されてもよいのはもちろんである。

【0220】

図19に示されるように、クロスポイント型メモリセルアレイ1の動作を制御する周辺回路は、層間絶縁膜70,71,72を介して、クロスポイント型メモリセルアレイ1下方の半導体基板10上に形成される。周辺回路とフックアップ領域7内の配線(高融点導電層)60とを接続する中間配線M0,M1やビアプラグVPに、配線60を形成するための高融点導電体と同じ材料(例えば、Mo)が用いられてもよい。

【0221】

周辺領域9上に、クロスポイント型メモリセルアレイ1が積層されることによって、抵抗変化型メモリのチップサイズが縮小される。

【0222】

例えば、セルユニットCU内のダイオード35がシリコンから形成される場合、抵抗変化型メモリの製造工程において、シリコンの結晶化のために、700℃以上の加熱処理を含む場合がある。それゆえ、本実施形態のように、高融点金属が配線に用いられることは、抵抗変化型メモリの製造工程に有効である。

【0223】

尚、上述の応用例1乃至3で述べた半導体装置に限定されず、DRAM又はSRAMなどの半導体メモリ、或いは、イメージセンサ(固体撮像装置)に、本実施形態で述べた高融点導電体を含む配線60が用いられてもよい。また、高融点導電体を含む配線60は、多層配線構造の半導体装置において、半導体基板直上の配線レベル(最下層の配線レベル)の配線に用いられてもよいし、半導体パッケージに設けられたパッド直下の配線レベル(最上層の配線レベル)の配線に用いられもよい。また、上層の配線レベルになるに従って配線幅を大きくできるので、上層の配線は、Al又はCuを用いて構成し、下層の配線は、本実施形態の高融点導電体(例えば、Mo)を用いて構成してもよい。

【0224】

(5) 製造方法

図21乃至図30を参照して、本実施形態の半導体装置の製造方法について、説明する。

【0225】

<製造方法1>

図21乃至図24を用いて、本実施形態の半導体装置の製造方法1について、説明する。図21乃至図24は、本実施形態の半導体装置の製造方法1における各工程の断面工程図を模式的に示している。

【0226】

図21示されるように、例えば、トランジスタ、キャパシタ、メモリ素子等の半導体装置の構成素子(図示せず)が、半導体基板10の表面上に形成される。素子が形成された半導体基板10上に、層間絶縁膜78が、例えば、CVD法(Chemical Vapor Deposition)又は塗布法を用いて、形成される。形成された層間絶縁膜78の上面は、例えば、CMP(Chemical Mechanical Polishing)などによって、平坦化される。

【0227】

開口部(図示せず)が、層間絶縁膜78内の所定の位置に形成される。その開口部内及び層間絶縁膜78上に、導電体が、例えば、PVD法(Physical Vapor Deposition)によって、形成される。そして、導電体が開口部内に残存するように、CMP又はエッチバックが導電体に対して施される。これによって、導電体が開口部内に埋め込まれ、コンタクトプラグ(図示せず)又はビアプラグ(図示せず)が、層間絶縁膜78内に形成される。プラグを形成するための導電体は、上述の高融点導電体(例えば、W又はMo)でもよい。

【0228】

プラグ上及び層間絶縁膜78上に、密着層(バリアメタル膜)67及び配線材60Zが、それぞれ所定の膜厚を有するように、順次堆積される。密着層67は、配線材60Zと層間絶縁膜78との密着性を確保するために設けられている。例えば、密着層67には、配線材60Zに応じて、窒化タングステン(WN)、MoN、Ti、TiN、Ta、窒化タンタル(TaN)、Ru、窒化ルテニウム(RuN)を含むグループの中から選択される。

【0229】

例えば、配線材60Z及び密着層67は、PVD法によって、それぞれ堆積される。例えば、DCスパッタ法によって配線材60Zが堆積される場合、スパッタガスとしてのArガスのガス圧は、1Pa以下に設定され、放電電圧は300V以上に設定されることが好ましい。

【0230】

例えば、配線材60Zは、Mo、W、Ru、Ta、Co及びNiを含むグループから選択される。また、配線材60Zは、高融点金属に限定されず、MoSi、WSi、NiSi、CoSiなどのシリサイドでもよい。配線材60ZがMoである場合には、上述の密着層67の材料のうち、MoN又はTiNが、選択される。但し、密着層67は、形成されなくともよく、配線材60Zが、層間絶縁膜78上に直接形成されてもよい。

【0231】

上述の高融点金属及びシリサイドを含む高融点導電体のうち、1000℃以下の再結晶化温度を有する導電体(例えば、Mo、Ru又はTa)が、配線材60Zに用いられることが、さらに好ましい。配線材60Zは、シリコン層と高融点金属層との積層構造でもよいし、シリサイド層とシリコン層との積層構造でもよいし、シリサイド層の単層構造でもよい。

【0232】

金属元素のセルフパッシベーションを利用してバリア膜が形成される場合、配線材としての高融点金属に、高融点金属以外の金属(金属元素)が添加されてもよい。添加される金属は、配線材60Zとしての高融点金属(例えば、Mo又はW)よりも速い拡散速度を有する金属の中から選択されることが好ましい。また、添加金属と高融点金属とから形成される化合物が高い抵抗を有さない材料(添加金属)が、高融点導電体に添加されることが好ましい。また、化学的に安定な酸化物及び窒化物を形成する材料(添加金属)が、高融点金属内に添加されることが好ましい。

【0233】

添加された金属の酸化物生成エネルギーが高融点金属の酸化物生成エネルギーより小さい材料の中から、添加される金属が選択されることが好ましい。高融点金属層60Zが、Mo又はWから形成される場合、酸化物生成エネルギーが450kJ/mol以下の材料がMo層又はW層に添加されることが好ましく、例えば、Al、Zr、Ti及びVなどから選択される少なくとも1つの材料が、添加金属として用いられる。

【0234】

金属の窒化物生成エネルギーが高融点金属の窒化物生成エネルギーより小さい材料が、高融点金属層内に添加されてもよい。高融点金属層60Zが、Moである場合、窒化物生成エネルギーが100kJ/mol以下の材料がMo層内に添加されることが好ましく、例えば、Al、Zr、Ti及びVなどから選択される少なくとも1つの材料が、添加金属として用いられる。

【0235】

添加金属は、スパッタリングされるターゲットに含まれてもよいし、イオン注入によって、堆積された配線材に添加されてもよい。

【0236】

上述したように、配線材60Zが堆積されている期間内において、基板10に対して、例えば、400℃から500℃の温度範囲の加熱処理が施されてもよい。基板加熱処理が施された高温条件下において、配線材60Zが層間絶縁膜78上に堆積されることによって、配線材としての高融点導電層60Zの結晶成長が促進され、高融点導電層60Zを構成する結晶粒が大きくなる。これによって、結晶粒界が減少し、配線の低抵抗化を図ることができる。尚、基板加熱処理の温度は、配線を構成する高融点導電体に応じて、500℃以上の温度に設定されてもよいし、400℃以下の温度に設定されてもよい。尚、基板加熱処理によって配線材が堆積される場合、酸素や窒素などのように、配線材60Zと反応し易いガスは、成膜条件下に含まれていないことが好ましい。

【0237】

尚、配線材60Zがポリメタル構造を有している場合、高融点金属層の結晶化のための加熱処理によって、高融点金属層とポリシリコン層との間にシリサイド層が形成される場合がある。

【0238】

窒化シリコン(SiN)層68が、キャップ層(又は、マスク層)として、例えば、400℃以下の成膜温度のプラズマCVD法を用いて、配線材60Z上に堆積される。さらに、キャップ層68上に、酸化シリコン層(例えば、TEOS層)90が、堆積される。配線材60Zに直接接触する絶縁膜(ここでは、SiN層)が、配線材60Z上に形成される際、配線材60Zが窒化(又は酸化)されないように、N2(又O2)のガス圧や成膜時の温度が適宜設定されることが好ましい。

【0239】

図22に示されるように、酸化シリコン層90上に、フォトリソグラフィ工程によって、所定のパターンを有するレジストマスク(図示せず)が形成される。そして、レジストマスクをマスクに用いて、酸化シリコン層90が、RIE法によって加工される。これによって、所定の配線パターンを有するマスク層90が、SiN層68上に、形成される。マスク層90が形成された後、レジストマスクは、除去される。

【0240】

加工されたマスク層90をマスクに用いて、キャップ層68、配線材60Z及び密着層67が、RIE(Reactive Ion Etching)法によって、加工される。尚、RIEに用いられるエッチングガスは、マスク層や配線材等の種類及びそれらの組み合わせに応じて、塩素(Cl)系ガスが用いられてもよいし、フッ素(F)系のガスが用いられてもよい。

【0241】

このキャップ層及び配線材に対するエッチングによって、図23に示されるように、所定のパターン(レイアウト、配線幅及び配線ピッチ)を有する高融点導電層(配線)60が、層間絶縁膜78上及びプラグ(図示せず)上に、形成される。

【0242】

尚、配線のパターニング及び加工は、側壁転写技術によって形成された側壁膜をマスクに用いて、実行されてもよい。

【0243】

キャップ層68上のマスク層及び加工で生じた残渣が除去された後、高融点導電層60が、還元雰囲気中で熱処理される。還元雰囲気は、水素(H2)ガス又はアンモニア(NH3)ガス等を用いて、形成される。この還元雰囲気中の熱処理によって、高融点導電層60に対する還元処理が施される。すなわち、加工によって生じた高融点導電層60上の表面酸化膜(自然酸化膜)が還元され、その酸化膜が、高融点導電層60の表面から除去される。これによって、高融点導電層上の自然酸化膜に起因する配線の寸法の縮小が、抑制される。

【0244】

そして、高融点導電層60の大粒径化(再結晶化)のためのポストアニール処理が、実行される。このポストアニール処理は、還元雰囲気中の熱処理と共通化されてもよいし、別途の工程で実行されてもよい。

【0245】

図24に示されるように、配線としての高融点導電層60の側面(及び上面)上に、バリア膜62が形成される。

【0246】

例えば、高融点導電体(高融点金属)の酸化物がバリア膜として形成される場合、高融点導電体の酸化速度が、高融点導電体(及びその酸化物)の気化速度より大きくなるように、バリア膜62を形成するための酸化雰囲気のガス圧及び加熱温度(アニール温度)が設定される。このような条件が設定されることによって、高融点導電体(又は高融点導電体の酸化物)が気化(昇華)せずに、バリア膜62としての酸化膜が、高融点金属層60の側面上に残留する。

【0247】

例えば、高融点導電層60としてのMo層の側面上に、Mo酸化膜が形成される場合、加熱温度が400℃から450℃の温度範囲に設定され、酸化雰囲気中におけるO2ガス圧が60Pa以下に設定されることが好ましい。これによって、高融点導電体の気化や高融点導電体の過剰酸化に起因する配線の寸法(配線幅または膜厚)の縮小が低減され、バリア膜の形成に起因した配線の抵抗値の上昇が抑制される。尚、高融点導電体がほとんど気化しない条件下で、高融点導電層60上に、バリア膜としての酸化物が形成されることがさらに好ましい。

【0248】

例えば、バリア膜62としてのMo酸化膜は、少なくともMoO2を含む膜である。上記の加熱温度及びガス圧の条件において、バリア膜としてのMoO2膜の膜厚が、1nmから3nm程度の範囲になるように、アニール処理の時間が設定されることが好ましい。

【0249】

尚、高融点導電体の大粒径化のためのポストアニール処理が、バリア膜を形成するための加熱処理と共通化されてもよい。

【0250】

高融点導電体(高融点金属)の窒化物がバリア膜として形成される場合においても、高融点導電体の窒化速度が、高融点導電体(又はその窒化物)の気化速度より大きくなるように、窒化雰囲気のガス圧及び加熱温度が設定される。尚、上述の表面酸化膜の除去のための還元雰囲気中の熱処理時において、還元雰囲気を形成するためのガスに、所定のガス圧のNH3ガスを用いたり、還元熱処理中又は還元熱処理後に、N2ガス又はNH3ガスを混合したりすることによって、高融点導電層60の露出面(例えば、側面)上に、バリア膜62としての窒化膜が、表面酸化膜の除去とほぼ同時に形成されてもよい。

【0251】

上述のように、高融点導電層60に、高融点金属以外の金属(金属元素)が添加されている場合、図13を用いて説明したように、その添加された金属元素が、酸化雰囲気中又は窒化雰囲気中の加熱処理によって、高融点配線層の露出面側(ここでは、側面側)に析出し、添加金属のセルフパッシベーション膜が、バリア膜として、高融点配線層60の側面上に、形成される。

【0252】

但し、セルフパッシベーションを促進するために、添加金属の酸化物生成エネルギー又は窒化物生成エネルギーが、高融点金属の酸化物生成エネルギー又は窒化物生成エネルギーより小さい材料の中から、添加される金属が選択されている。高融点導電層60がMo層である場合、上述のように、AlやZrなどが添加され、Alの酸化物、Alの窒化物、Zrの酸化物或いはZrの窒化物が、パッシベーション膜として形成される。尚、添加金属のセルフパッシベーション膜がバリア膜62として形成される場合、高融点導電層60内における添加金属の濃度プロファイルにおいて、高融点導電層60の露出面側(バリア膜側)における添加金属の濃度が、高融点導電層60の中央部における添加金属の濃度より高くなっている。

【0253】

バリア膜(又はセルフパッシベーション膜)62は、高融点金属と添加金属とを含む酸化物、又は、高融点金属と添加金属とを含む窒化物から構成されてもよい。

【0254】

バリア膜(又はセルフパッシベーション膜)が形成される前に、キャップ層68が高融点導電層60上から除去されてもよい。この場合、高融点導電層60の側面上に加えて、高融点導電層60の上面上に、バリア膜62が、形成される。高融点金属層の大粒径化のための加熱処理が、添加金属のセルフパッシベーション膜を形成するための加熱処理と共通化されてもよい。

【0255】

バリア膜(又はセルフパッシベーション膜)62が高融点導電層60に対する酸化処理によって形成された場合、高融点導電層60とバリア膜62との界面に、酸素が存在する場合がある。この場合、高融点導電層60とバリア膜62とを含む配線構造において、高融点導電層60とバリア膜62との界面における酸素濃度は、高融点導電層60の中央部における酸素濃度より高くなる。これと同様に、バリア膜(又はセルフパッシベーション膜)62が高融点導電層60に対する窒化処理によって形成された場合、高融点導電層60とバリア膜62との界面に、窒素が存在する。この場合、高融点導電層60とバリア膜62とを含む配線構造において、高融点導電層60とバリア膜62との界面における窒素濃度が、高融点導電層60の中央部における窒素濃度より高くなる。

【0256】

このように、バリア膜62としての機能を向上させるために、高融点導電層60とバリア膜62との界面において、酸素濃度又は窒素濃度が高くなるように、バリア膜の形成条件が設定されることが好ましい。また、配線(高融点導電層)60の電気伝導率を高くする(配線を低抵抗化する)ために、高融点導電層60の中央部の酸素濃度又は窒素濃度が低くなるように、バリア膜62の形成条件が設定されることが好ましい。

【0257】

バリア膜62が高融点導電層に対する酸化反応又は窒化反応によって形成された場合、導電層60の配線幅は、キャップ層68の配線幅より小さくなる。また、この場合、バリア膜62の側面とキャップ層68との側面との間に、段差はほとんど生じない。このように、バリア膜62が形成されることによって、高融点導電層60とバリア膜62とを含む配線構造の配線幅が広くならずに、微細なパターンを形成できる。

【0258】

そして、高融点導電層60を覆うように、層間絶縁膜が形成される。層間絶縁膜には、SiN、SiO2、SiOC又はSiCNなどのシリコン化合物が、配線間の容量の設計にあわせて、適宜選択される。

【0259】

例えば、図25に示されるように、層間絶縁膜(パッシベーション膜)としてのSiN膜69が、例えば、500℃の温度条件下におけるALD法(Atomic Layer Deposition)によって、堆積される。さらに、層間絶縁膜としてのSiO2層(図示せず)が、例えば、CVD法又は塗布法によってSiN膜69上に堆積される。

【0260】

上述のように、バリア膜62が、高融点導電層60の側面上に設けられていることによって、層間絶縁膜としてのSiN膜69が形成される際の窒化種(N)が、高融点導電層60内に拡散するのを抑制できる。それゆえ、窒素の拡散に起因した高融点金属層60の抵抗値の上昇が抑制される。

【0261】

例えば、窒素に起因する悪影響を受け易い高融点導電体が、配線を形成するための導電層60に用いられた場合、酸化膜からなるバリア膜が、Mo層の端部に設けられることは、有効である。

【0262】

また、バリア膜が高融点導電層に対する酸化処理又は窒化処理によって形成されている場合、キャップ層の側面とバリア膜62との側面に段差が生じにくい。そのため、バリア膜を含む配線構造に対する層間絶縁膜(SiN膜)69の密着性が向上し、後の工程で形成される層間絶縁膜の被覆性が改善される。

【0263】

酸化物からなる層間絶縁膜が、高融点導電層上に形成される場合、層間絶縁膜としてのシリコン酸化物の形成温度は、その層間絶縁膜の形成の初期段階において、400℃から450℃の温度範囲、より好ましくは、400℃以下に、設定されることが好ましい。また、酸化物からなる層間絶縁膜の形成時において、酸素のガス圧が、60Pa以下の条件になるように、設定される。このように、温度条件やガス圧条件が設定されることによって、配線としての高融点導電体の異常酸化や、バリア膜の劣化、高融点導電体及びバリア膜の気化が抑制される。この結果として、配線の寸法の縮小に起因した配線の抵抗値の上昇及び配線内に対する不純物の拡散に起因した配線の抵抗値の上昇が、抑制される。

【0264】

尚、酸化物からなる層間絶縁膜の堆積の初期段階において、400℃以下の成膜温度で、高融点導電体を含む配線を覆うように、薄い層間絶縁膜を堆積した後、400℃より高い成膜温度で、厚い層間絶縁膜を堆積してもよい。このように、ある配線レベルの層間絶縁膜が複数の段階(成膜温度の条件)に分けて形成される場合、高融点導電層に対するポストアニール処理が、層間絶縁膜の形成と共通化されてもよい。また、図16を用いて説明したように、隣接する配線(高融点導電層)60間を層間絶縁膜によって完全に埋め込まずに、エアギャップを形成してもよい。

【0265】

配線60の上面に接続されるプラグの形成位置において、層間絶縁膜及びキャップ層68が、フォトリソグラフィ工程及びエッチングによって、配線60上方から除去され、配線60の上面が露出される。そして、所定の配線レベルに達するまで、上述の配線の形成工程が繰り返され、本実施形態の半導体装置が形成される。

【0266】

上述の半導体装置の製造方法において、PVD法で堆積された高融点導電層について述べたが、PVD法に限定されたパラメータ以外については、CVD法に対しても共通のパラメータを適用できる。

【0267】

以上のように、本実施形態の半導体装置の製造方法において、高融点導電体を用いて配線60が形成される。配線としての高融点導電層60は、融解温度が1000℃以上の材料から形成され、例えば、Mo、W、Ru、Ta、Co及びNiを含むグループから選択される1つの材料から形成される。また、高融点導電層60はシリサイドを用いて形成されてもよい。配線としての高融点導電層60は、例えば、Mo、Ru及びTaのように、再結晶化温度が1000℃以下の材料から形成されることが好ましい。

【0268】

これによって、本実施形態の半導体装置の製造方法は、耐熱性を有する高融点導電体を用いて配線が形成されることによって、低融点の配線材に比較して、熱に起因した配線の劣化を抑制できる。また、再結晶化温度が1000℃以下の配線材が用いられることによって、製造工程の増加無しに、高融点導電体から構成される配線の結晶性の改善(再結晶化)を実行できる。

【0269】

本実施形態の半導体装置の製造工程中において、配線としての高融点導電層60の堆積中又は堆積後に、高融点導電層60に対して熱が印加される。これによって、高融点導電層60の結晶化が促進され、高融点導電層60が含む結晶粒が、大粒径化する。この結果として、本実施形態の半導体装置において、電子の粒界散乱が低減し、高融点導電層60から形成される配線の抵抗値(抵抗率)は、低下する。

【0270】

例えば、Moのように、再結晶化温度が1000℃以下の高融点導電体は、再結晶化温度が1000℃より大きい高融点導電体に比較して、加熱による高融点導電層が含む結晶の大粒径化の効果が大きく、配線の低抵抗化をさらに図ることができる。

【0271】

本実施形態の半導体装置の製造方法において、配線としての高融点導電層60の側面(露出面)上に、バリア膜62又はセルフパッシベーション膜62が形成される。バリア膜62やセルフパッシベーション膜62が、高融点導電層60と層間絶縁膜との間に形成されることによって、層間絶縁膜の形成時における高融点導電層に対する酸化種や窒化種の拡散を抑制でき、酸化種/窒化種と高融点導電体との化学反応に起因する高融点導電層60の線幅/膜厚の減少を防止できる。また、配線としての高融点金属層の酸化速度及び気化速度を考慮して、高融点金属層に対する加熱処理の条件及び層間絶縁膜の形成条件を、設定することによって、配線の酸化や昇華に起因する配線の寸法の縮小を、抑制できる。この結果として、配線としての高融点導電層60の抵抗値の上昇を抑制できる。

【0272】

高融点導電層60に対する還元処理、バリア膜62及びセルフパッシベーション膜62の形成工程は、高融点導電層60が含む結晶の大粒径化のためのアニール処理と共通に実行できる。それゆえ、半導体装置の製造工程を増加させずに、高融点金属層60を含む配線の抵抗値の上昇を防止でき、配線を低抵抗化できる。

【0273】

以上のように、本実施形態の半導体装置の製造方法によれば、低抵抗化された配線を含む半導体装置を提供できる。

【0274】

<製造方法2>

図26乃至図30を用いて、本実施形態の半導体装置の製造方法2について、説明する。本製造方法2において、上述の製造方法1と共通の構成要素、工程及び効果に関する説明は、必要に応じて行う。図26乃至図30は、本実施形態の半導体装置の製造方法2における各工程の断面工程図を模式的に示している。

【0275】

本実施形態の半導体装置の製造方法2は、例えば、クロスポイント型メモリの製造方法に適用できる。本実施形態の半導体装置の製造方法において、高融点導電体からなる配線は、基板(例えば、層間絶縁膜)内に形成された溝の段差(ステップ)を利用して微細な配線パターンが形成される側壁配線形成技術を用いて、形成される。

【0276】

図26に示されるように、絶縁膜(層間絶縁膜)79Aが、例えば、CVD法によって、素子が形成された半導体基板10上に堆積される。そして、堆積された絶縁膜29Aの上面が、CMP法によって平坦化される。絶縁膜79Aは、フォトリソグラフィ技術及びRIE法によって加工され、配線(例えば、ワード線)を形成するための溝(凹部)92が、絶縁膜79A内に形成される。溝92は、例えば、メモリセルアレイのロウ方向に潜在する。

【0277】

図27に示されるように、配線材60Zが、PVD法又はCVD法を用いて、溝内に埋め込まれる。配線材60Zは、上述のように、高融点導電体であって、例えば、Moが配線材60Zとして堆積される。シリサイドが、配線材60Zとして堆積されてもよい。さらに、配線材60Z内に、セルフパッシベーション膜を形成するための金属(例えば、Al、Zr)が添加されてもよい。配線材60Zは、高融点導電体の単層構造でもよいし、ポリメタル構造でもよいし、ポリサイド構造でもよい。

【0278】

また、配線材60Zと絶縁膜79Aとの間に、密着層(バリアメタル膜)67が、堆積されてもよい。例えば、配線材60ZがMoから構成される場合、MoN又はTiNが、密着層67として、堆積される。

【0279】

図28に示されるように、配線材が絶縁膜79Aに形成された溝の側面上にのみ残存するように、配線材が、例えば、RIE法やIBE(Ion Beam Etching)法によってエッチバックされる。これによって、溝の側面上に、高融点導電体からなる配線(例えば、ワード線)60Bが形成される。このように段差を利用して形成された配線60Bは、例えば、リソグラフィの解像度限界より小さい寸法(配線幅)を有する。

【0280】

高融点導電体を含む配線材の堆積時に、基板加熱処理を実行してもよいし、高融点導電体の堆積後において、高融点導電体に対して還元雰囲気中のアニール処理を実行してもよい。これによって、高融点導電体が含む結晶粒は大粒径化し、高融点導電体からなる配線を低抵抗化できる。

【0281】

高融点導電体が所定の配線パターンに加工された後、高融点導電層60Bに対して酸化雰囲気又は窒化雰囲気における加熱処理を施して、高融点導電体60Bの酸化物又は窒化物からなるバリア膜を形成してもよい。また、高融点導電層60Bに添加された金属のセルフパッシベーション膜を形成してもよい。これによって、後の工程における層間絶縁膜の形成時において、酸化種や窒化種に起因する高融点導電層60Bの抵抗値の増大を、防止できる。

【0282】

図29に示されるように、層間絶縁膜79A内の溝が絶縁体で満たされ、形成された配線60B間に層間絶縁膜79Bが埋め込まれる。配線60Bを覆う層間絶縁膜79Bは、少なくともその形成工程の初期段階において、配線としての高融点導電層がほとんど酸化(又は窒化)しない条件、例えば、400℃以下の成膜温度で、形成されることが好ましい。

【0283】

この後、高融点導電体からなる配線60Bの上面が露出され、メモリ素子(可変抵抗素子又は相変化素子)を含むセルユニットCUが、配線60B上に形成される。セルユニットCUは、例えば、側壁転写技術によって、加工される。

【0284】

そして、セルユニットCUを覆うように絶縁膜79Cが形成される。そして、図26乃至図29に示される各工程と実質的に同様に、その絶縁膜内に、カラム方向に延在する溝が形成され、セルユニットCU上の配線(例えば、ビット線)が、その溝の側面上に、側壁配線形成技術によって、形成される。

【0285】

尚、高融点導電体を堆積する工程において、選択CVD法やバイアスPVD法を用いて、配線としての高融点導電体を、絶縁膜79A内の溝の側面上にのみ、選択的に形成してもよい。

【0286】

例えば、図30に示されるように、配線材としての高融点導電体が選択CVD法によって堆積される場合、高融点導電体の形成の選択性が発現する下地層95が、溝92の側面上に沿って、絶縁膜79A上にあらかじめ形成される。ここで、配線が形成されない部分から、下地層95は除去され、層間絶縁膜79Aが露出する。これによって、配線としての高融点導電体が、溝の側面上の下地層95上に、選択的に形成される。

【0287】

尚、絶縁膜79A内に形成された溝92側面に沿って、高融点導電層が成長しやすい下地層95が形成され、露出した絶縁膜79Aの上面及び溝の底面には、高融点導電層が成長しにくい層が形成されてもよい。また、高融点導電体の成長に関して大きい選択性が確保されるように、下地層95の材料及び絶縁膜79Aの材料が選択されることが好ましい。

【0288】

下地(下地層及び層間絶縁膜)と高融点導電層との間に十分な選択性が確保されていれば、高融点導電体を加工するための工程は必要なく、半導体装置を形成するための製造工程を削減できる。但し、下地層95が形成されていても、高融点導電体の成長の選択性が崩れる場合もあるため、半導体装置の信頼性及び歩留まりの低下を防止するために、製造工程中に導電体を加工する工程が設けられてもよい。

【0289】

配線材としての高融点導電体がバイアスPVD法によって形成される場合、溝92の底部と絶縁膜79Aの上部に、導電体の残渣が生じる場合がある。そのため、バイアスPVD法によって、高融点導電体が堆積される場合、導電体の残渣を除去するための工程が設けられる。但し、高融点導電層が絶縁膜79A上の全体にコンフォーマルに形成されるプロセスでは、導電層に対する加工を十分に行う必要がある。それに対して、バイアスPVDを用いて高融点導電層を形成することによって、製造プロセス中における高融点導電層(配線材)に対する加工の負担を削減できる。

【0290】

以上のように、本実施形態の半導体装置の製造方法2において、絶縁膜(層間絶縁膜)内に形成された溝の側面上に、高融点導電体を含む配線が形成される。本製造方法2にように、部材(層間絶縁膜又は基板)に形成された段差(溝、ステップ)を利用して、高融点導電層61を溝の側面上に選択的(自己整合的)に残存させて、配線61を形成することによって、露光による解像度の限界以下の微細な配線を形成できる。また、配線をパターニングする工程を、削減できる。

【0291】

上述の製造方法1と同様に、本実施形態の製造方法2においても、配線に高融点導電体を用いることができ、高融点導電体の大粒径化及び高融点導電体に対する反応種の拡散を抑制することによって、配線の低抵抗化を図ることができる。

【0292】

したがって、本実施形態の半導体装置の製造方法2によれば、低抵抗化された配線を含む半導体装置を提供できるとともに、半導体装置の製造工程を簡略化できる。

【0293】

尚、本実施形態の半導体装置の製造方法2に関して、クロスポイント型メモリセルアレイを有する抵抗変化型メモリの製造方法について例示したが、他の半導体メモリや半導体集積回路の製造方法に、本製造方法2で述べた段差を利用した微細な配線パターンの形成方法が適用できる。

【0294】

[その他]

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0295】

60,60A,60B:配線(高融点導電層)、62:バリア膜(パッシベーション膜)、67:バリアメタル膜(密着層)、68:キャップ層、69,70,71,72,78,79A,79B,79C:層間絶縁膜

【技術分野】

【0001】

本発明の実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体装置の配線において、銅(Cu)が、配線及びビアを形成するための低抵抗配線材料として、主に用いられている。

【0003】

最先端の半導体装置に用いられる配線構造において、配線及びビアの微細化が進んでいる。微細化の結果として、電子の界面非弾性散乱による抵抗率の上昇や、電流密度の増加、ストレスマイグレーション又はエレクトロマイグレーションによる信頼性の劣化が、配線構造の問題として、顕在化している。

【0004】

さらに、微細化が進むにつれて、上記の問題に加え、Cuのように長い平均自由工程を有する低抵抗配線材料は、電気抵抗のサイズ依存性が微細化によって顕著になる。

【0005】

また、Cuを用いた配線は、ダマシン構造を有するため、配線材としてのCuに加えて、バリアメタル膜が、配線材が埋め込まれる配線溝(ダマシン溝)内に形成される。そのため、形成された配線溝の寸法に対して、配線の電気伝導に寄与する実効的な配線の断面寸法(断面積)は、減少する。

【0006】

また、DRAM、フラッシュメモリ、或いは、クロスポイント構造のメモリにおいて、それらの製造プロセスの観点から、トランジスタのゲート電極及び配線は、高融点かつ低抵抗の材料が用いられることが好ましい場合がある。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2005−236330号公報

【特許文献2】特開2009−267296号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

配線の低抵抗化を図る技術を提案する。

【課題を解決するための手段】

【0009】

本実施形態の半導体装置は、素子が形成された半導体基板を覆う第1の層間絶縁膜上に設けられた配線と、前記配線の上面上に設けられるキャップ層と、前記配線と前記配線を覆う第2の層間絶縁膜との間に設けられるバリア膜と、を具備し、前記配線は、高融点導電層を含み、前記配線の配線幅は、前記キャップ層の幅よりも小さく、前記バリア膜は、前記高融点導電層が含む元素の化合物から構成され、前記第2の層間絶縁膜に起因する不純物が前記配線内に拡散するのを抑制する。

【図面の簡単な説明】

【0010】

【図1】本実施形態の半導体装置の構成を説明するための図。

【図2】本実施形態の半導体装置の形成条件を説明するための図。

【図3】本実施形態の半導体装置の形成条件を説明するための図。

【図4】本実施形態の半導体装置の形成条件を説明するための図。

【図5】本実施形態の半導体装置の形成条件を説明するための図。

【図6】本実施形態の半導体装置の形成条件を説明するための図。

【図7】本実施形態の半導体装置の形成条件を説明するための図。

【図8】本実施形態の半導体装置の形成条件を説明するための図。

【図9】本実施形態の半導体装置の形成条件を説明するための図。

【図10】本実施形態の半導体装置の形成条件を説明するための図。

【図11】本実施形態の半導体装置の形成条件を説明するための図。

【図12】本実施形態の半導体装置の形成条件を説明するための図。

【図13】本実施形態の半導体装置の形成条件を説明するための図。

【図14】本実施形態の半導体装置の変形例を示す図。

【図15】本実施形態の半導体装置の変形例を示す図。

【図16】本実施形態の半導体装置の変形例を示す図。

【図17】本実施形態の半導体装置の応用例を示す図。

【図18】本実施形態の半導体装置の応用例を示す図。

【図19】本実施形態の半導体装置の応用例を示す図。

【図20】本実施形態の半導体装置の応用例を示す図。

【図21】本実施形態の半導体装置の製造方法1の一工程を示す断面工程図。

【図22】本実施形態の半導体装置の製造方法1の一工程を示す断面工程図。

【図23】本実施形態の半導体装置の製造方法1の一工程を示す断面工程図。

【図24】本実施形態の半導体装置の製造方法1の一工程を示す断面工程図。

【図25】本実施形態の半導体装置の製造方法1の一工程を示す断面工程図。

【図26】本実施形態の半導体装置の製造方法2の一工程を示す断面工程図。

【図27】本実施形態の半導体装置の製造方法2の一工程を示す断面工程図。

【図28】本実施形態の半導体装置の製造方法2の一工程を示す断面工程図。

【図29】本実施形態の半導体装置の製造方法2の一工程を示す断面工程図。

【図30】本実施形態の半導体装置の製造方法2の一工程を示す断面工程図。

【発明を実施するための形態】

【0011】

[実施形態]

以下、図1乃至図30を参照しながら、本実施形態について詳細に説明する。以下の説明において、同一の機能及び構成を有する要素については、同一符号を付し、重複する説明は必要に応じて行う。

【0012】

(1) 構成

図1を参照して、本実施形態の半導体装置の構成について、説明する。図1は、本実施形態の半導装置の構成を模式的に示す断面図である。

【0013】

半導体装置及び半導体装置が含む回路を形成する素子Trが、半導体基板10上に、設けられている。

【0014】

図1において、電界効果トランジスタTrが、半導体装置を形成する素子Trとして、図示されている。電界効果トランジスタは、例えば、MOSトランジスタである。

【0015】

トランジスタTrは、半導体基板10内の素子形成領域(アクティブ領域)29内に、設けられている。素子形成領域は、素子分離領域によって、定義されている。素子形成領域29内には、p型又はn型のウェル領域が設けられている。素子分離領域内に形成されたトレンチ内には、STI(Shallow Trench Isolation)構造の絶縁膜19が、埋め込まれている。

【0016】

トランジスタTrのゲート電極21は、ゲート絶縁膜22を介して、素子形成領域29の表面上に設けられている。素子形成領域29内には、トランジスタTrのソース/ドレインとしての2つの拡散層23が設けられている。素子形成領域29内における2つの拡散層23間の領域が、トランジスタTrのチャネル領域となる。ゲート電極21に所定の電圧が印加されることによって、チャネル領域の表層部(ゲート絶縁膜22の下方)に、チャネル(反転層)が形成される。

【0017】

尚、半導体装置が、抵抗素子、容量素子又はメモリ素子など、電界効果トランジスタ以外の素子を含んでいるのは、もちろんである。

【0018】

第1の層間絶縁膜70が、トランジスタTrを覆うように、半導体基板10上に設けられている。コンタクトプラグ51が、拡散層23に接続されるように、層間絶縁膜70内に形成されたコンタクトホール内に埋め込まれている。尚、ゲート電極21に接続されるコンタクトプラグも、層間絶縁膜70内に形成されている。

【0019】

第1の配線50が、コンタクトプラグ51に接続されるように、層間絶縁膜70上に設けられている。第1の配線50は、半導体基板10の表面からの高さ(半導体基板10の表面に対して垂直方向の位置)を基準として、第1の配線レベル内に設けられている。

【0020】

第2の層間絶縁膜71が、配線50上及び第1の層間絶縁膜70上に設けられている。ビアプラグ52が、第2の層間絶縁膜71内に形成されたコンタクトホール(ビアホール)内に、設けられている。

【0021】

第2の配線60が、ビアプラグ52に接続されるように、第2の層間絶縁膜71上に設けられている。第2の配線60は、第2の配線レベルに設けられている。

第3の層間絶縁膜72が、配線60及び層間絶縁膜71上に、設けられている。

【0022】

ここで、第2の配線60を用いて、本実施形態の半導体装置に用いられる配線の構造について、より具体的に説明する。

【0023】

本実施形態の半導体装置において、配線60は、高融点導電体を含む導電層を用いて、形成される。本実施形態における高融点導電体とは、融解温度(融点)TMが、1000℃以上、より好ましくは、1100℃より高い金属又は金属化合物のことである。高融点導電体は、AlやCuに比較して、配線の微細化の影響を受けにくい。

【0024】

密着層67は、配線60と層間絶縁膜71との間、及び、配線60とビアプラグ52との間に、設けられている。密着層67は、配線60と他の部材との密着性を確保するために設けられ、密着層67は、配線60が層間絶縁膜71及びプラグ52から剥離するのを防止する。また、密着層67は、例えば、バリアメタルとしての機能を有し、配線60と層間絶縁膜71との間に生じる不純物の拡散、及び、配線60とプラグ52との間に生じる不純物の拡散を、防止する。

例えば、密着層67には、窒化チタン(TiN)が用いられる。但し、密着層67の材料は、配線60の材料に応じて、適宜変更されてもよい。例えば、配線がMoによって形成される場合には、窒化モリブデン(MoN)が、密着層67として用いられる。

【0025】

例えば、配線60の上部(上面)上には、絶縁膜68が設けられている。絶縁膜68は、配線60を加工するためのマスクの一部として用いられる。以下では、絶縁膜68のことを、キャップ層とよぶ。配線60と上層の配線レベルの配線とを接続されるビアプラグの形成位置において、キャップ層68は、配線60の上面から除去されている。尚、キャップ層68は、配線60上に残存させなくともよく、キャップ層68は、配線60が加工された後に、除去されてもよい。

【0026】

パッシベーション膜(スペーサ膜ともよばれる)としての絶縁膜69は、メタル層61を覆っている。以下では、キャップ層68及びパッシベーション膜69のことを、層間絶縁膜として説明する場合がある。

【0027】

拡散防止膜62は、導電層60の外周に沿って、形成されている。図1に示される配線の構造において、拡散防止膜62は、導電層60の側部(側面)上に設けられている。図1において、拡散防止膜62は、導電層60とパッシベーション膜69との間に介在している。拡散防止膜62は、パッシベーション膜69や層間絶縁膜72を形成する際の酸化種又は窒化種が導電層60内に拡散するのを、抑制する。以下では、導電層60に対する不純物の拡散を抑制する膜62のことを、バリア膜62とよぶ。

バリア膜62は、導電層60を形成する材料(配線材)の酸化物又は窒化物である。例えば、配線60がMoを用いて形成された場合、バリア膜62は、二酸化モリブデン(MoO2)を含む。尚、バリア膜62は、酸窒化膜又は炭化膜でもよい。

【0028】

例えば、バリア膜62が、導電層60に対する酸化処理または窒化処理によって導電層60の側面上に形成された場合、導電層60の幅W1は、キャップ層68の幅W2よりも小さくなっている。

【0029】

例えば、配線としての高融点導電層60の配線幅W1は、半導体装置の配線パターン及び配線レベルに応じて、30nm以上、500nm以下の範囲で設定される。尚、配線60の配線幅W1は、500nmより大きい値に設定される場合もある。また、配線60の配線幅W1は、側壁転写技術などの微細加工技術を用いて、露光による解像度の限界より小さい寸法(例えば、20nm以下)に設定される場合もある。

【0030】

本実施形態の半導体装置において、配線60は、高融点導電体を含む導電層から構成される。本実施形態において、配線60を形成するための高融点導電体の具体例については、後述する。

【0031】

そして、後述の条件で、高融点導電体を含む配線(高融点導電層)60が形成されることによって、配線60が含む高融点導電体の結晶粒のサイズが大きくなる。この結果として、所定の面積(或いは単位体積)内における結晶粒界が減少し、高融点導電層60内における結晶粒界に起因する電子の散乱が減少する。それゆえ、高融点導電体を含む配線60の抵抗値は、減少する。

【0032】

高融点導電体が配線60に用いられる場合、高融点導電層が、エッチングによって所定のパターンに加工される。配線60の加工後に、配線60としての高融点導電層の側面が露出し、高融点導電層の露出した面が、層間絶縁膜(又はパッシベーション膜)の形成するための酸化雰囲気又は窒化雰囲気にさらされる。それゆえ、層間絶縁膜が、高融点導電層上に、直接形成された場合、層間絶縁膜の形成に起因した導電体層の過剰な酸化又は窒化に起因して、配線の電気抵抗が上昇することが懸念される。

これに対して、本実施形態の半導体装置の配線構造のように、配線60と層間絶縁膜との間に、バリア膜(拡散防止膜)62が設けられることによって、配線60を形成するための高融点導電層の酸化又は窒化が防止され、層間絶縁膜の形成に起因した配線60の抵抗の上昇が抑制される。

【0033】

また、バリア膜62が高融点導電層60に対する酸化処理又は窒化処理によって形成されることによって、高融点導電層60とバリア膜62とを含む配線構造の配線幅は、ほとんど増大しないため、微細化な配線構造を形成できる。

【0034】

したがって、本実施形態の半導体装置によれば、配線の低抵抗化を図ることができる。

【0035】

(2) 配線の材料及び配線構造の形成条件

図2乃至図13を参照して、本実施形態の半導体装置が含む配線60の材料及び配線構造の形成条件について、説明する。

【0036】

(a) 材料

図1を用いて説明したように、本実施形態の半導体装置において、高融点導電体(高融点導電層)が、配線60を形成するための材料(配線材)として、用いられている。

【0037】

本実施形態において、配線材としての高融点導電体は、モリブデン(Mo)、タングステン(W)、ルテニウム(Ru)、タンタル(Ta)、コバルト(Co)及びニッケル(Ni)を含むグループから選択される少なくとも1つの材料(元素)が、用いられる。これらの金属は、1000℃以上の融解温度TMを有する。これらの金属のことを、以下では、高融点金属とよぶ。尚、配線材としての高融点金属は、1000℃以上、より好ましくは1100℃より高い融解温度を有していれば、上記の金属に限定されない。また、1000℃以上の融解温度であれば、上記の高融点金属を含む合金でもよい。

【0038】

配線60を構成する高融点導電体は、1000℃以上の融解温度であれば、例えば、金属化合物でもよい。例えば、高融点導電体としての金属化合物(以下では、高融点金属化合物ともよぶ)には、上記の高融点金属の化合物、より具体的な例としては、モリブデンシリサイド(MoSi)、タングステンシリサイド(WSi)、ニッケルシリサイド(NiSi)、コバルトシリサイド(CoSi)などのシリサイドが、用いられてもよい。

【0039】

さらに、配線60としての高融点導電体は、上記の高融点金属及び高融点金属化合物のうち、再結晶化温度TRが1000℃以下の材料が用いられることが好ましい。Wの再結晶化温度は、1200℃以下である。Taの再結晶化温度は1000℃以下であり、Moの再結晶化温度は、900℃以下であり、Ruの再結晶化温度は900℃以下である。それゆえ、本実施形態において、上述の高融点金属のうち、Mo、Ru又はTaが、配線に用いられることがさらに好ましい。

【0040】

再結晶化温度が1000℃以下の高融点金属が、配線60に用いられることよって、比較的低い加熱温度で、高融点導電層から構成される配線60の結晶性の改善(結晶の大粒径化)を図ることができる。

【0041】

また、配線60だけでなく、図1のビアプラグ52に、上記に高融点導電体が用いられてもよい。

【0042】

半導体装置の製造プロセスは、温度条件が1000℃から1100℃程度又はこの温度以下のプロセスを含む。本実施形態のように、融解温度TMが1000℃以上の高融点導電体が、半導体基板10上の素子間を接続する配線60に用いられることによって、CuやAlなどの融解温度TMが比較的低い金属材料に比較して、過大な熱に起因した配線の劣化を抑制できる。

【0043】

また、再結晶化温度TRが1000℃以下の高融点導電体が、配線60に用いられた場合、上記の温度条件における製造プロセスにおいて、配線の結晶性の改善(結晶の大粒径化)を図ることができ、配線を低抵抗化できる。

【0044】

尚、配線を形成するための高融点導電体は、上述の金属及び金属化合物に限定されず、例えば、Tiのように、上述の融解温度及び再結晶化温度の条件を満たす金属又は金属化合物が、本実施形態の半導体装置の配線に用いられてもよい。

【0045】

(b) 形成条件

図2乃至図5を用いて、本実施形態の半導体装置が含む配線の形成条件について、説明する。

図2は、配線としての高融点導電層の堆積時における基板の加熱温度(以下、成膜温度とよぶ)と高融点導電層の電気的特性との関係を示すグラフである。

【0046】

図2において、グラフの横軸は、成膜温度を示している。図2において、グラフの縦軸は、成膜温度に対する配線の抵抗率の減少率(単位:[%])を示している。図2において、Mo又はWから構成される高融点導電層の電気的特性の変化が示されている。Mo層及びW層は、PVD(Physical Vapor Deposition)法によって、それぞれ形成される。

【0047】

図2において、配線の抵抗率の減少率は、基板の加熱無しに、室温(25℃〜30℃)で形成されたMo層又はW層の抵抗率を基準(参照値)として求められている。図2に示される例において、Mo層の成膜時に150℃、300℃、400℃及び500℃の基板加熱処理がそれぞれ施された場合における、Mo層の抵抗率の減少率が示されている。また、図2に示される例において、W層の成膜時に400℃の基板加熱処理が施された場合における、W層の抵抗率の減少率が示されている。

【0048】

図2に示されるように、配線を構成する導電層(ここでは、Mo層又はW層)が加熱された基板上に堆積されることによって、Mo層及びW層の抵抗率は、減少する。

図2に示される例において、W層の抵抗率は、400℃の成膜温度において、室温で形成されたW層に対して、30%程度、減少する。

また、図2に示される例において、150℃の成膜温度で形成されたMo層の抵抗率は、室温で形成されたMo層の抵抗率に比較して、20%程度低下し、成膜温度が高くなるにつれて、Mo層の抵抗率の減少率は大きくなる。500℃の成膜温度で形成されたMo層の抵抗率は、室温で形成されたMo層の抵抗率に比較して、60%から70%程度、減少する。

【0049】

室温の成膜温度で形成されたMo層及びW層の抵抗率は、所定の寸法(配線幅)において、例えば、15μΩ・cmから16μΩ・cm程度の大きさを有する。成膜時における400℃程度の基板加熱処理によって、W層の抵抗率は、11μΩ・cm程度の大きさを示す。

【0050】

成膜時に150℃程度の基板加熱処理が施されることよって、Mo層の抵抗率は、16μΩ・cm程度の大きさを示し、成膜時に500℃程度の基板加熱処理が施されることよって、Mo層の抵抗率は、8μΩ・cm程度の大きさを示す。

【0051】

このように、Mo層及びW層の抵抗率は、Mo層及びW層の成膜温度の上昇とともに、減少する。さらに、成膜時の加熱処理において、Moの再結晶化温度がWの再結晶化温度より低いため、Mo層の抵抗率の減少率は、W層の抵抗率の減少率より大きい。

【0052】

図3は、堆積後の配線に対して加熱処理(以下、ポストアニール処理とよぶ)が施された場合における加熱処理温度と配線(ここでは、Mo層及びW層)の電気的特性との関係を示すグラフである。

図3において、グラフの横軸は、ポストアニール処理の加熱温度を示している。加熱温度は、400℃から800℃程度に設定されている。図3において、グラフの縦軸は、ポストアニール処理を施した導電層の抵抗率の減少率(単位:[%])を示している。ここでは、室温(25℃〜30℃)の成膜温度で導電層が形成され、かつ、ポストアニール処理が施されていない導電層の抵抗率が、基準(参照値)とされている。

【0053】

図3に示される例において、400℃、600℃及び750℃のポストアニール処理が、室温で堆積されたMo層にそれぞれ施された場合における、Mo層の抵抗率の減少率が示されている。また、400℃及び750℃のポストアニール処理が室温で堆積されたW層に対してそれぞれ施された場合における、W層の抵抗率の減少率が示されている。尚、図2に示される例と同様に、Mo層及びW層は、PVD法によって、基板上に堆積されている。

【0054】

図3に示されるように、堆積された層に対してポストアニール処理が施されることによって、Mo層及びW層の抵抗率は、減少する。

W層の抵抗率は、400℃から750℃の範囲内のポストアニール処理によって、ポストアニール処理なしのW層に比較して、4%から10%程度の範囲内で、減少する。例えば、400℃から750℃の範囲においてポストアニール処理されたW層の抵抗率は、11μΩ・cmから12μΩ・cm程度の大きさを示す。

【0055】

Mo層の抵抗率は、400℃のポストアニール処理によって、10%程度減少し、600℃のポストアニール処理によって、15%程度減少する。また、750℃のポストアニール処理が施された場合、Mo層の抵抗率は、ポストアニール処理なしのMo層に比較して、27%程度減少する。例えば、400℃から750℃の範囲においてポストアニール処理されたMo層の抵抗率は、8μΩ・cmから10μΩ・cm程度の大きさを示す。上述のように、Moの再結晶化温度が比較的低いため、Mo層が含む結晶の大粒経化が促進され、Mo層の抵抗率の減少率が、W層の抵抗率の減少率よりも大きくなる。

【0056】

このように、成膜後のポストアニール処理によっても、成膜時の基板加熱と同様に、高融点導電層の抵抗率を低減できる。

【0057】

図4及び図5を用いて、PVD法を用いた場合における高融点導電層から構成される配線の成膜条件について説明する。図4及び図5において、スパッタ法が高融点導電層の成膜に用いられた場合の条件が示されている。

図4は、高融点導電層の堆積時における封入ガスのガス圧と高融点導電層の抵抗率との関係を示すグラフである。図4において、グラフの横軸は、スパッタガスのガス圧が示されている。図4において、グラフの縦軸は、各ガス圧で形成された導電層(ここでは、W層)の抵抗率が示されている。図4では、アルゴン(Ar)が、スパッタガスに用いられている。図4に示されるArガスのガス圧は、0.08Paから0.8Pa程度の範囲内にそれぞれに設定されている。また、図4では、放電電圧を変化させて、ガス圧に対する配線の抵抗率の変化が、測定されている。尚、図4において、3つの放電電圧A,B,Cのうち、放電電圧Cが最も大きく、放電電圧Aが最も小さく、放電電圧Bが、放電電圧Aと放電電圧Cとの間の大きさに設定されている。

【0058】

図5は、高融点導電層の堆積時における放電電圧と高融点導電層の抵抗率との関係を示すグラフである。図5において、グラフの横軸は、高融点導電層(ここでは、W層)の成膜のための放電電圧を示している。図5において、グラフの縦軸は、高融点導電層の抵抗率を示している。図5において、放電電圧は、250Wから600Wの範囲内にそれぞれ設定されて、導電層が堆積されている。図5において、スパッタガスとしてのArガスのガス圧が、0.08Pa、0.2Pa、0.6Pa及び0.8Paにそれぞれ設定された場合における放電電圧に対する高融点導電層の抵抗率の変化が示されている。

【0059】

図4に示されるように、各放電電圧で形成された高融点導電層において、スパッタ時におけるArのガス圧が低くなると、その導電層の抵抗率は低減する。このように、成膜時のスパッタガス圧が低くなると導電層の抵抗率が減少するのは、導電層内に取り込まれるガス成分が減少するためである。また、ガス圧が低減されることによって、スパッタリングのための放電電圧を高くできる。それゆえ、配線としての高融点導電層がスパッタ法によって堆積される場合、成膜時のチャンバ内のガス圧が小さくされることが、配線の抵抗率の低減に有効である。

【0060】

図5に示されるように、スパッタリングのための放電電圧が300Vより小さい場合、高融点導電層の抵抗率に対する放電電圧の依存性が大きくなる。これに対して、放電電圧が300V以上である場合、導電層の抵抗率の変化は、飽和した傾向を示す。また、導電層が300V以上の放電電圧を用いて堆積されることによって、300Vより小さい放電電圧で形成された導電層に比較して、配線の抵抗率を低減できる。

それゆえ、配線としての高融点導電層がスパッタ法によって堆積される場合、放電電圧が300V以上に設定されることが、その配線の抵抗率の低減に有効である。

【0061】

尚、図4及び図5において、W層が配線を形成するための導電層として例示されているが、Moや他の高融点金属がスパッタ法によって堆積される場合においても、実質的に同じ傾向を示す。

【0062】

図4及び図5に示されるように、スパッタ法によって配線を形成するための高融点導電層が堆積される場合、スパッタガスの圧力及びスパッタリングのための放電電圧を考慮することが、配線の低抵抗化のために好ましい。

【0063】

また、上記の形成条件及び形成工程に加えて、加工後の高融点導電層に対して、自然酸化膜を除去するための還元処理が施されることが好ましい。これによって、配線幅の減少を防止でき、配線の低抵抗化を図ることができる。還元処理は、高融点導電層に対するポストアニール処理と共通化できる。

【0064】

以上のように、本実施形態の半導体装置は、高融点導電体から構成される配線60を有している。

【0065】

図2及び図3に示されるように、高融点導電体を用いて形成される配線(ここでは、Mo層及びW層)60は、成膜時の基板加熱処理又は成膜後のポストアニール処理のように、高融点導電層60に熱を与えることによって、高融点導電層60の抵抗率が低減する。

【0066】

導電層に対する加熱処理によって、高融点導電層の結晶粒は、与えられた熱によって結晶成長し、結晶粒のサイズ(粒経)が大きくなり、高融点導電層内の粒界が減少する。その結果として、微細な配線内において、配線の表面や結晶粒界で生じる電子の散乱が減少し、高融点導電層の抵抗率(抵抗値)が低減する。

【0067】

また、加熱によるMo層の抵抗率の減少率は、W層の抵抗率の減少率よりも、大きい。これは、Moの再結晶化温度(1000℃程度)が、Wの再結晶化温度(1200℃程度)より低いため、Moの結晶核の生成及び結晶成長がWよりも促進されやすく、MoがWよりも大粒径化しやすいためである。それゆえ、配線に用いられる高融点導電体は、再結晶化温度が、1000℃以下であることが好ましい。

【0068】

このように、高融点導電層の成膜時又は成膜後に熱を与えることによって、高融点導電体から構成される配線が含む結晶粒を大きくでき、配線を低抵抗化できる。

【0069】

また、上述のように、高融点導電体から構成される配線が、スパッタ法を用いて形成される場合、ガス圧や放電電圧などの条件を適正な値に設定することで、配線の電気抵抗を低減できる。

【0070】

尚、図2乃至図5において、Mo又はWが配線を形成するための高融点導電体として用いられた場合について述べたが、RuやTaの高融点金属またはシリサイドが用いられた場合においても、上述の製造プロセス及び形成条件が適用可能な範囲において、実質的に同じ効果が得られる。

【0071】

以上のように、本実施形態の半導体装置によれば、配線を低抵抗化できる。

【0072】

(c) 層間絶縁膜の形成条件

図6及び図7を用いて、本実施形態の半導体装置における層間絶縁膜の形成条件について、説明する。

【0073】

層間絶縁膜が形成されるとき、加工された配線の露出面は、層間絶縁膜を形成するための原料ガス、ガス雰囲気及び温度条件にさらされる。そのため、層間絶縁膜の形成条件下において、配線の露出面の酸化又は窒化などの化学反応が生じ、配線の表面に絶縁膜が形成される場合がある。配線が過剰に酸化又は窒化されると、導電性に寄与する配線の配線幅は縮小し、配線の抵抗値の上昇が顕著になる。層間絶縁膜の形成に起因する配線抵抗の上昇を抑制するために、配線が酸化又は窒化しにくい条件下で、層間絶縁膜が形成されることが好ましい。

【0074】

図6は、高融点導電体の酸化速度を説明するための2次元マップである。図6の(a)は、Moの酸化速度(酸化レート)を示している。図6の(b)は、Wの酸化速度を示している。図6の(a)及び(b)において、グラフの横軸は酸素(O2)ガス圧(単位:[Pa])を示し、グラフの縦軸は加熱温度(単位:[℃])を示している。Mo及びWの酸化速度は、Mo酸化膜又はW酸化膜の形成速度に実質的に相当する。

【0075】

図7は、高融点導電体の酸化速度と加熱温度(アニール温度)との関係を示すグラフである。図7の(a)は、O2ガス圧が60Paに設定された場合におけるMo及びWの酸化速度と加熱温度との関係を示している。図7の(b)は、O2ガス圧が300Paに設定された場合におけるMo及びWの酸化速度と加熱温度との関係を示している。図7の(a)及び(b)において、グラフの横軸は加熱温度を示し、グラフの縦軸は酸化速度を示している。

【0076】

図6及び図7に示されるように、Mo層及びW層に関して、酸化雰囲気下における加熱温度が高くなると、酸化速度の増大が顕著になる。また、図6及び図7に示されるように、Mo層及びW層に関して、酸化処理に用いるO2ガス圧が高くなると、Mo層及びW層の酸化が促進される傾向を示している。そして、図6及び図7に示されるように、Wは、Moに比較して、酸化されやすい。

【0077】

図6の(a)及び図7の(a)に示されるように、60PaのO2ガス圧中において600℃の加熱処理が、Mo層に対して施された場合、0.15nm/sec以上の酸化速度を示す。その酸化速度に応じてMo層の表面(露出面)に、Mo酸化膜が形成される。また、図6の(a)及び図7の(b)に示されるように、300PaのO2ガス圧中において600℃の加熱処理が、Mo層に対して施された場合において、0.15nm/sec以上の酸化速度を示し、その速度に応じてMo酸化膜が形成される。

【0078】

この一方、図6の(a)及び図7の(a)及び(b)に示されるように、Mo層に対して450℃程度の加熱処理が施された場合、O2ガス圧が60Paから300Paの範囲内において、0.01〜0.03nm/sec程度の酸化速度を示す。

さらに、Mo層に対して400℃程度の加熱処理が施された場合、O2のガス圧にほとんど依存せずに、Moの酸化速度はほぼ0nm/sec程度となり、Mo層の表面上に、Mo酸化膜はほとんど形成されなくなる。

【0079】

図6の(b)及び図7の(a)に示されるように、60PaのO2ガス圧中において450℃以上の加熱処理が、W層に対して施された場合、0.10nm/sec以上の酸化速度を示し、その酸化速度に応じて、W層の表面(露出面)に、W酸化膜が形成される。これと同様に、図6の(a)及び図7の(b)に示されるように、W層が形成された基板に対して300PaのO2ガス圧中においても450℃以上の加熱処理が施された場合において、0.10nm/sec以上の酸化速度で、W酸化膜が形成される。そして、400℃程度の加熱処理が、W層が形成された基板に対して施された場合において、0.05nm/sec以下になる。加熱処理の温度が320℃以下で、Wの酸化速度は、実質的に0nm/sec程度になる。このように、図6及び図7に示される条件において、Wは、Moに比較して、酸化され易い傾向を示す。

【0080】

配線の線幅が酸化によって縮小すると、配線の抵抗値は増大する。そのため、層間絶縁膜の形成時における酸化雰囲気によって、配線が酸化されないことが好ましい。それゆえ、例えば、配線としての高融点導電層が、Mo層である場合、層間絶縁膜を形成するための温度は、400℃以下であることが好ましい。Mo層を覆う層間絶縁膜を形成するためのO2ガス圧(全圧又は分圧)は、60Pa以下であることが好ましい。また、配線としての高融点導電層が、W層である場合、層間絶縁膜を形成するための温度は、330℃以下であることが好ましい。W層を覆う層間絶縁膜を形成するためのO2ガス圧(全圧又は分圧)は、60Pa以下であることが好ましい。

【0081】

尚、ここでは、層間絶縁膜が酸化雰囲気中で形成される場合について述べたが、例えば、層間絶縁膜(キャップ層又はパッシベーション膜)が窒化雰囲気中で形成される場合においても、高融点導電体の窒化速度を考慮して、層間絶縁膜の形成温度(基板の加熱温度)及びN2ガス圧が適宜設定されることが好ましい。

【0082】

但し、層間絶縁膜の形成温度は、少なくとも層間絶縁膜の形成の初期段階において、例えば、層間絶縁膜の形成が開始されてから層間絶縁膜が高融点導電層(例えば、Mo層)から構成される配線を覆うまでの期間において、400℃以下であればよい。それゆえ、層間絶縁膜の形成工程を2段階に分け、400℃以下の温度条件下において薄い層間絶縁膜が配線上に形成された後、400℃より高い温度条件下において厚い層間絶縁膜が配線上に形成されてもよい。これによって、製造期間の長期化を回避して、配線の低抵抗化ができる。

【0083】

ここでは、Mo及びWが配線としての高融点導電層に用いられる場合について述べた。但し、高融点導電層が、Ru、Ta、又は、シリサイドなどから形成される場合においても、それらの導電層の酸化及び窒化反応、より具体的には、それらの導電層の酸化速度又は窒化速度を考慮して、層間絶縁膜の形成温度やガス圧が、それらの酸化又は窒化を抑制する条件に適宜設定すればよい。これによって、Mo及びW以外の高融点導電体を用いて配線が形成される場合であっても、層間絶縁膜の形成に起因した配線の抵抗値の上昇を抑制できる。

【0084】

尚、層間絶縁膜は、SiN、SiO2、SiOC又はSiCNなどが、配線間に生じる容量の設計に応じて、適宜選択される。層間絶縁膜が窒素又は炭素を含む場合、高融点導電層層の窒化速度又は炭化速度を考慮して、高融点導電層の窒化又は炭化が抑制される条件の層間絶縁膜の形成温度やガス圧が適宜設定すればよい。

【0085】

以上のように、層間絶縁膜を形成するためのガスと高融点導電層との反応速度を考慮して、層間絶縁膜の形成条件を設定することによって、配線としての高融点導電層の抵抗値の増加を抑制でき、配線の低抵抗化に貢献できる。

【0086】

(d) バリア膜及びその形成条件

図8乃至図13を参照して、配線としての高融点導電層上に設けられるバリア膜及びその形成条件について、説明する。

【0087】

図1に示されるように、半導体装置において、配線(高融点導電層)60が形成された後、窒化膜や酸化膜を含む層間絶縁膜68,69,71が、配線60を覆うように形成される。上述のように、層間絶縁膜68,69,71の形成時における酸化雰囲気中や窒化雰囲気中に、加工された配線60の露出面がさらされ、配線60の露出部分が酸化又は窒化される場合がある。図1に示されるように、配線としての高融点導電体層60の側面上に、バリア膜(拡散防止膜)62が設けられることによって、層間絶縁膜の形成時における配線に対する酸化種及び窒化種の拡散を抑制できる。バリア膜62は、例えば、酸化膜、窒化膜又は酸窒化膜から構成される。

【0088】

図8は、バリア膜を形成するための処理時間と高融点導電層の抵抗値の変化との関係を示すグラフである。図8のグラフの横軸は、バリア膜の形成時間(単位:[sec])を示している。図8のグラフの縦軸は、メタル層のシート抵抗(単位:[Ω/□])を示している。バリア膜は、高融点導電層の露出面に対する化学処理(ここでは、酸化処理)によって形成される。酸化処理によってバリア膜が形成される場合、バリア膜の形成時間と形成されるバリア膜の膜厚との間に相関関係が生じる。バリア膜の形成時間が長くなると、バリア膜の膜厚が厚くなる。

【0089】

尚、図8に示される例では、10sec、60sec、120secの処理時間でバリア膜が高融点導電層に形成される場合、及び、高融点導電層にバリア膜が形成されない場合(すなわち、バリア膜の形成時間がゼロ)における、高融点導電層のシート抵抗の変化が、それぞれ示されている。

図8の各サンプルにおいて、各形成時間によってバリア膜が形成された後に、高融点導電層上に、5nm程度の膜厚を有するシリコン窒化膜が形成される。図8において、高融点導電層には、50nm程度の膜厚を有するMo層が用いられている。

【0090】

図8に示されるように、バリア膜が形成された高融点導電層(Mo層)のシート抵抗は、バリア膜が形成されない高融点導電層のシート抵抗に比較して、低減する。これは、バリア膜が、シリコン窒化膜が形成される際の窒化種が高融点導電層に拡散するのを抑制するためである。それゆえ、高融点導電層と層間絶縁膜との間にバリア膜が設けられることによって、高融点導電層内に対する窒素(N)の拡散に起因した高融点導電層の抵抗値の上昇が、抑制される。

【0091】

このように、バリア膜62が、配線としての高融点導電層60の外周(例えば、側面)を覆うように、高融点導電層60と層間絶縁膜との間に形成されることによって、層間絶縁膜に起因する不純物が高融点導電層60内に拡散するのを防止でき、高融点導電層60の電気的特性の劣化を防止できる。

【0092】

例えば、Moのように、窒素の拡散により劣化しやすい高融点導電体が配線に用いられる場合、本実施形態のように、酸化膜からなるバリア膜が高融点導電層(配線)上に形成されることによって、キャップ層(ハードマスク)やパッシベーション膜に起因する窒素がMo層内に拡散するのを抑制することは、有効である。尚、酸素により劣化しやすい高融点導電体が配線に用いられる場合、窒化膜からなるバリア膜が、導電層と酸化膜からなる層間絶縁膜との間に設けられることが好ましい。

【0093】

バリア膜62が、高融点導電層60に対する酸化処理によって形成される酸化膜である場合、高融点導電層60とバリア膜(酸化膜)62との界面に、酸素が存在する。そして、高融点導電層60及びバリア膜62を含む配線構造において、その配線構造内の酸素濃度は、高融点導電層60とバリア膜62との界面(バリア膜側)から高融点導電層60の中央部に向かって、低くなる。これと同様に、バリア膜62が高融点導電層60に対する窒化処理によって形成される窒化膜である場合、高融点導電層60とバリア膜(窒化膜)62との界面に、窒素が存在する。高融点導電層60及びバリア膜62を含む配線構造内における窒素濃度は、高融点導電層60とバリア膜62との界面から高融点導電層60の中央部に向かって、低くなる。

【0094】

このように、バリア膜側から高融点導電層の中央部側に向かって、酸素又は窒素が濃度勾配を有することによって、酸素濃度又は窒素濃度の高いバリア膜側では、バリア膜としての機能を向上でき、酸素濃度又は窒素濃度の低い高融点導電層(配線)の中央部では、電気伝導率が向上する。

【0095】

例えば、高融点導電層60とバリア膜62との界面に、酸素又は窒素が存在する場合、高融点導電層(例えば、Mo層)の界面(表面)が、酸素又は窒素によって終端されている。

【0096】

バリア膜62を形成するための酸化処理(又は窒化処理)の時間が長くなると、高融点導電層60が過剰に酸化され、導電層60の配線幅(断面積)が縮小されるため、導電層60の抵抗値が増加する可能性がある。それゆえ、高融点導電層60に対する不純物の拡散の抑制と配線幅の縮小との関係を考慮して、バリア膜を形成するための酸化処理(又は窒化処理)の時間及びバリア膜の膜厚が、配線材の種類や配線の寸法に応じて、適宜設定されることが好ましい。

【0097】

図8に示される例において、Moが配線材に用いられた場合、Mo層の配線幅及び膜厚の縮小に起因する抵抗値の上昇を抑制するために、30secから130secの範囲内の酸化処理が実行されることが好ましい。但し、Moを用いて形成された配線の寸法に応じて、酸化処理の時間を調整してもよいのは、もちろんである。

【0098】

図6、図7及び図9を用いて、バリア膜の形成条件について、より具体的に説明する。ここでは、Mo及びWからなる高融点導電層を例示して、それらの導電層(Mo層及びW層)上に設けられるバリア膜について、説明する。ここでは、バリア膜がMo層及びW層に対する酸化処理によって形成される場合について述べる。

【0099】

上述のように、図6及び図7は、Mo及びWの酸化速度を示す図である。

図9は、高融点導電体の気化速度を説明するためのグラフである。図9の(a)は、酸素雰囲気中におけるMoの気化速度(気化レート)の2次元マップが示されている。図9の(a)において、グラフの横軸はO2ガス圧(単位:[Pa])を示し、グラフの縦軸は加熱温度を示している。図9の(b)は、O2ガス圧が60Paに設定された場合における、Mo及びWの気化速度と加熱温度との関係を一例として示している。図9の(b)において、グラフの横軸は加熱温度を示し、グラフの縦軸は気化速度を示している。

【0100】

バリア膜がMo層又はW層からなる配線の表面上に形成される場合、バリア膜の形成に起因して配線の抵抗値が上昇するのを抑制するために、導電体の過剰酸化、及び、導電体及び導電体の酸化物の気化(昇華)を考慮して、バリア膜の形成条件が設定されることが好ましい。

【0101】

図9の(a)及び(b)に示されるように、例えば、O2のガス圧が60Paに設定された場合、Moの気化速度は、450℃以下のMo層に対する加熱温度において、ほぼ0nm/sec程度になる。図6及び図7を用いて説明したように、O2ガス圧が60Paに設定された酸化雰囲気中において、Moの酸化速度は、加熱温度が400℃から450℃程度の範囲に設定された場合、0.02nm/secから0.03nm/sec程度になる。また、Mo層に対する加熱温度が500℃以上に設定された場合、Moの気化速度は0.04nm/sec以上になり、Moの酸化速度は0.05nm/sec以上になる。

【0102】

図9の(b)に示されるように、Wの気化速度は、O2のガス圧が60Paに設定された場合において、300℃から700℃の加熱温度の範囲内では、ほぼ0nm/secを示している。そして、図9の(b)に示される例に限らず、60Paから300PaのO2ガス圧の範囲、及び、300℃から700℃の範囲内において、Wは、ほぼ0nm/secの気化速度を示し、ほとんど気化(昇華)しない。このように、Wの気化レートは、Moの気化レートに比較して十分小さい。

【0103】

図6、図7及び図9に示されるように、Mo層がO2のガス圧が60Paの酸化雰囲気中において加熱処理された場合、酸化雰囲気中における500℃以上の加熱温度の条件下では、Moは気化する。そして、その条件下において、Mo(Mo酸化物)の気化速度及びMoの酸化速度は大きくなる。それゆえ、500℃以上の加熱温度において、バリア膜の形成時におけるMo層の過剰酸化やMo(又はMo酸化物)の気化に起因して、配線の導電性に寄与するMo層の寸法(断面積)が減少し、配線の抵抗値が大きくなる可能性がある。

【0104】

したがって、酸化処理によってMo層の側面(露出面)上にバリア膜が形成される場合、Moの気化を防ぐために、Mo層の側面が徐々に(ゆっくりと)酸化され、且つ、Mo(及びMo酸化物)がほとんど気化しない加熱温度及びO2ガス圧が設定されることが好ましい。例えば、Mo層上に酸化膜からなるバリア膜が形成される場合、バリア膜を形成するための酸化雰囲気中におけるMo層に対する加熱温度は、500℃より低い加熱温度、より好ましくは、400℃から450℃の温度範囲に設定される。また、導電体の過剰酸化を抑制するために、導電体の酸化速度は遅いほうが好ましい。それゆえ、Mo層に対する加熱温度が400℃から450℃に設定される場合、バリア膜を形成するためのO2のガス圧は、60Pa程度に設定されることが好ましい。

【0105】

また、Wが配線に用いられた場合、Wはほとんど気化しないので、Wが過剰酸化されないように、Wの酸化速度を考慮して、バリア膜を形成するためのO2のガス圧及び加熱温度が適宜設定される。

【0106】

以上のように、高融点導電体の気化速度が、高融点導電体の酸化速度より小さくなる条件で、バリア膜が高融点金属の配線上に形成されることが好ましい。このようなバリア膜の形成条件が設定されることによって、配線を構成する高融点導電体の気化や過剰酸化による配線の線幅及び膜厚の縮小や、バリア膜の昇華を防止できる。

これによって、バリア膜の形成が原因で配線の抵抗値が上昇するのを、防止できる。

【0107】

Moが配線に用いられた場合におけるバリア膜の形成条件例として、例えば、O2ガス圧が60Paに設定され、400℃から450℃の範囲に加熱温度が設定されることによって、Moの気化速度が、Moの酸化速度より小さくなる。

【0108】

上述のバリア膜の形成条件において、配線としてのMo層に対する酸化処理によって、バリア膜が形成される場合、Mo酸化物が、Mo層上に形成される。図10は、酸化処理によって形成されたMo酸化物の組成の一例のXRDプロファイルを示している。図10におけるXRDプロファイルは、2θ−θ法(粉末法)による測定結果が示されており、グラフの横軸は2θ(単位:[°])を示し、グラフの縦軸は回折強度(単位:[a.u])を示している。

【0109】

図10に示されるように、2θ=26°においてMoO2(11−1)の回折ピーク、2θ=37°においてMoO2(111)の回折ピーク、また、2θ=53.4°においてMoO2(211)の回折ピークが検出されている。

このXRDによる解析結果は、二酸化モリブデン(MoO2)の回折ピークを示している。

【0110】

このように、上記の条件によってMo層上に形成されるバリア膜(Mo酸化物)は、主に、MoO2を含んでいる。尚、Mo層上に形成されるMoの自然酸化膜は、例えば、三酸化モリブデン(MoO3)である。

【0111】

例えば、配線の膜厚が50nm程度である場合、バリア膜としてのMoO2膜の膜厚は、1nmから3nm程度の厚さであることが好ましい。MoO2膜の膜厚が、1nmから3nm程度であれば、配線(高融点導電層)に対する反応種(N)の拡散を抑制でき、かつ、バリア膜の形成による配線幅の縮小に起因した配線の抵抗値の上昇を抑制できる。但し、バリア膜の膜厚は、配線の寸法(膜厚又は幅)に応じて、適宜調整されるのはもちろんである。

【0112】

尚、Mo層上のバリア膜(Mo酸化膜)は、MoO2とMoO3とを両方含む膜でもよい。また、バリア膜は、高融点導電体が含む元素以外に、層間絶縁膜を形成するための元素を含んでいてもよい。例えば、バリア膜(例えば、MoO2を含むMo酸化膜)内に、Si、H、N又はCが、含まれる場合もある。配線としての高融点導電層60がMo層である場合、そのMo層上に形成されるバリア膜は、Mo窒化膜(MoN膜)でもよいのは、もちろんである。

【0113】

ここでは、配線材としてMo及びWが用いられた例について説明したが、導電体の酸化速度及び気化速度を考慮することによって、上述のTa、Ru又はシリサイドなど他の高融点導電体に、バリア膜を形成することができるのはもちろんである。

【0114】

尚、バリア膜としての酸化膜又は窒化膜が、酸化処理又は窒化処理によって形成される場合、酸化種又は窒化種が高融点金属層60の内部に拡散するとともに、酸化膜又は窒化膜の形成による体積の膨張が生じる場合がある。そのため、バリア膜が厚い場合、基板表面に対して水平方向において、バリア膜62の側面が、キャップ層68の側面よりも突出する可能性がある。この場合、配線の幅方向における高融点金属層60とバリア膜62とを含む寸法は、キャップ層69の幅W2よりも大きくなり、キャップ層68とバリア膜62との間に、段差が形成される。それゆえ、バリア膜の膜厚は、1〜3nm程度であることが好ましい。

【0115】

<セルフパッシベーションによるバリア膜の形成>

高融点導電層60上のバリア膜62は、金属のセルフパッシベーション(自己不動態化)によって、形成されてもよい。この場合、配線材として高融点導電体に、配線材として選択された高融点金属以外の元素(例えば、金属元素)が添加される。以下では、高融点導電層に添加される元素(金属元素)のことを、添加元素又は添加金属とよぶ。

【0116】

添加金属は、高融点導電体と添加金属との化合物によって、配線の抵抗値を上昇させない材料から選択されて、高融点導電層60内に添加される(ドーピングされる)ことが好ましい。高融点導電層60内における拡散速度が比較的速い金属が、高融点導電層60内に添加されることが好ましい。さらに、配線材に添加される材料(元素)の融点は、配線材(高融点導電体)の融点より低いことが好ましい。

【0117】

添加金属を含む高融点導電層60に対して酸化雰囲気中又は窒化雰囲気中における加熱処理が施されることによって、高融点導電層60内の添加金属が、高融点導電層の側面(露出面)に析出し、その析出した金属の酸化膜又は窒化膜が、高融点導電層の側面に沿って形成される。

【0118】

本実施形態において、金属のセルフパッシベーションによって形成されたバリア膜のことを、セルフパッシベーション膜とよぶ。

【0119】

図11は、金属の酸化物標準生成エネルギー(酸化物生成エネルギーともよばれる)を示す図である。図11の縦軸は各金属の酸化物の生成エネルギーを示し、図11の横軸は生成される酸化物を示している。

【0120】

例えば、配線としての高融点導電層にMo層又はW層が用いられている場合、Mo又はWの酸化物の酸化物標準生成エネルギー以下の金属元素(材料)が、配線材としてのMo層又はW層に添加されていることが、セルフパッシベーション膜を形成するために、好ましい。Mo酸化物(ここでは、MoO3)及びW酸化物(ここでは、WO2)の生成エネルギーは、450kJ/mol程度である。それゆえ、Mo層又はW層に対する酸化処理によって添加金属のセルフパッシベーション膜がバリア膜として形成される場合において、Mo層又はW層内に添加される金属の酸化物標準生成エネルギーは、450kJ/mol以下であることが好ましい。

また、添加された金属の酸化物が、Mo酸化物又はW酸化物に比較して、化学的に安定な材料であることが好ましい。

【0121】

これを鑑みて、Mo又はWを用いた配線60に対して酸化物からなるセルフパッシベーション膜が形成される場合、アルミニウム(Al)やジルコニウム(Zr)が、Mo層やW層に添加されることが好ましい。Alが、Mo又はW層内に形成された場合、酸化アルミニウム(AlxOy)膜が、Mo層又はW層の側面(露出面)上に形成される。また、ZrがMo又はW層内に形成された場合、酸化ジルコニウム(ZrOy)膜が、Mo層又はW層の側面上に形成される。バナジウム(V)やチタン(Ti)が、Mo層又はW層に添加されてもよい。尚、組成式中のx及びyの値(元素の組成比)は、化学量論的組成(ストキオメトリ)を満たすことが好ましいが、形成条件に応じて、組成のずれを含む場合がある。

【0122】

図12は、金属の窒化物標準生成エネルギー(窒化物生成エネルギーともよばれる)を示す図である。図12の縦軸は各金属の窒化物の生成エネルギーを示し、図12の横軸は生成される金属窒化物を示している。

【0123】

添加された金属元素の窒化物によって、セルフパッシベーション膜が形成される場合においても、添加される金属元素の窒化物生成エネルギーが、配線材としての高融点導電体の窒化物生成エネルギー以下であり、形成された窒化物が高融点導電体の窒化物よりも化学的に安定な材料であることが好ましい。Mo窒化物(ここでは、Mo2N)の生成エネルギーは、例えば、100kJ/mol程度である。例えば、Mo層に対する窒化処理によって添加金属のセルフパッシベーション膜が形成される場合、Mo層に添加される金属の窒化物生成エネルギーは100kJ/mol以下であることが好ましい。

【0124】

例えば、Moを用いて配線60が形成される場合、AlやZrが添加金属として用いられることが好ましい。AlがMo層内に添加された場合、AlxNy膜がMo層の外周(露出面)に沿って形成され、ZrがMo層内に添加された場合、ZrxNy膜がMo層の外周(露出面)に沿って形成される。

【0125】

ここで、図13を用いて、セルフパッシベーション膜の形成方法について、説明する。図13の(a)乃至(c)は、セルフパッシベーション膜の形成方法を説明するための模式図である。

【0126】

例えば、図13の(a)に示されるように、所定の濃度の添加金属81を含む高融点導電層60Xが、基板89上に堆積される。高融点導電層60Xの堆積時において、添加金属81は、高融点導電層60X内において、実質的に均一に分散している。

【0127】

尚、基板(例えば、SiO2層)上に、例えば、窒化モリブデンや窒化チタンなどの密着層(図示せず)が、形成され、その密着層上に、高融点導電層60Xが堆積されてもよい。

【0128】

添加金属81を含む高融点導電層(高融点金属層)60Xは、所定の組成比に設定された添加金属81と高融点金属とを含む合金ターゲットを用いたスパッタ法によって形成されてもよいし、添加金属81の金属ターゲットと高融点導電体のターゲットとを用いたスパッタ法によって形成されてもよい。また、高融点導電層が基板68上に堆積された後に、所定の金属元素がイオン注入によって高融点導電層に添加されてもよい。尚、高融点導電層に対する金属元素の添加は、ここで例示した方法に限定されない。

【0129】

そして、高融点導電層60X上に、マスク層(キャップ層)68が堆積される。

【0130】

図13の(b)に示されるように、パターニングされたマスク層68をマスクにして、添加金属81を含む高融点導電層60が、所定の配線パターンを有するように、加工される。加工された高融点導電60に対して、バリア膜を形成するために、例えば、酸素雰囲気中におけるアニール処理が、実行される。この際、高融点導電層60の露出面(ここでは、側面)から酸素が注入されるとともに、添加金属81が高融点導電層60の露出面側に向かって拡散し、添加金属81が高融点導電層60の露出面側において析出する。このように、添加金属81が高融点導電層60の露出面側へ析出させるために、添加金属81の拡散速度が、高融点導電体の拡散速度より速いことが好ましい。

【0131】

これによって、図13の(c)に示されるように、高融点導電層60の露出面上に、バリア膜としてのセルフパッシベーション膜62Aが、形成される。上述のように、添加金属81の酸化物生成エネルギーが、高融点導電体の酸化物生成エネルギーよりも小さい場合、主に、添加金属81が酸素と反応し、添加金属81の金属酸化膜が、高融点導電層60の露出面(側面)上に、形成される。但し、セルフパッシベーション膜62Aは、添加金属からなる金属酸化物と高融点導電体(高融点金属)からなる酸化物とを含んでいてもよい。

【0132】

添加金属81が高融点導電層60の露出面側に析出し、セルフパッシベーション膜62Aが高融点導電層60の露出面上に形成される結果として、高融点導電層60の中央部(内部)における添加金属81の元素濃度は、高融点導電層60の側面側(外周部)における添加金属81の元素濃度より低くなる。但し、高融点導電層60の中央部における添加金属81の元素濃度が、高融点導電層60の側面側における添加金属81の元素濃度と同程度となる場合もある。

【0133】

セルフパッシベーション膜62Aが形成された後、層間絶縁膜(図示せず)が、高融点導電層60及びセルフパッシベーション膜62Aを覆うように、基板89上に、堆積される。

【0134】

図13の(a)乃至(c)に示されるように、高融点導電層60,60X内に添加された金属81のセルフパッシベーションによって、配線としての導電層60,60Xの側面上に、バリア膜としてのセルフパッシベーション膜82Aが形成される。

【0135】

尚、バリア膜62が添加金属のセルフパッシベーションによって形成される場合においても、セルフパッシベーション膜が酸化膜か窒化膜かに応じて、高融点導電層60とセルフパッシベーション膜62との界面に、酸素又は窒素が存在する。高融点導電層60とセルフパッシベーション膜62とを含む配線構造内における酸素濃度又は窒素濃度は、高融点導電層60とセルフパッシベーション膜62との界面から高融点導電層60の中央部に向かって、低くなる。

【0136】