半導体装置及びその製造方法

【課題】チャネル形成領域に印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させる半導体装置を提供する。

【解決手段】チャネル形成領域を有する半導体基板10上にゲート絶縁膜20が形成され、ゲート絶縁膜20の上層にゲート電極21が形成され、ゲート電極21の上層にチャネル形成領域に応力を印加する第1応力導入層22が形成されており、ゲート電極21及び第1応力導入層22の両側部における半導体基板10の表層部にソースドレイン領域13が形成されており、少なくとも第1応力導入層22の領域を除き、ソースドレイン領域13の上層に、チャネル形成領域に第1応力導入層22と異なる応力を印加する第2応力導入層26が形成されている構成とする。

【解決手段】チャネル形成領域を有する半導体基板10上にゲート絶縁膜20が形成され、ゲート絶縁膜20の上層にゲート電極21が形成され、ゲート電極21の上層にチャネル形成領域に応力を印加する第1応力導入層22が形成されており、ゲート電極21及び第1応力導入層22の両側部における半導体基板10の表層部にソースドレイン領域13が形成されており、少なくとも第1応力導入層22の領域を除き、ソースドレイン領域13の上層に、チャネル形成領域に第1応力導入層22と異なる応力を印加する第2応力導入層26が形成されている構成とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置及びその製造方法に関し、特に、金属―絶縁膜(酸化膜)―半導体電界効果トランジスタを有する半導体装置及びその製造方法に関するものである。

【背景技術】

【0002】

金属−酸化膜(絶縁膜)−半導体電界効果トランジスタ(metal-oxide(insulator)-semiconductor field effect transistor、MOSFETあるいはMISFET、以下代表してMOSFETと称する)は、半導体装置の基本的な素子である。

MOSFETは、半導体装置の小型化及び高集積化を進めるにつれてますます微細化されてきている。

【0003】

同一基板上にnチャネルMOSFET(以下NTrとも称する)とpチャネルMOSFET(以下PTrとも称する)を有する構成は、一般にCMOS(Complementary MOS)回路と呼ばれている。

CMOS回路は、消費電力が少なく、また微細化や高集積化が容易で高速動作が可能であることから、多くのLSIを構成するデバイスとして広く用いられている。

【0004】

近年の半導体集積回路では、回路を構成するトランジスタの駆動能力の向上を目的として、応力導入層を用いてトランジスタのチャネル形成領域へ応力を印加することにより、キャリアの移動度を高くする技術が盛んに用いられている。

【0005】

また、チャネル形成領域の形状をフィン(Fin)型にしたフィン型MOSFETが知られている。フィン型に対して、半導体基板上に形成される従来の構成のMOSFETはプレーナー型と称せられる。

フィン型MOSFETは、フィン型のチャネル形成領域をダブルゲート電極あるいはトリプルゲート電極で挟み込んだ構成であり、完全空乏化が可能であり、短チャネル特性やサブスレッショルド特性を向上させることができる。

【0006】

近年の半導体装置では、ゲート長の縮小に伴い、エッチング後のゲート電極形状やゲート長のばらつきが悪化している。これらを改善するため、ゲート電極材料の薄膜化が進んでいる。

そのため、特許文献1の従来技術のように、ゲート電極を覆うように応力導入層が配置された構造では、ゲート電極の薄膜化に伴い、応力導入層が平坦化されていく傾向にある。

【0007】

一方、応力導入層はゲート電極やパターニングなどによりその平坦性が途切れることで、チャネル形成領域へ応力を局在化させる効果が得られることが報告されている。

そのため、ゲート電極材料の薄膜化により、応力導入層からチャネル形成領域へ印加される応力が低下しており、トランジスタの駆動能力向上効果が低下している。

【0008】

図31は従来例に係るプレーナー型のMOSFETの断面図である。

例えば、シリコン基板などからなる半導体基板110上にゲート絶縁膜120が形成されている。

ゲート絶縁膜120の上層にポリシリコンなどからなるゲート電極121が形成されている。

ゲート電極121の両側部に窒化シリコンなどからなる第1サイドウォール絶縁膜122及び第2サイドウォール絶縁膜123が形成されている。

【0009】

例えば、ゲート電極121の両側部における半導体基板110の表層部においてゲート電極121の下方まで至るエクステンション領域111が形成されている。

また、第2サイドウォール絶縁膜123の両側部における半導体基板110の表層部において、エクステンション領域111に接続してソースドレイン領域112が形成されている。

ゲート電極121の表面にNiSiなどの高融点金属シリサイド層124が形成されている。また、ソースドレイン領域112の表面においても高融点金属シリサイド層113が形成されている。

上記のようにして、MOSFETが形成されている。

【0010】

例えば、MOSFETを被覆して全面に窒化シリコンなどからなる応力導入層130が形成されている。

応力導入層130の上層に酸化シリコンなどからなる層間絶縁膜131が形成されている。

【0011】

上記の構成において、応力導入層130はゲート電極121とその両側部に配置された第2サイドウォール絶縁膜123の脇で屈曲した形状となっている。

この形状により、ゲート電極121の端部近傍にて半導体基板110の内部へ応力が印加され、キャリア移動度が向上する。

【0012】

ところが、ゲート電極121を薄膜化すると、応力導入層130の曲がり方が小さくなり、応力導入層130が平坦化されてしまう。

そのため、ゲート電極121の端部近傍において半導体基板110の内部へ印加される応力が小さくなってしまう。

【0013】

特許文献2及び特許文献3に報告されているダブルゲート電極あるいはトリプルゲート電極を有するフィン型のMOSFETでは、応力導入層を用いることによるキャリア移動度の向上が実現されていない。

【0014】

上記のフィン型のMOSFETに対して、図31に示すプレーナー型のMOSFETと同様にゲート電極を覆うように応力導入層を適用しても、上記と同様にゲート電極の薄膜化に伴いフィン型のチャネルへ印加される応力が低下してしまう問題が生じる。

【0015】

応力の印加によるキャリア移動度の変化は、ピエゾ係数を用いて以下の式(1)で示される。

【0016】

[数1]

…(1)

【0017】

ここで、μxxは応力印加後のキャリア移動度、μ0は応力印加前のキャリア移動度である。Sxx,Syy,Szzは、それぞれゲート長方向(longitudinal方向)L、ゲート幅方向(transverse方向)Tおよび基板に垂直な方向(vertical方向)Vに印加される応力である。πl,πt,πvは、それぞれゲート長方向(longitudinal方向)L、ゲート幅方向(transverse方向)Tおよび基板に垂直な方向(vertical方向)Vのピエゾ係数である。

【0018】

図32及び図33は、それぞれプレーナー型のMOSFETおよびフィン型のMOSFETのチャネル形成領域における応力の方向を示す模式的斜視図である。

図32において、半導体基板SUB上に不図示のゲート絶縁膜を介してゲート電極Gが形成されており、ゲート電極Gの両側部における半導体基板SUBの表層部にソースドレイン領域SDが形成されている。

図33において、フィン型の半導体領域Fの上面及び側面Sを被覆して不図示のゲート絶縁膜を介してゲート電極Gが形成されており、ゲート電極Gの両側部におけるフィン型の半導体領域Fに接続してソースドレイン領域SDが形成されている。

【0019】

表1及び表2は、非特許文献2及び非特許文献3にて報告されているプレーナー型のMOSFETおよびフィン型のMOSFETにおける各ピエゾ係数をまとめたものである。

【0020】

【表1】

【0021】

【表2】

【0022】

表1及び表2より、チャネルの種類および面方位、チャネル方向により、πlとπvの符号が異なることがわかる。

これは、ゲート長方向(longitudinal方向)Lと基板に垂直な方向(vertical方向)Vで異なる応力を印加するとキャリア移動度の向上効果が高くなることを表している。

【先行技術文献】

【特許文献】

【0023】

【特許文献1】特開2002−198368号公報

【特許文献2】特開2006−13303号公報

【特許文献3】特開2006−517060号公報

【非特許文献】

【0024】

【非特許文献1】D.Kosemura et al.、 “Characterization of Strain for High Performance MOSFETs”, SSDM, pp.390, (2007)

【非特許文献2】S.E. Thompson et al., “Uniaxial-Process-Induced Strained-Si: Extending the CMOS Roadmap”, IEEE Trans. Electron. Device, Vol. 53, pp.1010 (2006)

【非特許文献3】M. Saitoh et al., “Three-Dimensional Stress Engineering in FinFETs for Mobility/On-Current Enhancement and Gate Current Reduction”, Symp. On VLSI, pp. 18 (2008)

【発明の概要】

【発明が解決しようとする課題】

【0025】

解決しようとする課題は、チャネル形成領域に印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させることである。

【課題を解決するための手段】

【0026】

本発明の半導体装置は、チャネル形成領域を有する半導体基板と、前記チャネル形成領域において前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜の上層に形成されたゲート電極と、前記ゲート電極の上層に形成され、前記チャネル形成領域に応力を印加する第1応力導入層と、前記ゲート電極及び前記第1応力導入層の両側部における前記半導体基板の表層部に形成されたソースドレイン領域と、少なくとも前記第1応力導入層の領域を除き、前記ソースドレイン領域の上層に形成され、前記チャネル形成領域に前記第1応力導入層と異なる応力を印加する第2応力導入層とを有する。

【0027】

上記の本発明の半導体装置は、チャネル形成領域を有する半導体基板上にゲート絶縁膜が形成され、ゲート絶縁膜の上層にゲート電極が形成され、ゲート電極の上層にチャネル形成領域に応力を印加する第1応力導入層が形成されている。ゲート電極及び第1応力導入層の両側部における半導体基板の表層部にソースドレイン領域が形成されている。また、少なくとも第1応力導入層の領域を除き、ソースドレイン領域の上層に、チャネル形成領域に第1応力導入層と異なる応力を印加する第2応力導入層が形成されている。

【0028】

また、本発明の半導体装置の製造方法は、チャネル形成領域を有する半導体基板の前記チャネル形成領域において前記半導体基板上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜の上層にゲート電極を形成する工程と、前記ゲート電極の上層に、前記チャネル形成領域に応力を印加する第1応力導入層を形成する工程と、前記ゲート電極及び前記第1応力導入層の両側部における前記半導体基板の表層部にソースドレイン領域を形成する工程と、少なくとも前記第1応力導入層の領域を除き、前記ソースドレイン領域の上層に、前記チャネル形成領域に前記第1応力導入層と異なる応力を印加する第2応力導入層を形成する工程とを有し、電界効果トランジスタを形成する。

【0029】

上記の本発明の半導体装置の製造方法は、チャネル形成領域を有する半導体基板のチャネル形成領域において半導体基板上にゲート絶縁膜を形成する。

次に、ゲート絶縁膜の上層にゲート電極を形成し、ゲート電極の上層に、チャネル形成領域に応力を印加する第1応力導入層を形成する。

次に、ゲート電極及び第1応力導入層の両側部における半導体基板の表層部にソースドレイン領域を形成する。

次に、少なくとも第1応力導入層の領域を除き、ソースドレイン領域の上層に、チャネル形成領域に第1応力導入層と異なる応力を印加する第2応力導入層を形成する。

上記のようにして、電界効果トランジスタを形成する。

【0030】

また、本発明の半導体装置の製造方法は、チャネル形成領域を有する半導体基板の前記チャネル形成領域において前記半導体基板上にダミーゲート絶縁膜を形成する工程と、前記ダミーゲート絶縁膜の上層にダミーゲート電極を形成する工程と、前記ダミーゲート電極の上層にオフセット膜を形成する工程と、前記ダミーゲート電極及び前記オフセット膜の両側部における前記半導体基板の表層部にソースドレイン領域を形成する工程と、少なくとも前記オフセット膜の領域を除き、前記ソースドレイン領域の上層に、前記チャネル形成領域に応力を導入する第1応力導入層を形成する工程と、前記オフセット膜、前記ダミーゲート電極及び前記ダミーゲート絶縁膜を除去し、ゲート電極用溝を形成する工程と、前記ゲート電極用溝の底面を被覆してゲート絶縁膜を形成する工程と、前記ゲート絶縁膜の上層に前記ゲート電極用溝の途中の深さまでのゲート電極を形成する工程と、前記ゲート電極の上層に前記ゲート電極用溝を埋め込んで前記チャネル形成領域に前記第1応力導入層と異なる応力を導入する第2応力導入層を形成する工程とを有し、電界効果トランジスタを形成する。

【0031】

上記の本発明の半導体装置の製造方法は、チャネル形成領域を有する半導体基板のチャネル形成領域において半導体基板上にダミーゲート絶縁膜を形成する。

次に、ダミーゲート絶縁膜の上層にダミーゲート電極を形成し、ダミーゲート電極の上層にオフセット膜を形成する。

次に、ダミーゲート電極及びオフセット膜の両側部における半導体基板の表層部にソースドレイン領域を形成する。

次に、少なくともオフセット膜の領域を除き、ソースドレイン領域の上層に、チャネル形成領域に応力を導入する第1応力導入層を形成する。

次にオフセット層、ダミーゲート電極及びダミーゲート絶縁膜を除去し、ゲート電極用溝を形成する。

次に、ゲート電極用溝の底面を被覆してゲート絶縁膜を形成し、ゲート絶縁膜の上層にゲート電極用溝の途中の深さまでのゲート電極を形成する。

次に、ゲート電極の上層にゲート電極用溝を埋め込んでチャネル形成領域に第1応力導入層と異なる応力を導入する第2応力導入層を形成する。

上記のようにして、電界効果トランジスタを形成する。

【発明の効果】

【0032】

本発明の半導体装置は、第1応力導入層と第2応力導入層により印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させることができる。

【0033】

本発明の半導体装置の製造方法によれば、第1応力導入層と第2応力導入層を形成することにより印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させることができる。

【図面の簡単な説明】

【0034】

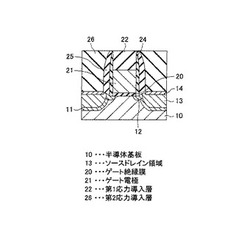

【図1】図1は本発明の第1実施形態に係る半導体装置の模式断面図である。

【図2】図2(a)〜(c)は本発明の第1実施形態に係る半導体装置の製造方法の製造工程を示す模式断面図である。

【図3】図3(a)及び図3(b)は本発明の第1実施形態に係る半導体装置の製造方法の製造工程を示す模式断面図である。

【図4】図4(a)及び図4(b)は本発明の第1実施形態に係る半導体装置の製造方法の製造工程を示す模式断面図である。

【図5】図5は本発明の第2実施形態に係る半導体装置の模式断面図である。

【図6】図6(a)〜(c)は本発明の第2実施形態の変形例に係る半導体装置の製造方法の製造工程を示す模式断面図である。

【図7】図7(a)及び図7(b)は本発明の第2実施形態の変形例に係る半導体装置の製造方法の製造工程を示す模式断面図である。

【図8】図8(a)〜(c)は本発明の第2実施形態に係る半導体装置の製造方法の製造工程を示す模式断面図である。

【図9】図9(a)〜(c)は本発明の第2実施形態に係る半導体装置の製造方法の製造工程を示す模式断面図である。

【図10】図10は本発明の第1変形例に係る半導体装置の模式断面図である。

【図11】図11は本発明の第2変形例に係る半導体装置の模式断面図である。

【図12】図12(a)は本発明の第3実施形態に係る半導体装置の平面図であり、図12(b)は図12(a)中のA−A’における模式断面図であり、図12(c)は図12(a)中のB−B’における模式断面図である。

【図13】図13(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図13(b)は図13(a)中のA−A’における模式断面図であり、図13(c)は図13(a)中のB−B’における模式断面図である。

【図14】図14(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図14(b)は図14(a)中のA−A’における模式断面図であり、図14(c)は図14(a)中のB−B’における模式断面図である。

【図15】図15(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図15(b)は図15(a)中のA−A’における模式断面図であり、図15(c)は図15(a)中のB−B’における模式断面図である。

【図16】図16(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図16(b)は図16(a)中のA−A’における模式断面図であり、図16(c)は図16(a)中のB−B’における模式断面図である。

【図17】図17(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図17(b)は図17(a)中のA−A’における模式断面図であり、図17(c)は図17(a)中のB−B’における模式断面図である。

【図18】図18(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図18(b)は図18(a)中のA−A’における模式断面図であり、図18(c)は図18(a)中のB−B’における模式断面図である。

【図19】図19(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図19(b)は図19(a)中のA−A’における模式断面図であり、図19(c)は図19(a)中のB−B’における模式断面図である。

【図20】図20(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図20(b)は図20(a)中のA−A’における模式断面図であり、図20(c)は図20(a)中のB−B’における模式断面図である。

【図21】図21(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図21(b)は図21(a)中のA−A’における模式断面図であり、図21(c)は図21(a)中のB−B’における模式断面図である。

【図22】図22(a)は本発明の第4実施形態に係る半導体装置の平面図であり、図22(b)は図22(a)中のA−A’における模式断面図であり、図22(c)は図22(a)中のB−B’における模式断面図である。

【図23】図23(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図23(b)は図23(a)中のA−A’における模式断面図であり、図23(c)は図23(a)中のB−B’における模式断面図である。

【図24】図24(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図24(b)は図24(a)中のA−A’における模式断面図であり、図24(c)は図24(a)中のB−B’における模式断面図である。

【図25】図25(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図25(b)は図25(a)中のA−A’における模式断面図であり、図25(c)は図25(a)中のB−B’における模式断面図である。

【図26】図26(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図26(b)は図26(a)中のA−A’における模式断面図であり、図26(c)は図26(a)中のB−B’における模式断面図である。

【図27】図27(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図27(b)は図27(a)中のA−A’における模式断面図であり、図27(c)は図27(a)中のB−B’における模式断面図である。

【図28】図28(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図28(b)は図28(a)中のA−A’における模式断面図であり、図28(c)は図28(a)中のB−B’における模式断面図である。

【図29】図29(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図29(b)は図29(a)中のA−A’における模式断面図であり、図29(c)は図29(a)中のB−B’における模式断面図である。

【図30】図30(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図30(b)は図30(a)中のA−A’における模式断面図であり、図30(c)は図30(a)中のB−B’における模式断面図である。

【図31】図31は従来例に係るプレーナー型のMOSFETの断面図である。

【図32】図32はプレーナー型のMOSFETのチャネル形成領域における応力の方向を示す模式的斜視図である。

【図33】図33はフィン型のMOSFETのチャネル形成領域における応力の方向を示す模式的斜視図である。

【発明を実施するための形態】

【0035】

以下に、本発明の半導体装置及びその製造方法の実施の形態について、図面を参照して説明する。

【0036】

尚、説明は以下の順序で行う。

1.第1実施形態(プレーナー型MOSFETにおいてゲートファーストでゲートを形成した構成)

2.第2実施形態(プレーナー型MOSFETにおいてゲートラストでゲートを形成した構成)

3.第1変形例(ゲート電極が全て高融点金属シリサイド化された構成)

4.第2変形例(ゲート電極が全て高融点金属シリサイド化された構成)

5.第3実施形態(フィン型MOSFETにおいてフィン型半導体領域の2面にゲート電極を有する構成)

6.第4実施形態(フィン型MOSFETにおいてフィン型半導体領域の3面にゲート電極を有する構成)

【0037】

<第1実施形態>

[半導体装置の構造]

図1は本実施形態に係る半導体装置の模式断面図である。

例えば、シリコン基板などからなる半導体基板10上にゲート絶縁膜20が形成されている。

ゲート絶縁膜20の上層にポリシリコンなどからなるゲート電極21が形成されている。

ゲート電極21の上層に第1応力導入層22が形成されている。

ゲート電極21及び第1応力導入層22の両側部に窒化シリコンなどからなる第1サイドウォール絶縁膜24及び第2サイドウォール絶縁膜25が形成されている。

【0038】

例えば、ゲート電極21及び第1応力導入層22の両側部における半導体基板10の表層部においてゲート電極21の下方まで至るエクステンション領域12が形成されている。

また、第2サイドウォール絶縁膜25の両側部における半導体基板10の表層部において、エクステンション領域12に接続してソースドレイン領域13が形成されている。

ソースドレイン領域13の表面において高融点金属シリサイド層14が形成されている。

上記のようにして、MOSFETが形成されている。

【0039】

例えば、第1応力導入層22の形成領域を除いて、MOSFETを被覆して全面に窒化シリコンなどからなる第2応力導入層26が形成されている。より具体的には、第2応力導入層26は第1応力導入層22の上部領域には形成されておらず、第1応力導入層22とゲート電極21の両側部に第2応力導入層26が形成されている。

例えば、第2応力導入層26の上層に酸化シリコンなどからなる不図示の層間絶縁膜が形成され、ゲート電極21及びソースドレイン領域13に対するコンタクトホールが開口され、コンタクトプラグが埋め込まれ、上層配線に接続されている。

【0040】

上記の構成において、第1応力導入層22は、ゲート電極21の上層に形成されている。第1応力導入層22は、チャネル形成領域に応力を導入する。

一方、第2応力導入層26は、少なくとも第1応力導入層22の領域を除き、ソースドレイン領域13の上層に形成されている。

第2応力導入層26は、チャネル形成領域に第1応力導入層と異なる応力を導入する。

【0041】

また、エクステンション領域12及びソースドレイン領域13の一部または全部を含む領域において、SiCあるいはSiGeなどからなる第3応力導入層11が形成されている。第3応力導入層11は、チャネル形成領域に応力を導入する。

【0042】

半導体基板10は,例えばシリコン(Si)基板が用いられる。

ゲート絶縁膜20は、例えば1〜3nm程度の酸化ハフニウム(HfO2)、酸化アルミニウムハフニウム(HfAlO2)、酸化シリコンハフニウム(HfSiO)、酸化タンタル(Ta2O5)、酸化アルミニウム(Al2O3)、酸化ジルコニウム(ZrO2)などのいわゆる高誘電率(High−k)膜を用いることができる。また、酸化シリコン(SiO2)および酸窒化シリコン(SiON)などを用いることができる。さらに、各膜を積層にして用いることもできる。

【0043】

ゲート電極21は、30〜100nm程度の厚さを持つポリシリコン層、金属層、金属化合物層を用いることができる。

金属層や金属化合物層としては,窒化チタン(TiN)、チタン(Ti)、チタンシリコン(TiSi)、ニッケル(Ni)、ニッケルシリコン(NiSi)、ハフニウム(Hf)、ハフニウムシリコン(HfSi)、タングステン(W)、タンタル(Ta)、タンタルシリコン(TaSi)、窒化タンタルシリコン(TaSiN)、コバルト(Co)、コバルトシリコン(CoSi)、ルテニウム(Ru)、あるいはインジウム(In)などを用いることができる。

しきい値電圧や抵抗値の調整のために,これらの膜を積層して用いることができる。

また,酸化アルミニウム(AlO)あるいは酸化ランタン(LaO)などと前述の金属層や金属化合物層を積層にすることでしきい値電圧の調整を行うこともできる。また、前述の金属層や金属化合物層により、チャネルの種類に応じて応力を印加することもできる。

【0044】

第1応力導入層22は、例えば窒化シリコンを30〜100nm程度の膜厚で用いることができる。NTrの場合は2.0GPa程度の圧縮応力を持った膜、PTrの場合は1.5GPa程度の引っ張り応力を持った膜を用いることができる。

なお、本実施形態では記載していないが,第1応力導入層22の上部または下部に第1応力導入層22と異なる絶縁膜を積層してもよい。

【0045】

第1サイドウォール絶縁膜24及び第2サイドウォール絶縁膜25は、それぞれ酸化シリコンあるいは窒化シリコン膜などを単層であるいは積層して用いることができる。それぞれ、例えば2〜10nmおよび20〜60nm程度の厚さに形成されている。

また、ゲート容量を低減するために、配線絶縁膜などに用いられるいわゆる低誘電率(Low−k)膜を用いることもできる。

【0046】

半導体基板10のチャネル形成領域とエクステンション領域12には、NTrの場合にはそれぞれp型不純物とn型不純物、PTrの場合にはそれぞれn型不純物とp型不純物が導入される。

例えば、n型不純物としてはリン(P)あるいはヒ素(As)などが用いられる。p型不純物としては、ホウ素(B)、フッ化ボロン(BF2)あるいは(In)などを用いることができる。

場合によっては、エクステンション領域12と異なる導電型の不純物をエクステンション領域12よりも深く注入した構成としてもよい。この場合、エクステンション領域12の深さ方向の不純物プロファイルをさらに急峻にすることができる。

【0047】

ソースドレイン領域13にはエクステンション領域12と同じ導電型の不純物が導入されている。

本実施形態においては、エクステンション領域12及びソースドレイン領域13の一部または全部が第3応力導入層11中に形成されているが、第3応力導入層11が形成されていない構成でもよい。

第3応力導入層11は、炭素(C)あるいはゲルマニウム(Ge)などとシリコンの化合物からなり、30〜100nm程度の厚さで形成されている。半導体基板10のチャネル形成領域に印加したい応力に応じてCとGeの含有量を調整することができる。

【0048】

高融点金属シリサイド層14は、例えばTi,Co,Ni,Ptまたはそれらの化合物からなり、20〜70nm程度の厚さで形成されている。

【0049】

第2応力導入層26は、第2サイドウォール絶縁膜25と高融点金属シリサイド層14を覆うように形成されており、第1応力導入層22と第2サイドウォール絶縁膜25の両端で切断された形状になっている。

第2応力導入層26は、例えば窒化シリコンを80〜200nm程度の膜厚で、NTrの場合は1.6GPa程度の引っ張り応力を持った膜が用いられ、PTrの場合は2.0GPa程度の圧縮応力を持った膜が用いられる。

【0050】

上記のように、ゲート電極21上に第1応力導入層22が形成され、第1応力導入層22の領域を除く領域における半導体基板10上が第2応力導入層26で被覆された構造となっている。これにより、第2応力導入層26がゲートの端部で切断された構造となる。

また、第1応力導入層22と第2応力導入層26で異なる応力を有する材料が用いられている。

【0051】

非特許文献1によると、応力導入層が切断されると、切断された応力導入層の端部の半導体基板上に応力が局在化されることが報告されている。

本実施形態では、第2応力導入層26がゲートの端部で切断された構造となっており、ゲートの端部において効果的にチャネル形成領域へ応力印加を行うことができる。

【0052】

さらに、ゲート電極の薄膜化を行っても、第1応力導入層22の膜厚を調整することで、第2応力導入層26の膜厚を厚くすることができるため、第2応力導入層26からチャネル形成領域に印加される応力の緩和が起こらない。

【0053】

本実施形態の半導体装置によれば、チャネル形成領域に異なる応力を印加する第1および第2応力導入層を用い、印加する応力の組み合わせを調整することで、従来例よりもキャリア移動度を向上させることができる。

【0054】

[半導体装置の製造方法]

本実施形態の半導体装置の製造方法について、図2〜4を参照して説明する。

まず、図2(a)に示すように、例えば半導体基板10上にゲート絶縁膜20、ゲート電極21及び第1応力導入層22を積層する。

次に、フォトリソグラフィー技術や電子線リソグラフィー技術を用いてレジストパターンを形成し、そのレジストパターンをマスクとしてドライエッチングなどを行い、ゲート絶縁膜20、ゲート電極21及び第1応力導入層22をパターン加工する。

なお、図面上に明示されていないが、ゲート絶縁膜20を形成する前に、半導体基板10中に素子分離領域を形成し、イオン注入法にて不純物を導入してウェル領域を形成しておいてもよい。

【0055】

ゲート絶縁膜20は、例えば1〜3nm程度の1〜3nm程度の酸化ハフニウム(HfO2)、酸化アルミニウムハフニウム(HfAlO2)、酸化シリコンハフニウム(HfSiO)、酸化タンタル(Ta2O5)、酸化アルミニウム(Al2O3)、酸化ジルコニウム(ZrO2)などのいわゆる高誘電率(High−k)膜により形成する。また、酸化シリコン(SiO2)および酸窒化シリコン(SiON)などを用いることができる。さらに、各膜を積層にして用いることもできる。その形成方法は、熱酸化プロセス、化学気相成長法(CVD法)、あるいは物理気相成長法(PVD法)などを用いることができる。

【0056】

ゲート電極21は、例えばCVD法、ALD(Atomic Layer Deposition)法あるいはPVD法により、50〜100nm程度の厚さを持つポリシリコン層、金属層、金属化合物層を堆積して形成する。

金属層や金属化合物層としては,窒化チタン(TiN)、チタン(Ti)、チタンシリコン(TiSi)、ニッケル(Ni)、ニッケルシリコン(NiSi)、ハフニウム(Hf)、ハフニウムシリコン(HfSi)、タングステン(W)、タンタル(Ta)、タンタルシリコン(TaSi)、窒化タンタルシリコン(TaSiN)、コバルト(Co)、コバルトシリコン(CoSi)、ルテニウム(Ru)、あるいはインジウム(In)などを用いることができる。

しきい値電圧や抵抗値の調整のために、これらの膜を積層してもよい。また、酸化アルミニウム(AlO)あるいは酸化ランタン(LaO)などと前述の金属層や金属化合物層を積層にすることもできる。また、前述の金属層や金属化合物層により、チャネルの種類に応じて応力を印加することもできる。

【0057】

第1応力導入層22は、例えば窒化シリコンを30〜100nm程度の膜厚で用いることができる。NTrの場合は2.0GPa程度の圧縮応力を持った膜、PTrの場合は1.5GPa程度の引っ張り応力を持った膜を用いることができる。

【0058】

次に、図2(b)に示すように、絶縁膜を基板全面に形成した後、ドライエッチング法などによりリセスエッチングして、ゲート絶縁膜20、ゲート電極21、第1応力導入層22の側壁部のみにダミーサイドウォール絶縁膜23を形成する。

ダミーサイドウォール絶縁膜23の形成には、まず、例えば50〜150nm程度の窒化シリコン膜、酸化シリコン、TEOS(原料ガスにtetraethylorthosilicateを用いた酸化シリコン膜)、NSG膜をCVD法などにより形成する。

その後、ドライエッチング法などにより全面にリセスエッチングする。この時、半導体基板10に対して第1応力導入層22とダミーサイドウォール絶縁膜23の選択比を高くすることで,半導体基板10を選択的にエッチングできる。

また、素子分離領域を形成している場合は、素子分離領域材料との選択比もできるだけ高くしておくことが望ましい。

上記により、半導体基板10に50〜100nm程度の溝を形成する。

【0059】

その後、半導体基板10のエッチングした領域内へ選択的に第3応力導入層11を形成する。第3応力導入層11は、例えば、圧縮応力を導入する際にはシリコンゲルマニウム(SiGe)、引っ張り応力を導入する際には炭化シリコン(SiC)を選択エピタキシャル成長法にて50〜200nm程度の膜厚で形成する。

さらに、第3応力導入層11を形成する際には、ソースドレイン領域を形成することを目的として、不純物を導入しておいてもよい。例えば、NTrの場合にはn型不純物を導入し、PTrの場合にはそれぞれp型不純物を導入しておく。

【0060】

次に、図2(c)に示すように、ダミーサイドウォール絶縁膜23をウェットエッチング法にて除去する。

次に、絶縁膜を基板全面に形成した後、ドライエッチング法などによりリセスエッチングして、ゲート絶縁膜20、ゲート電極21、第1応力導入層22の側壁部のみに第1サイドウォール絶縁膜24を形成する。

第1サイドウォール絶縁膜24の形成には、まず、例えば2〜10nm程度の窒化シリコン膜、酸化シリコン、TEOS、NSG膜をCVD法などにより形成する。その後、ドライエッチング法などにより全面にリセスエッチングする。

【0061】

本実施形態では第1サイドウォール絶縁膜24を形成しているが、不要であれば形成しなくてもよい。また、ダミーサイドウォール絶縁膜23を除去せずに、そのまま残して第1サイドウォール絶縁膜24として用いてもよい。

【0062】

その後、イオン注入法により不純物をイオン注入してエクステンション領域12を形成する。

エクステンション領域12は、NTrの場合にはそれぞれn型不純物を、PTrの場合にはp型不純物を導入して形成する。

さらに、場合によってはエクステンション領域12と異なる導電型の不純物をエクステンション領域12よりも深く注入してもよい。この場合、エクステンション領域12の深さ方向の不純物プロファイルをさらに急峻にすることもできる。

【0063】

次に、図3(a)に示すように、絶縁膜を基板全面に形成した後、ドライエッチング法などによりリセスエッチングして、第1サイドウォール絶縁膜24の側壁部のみに第2サイドウォール絶縁膜25を形成する。

第2サイドウォール絶縁膜25の形成には、まず、例えば20〜60nm程度の窒化シリコン膜、酸化シリコン、TEOS、NSG膜をCVD法などにより形成する。その後、ドライエッチング法などにより全面にリセスエッチングする。

【0064】

本実施形態では第2サイドウォール絶縁膜25を単層構成で形成しているが、複数層を積層した構成としてもよい。

【0065】

その後、イオン注入法により不純物をイオン注入してソースドレイン領域13を形成する。

ソースドレイン領域13は、エクステンション領域12と同じ導電型の不純物にて形成する。

その後、エクステンション領域12及びソースドレイン領域13に注入された不純物をアニール処理により活性化する。この活性化アニール処理は、例えば1000〜1100℃度程度の急速熱処理(Rapid Thermal Annealing)により行う。

【0066】

次に、サリサイドプロセス技術により、ソースドレイン領域13の表面に高融点金属シリサイド層14を形成する。これは、例えばTi,Co,Ni,Ptまたはそれらの化合物により、20〜70nm程度の厚さで形成する。

【0067】

次に、図3(b)に示すように、例えばCVD法により基板全面に第2応力導入層26と層間絶縁膜27を形成する。

第2応力導入層26としては、例えば窒化シリコンを200〜300nm程度の膜厚で形成し、チャネルの種類に応じて1.5〜2.0GPa程度の引っ張り応力や圧縮応力を持った膜を形成する。

また、層間絶縁膜27としては,例えばTEOSやNSG膜などを用いることができる。さらに、場合によっては第2応力導入層26のみを形成し、層間絶縁膜27を形成しないこともある。

【0068】

次に、図4(a)に示すように、第1応力導入層22の上面部が露出するように、第2応力導入層26と層間絶縁膜27を除去する。例えば、CMP(Chemical Mechanical Polishing)法によりそれぞれの膜を研磨除去する。

これにより、第2応力導入層26が第1応力導入層22の両脇で切断された構造となる。

以上のようにして、図1に示す構成の本実施形態に係る半導体装置を製造できる。

【0069】

以降の工程としては、例えば図4(b)に示すように、基板全面に第2層間絶縁膜28を堆積し、ソースドレイン領域及びゲート電極に達するコンタクトホールCHを開口し、プラグ29を埋め込んで形成し、必要に応じて上層配線30を形成する。

【0070】

本発明の半導体装置の製造方法によれば、第1応力導入層と第2応力導入層を形成することにより印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させることができる。

【0071】

<第2実施形態>

[半導体装置の構造]

図5は本実施形態に係る半導体装置の模式断面図である。

実質的には第1実施形態と同様の構成であるが、以下の点が異なる。

第1実施形態の半導体装置におけるゲート絶縁膜20、ゲート電極21及び第1応力導入層22が除去されてゲート電極用溝TRが形成されており、ゲート電極用溝TR内にゲート絶縁膜31、ゲート電極32及び第1応力導入層33が埋め込まれている。

【0072】

ゲート絶縁膜31は、ゲート電極用溝TRの底面とゲート電極用溝TRの途中の深さまでの側面を被覆して形成されており、ゲート電極32はゲート絶縁膜31が形成された深さまで形成されている。

ゲート電極32の上層において、ゲート電極用溝TRを埋め込んで、第1応力導入層33が形成されている。

【0073】

本実施形態の半導体装置によれば、チャネル形成領域に異なる応力を印加する第1および第2応力導入層を用い、印加する応力の組み合わせを調整することで、従来例よりもキャリア移動度を向上させることができる。

【0074】

[半導体装置の製造方法]

本実施形態の半導体装置の製造方法について、図6〜9を参照して説明する。

まず、図6(a)に示すように、例えば半導体基板10上にダミーゲート絶縁膜20a、ダミーゲート電極21a及びハードマスクとなるオフセット膜22aを積層する。

次に、フォトリソグラフィー技術や電子線リソグラフィー技術を用いてレジストパターンを形成し、そのレジストパターンをマスクとしてドライエッチングなどを行う。これにより、ダミーゲート絶縁膜20a、ダミーゲート電極21a及びオフセット膜22aをパターン加工する。そのレジストパターンをマスクとしてオフセット膜22aのパターン加工を行い、オフセット膜22aをハードマスクとしてダミーゲート絶縁膜20aとダミーゲート電極21aをパターン加工してもよい。

なお、図面上に明示されていないが、ダミーゲート絶縁膜20aを形成する前に、半導体基板10中に素子分離領域を形成し、イオン注入法にて不純物を導入してウェル領域を形成しておいてもよい。

【0075】

ダミーゲート絶縁膜20aは、例えば1〜3nm程度の例えば1〜3nm程度の酸化シリコン(SiO2)および酸窒化シリコン(SiON)などを用いることができる。その形成方法は、熱酸化プロセス、化学気相成長法(CVD法)、あるいは物理気相成長法(PVD法)などを用いることができる。

【0076】

ダミーゲート電極21aは、例えばCVD法あるいはPVD法により、30〜100nm程度の厚さを持つポリシリコン層を堆積して形成する。

【0077】

オフセット膜22aは、例えばCVD法により酸化シリコンを30〜100nm程度の膜厚で形成することができる。

【0078】

次に、図6(b)に示すように、絶縁膜を基板全面に形成した後、ドライエッチング法などによりリセスエッチングして、ダミーゲート絶縁膜20a、ダミーゲート電極21a、オフセット膜22aの側壁部のみにダミーサイドウォール絶縁膜23を形成する。

ダミーサイドウォール絶縁膜23の形成には、まず、例えば50〜150nm程度の窒化シリコン膜、酸化シリコン、TEOS(原料ガスにtetraethylorthosilicateを用いた酸化シリコン膜)、NSG膜をCVD法などにより形成する。

その後、ドライエッチング法などにより全面にリセスエッチングする。この時、半導体基板10に対してオフセット膜22aとダミーサイドウォール絶縁膜23の選択比を高くすることで、半導体基板10を選択的にエッチングできる。

また、素子分離領域を形成している場合は、素子分離領域材料との選択比もできるだけ高くしておくことが望ましい。

上記により、半導体基板10に50〜100nm程度の溝を形成する。

【0079】

その後、半導体基板10のエッチングした領域内へ選択的に第3応力導入層11を形成する。第3応力導入層11は、例えば、圧縮応力を導入する際にはシリコンゲルマニウム(SiGe)、引っ張り応力を導入する際には炭化シリコン(SiC)を選択エピタキシャル成長法にて50〜200nm程度の膜厚で形成する。

さらに、第3応力導入層11を形成する際には、ソースドレイン領域を形成することを目的として、不純物を導入しておいてもよい。例えば、NTrの場合にはn型不純物を導入し、PTrの場合にはそれぞれp型不純物を導入しておく。

【0080】

次に、図6(c)に示すように、ダミーサイドウォール絶縁膜23をウェットエッチング法にて除去する。

次に、絶縁膜を基板全面に形成した後、ドライエッチング法などによりリセスエッチングして、ダミーゲート絶縁膜20a、ダミーゲート電極21a、オフセット膜22aの側壁部のみに第1サイドウォール絶縁膜24を形成する。

第1サイドウォール絶縁膜24の形成には、まず、例えば2〜10nm程度の窒化シリコン膜、酸化シリコン、TEOS、NSG膜をCVD法などにより形成する。その後、ドライエッチング法などにより全面にリセスエッチングする。

【0081】

本実施形態では第1サイドウォール絶縁膜24を形成しているが、不要であれば形成しなくてもよい。また、ダミーサイドウォール絶縁膜23を除去せずに、そのまま残して第1サイドウォール絶縁膜24として用いてもよい。

【0082】

その後、イオン注入法により不純物をイオン注入してエクステンション領域12を形成する。

エクステンション領域12は、NTrの場合にはそれぞれn型不純物を、PTrの場合にはp型不純物を導入して形成する。

さらに、場合によってはエクステンション領域12と異なる導電型の不純物をエクステンション領域12よりも深く注入してもよい。この場合、エクステンション領域12の深さ方向の不純物プロファイルをさらに急峻にすることもできる。

【0083】

次に、図7(a)に示すように、絶縁膜を基板全面に形成した後、ドライエッチング法などによりリセスエッチングして、第1サイドウォール絶縁膜24の側壁部のみに第2サイドウォール絶縁膜25を形成する。

第2サイドウォール絶縁膜25の形成には、まず、例えば20〜60nm程度の窒化シリコン膜、酸化シリコン、TEOS、NSG膜をCVD法などにより形成する。その後、ドライエッチング法などにより全面にリセスエッチングする。

【0084】

本実施形態では第2サイドウォール絶縁膜25を単層構成で形成しているが、複数層を積層した構成としてもよい。

【0085】

その後、イオン注入法により不純物をイオン注入してソースドレイン領域13を形成する。

ソースドレイン領域13は、エクステンション領域12と同じ導電型の不純物にて形成する。

その後、エクステンション領域12及びソースドレイン領域13に注入された不純物をアニール処理により活性化する。この活性化アニール処理は、例えば1000〜1100℃度程度の急速熱処理(Rapid Thermal Annealing)により行う。

【0086】

次に、サリサイドプロセス技術により、ソースドレイン領域13の表面に高融点金属シリサイド層14を形成する。これは、例えばTi,Co,Ni,Ptまたはそれらの化合物により、20〜70nm程度の厚さで形成する。

【0087】

次に、図7(b)に示すように、例えばCVD法により基板全面に第2応力導入層26と層間絶縁膜27を形成する。

第2応力導入層26としては、例えば窒化シリコンを200〜300nm程度の膜厚で形成し、チャネルの種類に応じて1.5〜2.0GPa程度の引っ張り応力や圧縮応力を持った膜を形成する。

また、層間絶縁膜27としては,例えばTEOSやNSG膜などを用いることができる。さらに、場合によっては第2応力導入層26のみを形成し、層間絶縁膜27を形成しないこともある。

【0088】

次に、図8(a)に示すように、オフセット膜22aの上面部が露出するように、第2応力導入層26と層間絶縁膜27を除去する。例えば、CMP(Chemical Mechanical Polishing)法によりそれぞれの膜を研磨除去する。

これにより、第2応力導入層26がオフセット膜22aの両脇で切断された構造となる。

【0089】

次に、図8(b)に示すように、オフセット膜22a、ダミーゲート電極21a及びダミーゲート絶縁膜20aを除去して、ゲート電極用溝TRを形成する。

ダミーゲート電極21aは,例えばドライエッチング法を用いて選択的に除去する。また、オフセット膜22aとダミーゲート絶縁膜20aは、例えばドライエッチング法やウェットエッチング法を用いて選択的に除去する。

【0090】

次に、図8(c)に示すように、ゲート電極用溝TRの内部にゲート絶縁膜31とゲート電極32を形成するための材料を半導体基板10上全面に堆積する。

ここで、ゲート絶縁膜31には、1〜3nm程度の酸化ハフニウム(HfO2)、酸化アルミニウムハフニウム(HfAlO2)、酸化シリコンハフニウム(HfSiO)、酸化タンタル(Ta2O5)、酸化アルミニウム(Al2O3)、酸化ジルコニウム(ZrO2)などのいわゆる高誘電率(High−k)膜により形成する。また、酸化シリコン(SiO2)および酸窒化シリコン(SiON)などを用いることができる。さらに、各膜を積層にして用いることもできる。その形成方法は、ALD法あるいはCVD法などを用いることができる。

【0091】

ゲート電極32は、例えばCVD法、ALD法あるいはPVD法により、50〜100nm程度の厚さを持つポリシリコン層、金属層、金属化合物層を堆積して形成する。

金属層や金属化合物層としては,窒化チタン(TiN)、チタン(Ti)、チタンシリコン(TiSi)、ニッケル(Ni)、ニッケルシリコン(NiSi)、ハフニウム(Hf)、ハフニウムシリコン(HfSi)、タングステン(W)、タンタル(Ta)、タンタルシリコン(TaSi)、窒化タンタルシリコン(TaSiN)、コバルト(Co)、コバルトシリコン(CoSi)、ルテニウム(Ru)、あるいはインジウム(In)などを用いることができる。その形成方法は、ALD法あるいはPVD法などを用いることができる。

しきい値電圧や抵抗値の調整のために、これらの膜を積層してもよい。また、酸化アルミニウム(AlO)あるいは酸化ランタン(LaO)などと前述の金属層や金属化合物層を積層にすることもできる。また、前述の金属層や金属化合物層により、チャネルの種類に応じて応力を印加することもできる。

【0092】

次に、図9(a)に示すように、第2応力導入層26の上部にあるゲート絶縁膜31とゲート電極32の材料をCMP法あるいはドライエッチング法を用いて除去する。

これにより、ゲート電極用溝TR内部のみにゲート絶縁膜31とゲート電極32が残る構造となる。

【0093】

次に、図9(b)に示すように、例えばゲート電極用溝TR内のゲート絶縁膜31とゲート電極32をドライエッチング法を用いて選択的にゲート電極用溝TRの深さの半分程度のところまで除去する。

このとき、第2応力導入層26、第1サイドウォール絶縁膜24及び第2サイドウォール絶縁膜25と、ゲート絶縁膜31およびゲート電極32との選択比を高めておく必要がある。

【0094】

次に、図9(c)に示すように、ゲート電極用溝TR内部のゲート電極32と第2応力導入層26の上部を覆うように、第1応力導入層33を堆積する。

第1応力導入層33には、例えば窒化シリコンを50〜150nm程度の膜厚で、チャネル種類に応じて1.5〜2.0GPa程度の引っ張り応力や圧縮応力を持った膜を形成し、第2応力導入層26と異なる応力を印加する膜とする。

次に、第2応力導入層26の上部にある第1応力導入層33をCMP法を用いて除去する。

なお、本実形態で示した各材料の膜厚や応力は、形成するトランジスタ特性や半導体基板へ導入する応力に応じて調整する必要があるため、これに限定されるものではない。

以上のようにして、図5に示す構成の本実施形態に係る半導体装置を製造できる。

【0095】

上記の製造方法では、ダミーゲート絶縁膜を除去して、改めてゲート絶縁膜を形成しているが、これに限らず、除去せずにそのまま用いるようにしてもよい。

【0096】

以降の工程としては、例えば、基板全面に第2層間絶縁膜を堆積し、ソースドレイン領域及びゲート電極に達するコンタクトホールを開口し、プラグを埋め込んで形成し、必要に応じて上層配線を形成する。

【0097】

本発明の半導体装置の製造方法によれば、第1応力導入層と第2応力導入層を形成することにより印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させることができる。

【0098】

<第1変形例>

図10は本変形例に係る半導体装置の模式断面図である。

実質的には第2実施形態と同様の構成であるが、ゲート電極が全て高融点金属シリサイドにより形成されたゲート電極32sからなることが異なる。

本変形例に係る半導体装置の製造方法は、図9(b)まで第2実施形態と同様に形成した後、ゲート電極32を全てシリサイド化する。

以降は第2実施形態と同様にして形成できる。

【0099】

<第2変形例>

図11は本変形例に係る半導体装置の模式断面図である。

実質的には第1実施形態と同様の構成であるが、ゲート電極が全て高融点金属シリサイドにより形成されたゲート電極21sからなることが異なる。

本変形例に係る半導体装置の製造方法は、図8(a)まで第2実施形態と同様に形成した後、オフセット膜22aを除去し、ダミーゲート電極をシリサイド化する。

得られたシリサイド化したダミーゲート電極21aをそのままゲート電極として用いる。また、ダミーゲート絶縁膜をそのままゲート絶縁膜として用いる。

以降は第2実施形態と同様にして形成できる。

【0100】

<第3実施形態>

[半導体装置の構造]

図12(a)は本実施形態に係る半導体装置の平面図であり、図12(b)は図12(a)中のA−A’における模式断面図であり、図12(c)は図12(a)中のB−B’における模式断面図である。

半導体基板40上に埋め込み絶縁膜41が形成されており、埋め込み絶縁膜41の上部にフィン型のチャネル形成領域を有する半導体領域42とハードマスク43が形成されている。

例えば,半導体基板40はシリコン基板であり、埋め込み絶縁膜41は50〜100nm程度の酸化シリコンが用いられる。

また、フィン型の半導体領域42とハードマスク43は、30〜80nm程度の膜厚のシリコン、50nmの膜厚の窒化シリコンが用いられる。

フィン型の半導体領域42は、半導体基板40の主面から突出した凸状の半導体領域であり、チャネル形成領域が半導体領域42に形成されている。

ここでは、フィン型の半導体領域42が埋め込み絶縁膜41の上部に配置されているが、埋め込み絶縁膜41が形成されておらず、半導体基板40とフィン型の半導体領域42が直接つながった構造を用いてもよい。

【0101】

埋め込み絶縁膜41、フィン型の半導体領域42およびハードマスク43を覆うように、ゲート絶縁膜45とゲート電極46が形成されている。

ゲート絶縁膜45は、1〜3nm程度の酸化ハフニウム(HfO2)、酸化アルミニウムハフニウム(HfAlO2)、酸化シリコンハフニウム(HfSiO)、酸化タンタル(Ta2O5)、酸化アルミニウム(Al2O3)、酸化ジルコニウム(ZrO2)などのいわゆる高誘電率(High−k)膜により形成する。また、酸化シリコン(SiO2)および酸窒化シリコン(SiON)などを用いることができる。さらに、各膜を積層にして用いることもできる。

フィン型のチャネル形成領域をダブルゲート電極で挟み込んだ構成である。

【0102】

ゲート電極46は、例えばポリシリコン層、金属層、金属化合物層を用いて形成されている。

金属層や金属化合物層としては,窒化チタン(TiN)、チタン(Ti)、チタンシリコン(TiSi)、ニッケル(Ni)、ニッケルシリコン(NiSi)、ハフニウム(Hf)、ハフニウムシリコン(HfSi)、タングステン(W)、タンタル(Ta)、タンタルシリコン(TaSi)、窒化タンタルシリコン(TaSiN)、コバルト(Co)、コバルトシリコン(CoSi)、ルテニウム(Ru)、あるいはインジウム(In)などを用いることができる。

しきい値電圧や抵抗値の調整のために、これらの膜を積層してもよい。また、酸化アルミニウム(AlO)あるいは酸化ランタン(LaO)などと前述の金属層や金属化合物層を積層にすることもできる。また、前述の金属層や金属化合物層により、チャネルの種類に応じて応力を印加することもできる。

【0103】

また、フィン型の半導体領域42が形成されていない領域にある埋め込み絶縁膜41の上面がフィン型の半導体領域42の底面よりも低く形成されている。

このため、フィン型の半導体領域42の側壁面がゲート絶縁膜45とゲート電極46で完全に覆われる構造となっている。

【0104】

ゲート電極46の上部には、第1応力導入層47が形成されている。第1応力導入層47としては、例えば30〜100nm程度膜厚の窒化シリコンが用いられる。フィン型のMOSFETのチャネル種類に応じて、1.0GPa程度の圧縮応力または1.5GPa程度の引っ張り応力を持った膜を用いることができる。

【0105】

ゲート絶縁膜45、ゲート電極46及び第1応力導入層47の側壁部には,サイドウォール絶縁膜50,51が形成されている。

サイドウォール絶縁膜50,51は、例えば酸化シリコンや窒化シリコン膜等などを単層あるいは複数層を積層して用いることができ、20〜100nm程度の膜厚で形成されている。

また、ゲート容量を低減するために、配線絶縁膜等に用いられるいわゆる低誘電率(Low−k)膜を用いることもできる。

サイドウォール絶縁膜50,51の側面には、第2応力導入層54が形成されており、第2応力導入層54の上面部は、第1応力導入層47の上面部と同じ高さなっている。

さらに、第2応力導入層54はサイドウォール絶縁膜50の両端で分離された構造になっている。より具体的には、第2応力導入層54は第1応力導入層47の上部領域には形成されておらず、第1応力導入層47とゲート電極46の両側部に第2応力導入層54が形成されている。

【0106】

本実施形態の半導体装置のMOSFETは、フィン型のMOSFETである。

ここで、本実施形態の半導体装置によれば、チャネル形成領域に異なる応力を印加する第1および第2応力導入層を用い、印加する応力の組み合わせを調整することで、従来例よりもキャリア移動度を向上させることができる。

【0107】

[半導体装置の製造方法]

本実施形態の半導体装置の製造方法について、図13〜21を参照して説明する。

図13(a)は本実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図13(b)は図13(a)中のA−A’における模式断面図であり、図13(c)は図13(a)中のB−B’における模式断面図である。

半導体基板40、埋め込み絶縁膜41および半導体領域42の3層構造を持ったSOI(Silicon On Insulator)基板上に、ハードマスク43を堆積する。その後、フォトリソグラフィー技術や電子線リソグラフィー技術を用いてレジスト膜44を形成する。

次に、レジスト膜44をマスクとしてドライエッチング法などによるエッチングを行い、ハードマスク43をパターンエッチングする。

このとき,例えば半導体基板40はシリコン基板、埋め込み絶縁膜41は50〜100nm程度の酸化シリコンを用いる。

また、半導体領域42としては、30〜80nmのシリコン層を用いる。また、ハードマスク43には、例えば50nm程度の膜厚の窒化シリコンを用いる。

【0108】

図14(a)は図13の次の工程を示す平面図であり、図14(b)は図14(a)中のA−A’における模式断面図であり、図14(c)は図14(a)中のB−B’における模式断面図である。

レジスト膜44を削除した後、ハードマスク43を用いて半導体領域42をドライエッチング処理によりエッチングする。

このとき、埋め込み絶縁膜41の一部も同時にエッチングしておくことで、フィン型の半導体領域42の端部で埋め込み絶縁膜41が凹んだ構造にしておく。

上記により、フィン型の半導体領域42は、半導体基板40の主面から突出した凸状の形状となる。

【0109】

本実施形態では、SOI基板を用いてフィン型の半導体領域42を形成しているが、SOI基板を用いない方法もある。例えば、半導体基板40上にハードマスク43及びレジスト膜44を形成し、直接フィン型の半導体領域を形成する。半導体基板40上の全面にハードマスク43の上面と同じかそれよりも高くなる膜厚で酸化シリコンなどの絶縁膜を堆積する。その後、CMP法を用いてハードマスク43の上面まで絶縁膜を除去した後、ドライエッチング法を用いて選択的に絶縁膜をエッチングすることで、半導体基板40上でフィン型の半導体領域が形成されていない領域のみ酸化シリコン膜を形成することが可能となる。

【0110】

図15(a)は図14の次の工程を示す平面図であり、図15(b)は図15(a)中のA−A’における模式断面図であり、図15(c)は図15(a)中のB−B’における模式断面図である。

半導体基板40上の全面に、ゲート絶縁膜45とゲート電極46を堆積して形成する。

ここで、ゲート絶縁膜45には、1〜3nm程度の酸化ハフニウム(HfO2)、酸化アルミニウムハフニウム(HfAlO2)、酸化シリコンハフニウム(HfSiO)、酸化タンタル(Ta2O5)、酸化アルミニウム(Al2O3)、酸化ジルコニウム(ZrO2)などのいわゆる高誘電率(High−k)膜により形成する。また、酸化シリコン(SiO2)および酸窒化シリコン(SiON)などを用いることができる。さらに、各膜を積層にして用いることもできる。その形成方法は、ALD法あるいはCVD法などを用いることができる。

【0111】

ゲート電極46は、例えばCVD法、ALD法あるいはPVD法により、50〜100nm程度の厚さを持つポリシリコン層、金属層、金属化合物層を堆積して形成する。

金属層や金属化合物層としては,窒化チタン(TiN)、チタン(Ti)、チタンシリコン(TiSi)、ニッケル(Ni)、ニッケルシリコン(NiSi)、ハフニウム(Hf)、ハフニウムシリコン(HfSi)、タングステン(W)、タンタル(Ta)、タンタルシリコン(TaSi)、窒化タンタルシリコン(TaSiN)、コバルト(Co)、コバルトシリコン(CoSi)、ルテニウム(Ru)、あるいはインジウム(In)などを用いることができる。その形成方法は、ALD法あるいはPVD法などを用いることができる。

しきい値電圧や抵抗値の調整のために、これらの膜を積層してもよい。また、酸化アルミニウム(AlO)あるいは酸化ランタン(LaO)などと前述の金属層や金属化合物層を積層にすることもできる。また、前述の金属層や金属化合物層により、チャネルの種類に応じて応力を印加することもできる。

【0112】

図16(a)は図15の次の工程を示す平面図であり、図16(b)は図16(a)中のA−A’における模式断面図であり、図16(c)は図16(a)中のB−B’における模式断面図である。

ゲート電極46の上面からCMP処理を行ってゲート電極46を所定の膜厚に加工する。

次に、ゲート電極46上に第1応力導入層47を形成した後、フォトリソグラフィー技術や電子線リソグラフィー技術を用いてレジスト膜48を形成する。

レジスト膜48をマスクとしてドライエッチング法などのエッチング処理を行うことで、第1応力導入層47をエッチングする。

ここで,第1応力導入膜47は、例えば30〜100nm程度の膜厚の窒化シリコンを用いることができる。

フィン型のMOSFETのチャネルの種類に応じて、2.0GPa程度の圧縮応力または1.5GPa程度の引っ張り応力を持った膜を用いることができる。

【0113】

図17(a)は図16の次の工程を示す平面図であり、図17(b)は図17(a)のA−A’における模式断面図であり、図17(c)は図17(a)中のB−B’における模式断面図である。

レジスト膜48を除去した後、第1応力導入層47をマスクとしてドライエッチング法などによりエッチング処理を行い、ゲート電極46とゲート絶縁膜45をエッチングする。

また、本実施形態とは異なり、レジスト膜48を残したまま、レジスト膜48を第1応力導入層47とゲート電極46及びゲート絶縁膜45のエッチングのマスクとして用いてもよい。

【0114】

図18(a)は図17の次の工程を示す平面図であり、図18(b)は図18(a)のA−A’における模式断面図であり、図18(c)は図18(a)中のB−B’における模式断面図である。

フィン型の半導体領域42内にイオン注入法を用いてエクステンション領域49を形成する。

エクステンション領域49は、NTrの場合にはそれぞれn型不純物、PTrの場合にはp型不純物を導入する。

さらに、場合によってはエクステンション領域49と異なる導電型の不純物をエクステンション領域49よりも深く注入してもよい。この場合、エクステンション領域49の深さ方向の不純物プロファイルをさらに急峻にすることもできる。

【0115】

図19(a)は図18の次の工程を示す平面図であり、図19(b)は図19(a)のA−A’における模式断面図であり、図19(c)は図19(a)中のB−B’における模式断面図である。

半導体基板上の全面に絶縁膜を形成後、ドライエッチング法を用いてリセスエッチングして、ゲート絶縁膜45、ゲート電極46と第1応力導入層47の側壁にサイドウォール絶縁膜50,51を形成する。

サイドウォール絶縁膜50,51は、例えば20〜100nm程度の厚さで窒化シリコン膜、TEOS、NSG膜及び酸化シリコンをCVD法などによりにて形成することができる。

本実施形態では、サイドウォール絶縁膜50,51は1層で形成されているが、複数の膜を積層して形成することもできる。

その後、エクステンション領域49に接続するように、ソースドレイン領域52を埋め込み絶縁膜41の上面付近までの深さでイオン注入法を用いて形成する。

ソースドレイン領域52は、エクステンション領域49と同型の不純物にて形成する。

その後、エクステンション領域49、ソースドレイン領域52に注入された不純物をアニールにて活性化する。この活性化アニールは、例えば1000〜1100℃程度の急速熱処理(Rapid Thermal Annealing)により行う。

次に、サリサイドプロセス技術により、ソースドレイン領域52の表面に高融点金属シリサイド層53を形成する。これは、例えばTi,Co,Ni,Ptまたはそれらの化合物により、20〜70nm程度の厚さで形成する。

【0116】

図20(a)は図19の次の工程を示す平面図であり、図20(b)は図20(a)のA−A’における模式断面図であり、図20(c)は図20(a)中のB−B’における模式断面図である。

例えばCVD法により基板全面に第2応力導入層54を形成する。第2応力導入層54は、例えば窒化シリコンを200〜300nm程度の膜厚で、フィン型のMOSFETのチャネルの種類に応じて、1.5〜2.0GPa程度の引っ張り応力や圧縮応力を持った膜を形成する。

また、第1応力導入層47とは異なる応力を持った膜を形成する。

【0117】

図21(a)は図20の次の工程を示す平面図であり、図21(b)は図21(a)のA−A’における模式断面図であり、図21(c)は図21(a)中のB−B’における模式断面図である。

第1応力導入層47の上面部が露出するように、例えばCMP法により第2応力導入層54を除去する。

これにより、第2応力導入層54が第1応力導入層47の両脇で切断された構造となる。

以上のようにして、図12に示す構成の本実施形態に係る半導体装置を製造できる。

【0118】

以降の工程としては、例えば、基板全面に層間絶縁膜を堆積し、ソースドレイン領域及びゲート電極に達するコンタクトホールを開口し、プラグを埋め込んで形成し、必要に応じて上層配線を形成する。

【0119】

本発明の半導体装置の製造方法によれば、第1応力導入層と第2応力導入層を形成することにより印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させることができる。

【0120】

<第4実施形態>

[半導体装置の構造]

図22(a)は本実施形態に係る半導体装置の平面図であり、図22(b)は図22(a)中のA−A’における模式断面図であり、図22(c)は図22(a)中のB−B’における模式断面図である。

実質的には第3実施形態と同様の構成であるが、以下の点が異なる。

第3実施形態の半導体装置におけるハードマスク43が除去されている。このため、フィン型のチャネル形成領域をトリプルゲート電極で挟み込んだ構成となっている。

【0121】

本実施形態の半導体装置のMOSFETは、フィン型のMOSFETである。

ここで、本実施形態の半導体装置によれば、チャネル形成領域に異なる応力を印加する第1および第2応力導入層を用い、印加する応力の組み合わせを調整することで、従来例よりもキャリア移動度を向上させることができる。

【0122】

[半導体装置の製造方法]

本実施形態の半導体装置の製造方法について、図23〜30を参照して説明する。

図23(a)は本実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図23(b)は図23(a)中のA−A’における模式断面図であり、図23(c)は図23(a)中のB−B’における模式断面図である。

半導体基板40、埋め込み絶縁膜41および半導体領域42の3層構造を持ったSOI(Silicon On Insulator)基板上に、ハードマスク43を堆積する。その後、フォトリソグラフィー技術や電子線リソグラフィー技術を用いてレジスト膜44を形成する。

次に、レジスト膜44をマスクとしてドライエッチング法などによるエッチングを行い、ハードマスク43をパターンエッチングする。

このとき,例えば半導体基板40はシリコン基板、埋め込み絶縁膜41は50〜100nm程度の酸化シリコンを用いる。

また、半導体領域42としては、30〜80nmのシリコン層を用いる。また、ハードマスク43には、例えば50nm程度の膜厚の窒化シリコンを用いる。

【0123】

図24(a)は図23の次の工程を示す平面図であり、図24(b)は図24(a)中のA−A’における模式断面図であり、図24(c)は図24(a)中のB−B’における模式断面図である。

レジスト膜44を削除した後、ハードマスク43を用いて半導体領域42をドライエッチング処理によりエッチングする。

このとき、埋め込み絶縁膜41の一部も同時にエッチングしておくことで、フィン型の半導体領域42の端部で埋め込み絶縁膜41が凹んだ構造にしておく。

上記により、フィン型の半導体領域42は、半導体基板40の主面から突出した凸状の形状となる。

さらに、ハードマスク43をドライエッチングまたはウェットエッチング処理によりエッチングする。

【0124】

図25(a)は図24の次の工程を示す平面図であり、図25(b)は図25(a)中のA−A’における模式断面図であり、図25(c)は図25(a)中のB−B’における模式断面図である。

半導体基板40上の全面に、ゲート絶縁膜45とゲート電極46を堆積して形成する。

【0125】

図26(a)は図25の次の工程を示す平面図であり、図26(b)は図26(a)中のA−A’における模式断面図であり、図26(c)は図26(a)中のB−B’における模式断面図である。

ゲート電極46の上面からCMP処理を行ってゲート電極46を所定の膜厚に加工する。

次に、ゲート電極46上に第1応力導入層47を形成した後、フォトリソグラフィー技術や電子線リソグラフィー技術を用いてレジスト膜48を形成する。

レジスト膜48をマスクとしてドライエッチング法などのエッチング処理を行うことで、第1応力導入層47をエッチングする。

【0126】

図27(a)は図26の次の工程を示す平面図であり、図27(b)は図27(a)のA−A’における模式断面図であり、図27(c)は図27(a)中のB−B’における模式断面図である。

レジスト膜48を除去した後、第1応力導入層47をマスクとしてドライエッチング法などによりエッチング処理を行い、ゲート電極46とゲート絶縁膜45をエッチングする。

【0127】

図28(a)は図27の次の工程を示す平面図であり、図28(b)は図28(a)のA−A’における模式断面図であり、図28(c)は図28(a)中のB−B’における模式断面図である。

フィン型の半導体領域42内にイオン注入法を用いてエクステンション領域49を形成する。次に、ゲート絶縁膜45、ゲート電極46と第1応力導入層47の側壁にサイドウォール絶縁膜50,51を形成する。

その後、エクステンション領域49に接続するように、ソースドレイン領域52を埋め込み絶縁膜41の上面付近までの深さでイオン注入法を用いて形成する。

次に、サリサイドプロセス技術により、ソースドレイン領域52の表面に高融点金属シリサイド層53を形成する。

【0128】

図29(a)は図28の次の工程を示す平面図であり、図29(b)は図29(a)のA−A’における模式断面図であり、図29(c)は図29(a)中のB−B’における模式断面図である。

例えばCVD法により基板全面に第2応力導入層54を形成する。

【0129】

図30(a)は図29の次の工程を示す平面図であり、図30(b)は図30(a)のA−A’における模式断面図であり、図30(c)は図30(a)中のB−B’における模式断面図である。

第1応力導入層47の上面部が露出するように、例えばCMP法により第2応力導入層54を除去する。

これにより、第2応力導入層54が第1応力導入層47の両脇で切断された構造となる。

以上のようにして、図22に示す構成の本実施形態に係る半導体装置を製造できる。

【0130】

以降の工程としては、例えば、基板全面に層間絶縁膜を堆積し、ソースドレイン領域及びゲート電極に達するコンタクトホールを開口し、プラグを埋め込んで形成し、必要に応じて上層配線を形成する。

【0131】

本発明の半導体装置の製造方法によれば、第1応力導入層と第2応力導入層を形成することにより印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させることができる。

【0132】

本実施形態の半導体装置及びその製造方法では、ゲート電極上に第1応力導入層を配置して、半導体基板上でゲート電極と第1応力導入層が形成されていない領域に第2応力導入層を形成する。

これにより、第2応力導入層がゲート電極端で切断された構造となる。このため、ゲート電極端部の半導体基板内へ効果的に応力を印加することができる。

また、第2応力導入層が切断された構造になっているため、ゲート電極材料の薄膜化を行っても、第1応力導入層の膜厚を調整することで第2応力導入層の膜厚を厚くすることができる。これにより、第2応力導入層からチャネル形成領域に印加される応力の緩和を防ぐことができる。

さらに,第1応力導入層と第2応力導入層で異なる応力を有する材料を用いることにより、ゲート電極のゲート長方向(longitudinal方向)と基板に垂直な方向(vertical方向)に異なる応力を印加することができる。

これにより、FET構造、チャネルの種類、基板の面方位、チャネル方向に最適な応力印加が可能となり、キャリア移動度の向上効果を高めることができる。

【0133】

本発明は上記の説明に限定されない。

例えば、実施形態においてはNTrまたはPTrを有する半導体装置を説明しているが、これに限らず、両者を有するCMOS構成であってもよい。

その他、本発明の要旨を逸脱しない範囲で、種々の変更が可能である。

【符号の説明】

【0134】

10…半導体基板、11…第3応力導入層、12…エクステンション領域、13…ソースドレイン領域、14…高融点金属シリサイド層、20…ゲート絶縁膜、20a…ダミーゲート絶縁膜、21…ゲート電極、21a…ダミーゲート電極、22…第1応力導入層、22a…オフセット膜、23…ダミーサイドウォール絶縁膜、24…第1サイドウォール絶縁膜、25…第2サイドウォール絶縁膜、26…第2応力導入層、27…第1層間絶縁膜、28…第2層間絶縁膜、29…プラグ、30…上層配線、31…ゲート絶縁膜、32…ゲート電極、33…第1応力導入層、40…半導体基板、41…埋め込み絶縁膜、42…半導体領域、43…ハードマスク、44…レジスト膜、45…ゲート絶縁膜、46…ゲート電極、47…第1応力導入層、48…レジスト膜、49…エクステンション領域、50,51…サイドウォール絶縁膜、52…ソースドレイン領域、53…高融点金属シリサイド層、54…第2応力導入層、TR…ゲート電極用溝

【技術分野】

【0001】

本発明は半導体装置及びその製造方法に関し、特に、金属―絶縁膜(酸化膜)―半導体電界効果トランジスタを有する半導体装置及びその製造方法に関するものである。

【背景技術】

【0002】

金属−酸化膜(絶縁膜)−半導体電界効果トランジスタ(metal-oxide(insulator)-semiconductor field effect transistor、MOSFETあるいはMISFET、以下代表してMOSFETと称する)は、半導体装置の基本的な素子である。

MOSFETは、半導体装置の小型化及び高集積化を進めるにつれてますます微細化されてきている。

【0003】

同一基板上にnチャネルMOSFET(以下NTrとも称する)とpチャネルMOSFET(以下PTrとも称する)を有する構成は、一般にCMOS(Complementary MOS)回路と呼ばれている。

CMOS回路は、消費電力が少なく、また微細化や高集積化が容易で高速動作が可能であることから、多くのLSIを構成するデバイスとして広く用いられている。

【0004】

近年の半導体集積回路では、回路を構成するトランジスタの駆動能力の向上を目的として、応力導入層を用いてトランジスタのチャネル形成領域へ応力を印加することにより、キャリアの移動度を高くする技術が盛んに用いられている。

【0005】

また、チャネル形成領域の形状をフィン(Fin)型にしたフィン型MOSFETが知られている。フィン型に対して、半導体基板上に形成される従来の構成のMOSFETはプレーナー型と称せられる。

フィン型MOSFETは、フィン型のチャネル形成領域をダブルゲート電極あるいはトリプルゲート電極で挟み込んだ構成であり、完全空乏化が可能であり、短チャネル特性やサブスレッショルド特性を向上させることができる。

【0006】

近年の半導体装置では、ゲート長の縮小に伴い、エッチング後のゲート電極形状やゲート長のばらつきが悪化している。これらを改善するため、ゲート電極材料の薄膜化が進んでいる。

そのため、特許文献1の従来技術のように、ゲート電極を覆うように応力導入層が配置された構造では、ゲート電極の薄膜化に伴い、応力導入層が平坦化されていく傾向にある。

【0007】

一方、応力導入層はゲート電極やパターニングなどによりその平坦性が途切れることで、チャネル形成領域へ応力を局在化させる効果が得られることが報告されている。

そのため、ゲート電極材料の薄膜化により、応力導入層からチャネル形成領域へ印加される応力が低下しており、トランジスタの駆動能力向上効果が低下している。

【0008】

図31は従来例に係るプレーナー型のMOSFETの断面図である。

例えば、シリコン基板などからなる半導体基板110上にゲート絶縁膜120が形成されている。

ゲート絶縁膜120の上層にポリシリコンなどからなるゲート電極121が形成されている。

ゲート電極121の両側部に窒化シリコンなどからなる第1サイドウォール絶縁膜122及び第2サイドウォール絶縁膜123が形成されている。

【0009】

例えば、ゲート電極121の両側部における半導体基板110の表層部においてゲート電極121の下方まで至るエクステンション領域111が形成されている。

また、第2サイドウォール絶縁膜123の両側部における半導体基板110の表層部において、エクステンション領域111に接続してソースドレイン領域112が形成されている。

ゲート電極121の表面にNiSiなどの高融点金属シリサイド層124が形成されている。また、ソースドレイン領域112の表面においても高融点金属シリサイド層113が形成されている。

上記のようにして、MOSFETが形成されている。

【0010】

例えば、MOSFETを被覆して全面に窒化シリコンなどからなる応力導入層130が形成されている。

応力導入層130の上層に酸化シリコンなどからなる層間絶縁膜131が形成されている。

【0011】

上記の構成において、応力導入層130はゲート電極121とその両側部に配置された第2サイドウォール絶縁膜123の脇で屈曲した形状となっている。

この形状により、ゲート電極121の端部近傍にて半導体基板110の内部へ応力が印加され、キャリア移動度が向上する。

【0012】

ところが、ゲート電極121を薄膜化すると、応力導入層130の曲がり方が小さくなり、応力導入層130が平坦化されてしまう。

そのため、ゲート電極121の端部近傍において半導体基板110の内部へ印加される応力が小さくなってしまう。

【0013】

特許文献2及び特許文献3に報告されているダブルゲート電極あるいはトリプルゲート電極を有するフィン型のMOSFETでは、応力導入層を用いることによるキャリア移動度の向上が実現されていない。

【0014】

上記のフィン型のMOSFETに対して、図31に示すプレーナー型のMOSFETと同様にゲート電極を覆うように応力導入層を適用しても、上記と同様にゲート電極の薄膜化に伴いフィン型のチャネルへ印加される応力が低下してしまう問題が生じる。

【0015】

応力の印加によるキャリア移動度の変化は、ピエゾ係数を用いて以下の式(1)で示される。

【0016】

[数1]

…(1)

【0017】

ここで、μxxは応力印加後のキャリア移動度、μ0は応力印加前のキャリア移動度である。Sxx,Syy,Szzは、それぞれゲート長方向(longitudinal方向)L、ゲート幅方向(transverse方向)Tおよび基板に垂直な方向(vertical方向)Vに印加される応力である。πl,πt,πvは、それぞれゲート長方向(longitudinal方向)L、ゲート幅方向(transverse方向)Tおよび基板に垂直な方向(vertical方向)Vのピエゾ係数である。

【0018】

図32及び図33は、それぞれプレーナー型のMOSFETおよびフィン型のMOSFETのチャネル形成領域における応力の方向を示す模式的斜視図である。

図32において、半導体基板SUB上に不図示のゲート絶縁膜を介してゲート電極Gが形成されており、ゲート電極Gの両側部における半導体基板SUBの表層部にソースドレイン領域SDが形成されている。

図33において、フィン型の半導体領域Fの上面及び側面Sを被覆して不図示のゲート絶縁膜を介してゲート電極Gが形成されており、ゲート電極Gの両側部におけるフィン型の半導体領域Fに接続してソースドレイン領域SDが形成されている。

【0019】

表1及び表2は、非特許文献2及び非特許文献3にて報告されているプレーナー型のMOSFETおよびフィン型のMOSFETにおける各ピエゾ係数をまとめたものである。

【0020】

【表1】

【0021】

【表2】

【0022】

表1及び表2より、チャネルの種類および面方位、チャネル方向により、πlとπvの符号が異なることがわかる。

これは、ゲート長方向(longitudinal方向)Lと基板に垂直な方向(vertical方向)Vで異なる応力を印加するとキャリア移動度の向上効果が高くなることを表している。

【先行技術文献】

【特許文献】

【0023】

【特許文献1】特開2002−198368号公報

【特許文献2】特開2006−13303号公報

【特許文献3】特開2006−517060号公報

【非特許文献】

【0024】

【非特許文献1】D.Kosemura et al.、 “Characterization of Strain for High Performance MOSFETs”, SSDM, pp.390, (2007)

【非特許文献2】S.E. Thompson et al., “Uniaxial-Process-Induced Strained-Si: Extending the CMOS Roadmap”, IEEE Trans. Electron. Device, Vol. 53, pp.1010 (2006)

【非特許文献3】M. Saitoh et al., “Three-Dimensional Stress Engineering in FinFETs for Mobility/On-Current Enhancement and Gate Current Reduction”, Symp. On VLSI, pp. 18 (2008)

【発明の概要】

【発明が解決しようとする課題】

【0025】

解決しようとする課題は、チャネル形成領域に印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させることである。

【課題を解決するための手段】

【0026】

本発明の半導体装置は、チャネル形成領域を有する半導体基板と、前記チャネル形成領域において前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜の上層に形成されたゲート電極と、前記ゲート電極の上層に形成され、前記チャネル形成領域に応力を印加する第1応力導入層と、前記ゲート電極及び前記第1応力導入層の両側部における前記半導体基板の表層部に形成されたソースドレイン領域と、少なくとも前記第1応力導入層の領域を除き、前記ソースドレイン領域の上層に形成され、前記チャネル形成領域に前記第1応力導入層と異なる応力を印加する第2応力導入層とを有する。

【0027】

上記の本発明の半導体装置は、チャネル形成領域を有する半導体基板上にゲート絶縁膜が形成され、ゲート絶縁膜の上層にゲート電極が形成され、ゲート電極の上層にチャネル形成領域に応力を印加する第1応力導入層が形成されている。ゲート電極及び第1応力導入層の両側部における半導体基板の表層部にソースドレイン領域が形成されている。また、少なくとも第1応力導入層の領域を除き、ソースドレイン領域の上層に、チャネル形成領域に第1応力導入層と異なる応力を印加する第2応力導入層が形成されている。

【0028】

また、本発明の半導体装置の製造方法は、チャネル形成領域を有する半導体基板の前記チャネル形成領域において前記半導体基板上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜の上層にゲート電極を形成する工程と、前記ゲート電極の上層に、前記チャネル形成領域に応力を印加する第1応力導入層を形成する工程と、前記ゲート電極及び前記第1応力導入層の両側部における前記半導体基板の表層部にソースドレイン領域を形成する工程と、少なくとも前記第1応力導入層の領域を除き、前記ソースドレイン領域の上層に、前記チャネル形成領域に前記第1応力導入層と異なる応力を印加する第2応力導入層を形成する工程とを有し、電界効果トランジスタを形成する。

【0029】

上記の本発明の半導体装置の製造方法は、チャネル形成領域を有する半導体基板のチャネル形成領域において半導体基板上にゲート絶縁膜を形成する。

次に、ゲート絶縁膜の上層にゲート電極を形成し、ゲート電極の上層に、チャネル形成領域に応力を印加する第1応力導入層を形成する。

次に、ゲート電極及び第1応力導入層の両側部における半導体基板の表層部にソースドレイン領域を形成する。

次に、少なくとも第1応力導入層の領域を除き、ソースドレイン領域の上層に、チャネル形成領域に第1応力導入層と異なる応力を印加する第2応力導入層を形成する。

上記のようにして、電界効果トランジスタを形成する。

【0030】

また、本発明の半導体装置の製造方法は、チャネル形成領域を有する半導体基板の前記チャネル形成領域において前記半導体基板上にダミーゲート絶縁膜を形成する工程と、前記ダミーゲート絶縁膜の上層にダミーゲート電極を形成する工程と、前記ダミーゲート電極の上層にオフセット膜を形成する工程と、前記ダミーゲート電極及び前記オフセット膜の両側部における前記半導体基板の表層部にソースドレイン領域を形成する工程と、少なくとも前記オフセット膜の領域を除き、前記ソースドレイン領域の上層に、前記チャネル形成領域に応力を導入する第1応力導入層を形成する工程と、前記オフセット膜、前記ダミーゲート電極及び前記ダミーゲート絶縁膜を除去し、ゲート電極用溝を形成する工程と、前記ゲート電極用溝の底面を被覆してゲート絶縁膜を形成する工程と、前記ゲート絶縁膜の上層に前記ゲート電極用溝の途中の深さまでのゲート電極を形成する工程と、前記ゲート電極の上層に前記ゲート電極用溝を埋め込んで前記チャネル形成領域に前記第1応力導入層と異なる応力を導入する第2応力導入層を形成する工程とを有し、電界効果トランジスタを形成する。

【0031】

上記の本発明の半導体装置の製造方法は、チャネル形成領域を有する半導体基板のチャネル形成領域において半導体基板上にダミーゲート絶縁膜を形成する。

次に、ダミーゲート絶縁膜の上層にダミーゲート電極を形成し、ダミーゲート電極の上層にオフセット膜を形成する。

次に、ダミーゲート電極及びオフセット膜の両側部における半導体基板の表層部にソースドレイン領域を形成する。

次に、少なくともオフセット膜の領域を除き、ソースドレイン領域の上層に、チャネル形成領域に応力を導入する第1応力導入層を形成する。

次にオフセット層、ダミーゲート電極及びダミーゲート絶縁膜を除去し、ゲート電極用溝を形成する。

次に、ゲート電極用溝の底面を被覆してゲート絶縁膜を形成し、ゲート絶縁膜の上層にゲート電極用溝の途中の深さまでのゲート電極を形成する。

次に、ゲート電極の上層にゲート電極用溝を埋め込んでチャネル形成領域に第1応力導入層と異なる応力を導入する第2応力導入層を形成する。

上記のようにして、電界効果トランジスタを形成する。

【発明の効果】

【0032】

本発明の半導体装置は、第1応力導入層と第2応力導入層により印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させることができる。

【0033】

本発明の半導体装置の製造方法によれば、第1応力導入層と第2応力導入層を形成することにより印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させることができる。

【図面の簡単な説明】

【0034】

【図1】図1は本発明の第1実施形態に係る半導体装置の模式断面図である。

【図2】図2(a)〜(c)は本発明の第1実施形態に係る半導体装置の製造方法の製造工程を示す模式断面図である。

【図3】図3(a)及び図3(b)は本発明の第1実施形態に係る半導体装置の製造方法の製造工程を示す模式断面図である。

【図4】図4(a)及び図4(b)は本発明の第1実施形態に係る半導体装置の製造方法の製造工程を示す模式断面図である。

【図5】図5は本発明の第2実施形態に係る半導体装置の模式断面図である。

【図6】図6(a)〜(c)は本発明の第2実施形態の変形例に係る半導体装置の製造方法の製造工程を示す模式断面図である。

【図7】図7(a)及び図7(b)は本発明の第2実施形態の変形例に係る半導体装置の製造方法の製造工程を示す模式断面図である。

【図8】図8(a)〜(c)は本発明の第2実施形態に係る半導体装置の製造方法の製造工程を示す模式断面図である。

【図9】図9(a)〜(c)は本発明の第2実施形態に係る半導体装置の製造方法の製造工程を示す模式断面図である。

【図10】図10は本発明の第1変形例に係る半導体装置の模式断面図である。

【図11】図11は本発明の第2変形例に係る半導体装置の模式断面図である。

【図12】図12(a)は本発明の第3実施形態に係る半導体装置の平面図であり、図12(b)は図12(a)中のA−A’における模式断面図であり、図12(c)は図12(a)中のB−B’における模式断面図である。

【図13】図13(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図13(b)は図13(a)中のA−A’における模式断面図であり、図13(c)は図13(a)中のB−B’における模式断面図である。

【図14】図14(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図14(b)は図14(a)中のA−A’における模式断面図であり、図14(c)は図14(a)中のB−B’における模式断面図である。

【図15】図15(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図15(b)は図15(a)中のA−A’における模式断面図であり、図15(c)は図15(a)中のB−B’における模式断面図である。

【図16】図16(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図16(b)は図16(a)中のA−A’における模式断面図であり、図16(c)は図16(a)中のB−B’における模式断面図である。

【図17】図17(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図17(b)は図17(a)中のA−A’における模式断面図であり、図17(c)は図17(a)中のB−B’における模式断面図である。

【図18】図18(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図18(b)は図18(a)中のA−A’における模式断面図であり、図18(c)は図18(a)中のB−B’における模式断面図である。

【図19】図19(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図19(b)は図19(a)中のA−A’における模式断面図であり、図19(c)は図19(a)中のB−B’における模式断面図である。

【図20】図20(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図20(b)は図20(a)中のA−A’における模式断面図であり、図20(c)は図20(a)中のB−B’における模式断面図である。

【図21】図21(a)は本発明の第3実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図21(b)は図21(a)中のA−A’における模式断面図であり、図21(c)は図21(a)中のB−B’における模式断面図である。

【図22】図22(a)は本発明の第4実施形態に係る半導体装置の平面図であり、図22(b)は図22(a)中のA−A’における模式断面図であり、図22(c)は図22(a)中のB−B’における模式断面図である。

【図23】図23(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図23(b)は図23(a)中のA−A’における模式断面図であり、図23(c)は図23(a)中のB−B’における模式断面図である。

【図24】図24(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図24(b)は図24(a)中のA−A’における模式断面図であり、図24(c)は図24(a)中のB−B’における模式断面図である。

【図25】図25(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図25(b)は図25(a)中のA−A’における模式断面図であり、図25(c)は図25(a)中のB−B’における模式断面図である。

【図26】図26(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図26(b)は図26(a)中のA−A’における模式断面図であり、図26(c)は図26(a)中のB−B’における模式断面図である。

【図27】図27(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図27(b)は図27(a)中のA−A’における模式断面図であり、図27(c)は図27(a)中のB−B’における模式断面図である。

【図28】図28(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図28(b)は図28(a)中のA−A’における模式断面図であり、図28(c)は図28(a)中のB−B’における模式断面図である。

【図29】図29(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図29(b)は図29(a)中のA−A’における模式断面図であり、図29(c)は図29(a)中のB−B’における模式断面図である。

【図30】図30(a)は本発明の第4実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図30(b)は図30(a)中のA−A’における模式断面図であり、図30(c)は図30(a)中のB−B’における模式断面図である。

【図31】図31は従来例に係るプレーナー型のMOSFETの断面図である。

【図32】図32はプレーナー型のMOSFETのチャネル形成領域における応力の方向を示す模式的斜視図である。

【図33】図33はフィン型のMOSFETのチャネル形成領域における応力の方向を示す模式的斜視図である。

【発明を実施するための形態】

【0035】

以下に、本発明の半導体装置及びその製造方法の実施の形態について、図面を参照して説明する。

【0036】

尚、説明は以下の順序で行う。

1.第1実施形態(プレーナー型MOSFETにおいてゲートファーストでゲートを形成した構成)

2.第2実施形態(プレーナー型MOSFETにおいてゲートラストでゲートを形成した構成)

3.第1変形例(ゲート電極が全て高融点金属シリサイド化された構成)

4.第2変形例(ゲート電極が全て高融点金属シリサイド化された構成)

5.第3実施形態(フィン型MOSFETにおいてフィン型半導体領域の2面にゲート電極を有する構成)

6.第4実施形態(フィン型MOSFETにおいてフィン型半導体領域の3面にゲート電極を有する構成)

【0037】

<第1実施形態>

[半導体装置の構造]

図1は本実施形態に係る半導体装置の模式断面図である。

例えば、シリコン基板などからなる半導体基板10上にゲート絶縁膜20が形成されている。

ゲート絶縁膜20の上層にポリシリコンなどからなるゲート電極21が形成されている。

ゲート電極21の上層に第1応力導入層22が形成されている。

ゲート電極21及び第1応力導入層22の両側部に窒化シリコンなどからなる第1サイドウォール絶縁膜24及び第2サイドウォール絶縁膜25が形成されている。

【0038】

例えば、ゲート電極21及び第1応力導入層22の両側部における半導体基板10の表層部においてゲート電極21の下方まで至るエクステンション領域12が形成されている。

また、第2サイドウォール絶縁膜25の両側部における半導体基板10の表層部において、エクステンション領域12に接続してソースドレイン領域13が形成されている。

ソースドレイン領域13の表面において高融点金属シリサイド層14が形成されている。

上記のようにして、MOSFETが形成されている。

【0039】

例えば、第1応力導入層22の形成領域を除いて、MOSFETを被覆して全面に窒化シリコンなどからなる第2応力導入層26が形成されている。より具体的には、第2応力導入層26は第1応力導入層22の上部領域には形成されておらず、第1応力導入層22とゲート電極21の両側部に第2応力導入層26が形成されている。

例えば、第2応力導入層26の上層に酸化シリコンなどからなる不図示の層間絶縁膜が形成され、ゲート電極21及びソースドレイン領域13に対するコンタクトホールが開口され、コンタクトプラグが埋め込まれ、上層配線に接続されている。

【0040】

上記の構成において、第1応力導入層22は、ゲート電極21の上層に形成されている。第1応力導入層22は、チャネル形成領域に応力を導入する。

一方、第2応力導入層26は、少なくとも第1応力導入層22の領域を除き、ソースドレイン領域13の上層に形成されている。

第2応力導入層26は、チャネル形成領域に第1応力導入層と異なる応力を導入する。

【0041】

また、エクステンション領域12及びソースドレイン領域13の一部または全部を含む領域において、SiCあるいはSiGeなどからなる第3応力導入層11が形成されている。第3応力導入層11は、チャネル形成領域に応力を導入する。

【0042】

半導体基板10は,例えばシリコン(Si)基板が用いられる。

ゲート絶縁膜20は、例えば1〜3nm程度の酸化ハフニウム(HfO2)、酸化アルミニウムハフニウム(HfAlO2)、酸化シリコンハフニウム(HfSiO)、酸化タンタル(Ta2O5)、酸化アルミニウム(Al2O3)、酸化ジルコニウム(ZrO2)などのいわゆる高誘電率(High−k)膜を用いることができる。また、酸化シリコン(SiO2)および酸窒化シリコン(SiON)などを用いることができる。さらに、各膜を積層にして用いることもできる。

【0043】

ゲート電極21は、30〜100nm程度の厚さを持つポリシリコン層、金属層、金属化合物層を用いることができる。

金属層や金属化合物層としては,窒化チタン(TiN)、チタン(Ti)、チタンシリコン(TiSi)、ニッケル(Ni)、ニッケルシリコン(NiSi)、ハフニウム(Hf)、ハフニウムシリコン(HfSi)、タングステン(W)、タンタル(Ta)、タンタルシリコン(TaSi)、窒化タンタルシリコン(TaSiN)、コバルト(Co)、コバルトシリコン(CoSi)、ルテニウム(Ru)、あるいはインジウム(In)などを用いることができる。

しきい値電圧や抵抗値の調整のために,これらの膜を積層して用いることができる。

また,酸化アルミニウム(AlO)あるいは酸化ランタン(LaO)などと前述の金属層や金属化合物層を積層にすることでしきい値電圧の調整を行うこともできる。また、前述の金属層や金属化合物層により、チャネルの種類に応じて応力を印加することもできる。

【0044】

第1応力導入層22は、例えば窒化シリコンを30〜100nm程度の膜厚で用いることができる。NTrの場合は2.0GPa程度の圧縮応力を持った膜、PTrの場合は1.5GPa程度の引っ張り応力を持った膜を用いることができる。

なお、本実施形態では記載していないが,第1応力導入層22の上部または下部に第1応力導入層22と異なる絶縁膜を積層してもよい。

【0045】

第1サイドウォール絶縁膜24及び第2サイドウォール絶縁膜25は、それぞれ酸化シリコンあるいは窒化シリコン膜などを単層であるいは積層して用いることができる。それぞれ、例えば2〜10nmおよび20〜60nm程度の厚さに形成されている。

また、ゲート容量を低減するために、配線絶縁膜などに用いられるいわゆる低誘電率(Low−k)膜を用いることもできる。

【0046】

半導体基板10のチャネル形成領域とエクステンション領域12には、NTrの場合にはそれぞれp型不純物とn型不純物、PTrの場合にはそれぞれn型不純物とp型不純物が導入される。

例えば、n型不純物としてはリン(P)あるいはヒ素(As)などが用いられる。p型不純物としては、ホウ素(B)、フッ化ボロン(BF2)あるいは(In)などを用いることができる。

場合によっては、エクステンション領域12と異なる導電型の不純物をエクステンション領域12よりも深く注入した構成としてもよい。この場合、エクステンション領域12の深さ方向の不純物プロファイルをさらに急峻にすることができる。

【0047】

ソースドレイン領域13にはエクステンション領域12と同じ導電型の不純物が導入されている。

本実施形態においては、エクステンション領域12及びソースドレイン領域13の一部または全部が第3応力導入層11中に形成されているが、第3応力導入層11が形成されていない構成でもよい。

第3応力導入層11は、炭素(C)あるいはゲルマニウム(Ge)などとシリコンの化合物からなり、30〜100nm程度の厚さで形成されている。半導体基板10のチャネル形成領域に印加したい応力に応じてCとGeの含有量を調整することができる。

【0048】

高融点金属シリサイド層14は、例えばTi,Co,Ni,Ptまたはそれらの化合物からなり、20〜70nm程度の厚さで形成されている。

【0049】

第2応力導入層26は、第2サイドウォール絶縁膜25と高融点金属シリサイド層14を覆うように形成されており、第1応力導入層22と第2サイドウォール絶縁膜25の両端で切断された形状になっている。

第2応力導入層26は、例えば窒化シリコンを80〜200nm程度の膜厚で、NTrの場合は1.6GPa程度の引っ張り応力を持った膜が用いられ、PTrの場合は2.0GPa程度の圧縮応力を持った膜が用いられる。

【0050】

上記のように、ゲート電極21上に第1応力導入層22が形成され、第1応力導入層22の領域を除く領域における半導体基板10上が第2応力導入層26で被覆された構造となっている。これにより、第2応力導入層26がゲートの端部で切断された構造となる。

また、第1応力導入層22と第2応力導入層26で異なる応力を有する材料が用いられている。

【0051】

非特許文献1によると、応力導入層が切断されると、切断された応力導入層の端部の半導体基板上に応力が局在化されることが報告されている。

本実施形態では、第2応力導入層26がゲートの端部で切断された構造となっており、ゲートの端部において効果的にチャネル形成領域へ応力印加を行うことができる。

【0052】

さらに、ゲート電極の薄膜化を行っても、第1応力導入層22の膜厚を調整することで、第2応力導入層26の膜厚を厚くすることができるため、第2応力導入層26からチャネル形成領域に印加される応力の緩和が起こらない。

【0053】

本実施形態の半導体装置によれば、チャネル形成領域に異なる応力を印加する第1および第2応力導入層を用い、印加する応力の組み合わせを調整することで、従来例よりもキャリア移動度を向上させることができる。

【0054】

[半導体装置の製造方法]

本実施形態の半導体装置の製造方法について、図2〜4を参照して説明する。

まず、図2(a)に示すように、例えば半導体基板10上にゲート絶縁膜20、ゲート電極21及び第1応力導入層22を積層する。

次に、フォトリソグラフィー技術や電子線リソグラフィー技術を用いてレジストパターンを形成し、そのレジストパターンをマスクとしてドライエッチングなどを行い、ゲート絶縁膜20、ゲート電極21及び第1応力導入層22をパターン加工する。

なお、図面上に明示されていないが、ゲート絶縁膜20を形成する前に、半導体基板10中に素子分離領域を形成し、イオン注入法にて不純物を導入してウェル領域を形成しておいてもよい。

【0055】

ゲート絶縁膜20は、例えば1〜3nm程度の1〜3nm程度の酸化ハフニウム(HfO2)、酸化アルミニウムハフニウム(HfAlO2)、酸化シリコンハフニウム(HfSiO)、酸化タンタル(Ta2O5)、酸化アルミニウム(Al2O3)、酸化ジルコニウム(ZrO2)などのいわゆる高誘電率(High−k)膜により形成する。また、酸化シリコン(SiO2)および酸窒化シリコン(SiON)などを用いることができる。さらに、各膜を積層にして用いることもできる。その形成方法は、熱酸化プロセス、化学気相成長法(CVD法)、あるいは物理気相成長法(PVD法)などを用いることができる。

【0056】

ゲート電極21は、例えばCVD法、ALD(Atomic Layer Deposition)法あるいはPVD法により、50〜100nm程度の厚さを持つポリシリコン層、金属層、金属化合物層を堆積して形成する。

金属層や金属化合物層としては,窒化チタン(TiN)、チタン(Ti)、チタンシリコン(TiSi)、ニッケル(Ni)、ニッケルシリコン(NiSi)、ハフニウム(Hf)、ハフニウムシリコン(HfSi)、タングステン(W)、タンタル(Ta)、タンタルシリコン(TaSi)、窒化タンタルシリコン(TaSiN)、コバルト(Co)、コバルトシリコン(CoSi)、ルテニウム(Ru)、あるいはインジウム(In)などを用いることができる。

しきい値電圧や抵抗値の調整のために、これらの膜を積層してもよい。また、酸化アルミニウム(AlO)あるいは酸化ランタン(LaO)などと前述の金属層や金属化合物層を積層にすることもできる。また、前述の金属層や金属化合物層により、チャネルの種類に応じて応力を印加することもできる。

【0057】

第1応力導入層22は、例えば窒化シリコンを30〜100nm程度の膜厚で用いることができる。NTrの場合は2.0GPa程度の圧縮応力を持った膜、PTrの場合は1.5GPa程度の引っ張り応力を持った膜を用いることができる。

【0058】

次に、図2(b)に示すように、絶縁膜を基板全面に形成した後、ドライエッチング法などによりリセスエッチングして、ゲート絶縁膜20、ゲート電極21、第1応力導入層22の側壁部のみにダミーサイドウォール絶縁膜23を形成する。

ダミーサイドウォール絶縁膜23の形成には、まず、例えば50〜150nm程度の窒化シリコン膜、酸化シリコン、TEOS(原料ガスにtetraethylorthosilicateを用いた酸化シリコン膜)、NSG膜をCVD法などにより形成する。

その後、ドライエッチング法などにより全面にリセスエッチングする。この時、半導体基板10に対して第1応力導入層22とダミーサイドウォール絶縁膜23の選択比を高くすることで,半導体基板10を選択的にエッチングできる。

また、素子分離領域を形成している場合は、素子分離領域材料との選択比もできるだけ高くしておくことが望ましい。

上記により、半導体基板10に50〜100nm程度の溝を形成する。

【0059】

その後、半導体基板10のエッチングした領域内へ選択的に第3応力導入層11を形成する。第3応力導入層11は、例えば、圧縮応力を導入する際にはシリコンゲルマニウム(SiGe)、引っ張り応力を導入する際には炭化シリコン(SiC)を選択エピタキシャル成長法にて50〜200nm程度の膜厚で形成する。

さらに、第3応力導入層11を形成する際には、ソースドレイン領域を形成することを目的として、不純物を導入しておいてもよい。例えば、NTrの場合にはn型不純物を導入し、PTrの場合にはそれぞれp型不純物を導入しておく。

【0060】

次に、図2(c)に示すように、ダミーサイドウォール絶縁膜23をウェットエッチング法にて除去する。

次に、絶縁膜を基板全面に形成した後、ドライエッチング法などによりリセスエッチングして、ゲート絶縁膜20、ゲート電極21、第1応力導入層22の側壁部のみに第1サイドウォール絶縁膜24を形成する。

第1サイドウォール絶縁膜24の形成には、まず、例えば2〜10nm程度の窒化シリコン膜、酸化シリコン、TEOS、NSG膜をCVD法などにより形成する。その後、ドライエッチング法などにより全面にリセスエッチングする。

【0061】

本実施形態では第1サイドウォール絶縁膜24を形成しているが、不要であれば形成しなくてもよい。また、ダミーサイドウォール絶縁膜23を除去せずに、そのまま残して第1サイドウォール絶縁膜24として用いてもよい。

【0062】

その後、イオン注入法により不純物をイオン注入してエクステンション領域12を形成する。

エクステンション領域12は、NTrの場合にはそれぞれn型不純物を、PTrの場合にはp型不純物を導入して形成する。

さらに、場合によってはエクステンション領域12と異なる導電型の不純物をエクステンション領域12よりも深く注入してもよい。この場合、エクステンション領域12の深さ方向の不純物プロファイルをさらに急峻にすることもできる。

【0063】

次に、図3(a)に示すように、絶縁膜を基板全面に形成した後、ドライエッチング法などによりリセスエッチングして、第1サイドウォール絶縁膜24の側壁部のみに第2サイドウォール絶縁膜25を形成する。

第2サイドウォール絶縁膜25の形成には、まず、例えば20〜60nm程度の窒化シリコン膜、酸化シリコン、TEOS、NSG膜をCVD法などにより形成する。その後、ドライエッチング法などにより全面にリセスエッチングする。

【0064】

本実施形態では第2サイドウォール絶縁膜25を単層構成で形成しているが、複数層を積層した構成としてもよい。

【0065】

その後、イオン注入法により不純物をイオン注入してソースドレイン領域13を形成する。

ソースドレイン領域13は、エクステンション領域12と同じ導電型の不純物にて形成する。

その後、エクステンション領域12及びソースドレイン領域13に注入された不純物をアニール処理により活性化する。この活性化アニール処理は、例えば1000〜1100℃度程度の急速熱処理(Rapid Thermal Annealing)により行う。

【0066】

次に、サリサイドプロセス技術により、ソースドレイン領域13の表面に高融点金属シリサイド層14を形成する。これは、例えばTi,Co,Ni,Ptまたはそれらの化合物により、20〜70nm程度の厚さで形成する。

【0067】

次に、図3(b)に示すように、例えばCVD法により基板全面に第2応力導入層26と層間絶縁膜27を形成する。

第2応力導入層26としては、例えば窒化シリコンを200〜300nm程度の膜厚で形成し、チャネルの種類に応じて1.5〜2.0GPa程度の引っ張り応力や圧縮応力を持った膜を形成する。

また、層間絶縁膜27としては,例えばTEOSやNSG膜などを用いることができる。さらに、場合によっては第2応力導入層26のみを形成し、層間絶縁膜27を形成しないこともある。

【0068】

次に、図4(a)に示すように、第1応力導入層22の上面部が露出するように、第2応力導入層26と層間絶縁膜27を除去する。例えば、CMP(Chemical Mechanical Polishing)法によりそれぞれの膜を研磨除去する。

これにより、第2応力導入層26が第1応力導入層22の両脇で切断された構造となる。

以上のようにして、図1に示す構成の本実施形態に係る半導体装置を製造できる。

【0069】

以降の工程としては、例えば図4(b)に示すように、基板全面に第2層間絶縁膜28を堆積し、ソースドレイン領域及びゲート電極に達するコンタクトホールCHを開口し、プラグ29を埋め込んで形成し、必要に応じて上層配線30を形成する。

【0070】

本発明の半導体装置の製造方法によれば、第1応力導入層と第2応力導入層を形成することにより印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させることができる。

【0071】

<第2実施形態>

[半導体装置の構造]

図5は本実施形態に係る半導体装置の模式断面図である。

実質的には第1実施形態と同様の構成であるが、以下の点が異なる。

第1実施形態の半導体装置におけるゲート絶縁膜20、ゲート電極21及び第1応力導入層22が除去されてゲート電極用溝TRが形成されており、ゲート電極用溝TR内にゲート絶縁膜31、ゲート電極32及び第1応力導入層33が埋め込まれている。

【0072】

ゲート絶縁膜31は、ゲート電極用溝TRの底面とゲート電極用溝TRの途中の深さまでの側面を被覆して形成されており、ゲート電極32はゲート絶縁膜31が形成された深さまで形成されている。

ゲート電極32の上層において、ゲート電極用溝TRを埋め込んで、第1応力導入層33が形成されている。

【0073】

本実施形態の半導体装置によれば、チャネル形成領域に異なる応力を印加する第1および第2応力導入層を用い、印加する応力の組み合わせを調整することで、従来例よりもキャリア移動度を向上させることができる。

【0074】

[半導体装置の製造方法]

本実施形態の半導体装置の製造方法について、図6〜9を参照して説明する。

まず、図6(a)に示すように、例えば半導体基板10上にダミーゲート絶縁膜20a、ダミーゲート電極21a及びハードマスクとなるオフセット膜22aを積層する。

次に、フォトリソグラフィー技術や電子線リソグラフィー技術を用いてレジストパターンを形成し、そのレジストパターンをマスクとしてドライエッチングなどを行う。これにより、ダミーゲート絶縁膜20a、ダミーゲート電極21a及びオフセット膜22aをパターン加工する。そのレジストパターンをマスクとしてオフセット膜22aのパターン加工を行い、オフセット膜22aをハードマスクとしてダミーゲート絶縁膜20aとダミーゲート電極21aをパターン加工してもよい。

なお、図面上に明示されていないが、ダミーゲート絶縁膜20aを形成する前に、半導体基板10中に素子分離領域を形成し、イオン注入法にて不純物を導入してウェル領域を形成しておいてもよい。

【0075】

ダミーゲート絶縁膜20aは、例えば1〜3nm程度の例えば1〜3nm程度の酸化シリコン(SiO2)および酸窒化シリコン(SiON)などを用いることができる。その形成方法は、熱酸化プロセス、化学気相成長法(CVD法)、あるいは物理気相成長法(PVD法)などを用いることができる。

【0076】

ダミーゲート電極21aは、例えばCVD法あるいはPVD法により、30〜100nm程度の厚さを持つポリシリコン層を堆積して形成する。

【0077】

オフセット膜22aは、例えばCVD法により酸化シリコンを30〜100nm程度の膜厚で形成することができる。

【0078】

次に、図6(b)に示すように、絶縁膜を基板全面に形成した後、ドライエッチング法などによりリセスエッチングして、ダミーゲート絶縁膜20a、ダミーゲート電極21a、オフセット膜22aの側壁部のみにダミーサイドウォール絶縁膜23を形成する。

ダミーサイドウォール絶縁膜23の形成には、まず、例えば50〜150nm程度の窒化シリコン膜、酸化シリコン、TEOS(原料ガスにtetraethylorthosilicateを用いた酸化シリコン膜)、NSG膜をCVD法などにより形成する。

その後、ドライエッチング法などにより全面にリセスエッチングする。この時、半導体基板10に対してオフセット膜22aとダミーサイドウォール絶縁膜23の選択比を高くすることで、半導体基板10を選択的にエッチングできる。

また、素子分離領域を形成している場合は、素子分離領域材料との選択比もできるだけ高くしておくことが望ましい。

上記により、半導体基板10に50〜100nm程度の溝を形成する。

【0079】

その後、半導体基板10のエッチングした領域内へ選択的に第3応力導入層11を形成する。第3応力導入層11は、例えば、圧縮応力を導入する際にはシリコンゲルマニウム(SiGe)、引っ張り応力を導入する際には炭化シリコン(SiC)を選択エピタキシャル成長法にて50〜200nm程度の膜厚で形成する。

さらに、第3応力導入層11を形成する際には、ソースドレイン領域を形成することを目的として、不純物を導入しておいてもよい。例えば、NTrの場合にはn型不純物を導入し、PTrの場合にはそれぞれp型不純物を導入しておく。

【0080】

次に、図6(c)に示すように、ダミーサイドウォール絶縁膜23をウェットエッチング法にて除去する。

次に、絶縁膜を基板全面に形成した後、ドライエッチング法などによりリセスエッチングして、ダミーゲート絶縁膜20a、ダミーゲート電極21a、オフセット膜22aの側壁部のみに第1サイドウォール絶縁膜24を形成する。

第1サイドウォール絶縁膜24の形成には、まず、例えば2〜10nm程度の窒化シリコン膜、酸化シリコン、TEOS、NSG膜をCVD法などにより形成する。その後、ドライエッチング法などにより全面にリセスエッチングする。

【0081】

本実施形態では第1サイドウォール絶縁膜24を形成しているが、不要であれば形成しなくてもよい。また、ダミーサイドウォール絶縁膜23を除去せずに、そのまま残して第1サイドウォール絶縁膜24として用いてもよい。

【0082】

その後、イオン注入法により不純物をイオン注入してエクステンション領域12を形成する。

エクステンション領域12は、NTrの場合にはそれぞれn型不純物を、PTrの場合にはp型不純物を導入して形成する。

さらに、場合によってはエクステンション領域12と異なる導電型の不純物をエクステンション領域12よりも深く注入してもよい。この場合、エクステンション領域12の深さ方向の不純物プロファイルをさらに急峻にすることもできる。

【0083】

次に、図7(a)に示すように、絶縁膜を基板全面に形成した後、ドライエッチング法などによりリセスエッチングして、第1サイドウォール絶縁膜24の側壁部のみに第2サイドウォール絶縁膜25を形成する。

第2サイドウォール絶縁膜25の形成には、まず、例えば20〜60nm程度の窒化シリコン膜、酸化シリコン、TEOS、NSG膜をCVD法などにより形成する。その後、ドライエッチング法などにより全面にリセスエッチングする。

【0084】

本実施形態では第2サイドウォール絶縁膜25を単層構成で形成しているが、複数層を積層した構成としてもよい。

【0085】

その後、イオン注入法により不純物をイオン注入してソースドレイン領域13を形成する。

ソースドレイン領域13は、エクステンション領域12と同じ導電型の不純物にて形成する。

その後、エクステンション領域12及びソースドレイン領域13に注入された不純物をアニール処理により活性化する。この活性化アニール処理は、例えば1000〜1100℃度程度の急速熱処理(Rapid Thermal Annealing)により行う。

【0086】

次に、サリサイドプロセス技術により、ソースドレイン領域13の表面に高融点金属シリサイド層14を形成する。これは、例えばTi,Co,Ni,Ptまたはそれらの化合物により、20〜70nm程度の厚さで形成する。

【0087】

次に、図7(b)に示すように、例えばCVD法により基板全面に第2応力導入層26と層間絶縁膜27を形成する。

第2応力導入層26としては、例えば窒化シリコンを200〜300nm程度の膜厚で形成し、チャネルの種類に応じて1.5〜2.0GPa程度の引っ張り応力や圧縮応力を持った膜を形成する。

また、層間絶縁膜27としては,例えばTEOSやNSG膜などを用いることができる。さらに、場合によっては第2応力導入層26のみを形成し、層間絶縁膜27を形成しないこともある。

【0088】

次に、図8(a)に示すように、オフセット膜22aの上面部が露出するように、第2応力導入層26と層間絶縁膜27を除去する。例えば、CMP(Chemical Mechanical Polishing)法によりそれぞれの膜を研磨除去する。

これにより、第2応力導入層26がオフセット膜22aの両脇で切断された構造となる。

【0089】

次に、図8(b)に示すように、オフセット膜22a、ダミーゲート電極21a及びダミーゲート絶縁膜20aを除去して、ゲート電極用溝TRを形成する。

ダミーゲート電極21aは,例えばドライエッチング法を用いて選択的に除去する。また、オフセット膜22aとダミーゲート絶縁膜20aは、例えばドライエッチング法やウェットエッチング法を用いて選択的に除去する。

【0090】

次に、図8(c)に示すように、ゲート電極用溝TRの内部にゲート絶縁膜31とゲート電極32を形成するための材料を半導体基板10上全面に堆積する。

ここで、ゲート絶縁膜31には、1〜3nm程度の酸化ハフニウム(HfO2)、酸化アルミニウムハフニウム(HfAlO2)、酸化シリコンハフニウム(HfSiO)、酸化タンタル(Ta2O5)、酸化アルミニウム(Al2O3)、酸化ジルコニウム(ZrO2)などのいわゆる高誘電率(High−k)膜により形成する。また、酸化シリコン(SiO2)および酸窒化シリコン(SiON)などを用いることができる。さらに、各膜を積層にして用いることもできる。その形成方法は、ALD法あるいはCVD法などを用いることができる。

【0091】

ゲート電極32は、例えばCVD法、ALD法あるいはPVD法により、50〜100nm程度の厚さを持つポリシリコン層、金属層、金属化合物層を堆積して形成する。

金属層や金属化合物層としては,窒化チタン(TiN)、チタン(Ti)、チタンシリコン(TiSi)、ニッケル(Ni)、ニッケルシリコン(NiSi)、ハフニウム(Hf)、ハフニウムシリコン(HfSi)、タングステン(W)、タンタル(Ta)、タンタルシリコン(TaSi)、窒化タンタルシリコン(TaSiN)、コバルト(Co)、コバルトシリコン(CoSi)、ルテニウム(Ru)、あるいはインジウム(In)などを用いることができる。その形成方法は、ALD法あるいはPVD法などを用いることができる。

しきい値電圧や抵抗値の調整のために、これらの膜を積層してもよい。また、酸化アルミニウム(AlO)あるいは酸化ランタン(LaO)などと前述の金属層や金属化合物層を積層にすることもできる。また、前述の金属層や金属化合物層により、チャネルの種類に応じて応力を印加することもできる。

【0092】

次に、図9(a)に示すように、第2応力導入層26の上部にあるゲート絶縁膜31とゲート電極32の材料をCMP法あるいはドライエッチング法を用いて除去する。

これにより、ゲート電極用溝TR内部のみにゲート絶縁膜31とゲート電極32が残る構造となる。

【0093】

次に、図9(b)に示すように、例えばゲート電極用溝TR内のゲート絶縁膜31とゲート電極32をドライエッチング法を用いて選択的にゲート電極用溝TRの深さの半分程度のところまで除去する。

このとき、第2応力導入層26、第1サイドウォール絶縁膜24及び第2サイドウォール絶縁膜25と、ゲート絶縁膜31およびゲート電極32との選択比を高めておく必要がある。

【0094】

次に、図9(c)に示すように、ゲート電極用溝TR内部のゲート電極32と第2応力導入層26の上部を覆うように、第1応力導入層33を堆積する。

第1応力導入層33には、例えば窒化シリコンを50〜150nm程度の膜厚で、チャネル種類に応じて1.5〜2.0GPa程度の引っ張り応力や圧縮応力を持った膜を形成し、第2応力導入層26と異なる応力を印加する膜とする。

次に、第2応力導入層26の上部にある第1応力導入層33をCMP法を用いて除去する。

なお、本実形態で示した各材料の膜厚や応力は、形成するトランジスタ特性や半導体基板へ導入する応力に応じて調整する必要があるため、これに限定されるものではない。

以上のようにして、図5に示す構成の本実施形態に係る半導体装置を製造できる。

【0095】

上記の製造方法では、ダミーゲート絶縁膜を除去して、改めてゲート絶縁膜を形成しているが、これに限らず、除去せずにそのまま用いるようにしてもよい。

【0096】

以降の工程としては、例えば、基板全面に第2層間絶縁膜を堆積し、ソースドレイン領域及びゲート電極に達するコンタクトホールを開口し、プラグを埋め込んで形成し、必要に応じて上層配線を形成する。

【0097】

本発明の半導体装置の製造方法によれば、第1応力導入層と第2応力導入層を形成することにより印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させることができる。

【0098】

<第1変形例>

図10は本変形例に係る半導体装置の模式断面図である。

実質的には第2実施形態と同様の構成であるが、ゲート電極が全て高融点金属シリサイドにより形成されたゲート電極32sからなることが異なる。

本変形例に係る半導体装置の製造方法は、図9(b)まで第2実施形態と同様に形成した後、ゲート電極32を全てシリサイド化する。

以降は第2実施形態と同様にして形成できる。

【0099】

<第2変形例>

図11は本変形例に係る半導体装置の模式断面図である。

実質的には第1実施形態と同様の構成であるが、ゲート電極が全て高融点金属シリサイドにより形成されたゲート電極21sからなることが異なる。

本変形例に係る半導体装置の製造方法は、図8(a)まで第2実施形態と同様に形成した後、オフセット膜22aを除去し、ダミーゲート電極をシリサイド化する。

得られたシリサイド化したダミーゲート電極21aをそのままゲート電極として用いる。また、ダミーゲート絶縁膜をそのままゲート絶縁膜として用いる。

以降は第2実施形態と同様にして形成できる。

【0100】

<第3実施形態>

[半導体装置の構造]

図12(a)は本実施形態に係る半導体装置の平面図であり、図12(b)は図12(a)中のA−A’における模式断面図であり、図12(c)は図12(a)中のB−B’における模式断面図である。

半導体基板40上に埋め込み絶縁膜41が形成されており、埋め込み絶縁膜41の上部にフィン型のチャネル形成領域を有する半導体領域42とハードマスク43が形成されている。

例えば,半導体基板40はシリコン基板であり、埋め込み絶縁膜41は50〜100nm程度の酸化シリコンが用いられる。

また、フィン型の半導体領域42とハードマスク43は、30〜80nm程度の膜厚のシリコン、50nmの膜厚の窒化シリコンが用いられる。

フィン型の半導体領域42は、半導体基板40の主面から突出した凸状の半導体領域であり、チャネル形成領域が半導体領域42に形成されている。

ここでは、フィン型の半導体領域42が埋め込み絶縁膜41の上部に配置されているが、埋め込み絶縁膜41が形成されておらず、半導体基板40とフィン型の半導体領域42が直接つながった構造を用いてもよい。

【0101】

埋め込み絶縁膜41、フィン型の半導体領域42およびハードマスク43を覆うように、ゲート絶縁膜45とゲート電極46が形成されている。

ゲート絶縁膜45は、1〜3nm程度の酸化ハフニウム(HfO2)、酸化アルミニウムハフニウム(HfAlO2)、酸化シリコンハフニウム(HfSiO)、酸化タンタル(Ta2O5)、酸化アルミニウム(Al2O3)、酸化ジルコニウム(ZrO2)などのいわゆる高誘電率(High−k)膜により形成する。また、酸化シリコン(SiO2)および酸窒化シリコン(SiON)などを用いることができる。さらに、各膜を積層にして用いることもできる。

フィン型のチャネル形成領域をダブルゲート電極で挟み込んだ構成である。

【0102】

ゲート電極46は、例えばポリシリコン層、金属層、金属化合物層を用いて形成されている。

金属層や金属化合物層としては,窒化チタン(TiN)、チタン(Ti)、チタンシリコン(TiSi)、ニッケル(Ni)、ニッケルシリコン(NiSi)、ハフニウム(Hf)、ハフニウムシリコン(HfSi)、タングステン(W)、タンタル(Ta)、タンタルシリコン(TaSi)、窒化タンタルシリコン(TaSiN)、コバルト(Co)、コバルトシリコン(CoSi)、ルテニウム(Ru)、あるいはインジウム(In)などを用いることができる。

しきい値電圧や抵抗値の調整のために、これらの膜を積層してもよい。また、酸化アルミニウム(AlO)あるいは酸化ランタン(LaO)などと前述の金属層や金属化合物層を積層にすることもできる。また、前述の金属層や金属化合物層により、チャネルの種類に応じて応力を印加することもできる。

【0103】

また、フィン型の半導体領域42が形成されていない領域にある埋め込み絶縁膜41の上面がフィン型の半導体領域42の底面よりも低く形成されている。

このため、フィン型の半導体領域42の側壁面がゲート絶縁膜45とゲート電極46で完全に覆われる構造となっている。

【0104】

ゲート電極46の上部には、第1応力導入層47が形成されている。第1応力導入層47としては、例えば30〜100nm程度膜厚の窒化シリコンが用いられる。フィン型のMOSFETのチャネル種類に応じて、1.0GPa程度の圧縮応力または1.5GPa程度の引っ張り応力を持った膜を用いることができる。

【0105】

ゲート絶縁膜45、ゲート電極46及び第1応力導入層47の側壁部には,サイドウォール絶縁膜50,51が形成されている。

サイドウォール絶縁膜50,51は、例えば酸化シリコンや窒化シリコン膜等などを単層あるいは複数層を積層して用いることができ、20〜100nm程度の膜厚で形成されている。

また、ゲート容量を低減するために、配線絶縁膜等に用いられるいわゆる低誘電率(Low−k)膜を用いることもできる。

サイドウォール絶縁膜50,51の側面には、第2応力導入層54が形成されており、第2応力導入層54の上面部は、第1応力導入層47の上面部と同じ高さなっている。

さらに、第2応力導入層54はサイドウォール絶縁膜50の両端で分離された構造になっている。より具体的には、第2応力導入層54は第1応力導入層47の上部領域には形成されておらず、第1応力導入層47とゲート電極46の両側部に第2応力導入層54が形成されている。

【0106】

本実施形態の半導体装置のMOSFETは、フィン型のMOSFETである。

ここで、本実施形態の半導体装置によれば、チャネル形成領域に異なる応力を印加する第1および第2応力導入層を用い、印加する応力の組み合わせを調整することで、従来例よりもキャリア移動度を向上させることができる。

【0107】

[半導体装置の製造方法]

本実施形態の半導体装置の製造方法について、図13〜21を参照して説明する。

図13(a)は本実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図13(b)は図13(a)中のA−A’における模式断面図であり、図13(c)は図13(a)中のB−B’における模式断面図である。

半導体基板40、埋め込み絶縁膜41および半導体領域42の3層構造を持ったSOI(Silicon On Insulator)基板上に、ハードマスク43を堆積する。その後、フォトリソグラフィー技術や電子線リソグラフィー技術を用いてレジスト膜44を形成する。

次に、レジスト膜44をマスクとしてドライエッチング法などによるエッチングを行い、ハードマスク43をパターンエッチングする。

このとき,例えば半導体基板40はシリコン基板、埋め込み絶縁膜41は50〜100nm程度の酸化シリコンを用いる。

また、半導体領域42としては、30〜80nmのシリコン層を用いる。また、ハードマスク43には、例えば50nm程度の膜厚の窒化シリコンを用いる。

【0108】

図14(a)は図13の次の工程を示す平面図であり、図14(b)は図14(a)中のA−A’における模式断面図であり、図14(c)は図14(a)中のB−B’における模式断面図である。

レジスト膜44を削除した後、ハードマスク43を用いて半導体領域42をドライエッチング処理によりエッチングする。

このとき、埋め込み絶縁膜41の一部も同時にエッチングしておくことで、フィン型の半導体領域42の端部で埋め込み絶縁膜41が凹んだ構造にしておく。

上記により、フィン型の半導体領域42は、半導体基板40の主面から突出した凸状の形状となる。

【0109】

本実施形態では、SOI基板を用いてフィン型の半導体領域42を形成しているが、SOI基板を用いない方法もある。例えば、半導体基板40上にハードマスク43及びレジスト膜44を形成し、直接フィン型の半導体領域を形成する。半導体基板40上の全面にハードマスク43の上面と同じかそれよりも高くなる膜厚で酸化シリコンなどの絶縁膜を堆積する。その後、CMP法を用いてハードマスク43の上面まで絶縁膜を除去した後、ドライエッチング法を用いて選択的に絶縁膜をエッチングすることで、半導体基板40上でフィン型の半導体領域が形成されていない領域のみ酸化シリコン膜を形成することが可能となる。

【0110】

図15(a)は図14の次の工程を示す平面図であり、図15(b)は図15(a)中のA−A’における模式断面図であり、図15(c)は図15(a)中のB−B’における模式断面図である。

半導体基板40上の全面に、ゲート絶縁膜45とゲート電極46を堆積して形成する。

ここで、ゲート絶縁膜45には、1〜3nm程度の酸化ハフニウム(HfO2)、酸化アルミニウムハフニウム(HfAlO2)、酸化シリコンハフニウム(HfSiO)、酸化タンタル(Ta2O5)、酸化アルミニウム(Al2O3)、酸化ジルコニウム(ZrO2)などのいわゆる高誘電率(High−k)膜により形成する。また、酸化シリコン(SiO2)および酸窒化シリコン(SiON)などを用いることができる。さらに、各膜を積層にして用いることもできる。その形成方法は、ALD法あるいはCVD法などを用いることができる。

【0111】

ゲート電極46は、例えばCVD法、ALD法あるいはPVD法により、50〜100nm程度の厚さを持つポリシリコン層、金属層、金属化合物層を堆積して形成する。

金属層や金属化合物層としては,窒化チタン(TiN)、チタン(Ti)、チタンシリコン(TiSi)、ニッケル(Ni)、ニッケルシリコン(NiSi)、ハフニウム(Hf)、ハフニウムシリコン(HfSi)、タングステン(W)、タンタル(Ta)、タンタルシリコン(TaSi)、窒化タンタルシリコン(TaSiN)、コバルト(Co)、コバルトシリコン(CoSi)、ルテニウム(Ru)、あるいはインジウム(In)などを用いることができる。その形成方法は、ALD法あるいはPVD法などを用いることができる。

しきい値電圧や抵抗値の調整のために、これらの膜を積層してもよい。また、酸化アルミニウム(AlO)あるいは酸化ランタン(LaO)などと前述の金属層や金属化合物層を積層にすることもできる。また、前述の金属層や金属化合物層により、チャネルの種類に応じて応力を印加することもできる。

【0112】

図16(a)は図15の次の工程を示す平面図であり、図16(b)は図16(a)中のA−A’における模式断面図であり、図16(c)は図16(a)中のB−B’における模式断面図である。

ゲート電極46の上面からCMP処理を行ってゲート電極46を所定の膜厚に加工する。

次に、ゲート電極46上に第1応力導入層47を形成した後、フォトリソグラフィー技術や電子線リソグラフィー技術を用いてレジスト膜48を形成する。

レジスト膜48をマスクとしてドライエッチング法などのエッチング処理を行うことで、第1応力導入層47をエッチングする。

ここで,第1応力導入膜47は、例えば30〜100nm程度の膜厚の窒化シリコンを用いることができる。

フィン型のMOSFETのチャネルの種類に応じて、2.0GPa程度の圧縮応力または1.5GPa程度の引っ張り応力を持った膜を用いることができる。

【0113】

図17(a)は図16の次の工程を示す平面図であり、図17(b)は図17(a)のA−A’における模式断面図であり、図17(c)は図17(a)中のB−B’における模式断面図である。

レジスト膜48を除去した後、第1応力導入層47をマスクとしてドライエッチング法などによりエッチング処理を行い、ゲート電極46とゲート絶縁膜45をエッチングする。

また、本実施形態とは異なり、レジスト膜48を残したまま、レジスト膜48を第1応力導入層47とゲート電極46及びゲート絶縁膜45のエッチングのマスクとして用いてもよい。

【0114】

図18(a)は図17の次の工程を示す平面図であり、図18(b)は図18(a)のA−A’における模式断面図であり、図18(c)は図18(a)中のB−B’における模式断面図である。

フィン型の半導体領域42内にイオン注入法を用いてエクステンション領域49を形成する。

エクステンション領域49は、NTrの場合にはそれぞれn型不純物、PTrの場合にはp型不純物を導入する。

さらに、場合によってはエクステンション領域49と異なる導電型の不純物をエクステンション領域49よりも深く注入してもよい。この場合、エクステンション領域49の深さ方向の不純物プロファイルをさらに急峻にすることもできる。

【0115】

図19(a)は図18の次の工程を示す平面図であり、図19(b)は図19(a)のA−A’における模式断面図であり、図19(c)は図19(a)中のB−B’における模式断面図である。

半導体基板上の全面に絶縁膜を形成後、ドライエッチング法を用いてリセスエッチングして、ゲート絶縁膜45、ゲート電極46と第1応力導入層47の側壁にサイドウォール絶縁膜50,51を形成する。

サイドウォール絶縁膜50,51は、例えば20〜100nm程度の厚さで窒化シリコン膜、TEOS、NSG膜及び酸化シリコンをCVD法などによりにて形成することができる。

本実施形態では、サイドウォール絶縁膜50,51は1層で形成されているが、複数の膜を積層して形成することもできる。

その後、エクステンション領域49に接続するように、ソースドレイン領域52を埋め込み絶縁膜41の上面付近までの深さでイオン注入法を用いて形成する。

ソースドレイン領域52は、エクステンション領域49と同型の不純物にて形成する。

その後、エクステンション領域49、ソースドレイン領域52に注入された不純物をアニールにて活性化する。この活性化アニールは、例えば1000〜1100℃程度の急速熱処理(Rapid Thermal Annealing)により行う。

次に、サリサイドプロセス技術により、ソースドレイン領域52の表面に高融点金属シリサイド層53を形成する。これは、例えばTi,Co,Ni,Ptまたはそれらの化合物により、20〜70nm程度の厚さで形成する。

【0116】

図20(a)は図19の次の工程を示す平面図であり、図20(b)は図20(a)のA−A’における模式断面図であり、図20(c)は図20(a)中のB−B’における模式断面図である。

例えばCVD法により基板全面に第2応力導入層54を形成する。第2応力導入層54は、例えば窒化シリコンを200〜300nm程度の膜厚で、フィン型のMOSFETのチャネルの種類に応じて、1.5〜2.0GPa程度の引っ張り応力や圧縮応力を持った膜を形成する。

また、第1応力導入層47とは異なる応力を持った膜を形成する。

【0117】

図21(a)は図20の次の工程を示す平面図であり、図21(b)は図21(a)のA−A’における模式断面図であり、図21(c)は図21(a)中のB−B’における模式断面図である。

第1応力導入層47の上面部が露出するように、例えばCMP法により第2応力導入層54を除去する。

これにより、第2応力導入層54が第1応力導入層47の両脇で切断された構造となる。

以上のようにして、図12に示す構成の本実施形態に係る半導体装置を製造できる。

【0118】

以降の工程としては、例えば、基板全面に層間絶縁膜を堆積し、ソースドレイン領域及びゲート電極に達するコンタクトホールを開口し、プラグを埋め込んで形成し、必要に応じて上層配線を形成する。

【0119】

本発明の半導体装置の製造方法によれば、第1応力導入層と第2応力導入層を形成することにより印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させることができる。

【0120】

<第4実施形態>

[半導体装置の構造]

図22(a)は本実施形態に係る半導体装置の平面図であり、図22(b)は図22(a)中のA−A’における模式断面図であり、図22(c)は図22(a)中のB−B’における模式断面図である。

実質的には第3実施形態と同様の構成であるが、以下の点が異なる。

第3実施形態の半導体装置におけるハードマスク43が除去されている。このため、フィン型のチャネル形成領域をトリプルゲート電極で挟み込んだ構成となっている。

【0121】

本実施形態の半導体装置のMOSFETは、フィン型のMOSFETである。

ここで、本実施形態の半導体装置によれば、チャネル形成領域に異なる応力を印加する第1および第2応力導入層を用い、印加する応力の組み合わせを調整することで、従来例よりもキャリア移動度を向上させることができる。

【0122】

[半導体装置の製造方法]

本実施形態の半導体装置の製造方法について、図23〜30を参照して説明する。

図23(a)は本実施形態に係る半導体装置の製造方法の製造工程を示す平面図であり、図23(b)は図23(a)中のA−A’における模式断面図であり、図23(c)は図23(a)中のB−B’における模式断面図である。

半導体基板40、埋め込み絶縁膜41および半導体領域42の3層構造を持ったSOI(Silicon On Insulator)基板上に、ハードマスク43を堆積する。その後、フォトリソグラフィー技術や電子線リソグラフィー技術を用いてレジスト膜44を形成する。

次に、レジスト膜44をマスクとしてドライエッチング法などによるエッチングを行い、ハードマスク43をパターンエッチングする。

このとき,例えば半導体基板40はシリコン基板、埋め込み絶縁膜41は50〜100nm程度の酸化シリコンを用いる。

また、半導体領域42としては、30〜80nmのシリコン層を用いる。また、ハードマスク43には、例えば50nm程度の膜厚の窒化シリコンを用いる。

【0123】

図24(a)は図23の次の工程を示す平面図であり、図24(b)は図24(a)中のA−A’における模式断面図であり、図24(c)は図24(a)中のB−B’における模式断面図である。

レジスト膜44を削除した後、ハードマスク43を用いて半導体領域42をドライエッチング処理によりエッチングする。

このとき、埋め込み絶縁膜41の一部も同時にエッチングしておくことで、フィン型の半導体領域42の端部で埋め込み絶縁膜41が凹んだ構造にしておく。

上記により、フィン型の半導体領域42は、半導体基板40の主面から突出した凸状の形状となる。

さらに、ハードマスク43をドライエッチングまたはウェットエッチング処理によりエッチングする。

【0124】

図25(a)は図24の次の工程を示す平面図であり、図25(b)は図25(a)中のA−A’における模式断面図であり、図25(c)は図25(a)中のB−B’における模式断面図である。

半導体基板40上の全面に、ゲート絶縁膜45とゲート電極46を堆積して形成する。

【0125】

図26(a)は図25の次の工程を示す平面図であり、図26(b)は図26(a)中のA−A’における模式断面図であり、図26(c)は図26(a)中のB−B’における模式断面図である。

ゲート電極46の上面からCMP処理を行ってゲート電極46を所定の膜厚に加工する。

次に、ゲート電極46上に第1応力導入層47を形成した後、フォトリソグラフィー技術や電子線リソグラフィー技術を用いてレジスト膜48を形成する。

レジスト膜48をマスクとしてドライエッチング法などのエッチング処理を行うことで、第1応力導入層47をエッチングする。

【0126】

図27(a)は図26の次の工程を示す平面図であり、図27(b)は図27(a)のA−A’における模式断面図であり、図27(c)は図27(a)中のB−B’における模式断面図である。

レジスト膜48を除去した後、第1応力導入層47をマスクとしてドライエッチング法などによりエッチング処理を行い、ゲート電極46とゲート絶縁膜45をエッチングする。

【0127】

図28(a)は図27の次の工程を示す平面図であり、図28(b)は図28(a)のA−A’における模式断面図であり、図28(c)は図28(a)中のB−B’における模式断面図である。

フィン型の半導体領域42内にイオン注入法を用いてエクステンション領域49を形成する。次に、ゲート絶縁膜45、ゲート電極46と第1応力導入層47の側壁にサイドウォール絶縁膜50,51を形成する。

その後、エクステンション領域49に接続するように、ソースドレイン領域52を埋め込み絶縁膜41の上面付近までの深さでイオン注入法を用いて形成する。

次に、サリサイドプロセス技術により、ソースドレイン領域52の表面に高融点金属シリサイド層53を形成する。

【0128】

図29(a)は図28の次の工程を示す平面図であり、図29(b)は図29(a)のA−A’における模式断面図であり、図29(c)は図29(a)中のB−B’における模式断面図である。

例えばCVD法により基板全面に第2応力導入層54を形成する。

【0129】

図30(a)は図29の次の工程を示す平面図であり、図30(b)は図30(a)のA−A’における模式断面図であり、図30(c)は図30(a)中のB−B’における模式断面図である。

第1応力導入層47の上面部が露出するように、例えばCMP法により第2応力導入層54を除去する。

これにより、第2応力導入層54が第1応力導入層47の両脇で切断された構造となる。

以上のようにして、図22に示す構成の本実施形態に係る半導体装置を製造できる。

【0130】

以降の工程としては、例えば、基板全面に層間絶縁膜を堆積し、ソースドレイン領域及びゲート電極に達するコンタクトホールを開口し、プラグを埋め込んで形成し、必要に応じて上層配線を形成する。

【0131】

本発明の半導体装置の製造方法によれば、第1応力導入層と第2応力導入層を形成することにより印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させることができる。

【0132】

本実施形態の半導体装置及びその製造方法では、ゲート電極上に第1応力導入層を配置して、半導体基板上でゲート電極と第1応力導入層が形成されていない領域に第2応力導入層を形成する。

これにより、第2応力導入層がゲート電極端で切断された構造となる。このため、ゲート電極端部の半導体基板内へ効果的に応力を印加することができる。

また、第2応力導入層が切断された構造になっているため、ゲート電極材料の薄膜化を行っても、第1応力導入層の膜厚を調整することで第2応力導入層の膜厚を厚くすることができる。これにより、第2応力導入層からチャネル形成領域に印加される応力の緩和を防ぐことができる。

さらに,第1応力導入層と第2応力導入層で異なる応力を有する材料を用いることにより、ゲート電極のゲート長方向(longitudinal方向)と基板に垂直な方向(vertical方向)に異なる応力を印加することができる。

これにより、FET構造、チャネルの種類、基板の面方位、チャネル方向に最適な応力印加が可能となり、キャリア移動度の向上効果を高めることができる。

【0133】

本発明は上記の説明に限定されない。

例えば、実施形態においてはNTrまたはPTrを有する半導体装置を説明しているが、これに限らず、両者を有するCMOS構成であってもよい。

その他、本発明の要旨を逸脱しない範囲で、種々の変更が可能である。

【符号の説明】

【0134】

10…半導体基板、11…第3応力導入層、12…エクステンション領域、13…ソースドレイン領域、14…高融点金属シリサイド層、20…ゲート絶縁膜、20a…ダミーゲート絶縁膜、21…ゲート電極、21a…ダミーゲート電極、22…第1応力導入層、22a…オフセット膜、23…ダミーサイドウォール絶縁膜、24…第1サイドウォール絶縁膜、25…第2サイドウォール絶縁膜、26…第2応力導入層、27…第1層間絶縁膜、28…第2層間絶縁膜、29…プラグ、30…上層配線、31…ゲート絶縁膜、32…ゲート電極、33…第1応力導入層、40…半導体基板、41…埋め込み絶縁膜、42…半導体領域、43…ハードマスク、44…レジスト膜、45…ゲート絶縁膜、46…ゲート電極、47…第1応力導入層、48…レジスト膜、49…エクステンション領域、50,51…サイドウォール絶縁膜、52…ソースドレイン領域、53…高融点金属シリサイド層、54…第2応力導入層、TR…ゲート電極用溝

【特許請求の範囲】

【請求項1】

チャネル形成領域を有する半導体基板と、

前記チャネル形成領域において前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜の上層に形成されたゲート電極と、

前記ゲート電極の上層に形成され、前記チャネル形成領域に応力を導入する第1応力導入層と、

前記ゲート電極及び前記第1応力導入層の両側部における前記半導体基板の表層部に形成されたソースドレイン領域と、

少なくとも前記第1応力導入層の領域を除き、前記ソースドレイン領域の上層に形成され、前記チャネル形成領域に前記第1応力導入層と異なる応力を導入する第2応力導入層と

を有する電界効果トランジスタを有する半導体装置。

【請求項2】

前記第1応力導入層の上面と前記第2応力導入層の上面が同じ高さに形成されている

請求項1に記載の半導体装置。

【請求項3】

前記チャネル形成領域が前記半導体基板の平坦な領域に形成されており、

前記電界効果トランジスタがプレーナー型の電界効果トランジスタである

請求項1に記載の半導体装置。

【請求項4】

前記第1応力導入層が前記チャネル形成領域に圧縮応力を導入し、前記第2応力導入層が前記チャネル形成領域に引っ張り応力を導入する

請求項3に記載の半導体装置。

【請求項5】

前記ゲート電極が前記チャネル形成領域に圧縮応力を導入する

請求項4に記載の半導体装置。

【請求項6】

前記第1応力導入層が前記チャネル形成領域に引っ張り応力を導入し、前記第2応力導入層が前記チャネル形成領域に圧縮応力を導入する

請求項3に記載の半導体装置。

【請求項7】

前記ゲート電極が前記チャネル形成領域に引っ張り応力を導入する

請求項6に記載の半導体装置。

【請求項8】

前記第1応力導入層は、前記電界効果トランジスタがnチャネル電界効果トランジスタの場合は圧縮応力を持った膜、前記電界効果トランジスタがpチャネル電界効果トランジスタの場合は引っ張り応力を持った膜であり、

前記第2応力導入層は、前記電界効果トランジスタがnチャネル電界効果トランジスタの場合は引っ張り応力を持った膜、前記電界効果トランジスタがpチャネル電界効果トランジスタの場合は圧縮応力を持った膜である

請求項3に記載の半導体装置。

【請求項9】

前記チャネル形成領域が前記半導体基板の主面から突出した凸状の半導体領域に形成されており、

前記電界効果トランジスタがフィン型の電界効果トランジスタである

請求項1に記載の半導体装置。

【請求項10】

前記ゲート電極と前記ゲート絶縁膜が前記半導体領域の対向する2つの側面を被覆するように形成されている

請求項9に記載の半導体装置。

【請求項11】

前記ゲート電極と前記ゲート絶縁膜が前記半導体領域の対抗する2つ側面及び上面の3面を被覆するように形成されている

請求項9に記載の半導体装置。

【請求項12】

前記第1応力導入層が前記チャネル形成領域に圧縮応力を導入し、前記第2応力導入層が前記チャネル形成領域に引っ張り応力を導入する

請求項9に記載の半導体装置。

【請求項13】

前記ゲート電極が前記チャネル形成領域に圧縮応力を導入する

請求項12に記載の半導体装置。

【請求項14】

前記第1応力導入層が前記チャネル形成領域に引っ張り応力を導入し、前記第2応力導入層が前記チャネル形成領域に圧縮応力を導入する

請求項9に記載の半導体装置。

【請求項15】

前記ゲート電極が前記チャネル形成領域に引っ張り応力を導入する

請求項14に記載の半導体装置。

【請求項16】

前記第1応力導入層は、前記電界効果トランジスタがnチャネル電界効果トランジスタの場合は圧縮応力を持った膜、前記電界効果トランジスタがpチャネル電界効果トランジスタの場合は引っ張り応力を持った膜であり、

前記第2応力導入層は、前記電界効果トランジスタがnチャネル電界効果トランジスの場合は引っ張り応力を持った膜、前記電界効果トランジスタがpチャネル電界効果トランジスタの場合は圧縮応力を持った膜である

請求項9に記載の半導体装置。

【請求項17】

前記半導体領域が絶縁膜を介して前記半導体基板から分離して形成されている

請求項9〜16のいずれかに記載の半導体装置。

【請求項18】

前記半導体領域が前記半導体基板に接続して形成されている

請求項9〜16のいずれかに記載の半導体装置。

【請求項19】

チャネル形成領域を有する半導体基板の前記チャネル形成領域において前記半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜の上層にゲート電極を形成する工程と、

前記ゲート電極の上層に、前記チャネル形成領域に応力を導入する第1応力導入層を形成する工程と、

前記ゲート電極及び前記第1応力導入層の両側部における前記半導体基板の表層部にソースドレイン領域を形成する工程と、

少なくとも前記第1応力導入層の領域を除き、前記ソースドレイン領域の上層に、前記チャネル形成領域に前記第1応力導入層と異なる応力を導入する第2応力導入層を形成する工程と

を有し、電界効果トランジスタを形成する

半導体装置の製造方法。

【請求項20】

前記第2応力導入層を形成する工程の後に、前記第1応力導入層の上面と前記第2応力導入層の上面が同じ高さとなるように少なくとも前記第1応力導入層または前記第2応力導入層の上面から研磨処理する工程をさらに有する

請求項19に記載の半導体装置の製造方法。

【請求項21】

前記チャネル形成領域を有する半導体基板として前記チャネル形成領域が前記半導体基板の平坦な領域に形成された半導体基板を用い、前記電界効果トランジスタとしてプレーナー型の電界効果トランジスタを形成する

請求項19記載の半導体装置の製造方法。

【請求項22】

前記チャネル形成領域を有する半導体基板として前記チャネル形成領域が前記半導体基板の主面から突出した凸状の半導体領域と用い、前記電界効果トランジスタとしてフィン型の電界効果トランジスタを形成する

請求項19に記載の半導体装置の製造方法。

【請求項23】

チャネル形成領域を有する半導体基板の前記チャネル形成領域において前記半導体基板上にダミーゲート絶縁膜を形成する工程と、

前記ダミーゲート絶縁膜の上層にダミーゲート電極を形成する工程と、

前記ダミーゲート電極の上層にオフセット膜を形成する工程と、

前記ダミーゲート電極及び前記オフセット膜の両側部における前記半導体基板の表層部にソースドレイン領域を形成する工程と、

少なくとも前記オフセット膜の領域を除き、前記ソースドレイン領域の上層に、前記チャネル形成領域に応力を導入する第1応力導入層を形成する工程と、

前記オフセット層、前記ダミーゲート電極及び前記ダミーゲート絶縁膜を除去し、ゲート電極用溝を形成する工程と、

前記ゲート電極用溝の底面を被覆してゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜の上層に前記ゲート電極用溝の途中の深さまでのゲート電極を形成する工程と、

前記ゲート電極の上層に前記ゲート電極用溝を埋め込んで前記チャネル形成領域に前記第1応力導入層と異なる応力を導入する第2応力導入層を形成する工程と

を有し、電界効果トランジスタを形成する

半導体装置の製造方法。

【請求項24】

前記第2応力導入層を形成する工程の後に、前記第1応力導入層の上面と前記第2応力導入層の上面が同じ高さとなるように少なくとも前記第1応力導入層または前記第2応力導入層の上面から研磨処理する工程をさらに有する

請求項23に記載の半導体装置の製造方法。

【請求項1】

チャネル形成領域を有する半導体基板と、

前記チャネル形成領域において前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜の上層に形成されたゲート電極と、

前記ゲート電極の上層に形成され、前記チャネル形成領域に応力を導入する第1応力導入層と、

前記ゲート電極及び前記第1応力導入層の両側部における前記半導体基板の表層部に形成されたソースドレイン領域と、

少なくとも前記第1応力導入層の領域を除き、前記ソースドレイン領域の上層に形成され、前記チャネル形成領域に前記第1応力導入層と異なる応力を導入する第2応力導入層と

を有する電界効果トランジスタを有する半導体装置。

【請求項2】

前記第1応力導入層の上面と前記第2応力導入層の上面が同じ高さに形成されている

請求項1に記載の半導体装置。

【請求項3】

前記チャネル形成領域が前記半導体基板の平坦な領域に形成されており、

前記電界効果トランジスタがプレーナー型の電界効果トランジスタである

請求項1に記載の半導体装置。

【請求項4】

前記第1応力導入層が前記チャネル形成領域に圧縮応力を導入し、前記第2応力導入層が前記チャネル形成領域に引っ張り応力を導入する

請求項3に記載の半導体装置。

【請求項5】

前記ゲート電極が前記チャネル形成領域に圧縮応力を導入する

請求項4に記載の半導体装置。

【請求項6】

前記第1応力導入層が前記チャネル形成領域に引っ張り応力を導入し、前記第2応力導入層が前記チャネル形成領域に圧縮応力を導入する

請求項3に記載の半導体装置。

【請求項7】

前記ゲート電極が前記チャネル形成領域に引っ張り応力を導入する

請求項6に記載の半導体装置。

【請求項8】

前記第1応力導入層は、前記電界効果トランジスタがnチャネル電界効果トランジスタの場合は圧縮応力を持った膜、前記電界効果トランジスタがpチャネル電界効果トランジスタの場合は引っ張り応力を持った膜であり、

前記第2応力導入層は、前記電界効果トランジスタがnチャネル電界効果トランジスタの場合は引っ張り応力を持った膜、前記電界効果トランジスタがpチャネル電界効果トランジスタの場合は圧縮応力を持った膜である

請求項3に記載の半導体装置。

【請求項9】

前記チャネル形成領域が前記半導体基板の主面から突出した凸状の半導体領域に形成されており、

前記電界効果トランジスタがフィン型の電界効果トランジスタである

請求項1に記載の半導体装置。

【請求項10】

前記ゲート電極と前記ゲート絶縁膜が前記半導体領域の対向する2つの側面を被覆するように形成されている

請求項9に記載の半導体装置。

【請求項11】

前記ゲート電極と前記ゲート絶縁膜が前記半導体領域の対抗する2つ側面及び上面の3面を被覆するように形成されている

請求項9に記載の半導体装置。

【請求項12】

前記第1応力導入層が前記チャネル形成領域に圧縮応力を導入し、前記第2応力導入層が前記チャネル形成領域に引っ張り応力を導入する

請求項9に記載の半導体装置。

【請求項13】

前記ゲート電極が前記チャネル形成領域に圧縮応力を導入する

請求項12に記載の半導体装置。

【請求項14】

前記第1応力導入層が前記チャネル形成領域に引っ張り応力を導入し、前記第2応力導入層が前記チャネル形成領域に圧縮応力を導入する

請求項9に記載の半導体装置。

【請求項15】

前記ゲート電極が前記チャネル形成領域に引っ張り応力を導入する

請求項14に記載の半導体装置。

【請求項16】

前記第1応力導入層は、前記電界効果トランジスタがnチャネル電界効果トランジスタの場合は圧縮応力を持った膜、前記電界効果トランジスタがpチャネル電界効果トランジスタの場合は引っ張り応力を持った膜であり、

前記第2応力導入層は、前記電界効果トランジスタがnチャネル電界効果トランジスの場合は引っ張り応力を持った膜、前記電界効果トランジスタがpチャネル電界効果トランジスタの場合は圧縮応力を持った膜である

請求項9に記載の半導体装置。

【請求項17】

前記半導体領域が絶縁膜を介して前記半導体基板から分離して形成されている

請求項9〜16のいずれかに記載の半導体装置。

【請求項18】

前記半導体領域が前記半導体基板に接続して形成されている

請求項9〜16のいずれかに記載の半導体装置。

【請求項19】

チャネル形成領域を有する半導体基板の前記チャネル形成領域において前記半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜の上層にゲート電極を形成する工程と、

前記ゲート電極の上層に、前記チャネル形成領域に応力を導入する第1応力導入層を形成する工程と、

前記ゲート電極及び前記第1応力導入層の両側部における前記半導体基板の表層部にソースドレイン領域を形成する工程と、

少なくとも前記第1応力導入層の領域を除き、前記ソースドレイン領域の上層に、前記チャネル形成領域に前記第1応力導入層と異なる応力を導入する第2応力導入層を形成する工程と

を有し、電界効果トランジスタを形成する

半導体装置の製造方法。

【請求項20】

前記第2応力導入層を形成する工程の後に、前記第1応力導入層の上面と前記第2応力導入層の上面が同じ高さとなるように少なくとも前記第1応力導入層または前記第2応力導入層の上面から研磨処理する工程をさらに有する

請求項19に記載の半導体装置の製造方法。

【請求項21】

前記チャネル形成領域を有する半導体基板として前記チャネル形成領域が前記半導体基板の平坦な領域に形成された半導体基板を用い、前記電界効果トランジスタとしてプレーナー型の電界効果トランジスタを形成する

請求項19記載の半導体装置の製造方法。

【請求項22】

前記チャネル形成領域を有する半導体基板として前記チャネル形成領域が前記半導体基板の主面から突出した凸状の半導体領域と用い、前記電界効果トランジスタとしてフィン型の電界効果トランジスタを形成する

請求項19に記載の半導体装置の製造方法。

【請求項23】

チャネル形成領域を有する半導体基板の前記チャネル形成領域において前記半導体基板上にダミーゲート絶縁膜を形成する工程と、

前記ダミーゲート絶縁膜の上層にダミーゲート電極を形成する工程と、

前記ダミーゲート電極の上層にオフセット膜を形成する工程と、

前記ダミーゲート電極及び前記オフセット膜の両側部における前記半導体基板の表層部にソースドレイン領域を形成する工程と、

少なくとも前記オフセット膜の領域を除き、前記ソースドレイン領域の上層に、前記チャネル形成領域に応力を導入する第1応力導入層を形成する工程と、

前記オフセット層、前記ダミーゲート電極及び前記ダミーゲート絶縁膜を除去し、ゲート電極用溝を形成する工程と、

前記ゲート電極用溝の底面を被覆してゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜の上層に前記ゲート電極用溝の途中の深さまでのゲート電極を形成する工程と、

前記ゲート電極の上層に前記ゲート電極用溝を埋め込んで前記チャネル形成領域に前記第1応力導入層と異なる応力を導入する第2応力導入層を形成する工程と

を有し、電界効果トランジスタを形成する

半導体装置の製造方法。

【請求項24】

前記第2応力導入層を形成する工程の後に、前記第1応力導入層の上面と前記第2応力導入層の上面が同じ高さとなるように少なくとも前記第1応力導入層または前記第2応力導入層の上面から研磨処理する工程をさらに有する

請求項23に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【公開番号】特開2012−38979(P2012−38979A)

【公開日】平成24年2月23日(2012.2.23)

【国際特許分類】

【出願番号】特願2010−178976(P2010−178976)

【出願日】平成22年8月9日(2010.8.9)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成24年2月23日(2012.2.23)

【国際特許分類】

【出願日】平成22年8月9日(2010.8.9)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]