半導体装置及びその製造方法

【課題】種類の異なる半導体チップの間で接合不良が発生することを防止した半導体装置及びその製造方法を提供する。

【解決手段】配線基板2の一面に実装されたチップ積層体3は、配線基板2の一面とは反対側から順に、一面側に第1のバンプ電極12と他面側に第2のバンプ電極13とを有する複数のメモリーチップ10a〜10dを、それぞれの一面と他面とを対向させながら、それぞれの間にある第1のバンプ電極12と第2のバンプ電極13とを接合して積層し、その上に、一面側に第3のバンプ電極15と他面側に第4のバンプ電極16とを有するロジックチップ11を、その一面と、その下にあるメモリーチップ10dの他面とを対向させながら、その間にある第2のバンプ電極13と第3のバンプ電極15とを接合部材18を介して接合して積層した構造を有する。

【解決手段】配線基板2の一面に実装されたチップ積層体3は、配線基板2の一面とは反対側から順に、一面側に第1のバンプ電極12と他面側に第2のバンプ電極13とを有する複数のメモリーチップ10a〜10dを、それぞれの一面と他面とを対向させながら、それぞれの間にある第1のバンプ電極12と第2のバンプ電極13とを接合して積層し、その上に、一面側に第3のバンプ電極15と他面側に第4のバンプ電極16とを有するロジックチップ11を、その一面と、その下にあるメモリーチップ10dの他面とを対向させながら、その間にある第2のバンプ電極13と第3のバンプ電極15とを接合部材18を介して接合して積層した構造を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、半導体チップの集積度が年々向上し、それに伴ってチップサイズの大型化や、配線の微細化及び多層化などが進んでいる。一方、高密度実装化のためには、パッケージサイズの小型化及び薄型化が必要となっている。

【0003】

このような要求に対して、MCP(Multi Chip Package)と呼ばれる1つの配線基板の上に複数の半導体チップを高密度実装する技術が開発されている。その中でも、TSV(Through Silicon Via)と呼ばれる貫通電極を有する半導体チップを積層したチップ積層体を配線基板の一面に実装したCoC(Chip on Chip)型の半導体パッケージが注目されている(例えば、特許文献1を参照。)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−214220号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、上述したCoC型の半導体パッケージでは、例えばDRAM(Dynamic Random Access Memory)回路などが形成された複数のメモリーチップを積層したチップ積層体の上に更に、このメモリーチップを制御するロジック回路などが形成されたロジックチップを積層搭載することが検討されている。

【0006】

しかしながら、メモリーチップとロジックチップとの種類の異なる半導体チップの間では、互いの接続端子(バンプ電極)を構成する電極材料の制約などによって、これら接続端子の間で接合不良が生じる虞があった。

【課題を解決するための手段】

【0007】

本発明に係る半導体装置は、少なくとも配線基板と、この配線基板の一面に実装されたチップ積層体とを備える半導体パッケージであって、チップ積層体は、配線基板の一面とは反対側から順に、一面側に第1の接続端子と他面側に第2の接続端子とを有する複数の第1の半導体チップを、それぞれの一面と他面とを対向させながら、それぞれの間にある第1の接続端子と第2の接続端子とを接合して積層し、その上に、一面側に第3の接続端子と他面側に第4の接続端子とを有する第2の半導体チップを、その一面と、その下にある第1の半導体チップの他面とを対向させながら、その間にある第2の接続端子と第3の接続端子とを接合部材を介して接合して積層した構造を有することを特徴とする。

【0008】

また、本発明に係る半導体装置の製造方法は、少なくとも配線基板と、この配線基板の一面に実装されたチップ積層体とを備える半導体パッケージの製造方法であって、チップ積層体を形成する際に、一面側に第1の接続端子と他面側に第2の接続端子とを有する複数の第1の半導体チップを、それぞれの一面と他面とを対向させながら、それぞれの間にある第1の接続端子と第2の接続端子とを接合して積層する工程と、積層された複数の第1の半導体チップの最上層に位置する第1の半導体チップの第2の接続端子の上に接合部材を配置する工程と、その上に、一面側に第3の接続端子と他面側に第4の接続端子とを有する第2の半導体チップを、その一面と、その下にある第1の半導体チップの他面とを対向させながら、その間にある第2の接続端子と第3の接続端子とを接合部材を介して接合して積層する工程とを含むことを特徴とする。

【発明の効果】

【0009】

以上のように、本発明では、複数の第1の半導体チップを積層し、その上に第2の半導体チップを積層したチップ積層体において、種類の異なる第1の半導体チップと第2の半導体チップとの間で互いの接続端子を接合する際に、これら接続端子の間に接合部材を介在させることによって、電極材料や接合方法などの制約がなく、熱による接合が困難な半導体チップの接続端子同士を良好に接合することが可能となる。

【図面の簡単な説明】

【0010】

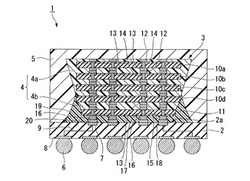

【図1A】本発明を適用した半導体パッケージの一例を示す断面図である。

【図1B】図1Aに示す半導体パッケージの要部を拡大して示す断面図である。

【図2A】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップを積層する工程を順に示す断面図である。

【図2B】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップを積層する工程を順に示す断面図である。

【図2C】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップを積層する工程を順に示す断面図である。

【図3A】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップの間に第1のアンダーフィル材を充填する工程を順に示す断面図である。

【図3B】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップの間に第1のアンダーフィル材を充填する工程を順に示す断面図である。

【図3C】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップの間に第1のアンダーフィル材を充填する工程を順に示す断面図である。

【図3D】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップの間に第1のアンダーフィル材を充填する工程を順に示す断面図である。

【図4A】図1Aに示す半導体パッケージの製造工程として、第1の接合部材を配置する工程を順に示す断面図である。

【図4B】図1Aに示す半導体パッケージの製造工程として、第1の接合部材を配置する工程を順に示す断面図である。

【図4C】図1Aに示す半導体パッケージの製造工程として、第1の接合部材を配置する工程を順に示す断面図である。

【図5A】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップの上にロジックチップを積層する工程を順に示す断面図である。

【図5B】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップの上にロジックチップを積層する工程を順に示す断面図である。

【図6A】図1Aに示す半導体パッケージの製造工程として、ロジックチップとメモリーチップとの間に第2のアンダーフィル材を充填する工程を順に示す断面図である。

【図6B】図1Aに示す半導体パッケージの製造工程として、ロジックチップとメモリーチップとの間に第2のアンダーフィル材を充填する工程を順に示す断面図である。

【図7A】図1Aに示す半導体パッケージの製造工程として、チップ積層体を母配線基板上に実装する工程を順に示す断面図である。

【図7B】図1Aに示す半導体パッケージの製造工程として、チップ積層体を母配線基板上に実装する工程を順に示す断面図である。

【図7C】図1Aに示す半導体パッケージの製造工程として、チップ積層体を母配線基板上に実装する工程を順に示す断面図である。

【図8】図1Aに示す半導体パッケージの製造工程として、チップ積層体を第2の封止体で封止する工程を示す断面図である。

【図9】図1Aに示す半導体パッケージの製造工程として、はんだボールを配置する工程を示す断面図である。

【図10】図1Aに示す半導体パッケージの製造工程として、個々の半導体パッケージに分割する工程を示す断面図である。

【図11A】図1Aに示す半導体パッケージの別の製造工程として、複数のメモリーチップ及びロジックチップを積層した後、第1の封止体で封止する工程を順に示す断面図である。

【図11B】図1Aに示す半導体パッケージの別の製造工程として、複数のメモリーチップ及びロジックチップを積層して、第1の封止体で封止する工程を順に示す断面図である。

【図11C】図1Aに示す半導体パッケージの別の製造工程として、複数のメモリーチップ及びロジックチップを積層して、第1の封止体で封止する工程を順に示す断面図である。

【図11D】図1Aに示す半導体パッケージの別の製造工程として、複数のメモリーチップ及びロジックチップを積層して、第1の封止体で封止する工程を順に示す断面図である。

【発明を実施するための形態】

【0011】

以下、本発明を適用した半導体装置及びその製造方法について、図面を参照して詳細に説明する。

なお、以下の説明で用いる図面は、特徴をわかりやすくするために、便宜上特徴となる部分を拡大して示している場合があり、各構成要素の寸法比率などが実際と同じであるとは限らない。また、以下の説明において例示される材料、寸法等は一例であって、本発明はそれらに必ずしも限定されるものではなく、その要旨を変更しない範囲で適宜変更して実施することが可能である。

【0012】

(半導体装置)

先ず、本発明を適用した半導体装置の一例として、図1Aに示すCoC型の半導体パッケージ1について説明する。

この半導体パッケージ1は、図1Aに示すように、配線基板2と、この配線基板2の一面(上面)に実装されたチップ積層体3と、このチップ積層体3を覆う第1の封止体4と、この第1の封止体4を覆う第2の封止体5と、配線基板2の他面に配置された複数のはんだボール(外部接続端子)6とを備えることによって、BGA(Ball Grid Array)と呼ばれるパッケージ構造を有している。

【0013】

配線基板2は、平面視で矩形状を為すプリント配線板からなり、この配線基板2の上面中央部には、チップ積層体3が実装される実装領域2aが設けられている。また、配線基板2の実装領域2aには、複数のパッド電極(第5の接続端子)7が並んで設けられている。一方、配線基板2の他面(下面)には、複数の接続ランド8が並んで設けられている。そして、上記はんだボール6は、これら接続ランド8の上に配置されている。その他にも、配線基板2には、パッド電極7と接続ランド8との間を電気的に接続するためのビア(貫通電極)や配線パターンなどの引回し配線部9(図1A中において模式的に示す。)が設けられている。また、配線基板2の表面は、パッド電極7や接続ランド8などを除いて、例えばソルダーレジストなどの絶縁膜(図示せず。)で覆われている。

【0014】

チップ積層体3は、配線基板2の一面とは反対側から順に、DRAM(Dynamic Random Access Memory)回路などが形成された複数(本例では4つ)のメモリーチップ(第1の半導体チップ)10a〜10dと、この上に、各メモリーチップ10a〜10dを制御するロジック回路などが形成されたロジックチップ(第2の半導体チップ)11を積層した構造を有している。

【0015】

このうち、複数のメモリーチップ10a〜10dは、平面視で矩形状を為すと共に、配線基板2よりも小さく、それぞれ一面側に複数の第1のバンプ電極(第1の接続端子)12と、他面側に複数の第2のバンプ電極(第2の接続端子)13と、これら第1のバンプ電極12と第2のバンプ電極13との間を接続する複数の貫通電極(TSV)14とを有している。そして、これら複数のメモリーチップ10a〜10dは、それぞれの一面と他面とを対向させながら、それぞれの間にある第1のバンプ電極12と第2のバンプ電極13とを接合して積層されている。

【0016】

一方、ロジックチップ11は、平面視で矩形状を為すと共に、メモリーチップ10a〜10dよりも僅かに小さく、一面側に複数の第3のバンプ電極(第3の接続端子)15と、他面側に複数の第4のバンプ電極(第4の接続端子)16と、これら第3のバンプ電極15と第4のバンプ電極16との間を接続する複数の貫通電極(TSV)17とを有している。また、第4のバンプ電極16は、例えば30μm程度のCuピラーが形成されることによって、第3のバンプ電極15より高く形成されている。これにより、ロジックチップ11に反りが発生しても、配線基板2との間で良好に接合を維持できる。

【0017】

そして、このロジックチップ11は、その一面と、その下にあるメモリーチップ10dの他面とを対向させながら、その間にある第2のバンプ電極13と第3のバンプ電極15とを第1の接合部材18を介して接合して積層されている。

【0018】

チップ積層体3は、配線基板2の一面とロジックチップ11の他面とを対向させながら、その間からはみ出して設けられた絶縁性の接着部材19を介して配線基板2の実装領域2aに接着固定されている。また、その間にある第4のバンプ電極16とパッド電極7とが第2の接合部材20を介して接合されている。この第2の接合部材20には、ワイヤーバンプを用いることができる。

【0019】

第1の封止体4は、複数のメモリーチップ10a〜10dの各隙間に充填された第1のアンダーフィル材4aと、ロジックチップ11とメモリーチップ10dとの隙間に充填された第2のアンダーフィル材4bとによって、チップ積層体3を封止している。

【0020】

第2の封止体5は、第1の封止体4で封止されたチップ積層体3の全体を覆うモールド樹脂によって、配線基板2の一面側を全面的に封止している。

【0021】

ところで、この半導体パッケージ1では、上述した複数のメモリーチップ10a〜10dを、それぞれの間にある第1のバンプ電極12と第2のバンプ電極13とを接合して積層する際に、これら第1のバンプ電極12と第2のバンプ電極13との接続性を考慮して、例えばCuの表面にSnAg層が形成された第1のバンプ電極12と、例えばCuの表面にNiAu層が形成された第2のバンプ電極13とを用いている。そして、ボンディングツールを用いて約300℃で加熱しながら荷重を加えることで、これら第1のバンプ電極12と第2のバンプ電極13とを熱圧着により接合(フリップチップボンディング)している。

【0022】

すなわち、複数のメモリーチップ10a〜10dを、それぞれの間にある第1のバンプ電極12と第2のバンプ電極13とを接合して積層する際は、第1のバンプ電極12にボンディングツールで加熱溶融される電極材料を用いる一方、第2のバンプ電極13にそれよりも融点の高い電極材料を用いている。これにより、熱圧着時に、高温のボンディングツールによって加熱された第1のバンプ電極12が溶融される温度となっても、第2のバンプ電極13は溶融しないため、ボンディングツールに付着することなく、これら第1のバンプ電極12と第2のバンプ電極13とを熱圧着により接合することができる。

【0023】

一方、ロジックチップ11は、上述したメモリーチップ10a〜10dのように多段に積層する構成とはなっておらず、例えばCuの表面にNiAu層が形成された第3のバンプ電極15及び第4のバンプ電極16を用いている。したがって、このロジックチップ11を上記複数のメモリーチップ10a〜10dの上に積層搭載する際は、ロジックチップ11の第3のバンプ電極15と、その下にあるメモリーチップ10dの第2のバンプ電極13とが対向することになる。しかしながら、これら対向する第2のバンプ電極13及び第3のバンプ電極15は、何れもCuの表面にNiAu層が形成された電極材料を用いており、上述したボンディングツールを用いて熱圧着により直接接合することは困難である。

【0024】

そこで、本発明を適用した半導体パッケージ1では、ロジックチップ11の第3のバンプ電極15と、その下にあるメモリーチップ10dの第2のバンプ電極13との間に第1の接合部材18を介在させることによって、これらCuの表面にNiAu層が形成された第2のバンプ電極13と第3のバンプ電極15とを良好に接合することが可能となっている。この第1の接合部材18には、第2のバンプ電極13と第3のバンプ電極15とを良好に接合できる材料であればよく、例えば、はんだバンプを用いることができる。

【0025】

以上のように、本発明を適用した半導体パッケージ1では、複数のメモリーチップ10a〜10dを積層し、その上にロジックチップ11を積層したチップ積層体3において、これら種類の異なるメモリーチップ10dとロジックチップ11との間で互いのバンプ電極13,15を接合する際に、これらバンプ電極13,15の間に第1の接合部材18を介在させることによって、電極材料や接合方法の制約がなく、熱による接合が困難なメモリーチップ10dとロジックチップ11のバンプ電極13,15同士を良好に接合することが可能である。

【0026】

また、本発明では、図1Bに示すように、第2のバンプ電極13と第3のバンプ電極15との互いに対向する面に、それぞれ凹部13a,15aを設けた構成としてもよい。これら凹部13a,15aは、第2のバンプ電極13及び第3のバンプ電極15の互いに対向する面の中央部分を凹ませた形状を有している。

【0027】

この場合、第2のバンプ電極13と第3のバンプ電極15との凹部13a,15aの間には、第1の接合部材18を内側に保持するのに十分な空間が形成されるため、第2のバンプ電極13と第3のバンプ電極15との接合時に加圧された第1の接合部材(はんだバンプ)18が、これらバンプ電極13,15の間から外側に流出し、ショート等の接合不良が発生することを防止できる。

【0028】

また、第1の接合部材18を形成するはんだバンプは、第2のバンプ電極13と第3のバンプ電極15との間隔が狭くなり過ぎると、接合時にAuの拡散によってAu濃度の高い部分が生じてしまい、接合強度が低下することがある。これに対して、上記凹部13,15を設けた構成では、第2のバンプ電極13と第3のバンプ電極15との間隔を十分確保できるため、Au濃度が高くなる部分を減らし、これらバンプ電極13,15間の接合強度を高めることが可能である。

【0029】

因みに、第1の接合部材18を形成するはんだバンプは、接合時にCuの拡散によって一部のはんだが硬い構造のCuSn系はんだに変わることで、バンプ電極13,15の間からの流出が防止されるものの、Cuが露出した状態からはんだを供給する方式は、Cuの酸化等の問題を招くため適用が困難である。

【0030】

凹部13a,15aの形成方法については、特に限定されないものの、例えば上記貫通電極14を形成した後に、これに連続するバンプ電極13,15をめっき形成する際のめっき条件を調整することで、その中央部分よりも周辺部分のめっき成長速度を高くし、バンプ電極13,15の中央部分に凹みを形成することが可能である。

【0031】

なお、本発明は、第2のバンプ電極13と第3のバンプ電極15との互いに対向する少なくとも一方の面に上記凹部13a,15bを設けた構成であればよい。

また、本発明では、複数のメモリーチップ10a〜10dの間にある第1のバンプ電極12と第2のバンプ電極13とを接合する場合にも、上述したはんだバンプを用いた接合方法や、更に凹部を設けるといった接合方法を適用してもよい。

【0032】

(半導体パッケージの製造方法)

次に、本発明を適用した半導体装置の製造方法として、上記図1Aに示す半導体パッケージ1の製造工程について説明する。

上記半導体パッケージ1を製造する際は、先ず、図2A〜図2Cに示すように、例えば厚みが50μm程度の上記複数のメモリーチップ10a〜10dを、それぞれの一面と他面とを対向させながら、それぞれの間にある第1のバンプ電極12と第2のバンプ電極13とを接合して積層する。

【0033】

具体的には、図2Aに示すように、吸着ステージ200上に、1層目のメモリーチップ10aを複数の第1のバンプ電極12が形成された面(一面)を下方に向けた状態で載置する。そして、このメモリーチップ10aは、吸着ステージ200に設けられた複数の吸引孔201により吸引されながら、この吸着ステージ200上に保持される。

【0034】

この状態から、図2Bに示すように、ボンディングツール300を用いて、2層目のメモリーチップ10bを1層目のメモリーチップ10a上に積層搭載(フリップチップ実装)する。このフリップチップ実装では、ボンディングツール300に設けられた吸引孔301により2層目のメモリーチップ10bを吸引保持しながら、このボンディングツール300がメモリーチップ10bを複数の第1のバンプ電極12が形成された面(一面)を下方に向けた状態で保持する。

【0035】

このボンディングツール300は、2層目のメモリーチップ10bの一面と、その下にある1層目のメモリーチップ10aの他面とを対向させながら、その間にある第1のバンプ電極12と第2のバンプ電極13との位置を合わせた状態で、2層目のメモリーチップ10bを1層目のメモリーチップ10a上に載置する。そして、この状態でボンディングツール300が約300℃で加熱しながら荷重を加えることによって、上記Cuの表面にSnAg層が形成された第1のバンプ電極12と、上記Cuの表面にNiAu層が形成された第2のバンプ電極13とを熱圧着により接合(フリップチップボンディング)する。なお、この接合時には、荷重だけでなく、超音波も印加するようにしてもよい。

【0036】

これにより、第1のバンプ電極12と第2のバンプ電極13との間が電気的に接続(フリップチップ接続)されて、2層目のメモリーチップ10bが1層目のメモリーチップ10a上にフリップチップ実装される。

【0037】

この状態から更に、図2Cに示すように、上述した1層目のメモリーチップ10a上に2層目のメモリーチップ10bをフリップチップ実装する場合と同様の方法を用いて、この2層目のメモリーチップ10b上に3層目のメモリーチップ10cと、この3層目のメモリーチップ10c上に4層目のメモリーチップ10dとを、順にフリップチップ実装する。

【0038】

次に、図3A〜図3Dに示すように、上記複数のメモリーチップ10a〜10dを積層した積層体の各隙間に第1のアンダーフィル材4aを充填し、この第1のアンダーフィル材4aによりメモリーチップ10a〜10dの積層体を封止する。

【0039】

具体的には、図3Aに示すように、塗布ステージ400上に、上記メモリーチップ10a〜10dの積層体を載置する。この塗布ステージ400の面上には、例えばフッ素系シートや、シリコーン系接着材の付いたシートなど、第1のアンダーフィル材4aとの濡れ性の悪い材料からなる塗布用シート401が貼り渡されている。

【0040】

この状態から、図3Bに示すように、液状の第1のアンダーフィル材4aを供給するディスペンサー500を用いて、上記メモリーチップ10a〜10dの積層体の端部近傍に向かって第1のアンダーフィル材4aを塗布する。このとき、第1のアンダーフィル材4aは、毛細管現象により、各メモリーチップ10a〜10dの間に形成される隙間、及びメモリーチップ10aと上記塗布用シート401との間に形成される隙間に浸透しながら充填される。また、各隙間からはみ出した第1のアンダーフィル材4aは、上記塗布用シート401によって面内に広がることが抑制される。これにより、各隙間からはみ出す第1のアンダーフィル材4aの幅を縮小することができる。

【0041】

この状態から、図3Cに示すように、第1のアンダーフィル材4aを例えば150℃程度で加熱(キュア)することで、この第1のアンダーフィル材4aを硬化させる。そして、第1のアンダーフィル材4aが硬化した後は、図3Dに示すように、この第1のアンダーフィル材4aにより封止されたメモリーチップ10a〜10dの積層体を塗布用シート401から引き剥がす。上述したように、塗布用シート401には、第1のアンダーフィル材4aとの濡れ性が悪い材料を用いているため、この第1のアンダーフィル材4aにより封止されたメモリーチップ10a〜10dの積層体は、塗布用シート401から容易に引き剥がすことが可能である。

【0042】

そして、この第1のアンダーフィル材4aにより封止されたメモリーチップ10a〜10dの積層体は、図示を省略する収納用トレイに収容されて、次工程へと送られる。なお、上記メモリーチップ10a〜10dの積層体を第1のアンダーフィル材4aにより封止する際は、リング状治具に貼り渡した塗布用シート401に上記メモリーチップ10a〜10dの積層体を搭載して、このリング状治具の内側に第1のアンダーフィル材4aを供給するようにしてもよい。

【0043】

次に、図4A〜図4Cに示すように、上記積層体の最上層に位置するメモリーチップ10dの第2のバンプ電極13の上に第1の接合部材18を配置する。

【0044】

具体的には、図4Aに示すように、上記第1のアンダーフィル材4aにより封止されたメモリーチップ10a〜10dの積層体の上に印刷用マスク600を配置する。この印刷用マスク600には、メモリーチップ10dの第2のバンプ電極13に対応した位置に孔部601が設けられている。そして、この印刷用マスク600の上に、上記第1の接合部材18となるはんだペーストPを塗布した後、スキージ602を用いてスクリーン印刷を行う。

【0045】

すなわち、図4Aから図4Bに示すように、スキージ602を印刷用マスク600上で移動させながら、この印刷用マスク600上に塗布されたはんだペーストPを孔部601に埋め込み配置する。その後、所定の温度でリフローすることで、図4Cに示すように、メモリーチップ10dの第2のバンプ電極13の上に上記はんだバンプからなる第1の接合部材18が配置される。

【0046】

次に、図5Aに示すように、例えば厚みが50μm程度の上記ロジックチップ11を、その一面と、その下にあるメモリーチップ10dの他面とを対向させながら、その間にある第2のバンプ電極13と第3のバンプ電極15とを第1の接合部材18を介して接合して積層する。

【0047】

具体的には、1層目のメモリーチップ10aを下方に向けた状態で、上記第1のアンダーフィル材4aにより封止されたメモリーチップ10a〜10dの積層体を吸着ステージ200上に載置する。そして、この積層体は、吸着ステージ200の複数の吸引孔201により吸引されながら、この吸着ステージ200上に保持される。

【0048】

この状態から、ボンディングツール300を用いて、ロジックチップ11を最上層(4層目)に位置するメモリーチップ10d上に積層搭載(フリップチップ実装)する。このフリップチップ実装では、ボンディングツール300の吸引孔301によりロジックチップ11を吸引保持しながら、このボンディングツール300がロジックチップ11を複数の第3のバンプ電極15が形成された面(一面)を下方に向けた状態で保持する。

【0049】

このボンディングツール300は、ロジックチップ11の一面と、その下にある4層目のメモリーチップ10dの他面とを対向させながら、その間にある第3のバンプ電極13と第3のバンプ電極15との位置を合わせた状態で、ロジックチップ11を4層目のメモリーチップ10d上に載置する。そして、この状態でボンディングツール300が約300℃で加熱しながら荷重を加えることによって、上記Cuの表面にNiAu層が形成された第2のバンプ電極13と、上記Cuの表面にNiAu層が形成された第3のバンプ電極15とを第1の接合部材(はんだバンプ)18を介して熱圧着により接合(フリップチップボンディング)する。なお、この接合時には、荷重だけでなく、超音波も印加するようにしてもよい。

【0050】

これにより、第2のバンプ電極13と第3のバンプ電極15との間が第1の接合部材(はんだバンプ)18を介して電気的に接続(フリップチップ接続)されて、ロジックチップ11が4層目のメモリーチップ10d上にフリップチップ実装される。

【0051】

また、このフリップチップ実装後は、図5Bに示すように、ロジックチップ11と4層目のメモリーチップ10dとの間の隙間を広げるようにボンディングツール300を上方へと移動させる。これにより、第1の接合部材18を形成するはんだバンプの量を多めにしても、隣接するバンプ電極13,15に広がりショートを引き起こすリスクを低減できる。また、はんだバンプの量を多めにすることで、ロジックチップ11に反りが発生しても良好に接合を維持できる。

【0052】

また、本発明では、上記図1Bに示すように、第2のバンプ電極13と第3のバンプ電極15との互いに対向する少なくとも一方の面に、上述した凹部13a,15aを形成しておくことで、これら第2のバンプ電極13と第3のバンプ電極15とを第1の接合部材18を介して接合する際に、その接合強度を更に高めることが可能である。

【0053】

次に、図6A及び図6Bに示すように、ロジックチップ11と4層目のメモリーチップ10dとの隙間に第2のアンダーフィル材4bを充填し、この第2のアンダーフィル材4bによりロジックチップ11を封止する。

【0054】

具体的には、図6Aに示すように、塗布ステージ400の塗布用シート401上に、上記メモリーチップ10a〜10d及びロジックチップ11の積層体を載置した後、液状の第2のアンダーフィル材4bを供給するディスペンサー700を用いて、ロジックチップ11の端部近傍に向かって第2のアンダーフィル材4bを塗布する。

【0055】

このとき、第2のアンダーフィル材4bは、毛細管現象により、ロジックチップ11と4層目のメモリーチップ10dとの間に形成される隙間に浸透しながら充填される。また、ロジックチップ11は、4層目のメモリーチップ10dよりも小さいため、隙間からはみ出した第2のアンダーフィル材4bは、メモリーチップ10d上に留まることになる。

【0056】

この状態から、第2のアンダーフィル材4bを例えば150℃程度で加熱(キュア)することで、この第2のアンダーフィル材4bを硬化させる。そして、第2のアンダーフィル材4bが硬化した後は、図3Bに示すように、チップ積層体3を上記塗布用シート401から引き剥がす。なお、この場合もチップ積層体3を上記塗布用シート401から容易に引き剥がすことが可能である。そして、このチップ積層体3は、図示を省略する収納用トレイに収容されて、次工程へと送られる。

【0057】

次に、図7A〜図7Cに示すように、上記配線基板2となる部分が複数並んで形成された母配線基板100を用意する。この母配線基板100は、例えば厚み0.14mm程度のガラスエポキシ配線基板からなり、上記配線基板2となる部分がマトリックス状に複数並んで形成されると共に、最終的にダイシングラインLに沿って切断することで、上記配線基板2となる部分を個々の配線基板2として切り出すことが可能となっている。また、上記配線基板2となる部分の各パッド電極7上には、上記第2の接合部材20となるワイヤーバンプが配置されている。

【0058】

そして、この母配線基板100の一面に、上記チップ積層体3を上記配線基板2となる部分毎に実装する。具体的には、図7Aに示すように、NCP(Non Conductive Paste)と呼ばれる液状の接着部材19を供給するディスペンサー800を用いて、母配線基板100上に、上記配線基板2となる部分の実装領域2a毎に液状の接着部材19を塗布する。

【0059】

この状態から、図7Bに示すように、ボンディングツール300を用いて、チップ積層体3を母配線基板100の上記配線基板2となる部分の実装領域2aにフリップ実装する。このフリップチップ実装では、ボンディングツール300の吸引孔301によりチップ積層体3を吸引保持しながら、このボンディングツール300がチップ積層体3をロジックチップ11を下方に向けた状態で保持する。

【0060】

このボンディングツール300は、ロジックチップ11と上記配線基板2となる部分の実装領域2aとを対向させながら、その間にある第4のバンプ電極16とパッド電極7との位置を合わせた状態で、チップ積層体3を上記配線基板2となる部分の実装領域2a上に載置する。そして、この状態でボンディングツール300が約300℃で加熱しながら荷重を加えることによって、第4のバンプ電極16とパッド電極7とを第2の接合部材(ワイヤーバンプ)20を介して熱圧着により接合(フリップチップボンディング)する。なお、この接合時には、荷重だけでなく、超音波も印加するようにしてもよい。

【0061】

これにより、第4のバンプ電極16とパッド電極7との間が第2の接合部材(ワイヤーバンプ)20を介して電気的に接続(フリップチップ接続)されて、チップ積層体3が母配線基板100の配線基板2となる部分の実装領域2aにフリップチップ実装される。

【0062】

また、接着部材19は、図7Cに示すように、配線基板2の一面とロジックチップ11の他面との間からはみ出した状態で硬化される。これにより、チップ積層体3は、この接着部材19を介して母配線基板100の配線基板2となる部分の実装領域2aに接着固定される。

【0063】

ここで、チップ積層体3を封止する第1の封止体4(第1のアンダーフィル材4a及び第2のアンダーフィル材4b)は、このチップ積層体3の各隙間からはみ出す第1及び第2のアンダーフィル材4a,4bの幅が下層側から上層側に向かって漸次大きくなる、いわゆる逆テーパー形状を有している。この場合、配線基板2の一面とロジックチップ11の他面との間からはみ出した接着部材19の這い上がりを防止できるため、ボンディングツール300への接着部材19の付着に起因するチップ積層体3の割れや接合不良等の発生を低減できる。

【0064】

次に、図8に示すように、チップ積層体3を覆うように母配線基板100の一面側を上記第2の封止体5となるモールド樹脂で封止する。具体的には、トランスファモールド装置(図示せず。)を用いる。このトランスファモールド装置は、母配線基板100の他面側を保持する下金型(固定型)と、母配線基板100の一面側に対向してモールド樹脂が充填されるキャビティ空間を形成すると共に、下金型に対して相対的に接離自在に移動される上金型(可動型)とからなる一対の成型金型を備える。

【0065】

そして、このトランスファモールド装置の成形金型に、上記チップ積層体3が実装された母配線基板100をセットした後、成形金型内のキャビティ空間内に加熱溶融されたモールド樹脂を注入する。このモールド樹脂には、例えばエポキシ樹脂等の熱硬化性樹脂が用いられる。

【0066】

そして、この状態で、モールド樹脂を所定の温度(例えば180℃程度)で加熱(キュア)することで、モールド樹脂を硬化させる。さらに、所定の温度でベークすることで、モールド樹脂が完全に硬化される。これにより、母配線基板100の一面側が上記第2の封止体5となるモールド樹脂で完全に封止される。

【0067】

本発明では、上述したように、第1の封止体4(第1のアンダーフィル材4a及び第2のアンダーフィル材4b)で封止された複数のチップ積層体3を母配線基板100上に実装した後、この母配線基板100上を第2の封止体5で一括的に封止することで、ボイド(気泡)の発生を低減できる。

【0068】

次に、図9に示すように、母配線基板100の各配線基板2となる部分に設けられた上記接続ランド8上に、上記はんだボール6を配置する。具体的には、複数の吸着孔(図示せず。)が形成されたボールマウンターのマウントツール900を用いて、複数のはんだボール6をマウントツール900で吸着保持しながら、これら複数のはんだボール6にフラックスを転写形成した後、母配線基板100の各配線基板2となる部分毎にはんだボール6を接続ランド7上に載置する。そして、母配線基板100の全ての配線基板2となる部分にはんだボール6を載置した後、この母配線基板100をリフローする。これにより、母配線基板100の各配線基板2となる部分の接続ランド8上に、はんだボール6が配置される。

【0069】

次に、図10に示すように、母配線基板100を配線基板2となる部分毎に切断することによって個々の半導体パッケージ1に分割する。具体的には、母配線基板100の第2の封止体5側にダイシングテープ1000を貼着した後、ダイシングブレード1001を用いて母配線基板100をダイシングテープ1000とは反対側からダイシングラインLに沿って切断する。これにより、半導体パッケージ1毎に分割される。そして、これら半導体パッケージ1をダイシングテープ1000から引き剥がすことで、上記図1Aに示す半導体パッケージ1を得ることができる。

【0070】

以上のように、本発明を適用した半導体パッケージ1の製造方法では、上述したように、ロジックチップ11の第3のバンプ電極15と、その下にあるメモリーチップ10dの第2のバンプ電極13との間に第1の接合部材18を介在させることによって、電極材料や接合方法の制約がなく、熱による接合が困難なメモリーチップ10dとロジックチップ11のバンプ電極13,15同士を良好に接合することが可能である。

【0071】

なお、本発明は、上記実施形態のものに必ずしも限定されるものではなく、本発明の趣旨を逸脱しない範囲において種々の変更を加えることが可能である。なお、以下の説明では、上記半導体パッケージ1と同等の部位については、説明を省略すると共に、図面において同じ符号を付すものとする。

【0072】

例えば、本発明では、図11A〜図11Dに示すように、複数のメモリーチップ10a〜10d及びロジックチップ11を積層した後に、この積層体の各隙間に上記第1の封止体4となるアンダーフィル材を充填するようにしてもよい。この場合、製造工程を簡略化することが可能である。

【0073】

具体的には、先ず、図11Aに示すように、上記図2A〜図2Cに示す場合と同様にして、吸着ステージ200上に、複数のメモリーチップ10a〜10dを、それぞれの一面と他面とを対向させながら、それぞれの間にある第1のバンプ電極12と第2のバンプ電極13とを接合して積層する。

【0074】

次に、図11Bに示すように、上記図4A〜図4Cに示す場合と同様にして、最上層に位置するメモリーチップ10dの第2のバンプ電極13の上に第1の接合部材18を配置する。

【0075】

次に、図11Cに示すように、上記図5A及び図5Bに示す場合と同様にして、ロジックチップ11を、その一面と、その下にあるメモリーチップ10dの他面とを対向させながら、その間にある第2のバンプ電極13と第3のバンプ電極15とを第1の接合部材18を介して接合して積層した後、ボンディングツール300(図示せず。)を上方へと移動させながら、ロジックチップ11と4層目のメモリーチップ11dとの間の隙間を広げるようにする。

【0076】

次に、図11Dに示すように、上記複数のメモリーチップ10a〜10d及びロジックチップ11を積層した積層体の各隙間にアンダーフィル材を充填し、このアンダーフィル材(第1の封止体4)によりチップ積層体3を封止する。

【0077】

また、上記実施形態では、母配線基板100上に接着部材19を塗布した後、チップ積層体3を実装するようにしたが、母配線基板100上にチップ積層体3を実装した後に、その間に接着部材19を充填するようにしてもよい。この場合、ロジックチップ11の第4のバンプ電極16を高く形成することで、チップ積層体3と母配線基板100との隙間を広く確保することができ、接着部材19の充填性を向上できる。

【0078】

なお、上記チップ積層体3は、4つのメモリーチップ10a〜10dとロジックチップ11を積層した構成となっているが、メモリーチップの積層数については2つ以上であればよく、このような構成に必ずしも限定されるものではない。

【0079】

また、上記チップ積層体3は、メモリーチップとロジックチップとを組み合わせた構成となっているが、種類の異なるデバイスを直接接続するチップ積層体であればどのようなチップの組合せ、又はデバイスチップとSiインターポーザの組合せに、本発明を適用してもよい。

【0080】

また、本発明は、上記BGA型の半導体パッケージ1に限らず、例えば、LGA(Land Grid Array)型やCSP(Chip Size Package)型などの他の半導体パッケージにも適用可能である。

【符号の説明】

【0081】

1…半導体パッケージ(半導体装置) 2…配線基板 2a…実装領域 3…チップ積層体 4…第1の封止体 4a…第1のアンダーフィル材 4b…第2のアンダーフィル材 5…第2の封止体 6…はんだボール(外部接続端子) 7…パッド電極(第5の接続端子) 8…接続ランド 9…引回し配線部 10a〜10d…メモリーチップ(第1の半導体チップ) 11…ロジックチップ(第2の半導体チップ) 12…第1のバンプ電極(第1の接続端子) 13…第2のバンプ電極(第2の接続端子) 13a…凹部 14…貫通電極 15…第3のバンプ電極(第3の接続端子) 15a…凹部 16…第4のバンプ電極(第4の接続端子) 17…貫通電極 18…第1の接合部材 19…接着部材 20…第2の接合部材 100…母配線基板

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、半導体チップの集積度が年々向上し、それに伴ってチップサイズの大型化や、配線の微細化及び多層化などが進んでいる。一方、高密度実装化のためには、パッケージサイズの小型化及び薄型化が必要となっている。

【0003】

このような要求に対して、MCP(Multi Chip Package)と呼ばれる1つの配線基板の上に複数の半導体チップを高密度実装する技術が開発されている。その中でも、TSV(Through Silicon Via)と呼ばれる貫通電極を有する半導体チップを積層したチップ積層体を配線基板の一面に実装したCoC(Chip on Chip)型の半導体パッケージが注目されている(例えば、特許文献1を参照。)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−214220号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、上述したCoC型の半導体パッケージでは、例えばDRAM(Dynamic Random Access Memory)回路などが形成された複数のメモリーチップを積層したチップ積層体の上に更に、このメモリーチップを制御するロジック回路などが形成されたロジックチップを積層搭載することが検討されている。

【0006】

しかしながら、メモリーチップとロジックチップとの種類の異なる半導体チップの間では、互いの接続端子(バンプ電極)を構成する電極材料の制約などによって、これら接続端子の間で接合不良が生じる虞があった。

【課題を解決するための手段】

【0007】

本発明に係る半導体装置は、少なくとも配線基板と、この配線基板の一面に実装されたチップ積層体とを備える半導体パッケージであって、チップ積層体は、配線基板の一面とは反対側から順に、一面側に第1の接続端子と他面側に第2の接続端子とを有する複数の第1の半導体チップを、それぞれの一面と他面とを対向させながら、それぞれの間にある第1の接続端子と第2の接続端子とを接合して積層し、その上に、一面側に第3の接続端子と他面側に第4の接続端子とを有する第2の半導体チップを、その一面と、その下にある第1の半導体チップの他面とを対向させながら、その間にある第2の接続端子と第3の接続端子とを接合部材を介して接合して積層した構造を有することを特徴とする。

【0008】

また、本発明に係る半導体装置の製造方法は、少なくとも配線基板と、この配線基板の一面に実装されたチップ積層体とを備える半導体パッケージの製造方法であって、チップ積層体を形成する際に、一面側に第1の接続端子と他面側に第2の接続端子とを有する複数の第1の半導体チップを、それぞれの一面と他面とを対向させながら、それぞれの間にある第1の接続端子と第2の接続端子とを接合して積層する工程と、積層された複数の第1の半導体チップの最上層に位置する第1の半導体チップの第2の接続端子の上に接合部材を配置する工程と、その上に、一面側に第3の接続端子と他面側に第4の接続端子とを有する第2の半導体チップを、その一面と、その下にある第1の半導体チップの他面とを対向させながら、その間にある第2の接続端子と第3の接続端子とを接合部材を介して接合して積層する工程とを含むことを特徴とする。

【発明の効果】

【0009】

以上のように、本発明では、複数の第1の半導体チップを積層し、その上に第2の半導体チップを積層したチップ積層体において、種類の異なる第1の半導体チップと第2の半導体チップとの間で互いの接続端子を接合する際に、これら接続端子の間に接合部材を介在させることによって、電極材料や接合方法などの制約がなく、熱による接合が困難な半導体チップの接続端子同士を良好に接合することが可能となる。

【図面の簡単な説明】

【0010】

【図1A】本発明を適用した半導体パッケージの一例を示す断面図である。

【図1B】図1Aに示す半導体パッケージの要部を拡大して示す断面図である。

【図2A】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップを積層する工程を順に示す断面図である。

【図2B】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップを積層する工程を順に示す断面図である。

【図2C】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップを積層する工程を順に示す断面図である。

【図3A】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップの間に第1のアンダーフィル材を充填する工程を順に示す断面図である。

【図3B】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップの間に第1のアンダーフィル材を充填する工程を順に示す断面図である。

【図3C】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップの間に第1のアンダーフィル材を充填する工程を順に示す断面図である。

【図3D】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップの間に第1のアンダーフィル材を充填する工程を順に示す断面図である。

【図4A】図1Aに示す半導体パッケージの製造工程として、第1の接合部材を配置する工程を順に示す断面図である。

【図4B】図1Aに示す半導体パッケージの製造工程として、第1の接合部材を配置する工程を順に示す断面図である。

【図4C】図1Aに示す半導体パッケージの製造工程として、第1の接合部材を配置する工程を順に示す断面図である。

【図5A】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップの上にロジックチップを積層する工程を順に示す断面図である。

【図5B】図1Aに示す半導体パッケージの製造工程として、複数のメモリーチップの上にロジックチップを積層する工程を順に示す断面図である。

【図6A】図1Aに示す半導体パッケージの製造工程として、ロジックチップとメモリーチップとの間に第2のアンダーフィル材を充填する工程を順に示す断面図である。

【図6B】図1Aに示す半導体パッケージの製造工程として、ロジックチップとメモリーチップとの間に第2のアンダーフィル材を充填する工程を順に示す断面図である。

【図7A】図1Aに示す半導体パッケージの製造工程として、チップ積層体を母配線基板上に実装する工程を順に示す断面図である。

【図7B】図1Aに示す半導体パッケージの製造工程として、チップ積層体を母配線基板上に実装する工程を順に示す断面図である。

【図7C】図1Aに示す半導体パッケージの製造工程として、チップ積層体を母配線基板上に実装する工程を順に示す断面図である。

【図8】図1Aに示す半導体パッケージの製造工程として、チップ積層体を第2の封止体で封止する工程を示す断面図である。

【図9】図1Aに示す半導体パッケージの製造工程として、はんだボールを配置する工程を示す断面図である。

【図10】図1Aに示す半導体パッケージの製造工程として、個々の半導体パッケージに分割する工程を示す断面図である。

【図11A】図1Aに示す半導体パッケージの別の製造工程として、複数のメモリーチップ及びロジックチップを積層した後、第1の封止体で封止する工程を順に示す断面図である。

【図11B】図1Aに示す半導体パッケージの別の製造工程として、複数のメモリーチップ及びロジックチップを積層して、第1の封止体で封止する工程を順に示す断面図である。

【図11C】図1Aに示す半導体パッケージの別の製造工程として、複数のメモリーチップ及びロジックチップを積層して、第1の封止体で封止する工程を順に示す断面図である。

【図11D】図1Aに示す半導体パッケージの別の製造工程として、複数のメモリーチップ及びロジックチップを積層して、第1の封止体で封止する工程を順に示す断面図である。

【発明を実施するための形態】

【0011】

以下、本発明を適用した半導体装置及びその製造方法について、図面を参照して詳細に説明する。

なお、以下の説明で用いる図面は、特徴をわかりやすくするために、便宜上特徴となる部分を拡大して示している場合があり、各構成要素の寸法比率などが実際と同じであるとは限らない。また、以下の説明において例示される材料、寸法等は一例であって、本発明はそれらに必ずしも限定されるものではなく、その要旨を変更しない範囲で適宜変更して実施することが可能である。

【0012】

(半導体装置)

先ず、本発明を適用した半導体装置の一例として、図1Aに示すCoC型の半導体パッケージ1について説明する。

この半導体パッケージ1は、図1Aに示すように、配線基板2と、この配線基板2の一面(上面)に実装されたチップ積層体3と、このチップ積層体3を覆う第1の封止体4と、この第1の封止体4を覆う第2の封止体5と、配線基板2の他面に配置された複数のはんだボール(外部接続端子)6とを備えることによって、BGA(Ball Grid Array)と呼ばれるパッケージ構造を有している。

【0013】

配線基板2は、平面視で矩形状を為すプリント配線板からなり、この配線基板2の上面中央部には、チップ積層体3が実装される実装領域2aが設けられている。また、配線基板2の実装領域2aには、複数のパッド電極(第5の接続端子)7が並んで設けられている。一方、配線基板2の他面(下面)には、複数の接続ランド8が並んで設けられている。そして、上記はんだボール6は、これら接続ランド8の上に配置されている。その他にも、配線基板2には、パッド電極7と接続ランド8との間を電気的に接続するためのビア(貫通電極)や配線パターンなどの引回し配線部9(図1A中において模式的に示す。)が設けられている。また、配線基板2の表面は、パッド電極7や接続ランド8などを除いて、例えばソルダーレジストなどの絶縁膜(図示せず。)で覆われている。

【0014】

チップ積層体3は、配線基板2の一面とは反対側から順に、DRAM(Dynamic Random Access Memory)回路などが形成された複数(本例では4つ)のメモリーチップ(第1の半導体チップ)10a〜10dと、この上に、各メモリーチップ10a〜10dを制御するロジック回路などが形成されたロジックチップ(第2の半導体チップ)11を積層した構造を有している。

【0015】

このうち、複数のメモリーチップ10a〜10dは、平面視で矩形状を為すと共に、配線基板2よりも小さく、それぞれ一面側に複数の第1のバンプ電極(第1の接続端子)12と、他面側に複数の第2のバンプ電極(第2の接続端子)13と、これら第1のバンプ電極12と第2のバンプ電極13との間を接続する複数の貫通電極(TSV)14とを有している。そして、これら複数のメモリーチップ10a〜10dは、それぞれの一面と他面とを対向させながら、それぞれの間にある第1のバンプ電極12と第2のバンプ電極13とを接合して積層されている。

【0016】

一方、ロジックチップ11は、平面視で矩形状を為すと共に、メモリーチップ10a〜10dよりも僅かに小さく、一面側に複数の第3のバンプ電極(第3の接続端子)15と、他面側に複数の第4のバンプ電極(第4の接続端子)16と、これら第3のバンプ電極15と第4のバンプ電極16との間を接続する複数の貫通電極(TSV)17とを有している。また、第4のバンプ電極16は、例えば30μm程度のCuピラーが形成されることによって、第3のバンプ電極15より高く形成されている。これにより、ロジックチップ11に反りが発生しても、配線基板2との間で良好に接合を維持できる。

【0017】

そして、このロジックチップ11は、その一面と、その下にあるメモリーチップ10dの他面とを対向させながら、その間にある第2のバンプ電極13と第3のバンプ電極15とを第1の接合部材18を介して接合して積層されている。

【0018】

チップ積層体3は、配線基板2の一面とロジックチップ11の他面とを対向させながら、その間からはみ出して設けられた絶縁性の接着部材19を介して配線基板2の実装領域2aに接着固定されている。また、その間にある第4のバンプ電極16とパッド電極7とが第2の接合部材20を介して接合されている。この第2の接合部材20には、ワイヤーバンプを用いることができる。

【0019】

第1の封止体4は、複数のメモリーチップ10a〜10dの各隙間に充填された第1のアンダーフィル材4aと、ロジックチップ11とメモリーチップ10dとの隙間に充填された第2のアンダーフィル材4bとによって、チップ積層体3を封止している。

【0020】

第2の封止体5は、第1の封止体4で封止されたチップ積層体3の全体を覆うモールド樹脂によって、配線基板2の一面側を全面的に封止している。

【0021】

ところで、この半導体パッケージ1では、上述した複数のメモリーチップ10a〜10dを、それぞれの間にある第1のバンプ電極12と第2のバンプ電極13とを接合して積層する際に、これら第1のバンプ電極12と第2のバンプ電極13との接続性を考慮して、例えばCuの表面にSnAg層が形成された第1のバンプ電極12と、例えばCuの表面にNiAu層が形成された第2のバンプ電極13とを用いている。そして、ボンディングツールを用いて約300℃で加熱しながら荷重を加えることで、これら第1のバンプ電極12と第2のバンプ電極13とを熱圧着により接合(フリップチップボンディング)している。

【0022】

すなわち、複数のメモリーチップ10a〜10dを、それぞれの間にある第1のバンプ電極12と第2のバンプ電極13とを接合して積層する際は、第1のバンプ電極12にボンディングツールで加熱溶融される電極材料を用いる一方、第2のバンプ電極13にそれよりも融点の高い電極材料を用いている。これにより、熱圧着時に、高温のボンディングツールによって加熱された第1のバンプ電極12が溶融される温度となっても、第2のバンプ電極13は溶融しないため、ボンディングツールに付着することなく、これら第1のバンプ電極12と第2のバンプ電極13とを熱圧着により接合することができる。

【0023】

一方、ロジックチップ11は、上述したメモリーチップ10a〜10dのように多段に積層する構成とはなっておらず、例えばCuの表面にNiAu層が形成された第3のバンプ電極15及び第4のバンプ電極16を用いている。したがって、このロジックチップ11を上記複数のメモリーチップ10a〜10dの上に積層搭載する際は、ロジックチップ11の第3のバンプ電極15と、その下にあるメモリーチップ10dの第2のバンプ電極13とが対向することになる。しかしながら、これら対向する第2のバンプ電極13及び第3のバンプ電極15は、何れもCuの表面にNiAu層が形成された電極材料を用いており、上述したボンディングツールを用いて熱圧着により直接接合することは困難である。

【0024】

そこで、本発明を適用した半導体パッケージ1では、ロジックチップ11の第3のバンプ電極15と、その下にあるメモリーチップ10dの第2のバンプ電極13との間に第1の接合部材18を介在させることによって、これらCuの表面にNiAu層が形成された第2のバンプ電極13と第3のバンプ電極15とを良好に接合することが可能となっている。この第1の接合部材18には、第2のバンプ電極13と第3のバンプ電極15とを良好に接合できる材料であればよく、例えば、はんだバンプを用いることができる。

【0025】

以上のように、本発明を適用した半導体パッケージ1では、複数のメモリーチップ10a〜10dを積層し、その上にロジックチップ11を積層したチップ積層体3において、これら種類の異なるメモリーチップ10dとロジックチップ11との間で互いのバンプ電極13,15を接合する際に、これらバンプ電極13,15の間に第1の接合部材18を介在させることによって、電極材料や接合方法の制約がなく、熱による接合が困難なメモリーチップ10dとロジックチップ11のバンプ電極13,15同士を良好に接合することが可能である。

【0026】

また、本発明では、図1Bに示すように、第2のバンプ電極13と第3のバンプ電極15との互いに対向する面に、それぞれ凹部13a,15aを設けた構成としてもよい。これら凹部13a,15aは、第2のバンプ電極13及び第3のバンプ電極15の互いに対向する面の中央部分を凹ませた形状を有している。

【0027】

この場合、第2のバンプ電極13と第3のバンプ電極15との凹部13a,15aの間には、第1の接合部材18を内側に保持するのに十分な空間が形成されるため、第2のバンプ電極13と第3のバンプ電極15との接合時に加圧された第1の接合部材(はんだバンプ)18が、これらバンプ電極13,15の間から外側に流出し、ショート等の接合不良が発生することを防止できる。

【0028】

また、第1の接合部材18を形成するはんだバンプは、第2のバンプ電極13と第3のバンプ電極15との間隔が狭くなり過ぎると、接合時にAuの拡散によってAu濃度の高い部分が生じてしまい、接合強度が低下することがある。これに対して、上記凹部13,15を設けた構成では、第2のバンプ電極13と第3のバンプ電極15との間隔を十分確保できるため、Au濃度が高くなる部分を減らし、これらバンプ電極13,15間の接合強度を高めることが可能である。

【0029】

因みに、第1の接合部材18を形成するはんだバンプは、接合時にCuの拡散によって一部のはんだが硬い構造のCuSn系はんだに変わることで、バンプ電極13,15の間からの流出が防止されるものの、Cuが露出した状態からはんだを供給する方式は、Cuの酸化等の問題を招くため適用が困難である。

【0030】

凹部13a,15aの形成方法については、特に限定されないものの、例えば上記貫通電極14を形成した後に、これに連続するバンプ電極13,15をめっき形成する際のめっき条件を調整することで、その中央部分よりも周辺部分のめっき成長速度を高くし、バンプ電極13,15の中央部分に凹みを形成することが可能である。

【0031】

なお、本発明は、第2のバンプ電極13と第3のバンプ電極15との互いに対向する少なくとも一方の面に上記凹部13a,15bを設けた構成であればよい。

また、本発明では、複数のメモリーチップ10a〜10dの間にある第1のバンプ電極12と第2のバンプ電極13とを接合する場合にも、上述したはんだバンプを用いた接合方法や、更に凹部を設けるといった接合方法を適用してもよい。

【0032】

(半導体パッケージの製造方法)

次に、本発明を適用した半導体装置の製造方法として、上記図1Aに示す半導体パッケージ1の製造工程について説明する。

上記半導体パッケージ1を製造する際は、先ず、図2A〜図2Cに示すように、例えば厚みが50μm程度の上記複数のメモリーチップ10a〜10dを、それぞれの一面と他面とを対向させながら、それぞれの間にある第1のバンプ電極12と第2のバンプ電極13とを接合して積層する。

【0033】

具体的には、図2Aに示すように、吸着ステージ200上に、1層目のメモリーチップ10aを複数の第1のバンプ電極12が形成された面(一面)を下方に向けた状態で載置する。そして、このメモリーチップ10aは、吸着ステージ200に設けられた複数の吸引孔201により吸引されながら、この吸着ステージ200上に保持される。

【0034】

この状態から、図2Bに示すように、ボンディングツール300を用いて、2層目のメモリーチップ10bを1層目のメモリーチップ10a上に積層搭載(フリップチップ実装)する。このフリップチップ実装では、ボンディングツール300に設けられた吸引孔301により2層目のメモリーチップ10bを吸引保持しながら、このボンディングツール300がメモリーチップ10bを複数の第1のバンプ電極12が形成された面(一面)を下方に向けた状態で保持する。

【0035】

このボンディングツール300は、2層目のメモリーチップ10bの一面と、その下にある1層目のメモリーチップ10aの他面とを対向させながら、その間にある第1のバンプ電極12と第2のバンプ電極13との位置を合わせた状態で、2層目のメモリーチップ10bを1層目のメモリーチップ10a上に載置する。そして、この状態でボンディングツール300が約300℃で加熱しながら荷重を加えることによって、上記Cuの表面にSnAg層が形成された第1のバンプ電極12と、上記Cuの表面にNiAu層が形成された第2のバンプ電極13とを熱圧着により接合(フリップチップボンディング)する。なお、この接合時には、荷重だけでなく、超音波も印加するようにしてもよい。

【0036】

これにより、第1のバンプ電極12と第2のバンプ電極13との間が電気的に接続(フリップチップ接続)されて、2層目のメモリーチップ10bが1層目のメモリーチップ10a上にフリップチップ実装される。

【0037】

この状態から更に、図2Cに示すように、上述した1層目のメモリーチップ10a上に2層目のメモリーチップ10bをフリップチップ実装する場合と同様の方法を用いて、この2層目のメモリーチップ10b上に3層目のメモリーチップ10cと、この3層目のメモリーチップ10c上に4層目のメモリーチップ10dとを、順にフリップチップ実装する。

【0038】

次に、図3A〜図3Dに示すように、上記複数のメモリーチップ10a〜10dを積層した積層体の各隙間に第1のアンダーフィル材4aを充填し、この第1のアンダーフィル材4aによりメモリーチップ10a〜10dの積層体を封止する。

【0039】

具体的には、図3Aに示すように、塗布ステージ400上に、上記メモリーチップ10a〜10dの積層体を載置する。この塗布ステージ400の面上には、例えばフッ素系シートや、シリコーン系接着材の付いたシートなど、第1のアンダーフィル材4aとの濡れ性の悪い材料からなる塗布用シート401が貼り渡されている。

【0040】

この状態から、図3Bに示すように、液状の第1のアンダーフィル材4aを供給するディスペンサー500を用いて、上記メモリーチップ10a〜10dの積層体の端部近傍に向かって第1のアンダーフィル材4aを塗布する。このとき、第1のアンダーフィル材4aは、毛細管現象により、各メモリーチップ10a〜10dの間に形成される隙間、及びメモリーチップ10aと上記塗布用シート401との間に形成される隙間に浸透しながら充填される。また、各隙間からはみ出した第1のアンダーフィル材4aは、上記塗布用シート401によって面内に広がることが抑制される。これにより、各隙間からはみ出す第1のアンダーフィル材4aの幅を縮小することができる。

【0041】

この状態から、図3Cに示すように、第1のアンダーフィル材4aを例えば150℃程度で加熱(キュア)することで、この第1のアンダーフィル材4aを硬化させる。そして、第1のアンダーフィル材4aが硬化した後は、図3Dに示すように、この第1のアンダーフィル材4aにより封止されたメモリーチップ10a〜10dの積層体を塗布用シート401から引き剥がす。上述したように、塗布用シート401には、第1のアンダーフィル材4aとの濡れ性が悪い材料を用いているため、この第1のアンダーフィル材4aにより封止されたメモリーチップ10a〜10dの積層体は、塗布用シート401から容易に引き剥がすことが可能である。

【0042】

そして、この第1のアンダーフィル材4aにより封止されたメモリーチップ10a〜10dの積層体は、図示を省略する収納用トレイに収容されて、次工程へと送られる。なお、上記メモリーチップ10a〜10dの積層体を第1のアンダーフィル材4aにより封止する際は、リング状治具に貼り渡した塗布用シート401に上記メモリーチップ10a〜10dの積層体を搭載して、このリング状治具の内側に第1のアンダーフィル材4aを供給するようにしてもよい。

【0043】

次に、図4A〜図4Cに示すように、上記積層体の最上層に位置するメモリーチップ10dの第2のバンプ電極13の上に第1の接合部材18を配置する。

【0044】

具体的には、図4Aに示すように、上記第1のアンダーフィル材4aにより封止されたメモリーチップ10a〜10dの積層体の上に印刷用マスク600を配置する。この印刷用マスク600には、メモリーチップ10dの第2のバンプ電極13に対応した位置に孔部601が設けられている。そして、この印刷用マスク600の上に、上記第1の接合部材18となるはんだペーストPを塗布した後、スキージ602を用いてスクリーン印刷を行う。

【0045】

すなわち、図4Aから図4Bに示すように、スキージ602を印刷用マスク600上で移動させながら、この印刷用マスク600上に塗布されたはんだペーストPを孔部601に埋め込み配置する。その後、所定の温度でリフローすることで、図4Cに示すように、メモリーチップ10dの第2のバンプ電極13の上に上記はんだバンプからなる第1の接合部材18が配置される。

【0046】

次に、図5Aに示すように、例えば厚みが50μm程度の上記ロジックチップ11を、その一面と、その下にあるメモリーチップ10dの他面とを対向させながら、その間にある第2のバンプ電極13と第3のバンプ電極15とを第1の接合部材18を介して接合して積層する。

【0047】

具体的には、1層目のメモリーチップ10aを下方に向けた状態で、上記第1のアンダーフィル材4aにより封止されたメモリーチップ10a〜10dの積層体を吸着ステージ200上に載置する。そして、この積層体は、吸着ステージ200の複数の吸引孔201により吸引されながら、この吸着ステージ200上に保持される。

【0048】

この状態から、ボンディングツール300を用いて、ロジックチップ11を最上層(4層目)に位置するメモリーチップ10d上に積層搭載(フリップチップ実装)する。このフリップチップ実装では、ボンディングツール300の吸引孔301によりロジックチップ11を吸引保持しながら、このボンディングツール300がロジックチップ11を複数の第3のバンプ電極15が形成された面(一面)を下方に向けた状態で保持する。

【0049】

このボンディングツール300は、ロジックチップ11の一面と、その下にある4層目のメモリーチップ10dの他面とを対向させながら、その間にある第3のバンプ電極13と第3のバンプ電極15との位置を合わせた状態で、ロジックチップ11を4層目のメモリーチップ10d上に載置する。そして、この状態でボンディングツール300が約300℃で加熱しながら荷重を加えることによって、上記Cuの表面にNiAu層が形成された第2のバンプ電極13と、上記Cuの表面にNiAu層が形成された第3のバンプ電極15とを第1の接合部材(はんだバンプ)18を介して熱圧着により接合(フリップチップボンディング)する。なお、この接合時には、荷重だけでなく、超音波も印加するようにしてもよい。

【0050】

これにより、第2のバンプ電極13と第3のバンプ電極15との間が第1の接合部材(はんだバンプ)18を介して電気的に接続(フリップチップ接続)されて、ロジックチップ11が4層目のメモリーチップ10d上にフリップチップ実装される。

【0051】

また、このフリップチップ実装後は、図5Bに示すように、ロジックチップ11と4層目のメモリーチップ10dとの間の隙間を広げるようにボンディングツール300を上方へと移動させる。これにより、第1の接合部材18を形成するはんだバンプの量を多めにしても、隣接するバンプ電極13,15に広がりショートを引き起こすリスクを低減できる。また、はんだバンプの量を多めにすることで、ロジックチップ11に反りが発生しても良好に接合を維持できる。

【0052】

また、本発明では、上記図1Bに示すように、第2のバンプ電極13と第3のバンプ電極15との互いに対向する少なくとも一方の面に、上述した凹部13a,15aを形成しておくことで、これら第2のバンプ電極13と第3のバンプ電極15とを第1の接合部材18を介して接合する際に、その接合強度を更に高めることが可能である。

【0053】

次に、図6A及び図6Bに示すように、ロジックチップ11と4層目のメモリーチップ10dとの隙間に第2のアンダーフィル材4bを充填し、この第2のアンダーフィル材4bによりロジックチップ11を封止する。

【0054】

具体的には、図6Aに示すように、塗布ステージ400の塗布用シート401上に、上記メモリーチップ10a〜10d及びロジックチップ11の積層体を載置した後、液状の第2のアンダーフィル材4bを供給するディスペンサー700を用いて、ロジックチップ11の端部近傍に向かって第2のアンダーフィル材4bを塗布する。

【0055】

このとき、第2のアンダーフィル材4bは、毛細管現象により、ロジックチップ11と4層目のメモリーチップ10dとの間に形成される隙間に浸透しながら充填される。また、ロジックチップ11は、4層目のメモリーチップ10dよりも小さいため、隙間からはみ出した第2のアンダーフィル材4bは、メモリーチップ10d上に留まることになる。

【0056】

この状態から、第2のアンダーフィル材4bを例えば150℃程度で加熱(キュア)することで、この第2のアンダーフィル材4bを硬化させる。そして、第2のアンダーフィル材4bが硬化した後は、図3Bに示すように、チップ積層体3を上記塗布用シート401から引き剥がす。なお、この場合もチップ積層体3を上記塗布用シート401から容易に引き剥がすことが可能である。そして、このチップ積層体3は、図示を省略する収納用トレイに収容されて、次工程へと送られる。

【0057】

次に、図7A〜図7Cに示すように、上記配線基板2となる部分が複数並んで形成された母配線基板100を用意する。この母配線基板100は、例えば厚み0.14mm程度のガラスエポキシ配線基板からなり、上記配線基板2となる部分がマトリックス状に複数並んで形成されると共に、最終的にダイシングラインLに沿って切断することで、上記配線基板2となる部分を個々の配線基板2として切り出すことが可能となっている。また、上記配線基板2となる部分の各パッド電極7上には、上記第2の接合部材20となるワイヤーバンプが配置されている。

【0058】

そして、この母配線基板100の一面に、上記チップ積層体3を上記配線基板2となる部分毎に実装する。具体的には、図7Aに示すように、NCP(Non Conductive Paste)と呼ばれる液状の接着部材19を供給するディスペンサー800を用いて、母配線基板100上に、上記配線基板2となる部分の実装領域2a毎に液状の接着部材19を塗布する。

【0059】

この状態から、図7Bに示すように、ボンディングツール300を用いて、チップ積層体3を母配線基板100の上記配線基板2となる部分の実装領域2aにフリップ実装する。このフリップチップ実装では、ボンディングツール300の吸引孔301によりチップ積層体3を吸引保持しながら、このボンディングツール300がチップ積層体3をロジックチップ11を下方に向けた状態で保持する。

【0060】

このボンディングツール300は、ロジックチップ11と上記配線基板2となる部分の実装領域2aとを対向させながら、その間にある第4のバンプ電極16とパッド電極7との位置を合わせた状態で、チップ積層体3を上記配線基板2となる部分の実装領域2a上に載置する。そして、この状態でボンディングツール300が約300℃で加熱しながら荷重を加えることによって、第4のバンプ電極16とパッド電極7とを第2の接合部材(ワイヤーバンプ)20を介して熱圧着により接合(フリップチップボンディング)する。なお、この接合時には、荷重だけでなく、超音波も印加するようにしてもよい。

【0061】

これにより、第4のバンプ電極16とパッド電極7との間が第2の接合部材(ワイヤーバンプ)20を介して電気的に接続(フリップチップ接続)されて、チップ積層体3が母配線基板100の配線基板2となる部分の実装領域2aにフリップチップ実装される。

【0062】

また、接着部材19は、図7Cに示すように、配線基板2の一面とロジックチップ11の他面との間からはみ出した状態で硬化される。これにより、チップ積層体3は、この接着部材19を介して母配線基板100の配線基板2となる部分の実装領域2aに接着固定される。

【0063】

ここで、チップ積層体3を封止する第1の封止体4(第1のアンダーフィル材4a及び第2のアンダーフィル材4b)は、このチップ積層体3の各隙間からはみ出す第1及び第2のアンダーフィル材4a,4bの幅が下層側から上層側に向かって漸次大きくなる、いわゆる逆テーパー形状を有している。この場合、配線基板2の一面とロジックチップ11の他面との間からはみ出した接着部材19の這い上がりを防止できるため、ボンディングツール300への接着部材19の付着に起因するチップ積層体3の割れや接合不良等の発生を低減できる。

【0064】

次に、図8に示すように、チップ積層体3を覆うように母配線基板100の一面側を上記第2の封止体5となるモールド樹脂で封止する。具体的には、トランスファモールド装置(図示せず。)を用いる。このトランスファモールド装置は、母配線基板100の他面側を保持する下金型(固定型)と、母配線基板100の一面側に対向してモールド樹脂が充填されるキャビティ空間を形成すると共に、下金型に対して相対的に接離自在に移動される上金型(可動型)とからなる一対の成型金型を備える。

【0065】

そして、このトランスファモールド装置の成形金型に、上記チップ積層体3が実装された母配線基板100をセットした後、成形金型内のキャビティ空間内に加熱溶融されたモールド樹脂を注入する。このモールド樹脂には、例えばエポキシ樹脂等の熱硬化性樹脂が用いられる。

【0066】

そして、この状態で、モールド樹脂を所定の温度(例えば180℃程度)で加熱(キュア)することで、モールド樹脂を硬化させる。さらに、所定の温度でベークすることで、モールド樹脂が完全に硬化される。これにより、母配線基板100の一面側が上記第2の封止体5となるモールド樹脂で完全に封止される。

【0067】

本発明では、上述したように、第1の封止体4(第1のアンダーフィル材4a及び第2のアンダーフィル材4b)で封止された複数のチップ積層体3を母配線基板100上に実装した後、この母配線基板100上を第2の封止体5で一括的に封止することで、ボイド(気泡)の発生を低減できる。

【0068】

次に、図9に示すように、母配線基板100の各配線基板2となる部分に設けられた上記接続ランド8上に、上記はんだボール6を配置する。具体的には、複数の吸着孔(図示せず。)が形成されたボールマウンターのマウントツール900を用いて、複数のはんだボール6をマウントツール900で吸着保持しながら、これら複数のはんだボール6にフラックスを転写形成した後、母配線基板100の各配線基板2となる部分毎にはんだボール6を接続ランド7上に載置する。そして、母配線基板100の全ての配線基板2となる部分にはんだボール6を載置した後、この母配線基板100をリフローする。これにより、母配線基板100の各配線基板2となる部分の接続ランド8上に、はんだボール6が配置される。

【0069】

次に、図10に示すように、母配線基板100を配線基板2となる部分毎に切断することによって個々の半導体パッケージ1に分割する。具体的には、母配線基板100の第2の封止体5側にダイシングテープ1000を貼着した後、ダイシングブレード1001を用いて母配線基板100をダイシングテープ1000とは反対側からダイシングラインLに沿って切断する。これにより、半導体パッケージ1毎に分割される。そして、これら半導体パッケージ1をダイシングテープ1000から引き剥がすことで、上記図1Aに示す半導体パッケージ1を得ることができる。

【0070】

以上のように、本発明を適用した半導体パッケージ1の製造方法では、上述したように、ロジックチップ11の第3のバンプ電極15と、その下にあるメモリーチップ10dの第2のバンプ電極13との間に第1の接合部材18を介在させることによって、電極材料や接合方法の制約がなく、熱による接合が困難なメモリーチップ10dとロジックチップ11のバンプ電極13,15同士を良好に接合することが可能である。

【0071】

なお、本発明は、上記実施形態のものに必ずしも限定されるものではなく、本発明の趣旨を逸脱しない範囲において種々の変更を加えることが可能である。なお、以下の説明では、上記半導体パッケージ1と同等の部位については、説明を省略すると共に、図面において同じ符号を付すものとする。

【0072】

例えば、本発明では、図11A〜図11Dに示すように、複数のメモリーチップ10a〜10d及びロジックチップ11を積層した後に、この積層体の各隙間に上記第1の封止体4となるアンダーフィル材を充填するようにしてもよい。この場合、製造工程を簡略化することが可能である。

【0073】

具体的には、先ず、図11Aに示すように、上記図2A〜図2Cに示す場合と同様にして、吸着ステージ200上に、複数のメモリーチップ10a〜10dを、それぞれの一面と他面とを対向させながら、それぞれの間にある第1のバンプ電極12と第2のバンプ電極13とを接合して積層する。

【0074】

次に、図11Bに示すように、上記図4A〜図4Cに示す場合と同様にして、最上層に位置するメモリーチップ10dの第2のバンプ電極13の上に第1の接合部材18を配置する。

【0075】

次に、図11Cに示すように、上記図5A及び図5Bに示す場合と同様にして、ロジックチップ11を、その一面と、その下にあるメモリーチップ10dの他面とを対向させながら、その間にある第2のバンプ電極13と第3のバンプ電極15とを第1の接合部材18を介して接合して積層した後、ボンディングツール300(図示せず。)を上方へと移動させながら、ロジックチップ11と4層目のメモリーチップ11dとの間の隙間を広げるようにする。

【0076】

次に、図11Dに示すように、上記複数のメモリーチップ10a〜10d及びロジックチップ11を積層した積層体の各隙間にアンダーフィル材を充填し、このアンダーフィル材(第1の封止体4)によりチップ積層体3を封止する。

【0077】

また、上記実施形態では、母配線基板100上に接着部材19を塗布した後、チップ積層体3を実装するようにしたが、母配線基板100上にチップ積層体3を実装した後に、その間に接着部材19を充填するようにしてもよい。この場合、ロジックチップ11の第4のバンプ電極16を高く形成することで、チップ積層体3と母配線基板100との隙間を広く確保することができ、接着部材19の充填性を向上できる。

【0078】

なお、上記チップ積層体3は、4つのメモリーチップ10a〜10dとロジックチップ11を積層した構成となっているが、メモリーチップの積層数については2つ以上であればよく、このような構成に必ずしも限定されるものではない。

【0079】

また、上記チップ積層体3は、メモリーチップとロジックチップとを組み合わせた構成となっているが、種類の異なるデバイスを直接接続するチップ積層体であればどのようなチップの組合せ、又はデバイスチップとSiインターポーザの組合せに、本発明を適用してもよい。

【0080】

また、本発明は、上記BGA型の半導体パッケージ1に限らず、例えば、LGA(Land Grid Array)型やCSP(Chip Size Package)型などの他の半導体パッケージにも適用可能である。

【符号の説明】

【0081】

1…半導体パッケージ(半導体装置) 2…配線基板 2a…実装領域 3…チップ積層体 4…第1の封止体 4a…第1のアンダーフィル材 4b…第2のアンダーフィル材 5…第2の封止体 6…はんだボール(外部接続端子) 7…パッド電極(第5の接続端子) 8…接続ランド 9…引回し配線部 10a〜10d…メモリーチップ(第1の半導体チップ) 11…ロジックチップ(第2の半導体チップ) 12…第1のバンプ電極(第1の接続端子) 13…第2のバンプ電極(第2の接続端子) 13a…凹部 14…貫通電極 15…第3のバンプ電極(第3の接続端子) 15a…凹部 16…第4のバンプ電極(第4の接続端子) 17…貫通電極 18…第1の接合部材 19…接着部材 20…第2の接合部材 100…母配線基板

【特許請求の範囲】

【請求項1】

少なくとも配線基板と、この配線基板の一面に実装されたチップ積層体とを備える半導体パッケージであって、

前記チップ積層体は、前記配線基板の一面とは反対側から順に、一面側に第1の接続端子と他面側に第2の接続端子とを有する複数の第1の半導体チップを、それぞれの一面と他面とを対向させながら、それぞれの間にある前記第1の接続端子と前記第2の接続端子とを接合して積層し、その上に、一面側に第3の接続端子と他面側に第4の接続端子とを有する第2の半導体チップを、その一面と、その下にある前記第1の半導体チップの他面とを対向させながら、その間にある前記第2の接続端子と前記第3の接続端子とを接合部材を介して接合して積層した構造を有することを特徴とする半導体装置。

【請求項2】

前記第2の接続端子と前記第3の接続端子との互いに対向する面の少なくとも一方の面が凹部を有することを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第1及び第2の半導体チップは、それぞれ前記第1の接続端子と前記第2の接続端子との間及び前記第3の接続端子と前記第4の接続端子との間を接続する貫通電極を有することを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記第2の半導体チップの第4の接続端子と、前記配線基板の一面に設けられた第5の接続端子とが接合部材を介して接合されていることを特徴とする請求項1〜3の何れか一項に記載の半導体装置。

【請求項5】

前記第2の半導体チップと前記配線基板との間に接着部材が設けられていることを特徴とする請求項4に記載の半導体装置。

【請求項6】

前記配線基板の一面側に、前記チップ積層体を覆う第1の封止体と、この第1の封止体を覆う第2の封止体とが設けられていることを特徴とする請求項1〜5の何れか一項に記載の半導体装置。

【請求項7】

前記配線基板の他面側に、外部接続端子が設けられていることを特徴とする請求項1〜6の何れか一項に記載の半導体装置。

【請求項8】

少なくとも配線基板と、この配線基板の一面に実装されたチップ積層体とを備える半導体装置の製造方法であって、

前記チップ積層体を形成する際に、一面側に第1の接続端子と他面側に第2の接続端子とを有する複数の第1の半導体チップを、それぞれの一面と他面とを対向させながら、それぞれの間にある前記第1の接続端子と前記第2の接続端子とを接合して積層する工程と、

前記積層された複数の第1の半導体チップの最上層に位置する第1の半導体チップの前記第2の接続端子の上に接合部材を配置する工程と、

その上に、一面側に第3の接続端子と他面側に第4の接続端子とを有する第2の半導体チップを、その一面と、その下にある前記第1の半導体チップの他面とを対向させながら、その間にある前記第2の接続端子と前記第3の接続端子とを前記接合部材を介して接合して積層する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項9】

前記最上層に位置する第1の半導体チップとして、前記第2の接続端子の前記接合部材が配置される面に凹部を有する第1の半導体チップを用いることを特徴とする請求項8に記載の半導体装置の製造方法。

【請求項10】

前記第2の半導体チップとして、前記第3の接続端子の前記接合部材を介して前記第2の接続端子と接合される面に凹部を有する第2の半導体チップを用いることを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

前記チップ積層体を覆うように第1の封止体で封止する工程を含むことを特徴とする請求項8〜10の何れか一項に記載の半導体装置の製造方法。

【請求項12】

前記チップ積層体を前記第1の封止体で封止する工程は、前記複数の第1の半導体チップを積層した後と、前記第2の半導体チップを積層した後とに分けて行うことを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項13】

前記チップ積層体を前記第1の封止体で封止する工程は、前記複数の第1の半導体チップと前記第2の半導体チップとを積層した後に連続して行うことを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項14】

前記配線基板となる部分が複数並んで形成された母配線基板の一面に、前記第2の半導体チップを対向させながら、前記第1の封止体で封止されたチップ積層体を前記配線基板となる部分毎に実装する工程と、

前記第1の封止体で封止されたチップ積層体を覆うように前記母配線基板の一面側を第2の封止体で封止する工程と、

前記母配線基板の他面側に前記配線基板となる部分毎に外部接続端子を配置する工程と、

前記母配線基板を前記配線基板となる部分毎に切断することによって個々の半導体装置に分割する工程とを含むことを特徴とする請求項11〜13の何れか一項に記載の半導体装置の製造方法。

【請求項15】

前記第1の封止体で封止されたチップ積層体を前記母配線基板の一面に実装する際に、

前記母配線基板の前記配線基板となる部分に設けられた第5の接続端子の上に接合部材を配置する工程と、

前記母配線基板の前記配線基板となる部分に接着部材を配置する工程と、

前記母配線基板の一面と前記第2の半導体チップの他面とを対向させながら、その間を前記接着部材で接着すると共に、その間にある前記第4の接続端子と前記第5の接続端子とを前記接合部材を介して接合する工程とを含むことを特徴とする請求項14に記載の半導体装置の製造方法。

【請求項1】

少なくとも配線基板と、この配線基板の一面に実装されたチップ積層体とを備える半導体パッケージであって、

前記チップ積層体は、前記配線基板の一面とは反対側から順に、一面側に第1の接続端子と他面側に第2の接続端子とを有する複数の第1の半導体チップを、それぞれの一面と他面とを対向させながら、それぞれの間にある前記第1の接続端子と前記第2の接続端子とを接合して積層し、その上に、一面側に第3の接続端子と他面側に第4の接続端子とを有する第2の半導体チップを、その一面と、その下にある前記第1の半導体チップの他面とを対向させながら、その間にある前記第2の接続端子と前記第3の接続端子とを接合部材を介して接合して積層した構造を有することを特徴とする半導体装置。

【請求項2】

前記第2の接続端子と前記第3の接続端子との互いに対向する面の少なくとも一方の面が凹部を有することを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第1及び第2の半導体チップは、それぞれ前記第1の接続端子と前記第2の接続端子との間及び前記第3の接続端子と前記第4の接続端子との間を接続する貫通電極を有することを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記第2の半導体チップの第4の接続端子と、前記配線基板の一面に設けられた第5の接続端子とが接合部材を介して接合されていることを特徴とする請求項1〜3の何れか一項に記載の半導体装置。

【請求項5】

前記第2の半導体チップと前記配線基板との間に接着部材が設けられていることを特徴とする請求項4に記載の半導体装置。

【請求項6】

前記配線基板の一面側に、前記チップ積層体を覆う第1の封止体と、この第1の封止体を覆う第2の封止体とが設けられていることを特徴とする請求項1〜5の何れか一項に記載の半導体装置。

【請求項7】

前記配線基板の他面側に、外部接続端子が設けられていることを特徴とする請求項1〜6の何れか一項に記載の半導体装置。

【請求項8】

少なくとも配線基板と、この配線基板の一面に実装されたチップ積層体とを備える半導体装置の製造方法であって、

前記チップ積層体を形成する際に、一面側に第1の接続端子と他面側に第2の接続端子とを有する複数の第1の半導体チップを、それぞれの一面と他面とを対向させながら、それぞれの間にある前記第1の接続端子と前記第2の接続端子とを接合して積層する工程と、

前記積層された複数の第1の半導体チップの最上層に位置する第1の半導体チップの前記第2の接続端子の上に接合部材を配置する工程と、

その上に、一面側に第3の接続端子と他面側に第4の接続端子とを有する第2の半導体チップを、その一面と、その下にある前記第1の半導体チップの他面とを対向させながら、その間にある前記第2の接続端子と前記第3の接続端子とを前記接合部材を介して接合して積層する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項9】

前記最上層に位置する第1の半導体チップとして、前記第2の接続端子の前記接合部材が配置される面に凹部を有する第1の半導体チップを用いることを特徴とする請求項8に記載の半導体装置の製造方法。

【請求項10】

前記第2の半導体チップとして、前記第3の接続端子の前記接合部材を介して前記第2の接続端子と接合される面に凹部を有する第2の半導体チップを用いることを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

前記チップ積層体を覆うように第1の封止体で封止する工程を含むことを特徴とする請求項8〜10の何れか一項に記載の半導体装置の製造方法。

【請求項12】

前記チップ積層体を前記第1の封止体で封止する工程は、前記複数の第1の半導体チップを積層した後と、前記第2の半導体チップを積層した後とに分けて行うことを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項13】

前記チップ積層体を前記第1の封止体で封止する工程は、前記複数の第1の半導体チップと前記第2の半導体チップとを積層した後に連続して行うことを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項14】

前記配線基板となる部分が複数並んで形成された母配線基板の一面に、前記第2の半導体チップを対向させながら、前記第1の封止体で封止されたチップ積層体を前記配線基板となる部分毎に実装する工程と、

前記第1の封止体で封止されたチップ積層体を覆うように前記母配線基板の一面側を第2の封止体で封止する工程と、

前記母配線基板の他面側に前記配線基板となる部分毎に外部接続端子を配置する工程と、

前記母配線基板を前記配線基板となる部分毎に切断することによって個々の半導体装置に分割する工程とを含むことを特徴とする請求項11〜13の何れか一項に記載の半導体装置の製造方法。

【請求項15】

前記第1の封止体で封止されたチップ積層体を前記母配線基板の一面に実装する際に、

前記母配線基板の前記配線基板となる部分に設けられた第5の接続端子の上に接合部材を配置する工程と、

前記母配線基板の前記配線基板となる部分に接着部材を配置する工程と、

前記母配線基板の一面と前記第2の半導体チップの他面とを対向させながら、その間を前記接着部材で接着すると共に、その間にある前記第4の接続端子と前記第5の接続端子とを前記接合部材を介して接合する工程とを含むことを特徴とする請求項14に記載の半導体装置の製造方法。

【図1A】

【図1B】

【図2A】

【図2B】

【図2C】

【図3A】

【図3B】

【図3C】

【図3D】

【図4A】

【図4B】

【図4C】

【図5A】

【図5B】

【図6A】

【図6B】

【図7A】

【図7B】

【図7C】

【図8】

【図9】

【図10】

【図11A】

【図11B】

【図11C】

【図11D】

【図1B】

【図2A】

【図2B】

【図2C】

【図3A】

【図3B】

【図3C】

【図3D】

【図4A】

【図4B】

【図4C】

【図5A】

【図5B】

【図6A】

【図6B】

【図7A】

【図7B】

【図7C】

【図8】

【図9】

【図10】

【図11A】

【図11B】

【図11C】

【図11D】

【公開番号】特開2012−69903(P2012−69903A)

【公開日】平成24年4月5日(2012.4.5)

【国際特許分類】

【出願番号】特願2011−38263(P2011−38263)

【出願日】平成23年2月24日(2011.2.24)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成24年4月5日(2012.4.5)

【国際特許分類】

【出願日】平成23年2月24日(2011.2.24)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]