半導体装置及びその製造方法

【課題】製造コストの増加を抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体装置の製造方法は、(a)オフ角を有するSiC基板1上に、ドリフト層2と、酸化膜31と、レジスト32とをこの順に形成する工程と、(b)酸化膜31に第1開口部31aを形成するともに、レジスト32に第2開口部32bを形成する工程と、(c)不純物を、酸化膜31及びレジスト32を介してドリフト層2にイオン注入することにより、p型領域13,23をドリフト層2の上部に形成する工程とを備える。

【解決手段】半導体装置の製造方法は、(a)オフ角を有するSiC基板1上に、ドリフト層2と、酸化膜31と、レジスト32とをこの順に形成する工程と、(b)酸化膜31に第1開口部31aを形成するともに、レジスト32に第2開口部32bを形成する工程と、(c)不純物を、酸化膜31及びレジスト32を介してドリフト層2にイオン注入することにより、p型領域13,23をドリフト層2の上部に形成する工程とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関するものであり、特に、高耐圧下で使用可能な半導体装置及びその製造方法に関する。

【背景技術】

【0002】

温度特性及び耐圧特性に優れたデバイスとして、SiC(炭化シリコン)を用いた半導体装置が知られている。しかし、SiCを使用した半導体装置の製造技術には、多くの解決すべき課題が残されており、特に高電圧用のデバイスに関しては課題が多い。その一つとして、高耐圧下においてパワーデバイスとして動作する半導体素子の活性領域の外縁部には、電界のピーク(電界集中)が発生してしまうことが知られている。そこで、高耐圧下においても安定に動作するデバイスを実現するために、半導体素子の周囲の電界集中を緩和することが可能な適切な終端構造が求められている。

【0003】

このような終端構造としては、従来、pn接合を設ける構成が用いられるが、当該pn接合を構成するp型領域のうち、半導体素子の活性領域と逆側の端部は高電界となる。そこでの電界集中を緩和するために、例えば、特許文献1には、当該端部に濃度及び深さが異なるp型領域を重ねて形成する構造が提案されている。なお、深さや濃度分布の異なる領域を形成する方法としては、特許文献2及び特許文献3に開示されているように、注入マスクとして酸化膜を組み合せて行う方法が知られている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平7−99328号公報

【特許文献2】特開2005−135972号公報

【特許文献3】特開平2−231711号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、p型領域の上記端部に別途深いp型領域を形成するためには、濃度及び深さが異なるp型領域を重ねて形成するための複数のイオン注入用マスクと、複数回数のイオン注入工程とが必要となる。その結果、製造コストが増加するという問題があった。また、電界集中がより緩和された、信頼性の高い半導体装置が求められているという問題があった。

【0006】

そこで、本発明は、上記のような問題点を鑑みてなされたものであり、製造コストの増加を抑制することが可能な技術を提供することを目的とする。また、本発明は、半導体装置の信頼性を向上させることが可能な技術を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明に係る半導体装置は、半導体素子の外周にpn接合からなる終端構造を設けた半導体装置であって、オフ角を有する半導体基板と、前記半導体基板上に形成された第1導電型のドリフト層と、前記ドリフト層の上部に形成されて前記ドリフト層と前記pn接合を構成し、かつ、端部が中央部よりも深い第2導電型を有する不純物領域とを備える。そして、前記不純物領域に含まれる前記第2導電型の不純物の濃度は、前記不純物領域の所定深さから深くなるにつれて低減し、その低減の程度は、前記中央部よりも前記端部のほうが緩やかである。

【0008】

また、本発明に係る半導体装置の製造方法は、半導体素子の外周にpn接合からなる終端構造を設けた半導体装置の製造方法であって、(a)オフ角を有する半導体基板上に、第1導電型のドリフト層と、絶縁膜と、レジストとをこの順に形成する工程と、(b)前記絶縁膜に第1開口部を形成するともに、前記レジストに、前記第1開口部と前記第1開口部周囲の前記絶縁膜であるスルー絶縁膜とを露出する第2開口部を形成する工程と、(c)第2導電型の不純物を、前記絶縁膜及び前記レジストを介して前記ドリフト層にイオン注入することにより、前記ドリフト層と前記pn接合を構成し、かつ、端部が中央部よりも深い前記第2導電型を有する不純物領域を前記ドリフト層の上部に形成する工程とを備える。そして、前記不純物領域に含まれる前記第2導電型の不純物の濃度は、前記不純物領域の所定深さから深くなるにつれて低減し、その低減の程度は、前記中央部よりも前記端部のほうが緩やかである。

【発明の効果】

【0009】

本発明によれば、不純物領域での不純物の濃度の低減の程度が、中央部よりも端部のほうが緩やかである。したがって、不純物領域端部における電界集中、つまり、半導体素子の終端における電界集中を緩和できることから、半導体装置の信頼性を向上させることができる。

【0010】

本発明によれば、端部及び中央部にける深さ及び濃度変化が異なる不純物領域を、1回のイオン注入工程で製造することができるので、製造コストを低減することができる。

【図面の簡単な説明】

【0011】

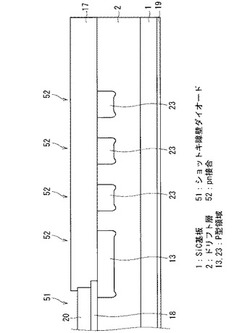

【図1】実施の形態1に係る半導体装置の構成を示す断面図である。

【図2】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図3】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図4】実施の形態1に係る半導体装置の構成を示す図である。

【図5】実施の形態1に係る半導体装置の構成を示す図である。

【図6】実施の形態1に係る半導体装置の構成を示す図である。

【図7】実施の形態2に係る半導体装置の製造方法を示す断面図である。

【図8】実施の形態2に係る半導体装置の製造方法を示す断面図である。

【発明を実施するための形態】

【0012】

<実施の形態1>

図1は、本発明の実施の形態1に係る半導体装置の構成を示す断面図である。図1に示すように、この半導体装置は、n型(第1導電型)を有するワイドバンドギャップ半導体基板であるSiC基板1と、SiCを含むn型のドリフト層2と、p型(第2導電型)の不純物領域であるp型領域13,23と、絶縁膜17と、アノード電極(ショットキ電極)18と、カソード電極19と、メタライズ電極(配線電極)20とを備えている。

【0013】

このうち、SiC基板1、ドリフト層2、アノード電極18及びカソード電極19はショットキ障壁ダイオード51を構成しており、ドリフト層2及び各p型領域13,23は、pn接合52を構成している。したがって、本実施の形態に係る半導体装置は、半導体素子であるショットキ障壁ダイオード51の外周(ここではアノード電極18の外周)にpn接合52からなる終端構造が設けられたものとなっている。次に、本実施の形態に係る半導体装置の構成要素について詳細に説明する。

【0014】

本実施の形態では、SiC基板1は、例えば、(0001)面から<11−20>方向に2°〜10°のオフ角を有している。ここでは、SiC基板1は、(0001)面から<11−20>方向に4°のオフ角を有しているものとして、以下説明する。

【0015】

SiC基板1上には、ドリフト層2が形成されている。ドリフト層2のドーピング濃度及び厚さは、ショットキ障壁ダイオード51において想定される耐圧に応じて設定される。本実施の形態では、ドリフト層2のドーピング濃度は5×1014〜3×1016cm-3であり、ドリフト層2の厚さは4〜150μmであるものとする。

【0016】

ドリフト層2の上面には、それとショットキ接続するアノード電極18が選択的に形成され、アノード電極18上には、メタライズ電極20が形成される。アノード電極18が形成されていないドリフト層2の上面には、アノード電極18及びメタライズ電極20の端部を覆う絶縁膜17が形成される。また、SiC基板1の底面には、ショットキ障壁ダイオード51のカソード電極19が形成されている。

【0017】

アノード電極18の外周(アノード電極18の端部及びその外側)に位置するドリフト層2の上部(ドリフト層2のSiC基板1と反対側の部分)には、上述したように、ドリフト層2とpn接合52を構成するp型領域13,23が選択的に形成されている。このうちp型領域13は、アノード電極18の端部と接続されている。具体的には、p型領域13は、ドリフト層2の上部のうち、アノード電極18のエッジと接する部分を含む領域に選択的に形成されている。

【0018】

一方、p型領域23は、アノード電極18の外側に形成されている。つまり、p型領域23は、p型領域13に関して、ショットキ障壁ダイオード51の活性領域(ドリフト層2のアノード電極18が形成される領域)と逆側に、p型領域13と離間して形成されている。なお、本実施の形態では、このようなp型領域23が複数(図1では3個)配設されている。つまり、本実施の形態では、p型領域13,23が、ショットキ障壁ダイオード51の外周に複数(図1では合計4個)配設されている。また、図1に示されるように、各p型領域13,23においては、端部が中央部よりも深くなっている。

【0019】

図2及び図3は、以上のように構成された本実施の形態に係る半導体装置の製造方法を示す図である。次に、図2及び図3を用いて当該製造方法について説明する。特に、ここでは終端構造を構成するpn接合52の作成工程について詳細に説明する。

【0020】

まず、SiC基板1上に、ドリフト層2を形成する。なお、本実施の形態では、ドリフト層2は、その不純物の濃度領域が5×1014〜1×1017cm-3となるように形成されている。続けて、ドリフト層2上に、絶縁膜である酸化膜31と、レジスト32とをこの順に形成する。なお、本実施の形態では、酸化膜31の厚さは20nmとしている。酸化膜31は、ドライ酸化及びウェット酸化のいずれによって形成されてもよく、または、堆積によって形成されてもよい。

【0021】

次に、写真製版工程によってレジスト32を選択的に現像及びエッチングすることにより、レジスト32に開口パターン32aを形成する。それから、開口パターン32aが形成されたレジスト32をマスクとして、酸化膜31をエッチングすることにより、酸化膜31に第1開口部31aを形成する。以上の工程を行うことにより、図2に示す構成が得られる。

【0022】

それから、レジスト32を細らす工程(レジスト32の開口パターン32aを広げる工程)を行う。つまり、図3に示すように、第1開口部31aと、第1開口部31a周囲の酸化膜31(以下、「スルー酸化膜31b」と呼ぶこともある)とを露出する第2開口部32bをレジスト32に形成する工程を行う。ここで、レジスト32を細らす工程としては、例えば特開2009−49363号公報に記載されているようなドライエッチングを短時間行い、当該レジスト32の周縁部分を除去することが考えられる。

【0023】

上述したように、本実施の形態では、酸化膜31の厚さは20nmとしていることから、スルー酸化膜31bの厚さも20nmとなっている。また、第2開口部32bの内壁から突出しているスルー酸化膜31bの寸法は、エッチングの精度や、電界緩和への有効性などを考慮して、0.3μm〜1μm程度が好ましい。

【0024】

次に、図3に示される酸化膜31及びレジスト32からなる2層構造をマスクとして、p型の不純物をドリフト層2にイオン注入する。つまり、p型の不純物を、酸化膜31及びレジスト32を介してドリフト層2にイオン注入する。本実施の形態では、p型の不純物であるアルミニウムを、SiC基板1の表面(結晶面)に対して垂直方向から450〜500keVのエネルギーで上記イオン注入したものとする。このようなイオン注入を、以上のような構造物に対して行うと、図3に示すように、端部が中央部よりも深いp型領域13,23が形成された。なお、本実施の形態では、p型領域13,23は、その不純物の濃度領域が1×1017〜1×1019cm-3となるように形成されているものとする。

【0025】

ここで、p型領域13,23において、スルー酸化膜31b下の端部が、第1開口部31a下の中央部よりも深くなった理由について考察する。

【0026】

一般に、シリコンなどの通常の半導体基板では、その表面が結晶方位に対してジャスト面か、オフ角を有していてもたかだか結晶方位から2°程度である。このような通常の半導体基板にその表面に対して垂直方向からイオン注入すると、不純物が基板中の原子配列の隙間を通じて所望の深さよりも基板の深い位置まで達してしまうチャネリング現象が生じる。そこで、通常の半導体基板においてイオン注入する際には、このチャネリング現象を抑制するために、半導体基板表面に対して垂直方向からずらした方位でイオン注入が一般に行われる。

【0027】

それに対し、SiC基板では結晶多形の制御のため、その表面が結晶方位に対して4°から8°、その範囲を広く見積もっても2°から10°のオフ角を有している。そのため、SiC基板表面に対してずらさずに垂直方向からイオン注入しても、もともとチャネリング現象が抑制されたものとなっている。その結果、第1開口部31a及び第2開口部32bを通してドリフト層2にイオン注入された不純物は、p型領域13,23表面から比較的浅い位置までしか到達しなかったと考えられる。一方、スルー酸化膜31b及び第2開口部32bを通してドリフト層2にイオン注入された不純物は、チャネリング現象が生じ易くなるようにスルー酸化膜31b中で適度に散乱されたことにより、p型領域13,23表面から比較的深い位置まで到達したと考えられる。

【0028】

以上の結果、スルー酸化膜31b及び第2開口部32bを通してイオン注入された不純物が、第1開口部31a及び第2開口部32bを通してイオン注入された不純物よりも、p型領域13,23表面から深い位置まで到達し、端部が中央部よりも深いp型領域13,23が形成されたと考えられる。

【0029】

図4は、本実施の形態に係るイオン注入により形成されたp型領域13,23に含まれるp型の不純物の濃度の変化を、その表面からの深さ方向について調べた結果を示す図である。この図4において、「○」のプロットは、図3の「一点鎖線a」上のp型不純物の濃度、つまり、p型領域13,23の中央部におけるp型不純物の濃度を示す。同様に、図4において、「+」のプロットは、図3の「一点鎖線b」上のp型不純物の濃度、つまり、p型領域13,23の端部におけるp型不純物の濃度を示す。

【0030】

この図4から分かるように、p型領域13,23に含まれるp型不純物の濃度は、p型領域13,23の所定深さから深くなるにつれて低減し、その低減の程度(図3における傾斜)は、中央部よりも端部のほうが緩やかになっている。また、p型領域13,23に含まれるp型不純物は、中央部よりも端部のほうが深くまで到達している。

【0031】

以上のイオン注入によってp型領域13,23を形成した後、図3に示すレジスト32及び酸化膜31を除去する。その後、以上の工程により得られた構造に対してアニールを行うことにより、p型領域13,23などの様々な不純物領域に注入されている不純物(イオン)を活性化する。そして、カソード電極19、アノード電極18、メタライズ電極20、及び絶縁膜17を形成することにより、ショットキ障壁ダイオード51が完成する。

【0032】

以上のように構成された本実施の形態に係る半導体装置によれば、p型領域13,23でのp型不純物の濃度の低減の程度が、中央部よりも端部のほうが緩やかである。したがって、p型領域13,23端部における電界集中、つまり、ショットキ障壁ダイオード51の終端における電界集中を緩和できることから、半導体装置の信頼性を向上させることができる。

【0033】

また、本実施の形態に係る半導体装置によれば、以上のようなp型領域13,23がショットキ障壁ダイオード51の外周に複数配設されている。したがって、ショットキ障壁ダイオード51の終端における電界集中をより緩和することができることから、半導体装置の信頼性をより向上させることができる。

【0034】

また、本実施の形態に係る半導体装置の製造方法によれば、端部及び中央部における深さ及び濃度変化が異なるp型領域13,23を、1回のイオン注入工程で製造することができるので、製造コストを低減することができる。

【0035】

なお、以上の説明では、両端部が中央部よりも濃度変化が緩やかでかつ深くまで達するp型領域13,23を形成した。しかしこれに限ったものではなく、外側の端部(ショットキ障壁ダイオード51と逆側の端部)のみが、中央部よりも濃度変化が緩やかでかつ深くまで達するp型領域13,23を形成するようにしてもよい。このようなp型領域13,23を形成するためには、例えば、図3に示される第2開口部32bとして、第1開口部31aと、外側のみのスルー酸化膜31bとを露出する開口部を形成すればよい。

【0036】

また、以上の説明では、スルー酸化膜31bの厚さは20nmであるものとした。ここで、図5に、エネルギーを450keV、イオン注入量を3×1013cm-2として、p型不純物であるアルミニウムをドリフト層2にイオン注入したときの不純物濃度を、深さ方向について調べた結果を示す。この図5に示されるように、厚さが20〜100nmであるスルー酸化膜31bを設けた場合の濃度は、スルー酸化膜31bが設けられていない場合の濃度よりも、深さ方向に対する低減の程度が緩やかとなっている。したがって、上記イオン注入の条件においては、厚さが20〜100nmであるスルー酸化膜31bを用いることができる。なお、スルー酸化膜31bとして説明されたスルー絶縁膜は、シリコン酸化膜と同程度の密度の非結晶からなる絶縁膜であれば、酸化膜に限ったものではなく、また、スルー酸化膜31bを含むスルー絶縁膜の膜厚は、その材料、イオン注入の条件、不純物の種類によって適宜変更されるべきであると考えられる。

【0037】

また、以上の説明では、ドリフト層2にp型不純物であるアルミニウムをイオン注入するものとした。ここで、図6に、スルー酸化膜31bの厚さを20nmとして、様々な不純物をイオン注入したときの不純物濃度を、深さ方向について調べた結果を示す。ここでは、エネルギーを110keV、イオン注入量を1.4×1013cm-2として、アルミニウム(Al)をイオン注入した場合の結果と、エネルギーを250keV、イオン注入量を3.0×1012cm-2として、p型不純物であるボロン(B)をイオン注入した場合の結果と、エネルギーを350keV、イオン注入量を5.3×1013cm-2として、n型不純物である窒素(N)をイオン注入した場合の結果とが示されている。

【0038】

この図6に示されるように、ボロンを用いた場合でも、スルー酸化膜31bがある場合の濃度は、スルー酸化膜31bがない場合の濃度よりも、深さ方向に対する低減の程度が緩やかとなることから、アルミニウムの代わりにボロンを用いることができる。また、窒素を用いた場合でも、スルー酸化膜31bがある場合の濃度は、スルー酸化膜31bがない場合の濃度よりも、深さ方向に対する低減の程度が緩やかとなっている。したがって、上述のp型領域13,23のプロファイルと同様の傾向を有するn型領域を、p型の半導体層に形成することができる。

【0039】

また、以上の説明では、SiC基板1を例に説明したが、オフ角を有する半導体基板であればよく、シリコン基板や、GaN基板などにも適用できると考えられる。

【0040】

<実施の形態2>

本発明の実施の形態2に係る半導体装置の構成は、実施の形態1とほぼ同じである。本実施の形態では、実施の形態1と製造方法が異なっている。なお、本実施の形態において、実施の形態1と同一または類似する部位には同一の符号を付与し、重複する詳細な説明は省略する。

【0041】

図7及び図8は、本実施の形態に係る半導体装置の製造方法を示す図であり、図2及び図3とそれぞれ対応している。以下、図7及び図8を用いて当該製造方法について説明する。

【0042】

まず、SiC基板1上に、ドリフト層2と、絶縁膜である酸化膜31と、レジスト32とをこの順に形成する。そして、写真製版工程によってレジスト32を選択的に現像及びエッチングすることにより、レジスト32に開口パターン32aを形成する。それから、開口パターン32aが形成されたレジスト32をマスクとして、酸化膜31をエッチングすることにより、酸化膜31に第1開口部31aを形成する。この際、図7に示すように、酸化膜31が、第1開口部31a周辺に例えば0.3μm以上1μm以下の横幅を持つテーパ形状を有するように、酸化膜31に対するエッチングの条件を適切に選択する。

【0043】

それから、実施の形態1と同様に、レジストを細らす工程を行う。酸化膜31が上述のようにエッチングされていることから、図8に示すように、本実施の形態に係るスルー酸化膜31bは、第1開口部31a周辺にテーパ形状を有している。次に、実施の形態1と同様にしてイオン注入を行う。本実施の形態では、テーパ形状を有するスルー酸化膜31bを通してイオン注入することから、実施の形態1で説明した構造を有するだけでなく、横方向に対しても濃度変化が緩やかなp型領域13,23がドリフト層2に形成される。

【0044】

それから、実施の形態1と同様に、レジスト32及び酸化膜31の除去と、アニールとを行い、その後、カソード電極19、アノード電極18、メタライズ電極20、及び絶縁膜17の形成を行うことにより、ショットキ障壁ダイオード51が完成する。

【0045】

以上のような本実施の形態に係る半導体装置の製造方法によれば、実施の形態1と同様の効果を得ることができるだけでなく、横方向に対しても濃度変化が緩やかなp型領域13,23をドリフト層2に形成することができる。したがって、ショットキ障壁ダイオード51の終端における電界集中をより緩和することができることから、半導体装置の信頼性をより向上させることができる。

【0046】

なお、本発明は、その発明の範囲内において、各実施の形態を自由に組み合わせたり、各実施の形態を適宜、変形、省略することが可能である。

【符号の説明】

【0047】

1 SiC基板、2 ドリフト層、13,23 p型領域、31 酸化膜、31a 第1開口部、31b スルー酸化膜、32 レジスト、32b 第2開口部、51 ショットキ障壁ダイオード、52 pn接合。

【技術分野】

【0001】

本発明は、半導体装置に関するものであり、特に、高耐圧下で使用可能な半導体装置及びその製造方法に関する。

【背景技術】

【0002】

温度特性及び耐圧特性に優れたデバイスとして、SiC(炭化シリコン)を用いた半導体装置が知られている。しかし、SiCを使用した半導体装置の製造技術には、多くの解決すべき課題が残されており、特に高電圧用のデバイスに関しては課題が多い。その一つとして、高耐圧下においてパワーデバイスとして動作する半導体素子の活性領域の外縁部には、電界のピーク(電界集中)が発生してしまうことが知られている。そこで、高耐圧下においても安定に動作するデバイスを実現するために、半導体素子の周囲の電界集中を緩和することが可能な適切な終端構造が求められている。

【0003】

このような終端構造としては、従来、pn接合を設ける構成が用いられるが、当該pn接合を構成するp型領域のうち、半導体素子の活性領域と逆側の端部は高電界となる。そこでの電界集中を緩和するために、例えば、特許文献1には、当該端部に濃度及び深さが異なるp型領域を重ねて形成する構造が提案されている。なお、深さや濃度分布の異なる領域を形成する方法としては、特許文献2及び特許文献3に開示されているように、注入マスクとして酸化膜を組み合せて行う方法が知られている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平7−99328号公報

【特許文献2】特開2005−135972号公報

【特許文献3】特開平2−231711号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、p型領域の上記端部に別途深いp型領域を形成するためには、濃度及び深さが異なるp型領域を重ねて形成するための複数のイオン注入用マスクと、複数回数のイオン注入工程とが必要となる。その結果、製造コストが増加するという問題があった。また、電界集中がより緩和された、信頼性の高い半導体装置が求められているという問題があった。

【0006】

そこで、本発明は、上記のような問題点を鑑みてなされたものであり、製造コストの増加を抑制することが可能な技術を提供することを目的とする。また、本発明は、半導体装置の信頼性を向上させることが可能な技術を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明に係る半導体装置は、半導体素子の外周にpn接合からなる終端構造を設けた半導体装置であって、オフ角を有する半導体基板と、前記半導体基板上に形成された第1導電型のドリフト層と、前記ドリフト層の上部に形成されて前記ドリフト層と前記pn接合を構成し、かつ、端部が中央部よりも深い第2導電型を有する不純物領域とを備える。そして、前記不純物領域に含まれる前記第2導電型の不純物の濃度は、前記不純物領域の所定深さから深くなるにつれて低減し、その低減の程度は、前記中央部よりも前記端部のほうが緩やかである。

【0008】

また、本発明に係る半導体装置の製造方法は、半導体素子の外周にpn接合からなる終端構造を設けた半導体装置の製造方法であって、(a)オフ角を有する半導体基板上に、第1導電型のドリフト層と、絶縁膜と、レジストとをこの順に形成する工程と、(b)前記絶縁膜に第1開口部を形成するともに、前記レジストに、前記第1開口部と前記第1開口部周囲の前記絶縁膜であるスルー絶縁膜とを露出する第2開口部を形成する工程と、(c)第2導電型の不純物を、前記絶縁膜及び前記レジストを介して前記ドリフト層にイオン注入することにより、前記ドリフト層と前記pn接合を構成し、かつ、端部が中央部よりも深い前記第2導電型を有する不純物領域を前記ドリフト層の上部に形成する工程とを備える。そして、前記不純物領域に含まれる前記第2導電型の不純物の濃度は、前記不純物領域の所定深さから深くなるにつれて低減し、その低減の程度は、前記中央部よりも前記端部のほうが緩やかである。

【発明の効果】

【0009】

本発明によれば、不純物領域での不純物の濃度の低減の程度が、中央部よりも端部のほうが緩やかである。したがって、不純物領域端部における電界集中、つまり、半導体素子の終端における電界集中を緩和できることから、半導体装置の信頼性を向上させることができる。

【0010】

本発明によれば、端部及び中央部にける深さ及び濃度変化が異なる不純物領域を、1回のイオン注入工程で製造することができるので、製造コストを低減することができる。

【図面の簡単な説明】

【0011】

【図1】実施の形態1に係る半導体装置の構成を示す断面図である。

【図2】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図3】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図4】実施の形態1に係る半導体装置の構成を示す図である。

【図5】実施の形態1に係る半導体装置の構成を示す図である。

【図6】実施の形態1に係る半導体装置の構成を示す図である。

【図7】実施の形態2に係る半導体装置の製造方法を示す断面図である。

【図8】実施の形態2に係る半導体装置の製造方法を示す断面図である。

【発明を実施するための形態】

【0012】

<実施の形態1>

図1は、本発明の実施の形態1に係る半導体装置の構成を示す断面図である。図1に示すように、この半導体装置は、n型(第1導電型)を有するワイドバンドギャップ半導体基板であるSiC基板1と、SiCを含むn型のドリフト層2と、p型(第2導電型)の不純物領域であるp型領域13,23と、絶縁膜17と、アノード電極(ショットキ電極)18と、カソード電極19と、メタライズ電極(配線電極)20とを備えている。

【0013】

このうち、SiC基板1、ドリフト層2、アノード電極18及びカソード電極19はショットキ障壁ダイオード51を構成しており、ドリフト層2及び各p型領域13,23は、pn接合52を構成している。したがって、本実施の形態に係る半導体装置は、半導体素子であるショットキ障壁ダイオード51の外周(ここではアノード電極18の外周)にpn接合52からなる終端構造が設けられたものとなっている。次に、本実施の形態に係る半導体装置の構成要素について詳細に説明する。

【0014】

本実施の形態では、SiC基板1は、例えば、(0001)面から<11−20>方向に2°〜10°のオフ角を有している。ここでは、SiC基板1は、(0001)面から<11−20>方向に4°のオフ角を有しているものとして、以下説明する。

【0015】

SiC基板1上には、ドリフト層2が形成されている。ドリフト層2のドーピング濃度及び厚さは、ショットキ障壁ダイオード51において想定される耐圧に応じて設定される。本実施の形態では、ドリフト層2のドーピング濃度は5×1014〜3×1016cm-3であり、ドリフト層2の厚さは4〜150μmであるものとする。

【0016】

ドリフト層2の上面には、それとショットキ接続するアノード電極18が選択的に形成され、アノード電極18上には、メタライズ電極20が形成される。アノード電極18が形成されていないドリフト層2の上面には、アノード電極18及びメタライズ電極20の端部を覆う絶縁膜17が形成される。また、SiC基板1の底面には、ショットキ障壁ダイオード51のカソード電極19が形成されている。

【0017】

アノード電極18の外周(アノード電極18の端部及びその外側)に位置するドリフト層2の上部(ドリフト層2のSiC基板1と反対側の部分)には、上述したように、ドリフト層2とpn接合52を構成するp型領域13,23が選択的に形成されている。このうちp型領域13は、アノード電極18の端部と接続されている。具体的には、p型領域13は、ドリフト層2の上部のうち、アノード電極18のエッジと接する部分を含む領域に選択的に形成されている。

【0018】

一方、p型領域23は、アノード電極18の外側に形成されている。つまり、p型領域23は、p型領域13に関して、ショットキ障壁ダイオード51の活性領域(ドリフト層2のアノード電極18が形成される領域)と逆側に、p型領域13と離間して形成されている。なお、本実施の形態では、このようなp型領域23が複数(図1では3個)配設されている。つまり、本実施の形態では、p型領域13,23が、ショットキ障壁ダイオード51の外周に複数(図1では合計4個)配設されている。また、図1に示されるように、各p型領域13,23においては、端部が中央部よりも深くなっている。

【0019】

図2及び図3は、以上のように構成された本実施の形態に係る半導体装置の製造方法を示す図である。次に、図2及び図3を用いて当該製造方法について説明する。特に、ここでは終端構造を構成するpn接合52の作成工程について詳細に説明する。

【0020】

まず、SiC基板1上に、ドリフト層2を形成する。なお、本実施の形態では、ドリフト層2は、その不純物の濃度領域が5×1014〜1×1017cm-3となるように形成されている。続けて、ドリフト層2上に、絶縁膜である酸化膜31と、レジスト32とをこの順に形成する。なお、本実施の形態では、酸化膜31の厚さは20nmとしている。酸化膜31は、ドライ酸化及びウェット酸化のいずれによって形成されてもよく、または、堆積によって形成されてもよい。

【0021】

次に、写真製版工程によってレジスト32を選択的に現像及びエッチングすることにより、レジスト32に開口パターン32aを形成する。それから、開口パターン32aが形成されたレジスト32をマスクとして、酸化膜31をエッチングすることにより、酸化膜31に第1開口部31aを形成する。以上の工程を行うことにより、図2に示す構成が得られる。

【0022】

それから、レジスト32を細らす工程(レジスト32の開口パターン32aを広げる工程)を行う。つまり、図3に示すように、第1開口部31aと、第1開口部31a周囲の酸化膜31(以下、「スルー酸化膜31b」と呼ぶこともある)とを露出する第2開口部32bをレジスト32に形成する工程を行う。ここで、レジスト32を細らす工程としては、例えば特開2009−49363号公報に記載されているようなドライエッチングを短時間行い、当該レジスト32の周縁部分を除去することが考えられる。

【0023】

上述したように、本実施の形態では、酸化膜31の厚さは20nmとしていることから、スルー酸化膜31bの厚さも20nmとなっている。また、第2開口部32bの内壁から突出しているスルー酸化膜31bの寸法は、エッチングの精度や、電界緩和への有効性などを考慮して、0.3μm〜1μm程度が好ましい。

【0024】

次に、図3に示される酸化膜31及びレジスト32からなる2層構造をマスクとして、p型の不純物をドリフト層2にイオン注入する。つまり、p型の不純物を、酸化膜31及びレジスト32を介してドリフト層2にイオン注入する。本実施の形態では、p型の不純物であるアルミニウムを、SiC基板1の表面(結晶面)に対して垂直方向から450〜500keVのエネルギーで上記イオン注入したものとする。このようなイオン注入を、以上のような構造物に対して行うと、図3に示すように、端部が中央部よりも深いp型領域13,23が形成された。なお、本実施の形態では、p型領域13,23は、その不純物の濃度領域が1×1017〜1×1019cm-3となるように形成されているものとする。

【0025】

ここで、p型領域13,23において、スルー酸化膜31b下の端部が、第1開口部31a下の中央部よりも深くなった理由について考察する。

【0026】

一般に、シリコンなどの通常の半導体基板では、その表面が結晶方位に対してジャスト面か、オフ角を有していてもたかだか結晶方位から2°程度である。このような通常の半導体基板にその表面に対して垂直方向からイオン注入すると、不純物が基板中の原子配列の隙間を通じて所望の深さよりも基板の深い位置まで達してしまうチャネリング現象が生じる。そこで、通常の半導体基板においてイオン注入する際には、このチャネリング現象を抑制するために、半導体基板表面に対して垂直方向からずらした方位でイオン注入が一般に行われる。

【0027】

それに対し、SiC基板では結晶多形の制御のため、その表面が結晶方位に対して4°から8°、その範囲を広く見積もっても2°から10°のオフ角を有している。そのため、SiC基板表面に対してずらさずに垂直方向からイオン注入しても、もともとチャネリング現象が抑制されたものとなっている。その結果、第1開口部31a及び第2開口部32bを通してドリフト層2にイオン注入された不純物は、p型領域13,23表面から比較的浅い位置までしか到達しなかったと考えられる。一方、スルー酸化膜31b及び第2開口部32bを通してドリフト層2にイオン注入された不純物は、チャネリング現象が生じ易くなるようにスルー酸化膜31b中で適度に散乱されたことにより、p型領域13,23表面から比較的深い位置まで到達したと考えられる。

【0028】

以上の結果、スルー酸化膜31b及び第2開口部32bを通してイオン注入された不純物が、第1開口部31a及び第2開口部32bを通してイオン注入された不純物よりも、p型領域13,23表面から深い位置まで到達し、端部が中央部よりも深いp型領域13,23が形成されたと考えられる。

【0029】

図4は、本実施の形態に係るイオン注入により形成されたp型領域13,23に含まれるp型の不純物の濃度の変化を、その表面からの深さ方向について調べた結果を示す図である。この図4において、「○」のプロットは、図3の「一点鎖線a」上のp型不純物の濃度、つまり、p型領域13,23の中央部におけるp型不純物の濃度を示す。同様に、図4において、「+」のプロットは、図3の「一点鎖線b」上のp型不純物の濃度、つまり、p型領域13,23の端部におけるp型不純物の濃度を示す。

【0030】

この図4から分かるように、p型領域13,23に含まれるp型不純物の濃度は、p型領域13,23の所定深さから深くなるにつれて低減し、その低減の程度(図3における傾斜)は、中央部よりも端部のほうが緩やかになっている。また、p型領域13,23に含まれるp型不純物は、中央部よりも端部のほうが深くまで到達している。

【0031】

以上のイオン注入によってp型領域13,23を形成した後、図3に示すレジスト32及び酸化膜31を除去する。その後、以上の工程により得られた構造に対してアニールを行うことにより、p型領域13,23などの様々な不純物領域に注入されている不純物(イオン)を活性化する。そして、カソード電極19、アノード電極18、メタライズ電極20、及び絶縁膜17を形成することにより、ショットキ障壁ダイオード51が完成する。

【0032】

以上のように構成された本実施の形態に係る半導体装置によれば、p型領域13,23でのp型不純物の濃度の低減の程度が、中央部よりも端部のほうが緩やかである。したがって、p型領域13,23端部における電界集中、つまり、ショットキ障壁ダイオード51の終端における電界集中を緩和できることから、半導体装置の信頼性を向上させることができる。

【0033】

また、本実施の形態に係る半導体装置によれば、以上のようなp型領域13,23がショットキ障壁ダイオード51の外周に複数配設されている。したがって、ショットキ障壁ダイオード51の終端における電界集中をより緩和することができることから、半導体装置の信頼性をより向上させることができる。

【0034】

また、本実施の形態に係る半導体装置の製造方法によれば、端部及び中央部における深さ及び濃度変化が異なるp型領域13,23を、1回のイオン注入工程で製造することができるので、製造コストを低減することができる。

【0035】

なお、以上の説明では、両端部が中央部よりも濃度変化が緩やかでかつ深くまで達するp型領域13,23を形成した。しかしこれに限ったものではなく、外側の端部(ショットキ障壁ダイオード51と逆側の端部)のみが、中央部よりも濃度変化が緩やかでかつ深くまで達するp型領域13,23を形成するようにしてもよい。このようなp型領域13,23を形成するためには、例えば、図3に示される第2開口部32bとして、第1開口部31aと、外側のみのスルー酸化膜31bとを露出する開口部を形成すればよい。

【0036】

また、以上の説明では、スルー酸化膜31bの厚さは20nmであるものとした。ここで、図5に、エネルギーを450keV、イオン注入量を3×1013cm-2として、p型不純物であるアルミニウムをドリフト層2にイオン注入したときの不純物濃度を、深さ方向について調べた結果を示す。この図5に示されるように、厚さが20〜100nmであるスルー酸化膜31bを設けた場合の濃度は、スルー酸化膜31bが設けられていない場合の濃度よりも、深さ方向に対する低減の程度が緩やかとなっている。したがって、上記イオン注入の条件においては、厚さが20〜100nmであるスルー酸化膜31bを用いることができる。なお、スルー酸化膜31bとして説明されたスルー絶縁膜は、シリコン酸化膜と同程度の密度の非結晶からなる絶縁膜であれば、酸化膜に限ったものではなく、また、スルー酸化膜31bを含むスルー絶縁膜の膜厚は、その材料、イオン注入の条件、不純物の種類によって適宜変更されるべきであると考えられる。

【0037】

また、以上の説明では、ドリフト層2にp型不純物であるアルミニウムをイオン注入するものとした。ここで、図6に、スルー酸化膜31bの厚さを20nmとして、様々な不純物をイオン注入したときの不純物濃度を、深さ方向について調べた結果を示す。ここでは、エネルギーを110keV、イオン注入量を1.4×1013cm-2として、アルミニウム(Al)をイオン注入した場合の結果と、エネルギーを250keV、イオン注入量を3.0×1012cm-2として、p型不純物であるボロン(B)をイオン注入した場合の結果と、エネルギーを350keV、イオン注入量を5.3×1013cm-2として、n型不純物である窒素(N)をイオン注入した場合の結果とが示されている。

【0038】

この図6に示されるように、ボロンを用いた場合でも、スルー酸化膜31bがある場合の濃度は、スルー酸化膜31bがない場合の濃度よりも、深さ方向に対する低減の程度が緩やかとなることから、アルミニウムの代わりにボロンを用いることができる。また、窒素を用いた場合でも、スルー酸化膜31bがある場合の濃度は、スルー酸化膜31bがない場合の濃度よりも、深さ方向に対する低減の程度が緩やかとなっている。したがって、上述のp型領域13,23のプロファイルと同様の傾向を有するn型領域を、p型の半導体層に形成することができる。

【0039】

また、以上の説明では、SiC基板1を例に説明したが、オフ角を有する半導体基板であればよく、シリコン基板や、GaN基板などにも適用できると考えられる。

【0040】

<実施の形態2>

本発明の実施の形態2に係る半導体装置の構成は、実施の形態1とほぼ同じである。本実施の形態では、実施の形態1と製造方法が異なっている。なお、本実施の形態において、実施の形態1と同一または類似する部位には同一の符号を付与し、重複する詳細な説明は省略する。

【0041】

図7及び図8は、本実施の形態に係る半導体装置の製造方法を示す図であり、図2及び図3とそれぞれ対応している。以下、図7及び図8を用いて当該製造方法について説明する。

【0042】

まず、SiC基板1上に、ドリフト層2と、絶縁膜である酸化膜31と、レジスト32とをこの順に形成する。そして、写真製版工程によってレジスト32を選択的に現像及びエッチングすることにより、レジスト32に開口パターン32aを形成する。それから、開口パターン32aが形成されたレジスト32をマスクとして、酸化膜31をエッチングすることにより、酸化膜31に第1開口部31aを形成する。この際、図7に示すように、酸化膜31が、第1開口部31a周辺に例えば0.3μm以上1μm以下の横幅を持つテーパ形状を有するように、酸化膜31に対するエッチングの条件を適切に選択する。

【0043】

それから、実施の形態1と同様に、レジストを細らす工程を行う。酸化膜31が上述のようにエッチングされていることから、図8に示すように、本実施の形態に係るスルー酸化膜31bは、第1開口部31a周辺にテーパ形状を有している。次に、実施の形態1と同様にしてイオン注入を行う。本実施の形態では、テーパ形状を有するスルー酸化膜31bを通してイオン注入することから、実施の形態1で説明した構造を有するだけでなく、横方向に対しても濃度変化が緩やかなp型領域13,23がドリフト層2に形成される。

【0044】

それから、実施の形態1と同様に、レジスト32及び酸化膜31の除去と、アニールとを行い、その後、カソード電極19、アノード電極18、メタライズ電極20、及び絶縁膜17の形成を行うことにより、ショットキ障壁ダイオード51が完成する。

【0045】

以上のような本実施の形態に係る半導体装置の製造方法によれば、実施の形態1と同様の効果を得ることができるだけでなく、横方向に対しても濃度変化が緩やかなp型領域13,23をドリフト層2に形成することができる。したがって、ショットキ障壁ダイオード51の終端における電界集中をより緩和することができることから、半導体装置の信頼性をより向上させることができる。

【0046】

なお、本発明は、その発明の範囲内において、各実施の形態を自由に組み合わせたり、各実施の形態を適宜、変形、省略することが可能である。

【符号の説明】

【0047】

1 SiC基板、2 ドリフト層、13,23 p型領域、31 酸化膜、31a 第1開口部、31b スルー酸化膜、32 レジスト、32b 第2開口部、51 ショットキ障壁ダイオード、52 pn接合。

【特許請求の範囲】

【請求項1】

半導体素子の外周にpn接合からなる終端構造を設けた半導体装置であって、

オフ角を有する半導体基板と、

前記半導体基板上に形成された第1導電型のドリフト層と、

前記ドリフト層の上部に形成されて前記ドリフト層と前記pn接合を構成し、かつ、端部が中央部よりも深い第2導電型を有する不純物領域と

を備え、

前記不純物領域に含まれる前記第2導電型の不純物の濃度は、前記不純物領域の所定深さから深くなるにつれて低減し、その低減の程度は、前記中央部よりも前記端部のほうが緩やかである、半導体装置。

【請求項2】

請求項1に記載の半導体装置であって、

前記半導体基板は、(0001)面から2〜10°のオフ角を有するSiC基板である、半導体装置。

【請求項3】

請求項1または請求項2に記載の半導体装置であって、

前記不純物領域は、前記半導体素子の外周に複数配設されている、半導体装置。

【請求項4】

半導体素子の外周にpn接合からなる終端構造を設けた半導体装置の製造方法であって、

(a)オフ角を有する半導体基板上に、第1導電型のドリフト層と、絶縁膜と、レジストとをこの順に形成する工程と、

(b)前記絶縁膜に第1開口部を形成するともに、前記レジストに、前記第1開口部と前記第1開口部周囲の前記絶縁膜であるスルー絶縁膜とを露出する第2開口部を形成する工程と、

(c)第2導電型の不純物を、前記絶縁膜及び前記レジストを介して前記ドリフト層にイオン注入することにより、前記ドリフト層と前記pn接合を構成し、かつ、端部が中央部よりも深い前記第2導電型を有する不純物領域を前記ドリフト層の上部に形成する工程と

を備え、

前記不純物領域に含まれる前記第2導電型の不純物の濃度は、前記不純物領域の所定深さから深くなるにつれて低減し、その低減の程度は、前記中央部よりも前記端部のほうが緩やかである、半導体装置の製造方法。

【請求項5】

請求項4に記載の半導体装置の製造方法であって、

前記半導体基板は、(0001)面から2〜10°のオフ角を有するSiC基板である、半導体装置の製造方法。

【請求項6】

請求項4または請求項5に記載の半導体装置の製造方法であって、

前記スルー絶縁膜は、厚さが20nm以上100nm以下である、半導体装置の製造方法。

【請求項7】

請求項4乃至請求項6のいずれかに記載の半導体装置の製造方法であって、

前記スルー絶縁膜は、前記第1開口部周辺にテーパ形状を有している、半導体装置の製造方法。

【請求項8】

請求項7に記載の半導体装置の製造方法であって、

前記テーパ形状は、0.3μ以上1μm以下の横幅を持つ、半導体装置の製造方法。

【請求項1】

半導体素子の外周にpn接合からなる終端構造を設けた半導体装置であって、

オフ角を有する半導体基板と、

前記半導体基板上に形成された第1導電型のドリフト層と、

前記ドリフト層の上部に形成されて前記ドリフト層と前記pn接合を構成し、かつ、端部が中央部よりも深い第2導電型を有する不純物領域と

を備え、

前記不純物領域に含まれる前記第2導電型の不純物の濃度は、前記不純物領域の所定深さから深くなるにつれて低減し、その低減の程度は、前記中央部よりも前記端部のほうが緩やかである、半導体装置。

【請求項2】

請求項1に記載の半導体装置であって、

前記半導体基板は、(0001)面から2〜10°のオフ角を有するSiC基板である、半導体装置。

【請求項3】

請求項1または請求項2に記載の半導体装置であって、

前記不純物領域は、前記半導体素子の外周に複数配設されている、半導体装置。

【請求項4】

半導体素子の外周にpn接合からなる終端構造を設けた半導体装置の製造方法であって、

(a)オフ角を有する半導体基板上に、第1導電型のドリフト層と、絶縁膜と、レジストとをこの順に形成する工程と、

(b)前記絶縁膜に第1開口部を形成するともに、前記レジストに、前記第1開口部と前記第1開口部周囲の前記絶縁膜であるスルー絶縁膜とを露出する第2開口部を形成する工程と、

(c)第2導電型の不純物を、前記絶縁膜及び前記レジストを介して前記ドリフト層にイオン注入することにより、前記ドリフト層と前記pn接合を構成し、かつ、端部が中央部よりも深い前記第2導電型を有する不純物領域を前記ドリフト層の上部に形成する工程と

を備え、

前記不純物領域に含まれる前記第2導電型の不純物の濃度は、前記不純物領域の所定深さから深くなるにつれて低減し、その低減の程度は、前記中央部よりも前記端部のほうが緩やかである、半導体装置の製造方法。

【請求項5】

請求項4に記載の半導体装置の製造方法であって、

前記半導体基板は、(0001)面から2〜10°のオフ角を有するSiC基板である、半導体装置の製造方法。

【請求項6】

請求項4または請求項5に記載の半導体装置の製造方法であって、

前記スルー絶縁膜は、厚さが20nm以上100nm以下である、半導体装置の製造方法。

【請求項7】

請求項4乃至請求項6のいずれかに記載の半導体装置の製造方法であって、

前記スルー絶縁膜は、前記第1開口部周辺にテーパ形状を有している、半導体装置の製造方法。

【請求項8】

請求項7に記載の半導体装置の製造方法であって、

前記テーパ形状は、0.3μ以上1μm以下の横幅を持つ、半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−105798(P2013−105798A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−247112(P2011−247112)

【出願日】平成23年11月11日(2011.11.11)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月11日(2011.11.11)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]