半導体装置及びその製造方法

【課題】ブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる半導体装置及びその製造方法を得る。

【解決手段】半導体基板1の有効領域2と有効領域2の周囲の無効領域3にそれぞれ拡散層4,5を同時に形成する。拡散層4,5上にそれぞれエミッタ電極6及び小信号電極7を同時に形成する。小信号電極7にプローブ12を接触させて拡散層5の電気特性又は拡散層5と小信号電極7のコンタクト抵抗を測定するテストを行う。テストの後に、エミッタ電極6上に開口10を有し、小信号電極7を覆う絶縁膜9を形成する。開口10を介してエミッタ電極6上にメッキ11を形成する。

【解決手段】半導体基板1の有効領域2と有効領域2の周囲の無効領域3にそれぞれ拡散層4,5を同時に形成する。拡散層4,5上にそれぞれエミッタ電極6及び小信号電極7を同時に形成する。小信号電極7にプローブ12を接触させて拡散層5の電気特性又は拡散層5と小信号電極7のコンタクト抵抗を測定するテストを行う。テストの後に、エミッタ電極6上に開口10を有し、小信号電極7を覆う絶縁膜9を形成する。開口10を介してエミッタ電極6上にメッキ11を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる半導体装置及びその製造方法に関する。

【背景技術】

【0002】

パワーデバイスを外部電極と接続するために、Alワイヤなどによるボンディングが一般的に行われていた。しかし、パワーデバイスの定格電流値が大きくなると、ワイヤの本数も増え、ボンディングに要する時間が増加してしまう。また、パワーデバイスの損失改善が進んで電流密度が高くなると、ワイヤを接続できるスペースが確保できなくなる。

【0003】

そこで、パワーデバイスの表面にメッキを形成し、このメッキと外部電極を直接はんだ付けする方法が考案され、広く普及している。この方法により、ワイヤボンディングなどの時間を短縮できるだけでなく、パワーサイクル寿命なども大幅に伸ばすことができ、信頼性の向上にもつながる。

【0004】

また、パワーデバイスの製造において、拡散層とそれに接続された電極からなるサンプルテストモニターを形成し、ウエハプロセスの最後にその測定を行う。これにより、ウエハプロセス中の異常の有無が分かる。さらに、例えばIGBTのMOS部を形成する複数の拡散層のどこに異常が生じているのか、又は拡散層と電極のどの部分のコンタクト抵抗に異常が生じているのかも分かる。サンプルテストモニターは、ウエハプロセスの評価だけに使用され、実際のデバイスには不要であるため、ダイシングライン上など、ウエハ上の無効領域に形成される(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009−231586号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、ウエハ表面にメッキ処理を行うと、ダイシングライン上のサンプルテストモニターの電極にもメッキが形成されてしまう。通常メッキ厚みは数μmと厚いため、ダイシング時にブレードがメッキ上を通過する際に、ブレードが欠ける、チップ端部にチッピングが発生するなどの問題が生じる。

【0007】

本発明は、上述のような課題を解決するためになされたもので、その目的はブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる半導体装置及びその製造方法を得るものである。

【課題を解決するための手段】

【0008】

本発明に係る半導体装置の製造方法は、半導体基板の有効領域と前記有効領域の周囲の無効領域にそれぞれ第1及び第2の拡散層を同時に形成する工程と、前記第1及び第2の拡散層上にそれぞれ第1及び第2の電極を同時に形成する工程と、前記第2の電極にプローブを接触させて前記第2の拡散層の電気特性又は前記第2の拡散層と前記第2の電極のコンタクト抵抗を測定するテストを行う工程と、前記テストの後に、前記第1の電極上に開口を有し、前記第2の電極を覆う絶縁膜を形成する工程と、前記開口を介して前記第1の電極上にメッキを形成する工程とを備えることを特徴とする。

【発明の効果】

【0009】

本発明により、ブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる。

【図面の簡単な説明】

【0010】

【図1】本発明の実施の形態に係る半導体装置を示す平面図である。

【図2】図1の一部を拡大した平面図である。

【図3】図2のI−IIに沿った断面図である。

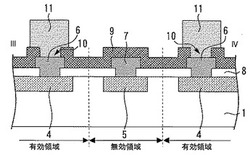

【図4】図2のIII−IVに沿った断面図である。

【図5】本発明の実施の形態に係る半導体装置の製造方法を示す図である。

【図6】本発明の実施の形態に係る半導体装置の製造方法を示す図である。

【図7】本発明の実施の形態に係る半導体装置の製造方法を示す図である。

【図8】本発明の実施の形態に係る半導体装置の製造方法を示す図である。

【図9】本発明の実施の形態に係る半導体装置の製造方法を示す図である。

【発明を実施するための形態】

【0011】

図1は、本発明の実施の形態に係る半導体装置を示す平面図である。ウエハ状の半導体基板1は、行列状に配置された四角形の複数の有効領域2と、それぞれの有効領域2の周囲に配置された無効領域3とを有する。有効領域2には、IGBT(Insulated Gate Bipolar Transistor)やDiodeやMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)などのパワーデバイスが設けられている。無効領域3はダイシングラインを含む。

【0012】

図2は図1の一部を拡大した平面図である。図3は図2のI−IIに沿った断面図であり、図4は図2のIII−IVに沿った断面図である。有効領域2及び無効領域3にそれぞれ拡散層4,5が設けられている。拡散層4はパワーデバイスを構成する複数の拡散層のうちの1つである。ただし、拡散層4,5は単一の拡散層に限らず、2〜3の積層された拡散層でもよい。

【0013】

拡散層4,5上にそれぞれAlやAlSiなどのエミッタ電極6及び小信号電極7が設けられている。エミッタ電極6及び小信号電極7は、半導体基板1を覆う絶縁膜8の開口を介して拡散層4,5に電気的に接続されている。小信号電極7及び拡散層5がサンプルテストモニターを構成する。小信号電極7はダイシングラインの中央に配置されている。

【0014】

ガラスコート酸化膜やポリイミドなどの絶縁膜9が小信号電極7を覆っている。絶縁膜9はエミッタ電極6上に開口10を有する。この開口10を介してエミッタ電極6上にNi−Auなどのメッキ11が設けられ、互いに電気的に接続されている。

【0015】

続いて、本発明の実施の形態に係る半導体装置の製造方法を説明する。図5−9は本発明の実施の形態に係る半導体装置の製造方法を示す図である。図5は平面図であり、図6は図5のI−IIに沿った断面図であり、図7は図5のIII−IVに沿った断面図である。図8は図6と同じ方向から見た断面図であり、図9は図7と同じ方向から見た断面図である。

【0016】

まず、図5〜7に示すように、半導体基板1の有効領域2と無効領域3にそれぞれ拡散層4,5を同時に形成する。この拡散層4,5上にそれぞれエミッタ電極6及び小信号電極7を同時に形成する。また、図示は省略するが、有効領域2にその他の拡散層や電極も形成してパワーデバイスの表面側の構造を形成する。

【0017】

次に、図8に示すように、小信号電極7にプローブ12を接触させて拡散層5の電気特性又は拡散層5と小信号電極7のコンタクト抵抗を測定するテストを行う。サンプルテストモニターの拡散層5及び小信号電極7は、それぞれパワーデバイスの拡散層4及びエミッタ電極6と同時に形成されるため、このサンプルテストモニターでテストを行うことで、パワーデバイス側の評価を行うことができる。

【0018】

次に、図9に示すように、全面に絶縁膜9を形成し、エミッタ電極6上において絶縁膜9に開口10を形成する。そして、半導体基板1の裏面にパワーデバイスの裏面側の構造を形成する。次に、図4に示すように、絶縁膜9をマスクにしてメッキ処理を行うことで、開口10を介してエミッタ電極6上にメッキ11を形成する。この際に、小信号電極7は絶縁膜9で覆われて外部と電気的に接続できないため、小信号電極7上にはメッキ11が形成されない。

【0019】

次に、ウェハテストを行う。その後に、無効領域3のダイシングラインに沿って半導体基板1をダイシングする。この際に、サンプルテストモニターの小信号電極7上にメッキ11が形成されていないため、ブレード欠けやチップ端部のチッピングを防ぐことができる。

【0020】

以上説明したように、本実施の形態では、サンプルテストモニターでテストを行った後に、サンプルテストモニターの小信号電極7を絶縁膜9でコーティングする。その後にメッキ処理を行う。これにより、ブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる。

【符号の説明】

【0021】

1 半導体基板

2 有効領域

3 無効領域

4 拡散層(第1の拡散層)

5 拡散層(第2の拡散層)

6 エミッタ電極(第1の電極)

7 小信号電極(第2の電極)

9 絶縁膜

10 開口

11 メッキ

12 プローブ

【技術分野】

【0001】

本発明は、ブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる半導体装置及びその製造方法に関する。

【背景技術】

【0002】

パワーデバイスを外部電極と接続するために、Alワイヤなどによるボンディングが一般的に行われていた。しかし、パワーデバイスの定格電流値が大きくなると、ワイヤの本数も増え、ボンディングに要する時間が増加してしまう。また、パワーデバイスの損失改善が進んで電流密度が高くなると、ワイヤを接続できるスペースが確保できなくなる。

【0003】

そこで、パワーデバイスの表面にメッキを形成し、このメッキと外部電極を直接はんだ付けする方法が考案され、広く普及している。この方法により、ワイヤボンディングなどの時間を短縮できるだけでなく、パワーサイクル寿命なども大幅に伸ばすことができ、信頼性の向上にもつながる。

【0004】

また、パワーデバイスの製造において、拡散層とそれに接続された電極からなるサンプルテストモニターを形成し、ウエハプロセスの最後にその測定を行う。これにより、ウエハプロセス中の異常の有無が分かる。さらに、例えばIGBTのMOS部を形成する複数の拡散層のどこに異常が生じているのか、又は拡散層と電極のどの部分のコンタクト抵抗に異常が生じているのかも分かる。サンプルテストモニターは、ウエハプロセスの評価だけに使用され、実際のデバイスには不要であるため、ダイシングライン上など、ウエハ上の無効領域に形成される(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009−231586号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、ウエハ表面にメッキ処理を行うと、ダイシングライン上のサンプルテストモニターの電極にもメッキが形成されてしまう。通常メッキ厚みは数μmと厚いため、ダイシング時にブレードがメッキ上を通過する際に、ブレードが欠ける、チップ端部にチッピングが発生するなどの問題が生じる。

【0007】

本発明は、上述のような課題を解決するためになされたもので、その目的はブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる半導体装置及びその製造方法を得るものである。

【課題を解決するための手段】

【0008】

本発明に係る半導体装置の製造方法は、半導体基板の有効領域と前記有効領域の周囲の無効領域にそれぞれ第1及び第2の拡散層を同時に形成する工程と、前記第1及び第2の拡散層上にそれぞれ第1及び第2の電極を同時に形成する工程と、前記第2の電極にプローブを接触させて前記第2の拡散層の電気特性又は前記第2の拡散層と前記第2の電極のコンタクト抵抗を測定するテストを行う工程と、前記テストの後に、前記第1の電極上に開口を有し、前記第2の電極を覆う絶縁膜を形成する工程と、前記開口を介して前記第1の電極上にメッキを形成する工程とを備えることを特徴とする。

【発明の効果】

【0009】

本発明により、ブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる。

【図面の簡単な説明】

【0010】

【図1】本発明の実施の形態に係る半導体装置を示す平面図である。

【図2】図1の一部を拡大した平面図である。

【図3】図2のI−IIに沿った断面図である。

【図4】図2のIII−IVに沿った断面図である。

【図5】本発明の実施の形態に係る半導体装置の製造方法を示す図である。

【図6】本発明の実施の形態に係る半導体装置の製造方法を示す図である。

【図7】本発明の実施の形態に係る半導体装置の製造方法を示す図である。

【図8】本発明の実施の形態に係る半導体装置の製造方法を示す図である。

【図9】本発明の実施の形態に係る半導体装置の製造方法を示す図である。

【発明を実施するための形態】

【0011】

図1は、本発明の実施の形態に係る半導体装置を示す平面図である。ウエハ状の半導体基板1は、行列状に配置された四角形の複数の有効領域2と、それぞれの有効領域2の周囲に配置された無効領域3とを有する。有効領域2には、IGBT(Insulated Gate Bipolar Transistor)やDiodeやMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)などのパワーデバイスが設けられている。無効領域3はダイシングラインを含む。

【0012】

図2は図1の一部を拡大した平面図である。図3は図2のI−IIに沿った断面図であり、図4は図2のIII−IVに沿った断面図である。有効領域2及び無効領域3にそれぞれ拡散層4,5が設けられている。拡散層4はパワーデバイスを構成する複数の拡散層のうちの1つである。ただし、拡散層4,5は単一の拡散層に限らず、2〜3の積層された拡散層でもよい。

【0013】

拡散層4,5上にそれぞれAlやAlSiなどのエミッタ電極6及び小信号電極7が設けられている。エミッタ電極6及び小信号電極7は、半導体基板1を覆う絶縁膜8の開口を介して拡散層4,5に電気的に接続されている。小信号電極7及び拡散層5がサンプルテストモニターを構成する。小信号電極7はダイシングラインの中央に配置されている。

【0014】

ガラスコート酸化膜やポリイミドなどの絶縁膜9が小信号電極7を覆っている。絶縁膜9はエミッタ電極6上に開口10を有する。この開口10を介してエミッタ電極6上にNi−Auなどのメッキ11が設けられ、互いに電気的に接続されている。

【0015】

続いて、本発明の実施の形態に係る半導体装置の製造方法を説明する。図5−9は本発明の実施の形態に係る半導体装置の製造方法を示す図である。図5は平面図であり、図6は図5のI−IIに沿った断面図であり、図7は図5のIII−IVに沿った断面図である。図8は図6と同じ方向から見た断面図であり、図9は図7と同じ方向から見た断面図である。

【0016】

まず、図5〜7に示すように、半導体基板1の有効領域2と無効領域3にそれぞれ拡散層4,5を同時に形成する。この拡散層4,5上にそれぞれエミッタ電極6及び小信号電極7を同時に形成する。また、図示は省略するが、有効領域2にその他の拡散層や電極も形成してパワーデバイスの表面側の構造を形成する。

【0017】

次に、図8に示すように、小信号電極7にプローブ12を接触させて拡散層5の電気特性又は拡散層5と小信号電極7のコンタクト抵抗を測定するテストを行う。サンプルテストモニターの拡散層5及び小信号電極7は、それぞれパワーデバイスの拡散層4及びエミッタ電極6と同時に形成されるため、このサンプルテストモニターでテストを行うことで、パワーデバイス側の評価を行うことができる。

【0018】

次に、図9に示すように、全面に絶縁膜9を形成し、エミッタ電極6上において絶縁膜9に開口10を形成する。そして、半導体基板1の裏面にパワーデバイスの裏面側の構造を形成する。次に、図4に示すように、絶縁膜9をマスクにしてメッキ処理を行うことで、開口10を介してエミッタ電極6上にメッキ11を形成する。この際に、小信号電極7は絶縁膜9で覆われて外部と電気的に接続できないため、小信号電極7上にはメッキ11が形成されない。

【0019】

次に、ウェハテストを行う。その後に、無効領域3のダイシングラインに沿って半導体基板1をダイシングする。この際に、サンプルテストモニターの小信号電極7上にメッキ11が形成されていないため、ブレード欠けやチップ端部のチッピングを防ぐことができる。

【0020】

以上説明したように、本実施の形態では、サンプルテストモニターでテストを行った後に、サンプルテストモニターの小信号電極7を絶縁膜9でコーティングする。その後にメッキ処理を行う。これにより、ブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる。

【符号の説明】

【0021】

1 半導体基板

2 有効領域

3 無効領域

4 拡散層(第1の拡散層)

5 拡散層(第2の拡散層)

6 エミッタ電極(第1の電極)

7 小信号電極(第2の電極)

9 絶縁膜

10 開口

11 メッキ

12 プローブ

【特許請求の範囲】

【請求項1】

半導体基板の有効領域と前記有効領域の周囲の無効領域にそれぞれ第1及び第2の拡散層を同時に形成する工程と、

前記第1及び第2の拡散層上にそれぞれ第1及び第2の電極を同時に形成する工程と、

前記第2の電極にプローブを接触させて前記第2の拡散層の電気特性又は前記第2の拡散層と前記第2の電極のコンタクト抵抗を測定するテストを行う工程と、

前記テストの後に、前記第1の電極上に開口を有し、前記第2の電極を覆う絶縁膜を形成する工程と、

前記開口を介して前記第1の電極上にメッキを形成する工程とを備えることを特徴とする半導体装置の製造方法。

【請求項2】

前記メッキを形成した後に、前記無効領域に沿って前記半導体基板をダイシングする工程を更に備えることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

有効領域と前記有効領域の周囲の無効領域とを有する半導体基板と、

前記有効領域及び前記無効領域にそれぞれ設けられた第1及び第2の拡散層と、

前記第1及び第2の拡散層上にそれぞれ設けられた第1及び第2の電極と、

前記第1の電極上に開口を有し、前記第2の電極を覆う絶縁膜と、

前記開口を介して前記第1の電極上に設けられたメッキとを備えることを特徴とする半導体装置。

【請求項1】

半導体基板の有効領域と前記有効領域の周囲の無効領域にそれぞれ第1及び第2の拡散層を同時に形成する工程と、

前記第1及び第2の拡散層上にそれぞれ第1及び第2の電極を同時に形成する工程と、

前記第2の電極にプローブを接触させて前記第2の拡散層の電気特性又は前記第2の拡散層と前記第2の電極のコンタクト抵抗を測定するテストを行う工程と、

前記テストの後に、前記第1の電極上に開口を有し、前記第2の電極を覆う絶縁膜を形成する工程と、

前記開口を介して前記第1の電極上にメッキを形成する工程とを備えることを特徴とする半導体装置の製造方法。

【請求項2】

前記メッキを形成した後に、前記無効領域に沿って前記半導体基板をダイシングする工程を更に備えることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

有効領域と前記有効領域の周囲の無効領域とを有する半導体基板と、

前記有効領域及び前記無効領域にそれぞれ設けられた第1及び第2の拡散層と、

前記第1及び第2の拡散層上にそれぞれ設けられた第1及び第2の電極と、

前記第1の電極上に開口を有し、前記第2の電極を覆う絶縁膜と、

前記開口を介して前記第1の電極上に設けられたメッキとを備えることを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−105937(P2013−105937A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−249602(P2011−249602)

【出願日】平成23年11月15日(2011.11.15)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月15日(2011.11.15)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]