半導体装置及びその製造方法

【課題】半導体装置の特性の均一化を図る。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に設けられた積層体と、絶縁膜と、チャネルボディと、半導体層とを備えている。前記積層体は、選択ゲートと、前記選択ゲート上に設けられた絶縁層とを有する。前記絶縁膜は、前記積層体を積層方向に貫通して形成されたホールの側壁に設けられている。前記チャネルボディは、前記ホール内における前記絶縁膜の側壁に設けられ、前記選択ゲートにおける前記絶縁層側の端部近傍で前記ホールを閉塞し、且つ前記ホールを閉塞する部分より下で空洞を囲む。前記半導体層は、前記チャネルボディが前記ホールを閉塞する部分より上の前記ホール内に、前記チャネルボディと同材料で連続して埋め込まれている。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に設けられた積層体と、絶縁膜と、チャネルボディと、半導体層とを備えている。前記積層体は、選択ゲートと、前記選択ゲート上に設けられた絶縁層とを有する。前記絶縁膜は、前記積層体を積層方向に貫通して形成されたホールの側壁に設けられている。前記チャネルボディは、前記ホール内における前記絶縁膜の側壁に設けられ、前記選択ゲートにおける前記絶縁層側の端部近傍で前記ホールを閉塞し、且つ前記ホールを閉塞する部分より下で空洞を囲む。前記半導体層は、前記チャネルボディが前記ホールを閉塞する部分より上の前記ホール内に、前記チャネルボディと同材料で連続して埋め込まれている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

メモリセルにおけるコントロールゲートとして機能する電極層と、絶縁層とを交互に複数積層した積層体にメモリホールを形成し、そのメモリホールの側壁に電荷蓄積膜を形成した後、メモリホール内にチャネルとなるシリコンを設けることでメモリセルを3次元配列したメモリデバイスが提案されている。

【0003】

そのような3次元積層メモリに特有のデータ消去方法として、GIDL(Gate Induced Drain Leakage)電流を利用した消去方法が提案されている。この消去方法を利用するには、メモリセルの上方に設けられた選択ゲートの上端部近傍のチャネルボディに高濃度の不純物拡散領域が要求される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−225946号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

半導体装置の特性の均一化を図る。

【課題を解決するための手段】

【0006】

実施形態によれば、半導体装置は、基板と、前記基板上に設けられた積層体と、絶縁膜と、チャネルボディと、半導体層とを備えている。前記積層体は、選択ゲートと、前記選択ゲート上に設けられた絶縁層とを有する。前記絶縁膜は、前記積層体を積層方向に貫通して形成されたホールの側壁に設けられている。前記チャネルボディは、前記ホール内における前記絶縁膜の側壁に設けられ、前記選択ゲートにおける前記絶縁層側の端部近傍で前記ホールを閉塞し、且つ前記ホールを閉塞する部分より下で空洞を囲む。前記半導体層は、前記チャネルボディが前記ホールを閉塞する部分より上の前記ホール内に、前記チャネルボディと同材料で連続して埋め込まれている。

【図面の簡単な説明】

【0007】

【図1】実施形態の半導体装置の模式斜視図。

【図2】実施形態の半導体装置におけるメモリセルの模式拡大断面図。

【図3】実施形態の半導体装置の製造方法を示す模式断面図。

【図4】実施形態の半導体装置の製造方法を示す模式断面図。

【図5】実施形態の半導体装置の製造方法を示す模式断面図。

【図6】実施形態の半導体装置の製造方法を示す模式断面図。

【図7】実施形態の半導体装置の製造方法を示す模式断面図。

【発明を実施するための形態】

【0008】

以下、図面を参照し、実施形態について説明する。なお、各図面中、同じ要素には同じ符号を付している。

【0009】

図1は、実施形態の半導体装置におけるメモリセルアレイの模式斜視図である。なお、図1においては、図を見易くするために、絶縁部分については図示を省略している。

図2は、図1におけるメモリセルが設けられた部分の拡大断面図である。

【0010】

また、図1において、説明の便宜上、XYZ直交座標系を導入する。この座標系においては、基板10の主面に対して平行な方向であって相互に直交する2方向をX方向及びY方向とし、これらX方向及びY方向の双方に対して直交する方向をZ方向とする。

【0011】

図1において、基板10上には図示しない絶縁層を介してバックゲートBGが設けられている。バックゲートBGは、例えば不純物が添加され導電性を有するシリコン層を用いることができる。

【0012】

バックゲートBG上には、複数の第1の絶縁層42(図2に示す)と、複数の電極層WL1D、WL2D、WL3D、WL4D、WL1S、WL2S、WL3S、WL4Sが、交互に積層されている。

【0013】

電極層WL1Dと電極層WL1Sは、同じ階層に設けられ、下から(基板10側から)1層目の電極層を表す。電極層WL2Dと電極層WL2Sは、同じ階層に設けられ、下から2層目の電極層を表す。電極層WL3Dと電極層WL3Sは、同じ階層に設けられ、下から3層目の電極層を表す。電極層WL4Dと電極層WL4Sは、同じ階層に設けられ、下から4層目の電極層を表す。

【0014】

電極層WL1Dと電極層WL1Sとは、Y方向に分断されている。電極層WL2Dと電極層WL2Sとは、Y方向に分断されている。電極層WL3Dと電極層WL3Sとは、Y方向に分断されている。電極層WL4Dと電極層WL4Sとは、Y方向に分断されている。

【0015】

電極層WL1Dと電極層WL1Sとの間、電極層WL2Dと電極層WL2Sとの間、電極層WL3Dと電極層WL3Sとの間、および電極層WL4Dと電極層WL4Sとの間には、図4(b)〜図5(b)に示す絶縁膜45が設けられている。

【0016】

電極層WL1D〜WL4Dは、バックゲートBGとドレイン側選択ゲートSGDとの間に設けられている。電極層WL1S〜WL4Sは、バックゲートBGとソース側選択ゲートSGSとの間に設けられている。

【0017】

電極層の層数は任意であり、図1に例示する4層に限らない。また、以下の説明において、各電極層WL1D〜WL4D及びWL1S〜WL4Sを、単に電極層WLと表すこともある。また、図2に示す第1の絶縁層42を、単に絶縁層42と表すこともある。

【0018】

電極層WLは、例えば不純物が添加され導電性を有するシリコン層を用いることができる。絶縁層42は、例えばシリコン酸化物を含むTEOS(tetraethoxysilane)層を用いることができる。

【0019】

電極層WL4D上には、ドレイン側選択ゲートSGDが設けられている。ドレイン側選択ゲートSGDは、例えば不純物が添加され導電性を有するシリコン層を用いることができる。

【0020】

電極層WL4S上には、ソース側選択ゲートSGSが設けられている。ソース側選択ゲートSGSは、例えば不純物が添加され導電性を有するシリコン層を用いることができる。

【0021】

ドレイン側選択ゲートSGDとソース側選択ゲートSGSとは、Y方向に分断されている。なお、以下の説明において、ドレイン側選択ゲートSGDとソース側選択ゲートSGSとを区別することなく単に選択ゲートSGと表すこともある。

【0022】

ソース側選択ゲートSGS上には、ソース線SLが設けられている。ソース線SLは、例えば金属層を用いることができる。

【0023】

ドレイン側選択ゲートSGD及びソース線SL上には、複数本の金属配線であるビット線BLが設けられている。各ビット線BLはY方向に延在している。

【0024】

バックゲートBG及びこのバックゲートBG上の積層体には、図5(b)に示すU字状のメモリホールMHが複数形成されている。電極層WL1D〜WL4Dおよびドレイン側選択ゲートSGDには、それらを貫通しZ方向に延びるホールhが形成されている。電極層WL1S〜WL4Sおよびソース側選択ゲートSGSには、それらを貫通しZ方向に延びるホールhが形成されている。それらZ方向に延びる一対のホールhは、バックゲートBG内に形成された溝81を介してつながり、U字状のメモリホールMHを構成する。

【0025】

メモリホールMHの内部には、図2に示すチャネルボディ20が設けられている。チャネルボディ20は、例えばシリコン膜を用いることができる。チャネルボディ20と、メモリホールMHの内壁との間にはメモリ膜30が設けられている。

【0026】

電極層WL及び絶縁層42を貫通する部分で、チャネルボディ20はメモリホールMHの中心軸側に空洞が残るように形成される。チャネルボディ20は、メモリホールMHの中心軸まわりに、空洞を囲んでいる。

【0027】

ドレイン側選択ゲートSGDとチャネルボディ20との間、およびソース側選択ゲートSGSとチャネルボディ20との間には、図7(c)に示すゲート絶縁膜GDが設けられている。

【0028】

メモリセルトランジスタ(以下、単にメモリセルとも言う)における各電極層WLとチャネルボディ20との間には、図2に示すように、電極層WL側から順に第1の絶縁膜としてブロック膜31、電荷蓄積膜32、および第2の絶縁膜としてトンネル膜33が設けられている。ブロック膜31は電極層WLに接し、トンネル膜33はチャネルボディ20に接し、ブロック膜31とトンネル膜33との間に電荷蓄積膜32が設けられている。

【0029】

チャネルボディ20は、メモリセルトランジスタにおけるチャネルとして機能し、電極層WLはコントロールゲートとして機能し、電荷蓄積膜32はチャネルボディ20から注入される電荷を蓄積するデータ記憶層として機能する。すなわち、チャネルボディ20と各電極層WLとの交差部分に、チャネルの周囲をコントロールゲートが囲んだ構造のメモリセルが形成されている。

【0030】

実施形態の半導体装置は、データの消去・書き込みを電気的に自由に行うことができ、電源を切っても記憶内容を保持することができる不揮発性半導体記憶装置である。

【0031】

メモリセルは、例えばチャージトラップ型のメモリセルである。電荷蓄積膜32は、電荷を捕獲するトラップサイトを多数有し、例えばシリコン窒化膜を用いることができる。

【0032】

トンネル膜33は、例えばシリコン酸化膜を用いることができ、電荷蓄積膜32にチャネルボディ20から電荷が注入される際、または電荷蓄積膜32に蓄積された電荷がチャネルボディ20へ拡散する際に電位障壁となる。

【0033】

ブロック膜31は、例えばシリコン酸化膜を用いることができ、電荷蓄積膜32に蓄積された電荷が、電極層WLへ拡散するのを防止する。

【0034】

ドレイン側選択ゲートSGD、チャネルボディ20及びそれらの間のゲート絶縁膜GDは、ドレイン側選択トランジスタを構成する。ドレイン側選択トランジスタにおけるチャネルボディ20は、ビット線BLと接続されている。

【0035】

ソース側選択ゲートSGS、チャネルボディ20及びそれらの間のゲート絶縁膜GDは、ソース側選択トランジスタを構成する。ソース側選択トランジスタにおけるチャネルボディ20は、ソース線SLと接続されている。

【0036】

バックゲートBG、このバックゲートBG内に設けられたチャネルボディ20及びメモリ膜30は、バックゲートトランジスタを構成する。

【0037】

ドレイン側選択トランジスタとバックゲートトランジスタとの間には、各電極層WL4D〜WL1Dをコントロールゲートとするメモリセルが複数設けられている。同様に、バックゲートトランジスタとソース側選択トランジスタとの間にも、各電極層WL1S〜WL4Sをコントロールゲートとするメモリセルが複数設けられている。

【0038】

それら複数のメモリセル、ドレイン側選択トランジスタ、バックゲートトランジスタおよびソース側選択トランジスタは、チャネルボディ20を通じて直列接続され、U字状の1つのメモリストリングMSを構成する。

【0039】

1つのメモリストリングMSは、複数の電極層WLを含む積層体の積層方向に延びる一対の柱状部CLと、バックゲートBGに埋め込まれ、一対の柱状部CLの下端をつなぐ連結部JPとを有する。このメモリストリングMSがX方向及びY方向に複数配列されていることにより、複数のメモリセルがX方向、Y方向及びZ方向に3次元的に設けられている。

【0040】

次に、図3(a)〜図7(c)を参照して、実施形態の半導体装置におけるメモリセルアレイの製造方法について説明する。

【0041】

図3(a)に示すように、基板10上には絶縁層11を介してバックゲートBGが設けられる。なお、図3(b)以降の工程断面図では、基板10及び絶縁層11の図示は省略する。

【0042】

バックゲートBG上にはレジスト94が形成される。レジスト94はパターニングされ、レジスト94には選択的に開口94aが形成される。

【0043】

そのレジスト94をマスクにして、バックゲートBGを選択的にドライエッチングする。これにより、図3(b)に示すように、バックゲートBGに溝(または凹部)81が形成される。

【0044】

溝81内には、図3(c)に示すように、犠牲膜82が埋め込まれる。犠牲膜82は、例えばシリコン窒化膜を用いることができる。その後、犠牲膜82を全面エッチングして、図3(d)に示すように、溝81と溝81との間のバックゲートBGの上面を露出させる。

【0045】

次に、図4(a)に示すように、バックゲートBG上に絶縁層41を形成した後、その上に、複数の電極層WL及び複数の絶縁層42を含む第1の積層体を形成する。電極層WLと絶縁層42とは交互に積層され、絶縁層42は電極層WL間に介在される。最上層の電極層WL上には、絶縁層43が形成される。

【0046】

次に、フォトリソグラフィとエッチングにより、第1の積層体を分断し、絶縁層41に達する溝を形成した後、その溝を、図4(b)に示すように、絶縁膜45で埋め込む。

【0047】

溝を絶縁膜45で埋め込んだ後、全面エッチングにより絶縁層43を露出させる。その絶縁層43上には、図4(c)に示すように、絶縁層46が形成される。

【0048】

さらに、絶縁層46上には、選択ゲートSG及び第2の絶縁層(以下、単に絶縁層とも言う)47を含む第2の積層体が形成される。絶縁膜46上に選択ゲートSGが形成され、選択ゲートSG上に絶縁層47が形成される。選択ゲートSGは、後述する工程で分断されて、ドレン側選択ゲートSGDまたはソース側選択ゲートSGSとなる。

【0049】

次に、図5(a)に示すように、バックゲートBG上の前述した第1の積層体及び第2の積層体に、ホールhを形成する。ホールhは、図示しないマスクを用いた例えばRIE(Reactive Ion Etching)法で形成される。ホールhの下端は犠牲膜82に達し、ホールhの底部に犠牲膜82が露出する。犠牲膜82のほぼ中央に位置する絶縁膜45を挟むように、一対のホールhが1つの犠牲膜82上に位置する。

【0050】

次に、犠牲膜82を例えばウェットエッチングによりホールhを通じて除去する。このときのエッチング液としては、例えばKOH(水酸化カリウム)溶液等のアルカリ系薬液、あるいは、温度条件によりエッチングレートが調整されたリン酸溶液(H3PO4)を用いることができる。

【0051】

これにより、犠牲膜82は、図5(b)に示すように、除去される。犠牲膜82の除去により、バックゲートBGに溝81が形成される。1つの溝81につき、一対のホールhがつながっている。すなわち、一対のホールhのそれぞれの下端が1つの共通の溝81とつながり、1つのU字状のメモリホールMHが形成される。

【0052】

この後、複数の電極層WLを含む第1の積層体におけるメモリホールMHの側壁に、図2に示すメモリ膜30を形成する。さらに、メモリホールMH内におけるメモリ膜30の内側に、チャネルボディ20を形成する。

【0053】

一方、選択ゲートSGを含む第2の積層体に対しては、後述するように、図6(a)以降の工程が行われる。

【0054】

本実施形態の半導体装置において、データの消去動作は、電荷蓄積膜32からの電子の引き抜き、あるいは、電荷蓄積膜32への正孔の注入を行う動作である。電極層WLをコントロールゲートとするメモリセルを構成するトランジスタは、しきい値電圧が相対的に低い状態(消去状態)と、しきい値電圧が相対的に高い状態(書き込み状態)とを有する。そして、消去動作は、メモリセルのしきい値電圧を低い側の状態に設定する動作である。

【0055】

一般的な2次元構造のメモリでは、基板電位を上げることでフローティングゲートに書き込まれた電子を引き抜いている。しかし、本実施形態のような3次元構造の半導体装置では、メモリセルのチャネルが直接基板とつながっていない。そのため、選択ゲート端のチャネルで生じるGIDL(Gate Induced Drain Leakage)電流を利用してメモリセルのチャネル電位をブーストする方法が提案されている。

【0056】

すなわち、選択ゲートSGの上端部近傍のチャネルボディ20に形成した高濃度に不純物が添加された拡散領域に高電圧を印加することで、選択ゲートSGと拡散領域との間にに形成された空乏層に高電界を発生させる。これにより、バンド間トンネリングを起こし、生成される正孔をチャネルボディ20に供給することでチャネル電位を上昇させる。電極層WLの電位を例えばグランド電位(0V)にすることで、チャネルボディ20と電極層WLとの電位差で、電荷蓄積膜32の電子が引き抜かれ、あるいは、電荷蓄積膜32に正孔が注入され、消去動作が行われる。

【0057】

このような消去動作の高速化には、選択ゲートSG上端部近傍のチャネルボディ20に高濃度に不純物を含む拡散領域が要求される。

【0058】

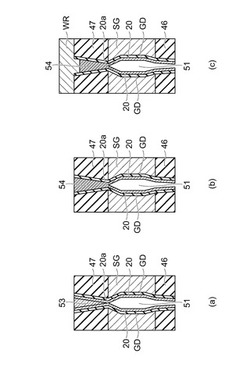

以下、図6(a)〜図7(c)を参照して、実施形態における選択トランジスタ(ドレイン側選択トランジスタ、ソース側選択トランジスタ)の形成方法及び構造について説明する。

【0059】

メモリホールMHにおいて、特に、選択ゲートSG及び絶縁層47を含む第2の積層体を貫通する部分をホールh2とする。

図6(a)は、第2の積層体にホールh2が形成された状態を表す。

【0060】

ホールh2は、その孔径が選択ゲートSGにおける絶縁層47側の上端部近傍で最も狭くなるように形成される。ホールh2は、例えばRIE(Reactive Ion Etching)法で形成される。

【0061】

上記積層体が形成されたウェーハは、処理室内のウェーハ保持部に保持される。そして、処理室内に所望のガスが導入され、下部電極として機能するウェーハ保持部と、ウェーハ保持部に対向する上部電極との間に電力を印加し、処理室内に放電を生じさせる。このときのガス種、ガス流量、電力の大きさなどを制御することで、ホールh2の形状及び孔径を制御する。

【0062】

選択ゲートSGにおける絶縁層47側の上端部近傍のエッチング時には、他の部位のエッチング時に比べて、例えばウェーハ側に印加する電力を大きくして、縦方向(積層方法)のエッチングが支配的になるようにして、横方向のエッチングを抑制する。

【0063】

ホールh2の形成後、図6(b)に示すように、ホールh2の側壁にゲート絶縁膜GDが形成される。ゲート絶縁膜GDは、例えば、シリコン酸化膜あるいはシリコン窒化膜を用いることができる。例えば、ゲート絶縁膜GDは、選択ゲートSG側から順に積層されたブロック膜(シリコン酸化膜)、電荷蓄積膜(シリコン窒化膜)およびトンネル膜(シリコン酸化膜)を含む積層膜を用いることができる。

【0064】

次に、図6(c)に示すように、ホールh2内におけるゲート絶縁膜GDの内側にチャネルボディ20を形成する。チャネルボディ20として、例えばノンドープのアモルファスシリコン膜が形成される。ここで、ノンドープとは、成膜時の原料ガスに起因する元素以外に、意図的にシリコン膜に不純物が添加されていないことを表す。

【0065】

ホールh2の孔径は選択ゲートSGにおける絶縁層47側の上端部近傍で最も狭くなっている。したがって、チャネルボディ20は、選択ゲートSGにおける絶縁層47側の上端部近傍でホールh2を閉塞し、その閉塞部20aより下で、ホールh2の中心軸まわりに空洞51を囲む。

【0066】

次に、図7(a)に示すように、チャネルボディ20の閉塞部20aより上のチャネルボディ20の内側に、半導体層53を埋め込む。半導体層53は、チャネルボディ20と同じ材料であるアモルファスシリコンであるが、ノンドープのチャネルボディ20に対して半導体層53は不純物を含む。半導体層53は、半導体層53に導電性を与える不純物として、例えばn形不純物を含む。あるいは、半導体層53は、p形不純物を含んでいてもよい。

【0067】

チャネルボディ20と半導体層53とは、同じ処理室内で、大気開放されることなく続けて成膜される。シリコンを含む原料ガスを用いた例えばCVD(chemical vapor deposition)法でチャネルボディ20を形成し、続けて、シリコンを含む原料ガスに加えて不純物を含むガス(例えばホスフィン(PH3)ガス)を処理室内に導入して、半導体層53を形成する。したがって、チャネルボディ20と半導体層53との界面に、酸化膜が形成されない。

【0068】

その後、熱処理を行う。この熱処理により、チャネルボディ20及び半導体層53は多結晶シリコンになる。すなわち、閉塞部20aより上のチャネルボディ20及び半導体層53は、図7(b)に示すように、連続した一体の多結晶シリコンからなる半導体層54となる。ここで、「連続した一体」とは、チャネルボディ20と半導体層53との界面がなく、また酸化膜も介在していないことを表す。

【0069】

また、上記熱処理により、半導体層53に含まれていた不純物がチャネルボディ20に拡散する。不純物は、半導体層54全体および選択ゲートSG間のチャネルボディ20における閉塞部20a近傍部分に拡散する。

【0070】

したがって、半導体層54の不純物濃度及び閉塞部20a近傍のチャネルボディ20の不純物濃度は、選択ゲートSG間のチャネルボディ20の不純物濃度およびメモリセルのチャネルボディ20の不純物濃度よりも高い。半導体層54の不純物濃度及び閉塞部20a近傍のチャネルボディ20の不純物濃度(図7(b)においてドットを付した部分の不純物濃度)は、例えば、1×1018cm−3〜1×1019cm−3ほどである。

【0071】

半導体層54を形成した後、半導体層54の上部をエッチングによりリセスする。その後、ビット線BLまたはソース線SLとなる配線WRを、半導体層54のリセスした部分および絶縁層47上に形成する。半導体54は配線WRと接続される。したがって、チャネルボディ20は、半導体層54を通じて、配線WRと接続される。

【0072】

実施形態によれば、選択ゲートSG上端部近傍のチャネルボディ20(半導体層54に一体になった部分も含む)に高濃度に不純物を含む拡散領域が存在する。この結果、前述したGIDL電流を利用してメモリセルのチャネル電位を速やかにブーストでき、消去動作の高速化を図れる。

【0073】

なお、比較例として、以下に説明する方法が挙げられる。

【0074】

ホールh2の形成後、その側壁に絶縁膜GDを形成し、その後、チャネルボディを途中で閉塞させずに絶縁膜GDの側壁に形成する。ゲート絶縁膜GDは、例えば、選択ゲート側から順に積層されたブロック膜(シリコン酸化膜)、電荷蓄積膜(シリコン窒化膜)およびトンネル膜(シリコン酸化膜)を含む積層膜を用いることができる。その後、ホールh2内におけるチャネルボディの内側にコア絶縁膜を埋め込む。その後、コア絶縁膜を選択ゲートSGの上端付近までエッチングにより除去するリセス工程を行い、そのコア絶縁膜が除去された部分にノンドープシリコン膜を埋め込む。その後、ノンドープシリコン膜を、選択ゲートSGの上端付近までリセスし、そのリセスした部分に、不純物を含むキャップシリコン膜を埋め込む。

【0075】

選択ゲートSGの上端部近傍でGIDLを効果的に発生させるためには、高不純物濃度拡散領域の、選択ゲートSGに対する高い位置精度が求められる。しかしながら、上記比較例の方法では、拡散領域の不純物濃度および位置ともに制御することが困難で、特性ばらつきが生じやすく、かつ工程数の増加もまねいてしまう。

【0076】

上記比較例において、拡散領域の不純物濃度、深さのばらつきを生む要因として、複数回のリセス工程、チャネルボディと、不純物拡散源となるキャップシリコン層との界面抵抗の存在が考えられる。

【0077】

これに対して、実施形態によれば、チャネルボディ20を形成した後、その内側に埋め込まれる、不純物を含む半導体層53の下端位置は、チャネルボディ20の閉塞部20aの位置によって決まる。閉塞部20aの位置制御は、リセスエッチングによる膜の後退位置制御よりも容易であり、閉塞部20aの位置を選択ゲートSG上端部近傍に制御することで、選択ゲートSG上端部近傍に安定して高不純物濃度の拡散領域を形成することができる。

【0078】

すなわち、実施形態によれば、複数回のリセス工程を経て不純物拡散源の深さ位置が決まる比較例よりも、不純物拡散源である半導体層53の埋込位置のばらつきを抑制することができる。

【0079】

また、実施形態によれば、選択ゲートSG上端部近傍のチャネルボディ20と、半導体層54との間に界面がなく、自然酸化膜も介在していない。したがって、不純物拡散源である半導体層とチャネルボディとの界面抵抗に起因する抵抗上昇をまねかない。

【0080】

以上説明したように、実施形態によれば、リセス工程の省略および不純物拡散領域におけるシリコン膜間の界面を有しない構造を実現できる。この結果、工程省略とプロセス安定化の両立を図ることができ、なおかつデバイス特性が均一な縦型構造の選択トランジスタひいてはメモリセルアレイを提供することができる。

【0081】

閉塞部20aより下のホールh2内は、絶縁膜やチャネルボディ20で埋め込まれず、選択ゲートSG間のチャネルボディ20の内側およびメモリセルにおけるチャネルボディ20の内側には空洞51が形成されている。その空洞51を囲むチャネルボディ20には、ほとんど不純物が含まれていない。

【0082】

したがって、高濃度不純物にゲート絶縁膜GDがさらされることによるゲート絶縁膜GDの耐圧低下や、高濃度不純物が選択トランジスタやメモリセルのチャネルボディ20に供給されることにより引き起こされるしきい値変動を防ぐことができる。

【0083】

また、空洞51に隣接するチャネルボディ20の内側には絶縁膜が形成されていないため、その絶縁膜とチャネルボディ20との界面の電荷トラップ準位に起因する選択トランジスタやメモリセルのしきい値変動シフトを抑制できる。

【0084】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0085】

10…基板、20…チャネルボディ、30…メモリ膜、32…電荷蓄積膜、42,43,46,47…絶縁層、51…空洞、53,54…半導体層、WL,WL1D〜WL4D,WL1S〜WL4S…電極層、SG…選択ゲート

【技術分野】

【0001】

本発明の実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

メモリセルにおけるコントロールゲートとして機能する電極層と、絶縁層とを交互に複数積層した積層体にメモリホールを形成し、そのメモリホールの側壁に電荷蓄積膜を形成した後、メモリホール内にチャネルとなるシリコンを設けることでメモリセルを3次元配列したメモリデバイスが提案されている。

【0003】

そのような3次元積層メモリに特有のデータ消去方法として、GIDL(Gate Induced Drain Leakage)電流を利用した消去方法が提案されている。この消去方法を利用するには、メモリセルの上方に設けられた選択ゲートの上端部近傍のチャネルボディに高濃度の不純物拡散領域が要求される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−225946号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

半導体装置の特性の均一化を図る。

【課題を解決するための手段】

【0006】

実施形態によれば、半導体装置は、基板と、前記基板上に設けられた積層体と、絶縁膜と、チャネルボディと、半導体層とを備えている。前記積層体は、選択ゲートと、前記選択ゲート上に設けられた絶縁層とを有する。前記絶縁膜は、前記積層体を積層方向に貫通して形成されたホールの側壁に設けられている。前記チャネルボディは、前記ホール内における前記絶縁膜の側壁に設けられ、前記選択ゲートにおける前記絶縁層側の端部近傍で前記ホールを閉塞し、且つ前記ホールを閉塞する部分より下で空洞を囲む。前記半導体層は、前記チャネルボディが前記ホールを閉塞する部分より上の前記ホール内に、前記チャネルボディと同材料で連続して埋め込まれている。

【図面の簡単な説明】

【0007】

【図1】実施形態の半導体装置の模式斜視図。

【図2】実施形態の半導体装置におけるメモリセルの模式拡大断面図。

【図3】実施形態の半導体装置の製造方法を示す模式断面図。

【図4】実施形態の半導体装置の製造方法を示す模式断面図。

【図5】実施形態の半導体装置の製造方法を示す模式断面図。

【図6】実施形態の半導体装置の製造方法を示す模式断面図。

【図7】実施形態の半導体装置の製造方法を示す模式断面図。

【発明を実施するための形態】

【0008】

以下、図面を参照し、実施形態について説明する。なお、各図面中、同じ要素には同じ符号を付している。

【0009】

図1は、実施形態の半導体装置におけるメモリセルアレイの模式斜視図である。なお、図1においては、図を見易くするために、絶縁部分については図示を省略している。

図2は、図1におけるメモリセルが設けられた部分の拡大断面図である。

【0010】

また、図1において、説明の便宜上、XYZ直交座標系を導入する。この座標系においては、基板10の主面に対して平行な方向であって相互に直交する2方向をX方向及びY方向とし、これらX方向及びY方向の双方に対して直交する方向をZ方向とする。

【0011】

図1において、基板10上には図示しない絶縁層を介してバックゲートBGが設けられている。バックゲートBGは、例えば不純物が添加され導電性を有するシリコン層を用いることができる。

【0012】

バックゲートBG上には、複数の第1の絶縁層42(図2に示す)と、複数の電極層WL1D、WL2D、WL3D、WL4D、WL1S、WL2S、WL3S、WL4Sが、交互に積層されている。

【0013】

電極層WL1Dと電極層WL1Sは、同じ階層に設けられ、下から(基板10側から)1層目の電極層を表す。電極層WL2Dと電極層WL2Sは、同じ階層に設けられ、下から2層目の電極層を表す。電極層WL3Dと電極層WL3Sは、同じ階層に設けられ、下から3層目の電極層を表す。電極層WL4Dと電極層WL4Sは、同じ階層に設けられ、下から4層目の電極層を表す。

【0014】

電極層WL1Dと電極層WL1Sとは、Y方向に分断されている。電極層WL2Dと電極層WL2Sとは、Y方向に分断されている。電極層WL3Dと電極層WL3Sとは、Y方向に分断されている。電極層WL4Dと電極層WL4Sとは、Y方向に分断されている。

【0015】

電極層WL1Dと電極層WL1Sとの間、電極層WL2Dと電極層WL2Sとの間、電極層WL3Dと電極層WL3Sとの間、および電極層WL4Dと電極層WL4Sとの間には、図4(b)〜図5(b)に示す絶縁膜45が設けられている。

【0016】

電極層WL1D〜WL4Dは、バックゲートBGとドレイン側選択ゲートSGDとの間に設けられている。電極層WL1S〜WL4Sは、バックゲートBGとソース側選択ゲートSGSとの間に設けられている。

【0017】

電極層の層数は任意であり、図1に例示する4層に限らない。また、以下の説明において、各電極層WL1D〜WL4D及びWL1S〜WL4Sを、単に電極層WLと表すこともある。また、図2に示す第1の絶縁層42を、単に絶縁層42と表すこともある。

【0018】

電極層WLは、例えば不純物が添加され導電性を有するシリコン層を用いることができる。絶縁層42は、例えばシリコン酸化物を含むTEOS(tetraethoxysilane)層を用いることができる。

【0019】

電極層WL4D上には、ドレイン側選択ゲートSGDが設けられている。ドレイン側選択ゲートSGDは、例えば不純物が添加され導電性を有するシリコン層を用いることができる。

【0020】

電極層WL4S上には、ソース側選択ゲートSGSが設けられている。ソース側選択ゲートSGSは、例えば不純物が添加され導電性を有するシリコン層を用いることができる。

【0021】

ドレイン側選択ゲートSGDとソース側選択ゲートSGSとは、Y方向に分断されている。なお、以下の説明において、ドレイン側選択ゲートSGDとソース側選択ゲートSGSとを区別することなく単に選択ゲートSGと表すこともある。

【0022】

ソース側選択ゲートSGS上には、ソース線SLが設けられている。ソース線SLは、例えば金属層を用いることができる。

【0023】

ドレイン側選択ゲートSGD及びソース線SL上には、複数本の金属配線であるビット線BLが設けられている。各ビット線BLはY方向に延在している。

【0024】

バックゲートBG及びこのバックゲートBG上の積層体には、図5(b)に示すU字状のメモリホールMHが複数形成されている。電極層WL1D〜WL4Dおよびドレイン側選択ゲートSGDには、それらを貫通しZ方向に延びるホールhが形成されている。電極層WL1S〜WL4Sおよびソース側選択ゲートSGSには、それらを貫通しZ方向に延びるホールhが形成されている。それらZ方向に延びる一対のホールhは、バックゲートBG内に形成された溝81を介してつながり、U字状のメモリホールMHを構成する。

【0025】

メモリホールMHの内部には、図2に示すチャネルボディ20が設けられている。チャネルボディ20は、例えばシリコン膜を用いることができる。チャネルボディ20と、メモリホールMHの内壁との間にはメモリ膜30が設けられている。

【0026】

電極層WL及び絶縁層42を貫通する部分で、チャネルボディ20はメモリホールMHの中心軸側に空洞が残るように形成される。チャネルボディ20は、メモリホールMHの中心軸まわりに、空洞を囲んでいる。

【0027】

ドレイン側選択ゲートSGDとチャネルボディ20との間、およびソース側選択ゲートSGSとチャネルボディ20との間には、図7(c)に示すゲート絶縁膜GDが設けられている。

【0028】

メモリセルトランジスタ(以下、単にメモリセルとも言う)における各電極層WLとチャネルボディ20との間には、図2に示すように、電極層WL側から順に第1の絶縁膜としてブロック膜31、電荷蓄積膜32、および第2の絶縁膜としてトンネル膜33が設けられている。ブロック膜31は電極層WLに接し、トンネル膜33はチャネルボディ20に接し、ブロック膜31とトンネル膜33との間に電荷蓄積膜32が設けられている。

【0029】

チャネルボディ20は、メモリセルトランジスタにおけるチャネルとして機能し、電極層WLはコントロールゲートとして機能し、電荷蓄積膜32はチャネルボディ20から注入される電荷を蓄積するデータ記憶層として機能する。すなわち、チャネルボディ20と各電極層WLとの交差部分に、チャネルの周囲をコントロールゲートが囲んだ構造のメモリセルが形成されている。

【0030】

実施形態の半導体装置は、データの消去・書き込みを電気的に自由に行うことができ、電源を切っても記憶内容を保持することができる不揮発性半導体記憶装置である。

【0031】

メモリセルは、例えばチャージトラップ型のメモリセルである。電荷蓄積膜32は、電荷を捕獲するトラップサイトを多数有し、例えばシリコン窒化膜を用いることができる。

【0032】

トンネル膜33は、例えばシリコン酸化膜を用いることができ、電荷蓄積膜32にチャネルボディ20から電荷が注入される際、または電荷蓄積膜32に蓄積された電荷がチャネルボディ20へ拡散する際に電位障壁となる。

【0033】

ブロック膜31は、例えばシリコン酸化膜を用いることができ、電荷蓄積膜32に蓄積された電荷が、電極層WLへ拡散するのを防止する。

【0034】

ドレイン側選択ゲートSGD、チャネルボディ20及びそれらの間のゲート絶縁膜GDは、ドレイン側選択トランジスタを構成する。ドレイン側選択トランジスタにおけるチャネルボディ20は、ビット線BLと接続されている。

【0035】

ソース側選択ゲートSGS、チャネルボディ20及びそれらの間のゲート絶縁膜GDは、ソース側選択トランジスタを構成する。ソース側選択トランジスタにおけるチャネルボディ20は、ソース線SLと接続されている。

【0036】

バックゲートBG、このバックゲートBG内に設けられたチャネルボディ20及びメモリ膜30は、バックゲートトランジスタを構成する。

【0037】

ドレイン側選択トランジスタとバックゲートトランジスタとの間には、各電極層WL4D〜WL1Dをコントロールゲートとするメモリセルが複数設けられている。同様に、バックゲートトランジスタとソース側選択トランジスタとの間にも、各電極層WL1S〜WL4Sをコントロールゲートとするメモリセルが複数設けられている。

【0038】

それら複数のメモリセル、ドレイン側選択トランジスタ、バックゲートトランジスタおよびソース側選択トランジスタは、チャネルボディ20を通じて直列接続され、U字状の1つのメモリストリングMSを構成する。

【0039】

1つのメモリストリングMSは、複数の電極層WLを含む積層体の積層方向に延びる一対の柱状部CLと、バックゲートBGに埋め込まれ、一対の柱状部CLの下端をつなぐ連結部JPとを有する。このメモリストリングMSがX方向及びY方向に複数配列されていることにより、複数のメモリセルがX方向、Y方向及びZ方向に3次元的に設けられている。

【0040】

次に、図3(a)〜図7(c)を参照して、実施形態の半導体装置におけるメモリセルアレイの製造方法について説明する。

【0041】

図3(a)に示すように、基板10上には絶縁層11を介してバックゲートBGが設けられる。なお、図3(b)以降の工程断面図では、基板10及び絶縁層11の図示は省略する。

【0042】

バックゲートBG上にはレジスト94が形成される。レジスト94はパターニングされ、レジスト94には選択的に開口94aが形成される。

【0043】

そのレジスト94をマスクにして、バックゲートBGを選択的にドライエッチングする。これにより、図3(b)に示すように、バックゲートBGに溝(または凹部)81が形成される。

【0044】

溝81内には、図3(c)に示すように、犠牲膜82が埋め込まれる。犠牲膜82は、例えばシリコン窒化膜を用いることができる。その後、犠牲膜82を全面エッチングして、図3(d)に示すように、溝81と溝81との間のバックゲートBGの上面を露出させる。

【0045】

次に、図4(a)に示すように、バックゲートBG上に絶縁層41を形成した後、その上に、複数の電極層WL及び複数の絶縁層42を含む第1の積層体を形成する。電極層WLと絶縁層42とは交互に積層され、絶縁層42は電極層WL間に介在される。最上層の電極層WL上には、絶縁層43が形成される。

【0046】

次に、フォトリソグラフィとエッチングにより、第1の積層体を分断し、絶縁層41に達する溝を形成した後、その溝を、図4(b)に示すように、絶縁膜45で埋め込む。

【0047】

溝を絶縁膜45で埋め込んだ後、全面エッチングにより絶縁層43を露出させる。その絶縁層43上には、図4(c)に示すように、絶縁層46が形成される。

【0048】

さらに、絶縁層46上には、選択ゲートSG及び第2の絶縁層(以下、単に絶縁層とも言う)47を含む第2の積層体が形成される。絶縁膜46上に選択ゲートSGが形成され、選択ゲートSG上に絶縁層47が形成される。選択ゲートSGは、後述する工程で分断されて、ドレン側選択ゲートSGDまたはソース側選択ゲートSGSとなる。

【0049】

次に、図5(a)に示すように、バックゲートBG上の前述した第1の積層体及び第2の積層体に、ホールhを形成する。ホールhは、図示しないマスクを用いた例えばRIE(Reactive Ion Etching)法で形成される。ホールhの下端は犠牲膜82に達し、ホールhの底部に犠牲膜82が露出する。犠牲膜82のほぼ中央に位置する絶縁膜45を挟むように、一対のホールhが1つの犠牲膜82上に位置する。

【0050】

次に、犠牲膜82を例えばウェットエッチングによりホールhを通じて除去する。このときのエッチング液としては、例えばKOH(水酸化カリウム)溶液等のアルカリ系薬液、あるいは、温度条件によりエッチングレートが調整されたリン酸溶液(H3PO4)を用いることができる。

【0051】

これにより、犠牲膜82は、図5(b)に示すように、除去される。犠牲膜82の除去により、バックゲートBGに溝81が形成される。1つの溝81につき、一対のホールhがつながっている。すなわち、一対のホールhのそれぞれの下端が1つの共通の溝81とつながり、1つのU字状のメモリホールMHが形成される。

【0052】

この後、複数の電極層WLを含む第1の積層体におけるメモリホールMHの側壁に、図2に示すメモリ膜30を形成する。さらに、メモリホールMH内におけるメモリ膜30の内側に、チャネルボディ20を形成する。

【0053】

一方、選択ゲートSGを含む第2の積層体に対しては、後述するように、図6(a)以降の工程が行われる。

【0054】

本実施形態の半導体装置において、データの消去動作は、電荷蓄積膜32からの電子の引き抜き、あるいは、電荷蓄積膜32への正孔の注入を行う動作である。電極層WLをコントロールゲートとするメモリセルを構成するトランジスタは、しきい値電圧が相対的に低い状態(消去状態)と、しきい値電圧が相対的に高い状態(書き込み状態)とを有する。そして、消去動作は、メモリセルのしきい値電圧を低い側の状態に設定する動作である。

【0055】

一般的な2次元構造のメモリでは、基板電位を上げることでフローティングゲートに書き込まれた電子を引き抜いている。しかし、本実施形態のような3次元構造の半導体装置では、メモリセルのチャネルが直接基板とつながっていない。そのため、選択ゲート端のチャネルで生じるGIDL(Gate Induced Drain Leakage)電流を利用してメモリセルのチャネル電位をブーストする方法が提案されている。

【0056】

すなわち、選択ゲートSGの上端部近傍のチャネルボディ20に形成した高濃度に不純物が添加された拡散領域に高電圧を印加することで、選択ゲートSGと拡散領域との間にに形成された空乏層に高電界を発生させる。これにより、バンド間トンネリングを起こし、生成される正孔をチャネルボディ20に供給することでチャネル電位を上昇させる。電極層WLの電位を例えばグランド電位(0V)にすることで、チャネルボディ20と電極層WLとの電位差で、電荷蓄積膜32の電子が引き抜かれ、あるいは、電荷蓄積膜32に正孔が注入され、消去動作が行われる。

【0057】

このような消去動作の高速化には、選択ゲートSG上端部近傍のチャネルボディ20に高濃度に不純物を含む拡散領域が要求される。

【0058】

以下、図6(a)〜図7(c)を参照して、実施形態における選択トランジスタ(ドレイン側選択トランジスタ、ソース側選択トランジスタ)の形成方法及び構造について説明する。

【0059】

メモリホールMHにおいて、特に、選択ゲートSG及び絶縁層47を含む第2の積層体を貫通する部分をホールh2とする。

図6(a)は、第2の積層体にホールh2が形成された状態を表す。

【0060】

ホールh2は、その孔径が選択ゲートSGにおける絶縁層47側の上端部近傍で最も狭くなるように形成される。ホールh2は、例えばRIE(Reactive Ion Etching)法で形成される。

【0061】

上記積層体が形成されたウェーハは、処理室内のウェーハ保持部に保持される。そして、処理室内に所望のガスが導入され、下部電極として機能するウェーハ保持部と、ウェーハ保持部に対向する上部電極との間に電力を印加し、処理室内に放電を生じさせる。このときのガス種、ガス流量、電力の大きさなどを制御することで、ホールh2の形状及び孔径を制御する。

【0062】

選択ゲートSGにおける絶縁層47側の上端部近傍のエッチング時には、他の部位のエッチング時に比べて、例えばウェーハ側に印加する電力を大きくして、縦方向(積層方法)のエッチングが支配的になるようにして、横方向のエッチングを抑制する。

【0063】

ホールh2の形成後、図6(b)に示すように、ホールh2の側壁にゲート絶縁膜GDが形成される。ゲート絶縁膜GDは、例えば、シリコン酸化膜あるいはシリコン窒化膜を用いることができる。例えば、ゲート絶縁膜GDは、選択ゲートSG側から順に積層されたブロック膜(シリコン酸化膜)、電荷蓄積膜(シリコン窒化膜)およびトンネル膜(シリコン酸化膜)を含む積層膜を用いることができる。

【0064】

次に、図6(c)に示すように、ホールh2内におけるゲート絶縁膜GDの内側にチャネルボディ20を形成する。チャネルボディ20として、例えばノンドープのアモルファスシリコン膜が形成される。ここで、ノンドープとは、成膜時の原料ガスに起因する元素以外に、意図的にシリコン膜に不純物が添加されていないことを表す。

【0065】

ホールh2の孔径は選択ゲートSGにおける絶縁層47側の上端部近傍で最も狭くなっている。したがって、チャネルボディ20は、選択ゲートSGにおける絶縁層47側の上端部近傍でホールh2を閉塞し、その閉塞部20aより下で、ホールh2の中心軸まわりに空洞51を囲む。

【0066】

次に、図7(a)に示すように、チャネルボディ20の閉塞部20aより上のチャネルボディ20の内側に、半導体層53を埋め込む。半導体層53は、チャネルボディ20と同じ材料であるアモルファスシリコンであるが、ノンドープのチャネルボディ20に対して半導体層53は不純物を含む。半導体層53は、半導体層53に導電性を与える不純物として、例えばn形不純物を含む。あるいは、半導体層53は、p形不純物を含んでいてもよい。

【0067】

チャネルボディ20と半導体層53とは、同じ処理室内で、大気開放されることなく続けて成膜される。シリコンを含む原料ガスを用いた例えばCVD(chemical vapor deposition)法でチャネルボディ20を形成し、続けて、シリコンを含む原料ガスに加えて不純物を含むガス(例えばホスフィン(PH3)ガス)を処理室内に導入して、半導体層53を形成する。したがって、チャネルボディ20と半導体層53との界面に、酸化膜が形成されない。

【0068】

その後、熱処理を行う。この熱処理により、チャネルボディ20及び半導体層53は多結晶シリコンになる。すなわち、閉塞部20aより上のチャネルボディ20及び半導体層53は、図7(b)に示すように、連続した一体の多結晶シリコンからなる半導体層54となる。ここで、「連続した一体」とは、チャネルボディ20と半導体層53との界面がなく、また酸化膜も介在していないことを表す。

【0069】

また、上記熱処理により、半導体層53に含まれていた不純物がチャネルボディ20に拡散する。不純物は、半導体層54全体および選択ゲートSG間のチャネルボディ20における閉塞部20a近傍部分に拡散する。

【0070】

したがって、半導体層54の不純物濃度及び閉塞部20a近傍のチャネルボディ20の不純物濃度は、選択ゲートSG間のチャネルボディ20の不純物濃度およびメモリセルのチャネルボディ20の不純物濃度よりも高い。半導体層54の不純物濃度及び閉塞部20a近傍のチャネルボディ20の不純物濃度(図7(b)においてドットを付した部分の不純物濃度)は、例えば、1×1018cm−3〜1×1019cm−3ほどである。

【0071】

半導体層54を形成した後、半導体層54の上部をエッチングによりリセスする。その後、ビット線BLまたはソース線SLとなる配線WRを、半導体層54のリセスした部分および絶縁層47上に形成する。半導体54は配線WRと接続される。したがって、チャネルボディ20は、半導体層54を通じて、配線WRと接続される。

【0072】

実施形態によれば、選択ゲートSG上端部近傍のチャネルボディ20(半導体層54に一体になった部分も含む)に高濃度に不純物を含む拡散領域が存在する。この結果、前述したGIDL電流を利用してメモリセルのチャネル電位を速やかにブーストでき、消去動作の高速化を図れる。

【0073】

なお、比較例として、以下に説明する方法が挙げられる。

【0074】

ホールh2の形成後、その側壁に絶縁膜GDを形成し、その後、チャネルボディを途中で閉塞させずに絶縁膜GDの側壁に形成する。ゲート絶縁膜GDは、例えば、選択ゲート側から順に積層されたブロック膜(シリコン酸化膜)、電荷蓄積膜(シリコン窒化膜)およびトンネル膜(シリコン酸化膜)を含む積層膜を用いることができる。その後、ホールh2内におけるチャネルボディの内側にコア絶縁膜を埋め込む。その後、コア絶縁膜を選択ゲートSGの上端付近までエッチングにより除去するリセス工程を行い、そのコア絶縁膜が除去された部分にノンドープシリコン膜を埋め込む。その後、ノンドープシリコン膜を、選択ゲートSGの上端付近までリセスし、そのリセスした部分に、不純物を含むキャップシリコン膜を埋め込む。

【0075】

選択ゲートSGの上端部近傍でGIDLを効果的に発生させるためには、高不純物濃度拡散領域の、選択ゲートSGに対する高い位置精度が求められる。しかしながら、上記比較例の方法では、拡散領域の不純物濃度および位置ともに制御することが困難で、特性ばらつきが生じやすく、かつ工程数の増加もまねいてしまう。

【0076】

上記比較例において、拡散領域の不純物濃度、深さのばらつきを生む要因として、複数回のリセス工程、チャネルボディと、不純物拡散源となるキャップシリコン層との界面抵抗の存在が考えられる。

【0077】

これに対して、実施形態によれば、チャネルボディ20を形成した後、その内側に埋め込まれる、不純物を含む半導体層53の下端位置は、チャネルボディ20の閉塞部20aの位置によって決まる。閉塞部20aの位置制御は、リセスエッチングによる膜の後退位置制御よりも容易であり、閉塞部20aの位置を選択ゲートSG上端部近傍に制御することで、選択ゲートSG上端部近傍に安定して高不純物濃度の拡散領域を形成することができる。

【0078】

すなわち、実施形態によれば、複数回のリセス工程を経て不純物拡散源の深さ位置が決まる比較例よりも、不純物拡散源である半導体層53の埋込位置のばらつきを抑制することができる。

【0079】

また、実施形態によれば、選択ゲートSG上端部近傍のチャネルボディ20と、半導体層54との間に界面がなく、自然酸化膜も介在していない。したがって、不純物拡散源である半導体層とチャネルボディとの界面抵抗に起因する抵抗上昇をまねかない。

【0080】

以上説明したように、実施形態によれば、リセス工程の省略および不純物拡散領域におけるシリコン膜間の界面を有しない構造を実現できる。この結果、工程省略とプロセス安定化の両立を図ることができ、なおかつデバイス特性が均一な縦型構造の選択トランジスタひいてはメモリセルアレイを提供することができる。

【0081】

閉塞部20aより下のホールh2内は、絶縁膜やチャネルボディ20で埋め込まれず、選択ゲートSG間のチャネルボディ20の内側およびメモリセルにおけるチャネルボディ20の内側には空洞51が形成されている。その空洞51を囲むチャネルボディ20には、ほとんど不純物が含まれていない。

【0082】

したがって、高濃度不純物にゲート絶縁膜GDがさらされることによるゲート絶縁膜GDの耐圧低下や、高濃度不純物が選択トランジスタやメモリセルのチャネルボディ20に供給されることにより引き起こされるしきい値変動を防ぐことができる。

【0083】

また、空洞51に隣接するチャネルボディ20の内側には絶縁膜が形成されていないため、その絶縁膜とチャネルボディ20との界面の電荷トラップ準位に起因する選択トランジスタやメモリセルのしきい値変動シフトを抑制できる。

【0084】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0085】

10…基板、20…チャネルボディ、30…メモリ膜、32…電荷蓄積膜、42,43,46,47…絶縁層、51…空洞、53,54…半導体層、WL,WL1D〜WL4D,WL1S〜WL4S…電極層、SG…選択ゲート

【特許請求の範囲】

【請求項1】

基板と、

前記基板上にそれぞれ交互に積層された複数の電極層と複数の第1の絶縁層とを有する第1の積層体と、

前記第1の積層体を積層方向に貫通して形成された第1のホールの側壁に設けられたメモリ膜と、

前記第1の積層体上に設けられた第2の積層体であって、選択ゲートと前記選択ゲート上に設けられた第2の絶縁層とを有する第2の積層体と、

前記第2の積層体を積層方向に貫通して前記第1のホールと連通する第2のホールの側壁に設けられた絶縁膜と、

前記第1のホール内における前記メモリ膜の側壁および前記第2のホール内における前記絶縁膜の側壁に設けられ、前記選択ゲートにおける前記第2の絶縁層側の端部近傍で前記第2のホールを閉塞し、且つ前記第2のホールを閉塞する部分より下で空洞を囲むチャネルボディと、

前記チャネルボディが前記第2のホールを閉塞する部分より上の前記第2のホール内に、前記チャネルボディと同材料で連続して埋め込まれ、前記チャネルボディよりも不純物濃度が高い半導体層と、

を備えた半導体装置。

【請求項2】

基板と、

前記基板上に設けられた積層体であって、選択ゲートと前記選択ゲート上に設けられた絶縁層とを有する積層体と、

前記積層体を積層方向に貫通して形成されたホールの側壁に設けられた絶縁膜と、

前記ホール内における前記絶縁膜の側壁に設けられ、前記選択ゲートにおける前記絶縁層側の端部近傍で前記ホールを閉塞し、且つ前記ホールを閉塞する部分より下で空洞を囲むチャネルボディと、

前記チャネルボディが前記ホールを閉塞する部分より上の前記ホール内に、前記チャネルボディと同材料で連続して埋め込まれた半導体層と、

を備えた半導体装置。

【請求項3】

前記半導体層の不純物濃度は前記チャネルボディの不純物濃度よりも高い請求項2記載の半導体装置。

【請求項4】

基板上に、選択ゲートと、前記選択ゲート上に設けられた絶縁層とを有する積層体を形成する工程と、

前記積層体を積層方向に貫通するホールを形成する工程と、

前記ホールの側壁に絶縁膜を形成する工程と、

前記選択ゲートにおける前記絶縁層側の端部近傍で前記ホールを閉塞し、且つ前記ホールを閉塞する部分より下で空洞を囲むチャネルボディを、前記絶縁膜の側壁に形成する工程と、

前記チャネルボディを形成する処理室と同じ処理室内で、前記チャネルボディの形成に続けて、前記チャネルボディと同じ材料であって不純物を含む半導体層を、前記チャネルボディが前記ホールを閉塞する部分よりも上の前記ホール内における前記チャネルボディの内側に埋め込む工程と、

前記半導体層に含まれる前記不純物を、前記チャネルボディに拡散させる熱処理をする工程と、

を備えた半導体装置の製造方法。

【請求項5】

前記ホールの孔径が前記選択ゲートの前記絶縁層側の端部近傍で最も狭くなるように、前記ホールを形成する請求項4記載の半導体装置の製造方法。

【請求項1】

基板と、

前記基板上にそれぞれ交互に積層された複数の電極層と複数の第1の絶縁層とを有する第1の積層体と、

前記第1の積層体を積層方向に貫通して形成された第1のホールの側壁に設けられたメモリ膜と、

前記第1の積層体上に設けられた第2の積層体であって、選択ゲートと前記選択ゲート上に設けられた第2の絶縁層とを有する第2の積層体と、

前記第2の積層体を積層方向に貫通して前記第1のホールと連通する第2のホールの側壁に設けられた絶縁膜と、

前記第1のホール内における前記メモリ膜の側壁および前記第2のホール内における前記絶縁膜の側壁に設けられ、前記選択ゲートにおける前記第2の絶縁層側の端部近傍で前記第2のホールを閉塞し、且つ前記第2のホールを閉塞する部分より下で空洞を囲むチャネルボディと、

前記チャネルボディが前記第2のホールを閉塞する部分より上の前記第2のホール内に、前記チャネルボディと同材料で連続して埋め込まれ、前記チャネルボディよりも不純物濃度が高い半導体層と、

を備えた半導体装置。

【請求項2】

基板と、

前記基板上に設けられた積層体であって、選択ゲートと前記選択ゲート上に設けられた絶縁層とを有する積層体と、

前記積層体を積層方向に貫通して形成されたホールの側壁に設けられた絶縁膜と、

前記ホール内における前記絶縁膜の側壁に設けられ、前記選択ゲートにおける前記絶縁層側の端部近傍で前記ホールを閉塞し、且つ前記ホールを閉塞する部分より下で空洞を囲むチャネルボディと、

前記チャネルボディが前記ホールを閉塞する部分より上の前記ホール内に、前記チャネルボディと同材料で連続して埋め込まれた半導体層と、

を備えた半導体装置。

【請求項3】

前記半導体層の不純物濃度は前記チャネルボディの不純物濃度よりも高い請求項2記載の半導体装置。

【請求項4】

基板上に、選択ゲートと、前記選択ゲート上に設けられた絶縁層とを有する積層体を形成する工程と、

前記積層体を積層方向に貫通するホールを形成する工程と、

前記ホールの側壁に絶縁膜を形成する工程と、

前記選択ゲートにおける前記絶縁層側の端部近傍で前記ホールを閉塞し、且つ前記ホールを閉塞する部分より下で空洞を囲むチャネルボディを、前記絶縁膜の側壁に形成する工程と、

前記チャネルボディを形成する処理室と同じ処理室内で、前記チャネルボディの形成に続けて、前記チャネルボディと同じ材料であって不純物を含む半導体層を、前記チャネルボディが前記ホールを閉塞する部分よりも上の前記ホール内における前記チャネルボディの内側に埋め込む工程と、

前記半導体層に含まれる前記不純物を、前記チャネルボディに拡散させる熱処理をする工程と、

を備えた半導体装置の製造方法。

【請求項5】

前記ホールの孔径が前記選択ゲートの前記絶縁層側の端部近傍で最も狭くなるように、前記ホールを形成する請求項4記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−105979(P2013−105979A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−250475(P2011−250475)

【出願日】平成23年11月16日(2011.11.16)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月16日(2011.11.16)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]