半導体装置及びその製造方法

【課題】封止材により封止された半導体装置において、リードに電気的に接続されて固着された電子デバイスと、該電子デバイスに電気的に接続される必要のないリードとのショートの回避を図る。

【解決手段】アイランド11に導電性ペースト15を介して半導体チップ20が固着されている。このアイランド11に向かって複数のリード12,12A,12Bが延びている。電子デバイス30は、該電子デバイス30に電気的に接続される必要の無いリード12Aの両側に並列するリード12の各表面上で、該表面上に形成された複数の導電突起体14によって支持され、導電性ペースト15を介して固着されている。これにより、電子デバイス30と、電子デバイス30に接続される必要の無いリード12Aの表面との間には、それらのショートを回避するのに十分な離間距離D1が確保される。

【解決手段】アイランド11に導電性ペースト15を介して半導体チップ20が固着されている。このアイランド11に向かって複数のリード12,12A,12Bが延びている。電子デバイス30は、該電子デバイス30に電気的に接続される必要の無いリード12Aの両側に並列するリード12の各表面上で、該表面上に形成された複数の導電突起体14によって支持され、導電性ペースト15を介して固着されている。これにより、電子デバイス30と、電子デバイス30に接続される必要の無いリード12Aの表面との間には、それらのショートを回避するのに十分な離間距離D1が確保される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、半導体チップと電子デバイスが封止材により封止されてなる半導体装置及びその製造方法に関する。

【背景技術】

【0002】

従来、IC(Integrated Circuit)などの半導体チップをエポキシ樹脂等の封止材で封止した半導体装置が開発されている。この半導体装置においては、半導体チップは、封止材により封止される前に、外部接続媒体であるリードフレームのアイランドに載置され、リードフレームのリードと接続される。

【0003】

図7は、樹脂封止された半導体装置の構造の一例を簡略して示す平面図であり、リードフレームのアイランドの周辺を図示したものである。図8(A)及び図8(B)は、図7のZ−Z線に対応した断面図である。

【0004】

図7に示すように、IC等の半導体チップ120は、その表面にパッド電極121を有している。半導体チップ120は、導電性ペースト115(例えば銀粒子を含む銀ペースト)を介して、アイランド111(接地電位や電源電位の供給を受ける)上に固着(即ちダイボンド)されている。なお、導電性ペースト115には、導電性粒子(例えば銀粒子)と、導電性ペースト115に若干の厚さを与えるためのフィラー粒子(例えばシリカ粒子)が含まれている。

【0005】

半導体チップ120の表面のパッド電極121とリードフレームのリード112は、ボンディングワイヤ113(例えば金を含む材料からなる金属細線)を介して電気的に接続(即ちワイヤボンディング)されている。

【0006】

さらに、この半導体装置には、図7及び図8(A)に示すようにリード112上に電子デバイス130が導電性ペースト115を介して電気的に接続され、固着される場合がある。この電子デバイス130は、例えばコンデンサや抵抗のような受動素子とすることができる。図8(A)では、一例として、電子デバイス130の両端部が導電性ペースト115を介して2つのリード112(例えば信号線として用いられる)と接続して固着され、それらのリード112の間には、電子デバイス130と離間して、電気的に接続される必要の無い他のリード112Aが存在する場合を示している。接続される必要の無いリード112Aと電子デバイス130の間に、導電性ペースト115は配置されない。

【0007】

上述したアイランド111上の半導体チップ120とリード112上の電子デバイス130は、アイランド111上からリード112,112A,112Bの一部上までを覆う封止材(例えば樹脂パッケージ)116によって封止される。

【0008】

アイランド上の半導体チップが封止材により封止されてなる半導体装置については、例えば特許文献1、2に開示されている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2004−228167号公報

【特許文献2】特開2005−26415号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、図8(A)に示すように、リード112と電子デバイス130の固着を介在する導電性ペースト115は、例えば5μm程度の厚さを目標に形成されるが、それに含まれるフィラー粒子(導電性ペースト115に厚さを与えるための粒子)の粒径のばらつきや、フィラー粒子の分布のばらつきによって、一様な厚さに形成することは極めて困難であった。これにより、特にリード112上の導電性ペースト115の厚さが所望の厚さよりも小さくなることが多く生じていた。

【0011】

この場合、導電性ペースト115の厚さに応じて、電子デバイス130と、電気的に接続される必要の無いリード112Aとの離間距離D3が小さくなり、そのリード112Aと電子デバイス130が近接してショートするおそれがあった。

【0012】

そこで本発明は、封止材により封止された半導体装置において、リードに電気的に接続されて固着された電子デバイスと、該電子デバイスに電気的に接続される必要のないリードとのショートの回避を図る。

【課題を解決するための手段】

【0013】

本発明の半導体装置は、アイランドと、前記アイランドに向かって並列して延びる第1及び第2のリードと、前記第1及び第2のリードの間で前記アイランドに向かって延びる第3のリードと、前記第1及び第2のリードの各表面上に配置された複数の第1の導電突起体と、両端部が前記複数の第1の導電突起体と重畳するように、前記第1、第2、及び第3のリードに跨って配置され、第1の導電性ペーストを介して前記第1及び第2のリードの各表面上に固着された電子デバイスと、表面に複数のパッド電極を有し、第2の導電性ペーストを介して前記アイランドの表面上に固着された半導体チップと、前記第1乃至第3のリードのそれぞれと前記パッド電極を接続するボンディングワイヤと、前記電子デバイス、前記半導体チップ、及び前記ボンディングワイヤを覆って封止する封止材と、を備え、前記電子デバイスは、厚さ方向で前記第3のリードの表面と離間するように、前記第1及び第2のリードの各表面上で前記複数の第1の導電突起体によって支持されることを特徴とする。

【0014】

また、本発明の半導体装置は、上記構成に加えて、前記アイランドの表面上に配置された複数の第2の導電突起体を備え、前記半導体チップは、その裏面が前記複数の第2の導電突起体と対向して直接接するように、前記第2の導電性ペーストを介して前記アイランドの表面上に固着され、前記半導体チップの周端部の少なくとも一部は、前記アイランドの周端部を越えて延在し、前記複数の第2の導電突起体は、前記半導体チップを前記アイランドの表面に対して平行に離間して支持する高さを有することを特徴とする。

【0015】

また、本発明の半導体装置の製造方法は、アイランド、前記アイランドに向かって並列して延びる第1及び第2のリード、及び前記第1及び第2のリードの間で前記アイランドに向かって延びる第3のリードが外枠に繋がれたリードフレームと、表面に複数のパッド電極を有した半導体チップと、電子デバイスと、を準備し、前記第1及び第2のリードの各表面上に複数の導電突起体を形成する工程と、前記導電突起体の形成工程の後、前記第1及び第2のリードの各表面上、及び前記アイランドの表面上に導電性ペーストを塗布する工程と、前記導電性ペーストの塗布工程の後、前記電子デバイスを、前記第1、第2、及び第3のリードに跨るように配置し、その両端部が前記複数の導電突起体と重畳して直接接するように、前記第1及び第2のリードの各表面上に圧着し、前記導電性ペーストを介して固着すると共に、前記半導体チップを、前記アイランドの表面上に圧着し、前記導電性ペーストを介して固着する工程と、ワイヤボンダーによって形成される複数のボンディングワイヤを介して、前記第1乃至第3のリードのそれぞれと前記パッド電極を接続する工程と、前記電子デバイス、前記半導体チップ、及び前記ボンディングワイヤを封止材で覆って封止する工程と、前記アイランド、及び前記第1乃至第3のリードを、前記外枠から切り離す工程と、を備え、前記電子デバイスは、厚さ方向で前記第3のリードと離間するように、前記第1及び第2のリードの各表面で前記複数の導電突起体によって支持されることを特徴とする。

【発明の効果】

【0016】

本発明によれば、封止材により封止された半導体装置において、リードに接続されて固着された電子デバイスと、該電子デバイスに電気的に接続される必要のないリードとのショートを回避できる。

【図面の簡単な説明】

【0017】

【図1】本発明の第1の実施形態による半導体装置を説明する平面図である。

【図2】本発明の第1の実施形態による半導体装置を説明する断面図である。

【図3】導電突起体の断面形状を説明する図である。

【図4】導電突起体の断面形状を説明する図である。

【図5】本発明の第2の実施形態による半導体装置を説明する平面図である。

【図6】本発明の第2の実施形態による半導体装置を説明する断面図ある。

【図7】従来例による半導体装置を示す平面図である。

【図8】従来例による半導体装置を示す断面図である。

【発明を実施するための形態】

【0018】

[第1の実施形態]

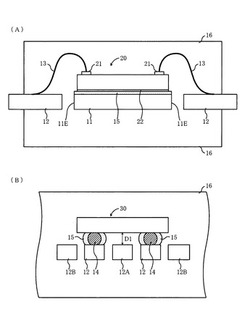

本発明の第1の実施形態による半導体装置について、図面を参照して説明する。図1は、この半導体装置の平面図であり、リードフレームの外枠(不図示)から、アイランド11及びリード12,12A,12Bが切り離された状態を図示している。なお、図1は、主要な構成要素のみを図示し、リードフレームの外枠とアイランド11を接続する吊りリード(半導体装置の完成後は外枠から切り離されている)や、導電性ペースト15等の図示は省略されている。図2(A)は、図1のX−X線における断面図であり、図2(B)は、図1のY−Y線における断面図である。

【0019】

図1に示すように、アイランド11の周囲では、複数のリード12,12A,12Bがアイランド11に向かって並列して延在している。なお、アイランド11とリード12,12A,12Bは、例えば銅を含む金属からなる。アイランド11は、例えば吊りリード(不図示)を端子として用いることで、その端子から接地電位または電源電位の供給を受ける。

【0020】

図1及び図2(A)に示すように、アイランド11の表面上には、IC等の半導体チップ20が導電性ペースト15(例えば導電性粒子として銀粒子を含む)を介して固着(即ちダイボンド)されている。導電性ペースト15は、導電性ペースト15に厚さを与えるためのフィラー粒子(例えばシリカ粒子)を含んでもよい。

【0021】

半導体チップ20は、その内部に、例えばトランジスタ等を含む集積回路を有し、周端部20Eに沿った表面に複数のパッド電極21を有している。各パッド電極21は、ボンディングワイヤ13(例えば金を含む金属材料からなる金属細線)を介して、リード12,12A,12Bと接続される。

【0022】

他方、半導体チップ20の裏面には、裏面電極22(例えば銅を含む金属層からなる)が配置されている。半導体チップ20、あるいはその集積回路は、裏面電極22、導電突起体14、導電性ペースト15、及びアイランド11を介することで、接地電位または電源電位の供給を受ける。

【0023】

また、図1および図2(B)に示すように、複数のリード上に跨って、電子デバイス30が配置されている。本実施形態では、一例として、電子デバイス30は、例えば受動素子(コンデンサや抵抗)であり、3つのリード12,12A,12(例えば半導体チップの20の信号線として用いられる)に跨って配置される場合について説明する。3つのリード12,12A,12のうち両側の2つのリード12は、電子デバイス30と電気的に接続される必要のあるリードとし、これら2つのリード12の間に延びるリード12Aは、電子デバイス30と電気的に接続される必要はないものとする。

【0024】

3つのリード12,12A,12のうち両側の2つのリード12の各表面の一部上(電子デバイス30が配置される領域上)には、複数の導電突起体14が配置されている。複数の導電突起体14は、互いに同一あるいは略同一の高さを有していることが好ましい。また、複数の導電突起体14は、それらの形状についても同一あるいは略同一であることが好ましい。1つのリード12の表面上には、2個以上の導電突起体14が配置される。そして、電子デバイス30は、その両端部(例えば電極部)の裏面が2つのリード12の各表面上の複数の導電突起体14と重畳して直接接するように、第1の導電性ペーストを介して2つのリード12の各表面上に固着される。

【0025】

2つのリード12上に固着された電子デバイス30、アイランド11上に固着された半導体チップ20、ボンディングワイヤ13、及びリード12,12A,12Bの一部は、絶縁性の封止材16(例えば樹脂パッケージ)によって封止されている。なお、図1、図2(A)及び図2(B)では、一例として、封止材16がアイランド11及びリード12,12A,12Bの両面を挟むように封止している場合を示したが、これに限定されず、封止材16は、アイランド11及びリード12,12A,12Bの表面と同一平面よりも上方(半導体チップ20に向かう方向)の領域のみを覆ってもよい。または、リード12,12A,12Bと吊りリード(不図示)の裏面及び側端部が、封止材16の裏面及び側面に対して同一面あるいは略同一面で露出するように、封止材16を形成してもよい。

【0026】

上記構成によれば、電子デバイス30は、複数の導電突起体14によって支持されることで、リード12,12Aの各表面から一定の離間距離D1で離間する。この離間距離D1は、導電突起体14の高さに応じて決定され、変動しないことから、導電性ペースト15の厚さのばらつきに影響されることはない。この離間距離D1によって、電子デバイス30と、電子デバイス30に接続される必要の無い中央のリード12Aの表面との間には、それらのショートを回避するのに十分な間隔が確保される。つまり、導電突起体14を介在させない図8(A)の従来例のように、導電性ペースト115が所望の厚さよりも小さくなり、電子デバイス130に接続される必要の無いリード112Aと電子デバイス130が近接してショートすることを回避できる。

【0027】

さらに、複数の導電突起体14が、互いに同一あるいは略同一の高さを有して形成されていれば、電子デバイス30は、複数の導電突起体よって、リード12,12Aの各表面に対して平行あるいは略平行に支持され、固着される。

【0028】

これに対して図8(A)の従来例では、導電性ペースト115の厚さのばらつきにより、図8(B)に示すように電子デバイス130の両端部に接続される2つのリード112のうち、一方のリード112上の導電性ペースト115の厚さが所望の厚さよりも小さくなる場合がある。この場合、電子デバイス130は、複数のリード112の各表面(あるいはアイランド111の表面)に対して平行あるいは略平行に載置されず、傾いた状態で固着される。この傾きの程度によっては、電子デバイス130の端部が、その周囲に延びるリード112B(電気的に接続される必要のないリード)と近接してショートしてしまうおそれがある。

【0029】

そこで上記のように電子デバイス30を同一あるいは略同一の高さを有した導電突起体14によって支持し、リード12,12Aの各表面に対して平行あるいは略平行に固着すれば、電子デバイス30の端部と、その周囲に延びるリード12B(電気的に接続される必要のないリード)との間においても、それらのショートを回避するのに十分な離間距離が確保されることになる。

【0030】

また、上述したリード12A,12Bと電子デバイス30のショートの回避によれば、汎用性のある通常のリードフレーム(リード12A,12Bの薄さを調整するエッチング加工等が施されていないもの)を、そのままの状態(アイランド11とリード12,12A,12Bが同一の厚さのままの状態)で用いて実現できるという利点もある。

【0031】

また、電子デバイス30とリード12は、導電性ペースト15に加えて、複数の導電突起体14を介して電気的に接続されるので、導電突起体14を配置しない場合に比して、電子デバイス30とリード12の間の導電性を向上させることができ、接続抵抗を低く抑えることができる。

【0032】

さらに、封止された半導体装置の使用時等においてジュール熱が生じた場合、そのジュール熱は、導電突起体14を通して効率よくリード12に伝わって放出されるため、ジュール熱の影響を極力小さくすることができる。特に、電子デバイス30が発熱しやすい素子(例えば抵抗)である場合、上述した熱放出効果が顕著となる。

【0033】

以下に、上述した導電突起体14の詳細について説明する。導電突起体14の形状は、図3(A)の断面図の示すように、その下端部14A(リード12の表面と接する側の端)は平坦面となっている。さらに、導電突起体14の上端部14Bも、リード12の表面に対して平行あるいは略平行な平坦面を有することが好ましい。この上端部14Bの平坦面が電子デバイス30の裏面側と接することで、電子デバイス30は、より確実に、リード12上で安定的に支持されると共に、リード12の表面に対する平行性が高められる。

【0034】

また、この構成によれば、導電突起体14と電子デバイス30の接触面積、及び導電突起体14とリード12の接触面積が広がることから、電子デバイス30に生じたジュール熱を、導電突起体14を通して、より効率よくリード12に放出することができる。

【0035】

導電突起体14は、好ましくは、ボンディングワイヤ13の形成装置、つまりワイヤボンダーを用いて形成される。即ち、導電突起体14は、基本的には、ワイヤボンダーが溶融した金属材料を球状体としてリード12の表面上に点状に溶着し、所定の圧力で押し付けることで形成される。

【0036】

導電突起体14の金属材料は、ワイヤボンダーで使用できるものであれば特に限定されないが、良好な導電性と熱伝導性を得るためには、例えば金を含むもの、あるいは銅を含むものであることが好ましい。製造プロセスの簡略化が要求される場合、導電突起体14の金属材料は、ボンディングワイヤ13と同一の金属材料を用いることができる。

【0037】

導電突起体14の上端部14Bの平坦面は、溶融した金属材料を球状体としてリード12の表面上に点状に溶着して所定の圧力で押し付けた後に、ワイヤボンダーの金属材料の吐出口をリード12の表面と平行な方向に高速でスライドさせるという、ワイヤボンダーの動作モードによって形成することができる。

【0038】

各導電突起体14のリード12からの高さH1は、ワイヤボンダーが金属材料の吐出量、押し付け時の圧力、吐出口の動作等のパラメータを制御することで、例えば約20μm〜150μmの範囲で設定することができる。この導電突起体14の高さH1が、リード12,12A,12Bと電子デバイス30の間の一定の離間距離D1を決定する。

【0039】

なお、各導電突起体14のリード12からの高さH1は、理想的には全て同一であることが好ましいが、実際のプロセスで形成される各導電突起体14の高さH1は、加工精度による僅かな誤差を含む。この誤差は、ワイヤボンダーを形成装置として用いることによって極めて小さくできる。例えば高さH1が約20μmで設定された場合の誤差は約2μm以下、高さH1が約150μmで設定された場合の誤差は約15μm以下とすることができる。つまり、高さH1の誤差を設定値の約10%以下に抑えることができる。この程度の高さH1の誤差は、本発明が奏する効果について影響を与えるものではない。

【0040】

下端部14Aの径R1と上端部14Bの径R2は、ワイヤボンダーが金属材料の吐出量、押し付け時の圧力、吐出口の動作等のパラメータを制御することで、例えば約15μm〜100μmの範囲で設定することができる。このとき、下端部14Aの径R1を、上端部14Bの径R2よりも大きく設定することで、下端部14Aとリード12の密着性を高めることができ、また、その下端部14Aの高い密着性により、リード12の表面に対する平行性を劣化させることなく、上端部14Bの平坦面を形成しやすくなる。

【0041】

さらに上記構成の変形例として、導電突起体14は、図3(B)に示すように、ワイヤボンダーによって2段に積層して形成することもできる。このような導電突起体14の積層構造によれば、その高さH1を大きくすることができるため、リード12と電子デバイス30の離間距離D1も大きくすることができる。

【0042】

なお、導電突起体14は、全て同一あるいは略同一の高さH1を有していれば、上記以外の形状で形成されてもよい。例えば、図4(A)に示すように上端部14Bが上方に突出し、その先端が尖っていてもよく、また、図4(B)に示すように上端部14Bが上方に突出し、その先端が平坦面となるものであってもよい。これらの形状は、ワイヤボンダーの動作モードに応じて適宜選択することができる。

【0043】

以下に、上述した半導体装置の製造方法について説明する。最初の状態では、アイランド11が、吊りリード(不図示)を介してリードフレームの外枠に繋がれ、複数のリード12,12A,12Bも外枠に繋がれているものとする。この状態で、上述したように、好ましくはワイヤボンダーにより、電子デバイス30が跨って配置される領域のリード12の各表面上に複数の導電突起体14を形成する。

【0044】

この導電突起体14の形成工程の後、電子デバイス30が跨って配置される領域のリード12の各表面上と、アイランド11の表面上に、導電性ペースト15を塗布する。導電性ペースト15は、例えばマルチニードルによって、点状に塗布されてもよいし、ライン状に塗布されてもよい。

【0045】

その後、電子デバイス30を、所定のリード12,12A,12に跨るように配置し、電子デバイス30の両端部の裏面が複数の導電突起体14と重畳して直接接するように、リード12の各表面上に圧着し、導電性ペースト15を介して固着する。これと同時に、あるいは前後して、半導体チップ20をアイランド11の表面上に圧着し、導電性ペースト15を介して固着する。

【0046】

次に、ワイヤボンダーによって、各リード12,12A,12Bのそれぞれと各パッド電極21を接続する複数のボンディングワイヤを形成し、さらに、リード12上に固着された電子デバイス30、アイランド11上に固着された半導体チップ20、複数のボンディングワイヤ13、及び複数のリード12,12A,12Bの一部を、封止材16で覆って封止する。

【0047】

その後、吊りリード(不図示)とリード12,12A,12Bを切断して、リードフレームの外枠からアイランド11及びリード12,12A,12Bを切り離す。封止材16の外側に延びるリード12,12A,12Bの一部は、外部接続用の端子として適した形状に折り曲げられる(不図示)。

【0048】

[第2の実施形態]

本発明の第2の実施形態による半導体装置について、図面を参照して説明する。図5は、この半導体装置の平面図であり、図6は、図5のX’−X’線における断面図である。この半導体装置では、図5のY−Y線における断面図、つまり、導電突起体14に支持されてリード12の表面上に固着される電子デバイス30の断面図については、図2(B)と同様である。図5及び図6では、第1の実施形態に示したものと同一の構成要素については同一の参照番号を付して、その説明を省略する。

【0049】

図5及び図6に示すように、電子デバイス30が固着されるリード12の表面上だけではなく、アイランド11の表面上にも、互いに同一あるいは略同一の高さを有した複数の導電突起体14が形成されている。アイランド11の表面上の複数の導電突起体14は、それらの形状についても同一あるいは略同一であることが好ましい。アイランド11の表面上の導電突起体14は、第1の実施形態におけるリード12の表面上の導電突起体14と同一の材料を用いて、同一の工程で形成することができる。このアイランド11上で、IC等の半導体チップ40が、導電突起体14に支持されると共に、導電性ペースト15(例えば導電性粒子として銀粒子を含む)を介して固着(即ちダイボンド)されている。本実施形態では、導電性ペースト15は、導電性ペースト15に厚さを与えるためのフィラー粒子(例えばシリカ粒子)を含む必要はない。

【0050】

この半導体チップ40は、その周端部40Eの少なくとも一部がアイランド11の周端部11Eを越えてリード12側に向かって広がっている。本実施形態では、一例として、半導体チップ40は平面的に矩形状であるものとし、その周端部40Eの全て、つまり全ての辺がアイランド11よりも大きくなるようなサイズを有する場合について説明する。

【0051】

半導体チップ40は、その内部に、例えばトランジスタ等を含む集積回路を有し、周端部40Eに沿った表面に複数のパッド電極41を有している。各パッド電極41は、ボンディングワイヤ13(例えば金を含む金属材料からなる金属細線)を介して、リード12,12A,12Bと接続される。

【0052】

また、半導体チップ40の裏面は平坦か略平坦であるものとし、その裏面で裏面電極42が平坦か略平坦に形成されているものとする。裏面電極42は、半導体チップ40の裏面の全面あるいは略全面に形成されることが好ましい。この裏面電極42の表面(下面)と、導電突起体14の上端は、直接接している。

【0053】

複数の導電突起体14の少なくとも一部は、半導体チップ40とアイランド11が重畳する領域の周端部に沿って、あるいはその周端部の近傍に沿って配置されることが好ましい。図5及び図6では、半導体チップ40とアイランド11が重畳する領域の四隅に導電突起体14が配置され、さらに、半導体チップ40とアイランド11が重畳する領域の中央にも、導電突起体14が配置された場合を示す。アイランド11の表面に配置される導電突起体14の個数は、3個以上である。

【0054】

なお、アイランド11の表面上に配置される複数の導電突起体14の高さ、下端部14Aの径、上端部14Bの径は、必要に応じて、リード12の表面上に配置される複数の導電突起体14の高さH1、下端部14Aの径R1、上端部14Bの径R2とは異なる値に設定されてもよい。

【0055】

上記構成によれば、半導体チップ40は、同一あるいは略同一の高さを有した複数の導電突起体14によって支持されることで、アイランド11の表面に対して平行あるいは略平行に、即ちアイランド11の表面と一定の離間距離D2を保って固着される。そして、離間距離D2に応じて、半導体チップ40とリード12の端との間隔も大きく確保することができる。また、導電突起体14を介在させない場合と比較すると、導電性ペースト15の厚さが均一にならずに半導体チップ40がアイランド11上で傾いて、半導体チップ40とリード12の端との間隔が小さくなるおそれもない。

【0056】

従って、半導体チップ40の裏面側の周端部40E(半導体基板または裏面電極42)とリード12が近接あるいは接触して電気的にショートすることを回避することができる。

【0057】

また、このような半導体チップ40とリード12のショートの回避によれば、汎用性のある通常のリードフレーム(リード12,12A,12Bの薄さを調整するエッチング加工等が施されていないもの)を、そのままの状態(アイランド11とリード12,12A,12Bが同一の厚さのままの状態)で用いて実現できるという利点もある。

【0058】

また、裏面電極42とアイランド11は、導電性ペースト15に加えて、複数の導電突起体14を介して接続されるので、導電突起体14を配置しない場合に比して、裏面電極42とアイランド11の間の導電性を向上させることができ、接続抵抗を低く抑えることができる。

【0059】

さらに、封止された半導体装置の使用時等においてジュール熱が生じた場合、半導体チップ40の基板(例えばシリコン基板)とアイランド11(例えば銅)は、それぞれの異なる熱膨張係数に応じて熱膨張し、その熱膨張の差異によって機械的応力が生じても、半導体チップ40は、複数の導電突起体14に支持されアイランド11に対して平行あるいは略平行に固着されているため、上記機械的応力は、局所的に集中することなく、均等に分散しやすくなる。つまり、半導体装置において上記機械的応力を起因とするクラック等の損傷を防止することができる。

【0060】

また、半導体チップ40に生じたジュール熱は、導電突起体14を通して効率よくアイランド11に伝わって放出されるため、ジュール熱の影響を極力小さくすることができる。特に、半導体チップ40の発熱しやすい領域、例えばトランジスタの形成領域と重畳するアイランド11上の領域に、複数の導電突起体14のうちの少なくとも一部を配置すれば、上述した熱放出効果をより確実に高めることができる。

【0061】

なお、本発明は上記いずれの実施形態にも限定されず、要旨を逸脱しない範囲で変更が可能なことは言うまでもない。例えば、各実施形態では、複数の導電突起体14が配置されて電子デバイス30と電気的に接続された2つのリード12の間に、電子デバイス30と電気的に接続される必要のないリード12Aが1つだけ配置された例を示したが、本発明は、これらのリード12,12A,12の配置に限定されない。つまり、電子デバイス30と電気的に接続された2つのリード12の間には、電子デバイス30と電気的に接続される必要のないリード12Aが、2つ以上配置されてもよい。また、複数の導電突起体14が配置されて電子デバイス30と電気的に接続されるリード12は、2つに限定されず、3つ以上配置されてもよい。

【0062】

また、各実施形態における電子デバイス30は受動素子であるものとしたが、これ以外の素子、例えば能動素子や集積回路であってもよい。

【0063】

また、各実施形態における半導体チップ20,40の裏面には、裏面電極22,42が形成されるものとしたが、この裏面電極22,42は必ずしも形成されなくてもよい。この場合、第2の実施形態では、導電突起体14と直接接する半導体チップ40の裏面、あるいは他の構成物は平坦面を有していればよい。

【0064】

また、各実施形態では、導電突起体14は、ワイヤボンダーを用いて形成されるものとしたが、これ以外の方法で形成されてもよい。

【符号の説明】

【0065】

11 アイランド 12 リード

13 ボンディングワイヤ 14 導電突起体

15 導電性ペースト 16 封止材

20,40 半導体チップ 21,41 パッド電極

22,42 裏面電極 30 電子デバイス

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、半導体チップと電子デバイスが封止材により封止されてなる半導体装置及びその製造方法に関する。

【背景技術】

【0002】

従来、IC(Integrated Circuit)などの半導体チップをエポキシ樹脂等の封止材で封止した半導体装置が開発されている。この半導体装置においては、半導体チップは、封止材により封止される前に、外部接続媒体であるリードフレームのアイランドに載置され、リードフレームのリードと接続される。

【0003】

図7は、樹脂封止された半導体装置の構造の一例を簡略して示す平面図であり、リードフレームのアイランドの周辺を図示したものである。図8(A)及び図8(B)は、図7のZ−Z線に対応した断面図である。

【0004】

図7に示すように、IC等の半導体チップ120は、その表面にパッド電極121を有している。半導体チップ120は、導電性ペースト115(例えば銀粒子を含む銀ペースト)を介して、アイランド111(接地電位や電源電位の供給を受ける)上に固着(即ちダイボンド)されている。なお、導電性ペースト115には、導電性粒子(例えば銀粒子)と、導電性ペースト115に若干の厚さを与えるためのフィラー粒子(例えばシリカ粒子)が含まれている。

【0005】

半導体チップ120の表面のパッド電極121とリードフレームのリード112は、ボンディングワイヤ113(例えば金を含む材料からなる金属細線)を介して電気的に接続(即ちワイヤボンディング)されている。

【0006】

さらに、この半導体装置には、図7及び図8(A)に示すようにリード112上に電子デバイス130が導電性ペースト115を介して電気的に接続され、固着される場合がある。この電子デバイス130は、例えばコンデンサや抵抗のような受動素子とすることができる。図8(A)では、一例として、電子デバイス130の両端部が導電性ペースト115を介して2つのリード112(例えば信号線として用いられる)と接続して固着され、それらのリード112の間には、電子デバイス130と離間して、電気的に接続される必要の無い他のリード112Aが存在する場合を示している。接続される必要の無いリード112Aと電子デバイス130の間に、導電性ペースト115は配置されない。

【0007】

上述したアイランド111上の半導体チップ120とリード112上の電子デバイス130は、アイランド111上からリード112,112A,112Bの一部上までを覆う封止材(例えば樹脂パッケージ)116によって封止される。

【0008】

アイランド上の半導体チップが封止材により封止されてなる半導体装置については、例えば特許文献1、2に開示されている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2004−228167号公報

【特許文献2】特開2005−26415号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、図8(A)に示すように、リード112と電子デバイス130の固着を介在する導電性ペースト115は、例えば5μm程度の厚さを目標に形成されるが、それに含まれるフィラー粒子(導電性ペースト115に厚さを与えるための粒子)の粒径のばらつきや、フィラー粒子の分布のばらつきによって、一様な厚さに形成することは極めて困難であった。これにより、特にリード112上の導電性ペースト115の厚さが所望の厚さよりも小さくなることが多く生じていた。

【0011】

この場合、導電性ペースト115の厚さに応じて、電子デバイス130と、電気的に接続される必要の無いリード112Aとの離間距離D3が小さくなり、そのリード112Aと電子デバイス130が近接してショートするおそれがあった。

【0012】

そこで本発明は、封止材により封止された半導体装置において、リードに電気的に接続されて固着された電子デバイスと、該電子デバイスに電気的に接続される必要のないリードとのショートの回避を図る。

【課題を解決するための手段】

【0013】

本発明の半導体装置は、アイランドと、前記アイランドに向かって並列して延びる第1及び第2のリードと、前記第1及び第2のリードの間で前記アイランドに向かって延びる第3のリードと、前記第1及び第2のリードの各表面上に配置された複数の第1の導電突起体と、両端部が前記複数の第1の導電突起体と重畳するように、前記第1、第2、及び第3のリードに跨って配置され、第1の導電性ペーストを介して前記第1及び第2のリードの各表面上に固着された電子デバイスと、表面に複数のパッド電極を有し、第2の導電性ペーストを介して前記アイランドの表面上に固着された半導体チップと、前記第1乃至第3のリードのそれぞれと前記パッド電極を接続するボンディングワイヤと、前記電子デバイス、前記半導体チップ、及び前記ボンディングワイヤを覆って封止する封止材と、を備え、前記電子デバイスは、厚さ方向で前記第3のリードの表面と離間するように、前記第1及び第2のリードの各表面上で前記複数の第1の導電突起体によって支持されることを特徴とする。

【0014】

また、本発明の半導体装置は、上記構成に加えて、前記アイランドの表面上に配置された複数の第2の導電突起体を備え、前記半導体チップは、その裏面が前記複数の第2の導電突起体と対向して直接接するように、前記第2の導電性ペーストを介して前記アイランドの表面上に固着され、前記半導体チップの周端部の少なくとも一部は、前記アイランドの周端部を越えて延在し、前記複数の第2の導電突起体は、前記半導体チップを前記アイランドの表面に対して平行に離間して支持する高さを有することを特徴とする。

【0015】

また、本発明の半導体装置の製造方法は、アイランド、前記アイランドに向かって並列して延びる第1及び第2のリード、及び前記第1及び第2のリードの間で前記アイランドに向かって延びる第3のリードが外枠に繋がれたリードフレームと、表面に複数のパッド電極を有した半導体チップと、電子デバイスと、を準備し、前記第1及び第2のリードの各表面上に複数の導電突起体を形成する工程と、前記導電突起体の形成工程の後、前記第1及び第2のリードの各表面上、及び前記アイランドの表面上に導電性ペーストを塗布する工程と、前記導電性ペーストの塗布工程の後、前記電子デバイスを、前記第1、第2、及び第3のリードに跨るように配置し、その両端部が前記複数の導電突起体と重畳して直接接するように、前記第1及び第2のリードの各表面上に圧着し、前記導電性ペーストを介して固着すると共に、前記半導体チップを、前記アイランドの表面上に圧着し、前記導電性ペーストを介して固着する工程と、ワイヤボンダーによって形成される複数のボンディングワイヤを介して、前記第1乃至第3のリードのそれぞれと前記パッド電極を接続する工程と、前記電子デバイス、前記半導体チップ、及び前記ボンディングワイヤを封止材で覆って封止する工程と、前記アイランド、及び前記第1乃至第3のリードを、前記外枠から切り離す工程と、を備え、前記電子デバイスは、厚さ方向で前記第3のリードと離間するように、前記第1及び第2のリードの各表面で前記複数の導電突起体によって支持されることを特徴とする。

【発明の効果】

【0016】

本発明によれば、封止材により封止された半導体装置において、リードに接続されて固着された電子デバイスと、該電子デバイスに電気的に接続される必要のないリードとのショートを回避できる。

【図面の簡単な説明】

【0017】

【図1】本発明の第1の実施形態による半導体装置を説明する平面図である。

【図2】本発明の第1の実施形態による半導体装置を説明する断面図である。

【図3】導電突起体の断面形状を説明する図である。

【図4】導電突起体の断面形状を説明する図である。

【図5】本発明の第2の実施形態による半導体装置を説明する平面図である。

【図6】本発明の第2の実施形態による半導体装置を説明する断面図ある。

【図7】従来例による半導体装置を示す平面図である。

【図8】従来例による半導体装置を示す断面図である。

【発明を実施するための形態】

【0018】

[第1の実施形態]

本発明の第1の実施形態による半導体装置について、図面を参照して説明する。図1は、この半導体装置の平面図であり、リードフレームの外枠(不図示)から、アイランド11及びリード12,12A,12Bが切り離された状態を図示している。なお、図1は、主要な構成要素のみを図示し、リードフレームの外枠とアイランド11を接続する吊りリード(半導体装置の完成後は外枠から切り離されている)や、導電性ペースト15等の図示は省略されている。図2(A)は、図1のX−X線における断面図であり、図2(B)は、図1のY−Y線における断面図である。

【0019】

図1に示すように、アイランド11の周囲では、複数のリード12,12A,12Bがアイランド11に向かって並列して延在している。なお、アイランド11とリード12,12A,12Bは、例えば銅を含む金属からなる。アイランド11は、例えば吊りリード(不図示)を端子として用いることで、その端子から接地電位または電源電位の供給を受ける。

【0020】

図1及び図2(A)に示すように、アイランド11の表面上には、IC等の半導体チップ20が導電性ペースト15(例えば導電性粒子として銀粒子を含む)を介して固着(即ちダイボンド)されている。導電性ペースト15は、導電性ペースト15に厚さを与えるためのフィラー粒子(例えばシリカ粒子)を含んでもよい。

【0021】

半導体チップ20は、その内部に、例えばトランジスタ等を含む集積回路を有し、周端部20Eに沿った表面に複数のパッド電極21を有している。各パッド電極21は、ボンディングワイヤ13(例えば金を含む金属材料からなる金属細線)を介して、リード12,12A,12Bと接続される。

【0022】

他方、半導体チップ20の裏面には、裏面電極22(例えば銅を含む金属層からなる)が配置されている。半導体チップ20、あるいはその集積回路は、裏面電極22、導電突起体14、導電性ペースト15、及びアイランド11を介することで、接地電位または電源電位の供給を受ける。

【0023】

また、図1および図2(B)に示すように、複数のリード上に跨って、電子デバイス30が配置されている。本実施形態では、一例として、電子デバイス30は、例えば受動素子(コンデンサや抵抗)であり、3つのリード12,12A,12(例えば半導体チップの20の信号線として用いられる)に跨って配置される場合について説明する。3つのリード12,12A,12のうち両側の2つのリード12は、電子デバイス30と電気的に接続される必要のあるリードとし、これら2つのリード12の間に延びるリード12Aは、電子デバイス30と電気的に接続される必要はないものとする。

【0024】

3つのリード12,12A,12のうち両側の2つのリード12の各表面の一部上(電子デバイス30が配置される領域上)には、複数の導電突起体14が配置されている。複数の導電突起体14は、互いに同一あるいは略同一の高さを有していることが好ましい。また、複数の導電突起体14は、それらの形状についても同一あるいは略同一であることが好ましい。1つのリード12の表面上には、2個以上の導電突起体14が配置される。そして、電子デバイス30は、その両端部(例えば電極部)の裏面が2つのリード12の各表面上の複数の導電突起体14と重畳して直接接するように、第1の導電性ペーストを介して2つのリード12の各表面上に固着される。

【0025】

2つのリード12上に固着された電子デバイス30、アイランド11上に固着された半導体チップ20、ボンディングワイヤ13、及びリード12,12A,12Bの一部は、絶縁性の封止材16(例えば樹脂パッケージ)によって封止されている。なお、図1、図2(A)及び図2(B)では、一例として、封止材16がアイランド11及びリード12,12A,12Bの両面を挟むように封止している場合を示したが、これに限定されず、封止材16は、アイランド11及びリード12,12A,12Bの表面と同一平面よりも上方(半導体チップ20に向かう方向)の領域のみを覆ってもよい。または、リード12,12A,12Bと吊りリード(不図示)の裏面及び側端部が、封止材16の裏面及び側面に対して同一面あるいは略同一面で露出するように、封止材16を形成してもよい。

【0026】

上記構成によれば、電子デバイス30は、複数の導電突起体14によって支持されることで、リード12,12Aの各表面から一定の離間距離D1で離間する。この離間距離D1は、導電突起体14の高さに応じて決定され、変動しないことから、導電性ペースト15の厚さのばらつきに影響されることはない。この離間距離D1によって、電子デバイス30と、電子デバイス30に接続される必要の無い中央のリード12Aの表面との間には、それらのショートを回避するのに十分な間隔が確保される。つまり、導電突起体14を介在させない図8(A)の従来例のように、導電性ペースト115が所望の厚さよりも小さくなり、電子デバイス130に接続される必要の無いリード112Aと電子デバイス130が近接してショートすることを回避できる。

【0027】

さらに、複数の導電突起体14が、互いに同一あるいは略同一の高さを有して形成されていれば、電子デバイス30は、複数の導電突起体よって、リード12,12Aの各表面に対して平行あるいは略平行に支持され、固着される。

【0028】

これに対して図8(A)の従来例では、導電性ペースト115の厚さのばらつきにより、図8(B)に示すように電子デバイス130の両端部に接続される2つのリード112のうち、一方のリード112上の導電性ペースト115の厚さが所望の厚さよりも小さくなる場合がある。この場合、電子デバイス130は、複数のリード112の各表面(あるいはアイランド111の表面)に対して平行あるいは略平行に載置されず、傾いた状態で固着される。この傾きの程度によっては、電子デバイス130の端部が、その周囲に延びるリード112B(電気的に接続される必要のないリード)と近接してショートしてしまうおそれがある。

【0029】

そこで上記のように電子デバイス30を同一あるいは略同一の高さを有した導電突起体14によって支持し、リード12,12Aの各表面に対して平行あるいは略平行に固着すれば、電子デバイス30の端部と、その周囲に延びるリード12B(電気的に接続される必要のないリード)との間においても、それらのショートを回避するのに十分な離間距離が確保されることになる。

【0030】

また、上述したリード12A,12Bと電子デバイス30のショートの回避によれば、汎用性のある通常のリードフレーム(リード12A,12Bの薄さを調整するエッチング加工等が施されていないもの)を、そのままの状態(アイランド11とリード12,12A,12Bが同一の厚さのままの状態)で用いて実現できるという利点もある。

【0031】

また、電子デバイス30とリード12は、導電性ペースト15に加えて、複数の導電突起体14を介して電気的に接続されるので、導電突起体14を配置しない場合に比して、電子デバイス30とリード12の間の導電性を向上させることができ、接続抵抗を低く抑えることができる。

【0032】

さらに、封止された半導体装置の使用時等においてジュール熱が生じた場合、そのジュール熱は、導電突起体14を通して効率よくリード12に伝わって放出されるため、ジュール熱の影響を極力小さくすることができる。特に、電子デバイス30が発熱しやすい素子(例えば抵抗)である場合、上述した熱放出効果が顕著となる。

【0033】

以下に、上述した導電突起体14の詳細について説明する。導電突起体14の形状は、図3(A)の断面図の示すように、その下端部14A(リード12の表面と接する側の端)は平坦面となっている。さらに、導電突起体14の上端部14Bも、リード12の表面に対して平行あるいは略平行な平坦面を有することが好ましい。この上端部14Bの平坦面が電子デバイス30の裏面側と接することで、電子デバイス30は、より確実に、リード12上で安定的に支持されると共に、リード12の表面に対する平行性が高められる。

【0034】

また、この構成によれば、導電突起体14と電子デバイス30の接触面積、及び導電突起体14とリード12の接触面積が広がることから、電子デバイス30に生じたジュール熱を、導電突起体14を通して、より効率よくリード12に放出することができる。

【0035】

導電突起体14は、好ましくは、ボンディングワイヤ13の形成装置、つまりワイヤボンダーを用いて形成される。即ち、導電突起体14は、基本的には、ワイヤボンダーが溶融した金属材料を球状体としてリード12の表面上に点状に溶着し、所定の圧力で押し付けることで形成される。

【0036】

導電突起体14の金属材料は、ワイヤボンダーで使用できるものであれば特に限定されないが、良好な導電性と熱伝導性を得るためには、例えば金を含むもの、あるいは銅を含むものであることが好ましい。製造プロセスの簡略化が要求される場合、導電突起体14の金属材料は、ボンディングワイヤ13と同一の金属材料を用いることができる。

【0037】

導電突起体14の上端部14Bの平坦面は、溶融した金属材料を球状体としてリード12の表面上に点状に溶着して所定の圧力で押し付けた後に、ワイヤボンダーの金属材料の吐出口をリード12の表面と平行な方向に高速でスライドさせるという、ワイヤボンダーの動作モードによって形成することができる。

【0038】

各導電突起体14のリード12からの高さH1は、ワイヤボンダーが金属材料の吐出量、押し付け時の圧力、吐出口の動作等のパラメータを制御することで、例えば約20μm〜150μmの範囲で設定することができる。この導電突起体14の高さH1が、リード12,12A,12Bと電子デバイス30の間の一定の離間距離D1を決定する。

【0039】

なお、各導電突起体14のリード12からの高さH1は、理想的には全て同一であることが好ましいが、実際のプロセスで形成される各導電突起体14の高さH1は、加工精度による僅かな誤差を含む。この誤差は、ワイヤボンダーを形成装置として用いることによって極めて小さくできる。例えば高さH1が約20μmで設定された場合の誤差は約2μm以下、高さH1が約150μmで設定された場合の誤差は約15μm以下とすることができる。つまり、高さH1の誤差を設定値の約10%以下に抑えることができる。この程度の高さH1の誤差は、本発明が奏する効果について影響を与えるものではない。

【0040】

下端部14Aの径R1と上端部14Bの径R2は、ワイヤボンダーが金属材料の吐出量、押し付け時の圧力、吐出口の動作等のパラメータを制御することで、例えば約15μm〜100μmの範囲で設定することができる。このとき、下端部14Aの径R1を、上端部14Bの径R2よりも大きく設定することで、下端部14Aとリード12の密着性を高めることができ、また、その下端部14Aの高い密着性により、リード12の表面に対する平行性を劣化させることなく、上端部14Bの平坦面を形成しやすくなる。

【0041】

さらに上記構成の変形例として、導電突起体14は、図3(B)に示すように、ワイヤボンダーによって2段に積層して形成することもできる。このような導電突起体14の積層構造によれば、その高さH1を大きくすることができるため、リード12と電子デバイス30の離間距離D1も大きくすることができる。

【0042】

なお、導電突起体14は、全て同一あるいは略同一の高さH1を有していれば、上記以外の形状で形成されてもよい。例えば、図4(A)に示すように上端部14Bが上方に突出し、その先端が尖っていてもよく、また、図4(B)に示すように上端部14Bが上方に突出し、その先端が平坦面となるものであってもよい。これらの形状は、ワイヤボンダーの動作モードに応じて適宜選択することができる。

【0043】

以下に、上述した半導体装置の製造方法について説明する。最初の状態では、アイランド11が、吊りリード(不図示)を介してリードフレームの外枠に繋がれ、複数のリード12,12A,12Bも外枠に繋がれているものとする。この状態で、上述したように、好ましくはワイヤボンダーにより、電子デバイス30が跨って配置される領域のリード12の各表面上に複数の導電突起体14を形成する。

【0044】

この導電突起体14の形成工程の後、電子デバイス30が跨って配置される領域のリード12の各表面上と、アイランド11の表面上に、導電性ペースト15を塗布する。導電性ペースト15は、例えばマルチニードルによって、点状に塗布されてもよいし、ライン状に塗布されてもよい。

【0045】

その後、電子デバイス30を、所定のリード12,12A,12に跨るように配置し、電子デバイス30の両端部の裏面が複数の導電突起体14と重畳して直接接するように、リード12の各表面上に圧着し、導電性ペースト15を介して固着する。これと同時に、あるいは前後して、半導体チップ20をアイランド11の表面上に圧着し、導電性ペースト15を介して固着する。

【0046】

次に、ワイヤボンダーによって、各リード12,12A,12Bのそれぞれと各パッド電極21を接続する複数のボンディングワイヤを形成し、さらに、リード12上に固着された電子デバイス30、アイランド11上に固着された半導体チップ20、複数のボンディングワイヤ13、及び複数のリード12,12A,12Bの一部を、封止材16で覆って封止する。

【0047】

その後、吊りリード(不図示)とリード12,12A,12Bを切断して、リードフレームの外枠からアイランド11及びリード12,12A,12Bを切り離す。封止材16の外側に延びるリード12,12A,12Bの一部は、外部接続用の端子として適した形状に折り曲げられる(不図示)。

【0048】

[第2の実施形態]

本発明の第2の実施形態による半導体装置について、図面を参照して説明する。図5は、この半導体装置の平面図であり、図6は、図5のX’−X’線における断面図である。この半導体装置では、図5のY−Y線における断面図、つまり、導電突起体14に支持されてリード12の表面上に固着される電子デバイス30の断面図については、図2(B)と同様である。図5及び図6では、第1の実施形態に示したものと同一の構成要素については同一の参照番号を付して、その説明を省略する。

【0049】

図5及び図6に示すように、電子デバイス30が固着されるリード12の表面上だけではなく、アイランド11の表面上にも、互いに同一あるいは略同一の高さを有した複数の導電突起体14が形成されている。アイランド11の表面上の複数の導電突起体14は、それらの形状についても同一あるいは略同一であることが好ましい。アイランド11の表面上の導電突起体14は、第1の実施形態におけるリード12の表面上の導電突起体14と同一の材料を用いて、同一の工程で形成することができる。このアイランド11上で、IC等の半導体チップ40が、導電突起体14に支持されると共に、導電性ペースト15(例えば導電性粒子として銀粒子を含む)を介して固着(即ちダイボンド)されている。本実施形態では、導電性ペースト15は、導電性ペースト15に厚さを与えるためのフィラー粒子(例えばシリカ粒子)を含む必要はない。

【0050】

この半導体チップ40は、その周端部40Eの少なくとも一部がアイランド11の周端部11Eを越えてリード12側に向かって広がっている。本実施形態では、一例として、半導体チップ40は平面的に矩形状であるものとし、その周端部40Eの全て、つまり全ての辺がアイランド11よりも大きくなるようなサイズを有する場合について説明する。

【0051】

半導体チップ40は、その内部に、例えばトランジスタ等を含む集積回路を有し、周端部40Eに沿った表面に複数のパッド電極41を有している。各パッド電極41は、ボンディングワイヤ13(例えば金を含む金属材料からなる金属細線)を介して、リード12,12A,12Bと接続される。

【0052】

また、半導体チップ40の裏面は平坦か略平坦であるものとし、その裏面で裏面電極42が平坦か略平坦に形成されているものとする。裏面電極42は、半導体チップ40の裏面の全面あるいは略全面に形成されることが好ましい。この裏面電極42の表面(下面)と、導電突起体14の上端は、直接接している。

【0053】

複数の導電突起体14の少なくとも一部は、半導体チップ40とアイランド11が重畳する領域の周端部に沿って、あるいはその周端部の近傍に沿って配置されることが好ましい。図5及び図6では、半導体チップ40とアイランド11が重畳する領域の四隅に導電突起体14が配置され、さらに、半導体チップ40とアイランド11が重畳する領域の中央にも、導電突起体14が配置された場合を示す。アイランド11の表面に配置される導電突起体14の個数は、3個以上である。

【0054】

なお、アイランド11の表面上に配置される複数の導電突起体14の高さ、下端部14Aの径、上端部14Bの径は、必要に応じて、リード12の表面上に配置される複数の導電突起体14の高さH1、下端部14Aの径R1、上端部14Bの径R2とは異なる値に設定されてもよい。

【0055】

上記構成によれば、半導体チップ40は、同一あるいは略同一の高さを有した複数の導電突起体14によって支持されることで、アイランド11の表面に対して平行あるいは略平行に、即ちアイランド11の表面と一定の離間距離D2を保って固着される。そして、離間距離D2に応じて、半導体チップ40とリード12の端との間隔も大きく確保することができる。また、導電突起体14を介在させない場合と比較すると、導電性ペースト15の厚さが均一にならずに半導体チップ40がアイランド11上で傾いて、半導体チップ40とリード12の端との間隔が小さくなるおそれもない。

【0056】

従って、半導体チップ40の裏面側の周端部40E(半導体基板または裏面電極42)とリード12が近接あるいは接触して電気的にショートすることを回避することができる。

【0057】

また、このような半導体チップ40とリード12のショートの回避によれば、汎用性のある通常のリードフレーム(リード12,12A,12Bの薄さを調整するエッチング加工等が施されていないもの)を、そのままの状態(アイランド11とリード12,12A,12Bが同一の厚さのままの状態)で用いて実現できるという利点もある。

【0058】

また、裏面電極42とアイランド11は、導電性ペースト15に加えて、複数の導電突起体14を介して接続されるので、導電突起体14を配置しない場合に比して、裏面電極42とアイランド11の間の導電性を向上させることができ、接続抵抗を低く抑えることができる。

【0059】

さらに、封止された半導体装置の使用時等においてジュール熱が生じた場合、半導体チップ40の基板(例えばシリコン基板)とアイランド11(例えば銅)は、それぞれの異なる熱膨張係数に応じて熱膨張し、その熱膨張の差異によって機械的応力が生じても、半導体チップ40は、複数の導電突起体14に支持されアイランド11に対して平行あるいは略平行に固着されているため、上記機械的応力は、局所的に集中することなく、均等に分散しやすくなる。つまり、半導体装置において上記機械的応力を起因とするクラック等の損傷を防止することができる。

【0060】

また、半導体チップ40に生じたジュール熱は、導電突起体14を通して効率よくアイランド11に伝わって放出されるため、ジュール熱の影響を極力小さくすることができる。特に、半導体チップ40の発熱しやすい領域、例えばトランジスタの形成領域と重畳するアイランド11上の領域に、複数の導電突起体14のうちの少なくとも一部を配置すれば、上述した熱放出効果をより確実に高めることができる。

【0061】

なお、本発明は上記いずれの実施形態にも限定されず、要旨を逸脱しない範囲で変更が可能なことは言うまでもない。例えば、各実施形態では、複数の導電突起体14が配置されて電子デバイス30と電気的に接続された2つのリード12の間に、電子デバイス30と電気的に接続される必要のないリード12Aが1つだけ配置された例を示したが、本発明は、これらのリード12,12A,12の配置に限定されない。つまり、電子デバイス30と電気的に接続された2つのリード12の間には、電子デバイス30と電気的に接続される必要のないリード12Aが、2つ以上配置されてもよい。また、複数の導電突起体14が配置されて電子デバイス30と電気的に接続されるリード12は、2つに限定されず、3つ以上配置されてもよい。

【0062】

また、各実施形態における電子デバイス30は受動素子であるものとしたが、これ以外の素子、例えば能動素子や集積回路であってもよい。

【0063】

また、各実施形態における半導体チップ20,40の裏面には、裏面電極22,42が形成されるものとしたが、この裏面電極22,42は必ずしも形成されなくてもよい。この場合、第2の実施形態では、導電突起体14と直接接する半導体チップ40の裏面、あるいは他の構成物は平坦面を有していればよい。

【0064】

また、各実施形態では、導電突起体14は、ワイヤボンダーを用いて形成されるものとしたが、これ以外の方法で形成されてもよい。

【符号の説明】

【0065】

11 アイランド 12 リード

13 ボンディングワイヤ 14 導電突起体

15 導電性ペースト 16 封止材

20,40 半導体チップ 21,41 パッド電極

22,42 裏面電極 30 電子デバイス

【特許請求の範囲】

【請求項1】

アイランドと、

前記アイランドに向かって並列して延びる第1及び第2のリードと、

前記第1及び第2のリードの間で前記アイランドに向かって延びる第3のリードと、

前記第1及び第2のリードの各表面上に配置された複数の第1の導電突起体と、

両端部が前記複数の第1の導電突起体と重畳するように、前記第1、第2、及び第3のリードに跨って配置され、第1の導電性ペーストを介して前記第1及び第2のリードの各表面上に固着された電子デバイスと、

表面に複数のパッド電極を有し、第2の導電性ペーストを介して前記アイランドの表面上に固着された半導体チップと、

前記第1乃至第3のリードのそれぞれと前記パッド電極を接続するボンディングワイヤと、

前記電子デバイス、前記半導体チップ、及び前記ボンディングワイヤを覆って封止する封止材と、を備え、

前記電子デバイスは、厚さ方向で前記第3のリードの表面と離間するように、前記第1及び第2のリードの各表面上で前記複数の第1の導電突起体によって支持されることを特徴とする半導体装置。

【請求項2】

前記複数の第1の導電突起体は、前記電子デバイスを前記第1及び第2のリードの各表面に対して平行に支持する高さを有していることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記電子デバイスと対向する前記複数の第1の導電突起体の各上端は、前記電子デバイスを前記第1及び第2のリードの各表面に対して平行に支持する平坦面を有することを特徴とする請求項1または請求項2に記載の半導体装置。

【請求項4】

前記第1の導電突起体は、前記ボンディングワイヤと同一の金属材料からなることを特徴とする請求項1乃至請求項3のいずれかに記載の半導体装置。

【請求項5】

前記アイランドの表面上に配置された複数の第2の導電突起体を備え、

前記半導体チップは、その裏面が前記複数の第2の導電突起体と対向して直接接するように、前記第2の導電性ペーストを介して前記アイランドの表面上に固着され、前記半導体チップの周端部の少なくとも一部は、前記アイランドの周端部を越えて延在し、前記複数の第2の導電突起体は、前記半導体チップを前記アイランドの表面に対して平行に離間して支持する高さを有することを特徴とする請求項1乃至請求項4のいずれかに記載の半導体装置。

【請求項6】

前記半導体チップの裏面と対向する前記複数の第2の導電突起体の各上端は、前記半導体チップを前記アイランドの表面に対して平行に支持する平坦面を有することを特徴とする請求項5に記載の半導体装置。

【請求項7】

前記第2の導電突起体は、前記ボンディングワイヤと同一の金属材料からなることを特徴とする請求項5または請求項6に記載の半導体装置。

【請求項8】

アイランド、前記アイランドに向かって並列して延びる第1及び第2のリード、及び前記第1及び第2のリードの間で前記アイランドに向かって延びる第3のリードが外枠に繋がれたリードフレームと、表面に複数のパッド電極を有した半導体チップと、電子デバイスと、を準備し、

前記第1及び第2のリードの各表面上に複数の導電突起体を形成する工程と、

前記導電突起体の形成工程の後、前記第1及び第2のリードの各表面上、及び前記アイランドの表面上に導電性ペーストを塗布する工程と、

前記導電性ペーストの塗布工程の後、前記電子デバイスを、前記第1、第2、及び第3のリードに跨るように配置し、その両端部が前記複数の導電突起体と重畳して直接接するように、前記第1及び第2のリードの各表面上に圧着し、前記導電性ペーストを介して固着すると共に、前記半導体チップを、前記アイランドの表面上に圧着し、前記導電性ペーストを介して固着する工程と、

ワイヤボンダーによって形成される複数のボンディングワイヤを介して、前記第1乃至第3のリードのそれぞれと前記パッド電極を接続する工程と、

前記電子デバイス、前記半導体チップ、及び前記ボンディングワイヤを封止材で覆って封止する工程と、

前記アイランド、及び前記第1乃至第3のリードを、前記外枠から切り離す工程と、を備え、

前記電子デバイスは、厚さ方向で前記第3のリードと離間するように、前記第1及び第2のリードの各表面で前記複数の導電突起体によって支持されることを特徴とする半導体装置の製造方法。

【請求項9】

前記複数の導電突起体を形成する工程において、前記複数の導電突起体は、前記電子デバイスを前記第1及び第2のリードの各表面に対して平行に支持する高さに形成されることを特徴とする請求項8に記載の半導体装置の製造方法。

【請求項10】

前記複数の導電突起体を形成する工程は、前記ワイヤボンダーにより、溶融した金属材料を前記第1及び第2のリードの各表面上に点状に溶着する工程を含むことを特徴とする請求項8または請求項9に記載の半導体装置の製造方法。

【請求項1】

アイランドと、

前記アイランドに向かって並列して延びる第1及び第2のリードと、

前記第1及び第2のリードの間で前記アイランドに向かって延びる第3のリードと、

前記第1及び第2のリードの各表面上に配置された複数の第1の導電突起体と、

両端部が前記複数の第1の導電突起体と重畳するように、前記第1、第2、及び第3のリードに跨って配置され、第1の導電性ペーストを介して前記第1及び第2のリードの各表面上に固着された電子デバイスと、

表面に複数のパッド電極を有し、第2の導電性ペーストを介して前記アイランドの表面上に固着された半導体チップと、

前記第1乃至第3のリードのそれぞれと前記パッド電極を接続するボンディングワイヤと、

前記電子デバイス、前記半導体チップ、及び前記ボンディングワイヤを覆って封止する封止材と、を備え、

前記電子デバイスは、厚さ方向で前記第3のリードの表面と離間するように、前記第1及び第2のリードの各表面上で前記複数の第1の導電突起体によって支持されることを特徴とする半導体装置。

【請求項2】

前記複数の第1の導電突起体は、前記電子デバイスを前記第1及び第2のリードの各表面に対して平行に支持する高さを有していることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記電子デバイスと対向する前記複数の第1の導電突起体の各上端は、前記電子デバイスを前記第1及び第2のリードの各表面に対して平行に支持する平坦面を有することを特徴とする請求項1または請求項2に記載の半導体装置。

【請求項4】

前記第1の導電突起体は、前記ボンディングワイヤと同一の金属材料からなることを特徴とする請求項1乃至請求項3のいずれかに記載の半導体装置。

【請求項5】

前記アイランドの表面上に配置された複数の第2の導電突起体を備え、

前記半導体チップは、その裏面が前記複数の第2の導電突起体と対向して直接接するように、前記第2の導電性ペーストを介して前記アイランドの表面上に固着され、前記半導体チップの周端部の少なくとも一部は、前記アイランドの周端部を越えて延在し、前記複数の第2の導電突起体は、前記半導体チップを前記アイランドの表面に対して平行に離間して支持する高さを有することを特徴とする請求項1乃至請求項4のいずれかに記載の半導体装置。

【請求項6】

前記半導体チップの裏面と対向する前記複数の第2の導電突起体の各上端は、前記半導体チップを前記アイランドの表面に対して平行に支持する平坦面を有することを特徴とする請求項5に記載の半導体装置。

【請求項7】

前記第2の導電突起体は、前記ボンディングワイヤと同一の金属材料からなることを特徴とする請求項5または請求項6に記載の半導体装置。

【請求項8】

アイランド、前記アイランドに向かって並列して延びる第1及び第2のリード、及び前記第1及び第2のリードの間で前記アイランドに向かって延びる第3のリードが外枠に繋がれたリードフレームと、表面に複数のパッド電極を有した半導体チップと、電子デバイスと、を準備し、

前記第1及び第2のリードの各表面上に複数の導電突起体を形成する工程と、

前記導電突起体の形成工程の後、前記第1及び第2のリードの各表面上、及び前記アイランドの表面上に導電性ペーストを塗布する工程と、

前記導電性ペーストの塗布工程の後、前記電子デバイスを、前記第1、第2、及び第3のリードに跨るように配置し、その両端部が前記複数の導電突起体と重畳して直接接するように、前記第1及び第2のリードの各表面上に圧着し、前記導電性ペーストを介して固着すると共に、前記半導体チップを、前記アイランドの表面上に圧着し、前記導電性ペーストを介して固着する工程と、

ワイヤボンダーによって形成される複数のボンディングワイヤを介して、前記第1乃至第3のリードのそれぞれと前記パッド電極を接続する工程と、

前記電子デバイス、前記半導体チップ、及び前記ボンディングワイヤを封止材で覆って封止する工程と、

前記アイランド、及び前記第1乃至第3のリードを、前記外枠から切り離す工程と、を備え、

前記電子デバイスは、厚さ方向で前記第3のリードと離間するように、前記第1及び第2のリードの各表面で前記複数の導電突起体によって支持されることを特徴とする半導体装置の製造方法。

【請求項9】

前記複数の導電突起体を形成する工程において、前記複数の導電突起体は、前記電子デバイスを前記第1及び第2のリードの各表面に対して平行に支持する高さに形成されることを特徴とする請求項8に記載の半導体装置の製造方法。

【請求項10】

前記複数の導電突起体を形成する工程は、前記ワイヤボンダーにより、溶融した金属材料を前記第1及び第2のリードの各表面上に点状に溶着する工程を含むことを特徴とする請求項8または請求項9に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−110189(P2013−110189A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−252412(P2011−252412)

【出願日】平成23年11月18日(2011.11.18)

【出願人】(300057230)セミコンダクター・コンポーネンツ・インダストリーズ・リミテッド・ライアビリティ・カンパニー (119)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月18日(2011.11.18)

【出願人】(300057230)セミコンダクター・コンポーネンツ・インダストリーズ・リミテッド・ライアビリティ・カンパニー (119)

【Fターム(参考)】

[ Back to top ]