半導体装置及びその製造方法

【課題】所望の領域に容易に第1の膜を形成して半導体装置の不良を低減する。また、スループットが向上して、製造コストの低減を図る。

【解決手段】半導体装置の製造方法では、半導体基板の第1及び第2の領域上に第1の膜を形成した後、第1の膜上にフォトレジストパターンを形成する。フォトレジストパターンをマスクに用いた第1の膜のエッチングにより、第2の領域上の第1の膜を除去すると共に第2の領域上を覆うように被覆膜を形成する。半導体基板に熱処理を行うことにより、被覆膜を除去すると共にフォトレジストパターンに焼き締め処理を行う。この後、フォトレジストパターンを除去する。

【解決手段】半導体装置の製造方法では、半導体基板の第1及び第2の領域上に第1の膜を形成した後、第1の膜上にフォトレジストパターンを形成する。フォトレジストパターンをマスクに用いた第1の膜のエッチングにより、第2の領域上の第1の膜を除去すると共に第2の領域上を覆うように被覆膜を形成する。半導体基板に熱処理を行うことにより、被覆膜を除去すると共にフォトレジストパターンに焼き締め処理を行う。この後、フォトレジストパターンを除去する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

従来から、シリコン酸化膜やシリコン窒化膜等の除去にウェットエッチングが使用されている。ウェットエッチングは多数の基板を同時に処理でき、装置も簡易で低コストといった利点を有する。

【0003】

特許文献1の請求項1及び図2、特許文献2の段落[0042]及び図4(C)には、ウェットエッチングにより、シリコン酸化膜を除去する工程が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平5−211172号公報(請求項1及び図2)

【特許文献2】特開2008−235351号公報(段落[0042]及び図4(C))

【発明の概要】

【発明が解決しようとする課題】

【0005】

図1から3では、従来技術のウェットエッチングを行う例として、フォトレジストを用いてゲート絶縁膜4Aをエッチングする場合を示す。図1に示すように、シリコン基板1上にゲート絶縁膜4Aを成膜する。この後、フォトレジスト5をゲート絶縁膜4A上に塗布し、領域Dのゲート絶縁膜4Aが露出するようにパターニングする。次に、シリコン基板1の温度を130℃とする紫外線照射方式で、フォトレジスト5を焼き締めて、後続工程においてフォトレジスト5をゲート絶縁膜4Aから剥離し易くさせておく。このとき、加熱されたフォトレジスト5は熱収縮して、ゲート絶縁膜4Aから一部が剥離する。このため、ゲート絶縁膜4Aとフォトレジスト5の間に20nm程度の隙間Z3が生ずる。

【0006】

図2に示すように、下記条件のウェットエッチング方式によって、領域Dのゲート絶縁膜4Aを除去する。このとき、領域Dだけでなく、領域Cにおけるゲート絶縁膜4Aの一部も除去される。これは、領域Dに生じていた隙間Z3から、ゲート絶縁膜4Aを溶解して除去する薬液が毛細管現象によって進入してしまうためである。この現象は、隙間Z3が生じてしまうフォトレジスト5の焼き締め処理に伴って、避けることのできないものである。なお、焼き締め処理を行わなければ、隙間Z3が生じることはなく、それに伴って領域Cのゲート絶縁膜4Aは、その側面部からのサイドエッチによる除去となる。このため、過剰なオーバーエッチングを行わなければ、除去された領域の水平距離X2は、ゲート絶縁膜4Aの厚さZ1を越えることはない。しかし、焼き締め処理を行わなければ、フォトレジスト5の剥離処理において、ゲート絶縁膜4A上に少なくとも一部のフォトレジスト5が残留するので、残留したフォトレジスト5に起因した成膜不良などの問題が、後続工程で生じる。

(ウェットエッチ条件)

温度:20〜25℃

薬液:フッ化水素(HF)とフッ化アンモニウム(NH4F)の混合溶液

エッチング速度:2.2nm/min。

【0007】

図3に示すように、下記条件にて、ゲート絶縁膜4A上からフォトレジスト5を剥離して除去すると、すでに露出していた領域Dのシリコン基板1とともに、領域Cのゲート絶縁膜4Aが露出する。

(剥離条件)

温度:140℃

薬液:硫酸(H2SO4)と過酸化水素(H2O2)の混合液。

【0008】

このとき、フォトレジスト5以外の膜は除去されないので、残留している領域Cのゲート絶縁膜4Aの厚さは変動しない。また、領域Dにおけるゲート絶縁膜4Aの除去と、領域Dのフォトレジスト5の剥離は、同じ装置内でチャンバーを変更して処理しているので、夫々の処理を連続して行うことで、シリコン基板1の搬送時間を短縮し、スループットの向上を果たしている。ここで、フォトレジスト5の焼き締め処理をフォトレジスト5の剥離直前に行えば、領域DのP型ウェル上におけるゲート絶縁膜4Aの除去とフォトレジスト5の残留を避けることができる。しかし、ゲート絶縁膜4Aの除去後にシリコン基板1を一旦、装置外に搬出して、紫外線照射装置へ搬送する必要があるため、スループットを低下させてしまう問題が生じる。

【課題を解決するための手段】

【0009】

一実施形態は、

半導体基板の第1及び第2の領域上に、第1の膜を形成する工程と、

前記第1の膜上にフォトレジストパターンを形成する工程と、

前記フォトレジストパターンをマスクに用いた第1の膜のエッチングにより前記第2の領域上の第1の膜を除去すると共に、前記第2の領域上を覆うように被覆膜を形成する工程と、

前記半導体基板に熱処理を行うことにより、前記被覆膜を除去すると共に前記フォトレジストパターンの焼き締め処理を行う工程と、

前記フォトレジストパターンを除去する工程と、

を有する半導体装置の製造方法に関する。

【0010】

他の実施形態は、

半導体基板の第1及び第2の領域上に、第1の絶縁膜を形成する工程と、

前記第1の絶縁膜上にフォトレジストパターンを形成する工程と、

前記フォトレジストパターンをマスクに用いた第1の絶縁膜のエッチングにより、前記第2の領域上の第1の絶縁膜を除去すると共に前記半導体基板の第2の領域上に被覆膜を形成する工程と、

前記半導体基板に熱処理を行うことにより、前記被覆膜を除去すると共に前記フォトレジストパターンに焼き締め処理を行う工程と、

前記フォトレジストパターンを除去する工程と、

前記第1及び第2の領域上に、第2の絶縁膜及び導電膜をこの順に形成する工程と、

前記第1及び第2の絶縁膜並びに導電膜を加工して、前記第1及び第2の領域上の各々に、前記第1及び第2の絶縁膜を有するゲート絶縁膜並びにゲート電極を形成する工程と、

前記半導体基板の第1及び第2の領域内の各々にソース及びドレイン領域を形成する工程と、

を有する半導体装置の製造方法に関する。

【0011】

他の実施形態は、

第1の領域と第2の領域とを有する半導体基板と、

前記第1の領域に設けられた第1のトランジスタと、

前記第2の領域に設けられた第2のトランジスタと、

を有し、

前記第1のトランジスタのゲート絶縁膜は、前記第2のトランジスタのゲート絶縁膜よりも膜厚が厚い、半導体装置に関する。

【発明の効果】

【0012】

所望の領域に第1の膜を形成することが容易となり、半導体装置の不良を低減することができる。また、スループットが向上して、製造コストの低減を図ることができる。

【図面の簡単な説明】

【0013】

【図1】関連する技術のゲート絶縁膜の形成方法を表す図である。

【図2】関連する技術のゲート絶縁膜の形成方法を表す図である。

【図3】関連する技術のゲート絶縁膜の形成方法を表す図である。

【図4】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図5】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図6】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図7】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図8】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図9】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図10】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図11】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図12】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図13】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図14】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図15】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図16】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図17】本発明の一実施形態の半導体装置の製造方法を表す図である。

【発明を実施するための形態】

【0014】

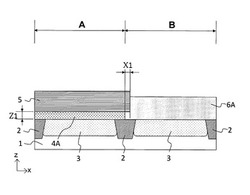

本発明の一実施形態として、NMOS(Negative channel Metal Oxide Semiconductor)型トランジスタにおけるマルチオキサイドの形成方法について、図4から図16を用いて説明する。なお、「マルチオキサイド」とは、一つのシリコン基板上に膜厚の異なるゲート絶縁膜を形成する技術である。図中の左側はマルチオキサイドの厚膜を形成する第1の領域Aであり、右側は薄膜を形成する第2の領域Bを示しており、以降の図2から図16でも同様である。

【0015】

図4に示すように、P型のシリコン基板1を準備し、フォトリソグラフィとドライエッチングによって、シリコン基板1に深さ200nmのトレンチ溝(図示せず)を形成する。次に、トレンチ溝内を埋め込むように、HDP−CVD(High Density Plasma− Chemical Vapor Deposition)法によるシリコン酸化膜(SiO2)である絶縁膜を成膜する。次に、シリコン基板1上の絶縁膜をCMP(Chemical Mechanical Polishing)によって除去すると、シリコン基板1の活性領域を区画する素子分離領域2が形成される。

【0016】

図5に示すように、シリコン基板1の表面が露出している領域に、下記のイオン注入条件にて、P型の不純物をシリコン基板1に注入し、P型ウェル3を形成する。

(イオン注入条件)

不純物:ボロン(B)

注入エネルギー:65〜100KeV

ドーズ量:8×1011〜8×1013atoms/cm2。

【0017】

さらに、エネルギーを200〜250KeVと高くした設定で、ボロンを追加注入して、P型ウェル3が深くなるようにしてもよい。この工程によって、第1の領域Aと第2の領域Bには、同時に同じ深さのP型ウェル3が形成される。

【0018】

図6に示すように、シリコン基板1上に、熱酸化法によるシリコン酸化膜である厚さZ1が5nmのゲート絶縁膜(第1の膜)4Aを成膜する。ゲート絶縁膜(第1の絶縁膜)4Aは単層のシリコン酸化膜以外に、ハフニウム(Hf)等を含有した高誘電率絶縁膜(High−K膜)や、シリコン窒化膜(SiN)とシリコン酸化膜の積層膜等でもよい。次に、フォトレジストをゲート絶縁膜4A上に塗布し、第2の領域Bのゲート絶縁膜4Aの表面が露出するようにパターニングして、フォトレジストパターン5を形成する。

【0019】

図7に示すように、フォトレジストパターン5をマスクにした下記条件のケミカルエッチング方式により、第2の領域Bにおけるゲート絶縁膜4Aをエッチングする。

(ケミカルエッチング条件)

圧力:10〜300mTorr

エッチングガス:アンモニア(NH3)、フッ化水素(HF)、フッ化窒素(NFX)

エッチングガス流量:10〜100sccm

チャンバー温度:25〜80℃

エッチング速度:1〜20nm/min。

【0020】

この条件によって、第2の領域Bにおけるゲート絶縁膜4Aをエッチングすると、エッチングガスとゲート絶縁膜4Aを構成しているシリコン酸化膜(SiO2)が下記に示す反応式で化合して、ケイフッ化アンモニウム((NH4)2SiF6)である被覆膜6が生ずる。

【0021】

NH3+HF→NH4F

6NH4F+SiO2→(NH4)2SiF6+4NH3+2H2O

このときの被覆膜6は、エッチングされて膜厚が減少したゲート絶縁膜4A上に順次、積層されるので、露出していたゲート絶縁膜4Aの表面は、被覆膜6で覆われる。しかし、エッチングガスは、被覆膜6の表面からその膜中を透過して、被覆膜6の底面に接しているゲート絶縁膜4Aに到達できるので、被覆膜6で覆われていても、ゲート絶縁膜4Aのエッチングを継続することができる。また、ケミカルエッチングは、等方性のエッチングであるので、膜厚を減らすZ方向だけでなく、X方向にもエッチングが進行する。このため、フォトレジスト5の端部を支持していたゲート絶縁膜4Aがエッチングされて、フォトレジスト5がオーバーハングしてしまうが、ここでもゲート絶縁膜4Aの表面が被覆膜6で覆われるので、オーバーハング部分は被覆膜6で埋め込まれる。

【0022】

図8に示すように、上記ケミカルエッチング条件にて、第2の領域Bにおけるゲート絶縁膜4Aのエッチングを継続すると、ゲート絶縁膜4Aは除去される。最終的に、第2の領域Bにおけるシリコン基板1上が、図4における被覆膜6よりも厚い被覆膜6Aで覆われる。被覆膜6Aの厚さは、除去したゲート絶縁膜4Aの厚さの3〜4倍となるが、140nmを超えてしまうとエッチングガスの透過率が著しく低下して、ゲート絶縁膜4Aの除去が困難となる。しかし、被覆膜6Aを140nm厚で生成させるには、ゲート絶縁膜4Aの厚さを35nm以上にしておく必要がある。このため、ゲート絶縁膜4Aの厚さを35nm未満にしておけば、被覆膜6で覆われたゲート絶縁膜4Aでも、ケミカルエッチングによって除去することができる。本実施形態では、5nm厚のゲート絶縁膜4Aは、微細化に伴ってさらに薄膜化されるので、ケミカルエッチングによって除去することができる。なお、この時点ではフォトレジスト5に焼き締め処理を行っておらず、オーバーハングしたフォトレジスト5の下面には他の部分よりもエッチングガスが到達し難くなる。このため、X方向におけるゲート絶縁膜4Aの除去量X1は、ゲート絶縁膜4Aの厚さZ1よりも小さくなる。このように本実施形態では、フォトレジスト5下のゲート絶縁膜4Aの除去量X1を、関連する技術である図2の除去量X2と比べて小さくすることができる。ゲート絶縁膜4AがX1だけ除去された後であっても、ゲート絶縁膜4Aは第1の領域AのP型ウェル3の全体に設けられている。このため、後述の工程で形成する第1のトランジスタTr1の装置に不良が発生するのを防止することができる。

【0023】

図9に示すように、下記条件にてシリコン基板1の熱処理を行うと、下記反応式に示すように被覆膜6Aが揮発性分子となって昇華し、シリコン基板1上から除去されるので、第2の領域Bのシリコン基板1が露出する。

(加熱条件)

温度:80〜500℃

チャンバー雰囲気:窒素(N2)、水素(H2)

(NH4)2SiF6→SiF4+2NH3+2HF

このとき、加熱されたフォトレジストパターン5は、熱収縮してゲート絶縁膜4Aから一部が剥離するので、ゲート絶縁膜4Aとフォトレジストパターン5の間に20nm程度の隙間Z2が生ずる(焼き締め処理)。ここでは、すでに第2の領域Bのゲート絶縁膜4Aを除去してあるので、隙間Z2に起因した問題は生じない。また、この加熱処理は、隙間Z2が生じることから明らかなように、ゲート絶縁膜4Aからフォトレジストパターン5を除去する際において、フォトレジストパターン5を残留させずに容易に剥離させる効果を奏する。さらに、第2の領域Bにおけるゲート絶縁膜4Aの除去と被覆膜6の除去は、同じ装置内でチャンバーだけを変更して処理しており、夫々の処理を連続して行うことで、シリコン基板1の搬送時間を短縮して、スループットの向上を果たしている。

【0024】

図10に示すように、下記条件にて、ゲート絶縁膜4A上からフォトレジストパターン5を剥離して除去すると、すでに露出していた第2の領域Bのシリコン基板1とともに、第1の領域Aのゲート絶縁膜4Aが露出する。

(剥離条件)

温度:140℃

薬液:硫酸(H2SO4)と過酸化水素(H2O2)の混合溶液

このとき、フォトレジストパターン5以外の膜は除去されないので、残留している第1の領域Aのゲート絶縁膜4Aの厚さは変動しない。

【0025】

図11に示すように、下記の洗浄条件にて、露出していた第2の領域Bのシリコン基板1上から異物を除去すると、露出していた第1の領域Aのゲート絶縁膜4Aが膜減りして、3nm厚のゲート絶縁膜4Bとなる。

(剥離条件)

温度:35℃

薬液:アンモニア(NH3)と過酸化水素(H2O2)の混合溶液。

【0026】

次に、第2の領域Bのシリコン基板1上に、熱酸化法による厚さZ4が3nmのシリコン酸化膜であるゲート絶縁膜(第2の絶縁膜)4Cを成膜する。ゲート絶縁膜4Cは、単層のシリコン酸化膜以外に、ハフニウム等を含有した高誘電率絶縁膜や、シリコン窒化膜とシリコン酸化膜の積層膜等でもよい。ここでは、第2の領域Bだけでなく、第1の領域Aにもゲート絶縁膜4Cが形成されるので、第1の領域Aでのゲート絶縁膜4Dの膜厚は、ゲート絶縁膜4Bの厚さにゲート絶縁膜4Cの厚さが加わって6nmとなる。これ以降、第2の領域Bのゲート絶縁膜4Cと第1の領域Aのゲート絶縁膜4Dを合わせて、ゲート絶縁膜4と称する。

【0027】

図12に示すように、ゲート絶縁膜4上に、CVD法によって60〜100nm厚のポリシリコン(多結晶シリコン)である導電膜7A(図示せず)を成膜する。この成膜時には、導電膜7Aには不純物を導入しない。次に、下記のイオン注入条件にて、N型の不純物を導電膜7Aに注入する。

(イオン注入条件)

不純物:リン(P)

注入エネルギー:5〜8KeV

ドーズ量:3.6×1014〜3.6×1016atoms/cm2。

【0028】

以上のイオン注入で、導電膜7A内にリンがドープされたN型ドープポリシリコンである導電膜7が形成される。次に、導電膜7上にCVD法によって、5nm厚のタングステンシリサイド(WSi)上に45nm厚のタングステン(W)を積層した導電膜8と、CVD法によって200nm厚のシリコン窒化膜(SiN)である絶縁膜9を順次、成膜する。なお、導電膜7上に形成するのは、タングステン以外の高融点金属膜でもよい。

【0029】

図13に示すように、フォトリソグラフィとドライエッチングによって、ゲート絶縁膜4と導電膜7と導電膜8と絶縁膜9の不要な部分を除去すると、シリコン基板1に形成したP型ウェル3上に、ゲート絶縁膜4と、ゲート電極となる導電膜7及び導電膜8と、絶縁膜9で構成されたパターンが形成されて、NMOS10が完成する。ここで、ゲート絶縁膜4Cは、NMOS10aにおいて、後に形成する第2のトランジスタTr2のゲート絶縁膜4aとなっており、ゲート絶縁膜4Dは、NMOS10bにおいて後に形成する第1のトランジスタTr1のゲート絶縁膜4bとなっている。しかし、第2の領域Bに形成したNMOS10aにおけるゲート絶縁膜4aの膜厚と、第1の領域Aに形成したNMOS10bにおけるゲート絶縁膜4bの膜厚は異なっているので、NMOS10bを有する第1のトランジスタTr1、NMOS10aを有する第2のトランジスタTr2の使用環境は異なる。つまり、外部とのインターフェースに用いるトランジスタは、比較的、高い電源電圧を必要とするので、厚いゲート絶縁膜4bを有する第1のトランジスタTr1が最適であるに対して、高速動作をさせるトランジスタでは、電源電圧を低くするので、薄いゲート絶縁膜4bを有する第2のトランジスタTr2が最適となる。

【0030】

図14に示すように、下記のイオン注入条件にて、N型の不純物をシリコン基板1に注入する。

(イオン注入条件)

不純物:砒素(As)またはリン(P)

注入エネルギー:2〜4KeV

ドーズ量:1×1013〜8×1014atoms/cm2

以上のイオン注入で、P型ウェル3中にN型LDD11が形成される。

【0031】

図15に示すように、NMOS10上に、CVD法において20nm厚のシリコン窒化膜(SiN)を成膜した後に、エッチバックして、NMOS10の側面を被覆するサイドウォール12を形成する。次に、下記のイオン注入条件にて、N型の不純物をシリコン基板1に注入する。

(イオン注入条件)

不純物:砒素(As)

注入エネルギー:12〜20KeV

ドーズ量:3×1014〜3×1016atoms/cm2。

【0032】

この際に、注入するドーズ量は先に形成したN型LDD11に注入したドーズ量よりも多くなるように設定する。以上のイオン注入で、P型ウェル3中に高濃度のN型拡散領域13が、N型LDD11よりも深い位置に形成される。N型拡散領域13は、トランジスタのソース・ドレイン領域として機能する。これにより、第1の領域Aに第1のトランジスタTr1、第2の領域Bに第2のトランジスタTr2が完成する。

【0033】

図16に示すように、NMOS10を埋め込むように、CVD法によるシリコン酸化膜である層間絶縁膜14を形成し、CMP法によってNMOS10aと10bの絶縁膜9が露出するまで平坦化する。引き続き、CVD法による150〜200nm厚のシリコン酸化膜である層間絶縁膜15を成膜する。次に、フォトリソグラフィとドライエッチングにより、N型拡散領域13の上面の一部が露出するように、層間絶縁膜14と層間絶縁膜15を貫通するコンタクトホール(図示せず)を形成する。次に、コンタクトホールを埋め込むように、CVD法によるタングステン等の導電膜を形成し、CMPによって層間絶縁膜15上に堆積された導電膜を除去して、コンタクトプラグ16を形成する。ゲート電極を構成する導電膜8に接続するコンタクトプラグ(図示せず)も同様にして形成する。

【0034】

図17に示すように、コンタクトプラグ16に接続する配線17を、スパッタ法によるアルミニウム(Al)、銅(Cu)、タングステン(W)等の金属を用いて形成する。配線17を覆う保護膜18をCVD法によるシリコン酸窒化(SiON)等を用いて形成すれば、半導体装置が完成する。

【0035】

保護膜18を形成する前に、さらに別の配線層を形成した多層配線構造としてもよい。また、DRAM等の記憶装置を形成するために、メモリセル領域を構成するトランジスタや記憶素子を有するようにしてもよい。

【0036】

本実施形態では、マルチオキサイドの形成時における第2の領域Bのゲート絶縁膜除去をケミカルエッチングで行い、その後、ケミカルエッチで生じた被覆膜の除去とともにフォトレジストパターンの焼き締め処理を行っている。このため、第1の領域Aにおけるゲート絶縁膜上に焼き締め処理によって隙間が生じても、エッチングガスが侵入することがなく、ゲート絶縁膜の過剰エッチングを防止できる。従って、第1の領域Aにおけるゲート絶縁膜の領域確保が容易となり、半導体装置の不良を低減することができる。さらに、焼き締め処理は、被覆膜の除去と同じ処理装置で行えるので、スループットが向上して、製造コストの低減も図ることができる。なお、膜厚の数値や処理条件は一例であって、変更が可能である。

【0037】

以上、本発明の好ましい実施形態について説明したが、本発明は、上記の実施形態に限定されることなく、本発明の主旨を逸脱しない範囲で種々の変更が可能であり、それらも本発明の範囲内に包含されるものであることはいうまでもない。

【符号の説明】

【0038】

1 シリコン基板

2 素子分離領域

3 P型ウェル

4、4a、4b、4A、4C、4D ゲート絶縁膜

5 フォトレジスト

6 被覆膜

7、7A、8 導電膜

9 絶縁膜

10、10a、10b NMOS

11 N型LDD

12 サイドウォール

13 N型拡散領域

14、15 層間絶縁膜

16 コンタクトプラグ

17 配線

18 保護膜

A 第1の領域

B 第2の領域

C、D 領域

Tr1 第1のトランジスタ

Tr2 第2のトランジスタ

X1 除去量

X2 水平距離

Z1 ゲート絶縁膜4Aの厚さ

Z2、Z3 隙間

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

従来から、シリコン酸化膜やシリコン窒化膜等の除去にウェットエッチングが使用されている。ウェットエッチングは多数の基板を同時に処理でき、装置も簡易で低コストといった利点を有する。

【0003】

特許文献1の請求項1及び図2、特許文献2の段落[0042]及び図4(C)には、ウェットエッチングにより、シリコン酸化膜を除去する工程が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平5−211172号公報(請求項1及び図2)

【特許文献2】特開2008−235351号公報(段落[0042]及び図4(C))

【発明の概要】

【発明が解決しようとする課題】

【0005】

図1から3では、従来技術のウェットエッチングを行う例として、フォトレジストを用いてゲート絶縁膜4Aをエッチングする場合を示す。図1に示すように、シリコン基板1上にゲート絶縁膜4Aを成膜する。この後、フォトレジスト5をゲート絶縁膜4A上に塗布し、領域Dのゲート絶縁膜4Aが露出するようにパターニングする。次に、シリコン基板1の温度を130℃とする紫外線照射方式で、フォトレジスト5を焼き締めて、後続工程においてフォトレジスト5をゲート絶縁膜4Aから剥離し易くさせておく。このとき、加熱されたフォトレジスト5は熱収縮して、ゲート絶縁膜4Aから一部が剥離する。このため、ゲート絶縁膜4Aとフォトレジスト5の間に20nm程度の隙間Z3が生ずる。

【0006】

図2に示すように、下記条件のウェットエッチング方式によって、領域Dのゲート絶縁膜4Aを除去する。このとき、領域Dだけでなく、領域Cにおけるゲート絶縁膜4Aの一部も除去される。これは、領域Dに生じていた隙間Z3から、ゲート絶縁膜4Aを溶解して除去する薬液が毛細管現象によって進入してしまうためである。この現象は、隙間Z3が生じてしまうフォトレジスト5の焼き締め処理に伴って、避けることのできないものである。なお、焼き締め処理を行わなければ、隙間Z3が生じることはなく、それに伴って領域Cのゲート絶縁膜4Aは、その側面部からのサイドエッチによる除去となる。このため、過剰なオーバーエッチングを行わなければ、除去された領域の水平距離X2は、ゲート絶縁膜4Aの厚さZ1を越えることはない。しかし、焼き締め処理を行わなければ、フォトレジスト5の剥離処理において、ゲート絶縁膜4A上に少なくとも一部のフォトレジスト5が残留するので、残留したフォトレジスト5に起因した成膜不良などの問題が、後続工程で生じる。

(ウェットエッチ条件)

温度:20〜25℃

薬液:フッ化水素(HF)とフッ化アンモニウム(NH4F)の混合溶液

エッチング速度:2.2nm/min。

【0007】

図3に示すように、下記条件にて、ゲート絶縁膜4A上からフォトレジスト5を剥離して除去すると、すでに露出していた領域Dのシリコン基板1とともに、領域Cのゲート絶縁膜4Aが露出する。

(剥離条件)

温度:140℃

薬液:硫酸(H2SO4)と過酸化水素(H2O2)の混合液。

【0008】

このとき、フォトレジスト5以外の膜は除去されないので、残留している領域Cのゲート絶縁膜4Aの厚さは変動しない。また、領域Dにおけるゲート絶縁膜4Aの除去と、領域Dのフォトレジスト5の剥離は、同じ装置内でチャンバーを変更して処理しているので、夫々の処理を連続して行うことで、シリコン基板1の搬送時間を短縮し、スループットの向上を果たしている。ここで、フォトレジスト5の焼き締め処理をフォトレジスト5の剥離直前に行えば、領域DのP型ウェル上におけるゲート絶縁膜4Aの除去とフォトレジスト5の残留を避けることができる。しかし、ゲート絶縁膜4Aの除去後にシリコン基板1を一旦、装置外に搬出して、紫外線照射装置へ搬送する必要があるため、スループットを低下させてしまう問題が生じる。

【課題を解決するための手段】

【0009】

一実施形態は、

半導体基板の第1及び第2の領域上に、第1の膜を形成する工程と、

前記第1の膜上にフォトレジストパターンを形成する工程と、

前記フォトレジストパターンをマスクに用いた第1の膜のエッチングにより前記第2の領域上の第1の膜を除去すると共に、前記第2の領域上を覆うように被覆膜を形成する工程と、

前記半導体基板に熱処理を行うことにより、前記被覆膜を除去すると共に前記フォトレジストパターンの焼き締め処理を行う工程と、

前記フォトレジストパターンを除去する工程と、

を有する半導体装置の製造方法に関する。

【0010】

他の実施形態は、

半導体基板の第1及び第2の領域上に、第1の絶縁膜を形成する工程と、

前記第1の絶縁膜上にフォトレジストパターンを形成する工程と、

前記フォトレジストパターンをマスクに用いた第1の絶縁膜のエッチングにより、前記第2の領域上の第1の絶縁膜を除去すると共に前記半導体基板の第2の領域上に被覆膜を形成する工程と、

前記半導体基板に熱処理を行うことにより、前記被覆膜を除去すると共に前記フォトレジストパターンに焼き締め処理を行う工程と、

前記フォトレジストパターンを除去する工程と、

前記第1及び第2の領域上に、第2の絶縁膜及び導電膜をこの順に形成する工程と、

前記第1及び第2の絶縁膜並びに導電膜を加工して、前記第1及び第2の領域上の各々に、前記第1及び第2の絶縁膜を有するゲート絶縁膜並びにゲート電極を形成する工程と、

前記半導体基板の第1及び第2の領域内の各々にソース及びドレイン領域を形成する工程と、

を有する半導体装置の製造方法に関する。

【0011】

他の実施形態は、

第1の領域と第2の領域とを有する半導体基板と、

前記第1の領域に設けられた第1のトランジスタと、

前記第2の領域に設けられた第2のトランジスタと、

を有し、

前記第1のトランジスタのゲート絶縁膜は、前記第2のトランジスタのゲート絶縁膜よりも膜厚が厚い、半導体装置に関する。

【発明の効果】

【0012】

所望の領域に第1の膜を形成することが容易となり、半導体装置の不良を低減することができる。また、スループットが向上して、製造コストの低減を図ることができる。

【図面の簡単な説明】

【0013】

【図1】関連する技術のゲート絶縁膜の形成方法を表す図である。

【図2】関連する技術のゲート絶縁膜の形成方法を表す図である。

【図3】関連する技術のゲート絶縁膜の形成方法を表す図である。

【図4】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図5】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図6】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図7】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図8】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図9】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図10】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図11】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図12】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図13】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図14】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図15】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図16】本発明の一実施形態の半導体装置の製造方法を表す図である。

【図17】本発明の一実施形態の半導体装置の製造方法を表す図である。

【発明を実施するための形態】

【0014】

本発明の一実施形態として、NMOS(Negative channel Metal Oxide Semiconductor)型トランジスタにおけるマルチオキサイドの形成方法について、図4から図16を用いて説明する。なお、「マルチオキサイド」とは、一つのシリコン基板上に膜厚の異なるゲート絶縁膜を形成する技術である。図中の左側はマルチオキサイドの厚膜を形成する第1の領域Aであり、右側は薄膜を形成する第2の領域Bを示しており、以降の図2から図16でも同様である。

【0015】

図4に示すように、P型のシリコン基板1を準備し、フォトリソグラフィとドライエッチングによって、シリコン基板1に深さ200nmのトレンチ溝(図示せず)を形成する。次に、トレンチ溝内を埋め込むように、HDP−CVD(High Density Plasma− Chemical Vapor Deposition)法によるシリコン酸化膜(SiO2)である絶縁膜を成膜する。次に、シリコン基板1上の絶縁膜をCMP(Chemical Mechanical Polishing)によって除去すると、シリコン基板1の活性領域を区画する素子分離領域2が形成される。

【0016】

図5に示すように、シリコン基板1の表面が露出している領域に、下記のイオン注入条件にて、P型の不純物をシリコン基板1に注入し、P型ウェル3を形成する。

(イオン注入条件)

不純物:ボロン(B)

注入エネルギー:65〜100KeV

ドーズ量:8×1011〜8×1013atoms/cm2。

【0017】

さらに、エネルギーを200〜250KeVと高くした設定で、ボロンを追加注入して、P型ウェル3が深くなるようにしてもよい。この工程によって、第1の領域Aと第2の領域Bには、同時に同じ深さのP型ウェル3が形成される。

【0018】

図6に示すように、シリコン基板1上に、熱酸化法によるシリコン酸化膜である厚さZ1が5nmのゲート絶縁膜(第1の膜)4Aを成膜する。ゲート絶縁膜(第1の絶縁膜)4Aは単層のシリコン酸化膜以外に、ハフニウム(Hf)等を含有した高誘電率絶縁膜(High−K膜)や、シリコン窒化膜(SiN)とシリコン酸化膜の積層膜等でもよい。次に、フォトレジストをゲート絶縁膜4A上に塗布し、第2の領域Bのゲート絶縁膜4Aの表面が露出するようにパターニングして、フォトレジストパターン5を形成する。

【0019】

図7に示すように、フォトレジストパターン5をマスクにした下記条件のケミカルエッチング方式により、第2の領域Bにおけるゲート絶縁膜4Aをエッチングする。

(ケミカルエッチング条件)

圧力:10〜300mTorr

エッチングガス:アンモニア(NH3)、フッ化水素(HF)、フッ化窒素(NFX)

エッチングガス流量:10〜100sccm

チャンバー温度:25〜80℃

エッチング速度:1〜20nm/min。

【0020】

この条件によって、第2の領域Bにおけるゲート絶縁膜4Aをエッチングすると、エッチングガスとゲート絶縁膜4Aを構成しているシリコン酸化膜(SiO2)が下記に示す反応式で化合して、ケイフッ化アンモニウム((NH4)2SiF6)である被覆膜6が生ずる。

【0021】

NH3+HF→NH4F

6NH4F+SiO2→(NH4)2SiF6+4NH3+2H2O

このときの被覆膜6は、エッチングされて膜厚が減少したゲート絶縁膜4A上に順次、積層されるので、露出していたゲート絶縁膜4Aの表面は、被覆膜6で覆われる。しかし、エッチングガスは、被覆膜6の表面からその膜中を透過して、被覆膜6の底面に接しているゲート絶縁膜4Aに到達できるので、被覆膜6で覆われていても、ゲート絶縁膜4Aのエッチングを継続することができる。また、ケミカルエッチングは、等方性のエッチングであるので、膜厚を減らすZ方向だけでなく、X方向にもエッチングが進行する。このため、フォトレジスト5の端部を支持していたゲート絶縁膜4Aがエッチングされて、フォトレジスト5がオーバーハングしてしまうが、ここでもゲート絶縁膜4Aの表面が被覆膜6で覆われるので、オーバーハング部分は被覆膜6で埋め込まれる。

【0022】

図8に示すように、上記ケミカルエッチング条件にて、第2の領域Bにおけるゲート絶縁膜4Aのエッチングを継続すると、ゲート絶縁膜4Aは除去される。最終的に、第2の領域Bにおけるシリコン基板1上が、図4における被覆膜6よりも厚い被覆膜6Aで覆われる。被覆膜6Aの厚さは、除去したゲート絶縁膜4Aの厚さの3〜4倍となるが、140nmを超えてしまうとエッチングガスの透過率が著しく低下して、ゲート絶縁膜4Aの除去が困難となる。しかし、被覆膜6Aを140nm厚で生成させるには、ゲート絶縁膜4Aの厚さを35nm以上にしておく必要がある。このため、ゲート絶縁膜4Aの厚さを35nm未満にしておけば、被覆膜6で覆われたゲート絶縁膜4Aでも、ケミカルエッチングによって除去することができる。本実施形態では、5nm厚のゲート絶縁膜4Aは、微細化に伴ってさらに薄膜化されるので、ケミカルエッチングによって除去することができる。なお、この時点ではフォトレジスト5に焼き締め処理を行っておらず、オーバーハングしたフォトレジスト5の下面には他の部分よりもエッチングガスが到達し難くなる。このため、X方向におけるゲート絶縁膜4Aの除去量X1は、ゲート絶縁膜4Aの厚さZ1よりも小さくなる。このように本実施形態では、フォトレジスト5下のゲート絶縁膜4Aの除去量X1を、関連する技術である図2の除去量X2と比べて小さくすることができる。ゲート絶縁膜4AがX1だけ除去された後であっても、ゲート絶縁膜4Aは第1の領域AのP型ウェル3の全体に設けられている。このため、後述の工程で形成する第1のトランジスタTr1の装置に不良が発生するのを防止することができる。

【0023】

図9に示すように、下記条件にてシリコン基板1の熱処理を行うと、下記反応式に示すように被覆膜6Aが揮発性分子となって昇華し、シリコン基板1上から除去されるので、第2の領域Bのシリコン基板1が露出する。

(加熱条件)

温度:80〜500℃

チャンバー雰囲気:窒素(N2)、水素(H2)

(NH4)2SiF6→SiF4+2NH3+2HF

このとき、加熱されたフォトレジストパターン5は、熱収縮してゲート絶縁膜4Aから一部が剥離するので、ゲート絶縁膜4Aとフォトレジストパターン5の間に20nm程度の隙間Z2が生ずる(焼き締め処理)。ここでは、すでに第2の領域Bのゲート絶縁膜4Aを除去してあるので、隙間Z2に起因した問題は生じない。また、この加熱処理は、隙間Z2が生じることから明らかなように、ゲート絶縁膜4Aからフォトレジストパターン5を除去する際において、フォトレジストパターン5を残留させずに容易に剥離させる効果を奏する。さらに、第2の領域Bにおけるゲート絶縁膜4Aの除去と被覆膜6の除去は、同じ装置内でチャンバーだけを変更して処理しており、夫々の処理を連続して行うことで、シリコン基板1の搬送時間を短縮して、スループットの向上を果たしている。

【0024】

図10に示すように、下記条件にて、ゲート絶縁膜4A上からフォトレジストパターン5を剥離して除去すると、すでに露出していた第2の領域Bのシリコン基板1とともに、第1の領域Aのゲート絶縁膜4Aが露出する。

(剥離条件)

温度:140℃

薬液:硫酸(H2SO4)と過酸化水素(H2O2)の混合溶液

このとき、フォトレジストパターン5以外の膜は除去されないので、残留している第1の領域Aのゲート絶縁膜4Aの厚さは変動しない。

【0025】

図11に示すように、下記の洗浄条件にて、露出していた第2の領域Bのシリコン基板1上から異物を除去すると、露出していた第1の領域Aのゲート絶縁膜4Aが膜減りして、3nm厚のゲート絶縁膜4Bとなる。

(剥離条件)

温度:35℃

薬液:アンモニア(NH3)と過酸化水素(H2O2)の混合溶液。

【0026】

次に、第2の領域Bのシリコン基板1上に、熱酸化法による厚さZ4が3nmのシリコン酸化膜であるゲート絶縁膜(第2の絶縁膜)4Cを成膜する。ゲート絶縁膜4Cは、単層のシリコン酸化膜以外に、ハフニウム等を含有した高誘電率絶縁膜や、シリコン窒化膜とシリコン酸化膜の積層膜等でもよい。ここでは、第2の領域Bだけでなく、第1の領域Aにもゲート絶縁膜4Cが形成されるので、第1の領域Aでのゲート絶縁膜4Dの膜厚は、ゲート絶縁膜4Bの厚さにゲート絶縁膜4Cの厚さが加わって6nmとなる。これ以降、第2の領域Bのゲート絶縁膜4Cと第1の領域Aのゲート絶縁膜4Dを合わせて、ゲート絶縁膜4と称する。

【0027】

図12に示すように、ゲート絶縁膜4上に、CVD法によって60〜100nm厚のポリシリコン(多結晶シリコン)である導電膜7A(図示せず)を成膜する。この成膜時には、導電膜7Aには不純物を導入しない。次に、下記のイオン注入条件にて、N型の不純物を導電膜7Aに注入する。

(イオン注入条件)

不純物:リン(P)

注入エネルギー:5〜8KeV

ドーズ量:3.6×1014〜3.6×1016atoms/cm2。

【0028】

以上のイオン注入で、導電膜7A内にリンがドープされたN型ドープポリシリコンである導電膜7が形成される。次に、導電膜7上にCVD法によって、5nm厚のタングステンシリサイド(WSi)上に45nm厚のタングステン(W)を積層した導電膜8と、CVD法によって200nm厚のシリコン窒化膜(SiN)である絶縁膜9を順次、成膜する。なお、導電膜7上に形成するのは、タングステン以外の高融点金属膜でもよい。

【0029】

図13に示すように、フォトリソグラフィとドライエッチングによって、ゲート絶縁膜4と導電膜7と導電膜8と絶縁膜9の不要な部分を除去すると、シリコン基板1に形成したP型ウェル3上に、ゲート絶縁膜4と、ゲート電極となる導電膜7及び導電膜8と、絶縁膜9で構成されたパターンが形成されて、NMOS10が完成する。ここで、ゲート絶縁膜4Cは、NMOS10aにおいて、後に形成する第2のトランジスタTr2のゲート絶縁膜4aとなっており、ゲート絶縁膜4Dは、NMOS10bにおいて後に形成する第1のトランジスタTr1のゲート絶縁膜4bとなっている。しかし、第2の領域Bに形成したNMOS10aにおけるゲート絶縁膜4aの膜厚と、第1の領域Aに形成したNMOS10bにおけるゲート絶縁膜4bの膜厚は異なっているので、NMOS10bを有する第1のトランジスタTr1、NMOS10aを有する第2のトランジスタTr2の使用環境は異なる。つまり、外部とのインターフェースに用いるトランジスタは、比較的、高い電源電圧を必要とするので、厚いゲート絶縁膜4bを有する第1のトランジスタTr1が最適であるに対して、高速動作をさせるトランジスタでは、電源電圧を低くするので、薄いゲート絶縁膜4bを有する第2のトランジスタTr2が最適となる。

【0030】

図14に示すように、下記のイオン注入条件にて、N型の不純物をシリコン基板1に注入する。

(イオン注入条件)

不純物:砒素(As)またはリン(P)

注入エネルギー:2〜4KeV

ドーズ量:1×1013〜8×1014atoms/cm2

以上のイオン注入で、P型ウェル3中にN型LDD11が形成される。

【0031】

図15に示すように、NMOS10上に、CVD法において20nm厚のシリコン窒化膜(SiN)を成膜した後に、エッチバックして、NMOS10の側面を被覆するサイドウォール12を形成する。次に、下記のイオン注入条件にて、N型の不純物をシリコン基板1に注入する。

(イオン注入条件)

不純物:砒素(As)

注入エネルギー:12〜20KeV

ドーズ量:3×1014〜3×1016atoms/cm2。

【0032】

この際に、注入するドーズ量は先に形成したN型LDD11に注入したドーズ量よりも多くなるように設定する。以上のイオン注入で、P型ウェル3中に高濃度のN型拡散領域13が、N型LDD11よりも深い位置に形成される。N型拡散領域13は、トランジスタのソース・ドレイン領域として機能する。これにより、第1の領域Aに第1のトランジスタTr1、第2の領域Bに第2のトランジスタTr2が完成する。

【0033】

図16に示すように、NMOS10を埋め込むように、CVD法によるシリコン酸化膜である層間絶縁膜14を形成し、CMP法によってNMOS10aと10bの絶縁膜9が露出するまで平坦化する。引き続き、CVD法による150〜200nm厚のシリコン酸化膜である層間絶縁膜15を成膜する。次に、フォトリソグラフィとドライエッチングにより、N型拡散領域13の上面の一部が露出するように、層間絶縁膜14と層間絶縁膜15を貫通するコンタクトホール(図示せず)を形成する。次に、コンタクトホールを埋め込むように、CVD法によるタングステン等の導電膜を形成し、CMPによって層間絶縁膜15上に堆積された導電膜を除去して、コンタクトプラグ16を形成する。ゲート電極を構成する導電膜8に接続するコンタクトプラグ(図示せず)も同様にして形成する。

【0034】

図17に示すように、コンタクトプラグ16に接続する配線17を、スパッタ法によるアルミニウム(Al)、銅(Cu)、タングステン(W)等の金属を用いて形成する。配線17を覆う保護膜18をCVD法によるシリコン酸窒化(SiON)等を用いて形成すれば、半導体装置が完成する。

【0035】

保護膜18を形成する前に、さらに別の配線層を形成した多層配線構造としてもよい。また、DRAM等の記憶装置を形成するために、メモリセル領域を構成するトランジスタや記憶素子を有するようにしてもよい。

【0036】

本実施形態では、マルチオキサイドの形成時における第2の領域Bのゲート絶縁膜除去をケミカルエッチングで行い、その後、ケミカルエッチで生じた被覆膜の除去とともにフォトレジストパターンの焼き締め処理を行っている。このため、第1の領域Aにおけるゲート絶縁膜上に焼き締め処理によって隙間が生じても、エッチングガスが侵入することがなく、ゲート絶縁膜の過剰エッチングを防止できる。従って、第1の領域Aにおけるゲート絶縁膜の領域確保が容易となり、半導体装置の不良を低減することができる。さらに、焼き締め処理は、被覆膜の除去と同じ処理装置で行えるので、スループットが向上して、製造コストの低減も図ることができる。なお、膜厚の数値や処理条件は一例であって、変更が可能である。

【0037】

以上、本発明の好ましい実施形態について説明したが、本発明は、上記の実施形態に限定されることなく、本発明の主旨を逸脱しない範囲で種々の変更が可能であり、それらも本発明の範囲内に包含されるものであることはいうまでもない。

【符号の説明】

【0038】

1 シリコン基板

2 素子分離領域

3 P型ウェル

4、4a、4b、4A、4C、4D ゲート絶縁膜

5 フォトレジスト

6 被覆膜

7、7A、8 導電膜

9 絶縁膜

10、10a、10b NMOS

11 N型LDD

12 サイドウォール

13 N型拡散領域

14、15 層間絶縁膜

16 コンタクトプラグ

17 配線

18 保護膜

A 第1の領域

B 第2の領域

C、D 領域

Tr1 第1のトランジスタ

Tr2 第2のトランジスタ

X1 除去量

X2 水平距離

Z1 ゲート絶縁膜4Aの厚さ

Z2、Z3 隙間

【特許請求の範囲】

【請求項1】

半導体基板の第1及び第2の領域上に、第1の膜を形成する工程と、

前記第1の膜上にフォトレジストパターンを形成する工程と、

前記フォトレジストパターンをマスクに用いた第1の膜のエッチングにより前記第2の領域上の第1の膜を除去すると共に、前記第2の領域上を覆うように被覆膜を形成する工程と、

前記半導体基板に熱処理を行うことにより、前記被覆膜を除去すると共に前記フォトレジストパターンの焼き締め処理を行う工程と、

前記フォトレジストパターンを除去する工程と、

を有する半導体装置の製造方法。

【請求項2】

前記第1の膜は、シリコン酸化膜である、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記被覆膜を形成する工程では、

アンモニア、フッ化水素、及びフッ化窒素を含有するガスを用いた前記エッチングにより、ケイフッ化アンモニウム((NH4)2SiF6)を含む前記被覆膜を形成する、請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記焼き締め処理を行う工程では、

前記熱処理として、窒素及び水素を含有する雰囲気中で前記半導体基板を80〜500℃に加熱する、請求項1〜3の何れか1項に記載の半導体装置の製造方法。

【請求項5】

前記被覆膜を形成する工程では、

前記エッチングとして等方性エッチングを行う、請求項1〜4の何れか1項に記載の半導体装置の製造方法。

【請求項6】

前記第1の膜を形成する工程では、

厚さが35nm未満の第1の膜を形成する、請求項1〜5の何れか1項に記載の半導体装置の製造方法。

【請求項7】

前記被覆膜を形成する工程と、前記焼き締め処理を行う工程は、同一の装置内の異なるチャンバー内で行われる、請求項1〜6の何れか1項に記載の半導体装置の製造方法。

【請求項8】

前記第1の膜を形成する工程では、

前記第1の膜として第1の絶縁膜を形成し、

更に、

前記第1の領域の第1の絶縁膜上に導電膜を形成する工程と、

前記第1の絶縁膜及び導電膜を加工してそれぞれ、ゲート絶縁膜及びゲート電極を形成する工程と、

前記半導体基板の第1の領域内にソース及びドレイン領域を形成する工程と、

を有する、請求項1〜7の何れか1項に記載の半導体装置の製造方法。

【請求項9】

前記第1の膜を形成する工程と、前記導電膜を形成する工程の間に更に、

前記第1及び第2の領域上に、第2の絶縁膜を形成する工程を有し、

前記ゲート絶縁膜及びゲート電極を形成する工程では、

第1及び第2の絶縁膜並びに導電膜を加工して、前記第1及び第2の領域上の各々に、第1及び第2の絶縁膜を有するゲート絶縁膜並びにゲート電極を形成し、

前記ソース及びドレイン領域を形成する工程では、

前記半導体基板の第2の領域内にもソース及びドレイン領域を形成する、請求項8に記載の半導体装置の製造方法。

【請求項10】

前記第2の絶縁膜を形成する工程では、

前記第2の絶縁膜として、シリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜、及び高誘電率絶縁膜からなる群から選択された少なくとも一種の膜を形成する、請求項9に記載の半導体装置の製造方法。

【請求項11】

半導体基板の第1及び第2の領域上に、第1の絶縁膜を形成する工程と、

前記第1の絶縁膜上にフォトレジストパターンを形成する工程と、

前記フォトレジストパターンをマスクに用いた第1の絶縁膜のエッチングにより、前記第2の領域上の第1の絶縁膜を除去すると共に前記半導体基板の第2の領域上に被覆膜を形成する工程と、

前記半導体基板に熱処理を行うことにより、前記被覆膜を除去すると共に前記フォトレジストパターンに焼き締め処理を行う工程と、

前記フォトレジストパターンを除去する工程と、

前記第1及び第2の領域上に、第2の絶縁膜及び導電膜をこの順に形成する工程と、

前記第1及び第2の絶縁膜並びに導電膜を加工して、前記第1及び第2の領域上の各々に、前記第1及び第2の絶縁膜を有するゲート絶縁膜並びにゲート電極を形成する工程と、

前記半導体基板の第1及び第2の領域内の各々にソース及びドレイン領域を形成する工程と、

を有する半導体装置の製造方法。

【請求項12】

第1の領域と第2の領域とを有する半導体基板と、

前記第1の領域に設けられた第1のトランジスタと、

前記第2の領域に設けられた第2のトランジスタと、

を有し、

前記第1のトランジスタのゲート絶縁膜は、前記第2のトランジスタのゲート絶縁膜よりも膜厚が厚い、半導体装置。

【請求項13】

前記第1のトランジスタのゲート絶縁膜のうち少なくともゲート電極に接する部分と、前記第2のトランジスタのゲート絶縁膜は同じ材料からなる、請求項12に記載の半導体装置。

【請求項14】

前記第1のトランジスタのゲート絶縁膜のうち前記半導体基板に接する部分はシリコン酸化膜である、請求項12又は13に記載の半導体装置。

【請求項1】

半導体基板の第1及び第2の領域上に、第1の膜を形成する工程と、

前記第1の膜上にフォトレジストパターンを形成する工程と、

前記フォトレジストパターンをマスクに用いた第1の膜のエッチングにより前記第2の領域上の第1の膜を除去すると共に、前記第2の領域上を覆うように被覆膜を形成する工程と、

前記半導体基板に熱処理を行うことにより、前記被覆膜を除去すると共に前記フォトレジストパターンの焼き締め処理を行う工程と、

前記フォトレジストパターンを除去する工程と、

を有する半導体装置の製造方法。

【請求項2】

前記第1の膜は、シリコン酸化膜である、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記被覆膜を形成する工程では、

アンモニア、フッ化水素、及びフッ化窒素を含有するガスを用いた前記エッチングにより、ケイフッ化アンモニウム((NH4)2SiF6)を含む前記被覆膜を形成する、請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記焼き締め処理を行う工程では、

前記熱処理として、窒素及び水素を含有する雰囲気中で前記半導体基板を80〜500℃に加熱する、請求項1〜3の何れか1項に記載の半導体装置の製造方法。

【請求項5】

前記被覆膜を形成する工程では、

前記エッチングとして等方性エッチングを行う、請求項1〜4の何れか1項に記載の半導体装置の製造方法。

【請求項6】

前記第1の膜を形成する工程では、

厚さが35nm未満の第1の膜を形成する、請求項1〜5の何れか1項に記載の半導体装置の製造方法。

【請求項7】

前記被覆膜を形成する工程と、前記焼き締め処理を行う工程は、同一の装置内の異なるチャンバー内で行われる、請求項1〜6の何れか1項に記載の半導体装置の製造方法。

【請求項8】

前記第1の膜を形成する工程では、

前記第1の膜として第1の絶縁膜を形成し、

更に、

前記第1の領域の第1の絶縁膜上に導電膜を形成する工程と、

前記第1の絶縁膜及び導電膜を加工してそれぞれ、ゲート絶縁膜及びゲート電極を形成する工程と、

前記半導体基板の第1の領域内にソース及びドレイン領域を形成する工程と、

を有する、請求項1〜7の何れか1項に記載の半導体装置の製造方法。

【請求項9】

前記第1の膜を形成する工程と、前記導電膜を形成する工程の間に更に、

前記第1及び第2の領域上に、第2の絶縁膜を形成する工程を有し、

前記ゲート絶縁膜及びゲート電極を形成する工程では、

第1及び第2の絶縁膜並びに導電膜を加工して、前記第1及び第2の領域上の各々に、第1及び第2の絶縁膜を有するゲート絶縁膜並びにゲート電極を形成し、

前記ソース及びドレイン領域を形成する工程では、

前記半導体基板の第2の領域内にもソース及びドレイン領域を形成する、請求項8に記載の半導体装置の製造方法。

【請求項10】

前記第2の絶縁膜を形成する工程では、

前記第2の絶縁膜として、シリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜、及び高誘電率絶縁膜からなる群から選択された少なくとも一種の膜を形成する、請求項9に記載の半導体装置の製造方法。

【請求項11】

半導体基板の第1及び第2の領域上に、第1の絶縁膜を形成する工程と、

前記第1の絶縁膜上にフォトレジストパターンを形成する工程と、

前記フォトレジストパターンをマスクに用いた第1の絶縁膜のエッチングにより、前記第2の領域上の第1の絶縁膜を除去すると共に前記半導体基板の第2の領域上に被覆膜を形成する工程と、

前記半導体基板に熱処理を行うことにより、前記被覆膜を除去すると共に前記フォトレジストパターンに焼き締め処理を行う工程と、

前記フォトレジストパターンを除去する工程と、

前記第1及び第2の領域上に、第2の絶縁膜及び導電膜をこの順に形成する工程と、

前記第1及び第2の絶縁膜並びに導電膜を加工して、前記第1及び第2の領域上の各々に、前記第1及び第2の絶縁膜を有するゲート絶縁膜並びにゲート電極を形成する工程と、

前記半導体基板の第1及び第2の領域内の各々にソース及びドレイン領域を形成する工程と、

を有する半導体装置の製造方法。

【請求項12】

第1の領域と第2の領域とを有する半導体基板と、

前記第1の領域に設けられた第1のトランジスタと、

前記第2の領域に設けられた第2のトランジスタと、

を有し、

前記第1のトランジスタのゲート絶縁膜は、前記第2のトランジスタのゲート絶縁膜よりも膜厚が厚い、半導体装置。

【請求項13】

前記第1のトランジスタのゲート絶縁膜のうち少なくともゲート電極に接する部分と、前記第2のトランジスタのゲート絶縁膜は同じ材料からなる、請求項12に記載の半導体装置。

【請求項14】

前記第1のトランジスタのゲート絶縁膜のうち前記半導体基板に接する部分はシリコン酸化膜である、請求項12又は13に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−110311(P2013−110311A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−255181(P2011−255181)

【出願日】平成23年11月22日(2011.11.22)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月22日(2011.11.22)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]