半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

【発明の詳細な説明】

【技術分野】

【0001】

実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、半導体基板上にフィン型の複数の半導体層(活性領域)を積み重ねた3次元構造の半導体装置が研究されている。

【0003】

例えば、半導体基板上の各半導体層を、メモリセル(セルトランジスタ)のチャネルとして用いれば、VLB (Vertical gate ladder-Bit cost scalable memory)と呼ばれる垂直ゲート型3次元不揮発性メモリを構成できる。また、半導体基板上の各半導体層を、メモリセル(抵抗変化素子)に接続される導電線として用いれば、クロスポイント型の3次元不揮発性メモリを構成できる。

【0004】

また、これら不揮発性メモリに代表される3次元構造の半導体装置を動作させるためには、半導体基板上の複数の半導体層のうちの1つに選択的にアクセスするための機構が必要である。その機構の一つとして、複数の半導体層(チャネル)に共通のゲート電極を持ち、複数の半導体層のうちの1つでノーマリーオン、残りの半導体層でオン/オフ制御可能なレイヤー選択トランジスタを設ける技術が知られている。

【0005】

しかし、レイヤー選択トランジスタにより複数の半導体層のうちの1つを選択するときは、積み重ねる半導体層の数と同じ数のゲート電極を並べて配置することが必要である。この場合、ウェハープロセス中の熱処理により、レイヤー選択トランジスタをノーマリーオンとするために各半導体層内に注入された不純物が不用意に拡散し、本来オン/オフ制御しなければならない部分でノーマリーオンとなってしまう、などの選択動作に支障をきたす問題が発生する。

【0006】

この問題は、デザインルールが縮小され、並べて配置された複数のゲート電極のピッチが小さくなるほど深刻となる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】米国特許第7,352,018号

【特許文献2】米国特許公開第2008/259687号

【特許文献3】特開2006−155750号公報

【非特許文献】

【0008】

【非特許文献1】W. Kim et al., 2009 Symp. on VLSI p188

【発明の概要】

【発明が解決しようとする課題】

【0009】

実施形態は、デザインルールが縮小されても、半導体基板上に積み重ねられた複数の半導体層のうちの1つを正確に選択するための技術を提案する。

【課題を解決するための手段】

【0010】

実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上の絶縁層と、前記絶縁層の表面に垂直な第1の方向に、前記絶縁層の表面から順番に積み重ねられ、前記絶縁層の表面に平行な第2の方向に延び、互いに絶縁される第1乃至第nの半導体層(nは2以上の自然数)と、前記第2の方向の一端において前記第1乃至第nの半導体層に接続される共通電極と、前記第1乃至第nの半導体層をチャネルとし、前記第1乃至第nの半導体層のうちの1つを選択するレイヤー選択トランジスタとを備え、前記レイヤー選択トランジスタは、前記第2の方向に、前記第2の方向の一端から順番に配置され、前記第1乃至第nの半導体層の前記第1及び第2の方向に垂直な第3の方向にある側面に沿って前記第1の方向に延びる第1乃至第mのゲート電極(m=n+k、kは偶数)と、前記第iの半導体層(iは1〜nのうちの1つ)内において前記第i乃至第(i+k)のゲート電極に隣接するチャネルを、前記第i乃至第(i+k)のゲート電極の電位に依存しないノーマリーオンチャネルにする第iのノーマリーオン領域とを備える。

【0011】

実施形態によれば、前記半導体装置の製造方法は、前記第iのノーマリーオン領域を、不純物の注入により前記第iの半導体層内の前記第(i+(k/2))のゲート電極に隣接するチャネルのみに形成する工程と、前記第iのノーマリーオン領域を形成した後の前記不純物の拡散により、前記第iのノーマリーオン領域が、前記第2の方向に前記第1乃至第mのゲート電極のピッチのj倍(jは自然数)以上、(j+1)倍未満伸張するとき、k=j×2に設定する工程とを備える。

【図面の簡単な説明】

【0012】

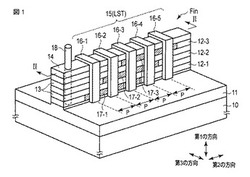

【図1】第1の実施例に係わる半導体装置を示す斜視図。

【図2】図1のII−II線に沿う断面図。

【図3】比較例を示す断面図。

【図4】比較例を示す断面図。

【図5】積層数と大きさとの関係を示す図。

【図6】積層数と大きさとの関係を示す図。

【図7】図1の半導体装置の製造方法を示す斜視図。

【図8】図1の半導体装置の製造方法を示す斜視図。

【図9】図1の半導体装置の製造方法を示す斜視図。

【図10】図1の半導体装置の製造方法を示す斜視図。

【図11】図1の半導体装置の製造方法を示す斜視図。

【図12】第1の実施例の第1の変形例を示す斜視図。

【図13】図12のXIII−XIII線に沿う断面図。

【図14】第1の実施例の第2の変形例を示す斜視図。

【図15】図14のXV−XV線に沿う断面図。

【図16】第2の実施例に係わる半導体装置を示す斜視図。

【図17】図16のXVII−XVII線に沿う断面図。

【図18】第3の実施例に係わる半導体装置を示す斜視図。

【図19】図18のXIX−XIX線に沿う断面図。

【図20】積層数と大きさとの関係を示す図。

【図21】図18の半導体装置の製造方法を示す斜視図。

【図22】図18の半導体装置の製造方法を示す斜視図。

【図23】図18の半導体装置の製造方法を示す斜視図。

【図24】図18の半導体装置の製造方法を示す斜視図。

【図25】図18の半導体装置の製造方法を示す斜視図。

【図26】図18の半導体装置の製造方法を示す斜視図。

【図27】図18の半導体装置の製造方法を示す斜視図。

【図28】図18の半導体装置の製造方法を示す斜視図。

【図29】第3の実施例の第1の変形例を示す斜視図。

【図30】図29のXXX−XXX線に沿う断面図。

【図31】第3の実施例の第2の変形例を示す斜視図。

【図32】図31のXXXII−XXXII線に沿う断面図。

【図33】第4の実施例に係わる半導体装置を示す斜視図。

【図34】図33のXXXIV−XXXIV線に沿う断面図。

【図35】適用例に係わる不揮発性半導体メモリを示す斜視図。

【図36】図35のXXXVI−XXXVI線に沿う断面図。

【図37】図35のメモリのメモリセルを示す斜視図。

【図38】適用例に係わる不揮発性半導体メモリを示す斜視図。

【図39】図38のメモリのメモリセルアレイを示す斜視図。

【図40】図39のアレイのA−A’線及びB−B’線に沿う断面図。

【発明を実施するための形態】

【0013】

以下、図面を参照しながら実施形態を説明する。尚、実施形態を通して共通の構成には同一の符号を付すものとし、重複する説明は省略する。また、各図は発明の説明とその理解を促すための模式図であり、その形状や寸法、比などは実際の装置と異なる個所があるが、これらは以下の説明と公知の技術を参酌して適宜、設計変更することができる。

【0014】

実施形態に係わる半導体装置は、ウェハープロセス中に発生する熱処理により、レイヤー選択トランジスタのノーマリーオン領域がチャネル長方向に伸張することを想定し、半導体基板上に積み重ねられる半導体層の数よりも多い数のゲート電極を有するレイヤー選択トランジスタを用いて、半導体層の選択を行うことに特徴を有する。

【0015】

また、単にレイヤー選択トランジスタのゲート電極の数を増やすのではなく、ノーマリーオン領域の伸張量(不純物の拡散長)とレイヤー選択トランジスタのゲート電極の数との関係を規定することにより、ゲート電極の増加数を必要最小限に抑え、レイヤー選択トランジスタの面積の増大を防止する。

【0016】

例えば、第1乃至第nの半導体層(nは2以上の自然数)内の第1乃至第nのノーマリーオン領域が両側に伸張するとき、レイヤー選択トランジスタは、第1乃至第mのゲート電極(m=n+k、kは偶数)を備える。この時、第iの半導体層(iは1〜nのうちの1つ)内の第iのノーマリーオン領域は、第i乃至第(i+k)のゲート電極に隣接するチャネルをノーマリーオンチャネルにする(第1及び第2の実施例に相当)。

【0017】

ここで、kは、ノーマリーオン領域の片側の伸張量(不純物の拡散長)により決定される値である。即ち、熱処理などにより、第iの半導体層内の第(i+(k/2))のゲート電極に隣接するチャネルに形成された第iのノーマリーオン領域が、第1乃至第mのゲート電極のピッチのj倍(jは自然数)以上、(j+1)倍未満伸張するとき、kはj×2に設定される。

【0018】

但し、ノーマリーオン領域のチャネル長方向の初期サイズ(不純物の拡散前のノーマリーオン領域の端の位置)は、ゲート電極のチャネル長(ゲート電極のチャネル長方向の端の位置)に一致すると仮定する。

【0019】

また、第1乃至第nの半導体層(nは2以上の自然数)内の第1乃至第nのノーマリーオン領域が片側のみに伸張するとき、レイヤー選択トランジスタは、第1乃至第mのゲート電極(m=n+k、kは自然数)を備える。この時、第iの半導体層(iは1〜nのうちの1つ)内の第iのノーマリーオン領域は、第i乃至第(i+k)のゲート電極に隣接するチャネルをノーマリーオンチャネルにする(第3及び第4の実施例に相当)。

【0020】

そして、熱処理などにより、第iの半導体層内の第iのゲート電極に隣接するチャネルに形成された第iのノーマリーオン領域が、第1乃至第mのゲート電極のピッチのj倍(jは自然数)以上、(j+1)倍未満伸張するとき、kはjに設定される。

【0021】

但し、ノーマリーオン領域のチャネル長方向の初期サイズ(不純物の拡散前のノーマリーオン領域の端の位置)は、ゲート電極のチャネル長(ゲート電極のチャネル長方向の端の位置)に一致すると仮定する。

【0022】

以上のように、半導体基板上に積み重ねられる半導体層の数よりも多い数のゲート電極を有するレイヤー選択トランジスタを用いて半導体層の選択を行うことにより、レイヤー選択トランジスタのノーマリーオン領域がチャネル長方向に伸張したとしても、半導体層の選択を正確に行うことができる。

【0023】

[第1の実施例]

図1は、第1の実施例に係わる半導体装置を示している。図2は、図1のII−II線に沿う断面図である。

【0024】

第1の実施例は、半導体層の積層数nが3、ノーマリーオン領域の片側の伸張量jが1(k=j×2=2)、ゲート電極の数m(=n+k)が5の例である。

【0025】

半導体基板10は、例えば、シリコン基板である。絶縁層11は、半導体基板10上に配置される。第1、第2及び第3の半導体層12−1,12−2,12−3は、絶縁層11の表面に垂直な第1の方向に、絶縁層11の表面から順番に互いに絶縁されて積み重ねられ、かつ、絶縁層11の表面に平行な第2の方向に延びる。

【0026】

本例では、第1、第2及び第3の半導体層12−1,12−2,12−3は、絶縁層13により互いに絶縁される。絶縁層14は、最上層としての第3の半導体層12−3上に配置される。絶縁層13,14は、例えば、酸化シリコン層である。絶縁層14は、酸化シリコン層以外に、窒化シリコン層や、酸化シリコン層と窒化シリコン層の積層などとすることも可能である。

【0027】

第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層13,14は、フィン型積層構造Finを構成する。第1、第2及び第3の半導体層12−1,12−2,12−3は、単結晶状態であるのが望ましいが、多結晶状態、アモルファス状態であっても構わない。

【0028】

フィン型積層構造Finの第2の方向の一端において、共通電極18は、第1、第2及び第3の半導体層12−1,12−2,12−3に共通に接続される。共通電極18は、例えば、タングステン、アルミニウムなどの金属層を備える。

【0029】

レイヤー選択トランジスタ15(LST)は、例えば、FET (Field Effect Transistor)であり、第1、第2及び第3の半導体層12−1,12−2,12−3をチャネルとし、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択する。

【0030】

レイヤー選択トランジスタ15(LST)は、第2の方向に、共通電極18側から順番に一定ピッチPで配置される第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5を有する。

【0031】

第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5は、例えば、導電性ポリシリコン層、ニッケルシリサイド層などの金属シリサイド層、又は、これらの積層を備える。

【0032】

第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5は、少なくとも、第1、第2及び第3の半導体層12−1,12−2,12−3の第1及び第2の方向に垂直な第3の方向にある側面に沿って第1の方向に延びる。

【0033】

本例では、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5は、フィン型積層構造Finの第1の方向にある上面及び第2の方向にある2つの側面を覆う。即ち、レイヤー選択トランジスタ15(LST)は、ダブルゲート構造を有するフィン型FETである。

【0034】

また、レイヤー選択トランジスタ15(LST)は、第1、第2及び第3の半導体層12−1,12−2,12−3内に、それぞれ、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を有する。

【0035】

第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3は、n型不純物(砒素、リンなどの5価元素)、p型不純物(硼素、インジウムなどの3価元素)、又は、それらの両方を含む不純物領域である。

【0036】

第1の半導体層12−1内に存在する第1のノーマリーオン領域17−1は、第1、第2及び第3のゲート電極16−1,16−2,16−3に隣接するチャネルを、それぞれ、第1、第2及び第3のゲート電極16−1,16−2,16−3の電位に依存しないノーマリーオンチャネルにする。

【0037】

第2の半導体層12−2内に存在する第2のノーマリーオン領域17−2は、第2、第3及び第4のゲート電極16−2,16−3,16−4に隣接するチャネルを、それぞれ、第2、第3及び第4のゲート電極16−2,16−3,16−4の電位に依存しないノーマリーオンチャネルにする。

【0038】

第3の半導体層12−3内に存在する第3のノーマリーオン領域17−3は、第3、第4及び第5のゲート電極16−3,16−4,16−5に隣接するチャネルを、それぞれ、第3、第4及び第5のゲート電極16−3,16−4,16−5の電位に依存しないノーマリーオンチャネルにする。

【0039】

尚、本例では、レイヤー選択トランジスタ15(LST)をFETとする場合について説明したが、これ以外のスイッチ素子をレイヤー選択トランジスタとして用いることもできる。即ち、レイヤー選択トランジスタ15(LST)は、スイッチ機能を有していればよい。

【0040】

また、本例では、第1、第2及び第3の半導体層12−1,12−2,12−3内に第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3のみが形成される例を示しているが、それに加えて、第1、第2及び第3の半導体層12−1,12−2,12−3内には、レイヤー選択トランジスタ15(LST)の閾値を制御するための不純物領域を設けてもよい。

【0041】

表1は、図1の半導体装置における半導体層の選択動作を示している。

【0042】

【表1】

【0043】

図1の半導体装置によれば、第1のゲート電極16−1に係わるレイヤー選択トランジスタ15(LST)は、最下層としての第1の半導体層12−1において常にオン状態(ノーマリーオン状態)であり、それ以外の第2及び第3の半導体層12−2,12−3においてスイッチ素子として機能する。

【0044】

第2のゲート電極16−2に係わるレイヤー選択トランジスタ15(LST)は、最下層としての第1の半導体層12−1及び中間層としての第2の半導体層12−2において常にオン状態(ノーマリーオン状態)であり、それ以外の第3の半導体層12−3においてスイッチ素子として機能する。

【0045】

第3のゲート電極16−3に係わるレイヤー選択トランジスタ15(LST)は、第1、第2及び第3の半導体層12−1,12−2,12−3の全てにおいて常にオン状態(ノーマリーオン状態)である。

【0046】

第4のゲート電極16−4に係わるレイヤー選択トランジスタ15(LST)は、中間層としての第2の半導体層12−2及び最上層としての第3の半導体層12−3において常にオン状態(ノーマリーオン状態)であり、それ以外の第1の半導体層12−1においてスイッチ素子として機能する。

【0047】

第5のゲート電極16−5に係わるレイヤー選択トランジスタ15(LST)は、最上層としての第3の半導体層12−3において常にオン状態(ノーマリーオン状態)であり、それ以外の第1及び第2の半導体層12−1,12−2においてスイッチ素子として機能する。

【0048】

従って、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5の電位を、表1に示す関係に設定することにより、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択することができる。

【0049】

尚、表1において、“H”は、レイヤー選択トランジスタ15(LST)のチャネルをオンチャネル(オン状態)にし得るオン電位のことであり、“L”は、レイヤー選択トランジスタ15(LST)のチャネルをオフチャネル(オフ状態)にし得るオフ電位のことである。

【0050】

例えば、レイヤー選択トランジスタ15(LST)がnチャネルFETのときは、“H”は正電位であり、“L”は接地電位である。また、レイヤー選択トランジスタ15(LST)がpチャネルFETのときは、“H”は負電位であり、“L”は接地電位である。

【0051】

第1の半導体層12−1を選択するときは、第1、第2及び第3のゲート電極16−1,16−2,16−3の電位を“L”に設定し、第4及び第5のゲート電極16−4,16−5の電位を“H”に設定する。

【0052】

この時、第1のゲート電極16−1に係わるレイヤー選択トランジスタ15(LST)は、第2及び第3の半導体層12−2,12−3においてオフ状態であり、第2のゲート電極16−2に係わるレイヤー選択トランジスタ15(LST)は、第3の半導体層12−3においてオフ状態であるため、第2及び第3の半導体層12−2,12−3は選択されない。これに対し、第1の半導体層12−1では、第1のノーマリーオン領域17−1が存在するため、第1乃至第5のゲート電極16−1〜16−5に隣接する全てのチャネルがオン状態になる。

【0053】

従って、第1の半導体層12−1が選択される。

【0054】

第2の半導体層12−2を選択するときは、第2、第3及び第4のゲート電極16−2,16−3,16−4の電位を“L”に設定し、第1及び第5のゲート電極16−1,16−5の電位を“H”に設定する。

【0055】

この時、第2のゲート電極16−2に係わるレイヤー選択トランジスタ15(LST)は、第3の半導体層12−3においてオフ状態であり、第4のゲート電極16−4に係わるレイヤー選択トランジスタ15(LST)は、第1の半導体層12−1においてオフ状態であるため、第1及び第3の半導体層12−1,12−3は選択されない。これに対し、第2の半導体層12−2では、第2のノーマリーオン領域17−2が存在するため、第1乃至第5のゲート電極16−1〜16−5に隣接する全てのチャネルがオン状態になる。

【0056】

従って、第2の半導体層12−2が選択される。

【0057】

第3の半導体層12−3を選択するときは、第3、第4及び第5のゲート電極16−3,16−4,16−5の電位を“L”に設定し、第1及び第2のゲート電極16−1,16−2の電位を“H”に設定する。

【0058】

この時、第4のゲート電極16−4に係わるレイヤー選択トランジスタ15(LST)は、第1の半導体層12−1においてオフ状態であり、第5のゲート電極16−5に係わるレイヤー選択トランジスタ15(LST)は、第1及び第2の半導体層12−1,12−2においてオフ状態であるため、第1及び第2の半導体層12−1,12−2は選択されない。これに対し、第3の半導体層12−3では、第3のノーマリーオン領域17−3が存在するため、第1乃至第5のゲート電極16−1〜16−5に隣接する全てのチャネルがオン状態になる。

【0059】

従って、第3の半導体層12−3が選択される。

【0060】

尚、上述の選択動作から明らかなように、第3のゲート電極16−3に係わるレイヤー選択トランジスタ15(LST)は、第1、第2及び第3の半導体層12−1,12−2,12−3の全てにおいてノーマリーオン状態である。

【0061】

そこで、表2に示すように、上述の選択動作において、第3のゲート電極16−3は、常に固定電位(“H”又は“L”)に設定しておいてもよいし、フローティング状態に設定しておいてもよい。

【0062】

【表2】

【0063】

また、上述の選択動作により、第1、第2及び第3の半導体層12−1,12−2,12−3に対しては、それらに共通に接続される共通電極18を設ければよい。即ち、第1、第2及び第3の半導体層12−1,12−2,12−3の各々に対して、個別に電極を設ける必要がないため、コンタクト領域のサイズを縮小可能である。

【0064】

図3及び図4は、比較例を示している。

【0065】

この比較例は、積層される半導体層の数とレイヤー選択トランジスタのゲート電極の数とが等しい場合の例である。

【0066】

図3は、理想的状態である。しかし、ウェハープロセスにおいて、ベーク処理、キュア処理、デンシファイ処理などの高温熱処理が必要となった場合、その高温熱処理に起因して、ノーマリーオン領域を形成する不純物の拡散が発生する。

【0067】

例えば、実験データによれば、半導体層として多結晶シリコン層を用い、ノーマリーオン領域を砒素(As)の添加により形成した場合、1000℃、10秒の熱処理で、砒素は多結晶シリコン層内を約70nm拡散する。また、1000℃、20秒の熱処理で、砒素は多結晶シリコン層内を160nm程度拡する。

【0068】

従って、例えば、レイヤー選択トランジスタのゲート電極のピッチが160nm以下になると、1000℃、20秒の熱処理で、ノーマリーオン領域17−1〜17−3は、図3の状態から図4の状態に変化する。

【0069】

図4の状態になると、半導体層12−2において、ノーマリーオン領域17−2は、全てのゲート電極16−1〜16−3に跨るため、半導体層12−2は、常に選択された状態になる。即ち、半導体層12−2を非選択にすることが不可能であるため、レイヤー選択トランジスタ15(LST)による選択機能が失われる。

【0070】

これに対し、第1の実施例では、比較例と同じ条件によりノーマリーオン領域が伸張したとしても、図2の状態となるため、レイヤー選択トランジスタ15(LST)による選択機能が失われることはない。

【0071】

図5は、半導体層の積層数とレイヤー選択トランジスタの大きさとの関係を示している。

【0072】

本例では、半導体層の積層数nは、3である。

【0073】

同図(a)は、図1に示す第1の実施例に相当する。第1の実施例の場合、レイヤー選択トランジスタ15(LST)の第2の方向の大きさは、P×4である。但し、Pは、ゲート電極16−1〜16−5のピッチである。

【0074】

尚、レイヤー選択トランジスタ15(LST)の第2の方向の大きさとは、レイヤー選択トランジスタの複数のゲート電極の第2の方向の一端にあるゲート電極の中心から第2の方向の他端にあるゲート電極の中心までのサイズのことである。

【0075】

同図(b)は、図4の比較例に対応する。但し、同図(b)は、図4の半導体装置において半導体層の選択機能を有効にするため、図4のゲート電極16−1〜16−3のピッチを2倍(P×2)に広げている。

【0076】

比較例の場合も、第1の実施例と同様に、レイヤー選択トランジスタ15(LST)の第2の方向の大きさは、P×4である。

【0077】

このように、半導体層の積層数nが3の場合、第1の実施例に係わるレイヤー選択トランジスタ15(LST)の第2方向の大きさは、比較例に係わるレイヤー選択トランジスタ15(LST)の第2方向の大きさと等しくなる。

【0078】

また、第1の実施例では、半導体層の積層数nが4以上になると、レイヤー選択トランジスタの第2方向の大きさが、比較例に係わるレイヤー選択トランジスタの第2方向の大きさよりも小さくなる、という効果を発揮する。この効果は、半導体層の積層数nが増加するほど大きくなるため、第1の実施例は、積層数をできるだけ多くしたい、という要望があるときに非常に有効な技術となる。

【0079】

半導体層の積層数とレイヤー選択トランジスタの大きさとの関係を一般化すると、以下のようになる。

【0080】

第1の実施例(図5(a))では、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n+k−1)となる。また、第1の実施例では、k=2であるから、レイヤー選択トランジスタの第2方向の大きさは、P×(n+1)となる。これに対し、比較例(図5(b))では、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n−1)×2となる。

【0081】

例えば、積層数nが2のとき、第1の実施例での大きさは、P×3、比較例での大きさは、P×2であり、第1の実施例のレイヤー選択トランジスタは、比較例のレイヤー選択トランジスタよりも大きい。

【0082】

しかし、積層数nが4のとき、第1の実施例での大きさは、P×5、比較例での大きさは、P×6であり、積層数nが5のとき、第1の実施例での大きさは、P×6、比較例での大きさは、P×8であり、積層数nが6のとき、第1の実施例での大きさは、P×7、比較例での大きさは、P×10である。

【0083】

尚、図6は、半導体層の積層数nが6の場合において、第1の実施例(同図(a))でのレイヤー選択トランジスタ15(LST)の大きさ(P×7)と、比較例(同図(b))でのレイヤー選択トランジスタ15(LST)の大きさ(P×10)とを、比較して示している。

【0084】

以上のように、積層数nが4以上になると、第1の実施例のレイヤー選択トランジスタは、比較例のレイヤー選択トランジスタよりも小さくなり、かつ、積層数nが大きくなるほど、その差も大きくなる。

【0085】

図7乃至図11は、図1の半導体装置の製造方法を示している。

【0086】

まず、図7に示すように、半導体基板10として、例えば、面方位(100)、比抵抗10〜20Ωcmのp型シリコン基板を用意する。この半導体基板10上に、絶縁層11,13,14としての酸化シリコン層と、第1、第2及び第3の半導体層12−1,12−2,12−3としての多結晶シリコン層とを、交互に形成する。

【0087】

次に、図8に示すように、例えば、PEP(Photo Engraving Process)とイオン注入を用いて、第1、第2及び第3の半導体層12−1,12−2,12−3内に、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を形成する。各ノーマリーオン領域17−1,17−2,17−3は、別々に形成される。また、イオン注入は、所定の加速電圧で、例えば、砒素イオンを第1、第2及び第3の半導体層12−1,12−2,12−3内に注入することにより実行される。

【0088】

尚、本例では、第1、第2及び第3の半導体層12−1,12−2,12−3の全てを形成した後に、第1、第2及び第3の半導体層12−1,12−2,12−3内に、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を形成する。

【0089】

但し、これに代えて、第1の半導体層12−1を形成した直後に第1のノーマリーオン領域17−1を形成し、この後、第2の半導体層12−2を形成した直後に第2のノーマリーオン領域17−2を形成し、さらに、この後、第3の半導体層12−3を形成した直後に第3のノーマリーオン領域17−3を形成してもよい。

【0090】

次に、図9に示すように、PEPとRIE(Reactive ion etching)を用いて、絶縁層13,14及び第1、第2及び第3の半導体層12−1,12−2,12−3をパターニングすることにより、フィン型積層構造Finを形成する。

【0091】

次に、図10に示すように、絶縁層11上に、フィン型積層構造Finを覆うゲート絶縁層(例えば、酸化シリコン層)と、ゲート絶縁層上の導電層とを形成する。そして、PEPとRIEとを用いて、この導電層をパターニングにすることにより、第2の方向に一定ピッチPで並んで配置される第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5を形成する。

【0092】

また、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5は、フィン型積層構造Finの第1の方向にある上面及び第2の方向にある2つの側面をそれぞれ覆うように形成される。

【0093】

この時点において、第1のノーマリーオン領域17−1は、第2のゲート電極16−2に隣接するチャネルのみに形成され、第2のノーマリーオン領域17−2は、第3のゲート電極16−3に隣接するチャネルのみに形成され、第3のノーマリーオン領域17−3は、第4のゲート電極16−4に隣接するチャネルのみに形成される。

【0094】

尚、ゲート絶縁層及び導電層を形成した後、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5を形成する前に、CMP(Chemical Mechanical Polishing)により、導電層の上面を平坦化してもよい。

【0095】

また、フィン型積層構造Fin以外の領域を絶縁層で満たした状態でCMPを行ってもよい。この場合、CMP後に、フィン型積層構造Fin以外の領域を満たした絶縁層を除去し、さらに、その後、PEPとRIEとを用いて、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5を形成する。

【0096】

次に、図11に示すように、フィン型積層構造Finの第2の方向の一端に、第1、第2及び第3の半導体層12−1,12−2,12−3に共通に接続される共通電極18を形成する。

【0097】

また、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3は、それらを形成した後に発生する、ベーク処理、キュア処理、デンシファイ処理などの高温熱処理により、第2の方向に伸張する。

【0098】

本例では、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3は、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5のピッチPの1倍以上、2倍未満伸張する。

【0099】

但し、不純物の拡散前の第1のノーマリーオン領域17−1の第2の方向の端は、第2のゲート電極16−2の第2の方向の端に一致し、不純物の拡散前の第2のノーマリーオン領域17−2の第2の方向の端は、第3のゲート電極16−3の第2の方向の端に一致し、不純物の拡散前の第3のノーマリーオン領域17−3の第2の方向の端は、第4のゲート電極16−4の第2の方向の端に一致する、と仮定する。

【0100】

以上の工程により、図1の半導体装置が完成する。

【0101】

図12は、第1の実施例の第1の変形例を示している。図13は、図12のXIII−XIII線に沿う断面図である。

【0102】

第1の変形例の特徴は、第1の実施例と比べると、第1、第2及び第3の半導体層12−1,12−2,12−3の第3の方向にある側面のうち、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5に覆われていない領域に、第1、第2及び第3の半導体層12−1,12−2,12−3の抵抗値よりも低い抵抗値を持つ低抵抗領域19が設けられる点にある。

【0103】

その他の構成については、第1の実施例に係わる半導体装置と同じであるため、ここでの説明を省略する。

【0104】

低抵抗領域19は、例えば、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3とは異なる不純物領域である。この場合、低抵抗領域19内の不純物は、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3内の不純物と同じであっても、異なっていてもよい。

【0105】

また、低抵抗領域19は、例えば、ニッケルシリサイド層などの金属シリサイド層である。この場合、低抵抗領域19は、フィン型積層構造Finを覆う金属層を形成した後、金属層と第1、第2及び第3の半導体層12−1,12−2,12−3とをシリサイド反応させ、さらに、この後、未反応の金属層を除去することにより形成される。

【0106】

この変形例によれば、低抵抗領域19により、寄生抵抗が下がり、動作速度の向上などのメモリ特性を向上させることができる。

【0107】

図14は、第1の実施例の第2の変形例を示している。図15は、図14のXV−XV線に沿う断面図である。

【0108】

第2の変形例の特徴は、第1の実施例と比べると、第1、第2及び第3の半導体層12−1,12−2,12−3間が空洞(CAVITY)であり、かつ、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5とフィン型積層構造Finとの間が空洞(CAVITY)である点にある。

【0109】

その他の構成については、第1の実施例に係わる半導体装置と同じであるため、ここでの説明を省略する。

【0110】

空洞(CAVITY)は、例えば、第1の実施例(図1及び図2)に示す構造を形成した後、図1及び図2に示す絶縁層13,14を選択的に除去することにより形成される。この場合、第1、第2及び第3の半導体層12−1,12−2,12−3は、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5により支えられる。

【0111】

この変形例によれば、絶縁領域の空洞化により、複数の半導体層間の絶縁性を向上させることができるため、メモリ素子の信頼性が向上する。

【0112】

以上、説明したように、第1の実施例及びその変形例によれば、デザインルールが縮小されても、半導体基板上に積み重ねられた複数の半導体層のうちの1つを正確に選択することができる。

【0113】

[第2の実施例]

図16は、第2の実施例に係わる半導体装置を示している。図17は、図16のXVII−XVII線に沿う断面図である。

【0114】

第2の実施例は、半導体層の積層数nが3、ノーマリーオン領域の片側の伸張量jが2(k=j×2=4)、ゲート電極の数m(=n+k)が7の例である。

【0115】

第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3の第2の方向の伸張量は、それらを形成した後に発生する高温熱処理(ベーク処理、キュア処理、デンシファイ処理など)の温度や時間(合計値)などに依存する。

【0116】

既に説明したように、例えば、実験データによれば、半導体層として多結晶シリコン層を用い、ノーマリーオン領域を砒素(As)の添加により形成した場合、1000℃、10秒の熱処理で、砒素は多結晶シリコン層内を約70nm拡散する。また、1000℃、20秒の熱処理で、砒素は多結晶シリコン層内を160nm程度拡する。

【0117】

そこで、第2の実施例では、第1の実施例よりも、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3の伸張量が多い場合、具体的には、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3が、ゲート電極のピッチPの2倍伸張する場合について説明する。

【0118】

この場合、第1、第2、第3、第4、第5、第6及び第7のゲート電極16−1,16−2,16−3,16−4,16−5,16−6,16−7は、第2の方向に、一定ピッチPで並んで配置される。

【0119】

また、第1のノーマリーオン領域17−1は、第1の半導体層12−1内において、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5に隣接するチャネルをノーマリーオン状態にする。

【0120】

第2のノーマリーオン領域17−2は、第2の半導体層12−2内において、第2、第3、第4、第5及び第6のゲート電極16−2,16−3,16−4,16−5,16−6に隣接するチャネルをノーマリーオン状態にする。

【0121】

第3のノーマリーオン領域17−3は、第3の半導体層12−3内において、第3、第4、第5、第6及び第7のゲート電極16−3,16−4,16−5,16−6,16−7に隣接するチャネルをノーマリーオン状態にする。

【0122】

ここで、第1の実施例と同様に、半導体層の積層数とレイヤー選択トランジスタの大きさとの関係を一般化する。

【0123】

第2の実施例でも、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n+k−1)となる。また、第2の実施例では、k=4であるから、レイヤー選択トランジスタの第2方向の大きさは、P×(n+3)となる。これに対し、比較例(図5(b)と同じ構造を想定する)では、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n−1)×3となる。

【0124】

例えば、積層数nが2のとき、第2の実施例での大きさは、P×5、比較例での大きさは、P×3であり、第2の実施例のレイヤー選択トランジスタは、比較例のレイヤー選択トランジスタよりも大きい。

【0125】

また、積層数nが3のとき、第2の実施例での大きさは、P×6、比較例での大きさは、P×6であり、第2の実施例のレイヤー選択トランジスタの大きさは、比較例のレイヤー選択トランジスタの大きいと同じである。

【0126】

さらに、積層数nが4のとき、第2の実施例での大きさは、P×7、比較例での大きさは、P×9であり、積層数nが5のとき、第2の実施例での大きさは、P×8、比較例での大きさは、P×12であり、積層数nが6のとき、第2の実施例での大きさは、P×9、比較例での大きさは、P×15である。

【0127】

以上のように、積層数nが4以上になると、第2の実施例のレイヤー選択トランジスタは、比較例のレイヤー選択トランジスタよりも小さくなり、かつ、積層数nが大きくなるほど、その差も大きくなる。

【0128】

尚、その他の構成及び製造方法については、第1の実施例に係わる半導体装置と同じであるため、ここでの説明を省略する。

【0129】

また、第2の実施例においても、第1の実施例における第1の変形例(図12及び図13)及び第2の変形例(図14及び図15)と同様の変形が可能である。

【0130】

以上、説明したように、第2の実施例によれば、第1の実施例と同様に、デザインルールが縮小されても、半導体基板上に積み重ねられた複数の半導体層のうちの1つを正確に選択することができる。

【0131】

[第3の実施例]

図18は、第3の実施例に係わる半導体装置を示している。図19は、図18のXIX−XIX線に沿う断面図である。

【0132】

第3の実施例は、半導体層の積層数nが3、ノーマリーオン領域の片側の伸張量jが1(k=j=1)、ゲート電極の数m(=n+k)が4の例である。

【0133】

半導体基板10は、例えば、シリコン基板である。絶縁層11は、半導体基板10上に配置される。第1、第2及び第3の半導体層12−1,12−2,12−3は、絶縁層11の表面に垂直な第1の方向に、絶縁層11の表面から順番に互いに絶縁されて積み重ねられ、かつ、絶縁層11の表面に平行な第2の方向に延びる。

【0134】

本例では、第1、第2及び第3の半導体層12−1,12−2,12−3は、絶縁層13により互いに絶縁される。絶縁層14は、最上層としての第3の半導体層12−3上に配置される。絶縁層13,14は、例えば、酸化シリコン層である。絶縁層14は、酸化シリコン層以外に、窒化シリコン層や、酸化シリコン層と窒化シリコン層の積層などとすることも可能である。

【0135】

第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層13,14の第2の方向の一端は、階段形状を有する。また、第1、第2及び第3の半導体層12−1,12−2,12−3の第2の方向の一端(階段形状の部分)は、第1、第2及び第3の拡散防止層20−1,20−1,20−3により覆われる。

【0136】

第1、第2及び第3の拡散防止層20−1,20−1,20−3は、FNトンネル電流又はダイレクトトンネル電流が流れる程度の厚さ、例えば、1nm以下の厚さを有する絶縁層を備える。この場合、第1、第2及び第3の拡散防止層20−1,20−1,20−3は、酸化シリコン層、窒化シリコン層、酸窒化シリコン層などから形成されるのが望ましい。

【0137】

また、第1、第2及び第3の拡散防止層20−1,20−1,20−3は、金属層や金属シリサイド層を備えていてもよい。この場合、第1、第2及び第3の拡散防止層20−1,20−1,20−3は、低抵抗であるため、共通電極18と、第1、第2及び第3の半導体層12−1,12−2,12−3との間の配線抵抗を下げることができる。

【0138】

共通半導体層21は、第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層13,14の第2の方向の一端に配置され、第1、第2及び第3の拡散防止層20−1,20−1,20−3を介して、第1、第2及び第3の半導体層12−1,12−2,12−3に共通に接続される。

【0139】

第1、第2及び第3の半導体層12−1,12−2,12−3、絶縁層13,14及び共通半導体層21は、フィン型積層構造Finを構成する。第1、第2及び第3の半導体層12−1,12−2,12−3は、単結晶状態であるのが望ましいが、多結晶状態、アモルファス状態であっても構わない。

【0140】

フィン型積層構造Finの第2の方向の一端において、共通電極18は、共通半導体層21に接続される。共通電極18は、例えば、タングステン、アルミニウムなどの金属層を備える。

【0141】

レイヤー選択トランジスタ15(LST)は、例えば、FETであり、第1、第2及び第3の半導体層12−1,12−2,12−3又は共通半導体層21をチャネルとし、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択する。

【0142】

レイヤー選択トランジスタ15(LST)は、第2の方向に、共通電極18側から順番に一定ピッチPで配置される第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4を有する。

【0143】

第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4は、例えば、導電性ポリシリコン層、ニッケルシリサイド層などの金属シリサイド層、又は、これらの積層を備える。

【0144】

第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4は、少なくとも、第1、第2及び第3の半導体層12−1,12−2,12−3及び共通半導体層21の第1及び第2の方向に垂直な第3の方向にある側面に沿って第1の方向に延びる。

【0145】

本例では、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4は、フィン型積層構造Finの第1の方向にある上面及び第2の方向にある2つの側面を覆う。即ち、レイヤー選択トランジスタ15(LST)は、ダブルゲート構造を有するフィン型FETである。

【0146】

また、第1のゲート電極16−1は、第1の拡散防止層20−1と第2の拡散防止層20−2との間に配置され、第2のゲート電極16−2は、第2の拡散防止層20−2と第3の拡散防止層20−3との間に配置される。第3及び第4のゲート電極16−3,16−4は、第3の拡散防止層20−3よりも、第1、第2及び第3の半導体層12−1,12−2,12−3側に配置される。

【0147】

レイヤー選択トランジスタ15(LST)は、第1、第2及び第3の半導体層12−1,12−2,12−3内に、それぞれ、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を有する。

【0148】

第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3は、n型不純物(砒素、リンなどの5価元素)、p型不純物(硼素、インジウムなどの3価元素)、又は、それらの両方を含む不純物領域である。

【0149】

第1の半導体層12−1内に存在する第1のノーマリーオン領域17−1は、第1及び第2のゲート電極16−1,16−2に隣接するチャネルを、それぞれ、第1及び第2のゲート電極16−1,16−2の電位に依存しないノーマリーオンチャネルにする。

【0150】

第2の半導体層12−2内に存在する第2のノーマリーオン領域17−2は、第2及び第3のゲート電極16−2,16−3に隣接するチャネルを、それぞれ、第2及び第3のゲート電極16−2,16−3の電位に依存しないノーマリーオンチャネルにする。

【0151】

第3の半導体層12−3内に存在する第3のノーマリーオン領域17−3は、第3及び第4のゲート電極16−3,16−4に隣接するチャネルを、それぞれ、第3及び第4のゲート電極16−3,16−4の電位に依存しないノーマリーオンチャネルにする。

【0152】

尚、本例では、レイヤー選択トランジスタ15(LST)をFETとする場合について説明したが、これ以外のスイッチ素子をレイヤー選択トランジスタとして用いることもできる。即ち、レイヤー選択トランジスタ15(LST)は、スイッチ機能を有していればよい。

【0153】

また、本例では、第1、第2及び第3の半導体層12−1,12−2,12−3内に第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3のみが形成される例を示しているが、それに加えて、第1、第2及び第3の半導体層12−1,12−2,12−3内には、レイヤー選択トランジスタ15(LST)の閾値を制御するための不純物領域を設けてもよい。

【0154】

表3は、図18の半導体装置における半導体層の選択動作を示している。

【0155】

【表3】

【0156】

図18の半導体装置によれば、第1のゲート電極16−1に係わるレイヤー選択トランジスタ15(LST)は、最下層としての第1の半導体層12−1において常にオン状態(ノーマリーオン状態)であり、それ以外の第2及び第3の半導体層12−2,12−3においてスイッチ素子として機能する。

【0157】

第2のゲート電極16−2に係わるレイヤー選択トランジスタ15(LST)は、最下層としての第1の半導体層12−1及び中間層としての第2の半導体層12−2において常にオン状態(ノーマリーオン状態)であり、それ以外の第3の半導体層12−3においてスイッチ素子として機能する。

【0158】

第3のゲート電極16−3に係わるレイヤー選択トランジスタ15(LST)は、中間層としての第2の半導体層12−2及び最上層としての第3の半導体層12−3において常にオン状態(ノーマリーオン状態)であり、それ以外の第1の半導体層12−1においてスイッチ素子として機能する。

【0159】

第4のゲート電極16−4に係わるレイヤー選択トランジスタ15(LST)は、最上層としての第3の半導体層12−3において常にオン状態(ノーマリーオン状態)であり、それ以外の第1及び第2の半導体層12−1,12−2においてスイッチ素子として機能する。

【0160】

従って、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4の電位を、表3に示す関係に設定することにより、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択することができる。

【0161】

尚、表3において、“H”は、レイヤー選択トランジスタ15(LST)のチャネルをオンチャネル(オン状態)にし得るオン電位のことであり、“L”は、レイヤー選択トランジスタ15(LST)のチャネルをオフチャネル(オフ状態)にし得るオフ電位のことである。

【0162】

例えば、レイヤー選択トランジスタ15(LST)がnチャネルFETのときは、“H”は正電位であり、“L”は接地電位である。また、レイヤー選択トランジスタ15(LST)がpチャネルFETのときは、“H”は負電位であり、“L”は接地電位である。

【0163】

第1の半導体層12−1を選択するときは、第1及び第2のゲート電極16−1,16−2の電位を“L”に設定し、第3及び第4のゲート電極16−3,16−4の電位を“H”に設定する。

【0164】

この時、第1のゲート電極16−1に係わるレイヤー選択トランジスタ15(LST)は、第2及び第3の半導体層12−2,12−3においてオフ状態であり、第2のゲート電極16−2に係わるレイヤー選択トランジスタ15(LST)は、第3の半導体層12−3においてオフ状態であるため、第2及び第3の半導体層12−2,12−3は選択されない。これに対し、第1の半導体層12−1では、第1のノーマリーオン領域17−1が存在するため、第1乃至第4のゲート電極16−1〜16−4に隣接する全てのチャネルがオン状態になる。

【0165】

従って、第1の半導体層12−1が選択される。

【0166】

第2の半導体層12−2を選択するときは、第2及び第3のゲート電極16−2,16−3の電位を“L”に設定し、第1及び第4のゲート電極16−1,16−4の電位を“H”に設定する。

【0167】

この時、第2のゲート電極16−2に係わるレイヤー選択トランジスタ15(LST)は、第3の半導体層12−3においてオフ状態であり、第3のゲート電極16−3に係わるレイヤー選択トランジスタ15(LST)は、第1の半導体層12−1においてオフ状態であるため、第1及び第3の半導体層12−1,12−3は選択されない。これに対し、第2の半導体層12−2では、第2のノーマリーオン領域17−2が存在するため、第1乃至第4のゲート電極16−1〜16−4に隣接する全てのチャネルがオン状態になる。

【0168】

従って、第2の半導体層12−2が選択される。

【0169】

第3の半導体層12−3を選択するときは、第3及び第4のゲート電極16−3,16−4の電位を“L”に設定し、第1及び第2のゲート電極16−1,16−2の電位を“H”に設定する。

【0170】

この時、第3のゲート電極16−3に係わるレイヤー選択トランジスタ15(LST)は、第1の半導体層12−1においてオフ状態であり、第4のゲート電極16−4に係わるレイヤー選択トランジスタ15(LST)は、第1及び第2の半導体層12−1,12−2においてオフ状態であるため、第1及び第2の半導体層12−1,12−2は選択されない。これに対し、第3の半導体層12−3では、第3のノーマリーオン領域17−3が存在するため、第1乃至第4のゲート電極16−1〜16−4に隣接する全てのチャネルがオン状態になる。

【0171】

従って、第3の半導体層12−3が選択される。

【0172】

上述の選択動作により、第1、第2及び第3の半導体層12−1,12−2,12−3に対しては、それらに共通に接続される共通電極18を設ければよい。即ち、第1、第2及び第3の半導体層12−1,12−2,12−3の各々に対して、個別に電極を設ける必要がないため、コンタクト領域のサイズを縮小可能である。

【0173】

図20は、半導体層の積層数とレイヤー選択トランジスタの大きさとの関係を示している。

【0174】

本例では、半導体層の積層数nは、3である。

【0175】

同図(a)は、図18に示す第3の実施例に相当する。第3の実施例の場合、レイヤー選択トランジスタ15(LST)の第2の方向の大きさは、P×3である。但し、Pは、ゲート電極16−1〜16−4のピッチである。

【0176】

同図(b)は、比較例である。比較例では、半導体層12−1〜12−3の積層数とゲート電極16−1〜16−3の数を等しくし、かつ、半導体層の選択機能を有効にするため、ゲート電極のピッチを2Pに設定している。

【0177】

比較例の場合、レイヤー選択トランジスタ15(LST)の第2の方向の大きさは、P×4である。

【0178】

このように、半導体層の積層数nが3の場合、第3の実施例に係わるレイヤー選択トランジスタ15(LST)は、比較例に係わるレイヤー選択トランジスタ15(LST)よりも小さくなる。

【0179】

第3の実施例では、半導体層の積層数nが2のとき、第3の実施例に係わるレイヤー選択トランジスタ15(LST)の大きさは、比較例に係わるレイヤー選択トランジスタ15(LST)の大きさに等しくなる。

【0180】

また、半導体層の積層数nが3以上になると、レイヤー選択トランジスタの大きさが、比較例に係わるレイヤー選択トランジスタの大きさよりも小さくなる、という効果を発揮する。この効果は、半導体層の積層数nが増加するほど大きくなるため、第3の実施例は、積層数をできるだけ多くしたい、という要望があるときに非常に有効な技術となる。

【0181】

半導体層の積層数とレイヤー選択トランジスタの大きさとの関係を一般化すると、以下のようになる。

【0182】

第3の実施例(図20(a))では、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n+k−1)となる。また、第3の実施例では、k=1であるから、レイヤー選択トランジスタの第2方向の大きさは、P×nとなる。これに対し、比較例(図20(b))では、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n−1)×2となる。

【0183】

例えば、積層数nが2のとき、第3の実施例での大きさは、P×2、比較例での大きさは、P×2であり、第3の実施例のレイヤー選択トランジスタの大きさは、比較例のレイヤー選択トランジスタの大きさに等しい。

【0184】

しかし、積層数nが3のとき、第3の実施例での大きさは、P×3、比較例での大きさは、P×4であり、積層数nが4のとき、第3の実施例での大きさは、P×4、比較例での大きさは、P×6であり、積層数nが5のとき、第3の実施例での大きさは、P×5、比較例での大きさは、P×8であり、積層数nが6のとき、第3の実施例での大きさは、P×6、比較例での大きさは、P×10である。

【0185】

以上のように、積層数nが3以上になると、第3の実施例のレイヤー選択トランジスタは、比較例のレイヤー選択トランジスタよりも小さくなり、かつ、積層数nが大きくなるほど、その差も大きくなる。

【0186】

図21乃至図28は、図18の半導体装置の製造方法を示している。

【0187】

まず、図21に示すように、半導体基板10として、例えば、面方位(100)、比抵抗10〜20Ωcmのp型シリコン基板を用意する。この半導体基板10上に、絶縁層11,13,14としての酸化シリコン層と、第1、第2及び第3の半導体層12−1,12−2,12−3としての多結晶シリコン層とを、交互に形成する。

【0188】

次に、図22に示すように、例えば、PEPとRIEを用いて、第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層13,14の第2の方向の端部に、階段形状を形成する。

【0189】

次に、図23に示すように、例えば、PEPを用いて、絶縁層14上にマスク層(フォトレジスト層)22を形成する。そして、マスク層22をマスクにして、イオン注入により、第1、第2及び第3の半導体層12−1,12−2,12−3内に、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を形成する。

【0190】

この場合、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3は、同時に形成される。また、イオン注入は、所定の加速電圧で、例えば、砒素イオンを第1、第2及び第3の半導体層12−1,12−2,12−3内に注入することにより実行される。

【0191】

尚、本例では、階段形状を形成した後に、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を形成する。

【0192】

但し、これに代えて、第1、第2及び第3の半導体層12−1,12−2,12−3を形成した後、階段形状を形成する前に、PEPとイオン注入により、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を形成してもよい。

【0193】

また、第1の半導体層12−1を形成した直後に第1のノーマリーオン領域17−1を形成し、この後、第2の半導体層12−2を形成した直後に第2のノーマリーオン領域17−2を形成し、さらに、この後、第3の半導体層12−3を形成した直後に第3のノーマリーオン領域17−3を形成してもよい。

【0194】

次に、図24に示すように、第1、第2及び第3の半導体層12−1,12−2,12−3の第2の方向にある側面(階段形状の部分)上に、第1、第2及び第3の拡散防止層20−1,20−2,20−3を形成する。

【0195】

第1、第2及び第3の拡散防止層20−1,20−2,20−3が絶縁層のとき、第1、第2及び第3の拡散防止層20−1,20−2,20−3は、熱酸化などにより積極的に形成してもよいし、例えば、ウェハープロセス中に酸素に触れることにより形成される自然酸化膜を利用してもよい。

【0196】

また、第1、第2及び第3の拡散防止層20−1,20−2,20−3が金属シリサイド層のとき、第1、第2及び第3の拡散防止層20−1,20−2,20−3は、金属層と、第1、第2及び第3の半導体層12−1,12−2,12−3とのシリサイド反応を利用する。

【0197】

本例では、第1、第2及び第3の拡散防止層20−1,20−2,20−3は、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を形成した後に形成する。但し、これに代えて、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を形成する前に、第1、第2及び第3の拡散防止層20−1,20−2,20−3を形成してもよい。

【0198】

次に、図25に示すように、絶縁層11上に、第1、第2及び第3の拡散防止層20−1,20−2,20−3を介して、第1、第2及び第3の半導体層12−1,12−2,12−3に接続される共通半導体層21を形成する。

【0199】

共通半導体層21は、第1、第2及び第3の半導体層12−1,12−2,12−3と同じ材料及び同じ結晶構造を有しているのが望ましい。また、共通半導体層21の上面は、CMPにより平坦化するのが望ましい。

【0200】

次に、図26に示すように、PEPとRIEを用いて、絶縁層13,14、第1、第2及び第3の半導体層12−1,12−2,12−3、及び、共通半導体層21を、それぞれ、パターニングすることにより、フィン型積層構造Finを形成する。

【0201】

次に、図27に示すように、絶縁層11上に、フィン型積層構造Finを覆うゲート絶縁層(例えば、酸化シリコン層)と、ゲート絶縁層上の導電層とを形成する。そして、PEPとRIEとを用いて、この導電層をパターニングにすることにより、第2の方向に一定ピッチPで並んで配置される第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4を形成する。

【0202】

また、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4は、フィン型積層構造Finの第1の方向にある上面及び第2の方向にある2つの側面をそれぞれ覆うように形成される。

【0203】

この時点において、第1のノーマリーオン領域17−1は、第1のゲート電極16−1に隣接するチャネルのみに形成され、第2のノーマリーオン領域17−2は、第2のゲート電極16−2に隣接するチャネルのみに形成され、第3のノーマリーオン領域17−3は、第3のゲート電極16−3に隣接するチャネルのみに形成される。

【0204】

尚、ゲート絶縁層及び導電層を形成した後、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4を形成する前に、CMPにより、導電層の上面を平坦化してもよい。

【0205】

また、フィン型積層構造Fin以外の領域を絶縁層で満たした状態でCMPを行ってもよい。この場合、CMP後に、フィン型積層構造Fin以外の領域を満たした絶縁層を除去し、さらに、その後、PEPとRIEとを用いて、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4を形成する。

【0206】

次に、図28に示すように、フィン型積層構造Finの第2の方向の一端に、第1、第2及び第3の半導体層12−1,12−2,12−3に共通に接続される共通電極18を形成する。

【0207】

また、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3は、それらを形成した後に発生する、ベーク処理、キュア処理、デンシファイ処理などの高温熱処理により、第2の方向に伸張する。

【0208】

本例では、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3は、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4のピッチPの1倍以上、2倍未満伸張する。

【0209】

但し、不純物の拡散前の第1のノーマリーオン領域17−1の第2の方向の端は、第1のゲート電極16−1の第2の方向の端に一致し、不純物の拡散前の第2のノーマリーオン領域17−2の第2の方向の端は、第2のゲート電極16−2の第2の方向の端に一致し、不純物の拡散前の第3のノーマリーオン領域17−3の第2の方向の端は、第3のゲート電極16−3の第2の方向の端に一致する、と仮定する。

【0210】

以上の工程により、図18の半導体装置が完成する。

【0211】

図29は、第3の実施例の第1の変形例を示している。図30は、図29のXXX−XXX線に沿う断面図である。

【0212】

第1の変形例の特徴は、第3の実施例と比べると、第1、第2及び第3の半導体層12−1,12−2,12−3の第3の方向にある側面のうち、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4に覆われていない領域に、第1、第2及び第3の半導体層12−1,12−2,12−3の抵抗値よりも低い抵抗値を持つ低抵抗領域19が設けられる点にある。

【0213】

その他の構成については、第3の実施例に係わる半導体装置と同じであるため、ここでの説明を省略する。

【0214】

低抵抗領域19は、例えば、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3とは異なる不純物領域である。この場合、低抵抗領域19内の不純物は、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3内の不純物と同じであっても、異なっていてもよい。

【0215】

また、低抵抗領域19は、例えば、ニッケルシリサイド層などの金属シリサイド層である。この場合、低抵抗領域19は、フィン型積層構造Finを覆う金属層を形成した後、金属層と第1、第2及び第3の半導体層12−1,12−2,12−3とをシリサイド反応させ、さらに、この後、未反応の金属層を除去することにより形成される。

【0216】

この変形例によれば、低抵抗領域19により、寄生抵抗が下がり、動作速度の向上などのメモリ特性を向上させることができる。

【0217】

図31は、第3の実施例の第2の変形例を示している。図32は、図31のXXXII−XXXII線に沿う断面図である。

【0218】

第2の変形例の特徴は、第3の実施例と比べると、第1、第2及び第3の半導体層12−1,12−2,12−3間が空洞(CAVITY)であり、かつ、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4とフィン型積層構造Finとの間が空洞(CAVITY)である点にある。

【0219】

その他の構成については、第3の実施例に係わる半導体装置と同じであるため、ここでの説明を省略する。

【0220】

空洞(CAVITY)は、例えば、第3の実施例(図18及び図19)に示す構造を形成した後、図18及び図19に示す絶縁層13,14を選択的に除去することにより形成される。この場合、第1、第2及び第3の半導体層12−1,12−2,12−3は、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4により支えられる。

【0221】

この変形例によれば、絶縁領域の空洞化により、複数の半導体層間の絶縁性を向上させることができるため、メモリ素子の信頼性が向上する。

【0222】

以上、説明したように、第3の実施例及びその変形例によれば、デザインルールが縮小されても、半導体基板上に積み重ねられた複数の半導体層のうちの1つを正確に選択することができる。

【0223】

[第4の実施例]

図33は、第4の実施例に係わる半導体装置を示している。図34は、図33のXXXIV−XXXIV線に沿う断面図である。

【0224】

第4の実施例は、半導体層の積層数nが3、ノーマリーオン領域の片側の伸張量jが2(k=j=2)、ゲート電極の数m(=n+k)が5の例である。

【0225】

第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3の第2の方向の伸張量は、それらを形成した後に発生する高温熱処理(ベーク処理、キュア処理、デンシファイ処理など)の温度や時間(合計値)などに依存する。

【0226】

既に説明したように、例えば、実験データによれば、半導体層として多結晶シリコン層を用い、ノーマリーオン領域を砒素(As)の添加により形成した場合、1000℃、10秒の熱処理で、砒素は多結晶シリコン層内を約70nm拡散する。また、1000℃、20秒の熱処理で、砒素は多結晶シリコン層内を160nm程度拡する。

【0227】

そこで、第4の実施例では、第3の実施例よりも、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3の伸張量が多い場合、具体的には、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3が、ゲート電極のピッチPの2倍伸張する場合について説明する。

【0228】

この場合、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5は、第2の方向に、一定ピッチPで並んで配置される。

【0229】

また、第1のノーマリーオン領域17−1は、第1の半導体層12−1内において、第1、第2及び第3のゲート電極16−1,16−2,16−3に隣接するチャネルをノーマリーオン状態にする。

【0230】

第2のノーマリーオン領域17−2は、第2の半導体層12−2内において、第2、第3及び第4のゲート電極16−2,16−3,16−4に隣接するチャネルをノーマリーオン状態にする。

【0231】

第3のノーマリーオン領域17−3は、第3の半導体層12−3内において、第3、第4及び第5のゲート電極16−3,16−4,16−5に隣接するチャネルをノーマリーオン状態にする。

【0232】

ここで、第3の実施例と同様に、半導体層の積層数とレイヤー選択トランジスタの大きさとの関係を一般化する。

【0233】

第4の実施例でも、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n+k−1)となる。また、第4の実施例では、k=2であるから、レイヤー選択トランジスタの第2方向の大きさは、P×(n+1)となる。これに対し、比較例(図20(b)のゲート電極16−1,16−2,16−3のピッチを、P×2からP×3に変更したもの)では、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n−1)×3となる。

【0234】

例えば、積層数nが2のとき、第4の実施例での大きさは、P×3、比較例での大きさは、P×3であり、第4の実施例のレイヤー選択トランジスタの大きさは、比較例のレイヤー選択トランジスタの大きさに等しい。

【0235】

また、積層数nが3のとき、第4の実施例での大きさは、P×4、比較例での大きさは、P×6であり、積層数nが4のとき、第4の実施例での大きさは、P×5、比較例での大きさは、P×9であり、積層数nが5のとき、第4の実施例での大きさは、P×6、比較例での大きさは、P×12であり、積層数nが6のとき、第4の実施例での大きさは、P×7、比較例での大きさは、P×15である。

【0236】

以上のように、積層数nが3以上になると、第4の実施例のレイヤー選択トランジスタは、比較例のレイヤー選択トランジスタよりも小さくなり、かつ、積層数nが大きくなるほど、その差も大きくなる。

【0237】

尚、その他の構成及び製造方法については、第3の実施例に係わる半導体装置と同じであるため、ここでの説明を省略する。

【0238】

また、第4の実施例においても、第3の実施例における第1の変形例(図29及び図30)及び第2の変形例(図31及び図32)と同様の変形が可能である。

【0239】

以上、説明したように、第4の実施例によれば、第3の実施例と同様に、デザインルールが縮小されても、半導体基板上に積み重ねられた複数の半導体層のうちの1つを正確に選択することができる。

【0240】

第3及び第4の実施例では、階段形状の部分に設けられた拡散防止層により、ノーマリーオン領域の伸張(不純物の拡散)が片側のみに発生する。このため、レイヤー選択トランジスタの大きさに関する説明で明らかなように、第3及び第4の実施例は、第1及び第2の実施例よりも、レイヤー選択トランジスタのサイズの縮小に関する効果が優れる。

【0241】

また、比較例との比較でも明らかなように、第1及び第2の実施例では、積層数nが4以上のときに、比較例よりも、レイヤー選択トランジスタのサイズが縮小されるのに対して、第3及び第4の実施例では、積層数nが3以上のときに、比較例よりも、レイヤー選択トランジスタのサイズが縮小される。

【0242】

[適用例]

実施形態に係わる半導体装置の適用例を説明する。

【0243】

以下に説明する適用例は、第1乃至第nの半導体層(nは2以上の自然数)に接続される複数のメモリセルを有する三次元不揮発性半導体メモリに関する。実施形態の技術により、第1乃至第nの半導体層のうちの1つを選択することにより、大容量メモリを実現することができる。

【0244】

図35は、適用例としてのVLBを示している。図36は、図35のXXXVI−XXXVI線に沿う断面図を示し、図37は、図36のメモリセルMCを示している。

【0245】

半導体基板10上の絶縁層11上には、第1の方向に積み重ねられ、第3の方向に延びる第1、第2及び第3のメモリストリングNa、Nb,Ncが配置される。本例では、メモリストリングの数は、3つであるが、これに限られない。即ち、第1の方向に積み重ねられるメモリストリングの数は、2つ以上であればよい。

【0246】

第1、第2及び第3のメモリストリングNa、Nb,Ncは、第1の方向に積み重ねられる第1、第2及び第3の半導体層12−1,12−2,12−3と、第3の方向に直列接続される複数のメモリセルMCとを備える。本例では、直列接続されるメモリセルMCの数は、6つであるが、これに限られない。即ち、第3の方向に直列接続されるメモリセルの数は、2つ以上であればよい。

【0247】

第1、第2及び第3の半導体層12−1,12−2,12−3は、絶縁層13により互いに絶縁される。また、最上層としての第3の半導体層12−3上には、絶縁層14が配置される。

【0248】

各メモリセルMCは、例えば、図37に示すように、第1、第2及び第3の半導体層12−1,12−2,12−3の第2の方向にある側面上に配置される絶縁層(ゲート絶縁層25−1、記録層25−2及びブロック絶縁層25−3)25と、絶縁層25の第1、第2及び第3の半導体層12−1,12−2,12−3側とは反対側に配置されるゲート電極(例えば、ワード線WL)26とを備える。

【0249】

ゲート電極26は、第1、第2及び第3の半導体層12−1,12−2,12−3の第2の方向にある側面に沿って第1の方向に延びる。また、ゲート電極26(WL)をその上面から見たとき、ゲート電極26(WL)は、第1、第2及び第3のメモリストリングNa、Nb,Ncを跨いで、第2の方向に延びる。

【0250】

第1、第2及び第3のメモリストリングNa、Nb,Ncの第3の方向の両端には、第2の方向に延びる梁27a,27bが接続される。

【0251】

第1、第2及び第3のメモリストリングNa、Nb,Ncが、第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層13,14を備えるフィン型積層構造を有するとき、梁27a,27bも、第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層13,14を備えるフィン型積層構造を有する。

【0252】

梁27a,27bは、第1、第2及び第3のメモリストリングNa、Nb,Ncのチャネルに電圧又は電流を供給する導電パスとなる。

【0253】

また、梁27a,27bは、第1、第2及び第3のメモリストリングNa、Nb,Ncを固定し、これらの倒壊を防止する機能を有する。梁27a,27bの第3の方向の幅は、第1、第2及び第3のメモリストリングNa、Nb,Ncの第2の方向の幅よりも広いのが望ましい。

【0254】

梁27a,27bの第2の方向の一端には、実施形態に係わる半導体装置、即ち、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択する機能が設けられる。

【0255】

本例の場合、この機能は、第3の実施例(図18及び図19参照)に相当する。例えば、梁27a,27bの第2の方向の一端には、共通半導体層21に接続される共通電極18と、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)が設けられる。

【0256】

共通電極18は、第1、第2及び第3のメモリストリングNa、Nb,Ncのソース電極(ソース線側電極)又はドレイン電極(ビット線側電極)として機能する。

【0257】

また、レイヤー選択トランジスタ15(LST)については、第1乃至第4の実施例で詳細に説明したので、ここでの説明を省略する。

【0258】

第1、第2及び第3のメモリストリングNa、Nb,Ncと梁27a,27bとの間には、例えば、メモリセルアレイを構成する複数(本例では4つ)のフィン型積層構造(第1、第2及び第3のメモリストリングNa、Nb,Ncを備える1グループ)のうちの1つを選択するためのアシストゲートトランジスタ24(AGT)が設けられる。

【0259】

尚、アシストゲートトランジスタ24(AGT)は、スイッチとして機能すればよい。このため、アシストゲートトランジスタ24(AGT)は、メモリセルMCと同じ構造を有していてもよいし、異なる構造を有していてもよい。

【0260】

例えば、アシストゲートトランジスタ24(AGT)がメモリセルMCと同じ構造を有するとき、アシストゲートトランジスタ24(AGT)は、絶縁層(ゲート絶縁層25−1、記録層25−2及びブロック絶縁層25−3)25と、絶縁層25の第1、第2及び第3の半導体層12−1,12−2,12−3側とは反対側に配置されるゲート電極26とを備える。

【0261】

また、アシストゲートトランジスタ24(AGT)がメモリセルMCと異なる構造を有するとき、アシストゲートトランジスタ24(AGT)は、ゲート絶縁層と、ゲート電極とを備えるMIS (Metal-Insulator-Semiconductor)型トランジスタである。

【0262】

アシストゲートトランジスタ24(AGT)は、例えば、メモリセルアレイを構成する複数(本例では4つ)のフィン型積層構造の各々に独立に設けられる。

【0263】

上述のVLBの各要素を構成する材料については、半導体メモリの各世代に応じた最適な材料を適宜選択することができるが、以下では、最もよく使用される材料例を説明する。

【0264】

半導体基板10は、例えば、単結晶シリコン基板である。また、絶縁層11,13は、例えば、酸化シリコン層である。

【0265】

第1、第2及び第3の半導体層12−1,12−2,12−3及び共通半導体層21は、それぞれ、例えば、シリコン(Si)層である。第1、第2及び第3の半導体層12−1,12−2,12−3及び共通半導体層21は、単結晶であるのが望ましいが、アモルファス又は多結晶であっても構わない。

【0266】

フィン型積層構造を構成する最上層の絶縁層14は、例えば、酸化シリコン(SiO2)、窒化シリコン(SiN)、又は、それらが積み重ねられた構造を有する。

【0267】

メモリセルMCを構成するゲート絶縁層25−1は、例えば、酸化シリコン層である。ゲート絶縁層25−1は、酸窒化シリコン、酸化シリコンと窒化シリコンとの積層構造などであってもよい。また、ゲート絶縁層25−1は、シリコンナノ粒子や、金属イオンなどを含んでいてもよい。

【0268】

記録層25−2は、例えば、電荷蓄積層(Si3N4など)、可変抵抗層(電圧、電流、熱、磁場などにより抵抗値が変化する材料層など)である。記録層25−2が電荷蓄積層のとき、記録層25−2は、絶縁層ではなく、導電層としてのフローティングゲート層であっても構わない。

【0269】

記録層25−2が電荷蓄積層のとき、電荷蓄積層は、例えば、シリコンリッチSiN、シリコンと窒素の組成比x、yが任意であるSixNy、酸窒化シリコン(SiON)、酸化アルミニウム(Al2O3)、酸窒化アルミニウム(AlON)、ハフニア(HfO2)、ハフニウム・アルミネート(HfAlO3)、窒化ハフニア(HfON)、窒化ハフニウム・アルミネート(HfAlON)、ハフニウム・シリケート(HfSiO)、窒化ハフニウム・シリケート(HfSiON)、酸化ランタン(La2O3)及びランタン・アルミネート(LaAlO3)のグループから選択される少なくとも1つであってもよい。

【0270】

また、電荷蓄積層は、シリコンナノ粒子や、金属イオンなどを含んでいてもよい。電荷蓄積層は、不純物が添加されたポリシリコン、メタルなどの導電体から構成してもよい。

【0271】

ブロック絶縁層25−3は、例えば、書き込み/消去時のリーク電流を防止する機能を有する。

【0272】

ブロック絶縁層25−3は、例えば、酸化シリコン(SiO2)、酸窒化シリコン(SiON)、酸化アルミニウム(Al2O3)、酸窒化アルミニウム(AlON)、ハフニア(HfO2)、ハフニウム・アルミネート(HfAlO3)、窒化ハフニア(HfON)、窒化ハフニウム・アルミネート(HfAlON)、ハフニウム・シリケート(HfSiO)、窒化ハフニウム・シリケート(HfSiON)、酸化ランタン(La2O3)、ランタン・アルミネート(LaAlO3)及びランタンアルミシリケート(LaAlSiO)のグループから選択される少なくとも1つであるのが望ましい。

【0273】

メモリセルMCを構成するゲート電極26は、例えば、珪化ニッケル(NiSi)などの金属シリサイド層を備える。

【0274】

ゲート電極26は、例えば、タンタルナイトライド(TaN)、タンタルカーバイト(TaC)、チタンナイトライド(TiN)などの金属化合物、又は、金属的な電気伝導特性を示す、Ni、V、Cr、Mn、Y、Mo、Ru、Rh、Hf、Ta、W,Ir、Co、Ti、Er、Pt、Pd、Zr、Gd、Dy、Ho、Er、及び、これらのシリサイドであってもよい。

【0275】

共通電極18及びレイヤー選択トランジスタ15のゲート電極16−1〜16−5は、例えば、W、Al、Cuなどの金属材料である。

【0276】

図38は、クロスポイント型メモリセルアレイを実現する不揮発性半導体メモリを示している。図39は、図38のメモリセルアレイを示している。図40は、図39のA−A’線及びB−B’線に沿う断面図を示している。

【0277】

2つのフィン型積層構造(第1乃至第nの半導体層)を互いに交差させ、これら2つのフィン型積層構造間に2端子型のメモリセルMCを配置すれば、クロスポイント型メモリセルアレイを実現できる。

【0278】

この場合、メモリセルMCは、ReRAM(Resistance Random Access Memory)、PCM(Phase Change Memory)、MRAM(Magnetic Random Access Memory)などの抵抗変化型のメモリに用いられるメモリセルをそのまま採用することが可能である。

【0279】

半導体基板10上の絶縁層11上には、互いに交差するワード線WL/ビット線BLとしての複数の導電線が設けられる。これら複数の導電線は、半導体基板10上の絶縁層11上に積み重ねられる第1、第2及び第3の半導体層12−1,12−2,12−3を備える。

【0280】

本例では、絶縁層11上に積み重ねられる導電線としての半導体層の数は、3つであるが、これに限られない。即ち、これら導電線としての半導体層の数は、2つ以上であればよい。

【0281】

また、互いに交差するワード線WL/ビット線BL間には、2端子型のメモリセルMCが配置される。

【0282】

メモリセルMCは、電圧、電流、熱、磁場などにより抵抗値が変化する抵抗変化素子、例えば、ReRAM(Resistance Random Access Memory)、PCM(Phase Change Memory)、MRAM(Magnetic Random Access Memory)などの抵抗変化型のメモリに用いられるメモリセルをそのまま採用することが可能である。

【0283】

互いに交差するワード線WL/ビット線BLの両端には、梁27a,27bがそれぞれ接続される。梁27a,27bは、ワード線WL/ビット線BLとしての複数の導電線と同じ構造を有する。

【0284】

梁27a,27bは、ワード線WL/ビット線BLを固定し、これらの倒壊を防止するために付加される。梁27a,27bの幅は、ワード線WL/ビット線BLの幅よりも広いのが望ましい。

【0285】

梁27a,27bの一端には、実施形態に係わる半導体装置、即ち、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択する機能が設けられる。

【0286】

本例の場合、この機能は、第3の実施例(図18及び図19参照)に相当する。例えば、梁27a,27bの一端には、共通半導体層21に接続される共通電極18と、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)が設けられる。

【0287】

共通電極18は、第1、第2及び第3の半導体層12−1,12−2,12−3を介して、複数のメモリセルMCに、電圧又は電流を供給するための電極として機能する。

【0288】

また、レイヤー選択トランジスタ15(LST)については、第1乃至第4の実施例で詳細に説明したので、ここでの説明を省略する。

【0289】

ワード線WL/ビット線BLと梁27a,27bとの間には、アシストゲートトランジスタ24(AGT)が配置される。アシストゲートトランジスタ24(AGT)は、例えば、ゲート絶縁層と、ゲート電極とを備えるMIS (Metal-Insulator-Semiconductor)型トランジスタである。但し、アシストゲートトランジスタ24(AGT)は、これに限られることはなく、スイッチとして機能すればよい。

【0290】

アシストゲートトランジスタ24(AGT)は、例えば、ワード線WL/ビット線BLを構成する複数(本例では4つ)のフィン型積層構造の各々に独立に設けられる。

【0291】

本例では、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択する機能は、互いに交差するワード線WL/ビット線BLの両方に設けられるが、互いに交差するワード線WL/ビット線BLの一方のみに設けてもよい。この場合も、クロスポイント型メモリセルアレイを正常に動作させることができる。

【0292】

[むすび]

実施形態によれば、デザインルールが縮小されても、半導体基板上に積み重ねられた複数の半導体層のうちの1つを正確に選択することができる。

【0293】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0294】

10: 半導体基板、 11,13,14: 絶縁層、 12−1,12−2,12−3,12−4,12−5,12−6: 半導体層、 15: レイヤー選択トランジスタ(LST)、 16−1,16−2,16−3,16−4,16−5,16−6,16−7,16−8: ゲート電極、 17−1,17−2,17−3,17−4,17−5,17−6: ノーマリーオン領域、 18: 共通電極、 19: 低抵抗領域、 20: 拡散防止層、 21: 共通半導体層、 22: マスク層、 23: メモリセルアレイ、 24: アシストゲートトランジスタ(AGT)、 25: 絶縁層、 25−1: ゲート絶縁層、 25−2: 電荷蓄積層、 26: 導電層(ワード線)、 MC: メモリセル、 WL: ワード線、 BL: ビット線。

【技術分野】

【0001】

実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、半導体基板上にフィン型の複数の半導体層(活性領域)を積み重ねた3次元構造の半導体装置が研究されている。

【0003】

例えば、半導体基板上の各半導体層を、メモリセル(セルトランジスタ)のチャネルとして用いれば、VLB (Vertical gate ladder-Bit cost scalable memory)と呼ばれる垂直ゲート型3次元不揮発性メモリを構成できる。また、半導体基板上の各半導体層を、メモリセル(抵抗変化素子)に接続される導電線として用いれば、クロスポイント型の3次元不揮発性メモリを構成できる。

【0004】

また、これら不揮発性メモリに代表される3次元構造の半導体装置を動作させるためには、半導体基板上の複数の半導体層のうちの1つに選択的にアクセスするための機構が必要である。その機構の一つとして、複数の半導体層(チャネル)に共通のゲート電極を持ち、複数の半導体層のうちの1つでノーマリーオン、残りの半導体層でオン/オフ制御可能なレイヤー選択トランジスタを設ける技術が知られている。

【0005】

しかし、レイヤー選択トランジスタにより複数の半導体層のうちの1つを選択するときは、積み重ねる半導体層の数と同じ数のゲート電極を並べて配置することが必要である。この場合、ウェハープロセス中の熱処理により、レイヤー選択トランジスタをノーマリーオンとするために各半導体層内に注入された不純物が不用意に拡散し、本来オン/オフ制御しなければならない部分でノーマリーオンとなってしまう、などの選択動作に支障をきたす問題が発生する。

【0006】

この問題は、デザインルールが縮小され、並べて配置された複数のゲート電極のピッチが小さくなるほど深刻となる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】米国特許第7,352,018号

【特許文献2】米国特許公開第2008/259687号

【特許文献3】特開2006−155750号公報

【非特許文献】

【0008】

【非特許文献1】W. Kim et al., 2009 Symp. on VLSI p188

【発明の概要】

【発明が解決しようとする課題】

【0009】

実施形態は、デザインルールが縮小されても、半導体基板上に積み重ねられた複数の半導体層のうちの1つを正確に選択するための技術を提案する。

【課題を解決するための手段】

【0010】

実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上の絶縁層と、前記絶縁層の表面に垂直な第1の方向に、前記絶縁層の表面から順番に積み重ねられ、前記絶縁層の表面に平行な第2の方向に延び、互いに絶縁される第1乃至第nの半導体層(nは2以上の自然数)と、前記第2の方向の一端において前記第1乃至第nの半導体層に接続される共通電極と、前記第1乃至第nの半導体層をチャネルとし、前記第1乃至第nの半導体層のうちの1つを選択するレイヤー選択トランジスタとを備え、前記レイヤー選択トランジスタは、前記第2の方向に、前記第2の方向の一端から順番に配置され、前記第1乃至第nの半導体層の前記第1及び第2の方向に垂直な第3の方向にある側面に沿って前記第1の方向に延びる第1乃至第mのゲート電極(m=n+k、kは偶数)と、前記第iの半導体層(iは1〜nのうちの1つ)内において前記第i乃至第(i+k)のゲート電極に隣接するチャネルを、前記第i乃至第(i+k)のゲート電極の電位に依存しないノーマリーオンチャネルにする第iのノーマリーオン領域とを備える。

【0011】

実施形態によれば、前記半導体装置の製造方法は、前記第iのノーマリーオン領域を、不純物の注入により前記第iの半導体層内の前記第(i+(k/2))のゲート電極に隣接するチャネルのみに形成する工程と、前記第iのノーマリーオン領域を形成した後の前記不純物の拡散により、前記第iのノーマリーオン領域が、前記第2の方向に前記第1乃至第mのゲート電極のピッチのj倍(jは自然数)以上、(j+1)倍未満伸張するとき、k=j×2に設定する工程とを備える。

【図面の簡単な説明】

【0012】

【図1】第1の実施例に係わる半導体装置を示す斜視図。

【図2】図1のII−II線に沿う断面図。

【図3】比較例を示す断面図。

【図4】比較例を示す断面図。

【図5】積層数と大きさとの関係を示す図。

【図6】積層数と大きさとの関係を示す図。

【図7】図1の半導体装置の製造方法を示す斜視図。

【図8】図1の半導体装置の製造方法を示す斜視図。

【図9】図1の半導体装置の製造方法を示す斜視図。

【図10】図1の半導体装置の製造方法を示す斜視図。

【図11】図1の半導体装置の製造方法を示す斜視図。

【図12】第1の実施例の第1の変形例を示す斜視図。

【図13】図12のXIII−XIII線に沿う断面図。

【図14】第1の実施例の第2の変形例を示す斜視図。

【図15】図14のXV−XV線に沿う断面図。

【図16】第2の実施例に係わる半導体装置を示す斜視図。

【図17】図16のXVII−XVII線に沿う断面図。

【図18】第3の実施例に係わる半導体装置を示す斜視図。

【図19】図18のXIX−XIX線に沿う断面図。

【図20】積層数と大きさとの関係を示す図。

【図21】図18の半導体装置の製造方法を示す斜視図。

【図22】図18の半導体装置の製造方法を示す斜視図。

【図23】図18の半導体装置の製造方法を示す斜視図。

【図24】図18の半導体装置の製造方法を示す斜視図。

【図25】図18の半導体装置の製造方法を示す斜視図。

【図26】図18の半導体装置の製造方法を示す斜視図。

【図27】図18の半導体装置の製造方法を示す斜視図。

【図28】図18の半導体装置の製造方法を示す斜視図。

【図29】第3の実施例の第1の変形例を示す斜視図。

【図30】図29のXXX−XXX線に沿う断面図。

【図31】第3の実施例の第2の変形例を示す斜視図。

【図32】図31のXXXII−XXXII線に沿う断面図。

【図33】第4の実施例に係わる半導体装置を示す斜視図。

【図34】図33のXXXIV−XXXIV線に沿う断面図。

【図35】適用例に係わる不揮発性半導体メモリを示す斜視図。

【図36】図35のXXXVI−XXXVI線に沿う断面図。

【図37】図35のメモリのメモリセルを示す斜視図。

【図38】適用例に係わる不揮発性半導体メモリを示す斜視図。

【図39】図38のメモリのメモリセルアレイを示す斜視図。

【図40】図39のアレイのA−A’線及びB−B’線に沿う断面図。

【発明を実施するための形態】

【0013】

以下、図面を参照しながら実施形態を説明する。尚、実施形態を通して共通の構成には同一の符号を付すものとし、重複する説明は省略する。また、各図は発明の説明とその理解を促すための模式図であり、その形状や寸法、比などは実際の装置と異なる個所があるが、これらは以下の説明と公知の技術を参酌して適宜、設計変更することができる。

【0014】

実施形態に係わる半導体装置は、ウェハープロセス中に発生する熱処理により、レイヤー選択トランジスタのノーマリーオン領域がチャネル長方向に伸張することを想定し、半導体基板上に積み重ねられる半導体層の数よりも多い数のゲート電極を有するレイヤー選択トランジスタを用いて、半導体層の選択を行うことに特徴を有する。

【0015】

また、単にレイヤー選択トランジスタのゲート電極の数を増やすのではなく、ノーマリーオン領域の伸張量(不純物の拡散長)とレイヤー選択トランジスタのゲート電極の数との関係を規定することにより、ゲート電極の増加数を必要最小限に抑え、レイヤー選択トランジスタの面積の増大を防止する。

【0016】

例えば、第1乃至第nの半導体層(nは2以上の自然数)内の第1乃至第nのノーマリーオン領域が両側に伸張するとき、レイヤー選択トランジスタは、第1乃至第mのゲート電極(m=n+k、kは偶数)を備える。この時、第iの半導体層(iは1〜nのうちの1つ)内の第iのノーマリーオン領域は、第i乃至第(i+k)のゲート電極に隣接するチャネルをノーマリーオンチャネルにする(第1及び第2の実施例に相当)。

【0017】

ここで、kは、ノーマリーオン領域の片側の伸張量(不純物の拡散長)により決定される値である。即ち、熱処理などにより、第iの半導体層内の第(i+(k/2))のゲート電極に隣接するチャネルに形成された第iのノーマリーオン領域が、第1乃至第mのゲート電極のピッチのj倍(jは自然数)以上、(j+1)倍未満伸張するとき、kはj×2に設定される。

【0018】

但し、ノーマリーオン領域のチャネル長方向の初期サイズ(不純物の拡散前のノーマリーオン領域の端の位置)は、ゲート電極のチャネル長(ゲート電極のチャネル長方向の端の位置)に一致すると仮定する。

【0019】

また、第1乃至第nの半導体層(nは2以上の自然数)内の第1乃至第nのノーマリーオン領域が片側のみに伸張するとき、レイヤー選択トランジスタは、第1乃至第mのゲート電極(m=n+k、kは自然数)を備える。この時、第iの半導体層(iは1〜nのうちの1つ)内の第iのノーマリーオン領域は、第i乃至第(i+k)のゲート電極に隣接するチャネルをノーマリーオンチャネルにする(第3及び第4の実施例に相当)。

【0020】

そして、熱処理などにより、第iの半導体層内の第iのゲート電極に隣接するチャネルに形成された第iのノーマリーオン領域が、第1乃至第mのゲート電極のピッチのj倍(jは自然数)以上、(j+1)倍未満伸張するとき、kはjに設定される。

【0021】

但し、ノーマリーオン領域のチャネル長方向の初期サイズ(不純物の拡散前のノーマリーオン領域の端の位置)は、ゲート電極のチャネル長(ゲート電極のチャネル長方向の端の位置)に一致すると仮定する。

【0022】

以上のように、半導体基板上に積み重ねられる半導体層の数よりも多い数のゲート電極を有するレイヤー選択トランジスタを用いて半導体層の選択を行うことにより、レイヤー選択トランジスタのノーマリーオン領域がチャネル長方向に伸張したとしても、半導体層の選択を正確に行うことができる。

【0023】

[第1の実施例]

図1は、第1の実施例に係わる半導体装置を示している。図2は、図1のII−II線に沿う断面図である。

【0024】

第1の実施例は、半導体層の積層数nが3、ノーマリーオン領域の片側の伸張量jが1(k=j×2=2)、ゲート電極の数m(=n+k)が5の例である。

【0025】

半導体基板10は、例えば、シリコン基板である。絶縁層11は、半導体基板10上に配置される。第1、第2及び第3の半導体層12−1,12−2,12−3は、絶縁層11の表面に垂直な第1の方向に、絶縁層11の表面から順番に互いに絶縁されて積み重ねられ、かつ、絶縁層11の表面に平行な第2の方向に延びる。

【0026】

本例では、第1、第2及び第3の半導体層12−1,12−2,12−3は、絶縁層13により互いに絶縁される。絶縁層14は、最上層としての第3の半導体層12−3上に配置される。絶縁層13,14は、例えば、酸化シリコン層である。絶縁層14は、酸化シリコン層以外に、窒化シリコン層や、酸化シリコン層と窒化シリコン層の積層などとすることも可能である。

【0027】

第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層13,14は、フィン型積層構造Finを構成する。第1、第2及び第3の半導体層12−1,12−2,12−3は、単結晶状態であるのが望ましいが、多結晶状態、アモルファス状態であっても構わない。

【0028】

フィン型積層構造Finの第2の方向の一端において、共通電極18は、第1、第2及び第3の半導体層12−1,12−2,12−3に共通に接続される。共通電極18は、例えば、タングステン、アルミニウムなどの金属層を備える。

【0029】

レイヤー選択トランジスタ15(LST)は、例えば、FET (Field Effect Transistor)であり、第1、第2及び第3の半導体層12−1,12−2,12−3をチャネルとし、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択する。

【0030】

レイヤー選択トランジスタ15(LST)は、第2の方向に、共通電極18側から順番に一定ピッチPで配置される第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5を有する。

【0031】

第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5は、例えば、導電性ポリシリコン層、ニッケルシリサイド層などの金属シリサイド層、又は、これらの積層を備える。

【0032】

第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5は、少なくとも、第1、第2及び第3の半導体層12−1,12−2,12−3の第1及び第2の方向に垂直な第3の方向にある側面に沿って第1の方向に延びる。

【0033】

本例では、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5は、フィン型積層構造Finの第1の方向にある上面及び第2の方向にある2つの側面を覆う。即ち、レイヤー選択トランジスタ15(LST)は、ダブルゲート構造を有するフィン型FETである。

【0034】

また、レイヤー選択トランジスタ15(LST)は、第1、第2及び第3の半導体層12−1,12−2,12−3内に、それぞれ、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を有する。

【0035】

第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3は、n型不純物(砒素、リンなどの5価元素)、p型不純物(硼素、インジウムなどの3価元素)、又は、それらの両方を含む不純物領域である。

【0036】

第1の半導体層12−1内に存在する第1のノーマリーオン領域17−1は、第1、第2及び第3のゲート電極16−1,16−2,16−3に隣接するチャネルを、それぞれ、第1、第2及び第3のゲート電極16−1,16−2,16−3の電位に依存しないノーマリーオンチャネルにする。

【0037】

第2の半導体層12−2内に存在する第2のノーマリーオン領域17−2は、第2、第3及び第4のゲート電極16−2,16−3,16−4に隣接するチャネルを、それぞれ、第2、第3及び第4のゲート電極16−2,16−3,16−4の電位に依存しないノーマリーオンチャネルにする。

【0038】

第3の半導体層12−3内に存在する第3のノーマリーオン領域17−3は、第3、第4及び第5のゲート電極16−3,16−4,16−5に隣接するチャネルを、それぞれ、第3、第4及び第5のゲート電極16−3,16−4,16−5の電位に依存しないノーマリーオンチャネルにする。

【0039】

尚、本例では、レイヤー選択トランジスタ15(LST)をFETとする場合について説明したが、これ以外のスイッチ素子をレイヤー選択トランジスタとして用いることもできる。即ち、レイヤー選択トランジスタ15(LST)は、スイッチ機能を有していればよい。

【0040】

また、本例では、第1、第2及び第3の半導体層12−1,12−2,12−3内に第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3のみが形成される例を示しているが、それに加えて、第1、第2及び第3の半導体層12−1,12−2,12−3内には、レイヤー選択トランジスタ15(LST)の閾値を制御するための不純物領域を設けてもよい。

【0041】

表1は、図1の半導体装置における半導体層の選択動作を示している。

【0042】

【表1】

【0043】

図1の半導体装置によれば、第1のゲート電極16−1に係わるレイヤー選択トランジスタ15(LST)は、最下層としての第1の半導体層12−1において常にオン状態(ノーマリーオン状態)であり、それ以外の第2及び第3の半導体層12−2,12−3においてスイッチ素子として機能する。

【0044】

第2のゲート電極16−2に係わるレイヤー選択トランジスタ15(LST)は、最下層としての第1の半導体層12−1及び中間層としての第2の半導体層12−2において常にオン状態(ノーマリーオン状態)であり、それ以外の第3の半導体層12−3においてスイッチ素子として機能する。

【0045】

第3のゲート電極16−3に係わるレイヤー選択トランジスタ15(LST)は、第1、第2及び第3の半導体層12−1,12−2,12−3の全てにおいて常にオン状態(ノーマリーオン状態)である。

【0046】

第4のゲート電極16−4に係わるレイヤー選択トランジスタ15(LST)は、中間層としての第2の半導体層12−2及び最上層としての第3の半導体層12−3において常にオン状態(ノーマリーオン状態)であり、それ以外の第1の半導体層12−1においてスイッチ素子として機能する。

【0047】

第5のゲート電極16−5に係わるレイヤー選択トランジスタ15(LST)は、最上層としての第3の半導体層12−3において常にオン状態(ノーマリーオン状態)であり、それ以外の第1及び第2の半導体層12−1,12−2においてスイッチ素子として機能する。

【0048】

従って、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5の電位を、表1に示す関係に設定することにより、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択することができる。

【0049】

尚、表1において、“H”は、レイヤー選択トランジスタ15(LST)のチャネルをオンチャネル(オン状態)にし得るオン電位のことであり、“L”は、レイヤー選択トランジスタ15(LST)のチャネルをオフチャネル(オフ状態)にし得るオフ電位のことである。

【0050】

例えば、レイヤー選択トランジスタ15(LST)がnチャネルFETのときは、“H”は正電位であり、“L”は接地電位である。また、レイヤー選択トランジスタ15(LST)がpチャネルFETのときは、“H”は負電位であり、“L”は接地電位である。

【0051】

第1の半導体層12−1を選択するときは、第1、第2及び第3のゲート電極16−1,16−2,16−3の電位を“L”に設定し、第4及び第5のゲート電極16−4,16−5の電位を“H”に設定する。

【0052】

この時、第1のゲート電極16−1に係わるレイヤー選択トランジスタ15(LST)は、第2及び第3の半導体層12−2,12−3においてオフ状態であり、第2のゲート電極16−2に係わるレイヤー選択トランジスタ15(LST)は、第3の半導体層12−3においてオフ状態であるため、第2及び第3の半導体層12−2,12−3は選択されない。これに対し、第1の半導体層12−1では、第1のノーマリーオン領域17−1が存在するため、第1乃至第5のゲート電極16−1〜16−5に隣接する全てのチャネルがオン状態になる。

【0053】

従って、第1の半導体層12−1が選択される。

【0054】

第2の半導体層12−2を選択するときは、第2、第3及び第4のゲート電極16−2,16−3,16−4の電位を“L”に設定し、第1及び第5のゲート電極16−1,16−5の電位を“H”に設定する。

【0055】

この時、第2のゲート電極16−2に係わるレイヤー選択トランジスタ15(LST)は、第3の半導体層12−3においてオフ状態であり、第4のゲート電極16−4に係わるレイヤー選択トランジスタ15(LST)は、第1の半導体層12−1においてオフ状態であるため、第1及び第3の半導体層12−1,12−3は選択されない。これに対し、第2の半導体層12−2では、第2のノーマリーオン領域17−2が存在するため、第1乃至第5のゲート電極16−1〜16−5に隣接する全てのチャネルがオン状態になる。

【0056】

従って、第2の半導体層12−2が選択される。

【0057】

第3の半導体層12−3を選択するときは、第3、第4及び第5のゲート電極16−3,16−4,16−5の電位を“L”に設定し、第1及び第2のゲート電極16−1,16−2の電位を“H”に設定する。

【0058】

この時、第4のゲート電極16−4に係わるレイヤー選択トランジスタ15(LST)は、第1の半導体層12−1においてオフ状態であり、第5のゲート電極16−5に係わるレイヤー選択トランジスタ15(LST)は、第1及び第2の半導体層12−1,12−2においてオフ状態であるため、第1及び第2の半導体層12−1,12−2は選択されない。これに対し、第3の半導体層12−3では、第3のノーマリーオン領域17−3が存在するため、第1乃至第5のゲート電極16−1〜16−5に隣接する全てのチャネルがオン状態になる。

【0059】

従って、第3の半導体層12−3が選択される。

【0060】

尚、上述の選択動作から明らかなように、第3のゲート電極16−3に係わるレイヤー選択トランジスタ15(LST)は、第1、第2及び第3の半導体層12−1,12−2,12−3の全てにおいてノーマリーオン状態である。

【0061】

そこで、表2に示すように、上述の選択動作において、第3のゲート電極16−3は、常に固定電位(“H”又は“L”)に設定しておいてもよいし、フローティング状態に設定しておいてもよい。

【0062】

【表2】

【0063】

また、上述の選択動作により、第1、第2及び第3の半導体層12−1,12−2,12−3に対しては、それらに共通に接続される共通電極18を設ければよい。即ち、第1、第2及び第3の半導体層12−1,12−2,12−3の各々に対して、個別に電極を設ける必要がないため、コンタクト領域のサイズを縮小可能である。

【0064】

図3及び図4は、比較例を示している。

【0065】

この比較例は、積層される半導体層の数とレイヤー選択トランジスタのゲート電極の数とが等しい場合の例である。

【0066】

図3は、理想的状態である。しかし、ウェハープロセスにおいて、ベーク処理、キュア処理、デンシファイ処理などの高温熱処理が必要となった場合、その高温熱処理に起因して、ノーマリーオン領域を形成する不純物の拡散が発生する。

【0067】

例えば、実験データによれば、半導体層として多結晶シリコン層を用い、ノーマリーオン領域を砒素(As)の添加により形成した場合、1000℃、10秒の熱処理で、砒素は多結晶シリコン層内を約70nm拡散する。また、1000℃、20秒の熱処理で、砒素は多結晶シリコン層内を160nm程度拡する。

【0068】

従って、例えば、レイヤー選択トランジスタのゲート電極のピッチが160nm以下になると、1000℃、20秒の熱処理で、ノーマリーオン領域17−1〜17−3は、図3の状態から図4の状態に変化する。

【0069】

図4の状態になると、半導体層12−2において、ノーマリーオン領域17−2は、全てのゲート電極16−1〜16−3に跨るため、半導体層12−2は、常に選択された状態になる。即ち、半導体層12−2を非選択にすることが不可能であるため、レイヤー選択トランジスタ15(LST)による選択機能が失われる。

【0070】

これに対し、第1の実施例では、比較例と同じ条件によりノーマリーオン領域が伸張したとしても、図2の状態となるため、レイヤー選択トランジスタ15(LST)による選択機能が失われることはない。

【0071】

図5は、半導体層の積層数とレイヤー選択トランジスタの大きさとの関係を示している。

【0072】

本例では、半導体層の積層数nは、3である。

【0073】

同図(a)は、図1に示す第1の実施例に相当する。第1の実施例の場合、レイヤー選択トランジスタ15(LST)の第2の方向の大きさは、P×4である。但し、Pは、ゲート電極16−1〜16−5のピッチである。

【0074】

尚、レイヤー選択トランジスタ15(LST)の第2の方向の大きさとは、レイヤー選択トランジスタの複数のゲート電極の第2の方向の一端にあるゲート電極の中心から第2の方向の他端にあるゲート電極の中心までのサイズのことである。

【0075】

同図(b)は、図4の比較例に対応する。但し、同図(b)は、図4の半導体装置において半導体層の選択機能を有効にするため、図4のゲート電極16−1〜16−3のピッチを2倍(P×2)に広げている。

【0076】

比較例の場合も、第1の実施例と同様に、レイヤー選択トランジスタ15(LST)の第2の方向の大きさは、P×4である。

【0077】

このように、半導体層の積層数nが3の場合、第1の実施例に係わるレイヤー選択トランジスタ15(LST)の第2方向の大きさは、比較例に係わるレイヤー選択トランジスタ15(LST)の第2方向の大きさと等しくなる。

【0078】

また、第1の実施例では、半導体層の積層数nが4以上になると、レイヤー選択トランジスタの第2方向の大きさが、比較例に係わるレイヤー選択トランジスタの第2方向の大きさよりも小さくなる、という効果を発揮する。この効果は、半導体層の積層数nが増加するほど大きくなるため、第1の実施例は、積層数をできるだけ多くしたい、という要望があるときに非常に有効な技術となる。

【0079】

半導体層の積層数とレイヤー選択トランジスタの大きさとの関係を一般化すると、以下のようになる。

【0080】

第1の実施例(図5(a))では、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n+k−1)となる。また、第1の実施例では、k=2であるから、レイヤー選択トランジスタの第2方向の大きさは、P×(n+1)となる。これに対し、比較例(図5(b))では、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n−1)×2となる。

【0081】

例えば、積層数nが2のとき、第1の実施例での大きさは、P×3、比較例での大きさは、P×2であり、第1の実施例のレイヤー選択トランジスタは、比較例のレイヤー選択トランジスタよりも大きい。

【0082】

しかし、積層数nが4のとき、第1の実施例での大きさは、P×5、比較例での大きさは、P×6であり、積層数nが5のとき、第1の実施例での大きさは、P×6、比較例での大きさは、P×8であり、積層数nが6のとき、第1の実施例での大きさは、P×7、比較例での大きさは、P×10である。

【0083】

尚、図6は、半導体層の積層数nが6の場合において、第1の実施例(同図(a))でのレイヤー選択トランジスタ15(LST)の大きさ(P×7)と、比較例(同図(b))でのレイヤー選択トランジスタ15(LST)の大きさ(P×10)とを、比較して示している。

【0084】

以上のように、積層数nが4以上になると、第1の実施例のレイヤー選択トランジスタは、比較例のレイヤー選択トランジスタよりも小さくなり、かつ、積層数nが大きくなるほど、その差も大きくなる。

【0085】

図7乃至図11は、図1の半導体装置の製造方法を示している。

【0086】

まず、図7に示すように、半導体基板10として、例えば、面方位(100)、比抵抗10〜20Ωcmのp型シリコン基板を用意する。この半導体基板10上に、絶縁層11,13,14としての酸化シリコン層と、第1、第2及び第3の半導体層12−1,12−2,12−3としての多結晶シリコン層とを、交互に形成する。

【0087】

次に、図8に示すように、例えば、PEP(Photo Engraving Process)とイオン注入を用いて、第1、第2及び第3の半導体層12−1,12−2,12−3内に、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を形成する。各ノーマリーオン領域17−1,17−2,17−3は、別々に形成される。また、イオン注入は、所定の加速電圧で、例えば、砒素イオンを第1、第2及び第3の半導体層12−1,12−2,12−3内に注入することにより実行される。

【0088】

尚、本例では、第1、第2及び第3の半導体層12−1,12−2,12−3の全てを形成した後に、第1、第2及び第3の半導体層12−1,12−2,12−3内に、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を形成する。

【0089】

但し、これに代えて、第1の半導体層12−1を形成した直後に第1のノーマリーオン領域17−1を形成し、この後、第2の半導体層12−2を形成した直後に第2のノーマリーオン領域17−2を形成し、さらに、この後、第3の半導体層12−3を形成した直後に第3のノーマリーオン領域17−3を形成してもよい。

【0090】

次に、図9に示すように、PEPとRIE(Reactive ion etching)を用いて、絶縁層13,14及び第1、第2及び第3の半導体層12−1,12−2,12−3をパターニングすることにより、フィン型積層構造Finを形成する。

【0091】

次に、図10に示すように、絶縁層11上に、フィン型積層構造Finを覆うゲート絶縁層(例えば、酸化シリコン層)と、ゲート絶縁層上の導電層とを形成する。そして、PEPとRIEとを用いて、この導電層をパターニングにすることにより、第2の方向に一定ピッチPで並んで配置される第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5を形成する。

【0092】

また、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5は、フィン型積層構造Finの第1の方向にある上面及び第2の方向にある2つの側面をそれぞれ覆うように形成される。

【0093】

この時点において、第1のノーマリーオン領域17−1は、第2のゲート電極16−2に隣接するチャネルのみに形成され、第2のノーマリーオン領域17−2は、第3のゲート電極16−3に隣接するチャネルのみに形成され、第3のノーマリーオン領域17−3は、第4のゲート電極16−4に隣接するチャネルのみに形成される。

【0094】

尚、ゲート絶縁層及び導電層を形成した後、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5を形成する前に、CMP(Chemical Mechanical Polishing)により、導電層の上面を平坦化してもよい。

【0095】

また、フィン型積層構造Fin以外の領域を絶縁層で満たした状態でCMPを行ってもよい。この場合、CMP後に、フィン型積層構造Fin以外の領域を満たした絶縁層を除去し、さらに、その後、PEPとRIEとを用いて、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5を形成する。

【0096】

次に、図11に示すように、フィン型積層構造Finの第2の方向の一端に、第1、第2及び第3の半導体層12−1,12−2,12−3に共通に接続される共通電極18を形成する。

【0097】

また、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3は、それらを形成した後に発生する、ベーク処理、キュア処理、デンシファイ処理などの高温熱処理により、第2の方向に伸張する。

【0098】

本例では、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3は、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5のピッチPの1倍以上、2倍未満伸張する。

【0099】

但し、不純物の拡散前の第1のノーマリーオン領域17−1の第2の方向の端は、第2のゲート電極16−2の第2の方向の端に一致し、不純物の拡散前の第2のノーマリーオン領域17−2の第2の方向の端は、第3のゲート電極16−3の第2の方向の端に一致し、不純物の拡散前の第3のノーマリーオン領域17−3の第2の方向の端は、第4のゲート電極16−4の第2の方向の端に一致する、と仮定する。

【0100】

以上の工程により、図1の半導体装置が完成する。

【0101】

図12は、第1の実施例の第1の変形例を示している。図13は、図12のXIII−XIII線に沿う断面図である。

【0102】

第1の変形例の特徴は、第1の実施例と比べると、第1、第2及び第3の半導体層12−1,12−2,12−3の第3の方向にある側面のうち、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5に覆われていない領域に、第1、第2及び第3の半導体層12−1,12−2,12−3の抵抗値よりも低い抵抗値を持つ低抵抗領域19が設けられる点にある。

【0103】

その他の構成については、第1の実施例に係わる半導体装置と同じであるため、ここでの説明を省略する。

【0104】

低抵抗領域19は、例えば、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3とは異なる不純物領域である。この場合、低抵抗領域19内の不純物は、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3内の不純物と同じであっても、異なっていてもよい。

【0105】

また、低抵抗領域19は、例えば、ニッケルシリサイド層などの金属シリサイド層である。この場合、低抵抗領域19は、フィン型積層構造Finを覆う金属層を形成した後、金属層と第1、第2及び第3の半導体層12−1,12−2,12−3とをシリサイド反応させ、さらに、この後、未反応の金属層を除去することにより形成される。

【0106】

この変形例によれば、低抵抗領域19により、寄生抵抗が下がり、動作速度の向上などのメモリ特性を向上させることができる。

【0107】

図14は、第1の実施例の第2の変形例を示している。図15は、図14のXV−XV線に沿う断面図である。

【0108】

第2の変形例の特徴は、第1の実施例と比べると、第1、第2及び第3の半導体層12−1,12−2,12−3間が空洞(CAVITY)であり、かつ、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5とフィン型積層構造Finとの間が空洞(CAVITY)である点にある。

【0109】

その他の構成については、第1の実施例に係わる半導体装置と同じであるため、ここでの説明を省略する。

【0110】

空洞(CAVITY)は、例えば、第1の実施例(図1及び図2)に示す構造を形成した後、図1及び図2に示す絶縁層13,14を選択的に除去することにより形成される。この場合、第1、第2及び第3の半導体層12−1,12−2,12−3は、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5により支えられる。

【0111】

この変形例によれば、絶縁領域の空洞化により、複数の半導体層間の絶縁性を向上させることができるため、メモリ素子の信頼性が向上する。

【0112】

以上、説明したように、第1の実施例及びその変形例によれば、デザインルールが縮小されても、半導体基板上に積み重ねられた複数の半導体層のうちの1つを正確に選択することができる。

【0113】

[第2の実施例]

図16は、第2の実施例に係わる半導体装置を示している。図17は、図16のXVII−XVII線に沿う断面図である。

【0114】

第2の実施例は、半導体層の積層数nが3、ノーマリーオン領域の片側の伸張量jが2(k=j×2=4)、ゲート電極の数m(=n+k)が7の例である。

【0115】

第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3の第2の方向の伸張量は、それらを形成した後に発生する高温熱処理(ベーク処理、キュア処理、デンシファイ処理など)の温度や時間(合計値)などに依存する。

【0116】

既に説明したように、例えば、実験データによれば、半導体層として多結晶シリコン層を用い、ノーマリーオン領域を砒素(As)の添加により形成した場合、1000℃、10秒の熱処理で、砒素は多結晶シリコン層内を約70nm拡散する。また、1000℃、20秒の熱処理で、砒素は多結晶シリコン層内を160nm程度拡する。

【0117】

そこで、第2の実施例では、第1の実施例よりも、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3の伸張量が多い場合、具体的には、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3が、ゲート電極のピッチPの2倍伸張する場合について説明する。

【0118】

この場合、第1、第2、第3、第4、第5、第6及び第7のゲート電極16−1,16−2,16−3,16−4,16−5,16−6,16−7は、第2の方向に、一定ピッチPで並んで配置される。

【0119】

また、第1のノーマリーオン領域17−1は、第1の半導体層12−1内において、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5に隣接するチャネルをノーマリーオン状態にする。

【0120】

第2のノーマリーオン領域17−2は、第2の半導体層12−2内において、第2、第3、第4、第5及び第6のゲート電極16−2,16−3,16−4,16−5,16−6に隣接するチャネルをノーマリーオン状態にする。

【0121】

第3のノーマリーオン領域17−3は、第3の半導体層12−3内において、第3、第4、第5、第6及び第7のゲート電極16−3,16−4,16−5,16−6,16−7に隣接するチャネルをノーマリーオン状態にする。

【0122】

ここで、第1の実施例と同様に、半導体層の積層数とレイヤー選択トランジスタの大きさとの関係を一般化する。

【0123】

第2の実施例でも、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n+k−1)となる。また、第2の実施例では、k=4であるから、レイヤー選択トランジスタの第2方向の大きさは、P×(n+3)となる。これに対し、比較例(図5(b)と同じ構造を想定する)では、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n−1)×3となる。

【0124】

例えば、積層数nが2のとき、第2の実施例での大きさは、P×5、比較例での大きさは、P×3であり、第2の実施例のレイヤー選択トランジスタは、比較例のレイヤー選択トランジスタよりも大きい。

【0125】

また、積層数nが3のとき、第2の実施例での大きさは、P×6、比較例での大きさは、P×6であり、第2の実施例のレイヤー選択トランジスタの大きさは、比較例のレイヤー選択トランジスタの大きいと同じである。

【0126】

さらに、積層数nが4のとき、第2の実施例での大きさは、P×7、比較例での大きさは、P×9であり、積層数nが5のとき、第2の実施例での大きさは、P×8、比較例での大きさは、P×12であり、積層数nが6のとき、第2の実施例での大きさは、P×9、比較例での大きさは、P×15である。

【0127】

以上のように、積層数nが4以上になると、第2の実施例のレイヤー選択トランジスタは、比較例のレイヤー選択トランジスタよりも小さくなり、かつ、積層数nが大きくなるほど、その差も大きくなる。

【0128】

尚、その他の構成及び製造方法については、第1の実施例に係わる半導体装置と同じであるため、ここでの説明を省略する。

【0129】

また、第2の実施例においても、第1の実施例における第1の変形例(図12及び図13)及び第2の変形例(図14及び図15)と同様の変形が可能である。

【0130】

以上、説明したように、第2の実施例によれば、第1の実施例と同様に、デザインルールが縮小されても、半導体基板上に積み重ねられた複数の半導体層のうちの1つを正確に選択することができる。

【0131】

[第3の実施例]

図18は、第3の実施例に係わる半導体装置を示している。図19は、図18のXIX−XIX線に沿う断面図である。

【0132】

第3の実施例は、半導体層の積層数nが3、ノーマリーオン領域の片側の伸張量jが1(k=j=1)、ゲート電極の数m(=n+k)が4の例である。

【0133】

半導体基板10は、例えば、シリコン基板である。絶縁層11は、半導体基板10上に配置される。第1、第2及び第3の半導体層12−1,12−2,12−3は、絶縁層11の表面に垂直な第1の方向に、絶縁層11の表面から順番に互いに絶縁されて積み重ねられ、かつ、絶縁層11の表面に平行な第2の方向に延びる。

【0134】

本例では、第1、第2及び第3の半導体層12−1,12−2,12−3は、絶縁層13により互いに絶縁される。絶縁層14は、最上層としての第3の半導体層12−3上に配置される。絶縁層13,14は、例えば、酸化シリコン層である。絶縁層14は、酸化シリコン層以外に、窒化シリコン層や、酸化シリコン層と窒化シリコン層の積層などとすることも可能である。

【0135】

第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層13,14の第2の方向の一端は、階段形状を有する。また、第1、第2及び第3の半導体層12−1,12−2,12−3の第2の方向の一端(階段形状の部分)は、第1、第2及び第3の拡散防止層20−1,20−1,20−3により覆われる。

【0136】

第1、第2及び第3の拡散防止層20−1,20−1,20−3は、FNトンネル電流又はダイレクトトンネル電流が流れる程度の厚さ、例えば、1nm以下の厚さを有する絶縁層を備える。この場合、第1、第2及び第3の拡散防止層20−1,20−1,20−3は、酸化シリコン層、窒化シリコン層、酸窒化シリコン層などから形成されるのが望ましい。

【0137】

また、第1、第2及び第3の拡散防止層20−1,20−1,20−3は、金属層や金属シリサイド層を備えていてもよい。この場合、第1、第2及び第3の拡散防止層20−1,20−1,20−3は、低抵抗であるため、共通電極18と、第1、第2及び第3の半導体層12−1,12−2,12−3との間の配線抵抗を下げることができる。

【0138】

共通半導体層21は、第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層13,14の第2の方向の一端に配置され、第1、第2及び第3の拡散防止層20−1,20−1,20−3を介して、第1、第2及び第3の半導体層12−1,12−2,12−3に共通に接続される。

【0139】

第1、第2及び第3の半導体層12−1,12−2,12−3、絶縁層13,14及び共通半導体層21は、フィン型積層構造Finを構成する。第1、第2及び第3の半導体層12−1,12−2,12−3は、単結晶状態であるのが望ましいが、多結晶状態、アモルファス状態であっても構わない。

【0140】

フィン型積層構造Finの第2の方向の一端において、共通電極18は、共通半導体層21に接続される。共通電極18は、例えば、タングステン、アルミニウムなどの金属層を備える。

【0141】

レイヤー選択トランジスタ15(LST)は、例えば、FETであり、第1、第2及び第3の半導体層12−1,12−2,12−3又は共通半導体層21をチャネルとし、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択する。

【0142】

レイヤー選択トランジスタ15(LST)は、第2の方向に、共通電極18側から順番に一定ピッチPで配置される第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4を有する。

【0143】

第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4は、例えば、導電性ポリシリコン層、ニッケルシリサイド層などの金属シリサイド層、又は、これらの積層を備える。

【0144】

第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4は、少なくとも、第1、第2及び第3の半導体層12−1,12−2,12−3及び共通半導体層21の第1及び第2の方向に垂直な第3の方向にある側面に沿って第1の方向に延びる。

【0145】

本例では、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4は、フィン型積層構造Finの第1の方向にある上面及び第2の方向にある2つの側面を覆う。即ち、レイヤー選択トランジスタ15(LST)は、ダブルゲート構造を有するフィン型FETである。

【0146】

また、第1のゲート電極16−1は、第1の拡散防止層20−1と第2の拡散防止層20−2との間に配置され、第2のゲート電極16−2は、第2の拡散防止層20−2と第3の拡散防止層20−3との間に配置される。第3及び第4のゲート電極16−3,16−4は、第3の拡散防止層20−3よりも、第1、第2及び第3の半導体層12−1,12−2,12−3側に配置される。

【0147】

レイヤー選択トランジスタ15(LST)は、第1、第2及び第3の半導体層12−1,12−2,12−3内に、それぞれ、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を有する。

【0148】

第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3は、n型不純物(砒素、リンなどの5価元素)、p型不純物(硼素、インジウムなどの3価元素)、又は、それらの両方を含む不純物領域である。

【0149】

第1の半導体層12−1内に存在する第1のノーマリーオン領域17−1は、第1及び第2のゲート電極16−1,16−2に隣接するチャネルを、それぞれ、第1及び第2のゲート電極16−1,16−2の電位に依存しないノーマリーオンチャネルにする。

【0150】

第2の半導体層12−2内に存在する第2のノーマリーオン領域17−2は、第2及び第3のゲート電極16−2,16−3に隣接するチャネルを、それぞれ、第2及び第3のゲート電極16−2,16−3の電位に依存しないノーマリーオンチャネルにする。

【0151】

第3の半導体層12−3内に存在する第3のノーマリーオン領域17−3は、第3及び第4のゲート電極16−3,16−4に隣接するチャネルを、それぞれ、第3及び第4のゲート電極16−3,16−4の電位に依存しないノーマリーオンチャネルにする。

【0152】

尚、本例では、レイヤー選択トランジスタ15(LST)をFETとする場合について説明したが、これ以外のスイッチ素子をレイヤー選択トランジスタとして用いることもできる。即ち、レイヤー選択トランジスタ15(LST)は、スイッチ機能を有していればよい。

【0153】

また、本例では、第1、第2及び第3の半導体層12−1,12−2,12−3内に第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3のみが形成される例を示しているが、それに加えて、第1、第2及び第3の半導体層12−1,12−2,12−3内には、レイヤー選択トランジスタ15(LST)の閾値を制御するための不純物領域を設けてもよい。

【0154】

表3は、図18の半導体装置における半導体層の選択動作を示している。

【0155】

【表3】

【0156】

図18の半導体装置によれば、第1のゲート電極16−1に係わるレイヤー選択トランジスタ15(LST)は、最下層としての第1の半導体層12−1において常にオン状態(ノーマリーオン状態)であり、それ以外の第2及び第3の半導体層12−2,12−3においてスイッチ素子として機能する。

【0157】

第2のゲート電極16−2に係わるレイヤー選択トランジスタ15(LST)は、最下層としての第1の半導体層12−1及び中間層としての第2の半導体層12−2において常にオン状態(ノーマリーオン状態)であり、それ以外の第3の半導体層12−3においてスイッチ素子として機能する。

【0158】

第3のゲート電極16−3に係わるレイヤー選択トランジスタ15(LST)は、中間層としての第2の半導体層12−2及び最上層としての第3の半導体層12−3において常にオン状態(ノーマリーオン状態)であり、それ以外の第1の半導体層12−1においてスイッチ素子として機能する。

【0159】

第4のゲート電極16−4に係わるレイヤー選択トランジスタ15(LST)は、最上層としての第3の半導体層12−3において常にオン状態(ノーマリーオン状態)であり、それ以外の第1及び第2の半導体層12−1,12−2においてスイッチ素子として機能する。

【0160】

従って、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4の電位を、表3に示す関係に設定することにより、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択することができる。

【0161】

尚、表3において、“H”は、レイヤー選択トランジスタ15(LST)のチャネルをオンチャネル(オン状態)にし得るオン電位のことであり、“L”は、レイヤー選択トランジスタ15(LST)のチャネルをオフチャネル(オフ状態)にし得るオフ電位のことである。

【0162】

例えば、レイヤー選択トランジスタ15(LST)がnチャネルFETのときは、“H”は正電位であり、“L”は接地電位である。また、レイヤー選択トランジスタ15(LST)がpチャネルFETのときは、“H”は負電位であり、“L”は接地電位である。

【0163】

第1の半導体層12−1を選択するときは、第1及び第2のゲート電極16−1,16−2の電位を“L”に設定し、第3及び第4のゲート電極16−3,16−4の電位を“H”に設定する。

【0164】

この時、第1のゲート電極16−1に係わるレイヤー選択トランジスタ15(LST)は、第2及び第3の半導体層12−2,12−3においてオフ状態であり、第2のゲート電極16−2に係わるレイヤー選択トランジスタ15(LST)は、第3の半導体層12−3においてオフ状態であるため、第2及び第3の半導体層12−2,12−3は選択されない。これに対し、第1の半導体層12−1では、第1のノーマリーオン領域17−1が存在するため、第1乃至第4のゲート電極16−1〜16−4に隣接する全てのチャネルがオン状態になる。

【0165】

従って、第1の半導体層12−1が選択される。

【0166】

第2の半導体層12−2を選択するときは、第2及び第3のゲート電極16−2,16−3の電位を“L”に設定し、第1及び第4のゲート電極16−1,16−4の電位を“H”に設定する。

【0167】

この時、第2のゲート電極16−2に係わるレイヤー選択トランジスタ15(LST)は、第3の半導体層12−3においてオフ状態であり、第3のゲート電極16−3に係わるレイヤー選択トランジスタ15(LST)は、第1の半導体層12−1においてオフ状態であるため、第1及び第3の半導体層12−1,12−3は選択されない。これに対し、第2の半導体層12−2では、第2のノーマリーオン領域17−2が存在するため、第1乃至第4のゲート電極16−1〜16−4に隣接する全てのチャネルがオン状態になる。

【0168】

従って、第2の半導体層12−2が選択される。

【0169】

第3の半導体層12−3を選択するときは、第3及び第4のゲート電極16−3,16−4の電位を“L”に設定し、第1及び第2のゲート電極16−1,16−2の電位を“H”に設定する。

【0170】

この時、第3のゲート電極16−3に係わるレイヤー選択トランジスタ15(LST)は、第1の半導体層12−1においてオフ状態であり、第4のゲート電極16−4に係わるレイヤー選択トランジスタ15(LST)は、第1及び第2の半導体層12−1,12−2においてオフ状態であるため、第1及び第2の半導体層12−1,12−2は選択されない。これに対し、第3の半導体層12−3では、第3のノーマリーオン領域17−3が存在するため、第1乃至第4のゲート電極16−1〜16−4に隣接する全てのチャネルがオン状態になる。

【0171】

従って、第3の半導体層12−3が選択される。

【0172】

上述の選択動作により、第1、第2及び第3の半導体層12−1,12−2,12−3に対しては、それらに共通に接続される共通電極18を設ければよい。即ち、第1、第2及び第3の半導体層12−1,12−2,12−3の各々に対して、個別に電極を設ける必要がないため、コンタクト領域のサイズを縮小可能である。

【0173】

図20は、半導体層の積層数とレイヤー選択トランジスタの大きさとの関係を示している。

【0174】

本例では、半導体層の積層数nは、3である。

【0175】

同図(a)は、図18に示す第3の実施例に相当する。第3の実施例の場合、レイヤー選択トランジスタ15(LST)の第2の方向の大きさは、P×3である。但し、Pは、ゲート電極16−1〜16−4のピッチである。

【0176】

同図(b)は、比較例である。比較例では、半導体層12−1〜12−3の積層数とゲート電極16−1〜16−3の数を等しくし、かつ、半導体層の選択機能を有効にするため、ゲート電極のピッチを2Pに設定している。

【0177】

比較例の場合、レイヤー選択トランジスタ15(LST)の第2の方向の大きさは、P×4である。

【0178】

このように、半導体層の積層数nが3の場合、第3の実施例に係わるレイヤー選択トランジスタ15(LST)は、比較例に係わるレイヤー選択トランジスタ15(LST)よりも小さくなる。

【0179】

第3の実施例では、半導体層の積層数nが2のとき、第3の実施例に係わるレイヤー選択トランジスタ15(LST)の大きさは、比較例に係わるレイヤー選択トランジスタ15(LST)の大きさに等しくなる。

【0180】

また、半導体層の積層数nが3以上になると、レイヤー選択トランジスタの大きさが、比較例に係わるレイヤー選択トランジスタの大きさよりも小さくなる、という効果を発揮する。この効果は、半導体層の積層数nが増加するほど大きくなるため、第3の実施例は、積層数をできるだけ多くしたい、という要望があるときに非常に有効な技術となる。

【0181】

半導体層の積層数とレイヤー選択トランジスタの大きさとの関係を一般化すると、以下のようになる。

【0182】

第3の実施例(図20(a))では、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n+k−1)となる。また、第3の実施例では、k=1であるから、レイヤー選択トランジスタの第2方向の大きさは、P×nとなる。これに対し、比較例(図20(b))では、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n−1)×2となる。

【0183】

例えば、積層数nが2のとき、第3の実施例での大きさは、P×2、比較例での大きさは、P×2であり、第3の実施例のレイヤー選択トランジスタの大きさは、比較例のレイヤー選択トランジスタの大きさに等しい。

【0184】

しかし、積層数nが3のとき、第3の実施例での大きさは、P×3、比較例での大きさは、P×4であり、積層数nが4のとき、第3の実施例での大きさは、P×4、比較例での大きさは、P×6であり、積層数nが5のとき、第3の実施例での大きさは、P×5、比較例での大きさは、P×8であり、積層数nが6のとき、第3の実施例での大きさは、P×6、比較例での大きさは、P×10である。

【0185】

以上のように、積層数nが3以上になると、第3の実施例のレイヤー選択トランジスタは、比較例のレイヤー選択トランジスタよりも小さくなり、かつ、積層数nが大きくなるほど、その差も大きくなる。

【0186】

図21乃至図28は、図18の半導体装置の製造方法を示している。

【0187】

まず、図21に示すように、半導体基板10として、例えば、面方位(100)、比抵抗10〜20Ωcmのp型シリコン基板を用意する。この半導体基板10上に、絶縁層11,13,14としての酸化シリコン層と、第1、第2及び第3の半導体層12−1,12−2,12−3としての多結晶シリコン層とを、交互に形成する。

【0188】

次に、図22に示すように、例えば、PEPとRIEを用いて、第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層13,14の第2の方向の端部に、階段形状を形成する。

【0189】

次に、図23に示すように、例えば、PEPを用いて、絶縁層14上にマスク層(フォトレジスト層)22を形成する。そして、マスク層22をマスクにして、イオン注入により、第1、第2及び第3の半導体層12−1,12−2,12−3内に、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を形成する。

【0190】

この場合、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3は、同時に形成される。また、イオン注入は、所定の加速電圧で、例えば、砒素イオンを第1、第2及び第3の半導体層12−1,12−2,12−3内に注入することにより実行される。

【0191】

尚、本例では、階段形状を形成した後に、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を形成する。

【0192】

但し、これに代えて、第1、第2及び第3の半導体層12−1,12−2,12−3を形成した後、階段形状を形成する前に、PEPとイオン注入により、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を形成してもよい。

【0193】

また、第1の半導体層12−1を形成した直後に第1のノーマリーオン領域17−1を形成し、この後、第2の半導体層12−2を形成した直後に第2のノーマリーオン領域17−2を形成し、さらに、この後、第3の半導体層12−3を形成した直後に第3のノーマリーオン領域17−3を形成してもよい。

【0194】

次に、図24に示すように、第1、第2及び第3の半導体層12−1,12−2,12−3の第2の方向にある側面(階段形状の部分)上に、第1、第2及び第3の拡散防止層20−1,20−2,20−3を形成する。

【0195】

第1、第2及び第3の拡散防止層20−1,20−2,20−3が絶縁層のとき、第1、第2及び第3の拡散防止層20−1,20−2,20−3は、熱酸化などにより積極的に形成してもよいし、例えば、ウェハープロセス中に酸素に触れることにより形成される自然酸化膜を利用してもよい。

【0196】

また、第1、第2及び第3の拡散防止層20−1,20−2,20−3が金属シリサイド層のとき、第1、第2及び第3の拡散防止層20−1,20−2,20−3は、金属層と、第1、第2及び第3の半導体層12−1,12−2,12−3とのシリサイド反応を利用する。

【0197】

本例では、第1、第2及び第3の拡散防止層20−1,20−2,20−3は、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を形成した後に形成する。但し、これに代えて、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3を形成する前に、第1、第2及び第3の拡散防止層20−1,20−2,20−3を形成してもよい。

【0198】

次に、図25に示すように、絶縁層11上に、第1、第2及び第3の拡散防止層20−1,20−2,20−3を介して、第1、第2及び第3の半導体層12−1,12−2,12−3に接続される共通半導体層21を形成する。

【0199】

共通半導体層21は、第1、第2及び第3の半導体層12−1,12−2,12−3と同じ材料及び同じ結晶構造を有しているのが望ましい。また、共通半導体層21の上面は、CMPにより平坦化するのが望ましい。

【0200】

次に、図26に示すように、PEPとRIEを用いて、絶縁層13,14、第1、第2及び第3の半導体層12−1,12−2,12−3、及び、共通半導体層21を、それぞれ、パターニングすることにより、フィン型積層構造Finを形成する。

【0201】

次に、図27に示すように、絶縁層11上に、フィン型積層構造Finを覆うゲート絶縁層(例えば、酸化シリコン層)と、ゲート絶縁層上の導電層とを形成する。そして、PEPとRIEとを用いて、この導電層をパターニングにすることにより、第2の方向に一定ピッチPで並んで配置される第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4を形成する。

【0202】

また、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4は、フィン型積層構造Finの第1の方向にある上面及び第2の方向にある2つの側面をそれぞれ覆うように形成される。

【0203】

この時点において、第1のノーマリーオン領域17−1は、第1のゲート電極16−1に隣接するチャネルのみに形成され、第2のノーマリーオン領域17−2は、第2のゲート電極16−2に隣接するチャネルのみに形成され、第3のノーマリーオン領域17−3は、第3のゲート電極16−3に隣接するチャネルのみに形成される。

【0204】

尚、ゲート絶縁層及び導電層を形成した後、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4を形成する前に、CMPにより、導電層の上面を平坦化してもよい。

【0205】

また、フィン型積層構造Fin以外の領域を絶縁層で満たした状態でCMPを行ってもよい。この場合、CMP後に、フィン型積層構造Fin以外の領域を満たした絶縁層を除去し、さらに、その後、PEPとRIEとを用いて、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4を形成する。

【0206】

次に、図28に示すように、フィン型積層構造Finの第2の方向の一端に、第1、第2及び第3の半導体層12−1,12−2,12−3に共通に接続される共通電極18を形成する。

【0207】

また、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3は、それらを形成した後に発生する、ベーク処理、キュア処理、デンシファイ処理などの高温熱処理により、第2の方向に伸張する。

【0208】

本例では、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3は、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4のピッチPの1倍以上、2倍未満伸張する。

【0209】

但し、不純物の拡散前の第1のノーマリーオン領域17−1の第2の方向の端は、第1のゲート電極16−1の第2の方向の端に一致し、不純物の拡散前の第2のノーマリーオン領域17−2の第2の方向の端は、第2のゲート電極16−2の第2の方向の端に一致し、不純物の拡散前の第3のノーマリーオン領域17−3の第2の方向の端は、第3のゲート電極16−3の第2の方向の端に一致する、と仮定する。

【0210】

以上の工程により、図18の半導体装置が完成する。

【0211】

図29は、第3の実施例の第1の変形例を示している。図30は、図29のXXX−XXX線に沿う断面図である。

【0212】

第1の変形例の特徴は、第3の実施例と比べると、第1、第2及び第3の半導体層12−1,12−2,12−3の第3の方向にある側面のうち、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4に覆われていない領域に、第1、第2及び第3の半導体層12−1,12−2,12−3の抵抗値よりも低い抵抗値を持つ低抵抗領域19が設けられる点にある。

【0213】

その他の構成については、第3の実施例に係わる半導体装置と同じであるため、ここでの説明を省略する。

【0214】

低抵抗領域19は、例えば、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3とは異なる不純物領域である。この場合、低抵抗領域19内の不純物は、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3内の不純物と同じであっても、異なっていてもよい。

【0215】

また、低抵抗領域19は、例えば、ニッケルシリサイド層などの金属シリサイド層である。この場合、低抵抗領域19は、フィン型積層構造Finを覆う金属層を形成した後、金属層と第1、第2及び第3の半導体層12−1,12−2,12−3とをシリサイド反応させ、さらに、この後、未反応の金属層を除去することにより形成される。

【0216】

この変形例によれば、低抵抗領域19により、寄生抵抗が下がり、動作速度の向上などのメモリ特性を向上させることができる。

【0217】

図31は、第3の実施例の第2の変形例を示している。図32は、図31のXXXII−XXXII線に沿う断面図である。

【0218】

第2の変形例の特徴は、第3の実施例と比べると、第1、第2及び第3の半導体層12−1,12−2,12−3間が空洞(CAVITY)であり、かつ、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4とフィン型積層構造Finとの間が空洞(CAVITY)である点にある。

【0219】

その他の構成については、第3の実施例に係わる半導体装置と同じであるため、ここでの説明を省略する。

【0220】

空洞(CAVITY)は、例えば、第3の実施例(図18及び図19)に示す構造を形成した後、図18及び図19に示す絶縁層13,14を選択的に除去することにより形成される。この場合、第1、第2及び第3の半導体層12−1,12−2,12−3は、第1、第2、第3及び第4のゲート電極16−1,16−2,16−3,16−4により支えられる。

【0221】

この変形例によれば、絶縁領域の空洞化により、複数の半導体層間の絶縁性を向上させることができるため、メモリ素子の信頼性が向上する。

【0222】

以上、説明したように、第3の実施例及びその変形例によれば、デザインルールが縮小されても、半導体基板上に積み重ねられた複数の半導体層のうちの1つを正確に選択することができる。

【0223】

[第4の実施例]

図33は、第4の実施例に係わる半導体装置を示している。図34は、図33のXXXIV−XXXIV線に沿う断面図である。

【0224】

第4の実施例は、半導体層の積層数nが3、ノーマリーオン領域の片側の伸張量jが2(k=j=2)、ゲート電極の数m(=n+k)が5の例である。

【0225】

第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3の第2の方向の伸張量は、それらを形成した後に発生する高温熱処理(ベーク処理、キュア処理、デンシファイ処理など)の温度や時間(合計値)などに依存する。

【0226】

既に説明したように、例えば、実験データによれば、半導体層として多結晶シリコン層を用い、ノーマリーオン領域を砒素(As)の添加により形成した場合、1000℃、10秒の熱処理で、砒素は多結晶シリコン層内を約70nm拡散する。また、1000℃、20秒の熱処理で、砒素は多結晶シリコン層内を160nm程度拡する。

【0227】

そこで、第4の実施例では、第3の実施例よりも、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3の伸張量が多い場合、具体的には、第1、第2及び第3のノーマリーオン領域17−1,17−2,17−3が、ゲート電極のピッチPの2倍伸張する場合について説明する。

【0228】

この場合、第1、第2、第3、第4及び第5のゲート電極16−1,16−2,16−3,16−4,16−5は、第2の方向に、一定ピッチPで並んで配置される。

【0229】

また、第1のノーマリーオン領域17−1は、第1の半導体層12−1内において、第1、第2及び第3のゲート電極16−1,16−2,16−3に隣接するチャネルをノーマリーオン状態にする。

【0230】

第2のノーマリーオン領域17−2は、第2の半導体層12−2内において、第2、第3及び第4のゲート電極16−2,16−3,16−4に隣接するチャネルをノーマリーオン状態にする。

【0231】

第3のノーマリーオン領域17−3は、第3の半導体層12−3内において、第3、第4及び第5のゲート電極16−3,16−4,16−5に隣接するチャネルをノーマリーオン状態にする。

【0232】

ここで、第3の実施例と同様に、半導体層の積層数とレイヤー選択トランジスタの大きさとの関係を一般化する。

【0233】

第4の実施例でも、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n+k−1)となる。また、第4の実施例では、k=2であるから、レイヤー選択トランジスタの第2方向の大きさは、P×(n+1)となる。これに対し、比較例(図20(b)のゲート電極16−1,16−2,16−3のピッチを、P×2からP×3に変更したもの)では、積層数がnのとき、レイヤー選択トランジスタの第2方向の大きさは、P×(n−1)×3となる。

【0234】

例えば、積層数nが2のとき、第4の実施例での大きさは、P×3、比較例での大きさは、P×3であり、第4の実施例のレイヤー選択トランジスタの大きさは、比較例のレイヤー選択トランジスタの大きさに等しい。

【0235】

また、積層数nが3のとき、第4の実施例での大きさは、P×4、比較例での大きさは、P×6であり、積層数nが4のとき、第4の実施例での大きさは、P×5、比較例での大きさは、P×9であり、積層数nが5のとき、第4の実施例での大きさは、P×6、比較例での大きさは、P×12であり、積層数nが6のとき、第4の実施例での大きさは、P×7、比較例での大きさは、P×15である。

【0236】

以上のように、積層数nが3以上になると、第4の実施例のレイヤー選択トランジスタは、比較例のレイヤー選択トランジスタよりも小さくなり、かつ、積層数nが大きくなるほど、その差も大きくなる。

【0237】

尚、その他の構成及び製造方法については、第3の実施例に係わる半導体装置と同じであるため、ここでの説明を省略する。

【0238】

また、第4の実施例においても、第3の実施例における第1の変形例(図29及び図30)及び第2の変形例(図31及び図32)と同様の変形が可能である。

【0239】

以上、説明したように、第4の実施例によれば、第3の実施例と同様に、デザインルールが縮小されても、半導体基板上に積み重ねられた複数の半導体層のうちの1つを正確に選択することができる。

【0240】

第3及び第4の実施例では、階段形状の部分に設けられた拡散防止層により、ノーマリーオン領域の伸張(不純物の拡散)が片側のみに発生する。このため、レイヤー選択トランジスタの大きさに関する説明で明らかなように、第3及び第4の実施例は、第1及び第2の実施例よりも、レイヤー選択トランジスタのサイズの縮小に関する効果が優れる。

【0241】

また、比較例との比較でも明らかなように、第1及び第2の実施例では、積層数nが4以上のときに、比較例よりも、レイヤー選択トランジスタのサイズが縮小されるのに対して、第3及び第4の実施例では、積層数nが3以上のときに、比較例よりも、レイヤー選択トランジスタのサイズが縮小される。

【0242】

[適用例]

実施形態に係わる半導体装置の適用例を説明する。

【0243】

以下に説明する適用例は、第1乃至第nの半導体層(nは2以上の自然数)に接続される複数のメモリセルを有する三次元不揮発性半導体メモリに関する。実施形態の技術により、第1乃至第nの半導体層のうちの1つを選択することにより、大容量メモリを実現することができる。

【0244】

図35は、適用例としてのVLBを示している。図36は、図35のXXXVI−XXXVI線に沿う断面図を示し、図37は、図36のメモリセルMCを示している。

【0245】

半導体基板10上の絶縁層11上には、第1の方向に積み重ねられ、第3の方向に延びる第1、第2及び第3のメモリストリングNa、Nb,Ncが配置される。本例では、メモリストリングの数は、3つであるが、これに限られない。即ち、第1の方向に積み重ねられるメモリストリングの数は、2つ以上であればよい。

【0246】

第1、第2及び第3のメモリストリングNa、Nb,Ncは、第1の方向に積み重ねられる第1、第2及び第3の半導体層12−1,12−2,12−3と、第3の方向に直列接続される複数のメモリセルMCとを備える。本例では、直列接続されるメモリセルMCの数は、6つであるが、これに限られない。即ち、第3の方向に直列接続されるメモリセルの数は、2つ以上であればよい。

【0247】

第1、第2及び第3の半導体層12−1,12−2,12−3は、絶縁層13により互いに絶縁される。また、最上層としての第3の半導体層12−3上には、絶縁層14が配置される。

【0248】

各メモリセルMCは、例えば、図37に示すように、第1、第2及び第3の半導体層12−1,12−2,12−3の第2の方向にある側面上に配置される絶縁層(ゲート絶縁層25−1、記録層25−2及びブロック絶縁層25−3)25と、絶縁層25の第1、第2及び第3の半導体層12−1,12−2,12−3側とは反対側に配置されるゲート電極(例えば、ワード線WL)26とを備える。

【0249】

ゲート電極26は、第1、第2及び第3の半導体層12−1,12−2,12−3の第2の方向にある側面に沿って第1の方向に延びる。また、ゲート電極26(WL)をその上面から見たとき、ゲート電極26(WL)は、第1、第2及び第3のメモリストリングNa、Nb,Ncを跨いで、第2の方向に延びる。

【0250】

第1、第2及び第3のメモリストリングNa、Nb,Ncの第3の方向の両端には、第2の方向に延びる梁27a,27bが接続される。

【0251】

第1、第2及び第3のメモリストリングNa、Nb,Ncが、第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層13,14を備えるフィン型積層構造を有するとき、梁27a,27bも、第1、第2及び第3の半導体層12−1,12−2,12−3及び絶縁層13,14を備えるフィン型積層構造を有する。

【0252】

梁27a,27bは、第1、第2及び第3のメモリストリングNa、Nb,Ncのチャネルに電圧又は電流を供給する導電パスとなる。

【0253】

また、梁27a,27bは、第1、第2及び第3のメモリストリングNa、Nb,Ncを固定し、これらの倒壊を防止する機能を有する。梁27a,27bの第3の方向の幅は、第1、第2及び第3のメモリストリングNa、Nb,Ncの第2の方向の幅よりも広いのが望ましい。

【0254】

梁27a,27bの第2の方向の一端には、実施形態に係わる半導体装置、即ち、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択する機能が設けられる。

【0255】

本例の場合、この機能は、第3の実施例(図18及び図19参照)に相当する。例えば、梁27a,27bの第2の方向の一端には、共通半導体層21に接続される共通電極18と、第1、第2及び第3の半導体層12−1,12−2,12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)が設けられる。

【0256】

共通電極18は、第1、第2及び第3のメモリストリングNa、Nb,Ncのソース電極(ソース線側電極)又はドレイン電極(ビット線側電極)として機能する。

【0257】

また、レイヤー選択トランジスタ15(LST)については、第1乃至第4の実施例で詳細に説明したので、ここでの説明を省略する。

【0258】

第1、第2及び第3のメモリストリングNa、Nb,Ncと梁27a,27bとの間には、例えば、メモリセルアレイを構成する複数(本例では4つ)のフィン型積層構造(第1、第2及び第3のメモリストリングNa、Nb,Ncを備える1グループ)のうちの1つを選択するためのアシストゲートトランジスタ24(AGT)が設けられる。

【0259】

尚、アシストゲートトランジスタ24(AGT)は、スイッチとして機能すればよい。このため、アシストゲートトランジスタ24(AGT)は、メモリセルMCと同じ構造を有していてもよいし、異なる構造を有していてもよい。

【0260】

例えば、アシストゲートトランジスタ24(AGT)がメモリセルMCと同じ構造を有するとき、アシストゲートトランジスタ24(AGT)は、絶縁層(ゲート絶縁層25−1、記録層25−2及びブロック絶縁層25−3)25と、絶縁層25の第1、第2及び第3の半導体層12−1,12−2,12−3側とは反対側に配置されるゲート電極26とを備える。

【0261】

また、アシストゲートトランジスタ24(AGT)がメモリセルMCと異なる構造を有するとき、アシストゲートトランジスタ24(AGT)は、ゲート絶縁層と、ゲート電極とを備えるMIS (Metal-Insulator-Semiconductor)型トランジスタである。

【0262】

アシストゲートトランジスタ24(AGT)は、例えば、メモリセルアレイを構成する複数(本例では4つ)のフィン型積層構造の各々に独立に設けられる。

【0263】

上述のVLBの各要素を構成する材料については、半導体メモリの各世代に応じた最適な材料を適宜選択することができるが、以下では、最もよく使用される材料例を説明する。

【0264】

半導体基板10は、例えば、単結晶シリコン基板である。また、絶縁層11,13は、例えば、酸化シリコン層である。

【0265】

第1、第2及び第3の半導体層12−1,12−2,12−3及び共通半導体層21は、それぞれ、例えば、シリコン(Si)層である。第1、第2及び第3の半導体層12−1,12−2,12−3及び共通半導体層21は、単結晶であるのが望ましいが、アモルファス又は多結晶であっても構わない。

【0266】

フィン型積層構造を構成する最上層の絶縁層14は、例えば、酸化シリコン(SiO2)、窒化シリコン(SiN)、又は、それらが積み重ねられた構造を有する。

【0267】

メモリセルMCを構成するゲート絶縁層25−1は、例えば、酸化シリコン層である。ゲート絶縁層25−1は、酸窒化シリコン、酸化シリコンと窒化シリコンとの積層構造などであってもよい。また、ゲート絶縁層25−1は、シリコンナノ粒子や、金属イオンなどを含んでいてもよい。

【0268】

記録層25−2は、例えば、電荷蓄積層(Si3N4など)、可変抵抗層(電圧、電流、熱、磁場などにより抵抗値が変化する材料層など)である。記録層25−2が電荷蓄積層のとき、記録層25−2は、絶縁層ではなく、導電層としてのフローティングゲート層であっても構わない。

【0269】

記録層25−2が電荷蓄積層のとき、電荷蓄積層は、例えば、シリコンリッチSiN、シリコンと窒素の組成比x、yが任意であるSixNy、酸窒化シリコン(SiON)、酸化アルミニウム(Al2O3)、酸窒化アルミニウム(AlON)、ハフニア(HfO2)、ハフニウム・アルミネート(HfAlO3)、窒化ハフニア(HfON)、窒化ハフニウム・アルミネート(HfAlON)、ハフニウム・シリケート(HfSiO)、窒化ハフニウム・シリケート(HfSiON)、酸化ランタン(La2O3)及びランタン・アルミネート(LaAlO3)のグループから選択される少なくとも1つであってもよい。

【0270】

また、電荷蓄積層は、シリコンナノ粒子や、金属イオンなどを含んでいてもよい。電荷蓄積層は、不純物が添加されたポリシリコン、メタルなどの導電体から構成してもよい。

【0271】

ブロック絶縁層25−3は、例えば、書き込み/消去時のリーク電流を防止する機能を有する。

【0272】

ブロック絶縁層25−3は、例えば、酸化シリコン(SiO2)、酸窒化シリコン(SiON)、酸化アルミニウム(Al2O3)、酸窒化アルミニウム(AlON)、ハフニア(HfO2)、ハフニウム・アルミネート(HfAlO3)、窒化ハフニア(HfON)、窒化ハフニウム・アルミネート(HfAlON)、ハフニウム・シリケート(HfSiO)、窒化ハフニウム・シリケート(HfSiON)、酸化ランタン(La2O3)、ランタン・アルミネート(LaAlO3)及びランタンアルミシリケート(LaAlSiO)のグループから選択される少なくとも1つであるのが望ましい。

【0273】

メモリセルMCを構成するゲート電極26は、例えば、珪化ニッケル(NiSi)などの金属シリサイド層を備える。

【0274】

ゲート電極26は、例えば、タンタルナイトライド(TaN)、タンタルカーバイト(TaC)、チタンナイトライド(TiN)などの金属化合物、又は、金属的な電気伝導特性を示す、Ni、V、Cr、Mn、Y、Mo、Ru、Rh、Hf、Ta、W,Ir、Co、Ti、Er、Pt、Pd、Zr、Gd、Dy、Ho、Er、及び、これらのシリサイドであってもよい。

【0275】

共通電極18及びレイヤー選択トランジスタ15のゲート電極16−1〜16−5は、例えば、W、Al、Cuなどの金属材料である。

【0276】

図38は、クロスポイント型メモリセルアレイを実現する不揮発性半導体メモリを示している。図39は、図38のメモリセルアレイを示している。図40は、図39のA−A’線及びB−B’線に沿う断面図を示している。

【0277】

2つのフィン型積層構造(第1乃至第nの半導体層)を互いに交差させ、これら2つのフィン型積層構造間に2端子型のメモリセルMCを配置すれば、クロスポイント型メモリセルアレイを実現できる。

【0278】

この場合、メモリセルMCは、ReRAM(Resistance Random Access Memory)、PCM(Phase Change Memory)、MRAM(Magnetic Random Access Memory)などの抵抗変化型のメモリに用いられるメモリセルをそのまま採用することが可能である。

【0279】

半導体基板10上の絶縁層11上には、互いに交差するワード線WL/ビット線BLとしての複数の導電線が設けられる。これら複数の導電線は、半導体基板10上の絶縁層11上に積み重ねられる第1、第2及び第3の半導体層12−1,12−2,12−3を備える。

【0280】

本例では、絶縁層11上に積み重ねられる導電線としての半導体層の数は、3つであるが、これに限られない。即ち、これら導電線としての半導体層の数は、2つ以上であればよい。

【0281】