半導体装置及びその製造方法

【課題】本発明は、保護膜の境界面での膜厚を厚くし、はんだが金属膜の下方に侵入し難い半導体装置を提供することを目的とする。

【解決手段】基板10と、

該基板に積層された金属膜30と、

該金属膜に積層されたはんだ層40と、

前記基板に積層され、前記金属膜及び前記はんだ層に接するように形成されたポリイミドからなる保護膜50とを備え、

該保護膜は、前記金属膜と接する界面において、前記基板から離れるにつれて前記金属膜側に迫り出す形状を有することを特徴とする。

【解決手段】基板10と、

該基板に積層された金属膜30と、

該金属膜に積層されたはんだ層40と、

前記基板に積層され、前記金属膜及び前記はんだ層に接するように形成されたポリイミドからなる保護膜50とを備え、

該保護膜は、前記金属膜と接する界面において、前記基板から離れるにつれて前記金属膜側に迫り出す形状を有することを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、基板と、金属膜と、はんだ層と、保護膜とを有する半導体装置及びその製造方法に関する。

【背景技術】

【0002】

従来から、下地層の上に無電解めっきニッケル層を形成し、無電解めっきニッケル層上に電解めっきニッケル層を形成したはんだ接合用電極が知られている(例えば、特許文献1参照)。

【0003】

かかる特許文献1に記載のはんだ接合用電極においては、はんだ接合用電極上に錫を90%以上含むはんだバンプが形成された際に、無電解めっきニッケル層が錫の電極内での拡散を防ぎ、電解めっきニッケル層によりはんだの濡れ性を良好に保つこととしている。これにより、ニッケルがはんだの中に溶け込み、はんだ接合用電極が消失してしまう電極食われという現象の発生を防止することができる。また、無電解めっきニッケル層は、はんだの濡れ性が電解めっきニッケル層に比較して劣ることから、無電解めっきニッケル層上に電解めっきニッケル層を形成することにより、はんだの濡れ性も良好に保っている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2000−349111号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に記載の構成では、はんだ接合用電極の周囲に、基板を覆う保護膜が必要な状況については何ら考慮されていない。一般的に、はんだ接合用電極は基板の表面上に形成された金属電極上に形成されるが、基板表面の他の露出箇所には半導体素子等の回路素子が形成されている場合が多く、かかる回路素子を保護すべく、基板の表面を覆うとともに、側面がはんだ接合用電極やはんだと接触して密閉するような保護膜を設ける必要がある場合が多い。

【0006】

かかる保護膜を設ける場合、保護膜で基板表面全体を覆ってから、めっき接合用電極を形成する箇所の保護膜をウェットエッチングで除去し、基板表面にある金属電極を露出さっせ、その上にめっき膜を形成してはんだ接合用電極とする場合が多い。

【0007】

しかしながら、保護膜をウェットエッチングで除去すると、保護膜のエッチング面はなだらかに裾が広がった斜面を形成し、保護膜の厚さが薄くなった裾の部分を、上下からめっき膜と金属電極で挟むような形状となり、挟んだ箇所よりも上側では、めっき膜の側面と保護膜の斜面との間に隙間が空くような形状となる場合が多い。かかる形状のはんだ接合用電極(めっき膜)上にはんだを形成すると、はんだがめっき膜と保護膜との隙間に入りこみ、はんだと金属電極との間を隔てているのが、保護膜が薄くなった裾の部分のみとなり、はんだと金属電極との合金化が発生するおそれがある。金属電極には、一般的にAl(アルミニウム)が用いられ、はんだには上述のように錫(Sn)が用いられるため、合金化が発生すると、Al−Sn合金が発生するが、かかるAl−Sn合金は脆弱であり、実装時や素子動作の熱負荷、また使用環境での温度変化の際に、各材料の熱膨張力の差により破断が発生し、システム不良が発生するおそれがあるという問題があった。

【0008】

また、結晶破壊やめっき剥離を起こし難い金属めっきを形成するめっき方法として、電極上に開口が形成され、開口の内周面が裏面側から表面側に向かうほど開口側に大きく迫り出すレジストパターンを形成する工程と、レジストパターンに形成される開口を電解めっきにより充填して金属めっきを形成する工程と、を含むめっき方法が知られている(例えば、特許文献2参照)。

【0009】

かかる方法では、電極上に、その外周面が表面側から裏面側に向かうほど側方に大きく迫り出す金属めっきを形成することができるが、上述のレジストパターンは、金属めっきを形成した後、除去されるものであり、最終的に残る保護膜とは異なっている。また、特許文献2に記載の金属めっきを形成した後に保護膜を形成する場合には、保護膜の形成のために300℃以上に加熱処理を行う必要があるが、金属めっきの耐熱が300℃未満であるので、金属めっきを形成してから保護膜を形成することは実質的に不可能である。よって、特許文献2に記載の構成も、保護膜が必要なはんだ接合用電極への応用は実質的に不可能であるという問題があった。

【0010】

そこで、本発明は、保護膜の境界面での膜厚を厚くし、はんだがめっき膜の下方に侵入し難い半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

上記目的を達成するため、本発明の一実施態様に係る半導体装置は、基板と、

該基板に積層された金属膜と、

該金属膜に積層されたはんだ層と、

前記基板に積層され、前記金属膜及び前記はんだ層に接するように形成されたポリイミドからなる保護膜とを備え、

該保護膜は、前記金属膜と接する界面において、前記基板側から離れて表面側に接近するにつれて前記金属膜側に迫り出す形状を有することを特徴とする。

【0012】

本発明の他の実施態様に係る半導体装置は、基板と、

該基板の表面に形成された金属パターンと、

該金属パターンに積層された金属膜と、

該金属膜に積層されたはんだ層と、

前記基板に積層されるとともに前記金属膜及び前記はんだ層に接するように形成され、前記金属パターン間を絶縁するポリイミドからなる保護膜とを備え、

該保護膜は、前記金属膜と接する界面において、前記基板側から離れて表面側に接近するにつれて前記金属膜側に迫り出す形状を有することを特徴とする。

【0013】

本発明の他の実施態様に係る半導体装置の製造方法は、基板上に金属パターンを形成する金属パターン形成工程と、

前記基板及び金属パターンに積層してポリイミドからなる保護膜を形成する保護膜形成工程と、

前記金属パターン上に形成された前記保護膜に、前記金属パターン側から離れて前記保護膜の表面側に接近するにつれて前記保護膜が内側に迫り出すような開口を形成し、前記金属パターンを露出させる開口形成工程と、

前記開口に金属膜を充填する金属膜形成工程と、を有することを特徴とする。

【0014】

本発明の他の実施態様に係る半導体装置は、基板と、

該基板に積層された金属膜と、

該金属膜に積層されたはんだ層と、

前記基板に積層され、前記金属膜及び前記はんだ層に接するように形成されたポリイミドからなる保護膜とを備え、

該保護膜と前記金属膜が接する界面は、前記基板に垂直であることを特徴とする。

【0015】

本発明の他の実施態様に係る半導体装置の製造方法は、基板上に金属パターンを形成する金属パターン形成工程と、

前記基板及び金属パターンに積層してポリイミドからなる保護膜を形成する保護膜形成工程と、

前記金属パターン上に形成された前記保護膜に、前記基板に垂直な開口を形成し、前記金属パターンを露出させる開口形成工程と、

前記開口に金属膜を充填する金属膜形成工程と、を有することを特徴とする。

【発明の効果】

【0016】

本発明によれば、保護膜との界面近傍においてもめっき膜の厚さを確保することができ、はんだのめっき膜下への侵入を防ぐことができる。

【図面の簡単な説明】

【0017】

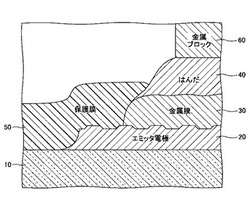

【図1】本発明の実施例1に係る半導体装置の一例を示した断面図である。

【図2】比較例として、従来の半導体装置の断面構成を示した図である。

【図3】比較例として、図2に示した従来の半導体装置のめっき膜形成過程を示した図である。図3(A)は、めっき膜の初期形成段階を示した図である。図3(B)は、めっき膜の途中形成段階を示した図である。図3(C)は、めっき膜の完成段階を示した図である。

【図4】本発明の実施例2に係る半導体装置の一例を示した断面構成図である。

【図5】実施例2に係る半導体装置の隣接する半導体素子間の構成を示した断面図である。

【図6】参考例として、従来の半導体装置の製造方法を説明するための図である。図6(A)は、従来の半導体装置の製造方法の第1段階を示した図である。図6(B)は、従来の半導体装置の製造方法の第2段階を示した図である。図6(C)は、従来の半導体装置の製造方法の第3段階を示した図である。図6(D)は、従来の半導体装置の製造方法の最終段階を示した図である。

【図7】実施例3に係る半導体装置の製造方法における保護膜の開口方法の一例を示した図である。図7(A)は、実施例3に係る半導体装置の製造方法の第1段階の一例を示した図である。図7(B)は、実施例3に係る半導体装置の製造方法の第2段階の一例を示した図である。図7(C)は、実施例3に係る半導体装置の製造方法の第3段階の一例を示した図である。図7(D)は、実施例3に係る半導体装置の製造方法の最終段階の一例を示した図である。

【図8】本発明の実施例4に係る半導体装置の製造方法の一例を説明するための図である。図8(A)は、実施例4に係る半導体装置の製造方法の第1段階を示した図である。図8(B)は、実施例4に係る半導体装置の製造方法の第2段階を示した図である。図8(C)は、実施例4に係る半導体装置の製造方法の最終段階を示した図である。

【図9】本発明の実施例5に係る半導体装置及びその製造方法の一例を説明するための図である。

【発明を実施するための形態】

【0018】

以下、図面を参照して、本発明を実施するための形態の説明を行う。

【実施例1】

【0019】

図1は、本発明の実施例1に係る半導体装置の一例を示した断面図である。図1において、実施例1に係る半導体装置は、半導体基板10と、エミッタ電極20と、金属膜30と、はんだ層40と、保護膜50と、金属ブロック60とを備える。図1において、半導体基板10の表面を覆うようにエミッタ電極20が形成されている。エミッタ電極20の表面上には、金属膜30が形成されており、金属膜30の表面上には、はんだ層40が形成されている。金属膜30の側面及びはんだ層40の側面の下側の一部は、保護膜50と接している。保護膜50は、半導体基板10の表面及びエミッタ電極20の表面の一部を覆うとともに、水平方向には金属膜30及びはんだ層40の方に延び、金属膜30の側面及びはんだ層40の側面の一部を覆っている。また、はんだ層40の表面上には、金属ブロック60が設けられている。

【0020】

半導体基板10は、IGBT(Insulated Gate Bipolar Transistor、絶縁ゲートバイポーラトランジスタ)等の回路素子を形成する対象であり、例えば、半導体ウエハ等が用いられる。半導体基板10には、IGBT等の半導体素子以外にも種々の回路素子が形成されてよいが、図1においては、IGBT(図示せず)のエミッタ電極が半導体基板10の表面に形成された例を挙げて説明する。

【0021】

エミッタ電極20は、半導体基板10上に形成された金属パターンであり、半導体基板10にIGBTが形成された場合のIGBTの電極の一部を構成する。図1においては、半導体基板10にIGBTが形成された例が示されているため、半導体基板10の表面にはエミッタ電極20が形成されているが、例えば、パワーMOS(Metal Oxide Semiconductor)トランジスタ等が形成された場合には、ドレイン電極やゲート電極であってもよい。また、その他の回路素子や回路端子の電極であってもよい。

【0022】

エミッタ電極20は、配線用の種々の金属材料で構成されてよいが、例えば、有るアルミニウム(Al)で構成されてもよい。また、エミッタ電極20は、種々の方法で形成することができ、例えば、蒸着法、スパッタリング法、CVD(Chemical Vapor Deposition、化学的気相成長)法等により形成されてよい。

【0023】

金属膜30は、はんだ接合用電極を構成する金属材料からなる膜である。金属膜30は、はんだとの接合性が考慮され、種々の材料が選択される。例えば、金属膜30は、ニッケル(Ni)膜であってもよいし、Ni−Sn合金膜であってもよい。また、金属膜30は、複数の金属から構成されてよく、ニッケル膜の表面に金(Au)の膜が形成されてもよいし、Ni−Sn合金膜の表面に金膜が形成されてもよい。

【0024】

金属膜30は、めっき、蒸着、CVD、スパッタリング等の種々のプロセスにより形成され得るが、例えば、めっき処理により形成されためっき膜として構成されてもよい。めっき膜は、無電解めっき処理により形成された無電解めっき膜であってもよいし、電気めっき処理により形成された電気めっき膜であってもよい。また、無電解めっき膜と電気めっき膜の2層から構成されてもよい。無電解めっき処理と電気めっき処理の双方を行う場合には、無電解めっき膜がエミッタ電極20上に形成され、無電解めっき膜上に電気めっき膜が形成される構成とされることが好ましい。

【0025】

はんだ層40は、金属ブロック60を金属膜30上に接合するための接合層である。はんだ層40は、種々のはんだ材から構成され得るが、例えば、鉛を含まない鉛フリーはんだから構成されてもよい。鉛フリーはんだの場合、例えば、錫を主成分とするはんだ材が用いられてもよい。

【0026】

保護膜50は、半導体基板10の表面に形成された回路素子を保護するための膜である。よって、保護膜50は、半導体基板10の表面全体を覆い、エミッタ電極20の露出部分も覆う。更に、金属膜30の側面全体とはんだ層40の側面の一部も覆って半導体基板10の表面を密閉し、半導体基板10の表面に形成された回路素子を埃や塵から保護する。

【0027】

保護膜50は、有機材料の一種であるポリイミドから構成される。ポリイミドは、例えば、非感光性ポリイミドを用いてもよい。この場合には、マスクを用いたエッチングによりパターニングを行い、ポリイミドからなる保護膜50を形成することができる。また、保護膜50には、感光性ポリイミドを用いるようにしてもよい。この場合には、露光、現像によりパターニングを行い、ポリイミドからなる保護膜50を形成することができる。

【0028】

保護膜50は、半導体基板10の表面及びエミッタ電極20の表面を適切に保護できるように、十分な厚さを有して保護膜50を形成することができ、例えば、5μm以上の厚さを有する保護膜50を形成してもよい。

【0029】

金属ブロック60は、半導体モジュールを形成する際の半導体素子間の接続用の配線及びスペーサとなる部材であり、銅やアルミニウム等の金属材料から構成される。

【0030】

実施例1に係る半導体装置は、上述のような機能を有する構成要素から構成されているが、図1において、金属膜30及びはんだ層40は、山の裾のように下側に行くにつれて広がる形状を有している。そして、金属膜30及びはんだ層40の側面を覆っている保護膜50は、基板10側から離れて表面側に向かうにつれて、金属膜30及びはんだ層40側に迫り出す形状となっている。これにより、はんだ層40は、金属膜30が存在する領域上にその存在が制約され、はんだ層40が保護膜50と金属膜30との界面に入り込むことを防止できる構成となっている。

【0031】

図2は、比較例として、従来の半導体装置の断面構成を示した図である。図2において、エミッタ電極120上にめっき膜130、めっき膜130の上にはんだ層140が形成され、はんだ層140とめっき膜130の側面に保護膜150が接触して形成され、半導体基板110の表面を覆っている。図2において、保護膜150は、なだらかに裾が広がる断面形状を有しており、めっき膜130とエミッタ電極120との間に裾の膜厚が薄い部分が入り込むような形状をしている。めっき膜130は、膜厚自体は、右側の領域においては、厚さBの十分な厚さを有しており、はんだ層140とエミッタ電極120との合金化を防ぐことができる厚さである。しかしながら、保護膜150との界面においては、はんだ層140がめっき膜130と保護膜150との間の隙間に入り込んでいるため、はんだ層140とエミッタ電極120表面との間隔は距離Aしか無い状態となっている。この場合において、めっき膜130がニッケル膜、エミッタ電極120がアルミニウム又はアルミニウム合金、錫(Sn)を含む鉛フリーはんだによりはんだ層140を形成して場合、めっき膜130とはんだ層140との界面に、Ni−Sn合金が形成される。ここで、Niめっき膜厚の設計値は、信頼性を考慮してNi−Sn合金が形成した後の健全層が残る値とされるが、保護膜150との界面近傍のめっき膜厚が薄い破線で囲まれた箇所では、総てのNiが合金化し、次いでAlとの合金化が始まり、Al−Sn合金が形成される。しかしながら、Al−Sn合金は脆弱であるため、実装時や素子動作時の熱負荷、また使用環境での温度変化の際に、各材料の熱膨張率の差により破断が生じ、システム不良が発生してしまう。

【0032】

図3は、比較例として、図2に示した従来の半導体装置のめっき膜形成過程を示した図である。図3(A)は、めっき膜の初期形成段階を示した図であり、保護膜150がウェットエッチングにより形成され、外側に裾が広がるなだらかな傾斜を有する形状を有している。

【0033】

図3(B)は、めっき膜の途中形成段階を示した図であり、めっき膜130が厚くなるとともに、保護膜150との間に隙間が発生し始めている。

【0034】

図3(C)は、めっき膜の完成段階を示した図であり、めっき膜130が厚く形成されたが、保護膜150との界面には、大きな隙間が残っている。めっき膜130と保護膜150が接触している界面の長さは、めっき膜130の厚さと比較して、非常に短くなっている。

【0035】

このように、従来の半導体装置の構成では、保護膜150の裾がなだらかに外側に広がる形状を有するため、はんだ層140がめっき膜130の下部に侵入し、エミッタ電極120との合金化のおそれがある構成を有していた。

【0036】

一方、図1に示すように、実施例1に係る半導体装置は、保護膜50が、下方の半導体基板10及びエミッタ電極20側から離れて上方の表面側に接近するにつれて外側に張り出すような形状を有しており、保護膜50は金属膜30の側面に完全に接触するような構成となっている。よって、保護膜50と金属膜30との界面において、金属膜30の膜厚は、形成した金属膜30の厚さ分が総て残った形状となっている。また、保護膜150は、金属膜30の上方を超えてはんだ層40側に迫り出した形状となっているため、はんだ層40に対してしっかりと壁を形成している。よって、はんだ層40が金属膜30の側面に侵入することを防止でき、はんだ層40のエミッタ電極20との合金化を確実に防ぐことができる構成となっている。

【0037】

なお、図1において、保護膜50は、比較的滑らかな逆テーパー状の形状を有しているが、半導体基板10から離れるにつれて金属膜30側に迫り出す形状を有していれば、例えば、階段状に段差を有していたり、テーパー面の表面に凹凸があったりする形状を有していてもよい。保護膜50は、金属膜30との界面が金属膜30側に迫り出している形状を有すれば、保護膜50の表面の微細な構造については、種々の構成とすることができる。

【0038】

このように、実施形態1に係る半導体装置によれば、表面はんだ実装を行う半導体装置において、鉛フリーはんだ実装後の接合信頼性を向上させることができる。また、保護膜50との界面近傍においても、金属膜厚が設計通りの膜を形成することができる。更に、金属膜30とはんだ層40との合金が形成した後も、金属膜30の健全層が残り、接合強度を維持する構造とすることができる。また、総ての界面において接合強度が維持されるため、実装時や素子動作時の熱負荷、使用環境での温度変化の際、各材料の熱膨張率の差により応力が発生しても、破断等の不良を無くすことができる。

【0039】

また、実施形態1において、エミッタ電極20上に金属膜30が形成されている例について説明したが、金属膜30自体は、無電解めっきで半導体基板10上の任意の箇所に形成することができるので、必ずしもエミッタ電極20のような金属パターン上に金属膜30が形成されている必要ななく、半導体基板10上に直接形成されていてもよいし、例えばチタン(Ti)のような金属下地層の上に形成されていてもよい。

【実施例2】

【0040】

図4は、本発明の実施例2に係る半導体装置の一例を示した断面構成図である。図4において、実施例2に係る半導体装置は、半導体ウエハ13と、エミッタ電極21と、金属膜31と、はんだ層41と、保護膜51と、金属ブロック61とを備える。構成要素としては、実施例1に係る半導体装置とほぼ同様であり、金属ブロック61が、はんだ層61の上だけでなく、保護膜50の上方も含めて全体を覆うように設けられている点のみ異なっている。半導体ウエハ13の表面上にエミッタ電極21が形成され、エミッタ電極21上に金属膜31、金属膜31上にはんだ層41が形成され、金属膜31の側面全体とはんだ層41の側面の下側に接触して保護膜51が形成され、保護膜51が半導体ウエハ13及びエミッタ電極21を覆っている点も、実施例1と同様である。また、保護膜51は、半導体ウエハ13側から離れて表面側に接近するにつれて、外側の金属膜31及びはんだ層41側に迫り出し、逆テーパー状に構成されている点も、実施例1と同様である。よって、実施例2に係る半導体装置において、各構成要素の材料や構成等の詳細な内容は、実施例1で説明した内容をそのまま適用できるものとし、その説明を省略する。

【0041】

図5は、実施例2に係る半導体装置の隣接する半導体素子間の構成を示した断面図である。図5において、半導体ウエハ13の右側には、図4と同様の半導体装置の構成が示されており、左側は、右側と対称な半導体装置の構成が示されている。また、左右の半導体素子の間の半導体ウエハ13の表面には、配線22が形成されている。保護膜51は、配線22及びエミッタ電極21を含めて、左右の金属膜31及びはんだ層41に挟まれるように、半導体ウエハ13の表面を覆うように形成されている。そして、保護膜51は、左側においても、半導体ウエハ13側から離れて保護膜51の表面側に接近するにつれて、左側にある金属膜31及びはんだ層41側に迫り出す形状を有している。これにより、左側にある半導体装置においても、金属膜31の膜厚を十分確保することができ、はんだ層41が金属膜31の側面に到達するのを防ぐことができる。

【0042】

このように、複数の半導体素子が半導体ウエハ13上に配置された場合であっても、各々の半導体素子の金属膜31及びはんだ層41に対し、保護膜51を迫り出させる構成とすることにより、各々の半導体素子について、はんだ接合の信頼性を向上させることができる。

【0043】

なお、金属ブロック61は、各半導体素子のエミッタ電極21を並列接続しているので、実施例1で示したように、個別に設けられて別の箇所で接続されてもよいし、実施例2で示したように、1つの金属ブロック61がまとめて半導体素子同士を接続している構成としてもよい。

【実施例3】

【0044】

実施例3においては、実施例1及び実施例2で説明したような、本発明の実施例に係る半導体装置の製造方法の一例について説明する。本実施例に係る半導体装置を製造するためには、基板10、11上にエミッタ電極20、21等の金属パターンを形成し(金属パターン形成工程)、エミッタ電極20、21を含めて基板10、11全体を覆うように保護膜50、51を形成する(保護膜形成工程)。保護膜50、51は、ポリイミドからなり、保護膜形成工程においては、十分な加熱が必要であるため、350℃以上で十分に加熱(ベーク)処理を行う(保護膜加熱工程)。その後、保護膜50、51に逆テーパー状の開口を形成し(開口形成工程)、当該開口に金属膜30、31を充填するため、金属膜30、31を形成する(金属膜形成工程)。金属膜30、31を形成した後、必要に応じて金属膜30、31を加熱する(金属膜加熱工程)。金属膜加熱工程においては、保護膜加熱工程よりも低い温度で金属膜30、31の加熱が行われる。次に、金属膜30、31上にはんだ層40、41を形成する(はんだ層形成工程)。かかる一連の工程により、本実施例に係る半導体装置が製造される。

【0045】

上述の工程において、保護膜形成工程は、金属膜形成工程及びはんだ層形成よりも先に行われている。上述のように、保護膜50、51にポリイミドを用いた場合、保護膜加熱工程においては、350℃以上で十分に加熱(ベーク)処理を行う。一方、はんだの融点は、350℃よりも低いため、保護膜50、51のベーキングは、金属膜30、31及びはんだ層40、41を形成する前に行う必要がある。よって、本実施例に係る半導体装置の製造方法においては、保護膜形成工程は、金属膜形成工程及びはんだ層形成よりも先に行う。

【0046】

なお、以下、実施例3においては、保護膜50、51に逆テーパー形状の開口を形成する工程について、詳細に説明する。

【0047】

まず、参考例として、従来の開口の形成方法を説明する。

【0048】

図6は、参考例として、従来の半導体装置の製造方法を説明するための図である。

【0049】

図6(A)は、従来の半導体装置の製造方法の第1段階を示した図である。図6(A)において、電極120の表面上に保護膜150が形成され、保護膜150の表面に開口171を有するマスク170が配置されている。マスク170は、塗布等により保護膜150の表面上に形成される。開口171から、エッチングにより保護膜150の腐食が開始する。

【0050】

図6(B)は、従来の半導体装置の製造方法の第2段階を示した図である。図6(B)において、保護膜150の腐食が進んでいるが、深さ方向だけではなく、横方向にも腐食が進み、マスク170の下方にも腐食が開始している。

【0051】

図6(C)は、従来の半導体装置の製造方法の第3段階を示した図である。図6(C)において、保護膜150の腐食が更に進んでいるが、深さ方向だけではなく、横方向にもかなり腐食が進んだ状態となっている。また、腐食の断面形状は、両側からな中央に向かってなだらかに深くなる形状である。

【0052】

図6(D)は、従来の半導体装置の製造方法の最終段階を示した図である。図6(D)において、電極120が露出しエッチングが終了する。このとき、開口の断面形状は、両側から中央に向かって傾斜するテーパー形状となっている。

【0053】

このように、マスクを保護膜150上に形成し、単にエッチングを行った開口の形成方法では、開口を逆テーパー形状とすることができない。

【0054】

図7は、実施例3に係る半導体装置の製造方法における保護膜の開口方法の一例を示した図である。

【0055】

図7(A)は、実施例3に係る半導体装置の製造方法の第1段階の一例を示した図である。図7(A)において、電極23の表面上に保護膜52が形成されており、保護膜52の表面上に開口71を有するマスク70が配置されている。ここで、マスク70は、プリベークが施されて硬化され、保護膜52との密着性が高まった状態となっている。また、電極23は、実施例1、2で説明したエミッタ電極20、21に相当する金属パターンである。この点は、以後の実施例においても同様とする。

【0056】

上述のように、保護膜52を形成するために、ベーキング処理を行うが、ベーキング処理の前に、プリベークというベーキング処理よりも低い温度で加熱を行う処理がある。かかるプリベークは、レジストマスクの水分を除去させるため、レジストが反応しない比較的低い温度で行われる加熱処理であるが、プリベークにおいて、時間を長くしたり、温度を値以上のプリベークよりも上げたりすると、マスク70が硬化し、マスク70と保護膜52との密着性が高まる。プリベークの温度や時間は、保護膜52の特性や用途に応じて適宜定められてよいが、例えば、300℃の温度に設定されてもよい。実施例3に係る保護膜の開口方法では、保護膜52とマスク70との密着性を高める処理を行ってから、保護膜52に開口を形成するエッチング処理を行う。

【0057】

図7(B)は、実施例3に係る半導体装置の製造方法の第2段階の一例を示した図である。図7(B)において、エッチングが進んでいるが、マスク70と保護膜52との密着性が高くなっているため、横方向へのエッチングがあまり進行せず、深さ方向にエッチングが進んだ断面形状となっている。

【0058】

図7(C)は、実施例3に係る半導体装置の製造方法の第3段階の一例を示した図である。図7(C)において、エッチングが更に進んでいるが、マスク70と保護膜52との密着性が高くなっているため、横方向へのエッチングが殆ど進行せず、深さ方向に大幅にエッチングが進んだ断面形状となっている。その結果、マスク70の開口71よりも、横幅の広い開口が形成されており、マスク70付近は逆テーパー形状となっている。

【0059】

図7(D)は、実施例3に係る半導体装置の製造方法の最終段階の一例を示した図である。図7(D)において、エッチングが更に進んで電極23の表面が露出している。マスク70と保護膜52との密着性が高いため、マスク70付近では横方向へのエッチングが殆ど進行せず、電極23付近の深い位置では横方向へのエッチングが進行した状態となっている。これにより、全体として逆テーパー状の開口が形成されている。

【0060】

このように、マスク70と保護膜52との密着性を高める処理を行ってから保護膜52にエッチングで開口を形成することにより、保護膜52を逆テーパー状の側面を有する形状に加工することができる。

【0061】

なお、上述の例では、プリベーク処理によりマスク70と保護膜52との密着性を高める例について説明したが、密着性の良い保護膜52とマスク70の組み合わせを採用し、それによりマスク70と保護膜52との密着性を高めてもよいし、更にプリベーク処理を組み合わせるようにしてもよい。

【0062】

このように、実施例3に係る半導体装置の製造方法によれば、保護膜52とマスク70との密着性を高めることにより、逆テーパー状の開口を形成し、本実施例に係る半導体装置を製造することができる。

【0063】

なお、逆テーパー形状のレジストを用いて、テーパー形状の金属めっきを形成する例として、上述の特許文献2に記載された製造方法がある。特許文献2に記載された金属めっきを先に形成し、その後に保護膜を形成して本実施例に係る半導体装置を製造する方法も形式上は考えられる。しかしながら、特許文献2に記載のめっき方法を、本実施例に係る半導体装置及びその製造方法に適用するのは、以下の理由で不可能である。

【0064】

まず、特許文献2に記載されためっき方法を応用した半導体装置の製造方法には、次の3つのプロセスが考えられる。

(1) レジスト→めっき→はんだ→レジスト除去→保護膜形成

(2) レジスト→めっき→レジスト除去→はんだ→保護膜形成

(3) レジスト→めっき→レジスト除去→保護膜形成→はんだ

まず、本実施例に係る半導体装置及びその製造方法において、保護膜52は、ポリイミド等の有機保護膜を用いることが好ましいが、例えばポリイミドをイミド化して形成するに当たり、350℃以上でベーク処理することが必要である。一方、はんだの融点は350℃未満であるため、はんだ層を形成してから保護膜52を形成することは、保護膜52の加熱処理の際にはんだが溶融していまい、不可能である。よって、上記(1)、(2)の製造方法では、本実施例に係る半導体装置を製造することはできない。

【0065】

また、上記(3)の製造方法においても、温度上の制約から、本実施例に係る半導体装置を製造することはできない。即ち、めっき処理により形成されためっき膜はアモルファス膜となるが、アモルファス膜は、熱が加わると再結晶化する。再結晶化が進むと、膜収縮が発生し、クラックが生じる。クラックが生じると、クラック中をはんだが浸透し、めっき膜の下層にある電極に到達する。そうすると、電極とはんだの合金化が進むため、脆弱化が問題となる。

【0066】

ここで、再結晶化が開始する温度は物質により異なるが、基本的に300℃以下の温度がアモルファス膜の温度限界となる。よって、めっき膜を形成した後に保護膜52のベーキング処理を行うと、めっき膜の再結晶化が開始してしまい、めっき膜にクラックが生じてしまう。

【0067】

よって、本実施例に係る半導体装置を製造するためには、本実施例に係る半導体装置の製造方法のように、保護膜52を形成してから金属膜30、31を形成する必要があり、特許文献2に記載のめっき方法を適用することはできない。

【実施例4】

【0068】

図8は、本発明の実施例4に係る半導体装置の製造方法の一例を説明するための図である。実施例4に係る半導体装置の製造方法においては、保護膜を複数種類用いて開口を行い、逆テーパー状の保護膜を形成する例について説明する。

【0069】

図8(A)は、実施例4に係る半導体装置の製造方法の第1段階を示した図である。図8(A)において、電極24上に3種類の保護膜53、54、55が積層され、その上に開口73を有するマスク72が配置された状態が示されている。保護膜53、54、55は、同一エッチング液を用いた場合に、エッチング速度が異なるポリイミド膜が3種類選択されている。そして、最下層の保護膜53は、中間層の保護膜54よりもエッチング速度が速く、保護膜54は最上層の保護膜55よりもエッチング速度が速い材料が選択されている。

【0070】

このような構成の保護膜53、54、55を用いて、エッチングを開始すると、図8(A)に示すように、まず最上層の保護膜55が腐食される。

【0071】

図8(B)は、実施例4に係る半導体装置の製造方法の第2段階を示した図である。図8(B)において、中間層の保護膜54がエッチングにより除去されているが、最上層の保護膜55よりもエッチング速度が速いため、エッチング面の傾斜が急になっている。

【0072】

図8(C)は、実施例4に係る半導体装置の製造方法の最終段階を示した図である。図8(C)において、最下層の保護膜53がエッチングにより除去され、電極24が露出して開口が完成しているが、保護膜53のエッチング速度が最も速いため、保護膜53の横方向のエッチングが進み、エッチング幅が大きくなっている。その結果、保護膜55、54、53の順に上から順にエッチング幅が大きくなり、逆テーパー状の開口が形成されている。

【0073】

このように、複数種類の保護膜53、54、55のエッチングの速度差を利用し、保護膜53、54、55を逆テーパー状に形成してもよい。なお、図8においては、3種類の保護膜53、54,55を用いたが、用途に応じて、2種類の保護膜を用いてもよいし、4種類以上の保護膜を用いるようにしてもよい。

【実施例5】

【0074】

図9は、本発明の実施例5に係る半導体装置及びその製造方法の一例を説明するめの図である。実施例5に係る半導体装置及びその製造方法においては、異方性ドライエッチングにより保護膜56の開口75を形成する例について説明する。

【0075】

図9において、電極25上に、垂直な側面の開口を有する保護膜56が積層され、保護膜56上に開口75を有するマスク74が配置された状態が示されている。保護膜56は、非感光性ポリイミド膜から構成される。マスク74は、保護膜56に比較して選択比が大きいものを使用する。例えば、酸化膜等を用いてもよい。マスク74の開口75形成後に、異方性ドライエッチングを行うことにより、マスク74の開口75に垂直に深掘りされ、保護膜56の表面に垂直な側面を有する開口が形成される。なお、図示されていないが、電極26は半導体基板上に形成されているので、開口は半導体基板にも垂直な開口となる。このように、ドライエッチングにより、保護膜56の表面及び基板に垂直な側壁を有する開口を保護膜56に形成するようにしてもよい。かかる構成を有する保護膜に金属膜30、31を充填し、その上にはんだ層40、41を形成した場合であっても、金属膜30、31は膜厚通りの厚さで電極25

とはんだ層40、41を隔てることができるため、はんだ層40、41と電極25との合金化を防止することができる。

【0076】

以上、本発明の好ましい実施例について詳説したが、本発明は、上述した実施例に制限されることはなく、本発明の範囲を逸脱することなく、上述した実施例に種々の変形及び置換を加えることができる。

【産業上の利用可能性】

【0077】

本発明は、はんだ実装構造を有する半導体装置に利用することができる。

【符号の説明】

【0078】

10、13 半導体基板

20〜25 電極

30、31 金属膜

40、41 はんだ層

50〜56 保護膜

60、61 金属ブロック

70、72、74 マスク

71、73、75 開口

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、基板と、金属膜と、はんだ層と、保護膜とを有する半導体装置及びその製造方法に関する。

【背景技術】

【0002】

従来から、下地層の上に無電解めっきニッケル層を形成し、無電解めっきニッケル層上に電解めっきニッケル層を形成したはんだ接合用電極が知られている(例えば、特許文献1参照)。

【0003】

かかる特許文献1に記載のはんだ接合用電極においては、はんだ接合用電極上に錫を90%以上含むはんだバンプが形成された際に、無電解めっきニッケル層が錫の電極内での拡散を防ぎ、電解めっきニッケル層によりはんだの濡れ性を良好に保つこととしている。これにより、ニッケルがはんだの中に溶け込み、はんだ接合用電極が消失してしまう電極食われという現象の発生を防止することができる。また、無電解めっきニッケル層は、はんだの濡れ性が電解めっきニッケル層に比較して劣ることから、無電解めっきニッケル層上に電解めっきニッケル層を形成することにより、はんだの濡れ性も良好に保っている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2000−349111号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に記載の構成では、はんだ接合用電極の周囲に、基板を覆う保護膜が必要な状況については何ら考慮されていない。一般的に、はんだ接合用電極は基板の表面上に形成された金属電極上に形成されるが、基板表面の他の露出箇所には半導体素子等の回路素子が形成されている場合が多く、かかる回路素子を保護すべく、基板の表面を覆うとともに、側面がはんだ接合用電極やはんだと接触して密閉するような保護膜を設ける必要がある場合が多い。

【0006】

かかる保護膜を設ける場合、保護膜で基板表面全体を覆ってから、めっき接合用電極を形成する箇所の保護膜をウェットエッチングで除去し、基板表面にある金属電極を露出さっせ、その上にめっき膜を形成してはんだ接合用電極とする場合が多い。

【0007】

しかしながら、保護膜をウェットエッチングで除去すると、保護膜のエッチング面はなだらかに裾が広がった斜面を形成し、保護膜の厚さが薄くなった裾の部分を、上下からめっき膜と金属電極で挟むような形状となり、挟んだ箇所よりも上側では、めっき膜の側面と保護膜の斜面との間に隙間が空くような形状となる場合が多い。かかる形状のはんだ接合用電極(めっき膜)上にはんだを形成すると、はんだがめっき膜と保護膜との隙間に入りこみ、はんだと金属電極との間を隔てているのが、保護膜が薄くなった裾の部分のみとなり、はんだと金属電極との合金化が発生するおそれがある。金属電極には、一般的にAl(アルミニウム)が用いられ、はんだには上述のように錫(Sn)が用いられるため、合金化が発生すると、Al−Sn合金が発生するが、かかるAl−Sn合金は脆弱であり、実装時や素子動作の熱負荷、また使用環境での温度変化の際に、各材料の熱膨張力の差により破断が発生し、システム不良が発生するおそれがあるという問題があった。

【0008】

また、結晶破壊やめっき剥離を起こし難い金属めっきを形成するめっき方法として、電極上に開口が形成され、開口の内周面が裏面側から表面側に向かうほど開口側に大きく迫り出すレジストパターンを形成する工程と、レジストパターンに形成される開口を電解めっきにより充填して金属めっきを形成する工程と、を含むめっき方法が知られている(例えば、特許文献2参照)。

【0009】

かかる方法では、電極上に、その外周面が表面側から裏面側に向かうほど側方に大きく迫り出す金属めっきを形成することができるが、上述のレジストパターンは、金属めっきを形成した後、除去されるものであり、最終的に残る保護膜とは異なっている。また、特許文献2に記載の金属めっきを形成した後に保護膜を形成する場合には、保護膜の形成のために300℃以上に加熱処理を行う必要があるが、金属めっきの耐熱が300℃未満であるので、金属めっきを形成してから保護膜を形成することは実質的に不可能である。よって、特許文献2に記載の構成も、保護膜が必要なはんだ接合用電極への応用は実質的に不可能であるという問題があった。

【0010】

そこで、本発明は、保護膜の境界面での膜厚を厚くし、はんだがめっき膜の下方に侵入し難い半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

上記目的を達成するため、本発明の一実施態様に係る半導体装置は、基板と、

該基板に積層された金属膜と、

該金属膜に積層されたはんだ層と、

前記基板に積層され、前記金属膜及び前記はんだ層に接するように形成されたポリイミドからなる保護膜とを備え、

該保護膜は、前記金属膜と接する界面において、前記基板側から離れて表面側に接近するにつれて前記金属膜側に迫り出す形状を有することを特徴とする。

【0012】

本発明の他の実施態様に係る半導体装置は、基板と、

該基板の表面に形成された金属パターンと、

該金属パターンに積層された金属膜と、

該金属膜に積層されたはんだ層と、

前記基板に積層されるとともに前記金属膜及び前記はんだ層に接するように形成され、前記金属パターン間を絶縁するポリイミドからなる保護膜とを備え、

該保護膜は、前記金属膜と接する界面において、前記基板側から離れて表面側に接近するにつれて前記金属膜側に迫り出す形状を有することを特徴とする。

【0013】

本発明の他の実施態様に係る半導体装置の製造方法は、基板上に金属パターンを形成する金属パターン形成工程と、

前記基板及び金属パターンに積層してポリイミドからなる保護膜を形成する保護膜形成工程と、

前記金属パターン上に形成された前記保護膜に、前記金属パターン側から離れて前記保護膜の表面側に接近するにつれて前記保護膜が内側に迫り出すような開口を形成し、前記金属パターンを露出させる開口形成工程と、

前記開口に金属膜を充填する金属膜形成工程と、を有することを特徴とする。

【0014】

本発明の他の実施態様に係る半導体装置は、基板と、

該基板に積層された金属膜と、

該金属膜に積層されたはんだ層と、

前記基板に積層され、前記金属膜及び前記はんだ層に接するように形成されたポリイミドからなる保護膜とを備え、

該保護膜と前記金属膜が接する界面は、前記基板に垂直であることを特徴とする。

【0015】

本発明の他の実施態様に係る半導体装置の製造方法は、基板上に金属パターンを形成する金属パターン形成工程と、

前記基板及び金属パターンに積層してポリイミドからなる保護膜を形成する保護膜形成工程と、

前記金属パターン上に形成された前記保護膜に、前記基板に垂直な開口を形成し、前記金属パターンを露出させる開口形成工程と、

前記開口に金属膜を充填する金属膜形成工程と、を有することを特徴とする。

【発明の効果】

【0016】

本発明によれば、保護膜との界面近傍においてもめっき膜の厚さを確保することができ、はんだのめっき膜下への侵入を防ぐことができる。

【図面の簡単な説明】

【0017】

【図1】本発明の実施例1に係る半導体装置の一例を示した断面図である。

【図2】比較例として、従来の半導体装置の断面構成を示した図である。

【図3】比較例として、図2に示した従来の半導体装置のめっき膜形成過程を示した図である。図3(A)は、めっき膜の初期形成段階を示した図である。図3(B)は、めっき膜の途中形成段階を示した図である。図3(C)は、めっき膜の完成段階を示した図である。

【図4】本発明の実施例2に係る半導体装置の一例を示した断面構成図である。

【図5】実施例2に係る半導体装置の隣接する半導体素子間の構成を示した断面図である。

【図6】参考例として、従来の半導体装置の製造方法を説明するための図である。図6(A)は、従来の半導体装置の製造方法の第1段階を示した図である。図6(B)は、従来の半導体装置の製造方法の第2段階を示した図である。図6(C)は、従来の半導体装置の製造方法の第3段階を示した図である。図6(D)は、従来の半導体装置の製造方法の最終段階を示した図である。

【図7】実施例3に係る半導体装置の製造方法における保護膜の開口方法の一例を示した図である。図7(A)は、実施例3に係る半導体装置の製造方法の第1段階の一例を示した図である。図7(B)は、実施例3に係る半導体装置の製造方法の第2段階の一例を示した図である。図7(C)は、実施例3に係る半導体装置の製造方法の第3段階の一例を示した図である。図7(D)は、実施例3に係る半導体装置の製造方法の最終段階の一例を示した図である。

【図8】本発明の実施例4に係る半導体装置の製造方法の一例を説明するための図である。図8(A)は、実施例4に係る半導体装置の製造方法の第1段階を示した図である。図8(B)は、実施例4に係る半導体装置の製造方法の第2段階を示した図である。図8(C)は、実施例4に係る半導体装置の製造方法の最終段階を示した図である。

【図9】本発明の実施例5に係る半導体装置及びその製造方法の一例を説明するための図である。

【発明を実施するための形態】

【0018】

以下、図面を参照して、本発明を実施するための形態の説明を行う。

【実施例1】

【0019】

図1は、本発明の実施例1に係る半導体装置の一例を示した断面図である。図1において、実施例1に係る半導体装置は、半導体基板10と、エミッタ電極20と、金属膜30と、はんだ層40と、保護膜50と、金属ブロック60とを備える。図1において、半導体基板10の表面を覆うようにエミッタ電極20が形成されている。エミッタ電極20の表面上には、金属膜30が形成されており、金属膜30の表面上には、はんだ層40が形成されている。金属膜30の側面及びはんだ層40の側面の下側の一部は、保護膜50と接している。保護膜50は、半導体基板10の表面及びエミッタ電極20の表面の一部を覆うとともに、水平方向には金属膜30及びはんだ層40の方に延び、金属膜30の側面及びはんだ層40の側面の一部を覆っている。また、はんだ層40の表面上には、金属ブロック60が設けられている。

【0020】

半導体基板10は、IGBT(Insulated Gate Bipolar Transistor、絶縁ゲートバイポーラトランジスタ)等の回路素子を形成する対象であり、例えば、半導体ウエハ等が用いられる。半導体基板10には、IGBT等の半導体素子以外にも種々の回路素子が形成されてよいが、図1においては、IGBT(図示せず)のエミッタ電極が半導体基板10の表面に形成された例を挙げて説明する。

【0021】

エミッタ電極20は、半導体基板10上に形成された金属パターンであり、半導体基板10にIGBTが形成された場合のIGBTの電極の一部を構成する。図1においては、半導体基板10にIGBTが形成された例が示されているため、半導体基板10の表面にはエミッタ電極20が形成されているが、例えば、パワーMOS(Metal Oxide Semiconductor)トランジスタ等が形成された場合には、ドレイン電極やゲート電極であってもよい。また、その他の回路素子や回路端子の電極であってもよい。

【0022】

エミッタ電極20は、配線用の種々の金属材料で構成されてよいが、例えば、有るアルミニウム(Al)で構成されてもよい。また、エミッタ電極20は、種々の方法で形成することができ、例えば、蒸着法、スパッタリング法、CVD(Chemical Vapor Deposition、化学的気相成長)法等により形成されてよい。

【0023】

金属膜30は、はんだ接合用電極を構成する金属材料からなる膜である。金属膜30は、はんだとの接合性が考慮され、種々の材料が選択される。例えば、金属膜30は、ニッケル(Ni)膜であってもよいし、Ni−Sn合金膜であってもよい。また、金属膜30は、複数の金属から構成されてよく、ニッケル膜の表面に金(Au)の膜が形成されてもよいし、Ni−Sn合金膜の表面に金膜が形成されてもよい。

【0024】

金属膜30は、めっき、蒸着、CVD、スパッタリング等の種々のプロセスにより形成され得るが、例えば、めっき処理により形成されためっき膜として構成されてもよい。めっき膜は、無電解めっき処理により形成された無電解めっき膜であってもよいし、電気めっき処理により形成された電気めっき膜であってもよい。また、無電解めっき膜と電気めっき膜の2層から構成されてもよい。無電解めっき処理と電気めっき処理の双方を行う場合には、無電解めっき膜がエミッタ電極20上に形成され、無電解めっき膜上に電気めっき膜が形成される構成とされることが好ましい。

【0025】

はんだ層40は、金属ブロック60を金属膜30上に接合するための接合層である。はんだ層40は、種々のはんだ材から構成され得るが、例えば、鉛を含まない鉛フリーはんだから構成されてもよい。鉛フリーはんだの場合、例えば、錫を主成分とするはんだ材が用いられてもよい。

【0026】

保護膜50は、半導体基板10の表面に形成された回路素子を保護するための膜である。よって、保護膜50は、半導体基板10の表面全体を覆い、エミッタ電極20の露出部分も覆う。更に、金属膜30の側面全体とはんだ層40の側面の一部も覆って半導体基板10の表面を密閉し、半導体基板10の表面に形成された回路素子を埃や塵から保護する。

【0027】

保護膜50は、有機材料の一種であるポリイミドから構成される。ポリイミドは、例えば、非感光性ポリイミドを用いてもよい。この場合には、マスクを用いたエッチングによりパターニングを行い、ポリイミドからなる保護膜50を形成することができる。また、保護膜50には、感光性ポリイミドを用いるようにしてもよい。この場合には、露光、現像によりパターニングを行い、ポリイミドからなる保護膜50を形成することができる。

【0028】

保護膜50は、半導体基板10の表面及びエミッタ電極20の表面を適切に保護できるように、十分な厚さを有して保護膜50を形成することができ、例えば、5μm以上の厚さを有する保護膜50を形成してもよい。

【0029】

金属ブロック60は、半導体モジュールを形成する際の半導体素子間の接続用の配線及びスペーサとなる部材であり、銅やアルミニウム等の金属材料から構成される。

【0030】

実施例1に係る半導体装置は、上述のような機能を有する構成要素から構成されているが、図1において、金属膜30及びはんだ層40は、山の裾のように下側に行くにつれて広がる形状を有している。そして、金属膜30及びはんだ層40の側面を覆っている保護膜50は、基板10側から離れて表面側に向かうにつれて、金属膜30及びはんだ層40側に迫り出す形状となっている。これにより、はんだ層40は、金属膜30が存在する領域上にその存在が制約され、はんだ層40が保護膜50と金属膜30との界面に入り込むことを防止できる構成となっている。

【0031】

図2は、比較例として、従来の半導体装置の断面構成を示した図である。図2において、エミッタ電極120上にめっき膜130、めっき膜130の上にはんだ層140が形成され、はんだ層140とめっき膜130の側面に保護膜150が接触して形成され、半導体基板110の表面を覆っている。図2において、保護膜150は、なだらかに裾が広がる断面形状を有しており、めっき膜130とエミッタ電極120との間に裾の膜厚が薄い部分が入り込むような形状をしている。めっき膜130は、膜厚自体は、右側の領域においては、厚さBの十分な厚さを有しており、はんだ層140とエミッタ電極120との合金化を防ぐことができる厚さである。しかしながら、保護膜150との界面においては、はんだ層140がめっき膜130と保護膜150との間の隙間に入り込んでいるため、はんだ層140とエミッタ電極120表面との間隔は距離Aしか無い状態となっている。この場合において、めっき膜130がニッケル膜、エミッタ電極120がアルミニウム又はアルミニウム合金、錫(Sn)を含む鉛フリーはんだによりはんだ層140を形成して場合、めっき膜130とはんだ層140との界面に、Ni−Sn合金が形成される。ここで、Niめっき膜厚の設計値は、信頼性を考慮してNi−Sn合金が形成した後の健全層が残る値とされるが、保護膜150との界面近傍のめっき膜厚が薄い破線で囲まれた箇所では、総てのNiが合金化し、次いでAlとの合金化が始まり、Al−Sn合金が形成される。しかしながら、Al−Sn合金は脆弱であるため、実装時や素子動作時の熱負荷、また使用環境での温度変化の際に、各材料の熱膨張率の差により破断が生じ、システム不良が発生してしまう。

【0032】

図3は、比較例として、図2に示した従来の半導体装置のめっき膜形成過程を示した図である。図3(A)は、めっき膜の初期形成段階を示した図であり、保護膜150がウェットエッチングにより形成され、外側に裾が広がるなだらかな傾斜を有する形状を有している。

【0033】

図3(B)は、めっき膜の途中形成段階を示した図であり、めっき膜130が厚くなるとともに、保護膜150との間に隙間が発生し始めている。

【0034】

図3(C)は、めっき膜の完成段階を示した図であり、めっき膜130が厚く形成されたが、保護膜150との界面には、大きな隙間が残っている。めっき膜130と保護膜150が接触している界面の長さは、めっき膜130の厚さと比較して、非常に短くなっている。

【0035】

このように、従来の半導体装置の構成では、保護膜150の裾がなだらかに外側に広がる形状を有するため、はんだ層140がめっき膜130の下部に侵入し、エミッタ電極120との合金化のおそれがある構成を有していた。

【0036】

一方、図1に示すように、実施例1に係る半導体装置は、保護膜50が、下方の半導体基板10及びエミッタ電極20側から離れて上方の表面側に接近するにつれて外側に張り出すような形状を有しており、保護膜50は金属膜30の側面に完全に接触するような構成となっている。よって、保護膜50と金属膜30との界面において、金属膜30の膜厚は、形成した金属膜30の厚さ分が総て残った形状となっている。また、保護膜150は、金属膜30の上方を超えてはんだ層40側に迫り出した形状となっているため、はんだ層40に対してしっかりと壁を形成している。よって、はんだ層40が金属膜30の側面に侵入することを防止でき、はんだ層40のエミッタ電極20との合金化を確実に防ぐことができる構成となっている。

【0037】

なお、図1において、保護膜50は、比較的滑らかな逆テーパー状の形状を有しているが、半導体基板10から離れるにつれて金属膜30側に迫り出す形状を有していれば、例えば、階段状に段差を有していたり、テーパー面の表面に凹凸があったりする形状を有していてもよい。保護膜50は、金属膜30との界面が金属膜30側に迫り出している形状を有すれば、保護膜50の表面の微細な構造については、種々の構成とすることができる。

【0038】

このように、実施形態1に係る半導体装置によれば、表面はんだ実装を行う半導体装置において、鉛フリーはんだ実装後の接合信頼性を向上させることができる。また、保護膜50との界面近傍においても、金属膜厚が設計通りの膜を形成することができる。更に、金属膜30とはんだ層40との合金が形成した後も、金属膜30の健全層が残り、接合強度を維持する構造とすることができる。また、総ての界面において接合強度が維持されるため、実装時や素子動作時の熱負荷、使用環境での温度変化の際、各材料の熱膨張率の差により応力が発生しても、破断等の不良を無くすことができる。

【0039】

また、実施形態1において、エミッタ電極20上に金属膜30が形成されている例について説明したが、金属膜30自体は、無電解めっきで半導体基板10上の任意の箇所に形成することができるので、必ずしもエミッタ電極20のような金属パターン上に金属膜30が形成されている必要ななく、半導体基板10上に直接形成されていてもよいし、例えばチタン(Ti)のような金属下地層の上に形成されていてもよい。

【実施例2】

【0040】

図4は、本発明の実施例2に係る半導体装置の一例を示した断面構成図である。図4において、実施例2に係る半導体装置は、半導体ウエハ13と、エミッタ電極21と、金属膜31と、はんだ層41と、保護膜51と、金属ブロック61とを備える。構成要素としては、実施例1に係る半導体装置とほぼ同様であり、金属ブロック61が、はんだ層61の上だけでなく、保護膜50の上方も含めて全体を覆うように設けられている点のみ異なっている。半導体ウエハ13の表面上にエミッタ電極21が形成され、エミッタ電極21上に金属膜31、金属膜31上にはんだ層41が形成され、金属膜31の側面全体とはんだ層41の側面の下側に接触して保護膜51が形成され、保護膜51が半導体ウエハ13及びエミッタ電極21を覆っている点も、実施例1と同様である。また、保護膜51は、半導体ウエハ13側から離れて表面側に接近するにつれて、外側の金属膜31及びはんだ層41側に迫り出し、逆テーパー状に構成されている点も、実施例1と同様である。よって、実施例2に係る半導体装置において、各構成要素の材料や構成等の詳細な内容は、実施例1で説明した内容をそのまま適用できるものとし、その説明を省略する。

【0041】

図5は、実施例2に係る半導体装置の隣接する半導体素子間の構成を示した断面図である。図5において、半導体ウエハ13の右側には、図4と同様の半導体装置の構成が示されており、左側は、右側と対称な半導体装置の構成が示されている。また、左右の半導体素子の間の半導体ウエハ13の表面には、配線22が形成されている。保護膜51は、配線22及びエミッタ電極21を含めて、左右の金属膜31及びはんだ層41に挟まれるように、半導体ウエハ13の表面を覆うように形成されている。そして、保護膜51は、左側においても、半導体ウエハ13側から離れて保護膜51の表面側に接近するにつれて、左側にある金属膜31及びはんだ層41側に迫り出す形状を有している。これにより、左側にある半導体装置においても、金属膜31の膜厚を十分確保することができ、はんだ層41が金属膜31の側面に到達するのを防ぐことができる。

【0042】

このように、複数の半導体素子が半導体ウエハ13上に配置された場合であっても、各々の半導体素子の金属膜31及びはんだ層41に対し、保護膜51を迫り出させる構成とすることにより、各々の半導体素子について、はんだ接合の信頼性を向上させることができる。

【0043】

なお、金属ブロック61は、各半導体素子のエミッタ電極21を並列接続しているので、実施例1で示したように、個別に設けられて別の箇所で接続されてもよいし、実施例2で示したように、1つの金属ブロック61がまとめて半導体素子同士を接続している構成としてもよい。

【実施例3】

【0044】

実施例3においては、実施例1及び実施例2で説明したような、本発明の実施例に係る半導体装置の製造方法の一例について説明する。本実施例に係る半導体装置を製造するためには、基板10、11上にエミッタ電極20、21等の金属パターンを形成し(金属パターン形成工程)、エミッタ電極20、21を含めて基板10、11全体を覆うように保護膜50、51を形成する(保護膜形成工程)。保護膜50、51は、ポリイミドからなり、保護膜形成工程においては、十分な加熱が必要であるため、350℃以上で十分に加熱(ベーク)処理を行う(保護膜加熱工程)。その後、保護膜50、51に逆テーパー状の開口を形成し(開口形成工程)、当該開口に金属膜30、31を充填するため、金属膜30、31を形成する(金属膜形成工程)。金属膜30、31を形成した後、必要に応じて金属膜30、31を加熱する(金属膜加熱工程)。金属膜加熱工程においては、保護膜加熱工程よりも低い温度で金属膜30、31の加熱が行われる。次に、金属膜30、31上にはんだ層40、41を形成する(はんだ層形成工程)。かかる一連の工程により、本実施例に係る半導体装置が製造される。

【0045】

上述の工程において、保護膜形成工程は、金属膜形成工程及びはんだ層形成よりも先に行われている。上述のように、保護膜50、51にポリイミドを用いた場合、保護膜加熱工程においては、350℃以上で十分に加熱(ベーク)処理を行う。一方、はんだの融点は、350℃よりも低いため、保護膜50、51のベーキングは、金属膜30、31及びはんだ層40、41を形成する前に行う必要がある。よって、本実施例に係る半導体装置の製造方法においては、保護膜形成工程は、金属膜形成工程及びはんだ層形成よりも先に行う。

【0046】

なお、以下、実施例3においては、保護膜50、51に逆テーパー形状の開口を形成する工程について、詳細に説明する。

【0047】

まず、参考例として、従来の開口の形成方法を説明する。

【0048】

図6は、参考例として、従来の半導体装置の製造方法を説明するための図である。

【0049】

図6(A)は、従来の半導体装置の製造方法の第1段階を示した図である。図6(A)において、電極120の表面上に保護膜150が形成され、保護膜150の表面に開口171を有するマスク170が配置されている。マスク170は、塗布等により保護膜150の表面上に形成される。開口171から、エッチングにより保護膜150の腐食が開始する。

【0050】

図6(B)は、従来の半導体装置の製造方法の第2段階を示した図である。図6(B)において、保護膜150の腐食が進んでいるが、深さ方向だけではなく、横方向にも腐食が進み、マスク170の下方にも腐食が開始している。

【0051】

図6(C)は、従来の半導体装置の製造方法の第3段階を示した図である。図6(C)において、保護膜150の腐食が更に進んでいるが、深さ方向だけではなく、横方向にもかなり腐食が進んだ状態となっている。また、腐食の断面形状は、両側からな中央に向かってなだらかに深くなる形状である。

【0052】

図6(D)は、従来の半導体装置の製造方法の最終段階を示した図である。図6(D)において、電極120が露出しエッチングが終了する。このとき、開口の断面形状は、両側から中央に向かって傾斜するテーパー形状となっている。

【0053】

このように、マスクを保護膜150上に形成し、単にエッチングを行った開口の形成方法では、開口を逆テーパー形状とすることができない。

【0054】

図7は、実施例3に係る半導体装置の製造方法における保護膜の開口方法の一例を示した図である。

【0055】

図7(A)は、実施例3に係る半導体装置の製造方法の第1段階の一例を示した図である。図7(A)において、電極23の表面上に保護膜52が形成されており、保護膜52の表面上に開口71を有するマスク70が配置されている。ここで、マスク70は、プリベークが施されて硬化され、保護膜52との密着性が高まった状態となっている。また、電極23は、実施例1、2で説明したエミッタ電極20、21に相当する金属パターンである。この点は、以後の実施例においても同様とする。

【0056】

上述のように、保護膜52を形成するために、ベーキング処理を行うが、ベーキング処理の前に、プリベークというベーキング処理よりも低い温度で加熱を行う処理がある。かかるプリベークは、レジストマスクの水分を除去させるため、レジストが反応しない比較的低い温度で行われる加熱処理であるが、プリベークにおいて、時間を長くしたり、温度を値以上のプリベークよりも上げたりすると、マスク70が硬化し、マスク70と保護膜52との密着性が高まる。プリベークの温度や時間は、保護膜52の特性や用途に応じて適宜定められてよいが、例えば、300℃の温度に設定されてもよい。実施例3に係る保護膜の開口方法では、保護膜52とマスク70との密着性を高める処理を行ってから、保護膜52に開口を形成するエッチング処理を行う。

【0057】

図7(B)は、実施例3に係る半導体装置の製造方法の第2段階の一例を示した図である。図7(B)において、エッチングが進んでいるが、マスク70と保護膜52との密着性が高くなっているため、横方向へのエッチングがあまり進行せず、深さ方向にエッチングが進んだ断面形状となっている。

【0058】

図7(C)は、実施例3に係る半導体装置の製造方法の第3段階の一例を示した図である。図7(C)において、エッチングが更に進んでいるが、マスク70と保護膜52との密着性が高くなっているため、横方向へのエッチングが殆ど進行せず、深さ方向に大幅にエッチングが進んだ断面形状となっている。その結果、マスク70の開口71よりも、横幅の広い開口が形成されており、マスク70付近は逆テーパー形状となっている。

【0059】

図7(D)は、実施例3に係る半導体装置の製造方法の最終段階の一例を示した図である。図7(D)において、エッチングが更に進んで電極23の表面が露出している。マスク70と保護膜52との密着性が高いため、マスク70付近では横方向へのエッチングが殆ど進行せず、電極23付近の深い位置では横方向へのエッチングが進行した状態となっている。これにより、全体として逆テーパー状の開口が形成されている。

【0060】

このように、マスク70と保護膜52との密着性を高める処理を行ってから保護膜52にエッチングで開口を形成することにより、保護膜52を逆テーパー状の側面を有する形状に加工することができる。

【0061】

なお、上述の例では、プリベーク処理によりマスク70と保護膜52との密着性を高める例について説明したが、密着性の良い保護膜52とマスク70の組み合わせを採用し、それによりマスク70と保護膜52との密着性を高めてもよいし、更にプリベーク処理を組み合わせるようにしてもよい。

【0062】

このように、実施例3に係る半導体装置の製造方法によれば、保護膜52とマスク70との密着性を高めることにより、逆テーパー状の開口を形成し、本実施例に係る半導体装置を製造することができる。

【0063】

なお、逆テーパー形状のレジストを用いて、テーパー形状の金属めっきを形成する例として、上述の特許文献2に記載された製造方法がある。特許文献2に記載された金属めっきを先に形成し、その後に保護膜を形成して本実施例に係る半導体装置を製造する方法も形式上は考えられる。しかしながら、特許文献2に記載のめっき方法を、本実施例に係る半導体装置及びその製造方法に適用するのは、以下の理由で不可能である。

【0064】

まず、特許文献2に記載されためっき方法を応用した半導体装置の製造方法には、次の3つのプロセスが考えられる。

(1) レジスト→めっき→はんだ→レジスト除去→保護膜形成

(2) レジスト→めっき→レジスト除去→はんだ→保護膜形成

(3) レジスト→めっき→レジスト除去→保護膜形成→はんだ

まず、本実施例に係る半導体装置及びその製造方法において、保護膜52は、ポリイミド等の有機保護膜を用いることが好ましいが、例えばポリイミドをイミド化して形成するに当たり、350℃以上でベーク処理することが必要である。一方、はんだの融点は350℃未満であるため、はんだ層を形成してから保護膜52を形成することは、保護膜52の加熱処理の際にはんだが溶融していまい、不可能である。よって、上記(1)、(2)の製造方法では、本実施例に係る半導体装置を製造することはできない。

【0065】

また、上記(3)の製造方法においても、温度上の制約から、本実施例に係る半導体装置を製造することはできない。即ち、めっき処理により形成されためっき膜はアモルファス膜となるが、アモルファス膜は、熱が加わると再結晶化する。再結晶化が進むと、膜収縮が発生し、クラックが生じる。クラックが生じると、クラック中をはんだが浸透し、めっき膜の下層にある電極に到達する。そうすると、電極とはんだの合金化が進むため、脆弱化が問題となる。

【0066】

ここで、再結晶化が開始する温度は物質により異なるが、基本的に300℃以下の温度がアモルファス膜の温度限界となる。よって、めっき膜を形成した後に保護膜52のベーキング処理を行うと、めっき膜の再結晶化が開始してしまい、めっき膜にクラックが生じてしまう。

【0067】

よって、本実施例に係る半導体装置を製造するためには、本実施例に係る半導体装置の製造方法のように、保護膜52を形成してから金属膜30、31を形成する必要があり、特許文献2に記載のめっき方法を適用することはできない。

【実施例4】

【0068】

図8は、本発明の実施例4に係る半導体装置の製造方法の一例を説明するための図である。実施例4に係る半導体装置の製造方法においては、保護膜を複数種類用いて開口を行い、逆テーパー状の保護膜を形成する例について説明する。

【0069】

図8(A)は、実施例4に係る半導体装置の製造方法の第1段階を示した図である。図8(A)において、電極24上に3種類の保護膜53、54、55が積層され、その上に開口73を有するマスク72が配置された状態が示されている。保護膜53、54、55は、同一エッチング液を用いた場合に、エッチング速度が異なるポリイミド膜が3種類選択されている。そして、最下層の保護膜53は、中間層の保護膜54よりもエッチング速度が速く、保護膜54は最上層の保護膜55よりもエッチング速度が速い材料が選択されている。

【0070】

このような構成の保護膜53、54、55を用いて、エッチングを開始すると、図8(A)に示すように、まず最上層の保護膜55が腐食される。

【0071】

図8(B)は、実施例4に係る半導体装置の製造方法の第2段階を示した図である。図8(B)において、中間層の保護膜54がエッチングにより除去されているが、最上層の保護膜55よりもエッチング速度が速いため、エッチング面の傾斜が急になっている。

【0072】

図8(C)は、実施例4に係る半導体装置の製造方法の最終段階を示した図である。図8(C)において、最下層の保護膜53がエッチングにより除去され、電極24が露出して開口が完成しているが、保護膜53のエッチング速度が最も速いため、保護膜53の横方向のエッチングが進み、エッチング幅が大きくなっている。その結果、保護膜55、54、53の順に上から順にエッチング幅が大きくなり、逆テーパー状の開口が形成されている。

【0073】

このように、複数種類の保護膜53、54、55のエッチングの速度差を利用し、保護膜53、54、55を逆テーパー状に形成してもよい。なお、図8においては、3種類の保護膜53、54,55を用いたが、用途に応じて、2種類の保護膜を用いてもよいし、4種類以上の保護膜を用いるようにしてもよい。

【実施例5】

【0074】

図9は、本発明の実施例5に係る半導体装置及びその製造方法の一例を説明するめの図である。実施例5に係る半導体装置及びその製造方法においては、異方性ドライエッチングにより保護膜56の開口75を形成する例について説明する。

【0075】

図9において、電極25上に、垂直な側面の開口を有する保護膜56が積層され、保護膜56上に開口75を有するマスク74が配置された状態が示されている。保護膜56は、非感光性ポリイミド膜から構成される。マスク74は、保護膜56に比較して選択比が大きいものを使用する。例えば、酸化膜等を用いてもよい。マスク74の開口75形成後に、異方性ドライエッチングを行うことにより、マスク74の開口75に垂直に深掘りされ、保護膜56の表面に垂直な側面を有する開口が形成される。なお、図示されていないが、電極26は半導体基板上に形成されているので、開口は半導体基板にも垂直な開口となる。このように、ドライエッチングにより、保護膜56の表面及び基板に垂直な側壁を有する開口を保護膜56に形成するようにしてもよい。かかる構成を有する保護膜に金属膜30、31を充填し、その上にはんだ層40、41を形成した場合であっても、金属膜30、31は膜厚通りの厚さで電極25

とはんだ層40、41を隔てることができるため、はんだ層40、41と電極25との合金化を防止することができる。

【0076】

以上、本発明の好ましい実施例について詳説したが、本発明は、上述した実施例に制限されることはなく、本発明の範囲を逸脱することなく、上述した実施例に種々の変形及び置換を加えることができる。

【産業上の利用可能性】

【0077】

本発明は、はんだ実装構造を有する半導体装置に利用することができる。

【符号の説明】

【0078】

10、13 半導体基板

20〜25 電極

30、31 金属膜

40、41 はんだ層

50〜56 保護膜

60、61 金属ブロック

70、72、74 マスク

71、73、75 開口

【特許請求の範囲】

【請求項1】

基板と、

該基板に積層された金属膜と、

該金属膜に積層されたはんだ層と、

前記基板に積層され、前記金属膜及び前記はんだ層に接するように形成されたポリイミドからなる保護膜とを備え、

該保護膜は、前記金属膜と接する界面において、前記基板側から離れて表面側に接近するにつれて前記金属膜側に迫り出す形状を有することを特徴とする半導体装置。

【請求項2】

基板と、

該基板の表面に形成された金属パターンと、

該金属パターンに積層された金属膜と、

該金属膜に積層されたはんだ層と、

前記基板に積層されるとともに前記金属膜及び前記はんだ層に接するように形成され、前記金属パターン間を絶縁するポリイミドからなる保護膜とを備え、

該保護膜は、前記金属膜と接する界面において、前記基板側から離れて表面側に接近するにつれて前記金属膜側に迫り出す形状を有することを特徴とする半導体装置。

【請求項3】

前記金属膜は、複数の金属が積層されて形成されていることを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記複数の金属は、ニッケルと金を含むことを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記金属膜は、めっき膜であることを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

【請求項6】

基板上に金属パターンを形成する金属パターン形成工程と、

前記基板及び金属パターンに積層してポリイミドからなる保護膜を形成する保護膜形成工程と、

前記金属パターン上に形成された前記保護膜に、前記金属パターン側から離れて前記保護膜の表面側に接近するにつれて前記保護膜が内側に迫り出すような開口を形成し、前記金属パターンを露出させる開口形成工程と、

前記開口に金属膜を充填する金属膜形成工程と、を有することを特徴とする半導体装置の製造方法。

【請求項7】

前記開口形成工程は、前記保護膜上にマスクを形成する工程と、

該マスクをパターニングする工程と、

前記基板を所定温度以上で加熱し、前記マスクと前記保護膜との密着性を高める工程と、

前記マスクを用いて、前記保護膜をエッチングして前記開口を形成する工程と、を含むことを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記金属膜形成工程は、めっき処理によりめっき膜を形成する工程であることを特徴とする請求項6又は7に記載の半導体装置の製造方法。

【請求項9】

前記金属膜形成工程の後、前記金属膜を加熱する金属膜加熱工程を更に有し、

前記保護膜形成工程は、ポリイミドを加熱する保護膜加熱工程を含み、

該保護膜加熱工程における加熱温度は、前記金属膜加熱工程における加熱温度の上限よりも高いことを特徴とする請求項6乃至8のいずれか一項に記載の半導体装置の製造方法。

【請求項10】

前記金属膜加熱工程の後、前記金属膜上にはんだ層を形成するはんだ層形成工程を更に有することを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

基板と、

該基板に積層された金属膜と、

該金属膜に積層されたはんだ層と、

前記基板に積層され、前記金属膜及び前記はんだ層に接するように形成されたポリイミドからなる保護膜とを備え、

該保護膜と前記金属膜が接する界面は、前記基板に垂直であることを特徴とする半導体装置。

【請求項12】

基板上に金属パターンを形成する金属パターン形成工程と、

前記基板及び金属パターンに積層してポリイミドからなる保護膜を形成する保護膜形成工程と、

前記金属パターン上に形成された前記保護膜に、前記基板に垂直な開口を形成し、前記金属パターンを露出させる開口形成工程と、

前記開口に金属膜を充填する金属膜形成工程と、を有することを特徴とする半導体装置の製造方法。

【請求項1】

基板と、

該基板に積層された金属膜と、

該金属膜に積層されたはんだ層と、

前記基板に積層され、前記金属膜及び前記はんだ層に接するように形成されたポリイミドからなる保護膜とを備え、

該保護膜は、前記金属膜と接する界面において、前記基板側から離れて表面側に接近するにつれて前記金属膜側に迫り出す形状を有することを特徴とする半導体装置。

【請求項2】

基板と、

該基板の表面に形成された金属パターンと、

該金属パターンに積層された金属膜と、

該金属膜に積層されたはんだ層と、

前記基板に積層されるとともに前記金属膜及び前記はんだ層に接するように形成され、前記金属パターン間を絶縁するポリイミドからなる保護膜とを備え、

該保護膜は、前記金属膜と接する界面において、前記基板側から離れて表面側に接近するにつれて前記金属膜側に迫り出す形状を有することを特徴とする半導体装置。

【請求項3】

前記金属膜は、複数の金属が積層されて形成されていることを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記複数の金属は、ニッケルと金を含むことを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記金属膜は、めっき膜であることを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

【請求項6】

基板上に金属パターンを形成する金属パターン形成工程と、

前記基板及び金属パターンに積層してポリイミドからなる保護膜を形成する保護膜形成工程と、

前記金属パターン上に形成された前記保護膜に、前記金属パターン側から離れて前記保護膜の表面側に接近するにつれて前記保護膜が内側に迫り出すような開口を形成し、前記金属パターンを露出させる開口形成工程と、

前記開口に金属膜を充填する金属膜形成工程と、を有することを特徴とする半導体装置の製造方法。

【請求項7】

前記開口形成工程は、前記保護膜上にマスクを形成する工程と、

該マスクをパターニングする工程と、

前記基板を所定温度以上で加熱し、前記マスクと前記保護膜との密着性を高める工程と、

前記マスクを用いて、前記保護膜をエッチングして前記開口を形成する工程と、を含むことを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記金属膜形成工程は、めっき処理によりめっき膜を形成する工程であることを特徴とする請求項6又は7に記載の半導体装置の製造方法。

【請求項9】

前記金属膜形成工程の後、前記金属膜を加熱する金属膜加熱工程を更に有し、

前記保護膜形成工程は、ポリイミドを加熱する保護膜加熱工程を含み、

該保護膜加熱工程における加熱温度は、前記金属膜加熱工程における加熱温度の上限よりも高いことを特徴とする請求項6乃至8のいずれか一項に記載の半導体装置の製造方法。

【請求項10】

前記金属膜加熱工程の後、前記金属膜上にはんだ層を形成するはんだ層形成工程を更に有することを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

基板と、

該基板に積層された金属膜と、

該金属膜に積層されたはんだ層と、

前記基板に積層され、前記金属膜及び前記はんだ層に接するように形成されたポリイミドからなる保護膜とを備え、

該保護膜と前記金属膜が接する界面は、前記基板に垂直であることを特徴とする半導体装置。

【請求項12】

基板上に金属パターンを形成する金属パターン形成工程と、

前記基板及び金属パターンに積層してポリイミドからなる保護膜を形成する保護膜形成工程と、

前記金属パターン上に形成された前記保護膜に、前記基板に垂直な開口を形成し、前記金属パターンを露出させる開口形成工程と、

前記開口に金属膜を充填する金属膜形成工程と、を有することを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−16538(P2013−16538A)

【公開日】平成25年1月24日(2013.1.24)

【国際特許分類】

【出願番号】特願2011−146279(P2011−146279)

【出願日】平成23年6月30日(2011.6.30)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

【公開日】平成25年1月24日(2013.1.24)

【国際特許分類】

【出願日】平成23年6月30日(2011.6.30)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

[ Back to top ]