半導体装置及びその製造方法

【課題】 対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和する。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、素子を形成するための活性領域を分離するための素子分離領域を有する半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体装置の活性領域を分離する構造体は素子分離領域と呼ばれ、一般的には、浅い溝によって分離されることから、シャロートレンチアイソレーション(Shallow Trench Isolation:STI)と呼ばれている構造で素子分離されている場合が多い。

【0003】

半導体装置での素子分離構造では、一般的に、STIが用いられている。このSTIでは、素子を分離するための溝を形成後、溝の内部に絶縁膜を埋め込んで素子の絶縁を行っている(例えば、特開2010−287774号公報(特許文献1)参照)。この場合、溝の深さは、STIで分離する活性領域を電気的に分離できる深さに設定される。

【0004】

また、場合によっては、製造回路パターン上、繰り返し構造を有する場合は、STIの溝を薄く絶縁膜で覆った後、ゲート電極と同等の材料を埋め込み、溝下部領域を電気的に絶縁させる方向に電圧を印加させる方法も近年提案されている(例えば、2008_IEDM_p1-4_6F2 buried wordline DRAM cell for 40nm and beyond _T.Schloesser etal(Qimonda)(非特許文献1)参照)されている。

【0005】

前者のSTIを絶縁膜で埋設した構造では、一般的には、CVD酸化膜で埋設するが、この構造でも、例えば、DRAMなどの高集積なメモリデバイスを微細化した場合、データを記憶させた対象セルのビット線と隣接セルのワードライン(Neighbor Word Line(NWL))の動作電圧条件によっては、STIの酸化膜(一般的には比誘電率:3.8-4.2)を通した電気力線が対象セルのビット線の静電ポテンシャルに影響を与え、閾値電圧の変動やp/n接合部の電界強度に影響を及ぼすという問題がある。

【0006】

一方、後者では、非特許文献1にも記述されている素子を分離する領域に通常のSTIの代わりに、絶縁ゲート(Isolation Gate(IG))を設け、電気的にIGの溝下部を電気的に絶縁させる手法が提案されている。

【0007】

しかし、IGの溝下部を電気的に絶縁するバイアスを印加すると、その隣接するセルのビット線の半導体層の静電ポテンシャルの影響により、当該ビット線のトランジスタ特性に影響を及ぼすという問題が、デバイスの微細化と共に顕著となってくる。

【0008】

例えば、P-Well内のn-chトランジスタを素子分離する際に、IGには負(-)のバイアスを印加し、IG下部の半導体層を空乏化させて電気的に絶縁する。このIGの電圧はそのまま対象セルのビット線の半導体層にも印加されるため、トランジスタ特性がIGのバイアス条件によって変動してしまうという問題がある。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2010−287774号公報

【非特許文献】

【0010】

【非特許文献1】2008_IEDM_p1-4_6F2 buried wordline DRAM cell for 40nm and beyond _T.Schloesser etal(Qimonda)

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明は、上記従来技術の問題点を解決するものであり、その目的は、対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和することが可能な半導体装置及びその製造方法を提供することにある。

【課題を解決するための手段】

【0012】

本発明に係る半導体装置は、

半導体基板に形成され、半導体素子を形成するための活性領域と、

前記半導体基板内に形成され、前記活性領域を分離するための素子分離領域と、

前記素子分離領域内に設けられた空洞部を有することを特徴とする。

【0013】

また、本発明に係る半導体装置の製造方法は、

半導体基板に、半導体素子を形成するための活性領域を形成し、

前記半導体基板内に、前記活性領域を分離するための素子分離領域を形成し、

前記素子分離領域内に空洞部を形成することを特徴とする。

【発明の効果】

【0014】

本発明によれば、対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和することができる。

【図面の簡単な説明】

【0015】

【図1】本発明の第1の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図2】本発明の第1の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図3】本発明の第1の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図4】本発明の第1の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図5】本発明の第1の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図6】本発明の第2の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図7】本発明の第2の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図8】本発明の第2の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図9】本発明の第2の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図10】本発明の第2の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図11】本発明の第2の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図12】本発明の実施の形態による効果を説明するための図である。

【発明を実施するための形態】

【0016】

本発明の実施の形態について図面を参照して詳細に説明する。

【0017】

(第1の実施の形態)

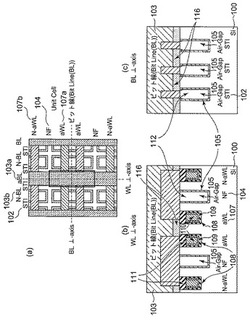

最初に、図1〜図5を参照して、本発明の第1の実施の形態に係る半導体装置の製造方法について説明する。ここで、図1〜図5において、(a)は平面図、(b)はワード線(Word-Line(WL))垂直断面図、(c)はビット線(Bit-Line(BL))垂直断面図をそれぞれ示す。

【0018】

図1に示すように、半導体基板100 中に、素子(セルアレイトランジスタ)101の分離を行うための素子分離領域(シャロートレンチアイソレーション(STI))102を形成するためのパターニングを行うため、フォトレジストの塗布及び露光を行う。

【0019】

この際、対象セルのビット線(BL)103aに隣接する隣接ビット線(N−BL)103bとの分離部のSTI102と同時に、WL垂直方向の隣接ビット線(N−BL)103b間の分離部(ここでは、ノーマルフィールド(NF)104と称する)の両方を同時にパターニングしても良いし、別々にラインパターンで形成してもよい。

【0020】

次いで、STI102及びNF104を形成するためのドライエッチングを行ない、STI102及びNF104の内壁を薄い内壁酸化膜105で覆う。

【0021】

次いで、STI102及びNF104内部を埋め込み絶縁膜(例えば、SiN膜)106で埋設し、平坦化する。

【0022】

次に、溝ゲート構造のセルアレイトランジスタ101を形成する。

【0023】

最初に、WL(ワードライン)107のパターンを形成するためマスク膜(図示せず)を形成し、次いでフォトリソグラフィーにてWL107のパターンを焼付けし、マスク膜をパターニングする。

【0024】

次に、レジスト除去後、パターニングしたマスク膜によるセルフアラインプロセスを介してWL107のパターンを半導体層の内部に形成する。

【0025】

次に、洗浄後、WL107のゲート絶縁膜108を形成する。ここでは、高温の高速昇温プロセス (Rapid Thermal Process(RTP))を用いてゲート酸化(例えば、6nm厚)を行なう。

【0026】

そのままポリシリコンのゲート電極を形成しても良いが、図1では、埋め込み型WL107の形成方法により説明する。

【0027】

埋め込み型WL107を形成するため、TiN109及びW110を埋設し、所望の深さで埋め込み型WL107の電極部を形成する。

【0028】

次いで、その上部に、キャップ絶縁膜111(例えば、CVD酸化膜)を埋設し、平坦化する。

【0029】

その後、BL線103及び後述のビットコンタクト(Bit-Contact(BC))形成のためのビットコンタクト層間膜112を堆積する。

【0030】

次に、図2に示すように、ビットコンタクト(BC)113を開口する。

【0031】

最初に、ビットコンタクト層間膜112上にフォトリソグラフィーで、BCパターンをレジストを用いてパターニングする。

【0032】

次いで、ドライエッチングプロセスでビットコンタクト(BC)113を開口する。この際、ビットコンタクト(BC)113はWL107(フィールド部)に開口端がオーバーラップし、STI102及びNF104の表面に埋設している埋め込み絶縁膜106の表面が露出するように開口する。

【0033】

次に、図3に示すように、STI102及びNF104に中空構造(Air Gap)構造を形成する。

【0034】

最初に、上述のようにビットコンタクト(BC)113を開口した後、洗浄を行なう。

【0035】

その後、STI102及びNF104の内部に埋設された埋め込み絶縁膜106を除去するために、ホットリン酸114で埋め込み絶縁膜106を除去し、空洞部115を形成する。このようにして、Air-Gap分離構造が形成される。

【0036】

次に、Air-Gap分離構造形成後、図4に示すように、ビットコンタクト(BC)113に選択エピタキシャル成長を行い、エピタキシャル成長層116を形成して、ビットコンタクト(BC)113の底部を埋設する。この際、STI102及びNF104の表面のホットリン酸114で除去された埋め込み絶縁膜(SIN膜)106の開口部は選択エピタキシャル成長のオーバー成長で埋設される。

【0037】

次に、図5に示すように、ビットコンタクト(BC)113に形成したエピタキシャル成長層116に不純物をイオン注入し、熱処理を行なった後、 ビット線(BL)103を形成するためのメタル配線を行なう。ここでは、TiN/W膜を成膜し、BL103の配線パターニングを行う。

【0038】

このようにして、STI102及びNF104に中空構造の素子分離構造を有する半等体装置が完成する。

【0039】

この半導体装置は、図5に示すように、半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する。

【0040】

また、素子分離領域(STI102、NF104)は溝状に形成されており、素子分離領域(STI102、NF104)の内壁には、内壁酸化膜105が形成されている。

【0041】

そして、空洞部105の比誘電率(理想的には1.0)は、内壁酸化膜105の比誘電率(3.8〜4.2程度)よりも低い。

【0042】

このような構造の下、半導体素子は、対象セル(Unit Cell)のワード線107とビット線103に接続されたセルアレイトランジスタ101である。空洞部105は、ワード線(aWL)107aに隣接する隣接ワード線(N−aWL)107bの電位の影響に伴うビット線(aBL)103aへの電界を緩和する。さらに、空洞部105は、ワード線(aWL)107aの接合リーク電流を減少させる。

【0043】

(第2の実施の形態)

最初に、図6〜図11を参照して、本発明の第2の実施の形態に係る半導体装置の製造方法について説明する。ここで、図6〜図11において、(a)は平面図、(b)はワード線(Word-Line(WL))垂直断面図、(c)はビット線(Bit-Line(BL))垂直断面図をそれぞれ示す。

【0044】

最初に、図6に示すように、半導体基板200中に、素子分離となるシャロートレンチアイソレーション(STI)201を形成するためのパターニングを行うため、フォトレジストの塗布及び霧光を行う。この時、対象セル(Unit Cell)のビット線(aBL)202aに隣接する隣接ビット線(N−BL)202bとの分離部のSTI201と同時に、WL垂直方向の隣接ビット線(N−BL)202b間の分離部(ここではノーマルフィールド(NF)203と称する)の両方を同時にパターニングしても良いし、別々にラインパターンで形成しても良い。

【0045】

次いで、STI201及び NF203を形成するためのドライエッチングを行って、STI用トレンチ204及びNF用トレンチ205を形成する。この時に、STI用トレンチ204及びNF用トレンチ205の溝形状を間口がやや狭くなるボーイング形状で形成する。近年の微細化したデバイスでは、STI201やNF203の分離幅が100nm以下になってきている。ここでは50nmの例で示す。

【0046】

次に、図7に示すように、図6で示したボーイング形状のSTI用トレンチ204及びNF用トレンチ205(素子分離構造部)に対して高温のRTPプロセスにより内壁酸化を行なって、STI用トレンチ204及びNF用トレンチ205の内壁に内壁酸化膜206を形成する。内壁酸化膜206の厚さは、例えば、10nmである。これにより、STI用トレンチ204及びNF用トレンチ205の素子分離開口部は約45nm程度となる。

【0047】

次に、図8に示すように、STI用トレンチ204及びNF用トレンチ205の内壁に形成した内壁酸化膜206の表面に、絶縁膜207を堆積する。この絶縁膜207は、例えば、CVD酸化膜或いはプラズマ酸化膜であり、その膜厚は、約30nm程度である。この時、STI用トレンチ204及びNF用トレンチ205の素子分離開口部が狭いために、開口部が先に閉塞し、内部に空洞が残ったまま絶縁膜207の成膜が完了する。このようにして、空洞部208を有するSTI201及びNF203が完成する。尚、この絶縁膜207は、場合によってはCVD-SiN膜やプラズマSiN膜でも良い。

【0048】

次に、空洞部208を有するSTI201及びNF203が完成した後、図9に示すように、溝ゲート構造のセルアレイトランジスタ209を形成する。

【0049】

最初に、WL210のパターン形成するためマスク膜(図示せず)を成膜し、次いで、フォトリソグラフィーにてWL210のパターンを焼付けし、マスク膜をパターニングする。

【0050】

レジスト除去後、パターニングしたマスク膜を用いてセルフアラインプロセスでWL210のパターンを半導体層の内部に形成する。

【0051】

洗浄後、WL210のゲート絶縁膜210を形成する。ここでは、高温の高速昇温プロセス(Rapid Thermal Process(RTP))を用いてゲート酸化(例えば、6nm厚)を行なう。そのままポリシリコンのゲート電極を形成しても良いが、図9では埋め込み型WL210の形成方法で説明する。

【0052】

埋め込み型WL210の形成のため、TiN211及びW212を埋設し、所望の深さで埋め込み型WL210の電極部を形成する。

【0053】

次いで、その上部に、キャップ絶縁膜213(ここでは、CVD酸化膜)を埋設し、平坦化する。

【0054】

その後、BL線103及び後述のビットコンタクト(Bit-Contact(BC))形成のためのビットコンタクト層間SiN膜214及びビットコンタクト層間酸化膜215を堆積する。

【0055】

次に、図10に示すように、ビットコンタクト(BC)216を開口する。

【0056】

最初に、ビットコンタクト層間酸化膜215上にフォトリソグラフィーで、BCパターンをレジストを用いてパターニングする。

【0057】

次いで、ドライエッチングプロセスでビットコンタクト(BC)216を開口する。

【0058】

その後、ビットコンタクト(BC)216が半導体層からはみ出さないように、ビットコンタクト層間SiN膜214で一度エッチストップした後、ビットコンタクトSW膜(SiN膜サイドウォール)217を形成し、ビットコンタクト層間SiN膜214をエッチングし、ビットコンタクト(BC)216を開口する。

【0059】

次に、図11に示すように、ビットコンタクト(BC)216に不純物をイオン注入し、熱処理を行なった後、ビット線(BL)202形成のためのメタル配線を行なう。ここではTiN/W膜を成膜し、ビット線(BL)202の配線パターニングを行なう。この際、ビットコンタクト(BC)216との接続に不純物がドープされたポリシリコンを用いても良い。これにより、STI201及びNF203に中空構造の素子分離構造を有する半導体装置が完成する。

【0060】

この半導体装置は、図11に示すように、半導体基板200に形成され、半導体素子201を形成するための活性領域と、半導体基板200内に形成され、活性領域を分離するための素子分離領域(STI201、NF203)と、素子分離領域(STI201、NF203)内に設けられた空洞部208を有する。

【0061】

また、素子分離領域(STI201、NF203)は、間口が狭くなるボーイング形状に形成されており、素子分離領域(STI201、NF203)の内壁には、内壁酸化膜206が形成され、内壁酸化膜206の表面には絶縁膜207が形成されている。

【0062】

そして、空洞部208の比誘電率(理想的には1.0)は、内壁酸化膜206の比誘電率(3.8〜4.2程度)よりも低い。

【0063】

このような構造に下、半導体素子は、対象セル(Unit Cell)のワード線210とビット線202に接続されたセルアレイトランジスタ209である。空洞部208は、ワード線(aWL)210aに隣接する隣接ワード線(N−aWL)210bの電位の影響に伴うビット線(aBL)202aへの電界を緩和する。さらに、空洞部208は、ワード線(aWL)210aの接合リーク電流を減少させる。

【0064】

次に、図12を参照して、本発明の実施の形態による効果について説明する。ここで、(a)はセルアレイトランジスタ特性のオン電流特性を示し、(b)はセルアレイトランジスタ特性の接合リーク電流を示す。

【0065】

図12(a)に示すように、本発明を用いることにより、デバイスの微細化に伴うセルアレイトランジスタのオン電流の隣接WLの影響による低下を抑制できる。また、隣接ワード電(WL)の電位の影響に伴う対象ビット線(BL)の電界緩和が可能となる。

【0066】

さらに、図12(b)に示すように、本発明を用いることにより、接合リーク電流も改善できる。

【0067】

以上、本発明者によってなされた発明を実施例に基づき説明したが、本発明は上記実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【符号の説明】

【0068】

100 半導体基板

101 セルアレイトランジスタ

102 STI

103 ビット線(BL)

104 NF

105 内壁酸化膜

106 埋め込み絶縁膜

107 ワード線(WL)

108 ゲート絶縁膜

109 TiN

110 W

111 キャップ絶縁膜

112 ビットコンタクト層間膜

113 ビットコンタクト(BC)

114 ホットリン酸

115 空洞部

116 エピタキシャル成長層

200 半導体基板

201 STI

202 ビット線(BL)

203 NF

204 STI用トレンチ

205 NF用トレンチ

206 内壁酸化膜

207 絶縁膜

208 空洞部

209 セルアレイトランジスタ

210 ワード線(WL)

211 TiN

212 W

213 キャップ絶縁膜

214 ビットコンタクト層間SiN膜

215 ビットコンタクト層間酸化膜215

216 ビットコンタクト(BC)

217 ビットコンタクトSW膜

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、素子を形成するための活性領域を分離するための素子分離領域を有する半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体装置の活性領域を分離する構造体は素子分離領域と呼ばれ、一般的には、浅い溝によって分離されることから、シャロートレンチアイソレーション(Shallow Trench Isolation:STI)と呼ばれている構造で素子分離されている場合が多い。

【0003】

半導体装置での素子分離構造では、一般的に、STIが用いられている。このSTIでは、素子を分離するための溝を形成後、溝の内部に絶縁膜を埋め込んで素子の絶縁を行っている(例えば、特開2010−287774号公報(特許文献1)参照)。この場合、溝の深さは、STIで分離する活性領域を電気的に分離できる深さに設定される。

【0004】

また、場合によっては、製造回路パターン上、繰り返し構造を有する場合は、STIの溝を薄く絶縁膜で覆った後、ゲート電極と同等の材料を埋め込み、溝下部領域を電気的に絶縁させる方向に電圧を印加させる方法も近年提案されている(例えば、2008_IEDM_p1-4_6F2 buried wordline DRAM cell for 40nm and beyond _T.Schloesser etal(Qimonda)(非特許文献1)参照)されている。

【0005】

前者のSTIを絶縁膜で埋設した構造では、一般的には、CVD酸化膜で埋設するが、この構造でも、例えば、DRAMなどの高集積なメモリデバイスを微細化した場合、データを記憶させた対象セルのビット線と隣接セルのワードライン(Neighbor Word Line(NWL))の動作電圧条件によっては、STIの酸化膜(一般的には比誘電率:3.8-4.2)を通した電気力線が対象セルのビット線の静電ポテンシャルに影響を与え、閾値電圧の変動やp/n接合部の電界強度に影響を及ぼすという問題がある。

【0006】

一方、後者では、非特許文献1にも記述されている素子を分離する領域に通常のSTIの代わりに、絶縁ゲート(Isolation Gate(IG))を設け、電気的にIGの溝下部を電気的に絶縁させる手法が提案されている。

【0007】

しかし、IGの溝下部を電気的に絶縁するバイアスを印加すると、その隣接するセルのビット線の半導体層の静電ポテンシャルの影響により、当該ビット線のトランジスタ特性に影響を及ぼすという問題が、デバイスの微細化と共に顕著となってくる。

【0008】

例えば、P-Well内のn-chトランジスタを素子分離する際に、IGには負(-)のバイアスを印加し、IG下部の半導体層を空乏化させて電気的に絶縁する。このIGの電圧はそのまま対象セルのビット線の半導体層にも印加されるため、トランジスタ特性がIGのバイアス条件によって変動してしまうという問題がある。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2010−287774号公報

【非特許文献】

【0010】

【非特許文献1】2008_IEDM_p1-4_6F2 buried wordline DRAM cell for 40nm and beyond _T.Schloesser etal(Qimonda)

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明は、上記従来技術の問題点を解決するものであり、その目的は、対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和することが可能な半導体装置及びその製造方法を提供することにある。

【課題を解決するための手段】

【0012】

本発明に係る半導体装置は、

半導体基板に形成され、半導体素子を形成するための活性領域と、

前記半導体基板内に形成され、前記活性領域を分離するための素子分離領域と、

前記素子分離領域内に設けられた空洞部を有することを特徴とする。

【0013】

また、本発明に係る半導体装置の製造方法は、

半導体基板に、半導体素子を形成するための活性領域を形成し、

前記半導体基板内に、前記活性領域を分離するための素子分離領域を形成し、

前記素子分離領域内に空洞部を形成することを特徴とする。

【発明の効果】

【0014】

本発明によれば、対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和することができる。

【図面の簡単な説明】

【0015】

【図1】本発明の第1の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図2】本発明の第1の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図3】本発明の第1の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図4】本発明の第1の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図5】本発明の第1の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図6】本発明の第2の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図7】本発明の第2の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図8】本発明の第2の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図9】本発明の第2の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図10】本発明の第2の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図11】本発明の第2の実施の形態に係る半導体装置の製造方法の一工程を示す図である。

【図12】本発明の実施の形態による効果を説明するための図である。

【発明を実施するための形態】

【0016】

本発明の実施の形態について図面を参照して詳細に説明する。

【0017】

(第1の実施の形態)

最初に、図1〜図5を参照して、本発明の第1の実施の形態に係る半導体装置の製造方法について説明する。ここで、図1〜図5において、(a)は平面図、(b)はワード線(Word-Line(WL))垂直断面図、(c)はビット線(Bit-Line(BL))垂直断面図をそれぞれ示す。

【0018】

図1に示すように、半導体基板100 中に、素子(セルアレイトランジスタ)101の分離を行うための素子分離領域(シャロートレンチアイソレーション(STI))102を形成するためのパターニングを行うため、フォトレジストの塗布及び露光を行う。

【0019】

この際、対象セルのビット線(BL)103aに隣接する隣接ビット線(N−BL)103bとの分離部のSTI102と同時に、WL垂直方向の隣接ビット線(N−BL)103b間の分離部(ここでは、ノーマルフィールド(NF)104と称する)の両方を同時にパターニングしても良いし、別々にラインパターンで形成してもよい。

【0020】

次いで、STI102及びNF104を形成するためのドライエッチングを行ない、STI102及びNF104の内壁を薄い内壁酸化膜105で覆う。

【0021】

次いで、STI102及びNF104内部を埋め込み絶縁膜(例えば、SiN膜)106で埋設し、平坦化する。

【0022】

次に、溝ゲート構造のセルアレイトランジスタ101を形成する。

【0023】

最初に、WL(ワードライン)107のパターンを形成するためマスク膜(図示せず)を形成し、次いでフォトリソグラフィーにてWL107のパターンを焼付けし、マスク膜をパターニングする。

【0024】

次に、レジスト除去後、パターニングしたマスク膜によるセルフアラインプロセスを介してWL107のパターンを半導体層の内部に形成する。

【0025】

次に、洗浄後、WL107のゲート絶縁膜108を形成する。ここでは、高温の高速昇温プロセス (Rapid Thermal Process(RTP))を用いてゲート酸化(例えば、6nm厚)を行なう。

【0026】

そのままポリシリコンのゲート電極を形成しても良いが、図1では、埋め込み型WL107の形成方法により説明する。

【0027】

埋め込み型WL107を形成するため、TiN109及びW110を埋設し、所望の深さで埋め込み型WL107の電極部を形成する。

【0028】

次いで、その上部に、キャップ絶縁膜111(例えば、CVD酸化膜)を埋設し、平坦化する。

【0029】

その後、BL線103及び後述のビットコンタクト(Bit-Contact(BC))形成のためのビットコンタクト層間膜112を堆積する。

【0030】

次に、図2に示すように、ビットコンタクト(BC)113を開口する。

【0031】

最初に、ビットコンタクト層間膜112上にフォトリソグラフィーで、BCパターンをレジストを用いてパターニングする。

【0032】

次いで、ドライエッチングプロセスでビットコンタクト(BC)113を開口する。この際、ビットコンタクト(BC)113はWL107(フィールド部)に開口端がオーバーラップし、STI102及びNF104の表面に埋設している埋め込み絶縁膜106の表面が露出するように開口する。

【0033】

次に、図3に示すように、STI102及びNF104に中空構造(Air Gap)構造を形成する。

【0034】

最初に、上述のようにビットコンタクト(BC)113を開口した後、洗浄を行なう。

【0035】

その後、STI102及びNF104の内部に埋設された埋め込み絶縁膜106を除去するために、ホットリン酸114で埋め込み絶縁膜106を除去し、空洞部115を形成する。このようにして、Air-Gap分離構造が形成される。

【0036】

次に、Air-Gap分離構造形成後、図4に示すように、ビットコンタクト(BC)113に選択エピタキシャル成長を行い、エピタキシャル成長層116を形成して、ビットコンタクト(BC)113の底部を埋設する。この際、STI102及びNF104の表面のホットリン酸114で除去された埋め込み絶縁膜(SIN膜)106の開口部は選択エピタキシャル成長のオーバー成長で埋設される。

【0037】

次に、図5に示すように、ビットコンタクト(BC)113に形成したエピタキシャル成長層116に不純物をイオン注入し、熱処理を行なった後、 ビット線(BL)103を形成するためのメタル配線を行なう。ここでは、TiN/W膜を成膜し、BL103の配線パターニングを行う。

【0038】

このようにして、STI102及びNF104に中空構造の素子分離構造を有する半等体装置が完成する。

【0039】

この半導体装置は、図5に示すように、半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する。

【0040】

また、素子分離領域(STI102、NF104)は溝状に形成されており、素子分離領域(STI102、NF104)の内壁には、内壁酸化膜105が形成されている。

【0041】

そして、空洞部105の比誘電率(理想的には1.0)は、内壁酸化膜105の比誘電率(3.8〜4.2程度)よりも低い。

【0042】

このような構造の下、半導体素子は、対象セル(Unit Cell)のワード線107とビット線103に接続されたセルアレイトランジスタ101である。空洞部105は、ワード線(aWL)107aに隣接する隣接ワード線(N−aWL)107bの電位の影響に伴うビット線(aBL)103aへの電界を緩和する。さらに、空洞部105は、ワード線(aWL)107aの接合リーク電流を減少させる。

【0043】

(第2の実施の形態)

最初に、図6〜図11を参照して、本発明の第2の実施の形態に係る半導体装置の製造方法について説明する。ここで、図6〜図11において、(a)は平面図、(b)はワード線(Word-Line(WL))垂直断面図、(c)はビット線(Bit-Line(BL))垂直断面図をそれぞれ示す。

【0044】

最初に、図6に示すように、半導体基板200中に、素子分離となるシャロートレンチアイソレーション(STI)201を形成するためのパターニングを行うため、フォトレジストの塗布及び霧光を行う。この時、対象セル(Unit Cell)のビット線(aBL)202aに隣接する隣接ビット線(N−BL)202bとの分離部のSTI201と同時に、WL垂直方向の隣接ビット線(N−BL)202b間の分離部(ここではノーマルフィールド(NF)203と称する)の両方を同時にパターニングしても良いし、別々にラインパターンで形成しても良い。

【0045】

次いで、STI201及び NF203を形成するためのドライエッチングを行って、STI用トレンチ204及びNF用トレンチ205を形成する。この時に、STI用トレンチ204及びNF用トレンチ205の溝形状を間口がやや狭くなるボーイング形状で形成する。近年の微細化したデバイスでは、STI201やNF203の分離幅が100nm以下になってきている。ここでは50nmの例で示す。

【0046】

次に、図7に示すように、図6で示したボーイング形状のSTI用トレンチ204及びNF用トレンチ205(素子分離構造部)に対して高温のRTPプロセスにより内壁酸化を行なって、STI用トレンチ204及びNF用トレンチ205の内壁に内壁酸化膜206を形成する。内壁酸化膜206の厚さは、例えば、10nmである。これにより、STI用トレンチ204及びNF用トレンチ205の素子分離開口部は約45nm程度となる。

【0047】

次に、図8に示すように、STI用トレンチ204及びNF用トレンチ205の内壁に形成した内壁酸化膜206の表面に、絶縁膜207を堆積する。この絶縁膜207は、例えば、CVD酸化膜或いはプラズマ酸化膜であり、その膜厚は、約30nm程度である。この時、STI用トレンチ204及びNF用トレンチ205の素子分離開口部が狭いために、開口部が先に閉塞し、内部に空洞が残ったまま絶縁膜207の成膜が完了する。このようにして、空洞部208を有するSTI201及びNF203が完成する。尚、この絶縁膜207は、場合によってはCVD-SiN膜やプラズマSiN膜でも良い。

【0048】

次に、空洞部208を有するSTI201及びNF203が完成した後、図9に示すように、溝ゲート構造のセルアレイトランジスタ209を形成する。

【0049】

最初に、WL210のパターン形成するためマスク膜(図示せず)を成膜し、次いで、フォトリソグラフィーにてWL210のパターンを焼付けし、マスク膜をパターニングする。

【0050】

レジスト除去後、パターニングしたマスク膜を用いてセルフアラインプロセスでWL210のパターンを半導体層の内部に形成する。

【0051】

洗浄後、WL210のゲート絶縁膜210を形成する。ここでは、高温の高速昇温プロセス(Rapid Thermal Process(RTP))を用いてゲート酸化(例えば、6nm厚)を行なう。そのままポリシリコンのゲート電極を形成しても良いが、図9では埋め込み型WL210の形成方法で説明する。

【0052】

埋め込み型WL210の形成のため、TiN211及びW212を埋設し、所望の深さで埋め込み型WL210の電極部を形成する。

【0053】

次いで、その上部に、キャップ絶縁膜213(ここでは、CVD酸化膜)を埋設し、平坦化する。

【0054】

その後、BL線103及び後述のビットコンタクト(Bit-Contact(BC))形成のためのビットコンタクト層間SiN膜214及びビットコンタクト層間酸化膜215を堆積する。

【0055】

次に、図10に示すように、ビットコンタクト(BC)216を開口する。

【0056】

最初に、ビットコンタクト層間酸化膜215上にフォトリソグラフィーで、BCパターンをレジストを用いてパターニングする。

【0057】

次いで、ドライエッチングプロセスでビットコンタクト(BC)216を開口する。

【0058】

その後、ビットコンタクト(BC)216が半導体層からはみ出さないように、ビットコンタクト層間SiN膜214で一度エッチストップした後、ビットコンタクトSW膜(SiN膜サイドウォール)217を形成し、ビットコンタクト層間SiN膜214をエッチングし、ビットコンタクト(BC)216を開口する。

【0059】

次に、図11に示すように、ビットコンタクト(BC)216に不純物をイオン注入し、熱処理を行なった後、ビット線(BL)202形成のためのメタル配線を行なう。ここではTiN/W膜を成膜し、ビット線(BL)202の配線パターニングを行なう。この際、ビットコンタクト(BC)216との接続に不純物がドープされたポリシリコンを用いても良い。これにより、STI201及びNF203に中空構造の素子分離構造を有する半導体装置が完成する。

【0060】

この半導体装置は、図11に示すように、半導体基板200に形成され、半導体素子201を形成するための活性領域と、半導体基板200内に形成され、活性領域を分離するための素子分離領域(STI201、NF203)と、素子分離領域(STI201、NF203)内に設けられた空洞部208を有する。

【0061】

また、素子分離領域(STI201、NF203)は、間口が狭くなるボーイング形状に形成されており、素子分離領域(STI201、NF203)の内壁には、内壁酸化膜206が形成され、内壁酸化膜206の表面には絶縁膜207が形成されている。

【0062】

そして、空洞部208の比誘電率(理想的には1.0)は、内壁酸化膜206の比誘電率(3.8〜4.2程度)よりも低い。

【0063】

このような構造に下、半導体素子は、対象セル(Unit Cell)のワード線210とビット線202に接続されたセルアレイトランジスタ209である。空洞部208は、ワード線(aWL)210aに隣接する隣接ワード線(N−aWL)210bの電位の影響に伴うビット線(aBL)202aへの電界を緩和する。さらに、空洞部208は、ワード線(aWL)210aの接合リーク電流を減少させる。

【0064】

次に、図12を参照して、本発明の実施の形態による効果について説明する。ここで、(a)はセルアレイトランジスタ特性のオン電流特性を示し、(b)はセルアレイトランジスタ特性の接合リーク電流を示す。

【0065】

図12(a)に示すように、本発明を用いることにより、デバイスの微細化に伴うセルアレイトランジスタのオン電流の隣接WLの影響による低下を抑制できる。また、隣接ワード電(WL)の電位の影響に伴う対象ビット線(BL)の電界緩和が可能となる。

【0066】

さらに、図12(b)に示すように、本発明を用いることにより、接合リーク電流も改善できる。

【0067】

以上、本発明者によってなされた発明を実施例に基づき説明したが、本発明は上記実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【符号の説明】

【0068】

100 半導体基板

101 セルアレイトランジスタ

102 STI

103 ビット線(BL)

104 NF

105 内壁酸化膜

106 埋め込み絶縁膜

107 ワード線(WL)

108 ゲート絶縁膜

109 TiN

110 W

111 キャップ絶縁膜

112 ビットコンタクト層間膜

113 ビットコンタクト(BC)

114 ホットリン酸

115 空洞部

116 エピタキシャル成長層

200 半導体基板

201 STI

202 ビット線(BL)

203 NF

204 STI用トレンチ

205 NF用トレンチ

206 内壁酸化膜

207 絶縁膜

208 空洞部

209 セルアレイトランジスタ

210 ワード線(WL)

211 TiN

212 W

213 キャップ絶縁膜

214 ビットコンタクト層間SiN膜

215 ビットコンタクト層間酸化膜215

216 ビットコンタクト(BC)

217 ビットコンタクトSW膜

【特許請求の範囲】

【請求項1】

半導体基板に形成され、半導体素子を形成するための活性領域と、

前記半導体基板内に形成され、前記活性領域を分離するための素子分離領域と、

前記素子分離領域内に設けられた空洞部を有することを特徴とする半導体装置。

【請求項2】

前記素子分離領域は溝状に形成されており、

前記素子分離領域の内壁には、内壁酸化膜が形成されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記素子分離領域は、間口が狭くなるボーイング形状に形成されており、

前記素子分離領域の内壁には、内壁酸化膜が形成され、

前記内壁酸化膜の表面には絶縁膜が形成されていることを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記空洞部の比誘電率は、前記内壁酸化膜の比誘電率よりも低いことを特徴とする請求項2又は3に記載の半導体装置。

【請求項5】

前記半導体素子は、ワード線とビット線に接続されたセルアレイトランジスタであり、

前記空洞部は、当該ワード線に隣接するワード線の電位の影響に伴う当該ビット線への電界を緩和することを特徴とする請求項1から4のいずれか1項に記載の半導体装置。

【請求項6】

前記半導体素子は、ワード線とビット線に接続されたセルアレイトランジスタであり、

前記空洞部は、当該ワード線の接合リーク電流を減少させることを特徴とする請求項1から4のいずれか1項に記載の半導体装置。

【請求項7】

半導体基板に、半導体素子を形成するための活性領域を形成し、

前記半導体基板内に、前記活性領域を分離するための素子分離領域を形成し、

前記素子分離領域内に空洞部を形成することを特徴とする半導体装置の製造方法。

【請求項8】

前記素子分離領域を溝状に形成し、

前記素子分離領域の内壁に、内壁酸化膜を形成することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記素子分離領域を間口が狭くなるボーイング形状に形成し、

前記素子分離領域の内壁に、内壁酸化膜を形成し、

前記内壁酸化膜の表面に、絶縁膜を形成することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項10】

前記内壁酸化膜の表面に前記絶縁膜を形成することにより、前記素子分離領域の間口が閉塞され、これにより、前記素子分離領域内に前記空洞部が形成されることを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

前記絶縁膜は、CVD酸化膜又はプラズマ酸化膜であることを特徴とする請求項9又は10に記載の半導体装置の製造方法。

【請求項12】

前記空洞部の比誘電率は、前記内壁酸化膜の比誘電率よりも低いことを特徴とする請求項7から11のいずれか1項に記載の半導体装置の製造方法。

【請求項13】

前記半導体素子は、ワード線とビット線に接続されたセルアレイトランジスタであり、

前記空洞部は、当該ワード線に隣接するワード線の電位の影響に伴う当該ビット線への電界を緩和するために形成されることを特徴とする請求項7から12のいずれか1項に記載の半導体装置の製造方法。

【請求項14】

前記半導体素子は、ワード線とビット線に接続されたセルアレイトランジスタであり、

前記空洞部は、当該ワード線の接合リーク電流を減少させるために形成されることを特徴とする請求項7から12のいずれか1項に記載の半導体装置の製造方法。

【請求項15】

前記素子分離領域の内壁に前記内壁酸化膜を形成した後、前記素子分離領域内を埋め込み絶縁膜で埋設して平坦化し、

前記半導体基板の表面に、前記ビット線を形成するためのビットコンタクト層間膜を形成し、

前記埋め込み絶縁膜の一部が前記素子分離領域の表面から露出するように、前記ビットコンタクト層間膜を開口し、

前記露出した素子分離領域の表面を介して、前記素子分離領域に埋設されている前記埋め込み絶縁膜を除去することにより前記空洞部を形成することを特徴とする請求項13又は14に記載の半導体装置の製造方法。

【請求項16】

前記埋め込み絶縁膜を除去は、ホットリン酸により行われることを特徴とする請求項15に記載の半導体装置の製造方法。

【請求項1】

半導体基板に形成され、半導体素子を形成するための活性領域と、

前記半導体基板内に形成され、前記活性領域を分離するための素子分離領域と、

前記素子分離領域内に設けられた空洞部を有することを特徴とする半導体装置。

【請求項2】

前記素子分離領域は溝状に形成されており、

前記素子分離領域の内壁には、内壁酸化膜が形成されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記素子分離領域は、間口が狭くなるボーイング形状に形成されており、

前記素子分離領域の内壁には、内壁酸化膜が形成され、

前記内壁酸化膜の表面には絶縁膜が形成されていることを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記空洞部の比誘電率は、前記内壁酸化膜の比誘電率よりも低いことを特徴とする請求項2又は3に記載の半導体装置。

【請求項5】

前記半導体素子は、ワード線とビット線に接続されたセルアレイトランジスタであり、

前記空洞部は、当該ワード線に隣接するワード線の電位の影響に伴う当該ビット線への電界を緩和することを特徴とする請求項1から4のいずれか1項に記載の半導体装置。

【請求項6】

前記半導体素子は、ワード線とビット線に接続されたセルアレイトランジスタであり、

前記空洞部は、当該ワード線の接合リーク電流を減少させることを特徴とする請求項1から4のいずれか1項に記載の半導体装置。

【請求項7】

半導体基板に、半導体素子を形成するための活性領域を形成し、

前記半導体基板内に、前記活性領域を分離するための素子分離領域を形成し、

前記素子分離領域内に空洞部を形成することを特徴とする半導体装置の製造方法。

【請求項8】

前記素子分離領域を溝状に形成し、

前記素子分離領域の内壁に、内壁酸化膜を形成することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記素子分離領域を間口が狭くなるボーイング形状に形成し、

前記素子分離領域の内壁に、内壁酸化膜を形成し、

前記内壁酸化膜の表面に、絶縁膜を形成することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項10】

前記内壁酸化膜の表面に前記絶縁膜を形成することにより、前記素子分離領域の間口が閉塞され、これにより、前記素子分離領域内に前記空洞部が形成されることを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

前記絶縁膜は、CVD酸化膜又はプラズマ酸化膜であることを特徴とする請求項9又は10に記載の半導体装置の製造方法。

【請求項12】

前記空洞部の比誘電率は、前記内壁酸化膜の比誘電率よりも低いことを特徴とする請求項7から11のいずれか1項に記載の半導体装置の製造方法。

【請求項13】

前記半導体素子は、ワード線とビット線に接続されたセルアレイトランジスタであり、

前記空洞部は、当該ワード線に隣接するワード線の電位の影響に伴う当該ビット線への電界を緩和するために形成されることを特徴とする請求項7から12のいずれか1項に記載の半導体装置の製造方法。

【請求項14】

前記半導体素子は、ワード線とビット線に接続されたセルアレイトランジスタであり、

前記空洞部は、当該ワード線の接合リーク電流を減少させるために形成されることを特徴とする請求項7から12のいずれか1項に記載の半導体装置の製造方法。

【請求項15】

前記素子分離領域の内壁に前記内壁酸化膜を形成した後、前記素子分離領域内を埋め込み絶縁膜で埋設して平坦化し、

前記半導体基板の表面に、前記ビット線を形成するためのビットコンタクト層間膜を形成し、

前記埋め込み絶縁膜の一部が前記素子分離領域の表面から露出するように、前記ビットコンタクト層間膜を開口し、

前記露出した素子分離領域の表面を介して、前記素子分離領域に埋設されている前記埋め込み絶縁膜を除去することにより前記空洞部を形成することを特徴とする請求項13又は14に記載の半導体装置の製造方法。

【請求項16】

前記埋め込み絶縁膜を除去は、ホットリン酸により行われることを特徴とする請求項15に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−26431(P2013−26431A)

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願番号】特願2011−159588(P2011−159588)

【出願日】平成23年7月21日(2011.7.21)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願日】平成23年7月21日(2011.7.21)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]