半導体装置及びその製造方法

【課題】ゲートラストプロセスの工程数を削減しつつ、所望の信頼性及び特性が得られるメタルゲート電極を備えたMISFETを実現できるようにする。

【解決手段】各ゲート溝の少なくとも底面上にゲート絶縁膜112及び保護膜113が順次形成されている。一方のゲート溝内の保護膜113の上には第1の金属含有膜114a及び第2の金属含有膜114bが順次形成されており、他方のゲート溝内の保護膜113の上には第2の金属含有膜114bが形成されている。一方のゲート溝内の保護膜113の厚さと比べて、他方のゲート溝内の保護膜113の厚さは薄い。

【解決手段】各ゲート溝の少なくとも底面上にゲート絶縁膜112及び保護膜113が順次形成されている。一方のゲート溝内の保護膜113の上には第1の金属含有膜114a及び第2の金属含有膜114bが順次形成されており、他方のゲート溝内の保護膜113の上には第2の金属含有膜114bが形成されている。一方のゲート溝内の保護膜113の厚さと比べて、他方のゲート溝内の保護膜113の厚さは薄い。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、メタルゲート電極を備えた相補型MISFET(Metal Insulator Semiconductor Field Effect Transistor)及びその形成方法に関する。

【背景技術】

【0002】

トランジスタの動作の高速化及び低消費電力化は、スケーリング則に基づき、トランジスタの微細化により実現されてきている。一般に、トランジスタにおけるゲート絶縁膜とゲート電極との積層構造(ゲートスタック)の材料として、酸化シリコン(SiO2 )又は酸窒化シリコン(SiON)/ポリシリコンが用いられてきたが、ゲートリーク電流の増大により、このような材料からなるゲート絶縁膜を薄膜化することは困難になってきている。そこで、高誘電率(High-k)ゲート絶縁膜とメタルゲート電極とを組み合わせたHigh-k/メタルゲート技術が注目されている。尚、High-k絶縁膜とは、SiNよりも高い誘電率(例えば比誘電率8以上)を持つ絶縁膜を意味する。また、メタルゲート電極とは、金属又は導電性金属化合物からなる電極部分を有するゲート電極を意味する。

【0003】

High-k/メタルゲート構造の形成方法としては、当初、従来のSiO2 /ポリシリコンゲート構造の形成方法と同様に、最初にHigh-kゲート絶縁膜及びメタルゲート電極を形成した後、不純物層及びシリサイド層等を形成する方法、いわゆるゲートファーストプロセスによる形成方法が検討された。しかしながら、相補型MISFETに用いられるメタルゲート(デュアルメタルゲート)においては、NMISFETとPMISFETとの間で異なるメタル材料を用いた場合にゲートエッチング形状の制御が難しいこと、及び、後工程での不純物注入層に対するスパイクアニール等の熱負荷に起因して閾値電圧や駆動電流等が劣化すること等のインテグレーション上の問題があることが明らかになってきた。

【0004】

そこで、最初にダミーゲート電極を形成した後、ダミーゲート電極をマスクとして、不純物層及びシリサイド層の形成を行い、その後、ダミーゲート電極を除去した後、メタルゲート電極を形成する方法(以下、ゲートラストプロセスと呼ぶ)が主流になりつつある(例えば特許文献1参照)。ゲートラストプロセスによると、ゲートファーストプロセスよりも工程数が増加するという欠点はあるものの、デュアルメタルゲートのインテグレーションを実現して、極めて良好なデバイス特性を得ることができる。特に、ゲートラストプロセスの場合、実効仕事関数の値を制御するための金属材料を成膜した後は、比較的低温のプロセスでデバイスを形成することができる。このため、スパイクアニール等に起因するメタルゲート電極特性の変質の影響を受けることなく、スタックゲートの実効的な仕事関数の値をバンド端の近傍に制御することが可能となる。また、ダミーゲート自体は、NMISFET及びPMISFETとも同一の材料で形成されるため、ゲートエッチング工程における形状の制御もゲートファーストプロセスと比較して容易になる。尚、「実効仕事関数」とは、MISFETの電気特性から求められる仕事関数であって、真空準位と金属のエネルギー準位との差を示す物性的な仕事関数に絶縁膜中の準位などの影響を加味したものを意味する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許出願公開第2010/0052070号明細書

【特許文献2】米国特許出願公開第2009/0039433号明細書

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献1に開示されている従来のゲートラストプロセスには、以下のような問題がある。すなわち、従来のゲートラストプロセスでは、ダミーゲート電極の除去後に、NMISFET及びPMISFETのそれぞれに応じた仕事関数調整用メタル材料を個別に成膜する必要がある。そのため、仕事関数調整用メタル材料の成膜、導電性埋め込み材料(ダミーゲート電極の除去により形成されたゲート溝を埋め込むための導電性材料)の成膜、及び層間膜上の(つまりゲート溝の外側の)前記各材料の除去をNMISFET及びPMISFETのそれぞれに対して個別に行う必要がある。従って、従来のゲートラストプロセスにおいては、工程数の増加、それに伴うコストの増大、加工工程が増加することに起因するプロセスばらつきの増大、及び、それに伴う歩留まりの低下等のリスクの増大等の問題が生じる。

【0007】

それに対して、特許文献2には、NMISFET及びPMISFETのそれぞれにおいてダミーゲート電極を同時に除去した後、例えばNMISFETの仕事関数調整用メタル材料を成膜し、その後、当該メタル材料をPMISFET上で除去した後、PMISFETの仕事関数調整用メタル材料を成膜するという方法が開示されている。特許文献2に開示されているゲートラストプロセスによると、ダミーゲートの加工工程及び除去工程、並びにCMP(Chemical Mechanical Polishing )による仕事関数調整用メタル材料の除去工程のそれぞれの実施回数を1回にできるため、工程数の削減が可能となる。

【0008】

しかしながら、特許文献2に開示されているゲートラストプロセスにおいては、High-kゲート絶縁膜の直上で仕事関数調整用メタル材料の除去を行う必要があるため、ドライエッチング法又はウェットエッチング法を用いてエッチングを行う際に、High-kゲート絶縁膜にエッチャントが浸入してダメージが生じる。その結果、閾値電圧制御の不良、デバイス信頼性やトランジスタ特性等の劣化が引き起こされる懸念がある。また、High-kゲート絶縁膜上に形成されたメタル膜は、例えばCVD(Chemical Vapor Deposition )法又はALD(Atomic Layer Deposition )法等による成膜のように、プラズマによる打ち込みがない環境で成膜されたとしても、High-kゲート絶縁膜と部分的に反応し、それにより、当該絶縁膜中にメタル材料が拡散して絶縁膜深さ方向に分布してしまう。その結果、後工程でのメタル材料除去時の除去性が劣化して、次のような問題が生じる。例えば、ダミーゲート電極の除去後に、NMISFETの仕事関数調整用メタル材料を成膜し、その後、当該メタル材料をPMISFET上で除去する場合、PMISFET上にNMISFETの仕事関数調整用メタル材料が残留してしまい、PMISFETに必要な仕事関数が得られなくなる。

【0009】

前記に鑑み、本発明は、ゲートラストプロセスの工程数を削減しつつ、所望の信頼性及び特性が得られるメタルゲート電極を備えたMISFETを実現できるようにすることを目的とする。

【課題を解決するための手段】

【0010】

前記の目的を達成するために、本発明に係る半導体装置は、半導体基板における第1の領域及び第2の領域のそれぞれの上に形成された第1のゲート溝及び第2のゲート溝と、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの少なくとも底面上に形成されたゲート絶縁膜と、前記第1のゲート溝内の前記ゲート絶縁膜の上及び前記第2のゲート溝内の前記ゲート絶縁膜の上にそれぞれ形成された保護膜と、前記第1のゲート溝の底面及び側壁面を覆うように、前記第1のゲート溝内の前記保護膜の上に形成された第1の金属含有膜と、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように、前記第1のゲート溝内の前記第1の金属含有膜の上及び前記第2のゲート溝内の前記保護膜の上に形成された第2の金属含有膜と、前記第1のゲート溝及び前記第2のゲート溝のそれぞれにおける前記第2の金属含有膜により形成される凹部が埋まるように、前記第1のゲート溝内の前記第2の金属含有膜の上及び前記第2のゲート溝内の前記第2の金属含有膜の上に形成された第3の金属含有膜とを備え、前記第1のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さと比べて、前記第2のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さは薄いことを特徴とする半導体装置。

【0011】

本発明に係る半導体装置において、前記第1のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さと、前記第2のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さとの差は、1nm以上で且つ3nm以下であってもよい。

【0012】

本発明に係る半導体装置において、前記半導体基板の上部における前記第1の領域と前記第2の領域との間に素子分離領域が形成されており、前記第1のゲート溝と前記第2のゲート溝とは前記素子分離領域上で接続しており、前記素子分離領域上に位置する部分の前記保護膜には段差が形成されていてもよい。

【0013】

本発明に係る半導体装置において、前記保護膜は、窒化チタン、窒化ハフニウム又は窒化タンタルから構成されていてもよい。

【0014】

本発明に係る半導体装置において、前記第1のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さは、2nm以上で且つ5nm以下であってもよい。

【0015】

本発明に係る半導体装置において、前記ゲート絶縁膜及び前記保護膜は、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように形成されていてもよい。

【0016】

本発明に係る半導体装置において、前記ゲート絶縁膜及び前記保護膜は、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの側壁面上には形成されていなくてもよい。

【0017】

本発明に係る半導体装置において、前記半導体基板における前記第1のゲート溝の両側方には第1導電型の第1のソース/ドレイン領域が形成されており、前記半導体基板における前記第2のゲート溝の両側方には第2導電型の第2のソース/ドレイン領域が形成されていてもよい。ここで、前記第1導電型がn型であり、前記第2導電型がp型である場合、前記第1の金属含有膜は、チタン、アルミニウム、チタンとアルミニウムとの合金、窒化ハフニウム又は炭化タンタルを含んでいてもよい。また、前記第1の金属含有膜の厚さは、1nm以上で且つ5nm以下であってもよい。また、前記第2の金属含有膜は、窒化チタン、酸化ルテニウム又は白金を含んでいてもよい。ここで、前記第2の金属含有膜は、白金以外の貴金属を含んでいてもよい。また、前記第2の金属含有膜の厚さは、4nm以上であってもよい。さらに、前記第2のソース/ドレイン領域は、シリコンゲルマニウム層を有していてもよい。

【0018】

尚、前記第3の金属含有膜(つまり導電性埋め込み材料)は、例えば、タングステン、アルミニウム又は窒化チタン等を含んでいてもよい。

【0019】

本発明に係る半導体装置において、前記ゲート絶縁膜は、高誘電率絶縁膜を含んでいてもよい。ここで、前記高誘電率絶縁膜は、少なくともハフニウム又はジルコニウムを含む絶縁膜であってもよい。

【0020】

本発明に係る半導体装置の製造方法は、半導体基板における第1の領域及び第2の領域のそれぞれの上に第1のゲート溝及び第2のゲート溝を形成する工程(a)と、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの少なくとも底面上にゲート絶縁膜を形成する工程(b)と、前記第1のゲート溝内の前記ゲート絶縁膜の上及び前記第2のゲート溝内の前記ゲート絶縁膜の上にそれぞれ保護膜を形成する工程(c)と、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように、前記第1のゲート溝内の前記保護膜の上及び前記第2のゲート溝内の前記保護膜の上に第1の金属含有膜を形成する工程(d)と、前記第2のゲート溝内の前記第1の金属含有膜、及び前記第2のゲート溝内の前記保護膜の上部を選択的に除去する工程(e)と、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように、前記第1のゲート溝内の前記第1の金属含有膜の上及び前記第2のゲート溝内の前記保護膜の上に第2の金属含有膜を形成する工程(f)と、前記第1のゲート溝及び前記第2のゲート溝のそれぞれにおける前記第2の金属含有膜により形成される凹部が埋まるように、前記第1のゲート溝内の前記第2の金属含有膜の上及び前記第2のゲート溝内の前記第2の金属含有膜の上に第3の金属含有膜を形成する工程(g)とを備えている。

【0021】

本発明に係る半導体装置の製造方法において、前記工程(a)は、前記半導体基板における前記第1の領域及び前記第2の領域のそれぞれの上に第1のダミーゲート電極及び第2のダミーゲート電極を形成する工程(a1)と、前記第1のダミーゲート電極及び前記第2のダミーゲート電極を覆うように、前記半導体基板における前記第1の領域及び前記第2の領域のそれぞれの上に層間絶縁膜を形成し、その後、前記第1のダミーゲート電極及び前記第2のダミーゲート電極のそれぞれの頂部が露出するように、前記層間絶縁膜を薄くする工程(a2)と、前記第1のダミーゲート電極及び前記第2のダミーゲート電極を除去して、前記第1のゲート溝及び前記第2のゲート溝を形成する工程(a3)とを含んでいてもよい。ここで、前記ゲート絶縁膜及び前記保護膜は、前記工程(a)の後に、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように形成されてもよい。或いは、前記ゲート絶縁膜及び前記保護膜は、前記工程(a)の前に、前記第1のゲート溝の底面となる部分の前記半導体基板の上及び前記第2のゲート溝の底面となる部分の前記半導体基板の上にそれぞれ形成され、前記工程(a1)では、前記第1の領域及び前記第2の領域のそれぞれの上に、前記ゲート絶縁膜及び前記保護膜を介して、前記第1のダミーゲート電極及び前記第2のダミーゲート電極が形成されてもよい。

【発明の効果】

【0022】

本発明によると、各トランジスタ領域上におけるゲート溝の形成に際し、ダミーゲート電極の除去を同時に行うことによって、言い換えると、ダミーゲート電極の除去工程を1回だけ実施することによって、ゲートラストプロセスの工程数を削減することができ、それにより、製造コスト及び歩留まり等を改善することができる。

【0023】

また、本発明によると、ゲート絶縁膜と各トランジスタの仕事関数調整用メタル材料(つまり第1の金属含有膜及び第2の金属含有膜)との間に保護膜が形成されているため、保護膜を仕事関数調整用メタル材料の拡散緩衝層として、ゲート絶縁膜と各トランジスタの仕事関数調整用メタル材料とを分離し、それにより、両者の間の相互拡散を制御することができる。また、第2のゲート溝内の仕事関数調整用メタル材料(つまり第1の金属含有膜)を選択的に除去する際に、ゲート絶縁膜がエッチャントに直接さらされてダメージが生じる事態を阻止することが可能となる。従って、前述の相互拡散やダメージに起因する閾値電圧制御の不良、デバイス信頼性やトランジスタ特性等の劣化を防止することができる。

【0024】

さらに、本発明によると、ゲート絶縁膜と各トランジスタの仕事関数調整用メタル材料との間に保護膜を挿入することによって、ゲート絶縁膜中への仕事関数調整用メタル材料の拡散を制御することが可能となるだけではなく、第2のゲート溝内の仕事関数調整用メタル材料(つまり第1の金属含有膜)を選択的に除去する際に、保護膜上部を同時に除去することによって、次のような効果も得ることができる。すなわち、保護膜上部に拡散した又は打ち込まれた仕事関数調整用メタル材料を除去することができるので、メタル材料の残留に起因する仕事関数の劣化及び閾値電圧の劣化を防止することが可能となる。

【図面の簡単な説明】

【0025】

【図1】図1は、第1の実施形態に係る半導体装置の平面図である。

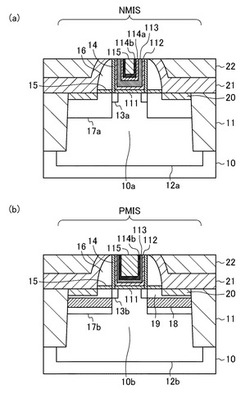

【図2】図2(a)及び(b)はそれぞれ、図1に示すAーA’線及びB−B’線における断面図である。

【図3】図3(a)及び(b)はそれぞれ、図1に示すC−C’線及びD−D’線における断面図である。

【図4】図4(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図4(a)は、図1に示すC−C’線における断面図であり、図4(b)は、図1に示すD−D’線における断面図である。

【図5】図5(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図5(a)は、図1に示すC−C’線における断面図であり、図5(b)は、図1に示すD−D’線における断面図である。

【図6】図6(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図6(a)は、図1に示すC−C’線における断面図であり、図6(b)は、図1に示すD−D’線における断面図である。

【図7】図7(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図7(a)は、図1に示すC−C’線における断面図であり、図7(b)は、図1に示すD−D’線における断面図である。

【図8】図8(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図8(a)は、図1に示すC−C’線における断面図であり、図8(b)は、図1に示すD−D’線における断面図である。

【図9】図9(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図9(a)は、図1に示すC−C’線における断面図であり、図9(b)は、図1に示すD−D’線における断面図である。

【図10】図10(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図10(a)は、図1に示すC−C’線における断面図であり、図10(b)は、図1に示すD−D’線における断面図である。

【図11】図11(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図11(a)は、図1に示すC−C’線における断面図であり、図11(b)は、図1に示すD−D’線における断面図である。

【図12】図12(a)及び(b)は、第1の実施形態に係る半導体装置の各工程を示す断面図(図1に示すA−A’線における断面図)である。

【図13】図13(a)及び(b)は、第1の実施形態に係る半導体装置の各工程を示す断面図(図1に示すA−A’線における断面図)である。

【図14】図14は、第2の実施形態に係る半導体装置の平面図である。

【図15】図15(a)及び(b)はそれぞれ、図14に示すAーA’線及びB−B’線における断面図である。

【図16】図16(a)及び(b)はそれぞれ、図14に示すC−C’線及びD−D’線における断面図である。

【図17】図17(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図17(a)は、図14に示すC−C’線における断面図であり、図17(b)は、図14に示すD−D’線における断面図である。

【図18】図18(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図18(a)は、図14に示すC−C’線における断面図であり、図18(b)は、図14に示すD−D’線における断面図である。

【図19】図19(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図19(a)は、図14に示すC−C’線における断面図であり、図19(b)は、図14に示すD−D’線における断面図である。

【図20】図20(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図20(a)は、図14に示すC−C’線における断面図であり、図20(b)は、図14に示すD−D’線における断面図である。

【図21】図21(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図21(a)は、図14に示すC−C’線における断面図であり、図21(b)は、図14に示すD−D’線における断面図である。

【図22】図22(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図22(a)は、図14に示すC−C’線における断面図であり、図22(b)は、図14に示すD−D’線における断面図である。

【図23】図23(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図23(a)は、図14に示すC−C’線における断面図であり、図23(b)は、図14に示すD−D’線における断面図である。

【図24】図24(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図24(a)は、図14に示すC−C’線における断面図であり、図24(b)は、図14に示すD−D’線における断面図である。

【図25】図25(a)及び(b)は、第2の実施形態に係る半導体装置の各工程を示す断面図(図14に示すA−A’線における断面図)である。

【図26】図26(a)及び(b)は、第2の実施形態に係る半導体装置の各工程を示す断面図(図14に示すA−A’線における断面図)である。

【発明を実施するための形態】

【0026】

以下、本発明の実施形態を図面に基づいて詳細に説明する。尚、本発明は、以下に示す実施形態に限定されない。例えば、構成材料は以下に示す材料に限定されず、膜厚及び濃度などもそれぞれ以下に示す数値に限定されず、成膜方法及びエッチング方法なども以下に示す方法に限定されない。また、各図面においては、同一の部材に対して同一の符号を付け、説明を省略する場合がある。

【0027】

(第1の実施形態)

まず、第1の実施形態に係る半導体装置の構造について、図1、図2(a)、(b)及び図3(a)、(b)を参照しながら説明する。図1は、本実施形態に係る半導体装置の平面図である。図2(a)、(b)及び図3(a)、(b)は、それぞれ、図1に示すAーA’線、B−B’線、C−C’線及びD−D’線における断面図である。尚、図1、図2(a)、(b)及び図3(a)、(b)において、「NMIS」とは、N型MISトランジスタ(NMISFET)が形成されるN型MISトランジスタ形成領域を示し、「PMIS」とは、P型MISトランジスタ(PMISFET)が形成されるP型MISトランジスタ形成領域を示している。また、図1では、シリサイド層20、応力絶縁膜21及び層間絶縁膜22の図示を省略している。

【0028】

図1及び図2(a)、(b)及び図3(a)、(b)に示すように、例えばシリコンからなる半導体基板10の上部(半導体領域)に、N型MISトランジスタ形成領域とP型MISトランジスタ形成領域とを区画するように素子分離領域11が形成されている。N型MISトランジスタ形成領域の半導体基板10の上部にはp型ウェル領域12aが形成されていると共に、P型MISトランジスタ形成領域の半導体基板10の上部にはn型ウェル領域12bが形成されている。ここで、p型ウェル領域12aのうち素子分離領域11に囲まれている部分が活性領域10aとなり、n型ウェル領域12bのうち素子分離領域11に囲まれている部分が活性領域10bとなる。図1及び図2(a)に示すように、活性領域10aと活性領域10bとは素子分離領域11を挟んでチャネル幅方向(ゲート幅方向)に並んで配置されている。本実施形態に係る半導体装置では、活性領域10a上にN型MISトランジスタが形成されており、活性領域10b上にP型MISトランジスタが形成されている。

【0029】

N型MISトランジスタの構成は、以下に示す通りである。図3(a)に示すように、活性領域10a上に、絶縁膜111を底部とし且つ内側サイドウォールスペーサ14を側壁部とするゲート溝が設けられており、内側サイドウォールスペーサ14における当該ゲート溝の反対側には外側サイドウォールスペーサ16が設けられている。ここで、外側サイドウォールスペーサ16と活性領域10aとの間には下敷き絶縁膜15が設けられている。前記ゲート溝の底面(つまり絶縁膜111)及び側壁面(つまり内側サイドウォールスペーサ14)を覆うように高誘電率絶縁膜112が設けられている。また、前記ゲート溝内における高誘電率絶縁膜112により形成される凹部の底面及び側壁面を覆うように保護膜113が形成されており、前記ゲート溝内における保護膜113により形成される凹部の底面及び側壁面を覆うように、N型MISトランジスタの仕事関数調整用メタル電極膜(以下、Nchメタル電極膜)114aが形成されている。さらに、前記ゲート溝内におけるNchメタル電極膜114aにより形成される凹部の底面及び側壁面を覆うように、P型MISトランジスタの仕事関数調整用メタル電極膜(以下、Pchメタル電極膜)114bが形成されており、前記ゲート溝内におけるPchメタル電極膜114bにより形成される凹部を埋め込むように、導電性埋め込み膜115が埋め込まれている。

【0030】

すなわち、本実施形態に係る半導体装置のN型MISトランジスタでは、活性領域10a上のゲート溝内に、絶縁膜111及び高誘電率絶縁膜112からなるゲート絶縁膜を挟んで、保護膜113、Nchメタル電極膜114a、Pchメタル電極膜114b及び導電性埋め込み膜115からなるゲート電極が形成されている。

【0031】

また、活性領域10aにおける前記ゲート電極の両側方下には、n型エクステンション領域13aが形成されており、活性領域10aにおける前記ゲート電極から見て内側サイドウォールスペーサ14の両側方下には、n型ソース/ドレイン領域17aが形成されている。ここで、n型ソース/ドレイン領域17aの方がn型エクステンション領域13aよりも接合深さが深い。また、下敷き絶縁膜15の外側のn型ソース/ドレイン領域17aの上面上にはシリサイド層20が設けられている。

【0032】

尚、絶縁膜111は、例えば厚さ0.8nm程度のシリコン酸化膜からなり、高誘電率絶縁膜112は、例えば厚さ2nm〜4nm程度のHfO2 膜からなる。また、保護膜113は、金属、金属酸化物又は金属窒化物からなり、例えば2nm〜5nm程度の厚さを有する。また、内側サイドウォールスペーサ14は、例えばシリコン窒化膜からなり、外側サイドウォールスペーサ16も、例えばシリコン窒化膜からなり、下敷き絶縁膜15は、例えばシリコン酸化膜からなる。n型エクステンション領域13a及びn型ソース/ドレイン領域17aのそれぞれには、例えばヒ素等のn型不純物が注入されている。シリサイド層20は、例えばCoSi、NiSi又はNiPtSiからなり、例えば5nm〜20nm程度の厚さを有する。

【0033】

P型MISトランジスタの構成は、以下に示す通りである。図3(b)に示すように、活性領域10b上に、絶縁膜111を底部とし且つ内側サイドウォールスペーサ14を側壁部とするゲート溝が設けられており、内側サイドウォールスペーサ14における当該ゲート溝の反対側には外側サイドウォールスペーサ16が設けられている。ここで、外側サイドウォールスペーサ16と活性領域10aとの間には下敷き絶縁膜15が設けられている。前記ゲート溝の底面(つまり絶縁膜111)及び側壁面(つまり内側サイドウォールスペーサ14)を覆うように高誘電率絶縁膜112が設けられている。また、前記ゲート溝内における高誘電率絶縁膜112により形成される凹部の底面及び側壁面を覆うように保護膜113が形成されており、前記ゲート溝内における保護膜113により形成される凹部の底面及び側壁面を覆うように、Pchメタル電極膜114bが形成されている。さらに、前記ゲート溝内におけるPchメタル電極膜114bにより形成される凹部を埋め込むように、導電性埋め込み膜115が埋め込まれている。

【0034】

すなわち、本実施形態に係る半導体装置のP型MISトランジスタでは、活性領域10b上のゲート溝内に、絶縁膜111及び高誘電率絶縁膜112からなるゲート絶縁膜を挟んで、保護膜113、Pchメタル電極膜114b及び導電性埋め込み膜115からなるゲート電極が形成されている。ここで、P型MISトランジスタのゲート電極に含まれる保護膜113は、N型MISトランジスタのゲート電極に含まれる保護膜113よりも例えば1nm〜3nm程度薄くなっている。

【0035】

また、活性領域10bにおける前記ゲート電極の両側方下には、p型エクステンション領域13bが形成されており、活性領域10bにおける前記ゲート電極から見て内側サイドウォールスペーサ14の両側方下には、p型ソース/ドレイン領域17bが形成されている。ここで、p型ソース/ドレイン領域17bの方がp型エクステンション領域13bよりも接合深さが深い。また、p型エクステンション領域13b及びp型ソース/ドレイン領域17bのそれぞれには、例えばボロン等のp型不純物が注入されている。さらに、p型ソース/ドレイン領域17bの上にはシリコンゲルマニウム層18が形成されている。シリコンゲルマニウム層18は、シリコンよりも大きい格子定数を有するシリコン混晶(例えばSiGe)からなり、圧縮応力(第1の応力)をゲート長方向及びゲート幅方向に生じさせる。また、このシリコンゲルマニウム層18は、例えば60nm程度の厚さを有しており、原子比でシリコンに対して例えば20%〜30%程度のGeを含有している。このシリコンゲルマニウム層18にも、ボロン等のp型不純物が注入されている。すなわち、シリコンゲルマニウム層18におけるp型不純物の濃度は、p型ソース/ドレイン領域17bにおけるp型不純物の濃度と同一であることが好ましい。このように、p型ソース/ドレイン領域17b内にシリコンゲルマニウム層18が形成されているので、P型MISトランジスタのチャネル領域におけるゲート長方向に圧縮応力が印加される。その結果、P型MISトランジスタにおけるキャリア移動度(正孔の移動度)の向上を図ることができる。さらに、シリコンゲルマニウム層18の上にはシリコンエピタキシャル層19が形成されており、下敷き絶縁膜15の外側のシリコンエピタキシャル層19の上面上にはシリサイド層20が設けられている。これにより、シリサイド拡散不良やゲルマニウム汚染等の影響が後工程に出ないように配慮されている。従って、本実施形態では、PMISトランジスタの電流駆動能力を向上させることができる。

【0036】

尚、シリコンゲルマニウム層18は、p型ソース/ドレイン領域17b上のみに形成されており、n型ソース/ドレイン領域17a上には形成されていない。

【0037】

また、P型MISトランジスタ形成領域に設けられている絶縁膜111、高誘電率絶縁膜112、保護膜113、Pchメタル電極膜114b、導電性埋め込み膜115、内側サイドウォールスペーサ14、外側サイドウォールスペーサ16、下敷き絶縁膜15及びシリサイド層20のそれぞれの材料は、N型MISトランジスタ形成領域に設けられている絶縁膜111、高誘電率絶縁膜112、保護膜113、Pchメタル電極膜114b、導電性埋め込み膜115、内側サイドウォールスペーサ14、外側サイドウォールスペーサ16、下敷き絶縁膜15及びシリサイド層20のそれぞれの材料と同じである。

【0038】

また、図2(b)及び図3(a)、(b)に示すように、各トランジスタのゲート電極頂部が露出するように、半導体基板10上には応力絶縁膜21を介して層間絶縁膜22が形成されている。

【0039】

また、図1及び図2(a)に示すように、各トランジスタのゲート電極(つまりゲート溝)は、活性領域10aと活性領域10bとの間の素子分離領域11上で接続しており、素子分離領域11上に位置する部分の保護膜113には段差が形成されている。

【0040】

以上に説明したように、本実施形態の半導体装置においてはリプレースメントゲート構造を用いており、N型MISトランジスタのゲート電極は、保護膜113の直上にNchメタル電極膜114aが形成され且つNchメタル電極膜114aの直上にPchメタル電極膜114bが形成された構造を有し、P型MISトランジスタのゲート電極は、保護膜113の直上にPchメタル電極膜114bが形成された構造を有している。

【0041】

従って、後述するように、各トランジスタ領域上におけるゲート溝の形成に際し、ダミーゲート電極の除去を同時に行うことによって、言い換えると、ダミーゲート電極の除去工程を1回だけ実施することによって、ゲートラストプロセスの工程数を削減することができ、それにより、製造コスト及び歩留まり等を改善することができる。

【0042】

また、本実施形態によると、ゲート絶縁膜と各トランジスタの仕事関数調整用メタル材料(つまりNchメタル電極膜114a及びPchメタル電極膜114b)との間に保護膜113が形成されているため、保護膜113を仕事関数調整用メタル材料の拡散緩衝層として、ゲート絶縁膜と各トランジスタの仕事関数調整用メタル材料とを分離し、それにより、両者の間の相互拡散を制御することができる。また、後述するように、P型MISトランジスタ領域のゲート溝内の仕事関数調整用メタル材料(つまりNchメタル電極膜114a)を選択的に除去する際に、ゲート絶縁膜がエッチャントに直接さらされてダメージが生じる事態を阻止することが可能となる。従って、前述の相互拡散やダメージに起因する閾値電圧制御の不良、デバイス信頼性やトランジスタ特性等の劣化を防止することができる。

【0043】

さらに、本実施形態によると、ゲート絶縁膜と各トランジスタの仕事関数調整用メタル材料との間に保護膜113を挿入することによって、ゲート絶縁膜中への仕事関数調整用メタル材料の拡散を制御することが可能となるだけではなく、後述するように、P型MISトランジスタ領域のゲート溝内の仕事関数調整用メタル材料(つまりNchメタル電極膜114a)を選択的に除去する際に、保護膜113上部を同時に除去することによって、次のような効果も得ることができる。すなわち、保護膜113上部に拡散した又は打ち込まれた仕事関数調整用メタル材料を除去することができるので、メタル材料の残留に起因する仕事関数の劣化及び閾値電圧の劣化を防止することが可能となる。

【0044】

以上のように、本実施形態によると、N型MISトランジスタ及びP型MISトランジスタのそれぞれの製造時の歩留まりを改善しつつ、N型MISトランジスタ及びP型MISトランジスタのそれぞれの低閾値電圧動作を可能とすることができる。

【0045】

以下、本実施形態に係る半導体装置の製造方法について、図面を参照しながら説明する。図4(a)、(b)、図5(a)、(b)、図6(a)、(b)、図7(a)、(b)、図8(a)、(b)、図9(a)、(b)、図10(a)、(b)及び図11(a)、(b)は、本実施形態に係る半導体装置の製造方法を工程順に示す断面図である。尚、図4(a)、図5(a)、図6(a)、図7(a)、図8(a)、図9(a)、図10(a)及び図11(a)は、図1に示すC−C’線における断面図であり、図4(b)、図5(b)、図6(b)、図7(b)、図8(b)、図9(b)、図10(b)及び図11(b)は、図1に示すD−D’線における断面図である。また、図4(a)、(b)、図5(a)、(b)、図6(a)、(b)、図7(a)、(b)、図8(a)、(b)、図9(a)、(b)、図10(a)、(b)及び図11(a)、(b)において、「NMIS」とは、N型MISトランジスタ(NMISFET)が形成されるN型MISトランジスタ形成領域を示し、「PMIS」とは、P型MISトランジスタ(PMISFET)が形成されるP型MISトランジスタ形成領域を示している。

【0046】

まず、図4(a)及び(b)に示すように、例えばシリコンからなる半導体基板10の上部(半導体領域)に、N型MISトランジスタ形成領域とP型MISトランジスタ形成領域とを区画するように素子分離領域11を形成する。続いて、N型MISトランジスタ形成領域の半導体基板10の上部にp型ウェル領域12aを形成すると共に、P型MISトランジスタ形成領域の半導体基板10の上部にn型ウェル領域12bを形成する。ここで、p型ウェル領域12aのうち素子分離領域11に囲まれている部分が活性領域10aとなり、n型ウェル領域12bのうち素子分離領域11に囲まれている部分が活性領域10bとなる。

【0047】

次に、図5(a)及び(b)に示すように、半導体基板10の表面全体に対して、例えばケミカル酸化処理を行って、ダミー界面シリコン酸化膜101を形成する。ケミカル酸化は、例えば、一般的に用いられている、塩酸(HCl)及び過酸化水素水(H2 O2 )の混合溶液、又は硫酸(H2 SO4 )及び過酸化水素水(H2 O2 )の混合溶液等により半導体基板10を処理することにより行ってもよい。ここで、ダミー界面シリコン酸化膜101として、光学膜厚が例えば1nm〜5nm程度のドライ酸化膜又はラジカル酸化膜等を用いることもできる。ラジカル酸化膜は、例えば、水素(H2 )と酸素(O2 )又は一酸化二窒素(N2 O)との混合ガス雰囲気中で600℃〜850℃程度の温度の熱処理を行うことにより形成してもよい。

【0048】

続いて、図5(a)及び(b)に示すように、ダミー界面シリコン酸化膜101上に、例えばCVD法等により、ダミーゲート電極として、例えば膜厚50nm〜100nm程度のポリシリコン膜102を堆積する。ここで、ポリシリコン膜102には不純物をドープする必要はない。逆に、ポリシリコン膜102に砒素等の不純物を高濃度でドープした場合、後工程のダミーゲート電極除去時に除去性が低下する等の悪影響が考えられるため、ポリシリコン膜102は、通常のノンドープポリシリコン膜でよい。その後、ポリシリコン膜102上に、例えばCVD法等により、例えば膜厚10nm〜50nm程度の酸化シリコン(SiO2 )からなるハードマスク膜103を形成する。

【0049】

次に、公知のリソグラフィ法及びエッチング法により、成膜したハードマスク膜103、ポリシリコン膜102及びダミー界面シリコン酸化膜101に対してゲートエッチングを行う。これにより、図5(a)及び(b)に示すように、活性領域10a及び10bのそれぞれの上に、ダミーゲート電極及びダミーゲート絶縁膜からなるダミーゲートスタック構造が形成される。

【0050】

続いて、図6(a)及び(b)に示すように、半導体基板10の表面全面の上並びに各ダミーゲートスタック構造の上面及び側面の上に、例えばALD法により、例えば膜厚5nm〜10nm程度のシリコン窒化(ALD−SiN)膜を成膜する。その後、成膜したシリコン窒化膜に対してエッチバックを行って、シリコン窒化膜における各ダミーゲートスタック構造の両側面上を除く部分を除去することにより、各ダミーゲートスタック構造の両側面上に内側サイドウォールスペーサ14を形成する。

【0051】

次に、図6(a)及び(b)に示すように、公知の方法により、活性領域10bをマスクした状態で、活性領域10a(p型ウェル領域12a)に、ダミーゲートスタック構造及び内側サイドウォールスペーサ14をマスクとしてn型ドーパントを注入することにより、接合深さが比較的浅いn型エクステンション領域13aを形成する。その後、活性領域10aをマスクした状態で、活性領域10b(n型ウェル領域12b)に、ダミーゲートスタック構造及び内側サイドウォールスペーサ14をマスクとしてp型ドーパントを注入することにより、接合深さが比較的浅いp型エクステンション領域13bを形成する。

【0052】

続いて、図6(a)及び(b)に示すように、各ダミーゲートスタック構造の両側面上に内側サイドウォールスペーサ14を挟んでサイドウォール構造を形成する。具体的には、半導体基板10上の全面に、内側サイドウォールスペーサ14を含む各ダミーゲートスタック構造を覆うように、例えばCVD法又はALD法を用いて、下敷き絶縁膜15を成膜した後、下敷き絶縁膜15上にシリコン窒化膜を成膜し、その後、エッチバックを行うことによって、各ダミーゲートスタック構造の両側面上に内側サイドウォールスペーサ14を挟んで外側サイドウォールスペーサ16を形成する。ここで、外側サイドウォールスペーサ16と活性領域10aとの間には下敷き絶縁膜15が介在する。

【0053】

続いて、図6(a)及び(b)に示すように、活性領域10bをマスクした状態で、活性領域10a(p型ウェル領域12a)に、ダミーゲートスタック構造、内側サイドウォールスペーサ14及び外側サイドウォールスペーサ16をマスクとして、n型ドーパントを注入することにより、n型エクステンション領域13aよりも接合深さが深いn型ソース/ドレイン領域17aを形成する。その後、活性領域10aをマスクした状態で、活性領域10b(n型ウェル領域12b)に、ダミーゲートスタック構造、内側サイドウォールスペーサ14及び外側サイドウォールスペーサ16をマスクとして、p型ドーパントを注入することにより、p型エクステンション領域13bよりも接合深さが深いp型ソース/ドレイン領域17bを形成する。

【0054】

続いて、N型MISトランジスタ形成領域を覆うレジストマスク(図示省略未記載)と、P型MISトランジスタ形成領域におけるハードマスク膜103、内側サイドウォールスペーサ14及び外側サイドウォールスペーサ16とをエッチングマスクとし、例えばHBrをエッチングガスとして、p型ソース/ドレイン領域17bの上部に対してドライエッチングを行う。これにより、p型ソース/ドレイン領域17bの上部にリセス部(シリコン混晶部を形成するための凹部)が形成される。リセス部の深さは、例えば60nmである。その後、図6(b)に示すように、リセス部内にシリコンゲルマニウム層18をエピタキシャル成長により形成する。ここで、Siのソースガスとして、例えばシラン(SiH4 )又はジクロロシラン(SiH4 Cl2 )等を、Geのソースガスとして、例えばゲルマン(GeH4 )等を使用することができる。また、ボロンなどのp型不純物を注入しながら、シリコンゲルマニウム層18をエピタキシャル成長により形成してもよい。このように形成されたシリコンゲルマニウム層(シリコン混晶層)18は活性領域10bの一部分となる。また、シリコンゲルマニウム層18は例えば60nm程度の厚さを有し、シリコンゲルマニウム層18におけるGeの濃度は例えば20〜30原子%程度である。その後、図6(b)に示すように、シリコンゲルマニウム層18上に、シリサイド用カバー膜として、例えばシラン(SiH4 )又はジクロロシラン(SiH4 Cl2 )等を用いて、例えば10nm〜30nm程度のシリコンエピタキシャル層(シリコンキャップ層)19をエピタキシャル成長により選択的に形成する。その後、前述のN型MISトランジスタ形成領域を覆うレジストマスクを除去した後、半導体基板10に対して例えば1000℃程度のスパイクアニール処理を行う。この熱処理により、半導体基板10に注入されたn型不純物及びp型不純物がそれぞれ活性化される。

【0055】

続いて、例えばPVD(Physical Vapor Deposition )法又はCVD法等により、各ソース/ドレイン領域17a及び17bが形成された半導体基板10の上に全面にわたって、例えば、コバルト(Co)、タングステン(W)、プラチナ(Pt)又はニッケル(Ni)等からなる金属膜を堆積する。その後、所定の熱処理及び未反応金属膜の選択除去を行う。これによって、図6(a)及び(b)に示すように、n型ソース/ドレイン領域17aの上部及びp型ソース/ドレイン領域17b(正確にはシリコンエピタキシャル層20)の上部に、金属シリサイドであるシリサイド層20を形成する。

【0056】

次に、図7(a)及び(b)に示すように、例えばCVD法等により、N型MISトランジスタ形成領域及びP型MISトランジスタ形成領域のそれぞれを覆うように、例えば窒化シリコン(SiN)からなる応力絶縁膜21を成膜する。この応力絶縁膜21を設けることにより、各シリサイド層20の酸化が抑制されると共に、各トランジスタにおけるチャネル方向の歪み効果を生じさせることができる。

【0057】

尚、N型MISトランジスタ形成領域及びP型MISトランジスタ形成領域をそれぞれ個別にマスクすることにより、応力絶縁膜21として、N型MISトランジスタ形成領域には引張り応力を生じさせる効果を持つSiN膜を、P型MISトランジスタ形成領域には圧縮応力を生じさせる効果を持つSiNをそれぞれ個別に形成してもよい。

【0058】

次に、図7(a)及び(b)に示すように、各ダミーゲートスタック構造の間を埋め込むように、応力絶縁膜21上に例えばシリコン酸化膜からなる層間絶縁膜22を堆積する。ここで、各ダミーゲートスタック構造の間にボイドやシーム等の埋め込み不良が生じることを阻止しつつ、応力絶縁膜21からの窒素の脱離、シリサイド層20の構成材料のチャネル領域側への拡散、及び、ソース/ドレイン領域等の不純物深さ分布の劣化等を防止するために、低温且つ埋め込み性に優れた成膜方法、例えばALD法又はCVD法を用いて層間絶縁膜22を成膜してもよい。

【0059】

次に、例えばCMP法により、層間絶縁膜22に対して平坦化処理を行って、層間絶縁膜22の上部、応力絶縁膜21の一部、及び各ダミーゲートスタック構造のハードマスク膜103を除去することにより、各ダミーゲートスタック構造のポリシリコン膜(ダミーゲート電極膜)102を露出させる。次に、例えばウェットエッチング法により、各ダミーゲートスタック構造のポリシリコン膜102を除去する。このポリシリコン膜102が除去された結果、図7(a)及び(b)に示すように、活性領域10a上に、互いに対向する内側サイドウォールスペーサ14を側壁部とし且つ露出したダミー界面シリコン酸化膜101を底部とするゲート溝23aが形成されると共に、活性領域10b上に、互いに対向する内側サイドウォールスペーサ14を側壁部とし且つ露出したダミー界面シリコン酸化膜101を底部とするゲート溝23bが形成される。ここで、ダミーゲート電極であるポリシリコン膜102を除去する際には、エッチングダメージがなく且つ酸化シリコンとの選択性が高い溶液、例えば水酸化テトラメチルアンモニウム(TMAH:TetraMethyl Ammonium Hydroxide)溶液を用いてもよい。この場合、薬液温度が例えば50℃程度で、濃度(体積%濃度)が例えば3%〜5%程度の低濃度溶液を用いると、取り扱いが容易になる。続いて、各ゲート溝23a及び23bの底部のダミー界面シリコン酸化膜101を除去する。ここで、例えば、希釈フッ化水素酸、具体的には、濃度(体積%濃度)が例えば1%〜2%程度のフッ化水素酸を用いてダミー界面シリコン酸化膜101を除去してもよいが、外側サイドウォールスペーサ16下の下敷き絶縁膜15がエッチングされないように注意する必要がある。

【0060】

続いて、図8(a)及び(b)に示すように、各ゲート溝23a及び23bの底部に、例えば界面シリコン酸化膜からなる絶縁膜111を形成する。絶縁膜111としては、例えば、光学膜厚が0.5nm〜1nm程度のケミカル酸化膜、又は光学膜厚が0.5nm〜2.0nm程度のドライ酸化膜若しくはラジカル酸化膜等を用いてもよい。ケミカル酸化膜は、例えば、一般的に用いられている、塩酸(HCl)及び過酸化水素水(H2 O2 )の混合溶液、又は硫酸(H2 SO4 )及び過酸化水素水(H2 O2 )の混合溶液等により半導体基板10を処理することにより形成してもよい。また、O3 を混入させた純水に半導体基板10を曝すことによって、ケミカル酸化膜を形成してもよい。一方、ラジカル酸化膜は、水素(H2 )と酸素(O2 )又は一酸化二窒素(N2 O)との混合ガス雰囲気中で600℃〜850℃程度の温度の熱処理を行うことにより形成してもよい。

【0061】

続いて、図8(a)及び(b)に示すように、例えば原子層堆積(ALD)法により、各ゲート溝23a及び23における絶縁膜111の上面及び各ゲート溝23a及び23の両側壁面を覆うように、半導体基板10上の全面に高誘電率絶縁膜112を形成する。高誘電率膜112としては、例えば、ハフニウムシリケート(HfSiO)、窒素添加ハフニウムシリケート(HfSiON)、酸化ハフニウム(HfO)又は酸化ハフニウムジルコニウム(HfZrO)等のハフニウム(Hf)含有絶縁膜を用いることができる。また、ALD法を用いて高誘電率絶縁膜112を形成する場合、例えば、原料として、テトラキス(エチルメチルアミノ)ハフニウム(Hf[N(C2 H5 )CH3 ]4 )等のハフニウム(Hf)を含む有機系材料と、モノシラン(SiH4 )等のシリコン(Si)を含むガス又はトリス(ジメチルアミノ)シラン(SiH[N(CH3 )2 ]3 )等のシリコン(Si)を含む有機系材料とを用いて、250℃〜350℃程度の成膜温度で、短時間に且つ繰り返し堆積を行うと共に、1つの堆積から次の堆積までの間に余剰原料のパージを行いながら、酸素(O2 )ガス、オゾン(O3 )ガス又は水蒸気(H2 O)等を用いて堆積膜の酸化を行ってもよい。尚、Hf含有原料として、有機系材料に代えて、塩化ハフニウム(HfCl4 )又は塩化ジルコニウム(ZrCl4 )等の無機系材料を用いてもよい。また、高誘電率絶縁膜112の膜厚を、例えばEOT(等価酸化膜厚)で0.5nm〜2.0nm程度とする場合には、高誘電率絶縁膜112と絶縁膜111とを合わせた物理膜厚を1nm〜3nm程度とすればよい。また、高誘電率絶縁膜112として、前述したように、酸化ジルコニウム(ZrO)を含むHf含有誘電体膜としてもよいし、又は、Hf含有誘電体膜に代えて、例えば、酸化ジルコニウム(ZrO)からなる単体の誘電率膜を用いてもよい。

【0062】

続いて、図8(a)及び(b)に示すように、各ゲート溝23a及び23の底面及び両側壁面を覆うように、高誘電率絶縁膜112の上に保護膜113を形成する。保護膜113は、後工程でP型MISトランジスタ形成領域上においてNchメタル電極膜を除去する際に、Nchメタル電極膜の構成材料がP型MISトランジスタ形成領域の高誘電率絶縁膜112中へ拡散することを防止するためのストッパー機能を有する。また、保護膜113は、Nchメタル電極膜の除去時に高誘電率絶縁膜112が薬液又はエッチャントに直接曝されてダメージを受けることを阻止するためのストッパー機能を有する。保護膜113の材料としては、例えば、窒化チタン、窒化ハフニウム、窒化タンタル若しくは窒化ニッケル等の金属窒化物を用いてもよい。保護膜113の膜厚(堆積時膜厚)は例えば2〜5nm程度であってもよい。また、保護膜113の成膜方法としては、例えばALD法又はPVD法のいずれを用いてもよい。

【0063】

続いて、図8(a)及び(b)に示すように、各ゲート溝23a及び23の底面及び両側壁面を覆うように、保護膜113上に、N型MISトランジスタの実効仕事関数の値をシフトさせるための仕事関数調整用メタル電極膜(Nchメタル電極膜)114aを形成する。Nchメタル電極膜114aの材料としては、N型MISトランジスタの仕事関数を持つ金属又は当該金属の化合物、例えば、金属アルミニウム、金属チタン、若しくはそれらの合金、窒化ハフニウム、炭化タンタル又はランタン酸化物等を用いてもよい。Nchメタル電極膜114aの膜厚(堆積時膜厚)は例えば1nm〜5nm程度であってもよい。また、Nchメタル電極膜114aの成膜方法としては、例えばALD法又はPVD法のいずれを用いてもよい。但し、Nchメタル電極膜114aについては、特に、短チャネル領域のしきい値劣化(つまり、チャネル長が短くなった場合の閾値電圧の劣化)を阻止する必要がある点、及び、各ゲート溝23a及び23の底面及び両側壁面を確実に被覆する必要がある点から、例えばALD法又は高指向性スパッタ法等による成膜方法を用いてもい。

【0064】

尚、Nchメタル電極膜114aの構成材料は、大気暴露やリソグラフィ工程等による酸化に起因して特性が容易に劣化する傾向があるので、Nchメタル電極膜114aの形成後に、保護膜113と同様の保護膜によってNchメタル電極膜114aを覆い、それによって、Nchメタル電極膜114aの酸化を防止して特性を安定化させてもよい。

【0065】

次に、図9(a)及び(b)に示すように、公知のリソグラフィ法を用いて、N型MISトランジスタ形成領域を覆うレジストパターン121を形成した後、レジストパターン121をマスクとして、P型MISトランジスタ形成領域に形成されたNchメタル電極膜114aの除去を行う。Nchメタル電極膜114aの除去には、ドライエッチング法又はウェットエッチング法のいずれの方法を用いてもよいが、エッチングダメージによって高誘電率絶縁膜112の信頼性を劣化させず、且つNchメタル電極膜114aを効率良く除去できる方法を用いることが望ましい。例えば、Nchメタル電極膜114aがAl、Ti又はTaを含む場合、硫酸(H2 SO4 )、過酸化水素(H2 O2 )、又は塩酸(HCl)と過酸化水素(H2 O2 )との混合薬液を用いてNchメタル電極膜114aを除去してもよい。

【0066】

図12(a)、(b)及び図13(a)、(b)は、本実施形態に係る半導体装置の製造方法のうち、図9(a)及び(b)に示す工程から図10(a)及び(b)に示す工程までの詳細を工程順に示す断面図(図1に示すA−A’線における断面図)である。図12(a)に示すように、N型MISトランジスタ形成領域を覆うレジストパターン121を形成した後、図12(b)に示すように、レジストパターン121をマスクとして、P型MISトランジスタ形成領域に形成されたNchメタル電極膜114aの除去を行う。このとき、P型MISトランジスタ形成領域において、Nchメタル電極膜114aの構成材料が拡散している保護膜113の上部も合わせて除去する。これにより、PN境界部(つまりN型MISトランジスタ形成領域とP型MISトランジスタ形成領域とを区画する素子分離領域11)上において保護膜113に段差が発生する。当該段差の大きさは、保護膜113の膜厚(堆積時膜厚)に依存するが、保護膜113の膜厚(堆積時膜厚)が例えば5nm程度である場合、1nm〜3nm程度となる。ここで、本実施形態は、P型MISトランジスタ形成領域において保護膜113を完全には除去しないことを特徴としている。また、P型MISトランジスタ形成領域においてNchメタル電極膜114aと共に保護膜113の上部を同時に除去することにより、P型MISトランジスタ形成領域においてNchメタル電極膜114aを完全に(つまり最大限に)除去することが可能となる。

【0067】

次に、図13(a)に示すように、レジストパターン121を除去した後、図10(a)、(b)及び図13(b)に示すように、各ゲート溝23a及び23bのそれぞれの底面及び側壁面を覆うように、ゲート溝23a内のNchメタル電極膜114aの上及びゲート溝23b内の保護膜113の上に、P型MISトランジスタの仕事関数調整用メタル電極膜(Pchメタル電極膜)114bを形成する。Pchメタル電極膜114bの材料としては、比較的高い仕事関数を持つ材料、例えば、窒化チタン、ルテニウム酸化物、又は白金若しくは金等の貴金属等を用いてもよい。Pchメタル電極膜114bの膜厚(堆積時膜厚)は例えば4nm〜10nm程度であってもよい。また、Pchメタル電極膜114bの成膜方法としては、PVD法の他、例えばALD法又はPVD法のいずれを用いてもよい。続いて、図10(a)、(b)及び図13(b)に示すように、各ゲート溝23a及び23bのそれぞれにおけるPchメタル電極膜114bにより形成される凹部が埋まるように、ゲート溝23a内のPchメタル電極膜114bの上及びゲート溝23b内のPchメタル電極膜114bの上に導電性の金属含有膜115を形成する。金属含有膜115の材料としては、例えば、タングステン(W)、アルミニウム(Al)、又は窒化チタン(TiN)等が適用可能である。また、各ゲート溝23a及び23b内でのシームやボイドの形成を抑制するために、例えば、金属含有膜115の成膜前に、金属含有膜115との親和性の高いシード層を形成しておき、その後、例えばALD法又は高温リフローを伴うPVD法のいずれかを用いて金属含有膜115を成膜することが望ましい。

【0068】

次に、図11(a)及び(b)に示すように、CMP法により、各ゲート溝23a及び23bの外側の金属含有膜115、Pchメタル電極膜114b、Nchメタル電極膜114a、保護膜113及び高誘電率絶縁膜112を研磨して除去すると共に、各ゲート溝23a及び23bに埋め込まれた前記の各膜の平坦化を行う。ここで、図11(a)及び(b)に示す研磨及び除去をCMP法のみを用いて実施すると、幅広パターンを有する各ゲート溝23a及び23bに形成されたゲート電極の上面高さが弧状に変化するように研磨される、いわゆるディッシングが問題になる場合がある。その場合には、CMP法とドライエッチングによるエッチバックとを組み合わせて前記の各膜を除去してもよい。

【0069】

その後、図示は省略しているが、n型ソース/ドレイン領域17a及びp型ソース/ドレイン領域17b(正確には各ソース/ドレイン領域上のシリサイド層20)、並びに各ゲート溝23a及び23bに埋め込まれたリプレースメントゲート電極のそれぞれに電気的に接続するコンタクト及び配線の形成を行うことにより、半導体装置を完成させる。

【0070】

(第2の実施形態)

まず、第2の実施形態に係る半導体装置の構造について、図14、図15(a)、(b)及び図16(a)、(b)を参照しながら説明する。図14は、本実施形態に係る半導体装置の平面図である。図15(a)、(b)及び図16(a)、(b)は、それぞれ、図14に示すAーA’線、B−B’線、C−C’線及びD−D’線における断面図である。尚、図14、図15(a)、(b)及び図16(a)、(b)において、図1、図2(a)、(b)及び図3(a)、(b)に示す第1の実施形態に係る半導体装置と同じ構成要素には同じ符号を付すことにより、重複する説明を省略する。また、図14、図15(a)、(b)及び図16(a)、(b)において、「NMIS」とは、N型MISトランジスタ(NMISFET)が形成されるN型MISトランジスタ形成領域を示し、「PMIS」とは、P型MISトランジスタ(PMISFET)が形成されるP型MISトランジスタ形成領域を示している。また、図14では、シリサイド層20、応力絶縁膜21及び層間絶縁膜22の図示を省略している。

【0071】

図14、図15(a)、(b)及び図16(a)、(b)に示すように、本実施形態に係る半導体装置が第1の実施形態と異なっている点は、活性領域10a及び10bのそれぞれの上における絶縁膜111を底部とし且つ内側サイドウォールスペーサ14を側壁部とするゲート溝の側壁面上には、高誘電率絶縁膜112及び保護膜113が形成されていないことである。

【0072】

このような本実施形態に係る半導体装置によっても、第1の実施形態と同様の効果を得ることができる。

【0073】

また、本実施形態に係る半導体装置を製造する方法が第1の実施形態と異なっている点は、ダミーゲート電極形成前に、絶縁膜(界面シリコン酸化膜)111、高誘電率絶縁膜112、及び、ダミーゲート電極除去時のエッチングストップ層として機能する保護膜(金属含有層)113の形成を行うことである。

【0074】

以下、本実施形態に係る半導体装置の製造方法について、図面を参照しながら詳細に説明する。図17(a)、(b)、図18(a)、(b)、図19(a)、(b)、図20(a)、(b)、図21(a)、(b)、図22(a)、(b)、図23(a)、(b)及び図24(a)、(b)は、本実施形態に係る半導体装置の製造方法を工程順に示す断面図である。尚、図17(a)、図18(a)、図19(a)、図20(a)、図21(a)、図22(a)、図23(a)及び図24(a)は、図14に示すC−C’線における断面図であり、図17(b)、図18(b)、図19(b)、図20(b)、図21(b)、図22(b)、図23(b)及び図24(b)は、図14に示すD−D’線における断面図である。また、図17(a)、(b)、図18(a)、(b)、図19(a)、(b)、図20(a)、(b)、図21(a)、(b)、図22(a)、(b)、図23(a)、(b)及び図24(a)、(b)において、「NMIS」とは、N型MISトランジスタ(NMISFET)が形成されるN型MISトランジスタ形成領域を示し、「PMIS」とは、P型MISトランジスタ(PMISFET)が形成されるP型MISトランジスタ形成領域を示している。

【0075】

まず、第1の実施形態の図4(a)及び(b)に示す工程と同様に、図17(a)及び(b)に示すように、例えばシリコンからなる半導体基板10の上部(半導体領域)に、N型MISトランジスタ形成領域とP型MISトランジスタ形成領域とを区画するように素子分離領域11を形成する。続いて、N型MISトランジスタ形成領域の半導体基板10の上部にp型ウェル領域12aを形成すると共に、P型MISトランジスタ形成領域の半導体基板10の上部にn型ウェル領域12bを形成する。ここで、p型ウェル領域12aのうち素子分離領域11に囲まれている部分が活性領域10aとなり、n型ウェル領域12bのうち素子分離領域11に囲まれている部分が活性領域10bとなる。

【0076】

次に、図18(a)及び(b)に示すように、半導体基板10に対して、例えばウェット処理を行うことにより、半導体基板10の表面上に、例えば厚さ1nm以下の薄い界面シリコン酸化膜からなる絶縁膜111を形成する。ウェット処理においては、例えば、塩酸(HCl)と過酸化水素(H2 O2 )との混合液であるHPM(Hydrochloric acid-Hydrogen Peroxide Mixture )溶液、又はオゾン(O3 )水等を用いてもよい。また必要に応じて、酸素(O2 )と水素(H2 )との混合ガス雰囲気中又は一酸化二窒素(N2 O)と水素(H2 )との混合ガス雰囲気中で低温RTP(Rapid Thermal Process )プロセスを行うことによって、絶縁膜111となる界面シリコン酸化膜を形成してもよい。

【0077】

次に、図18(a)及び(b)に示すように、例えばALD法により、絶縁膜111上に高誘電率絶縁膜112を形成する。高誘電率絶縁膜112の具体的な形成方法は、第1の実施形態の図8(a)及び(b)に示す工程における高誘電率絶縁膜112の形成方法と同様である。

【0078】

次に、図18(a)及び(b)に示すように、高誘電率絶縁膜112の上に、例えば厚さ2nm〜5nm程度の保護膜113を形成する。保護膜113は、後工程でダミーゲート電極を除去する際、及び、後工程でP型MISトランジスタ形成領域上においてNchメタル電極膜を除去する際に、高誘電率絶縁膜112がエッチングされることを防止するエッチングストップ層として機能する。保護膜113の材料としては、例えば、窒化チタン、窒化ハフニウム、窒化タンタル若しくは窒化ニッケル等の金属窒化物を用いてもよい。また、保護膜113の成膜方法としては、例えばALD法又はPVD法のいずれを用いてもよい。

【0079】

次に、図18(a)及び(b)に示すように、保護膜113上に、例えばCVD法等により、ダミーゲート電極として、例えば膜厚50nm〜100nm程度のポリシリコン膜102を堆積する。ここで、ポリシリコン膜102には不純物をドープする必要はない。逆に、ポリシリコン膜102に砒素等の不純物を高濃度でドープした場合、後工程のダミーゲート電極除去時に除去性が低下する等の悪影響が考えられるため、ポリシリコン膜102は、通常のノンドープポリシリコン膜でよい。その後、ポリシリコン膜102上に、例えばCVD法等により、例えば膜厚10nm〜50nm程度の酸化シリコン(SiO2 )からなるハードマスク膜103を形成する。

【0080】

次に、公知のリソグラフィ法及びエッチング法により、成膜したハードマスク膜103、ポリシリコン膜102、保護膜113、高誘電率絶縁膜112及び絶縁膜111に対してゲートエッチングを行う。これにより、図18(a)及び(b)に示すように、活性領域10a及び10bのそれぞれの上に、絶縁膜111及び高誘電率絶縁膜112からなるゲート絶縁膜並びに保護膜113を介して、ダミーゲート電極が形成される。

【0081】

次に、第1の実施形態の図6(a)、(b)及び図7(a)、(b)に示す工程と同様に、図19(a)及び(b)に示すように、内側サイドウォールスペーサ14、n型エクステンション領域13a、p型エクステンション領域13b、下敷き絶縁膜15、外側サイドウォールスペーサ16、n型ソース/ドレイン領域17a、p型ソース/ドレイン領域17b、シリコンゲルマニウム層18、シリコンエピタキシャル層(シリコンキャップ層)19、シリサイド層20、応力絶縁膜21及び層間絶縁膜22を形成した後、層間絶縁膜22に対して平坦化処理を行って、各ダミーゲートスタック構造のポリシリコン膜(ダミーゲート電極膜)102を露出させる。

【0082】

次に、図20(a)及び(b)に示すように、例えばTMAH溶液を用いたウェットエッチング法により、各ダミーゲートスタック構造のポリシリコン膜102を除去する。このポリシリコン膜102が除去された結果、図20(a)及び(b)に示すように、活性領域10a上に、互いに対向する内側サイドウォールスペーサ14を側壁部とし且つ露出した保護膜113を底部とするゲート溝23aが形成されると共に、活性領域10b上に、互いに対向する内側サイドウォールスペーサ14を側壁部とし且つ露出した保護膜113を底部とするゲート溝23bが形成される。

【0083】

次に、各ゲート溝23a及び23b内の保護膜113表面の残留酸化物の除去を行った後、図21(a)及び(b)に示すように、各ゲート溝23a及び23の底面及び両側壁面を覆うように、保護膜113上に、N型MISトランジスタの実効仕事関数の値をシフトさせるための仕事関数調整用メタル電極膜(Nchメタル電極膜)114aを形成する。Nchメタル電極膜114aの材料、膜厚及び成膜方法は、第1の実施形態の場合と同様である。

【0084】

次に、図22(a)及び(b)に示すように、公知のリソグラフィ法を用いて、N型MISトランジスタ形成領域を覆うレジストパターン121を形成した後、レジストパターン121をマスクとして、P型MISトランジスタ形成領域に形成されたNchメタル電極膜114aの除去を行う。Nchメタル電極膜114aの除去方法は、第1の実施形態の場合と同様である。

【0085】

図25(a)、(b)及び図26(a)、(b)は、本実施形態に係る半導体装置の製造方法のうち、図22(a)及び(b)に示す工程から図23(a)及び(b)に示す工程までの詳細を工程順に示す断面図(図14に示すA−A’線における断面図)である。図25(a)に示すように、N型MISトランジスタ形成領域を覆うレジストパターン121を形成した後、図25(b)に示すように、レジストパターン121をマスクとして、P型MISトランジスタ形成領域に形成されたNchメタル電極膜114aの除去を行う。このとき、P型MISトランジスタ形成領域において、Nchメタル電極膜114aの構成材料が拡散している保護膜113の上部も合わせて除去する。これにより、PN境界部(つまりN型MISトランジスタ形成領域とP型MISトランジスタ形成領域とを区画する素子分離領域11)上において保護膜113に段差が発生する。当該段差の大きさは、保護膜113の膜厚(堆積時膜厚)に依存するが、保護膜113の膜厚(堆積時膜厚)が例えば5nm程度である場合、1nm〜3nm程度となる。ここで、本実施形態は、P型MISトランジスタ形成領域において保護膜113を完全には除去しないことを特徴としている。また、P型MISトランジスタ形成領域においてNchメタル電極膜114aと共に保護膜113の上部を同時に除去することにより、P型MISトランジスタ形成領域においてNchメタル電極膜114aを完全に(つまり最大限に)除去することが可能となる。

【0086】

次に、図26(a)に示すように、レジストパターン121を除去した後、図23(a)、(b)及び図26(b)に示すように、各ゲート溝23a及び23bのそれぞれの底面及び側壁面を覆うように、ゲート溝23a内のNchメタル電極膜114aの上及びゲート溝23b内の保護膜113の上に、P型MISトランジスタの仕事関数調整用メタル電極膜(Pchメタル電極膜)114bを形成する。Pchメタル電極膜114bの材料、膜厚及び成膜方法は、第1の実施形態の場合と同様である。続いて、図23(a)、(b)及び図26(b)に示すように、各ゲート溝23a及び23bのそれぞれにおけるPchメタル電極膜114bにより形成される凹部が埋まるように、ゲート溝23a内のPchメタル電極膜114bの上及びゲート溝23b内のPchメタル電極膜114bの上に導電性の金属含有膜115を形成する。金属含有膜115の材料及び成膜方法は、第1の実施形態の場合と同様である。

【0087】

次に、図24(a)及び(b)に示すように、CMP法により、各ゲート溝23a及び23bの外側の金属含有膜115、Pchメタル電極膜114b及びNchメタル電極膜114aを研磨して除去すると共に、各ゲート溝23a及び23bに埋め込まれた前記の各膜の平坦化を行う。ここで、図24(a)及び(b)に示す研磨及び除去をCMP法のみを用いて実施すると、幅広パターンを有する各ゲート溝23a及び23bに形成されたゲート電極の上面高さが弧状に変化するように研磨される、いわゆるディッシングが問題になる場合がある。その場合には、CMP法とドライエッチングによるエッチバックとを組み合わせて前記の各膜を除去してもよい。

【0088】

その後、図示は省略しているが、n型ソース/ドレイン領域17a及びp型ソース/ドレイン領域17b(正確には各ソース/ドレイン領域上のシリサイド層20)、並びに各ゲート溝23a及び23bに埋め込まれたリプレースメントゲート電極のそれぞれに電気的に接続するコンタクト及び配線の形成を行うことにより、半導体装置を完成させる。

【0089】

尚、第1及び第2の実施形態においては、N型MISトランジスタ形成領域及びP型MISトランジスタ形成領域にN型MISトランジスタの仕事関数調整用メタル電極膜(Nchメタル電極膜)114aを形成した後、P型MISトランジスタ形成領域に形成されたNchメタル電極膜114aを除去し、その後、N型MISトランジスタ形成領域及びP型MISトランジスタ形成領域にP型MISトランジスタの仕事関数調整用メタル電極膜(Pchメタル電極膜)114bを形成した。しかし、これに代えて、N型MISトランジスタ形成領域及びP型MISトランジスタ形成領域にPchメタル電極膜を形成した後、N型MISトランジスタ形成領域に形成されたPchメタル電極膜を除去し、その後、N型MISトランジスタ形成領域及びP型MISトランジスタ形成領域にNchメタル電極膜を形成してもよい。但し、Nchメタル電極膜114aは、例えばAl、Ti又はMo等の酸化されやすい物質を含むと共に、当該酸化に起因してN型MISトランジスタの特性が変動して劣化する場合がある。このため、Pchメタル電極膜を先に形成した場合、例えば、高誘電率絶縁膜上におけるPchメタル電極膜の洗浄工程や除去工程等に伴う酸素残留、及び、その後に形成されるNchメタル電極膜との反応に起因するPchメタル電極膜の特性変動等が問題となる場合がある。このような場合には、第1及び第2の実施形態のように、Nchメタル電極膜を先に形成すること、言い換えると、N型MISトランジスタ形成領域においてPchメタル電極膜の除去を行わないことが望ましい。

【産業上の利用可能性】

【0090】

本発明に係る半導体装置及びその製造方法によると、トランジスタを構成するゲート絶縁膜のダメージ、及び仕事関数調整用メタルの加工に起因するトランジスタ特性の劣化等を防止して信頼性及び歩留まり等を改善することができるので、メタルゲート電極を有するトランジスタを備えた半導体装置等に有用である。

【符号の説明】

【0091】

10 半導体基板

10a、10b 活性領域

11 素子分離領域

12a p型ウェル領域

12b n型ウェル領域

13a n型エクステンション領域

13b p型エクステンション領域

14 内側サイドウォールスペーサ

15 下敷き絶縁膜

16 外側サイドウォールスペーサ

17a n型ソース/ドレイン領域

17b p型ソース/ドレイン領域

18 シリコンゲルマニウム層

19 シリコンキャップ層

20 シリサイド層

21 応力絶縁膜

22 層間絶縁膜

23a、23b ゲート溝

101 ダミー界面シリコン酸化膜

102 ポリシリコン膜

103 ハードマスク膜

111 絶縁膜

112 高誘電率ゲート絶縁膜

113 保護膜

114a Nchメタル電極膜

114b Pchメタル電極膜

115 導電性埋め込み膜

121 レジストパターン

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、メタルゲート電極を備えた相補型MISFET(Metal Insulator Semiconductor Field Effect Transistor)及びその形成方法に関する。

【背景技術】

【0002】

トランジスタの動作の高速化及び低消費電力化は、スケーリング則に基づき、トランジスタの微細化により実現されてきている。一般に、トランジスタにおけるゲート絶縁膜とゲート電極との積層構造(ゲートスタック)の材料として、酸化シリコン(SiO2 )又は酸窒化シリコン(SiON)/ポリシリコンが用いられてきたが、ゲートリーク電流の増大により、このような材料からなるゲート絶縁膜を薄膜化することは困難になってきている。そこで、高誘電率(High-k)ゲート絶縁膜とメタルゲート電極とを組み合わせたHigh-k/メタルゲート技術が注目されている。尚、High-k絶縁膜とは、SiNよりも高い誘電率(例えば比誘電率8以上)を持つ絶縁膜を意味する。また、メタルゲート電極とは、金属又は導電性金属化合物からなる電極部分を有するゲート電極を意味する。

【0003】

High-k/メタルゲート構造の形成方法としては、当初、従来のSiO2 /ポリシリコンゲート構造の形成方法と同様に、最初にHigh-kゲート絶縁膜及びメタルゲート電極を形成した後、不純物層及びシリサイド層等を形成する方法、いわゆるゲートファーストプロセスによる形成方法が検討された。しかしながら、相補型MISFETに用いられるメタルゲート(デュアルメタルゲート)においては、NMISFETとPMISFETとの間で異なるメタル材料を用いた場合にゲートエッチング形状の制御が難しいこと、及び、後工程での不純物注入層に対するスパイクアニール等の熱負荷に起因して閾値電圧や駆動電流等が劣化すること等のインテグレーション上の問題があることが明らかになってきた。

【0004】

そこで、最初にダミーゲート電極を形成した後、ダミーゲート電極をマスクとして、不純物層及びシリサイド層の形成を行い、その後、ダミーゲート電極を除去した後、メタルゲート電極を形成する方法(以下、ゲートラストプロセスと呼ぶ)が主流になりつつある(例えば特許文献1参照)。ゲートラストプロセスによると、ゲートファーストプロセスよりも工程数が増加するという欠点はあるものの、デュアルメタルゲートのインテグレーションを実現して、極めて良好なデバイス特性を得ることができる。特に、ゲートラストプロセスの場合、実効仕事関数の値を制御するための金属材料を成膜した後は、比較的低温のプロセスでデバイスを形成することができる。このため、スパイクアニール等に起因するメタルゲート電極特性の変質の影響を受けることなく、スタックゲートの実効的な仕事関数の値をバンド端の近傍に制御することが可能となる。また、ダミーゲート自体は、NMISFET及びPMISFETとも同一の材料で形成されるため、ゲートエッチング工程における形状の制御もゲートファーストプロセスと比較して容易になる。尚、「実効仕事関数」とは、MISFETの電気特性から求められる仕事関数であって、真空準位と金属のエネルギー準位との差を示す物性的な仕事関数に絶縁膜中の準位などの影響を加味したものを意味する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許出願公開第2010/0052070号明細書

【特許文献2】米国特許出願公開第2009/0039433号明細書

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献1に開示されている従来のゲートラストプロセスには、以下のような問題がある。すなわち、従来のゲートラストプロセスでは、ダミーゲート電極の除去後に、NMISFET及びPMISFETのそれぞれに応じた仕事関数調整用メタル材料を個別に成膜する必要がある。そのため、仕事関数調整用メタル材料の成膜、導電性埋め込み材料(ダミーゲート電極の除去により形成されたゲート溝を埋め込むための導電性材料)の成膜、及び層間膜上の(つまりゲート溝の外側の)前記各材料の除去をNMISFET及びPMISFETのそれぞれに対して個別に行う必要がある。従って、従来のゲートラストプロセスにおいては、工程数の増加、それに伴うコストの増大、加工工程が増加することに起因するプロセスばらつきの増大、及び、それに伴う歩留まりの低下等のリスクの増大等の問題が生じる。

【0007】

それに対して、特許文献2には、NMISFET及びPMISFETのそれぞれにおいてダミーゲート電極を同時に除去した後、例えばNMISFETの仕事関数調整用メタル材料を成膜し、その後、当該メタル材料をPMISFET上で除去した後、PMISFETの仕事関数調整用メタル材料を成膜するという方法が開示されている。特許文献2に開示されているゲートラストプロセスによると、ダミーゲートの加工工程及び除去工程、並びにCMP(Chemical Mechanical Polishing )による仕事関数調整用メタル材料の除去工程のそれぞれの実施回数を1回にできるため、工程数の削減が可能となる。

【0008】

しかしながら、特許文献2に開示されているゲートラストプロセスにおいては、High-kゲート絶縁膜の直上で仕事関数調整用メタル材料の除去を行う必要があるため、ドライエッチング法又はウェットエッチング法を用いてエッチングを行う際に、High-kゲート絶縁膜にエッチャントが浸入してダメージが生じる。その結果、閾値電圧制御の不良、デバイス信頼性やトランジスタ特性等の劣化が引き起こされる懸念がある。また、High-kゲート絶縁膜上に形成されたメタル膜は、例えばCVD(Chemical Vapor Deposition )法又はALD(Atomic Layer Deposition )法等による成膜のように、プラズマによる打ち込みがない環境で成膜されたとしても、High-kゲート絶縁膜と部分的に反応し、それにより、当該絶縁膜中にメタル材料が拡散して絶縁膜深さ方向に分布してしまう。その結果、後工程でのメタル材料除去時の除去性が劣化して、次のような問題が生じる。例えば、ダミーゲート電極の除去後に、NMISFETの仕事関数調整用メタル材料を成膜し、その後、当該メタル材料をPMISFET上で除去する場合、PMISFET上にNMISFETの仕事関数調整用メタル材料が残留してしまい、PMISFETに必要な仕事関数が得られなくなる。

【0009】

前記に鑑み、本発明は、ゲートラストプロセスの工程数を削減しつつ、所望の信頼性及び特性が得られるメタルゲート電極を備えたMISFETを実現できるようにすることを目的とする。

【課題を解決するための手段】

【0010】

前記の目的を達成するために、本発明に係る半導体装置は、半導体基板における第1の領域及び第2の領域のそれぞれの上に形成された第1のゲート溝及び第2のゲート溝と、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの少なくとも底面上に形成されたゲート絶縁膜と、前記第1のゲート溝内の前記ゲート絶縁膜の上及び前記第2のゲート溝内の前記ゲート絶縁膜の上にそれぞれ形成された保護膜と、前記第1のゲート溝の底面及び側壁面を覆うように、前記第1のゲート溝内の前記保護膜の上に形成された第1の金属含有膜と、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように、前記第1のゲート溝内の前記第1の金属含有膜の上及び前記第2のゲート溝内の前記保護膜の上に形成された第2の金属含有膜と、前記第1のゲート溝及び前記第2のゲート溝のそれぞれにおける前記第2の金属含有膜により形成される凹部が埋まるように、前記第1のゲート溝内の前記第2の金属含有膜の上及び前記第2のゲート溝内の前記第2の金属含有膜の上に形成された第3の金属含有膜とを備え、前記第1のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さと比べて、前記第2のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さは薄いことを特徴とする半導体装置。

【0011】

本発明に係る半導体装置において、前記第1のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さと、前記第2のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さとの差は、1nm以上で且つ3nm以下であってもよい。

【0012】

本発明に係る半導体装置において、前記半導体基板の上部における前記第1の領域と前記第2の領域との間に素子分離領域が形成されており、前記第1のゲート溝と前記第2のゲート溝とは前記素子分離領域上で接続しており、前記素子分離領域上に位置する部分の前記保護膜には段差が形成されていてもよい。

【0013】

本発明に係る半導体装置において、前記保護膜は、窒化チタン、窒化ハフニウム又は窒化タンタルから構成されていてもよい。

【0014】

本発明に係る半導体装置において、前記第1のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さは、2nm以上で且つ5nm以下であってもよい。

【0015】

本発明に係る半導体装置において、前記ゲート絶縁膜及び前記保護膜は、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように形成されていてもよい。

【0016】

本発明に係る半導体装置において、前記ゲート絶縁膜及び前記保護膜は、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの側壁面上には形成されていなくてもよい。

【0017】

本発明に係る半導体装置において、前記半導体基板における前記第1のゲート溝の両側方には第1導電型の第1のソース/ドレイン領域が形成されており、前記半導体基板における前記第2のゲート溝の両側方には第2導電型の第2のソース/ドレイン領域が形成されていてもよい。ここで、前記第1導電型がn型であり、前記第2導電型がp型である場合、前記第1の金属含有膜は、チタン、アルミニウム、チタンとアルミニウムとの合金、窒化ハフニウム又は炭化タンタルを含んでいてもよい。また、前記第1の金属含有膜の厚さは、1nm以上で且つ5nm以下であってもよい。また、前記第2の金属含有膜は、窒化チタン、酸化ルテニウム又は白金を含んでいてもよい。ここで、前記第2の金属含有膜は、白金以外の貴金属を含んでいてもよい。また、前記第2の金属含有膜の厚さは、4nm以上であってもよい。さらに、前記第2のソース/ドレイン領域は、シリコンゲルマニウム層を有していてもよい。

【0018】

尚、前記第3の金属含有膜(つまり導電性埋め込み材料)は、例えば、タングステン、アルミニウム又は窒化チタン等を含んでいてもよい。

【0019】

本発明に係る半導体装置において、前記ゲート絶縁膜は、高誘電率絶縁膜を含んでいてもよい。ここで、前記高誘電率絶縁膜は、少なくともハフニウム又はジルコニウムを含む絶縁膜であってもよい。

【0020】

本発明に係る半導体装置の製造方法は、半導体基板における第1の領域及び第2の領域のそれぞれの上に第1のゲート溝及び第2のゲート溝を形成する工程(a)と、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの少なくとも底面上にゲート絶縁膜を形成する工程(b)と、前記第1のゲート溝内の前記ゲート絶縁膜の上及び前記第2のゲート溝内の前記ゲート絶縁膜の上にそれぞれ保護膜を形成する工程(c)と、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように、前記第1のゲート溝内の前記保護膜の上及び前記第2のゲート溝内の前記保護膜の上に第1の金属含有膜を形成する工程(d)と、前記第2のゲート溝内の前記第1の金属含有膜、及び前記第2のゲート溝内の前記保護膜の上部を選択的に除去する工程(e)と、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように、前記第1のゲート溝内の前記第1の金属含有膜の上及び前記第2のゲート溝内の前記保護膜の上に第2の金属含有膜を形成する工程(f)と、前記第1のゲート溝及び前記第2のゲート溝のそれぞれにおける前記第2の金属含有膜により形成される凹部が埋まるように、前記第1のゲート溝内の前記第2の金属含有膜の上及び前記第2のゲート溝内の前記第2の金属含有膜の上に第3の金属含有膜を形成する工程(g)とを備えている。

【0021】

本発明に係る半導体装置の製造方法において、前記工程(a)は、前記半導体基板における前記第1の領域及び前記第2の領域のそれぞれの上に第1のダミーゲート電極及び第2のダミーゲート電極を形成する工程(a1)と、前記第1のダミーゲート電極及び前記第2のダミーゲート電極を覆うように、前記半導体基板における前記第1の領域及び前記第2の領域のそれぞれの上に層間絶縁膜を形成し、その後、前記第1のダミーゲート電極及び前記第2のダミーゲート電極のそれぞれの頂部が露出するように、前記層間絶縁膜を薄くする工程(a2)と、前記第1のダミーゲート電極及び前記第2のダミーゲート電極を除去して、前記第1のゲート溝及び前記第2のゲート溝を形成する工程(a3)とを含んでいてもよい。ここで、前記ゲート絶縁膜及び前記保護膜は、前記工程(a)の後に、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように形成されてもよい。或いは、前記ゲート絶縁膜及び前記保護膜は、前記工程(a)の前に、前記第1のゲート溝の底面となる部分の前記半導体基板の上及び前記第2のゲート溝の底面となる部分の前記半導体基板の上にそれぞれ形成され、前記工程(a1)では、前記第1の領域及び前記第2の領域のそれぞれの上に、前記ゲート絶縁膜及び前記保護膜を介して、前記第1のダミーゲート電極及び前記第2のダミーゲート電極が形成されてもよい。

【発明の効果】

【0022】

本発明によると、各トランジスタ領域上におけるゲート溝の形成に際し、ダミーゲート電極の除去を同時に行うことによって、言い換えると、ダミーゲート電極の除去工程を1回だけ実施することによって、ゲートラストプロセスの工程数を削減することができ、それにより、製造コスト及び歩留まり等を改善することができる。

【0023】

また、本発明によると、ゲート絶縁膜と各トランジスタの仕事関数調整用メタル材料(つまり第1の金属含有膜及び第2の金属含有膜)との間に保護膜が形成されているため、保護膜を仕事関数調整用メタル材料の拡散緩衝層として、ゲート絶縁膜と各トランジスタの仕事関数調整用メタル材料とを分離し、それにより、両者の間の相互拡散を制御することができる。また、第2のゲート溝内の仕事関数調整用メタル材料(つまり第1の金属含有膜)を選択的に除去する際に、ゲート絶縁膜がエッチャントに直接さらされてダメージが生じる事態を阻止することが可能となる。従って、前述の相互拡散やダメージに起因する閾値電圧制御の不良、デバイス信頼性やトランジスタ特性等の劣化を防止することができる。

【0024】

さらに、本発明によると、ゲート絶縁膜と各トランジスタの仕事関数調整用メタル材料との間に保護膜を挿入することによって、ゲート絶縁膜中への仕事関数調整用メタル材料の拡散を制御することが可能となるだけではなく、第2のゲート溝内の仕事関数調整用メタル材料(つまり第1の金属含有膜)を選択的に除去する際に、保護膜上部を同時に除去することによって、次のような効果も得ることができる。すなわち、保護膜上部に拡散した又は打ち込まれた仕事関数調整用メタル材料を除去することができるので、メタル材料の残留に起因する仕事関数の劣化及び閾値電圧の劣化を防止することが可能となる。

【図面の簡単な説明】

【0025】

【図1】図1は、第1の実施形態に係る半導体装置の平面図である。

【図2】図2(a)及び(b)はそれぞれ、図1に示すAーA’線及びB−B’線における断面図である。

【図3】図3(a)及び(b)はそれぞれ、図1に示すC−C’線及びD−D’線における断面図である。

【図4】図4(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図4(a)は、図1に示すC−C’線における断面図であり、図4(b)は、図1に示すD−D’線における断面図である。

【図5】図5(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図5(a)は、図1に示すC−C’線における断面図であり、図5(b)は、図1に示すD−D’線における断面図である。

【図6】図6(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図6(a)は、図1に示すC−C’線における断面図であり、図6(b)は、図1に示すD−D’線における断面図である。

【図7】図7(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図7(a)は、図1に示すC−C’線における断面図であり、図7(b)は、図1に示すD−D’線における断面図である。

【図8】図8(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図8(a)は、図1に示すC−C’線における断面図であり、図8(b)は、図1に示すD−D’線における断面図である。

【図9】図9(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図9(a)は、図1に示すC−C’線における断面図であり、図9(b)は、図1に示すD−D’線における断面図である。

【図10】図10(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図10(a)は、図1に示すC−C’線における断面図であり、図10(b)は、図1に示すD−D’線における断面図である。

【図11】図11(a)及び(b)は、第1の実施形態に係る半導体装置の一工程を示す断面図であり、図11(a)は、図1に示すC−C’線における断面図であり、図11(b)は、図1に示すD−D’線における断面図である。

【図12】図12(a)及び(b)は、第1の実施形態に係る半導体装置の各工程を示す断面図(図1に示すA−A’線における断面図)である。

【図13】図13(a)及び(b)は、第1の実施形態に係る半導体装置の各工程を示す断面図(図1に示すA−A’線における断面図)である。

【図14】図14は、第2の実施形態に係る半導体装置の平面図である。

【図15】図15(a)及び(b)はそれぞれ、図14に示すAーA’線及びB−B’線における断面図である。

【図16】図16(a)及び(b)はそれぞれ、図14に示すC−C’線及びD−D’線における断面図である。

【図17】図17(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図17(a)は、図14に示すC−C’線における断面図であり、図17(b)は、図14に示すD−D’線における断面図である。

【図18】図18(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図18(a)は、図14に示すC−C’線における断面図であり、図18(b)は、図14に示すD−D’線における断面図である。

【図19】図19(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図19(a)は、図14に示すC−C’線における断面図であり、図19(b)は、図14に示すD−D’線における断面図である。

【図20】図20(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図20(a)は、図14に示すC−C’線における断面図であり、図20(b)は、図14に示すD−D’線における断面図である。

【図21】図21(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図21(a)は、図14に示すC−C’線における断面図であり、図21(b)は、図14に示すD−D’線における断面図である。

【図22】図22(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図22(a)は、図14に示すC−C’線における断面図であり、図22(b)は、図14に示すD−D’線における断面図である。

【図23】図23(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図23(a)は、図14に示すC−C’線における断面図であり、図23(b)は、図14に示すD−D’線における断面図である。

【図24】図24(a)及び(b)は、第2の実施形態に係る半導体装置の一工程を示す断面図であり、図24(a)は、図14に示すC−C’線における断面図であり、図24(b)は、図14に示すD−D’線における断面図である。

【図25】図25(a)及び(b)は、第2の実施形態に係る半導体装置の各工程を示す断面図(図14に示すA−A’線における断面図)である。

【図26】図26(a)及び(b)は、第2の実施形態に係る半導体装置の各工程を示す断面図(図14に示すA−A’線における断面図)である。

【発明を実施するための形態】

【0026】

以下、本発明の実施形態を図面に基づいて詳細に説明する。尚、本発明は、以下に示す実施形態に限定されない。例えば、構成材料は以下に示す材料に限定されず、膜厚及び濃度などもそれぞれ以下に示す数値に限定されず、成膜方法及びエッチング方法なども以下に示す方法に限定されない。また、各図面においては、同一の部材に対して同一の符号を付け、説明を省略する場合がある。

【0027】

(第1の実施形態)

まず、第1の実施形態に係る半導体装置の構造について、図1、図2(a)、(b)及び図3(a)、(b)を参照しながら説明する。図1は、本実施形態に係る半導体装置の平面図である。図2(a)、(b)及び図3(a)、(b)は、それぞれ、図1に示すAーA’線、B−B’線、C−C’線及びD−D’線における断面図である。尚、図1、図2(a)、(b)及び図3(a)、(b)において、「NMIS」とは、N型MISトランジスタ(NMISFET)が形成されるN型MISトランジスタ形成領域を示し、「PMIS」とは、P型MISトランジスタ(PMISFET)が形成されるP型MISトランジスタ形成領域を示している。また、図1では、シリサイド層20、応力絶縁膜21及び層間絶縁膜22の図示を省略している。

【0028】

図1及び図2(a)、(b)及び図3(a)、(b)に示すように、例えばシリコンからなる半導体基板10の上部(半導体領域)に、N型MISトランジスタ形成領域とP型MISトランジスタ形成領域とを区画するように素子分離領域11が形成されている。N型MISトランジスタ形成領域の半導体基板10の上部にはp型ウェル領域12aが形成されていると共に、P型MISトランジスタ形成領域の半導体基板10の上部にはn型ウェル領域12bが形成されている。ここで、p型ウェル領域12aのうち素子分離領域11に囲まれている部分が活性領域10aとなり、n型ウェル領域12bのうち素子分離領域11に囲まれている部分が活性領域10bとなる。図1及び図2(a)に示すように、活性領域10aと活性領域10bとは素子分離領域11を挟んでチャネル幅方向(ゲート幅方向)に並んで配置されている。本実施形態に係る半導体装置では、活性領域10a上にN型MISトランジスタが形成されており、活性領域10b上にP型MISトランジスタが形成されている。

【0029】

N型MISトランジスタの構成は、以下に示す通りである。図3(a)に示すように、活性領域10a上に、絶縁膜111を底部とし且つ内側サイドウォールスペーサ14を側壁部とするゲート溝が設けられており、内側サイドウォールスペーサ14における当該ゲート溝の反対側には外側サイドウォールスペーサ16が設けられている。ここで、外側サイドウォールスペーサ16と活性領域10aとの間には下敷き絶縁膜15が設けられている。前記ゲート溝の底面(つまり絶縁膜111)及び側壁面(つまり内側サイドウォールスペーサ14)を覆うように高誘電率絶縁膜112が設けられている。また、前記ゲート溝内における高誘電率絶縁膜112により形成される凹部の底面及び側壁面を覆うように保護膜113が形成されており、前記ゲート溝内における保護膜113により形成される凹部の底面及び側壁面を覆うように、N型MISトランジスタの仕事関数調整用メタル電極膜(以下、Nchメタル電極膜)114aが形成されている。さらに、前記ゲート溝内におけるNchメタル電極膜114aにより形成される凹部の底面及び側壁面を覆うように、P型MISトランジスタの仕事関数調整用メタル電極膜(以下、Pchメタル電極膜)114bが形成されており、前記ゲート溝内におけるPchメタル電極膜114bにより形成される凹部を埋め込むように、導電性埋め込み膜115が埋め込まれている。

【0030】

すなわち、本実施形態に係る半導体装置のN型MISトランジスタでは、活性領域10a上のゲート溝内に、絶縁膜111及び高誘電率絶縁膜112からなるゲート絶縁膜を挟んで、保護膜113、Nchメタル電極膜114a、Pchメタル電極膜114b及び導電性埋め込み膜115からなるゲート電極が形成されている。

【0031】

また、活性領域10aにおける前記ゲート電極の両側方下には、n型エクステンション領域13aが形成されており、活性領域10aにおける前記ゲート電極から見て内側サイドウォールスペーサ14の両側方下には、n型ソース/ドレイン領域17aが形成されている。ここで、n型ソース/ドレイン領域17aの方がn型エクステンション領域13aよりも接合深さが深い。また、下敷き絶縁膜15の外側のn型ソース/ドレイン領域17aの上面上にはシリサイド層20が設けられている。

【0032】

尚、絶縁膜111は、例えば厚さ0.8nm程度のシリコン酸化膜からなり、高誘電率絶縁膜112は、例えば厚さ2nm〜4nm程度のHfO2 膜からなる。また、保護膜113は、金属、金属酸化物又は金属窒化物からなり、例えば2nm〜5nm程度の厚さを有する。また、内側サイドウォールスペーサ14は、例えばシリコン窒化膜からなり、外側サイドウォールスペーサ16も、例えばシリコン窒化膜からなり、下敷き絶縁膜15は、例えばシリコン酸化膜からなる。n型エクステンション領域13a及びn型ソース/ドレイン領域17aのそれぞれには、例えばヒ素等のn型不純物が注入されている。シリサイド層20は、例えばCoSi、NiSi又はNiPtSiからなり、例えば5nm〜20nm程度の厚さを有する。

【0033】

P型MISトランジスタの構成は、以下に示す通りである。図3(b)に示すように、活性領域10b上に、絶縁膜111を底部とし且つ内側サイドウォールスペーサ14を側壁部とするゲート溝が設けられており、内側サイドウォールスペーサ14における当該ゲート溝の反対側には外側サイドウォールスペーサ16が設けられている。ここで、外側サイドウォールスペーサ16と活性領域10aとの間には下敷き絶縁膜15が設けられている。前記ゲート溝の底面(つまり絶縁膜111)及び側壁面(つまり内側サイドウォールスペーサ14)を覆うように高誘電率絶縁膜112が設けられている。また、前記ゲート溝内における高誘電率絶縁膜112により形成される凹部の底面及び側壁面を覆うように保護膜113が形成されており、前記ゲート溝内における保護膜113により形成される凹部の底面及び側壁面を覆うように、Pchメタル電極膜114bが形成されている。さらに、前記ゲート溝内におけるPchメタル電極膜114bにより形成される凹部を埋め込むように、導電性埋め込み膜115が埋め込まれている。

【0034】

すなわち、本実施形態に係る半導体装置のP型MISトランジスタでは、活性領域10b上のゲート溝内に、絶縁膜111及び高誘電率絶縁膜112からなるゲート絶縁膜を挟んで、保護膜113、Pchメタル電極膜114b及び導電性埋め込み膜115からなるゲート電極が形成されている。ここで、P型MISトランジスタのゲート電極に含まれる保護膜113は、N型MISトランジスタのゲート電極に含まれる保護膜113よりも例えば1nm〜3nm程度薄くなっている。

【0035】

また、活性領域10bにおける前記ゲート電極の両側方下には、p型エクステンション領域13bが形成されており、活性領域10bにおける前記ゲート電極から見て内側サイドウォールスペーサ14の両側方下には、p型ソース/ドレイン領域17bが形成されている。ここで、p型ソース/ドレイン領域17bの方がp型エクステンション領域13bよりも接合深さが深い。また、p型エクステンション領域13b及びp型ソース/ドレイン領域17bのそれぞれには、例えばボロン等のp型不純物が注入されている。さらに、p型ソース/ドレイン領域17bの上にはシリコンゲルマニウム層18が形成されている。シリコンゲルマニウム層18は、シリコンよりも大きい格子定数を有するシリコン混晶(例えばSiGe)からなり、圧縮応力(第1の応力)をゲート長方向及びゲート幅方向に生じさせる。また、このシリコンゲルマニウム層18は、例えば60nm程度の厚さを有しており、原子比でシリコンに対して例えば20%〜30%程度のGeを含有している。このシリコンゲルマニウム層18にも、ボロン等のp型不純物が注入されている。すなわち、シリコンゲルマニウム層18におけるp型不純物の濃度は、p型ソース/ドレイン領域17bにおけるp型不純物の濃度と同一であることが好ましい。このように、p型ソース/ドレイン領域17b内にシリコンゲルマニウム層18が形成されているので、P型MISトランジスタのチャネル領域におけるゲート長方向に圧縮応力が印加される。その結果、P型MISトランジスタにおけるキャリア移動度(正孔の移動度)の向上を図ることができる。さらに、シリコンゲルマニウム層18の上にはシリコンエピタキシャル層19が形成されており、下敷き絶縁膜15の外側のシリコンエピタキシャル層19の上面上にはシリサイド層20が設けられている。これにより、シリサイド拡散不良やゲルマニウム汚染等の影響が後工程に出ないように配慮されている。従って、本実施形態では、PMISトランジスタの電流駆動能力を向上させることができる。

【0036】

尚、シリコンゲルマニウム層18は、p型ソース/ドレイン領域17b上のみに形成されており、n型ソース/ドレイン領域17a上には形成されていない。

【0037】

また、P型MISトランジスタ形成領域に設けられている絶縁膜111、高誘電率絶縁膜112、保護膜113、Pchメタル電極膜114b、導電性埋め込み膜115、内側サイドウォールスペーサ14、外側サイドウォールスペーサ16、下敷き絶縁膜15及びシリサイド層20のそれぞれの材料は、N型MISトランジスタ形成領域に設けられている絶縁膜111、高誘電率絶縁膜112、保護膜113、Pchメタル電極膜114b、導電性埋め込み膜115、内側サイドウォールスペーサ14、外側サイドウォールスペーサ16、下敷き絶縁膜15及びシリサイド層20のそれぞれの材料と同じである。

【0038】

また、図2(b)及び図3(a)、(b)に示すように、各トランジスタのゲート電極頂部が露出するように、半導体基板10上には応力絶縁膜21を介して層間絶縁膜22が形成されている。

【0039】

また、図1及び図2(a)に示すように、各トランジスタのゲート電極(つまりゲート溝)は、活性領域10aと活性領域10bとの間の素子分離領域11上で接続しており、素子分離領域11上に位置する部分の保護膜113には段差が形成されている。

【0040】

以上に説明したように、本実施形態の半導体装置においてはリプレースメントゲート構造を用いており、N型MISトランジスタのゲート電極は、保護膜113の直上にNchメタル電極膜114aが形成され且つNchメタル電極膜114aの直上にPchメタル電極膜114bが形成された構造を有し、P型MISトランジスタのゲート電極は、保護膜113の直上にPchメタル電極膜114bが形成された構造を有している。

【0041】

従って、後述するように、各トランジスタ領域上におけるゲート溝の形成に際し、ダミーゲート電極の除去を同時に行うことによって、言い換えると、ダミーゲート電極の除去工程を1回だけ実施することによって、ゲートラストプロセスの工程数を削減することができ、それにより、製造コスト及び歩留まり等を改善することができる。

【0042】

また、本実施形態によると、ゲート絶縁膜と各トランジスタの仕事関数調整用メタル材料(つまりNchメタル電極膜114a及びPchメタル電極膜114b)との間に保護膜113が形成されているため、保護膜113を仕事関数調整用メタル材料の拡散緩衝層として、ゲート絶縁膜と各トランジスタの仕事関数調整用メタル材料とを分離し、それにより、両者の間の相互拡散を制御することができる。また、後述するように、P型MISトランジスタ領域のゲート溝内の仕事関数調整用メタル材料(つまりNchメタル電極膜114a)を選択的に除去する際に、ゲート絶縁膜がエッチャントに直接さらされてダメージが生じる事態を阻止することが可能となる。従って、前述の相互拡散やダメージに起因する閾値電圧制御の不良、デバイス信頼性やトランジスタ特性等の劣化を防止することができる。

【0043】

さらに、本実施形態によると、ゲート絶縁膜と各トランジスタの仕事関数調整用メタル材料との間に保護膜113を挿入することによって、ゲート絶縁膜中への仕事関数調整用メタル材料の拡散を制御することが可能となるだけではなく、後述するように、P型MISトランジスタ領域のゲート溝内の仕事関数調整用メタル材料(つまりNchメタル電極膜114a)を選択的に除去する際に、保護膜113上部を同時に除去することによって、次のような効果も得ることができる。すなわち、保護膜113上部に拡散した又は打ち込まれた仕事関数調整用メタル材料を除去することができるので、メタル材料の残留に起因する仕事関数の劣化及び閾値電圧の劣化を防止することが可能となる。

【0044】

以上のように、本実施形態によると、N型MISトランジスタ及びP型MISトランジスタのそれぞれの製造時の歩留まりを改善しつつ、N型MISトランジスタ及びP型MISトランジスタのそれぞれの低閾値電圧動作を可能とすることができる。

【0045】

以下、本実施形態に係る半導体装置の製造方法について、図面を参照しながら説明する。図4(a)、(b)、図5(a)、(b)、図6(a)、(b)、図7(a)、(b)、図8(a)、(b)、図9(a)、(b)、図10(a)、(b)及び図11(a)、(b)は、本実施形態に係る半導体装置の製造方法を工程順に示す断面図である。尚、図4(a)、図5(a)、図6(a)、図7(a)、図8(a)、図9(a)、図10(a)及び図11(a)は、図1に示すC−C’線における断面図であり、図4(b)、図5(b)、図6(b)、図7(b)、図8(b)、図9(b)、図10(b)及び図11(b)は、図1に示すD−D’線における断面図である。また、図4(a)、(b)、図5(a)、(b)、図6(a)、(b)、図7(a)、(b)、図8(a)、(b)、図9(a)、(b)、図10(a)、(b)及び図11(a)、(b)において、「NMIS」とは、N型MISトランジスタ(NMISFET)が形成されるN型MISトランジスタ形成領域を示し、「PMIS」とは、P型MISトランジスタ(PMISFET)が形成されるP型MISトランジスタ形成領域を示している。

【0046】

まず、図4(a)及び(b)に示すように、例えばシリコンからなる半導体基板10の上部(半導体領域)に、N型MISトランジスタ形成領域とP型MISトランジスタ形成領域とを区画するように素子分離領域11を形成する。続いて、N型MISトランジスタ形成領域の半導体基板10の上部にp型ウェル領域12aを形成すると共に、P型MISトランジスタ形成領域の半導体基板10の上部にn型ウェル領域12bを形成する。ここで、p型ウェル領域12aのうち素子分離領域11に囲まれている部分が活性領域10aとなり、n型ウェル領域12bのうち素子分離領域11に囲まれている部分が活性領域10bとなる。

【0047】

次に、図5(a)及び(b)に示すように、半導体基板10の表面全体に対して、例えばケミカル酸化処理を行って、ダミー界面シリコン酸化膜101を形成する。ケミカル酸化は、例えば、一般的に用いられている、塩酸(HCl)及び過酸化水素水(H2 O2 )の混合溶液、又は硫酸(H2 SO4 )及び過酸化水素水(H2 O2 )の混合溶液等により半導体基板10を処理することにより行ってもよい。ここで、ダミー界面シリコン酸化膜101として、光学膜厚が例えば1nm〜5nm程度のドライ酸化膜又はラジカル酸化膜等を用いることもできる。ラジカル酸化膜は、例えば、水素(H2 )と酸素(O2 )又は一酸化二窒素(N2 O)との混合ガス雰囲気中で600℃〜850℃程度の温度の熱処理を行うことにより形成してもよい。

【0048】

続いて、図5(a)及び(b)に示すように、ダミー界面シリコン酸化膜101上に、例えばCVD法等により、ダミーゲート電極として、例えば膜厚50nm〜100nm程度のポリシリコン膜102を堆積する。ここで、ポリシリコン膜102には不純物をドープする必要はない。逆に、ポリシリコン膜102に砒素等の不純物を高濃度でドープした場合、後工程のダミーゲート電極除去時に除去性が低下する等の悪影響が考えられるため、ポリシリコン膜102は、通常のノンドープポリシリコン膜でよい。その後、ポリシリコン膜102上に、例えばCVD法等により、例えば膜厚10nm〜50nm程度の酸化シリコン(SiO2 )からなるハードマスク膜103を形成する。

【0049】

次に、公知のリソグラフィ法及びエッチング法により、成膜したハードマスク膜103、ポリシリコン膜102及びダミー界面シリコン酸化膜101に対してゲートエッチングを行う。これにより、図5(a)及び(b)に示すように、活性領域10a及び10bのそれぞれの上に、ダミーゲート電極及びダミーゲート絶縁膜からなるダミーゲートスタック構造が形成される。

【0050】

続いて、図6(a)及び(b)に示すように、半導体基板10の表面全面の上並びに各ダミーゲートスタック構造の上面及び側面の上に、例えばALD法により、例えば膜厚5nm〜10nm程度のシリコン窒化(ALD−SiN)膜を成膜する。その後、成膜したシリコン窒化膜に対してエッチバックを行って、シリコン窒化膜における各ダミーゲートスタック構造の両側面上を除く部分を除去することにより、各ダミーゲートスタック構造の両側面上に内側サイドウォールスペーサ14を形成する。

【0051】

次に、図6(a)及び(b)に示すように、公知の方法により、活性領域10bをマスクした状態で、活性領域10a(p型ウェル領域12a)に、ダミーゲートスタック構造及び内側サイドウォールスペーサ14をマスクとしてn型ドーパントを注入することにより、接合深さが比較的浅いn型エクステンション領域13aを形成する。その後、活性領域10aをマスクした状態で、活性領域10b(n型ウェル領域12b)に、ダミーゲートスタック構造及び内側サイドウォールスペーサ14をマスクとしてp型ドーパントを注入することにより、接合深さが比較的浅いp型エクステンション領域13bを形成する。

【0052】

続いて、図6(a)及び(b)に示すように、各ダミーゲートスタック構造の両側面上に内側サイドウォールスペーサ14を挟んでサイドウォール構造を形成する。具体的には、半導体基板10上の全面に、内側サイドウォールスペーサ14を含む各ダミーゲートスタック構造を覆うように、例えばCVD法又はALD法を用いて、下敷き絶縁膜15を成膜した後、下敷き絶縁膜15上にシリコン窒化膜を成膜し、その後、エッチバックを行うことによって、各ダミーゲートスタック構造の両側面上に内側サイドウォールスペーサ14を挟んで外側サイドウォールスペーサ16を形成する。ここで、外側サイドウォールスペーサ16と活性領域10aとの間には下敷き絶縁膜15が介在する。

【0053】

続いて、図6(a)及び(b)に示すように、活性領域10bをマスクした状態で、活性領域10a(p型ウェル領域12a)に、ダミーゲートスタック構造、内側サイドウォールスペーサ14及び外側サイドウォールスペーサ16をマスクとして、n型ドーパントを注入することにより、n型エクステンション領域13aよりも接合深さが深いn型ソース/ドレイン領域17aを形成する。その後、活性領域10aをマスクした状態で、活性領域10b(n型ウェル領域12b)に、ダミーゲートスタック構造、内側サイドウォールスペーサ14及び外側サイドウォールスペーサ16をマスクとして、p型ドーパントを注入することにより、p型エクステンション領域13bよりも接合深さが深いp型ソース/ドレイン領域17bを形成する。

【0054】

続いて、N型MISトランジスタ形成領域を覆うレジストマスク(図示省略未記載)と、P型MISトランジスタ形成領域におけるハードマスク膜103、内側サイドウォールスペーサ14及び外側サイドウォールスペーサ16とをエッチングマスクとし、例えばHBrをエッチングガスとして、p型ソース/ドレイン領域17bの上部に対してドライエッチングを行う。これにより、p型ソース/ドレイン領域17bの上部にリセス部(シリコン混晶部を形成するための凹部)が形成される。リセス部の深さは、例えば60nmである。その後、図6(b)に示すように、リセス部内にシリコンゲルマニウム層18をエピタキシャル成長により形成する。ここで、Siのソースガスとして、例えばシラン(SiH4 )又はジクロロシラン(SiH4 Cl2 )等を、Geのソースガスとして、例えばゲルマン(GeH4 )等を使用することができる。また、ボロンなどのp型不純物を注入しながら、シリコンゲルマニウム層18をエピタキシャル成長により形成してもよい。このように形成されたシリコンゲルマニウム層(シリコン混晶層)18は活性領域10bの一部分となる。また、シリコンゲルマニウム層18は例えば60nm程度の厚さを有し、シリコンゲルマニウム層18におけるGeの濃度は例えば20〜30原子%程度である。その後、図6(b)に示すように、シリコンゲルマニウム層18上に、シリサイド用カバー膜として、例えばシラン(SiH4 )又はジクロロシラン(SiH4 Cl2 )等を用いて、例えば10nm〜30nm程度のシリコンエピタキシャル層(シリコンキャップ層)19をエピタキシャル成長により選択的に形成する。その後、前述のN型MISトランジスタ形成領域を覆うレジストマスクを除去した後、半導体基板10に対して例えば1000℃程度のスパイクアニール処理を行う。この熱処理により、半導体基板10に注入されたn型不純物及びp型不純物がそれぞれ活性化される。

【0055】

続いて、例えばPVD(Physical Vapor Deposition )法又はCVD法等により、各ソース/ドレイン領域17a及び17bが形成された半導体基板10の上に全面にわたって、例えば、コバルト(Co)、タングステン(W)、プラチナ(Pt)又はニッケル(Ni)等からなる金属膜を堆積する。その後、所定の熱処理及び未反応金属膜の選択除去を行う。これによって、図6(a)及び(b)に示すように、n型ソース/ドレイン領域17aの上部及びp型ソース/ドレイン領域17b(正確にはシリコンエピタキシャル層20)の上部に、金属シリサイドであるシリサイド層20を形成する。

【0056】

次に、図7(a)及び(b)に示すように、例えばCVD法等により、N型MISトランジスタ形成領域及びP型MISトランジスタ形成領域のそれぞれを覆うように、例えば窒化シリコン(SiN)からなる応力絶縁膜21を成膜する。この応力絶縁膜21を設けることにより、各シリサイド層20の酸化が抑制されると共に、各トランジスタにおけるチャネル方向の歪み効果を生じさせることができる。

【0057】

尚、N型MISトランジスタ形成領域及びP型MISトランジスタ形成領域をそれぞれ個別にマスクすることにより、応力絶縁膜21として、N型MISトランジスタ形成領域には引張り応力を生じさせる効果を持つSiN膜を、P型MISトランジスタ形成領域には圧縮応力を生じさせる効果を持つSiNをそれぞれ個別に形成してもよい。

【0058】

次に、図7(a)及び(b)に示すように、各ダミーゲートスタック構造の間を埋め込むように、応力絶縁膜21上に例えばシリコン酸化膜からなる層間絶縁膜22を堆積する。ここで、各ダミーゲートスタック構造の間にボイドやシーム等の埋め込み不良が生じることを阻止しつつ、応力絶縁膜21からの窒素の脱離、シリサイド層20の構成材料のチャネル領域側への拡散、及び、ソース/ドレイン領域等の不純物深さ分布の劣化等を防止するために、低温且つ埋め込み性に優れた成膜方法、例えばALD法又はCVD法を用いて層間絶縁膜22を成膜してもよい。

【0059】

次に、例えばCMP法により、層間絶縁膜22に対して平坦化処理を行って、層間絶縁膜22の上部、応力絶縁膜21の一部、及び各ダミーゲートスタック構造のハードマスク膜103を除去することにより、各ダミーゲートスタック構造のポリシリコン膜(ダミーゲート電極膜)102を露出させる。次に、例えばウェットエッチング法により、各ダミーゲートスタック構造のポリシリコン膜102を除去する。このポリシリコン膜102が除去された結果、図7(a)及び(b)に示すように、活性領域10a上に、互いに対向する内側サイドウォールスペーサ14を側壁部とし且つ露出したダミー界面シリコン酸化膜101を底部とするゲート溝23aが形成されると共に、活性領域10b上に、互いに対向する内側サイドウォールスペーサ14を側壁部とし且つ露出したダミー界面シリコン酸化膜101を底部とするゲート溝23bが形成される。ここで、ダミーゲート電極であるポリシリコン膜102を除去する際には、エッチングダメージがなく且つ酸化シリコンとの選択性が高い溶液、例えば水酸化テトラメチルアンモニウム(TMAH:TetraMethyl Ammonium Hydroxide)溶液を用いてもよい。この場合、薬液温度が例えば50℃程度で、濃度(体積%濃度)が例えば3%〜5%程度の低濃度溶液を用いると、取り扱いが容易になる。続いて、各ゲート溝23a及び23bの底部のダミー界面シリコン酸化膜101を除去する。ここで、例えば、希釈フッ化水素酸、具体的には、濃度(体積%濃度)が例えば1%〜2%程度のフッ化水素酸を用いてダミー界面シリコン酸化膜101を除去してもよいが、外側サイドウォールスペーサ16下の下敷き絶縁膜15がエッチングされないように注意する必要がある。

【0060】

続いて、図8(a)及び(b)に示すように、各ゲート溝23a及び23bの底部に、例えば界面シリコン酸化膜からなる絶縁膜111を形成する。絶縁膜111としては、例えば、光学膜厚が0.5nm〜1nm程度のケミカル酸化膜、又は光学膜厚が0.5nm〜2.0nm程度のドライ酸化膜若しくはラジカル酸化膜等を用いてもよい。ケミカル酸化膜は、例えば、一般的に用いられている、塩酸(HCl)及び過酸化水素水(H2 O2 )の混合溶液、又は硫酸(H2 SO4 )及び過酸化水素水(H2 O2 )の混合溶液等により半導体基板10を処理することにより形成してもよい。また、O3 を混入させた純水に半導体基板10を曝すことによって、ケミカル酸化膜を形成してもよい。一方、ラジカル酸化膜は、水素(H2 )と酸素(O2 )又は一酸化二窒素(N2 O)との混合ガス雰囲気中で600℃〜850℃程度の温度の熱処理を行うことにより形成してもよい。

【0061】

続いて、図8(a)及び(b)に示すように、例えば原子層堆積(ALD)法により、各ゲート溝23a及び23における絶縁膜111の上面及び各ゲート溝23a及び23の両側壁面を覆うように、半導体基板10上の全面に高誘電率絶縁膜112を形成する。高誘電率膜112としては、例えば、ハフニウムシリケート(HfSiO)、窒素添加ハフニウムシリケート(HfSiON)、酸化ハフニウム(HfO)又は酸化ハフニウムジルコニウム(HfZrO)等のハフニウム(Hf)含有絶縁膜を用いることができる。また、ALD法を用いて高誘電率絶縁膜112を形成する場合、例えば、原料として、テトラキス(エチルメチルアミノ)ハフニウム(Hf[N(C2 H5 )CH3 ]4 )等のハフニウム(Hf)を含む有機系材料と、モノシラン(SiH4 )等のシリコン(Si)を含むガス又はトリス(ジメチルアミノ)シラン(SiH[N(CH3 )2 ]3 )等のシリコン(Si)を含む有機系材料とを用いて、250℃〜350℃程度の成膜温度で、短時間に且つ繰り返し堆積を行うと共に、1つの堆積から次の堆積までの間に余剰原料のパージを行いながら、酸素(O2 )ガス、オゾン(O3 )ガス又は水蒸気(H2 O)等を用いて堆積膜の酸化を行ってもよい。尚、Hf含有原料として、有機系材料に代えて、塩化ハフニウム(HfCl4 )又は塩化ジルコニウム(ZrCl4 )等の無機系材料を用いてもよい。また、高誘電率絶縁膜112の膜厚を、例えばEOT(等価酸化膜厚)で0.5nm〜2.0nm程度とする場合には、高誘電率絶縁膜112と絶縁膜111とを合わせた物理膜厚を1nm〜3nm程度とすればよい。また、高誘電率絶縁膜112として、前述したように、酸化ジルコニウム(ZrO)を含むHf含有誘電体膜としてもよいし、又は、Hf含有誘電体膜に代えて、例えば、酸化ジルコニウム(ZrO)からなる単体の誘電率膜を用いてもよい。

【0062】

続いて、図8(a)及び(b)に示すように、各ゲート溝23a及び23の底面及び両側壁面を覆うように、高誘電率絶縁膜112の上に保護膜113を形成する。保護膜113は、後工程でP型MISトランジスタ形成領域上においてNchメタル電極膜を除去する際に、Nchメタル電極膜の構成材料がP型MISトランジスタ形成領域の高誘電率絶縁膜112中へ拡散することを防止するためのストッパー機能を有する。また、保護膜113は、Nchメタル電極膜の除去時に高誘電率絶縁膜112が薬液又はエッチャントに直接曝されてダメージを受けることを阻止するためのストッパー機能を有する。保護膜113の材料としては、例えば、窒化チタン、窒化ハフニウム、窒化タンタル若しくは窒化ニッケル等の金属窒化物を用いてもよい。保護膜113の膜厚(堆積時膜厚)は例えば2〜5nm程度であってもよい。また、保護膜113の成膜方法としては、例えばALD法又はPVD法のいずれを用いてもよい。

【0063】

続いて、図8(a)及び(b)に示すように、各ゲート溝23a及び23の底面及び両側壁面を覆うように、保護膜113上に、N型MISトランジスタの実効仕事関数の値をシフトさせるための仕事関数調整用メタル電極膜(Nchメタル電極膜)114aを形成する。Nchメタル電極膜114aの材料としては、N型MISトランジスタの仕事関数を持つ金属又は当該金属の化合物、例えば、金属アルミニウム、金属チタン、若しくはそれらの合金、窒化ハフニウム、炭化タンタル又はランタン酸化物等を用いてもよい。Nchメタル電極膜114aの膜厚(堆積時膜厚)は例えば1nm〜5nm程度であってもよい。また、Nchメタル電極膜114aの成膜方法としては、例えばALD法又はPVD法のいずれを用いてもよい。但し、Nchメタル電極膜114aについては、特に、短チャネル領域のしきい値劣化(つまり、チャネル長が短くなった場合の閾値電圧の劣化)を阻止する必要がある点、及び、各ゲート溝23a及び23の底面及び両側壁面を確実に被覆する必要がある点から、例えばALD法又は高指向性スパッタ法等による成膜方法を用いてもい。

【0064】

尚、Nchメタル電極膜114aの構成材料は、大気暴露やリソグラフィ工程等による酸化に起因して特性が容易に劣化する傾向があるので、Nchメタル電極膜114aの形成後に、保護膜113と同様の保護膜によってNchメタル電極膜114aを覆い、それによって、Nchメタル電極膜114aの酸化を防止して特性を安定化させてもよい。

【0065】

次に、図9(a)及び(b)に示すように、公知のリソグラフィ法を用いて、N型MISトランジスタ形成領域を覆うレジストパターン121を形成した後、レジストパターン121をマスクとして、P型MISトランジスタ形成領域に形成されたNchメタル電極膜114aの除去を行う。Nchメタル電極膜114aの除去には、ドライエッチング法又はウェットエッチング法のいずれの方法を用いてもよいが、エッチングダメージによって高誘電率絶縁膜112の信頼性を劣化させず、且つNchメタル電極膜114aを効率良く除去できる方法を用いることが望ましい。例えば、Nchメタル電極膜114aがAl、Ti又はTaを含む場合、硫酸(H2 SO4 )、過酸化水素(H2 O2 )、又は塩酸(HCl)と過酸化水素(H2 O2 )との混合薬液を用いてNchメタル電極膜114aを除去してもよい。

【0066】

図12(a)、(b)及び図13(a)、(b)は、本実施形態に係る半導体装置の製造方法のうち、図9(a)及び(b)に示す工程から図10(a)及び(b)に示す工程までの詳細を工程順に示す断面図(図1に示すA−A’線における断面図)である。図12(a)に示すように、N型MISトランジスタ形成領域を覆うレジストパターン121を形成した後、図12(b)に示すように、レジストパターン121をマスクとして、P型MISトランジスタ形成領域に形成されたNchメタル電極膜114aの除去を行う。このとき、P型MISトランジスタ形成領域において、Nchメタル電極膜114aの構成材料が拡散している保護膜113の上部も合わせて除去する。これにより、PN境界部(つまりN型MISトランジスタ形成領域とP型MISトランジスタ形成領域とを区画する素子分離領域11)上において保護膜113に段差が発生する。当該段差の大きさは、保護膜113の膜厚(堆積時膜厚)に依存するが、保護膜113の膜厚(堆積時膜厚)が例えば5nm程度である場合、1nm〜3nm程度となる。ここで、本実施形態は、P型MISトランジスタ形成領域において保護膜113を完全には除去しないことを特徴としている。また、P型MISトランジスタ形成領域においてNchメタル電極膜114aと共に保護膜113の上部を同時に除去することにより、P型MISトランジスタ形成領域においてNchメタル電極膜114aを完全に(つまり最大限に)除去することが可能となる。

【0067】

次に、図13(a)に示すように、レジストパターン121を除去した後、図10(a)、(b)及び図13(b)に示すように、各ゲート溝23a及び23bのそれぞれの底面及び側壁面を覆うように、ゲート溝23a内のNchメタル電極膜114aの上及びゲート溝23b内の保護膜113の上に、P型MISトランジスタの仕事関数調整用メタル電極膜(Pchメタル電極膜)114bを形成する。Pchメタル電極膜114bの材料としては、比較的高い仕事関数を持つ材料、例えば、窒化チタン、ルテニウム酸化物、又は白金若しくは金等の貴金属等を用いてもよい。Pchメタル電極膜114bの膜厚(堆積時膜厚)は例えば4nm〜10nm程度であってもよい。また、Pchメタル電極膜114bの成膜方法としては、PVD法の他、例えばALD法又はPVD法のいずれを用いてもよい。続いて、図10(a)、(b)及び図13(b)に示すように、各ゲート溝23a及び23bのそれぞれにおけるPchメタル電極膜114bにより形成される凹部が埋まるように、ゲート溝23a内のPchメタル電極膜114bの上及びゲート溝23b内のPchメタル電極膜114bの上に導電性の金属含有膜115を形成する。金属含有膜115の材料としては、例えば、タングステン(W)、アルミニウム(Al)、又は窒化チタン(TiN)等が適用可能である。また、各ゲート溝23a及び23b内でのシームやボイドの形成を抑制するために、例えば、金属含有膜115の成膜前に、金属含有膜115との親和性の高いシード層を形成しておき、その後、例えばALD法又は高温リフローを伴うPVD法のいずれかを用いて金属含有膜115を成膜することが望ましい。

【0068】

次に、図11(a)及び(b)に示すように、CMP法により、各ゲート溝23a及び23bの外側の金属含有膜115、Pchメタル電極膜114b、Nchメタル電極膜114a、保護膜113及び高誘電率絶縁膜112を研磨して除去すると共に、各ゲート溝23a及び23bに埋め込まれた前記の各膜の平坦化を行う。ここで、図11(a)及び(b)に示す研磨及び除去をCMP法のみを用いて実施すると、幅広パターンを有する各ゲート溝23a及び23bに形成されたゲート電極の上面高さが弧状に変化するように研磨される、いわゆるディッシングが問題になる場合がある。その場合には、CMP法とドライエッチングによるエッチバックとを組み合わせて前記の各膜を除去してもよい。

【0069】

その後、図示は省略しているが、n型ソース/ドレイン領域17a及びp型ソース/ドレイン領域17b(正確には各ソース/ドレイン領域上のシリサイド層20)、並びに各ゲート溝23a及び23bに埋め込まれたリプレースメントゲート電極のそれぞれに電気的に接続するコンタクト及び配線の形成を行うことにより、半導体装置を完成させる。

【0070】

(第2の実施形態)

まず、第2の実施形態に係る半導体装置の構造について、図14、図15(a)、(b)及び図16(a)、(b)を参照しながら説明する。図14は、本実施形態に係る半導体装置の平面図である。図15(a)、(b)及び図16(a)、(b)は、それぞれ、図14に示すAーA’線、B−B’線、C−C’線及びD−D’線における断面図である。尚、図14、図15(a)、(b)及び図16(a)、(b)において、図1、図2(a)、(b)及び図3(a)、(b)に示す第1の実施形態に係る半導体装置と同じ構成要素には同じ符号を付すことにより、重複する説明を省略する。また、図14、図15(a)、(b)及び図16(a)、(b)において、「NMIS」とは、N型MISトランジスタ(NMISFET)が形成されるN型MISトランジスタ形成領域を示し、「PMIS」とは、P型MISトランジスタ(PMISFET)が形成されるP型MISトランジスタ形成領域を示している。また、図14では、シリサイド層20、応力絶縁膜21及び層間絶縁膜22の図示を省略している。

【0071】

図14、図15(a)、(b)及び図16(a)、(b)に示すように、本実施形態に係る半導体装置が第1の実施形態と異なっている点は、活性領域10a及び10bのそれぞれの上における絶縁膜111を底部とし且つ内側サイドウォールスペーサ14を側壁部とするゲート溝の側壁面上には、高誘電率絶縁膜112及び保護膜113が形成されていないことである。

【0072】

このような本実施形態に係る半導体装置によっても、第1の実施形態と同様の効果を得ることができる。

【0073】

また、本実施形態に係る半導体装置を製造する方法が第1の実施形態と異なっている点は、ダミーゲート電極形成前に、絶縁膜(界面シリコン酸化膜)111、高誘電率絶縁膜112、及び、ダミーゲート電極除去時のエッチングストップ層として機能する保護膜(金属含有層)113の形成を行うことである。

【0074】

以下、本実施形態に係る半導体装置の製造方法について、図面を参照しながら詳細に説明する。図17(a)、(b)、図18(a)、(b)、図19(a)、(b)、図20(a)、(b)、図21(a)、(b)、図22(a)、(b)、図23(a)、(b)及び図24(a)、(b)は、本実施形態に係る半導体装置の製造方法を工程順に示す断面図である。尚、図17(a)、図18(a)、図19(a)、図20(a)、図21(a)、図22(a)、図23(a)及び図24(a)は、図14に示すC−C’線における断面図であり、図17(b)、図18(b)、図19(b)、図20(b)、図21(b)、図22(b)、図23(b)及び図24(b)は、図14に示すD−D’線における断面図である。また、図17(a)、(b)、図18(a)、(b)、図19(a)、(b)、図20(a)、(b)、図21(a)、(b)、図22(a)、(b)、図23(a)、(b)及び図24(a)、(b)において、「NMIS」とは、N型MISトランジスタ(NMISFET)が形成されるN型MISトランジスタ形成領域を示し、「PMIS」とは、P型MISトランジスタ(PMISFET)が形成されるP型MISトランジスタ形成領域を示している。

【0075】

まず、第1の実施形態の図4(a)及び(b)に示す工程と同様に、図17(a)及び(b)に示すように、例えばシリコンからなる半導体基板10の上部(半導体領域)に、N型MISトランジスタ形成領域とP型MISトランジスタ形成領域とを区画するように素子分離領域11を形成する。続いて、N型MISトランジスタ形成領域の半導体基板10の上部にp型ウェル領域12aを形成すると共に、P型MISトランジスタ形成領域の半導体基板10の上部にn型ウェル領域12bを形成する。ここで、p型ウェル領域12aのうち素子分離領域11に囲まれている部分が活性領域10aとなり、n型ウェル領域12bのうち素子分離領域11に囲まれている部分が活性領域10bとなる。

【0076】

次に、図18(a)及び(b)に示すように、半導体基板10に対して、例えばウェット処理を行うことにより、半導体基板10の表面上に、例えば厚さ1nm以下の薄い界面シリコン酸化膜からなる絶縁膜111を形成する。ウェット処理においては、例えば、塩酸(HCl)と過酸化水素(H2 O2 )との混合液であるHPM(Hydrochloric acid-Hydrogen Peroxide Mixture )溶液、又はオゾン(O3 )水等を用いてもよい。また必要に応じて、酸素(O2 )と水素(H2 )との混合ガス雰囲気中又は一酸化二窒素(N2 O)と水素(H2 )との混合ガス雰囲気中で低温RTP(Rapid Thermal Process )プロセスを行うことによって、絶縁膜111となる界面シリコン酸化膜を形成してもよい。

【0077】

次に、図18(a)及び(b)に示すように、例えばALD法により、絶縁膜111上に高誘電率絶縁膜112を形成する。高誘電率絶縁膜112の具体的な形成方法は、第1の実施形態の図8(a)及び(b)に示す工程における高誘電率絶縁膜112の形成方法と同様である。

【0078】

次に、図18(a)及び(b)に示すように、高誘電率絶縁膜112の上に、例えば厚さ2nm〜5nm程度の保護膜113を形成する。保護膜113は、後工程でダミーゲート電極を除去する際、及び、後工程でP型MISトランジスタ形成領域上においてNchメタル電極膜を除去する際に、高誘電率絶縁膜112がエッチングされることを防止するエッチングストップ層として機能する。保護膜113の材料としては、例えば、窒化チタン、窒化ハフニウム、窒化タンタル若しくは窒化ニッケル等の金属窒化物を用いてもよい。また、保護膜113の成膜方法としては、例えばALD法又はPVD法のいずれを用いてもよい。

【0079】

次に、図18(a)及び(b)に示すように、保護膜113上に、例えばCVD法等により、ダミーゲート電極として、例えば膜厚50nm〜100nm程度のポリシリコン膜102を堆積する。ここで、ポリシリコン膜102には不純物をドープする必要はない。逆に、ポリシリコン膜102に砒素等の不純物を高濃度でドープした場合、後工程のダミーゲート電極除去時に除去性が低下する等の悪影響が考えられるため、ポリシリコン膜102は、通常のノンドープポリシリコン膜でよい。その後、ポリシリコン膜102上に、例えばCVD法等により、例えば膜厚10nm〜50nm程度の酸化シリコン(SiO2 )からなるハードマスク膜103を形成する。

【0080】

次に、公知のリソグラフィ法及びエッチング法により、成膜したハードマスク膜103、ポリシリコン膜102、保護膜113、高誘電率絶縁膜112及び絶縁膜111に対してゲートエッチングを行う。これにより、図18(a)及び(b)に示すように、活性領域10a及び10bのそれぞれの上に、絶縁膜111及び高誘電率絶縁膜112からなるゲート絶縁膜並びに保護膜113を介して、ダミーゲート電極が形成される。

【0081】

次に、第1の実施形態の図6(a)、(b)及び図7(a)、(b)に示す工程と同様に、図19(a)及び(b)に示すように、内側サイドウォールスペーサ14、n型エクステンション領域13a、p型エクステンション領域13b、下敷き絶縁膜15、外側サイドウォールスペーサ16、n型ソース/ドレイン領域17a、p型ソース/ドレイン領域17b、シリコンゲルマニウム層18、シリコンエピタキシャル層(シリコンキャップ層)19、シリサイド層20、応力絶縁膜21及び層間絶縁膜22を形成した後、層間絶縁膜22に対して平坦化処理を行って、各ダミーゲートスタック構造のポリシリコン膜(ダミーゲート電極膜)102を露出させる。

【0082】

次に、図20(a)及び(b)に示すように、例えばTMAH溶液を用いたウェットエッチング法により、各ダミーゲートスタック構造のポリシリコン膜102を除去する。このポリシリコン膜102が除去された結果、図20(a)及び(b)に示すように、活性領域10a上に、互いに対向する内側サイドウォールスペーサ14を側壁部とし且つ露出した保護膜113を底部とするゲート溝23aが形成されると共に、活性領域10b上に、互いに対向する内側サイドウォールスペーサ14を側壁部とし且つ露出した保護膜113を底部とするゲート溝23bが形成される。

【0083】

次に、各ゲート溝23a及び23b内の保護膜113表面の残留酸化物の除去を行った後、図21(a)及び(b)に示すように、各ゲート溝23a及び23の底面及び両側壁面を覆うように、保護膜113上に、N型MISトランジスタの実効仕事関数の値をシフトさせるための仕事関数調整用メタル電極膜(Nchメタル電極膜)114aを形成する。Nchメタル電極膜114aの材料、膜厚及び成膜方法は、第1の実施形態の場合と同様である。

【0084】

次に、図22(a)及び(b)に示すように、公知のリソグラフィ法を用いて、N型MISトランジスタ形成領域を覆うレジストパターン121を形成した後、レジストパターン121をマスクとして、P型MISトランジスタ形成領域に形成されたNchメタル電極膜114aの除去を行う。Nchメタル電極膜114aの除去方法は、第1の実施形態の場合と同様である。

【0085】

図25(a)、(b)及び図26(a)、(b)は、本実施形態に係る半導体装置の製造方法のうち、図22(a)及び(b)に示す工程から図23(a)及び(b)に示す工程までの詳細を工程順に示す断面図(図14に示すA−A’線における断面図)である。図25(a)に示すように、N型MISトランジスタ形成領域を覆うレジストパターン121を形成した後、図25(b)に示すように、レジストパターン121をマスクとして、P型MISトランジスタ形成領域に形成されたNchメタル電極膜114aの除去を行う。このとき、P型MISトランジスタ形成領域において、Nchメタル電極膜114aの構成材料が拡散している保護膜113の上部も合わせて除去する。これにより、PN境界部(つまりN型MISトランジスタ形成領域とP型MISトランジスタ形成領域とを区画する素子分離領域11)上において保護膜113に段差が発生する。当該段差の大きさは、保護膜113の膜厚(堆積時膜厚)に依存するが、保護膜113の膜厚(堆積時膜厚)が例えば5nm程度である場合、1nm〜3nm程度となる。ここで、本実施形態は、P型MISトランジスタ形成領域において保護膜113を完全には除去しないことを特徴としている。また、P型MISトランジスタ形成領域においてNchメタル電極膜114aと共に保護膜113の上部を同時に除去することにより、P型MISトランジスタ形成領域においてNchメタル電極膜114aを完全に(つまり最大限に)除去することが可能となる。

【0086】

次に、図26(a)に示すように、レジストパターン121を除去した後、図23(a)、(b)及び図26(b)に示すように、各ゲート溝23a及び23bのそれぞれの底面及び側壁面を覆うように、ゲート溝23a内のNchメタル電極膜114aの上及びゲート溝23b内の保護膜113の上に、P型MISトランジスタの仕事関数調整用メタル電極膜(Pchメタル電極膜)114bを形成する。Pchメタル電極膜114bの材料、膜厚及び成膜方法は、第1の実施形態の場合と同様である。続いて、図23(a)、(b)及び図26(b)に示すように、各ゲート溝23a及び23bのそれぞれにおけるPchメタル電極膜114bにより形成される凹部が埋まるように、ゲート溝23a内のPchメタル電極膜114bの上及びゲート溝23b内のPchメタル電極膜114bの上に導電性の金属含有膜115を形成する。金属含有膜115の材料及び成膜方法は、第1の実施形態の場合と同様である。

【0087】

次に、図24(a)及び(b)に示すように、CMP法により、各ゲート溝23a及び23bの外側の金属含有膜115、Pchメタル電極膜114b及びNchメタル電極膜114aを研磨して除去すると共に、各ゲート溝23a及び23bに埋め込まれた前記の各膜の平坦化を行う。ここで、図24(a)及び(b)に示す研磨及び除去をCMP法のみを用いて実施すると、幅広パターンを有する各ゲート溝23a及び23bに形成されたゲート電極の上面高さが弧状に変化するように研磨される、いわゆるディッシングが問題になる場合がある。その場合には、CMP法とドライエッチングによるエッチバックとを組み合わせて前記の各膜を除去してもよい。

【0088】

その後、図示は省略しているが、n型ソース/ドレイン領域17a及びp型ソース/ドレイン領域17b(正確には各ソース/ドレイン領域上のシリサイド層20)、並びに各ゲート溝23a及び23bに埋め込まれたリプレースメントゲート電極のそれぞれに電気的に接続するコンタクト及び配線の形成を行うことにより、半導体装置を完成させる。

【0089】

尚、第1及び第2の実施形態においては、N型MISトランジスタ形成領域及びP型MISトランジスタ形成領域にN型MISトランジスタの仕事関数調整用メタル電極膜(Nchメタル電極膜)114aを形成した後、P型MISトランジスタ形成領域に形成されたNchメタル電極膜114aを除去し、その後、N型MISトランジスタ形成領域及びP型MISトランジスタ形成領域にP型MISトランジスタの仕事関数調整用メタル電極膜(Pchメタル電極膜)114bを形成した。しかし、これに代えて、N型MISトランジスタ形成領域及びP型MISトランジスタ形成領域にPchメタル電極膜を形成した後、N型MISトランジスタ形成領域に形成されたPchメタル電極膜を除去し、その後、N型MISトランジスタ形成領域及びP型MISトランジスタ形成領域にNchメタル電極膜を形成してもよい。但し、Nchメタル電極膜114aは、例えばAl、Ti又はMo等の酸化されやすい物質を含むと共に、当該酸化に起因してN型MISトランジスタの特性が変動して劣化する場合がある。このため、Pchメタル電極膜を先に形成した場合、例えば、高誘電率絶縁膜上におけるPchメタル電極膜の洗浄工程や除去工程等に伴う酸素残留、及び、その後に形成されるNchメタル電極膜との反応に起因するPchメタル電極膜の特性変動等が問題となる場合がある。このような場合には、第1及び第2の実施形態のように、Nchメタル電極膜を先に形成すること、言い換えると、N型MISトランジスタ形成領域においてPchメタル電極膜の除去を行わないことが望ましい。

【産業上の利用可能性】

【0090】

本発明に係る半導体装置及びその製造方法によると、トランジスタを構成するゲート絶縁膜のダメージ、及び仕事関数調整用メタルの加工に起因するトランジスタ特性の劣化等を防止して信頼性及び歩留まり等を改善することができるので、メタルゲート電極を有するトランジスタを備えた半導体装置等に有用である。

【符号の説明】

【0091】

10 半導体基板

10a、10b 活性領域

11 素子分離領域

12a p型ウェル領域

12b n型ウェル領域

13a n型エクステンション領域

13b p型エクステンション領域

14 内側サイドウォールスペーサ

15 下敷き絶縁膜

16 外側サイドウォールスペーサ

17a n型ソース/ドレイン領域

17b p型ソース/ドレイン領域

18 シリコンゲルマニウム層

19 シリコンキャップ層

20 シリサイド層

21 応力絶縁膜

22 層間絶縁膜

23a、23b ゲート溝

101 ダミー界面シリコン酸化膜

102 ポリシリコン膜

103 ハードマスク膜

111 絶縁膜

112 高誘電率ゲート絶縁膜

113 保護膜

114a Nchメタル電極膜

114b Pchメタル電極膜

115 導電性埋め込み膜

121 レジストパターン

【特許請求の範囲】

【請求項1】

半導体基板における第1の領域及び第2の領域のそれぞれの上に形成された第1のゲート溝及び第2のゲート溝と、

前記第1のゲート溝及び前記第2のゲート溝のそれぞれの少なくとも底面上に形成されたゲート絶縁膜と、

前記第1のゲート溝内の前記ゲート絶縁膜の上及び前記第2のゲート溝内の前記ゲート絶縁膜の上にそれぞれ形成された保護膜と、

前記第1のゲート溝の底面及び側壁面を覆うように、前記第1のゲート溝内の前記保護膜の上に形成された第1の金属含有膜と、

前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように、前記第1のゲート溝内の前記第1の金属含有膜の上及び前記第2のゲート溝内の前記保護膜の上に形成された第2の金属含有膜と、

前記第1のゲート溝及び前記第2のゲート溝のそれぞれにおける前記第2の金属含有膜により形成される凹部が埋まるように、前記第1のゲート溝内の前記第2の金属含有膜の上及び前記第2のゲート溝内の前記第2の金属含有膜の上に形成された第3の金属含有膜とを備え、

前記第1のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さと比べて、前記第2のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さは薄いことを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記第1のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さと、前記第2のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さとの差は、1nm以上で且つ3nm以下であることを特徴とする半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、

前記半導体基板の上部における前記第1の領域と前記第2の領域との間に素子分離領域が形成されており、

前記第1のゲート溝と前記第2のゲート溝とは前記素子分離領域上で接続しており、

前記素子分離領域上に位置する部分の前記保護膜には段差が形成されていることを特徴とする半導体装置。

【請求項4】

請求項1〜3のいずれか1項に記載の半導体装置において、

前記保護膜は、窒化チタン、窒化ハフニウム又は窒化タンタルからなることを特徴とする半導体装置。

【請求項5】

請求項1〜4のいずれか1項に記載の半導体装置において、

前記第1のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さは、2nm以上で且つ5nm以下であることを特徴とする半導体装置。

【請求項6】

請求項1〜5のいずれか1項に記載の半導体装置において、

前記ゲート絶縁膜及び前記保護膜は、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように形成されていることを特徴とする半導体装置。

【請求項7】

請求項1〜5のいずれか1項に記載の半導体装置において、

前記ゲート絶縁膜及び前記保護膜は、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの側壁面上には形成されていないことを特徴とする半導体装置。

【請求項8】

請求項1〜7のいずれか1項に記載の半導体装置において、

前記半導体基板における前記第1のゲート溝の両側方には第1導電型の第1のソース/ドレイン領域が形成されており、

前記半導体基板における前記第2のゲート溝の両側方には第2導電型の第2のソース/ドレイン領域が形成されていることを特徴とする半導体装置。

【請求項9】

請求項8に記載の半導体装置において、

前記第1導電型はn型であり、

前記第2導電型はp型であることを特徴とする半導体装置。

【請求項10】

請求項9に記載の半導体装置において、

前記第1の金属含有膜は、チタン、アルミニウム、チタンとアルミニウムとの合金、窒化ハフニウム又は炭化タンタルを含むことを特徴とする半導体装置。

【請求項11】

請求項10に記載の半導体装置において、

前記第1の金属含有膜の厚さは、1nm以上で且つ5nm以下であることを特徴とする半導体装置。

【請求項12】

請求項9〜11のいずれか1項に記載の半導体装置において、

前記第2の金属含有膜は、窒化チタン、酸化ルテニウム又は白金を含むことを特徴とする半導体装置。

【請求項13】

請求項12に記載の半導体装置において、

前記第2の金属含有膜の厚さは、4nm以上であることを特徴とする半導体装置。

【請求項14】

請求項9〜13のいずれか1項に記載の半導体装置において、

前記第2のソース/ドレイン領域は、シリコンゲルマニウム層を有することを特徴とする半導体装置。

【請求項15】

請求項1〜14のいずれか1項に記載の半導体装置において、

前記ゲート絶縁膜は、高誘電率絶縁膜を含むことを特徴とする半導体装置。

【請求項16】

請求項15記載の半導体装置において、

前記高誘電率絶縁膜は、少なくともハフニウム又はジルコニウムを含む絶縁膜であることを半導体装置。

【請求項17】

半導体基板における第1の領域及び第2の領域のそれぞれの上に第1のゲート溝及び第2のゲート溝を形成する工程(a)と、

前記第1のゲート溝及び前記第2のゲート溝のそれぞれの少なくとも底面上にゲート絶縁膜を形成する工程(b)と、

前記第1のゲート溝内の前記ゲート絶縁膜の上及び前記第2のゲート溝内の前記ゲート絶縁膜の上にそれぞれ保護膜を形成する工程(c)と、

前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように、前記第1のゲート溝内の前記保護膜の上及び前記第2のゲート溝内の前記保護膜の上に第1の金属含有膜を形成する工程(d)と、

前記第2のゲート溝内の前記第1の金属含有膜、及び前記第2のゲート溝内の前記保護膜の上部を選択的に除去する工程(e)と、

前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように、前記第1のゲート溝内の前記第1の金属含有膜の上及び前記第2のゲート溝内の前記保護膜の上に第2の金属含有膜を形成する工程(f)と、

前記第1のゲート溝及び前記第2のゲート溝のそれぞれにおける前記第2の金属含有膜により形成される凹部が埋まるように、前記第1のゲート溝内の前記第2の金属含有膜の上及び前記第2のゲート溝内の前記第2の金属含有膜の上に第3の金属含有膜を形成する工程(g)とを備えていることを特徴とする半導体装置の製造方法。

【請求項18】

請求項17に記載の半導体装置の製造方法において、

前記工程(a)は、

前記半導体基板における前記第1の領域及び前記第2の領域のそれぞれの上に第1のダミーゲート電極及び第2のダミーゲート電極を形成する工程(a1)と、

前記第1のダミーゲート電極及び前記第2のダミーゲート電極を覆うように、前記半導体基板における前記第1の領域及び前記第2の領域のそれぞれの上に層間絶縁膜を形成し、その後、前記第1のダミーゲート電極及び前記第2のダミーゲート電極のそれぞれの頂部が露出するように、前記層間絶縁膜を薄くする工程(a2)と、

前記第1のダミーゲート電極及び前記第2のダミーゲート電極を除去して、前記第1のゲート溝及び前記第2のゲート溝を形成する工程(a3)とを含むことを特徴とする半導体装置の製造方法。

【請求項19】

請求項18に記載の半導体装置の製造方法において、

前記ゲート絶縁膜及び前記保護膜は、前記工程(a)の後に、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように形成されることを特徴とする半導体装置の製造方法。

【請求項20】

請求項18に記載の半導体装置の製造方法において、

前記ゲート絶縁膜及び前記保護膜は、前記工程(a)の前に、前記第1のゲート溝の底面となる部分の前記半導体基板の上及び前記第2のゲート溝の底面となる部分の前記半導体基板の上にそれぞれ形成され、

前記工程(a1)では、前記第1の領域及び前記第2の領域のそれぞれの上に、前記ゲート絶縁膜及び前記保護膜を介して、前記第1のダミーゲート電極及び前記第2のダミーゲート電極が形成されることを特徴とする半導体装置の製造方法。

【請求項1】

半導体基板における第1の領域及び第2の領域のそれぞれの上に形成された第1のゲート溝及び第2のゲート溝と、

前記第1のゲート溝及び前記第2のゲート溝のそれぞれの少なくとも底面上に形成されたゲート絶縁膜と、

前記第1のゲート溝内の前記ゲート絶縁膜の上及び前記第2のゲート溝内の前記ゲート絶縁膜の上にそれぞれ形成された保護膜と、

前記第1のゲート溝の底面及び側壁面を覆うように、前記第1のゲート溝内の前記保護膜の上に形成された第1の金属含有膜と、

前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように、前記第1のゲート溝内の前記第1の金属含有膜の上及び前記第2のゲート溝内の前記保護膜の上に形成された第2の金属含有膜と、

前記第1のゲート溝及び前記第2のゲート溝のそれぞれにおける前記第2の金属含有膜により形成される凹部が埋まるように、前記第1のゲート溝内の前記第2の金属含有膜の上及び前記第2のゲート溝内の前記第2の金属含有膜の上に形成された第3の金属含有膜とを備え、

前記第1のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さと比べて、前記第2のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さは薄いことを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記第1のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さと、前記第2のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さとの差は、1nm以上で且つ3nm以下であることを特徴とする半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、

前記半導体基板の上部における前記第1の領域と前記第2の領域との間に素子分離領域が形成されており、

前記第1のゲート溝と前記第2のゲート溝とは前記素子分離領域上で接続しており、

前記素子分離領域上に位置する部分の前記保護膜には段差が形成されていることを特徴とする半導体装置。

【請求項4】

請求項1〜3のいずれか1項に記載の半導体装置において、

前記保護膜は、窒化チタン、窒化ハフニウム又は窒化タンタルからなることを特徴とする半導体装置。

【請求項5】

請求項1〜4のいずれか1項に記載の半導体装置において、

前記第1のゲート溝内の前記ゲート絶縁膜の上に位置する部分の前記保護膜の厚さは、2nm以上で且つ5nm以下であることを特徴とする半導体装置。

【請求項6】

請求項1〜5のいずれか1項に記載の半導体装置において、

前記ゲート絶縁膜及び前記保護膜は、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように形成されていることを特徴とする半導体装置。

【請求項7】

請求項1〜5のいずれか1項に記載の半導体装置において、

前記ゲート絶縁膜及び前記保護膜は、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの側壁面上には形成されていないことを特徴とする半導体装置。

【請求項8】

請求項1〜7のいずれか1項に記載の半導体装置において、

前記半導体基板における前記第1のゲート溝の両側方には第1導電型の第1のソース/ドレイン領域が形成されており、

前記半導体基板における前記第2のゲート溝の両側方には第2導電型の第2のソース/ドレイン領域が形成されていることを特徴とする半導体装置。

【請求項9】

請求項8に記載の半導体装置において、

前記第1導電型はn型であり、

前記第2導電型はp型であることを特徴とする半導体装置。

【請求項10】

請求項9に記載の半導体装置において、

前記第1の金属含有膜は、チタン、アルミニウム、チタンとアルミニウムとの合金、窒化ハフニウム又は炭化タンタルを含むことを特徴とする半導体装置。

【請求項11】

請求項10に記載の半導体装置において、

前記第1の金属含有膜の厚さは、1nm以上で且つ5nm以下であることを特徴とする半導体装置。

【請求項12】

請求項9〜11のいずれか1項に記載の半導体装置において、

前記第2の金属含有膜は、窒化チタン、酸化ルテニウム又は白金を含むことを特徴とする半導体装置。

【請求項13】

請求項12に記載の半導体装置において、

前記第2の金属含有膜の厚さは、4nm以上であることを特徴とする半導体装置。

【請求項14】

請求項9〜13のいずれか1項に記載の半導体装置において、

前記第2のソース/ドレイン領域は、シリコンゲルマニウム層を有することを特徴とする半導体装置。

【請求項15】

請求項1〜14のいずれか1項に記載の半導体装置において、

前記ゲート絶縁膜は、高誘電率絶縁膜を含むことを特徴とする半導体装置。

【請求項16】

請求項15記載の半導体装置において、

前記高誘電率絶縁膜は、少なくともハフニウム又はジルコニウムを含む絶縁膜であることを半導体装置。

【請求項17】

半導体基板における第1の領域及び第2の領域のそれぞれの上に第1のゲート溝及び第2のゲート溝を形成する工程(a)と、

前記第1のゲート溝及び前記第2のゲート溝のそれぞれの少なくとも底面上にゲート絶縁膜を形成する工程(b)と、

前記第1のゲート溝内の前記ゲート絶縁膜の上及び前記第2のゲート溝内の前記ゲート絶縁膜の上にそれぞれ保護膜を形成する工程(c)と、

前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように、前記第1のゲート溝内の前記保護膜の上及び前記第2のゲート溝内の前記保護膜の上に第1の金属含有膜を形成する工程(d)と、

前記第2のゲート溝内の前記第1の金属含有膜、及び前記第2のゲート溝内の前記保護膜の上部を選択的に除去する工程(e)と、

前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように、前記第1のゲート溝内の前記第1の金属含有膜の上及び前記第2のゲート溝内の前記保護膜の上に第2の金属含有膜を形成する工程(f)と、

前記第1のゲート溝及び前記第2のゲート溝のそれぞれにおける前記第2の金属含有膜により形成される凹部が埋まるように、前記第1のゲート溝内の前記第2の金属含有膜の上及び前記第2のゲート溝内の前記第2の金属含有膜の上に第3の金属含有膜を形成する工程(g)とを備えていることを特徴とする半導体装置の製造方法。

【請求項18】

請求項17に記載の半導体装置の製造方法において、

前記工程(a)は、

前記半導体基板における前記第1の領域及び前記第2の領域のそれぞれの上に第1のダミーゲート電極及び第2のダミーゲート電極を形成する工程(a1)と、

前記第1のダミーゲート電極及び前記第2のダミーゲート電極を覆うように、前記半導体基板における前記第1の領域及び前記第2の領域のそれぞれの上に層間絶縁膜を形成し、その後、前記第1のダミーゲート電極及び前記第2のダミーゲート電極のそれぞれの頂部が露出するように、前記層間絶縁膜を薄くする工程(a2)と、

前記第1のダミーゲート電極及び前記第2のダミーゲート電極を除去して、前記第1のゲート溝及び前記第2のゲート溝を形成する工程(a3)とを含むことを特徴とする半導体装置の製造方法。

【請求項19】

請求項18に記載の半導体装置の製造方法において、

前記ゲート絶縁膜及び前記保護膜は、前記工程(a)の後に、前記第1のゲート溝及び前記第2のゲート溝のそれぞれの底面及び側壁面を覆うように形成されることを特徴とする半導体装置の製造方法。

【請求項20】

請求項18に記載の半導体装置の製造方法において、

前記ゲート絶縁膜及び前記保護膜は、前記工程(a)の前に、前記第1のゲート溝の底面となる部分の前記半導体基板の上及び前記第2のゲート溝の底面となる部分の前記半導体基板の上にそれぞれ形成され、

前記工程(a1)では、前記第1の領域及び前記第2の領域のそれぞれの上に、前記ゲート絶縁膜及び前記保護膜を介して、前記第1のダミーゲート電極及び前記第2のダミーゲート電極が形成されることを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【公開番号】特開2013−26466(P2013−26466A)

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願番号】特願2011−160274(P2011−160274)

【出願日】平成23年7月21日(2011.7.21)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願日】平成23年7月21日(2011.7.21)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]