半導体装置及びその製造方法

【課題】高品質な配線を有する半導体装置を提供する。

【解決手段】第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域に設けられた第1の絶縁層上に形成された第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層上に形成され、第2の絶縁層と略同一の高さを有する第3の絶縁層11cと、第1の領域に設けられた第1の絶縁層上及び第2の絶縁層の両方の側壁に形成された第1の配線層13aと、第2の領域に設けられた第1の絶縁層上、及び第3の絶縁層の上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層、第2の絶縁層、第1の配線層、及び第2の配線層を覆う第4の絶縁層15と、第1の領域に設けられた第4の絶縁層内に形成され、第1の配線層に接続された第1のコンタクトプラグ17aと、第2の領域に設けられた第4の絶縁層内に形成され、第2の配線層に接続された第2のコンタクトプラグ17bと、を備える。

【解決手段】第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域に設けられた第1の絶縁層上に形成された第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層上に形成され、第2の絶縁層と略同一の高さを有する第3の絶縁層11cと、第1の領域に設けられた第1の絶縁層上及び第2の絶縁層の両方の側壁に形成された第1の配線層13aと、第2の領域に設けられた第1の絶縁層上、及び第3の絶縁層の上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層、第2の絶縁層、第1の配線層、及び第2の配線層を覆う第4の絶縁層15と、第1の領域に設けられた第4の絶縁層内に形成され、第1の配線層に接続された第1のコンタクトプラグ17aと、第2の領域に設けられた第4の絶縁層内に形成され、第2の配線層に接続された第2のコンタクトプラグ17bと、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年半導体装置の微細化が進んでおり、微細な配線(単に微細配線とも呼ぶ)を形成することが求められている。その微細配線を形成する方法として、絶縁層のパタンの側壁に配線を形成する側壁配線技術(単に側壁加工とも呼ぶ)が検討されている。側壁配線技術を用いると、絶縁層のパタンの半分のピッチで配線の繰り返しパタンを形成することができる。このような側壁配線は、メモリセル部等に用いられる配線領域(細幅配線領域とも呼ぶ)で設けられることがある。

【0003】

ところで、製造工程数削減のために、そのような細幅配線領域と、微細配線を形成する必要のない周辺回路等の配線領域(太幅配線等とも呼ぶ)とを同時に形成することが求められている。

【0004】

そのような場合、細幅配線として形成される配線材料と、太幅配線として形成される配線材料とは同一工程で形成されることになり、それぞれの配線材料の膜厚は等しくなる。ところで、上述した側壁配線技術が用いられる細幅配線領域において、配線材料は絶縁層のパタンの側壁に形成される。そのため、配線の高さはパタンの高さに依存することになる。そして、微細配線を形成する必要のない太幅配線領域において、配線の高さは配線材料の膜厚に依存することになる。そのため、細幅配線領域における配線の高さは、太幅配線領域における配線の高さよりも高くなる。

【0005】

その結果、コンタクトプラグ(単にコンタクトとも呼ぶ)が細幅配線領域と太幅配線領域との両方に配置される場合には、各領域のコンタクトプラグの高さが異なり、コンタクトプラグの形成(コンタクト加工とも呼ぶ)の難易度が上がるという問題があった。

また、太幅配線領域における配線は、配線抵抗の低抵抗化の為に膜厚を厚くすることが望ましいが、配線材料の膜厚は側壁配線の線幅(ハーフピッチ)等で決まる。このため、太幅配線領域における配線の膜厚が薄くなってしまい、抵抗値が高くなってしまうという問題があった。

このように、従来は高品質な配線を有する半導体装置を形成することが容易ではなかった。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−27978号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

高品質な配線を有する半導体装置を提供する。

【課題を解決するための手段】

【0008】

実施形態の半導体装置は、第1の領域及び第2の領域に設けられた第1の絶縁層と、前記第1の領域に設けられた前記第1の絶縁層上に形成されたラインアンドスペース状の第2の絶縁層と、前記第2の領域に設けられた前記第1の絶縁層上に形成され、前記第2の絶縁層と略同一の高さを有する第3の絶縁層と、前記第1の領域に設けられた前記第1の絶縁層上及び前記第2の絶縁層の側壁に形成された第1の配線層と、前記第2の領域に設けられた前記第1の絶縁層上、及び前記第3の絶縁層の上面及び側壁上に形成された第2の配線層と、前記第1の絶縁層、前記第2の絶縁層、前記第1の配線層、及び前記第2の配線層を覆う第4の絶縁層と、前記第1の領域に設けられた前記第4の絶縁層内に形成され、前記第1の配線層に接続された第1のコンタクトプラグと、前記第2の領域に設けられた前記第4の絶縁層内に形成され、前記第2の配線層に接続された第2のコンタクトプラグと、を備える。

【図面の簡単な説明】

【0009】

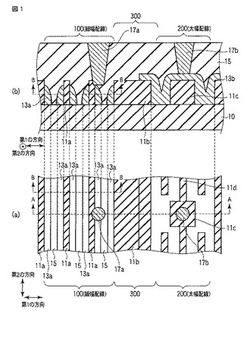

【図1】図1(a)は、第1の実施形態に係る半導体装置の基本的な構成について模式的に示した上面図であり、図1(b)は、図1(a)のA−A線に沿った断面図である。

【図2】図2(a)、図2(b)、及び図2(c)は、第1の実施形態に係る半導体装置の基本的な製造方法の一部を模式的に示した断面図である。

【図3】図3(a)、図3(b)、及び図3(c)は、第1の実施形態に係る半導体装置の基本的な製造方法の一部を模式的に示した断面図である。

【図4】第1の実施形態に係る半導体装置の基本的な製造方法の一部を模式的に示した断面図である。

【図5】第1の実施形態の変形例1に係る半導体装置の基本的な構成について模式的に示した断面図である。

【図6】第1の実施形態の変形例2に係る半導体装置の基本的な構成について模式的に示した断面図である。

【図7】第1の実施形態の変形例3に係る半導体装置の基本的な構成について模式的に示した断面図である。

【図8】図8(a)は、第1の実施形態の変形例4に係る半導体装置の基本的な構成について模式的に示した断面図であり、図8(b)は、上層コンタクトと側壁配線との接続関係を明確に示した断面図であり、図8(c)は、第1の実施形態の変形例5に係る半導体装置の基本的な構成について模式的に示した断面図である。

【図9】第2の実施形態に係る半導体装置の基本的な構成について模式的に示した断面図である。

【図10】第2の実施形態に係る半導体装置の基本的な製造方法の一部を模式的に示した断面図である。

【図11】第2の実施形態に係る半導体装置の基本的な製造方法の一部を模式的に示した断面図である。

【図12】第2の実施形態に係る半導体装置の基本的な製造方法の一部を模式的に示した断面図である。

【図13】第2の実施形態の変形例に係る半導体装置の基本的な構成について模式的に示した断面図である。

【図14】第1の実施形態の比較例に係る半導体装置の基本的な構成について模式的に示した断面図である。

【図15】第2の実施形態の比較例に係る半導体装置の基本的な構成について模式的に示した断面図である。

【発明を実施するための形態】

【0010】

以下、実施形態の詳細を図面を参照して説明する。この説明に際し、全図にわたり、共通する部分には共通する参照符号を付す。

【0011】

(第1の実施形態)

<配線の構成>

まず、図1を用いて、第1の実施形態に係る半導体装置の基本的な構成について説明する。図1(a)は、第1の実施形態に係る半導体装置の基本的な構成について模式的に示した上面図であり、図1(b)は、図1(a)のA−A線に沿った断面図である。

【0012】

図1に示すように、第1の実施形態に係る半導体装置は、細幅配線領域100と、太幅配線領域200と、領域300とを備えている。細幅配線領域(単に領域とも呼ぶ)100は、メモリセル部等に用いられる微細な配線が形成されている領域である。具体的には、ラインアンドスペース状の絶縁層のパタン(繰り返しパタンとも呼ぶ)の側壁に、2本1組の左右対称の構造を持つ配線(側壁配線とも呼ぶ)が形成されている領域である。太幅配線領域(単に領域とも呼ぶ)200は、周辺回路等に用いられる配線が形成されている領域である。領域300は、例えば細幅配線領域100と、太幅配線領域200との間に設けられ、実質的に動作する配線が形成されない領域である。

【0013】

細幅配線領域100において、絶縁層10上には、ラインアンドスペース状にパタニングされ、高さ(膜厚)が数十〜数百nm程度であり、第1の方向に沿った幅が数〜数十nm程度である第2の方向に延伸する絶縁層(単にパタンとも呼ぶ)11aが形成されている。また、絶縁層11aの両方の側壁(ラインアンドスペースの延伸方向に沿った側壁)には配線層13aが形成され、配線層13aの上部にはコンタクトプラグ(上層コンタクト層)17aが形成されている。そして、絶縁層10、絶縁層11a、及び配線層13aを覆う絶縁層15が形成されている。コンタクトプラグ17aは、この絶縁層15内に形成され、配線層13aに接続されている。ところで、図1(a)のB−B線に示すように、例えば絶縁層11aの底面及び上面の中間近傍の高さにおいて、第1の方向に沿った絶縁層11aの幅、配線層13aの幅、及び配線層13aに挟まれる絶縁層15の幅はそれぞれ略同一である。

【0014】

太幅配線領域200において、絶縁層10上には、高さが数十〜数百nm程度、1辺の幅が数十〜数百nm程度の芯材となる大パタン部(絶縁層)11cと、第2の方向に延伸する芯材部(絶縁層)11dとを有する絶縁層が形成されている。この芯材部11dの第1の方向に沿った幅は、例えば絶縁層11cと同程度である。また、絶縁層10上及び絶縁層11c、11dの側壁及び上面には膜厚が数〜数十nm程度の配線層13bが形成され、絶縁層11cの上方且つ配線層13b上にはコンタクトプラグ(上層コンタクト層)17bが形成されている。そして、配線層13bを覆う絶縁層15が形成されている。コンタクトプラグ17bは、この絶縁層15内に形成され、配線層13bに接続されている。尚、絶縁層11c及び11dの高さは、細幅配線領域100の絶縁層11aの高さと略同一である。また、大パタン部11cの上面の面積は、コンタクトプラグ17b及び配線層13bの接触している面積よりも大きい。また、延伸部11dの延伸方向は第2の方向に限定されない。

【0015】

また、領域300において、絶縁層10上に形成された高さが数十〜数百nm程度の絶縁層11bが形成されている。そして、絶縁層11bの細幅配線領域100側の側壁には配線層13aが形成され、太幅配線領域200側の側壁及び上面には配線層13bが形成されている。尚、絶縁層11bの側壁に形成された配線層13aはダミーの配線として用いられることがある。尚、絶縁層11bの高さは、細幅配線領域100の絶縁層11aの高さと略同一である。また、絶縁層11bの形状は特に決まっていないが、本実施形態では、絶縁層11aよりも第1方向に沿った幅が大きい大パタン形状である。

【0016】

絶縁層10、11a、11b、11c、11d及び15は、SiO2、SiN、またはSiOC等の絶縁材料である。配線層13a、13bは、一般的に側壁配線材料に用いられるものであれば良く、例えば、TiN、Ti、Ni、Co、W、Mo、Ru、Ta、Alなどや、またこの中のいずれかを含むバリアメタルである。その他の配線材料としては、例えばW、Ti、Ni、Co、Cuなどのシリサイドやドープしたシリコン等で良い。コンタクトプラグ17a、17bは、ダマシンができるメタルであれば良く、例えばW、Cu、Alなどである。

【0017】

<配線の製造方法>

次に、図2〜図4を用いて、第1の実施形態に係る半導体装置の基本的な製造方法について説明する。図2〜図4は、第1の実施形態に係る半導体装置の基本的な製造方法を模式的に示した断面図である。

【0018】

先ず、図2(a)に示すように、図示しないSi基盤等の半導体基板上に例えばSiO2で形成された絶縁層10上に膜厚が数十〜数百nm程度の絶縁層11となるSiO2を形成し、絶縁層11上にレジスト12を形成する。そして、レジスト12を、例えばフォトリソグラフィでパタニングする。具体的には、領域100におけるレジスト12を、ハーフピッチが数十nm程度のラインアンドスペース状にパタニングする。また、同時に領域200におけるレジスト12を、1辺の幅が数十〜数百nm程度の大パタン部と、第2の方向に延伸する芯材部(図2〜4において不図示)と、を有する形状にパタニングする。更に、同時に、領域300におけるレジスト12を、パタニングする。これにより、領域100においてレジスト12a、領域200においてレジスト12c(大パタン部、及び芯材部含む)、そして領域300においてレジスト12bがそれぞれ形成される。尚、レジスト12の代わりに、レジストによってパタニングされた膜を用いても良い。

【0019】

次に図2(b)に示すように、レジスト12a、12b、及び12cをマスクとして用いて、RIE(reactive ion etching)法等により絶縁層11をエッチングし、絶縁層11a、11b、11c、及び11d(不図示)を形成する。そして、アッシング等でレジスト12a、12b、及び12cを除去する。

【0020】

次に図2(c)に示すように、例えば絶縁層11aの第1の方向に沿った幅が半分程度になるまで絶縁層11a、11b及び11cに対して、ウェットエッチング等の等方性のエッチングを行う(スリミングとも呼ぶ)。

【0021】

次に図3(a)に示すように、絶縁層10上、及び絶縁層11a、11b、11c、11d(ここでは不図示なので図1(a)参照)の上面と、側壁とにPVD(Physical Vapor Deposition)法またはCVD(Chemical Vapor Deposition)法によって膜厚が数〜数十nm程度の配線層13となる例えばWを形成する。配線材料成膜時には領域100の絶縁層11aの側壁に配線材料が成膜されやすいように成膜方法を調整すると良い。例えば、PVD法を用いる場合は、成膜時のバイアスを調整する。

【0022】

次に図3(b)に示すように、配線層13上にレジストを形成し、太幅配線領域200をカバーするようにリソグラフィによってパタニングする。これにより、太幅配線領域200における配線層13上にレジスト14が形成される。

【0023】

次に図3(c)に示すように、レジスト14をマスクとして用いて、RIE等により配線層13をエッチバックする。そしてアッシング等により、レジスト14を除去する。これにより、領域100の絶縁層11aの側壁には配線層13aが形成され、領域200には、配線層13bが除去されずに残る。そして、領域300において、絶縁層11bの領域100側の側壁には、配線層13aが形成され、領域200側の上面及び側壁には配線層13bが形成されている。

【0024】

次に、図4に示すように、全面に絶縁層15が形成される。領域100において、絶縁層15、及び11aの一部をRIE等の異方性エッチングで除去して、配線層13aの上部を露出するコンタクトホール16aが形成される。また、領域200において、絶縁層15の一部を、RIE等の異方性エッチングで除去して、絶縁層11c(大パタン)上方の配線層13bを露出するコンタクトホール16bが形成される。このコンタクトホール16a、及び16bは同時に形成される。そして、図1に示すように、それぞれのコンタクトホール内にW等のダマシンができるメタルを埋め込むことで、領域100にコンタクトプラグ17aが形成され、領域200にコンタクトプラグ17bが形成される。また、配線層13bは配線層13aとは異なりエッチングされないので、エッチングコンタクトプラグ17aの頂部は、コンタクトプラグ17bの頂部よりも低い位置にある。

【0025】

<比較例>

ここで、図14を用いて、実施形態の比較例に係る半導体装置について簡単に説明する。

【0026】

図14に示すように、比較例に係る半導体装置は、細幅配線領域100と、太幅配線領域200と、領域300とを備えている。領域100は、側壁配線が形成されている領域である。領域200は、周辺回路等に用いられる配線が形成されている領域である。領域300は、領域100と、領域200との間に設けられ、配線が形成されない領域である。

【0027】

細幅配線領域100において、絶縁層10上には、第2の方向に延伸するラインアンドスペース状にパタニングされた絶縁層11aが形成されている。また、絶縁層11aの側壁には高さが数十〜数百nm程度である配線層13aが形成され、配線層13aの上部にはコンタクトプラグ17aが形成されている。そして、絶縁層10、絶縁層11a、及び配線層13aを覆う絶縁層15が形成されている。コンタクトプラグ17aは、この絶縁層15内に形成され、配線層13aに接続されている。

領域200において、絶縁層10上には、膜厚が数〜数十nm程度の配線層13dが形成され、配線層13d上にはコンタクトプラグ17bが形成されている。そして、配線層13bを覆う絶縁層15が形成されている。

また、領域300において、絶縁層10上には絶縁層15が形成されている。

【0028】

領域200の配線層13dは、領域100の配線層13aと同時に形成される。このため、配線層13dの膜厚は、配線層13aの幅や、配線層13a形成時における配線材料のエッチング量等で決まる。近年の微細化が進んでいる半導体装置において、配線13aの幅は狭くすることが望ましく、配線層13dの膜厚を充分に確保することができない。そのため、領域100の、コンタクトプラグ17aが形成される配線層13aの高さと、領域200の、コンタクトプラグ17bが形成される配線層13bの高さとの差が大きくなる。この結果、領域100及び領域200に形成される配線層の高さが異なり、コンタクトプラグ17a及び17bを形成するための、コンタクトホール形成時のエッチングの制御が困難である。

【0029】

また、領域300においては、領域100及び200とは異なり、絶縁層15しか形成されないので、領域100、200、及び300の間の絶縁層15の表面(不図示)における平坦性が悪くなってしまうこともある。

【0030】

<実施形態の作用効果>

上述した実施形態によれば、半導体装置は、第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域100に設けられた第1の絶縁層10上に形成されたラインアンドスペース状の第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層10上に形成され、第2の絶縁層11aと略同一の高さを有する第3の絶縁層11cと、第1の領域100に設けられた第1の絶縁層10上及び第2の絶縁層11aの側壁に形成された第1の配線層13aと、第2の領域200に設けられた第1の絶縁層10上、及び第3の絶縁層11cの上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層10、第2の絶縁層11a、第1の配線層13a、及び第2の配線層13bを覆う第4の絶縁層15と、第1の領域100に設けられた第4の絶縁層15内に形成され、第1の配線層13aに接続された第1のコンタクトプラグ17aと、第2の領域200に設けられた第4の絶縁層15内に形成され、第2の配線層13bに接続された第2のコンタクトプラグ17bと、を備える。第3の絶縁層11cは、第2のコンタクトプラグ17bと第2の配線13bとが接触している面積よりも面積の大きいパタン(大パタン部)を有している。また、第2のコンタクトプラグは、該大パタン部上方の第2の配線と接続されている。

【0031】

このように、細幅配線領域100においては、配線間隔の微細化に伴い、側壁加工用に芯材となる絶縁層11aが形成されている。そして、太幅配線領域200においても、芯材となる絶縁層11cを形成することで、絶縁層11の側壁にも配線層13bが形成される。そのため、配線層13bの電気伝導方向に垂直な断面の断面積が比較例で示した配線層13dよりも大きくなり、配線抵抗を減少させることができる。

【0032】

また、絶縁層11aの高さと絶縁層11cの高さとが実質的に同じであるため、細幅配線領域100におけるコンタクトプラグが接続される配線層13aの高さと、太幅配線領域200のコンタクトプラグが接続される配線層13cの高さとはほぼ同等になる。その結果、細幅配線領域100、及び太幅配線領域200において、同時にコンタクトプラグを形成することが容易となる。

【0033】

更に、第3の領域は、第1の絶縁層10上に形成され、第2の絶縁層11aと略同一の高さを有し、第4の絶縁膜で覆われた第5の絶縁層11bが設けされている。このように、実質的に何も形成されない領域300にも芯材となる付加的な絶縁層を形成することで、領域100〜300に絶縁層15を形成した際に、絶縁層15の平坦性を向上させることができる。

【0034】

上述したように、本実施形態では、配線抵抗が抑制された高品質な細幅配線領域と、太幅配線領域とを有する半導体装置(配線)を得ることができる。

【0035】

<第1の実施形態の変形例>

(変形例1)

尚、図5に示すように、太幅配線領域200に大パタン部11cを有する絶縁層の代わりに、細幅配線領域100と同様のラインアンドスペース状の絶縁層11eが形成されても良い。変形例1に係る基本的な製造方法は、上述した第1の実施形態とほぼ同様なので、詳細な説明は省略する。変形例1では、図2(a)に示す工程において、太幅配線領域200のレジスト12を、例えば細幅領域100のレジスト12aと同様のラインアンドスペース状のパタンにすることで、絶縁層11eを形成することが可能である。

【0036】

このように、第4の絶縁層11cを、ラインアンドスペース状としても、上述した第1の実施形態と同様に、比較例の配線層13dの場合と比べて、太幅配線領域200の配線層13cの断面積を充分に確保できる。これにより、上述した第1実施形態と同様に、配線層13cにおいて配線抵抗を抑制することができる。

【0037】

また、変形例1の配線層13cは、上述した第1の実施形態と同様に、細幅配線領域100の配線層13a及び太幅配線領域200の配線層13cの高さは、ほぼ同じである。そのため、第1の実施形態と同様に、比較例と比べてコンタクトプラグ17a、17bの形成が容易である。

【0038】

更に、上述した第1の実施形態と同様に、領域300には、領域100、200に形成された絶縁層11a、及び11eと同じ高さの大パタン部11bが形成されているので、絶縁層15の上面の平坦性の悪化を抑制することが可能である。

【0039】

尚、太幅配線領域200の絶縁層11eの幅や、本数は適宜変更可能である。絶縁層11eの幅をより細くし、本数を増やすことで、絶縁層11eを覆う配線層13cの電気伝導方向断面の金属膜の断面積がより大きくなるので、配線抵抗の抑制の観点で好ましい。

【0040】

(変形例2)

次に、図6を用いて、上述した第1の実施形態の変形例2について説明する。変形例2は、領域300に大パタンの絶縁層が形成されないという点で、第1の実施形態と異なっている。

【0041】

しかし、変形例2の配線層13bは、上述した第1の実施形態と同様に、比較例の配線層13dの場合と比べて、太幅配線領域200の配線層13cの断面積を充分に確保できる。これにより、上述した第1実施形態と同様に、配線層13bにおいて抵抗値を低下することができる。

【0042】

また、変形例2の配線層13bは、上述した第1の実施形態と同様に、細幅配線領域100の配線層13a及び太幅配線領域200の配線層13bの高さは、ほぼ同じである。そのため、第1の実施形態と同様に、比較例と比べてコンタクトプラグ17a、17bの形成が容易である。

【0043】

(変形例3)

次に、図7を用いて、上述した第1の実施形態の変形例3について説明する。変形例3は、領域300に大パタンの絶縁層が形成されず、太幅配線領域200に大パタン部11cを有する絶縁層の代わりに、細幅配線領域100と同様のラインアンドスペース状の絶縁層11eが形成されているという点で第1の実施形態と異なっている。

【0044】

これにより、変形例1では、上述した第1の実施形態と同様に、比較例の配線層13dの場合と比べて、太幅配線領域200の配線層13cの断面積を充分に確保できる。これにより、上述した第1実施形態と同様に、配線層13cにおいて抵抗値を低下することができる。

【0045】

また、変形例1の配線層13cは、上述した第1の実施形態と同様に、細幅配線領域100の配線層13a及び太幅配線領域200の配線層13cの高さは、ほぼ同じである。そのため、第1の実施形態と同様に、比較例と比べてコンタクトプラグ17a、17bの形成が容易である。

【0046】

尚、細幅配線領域100における配線層13a及びコンタクトプラグ17aは、図8(a)、及び図8(b)に示すように、側壁配線層13aに接触するコンタクトプラグ17aの底面と、側壁配線層13aの上面との距離d1が大きくなるほど、コンタクトプラグ17aと、側壁配線層13aとの接触面積が大きくなる。このd1の調整方法としては、上述した第1の実施形態で説明した図4のコンタクトホール16a、16bの形成の際、例えばエッチング時間を調整する方法等がある。d1が大きくなるほど(コンタクトプラグ17aと、側壁配線層13aとの接触面積が大きくなるほど)、コンタクト抵抗を抑制することができるようになる。

【0047】

また、図8(c)に示すように、細幅配線領域100における、ラインアンドスペース状の側壁配線層13a間の絶縁膜15に、エアギャップ15aを設けても良い。このエアギャップ15aの形成方法としては、上述した第1の実施形態で説明した図4の絶縁層15の形成の際、埋め込み性の悪い膜種、または成膜方法を用いることで、形成することができる。エアギャップ15aを側壁配線層13a間に形成することで、配線間容量を低減することが可能である。

【0048】

(第2の実施形態)

次に、図9を用いて、第2の実施形態に係る半導体装置の基本的な構成について、概略的に説明する。この第2の実施形態は、例えば不揮発性メモリに、上述した第1の実施形態の配線を適用したものである。

【0049】

<第2の実施形態に係る半導体装置の構成>

図9に示すように、第2の実施形態に係る半導体装置(半導体記憶装置)は、細幅配線領域100と、太幅配線領域200と、領域300とを備えている。また、第2の実施形態に係る半導体装置は、メモリセルトランジスタ等を含む各種トランジスタが形成されるトランジスタ領域400、及び配線が形成される配線領域500に分けられる。尚、配線領域500に関しては、上述した第1の実施形態及び各変形例と同様なので、詳細な説明は省略する。

【0050】

トランジスタ領域400の細幅配線領域100において、例えば半導体基板(シリコン基板)20には第2方向に延びるストライプ形状の素子領域AAが、第2方向に沿って複数設けられている。隣接する素子領域AA間には第2方向に延びる素子分離領域(Shallow Trench Isolation:STI)21が形成され、この素子分離領域21によって素子領域AAは電気的に分離されている。半導体基板20上には、複数の素子領域AAを跨ぐようにして、第2の方向に直交する第1方向に延びたストライプ形状のワード線WL(不図示)及びセレクトゲート線SGD,SGS(不図示)が形成されている。ワード線WLと素子領域AAとが交差する領域には、電荷蓄積絶縁膜(不図示)が設けられている。そして、ワード線WLと素子領域AAとが交差する領域にはメモリセルトランジスタMT(不図示)が設けられ、セレクトゲート線SGD、SGSと素子領域AAとが交差する領域には、それぞれ選択トランジスタST(不図示)が設けられている。第2方向で隣接するワード線WL間、セレクトゲート線間、及びワード線WLとセレクトゲート線との間の素子領域AAには、メモリセルトランジスタMT及び選択トランジスタSTのソース領域またはドレイン領域となる不純物拡散層が形成されている。

【0051】

第2方向で隣接するセレクトゲート線SGD間の素子領域AAに形成される不純物拡散層は、選択トランジスタSTのドレイン領域として機能する。そしてこのドレイン領域上には例えばコンタクトプラグ(下層プラグ)25aが形成される。配線領域500の細幅配線領域100において、コンタクトプラグ25aは、第2方向に沿って設けられたストライプ形状のビット線BL(配線層13a)に接続される。このコンタクトプラグ25aは、配線層13a、及び絶縁層11aの下方に設けられる。換言すると、コンタクトプラグ25aは、配線層13a間の絶縁層15と接触しないように形成されている。

【0052】

第2方向で隣接するセレクトゲート線SGS間の素子領域AAに形成される不純物拡散層は、選択トランジスタSTのソース領域として機能する。そしてこのソース領域上には、コンタクトプラグ(不図示)が形成される。該コンタクトプラグは図示せぬソース線SL(不図示)に接続される。尚、コンタクトプラグ25aは、選択トランジスタSTのソース領域上に形成され、配線層13aは、ソース線SLであっても良い。

【0053】

トランジスタ領域400の太幅配線領域200において、素子分離領域(不図示)に囲まれた半導体基板20の表面領域内には、N又はP型の不純物が拡散された一対のソース/ドレイン領域(第1の不純物拡散領域)20aが形成されている。そして、一対のソース/ドレイン領域20aにチャネル領域が挟まれている。また、前記チャネル領域上にはゲート絶縁膜22となる、例えばシリコン酸化膜が形成されている。ゲート絶縁膜22上には電極膜23となる、例えばポリシリコンが形成されている。また、電極膜23上には電極膜24となる、例えばポリシリコンが形成されている。この電極膜23と電極膜24とは電気的に接続され、ゲート電極として機能する。

【0054】

そして、ソース/ドレイン領域20aの上にはコンタクトプラグ25bとなる導電材料が形成されている。配線領域500の太幅配線領域200において、コンタクトプラグ25bは、配線層13bに接続される。

【0055】

また、電極膜24上にはコンタクトプラグ25cとなる導電材料が形成されている。配線領域500の太幅配線領域200において、コンタクトプラグ25cは、コンタクトプラグ25bが接続される配線層とは別の配線層13bに接続される。

【0056】

<第2の実施形態に係る半導体装置の製造方法>

次に、図9〜12を用いて、第2の実施形態に係る半導体装置の基本的な製造方法について、概略的に説明する。尚、トランジスタ領域400の形成方法は周知のものなので、詳細な説明は省略する。また、配線領域500の形成方法は、第1の実施形態で説明したものと同様なので、詳細な説明は省略する。

【0057】

まず図10に示すように、周知の技術を用いて、図9で説明したトランジスタ領域400が形成される。

【0058】

次に、図11に示すように、図2〜図3で説明した方法と同様にして、配線領域500且つ細幅配線領域100における絶縁層10上に、ラインアンドスペース状のスリミングされた絶縁層11aを形成し、配線領域500且つ太幅配線領域200における絶縁層10上に、大パタン部(絶縁層)11cと、第2の方向に延伸する配線部(絶縁層)11d(不図示)とを有する絶縁層を形成する。また、配線領域500且つ領域300における絶縁層10上に、大パタン部(絶縁層)11bを形成する。そして、絶縁層10上、及び絶縁層11a、11b、11c、11dの上面と、側壁と配線層13を形成する。この際、コンタクトプラグ25aが、配線層13、及び絶縁層11aの下方に設けられように、絶縁層11aを配置する。また、コンタクトプラグ25b、25cがそれぞれ、絶縁層11cの間で配線層13と接続するように、絶縁層11cが配置される。

【0059】

次に、図12に示すように、図3(b)、3(c)で説明した方法と同様にして、細幅配線領域100において、RIE等により配線層13をエッチバックして、絶縁層11aの側壁に、ラインアンドスペース状の配線層13aを形成する。また、太幅配線領域200において、コンタクトプラグ25b、25cが接続される配線層13の一部をパタニングすることで、コンタクトプラグ25b、25cを電気的に分離する。

【0060】

そして、図4、及び1で説明したような方法によって、図9に記載の構成を得ることが可能となる。

【0061】

<第2の実施形態の作用効果>

上述した実施形態によれば、上述で説明した第1の実施形態及び各変形例の配線構造を不揮発性メモリに適応することが可能である。

【0062】

ところで、図15に示すように、コンタクトプラグ25aが、配線層13及び絶縁層11aの下方に設けられない場合、配線層13のエッチバック時に、コンタクトプラグ25aの一部が露出され、露出部がエッチングされてしますことがある。このため、コンタクトプラグ25aのエッチングされた一部はダメージを受けてしまう。

【0063】

しかし、第2の実施形態のコンタクトプラグ25aは、配線層13a、及び絶縁層11aの下方に設けられている。これにより、側壁配線層13aを形成するための配線層13のエッチバック時に露出されない。そのため、配線層13のエッチバック時においても、コンタクトプラグ25aはダメージを受けす、良好なコンタクトプラグ25aを得ることができる。

【0064】

(変形例)

また、上述で説明した各実施形態、及び各変形例で説明した配線は、図13に示すように、第2の実施形態で説明したような不揮発性メモリだけでなく、揮発性メモリ(DRAM等)にも用いることが可能である。

【0065】

図13に示すように、第2の実施形態の変形例に係る半導体装置は、細幅配線領域100と、太幅配線領域200と、領域300とを備えている。また、第2の実施形態の変形例に係る半導体装置は、各種トランジスタが形成されるトランジスタ領域400、及び配線が形成される配線領域500に分けられる。尚、配線領域500に関しては、上述した第1の実施形態及び各変形例と同様なので、詳細な説明は省略する。

【0066】

トランジスタ領域400の太幅配線領域200において、半導体基板20の表面領域内には、N又はP型の不純物が拡散された一対のソース/ドレイン領域(第1の不純物拡散領域)20aが形成されている。そして、一対のソース/ドレイン領域20aにチャネル領域が挟まれている。また、前記チャネル領域上にはゲート絶縁膜22となる、例えばシリコン酸化膜が形成されている。ゲート絶縁膜22上には電極膜23となる、例えばポリシリコンが形成されている。この電極膜23はゲート電極として機能する。

【0067】

そして、ソース/ドレイン領域20aの上にはコンタクトプラグ25dとなる導電材料が形成されている。配線領域500の太幅配線領域200において、コンタクトプラグ25dは、配線層26aに接続される。そして、配線領域500の細幅配線領域100まで延伸された配線層26aと、配線層13aとの間にコンタクトプラグ27aが形成される。この際、コンタクトプラグ27aは、図9で説明したコンタクトプラグ25aと同様に、配線層13a、及び絶縁層11aの下方に設けられる。

【0068】

また、電極膜23上にはコンタクトプラグ25eとなる導電材料が形成されている。配線領域500の太幅配線領域200において、コンタクトプラグ25eは、配線層26bに接続される。また配線層26bと配線層13cとの間にはコンタクトプラグ27bが形成されている。

【0069】

このように、揮発性メモリにおいても、上述した各実施形態、及び各変形例を適応することができる。そのため、各実施形態、及び各変形例と同様の理由で、各実施形態、及び各変形例と同様の効果を得ることができる。

【0070】

尚、上述した各実施形態及び各変形例において、太幅配線領域200に、絶縁層11aと略同じ高さの絶縁層11c、d、e等を形成している。しかし、これに限らず、絶縁層11aと略同じ高さの絶縁層であれば、どのようなパタンでもかまわない。

【0071】

また、上述した各実施形態において、領域300に、芯材となる大パタンの絶縁層11bを形成している。配線を覆う絶縁層15の表面の平坦性を保つことができるのであれば、絶縁層11bのパタン形状はどのような形状でもかまわない。

【0072】

また、上述した第1の実施形態の変形例1、3及び第2の実施形態の変形例で説明した、太幅配線領域200における、ラインアンドスペース状の絶縁層11eの延伸方向は、細幅配線領域100における絶縁層11aと平行である。しかし、これに限らず、絶縁層11a、及び11eはかならずしも平行である必要はない。

【0073】

以上、本発明の実施形態を説明したが、本発明は上記実施形態に限定されるものではなく、その趣旨を逸脱しない範囲内において種々変形して実施することが可能である。さらに、上記実施形態には種々の段階の発明が含まれており、開示された構成要件を適宜組み合わせることによって種々の発明が抽出される。例えば、開示された構成要件からいくつかの構成要件が削除されても、所定の効果が得られるものであれば、発明として抽出され得る。

【符号の説明】

【0074】

10…絶縁層、 11a、11b、11c、11d、11e…絶縁層

12、12a、12b、12c…レジスト、 13、13a、13b、13c…配線層

14…レジスト、 15…絶縁層、 15a…エアギャップ

16a、16b…コンタクトホール、 17a、17b…コンタクトプラグ

20…半導体基板、 20a…ドレイン領域、 21…素子分離領域

22…ゲート絶縁膜、 23、24…電極膜

25a、25b、25c、25d、25e…コンタクトプラグ

26a、26b…配線層、 27a、27b…コンタクトプラグ

100…細幅配線領域、 200…太幅配線領域、 300…領域

400…トランジスタ領域、 500…配線領域。

【技術分野】

【0001】

本発明の実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年半導体装置の微細化が進んでおり、微細な配線(単に微細配線とも呼ぶ)を形成することが求められている。その微細配線を形成する方法として、絶縁層のパタンの側壁に配線を形成する側壁配線技術(単に側壁加工とも呼ぶ)が検討されている。側壁配線技術を用いると、絶縁層のパタンの半分のピッチで配線の繰り返しパタンを形成することができる。このような側壁配線は、メモリセル部等に用いられる配線領域(細幅配線領域とも呼ぶ)で設けられることがある。

【0003】

ところで、製造工程数削減のために、そのような細幅配線領域と、微細配線を形成する必要のない周辺回路等の配線領域(太幅配線等とも呼ぶ)とを同時に形成することが求められている。

【0004】

そのような場合、細幅配線として形成される配線材料と、太幅配線として形成される配線材料とは同一工程で形成されることになり、それぞれの配線材料の膜厚は等しくなる。ところで、上述した側壁配線技術が用いられる細幅配線領域において、配線材料は絶縁層のパタンの側壁に形成される。そのため、配線の高さはパタンの高さに依存することになる。そして、微細配線を形成する必要のない太幅配線領域において、配線の高さは配線材料の膜厚に依存することになる。そのため、細幅配線領域における配線の高さは、太幅配線領域における配線の高さよりも高くなる。

【0005】

その結果、コンタクトプラグ(単にコンタクトとも呼ぶ)が細幅配線領域と太幅配線領域との両方に配置される場合には、各領域のコンタクトプラグの高さが異なり、コンタクトプラグの形成(コンタクト加工とも呼ぶ)の難易度が上がるという問題があった。

また、太幅配線領域における配線は、配線抵抗の低抵抗化の為に膜厚を厚くすることが望ましいが、配線材料の膜厚は側壁配線の線幅(ハーフピッチ)等で決まる。このため、太幅配線領域における配線の膜厚が薄くなってしまい、抵抗値が高くなってしまうという問題があった。

このように、従来は高品質な配線を有する半導体装置を形成することが容易ではなかった。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−27978号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

高品質な配線を有する半導体装置を提供する。

【課題を解決するための手段】

【0008】

実施形態の半導体装置は、第1の領域及び第2の領域に設けられた第1の絶縁層と、前記第1の領域に設けられた前記第1の絶縁層上に形成されたラインアンドスペース状の第2の絶縁層と、前記第2の領域に設けられた前記第1の絶縁層上に形成され、前記第2の絶縁層と略同一の高さを有する第3の絶縁層と、前記第1の領域に設けられた前記第1の絶縁層上及び前記第2の絶縁層の側壁に形成された第1の配線層と、前記第2の領域に設けられた前記第1の絶縁層上、及び前記第3の絶縁層の上面及び側壁上に形成された第2の配線層と、前記第1の絶縁層、前記第2の絶縁層、前記第1の配線層、及び前記第2の配線層を覆う第4の絶縁層と、前記第1の領域に設けられた前記第4の絶縁層内に形成され、前記第1の配線層に接続された第1のコンタクトプラグと、前記第2の領域に設けられた前記第4の絶縁層内に形成され、前記第2の配線層に接続された第2のコンタクトプラグと、を備える。

【図面の簡単な説明】

【0009】

【図1】図1(a)は、第1の実施形態に係る半導体装置の基本的な構成について模式的に示した上面図であり、図1(b)は、図1(a)のA−A線に沿った断面図である。

【図2】図2(a)、図2(b)、及び図2(c)は、第1の実施形態に係る半導体装置の基本的な製造方法の一部を模式的に示した断面図である。

【図3】図3(a)、図3(b)、及び図3(c)は、第1の実施形態に係る半導体装置の基本的な製造方法の一部を模式的に示した断面図である。

【図4】第1の実施形態に係る半導体装置の基本的な製造方法の一部を模式的に示した断面図である。

【図5】第1の実施形態の変形例1に係る半導体装置の基本的な構成について模式的に示した断面図である。

【図6】第1の実施形態の変形例2に係る半導体装置の基本的な構成について模式的に示した断面図である。

【図7】第1の実施形態の変形例3に係る半導体装置の基本的な構成について模式的に示した断面図である。

【図8】図8(a)は、第1の実施形態の変形例4に係る半導体装置の基本的な構成について模式的に示した断面図であり、図8(b)は、上層コンタクトと側壁配線との接続関係を明確に示した断面図であり、図8(c)は、第1の実施形態の変形例5に係る半導体装置の基本的な構成について模式的に示した断面図である。

【図9】第2の実施形態に係る半導体装置の基本的な構成について模式的に示した断面図である。

【図10】第2の実施形態に係る半導体装置の基本的な製造方法の一部を模式的に示した断面図である。

【図11】第2の実施形態に係る半導体装置の基本的な製造方法の一部を模式的に示した断面図である。

【図12】第2の実施形態に係る半導体装置の基本的な製造方法の一部を模式的に示した断面図である。

【図13】第2の実施形態の変形例に係る半導体装置の基本的な構成について模式的に示した断面図である。

【図14】第1の実施形態の比較例に係る半導体装置の基本的な構成について模式的に示した断面図である。

【図15】第2の実施形態の比較例に係る半導体装置の基本的な構成について模式的に示した断面図である。

【発明を実施するための形態】

【0010】

以下、実施形態の詳細を図面を参照して説明する。この説明に際し、全図にわたり、共通する部分には共通する参照符号を付す。

【0011】

(第1の実施形態)

<配線の構成>

まず、図1を用いて、第1の実施形態に係る半導体装置の基本的な構成について説明する。図1(a)は、第1の実施形態に係る半導体装置の基本的な構成について模式的に示した上面図であり、図1(b)は、図1(a)のA−A線に沿った断面図である。

【0012】

図1に示すように、第1の実施形態に係る半導体装置は、細幅配線領域100と、太幅配線領域200と、領域300とを備えている。細幅配線領域(単に領域とも呼ぶ)100は、メモリセル部等に用いられる微細な配線が形成されている領域である。具体的には、ラインアンドスペース状の絶縁層のパタン(繰り返しパタンとも呼ぶ)の側壁に、2本1組の左右対称の構造を持つ配線(側壁配線とも呼ぶ)が形成されている領域である。太幅配線領域(単に領域とも呼ぶ)200は、周辺回路等に用いられる配線が形成されている領域である。領域300は、例えば細幅配線領域100と、太幅配線領域200との間に設けられ、実質的に動作する配線が形成されない領域である。

【0013】

細幅配線領域100において、絶縁層10上には、ラインアンドスペース状にパタニングされ、高さ(膜厚)が数十〜数百nm程度であり、第1の方向に沿った幅が数〜数十nm程度である第2の方向に延伸する絶縁層(単にパタンとも呼ぶ)11aが形成されている。また、絶縁層11aの両方の側壁(ラインアンドスペースの延伸方向に沿った側壁)には配線層13aが形成され、配線層13aの上部にはコンタクトプラグ(上層コンタクト層)17aが形成されている。そして、絶縁層10、絶縁層11a、及び配線層13aを覆う絶縁層15が形成されている。コンタクトプラグ17aは、この絶縁層15内に形成され、配線層13aに接続されている。ところで、図1(a)のB−B線に示すように、例えば絶縁層11aの底面及び上面の中間近傍の高さにおいて、第1の方向に沿った絶縁層11aの幅、配線層13aの幅、及び配線層13aに挟まれる絶縁層15の幅はそれぞれ略同一である。

【0014】

太幅配線領域200において、絶縁層10上には、高さが数十〜数百nm程度、1辺の幅が数十〜数百nm程度の芯材となる大パタン部(絶縁層)11cと、第2の方向に延伸する芯材部(絶縁層)11dとを有する絶縁層が形成されている。この芯材部11dの第1の方向に沿った幅は、例えば絶縁層11cと同程度である。また、絶縁層10上及び絶縁層11c、11dの側壁及び上面には膜厚が数〜数十nm程度の配線層13bが形成され、絶縁層11cの上方且つ配線層13b上にはコンタクトプラグ(上層コンタクト層)17bが形成されている。そして、配線層13bを覆う絶縁層15が形成されている。コンタクトプラグ17bは、この絶縁層15内に形成され、配線層13bに接続されている。尚、絶縁層11c及び11dの高さは、細幅配線領域100の絶縁層11aの高さと略同一である。また、大パタン部11cの上面の面積は、コンタクトプラグ17b及び配線層13bの接触している面積よりも大きい。また、延伸部11dの延伸方向は第2の方向に限定されない。

【0015】

また、領域300において、絶縁層10上に形成された高さが数十〜数百nm程度の絶縁層11bが形成されている。そして、絶縁層11bの細幅配線領域100側の側壁には配線層13aが形成され、太幅配線領域200側の側壁及び上面には配線層13bが形成されている。尚、絶縁層11bの側壁に形成された配線層13aはダミーの配線として用いられることがある。尚、絶縁層11bの高さは、細幅配線領域100の絶縁層11aの高さと略同一である。また、絶縁層11bの形状は特に決まっていないが、本実施形態では、絶縁層11aよりも第1方向に沿った幅が大きい大パタン形状である。

【0016】

絶縁層10、11a、11b、11c、11d及び15は、SiO2、SiN、またはSiOC等の絶縁材料である。配線層13a、13bは、一般的に側壁配線材料に用いられるものであれば良く、例えば、TiN、Ti、Ni、Co、W、Mo、Ru、Ta、Alなどや、またこの中のいずれかを含むバリアメタルである。その他の配線材料としては、例えばW、Ti、Ni、Co、Cuなどのシリサイドやドープしたシリコン等で良い。コンタクトプラグ17a、17bは、ダマシンができるメタルであれば良く、例えばW、Cu、Alなどである。

【0017】

<配線の製造方法>

次に、図2〜図4を用いて、第1の実施形態に係る半導体装置の基本的な製造方法について説明する。図2〜図4は、第1の実施形態に係る半導体装置の基本的な製造方法を模式的に示した断面図である。

【0018】

先ず、図2(a)に示すように、図示しないSi基盤等の半導体基板上に例えばSiO2で形成された絶縁層10上に膜厚が数十〜数百nm程度の絶縁層11となるSiO2を形成し、絶縁層11上にレジスト12を形成する。そして、レジスト12を、例えばフォトリソグラフィでパタニングする。具体的には、領域100におけるレジスト12を、ハーフピッチが数十nm程度のラインアンドスペース状にパタニングする。また、同時に領域200におけるレジスト12を、1辺の幅が数十〜数百nm程度の大パタン部と、第2の方向に延伸する芯材部(図2〜4において不図示)と、を有する形状にパタニングする。更に、同時に、領域300におけるレジスト12を、パタニングする。これにより、領域100においてレジスト12a、領域200においてレジスト12c(大パタン部、及び芯材部含む)、そして領域300においてレジスト12bがそれぞれ形成される。尚、レジスト12の代わりに、レジストによってパタニングされた膜を用いても良い。

【0019】

次に図2(b)に示すように、レジスト12a、12b、及び12cをマスクとして用いて、RIE(reactive ion etching)法等により絶縁層11をエッチングし、絶縁層11a、11b、11c、及び11d(不図示)を形成する。そして、アッシング等でレジスト12a、12b、及び12cを除去する。

【0020】

次に図2(c)に示すように、例えば絶縁層11aの第1の方向に沿った幅が半分程度になるまで絶縁層11a、11b及び11cに対して、ウェットエッチング等の等方性のエッチングを行う(スリミングとも呼ぶ)。

【0021】

次に図3(a)に示すように、絶縁層10上、及び絶縁層11a、11b、11c、11d(ここでは不図示なので図1(a)参照)の上面と、側壁とにPVD(Physical Vapor Deposition)法またはCVD(Chemical Vapor Deposition)法によって膜厚が数〜数十nm程度の配線層13となる例えばWを形成する。配線材料成膜時には領域100の絶縁層11aの側壁に配線材料が成膜されやすいように成膜方法を調整すると良い。例えば、PVD法を用いる場合は、成膜時のバイアスを調整する。

【0022】

次に図3(b)に示すように、配線層13上にレジストを形成し、太幅配線領域200をカバーするようにリソグラフィによってパタニングする。これにより、太幅配線領域200における配線層13上にレジスト14が形成される。

【0023】

次に図3(c)に示すように、レジスト14をマスクとして用いて、RIE等により配線層13をエッチバックする。そしてアッシング等により、レジスト14を除去する。これにより、領域100の絶縁層11aの側壁には配線層13aが形成され、領域200には、配線層13bが除去されずに残る。そして、領域300において、絶縁層11bの領域100側の側壁には、配線層13aが形成され、領域200側の上面及び側壁には配線層13bが形成されている。

【0024】

次に、図4に示すように、全面に絶縁層15が形成される。領域100において、絶縁層15、及び11aの一部をRIE等の異方性エッチングで除去して、配線層13aの上部を露出するコンタクトホール16aが形成される。また、領域200において、絶縁層15の一部を、RIE等の異方性エッチングで除去して、絶縁層11c(大パタン)上方の配線層13bを露出するコンタクトホール16bが形成される。このコンタクトホール16a、及び16bは同時に形成される。そして、図1に示すように、それぞれのコンタクトホール内にW等のダマシンができるメタルを埋め込むことで、領域100にコンタクトプラグ17aが形成され、領域200にコンタクトプラグ17bが形成される。また、配線層13bは配線層13aとは異なりエッチングされないので、エッチングコンタクトプラグ17aの頂部は、コンタクトプラグ17bの頂部よりも低い位置にある。

【0025】

<比較例>

ここで、図14を用いて、実施形態の比較例に係る半導体装置について簡単に説明する。

【0026】

図14に示すように、比較例に係る半導体装置は、細幅配線領域100と、太幅配線領域200と、領域300とを備えている。領域100は、側壁配線が形成されている領域である。領域200は、周辺回路等に用いられる配線が形成されている領域である。領域300は、領域100と、領域200との間に設けられ、配線が形成されない領域である。

【0027】

細幅配線領域100において、絶縁層10上には、第2の方向に延伸するラインアンドスペース状にパタニングされた絶縁層11aが形成されている。また、絶縁層11aの側壁には高さが数十〜数百nm程度である配線層13aが形成され、配線層13aの上部にはコンタクトプラグ17aが形成されている。そして、絶縁層10、絶縁層11a、及び配線層13aを覆う絶縁層15が形成されている。コンタクトプラグ17aは、この絶縁層15内に形成され、配線層13aに接続されている。

領域200において、絶縁層10上には、膜厚が数〜数十nm程度の配線層13dが形成され、配線層13d上にはコンタクトプラグ17bが形成されている。そして、配線層13bを覆う絶縁層15が形成されている。

また、領域300において、絶縁層10上には絶縁層15が形成されている。

【0028】

領域200の配線層13dは、領域100の配線層13aと同時に形成される。このため、配線層13dの膜厚は、配線層13aの幅や、配線層13a形成時における配線材料のエッチング量等で決まる。近年の微細化が進んでいる半導体装置において、配線13aの幅は狭くすることが望ましく、配線層13dの膜厚を充分に確保することができない。そのため、領域100の、コンタクトプラグ17aが形成される配線層13aの高さと、領域200の、コンタクトプラグ17bが形成される配線層13bの高さとの差が大きくなる。この結果、領域100及び領域200に形成される配線層の高さが異なり、コンタクトプラグ17a及び17bを形成するための、コンタクトホール形成時のエッチングの制御が困難である。

【0029】

また、領域300においては、領域100及び200とは異なり、絶縁層15しか形成されないので、領域100、200、及び300の間の絶縁層15の表面(不図示)における平坦性が悪くなってしまうこともある。

【0030】

<実施形態の作用効果>

上述した実施形態によれば、半導体装置は、第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域100に設けられた第1の絶縁層10上に形成されたラインアンドスペース状の第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層10上に形成され、第2の絶縁層11aと略同一の高さを有する第3の絶縁層11cと、第1の領域100に設けられた第1の絶縁層10上及び第2の絶縁層11aの側壁に形成された第1の配線層13aと、第2の領域200に設けられた第1の絶縁層10上、及び第3の絶縁層11cの上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層10、第2の絶縁層11a、第1の配線層13a、及び第2の配線層13bを覆う第4の絶縁層15と、第1の領域100に設けられた第4の絶縁層15内に形成され、第1の配線層13aに接続された第1のコンタクトプラグ17aと、第2の領域200に設けられた第4の絶縁層15内に形成され、第2の配線層13bに接続された第2のコンタクトプラグ17bと、を備える。第3の絶縁層11cは、第2のコンタクトプラグ17bと第2の配線13bとが接触している面積よりも面積の大きいパタン(大パタン部)を有している。また、第2のコンタクトプラグは、該大パタン部上方の第2の配線と接続されている。

【0031】

このように、細幅配線領域100においては、配線間隔の微細化に伴い、側壁加工用に芯材となる絶縁層11aが形成されている。そして、太幅配線領域200においても、芯材となる絶縁層11cを形成することで、絶縁層11の側壁にも配線層13bが形成される。そのため、配線層13bの電気伝導方向に垂直な断面の断面積が比較例で示した配線層13dよりも大きくなり、配線抵抗を減少させることができる。

【0032】

また、絶縁層11aの高さと絶縁層11cの高さとが実質的に同じであるため、細幅配線領域100におけるコンタクトプラグが接続される配線層13aの高さと、太幅配線領域200のコンタクトプラグが接続される配線層13cの高さとはほぼ同等になる。その結果、細幅配線領域100、及び太幅配線領域200において、同時にコンタクトプラグを形成することが容易となる。

【0033】

更に、第3の領域は、第1の絶縁層10上に形成され、第2の絶縁層11aと略同一の高さを有し、第4の絶縁膜で覆われた第5の絶縁層11bが設けされている。このように、実質的に何も形成されない領域300にも芯材となる付加的な絶縁層を形成することで、領域100〜300に絶縁層15を形成した際に、絶縁層15の平坦性を向上させることができる。

【0034】

上述したように、本実施形態では、配線抵抗が抑制された高品質な細幅配線領域と、太幅配線領域とを有する半導体装置(配線)を得ることができる。

【0035】

<第1の実施形態の変形例>

(変形例1)

尚、図5に示すように、太幅配線領域200に大パタン部11cを有する絶縁層の代わりに、細幅配線領域100と同様のラインアンドスペース状の絶縁層11eが形成されても良い。変形例1に係る基本的な製造方法は、上述した第1の実施形態とほぼ同様なので、詳細な説明は省略する。変形例1では、図2(a)に示す工程において、太幅配線領域200のレジスト12を、例えば細幅領域100のレジスト12aと同様のラインアンドスペース状のパタンにすることで、絶縁層11eを形成することが可能である。

【0036】

このように、第4の絶縁層11cを、ラインアンドスペース状としても、上述した第1の実施形態と同様に、比較例の配線層13dの場合と比べて、太幅配線領域200の配線層13cの断面積を充分に確保できる。これにより、上述した第1実施形態と同様に、配線層13cにおいて配線抵抗を抑制することができる。

【0037】

また、変形例1の配線層13cは、上述した第1の実施形態と同様に、細幅配線領域100の配線層13a及び太幅配線領域200の配線層13cの高さは、ほぼ同じである。そのため、第1の実施形態と同様に、比較例と比べてコンタクトプラグ17a、17bの形成が容易である。

【0038】

更に、上述した第1の実施形態と同様に、領域300には、領域100、200に形成された絶縁層11a、及び11eと同じ高さの大パタン部11bが形成されているので、絶縁層15の上面の平坦性の悪化を抑制することが可能である。

【0039】

尚、太幅配線領域200の絶縁層11eの幅や、本数は適宜変更可能である。絶縁層11eの幅をより細くし、本数を増やすことで、絶縁層11eを覆う配線層13cの電気伝導方向断面の金属膜の断面積がより大きくなるので、配線抵抗の抑制の観点で好ましい。

【0040】

(変形例2)

次に、図6を用いて、上述した第1の実施形態の変形例2について説明する。変形例2は、領域300に大パタンの絶縁層が形成されないという点で、第1の実施形態と異なっている。

【0041】

しかし、変形例2の配線層13bは、上述した第1の実施形態と同様に、比較例の配線層13dの場合と比べて、太幅配線領域200の配線層13cの断面積を充分に確保できる。これにより、上述した第1実施形態と同様に、配線層13bにおいて抵抗値を低下することができる。

【0042】

また、変形例2の配線層13bは、上述した第1の実施形態と同様に、細幅配線領域100の配線層13a及び太幅配線領域200の配線層13bの高さは、ほぼ同じである。そのため、第1の実施形態と同様に、比較例と比べてコンタクトプラグ17a、17bの形成が容易である。

【0043】

(変形例3)

次に、図7を用いて、上述した第1の実施形態の変形例3について説明する。変形例3は、領域300に大パタンの絶縁層が形成されず、太幅配線領域200に大パタン部11cを有する絶縁層の代わりに、細幅配線領域100と同様のラインアンドスペース状の絶縁層11eが形成されているという点で第1の実施形態と異なっている。

【0044】

これにより、変形例1では、上述した第1の実施形態と同様に、比較例の配線層13dの場合と比べて、太幅配線領域200の配線層13cの断面積を充分に確保できる。これにより、上述した第1実施形態と同様に、配線層13cにおいて抵抗値を低下することができる。

【0045】

また、変形例1の配線層13cは、上述した第1の実施形態と同様に、細幅配線領域100の配線層13a及び太幅配線領域200の配線層13cの高さは、ほぼ同じである。そのため、第1の実施形態と同様に、比較例と比べてコンタクトプラグ17a、17bの形成が容易である。

【0046】

尚、細幅配線領域100における配線層13a及びコンタクトプラグ17aは、図8(a)、及び図8(b)に示すように、側壁配線層13aに接触するコンタクトプラグ17aの底面と、側壁配線層13aの上面との距離d1が大きくなるほど、コンタクトプラグ17aと、側壁配線層13aとの接触面積が大きくなる。このd1の調整方法としては、上述した第1の実施形態で説明した図4のコンタクトホール16a、16bの形成の際、例えばエッチング時間を調整する方法等がある。d1が大きくなるほど(コンタクトプラグ17aと、側壁配線層13aとの接触面積が大きくなるほど)、コンタクト抵抗を抑制することができるようになる。

【0047】

また、図8(c)に示すように、細幅配線領域100における、ラインアンドスペース状の側壁配線層13a間の絶縁膜15に、エアギャップ15aを設けても良い。このエアギャップ15aの形成方法としては、上述した第1の実施形態で説明した図4の絶縁層15の形成の際、埋め込み性の悪い膜種、または成膜方法を用いることで、形成することができる。エアギャップ15aを側壁配線層13a間に形成することで、配線間容量を低減することが可能である。

【0048】

(第2の実施形態)

次に、図9を用いて、第2の実施形態に係る半導体装置の基本的な構成について、概略的に説明する。この第2の実施形態は、例えば不揮発性メモリに、上述した第1の実施形態の配線を適用したものである。

【0049】

<第2の実施形態に係る半導体装置の構成>

図9に示すように、第2の実施形態に係る半導体装置(半導体記憶装置)は、細幅配線領域100と、太幅配線領域200と、領域300とを備えている。また、第2の実施形態に係る半導体装置は、メモリセルトランジスタ等を含む各種トランジスタが形成されるトランジスタ領域400、及び配線が形成される配線領域500に分けられる。尚、配線領域500に関しては、上述した第1の実施形態及び各変形例と同様なので、詳細な説明は省略する。

【0050】

トランジスタ領域400の細幅配線領域100において、例えば半導体基板(シリコン基板)20には第2方向に延びるストライプ形状の素子領域AAが、第2方向に沿って複数設けられている。隣接する素子領域AA間には第2方向に延びる素子分離領域(Shallow Trench Isolation:STI)21が形成され、この素子分離領域21によって素子領域AAは電気的に分離されている。半導体基板20上には、複数の素子領域AAを跨ぐようにして、第2の方向に直交する第1方向に延びたストライプ形状のワード線WL(不図示)及びセレクトゲート線SGD,SGS(不図示)が形成されている。ワード線WLと素子領域AAとが交差する領域には、電荷蓄積絶縁膜(不図示)が設けられている。そして、ワード線WLと素子領域AAとが交差する領域にはメモリセルトランジスタMT(不図示)が設けられ、セレクトゲート線SGD、SGSと素子領域AAとが交差する領域には、それぞれ選択トランジスタST(不図示)が設けられている。第2方向で隣接するワード線WL間、セレクトゲート線間、及びワード線WLとセレクトゲート線との間の素子領域AAには、メモリセルトランジスタMT及び選択トランジスタSTのソース領域またはドレイン領域となる不純物拡散層が形成されている。

【0051】

第2方向で隣接するセレクトゲート線SGD間の素子領域AAに形成される不純物拡散層は、選択トランジスタSTのドレイン領域として機能する。そしてこのドレイン領域上には例えばコンタクトプラグ(下層プラグ)25aが形成される。配線領域500の細幅配線領域100において、コンタクトプラグ25aは、第2方向に沿って設けられたストライプ形状のビット線BL(配線層13a)に接続される。このコンタクトプラグ25aは、配線層13a、及び絶縁層11aの下方に設けられる。換言すると、コンタクトプラグ25aは、配線層13a間の絶縁層15と接触しないように形成されている。

【0052】

第2方向で隣接するセレクトゲート線SGS間の素子領域AAに形成される不純物拡散層は、選択トランジスタSTのソース領域として機能する。そしてこのソース領域上には、コンタクトプラグ(不図示)が形成される。該コンタクトプラグは図示せぬソース線SL(不図示)に接続される。尚、コンタクトプラグ25aは、選択トランジスタSTのソース領域上に形成され、配線層13aは、ソース線SLであっても良い。

【0053】

トランジスタ領域400の太幅配線領域200において、素子分離領域(不図示)に囲まれた半導体基板20の表面領域内には、N又はP型の不純物が拡散された一対のソース/ドレイン領域(第1の不純物拡散領域)20aが形成されている。そして、一対のソース/ドレイン領域20aにチャネル領域が挟まれている。また、前記チャネル領域上にはゲート絶縁膜22となる、例えばシリコン酸化膜が形成されている。ゲート絶縁膜22上には電極膜23となる、例えばポリシリコンが形成されている。また、電極膜23上には電極膜24となる、例えばポリシリコンが形成されている。この電極膜23と電極膜24とは電気的に接続され、ゲート電極として機能する。

【0054】

そして、ソース/ドレイン領域20aの上にはコンタクトプラグ25bとなる導電材料が形成されている。配線領域500の太幅配線領域200において、コンタクトプラグ25bは、配線層13bに接続される。

【0055】

また、電極膜24上にはコンタクトプラグ25cとなる導電材料が形成されている。配線領域500の太幅配線領域200において、コンタクトプラグ25cは、コンタクトプラグ25bが接続される配線層とは別の配線層13bに接続される。

【0056】

<第2の実施形態に係る半導体装置の製造方法>

次に、図9〜12を用いて、第2の実施形態に係る半導体装置の基本的な製造方法について、概略的に説明する。尚、トランジスタ領域400の形成方法は周知のものなので、詳細な説明は省略する。また、配線領域500の形成方法は、第1の実施形態で説明したものと同様なので、詳細な説明は省略する。

【0057】

まず図10に示すように、周知の技術を用いて、図9で説明したトランジスタ領域400が形成される。

【0058】

次に、図11に示すように、図2〜図3で説明した方法と同様にして、配線領域500且つ細幅配線領域100における絶縁層10上に、ラインアンドスペース状のスリミングされた絶縁層11aを形成し、配線領域500且つ太幅配線領域200における絶縁層10上に、大パタン部(絶縁層)11cと、第2の方向に延伸する配線部(絶縁層)11d(不図示)とを有する絶縁層を形成する。また、配線領域500且つ領域300における絶縁層10上に、大パタン部(絶縁層)11bを形成する。そして、絶縁層10上、及び絶縁層11a、11b、11c、11dの上面と、側壁と配線層13を形成する。この際、コンタクトプラグ25aが、配線層13、及び絶縁層11aの下方に設けられように、絶縁層11aを配置する。また、コンタクトプラグ25b、25cがそれぞれ、絶縁層11cの間で配線層13と接続するように、絶縁層11cが配置される。

【0059】

次に、図12に示すように、図3(b)、3(c)で説明した方法と同様にして、細幅配線領域100において、RIE等により配線層13をエッチバックして、絶縁層11aの側壁に、ラインアンドスペース状の配線層13aを形成する。また、太幅配線領域200において、コンタクトプラグ25b、25cが接続される配線層13の一部をパタニングすることで、コンタクトプラグ25b、25cを電気的に分離する。

【0060】

そして、図4、及び1で説明したような方法によって、図9に記載の構成を得ることが可能となる。

【0061】

<第2の実施形態の作用効果>

上述した実施形態によれば、上述で説明した第1の実施形態及び各変形例の配線構造を不揮発性メモリに適応することが可能である。

【0062】

ところで、図15に示すように、コンタクトプラグ25aが、配線層13及び絶縁層11aの下方に設けられない場合、配線層13のエッチバック時に、コンタクトプラグ25aの一部が露出され、露出部がエッチングされてしますことがある。このため、コンタクトプラグ25aのエッチングされた一部はダメージを受けてしまう。

【0063】

しかし、第2の実施形態のコンタクトプラグ25aは、配線層13a、及び絶縁層11aの下方に設けられている。これにより、側壁配線層13aを形成するための配線層13のエッチバック時に露出されない。そのため、配線層13のエッチバック時においても、コンタクトプラグ25aはダメージを受けす、良好なコンタクトプラグ25aを得ることができる。

【0064】

(変形例)

また、上述で説明した各実施形態、及び各変形例で説明した配線は、図13に示すように、第2の実施形態で説明したような不揮発性メモリだけでなく、揮発性メモリ(DRAM等)にも用いることが可能である。

【0065】

図13に示すように、第2の実施形態の変形例に係る半導体装置は、細幅配線領域100と、太幅配線領域200と、領域300とを備えている。また、第2の実施形態の変形例に係る半導体装置は、各種トランジスタが形成されるトランジスタ領域400、及び配線が形成される配線領域500に分けられる。尚、配線領域500に関しては、上述した第1の実施形態及び各変形例と同様なので、詳細な説明は省略する。

【0066】

トランジスタ領域400の太幅配線領域200において、半導体基板20の表面領域内には、N又はP型の不純物が拡散された一対のソース/ドレイン領域(第1の不純物拡散領域)20aが形成されている。そして、一対のソース/ドレイン領域20aにチャネル領域が挟まれている。また、前記チャネル領域上にはゲート絶縁膜22となる、例えばシリコン酸化膜が形成されている。ゲート絶縁膜22上には電極膜23となる、例えばポリシリコンが形成されている。この電極膜23はゲート電極として機能する。

【0067】

そして、ソース/ドレイン領域20aの上にはコンタクトプラグ25dとなる導電材料が形成されている。配線領域500の太幅配線領域200において、コンタクトプラグ25dは、配線層26aに接続される。そして、配線領域500の細幅配線領域100まで延伸された配線層26aと、配線層13aとの間にコンタクトプラグ27aが形成される。この際、コンタクトプラグ27aは、図9で説明したコンタクトプラグ25aと同様に、配線層13a、及び絶縁層11aの下方に設けられる。

【0068】

また、電極膜23上にはコンタクトプラグ25eとなる導電材料が形成されている。配線領域500の太幅配線領域200において、コンタクトプラグ25eは、配線層26bに接続される。また配線層26bと配線層13cとの間にはコンタクトプラグ27bが形成されている。

【0069】

このように、揮発性メモリにおいても、上述した各実施形態、及び各変形例を適応することができる。そのため、各実施形態、及び各変形例と同様の理由で、各実施形態、及び各変形例と同様の効果を得ることができる。

【0070】

尚、上述した各実施形態及び各変形例において、太幅配線領域200に、絶縁層11aと略同じ高さの絶縁層11c、d、e等を形成している。しかし、これに限らず、絶縁層11aと略同じ高さの絶縁層であれば、どのようなパタンでもかまわない。

【0071】

また、上述した各実施形態において、領域300に、芯材となる大パタンの絶縁層11bを形成している。配線を覆う絶縁層15の表面の平坦性を保つことができるのであれば、絶縁層11bのパタン形状はどのような形状でもかまわない。

【0072】

また、上述した第1の実施形態の変形例1、3及び第2の実施形態の変形例で説明した、太幅配線領域200における、ラインアンドスペース状の絶縁層11eの延伸方向は、細幅配線領域100における絶縁層11aと平行である。しかし、これに限らず、絶縁層11a、及び11eはかならずしも平行である必要はない。

【0073】

以上、本発明の実施形態を説明したが、本発明は上記実施形態に限定されるものではなく、その趣旨を逸脱しない範囲内において種々変形して実施することが可能である。さらに、上記実施形態には種々の段階の発明が含まれており、開示された構成要件を適宜組み合わせることによって種々の発明が抽出される。例えば、開示された構成要件からいくつかの構成要件が削除されても、所定の効果が得られるものであれば、発明として抽出され得る。

【符号の説明】

【0074】

10…絶縁層、 11a、11b、11c、11d、11e…絶縁層

12、12a、12b、12c…レジスト、 13、13a、13b、13c…配線層

14…レジスト、 15…絶縁層、 15a…エアギャップ

16a、16b…コンタクトホール、 17a、17b…コンタクトプラグ

20…半導体基板、 20a…ドレイン領域、 21…素子分離領域

22…ゲート絶縁膜、 23、24…電極膜

25a、25b、25c、25d、25e…コンタクトプラグ

26a、26b…配線層、 27a、27b…コンタクトプラグ

100…細幅配線領域、 200…太幅配線領域、 300…領域

400…トランジスタ領域、 500…配線領域。

【特許請求の範囲】

【請求項1】

第1の領域及び第2の領域に設けられた第1の絶縁層と、

前記第1の領域に設けられた前記第1の絶縁層上に形成されたラインアンドスペース状の第2の絶縁層と、

前記第2の領域に設けられた前記第1の絶縁層上に形成され、前記第2の絶縁層と略同一の高さを有する第3の絶縁層と、

前記第1の領域に設けられた前記第1の絶縁層上及び前記第2の絶縁層の両方の側壁に形成された第1の配線層と、

前記第2の領域に設けられた前記第1の絶縁層上、及び前記第3の絶縁層の上面及び側壁上に形成された第2の配線層と、

前記第1の絶縁層、前記第2の絶縁層、前記第1の配線層、及び前記第2の配線層を覆う第4の絶縁層と、

前記第1の領域に設けられた前記第4の絶縁層内に形成され、前記第1の配線層に接続された第1のコンタクトプラグと、

前記第2の領域に設けられた前記第4の絶縁層内に形成され、前記第2の配線層に接続された第2のコンタクトプラグと、

を備えることを特徴とする半導体装置。

【請求項2】

第3の領域に設けられた前記第1の絶縁層上に形成され、前記第2の絶縁層と略同一の高さを有し、前記第4の絶縁膜で覆われた第5の絶縁層を更に備えることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第3の絶縁層は、前記第2のコンタクトプラグと前記第2の配線とが接触している面積よりも面積の大きいパタンを有することを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

前記第4の絶縁層は、ラインアンドスペース状であることを特徴とする請求項1または2に記載の半導体装置。

【請求項5】

前記第1の配線層の頂部は、前記第2の絶縁層の頂部よりも低い位置にあることを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

【請求項6】

第1の領域に設けられた第1の絶縁層上にラインアンドスペース状の第2の絶縁層を形成し、第2の領域に設けられた第1の絶縁層上に第3の絶縁層を形成することと、

前記第1の領域に設けられた前記第1の絶縁層上、及び前記第2の絶縁層の側壁上に第1の配線層を形成し、前記第2の領域に設けられた前記第1の絶縁層上、前記第3の絶縁層の上面、及び側壁上に第2の配線層を形成することと、

前記第1の絶縁層、前記第2の絶縁層、前記第1の配線層、及び前記第2の配線層を覆う第4の絶縁層を形成することと、

前記第1の領域に設けられた前記第1の配線層に接続されるように前記第4の絶縁層内に第1のコンタクトプラグを形成し、前記第2の領域に設けられた前記第2の配線層に接続されるように前記第4の絶縁層内に第2のコンタクトプラグを形成することと

を備えることを特徴とする半導体装置の製造方法。

【請求項1】

第1の領域及び第2の領域に設けられた第1の絶縁層と、

前記第1の領域に設けられた前記第1の絶縁層上に形成されたラインアンドスペース状の第2の絶縁層と、

前記第2の領域に設けられた前記第1の絶縁層上に形成され、前記第2の絶縁層と略同一の高さを有する第3の絶縁層と、

前記第1の領域に設けられた前記第1の絶縁層上及び前記第2の絶縁層の両方の側壁に形成された第1の配線層と、

前記第2の領域に設けられた前記第1の絶縁層上、及び前記第3の絶縁層の上面及び側壁上に形成された第2の配線層と、

前記第1の絶縁層、前記第2の絶縁層、前記第1の配線層、及び前記第2の配線層を覆う第4の絶縁層と、

前記第1の領域に設けられた前記第4の絶縁層内に形成され、前記第1の配線層に接続された第1のコンタクトプラグと、

前記第2の領域に設けられた前記第4の絶縁層内に形成され、前記第2の配線層に接続された第2のコンタクトプラグと、

を備えることを特徴とする半導体装置。

【請求項2】

第3の領域に設けられた前記第1の絶縁層上に形成され、前記第2の絶縁層と略同一の高さを有し、前記第4の絶縁膜で覆われた第5の絶縁層を更に備えることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第3の絶縁層は、前記第2のコンタクトプラグと前記第2の配線とが接触している面積よりも面積の大きいパタンを有することを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

前記第4の絶縁層は、ラインアンドスペース状であることを特徴とする請求項1または2に記載の半導体装置。

【請求項5】

前記第1の配線層の頂部は、前記第2の絶縁層の頂部よりも低い位置にあることを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

【請求項6】

第1の領域に設けられた第1の絶縁層上にラインアンドスペース状の第2の絶縁層を形成し、第2の領域に設けられた第1の絶縁層上に第3の絶縁層を形成することと、

前記第1の領域に設けられた前記第1の絶縁層上、及び前記第2の絶縁層の側壁上に第1の配線層を形成し、前記第2の領域に設けられた前記第1の絶縁層上、前記第3の絶縁層の上面、及び側壁上に第2の配線層を形成することと、

前記第1の絶縁層、前記第2の絶縁層、前記第1の配線層、及び前記第2の配線層を覆う第4の絶縁層を形成することと、

前記第1の領域に設けられた前記第1の配線層に接続されるように前記第4の絶縁層内に第1のコンタクトプラグを形成し、前記第2の領域に設けられた前記第2の配線層に接続されるように前記第4の絶縁層内に第2のコンタクトプラグを形成することと

を備えることを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2013−42011(P2013−42011A)

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願番号】特願2011−178468(P2011−178468)

【出願日】平成23年8月17日(2011.8.17)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願日】平成23年8月17日(2011.8.17)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]