半導体装置及びその製造方法

【課題】トランジスタの集積度が高い半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、を備える。そして、前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なる。

【解決手段】実施形態に係る半導体装置は、第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、を備える。そして、前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、電子のスピンを利用してデータを記憶する新たな記憶装置として、MRAM(Magneto resistive Random Access Memory:磁気抵抗ランダムアクセスメモリ)が提案されている。MRAMにおいては、複数個のメモリセルがアレイ状に配列されており、各メモリセルにおいては、磁気抵抗記憶素子及びトランジスタが設けられている。MRAMにおいて、メモリセルの集積度を向上させるためには、所定のオン電流を確保しつつ、トランジスタを微細化することが必要となる。

【0003】

一方、MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor:金属酸化物半導体電界効果トランジスタ)の集積度の向上とオン電流の増大とを両立させるために、Fin型のMOSFET(以下、「FinFET」という)が提案されている。FinFETにおいては、半導体基板の上面に一方向に延びる凸状のフィンが形成されており、このフィンを跨ぐように、他方向に延びるゲート電極が設けられている。これにより、フィンにおけるゲート電極により囲まれた部分の外周がチャネル領域となり、素子面積を増大させることなく、チャネル幅を拡大することができる。

【0004】

そこで、MRAMのメモリセルの集積度を向上させるために、MRAMに形成されるトランジスタをFinFETとすることが考えられる。しかしながら、この場合は、MRAMを構成する複数種類のトランジスタの閾値を、それぞれ最適な値に調整することが困難になるという問題点がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−34427号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の目的は、トランジスタの集積度が高い半導体装置及びその製造方法を提供することである。

【課題を解決するための手段】

【0007】

実施形態に係る半導体装置は、第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、を備える。そして、前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なる。

【0008】

実施形態に係る半導体装置の製造方法は、半導体基板を選択的に除去することにより、第1領域に第1方向に延びる複数本のフィンを形成する工程と、前記フィン間の部分の下部に素子分離絶縁膜を埋め込む工程と、前記フィンにおける前記素子分離絶縁膜から突出した部分の表面上に第1ゲート絶縁膜を形成する工程と、前記フィン及び前記素子分離絶縁膜上に第1導電膜を形成する工程と、前記第1導電膜を選択的に除去することにより、前記第1領域において、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極を形成すると共に、第2領域において、前記第1導電膜を除去する工程と、前記半導体基板の上面における前記第2領域上に第2ゲート絶縁膜を形成する工程と、第2導電膜を形成する工程と、前記第2導電膜を選択的に除去することにより、前記第2ゲート絶縁膜上に第2ゲート電極を形成する工程と、を備える。

【図面の簡単な説明】

【0009】

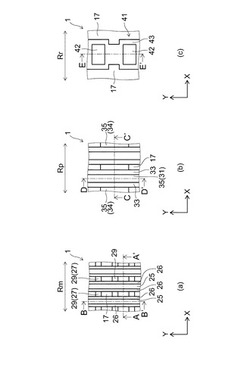

【図1】(a)〜(c)は、実施形態に係る半導体装置を例示する平面図である。

【図2】(a)〜(e)は、実施形態に係る半導体装置を例示する断面図である。

【図3】(a)及び(b)は、実施形態に係る半導体装置におけるメモリアレイ領域を例示する模式的断面図である。

【図4】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図5】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図6】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図7】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図8】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図9】(a)〜(c)は、実施形態に係る半導体装置の製造方法を例示する工程平面図である。

【図10】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図11】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図12】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図13】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図14】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図15】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図16】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図17】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【発明を実施するための形態】

【0010】

以下、図面を参照しつつ、本発明の実施形態について説明する。

図1(a)〜(c)は、本実施形態に係る半導体装置を例示する平面図であり、(a)はメモリアレイ領域を示し、(b)は周辺回路領域を示し、(c)は抵抗素子領域を示し、

図2(a)〜(e)は、本実施形態に係る半導体装置を例示する断面図であり、(a)は図1(a)に示すA−A’線による断面図であり、(b)は図1(a)に示すB−B’線による断面図であり、(c)は図1(b)に示すC−C’線による断面図であり、(d)は図1(b)に示すD−D’線による断面図であり、(e)は図1(c)に示すE−E’線による断面図であり、

図3(a)及び(b)は、本実施形態に係る半導体装置におけるメモリアレイ領域を例示する模式的断面図である。

なお、図示の便宜上、図1及び図2においては、層間絶縁膜及びそれより上方の上部構造が省略されている。また、図3においては、原則として導電部分のみを示し、絶縁部分は省略されている。

【0011】

図1(a)〜(c)及び図2(a)〜(e)に示すように、本実施形態に係る半導体装置1は、メモリアレイ領域Rm、周辺回路領域Rp及び抵抗素子領域Rrが設定された半導体記憶装置であり、より具体的にはMRAMである。メモリアレイ領域Rmにおいては、複数個のメモリセルが設けられており、各メモリセルにデータが記憶される。周辺回路領域Rpにおいては、メモリセルを駆動する周辺回路が設けられている。抵抗素子領域Rrにおいては、抵抗素子が設けられている。この抵抗素子は、例えば、周辺回路に接続されている。

【0012】

半導体装置1においては、シリコン基板11が設けられている。但し、シリコン基板11の上面11aは、上述の各領域毎に異なった加工が施されている。

メモリアレイ領域Rmにおいては、シリコン基板11の上面11aに一方向(以下、「X方向」という)に延びる複数本の溝12が形成されている。これにより、シリコン基板11の上層部分における溝12間の部分はフィン13となっている。フィン13は複数本形成され、周期的に配列されており、各フィン13はX方向に延びている。フィン13の上面上には、シリコン窒化膜14が設けられている。

【0013】

周辺回路領域Rpにおいては、シリコン基板11の上面11aに枠状の溝15が形成されている。シリコン基板11の上層部分における溝15によって囲まれた部分は能動部分16となっている。能動部分16は例えば複数形成されており、溝15によって区画されている。

抵抗素子領域Rrにおいては、シリコン基板11の上層部分が除去されている。これにより、抵抗素子領域Rrにおけるシリコン基板11の上面11aは、メモリアレイ領域Rmにおけるフィン13の上端及び周辺回路領域Rpにおけるシリコン基板11の上面11aよりも下方に位置しており、メモリアレイ領域Rmにおける溝12の底面及び周辺回路領域Rpにおける溝15の底面と同じ高さに位置している。

【0014】

シリコン基板11上には、例えばシリコン酸化物等の絶縁材料からなる素子分離絶縁膜17が設けられている。素子分離絶縁膜17は、メモリアレイ領域Rmにおいては、溝12の下部に配置されており、周辺回路領域Rpにおいては、溝15内に配置されており、抵抗素子領域Rrにおいては、シリコン基板11上に配置されている。周辺回路領域Rp及び抵抗素子領域Rrにおける素子分離絶縁膜17の上面17aの高さは相互に等しく、フィン13の上端及び能動部分16の上面16aの高さと一致している。また、メモリアレイ領域Rmにおける素子分離絶縁膜17の上面17aは、周辺回路領域Rp及び抵抗素子領域Rrにおける素子分離絶縁膜17の上面17aよりも下方に位置している。

【0015】

メモリアレイ領域Rmにおいては、シリコン基板11及び素子分離絶縁膜17上に、複数本のゲート電極21が周期的に設けられている。各ゲート電極21はX方向に対して直交した方向(以下、「Y方向」という)に延び、フィン13を跨いでいる。すなわち、ゲート電極21の下端は、フィン13の上端よりも下方に位置している。ゲート電極21の下部22は、不純物を含有するポリシリコンによって形成されている。ゲート電極21の上部23は、例えばタングステン等の金属によって形成されている。下部22と上部23との界面は平面であり、例えば、フィン13の上端面と同じ高さにある。なお、X方向及びY方向の双方に対して直交する方向、すなわち、上下方向を、「Z方向」とする。

【0016】

フィン13とゲート電極21との間には、ゲート絶縁膜24が設けられている。ゲート絶縁膜24は、フィン13における素子分離絶縁膜17の上面17aから突出した部分の側面を覆っている。各ゲート電極21の直上域には、例えばシリコン窒化物からなるハードマスク材25が設けられている。ゲート電極21及びハードマスク材25からなる積層体28の側面上には、例えばシリコン窒化物等の絶縁材料からなる側壁26が設けられている。フィン13におけるゲート電極21及び側壁26の直下域間の部分には、不純物が導入されたソース・ドレイン領域27が形成されている。すなわち、隣り合う一対のソース・ドレイン領域27は、フィン13におけるゲート電極21の直下域を挟んでいる。ソース・ドレイン領域27の上層部分には、シリサイド層29が形成されている。これにより、フィン13とゲート電極21との最近接点毎に、FinFETが構成されている。従って、メモリアレイ領域Rmにおいては、複数個のFinFETがマトリクス状に配列されている。これらのFinFETの電気的特性は、ほぼ均一である。

【0017】

周辺回路領域Rpにおいては、シリコン基板11及び素子分離絶縁膜17上に、能動部分16の直上域を横切るように、一方向に延びるゲート電極31が設けられている。1つの能動部分16の直上域を、例えば2本のゲート電極31が横切っている。なお、図1及び図2においては、ゲート電極31が延びる方向をY方向としているが、これには限定されない。ゲート電極31は、例えば、シリコンを含む導電性材料からなり、例えば、不純物を含有するポリシリコンによって形成されている。能動部分16とゲート電極31との間には、ゲート絶縁膜32が設けられている。能動部分16の上面及びゲート電極31の下面はそれぞれ平坦である。すなわち、ゲート電極31の下面は、能動部分16の上面よりも上方に位置している。従って、ゲート絶縁膜32の形状も平面状である。

【0018】

また、各ゲート電極31の両側面上には、例えばシリコン窒化物からなる側壁33が設けられている。能動部分16の上層部分におけるゲート電極31及び側壁33の直下域を挟む部分には、不純物が導入されたソース・ドレイン領域34が形成されている。ゲート電極31の上層部分及びソース・ドレイン領域34の上層部分には、例えばニッケルシリサイド等のシリサイドからなるシリサイド層35が形成されている。能動部分16の上層部分におけるゲート電極31の直下域に相当する部分、すなわち、一対のソース・ドレイン領域34によって挟まれた部分は、チャネル領域となっている。このようにして、能動部分16、ゲート絶縁膜32及びゲート電極31により、平面型のMOSFETが構成されている。周辺回路領域Rpに形成された複数個の平面型MOSFETはいくつかの種類に分けられ、その電気的特性は、その種類間で異なっている。これらの平面型MOSFETにより、周辺回路が構成されている。

【0019】

抵抗素子領域Rrにおいては、素子分離絶縁膜17上に、例えば不純物を含有したポリシリコンからなる抵抗部材41が設けられている。抵抗部材41の形状は略直方体であり、例えば、長手方向の中央部の幅は両端部の幅よりも狭い。抵抗部材41及びゲート電極31は、同じポリシリコン膜を加工して形成されたものであり、従って、組成及び厚さは相互に等しい。抵抗部材41の両端部の上面上には、シリサイド層42が形成されている。シリサイド層42及び35は、同じ処理によって形成されたものであり、従って、組成及び厚さは相互にほぼ等しい。抵抗部材41の上面のうち、シリサイド層42が形成されていない領域上、及び抵抗部材41の側面上には、絶縁膜43が設けられている。絶縁膜43は側壁33と同時に形成されたものであり、従って、組成が相互に等しい。

【0020】

フィン13、ゲート電極21、ゲート電極31及び抵抗部材41等を覆うように、層間絶縁膜(図示せず)が設けられている。

図3(a)及び(b)に示すように、メモリアレイ領域Rmにおいては、フィン13におけるゲート電極21の直下域を挟む2つの部分、すなわち、ソース・ドレイン領域27が形成された部分の直上域には、コンタクト51a及び51bが設けられている。コンタクト51a上には磁気抵抗記憶素子52が設けられており、コンタクト51b上にはビア53が設けられている。これにより、各FinFETを構成する一対のソース・ドレイン領域27のうち、一方のソース・ドレイン領域27はコンタクト51aを介して磁気抵抗記憶素子52に接続されており、他方のソース・ドレイン領域27はコンタクト51bを介してビア53に接続されている。磁気抵抗記憶素子52は、特定方向のスピンを持つ電子が注入されることにより電気抵抗値が変化し、これによってデータを記憶する素子である。

【0021】

磁気抵抗記憶素子52及びビア53の上方には、Y方向を長手方向とする短冊状の中間配線54が設けられている。隣り合うフィン13に接続された磁気抵抗記憶素子52とビア53とは、中間配線54を介して相互に接続されている。中間配線54上であってビア53の直上域には、ビア55が設けられている。ビア55上には、X方向に延びる上層配線56が設けられている。中間配線54は、ビア55を介して上層配線56に接続されている。そして、1つのFinFET及び1つの磁気抵抗記憶素子52により、1つのメモリセルが形成されている。すなわち、上述のFinFETはセルトランジスタである。

【0022】

次に、本実施形態に係る半導体装置の製造方法について説明する。

図4〜図8、図10〜図17は、本実施形態に係る半導体装置の製造方法を例示する工程断面図であり、各図の(a)は図1(a)に示すA−A’線による断面図に相当し、(b)は図1(a)に示すB−B’線による断面図に相当し、(c)は図1(b)に示すC−C’線による断面図に相当し、(d)は図1(b)に示すD−D’線による断面図に相当し、(e)は図1(c)に示すE−E’線による断面図に相当し、

図9(a)〜(c)は、本実施形態に係る半導体装置の製造方法を例示する工程平面図であり、(a)はメモリアレイ領域を示し、(b)は周辺回路領域を示し、(c)は抵抗素子領域を示す。

なお、図10(a)は図9(a)に示すA−A’線による断面図であり、(b)は図9(a)に示すB−B’線による断面図であり、(c)は図9(b)に示すC−C’線による断面図であり、(d)は図9(b)に示すD−D’線による断面図であり、(e)は図9(c)に示すE−E’線による断面図である。

【0023】

先ず、図4(a)〜(e)に示すように、シリコン基板11を用意する。次に、シリコン基板11上にシリコン窒化膜14を形成する。

次に、図5(a)〜(e)に示すように、シリコン窒化膜14上にマスクパターン(図示せず)を形成する。メモリアレイ領域Rmにおいては、マスクパターンは側壁法により形成する。そして、このマスクパターンをマスクとしてエッチングを施すことにより、シリコン窒化膜14及びシリコン基板11の上層部分を選択的に除去する。これにより、メモリアレイ領域Rmにおいては、シリコン基板11の上面にX方向に延びる溝12を複数本形成し、シリコン基板11における溝12間の部分をフィン13とする。周辺回路領域Rpにおいては、シリコン基板11の上面に枠状の溝15を形成し、シリコン基板11における溝15によって囲まれた部分を能動部分16とする。抵抗素子領域Rrにおいては、シリコン基板11の上面11aを後退させて、例えば溝12の底面と同じ高さとする。このとき、全てのフィン13について、その幅及び間隔は相互に同一とする。一方、複数の能動部分16については、その形状を相互に異ならせてもよい。

【0024】

次に、図6(a)〜(e)に示すように、全面にシリコン酸化物を堆積させて、加熱することによって焼き締め(Densify)を行う。これにより、シリコン基板11及びシリコン窒化膜14上に素子分離絶縁膜17を形成する。次に、シリコン窒化膜14をストッパとしてCMP(chemical mechanical polishing:化学的機械研磨)等の平坦化処理を施して、素子分離絶縁膜17の上面17aを平坦化すると共に、シリコン窒化膜14の上面と同じ高さとする。

【0025】

次に、図7(a)〜(e)に示すように、メモリアレイ領域Rmにおいて素子分離絶縁膜17をリセスし、上面17aを後退させる。この結果、フィン13の上部が素子分離絶縁膜17から突出し、露出する。次に、酸化処理を施す。これにより、フィン13の上部の側面上に、シリコン酸化物からなるゲート絶縁膜24が形成される。

【0026】

次に、図8(a)〜(e)に示すように、不純物が添加されたポリシリコン膜62を全面に成膜し、CMPを施す。これにより、ポリシリコン膜62は溝12内の上部に埋め込まれる。このとき、ポリシリコン膜62は、シリコン基板11及び素子分離絶縁膜17の上方から除去されてもよく、残留してもよい。図8(a)〜(e)には、ポリシリコン膜62が、フィン13を含むシリコン基板11及び素子分離絶縁膜17の上方から完全に除去され、溝12内のみに残留した場合を示している。次に、全面に金属、例えば、タングステンを堆積させて、全面に金属膜63を形成する。次に、全面にシリコン窒化物を堆積させて、全面にシリコン窒化膜65を形成する。

【0027】

次に、図9(a)〜(c)及び図10(a)〜(e)に示すように、メモリアレイ領域Rmにおいて、シリコン窒化膜65上にマスクパターン(図示せず)を形成する。このマスクパターンには、側壁法により、Y方向に延びるライン状のパターンを複数本形成する。一方、周辺回路領域Rp及び抵抗素子領域Rrには、マスクパターンを形成しない。

【0028】

次に、このマスクパターンをマスクとして、シリコン窒化膜65、金属膜63及びポリシリコン膜62をエッチングする。このとき、フィン13の直上域においては、シリコン窒化膜14においてエッチングが停止する。これにより、メモリアレイ領域Rmにおいて、シリコン窒化膜65がY方向に延びる複数本のハードマスク材25に加工されると共に、金属膜63及びポリシリコン膜62がゲート電極21に加工される。この結果、金属膜63はゲート電極21の上部23となり、ポリシリコン膜62はゲート電極21の下部22となる。一方、周辺回路領域Rp及び抵抗素子領域Rrにおいては、シリコン窒化膜65、金属膜63及びポリシリコン膜62が除去される。

【0029】

次に、図11(a)〜(e)に示すように、全面に例えばシリコン窒化物等の絶縁材料を堆積させて、絶縁膜を成膜する。次に、この絶縁膜をパターニングすることにより、メモリアレイ領域Rmに残留させると共に、周辺回路領域Rp及び抵抗素子領域Rrから除去する。このとき、周辺回路領域Rp及び抵抗素子領域Rrからは、シリコン窒化膜14も除去される。この結果、メモリアレイ領域Rmにおいて、素子分離絶縁膜17上に、ゲート電極21及びハードマスク材25からなる積層体28を覆うように、側壁26が形成される。

【0030】

次に、図12(a)〜(e)に示すように、酸化処理を施すことにより、周辺回路領域Rpにおいて、シリコン基板11の能動部分16の上面16a上に、シリコン酸化物からなるゲート絶縁膜32を形成する。次に、不純物が添加されたポリシリコンを堆積させることにより、全面にポリシリコン膜66を形成する。ポリシリコン膜66は、積層体28の相互間にも埋め込まれる。

【0031】

次に、図13(a)〜(e)に示すように、ポリシリコン膜66上に反射防止膜(図示せず)及びマスクパターン(図示せず)を形成し、このマスクパターンをマスクとしてエッチングを施す。これにより、ポリシリコン膜66のうち、周辺回路領域Rpに配置された部分をゲート電極31に加工すると共に、抵抗素子領域Rrに配置された部分を抵抗部材41に加工する。また、ポリシリコン膜66のうち、メモリアレイ領域Rmに配置された部分は、積層体28の上方に位置する部分が除去され、積層体28の相互間に埋め込まれた部分は残留する。

【0032】

ゲート電極31は、一方向に延び、能動部分16の直上域を横切るようにライン状に加工する。このとき、形成しようとする平面型MOSFETの電気的特性に応じて、複数本のゲート電極31間で相互に幅を異ならせてもよい。また、抵抗部材41は、一方向に延びる略直方体形状に加工し、長手方向中央部の幅を長手方向両端部の幅よりも細くする。このとき、抵抗部材41によって実現しようとする抵抗値の大きさに応じて、抵抗部材41の形状を制御する。

【0033】

次に、図14(a)〜(e)に示すように、全面に、例えばシリコン窒化膜等の絶縁材料からなる絶縁膜68を形成する。このとき、絶縁膜68は、ゲート電極31の側面上及び抵抗部材41の側面上には形成されるが、積層体28間にはポリシリコン膜66が埋め込まれているため、積層体28の側面上には形成されない。次に、絶縁膜68上にハードマスク材69を形成し、パターニングすることにより、マスク材69を、抵抗部材41の上面上のうち、長手方向両端部における中央部分を除く領域に残留させる。

【0034】

次に、図15(a)〜(e)に示すように、絶縁膜68をエッチバックする。これにより、絶縁膜68は、メモリアレイ領域Rmの全体、周辺回路領域Rpにおけるゲート電極31、能動部分16及び素子分離絶縁膜17の上面上、並びに、抵抗素子領域Rrにおける素子分離絶縁膜17の上面上及び抵抗部材41の上面上におけるハードマスク材69によって覆われていない領域から除去されると共に、ゲート電極31の側面上、並びに、抵抗部材41の側面上及び抵抗部材41の上面におけるハードマスク材69の直下域に残留する。この結果、絶縁膜68が選択的に除去されて、ゲート電極31の側面上に側壁33が形成されると共に、抵抗部材41の上面におけるハードマスク材69によって覆われている領域上及び抵抗部材41の側面上に絶縁膜43が形成される。

【0035】

次に、図16(a)〜(e)に示すように、周辺回路領域Rp及び抵抗素子領域Rrを覆い、メモリアレイ領域Rmを露出させるようなマスク(図示せず)を形成し、これを用いてウェットエッチングを施すことにより、積層体28の相互間からポリシリコン膜66を除去する。

次に、図17(a)〜(e)に示すように、側壁26における積層体28の上面上に形成された部分を除去する。

【0036】

次に、図1(a)〜(c)、図2(a)〜(e)並びに図3(a)及び(b)に示すように、メモリアレイ領域Rmを開口したレジストマスク(図示せず)を形成し、このレジストマスク並びに積層体28及び側壁26をマスクとして不純物を注入する。これにより、フィン13における積層体28及び側壁26によって覆われていない部分に、ソース・ドレイン領域27が形成される。この結果、フィン13とゲート電極21との最近接点毎に、FinFETが形成される。

【0037】

次に、周辺回路領域Rpを開口したレジストマスク(図示せず)を形成し、このレジストマスク並びにゲート電極31及び側壁33をマスクとして不純物を注入する。これにより、能動部分16におけるゲート電極31及び側壁33によって覆われていない部分に、ソース・ドレイン領域34が形成される。この結果、能動部分16とゲート電極31との最近接点毎に、平面型のMOSFETが形成される。このとき、各MOSFETに要求される電気的特性に応じて、不純物の注入量及び注入深さを異ならせてもよい。

【0038】

次に、例えばニッケルを堆積させて、加熱処理を施すことにより、シリコンの露出面をシリサイド化する。これにより、ソース・ドレイン領域27の上層部分にシリサイド層29が形成され、ゲート電極31の上層部分及びソース・ドレイン領域34の上層部分にシリサイド層35が形成され、抵抗部材41における長手方向両端部の中央部分の上面にシリサイド層42が形成される。

【0039】

次に、全体に層間絶縁膜(図示せず)を成膜して、フィン13、ゲート電極21、ゲート電極31及び抵抗部材41等を覆う。次に、層間絶縁膜及びシリコン窒化膜14にコンタクトホールを形成し、その内部に導電材料を埋め込み、コンタクト51a及び51bを形成する。次に、コンタクト51a上に磁気抵抗記憶素子52を形成し、コンタクト51b上にビア53を形成する。次に、磁気抵抗記憶素子52及びビア53の上方に中間配線54を形成し、隣り合うフィン13に接続された磁気抵抗記憶素子52及びビア53を同一の中間配線54に共通接続する。次に、中間配線54上であってビア53の直上域にビア55を形成し、ビア55上に、X方向に延びる上層配線56を形成する。このようにして、本実施形態に係る半導体装置1が製造される。

【0040】

次に、本実施形態の効果について説明する。

本実施形態においては、図5(a)〜(e)に示す工程において、シリコン基板11を選択的に除去することにより、メモリアレイ領域Rmにフィン13を形成し、周辺回路領域Rpに能動部分16を形成している。

そして、図8(a)〜(e)に示す工程において、ポリシリコン膜62及び金属膜63を成膜し、図9(a)〜(c)及び図10(a)〜(e)に示す工程において、これらをパターニングすることにより、ゲート電極21を形成している。その後、図11(a)〜(e)に示す工程において、側壁26を形成することにより、メモリアレイ領域RmにFinFETを形成している。

【0041】

一方、図12(a)〜(e)に示す工程において、ポリシリコン膜66を成膜し、図13(a)〜(e)に示す工程において、これをパターニングすることにより、周辺回路領域Rpにゲート電極31を形成している。また、図14(a)〜(e)に示す工程において、絶縁膜68を成膜し、図15(a)〜(e)に示す工程において、これをエッチバックすることにより、ゲート電極31の側面上に側壁33を形成している。このようにして、周辺回路領域Rpに平面型のMOSFETを形成している。なお、絶縁膜68を成膜する際には、積層体28間にポリシリコン膜66が埋め込まれているため、ゲート電極21の側面上に側壁33が形成されることはない。このように、本実施形態によれば、メモリアレイ領域RmにFinFETを形成すると共に、周辺回路領域Rpに平面型MOSFETを形成することができる。

【0042】

メモリアレイ領域Rmに形成されるトランジスタは、メモリセルを構成するトランジスタであるから、集積度が高く、特性が均一であることが好ましい。そこで、メモリアレイ領域Rmに形成するトランジスタをFinFETとすることにより、オン電流を確保しつつ、集積度を向上させることができる。また、FinFETは、完全空乏型のトランジスタであるから、その閾値は1水準である。このため、各FinFETの特性を揃え、メモリセルの特性を均一にすることができる。

【0043】

一方、周辺回路領域Rpに形成されるトランジスタは、コア部及びセンスアンプ部等を含む周辺回路を構成するトランジスタであるから、トランジスタ毎に種々の特性が要求される。そこで、周辺回路領域Rpに形成するトランジスタを平面型MOSFETとすることにより、必要とされる特性、例えば、オン電流の大きさに応じて、様々なサイズのトランジスタを形成することができる。また、平面型MOSFETは部分空乏型のトランジスタであるから、能動部分16及びゲート電極31のサイズ及び形状、並びに、ソース・ドレイン領域34の不純物濃度等を調整することにより、閾値を個別に制御することができる。このように、周辺回路領域Rpに形成するトランジスタを平面型MOSFETとすることにより、周辺回路において必要とされる種々の特性を持ったトランジスタを作り分けることができる。更に、平面型MOSFETは過去の設計資産を利用して設計することができため、信頼性が高いトランジスタを低コストで形成することができる。これに対して、仮に、過去の設計資産を利用できないと、設計に必要な情報を集めるためには膨大な実験と時間が必要となる。

【0044】

また、本実施形態においては、FinFETと平面型MOSFETを別々に形成することができるため、ゲート電極21の高さを、FinFETに必要とされる高さよりも高くする必要がない。そして、ゲート電極21を低く形成することにより、以後の工程が容易になる。例えば、製造工程中にゲート電極21が倒壊することを防止できる。また、ソース・ドレイン領域27に対する不純物の注入が容易になる。これに対して、仮に、FinFETのゲート電極21及び平面型MOSFETのゲート電極31を同一の導電膜をパターニングすることによって形成しようとすると、上下方向(Z方向)におけるゲート電極21の上面の位置とゲート電極31の上面の位置とが同じになる。このため、ゲート電極21の高さ、すなわち、溝12の底面からゲート電極21の上面までの距離が大きくなってしまい、以後の工程が困難になる。

【0045】

更に、本実施形態においては、図5(a)〜(e)に示す工程において、シリコン基板11を選択的に除去する際に、フィン13及び能動部分16を形成すると共に、抵抗素子領域Rrにおいてシリコン基板11の上面11aを後退させている。そして、図6(a)〜(e)に示す工程において、シリコン基板11上に素子分離絶縁膜17を形成し、図12(a)〜(e)に示す工程において、ポリシリコン膜66を成膜し、図13(a)〜(e)に示す工程において、ポリシリコン膜66をパターニングすることにより、ゲート電極31を形成すると共に、抵抗部材41を形成している。このように、本実施形態によれば、抵抗部材41を、ゲート電極31と同じプロセスで形成することができる。この結果、抵抗部材41の形成に伴って工程数が増えることを抑制でき、半導体装置1の製造コストを抑えることができる。

【0046】

以上説明した実施形態によれば、トランジスタの集積度が高い半導体装置及びその製造方法を実現することができる。

【0047】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明及びその等価物の範囲に含まれる。

【符号の説明】

【0048】

1:半導体装置、11:シリコン基板、11a:上面、12:溝、13:フィン、14:シリコン窒化膜、15:溝、16:能動部分、16a:上面、17:素子分離絶縁膜、17a:上面、21:ゲート電極、22:下部、23:上部、24:ゲート絶縁膜、25:ハードマスク材、26:側壁、27:ソース・ドレイン領域、28:積層体、29:シリサイド層、31:ゲート電極、32:ゲート絶縁膜、33:側壁、34:ソース・ドレイン領域、35:シリサイド層、41:抵抗部材、42:シリサイド層、43:絶縁膜、51a、51b:コンタクト、52:磁気抵抗記憶素子、53:ビア、54:中間配線、55:ビア、56:上層配線、62:ポリシリコン膜、63:金属膜、65:シリコン窒化膜、66:ポリシリコン膜、68:絶縁膜、69:ハードマスク材、Rm:メモリアレイ領域、Rp:周辺回路領域、Rr:抵抗素子領域

【技術分野】

【0001】

本発明の実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、電子のスピンを利用してデータを記憶する新たな記憶装置として、MRAM(Magneto resistive Random Access Memory:磁気抵抗ランダムアクセスメモリ)が提案されている。MRAMにおいては、複数個のメモリセルがアレイ状に配列されており、各メモリセルにおいては、磁気抵抗記憶素子及びトランジスタが設けられている。MRAMにおいて、メモリセルの集積度を向上させるためには、所定のオン電流を確保しつつ、トランジスタを微細化することが必要となる。

【0003】

一方、MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor:金属酸化物半導体電界効果トランジスタ)の集積度の向上とオン電流の増大とを両立させるために、Fin型のMOSFET(以下、「FinFET」という)が提案されている。FinFETにおいては、半導体基板の上面に一方向に延びる凸状のフィンが形成されており、このフィンを跨ぐように、他方向に延びるゲート電極が設けられている。これにより、フィンにおけるゲート電極により囲まれた部分の外周がチャネル領域となり、素子面積を増大させることなく、チャネル幅を拡大することができる。

【0004】

そこで、MRAMのメモリセルの集積度を向上させるために、MRAMに形成されるトランジスタをFinFETとすることが考えられる。しかしながら、この場合は、MRAMを構成する複数種類のトランジスタの閾値を、それぞれ最適な値に調整することが困難になるという問題点がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−34427号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の目的は、トランジスタの集積度が高い半導体装置及びその製造方法を提供することである。

【課題を解決するための手段】

【0007】

実施形態に係る半導体装置は、第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、を備える。そして、前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なる。

【0008】

実施形態に係る半導体装置の製造方法は、半導体基板を選択的に除去することにより、第1領域に第1方向に延びる複数本のフィンを形成する工程と、前記フィン間の部分の下部に素子分離絶縁膜を埋め込む工程と、前記フィンにおける前記素子分離絶縁膜から突出した部分の表面上に第1ゲート絶縁膜を形成する工程と、前記フィン及び前記素子分離絶縁膜上に第1導電膜を形成する工程と、前記第1導電膜を選択的に除去することにより、前記第1領域において、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極を形成すると共に、第2領域において、前記第1導電膜を除去する工程と、前記半導体基板の上面における前記第2領域上に第2ゲート絶縁膜を形成する工程と、第2導電膜を形成する工程と、前記第2導電膜を選択的に除去することにより、前記第2ゲート絶縁膜上に第2ゲート電極を形成する工程と、を備える。

【図面の簡単な説明】

【0009】

【図1】(a)〜(c)は、実施形態に係る半導体装置を例示する平面図である。

【図2】(a)〜(e)は、実施形態に係る半導体装置を例示する断面図である。

【図3】(a)及び(b)は、実施形態に係る半導体装置におけるメモリアレイ領域を例示する模式的断面図である。

【図4】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図5】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図6】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図7】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図8】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図9】(a)〜(c)は、実施形態に係る半導体装置の製造方法を例示する工程平面図である。

【図10】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図11】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図12】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図13】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図14】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図15】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図16】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図17】(a)〜(e)は、実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【発明を実施するための形態】

【0010】

以下、図面を参照しつつ、本発明の実施形態について説明する。

図1(a)〜(c)は、本実施形態に係る半導体装置を例示する平面図であり、(a)はメモリアレイ領域を示し、(b)は周辺回路領域を示し、(c)は抵抗素子領域を示し、

図2(a)〜(e)は、本実施形態に係る半導体装置を例示する断面図であり、(a)は図1(a)に示すA−A’線による断面図であり、(b)は図1(a)に示すB−B’線による断面図であり、(c)は図1(b)に示すC−C’線による断面図であり、(d)は図1(b)に示すD−D’線による断面図であり、(e)は図1(c)に示すE−E’線による断面図であり、

図3(a)及び(b)は、本実施形態に係る半導体装置におけるメモリアレイ領域を例示する模式的断面図である。

なお、図示の便宜上、図1及び図2においては、層間絶縁膜及びそれより上方の上部構造が省略されている。また、図3においては、原則として導電部分のみを示し、絶縁部分は省略されている。

【0011】

図1(a)〜(c)及び図2(a)〜(e)に示すように、本実施形態に係る半導体装置1は、メモリアレイ領域Rm、周辺回路領域Rp及び抵抗素子領域Rrが設定された半導体記憶装置であり、より具体的にはMRAMである。メモリアレイ領域Rmにおいては、複数個のメモリセルが設けられており、各メモリセルにデータが記憶される。周辺回路領域Rpにおいては、メモリセルを駆動する周辺回路が設けられている。抵抗素子領域Rrにおいては、抵抗素子が設けられている。この抵抗素子は、例えば、周辺回路に接続されている。

【0012】

半導体装置1においては、シリコン基板11が設けられている。但し、シリコン基板11の上面11aは、上述の各領域毎に異なった加工が施されている。

メモリアレイ領域Rmにおいては、シリコン基板11の上面11aに一方向(以下、「X方向」という)に延びる複数本の溝12が形成されている。これにより、シリコン基板11の上層部分における溝12間の部分はフィン13となっている。フィン13は複数本形成され、周期的に配列されており、各フィン13はX方向に延びている。フィン13の上面上には、シリコン窒化膜14が設けられている。

【0013】

周辺回路領域Rpにおいては、シリコン基板11の上面11aに枠状の溝15が形成されている。シリコン基板11の上層部分における溝15によって囲まれた部分は能動部分16となっている。能動部分16は例えば複数形成されており、溝15によって区画されている。

抵抗素子領域Rrにおいては、シリコン基板11の上層部分が除去されている。これにより、抵抗素子領域Rrにおけるシリコン基板11の上面11aは、メモリアレイ領域Rmにおけるフィン13の上端及び周辺回路領域Rpにおけるシリコン基板11の上面11aよりも下方に位置しており、メモリアレイ領域Rmにおける溝12の底面及び周辺回路領域Rpにおける溝15の底面と同じ高さに位置している。

【0014】

シリコン基板11上には、例えばシリコン酸化物等の絶縁材料からなる素子分離絶縁膜17が設けられている。素子分離絶縁膜17は、メモリアレイ領域Rmにおいては、溝12の下部に配置されており、周辺回路領域Rpにおいては、溝15内に配置されており、抵抗素子領域Rrにおいては、シリコン基板11上に配置されている。周辺回路領域Rp及び抵抗素子領域Rrにおける素子分離絶縁膜17の上面17aの高さは相互に等しく、フィン13の上端及び能動部分16の上面16aの高さと一致している。また、メモリアレイ領域Rmにおける素子分離絶縁膜17の上面17aは、周辺回路領域Rp及び抵抗素子領域Rrにおける素子分離絶縁膜17の上面17aよりも下方に位置している。

【0015】

メモリアレイ領域Rmにおいては、シリコン基板11及び素子分離絶縁膜17上に、複数本のゲート電極21が周期的に設けられている。各ゲート電極21はX方向に対して直交した方向(以下、「Y方向」という)に延び、フィン13を跨いでいる。すなわち、ゲート電極21の下端は、フィン13の上端よりも下方に位置している。ゲート電極21の下部22は、不純物を含有するポリシリコンによって形成されている。ゲート電極21の上部23は、例えばタングステン等の金属によって形成されている。下部22と上部23との界面は平面であり、例えば、フィン13の上端面と同じ高さにある。なお、X方向及びY方向の双方に対して直交する方向、すなわち、上下方向を、「Z方向」とする。

【0016】

フィン13とゲート電極21との間には、ゲート絶縁膜24が設けられている。ゲート絶縁膜24は、フィン13における素子分離絶縁膜17の上面17aから突出した部分の側面を覆っている。各ゲート電極21の直上域には、例えばシリコン窒化物からなるハードマスク材25が設けられている。ゲート電極21及びハードマスク材25からなる積層体28の側面上には、例えばシリコン窒化物等の絶縁材料からなる側壁26が設けられている。フィン13におけるゲート電極21及び側壁26の直下域間の部分には、不純物が導入されたソース・ドレイン領域27が形成されている。すなわち、隣り合う一対のソース・ドレイン領域27は、フィン13におけるゲート電極21の直下域を挟んでいる。ソース・ドレイン領域27の上層部分には、シリサイド層29が形成されている。これにより、フィン13とゲート電極21との最近接点毎に、FinFETが構成されている。従って、メモリアレイ領域Rmにおいては、複数個のFinFETがマトリクス状に配列されている。これらのFinFETの電気的特性は、ほぼ均一である。

【0017】

周辺回路領域Rpにおいては、シリコン基板11及び素子分離絶縁膜17上に、能動部分16の直上域を横切るように、一方向に延びるゲート電極31が設けられている。1つの能動部分16の直上域を、例えば2本のゲート電極31が横切っている。なお、図1及び図2においては、ゲート電極31が延びる方向をY方向としているが、これには限定されない。ゲート電極31は、例えば、シリコンを含む導電性材料からなり、例えば、不純物を含有するポリシリコンによって形成されている。能動部分16とゲート電極31との間には、ゲート絶縁膜32が設けられている。能動部分16の上面及びゲート電極31の下面はそれぞれ平坦である。すなわち、ゲート電極31の下面は、能動部分16の上面よりも上方に位置している。従って、ゲート絶縁膜32の形状も平面状である。

【0018】

また、各ゲート電極31の両側面上には、例えばシリコン窒化物からなる側壁33が設けられている。能動部分16の上層部分におけるゲート電極31及び側壁33の直下域を挟む部分には、不純物が導入されたソース・ドレイン領域34が形成されている。ゲート電極31の上層部分及びソース・ドレイン領域34の上層部分には、例えばニッケルシリサイド等のシリサイドからなるシリサイド層35が形成されている。能動部分16の上層部分におけるゲート電極31の直下域に相当する部分、すなわち、一対のソース・ドレイン領域34によって挟まれた部分は、チャネル領域となっている。このようにして、能動部分16、ゲート絶縁膜32及びゲート電極31により、平面型のMOSFETが構成されている。周辺回路領域Rpに形成された複数個の平面型MOSFETはいくつかの種類に分けられ、その電気的特性は、その種類間で異なっている。これらの平面型MOSFETにより、周辺回路が構成されている。

【0019】

抵抗素子領域Rrにおいては、素子分離絶縁膜17上に、例えば不純物を含有したポリシリコンからなる抵抗部材41が設けられている。抵抗部材41の形状は略直方体であり、例えば、長手方向の中央部の幅は両端部の幅よりも狭い。抵抗部材41及びゲート電極31は、同じポリシリコン膜を加工して形成されたものであり、従って、組成及び厚さは相互に等しい。抵抗部材41の両端部の上面上には、シリサイド層42が形成されている。シリサイド層42及び35は、同じ処理によって形成されたものであり、従って、組成及び厚さは相互にほぼ等しい。抵抗部材41の上面のうち、シリサイド層42が形成されていない領域上、及び抵抗部材41の側面上には、絶縁膜43が設けられている。絶縁膜43は側壁33と同時に形成されたものであり、従って、組成が相互に等しい。

【0020】

フィン13、ゲート電極21、ゲート電極31及び抵抗部材41等を覆うように、層間絶縁膜(図示せず)が設けられている。

図3(a)及び(b)に示すように、メモリアレイ領域Rmにおいては、フィン13におけるゲート電極21の直下域を挟む2つの部分、すなわち、ソース・ドレイン領域27が形成された部分の直上域には、コンタクト51a及び51bが設けられている。コンタクト51a上には磁気抵抗記憶素子52が設けられており、コンタクト51b上にはビア53が設けられている。これにより、各FinFETを構成する一対のソース・ドレイン領域27のうち、一方のソース・ドレイン領域27はコンタクト51aを介して磁気抵抗記憶素子52に接続されており、他方のソース・ドレイン領域27はコンタクト51bを介してビア53に接続されている。磁気抵抗記憶素子52は、特定方向のスピンを持つ電子が注入されることにより電気抵抗値が変化し、これによってデータを記憶する素子である。

【0021】

磁気抵抗記憶素子52及びビア53の上方には、Y方向を長手方向とする短冊状の中間配線54が設けられている。隣り合うフィン13に接続された磁気抵抗記憶素子52とビア53とは、中間配線54を介して相互に接続されている。中間配線54上であってビア53の直上域には、ビア55が設けられている。ビア55上には、X方向に延びる上層配線56が設けられている。中間配線54は、ビア55を介して上層配線56に接続されている。そして、1つのFinFET及び1つの磁気抵抗記憶素子52により、1つのメモリセルが形成されている。すなわち、上述のFinFETはセルトランジスタである。

【0022】

次に、本実施形態に係る半導体装置の製造方法について説明する。

図4〜図8、図10〜図17は、本実施形態に係る半導体装置の製造方法を例示する工程断面図であり、各図の(a)は図1(a)に示すA−A’線による断面図に相当し、(b)は図1(a)に示すB−B’線による断面図に相当し、(c)は図1(b)に示すC−C’線による断面図に相当し、(d)は図1(b)に示すD−D’線による断面図に相当し、(e)は図1(c)に示すE−E’線による断面図に相当し、

図9(a)〜(c)は、本実施形態に係る半導体装置の製造方法を例示する工程平面図であり、(a)はメモリアレイ領域を示し、(b)は周辺回路領域を示し、(c)は抵抗素子領域を示す。

なお、図10(a)は図9(a)に示すA−A’線による断面図であり、(b)は図9(a)に示すB−B’線による断面図であり、(c)は図9(b)に示すC−C’線による断面図であり、(d)は図9(b)に示すD−D’線による断面図であり、(e)は図9(c)に示すE−E’線による断面図である。

【0023】

先ず、図4(a)〜(e)に示すように、シリコン基板11を用意する。次に、シリコン基板11上にシリコン窒化膜14を形成する。

次に、図5(a)〜(e)に示すように、シリコン窒化膜14上にマスクパターン(図示せず)を形成する。メモリアレイ領域Rmにおいては、マスクパターンは側壁法により形成する。そして、このマスクパターンをマスクとしてエッチングを施すことにより、シリコン窒化膜14及びシリコン基板11の上層部分を選択的に除去する。これにより、メモリアレイ領域Rmにおいては、シリコン基板11の上面にX方向に延びる溝12を複数本形成し、シリコン基板11における溝12間の部分をフィン13とする。周辺回路領域Rpにおいては、シリコン基板11の上面に枠状の溝15を形成し、シリコン基板11における溝15によって囲まれた部分を能動部分16とする。抵抗素子領域Rrにおいては、シリコン基板11の上面11aを後退させて、例えば溝12の底面と同じ高さとする。このとき、全てのフィン13について、その幅及び間隔は相互に同一とする。一方、複数の能動部分16については、その形状を相互に異ならせてもよい。

【0024】

次に、図6(a)〜(e)に示すように、全面にシリコン酸化物を堆積させて、加熱することによって焼き締め(Densify)を行う。これにより、シリコン基板11及びシリコン窒化膜14上に素子分離絶縁膜17を形成する。次に、シリコン窒化膜14をストッパとしてCMP(chemical mechanical polishing:化学的機械研磨)等の平坦化処理を施して、素子分離絶縁膜17の上面17aを平坦化すると共に、シリコン窒化膜14の上面と同じ高さとする。

【0025】

次に、図7(a)〜(e)に示すように、メモリアレイ領域Rmにおいて素子分離絶縁膜17をリセスし、上面17aを後退させる。この結果、フィン13の上部が素子分離絶縁膜17から突出し、露出する。次に、酸化処理を施す。これにより、フィン13の上部の側面上に、シリコン酸化物からなるゲート絶縁膜24が形成される。

【0026】

次に、図8(a)〜(e)に示すように、不純物が添加されたポリシリコン膜62を全面に成膜し、CMPを施す。これにより、ポリシリコン膜62は溝12内の上部に埋め込まれる。このとき、ポリシリコン膜62は、シリコン基板11及び素子分離絶縁膜17の上方から除去されてもよく、残留してもよい。図8(a)〜(e)には、ポリシリコン膜62が、フィン13を含むシリコン基板11及び素子分離絶縁膜17の上方から完全に除去され、溝12内のみに残留した場合を示している。次に、全面に金属、例えば、タングステンを堆積させて、全面に金属膜63を形成する。次に、全面にシリコン窒化物を堆積させて、全面にシリコン窒化膜65を形成する。

【0027】

次に、図9(a)〜(c)及び図10(a)〜(e)に示すように、メモリアレイ領域Rmにおいて、シリコン窒化膜65上にマスクパターン(図示せず)を形成する。このマスクパターンには、側壁法により、Y方向に延びるライン状のパターンを複数本形成する。一方、周辺回路領域Rp及び抵抗素子領域Rrには、マスクパターンを形成しない。

【0028】

次に、このマスクパターンをマスクとして、シリコン窒化膜65、金属膜63及びポリシリコン膜62をエッチングする。このとき、フィン13の直上域においては、シリコン窒化膜14においてエッチングが停止する。これにより、メモリアレイ領域Rmにおいて、シリコン窒化膜65がY方向に延びる複数本のハードマスク材25に加工されると共に、金属膜63及びポリシリコン膜62がゲート電極21に加工される。この結果、金属膜63はゲート電極21の上部23となり、ポリシリコン膜62はゲート電極21の下部22となる。一方、周辺回路領域Rp及び抵抗素子領域Rrにおいては、シリコン窒化膜65、金属膜63及びポリシリコン膜62が除去される。

【0029】

次に、図11(a)〜(e)に示すように、全面に例えばシリコン窒化物等の絶縁材料を堆積させて、絶縁膜を成膜する。次に、この絶縁膜をパターニングすることにより、メモリアレイ領域Rmに残留させると共に、周辺回路領域Rp及び抵抗素子領域Rrから除去する。このとき、周辺回路領域Rp及び抵抗素子領域Rrからは、シリコン窒化膜14も除去される。この結果、メモリアレイ領域Rmにおいて、素子分離絶縁膜17上に、ゲート電極21及びハードマスク材25からなる積層体28を覆うように、側壁26が形成される。

【0030】

次に、図12(a)〜(e)に示すように、酸化処理を施すことにより、周辺回路領域Rpにおいて、シリコン基板11の能動部分16の上面16a上に、シリコン酸化物からなるゲート絶縁膜32を形成する。次に、不純物が添加されたポリシリコンを堆積させることにより、全面にポリシリコン膜66を形成する。ポリシリコン膜66は、積層体28の相互間にも埋め込まれる。

【0031】

次に、図13(a)〜(e)に示すように、ポリシリコン膜66上に反射防止膜(図示せず)及びマスクパターン(図示せず)を形成し、このマスクパターンをマスクとしてエッチングを施す。これにより、ポリシリコン膜66のうち、周辺回路領域Rpに配置された部分をゲート電極31に加工すると共に、抵抗素子領域Rrに配置された部分を抵抗部材41に加工する。また、ポリシリコン膜66のうち、メモリアレイ領域Rmに配置された部分は、積層体28の上方に位置する部分が除去され、積層体28の相互間に埋め込まれた部分は残留する。

【0032】

ゲート電極31は、一方向に延び、能動部分16の直上域を横切るようにライン状に加工する。このとき、形成しようとする平面型MOSFETの電気的特性に応じて、複数本のゲート電極31間で相互に幅を異ならせてもよい。また、抵抗部材41は、一方向に延びる略直方体形状に加工し、長手方向中央部の幅を長手方向両端部の幅よりも細くする。このとき、抵抗部材41によって実現しようとする抵抗値の大きさに応じて、抵抗部材41の形状を制御する。

【0033】

次に、図14(a)〜(e)に示すように、全面に、例えばシリコン窒化膜等の絶縁材料からなる絶縁膜68を形成する。このとき、絶縁膜68は、ゲート電極31の側面上及び抵抗部材41の側面上には形成されるが、積層体28間にはポリシリコン膜66が埋め込まれているため、積層体28の側面上には形成されない。次に、絶縁膜68上にハードマスク材69を形成し、パターニングすることにより、マスク材69を、抵抗部材41の上面上のうち、長手方向両端部における中央部分を除く領域に残留させる。

【0034】

次に、図15(a)〜(e)に示すように、絶縁膜68をエッチバックする。これにより、絶縁膜68は、メモリアレイ領域Rmの全体、周辺回路領域Rpにおけるゲート電極31、能動部分16及び素子分離絶縁膜17の上面上、並びに、抵抗素子領域Rrにおける素子分離絶縁膜17の上面上及び抵抗部材41の上面上におけるハードマスク材69によって覆われていない領域から除去されると共に、ゲート電極31の側面上、並びに、抵抗部材41の側面上及び抵抗部材41の上面におけるハードマスク材69の直下域に残留する。この結果、絶縁膜68が選択的に除去されて、ゲート電極31の側面上に側壁33が形成されると共に、抵抗部材41の上面におけるハードマスク材69によって覆われている領域上及び抵抗部材41の側面上に絶縁膜43が形成される。

【0035】

次に、図16(a)〜(e)に示すように、周辺回路領域Rp及び抵抗素子領域Rrを覆い、メモリアレイ領域Rmを露出させるようなマスク(図示せず)を形成し、これを用いてウェットエッチングを施すことにより、積層体28の相互間からポリシリコン膜66を除去する。

次に、図17(a)〜(e)に示すように、側壁26における積層体28の上面上に形成された部分を除去する。

【0036】

次に、図1(a)〜(c)、図2(a)〜(e)並びに図3(a)及び(b)に示すように、メモリアレイ領域Rmを開口したレジストマスク(図示せず)を形成し、このレジストマスク並びに積層体28及び側壁26をマスクとして不純物を注入する。これにより、フィン13における積層体28及び側壁26によって覆われていない部分に、ソース・ドレイン領域27が形成される。この結果、フィン13とゲート電極21との最近接点毎に、FinFETが形成される。

【0037】

次に、周辺回路領域Rpを開口したレジストマスク(図示せず)を形成し、このレジストマスク並びにゲート電極31及び側壁33をマスクとして不純物を注入する。これにより、能動部分16におけるゲート電極31及び側壁33によって覆われていない部分に、ソース・ドレイン領域34が形成される。この結果、能動部分16とゲート電極31との最近接点毎に、平面型のMOSFETが形成される。このとき、各MOSFETに要求される電気的特性に応じて、不純物の注入量及び注入深さを異ならせてもよい。

【0038】

次に、例えばニッケルを堆積させて、加熱処理を施すことにより、シリコンの露出面をシリサイド化する。これにより、ソース・ドレイン領域27の上層部分にシリサイド層29が形成され、ゲート電極31の上層部分及びソース・ドレイン領域34の上層部分にシリサイド層35が形成され、抵抗部材41における長手方向両端部の中央部分の上面にシリサイド層42が形成される。

【0039】

次に、全体に層間絶縁膜(図示せず)を成膜して、フィン13、ゲート電極21、ゲート電極31及び抵抗部材41等を覆う。次に、層間絶縁膜及びシリコン窒化膜14にコンタクトホールを形成し、その内部に導電材料を埋め込み、コンタクト51a及び51bを形成する。次に、コンタクト51a上に磁気抵抗記憶素子52を形成し、コンタクト51b上にビア53を形成する。次に、磁気抵抗記憶素子52及びビア53の上方に中間配線54を形成し、隣り合うフィン13に接続された磁気抵抗記憶素子52及びビア53を同一の中間配線54に共通接続する。次に、中間配線54上であってビア53の直上域にビア55を形成し、ビア55上に、X方向に延びる上層配線56を形成する。このようにして、本実施形態に係る半導体装置1が製造される。

【0040】

次に、本実施形態の効果について説明する。

本実施形態においては、図5(a)〜(e)に示す工程において、シリコン基板11を選択的に除去することにより、メモリアレイ領域Rmにフィン13を形成し、周辺回路領域Rpに能動部分16を形成している。

そして、図8(a)〜(e)に示す工程において、ポリシリコン膜62及び金属膜63を成膜し、図9(a)〜(c)及び図10(a)〜(e)に示す工程において、これらをパターニングすることにより、ゲート電極21を形成している。その後、図11(a)〜(e)に示す工程において、側壁26を形成することにより、メモリアレイ領域RmにFinFETを形成している。

【0041】

一方、図12(a)〜(e)に示す工程において、ポリシリコン膜66を成膜し、図13(a)〜(e)に示す工程において、これをパターニングすることにより、周辺回路領域Rpにゲート電極31を形成している。また、図14(a)〜(e)に示す工程において、絶縁膜68を成膜し、図15(a)〜(e)に示す工程において、これをエッチバックすることにより、ゲート電極31の側面上に側壁33を形成している。このようにして、周辺回路領域Rpに平面型のMOSFETを形成している。なお、絶縁膜68を成膜する際には、積層体28間にポリシリコン膜66が埋め込まれているため、ゲート電極21の側面上に側壁33が形成されることはない。このように、本実施形態によれば、メモリアレイ領域RmにFinFETを形成すると共に、周辺回路領域Rpに平面型MOSFETを形成することができる。

【0042】

メモリアレイ領域Rmに形成されるトランジスタは、メモリセルを構成するトランジスタであるから、集積度が高く、特性が均一であることが好ましい。そこで、メモリアレイ領域Rmに形成するトランジスタをFinFETとすることにより、オン電流を確保しつつ、集積度を向上させることができる。また、FinFETは、完全空乏型のトランジスタであるから、その閾値は1水準である。このため、各FinFETの特性を揃え、メモリセルの特性を均一にすることができる。

【0043】

一方、周辺回路領域Rpに形成されるトランジスタは、コア部及びセンスアンプ部等を含む周辺回路を構成するトランジスタであるから、トランジスタ毎に種々の特性が要求される。そこで、周辺回路領域Rpに形成するトランジスタを平面型MOSFETとすることにより、必要とされる特性、例えば、オン電流の大きさに応じて、様々なサイズのトランジスタを形成することができる。また、平面型MOSFETは部分空乏型のトランジスタであるから、能動部分16及びゲート電極31のサイズ及び形状、並びに、ソース・ドレイン領域34の不純物濃度等を調整することにより、閾値を個別に制御することができる。このように、周辺回路領域Rpに形成するトランジスタを平面型MOSFETとすることにより、周辺回路において必要とされる種々の特性を持ったトランジスタを作り分けることができる。更に、平面型MOSFETは過去の設計資産を利用して設計することができため、信頼性が高いトランジスタを低コストで形成することができる。これに対して、仮に、過去の設計資産を利用できないと、設計に必要な情報を集めるためには膨大な実験と時間が必要となる。

【0044】

また、本実施形態においては、FinFETと平面型MOSFETを別々に形成することができるため、ゲート電極21の高さを、FinFETに必要とされる高さよりも高くする必要がない。そして、ゲート電極21を低く形成することにより、以後の工程が容易になる。例えば、製造工程中にゲート電極21が倒壊することを防止できる。また、ソース・ドレイン領域27に対する不純物の注入が容易になる。これに対して、仮に、FinFETのゲート電極21及び平面型MOSFETのゲート電極31を同一の導電膜をパターニングすることによって形成しようとすると、上下方向(Z方向)におけるゲート電極21の上面の位置とゲート電極31の上面の位置とが同じになる。このため、ゲート電極21の高さ、すなわち、溝12の底面からゲート電極21の上面までの距離が大きくなってしまい、以後の工程が困難になる。

【0045】

更に、本実施形態においては、図5(a)〜(e)に示す工程において、シリコン基板11を選択的に除去する際に、フィン13及び能動部分16を形成すると共に、抵抗素子領域Rrにおいてシリコン基板11の上面11aを後退させている。そして、図6(a)〜(e)に示す工程において、シリコン基板11上に素子分離絶縁膜17を形成し、図12(a)〜(e)に示す工程において、ポリシリコン膜66を成膜し、図13(a)〜(e)に示す工程において、ポリシリコン膜66をパターニングすることにより、ゲート電極31を形成すると共に、抵抗部材41を形成している。このように、本実施形態によれば、抵抗部材41を、ゲート電極31と同じプロセスで形成することができる。この結果、抵抗部材41の形成に伴って工程数が増えることを抑制でき、半導体装置1の製造コストを抑えることができる。

【0046】

以上説明した実施形態によれば、トランジスタの集積度が高い半導体装置及びその製造方法を実現することができる。

【0047】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明及びその等価物の範囲に含まれる。

【符号の説明】

【0048】

1:半導体装置、11:シリコン基板、11a:上面、12:溝、13:フィン、14:シリコン窒化膜、15:溝、16:能動部分、16a:上面、17:素子分離絶縁膜、17a:上面、21:ゲート電極、22:下部、23:上部、24:ゲート絶縁膜、25:ハードマスク材、26:側壁、27:ソース・ドレイン領域、28:積層体、29:シリサイド層、31:ゲート電極、32:ゲート絶縁膜、33:側壁、34:ソース・ドレイン領域、35:シリサイド層、41:抵抗部材、42:シリサイド層、43:絶縁膜、51a、51b:コンタクト、52:磁気抵抗記憶素子、53:ビア、54:中間配線、55:ビア、56:上層配線、62:ポリシリコン膜、63:金属膜、65:シリコン窒化膜、66:ポリシリコン膜、68:絶縁膜、69:ハードマスク材、Rm:メモリアレイ領域、Rp:周辺回路領域、Rr:抵抗素子領域

【特許請求の範囲】

【請求項1】

メモリアレイ領域、周辺回路領域及び抵抗素子領域が設定された半導体装置であって、

前記メモリアレイ領域において上面に第1方向に延びる複数本のフィンが形成され、前記抵抗素子領域における上面が前記周辺回路領域における上面よりも下方に位置した半導体基板と、

前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、

前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、

前記周辺回路領域において前記半導体基板上に設けられた第2ゲート電極と、

前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、

前記半導体基板上に設けられ、前記メモリアレイ領域における上面が前記抵抗素子領域における上面よりも下方に位置した素子分離絶縁膜と、

前記抵抗素子領域において前記素子分離絶縁膜上に設けられ、その組成及び厚さが前記第2ゲート電極の組成及び厚さと等しい抵抗部材と、

前記メモリアレイ領域に設けられた磁気抵抗記憶素子と、

を備え、

前記第1ゲート電極は、

シリコンを含む下部と、

金属を含む上部と、

を有し、

前記第2ゲート電極は、シリコンを含む材料により形成されており、

前記第1ゲート電極の下端は前記フィンの上端よりも下方に位置しており、

前記第2ゲート電極の下面は、前記半導体基板の上面よりも上方に位置しており、

前記フィンの上端、前記第2領域における前記半導体基板の上面、及び前記第3領域における前記素子分離絶縁膜の上面は、相互に同じ高さに位置しており、

前記フィンにおける前記第1ゲート電極の直下域を挟む領域には、第1ソース・ドレイン領域が形成されており、

前記半導体基板の上層部分における前記第2ゲート電極の直下域を挟む領域には、第2ソース・ドレイン領域が形成されていることを特徴とする半導体装置。

【請求項2】

第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、

前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、

前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、

前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、

前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、

を備え、

前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なることを特徴とする半導体装置。

【請求項3】

前記第1領域に設けられた記憶素子をさらに備え、

前記第1領域はメモリアレイ領域であり、前記第2領域は周辺回路領域であることを特徴とする請求項2記載の半導体装置。

【請求項4】

前記記憶素子は磁気抵抗記憶素子であることを特徴とする請求項3記載の半導体装置。

【請求項5】

前記第1ゲート電極の下端は前記フィンの上端よりも下方に位置しており、前記第2ゲート電極の下面は、前記半導体基板の上面よりも上方に位置していることを特徴とする請求項2〜4のいずれか1つに記載の半導体装置。

【請求項6】

前記第1ゲート電極は、

シリコンを含む下部と、

金属を含む上部と、

を有し、

前記第2ゲート電極は、シリコンを含む材料により形成されていることを特徴とする請求項2〜5のいずれか1つに記載の半導体装置。

【請求項7】

前記半導体基板上に設けられ、前記フィン間の部分の下部及び前記第3領域に配置された素子分離絶縁膜と、

前記第3領域において前記素子分離絶縁膜上に設けられ、その組成及び厚さが前記第2ゲート電極の組成及び厚さと等しい抵抗部材と、

をさらに備え、

第3領域における前記半導体基板の上面は、前記第2領域における前記半導体基板の上面よりも下方に位置していることを特徴とする請求項2〜6のいずれか1つに記載の半導体装置。

【請求項8】

前記第1領域における前記素子分離絶縁膜の上面は、前記第3領域における前記素子分離絶縁膜の上面よりも下方に位置していることを特徴とする請求項7記載の半導体装置。

【請求項9】

前記フィンの上端、前記第2領域における前記半導体基板の上面、及び前記第3領域における前記素子分離絶縁膜の上面は、相互に同じ高さに位置していることを特徴とする請求項8記載の半導体装置。

【請求項10】

半導体基板を選択的に除去することにより、第1領域に第1方向に延びる複数本のフィンを形成する工程と、

前記フィン間の部分の下部に素子分離絶縁膜を埋め込む工程と、

前記フィンにおける前記素子分離絶縁膜から突出した部分の表面上に第1ゲート絶縁膜を形成する工程と、

前記フィン及び前記素子分離絶縁膜上に第1導電膜を形成する工程と、

前記第1導電膜を選択的に除去することにより、前記第1領域において、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極を形成すると共に、第2領域において、前記第1導電膜を除去する工程と、

前記半導体基板の上面における前記第2領域上に第2ゲート絶縁膜を形成する工程と、

第2導電膜を形成する工程と、

前記第2導電膜を選択的に除去することにより、前記第2ゲート絶縁膜上に第2ゲート電極を形成する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項11】

前記第2ゲート電極を形成する工程の後、絶縁膜を形成する工程と、

前記絶縁膜をエッチバックすることにより、前記第1領域から前記絶縁膜を除去すると共に、前記第2ゲート電極の側面上に側壁を形成する工程と、

前記側壁を形成する工程の後、前記第2導電膜を前記第1ゲート電極間から除去する工程と、

をさらに備えたことを特徴とする請求項10記載の半導体装置の製造方法。

【請求項12】

前記フィンを形成する工程において、第3領域における前記半導体基板の上面を後退させ、

前記素子分離絶縁膜を配置する工程において、前記第3領域にも前記素子分離絶縁膜を配置し、

前記第2導電膜を形成する工程において、前記第3領域にも前記第2導電膜を形成し、

前記第2ゲート電極を形成する工程において、前記第2導電膜における前記第3領域に形成された部分を抵抗部材に加工することを特徴とする請求項10または11に記載の半導体装置の製造方法。

【請求項13】

前記第1ゲート電極上に記憶素子を形成する工程をさらに備え、

前記第1領域にメモリセルを形成し、前記第2領域に周辺回路を形成することを特徴とする請求項10〜12のいずれか1つに記載の半導体装置の製造方法。

【請求項14】

前記記憶素子として磁気抵抗記憶素子を形成することを特徴とする請求項13記載の半導体装置の製造方法。

【請求項1】

メモリアレイ領域、周辺回路領域及び抵抗素子領域が設定された半導体装置であって、

前記メモリアレイ領域において上面に第1方向に延びる複数本のフィンが形成され、前記抵抗素子領域における上面が前記周辺回路領域における上面よりも下方に位置した半導体基板と、

前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、

前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、

前記周辺回路領域において前記半導体基板上に設けられた第2ゲート電極と、

前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、

前記半導体基板上に設けられ、前記メモリアレイ領域における上面が前記抵抗素子領域における上面よりも下方に位置した素子分離絶縁膜と、

前記抵抗素子領域において前記素子分離絶縁膜上に設けられ、その組成及び厚さが前記第2ゲート電極の組成及び厚さと等しい抵抗部材と、

前記メモリアレイ領域に設けられた磁気抵抗記憶素子と、

を備え、

前記第1ゲート電極は、

シリコンを含む下部と、

金属を含む上部と、

を有し、

前記第2ゲート電極は、シリコンを含む材料により形成されており、

前記第1ゲート電極の下端は前記フィンの上端よりも下方に位置しており、

前記第2ゲート電極の下面は、前記半導体基板の上面よりも上方に位置しており、

前記フィンの上端、前記第2領域における前記半導体基板の上面、及び前記第3領域における前記素子分離絶縁膜の上面は、相互に同じ高さに位置しており、

前記フィンにおける前記第1ゲート電極の直下域を挟む領域には、第1ソース・ドレイン領域が形成されており、

前記半導体基板の上層部分における前記第2ゲート電極の直下域を挟む領域には、第2ソース・ドレイン領域が形成されていることを特徴とする半導体装置。

【請求項2】

第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、

前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、

前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、

前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、

前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、

を備え、

前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なることを特徴とする半導体装置。

【請求項3】

前記第1領域に設けられた記憶素子をさらに備え、

前記第1領域はメモリアレイ領域であり、前記第2領域は周辺回路領域であることを特徴とする請求項2記載の半導体装置。

【請求項4】

前記記憶素子は磁気抵抗記憶素子であることを特徴とする請求項3記載の半導体装置。

【請求項5】

前記第1ゲート電極の下端は前記フィンの上端よりも下方に位置しており、前記第2ゲート電極の下面は、前記半導体基板の上面よりも上方に位置していることを特徴とする請求項2〜4のいずれか1つに記載の半導体装置。

【請求項6】

前記第1ゲート電極は、

シリコンを含む下部と、

金属を含む上部と、

を有し、

前記第2ゲート電極は、シリコンを含む材料により形成されていることを特徴とする請求項2〜5のいずれか1つに記載の半導体装置。

【請求項7】

前記半導体基板上に設けられ、前記フィン間の部分の下部及び前記第3領域に配置された素子分離絶縁膜と、

前記第3領域において前記素子分離絶縁膜上に設けられ、その組成及び厚さが前記第2ゲート電極の組成及び厚さと等しい抵抗部材と、

をさらに備え、

第3領域における前記半導体基板の上面は、前記第2領域における前記半導体基板の上面よりも下方に位置していることを特徴とする請求項2〜6のいずれか1つに記載の半導体装置。

【請求項8】

前記第1領域における前記素子分離絶縁膜の上面は、前記第3領域における前記素子分離絶縁膜の上面よりも下方に位置していることを特徴とする請求項7記載の半導体装置。

【請求項9】

前記フィンの上端、前記第2領域における前記半導体基板の上面、及び前記第3領域における前記素子分離絶縁膜の上面は、相互に同じ高さに位置していることを特徴とする請求項8記載の半導体装置。

【請求項10】

半導体基板を選択的に除去することにより、第1領域に第1方向に延びる複数本のフィンを形成する工程と、

前記フィン間の部分の下部に素子分離絶縁膜を埋め込む工程と、

前記フィンにおける前記素子分離絶縁膜から突出した部分の表面上に第1ゲート絶縁膜を形成する工程と、

前記フィン及び前記素子分離絶縁膜上に第1導電膜を形成する工程と、

前記第1導電膜を選択的に除去することにより、前記第1領域において、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極を形成すると共に、第2領域において、前記第1導電膜を除去する工程と、

前記半導体基板の上面における前記第2領域上に第2ゲート絶縁膜を形成する工程と、

第2導電膜を形成する工程と、

前記第2導電膜を選択的に除去することにより、前記第2ゲート絶縁膜上に第2ゲート電極を形成する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項11】

前記第2ゲート電極を形成する工程の後、絶縁膜を形成する工程と、

前記絶縁膜をエッチバックすることにより、前記第1領域から前記絶縁膜を除去すると共に、前記第2ゲート電極の側面上に側壁を形成する工程と、

前記側壁を形成する工程の後、前記第2導電膜を前記第1ゲート電極間から除去する工程と、

をさらに備えたことを特徴とする請求項10記載の半導体装置の製造方法。

【請求項12】

前記フィンを形成する工程において、第3領域における前記半導体基板の上面を後退させ、

前記素子分離絶縁膜を配置する工程において、前記第3領域にも前記素子分離絶縁膜を配置し、

前記第2導電膜を形成する工程において、前記第3領域にも前記第2導電膜を形成し、

前記第2ゲート電極を形成する工程において、前記第2導電膜における前記第3領域に形成された部分を抵抗部材に加工することを特徴とする請求項10または11に記載の半導体装置の製造方法。

【請求項13】

前記第1ゲート電極上に記憶素子を形成する工程をさらに備え、

前記第1領域にメモリセルを形成し、前記第2領域に周辺回路を形成することを特徴とする請求項10〜12のいずれか1つに記載の半導体装置の製造方法。

【請求項14】

前記記憶素子として磁気抵抗記憶素子を形成することを特徴とする請求項13記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−55297(P2013−55297A)

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願番号】特願2011−194161(P2011−194161)

【出願日】平成23年9月6日(2011.9.6)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願日】平成23年9月6日(2011.9.6)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]