半導体装置及びその製造方法

【課題】プラグが微細化しても埋め込み不良が生じることなく、低コストで形成することができ、さらに種々の半導体装置に適用可能であるプラグ及びその形成技術を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上に酸化シリコン膜を形成し、酸化シリコン膜にビアを形成し、ビア内側に密着層を形成し、密着層上にシリコン層を形成し、タングステンを含むガスをシリコン層と反応させることにより、ビアに埋め込まれたタングステン膜を形成する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上に酸化シリコン膜を形成し、酸化シリコン膜にビアを形成し、ビア内側に密着層を形成し、密着層上にシリコン層を形成し、タングステンを含むガスをシリコン層と反応させることにより、ビアに埋め込まれたタングステン膜を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体装置においては、半導体素子と配線との間、配線どうしの間にある各層間を接続するために、コンタクトプラグ、及び/又は、ビアプラグが形成されている。コンタクトプラグ及びビアプラグの形成は、以下のようにして行う。

【0003】

まず、シリコン基板などの半導体基板に素子分離膜及び半導体素子を形成し、さらに半導体素子及び素子分離膜上に層間絶縁膜を形成する。

【0004】

次に、層間絶縁膜をマスクパターン及びエッチングを用いて選択的に除去し、層間絶縁膜にビアを形成する。詳細には、この形成されたビアは、拡散層上、ゲート電極上のシリサイド層と配線をつなぐためのコンタクトプラグを形成するためのコンタクトビア、もしくは、下層の配線と上層の配線とをつなぐためのビアプラグを形成するためのプラグビアである。

【0005】

そして、このように形成されたビアの内側の側壁上に、例えばPVD(Physical Vapor Deposition)技術を用いて、密着層を形成する。この密着層は、タングステン膜とも層間絶縁膜とも密着性が高く、層間絶縁膜上に比べてタングステンの結晶核が生成しやすい窒化チタン膜等からなる。さらに、CVD(Chemical Vapor Deposition)技術を用いて、タングステン膜を密着層に覆われたビアに埋め込む。その後、CMP(Chemical mechanical Polishing)技術を用いて、ビアからはみ出た密着層及びタングステン膜を除去し、コンタクトプラグ、ビアプラグを形成する。

【0006】

このようにしてCVD技術により形成されるタングステン膜は、古くから検討されており、プラグの形成に広く用いられている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2009−267309号公報

【特許文献2】特開2005−129831号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明は、プラグが微細化しても埋め込み不良が生じることなく、低コストで形成することができ、さらに種々の半導体装置に適用可能であるプラグ及びその形成技術を提供する。

【課題を解決するための手段】

【0009】

本発明の実施形態によれば、半導体装置の製造方法は、半導体基板上に酸化シリコン膜を形成し、前記酸化シリコン膜にビアを形成し、前記ビア内側に密着層を形成し、前記密着層上にシリコン層を形成し、タングステンを含むガスを前記シリコン層と反応させることにより、前記ビアに埋め込まれたタングステン膜を形成する。

【図面の簡単な説明】

【0010】

【図1】第1の実施形態にかかる半導体装置の製造方法を説明するための断面図(その1)である。

【図2】第1の実施形態にかかる半導体装置の製造方法を説明するための断面図(その2)である。

【図3】第1の実施形態にかかる半導体装置の製造方法を説明するための断面図(その3)である。

【図4】第1の実施形態にかかる半導体装置の製造方法を説明するための断面図(その4)である。

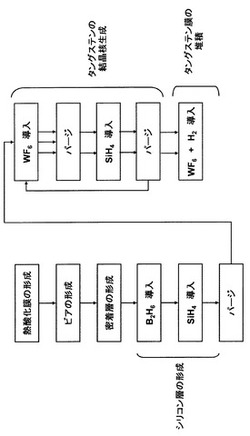

【図5】第1の実施形態にかかる半導体装置の製造方法のフローを示す図である。

【図6】第1の実施形態にかかる半導体装置の断面図である。

【図7】第1の実施形態にかかる半導体装置の断面の顕微鏡写真である。

【図8】比較例の半導体装置の製造方法のメカニズムを説明するための図である。

【図9】比較例の半導体装置の製造方法を説明するための断面図(その1)である。

【図10】比較例の半導体装置の製造方法を説明するための断面図(その2)である。

【図11】第1の実施形態にかかる半導体装置の製造方法のメカニズムを説明するための図である。

【図12】タングステンの結晶核の密度を比較した図である。

【図13】タングステンの結晶核の密度とビアの埋め込み程度との相関と、ビアの断面の顕微鏡写真を示した図である。

【図14】第3の実施形態にかかる半導体装置の製造方法のフローを示す図である。

【図15】B2H6の流量とシリコン層に含まれるボロンの濃度との相関を示した図である。

【図16】第4の実施形態にかかる半導体装置の製造方法を説明するための断面図(その1)である。

【図17】第4の実施形態にかかる半導体装置の製造方法を説明するための断面図(その2)である。

【図18】第4の実施形態にかかる半導体装置の製造方法を説明するための断面図(その3)である。

【図19】第4の実施形態にかかる半導体装置の製造方法を説明するための断面図(その4)である。

【図20】第4の実施形態にかかる半導体装置の断面図である。

【図21】窒化チタン膜上に形成されたシリコン層におけるボロンの濃度の測定結果である。

【図22】窒化チタン膜の有無とタングステン膜の堆積量との相関を示す測定結果である。

【図23】第2の実施形態にかかる半導体装置の製造方法のフローを示す図である。

【発明を実施するための形態】

【0011】

以下、図面を参照して、実施形態を説明する。ただし、本発明はこの実施形態に限定されるものではない。なお、全図面にわたり共通する部分には、共通する符号を付すものとし、重複する説明は省略する。また、図面は発明の説明とその理解を促すための模式図であり、その形状や寸法、比などは実際の装置とは異なる個所もあるが、これらは以下の説明と公知の技術とを参酌して適宜、設計変更することができる。

【0012】

(第1の実施形態)

図1から図4を用いて本実施形態にかかる半導体装置の製造方法を説明する。この図1から図4はプラグ31の製造過程を示し、半導体装置の有するプラグ31の断面に対応するものである。なお、本発明は、以下に説明するような形態のプラグに限定されるものではなく、他の形態のプラグにおいても用いることができる。

【0013】

まず、シリコン基板などの半導体基板1に素子分離膜(不図示)及び半導体層素子(不図示)を形成する。さらに、図1(a)に示すように、半導体基板1上に、例えば100nmの厚さを有する酸化シリコン膜2を層間絶縁膜として形成する。この際、多層構造を有する層間絶縁膜を形成しても良い。また、酸化シリコン膜2は、酸素とシリコンとを含有する絶縁膜であって、炭素や水素等を含有しても良い。

【0014】

次に、図1(b)に示すように、マスクパターンとRIE(Reactive Ion Etching)等のエッチングとを用いて酸化シリコン膜2を選択的に除去し、酸化シリコン膜2にビア11を形成する。例えば、ビア11のビア径は約40nm、深さが300〜400nmであり、すなわちビア11のアスペクト比は7以上である。なお、ビア11の底部には、酸化シリコン膜2の下方にある配線層(不図示)とのコンタクトをより確実にするために、チタン等からなるコンタクト層(不図示)を形成しても良い。

【0015】

そして、図2(c)に示すように、PVD技術を用いて密着層3として窒化チタン膜をビア11の内側の側壁及び底面上と酸化シリコン膜2の表面上とに形成する。なお、密着層3として、チタン膜、タンタル膜、窒化タンタル膜、窒化タングステン膜等を形成しても良い。また、密着層3は、ビア11の側壁及び底面の全体を覆うものであることが好ましいが、図2(c)に示されるように、ビア11の内側において、密着層3から酸化シリコン膜2が露出するような、不連続なものであっても良い。

【0016】

次に、ビア11の内側の密着層3の上に、薄いシリコン層4を形成する。すなわち、本実施形態においては、本発明者らがこれまで検討していた方法によるCVD技術によるタングステン膜6の埋め込みにおいて「還元ガスの吸着ステップ」と呼ばれる工程を行うかわりに、薄いシリコン層4の形成を行う。この本発明者らがこれまで検討していた方法については後で説明する。

【0017】

詳細には、まず、ビア11が形成された半導体基板1を成膜チャンバーに配置し、200〜500℃に加熱する。

【0018】

次に、1〜100000Paの条件で、10〜2000sccmのB2H6ガスを成膜チャンバー内へ導入し、その後パージを行うことなく、100〜2000sccmのSiH4ガスと100〜2000sccmのH2ガスとを成膜チャンバーに導入し、図2(d)に示されるように、シリコン層4をビア11の内側の密着層3の上に、CVD技術を用いてコンフォーマルに形成する。シリコン層4は、例えば0.2nm〜30nm程度と薄いものとして形成する。しかしながらこの膜厚に限定されるものではなく、この後の工程において、ビア11にタングステン膜6を十分に埋め込むことができ、且つ、プラグ31を形成した後に密着層3とタングステン膜6との間にシリコン層4が残存しないような膜厚になるように、シリコン層4を形成することが好ましい。但し、この後の工程において還元置換膜として消費するために必要なシリコン層4の膜厚は、タングステン膜6の成膜条件に依存して変わるため、一意的に決まるものではなく、従って、必要な条件に応じた膜厚を適用することとする。なお、B2H6ガスを用いて形成しているため、このシリコン層4にはシリコンだけでなくボロンも含まれる。

【0019】

このように、SiH4ガスとB2H6ガスとを用いてシリコン層4を形成することにより、370℃以下でSiH4ガスが熱分解することが可能となり、低温でもシリコン層4を形成することができる(このメカニズムは後で説明する)。しかしながら、低温での形成が必要でない場合には、B2H6ガスを用いる必要はなく、Si2H6ガス(熱分解温度は400℃近傍)や、SiH4ガス(熱分解温度は600℃近傍)などを利用して、薄いシリコン層4を形成してもよい。このような場合には、シリコン層4にはボロンが含まれることはない。

【0020】

シリコン層4を形成した後に、成膜チャンバー内のB2H6ガスとSiH4ガスとをパージする。

【0021】

そして、タングステン膜6を、CVD法を用いてビア11を埋め込むように形成する。すなわち、本実施形態においては、本発明者らがこれまで検討していた方法によるCVD技術によるタングステン膜6の埋め込みにおいて、「タングステンの結晶核5の生成ステップ」と「タングステン膜6の堆積ステップ」と呼ばれている工程と同様の工程を行う。なお、本発明者らがこれまで検討していた方法については、後で説明する。

【0022】

まず、「タングステンの結晶核5の生成ステップ」を行う。例えば、1〜100000Paの条件で、100〜1000sccmのWF6ガスを導入し、シリコン層4と置換反応させタングステンの初期結晶核5を形成する。その後、成膜チャンバー内のWF6ガスをいったんパージし、還元ガスであるSiH4ガスをチャンバー内に導入し、SiH4ガスをタングステンの初期結晶核5上へ吸着させる。さらに、SiH4ガスのパージを行った後、WF6ガスを成膜チャンバー内に導入する。このような、材料ガスの導入、パージ、還元ガスの導入、パージのサイクルを複数回、例えば2回から15回程度繰り返し、図3(e)に示されるように、WF6ガスと吸着したSiH4ガスを反応させ、密着層3上にタングステンの初期結晶核5を生成する。あらかじめ密着層3上に形成されたシリコン層4を反応させることにより、タングステンの初期結晶核5を密着層3上に高密度に生成することができる。この際、プラグ31の抵抗値や界面抵抗値が高くなることを避けるために、シリコン層4のすべてをWF6ガスと反応させることが好ましい。少なくとも、ビア11の底部の接触面積のうち1/2以上がタングステン膜6に覆われるように、すなわち、ビア11の底部において、タングステン膜6と密着層3との接合面がビア11の底部の接触面積に対して1/2以上の面積を有するように、ビア11の底部に位置するシリコン層4をタングステンの初期結晶核5に置換することが望ましい。シリコン層4の膜厚を調整することにより十分にタングステンの初期結晶核5を形成することができる場合には、この「タングステンの結晶核5の生成ステップ」を行わなくても良い。

【0023】

次に、「タングステン膜6の堆積ステップ」を行う。1〜100000Paの条件で、100〜1000sccmのWF6ガスと100〜3000sccmのH2ガスとを成膜チャンバー内に導入し、図3(f)に示すように、タングステン膜6を堆積させる。

【0024】

なお、これまで説明した各ステップにおけるキャリアガスとしては、例えば、100〜10000sccmのArガスや、100〜1000sccmのN2ガスを用いることができる。また、タングステン膜6の形成のためのプロセス温度は、200〜500℃で種々選択可能である。さらに、シリコン層4の形成、「タングステンの初期結晶核5の生成ステップ」、「タングステン膜6の堆積ステップ」の際のプロセス温度は、同じであっても、異なるものであってもよく、目的に応じて種々選択することができる。

【0025】

次いで、図4(g)に示すように、ビア11から突出したタングステン膜6と密着層3とをCMP(Chemical Mechanical Polishing)により研磨して除去することにより、プラグ31を形成する。

【0026】

なお、本実施形態の変形例として、上記の本実施形態と異なり、密着層3を形成しないものが挙げられる。

【0027】

これまで説明したプラグ31の製造方法のフローチャートを図5に示す。

【0028】

以上のようにして形成されたプラグ31は、図6(a)の断面図に示され、詳細には、本実施形態のプラグ31は、半導体基板1上に形成された酸化シリコン膜2に設けられたビア11と、ビア11の内側の側壁及び底面上の窒化チタン膜等からなる密着層3と、ビア11に埋め込まれたタングステン膜6とからなる。なお、密着層3は、ビア11の内側の側壁及び底面の全体を覆う膜であることに限定されるものではなく、ビア11の内側の側壁又は底面を覆うような、もしくは、これらの一部を覆うような不連続な膜であっても良い。また、密着層3とタングステン膜6との間にボロンが含まれることがある。さらに、タングステン膜6を埋め込む前に形成したシリコン層4は、WF6ガスと反応させて、最終的には密着層3上に残存しないほうが好ましいが、その一部は密着層3上に残存しても良い。この場合には、シリコン層4の膜厚は30nm以下となる。

【0029】

また、プラグ31においては、図6(b)に示されるように、酸化シリコン膜2の下方にある配線層(不図示)とのコンタクトをより確実にするために、ビア11の底部にチタン等からなるコンタクト層7を形成しても良い。

【0030】

図7に、このように形成したプラグ31の断面のSTEM(Scanning Transmission Electron Microscope)像を示す。図7からわかるように、PVD技術により形成された密着層3のカバレッジ不足により、ビア11の側壁において酸化シリコン膜2が密着層3から露出している箇所が確認されているが、それにもかかわらず、ビア11の全体がタングステン膜6で充填されているのがわかる。

【0031】

本実施形態においては、例えばビア11が高アスペクト比のものとなったことに起因して、PVD技術で形成された密着層3が不連続な膜となり、ビア11において酸化シリコン膜2の一部が密着層3から露出した状態であっても、ビア11の内側にシリコン層4を形成することにより、ビア11の内側に高密度のタングステンの初期結晶核5を生成することができる。従って、ビア11の内側に未充填の箇所を生じることなく、ビア11にタングステン膜6を埋め込むことができる。さらに、本実施形態においては、密着層3のカバレッジが悪くてもかまわないことからPVD技術を用いて密着層3を形成することができるため、装置コストやランニングコストの低減を行うことができる。また、本実施形態においては、高いプロセス温度を必要とすることがないため、低温度のプロセスを必要とするような種々の半導体装置の製造に適用可能である。

【0032】

以下、本実施形態のタングステン膜6の形成のメカニズムを説明する。この際、比較例として本発明者らがこれまで検討していた方法によるタングステン膜6の形成のメカニズムと比較しながら説明する。(以下、「本発明者らがこれまで検討していた方法」を「比較例の方法」と呼ぶ。)まず、比較例の方法におけるCVD技術を用いたタングステン膜6の埋め込み過程のメカニズムについて、図8を用いて詳細に説明する。図8は、酸化シリコン膜22上の密着層3としての窒化チタン膜23上にタングステンの結晶核25が生成される過程を模式的に示した図である。なお、比較例の方法におけるCVD法によるタングステン膜の埋め込みは、通常、「還元ガスの吸着ステップ」と、「タングステンの結晶核5の生成ステップ」と、「タングステン膜6の堆積ステップ」とに分けられる。

【0033】

まず、図8(a)に示すように、酸化シリコン膜22と密着層3としての窒化チタン膜23とが形成された半導体基板(不図示)を250〜500℃に加熱する。

【0034】

次に、図8(b)に示すように還元ガスの吸着ステップを行う。詳細には、例えば、1〜100000Paの条件で、吸着させる還元ガス種としては、100〜2000sccmのSiH4ガスを、全圧調整・ガス供給安定化のために100〜3000sccmのH2ガスとの混合ガスとして導入する。或いは、吸着させる還元ガス種としてB2H6を選択する場合には、100〜2000sccmのB2H6ガスと、前述と同様に全圧調整・ガス供給安定化のためのH2ガス100〜3000sccmとを混合させ、導入する。通常、上記のいずれかの手法で、窒化チタン膜23の表面に還元ガス種を吸着させる。SiH4ガスの熱分解温度は600℃近傍であるため、600℃近傍の熱分解温度に達しない温度、例えば本実施形態で示すような250〜500℃の温度領域では、SiH4ガスは熱分解してシリコン原子を生成することはなく、SiH4ガスのまま窒化チタン膜23に吸着する。SiH4ガスの吸着は、酸化シリコン膜上と窒化チタン膜上とでは吸着確率が異なるため、窒化チタン膜23上ではSiH4ガスは高密度に吸着可能である。或いは、SiH4ガスの吸着後、窒化チタン膜の電子の寄与によりシリコン原子を一部生成する可能性もあるため、この後のタングステン膜6の形成が容易となる。しかし一方で、酸化シリコン膜上ではSiH4ガスの吸着確率が低く、その後のタングステン膜6の形成が容易ではない。そのため、窒化チタン膜23のカバレッジが悪く不連続である場合、下地の酸化シリコン膜2が露出し、この露出した部分に対してのSiH4ガスの吸着が不十分になる。さらに、SiH4ガスの吸着が主となる反応の場合には、SiH4ガス分子のサイズにある程度の大きさがあるため、既に吸着したSiH4ガスが邪魔することにより、全体としてSiH4ガスの吸着確率が下がる可能性もある。

【0035】

そして、図8(c)に示すように、「タングステンの結晶核25の生成ステップ」を行う。例えば、本発明の第1の実施形態と同様に、材料ガスとしてWF6ガスをチャンバー内に導入し、次いで、成膜チャンバー内のWF6ガスをいったんパージし、SiH4ガス又はB2H6ガスをチャンバー内に導入し、さらに、SiH4ガス又はB2H6ガスのパージを行った後、WF6ガスを成膜チャンバー内に導入する。このような、材料ガスの導入、パージ、SiH4ガス又はB2H6ガスの導入、SiH4ガス又はB2H6ガスのパージのサイクルを複数回繰り返し、図8(d)に示されるように、窒化チタン膜23に吸着させたSiH4ガス又はB2H6ガスとWF6ガスとを反応させることにより、タングステンの結晶核25を窒化チタン膜23上に生成する。

【0036】

次に、図8(e)に示すように「タングステン膜26の堆積ステップ」を行う。例えば、本発明の第1の実施形態と同様に、WF6ガスとH2ガス とを成膜チャンバー内に導入し、タングステン膜26を窒化チタン膜23上に堆積させる。

【0037】

しかし、近年、プラグ31においては、半導体装置の微細化が進むにつれ、ビア11の開口の大きさに対するプラグ31の高さ(ビア11の深さ)の割合が高くなる傾向、すなわちビア11が高アスペクト化する傾向にある。そして、高いアスペクト比を有するビア11の内側にPVD技術で密着層3を形成しようとすると、ビア11の内側全体を覆うように形成することが難しくなってきていた。

【0038】

さらに、タングステン膜6の埋め込みにおいて用いられるSiH4ガスは、窒化チタン等からなる密着層3に対して吸着しやすく、一方、層間絶縁膜である酸化シリコン膜2上には吸着しにくい。

【0039】

従って、比較例の方法においては、以下のような問題が生じることとなる。この問題を、比較例の方法によるプラグ31の製造過程を示す図9及び図10を用いて説明する。まず、先に説明したようにPVD技術で形成された密着層3においてカバレッジが不足することに起因して、図9(a)に示すように酸化シリコン膜2が密着層3から一部露出する。このような場合、露出した酸化シリコン膜2上ではSiH4ガスの吸着不足が起こるため、図9(b)に示すように、露出した酸化シリコン膜2上ではタングステンの結晶核5の生成が難しい。従って、タングステンの結晶核5が十分に生成しないことから、その後の工程において、露出した酸化シリコン膜2上ではタングステン膜6を形成することが難しく、図10(c)に示されるように、ビア11の一部にタングステン膜6に充填されてない箇所が存在することとなる。すなわち、比較例の方法においては、ビア11が埋め込み不良となる問題が生じる。

【0040】

そこで、密着層3のカバレッジ不足を解決するため、密着層3をPVD技術にかわりCVD技術で形成する手法が検討されている。CVD技術にて密着層3を形成することにより、高アスペクトのビア11に対しても密着層3をカバレッジ良く形成することができることから、ビア11の全体がタングステン膜6で充填されているようなプラグ31を形成することができる。しかしながら、CVD技術による密着層3の形成時のプロセス温度は、例えば、TiCl4ソースを用いてCVD技術により窒化チタンからなる密着層3を形成する場合には、材料ガスであるTiCl4ガスの熱分解温度が640℃近傍であるため高温となる。従って、近年の半導体素子が多様化する中で、低温領域での形成を必要とする半導体素子等を有する半導体装置の製造に対して、このようなCVD技術により密着層3を形成することを適用することは難しい。また、低温のMOCVD(Metal Organic Chemical Vapor Deposition)技術により密着層3を形成する方法もあるが、この方法は、メタリックな低抵抗な密着層3を得るためにプラズマ処理等を必要とする。通常プラズマ処理を用いて膜質を改善すると、密着層3の成膜堆積がシュリンクし、メタリックな特性を得ることができる。このプラズマ処理は、酸化シリコン膜2の表面のようなフィールド表面及びビア11の底面に形成された密着層3に対しては十分に機能し、その膜質改善を行うことができるものの、ビア11の側壁に形成された密着層3の膜質改善については、有効には機能しない。従って、ビア11の側壁に形成された密着層3に対してはプラズマ処理が有効に働かないため、また、微細化すればするほど、プラズマ処理が十分に機能することができないという問題が顕著になってくるため、MOCVD技術により形成された高抵抗な密着層3が厚膜状態でそのままビア11の側壁に残ることになる。そのため、プラグ31はますます高抵抗化し、必ずしも最適な方法とはいえない。さらに、CVD技術は、装置コスト・運用コストがPVD技術と比較して高いという問題点も有する。

【0041】

次に、本実施形態におけるCVD技術を用いたタングステン膜6の埋め込み過程のメカニズムについて、図11を用いて詳細に説明する。図11は、層間絶縁膜である酸化シリコン膜2上にタングステンの結晶核5が生成される過程を模式的に示した図である。

【0042】

まず、図11(a)に示されるように、成膜チャンバー内に酸化シリコン膜22が形成された半導体基板(不図示)を配置し、例えば200から500℃に加熱する。

【0043】

次に、B2H6ガスを導入し、酸化シリコン膜22に吸着させる。詳細には、図11(b)に示されるように、B2H6ガスは、成膜チャンバーの気相内あるいは酸化シリコン膜2上でBH3に熱分解し、酸化シリコン膜22に吸着する。

【0044】

そして、比較例の方法とは異なり、図11(c)に示されるように、導入したB2H6ガスをパージせずに連続してSiH4ガスを導入する。先に説明したように、SiH4ガスの熱分解温度は600℃近傍であるため、それに達しない温度では熱分解しシリコン原子を生成することは無いが、本実施形態においては、酸化シリコン膜22の上にBH3が存在し、そのBH3が触媒として作用するため、SiH4ガスが熱分解されシリコン原子を生成する。これにより、370℃以下のような低温であっても、図11(d)に示されるように薄いシリコン層24を均一に形成することができる。また、この熱分解反応は非平衡反応であるため、シリコン層24の形成時間を長くすることにより、より高密度なシリコン原子からなるシリコン層24を形成することができる。さらに、堆積したシリコン原子は、ビア11の底面及び側壁上のキンクやステップといったエネルギー的により安定な箇所に移動しシリコン−シリコン結合を形成するため、より高密度なシリコン原子からなるシリコン層24を形成することができる。

【0045】

次に、「タングステンの結晶核25の生成ステップ」を行う。比較例の方法と同様に、SiH4ガスを導入し次いでパージし、WF6ガスを導入し次いでパージする、一連のサイクルを繰り返す。この際、このシリコン層24がWF6ガスと還元反応を生じ、シリコンはタングステンと置換され、タングステンの結晶核25が酸化シリコン膜22上に高密度に生成する。

【0046】

そして、比較例の方法と同様に、「タングステン膜26の堆積ステップ」を行う。この際、タングステンの結晶核25が高密度で存在することから、タングステン膜26と酸化シリコン膜22とが接する接点が増え、酸化シリコン膜22との密着性の高いタングステン膜26を形成することができる。

【0047】

すなわち、比較例の方法とは異なり、本実施形態においては、ビア11が微細化することに起因して、PVD技術により形成された密着層3のカバレッジが不足しても、シリコン層4を形成することにより、ビア11の内側に高密度のタングステンの初期結晶核5を生成することができる。従って、ビア11の内側に未充填の箇所が生じることを避け、ビア11にタングステン膜6を埋め込むことができる。さらに、本実施形態においては、密着層3のカバレッジが悪くてもかまわないことからPVD技術を用いて密着層3を形成することができるため、CVD技術を用いた場合と比べて装置コストやランニングコストの低減を行うことができる。また、本実施形態においては、高いプロセス温度を必要とすることがないため、低温度のプロセスを必要とするような種々の半導体装置の製造に適用可能である。

【0048】

さらに、本実施形態においては、シリコン層4の形成方法として、B2H6ガスを成膜チャンバーへ導入し、その後パージをすることなくSiH4ガスとH2ガスとを導入しているが、このようにB2H6ガスを導入し次いでSiH4ガスを導入することにより、シリコン層4の初期形成時にはボロン濃度の高いシリコン層4が半導体基板1側に形成され、次にシリコン濃度の高いシリコン層がシリコン層4の上層側に形成することができる。従って、本実施形態によれば、タングステン結晶核5の生成を行うために必要なシリコンを表層により高濃度に存在させることができることから、この後の工程においてタングステンの結晶核5の生成をより効率よく行うことができる。

【0049】

次に、本実施形態の効果を調べるため、以下のようなサンプルを作成し、その表面を走査型電子顕微鏡(SEM)で観察し、それによって得たSEM像から各表面におけるタングステンの初期結晶核5の密度を測定した。

【0050】

サンプルAは、上記の本実施形態の製造方法と同様に、半導体基板1上に厚さ100nmの酸化シリコン膜2を形成し、その上にシリコン層4を形成し、さらに「タングステンの結晶核5の生成ステップ」の一連のサイクルを2回行うことにより得たものである。比較例としてのサンプルBは、先に説明した比較例の方法と同様に、半導体基板1に厚さ100nmの酸化シリコン膜2を形成し、次いで、「還元ガスの吸着ステップ」を行い、さらに「タングステンの結晶核生成ステップ」の一連のサイクルを2回行うことにより得たものである。

【0051】

各サンプルの表面をSEMにて観察し、そのSEM像からタングステンの結晶核5の密度を測定した。その結果を示す図12によれば、本実施形態にあたるサンプルAのタングステンの結晶核5の密度は、14890個/μm2であり、サンプルBのタングステンの結晶核5の密度は、8330個/μm2であった。

【0052】

すなわち、本実施形態によれば、シリコン層4を形成することにより、タングステンの結晶核5を酸化シリコン膜2の上により高密度に形成することができることが明らかになった。

【0053】

さらに、本発明者らは詳細な解析を行い、タングステンの結晶核5の密度とビア11におけるタングステン膜6の埋め込み状態との関係を明らかにし、本実施形態の効果を確認した。この結果を示したものが図13となる。

【0054】

詳細には、図13(a)の横軸は、タングステンの結晶核5の密度を示し、縦軸はビア11におけるタングステン膜6の埋め込み程度(充填率)を示す。この埋め込み程度とは、図13(b)に示すように、ビア11の高さ(Y)に対する、ビア11の間口からビア11の底部にかけてのタングステン膜6が埋め込まれている高さ(X)の割合(X/Y)(充填率)のこととする。図13(a)に示されるように、タングステンの結晶核5の密度とタングステン膜6の埋め込み程度とには一定の相関があり、タングステンの結晶核5の密度が上昇することにより、タングステン膜6の埋め込み程度を示す値が高くなり、ビア11がタングステン膜6により充填されることが分かる。また、この図13(a)により、タングステンの結晶核5の密度が約12500個/μm2以上で、ビア11を完全に充填することが可能になることが予測できる。さらに、このようなビア11をタングステン膜6で完全に充填することが可能となると予測される密度の領域は、先に説明した比較例の方法を用いた場合では実現が難しく、一方、本実施形態を用いた場合では実現できると考えられる。

【0055】

すなわち、上記の結果から、タングステンの結晶核5の密度が高くなるほど、ビア11がタングステン膜6により充填されることがわかった。従って、本実施形態によれば、高密度のタングステンの結晶核5が生成できることから、ビア11の内側に未充填の箇所を生じることを避け、ビア11にタングステン膜6を埋め込むことができる。

【0056】

(第2の実施形態)

第1の実施形態においては、シリコン層4の形成方法の際、B2H6ガスを導入し次いでパージすることなくSiH4ガスを導入することにより、タングステン結晶核5の生成を行うために必要なシリコンを表層により高濃度に存在させ、この後の工程においてタングステンの結晶核5の生成を効率的に行っていた。一方、本実施形態においては、B2H6ガスを導入し、パージした後にSiH4ガスを導入し、次いでパージした後にWF6ガスを導入し、さらにパージする一連のサイクルを複数回繰り返す。言い換えると、これらのガスを順次導入してパージすることを繰り返すことによりシリコン層4の形成とタングステンの結晶核5の生成とを行うものである。このようにすることにより、成膜温度を高くしても、カバレッジの良いシリコン層4を形成し、ひいてはビア11の内側により高密度のタングステンの初期結晶核5を生成することができる。

【0057】

以下、本実施形態を説明する。以下、プラグ31の製造過程を例として説明するが、本発明は、以下に説明するような形態のプラグに限定されるものではない。また、本実施形態の製造工程は、第1の実施形態の説明で用いた図1から図4に表わされ、ここでは、第1の実施形態と共通する部分については説明を省略する。

【0058】

第1の実施形態と同様に、図1(a)に示すように半導体基板1上に酸化シリコン膜2を形成し、図1(b)に示すようにこの酸化シリコン膜2にビア11を形成する。次いで、図2(c)に示すように、PVD技術を用いてビア11の内側と酸化シリコン膜2の表面上とに密着層3として窒化チタン膜を形成する。さらに、密着層3が形成された半導体基板1を成膜チャンバーに配置し、所望の温度、例えば410℃で加熱する。

【0059】

次に、例えば1〜100000Paの条件で、10〜2000sccmのB2H6ガスを成膜チャンバー内へ導入し、一度パージを行い、次いで100〜2000sccmのSiH4ガスと100〜2000sccmのH2ガスとを成膜チャンバーに導入し、さらにパージを行う。次に、例えば、1〜100000Paの条件で、100〜1000sccmのWF6ガスを導入し、またパージを行う。このような一連のサイクルを複数回繰り返し、シリコン層4の形成とタングステンの結晶核5の生成とを行う。

【0060】

さらに、第1の実施形態と同様に、「タングステン膜6の堆積ステップ」を行う。例えば、1〜100000Paの条件で、100〜1000sccmのWF6ガスと100〜3000sccmのH2ガスとを成膜チャンバー内に導入し、図3(e)に示すように、タングステン膜6を堆積させる。この後の工程は、図3(f)及び図4(g)に示され、第1の実施形態と同様であるため、ここでは説明を省略する。

【0061】

本実施形態のプラグ31の製造方法のフローチャートを図23に示す。

【0062】

本実施形態によれば、B2H6ガスを導入し、パージした後にSiH4ガスを導入することにより、SiH4ガスは、ビア11の内側に吸着したB2H6ガスのみと主に反応し、シリコン層4を形成することができる。従って、成膜温度を高くしても、カバレッジの良いシリコン層4を形成し、ひいてはビア11の内側により高密度のタングステンの初期結晶核5を生成することができる。

【0063】

なお、成膜温度が低温である場合(例えば350℃以下の場合)において、第2の実施形態のようにB2H6ガスを導入し、パージした後にSiH4ガスを導入すると、ビア11の内側に吸着したB2H6ガスの吸着量が少ないことから、B2H6ガスとSiH4ガスとの反応速度が低下し、シリコン層4の形成時間が長くなってしまう。従って、生産性の観点から、成膜温度が低温の場合には第1の実施形態を行うことが望ましい。一方、成膜温度が高温である場合(例えば350℃より高い場合)において、第1の実施形態のようにB2H6ガスとSiH4ガスとが成膜チャンバー内で混ざってしまうと、B2H6ガスとSiH4ガスとの反応速度は増加し、ビア11の底までB2H6ガスとSiH4ガスとが到達する前にこれらのガスが消費されてしまう。よって、ビア11の内側に形成されるシリコン層4のカバレッジが悪くなってしまうこととなる。従って、このようなことを避けるために、成膜温度が高温の場合には、カバレッジの観点で、第2の実施形態を行うことが望ましい。

【0064】

(第3の実施形態)

第1の実施形態においては、シリコン層4の形成方法の際、B2H6ガスを導入し次いでパージすることなくSiH4ガスを導入することにより、タングステン結晶核5の生成を行うために必要なシリコンを表層により高濃度に存在させ、この後の工程においてタングステンの結晶核5の生成を効率的に行っていた。一方、所望のプラグ31を形成するためには、シリコン層4の膜厚を精度良く制御することも必要であり、その方法の1つとして、第1の実施形態と異なり、B2H6ガスとSiH4ガスとを同時に成膜チャンバー内へ導入してシリコン層4を形成する本実施形態が挙げられる。

【0065】

以下、本実施形態を説明する。以下、プラグ31の製造過程を例として説明するが、本発明は、以下に説明するような形態のプラグに限定されるものではない。また、本実施形態の製造工程は、第1の実施形態の説明で用いた図1から図4に表わされ、ここでは、第1の実施形態と共通する部分については説明を省略する。

【0066】

第1の実施形態と同様に、図1(a)に示すように半導体基板1上に酸化シリコン膜2を形成し、図1(b)に示すようにこの酸化シリコン膜2にビア11を形成する。次いで、図2(c)に示すように、PVD技術を用いてビア11の内側と酸化シリコン膜2の表面上とに密着層3として窒化チタン膜を形成する。さらに、密着層3が形成された半導体基板1を成膜チャンバーに配置し、所望の温度、例えば300℃で加熱する。

【0067】

次に、1〜100000Paの条件で、100〜2000sccmのSiH4ガスと、10〜2000sccmのB2H6ガスとを同時に成膜チャンバー内へ導入し、図2(d)に示されるように、シリコン層4をビア11の内側にCVD技術を用いて形成する。この際、B2H6ガスとSiH4ガスとの流量比を制御することによりシリコン層4の成膜レートを制御して、所望の膜厚を有するシリコン層4を精度良く形成することができる。さらに、シリコン層4のシリコン濃度を制御することができる。この後は、第1の実施形態と同様であるため、ここでは説明を省略する。

【0068】

本実施形態のプラグ31の製造方法のフローチャートを図14に示す。

【0069】

本実施形態によれば、B2H6ガスとSiH4ガスとの流量比を制御することにより、シリコン層4の成膜レートを制御して、所望の膜厚を有するシリコン層4を精度良く形成することができる。さらに、タングステンの結晶核5の効率的な生成のためのシリコン層4中のシリコン濃度を制御することが可能となる。これによって、この後の工程で生成されるタングステンの結晶核5の密度を制御することができる。

【0070】

以下に、B2H6ガスとSiH4ガスとの流量比を変化させた場合のシリコン層4中のボロン濃度について説明する。

【0071】

例えば、SiH4ガスを100〜2000sccm、B2H6 ガスを500〜2000sccmとした条件(条件A)でシリコン層4を形成し、SIMS(Secondary Ion Mass Spectrometry)を用いてシリコン層4中のボロンの濃度を分析したところ、3.3E+22atom/cm3であった。また、SiH4ガスを100〜2000sccm、B2H6ガスを10〜500sccmとした条件(条件B)でシリコン層4を形成し、SIMSを用いてシリコン層4中のボロンの濃度を分析したところ、1.3E+22atom/cm3であった。このようにして得られた結果をまとめたものが図15である。図15の横軸はB2H6/SiH4の流量比を示し、縦軸はシリコン層4中のボロン濃度を示す。ボロン濃度は、成膜時の圧力、温度等により変化するが、これらの条件を同じにした場合、B2H6とSiH4との流量比を制御することにより、シリコン層4中のボロン濃度を変えることが可能であることがわかる。従って、ボロン濃度が変化していることから、それにともない、シリコン層4中のシリコン濃度も変化していると考えられる。

【0072】

また、上記の条件A及び条件Bにてシリコン層4を形成し、その上に第1の実施形態と同様にタングステンの結晶核5を生成した。さらに、その表面をSEMで観察し、それによって得たSEM像から各表面におけるタングステンの初期結晶核5の密度を測定した。その結果、条件Aでは、タングステンの初期結晶核5の密度は11010個/μm2であり、条件Bでは12500個/μm2であった。この結果から、ボロン濃度の値が減少するに従って、言い換えると、シリコン濃度の値が増加するに従って、タングステンの初期結晶核5の密度が上昇することがわかった。

【0073】

すなわち、本実施形態によれば、B2H6ガスとSiH4ガスとの流量比を制御することにより、タングステンの結晶核5の効率的な生成のためのシリコン層4中のシリコン濃度を制御することができ、これによって、タングステンの結晶核5の密度を制御することができる。

【0074】

なお、第1の実施形態及び第3の実施形態においては、ともに、B2H6とSiH4との反応を利用したシリコン原子を生成する工程のプロセス温度が、SiH4ガスが熱分解するために必要な600℃近傍の温度に達していない場合を例として説明しているが、このプロセス温度が600℃を超える場合であっても、第1の実施形態及び第3の実施形態を適用してもよい。このようにプロセス温度が600℃を超える場合には、B2H6とSiH4との反応を利用して生成されるシリコン原子と、SiH4の熱分解から生成されるシリコン原子との両方を利用することができる。

【0075】

(第4の実施形態)

第1の実施形態では、酸化シリコン膜2のビア11の底面及び側壁上に密着層3を形成していたが、本実施形態においては、酸化シリコン膜2のビア11の内側の側壁上部に窒化チタンからなる密着層3を選択的に形成する点が、第1の実施形態と異なる点である。このようにすることで、ビア11の上部と下部とでタングステン膜6の堆積速度を変えることができ、従って、タングステン膜6に充填されたプラグ31を形成することができる。

【0076】

図16から図19を用いて本実施形態にかかる半導体装置の製造方法を説明する。この図16から図19は、プラグ31の製造過程を示し、半導体装置の有するプラグ31の断面に対応するものである。なお、本発明は、以下に説明するような形態のプラグに限定されるものではない。また、第1の実施形態と共通する部分については説明を省略する。

【0077】

第1の実施形態と同様に、図16(a)に示すように半導体基板1上に酸化シリコン膜2を形成し、図16(b)に示すように酸化シリコン膜2にビア11を形成する。

【0078】

そして、図17(c)に示すように、第1の実施形態と同様に、PVD技術を用いて、窒化チタンからなる密着層3をビア11の側壁上部と酸化シリコン膜2の表面との上に選択的に形成し、ビア11の側壁の中部から下部にかけては酸化シリコン膜2が露出したままとする。なお、ビア11の側壁上部に形成された密着層3は、ビア11の側壁上部を覆う連続した膜として形成されることが好ましい。

【0079】

さらに、図17(d)に示すように、第1の実施形態と同様にして、非常に薄いシリコン層4を形成する。この際、ボロンは窒化チタン膜と親和性が高いことから、B2H6ガスが窒化チタン膜に選択的に吸着する。従って、ビア11の側壁の上部に位置する窒化チタンからなる密着層3上に形成されたシリコン層4中のボロンの濃度は、ビア11の側壁の中部から下部の上に形成されたシリコン層4中のボロンの濃度よりも高くなる。それにともない、ビア11の側壁の上部に位置する密着層3上に形成されたシリコン層4中のシリコンの濃度は、ビア11の側壁の中部から下部の上に形成されたシリコン層4中のシリコンの濃度よりも低くなる。すなわち、窒化チタンからなる密着層3を選択的に形成することにより、ビア11の内側に形成するシリコン層4中のボロン及びシリコンの濃度を変化させることができる。本実施形態においては、窒化チタンからなる密着層をあらかじめ所望の位置に形成することにより、シリコン層4に含まれるボロン及びシリコンの濃度を、その位置に応じて容易に変化させることができる。

【0080】

次に、図18(e)及び図18(f)に示すように、タングステン膜6を、第1の実施形態と同様にCVD法を用いてビア11に埋め込む。この際、先に説明したように、ビア11の側壁の上部に位置する窒化チタンからなる密着層3上に形成されたシリコン層4中のシリコンの濃度は、ビア11の側壁の中部から下部の上に形成されたシリコン層4中シリコンの濃度よりも低いことから、シリコンと反応して形成されるタングステンの結晶核5の密度についても、ビア11の側壁の上部に位置する密着層3の上では、ビア11の側壁の中部及び下部の上よりも低くなる。そして、タングステンの結晶核5の密度が異なることから、ビア11の側壁の上部の上に堆積するタングステン膜6の堆積速度は、ビア11の側壁の中部から下部の上に堆積するタングステン膜6の堆積速度よりも遅くなることとなる。このようにすることにより、ビア11の開口部付近に先にタングステン膜6が堆積してビア11の開口部を塞ぎ、ビア11の下部にタングステン膜6を埋め込むことができないという、埋め込み不良のプラグ31が形成されてしまうような状況を避け、ビア11がタングステン膜6に十分に充填されたプラグ31を形成することができる。

【0081】

次いで、図19(g)に示すように、第1の実施形態と同様に、ビア11から突出したタングステン膜6と密着層3とをCMPにより研磨して除去することにより、プラグ31が形成される。

【0082】

なお、本実施形態においては、シリコン層4中のボロンの濃度差により、タングステン膜6の堆積速度が異なることを利用したが、本実施形態は、ボロンに限定するものではなく、ボロンのかわりに、WF6ガスと反応しない物質を用いても良く、このような物質としては、P(リン)、C(炭素)、Ge(ゲルマニウム)等を挙げることができる。例えば、Pを用いる場合にはPH3ガスを導入し、Cを用いる場合にはSiH3CH3ガスを導入し、Geを用いる場合にはGeH4ガスを導入する。

【0083】

また、本実施形態においては、酸化シリコン膜2のビア11の側壁上部の上に形成する密着層3は窒化シリコン膜に限定するものではなく、密着層3をチタン膜、タンタル膜、窒化タンタル膜、窒化タングステン膜等から形成しても、窒化チタン膜で形成した場合と同様の効果を得ることができる。

【0084】

以上のようにして、図20の断面図に示されるプラグ31が形成される。詳細には、本実施形態のプラグ31は、半導体基板1上に形成された酸化シリコン膜2に設けられたビア11と、ビア11の側壁上部の上に形成された窒化チタンからなる密着層3と、ビア11に埋め込まれたタングステン膜6とからなる。さらに、ビア11の側壁上部の上に形成された密着層3とタングステン膜6との間のボロンの濃度は、ビア11の側壁の中部及び下部とタングステン膜6との間のボロンの濃度と比べて高い。なお、タングステン膜6を形成する前に形成したシリコン層4はタングステンと置換させて、最終的には密着層3上に残存しないほうが好ましいが、その一部が密着層3上に残存してしまっても良い。

【0085】

本実施形態によれば、密着層3をビア11の側壁の上部に窒化チタンからなる密着層3を選択的に形成することにより、ビア11の側壁の上部の密着層3上に形成されたシリコン層4中のボロンの濃度は、ビア11の側壁の中部から下部の上に形成されたシリコン層4中のボロンの濃度よりも高くなる。その反対に、密着層3上に形成されたシリコン層4中のシリコンの濃度は、ビア11の側壁の中部から下部の上に形成されたシリコン層4中のシリコンの濃度よりも低くなる。このようにして、シリコン層4中のシリコンの濃度を変化させることにより、ビア11の側壁上部の上に堆積されるタングステン膜6の堆積速度が、ビア11の側壁の中部から下部の上に堆積されるタングステン膜6の堆積速度に比べて遅くすることができる。従って、ビア11の開口部付近に先にタングステン膜6が堆積してビア11の開口部を塞ぎ、ビア11の下部にタングステン膜6を埋め込むことができないという状況を避けることができる。言い換えると、ビア11がタングステン膜6に十分に充填されているような埋め込み性がより改善されたプラグ31を得ることができる。

【0086】

本実施形態において、密着層3である窒化チタン膜23の有無により、その上に形成したシリコン層中のボロン及びシリコンの濃度が異なることを確認するため以下のようなサンプルを作成し、各サンプルのボロン及びシリコンの濃度を電子エネルギー損失分光法(Electron Energy-Loss Spectroscopy;EELS)を用いて分析した。

【0087】

上記の本実施形態に対応するサンプルAは、図21の上段に示されるように、本実施形態の製造方法と同様に、B2H6ガスを成膜チャンバー内に導入し、パージをすることなくSiH4ガスを導入して、窒化チタン膜23の上に厚いシリコン層44を形成した。そのシリコン層44中のボロンの濃度をEELSにて測定したところ、図21に示されるように、シリコン層44の上層側に比べて、シリコン層44の下層にあたる窒化チタン膜23側にボロン濃度が高いことが確認された。また、シリコンの濃度についても、シリコン層44の上層側に比べて、シリコン層44の下層にあたる窒化チタン膜23側のシリコン濃度が低いことが確認された。

【0088】

一方、比較例としてのサンプルBは、酸化シリコン膜22の上に窒化チタン膜23を形成することなく、サンプルAの作成方法と同様に厚いシリコン層44を形成した。そのシリコン層44中のボロンの濃度をEELSにて測定したところ、シリコン層44の上層側のボロン濃度に対するシリコン層44の下層にあたる窒化チタン膜23側のボロン濃度の差は、サンプルAと比べて大きなものではなかった。

【0089】

以上のことから、シリコン層44の形成において、B2H6ガスを成膜チャンバー内に導入した場合、B2H6ガスが窒化チタン膜23に選択的に吸着したため、窒化チタン膜23直上のシリコン層44のボロン濃度が高くなり、さらに、酸化シリコン膜22上ではB2H6ガスの選択的な吸着が起こらないため、酸化シリコン膜上のシリコン層44中のボロン濃度に差が確認されなかったと考えられる。

【0090】

すなわち、窒化チタン膜23の有無により、その上に形成されるシリコン層44中のボロン濃度が変化することがわかった。

【0091】

さらに、本実施形態において、密着層3である窒化チタン膜の有無により、その上方に堆積されるタングステン膜6の堆積速度が異なることを確認するため、以下のようなサンプルを作成し、各サンプルのタングステン膜6の堆積量を蛍光X線分析により測定した。

【0092】

サンプルCは、酸化シリコン膜2上に0.2から30nmの膜厚のシリコン層4を形成したものであり、サンプルDは、酸化シリコン膜2上に窒化チタン膜を形成し、その上に0.2から30nmの膜厚のシリコン層4を形成したものである。そして、それぞれのサンプルに対して、1〜100000Paの条件の下、100〜1000sccmのWF6ガスを流してタングステン膜6を堆積し、それぞれのサンプルにおけるタングステン膜6の堆積量を蛍光X線分析により測定した。その結果を図22に示す。図22に示すように、サンプルCのタングステン膜6の堆積量は、サンプルDのタングステン膜6の堆積量と比べて1.5倍であることが確認された。

【0093】

すなわち、窒化チタン膜の有無により、その上方に堆積されるタングステン膜6の堆積速度が異なることが確認された。

【0094】

なお、ビア11の側壁の中部から下部の上に形成されるシリコン層4中のボロン濃度と、ビア11の側壁上部の上に形成されるシリコン層4中のボロン濃度とを変える方法としては、シリコン層4の形成条件を変えることによっても行うことができる。例えば、第3の実施形態と同様に、シリコン層4の形成時のB2H6ガスとSiH4ガスとの流量を制御することにより、シリコン層4中のボロン濃度を調整することができることから、最初にビア11にボロン濃度の低いシリコン層4をコンフォーマルに形成し、次いでシリコン層4のカバレッジが悪くなる条件、例えば供給律速となる条件にて、ボロン濃度の高いシリコン層4を形成することにより、ビア11の側壁の中部から下部の上に形成されたシリコン層4中のボロン濃度を低く、且つ、ビア11の側壁上部の上に形成されたシリコン層4中のボロン濃度を高く形成することができる。

【0095】

なお、第1から第4の実施形態においては、密着層3としての窒化チタン膜は、PVD技術を用いて形成するものとして説明したが、これに限定されるものではなく、CVD技術、ALD(Atomic Layer Deposition)技術を用いて薄い窒化チタン膜を形成しても同様の効果を得ることができる。なぜなら、高アスペクトのビア11の内側では、これらの技術を用いても、必ずしも、連続、且つ、均一であり、コンフォーマルな窒化チタン膜を形成できるとは限らないからである。このような場合にも、第1から第4の実施形態を用いることにより、これらの実施形態で得られる効果と同様の効果を得ることができる。

【0096】

本発明の実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0097】

1 半導体基板

2、22 酸化シリコン膜

3 密着層

4、24 薄いシリコン層

5、25 タングステン結晶核

6、26 タングステン膜

7 コンタクト層

11 ビア

23 窒化チタン膜

31 プラグ

44 厚いシリコン層

【技術分野】

【0001】

本発明の実施形態は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体装置においては、半導体素子と配線との間、配線どうしの間にある各層間を接続するために、コンタクトプラグ、及び/又は、ビアプラグが形成されている。コンタクトプラグ及びビアプラグの形成は、以下のようにして行う。

【0003】

まず、シリコン基板などの半導体基板に素子分離膜及び半導体素子を形成し、さらに半導体素子及び素子分離膜上に層間絶縁膜を形成する。

【0004】

次に、層間絶縁膜をマスクパターン及びエッチングを用いて選択的に除去し、層間絶縁膜にビアを形成する。詳細には、この形成されたビアは、拡散層上、ゲート電極上のシリサイド層と配線をつなぐためのコンタクトプラグを形成するためのコンタクトビア、もしくは、下層の配線と上層の配線とをつなぐためのビアプラグを形成するためのプラグビアである。

【0005】

そして、このように形成されたビアの内側の側壁上に、例えばPVD(Physical Vapor Deposition)技術を用いて、密着層を形成する。この密着層は、タングステン膜とも層間絶縁膜とも密着性が高く、層間絶縁膜上に比べてタングステンの結晶核が生成しやすい窒化チタン膜等からなる。さらに、CVD(Chemical Vapor Deposition)技術を用いて、タングステン膜を密着層に覆われたビアに埋め込む。その後、CMP(Chemical mechanical Polishing)技術を用いて、ビアからはみ出た密着層及びタングステン膜を除去し、コンタクトプラグ、ビアプラグを形成する。

【0006】

このようにしてCVD技術により形成されるタングステン膜は、古くから検討されており、プラグの形成に広く用いられている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2009−267309号公報

【特許文献2】特開2005−129831号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明は、プラグが微細化しても埋め込み不良が生じることなく、低コストで形成することができ、さらに種々の半導体装置に適用可能であるプラグ及びその形成技術を提供する。

【課題を解決するための手段】

【0009】

本発明の実施形態によれば、半導体装置の製造方法は、半導体基板上に酸化シリコン膜を形成し、前記酸化シリコン膜にビアを形成し、前記ビア内側に密着層を形成し、前記密着層上にシリコン層を形成し、タングステンを含むガスを前記シリコン層と反応させることにより、前記ビアに埋め込まれたタングステン膜を形成する。

【図面の簡単な説明】

【0010】

【図1】第1の実施形態にかかる半導体装置の製造方法を説明するための断面図(その1)である。

【図2】第1の実施形態にかかる半導体装置の製造方法を説明するための断面図(その2)である。

【図3】第1の実施形態にかかる半導体装置の製造方法を説明するための断面図(その3)である。

【図4】第1の実施形態にかかる半導体装置の製造方法を説明するための断面図(その4)である。

【図5】第1の実施形態にかかる半導体装置の製造方法のフローを示す図である。

【図6】第1の実施形態にかかる半導体装置の断面図である。

【図7】第1の実施形態にかかる半導体装置の断面の顕微鏡写真である。

【図8】比較例の半導体装置の製造方法のメカニズムを説明するための図である。

【図9】比較例の半導体装置の製造方法を説明するための断面図(その1)である。

【図10】比較例の半導体装置の製造方法を説明するための断面図(その2)である。

【図11】第1の実施形態にかかる半導体装置の製造方法のメカニズムを説明するための図である。

【図12】タングステンの結晶核の密度を比較した図である。

【図13】タングステンの結晶核の密度とビアの埋め込み程度との相関と、ビアの断面の顕微鏡写真を示した図である。

【図14】第3の実施形態にかかる半導体装置の製造方法のフローを示す図である。

【図15】B2H6の流量とシリコン層に含まれるボロンの濃度との相関を示した図である。

【図16】第4の実施形態にかかる半導体装置の製造方法を説明するための断面図(その1)である。

【図17】第4の実施形態にかかる半導体装置の製造方法を説明するための断面図(その2)である。

【図18】第4の実施形態にかかる半導体装置の製造方法を説明するための断面図(その3)である。

【図19】第4の実施形態にかかる半導体装置の製造方法を説明するための断面図(その4)である。

【図20】第4の実施形態にかかる半導体装置の断面図である。

【図21】窒化チタン膜上に形成されたシリコン層におけるボロンの濃度の測定結果である。

【図22】窒化チタン膜の有無とタングステン膜の堆積量との相関を示す測定結果である。

【図23】第2の実施形態にかかる半導体装置の製造方法のフローを示す図である。

【発明を実施するための形態】

【0011】

以下、図面を参照して、実施形態を説明する。ただし、本発明はこの実施形態に限定されるものではない。なお、全図面にわたり共通する部分には、共通する符号を付すものとし、重複する説明は省略する。また、図面は発明の説明とその理解を促すための模式図であり、その形状や寸法、比などは実際の装置とは異なる個所もあるが、これらは以下の説明と公知の技術とを参酌して適宜、設計変更することができる。

【0012】

(第1の実施形態)

図1から図4を用いて本実施形態にかかる半導体装置の製造方法を説明する。この図1から図4はプラグ31の製造過程を示し、半導体装置の有するプラグ31の断面に対応するものである。なお、本発明は、以下に説明するような形態のプラグに限定されるものではなく、他の形態のプラグにおいても用いることができる。

【0013】

まず、シリコン基板などの半導体基板1に素子分離膜(不図示)及び半導体層素子(不図示)を形成する。さらに、図1(a)に示すように、半導体基板1上に、例えば100nmの厚さを有する酸化シリコン膜2を層間絶縁膜として形成する。この際、多層構造を有する層間絶縁膜を形成しても良い。また、酸化シリコン膜2は、酸素とシリコンとを含有する絶縁膜であって、炭素や水素等を含有しても良い。

【0014】

次に、図1(b)に示すように、マスクパターンとRIE(Reactive Ion Etching)等のエッチングとを用いて酸化シリコン膜2を選択的に除去し、酸化シリコン膜2にビア11を形成する。例えば、ビア11のビア径は約40nm、深さが300〜400nmであり、すなわちビア11のアスペクト比は7以上である。なお、ビア11の底部には、酸化シリコン膜2の下方にある配線層(不図示)とのコンタクトをより確実にするために、チタン等からなるコンタクト層(不図示)を形成しても良い。

【0015】

そして、図2(c)に示すように、PVD技術を用いて密着層3として窒化チタン膜をビア11の内側の側壁及び底面上と酸化シリコン膜2の表面上とに形成する。なお、密着層3として、チタン膜、タンタル膜、窒化タンタル膜、窒化タングステン膜等を形成しても良い。また、密着層3は、ビア11の側壁及び底面の全体を覆うものであることが好ましいが、図2(c)に示されるように、ビア11の内側において、密着層3から酸化シリコン膜2が露出するような、不連続なものであっても良い。

【0016】

次に、ビア11の内側の密着層3の上に、薄いシリコン層4を形成する。すなわち、本実施形態においては、本発明者らがこれまで検討していた方法によるCVD技術によるタングステン膜6の埋め込みにおいて「還元ガスの吸着ステップ」と呼ばれる工程を行うかわりに、薄いシリコン層4の形成を行う。この本発明者らがこれまで検討していた方法については後で説明する。

【0017】

詳細には、まず、ビア11が形成された半導体基板1を成膜チャンバーに配置し、200〜500℃に加熱する。

【0018】

次に、1〜100000Paの条件で、10〜2000sccmのB2H6ガスを成膜チャンバー内へ導入し、その後パージを行うことなく、100〜2000sccmのSiH4ガスと100〜2000sccmのH2ガスとを成膜チャンバーに導入し、図2(d)に示されるように、シリコン層4をビア11の内側の密着層3の上に、CVD技術を用いてコンフォーマルに形成する。シリコン層4は、例えば0.2nm〜30nm程度と薄いものとして形成する。しかしながらこの膜厚に限定されるものではなく、この後の工程において、ビア11にタングステン膜6を十分に埋め込むことができ、且つ、プラグ31を形成した後に密着層3とタングステン膜6との間にシリコン層4が残存しないような膜厚になるように、シリコン層4を形成することが好ましい。但し、この後の工程において還元置換膜として消費するために必要なシリコン層4の膜厚は、タングステン膜6の成膜条件に依存して変わるため、一意的に決まるものではなく、従って、必要な条件に応じた膜厚を適用することとする。なお、B2H6ガスを用いて形成しているため、このシリコン層4にはシリコンだけでなくボロンも含まれる。

【0019】

このように、SiH4ガスとB2H6ガスとを用いてシリコン層4を形成することにより、370℃以下でSiH4ガスが熱分解することが可能となり、低温でもシリコン層4を形成することができる(このメカニズムは後で説明する)。しかしながら、低温での形成が必要でない場合には、B2H6ガスを用いる必要はなく、Si2H6ガス(熱分解温度は400℃近傍)や、SiH4ガス(熱分解温度は600℃近傍)などを利用して、薄いシリコン層4を形成してもよい。このような場合には、シリコン層4にはボロンが含まれることはない。

【0020】

シリコン層4を形成した後に、成膜チャンバー内のB2H6ガスとSiH4ガスとをパージする。

【0021】

そして、タングステン膜6を、CVD法を用いてビア11を埋め込むように形成する。すなわち、本実施形態においては、本発明者らがこれまで検討していた方法によるCVD技術によるタングステン膜6の埋め込みにおいて、「タングステンの結晶核5の生成ステップ」と「タングステン膜6の堆積ステップ」と呼ばれている工程と同様の工程を行う。なお、本発明者らがこれまで検討していた方法については、後で説明する。

【0022】

まず、「タングステンの結晶核5の生成ステップ」を行う。例えば、1〜100000Paの条件で、100〜1000sccmのWF6ガスを導入し、シリコン層4と置換反応させタングステンの初期結晶核5を形成する。その後、成膜チャンバー内のWF6ガスをいったんパージし、還元ガスであるSiH4ガスをチャンバー内に導入し、SiH4ガスをタングステンの初期結晶核5上へ吸着させる。さらに、SiH4ガスのパージを行った後、WF6ガスを成膜チャンバー内に導入する。このような、材料ガスの導入、パージ、還元ガスの導入、パージのサイクルを複数回、例えば2回から15回程度繰り返し、図3(e)に示されるように、WF6ガスと吸着したSiH4ガスを反応させ、密着層3上にタングステンの初期結晶核5を生成する。あらかじめ密着層3上に形成されたシリコン層4を反応させることにより、タングステンの初期結晶核5を密着層3上に高密度に生成することができる。この際、プラグ31の抵抗値や界面抵抗値が高くなることを避けるために、シリコン層4のすべてをWF6ガスと反応させることが好ましい。少なくとも、ビア11の底部の接触面積のうち1/2以上がタングステン膜6に覆われるように、すなわち、ビア11の底部において、タングステン膜6と密着層3との接合面がビア11の底部の接触面積に対して1/2以上の面積を有するように、ビア11の底部に位置するシリコン層4をタングステンの初期結晶核5に置換することが望ましい。シリコン層4の膜厚を調整することにより十分にタングステンの初期結晶核5を形成することができる場合には、この「タングステンの結晶核5の生成ステップ」を行わなくても良い。

【0023】

次に、「タングステン膜6の堆積ステップ」を行う。1〜100000Paの条件で、100〜1000sccmのWF6ガスと100〜3000sccmのH2ガスとを成膜チャンバー内に導入し、図3(f)に示すように、タングステン膜6を堆積させる。

【0024】

なお、これまで説明した各ステップにおけるキャリアガスとしては、例えば、100〜10000sccmのArガスや、100〜1000sccmのN2ガスを用いることができる。また、タングステン膜6の形成のためのプロセス温度は、200〜500℃で種々選択可能である。さらに、シリコン層4の形成、「タングステンの初期結晶核5の生成ステップ」、「タングステン膜6の堆積ステップ」の際のプロセス温度は、同じであっても、異なるものであってもよく、目的に応じて種々選択することができる。

【0025】

次いで、図4(g)に示すように、ビア11から突出したタングステン膜6と密着層3とをCMP(Chemical Mechanical Polishing)により研磨して除去することにより、プラグ31を形成する。

【0026】

なお、本実施形態の変形例として、上記の本実施形態と異なり、密着層3を形成しないものが挙げられる。

【0027】

これまで説明したプラグ31の製造方法のフローチャートを図5に示す。

【0028】

以上のようにして形成されたプラグ31は、図6(a)の断面図に示され、詳細には、本実施形態のプラグ31は、半導体基板1上に形成された酸化シリコン膜2に設けられたビア11と、ビア11の内側の側壁及び底面上の窒化チタン膜等からなる密着層3と、ビア11に埋め込まれたタングステン膜6とからなる。なお、密着層3は、ビア11の内側の側壁及び底面の全体を覆う膜であることに限定されるものではなく、ビア11の内側の側壁又は底面を覆うような、もしくは、これらの一部を覆うような不連続な膜であっても良い。また、密着層3とタングステン膜6との間にボロンが含まれることがある。さらに、タングステン膜6を埋め込む前に形成したシリコン層4は、WF6ガスと反応させて、最終的には密着層3上に残存しないほうが好ましいが、その一部は密着層3上に残存しても良い。この場合には、シリコン層4の膜厚は30nm以下となる。

【0029】

また、プラグ31においては、図6(b)に示されるように、酸化シリコン膜2の下方にある配線層(不図示)とのコンタクトをより確実にするために、ビア11の底部にチタン等からなるコンタクト層7を形成しても良い。

【0030】

図7に、このように形成したプラグ31の断面のSTEM(Scanning Transmission Electron Microscope)像を示す。図7からわかるように、PVD技術により形成された密着層3のカバレッジ不足により、ビア11の側壁において酸化シリコン膜2が密着層3から露出している箇所が確認されているが、それにもかかわらず、ビア11の全体がタングステン膜6で充填されているのがわかる。

【0031】

本実施形態においては、例えばビア11が高アスペクト比のものとなったことに起因して、PVD技術で形成された密着層3が不連続な膜となり、ビア11において酸化シリコン膜2の一部が密着層3から露出した状態であっても、ビア11の内側にシリコン層4を形成することにより、ビア11の内側に高密度のタングステンの初期結晶核5を生成することができる。従って、ビア11の内側に未充填の箇所を生じることなく、ビア11にタングステン膜6を埋め込むことができる。さらに、本実施形態においては、密着層3のカバレッジが悪くてもかまわないことからPVD技術を用いて密着層3を形成することができるため、装置コストやランニングコストの低減を行うことができる。また、本実施形態においては、高いプロセス温度を必要とすることがないため、低温度のプロセスを必要とするような種々の半導体装置の製造に適用可能である。

【0032】

以下、本実施形態のタングステン膜6の形成のメカニズムを説明する。この際、比較例として本発明者らがこれまで検討していた方法によるタングステン膜6の形成のメカニズムと比較しながら説明する。(以下、「本発明者らがこれまで検討していた方法」を「比較例の方法」と呼ぶ。)まず、比較例の方法におけるCVD技術を用いたタングステン膜6の埋め込み過程のメカニズムについて、図8を用いて詳細に説明する。図8は、酸化シリコン膜22上の密着層3としての窒化チタン膜23上にタングステンの結晶核25が生成される過程を模式的に示した図である。なお、比較例の方法におけるCVD法によるタングステン膜の埋め込みは、通常、「還元ガスの吸着ステップ」と、「タングステンの結晶核5の生成ステップ」と、「タングステン膜6の堆積ステップ」とに分けられる。

【0033】

まず、図8(a)に示すように、酸化シリコン膜22と密着層3としての窒化チタン膜23とが形成された半導体基板(不図示)を250〜500℃に加熱する。

【0034】

次に、図8(b)に示すように還元ガスの吸着ステップを行う。詳細には、例えば、1〜100000Paの条件で、吸着させる還元ガス種としては、100〜2000sccmのSiH4ガスを、全圧調整・ガス供給安定化のために100〜3000sccmのH2ガスとの混合ガスとして導入する。或いは、吸着させる還元ガス種としてB2H6を選択する場合には、100〜2000sccmのB2H6ガスと、前述と同様に全圧調整・ガス供給安定化のためのH2ガス100〜3000sccmとを混合させ、導入する。通常、上記のいずれかの手法で、窒化チタン膜23の表面に還元ガス種を吸着させる。SiH4ガスの熱分解温度は600℃近傍であるため、600℃近傍の熱分解温度に達しない温度、例えば本実施形態で示すような250〜500℃の温度領域では、SiH4ガスは熱分解してシリコン原子を生成することはなく、SiH4ガスのまま窒化チタン膜23に吸着する。SiH4ガスの吸着は、酸化シリコン膜上と窒化チタン膜上とでは吸着確率が異なるため、窒化チタン膜23上ではSiH4ガスは高密度に吸着可能である。或いは、SiH4ガスの吸着後、窒化チタン膜の電子の寄与によりシリコン原子を一部生成する可能性もあるため、この後のタングステン膜6の形成が容易となる。しかし一方で、酸化シリコン膜上ではSiH4ガスの吸着確率が低く、その後のタングステン膜6の形成が容易ではない。そのため、窒化チタン膜23のカバレッジが悪く不連続である場合、下地の酸化シリコン膜2が露出し、この露出した部分に対してのSiH4ガスの吸着が不十分になる。さらに、SiH4ガスの吸着が主となる反応の場合には、SiH4ガス分子のサイズにある程度の大きさがあるため、既に吸着したSiH4ガスが邪魔することにより、全体としてSiH4ガスの吸着確率が下がる可能性もある。

【0035】

そして、図8(c)に示すように、「タングステンの結晶核25の生成ステップ」を行う。例えば、本発明の第1の実施形態と同様に、材料ガスとしてWF6ガスをチャンバー内に導入し、次いで、成膜チャンバー内のWF6ガスをいったんパージし、SiH4ガス又はB2H6ガスをチャンバー内に導入し、さらに、SiH4ガス又はB2H6ガスのパージを行った後、WF6ガスを成膜チャンバー内に導入する。このような、材料ガスの導入、パージ、SiH4ガス又はB2H6ガスの導入、SiH4ガス又はB2H6ガスのパージのサイクルを複数回繰り返し、図8(d)に示されるように、窒化チタン膜23に吸着させたSiH4ガス又はB2H6ガスとWF6ガスとを反応させることにより、タングステンの結晶核25を窒化チタン膜23上に生成する。

【0036】

次に、図8(e)に示すように「タングステン膜26の堆積ステップ」を行う。例えば、本発明の第1の実施形態と同様に、WF6ガスとH2ガス とを成膜チャンバー内に導入し、タングステン膜26を窒化チタン膜23上に堆積させる。

【0037】

しかし、近年、プラグ31においては、半導体装置の微細化が進むにつれ、ビア11の開口の大きさに対するプラグ31の高さ(ビア11の深さ)の割合が高くなる傾向、すなわちビア11が高アスペクト化する傾向にある。そして、高いアスペクト比を有するビア11の内側にPVD技術で密着層3を形成しようとすると、ビア11の内側全体を覆うように形成することが難しくなってきていた。

【0038】

さらに、タングステン膜6の埋め込みにおいて用いられるSiH4ガスは、窒化チタン等からなる密着層3に対して吸着しやすく、一方、層間絶縁膜である酸化シリコン膜2上には吸着しにくい。

【0039】

従って、比較例の方法においては、以下のような問題が生じることとなる。この問題を、比較例の方法によるプラグ31の製造過程を示す図9及び図10を用いて説明する。まず、先に説明したようにPVD技術で形成された密着層3においてカバレッジが不足することに起因して、図9(a)に示すように酸化シリコン膜2が密着層3から一部露出する。このような場合、露出した酸化シリコン膜2上ではSiH4ガスの吸着不足が起こるため、図9(b)に示すように、露出した酸化シリコン膜2上ではタングステンの結晶核5の生成が難しい。従って、タングステンの結晶核5が十分に生成しないことから、その後の工程において、露出した酸化シリコン膜2上ではタングステン膜6を形成することが難しく、図10(c)に示されるように、ビア11の一部にタングステン膜6に充填されてない箇所が存在することとなる。すなわち、比較例の方法においては、ビア11が埋め込み不良となる問題が生じる。

【0040】

そこで、密着層3のカバレッジ不足を解決するため、密着層3をPVD技術にかわりCVD技術で形成する手法が検討されている。CVD技術にて密着層3を形成することにより、高アスペクトのビア11に対しても密着層3をカバレッジ良く形成することができることから、ビア11の全体がタングステン膜6で充填されているようなプラグ31を形成することができる。しかしながら、CVD技術による密着層3の形成時のプロセス温度は、例えば、TiCl4ソースを用いてCVD技術により窒化チタンからなる密着層3を形成する場合には、材料ガスであるTiCl4ガスの熱分解温度が640℃近傍であるため高温となる。従って、近年の半導体素子が多様化する中で、低温領域での形成を必要とする半導体素子等を有する半導体装置の製造に対して、このようなCVD技術により密着層3を形成することを適用することは難しい。また、低温のMOCVD(Metal Organic Chemical Vapor Deposition)技術により密着層3を形成する方法もあるが、この方法は、メタリックな低抵抗な密着層3を得るためにプラズマ処理等を必要とする。通常プラズマ処理を用いて膜質を改善すると、密着層3の成膜堆積がシュリンクし、メタリックな特性を得ることができる。このプラズマ処理は、酸化シリコン膜2の表面のようなフィールド表面及びビア11の底面に形成された密着層3に対しては十分に機能し、その膜質改善を行うことができるものの、ビア11の側壁に形成された密着層3の膜質改善については、有効には機能しない。従って、ビア11の側壁に形成された密着層3に対してはプラズマ処理が有効に働かないため、また、微細化すればするほど、プラズマ処理が十分に機能することができないという問題が顕著になってくるため、MOCVD技術により形成された高抵抗な密着層3が厚膜状態でそのままビア11の側壁に残ることになる。そのため、プラグ31はますます高抵抗化し、必ずしも最適な方法とはいえない。さらに、CVD技術は、装置コスト・運用コストがPVD技術と比較して高いという問題点も有する。

【0041】

次に、本実施形態におけるCVD技術を用いたタングステン膜6の埋め込み過程のメカニズムについて、図11を用いて詳細に説明する。図11は、層間絶縁膜である酸化シリコン膜2上にタングステンの結晶核5が生成される過程を模式的に示した図である。

【0042】

まず、図11(a)に示されるように、成膜チャンバー内に酸化シリコン膜22が形成された半導体基板(不図示)を配置し、例えば200から500℃に加熱する。

【0043】

次に、B2H6ガスを導入し、酸化シリコン膜22に吸着させる。詳細には、図11(b)に示されるように、B2H6ガスは、成膜チャンバーの気相内あるいは酸化シリコン膜2上でBH3に熱分解し、酸化シリコン膜22に吸着する。

【0044】

そして、比較例の方法とは異なり、図11(c)に示されるように、導入したB2H6ガスをパージせずに連続してSiH4ガスを導入する。先に説明したように、SiH4ガスの熱分解温度は600℃近傍であるため、それに達しない温度では熱分解しシリコン原子を生成することは無いが、本実施形態においては、酸化シリコン膜22の上にBH3が存在し、そのBH3が触媒として作用するため、SiH4ガスが熱分解されシリコン原子を生成する。これにより、370℃以下のような低温であっても、図11(d)に示されるように薄いシリコン層24を均一に形成することができる。また、この熱分解反応は非平衡反応であるため、シリコン層24の形成時間を長くすることにより、より高密度なシリコン原子からなるシリコン層24を形成することができる。さらに、堆積したシリコン原子は、ビア11の底面及び側壁上のキンクやステップといったエネルギー的により安定な箇所に移動しシリコン−シリコン結合を形成するため、より高密度なシリコン原子からなるシリコン層24を形成することができる。

【0045】

次に、「タングステンの結晶核25の生成ステップ」を行う。比較例の方法と同様に、SiH4ガスを導入し次いでパージし、WF6ガスを導入し次いでパージする、一連のサイクルを繰り返す。この際、このシリコン層24がWF6ガスと還元反応を生じ、シリコンはタングステンと置換され、タングステンの結晶核25が酸化シリコン膜22上に高密度に生成する。

【0046】

そして、比較例の方法と同様に、「タングステン膜26の堆積ステップ」を行う。この際、タングステンの結晶核25が高密度で存在することから、タングステン膜26と酸化シリコン膜22とが接する接点が増え、酸化シリコン膜22との密着性の高いタングステン膜26を形成することができる。

【0047】

すなわち、比較例の方法とは異なり、本実施形態においては、ビア11が微細化することに起因して、PVD技術により形成された密着層3のカバレッジが不足しても、シリコン層4を形成することにより、ビア11の内側に高密度のタングステンの初期結晶核5を生成することができる。従って、ビア11の内側に未充填の箇所が生じることを避け、ビア11にタングステン膜6を埋め込むことができる。さらに、本実施形態においては、密着層3のカバレッジが悪くてもかまわないことからPVD技術を用いて密着層3を形成することができるため、CVD技術を用いた場合と比べて装置コストやランニングコストの低減を行うことができる。また、本実施形態においては、高いプロセス温度を必要とすることがないため、低温度のプロセスを必要とするような種々の半導体装置の製造に適用可能である。

【0048】

さらに、本実施形態においては、シリコン層4の形成方法として、B2H6ガスを成膜チャンバーへ導入し、その後パージをすることなくSiH4ガスとH2ガスとを導入しているが、このようにB2H6ガスを導入し次いでSiH4ガスを導入することにより、シリコン層4の初期形成時にはボロン濃度の高いシリコン層4が半導体基板1側に形成され、次にシリコン濃度の高いシリコン層がシリコン層4の上層側に形成することができる。従って、本実施形態によれば、タングステン結晶核5の生成を行うために必要なシリコンを表層により高濃度に存在させることができることから、この後の工程においてタングステンの結晶核5の生成をより効率よく行うことができる。

【0049】

次に、本実施形態の効果を調べるため、以下のようなサンプルを作成し、その表面を走査型電子顕微鏡(SEM)で観察し、それによって得たSEM像から各表面におけるタングステンの初期結晶核5の密度を測定した。

【0050】

サンプルAは、上記の本実施形態の製造方法と同様に、半導体基板1上に厚さ100nmの酸化シリコン膜2を形成し、その上にシリコン層4を形成し、さらに「タングステンの結晶核5の生成ステップ」の一連のサイクルを2回行うことにより得たものである。比較例としてのサンプルBは、先に説明した比較例の方法と同様に、半導体基板1に厚さ100nmの酸化シリコン膜2を形成し、次いで、「還元ガスの吸着ステップ」を行い、さらに「タングステンの結晶核生成ステップ」の一連のサイクルを2回行うことにより得たものである。

【0051】

各サンプルの表面をSEMにて観察し、そのSEM像からタングステンの結晶核5の密度を測定した。その結果を示す図12によれば、本実施形態にあたるサンプルAのタングステンの結晶核5の密度は、14890個/μm2であり、サンプルBのタングステンの結晶核5の密度は、8330個/μm2であった。

【0052】

すなわち、本実施形態によれば、シリコン層4を形成することにより、タングステンの結晶核5を酸化シリコン膜2の上により高密度に形成することができることが明らかになった。

【0053】

さらに、本発明者らは詳細な解析を行い、タングステンの結晶核5の密度とビア11におけるタングステン膜6の埋め込み状態との関係を明らかにし、本実施形態の効果を確認した。この結果を示したものが図13となる。

【0054】

詳細には、図13(a)の横軸は、タングステンの結晶核5の密度を示し、縦軸はビア11におけるタングステン膜6の埋め込み程度(充填率)を示す。この埋め込み程度とは、図13(b)に示すように、ビア11の高さ(Y)に対する、ビア11の間口からビア11の底部にかけてのタングステン膜6が埋め込まれている高さ(X)の割合(X/Y)(充填率)のこととする。図13(a)に示されるように、タングステンの結晶核5の密度とタングステン膜6の埋め込み程度とには一定の相関があり、タングステンの結晶核5の密度が上昇することにより、タングステン膜6の埋め込み程度を示す値が高くなり、ビア11がタングステン膜6により充填されることが分かる。また、この図13(a)により、タングステンの結晶核5の密度が約12500個/μm2以上で、ビア11を完全に充填することが可能になることが予測できる。さらに、このようなビア11をタングステン膜6で完全に充填することが可能となると予測される密度の領域は、先に説明した比較例の方法を用いた場合では実現が難しく、一方、本実施形態を用いた場合では実現できると考えられる。

【0055】

すなわち、上記の結果から、タングステンの結晶核5の密度が高くなるほど、ビア11がタングステン膜6により充填されることがわかった。従って、本実施形態によれば、高密度のタングステンの結晶核5が生成できることから、ビア11の内側に未充填の箇所を生じることを避け、ビア11にタングステン膜6を埋め込むことができる。

【0056】

(第2の実施形態)

第1の実施形態においては、シリコン層4の形成方法の際、B2H6ガスを導入し次いでパージすることなくSiH4ガスを導入することにより、タングステン結晶核5の生成を行うために必要なシリコンを表層により高濃度に存在させ、この後の工程においてタングステンの結晶核5の生成を効率的に行っていた。一方、本実施形態においては、B2H6ガスを導入し、パージした後にSiH4ガスを導入し、次いでパージした後にWF6ガスを導入し、さらにパージする一連のサイクルを複数回繰り返す。言い換えると、これらのガスを順次導入してパージすることを繰り返すことによりシリコン層4の形成とタングステンの結晶核5の生成とを行うものである。このようにすることにより、成膜温度を高くしても、カバレッジの良いシリコン層4を形成し、ひいてはビア11の内側により高密度のタングステンの初期結晶核5を生成することができる。

【0057】

以下、本実施形態を説明する。以下、プラグ31の製造過程を例として説明するが、本発明は、以下に説明するような形態のプラグに限定されるものではない。また、本実施形態の製造工程は、第1の実施形態の説明で用いた図1から図4に表わされ、ここでは、第1の実施形態と共通する部分については説明を省略する。

【0058】

第1の実施形態と同様に、図1(a)に示すように半導体基板1上に酸化シリコン膜2を形成し、図1(b)に示すようにこの酸化シリコン膜2にビア11を形成する。次いで、図2(c)に示すように、PVD技術を用いてビア11の内側と酸化シリコン膜2の表面上とに密着層3として窒化チタン膜を形成する。さらに、密着層3が形成された半導体基板1を成膜チャンバーに配置し、所望の温度、例えば410℃で加熱する。

【0059】

次に、例えば1〜100000Paの条件で、10〜2000sccmのB2H6ガスを成膜チャンバー内へ導入し、一度パージを行い、次いで100〜2000sccmのSiH4ガスと100〜2000sccmのH2ガスとを成膜チャンバーに導入し、さらにパージを行う。次に、例えば、1〜100000Paの条件で、100〜1000sccmのWF6ガスを導入し、またパージを行う。このような一連のサイクルを複数回繰り返し、シリコン層4の形成とタングステンの結晶核5の生成とを行う。

【0060】

さらに、第1の実施形態と同様に、「タングステン膜6の堆積ステップ」を行う。例えば、1〜100000Paの条件で、100〜1000sccmのWF6ガスと100〜3000sccmのH2ガスとを成膜チャンバー内に導入し、図3(e)に示すように、タングステン膜6を堆積させる。この後の工程は、図3(f)及び図4(g)に示され、第1の実施形態と同様であるため、ここでは説明を省略する。

【0061】

本実施形態のプラグ31の製造方法のフローチャートを図23に示す。

【0062】

本実施形態によれば、B2H6ガスを導入し、パージした後にSiH4ガスを導入することにより、SiH4ガスは、ビア11の内側に吸着したB2H6ガスのみと主に反応し、シリコン層4を形成することができる。従って、成膜温度を高くしても、カバレッジの良いシリコン層4を形成し、ひいてはビア11の内側により高密度のタングステンの初期結晶核5を生成することができる。

【0063】

なお、成膜温度が低温である場合(例えば350℃以下の場合)において、第2の実施形態のようにB2H6ガスを導入し、パージした後にSiH4ガスを導入すると、ビア11の内側に吸着したB2H6ガスの吸着量が少ないことから、B2H6ガスとSiH4ガスとの反応速度が低下し、シリコン層4の形成時間が長くなってしまう。従って、生産性の観点から、成膜温度が低温の場合には第1の実施形態を行うことが望ましい。一方、成膜温度が高温である場合(例えば350℃より高い場合)において、第1の実施形態のようにB2H6ガスとSiH4ガスとが成膜チャンバー内で混ざってしまうと、B2H6ガスとSiH4ガスとの反応速度は増加し、ビア11の底までB2H6ガスとSiH4ガスとが到達する前にこれらのガスが消費されてしまう。よって、ビア11の内側に形成されるシリコン層4のカバレッジが悪くなってしまうこととなる。従って、このようなことを避けるために、成膜温度が高温の場合には、カバレッジの観点で、第2の実施形態を行うことが望ましい。

【0064】

(第3の実施形態)

第1の実施形態においては、シリコン層4の形成方法の際、B2H6ガスを導入し次いでパージすることなくSiH4ガスを導入することにより、タングステン結晶核5の生成を行うために必要なシリコンを表層により高濃度に存在させ、この後の工程においてタングステンの結晶核5の生成を効率的に行っていた。一方、所望のプラグ31を形成するためには、シリコン層4の膜厚を精度良く制御することも必要であり、その方法の1つとして、第1の実施形態と異なり、B2H6ガスとSiH4ガスとを同時に成膜チャンバー内へ導入してシリコン層4を形成する本実施形態が挙げられる。

【0065】

以下、本実施形態を説明する。以下、プラグ31の製造過程を例として説明するが、本発明は、以下に説明するような形態のプラグに限定されるものではない。また、本実施形態の製造工程は、第1の実施形態の説明で用いた図1から図4に表わされ、ここでは、第1の実施形態と共通する部分については説明を省略する。

【0066】

第1の実施形態と同様に、図1(a)に示すように半導体基板1上に酸化シリコン膜2を形成し、図1(b)に示すようにこの酸化シリコン膜2にビア11を形成する。次いで、図2(c)に示すように、PVD技術を用いてビア11の内側と酸化シリコン膜2の表面上とに密着層3として窒化チタン膜を形成する。さらに、密着層3が形成された半導体基板1を成膜チャンバーに配置し、所望の温度、例えば300℃で加熱する。

【0067】

次に、1〜100000Paの条件で、100〜2000sccmのSiH4ガスと、10〜2000sccmのB2H6ガスとを同時に成膜チャンバー内へ導入し、図2(d)に示されるように、シリコン層4をビア11の内側にCVD技術を用いて形成する。この際、B2H6ガスとSiH4ガスとの流量比を制御することによりシリコン層4の成膜レートを制御して、所望の膜厚を有するシリコン層4を精度良く形成することができる。さらに、シリコン層4のシリコン濃度を制御することができる。この後は、第1の実施形態と同様であるため、ここでは説明を省略する。

【0068】

本実施形態のプラグ31の製造方法のフローチャートを図14に示す。

【0069】

本実施形態によれば、B2H6ガスとSiH4ガスとの流量比を制御することにより、シリコン層4の成膜レートを制御して、所望の膜厚を有するシリコン層4を精度良く形成することができる。さらに、タングステンの結晶核5の効率的な生成のためのシリコン層4中のシリコン濃度を制御することが可能となる。これによって、この後の工程で生成されるタングステンの結晶核5の密度を制御することができる。

【0070】

以下に、B2H6ガスとSiH4ガスとの流量比を変化させた場合のシリコン層4中のボロン濃度について説明する。

【0071】

例えば、SiH4ガスを100〜2000sccm、B2H6 ガスを500〜2000sccmとした条件(条件A)でシリコン層4を形成し、SIMS(Secondary Ion Mass Spectrometry)を用いてシリコン層4中のボロンの濃度を分析したところ、3.3E+22atom/cm3であった。また、SiH4ガスを100〜2000sccm、B2H6ガスを10〜500sccmとした条件(条件B)でシリコン層4を形成し、SIMSを用いてシリコン層4中のボロンの濃度を分析したところ、1.3E+22atom/cm3であった。このようにして得られた結果をまとめたものが図15である。図15の横軸はB2H6/SiH4の流量比を示し、縦軸はシリコン層4中のボロン濃度を示す。ボロン濃度は、成膜時の圧力、温度等により変化するが、これらの条件を同じにした場合、B2H6とSiH4との流量比を制御することにより、シリコン層4中のボロン濃度を変えることが可能であることがわかる。従って、ボロン濃度が変化していることから、それにともない、シリコン層4中のシリコン濃度も変化していると考えられる。

【0072】

また、上記の条件A及び条件Bにてシリコン層4を形成し、その上に第1の実施形態と同様にタングステンの結晶核5を生成した。さらに、その表面をSEMで観察し、それによって得たSEM像から各表面におけるタングステンの初期結晶核5の密度を測定した。その結果、条件Aでは、タングステンの初期結晶核5の密度は11010個/μm2であり、条件Bでは12500個/μm2であった。この結果から、ボロン濃度の値が減少するに従って、言い換えると、シリコン濃度の値が増加するに従って、タングステンの初期結晶核5の密度が上昇することがわかった。

【0073】

すなわち、本実施形態によれば、B2H6ガスとSiH4ガスとの流量比を制御することにより、タングステンの結晶核5の効率的な生成のためのシリコン層4中のシリコン濃度を制御することができ、これによって、タングステンの結晶核5の密度を制御することができる。

【0074】

なお、第1の実施形態及び第3の実施形態においては、ともに、B2H6とSiH4との反応を利用したシリコン原子を生成する工程のプロセス温度が、SiH4ガスが熱分解するために必要な600℃近傍の温度に達していない場合を例として説明しているが、このプロセス温度が600℃を超える場合であっても、第1の実施形態及び第3の実施形態を適用してもよい。このようにプロセス温度が600℃を超える場合には、B2H6とSiH4との反応を利用して生成されるシリコン原子と、SiH4の熱分解から生成されるシリコン原子との両方を利用することができる。

【0075】

(第4の実施形態)

第1の実施形態では、酸化シリコン膜2のビア11の底面及び側壁上に密着層3を形成していたが、本実施形態においては、酸化シリコン膜2のビア11の内側の側壁上部に窒化チタンからなる密着層3を選択的に形成する点が、第1の実施形態と異なる点である。このようにすることで、ビア11の上部と下部とでタングステン膜6の堆積速度を変えることができ、従って、タングステン膜6に充填されたプラグ31を形成することができる。

【0076】

図16から図19を用いて本実施形態にかかる半導体装置の製造方法を説明する。この図16から図19は、プラグ31の製造過程を示し、半導体装置の有するプラグ31の断面に対応するものである。なお、本発明は、以下に説明するような形態のプラグに限定されるものではない。また、第1の実施形態と共通する部分については説明を省略する。

【0077】

第1の実施形態と同様に、図16(a)に示すように半導体基板1上に酸化シリコン膜2を形成し、図16(b)に示すように酸化シリコン膜2にビア11を形成する。

【0078】

そして、図17(c)に示すように、第1の実施形態と同様に、PVD技術を用いて、窒化チタンからなる密着層3をビア11の側壁上部と酸化シリコン膜2の表面との上に選択的に形成し、ビア11の側壁の中部から下部にかけては酸化シリコン膜2が露出したままとする。なお、ビア11の側壁上部に形成された密着層3は、ビア11の側壁上部を覆う連続した膜として形成されることが好ましい。

【0079】

さらに、図17(d)に示すように、第1の実施形態と同様にして、非常に薄いシリコン層4を形成する。この際、ボロンは窒化チタン膜と親和性が高いことから、B2H6ガスが窒化チタン膜に選択的に吸着する。従って、ビア11の側壁の上部に位置する窒化チタンからなる密着層3上に形成されたシリコン層4中のボロンの濃度は、ビア11の側壁の中部から下部の上に形成されたシリコン層4中のボロンの濃度よりも高くなる。それにともない、ビア11の側壁の上部に位置する密着層3上に形成されたシリコン層4中のシリコンの濃度は、ビア11の側壁の中部から下部の上に形成されたシリコン層4中のシリコンの濃度よりも低くなる。すなわち、窒化チタンからなる密着層3を選択的に形成することにより、ビア11の内側に形成するシリコン層4中のボロン及びシリコンの濃度を変化させることができる。本実施形態においては、窒化チタンからなる密着層をあらかじめ所望の位置に形成することにより、シリコン層4に含まれるボロン及びシリコンの濃度を、その位置に応じて容易に変化させることができる。

【0080】

次に、図18(e)及び図18(f)に示すように、タングステン膜6を、第1の実施形態と同様にCVD法を用いてビア11に埋め込む。この際、先に説明したように、ビア11の側壁の上部に位置する窒化チタンからなる密着層3上に形成されたシリコン層4中のシリコンの濃度は、ビア11の側壁の中部から下部の上に形成されたシリコン層4中シリコンの濃度よりも低いことから、シリコンと反応して形成されるタングステンの結晶核5の密度についても、ビア11の側壁の上部に位置する密着層3の上では、ビア11の側壁の中部及び下部の上よりも低くなる。そして、タングステンの結晶核5の密度が異なることから、ビア11の側壁の上部の上に堆積するタングステン膜6の堆積速度は、ビア11の側壁の中部から下部の上に堆積するタングステン膜6の堆積速度よりも遅くなることとなる。このようにすることにより、ビア11の開口部付近に先にタングステン膜6が堆積してビア11の開口部を塞ぎ、ビア11の下部にタングステン膜6を埋め込むことができないという、埋め込み不良のプラグ31が形成されてしまうような状況を避け、ビア11がタングステン膜6に十分に充填されたプラグ31を形成することができる。

【0081】

次いで、図19(g)に示すように、第1の実施形態と同様に、ビア11から突出したタングステン膜6と密着層3とをCMPにより研磨して除去することにより、プラグ31が形成される。

【0082】

なお、本実施形態においては、シリコン層4中のボロンの濃度差により、タングステン膜6の堆積速度が異なることを利用したが、本実施形態は、ボロンに限定するものではなく、ボロンのかわりに、WF6ガスと反応しない物質を用いても良く、このような物質としては、P(リン)、C(炭素)、Ge(ゲルマニウム)等を挙げることができる。例えば、Pを用いる場合にはPH3ガスを導入し、Cを用いる場合にはSiH3CH3ガスを導入し、Geを用いる場合にはGeH4ガスを導入する。

【0083】

また、本実施形態においては、酸化シリコン膜2のビア11の側壁上部の上に形成する密着層3は窒化シリコン膜に限定するものではなく、密着層3をチタン膜、タンタル膜、窒化タンタル膜、窒化タングステン膜等から形成しても、窒化チタン膜で形成した場合と同様の効果を得ることができる。

【0084】

以上のようにして、図20の断面図に示されるプラグ31が形成される。詳細には、本実施形態のプラグ31は、半導体基板1上に形成された酸化シリコン膜2に設けられたビア11と、ビア11の側壁上部の上に形成された窒化チタンからなる密着層3と、ビア11に埋め込まれたタングステン膜6とからなる。さらに、ビア11の側壁上部の上に形成された密着層3とタングステン膜6との間のボロンの濃度は、ビア11の側壁の中部及び下部とタングステン膜6との間のボロンの濃度と比べて高い。なお、タングステン膜6を形成する前に形成したシリコン層4はタングステンと置換させて、最終的には密着層3上に残存しないほうが好ましいが、その一部が密着層3上に残存してしまっても良い。

【0085】

本実施形態によれば、密着層3をビア11の側壁の上部に窒化チタンからなる密着層3を選択的に形成することにより、ビア11の側壁の上部の密着層3上に形成されたシリコン層4中のボロンの濃度は、ビア11の側壁の中部から下部の上に形成されたシリコン層4中のボロンの濃度よりも高くなる。その反対に、密着層3上に形成されたシリコン層4中のシリコンの濃度は、ビア11の側壁の中部から下部の上に形成されたシリコン層4中のシリコンの濃度よりも低くなる。このようにして、シリコン層4中のシリコンの濃度を変化させることにより、ビア11の側壁上部の上に堆積されるタングステン膜6の堆積速度が、ビア11の側壁の中部から下部の上に堆積されるタングステン膜6の堆積速度に比べて遅くすることができる。従って、ビア11の開口部付近に先にタングステン膜6が堆積してビア11の開口部を塞ぎ、ビア11の下部にタングステン膜6を埋め込むことができないという状況を避けることができる。言い換えると、ビア11がタングステン膜6に十分に充填されているような埋め込み性がより改善されたプラグ31を得ることができる。

【0086】

本実施形態において、密着層3である窒化チタン膜23の有無により、その上に形成したシリコン層中のボロン及びシリコンの濃度が異なることを確認するため以下のようなサンプルを作成し、各サンプルのボロン及びシリコンの濃度を電子エネルギー損失分光法(Electron Energy-Loss Spectroscopy;EELS)を用いて分析した。

【0087】

上記の本実施形態に対応するサンプルAは、図21の上段に示されるように、本実施形態の製造方法と同様に、B2H6ガスを成膜チャンバー内に導入し、パージをすることなくSiH4ガスを導入して、窒化チタン膜23の上に厚いシリコン層44を形成した。そのシリコン層44中のボロンの濃度をEELSにて測定したところ、図21に示されるように、シリコン層44の上層側に比べて、シリコン層44の下層にあたる窒化チタン膜23側にボロン濃度が高いことが確認された。また、シリコンの濃度についても、シリコン層44の上層側に比べて、シリコン層44の下層にあたる窒化チタン膜23側のシリコン濃度が低いことが確認された。

【0088】

一方、比較例としてのサンプルBは、酸化シリコン膜22の上に窒化チタン膜23を形成することなく、サンプルAの作成方法と同様に厚いシリコン層44を形成した。そのシリコン層44中のボロンの濃度をEELSにて測定したところ、シリコン層44の上層側のボロン濃度に対するシリコン層44の下層にあたる窒化チタン膜23側のボロン濃度の差は、サンプルAと比べて大きなものではなかった。

【0089】

以上のことから、シリコン層44の形成において、B2H6ガスを成膜チャンバー内に導入した場合、B2H6ガスが窒化チタン膜23に選択的に吸着したため、窒化チタン膜23直上のシリコン層44のボロン濃度が高くなり、さらに、酸化シリコン膜22上ではB2H6ガスの選択的な吸着が起こらないため、酸化シリコン膜上のシリコン層44中のボロン濃度に差が確認されなかったと考えられる。

【0090】

すなわち、窒化チタン膜23の有無により、その上に形成されるシリコン層44中のボロン濃度が変化することがわかった。

【0091】

さらに、本実施形態において、密着層3である窒化チタン膜の有無により、その上方に堆積されるタングステン膜6の堆積速度が異なることを確認するため、以下のようなサンプルを作成し、各サンプルのタングステン膜6の堆積量を蛍光X線分析により測定した。

【0092】

サンプルCは、酸化シリコン膜2上に0.2から30nmの膜厚のシリコン層4を形成したものであり、サンプルDは、酸化シリコン膜2上に窒化チタン膜を形成し、その上に0.2から30nmの膜厚のシリコン層4を形成したものである。そして、それぞれのサンプルに対して、1〜100000Paの条件の下、100〜1000sccmのWF6ガスを流してタングステン膜6を堆積し、それぞれのサンプルにおけるタングステン膜6の堆積量を蛍光X線分析により測定した。その結果を図22に示す。図22に示すように、サンプルCのタングステン膜6の堆積量は、サンプルDのタングステン膜6の堆積量と比べて1.5倍であることが確認された。

【0093】

すなわち、窒化チタン膜の有無により、その上方に堆積されるタングステン膜6の堆積速度が異なることが確認された。

【0094】

なお、ビア11の側壁の中部から下部の上に形成されるシリコン層4中のボロン濃度と、ビア11の側壁上部の上に形成されるシリコン層4中のボロン濃度とを変える方法としては、シリコン層4の形成条件を変えることによっても行うことができる。例えば、第3の実施形態と同様に、シリコン層4の形成時のB2H6ガスとSiH4ガスとの流量を制御することにより、シリコン層4中のボロン濃度を調整することができることから、最初にビア11にボロン濃度の低いシリコン層4をコンフォーマルに形成し、次いでシリコン層4のカバレッジが悪くなる条件、例えば供給律速となる条件にて、ボロン濃度の高いシリコン層4を形成することにより、ビア11の側壁の中部から下部の上に形成されたシリコン層4中のボロン濃度を低く、且つ、ビア11の側壁上部の上に形成されたシリコン層4中のボロン濃度を高く形成することができる。

【0095】

なお、第1から第4の実施形態においては、密着層3としての窒化チタン膜は、PVD技術を用いて形成するものとして説明したが、これに限定されるものではなく、CVD技術、ALD(Atomic Layer Deposition)技術を用いて薄い窒化チタン膜を形成しても同様の効果を得ることができる。なぜなら、高アスペクトのビア11の内側では、これらの技術を用いても、必ずしも、連続、且つ、均一であり、コンフォーマルな窒化チタン膜を形成できるとは限らないからである。このような場合にも、第1から第4の実施形態を用いることにより、これらの実施形態で得られる効果と同様の効果を得ることができる。

【0096】

本発明の実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0097】

1 半導体基板

2、22 酸化シリコン膜

3 密着層

4、24 薄いシリコン層

5、25 タングステン結晶核

6、26 タングステン膜

7 コンタクト層

11 ビア

23 窒化チタン膜

31 プラグ

44 厚いシリコン層

【特許請求の範囲】

【請求項1】

半導体基板上に酸化シリコン膜を形成し、

前記酸化シリコン膜にビアを形成し、

前記ビアの内側に密着層を形成し、

前記密着層上にシリコン層を形成し、

タングステンを含むガスを前記シリコン層と反応させることにより、前記ビアに埋め込まれたタングステン膜を形成する、

ことを特徴とする半導体装置の製造方法。

【請求項2】

前記シリコン層の膜厚は、0.2nm〜30nmであることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記シリコン層の形成は、シリコンを含むガスとボロンを含むガスとを用いて行うことを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記シリコン層の形成は、ボロンを含むガスを前記成膜チャンバー内に導入し、パージを行い、次いで、シリコンを含むガスを成膜チャンバー内に導入して行うことを特徴とする請求項1から3のいずれか1つに記載の半導体装置の製造方法。

【請求項5】

前記密着層を不連続な膜として形成することを特徴とする請求項1から4のいずれか1つに記載の半導体装置の製造方法。

【請求項6】

前記密着層は、前記ビアの内側の側壁上部に選択的に形成する、ことを特徴とする請求項1から4のいずれか1つに記載の半導体装置の製造方法。

【請求項7】

半導体基板上の酸化シリコン膜に設けられたビアと、

前記ビアの内側の密着層と、

前記密着層上に位置し、膜厚が30nm以下のシリコン層と、

前記ビアに埋め込まれたタングステン膜と、

からなるプラグを備える、ことを特徴とする半導体装置。

【請求項8】

前記密着層は不連続な膜であることを特徴とする請求項7に記載の半導体装置。

【請求項9】

半導体基板上の酸化シリコン膜に設けられたビアと、

前記ビア内側の側壁上部に選択的に形成された密着層と、

前記ビアに埋め込まれたタングステン膜と、

からなるプラグを備える、ことを特徴とする半導体装置。

【請求項10】

前記プラグはボロンを含み、

前記ビア内側の側壁上部に選択的に形成された前記密着層と前記タングステン膜との間に含まれるボロンの濃度は、前記ビアの側壁の中部及び下部と前記タングステン膜との間に含まれるボロンの濃度と比べて、高いことを特徴とする請求項9に記載の半導体装置。

【請求項1】

半導体基板上に酸化シリコン膜を形成し、

前記酸化シリコン膜にビアを形成し、

前記ビアの内側に密着層を形成し、

前記密着層上にシリコン層を形成し、

タングステンを含むガスを前記シリコン層と反応させることにより、前記ビアに埋め込まれたタングステン膜を形成する、

ことを特徴とする半導体装置の製造方法。

【請求項2】

前記シリコン層の膜厚は、0.2nm〜30nmであることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記シリコン層の形成は、シリコンを含むガスとボロンを含むガスとを用いて行うことを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記シリコン層の形成は、ボロンを含むガスを前記成膜チャンバー内に導入し、パージを行い、次いで、シリコンを含むガスを成膜チャンバー内に導入して行うことを特徴とする請求項1から3のいずれか1つに記載の半導体装置の製造方法。

【請求項5】

前記密着層を不連続な膜として形成することを特徴とする請求項1から4のいずれか1つに記載の半導体装置の製造方法。

【請求項6】

前記密着層は、前記ビアの内側の側壁上部に選択的に形成する、ことを特徴とする請求項1から4のいずれか1つに記載の半導体装置の製造方法。

【請求項7】

半導体基板上の酸化シリコン膜に設けられたビアと、

前記ビアの内側の密着層と、

前記密着層上に位置し、膜厚が30nm以下のシリコン層と、

前記ビアに埋め込まれたタングステン膜と、

からなるプラグを備える、ことを特徴とする半導体装置。

【請求項8】

前記密着層は不連続な膜であることを特徴とする請求項7に記載の半導体装置。

【請求項9】

半導体基板上の酸化シリコン膜に設けられたビアと、

前記ビア内側の側壁上部に選択的に形成された密着層と、

前記ビアに埋め込まれたタングステン膜と、

からなるプラグを備える、ことを特徴とする半導体装置。

【請求項10】

前記プラグはボロンを含み、

前記ビア内側の側壁上部に選択的に形成された前記密着層と前記タングステン膜との間に含まれるボロンの濃度は、前記ビアの側壁の中部及び下部と前記タングステン膜との間に含まれるボロンの濃度と比べて、高いことを特徴とする請求項9に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図9】

【図10】

【図12】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図22】

【図23】

【図7】

【図8】

【図11】

【図13】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図9】

【図10】

【図12】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図22】

【図23】

【図7】

【図8】

【図11】

【図13】

【図21】

【公開番号】特開2013−80891(P2013−80891A)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願番号】特願2012−60873(P2012−60873)

【出願日】平成24年3月16日(2012.3.16)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願日】平成24年3月16日(2012.3.16)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]