半導体装置及びその製造方法

【課題】記憶素子の実効面積の減少を抑制する半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法は、基板上に第1導電プラグを形成する工程と、基板上に第1導電プラグの上面を覆う可変抵抗膜を形成する工程と、基板上に第1導電プラグの上面を覆う第1絶縁膜を形成する工程と、第1絶縁膜のうち第1導電プラグ上の部分を除去して、第1絶縁膜に孔部を形成する工程と、第1絶縁膜の上面から孔部内にわたって第1導電膜を形成して孔部内を埋め込むことで、孔部内で可変抵抗膜に接触し、かつ、可変抵抗膜を介して第1導電プラグに電気的に接続するように第1導電膜を形成する工程と、を含む。

【解決手段】半導体装置の製造方法は、基板上に第1導電プラグを形成する工程と、基板上に第1導電プラグの上面を覆う可変抵抗膜を形成する工程と、基板上に第1導電プラグの上面を覆う第1絶縁膜を形成する工程と、第1絶縁膜のうち第1導電プラグ上の部分を除去して、第1絶縁膜に孔部を形成する工程と、第1絶縁膜の上面から孔部内にわたって第1導電膜を形成して孔部内を埋め込むことで、孔部内で可変抵抗膜に接触し、かつ、可変抵抗膜を介して第1導電プラグに電気的に接続するように第1導電膜を形成する工程と、を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、抵抗可変素子を有する半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、次世代の不揮発性メモリとして、抵抗可変メモリ(ReRAM;Resistance Random Access Memory)と呼ばれる半導体装置が注目されている。抵抗可変メモリは、一般的には、上部電極と、下部電極と、上部電極と下部電極との間に配された可変抵抗膜とを有する(例えば、特許文献1、非特許文献1及び非特許文献2参照)。

【0003】

例えば、特許文献1に記載の抵抗素子は、第1の電極と、第1の電極上に形成された酸化白金膜と、酸化白金膜上に形成された抵抗変化膜と、抵抗変化膜上に形成された第2の電極と、を有する。特許文献1に記載の抵抗素子は、層間絶縁膜上に、電極等の各膜を積層した後にドライエッチングによってパターニングされている。(特許文献1の段落0027〜0029及び図5C〜5E参照)。

【0004】

また、非特許文献2に記載の抵抗可変メモリは、上部電極及び下部電極であるTiN膜間に形成されたHfO2膜/Ti膜の積層体と、当該積層体及び上部電極の側面を覆う被覆層(Capping Layer)と、を有する。非特許文献2に記載の抵抗可変メモリにおいても、下部電極であるTiN電極上に、HfO2膜、Ti膜及びTiN膜を積層した後、eビームリソグラフィによって積層体のパターニングを行っている(非特許文献2のExperiment欄及びFig.1参照)。

【0005】

抵抗可変メモリにおいては、電圧印加による可変抵抗膜の電気抵抗の大きな変化(CER(Colossal Electron-Reistance)効果)を利用し、可変抵抗膜の低抵抗(SET)状態と高抵抗(RESET)状態の切り替えにより情報を記録する。

【0006】

抵抗可変メモリの動作原理について説明する。上部電極と下部電極間が高抵抗状態において、上部電極及び下部電極間に高電圧(フォーミング電圧)を印加すると、可変抵抗膜に上部電極と下部電極間を低抵抗化する電流経路(導電性フィラメント)が形成される(SET)。一方、上部電極と下部電極間が低抵抗状態において、上部電極及び下部電極間にある電圧を印加すると、当該電流経路は破断され、上部電極と下部電極間は高抵抗状態となる(RESET)。高抵抗状態と低抵抗状態の切り替えは上部電極と下部電極間に印加する電圧の大きさによって制御する。そして、上部電極と下部電極間が高抵抗状態にあるか低抵抗状態にあるかによって記録されている情報が読み込まれる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2010−10582号公報

【非特許文献】

【0008】

【非特許文献1】Akihito Sawa,"Resistive switching in transition metal oxides",materialstoday,11巻6号,2008年6月

【非特許文献2】Pei-Yiら,"Scalability with silicon nitride encapsulation layer for Ti/HfOx pillar PRAM",VLSI2010,146頁

【発明の概要】

【発明が解決しようとする課題】

【0009】

以下の分析は、本発明の観点から与えられる。

【0010】

特許文献1及び非特許文献2に記載の背景技術においては、可変抵抗メモリは、抵抗可変メモリの各要素の膜を積層した後に、ドライエッチング等の異方性エッチングによるパターニングによって形成されている。しかしながら、この場合、抵抗可変メモリを構成する積層体は、エッチング工程中の大気暴露等により酸化されてしまう。特に、上部電極の側壁が酸化を受けやすい。上部電極等の金属は酸化すると高抵抗化することになる。したがって、上部電極等が酸化されると、高抵抗化により素子面積の実効値が低下することになり、これにより所望の抵抗値を実現するためには素子面積を増大させなければならなくなる。すなわち、微細化による高集積化が阻害されてしまうことになる。

【0011】

また、実効的な素子面積が縮小すると、フォーミングを誘発する欠陥因子の数が減少することになるので、フォーミング電圧が大きくなってしまう。この場合、抵抗可変メモリの消費電力が大きくならざるを得ない。

【課題を解決するための手段】

【0012】

本発明の第1視点によれば、基板上に第1導電プラグを形成する工程と、基板上に第1導電プラグの上面を覆う可変抵抗膜を形成する工程と、基板上に第1導電プラグの上面を覆う第1絶縁膜を形成する工程と、第1絶縁膜のうち第1導電プラグ上の部分を除去して、第1絶縁膜に孔部を形成する工程と、第1絶縁膜の上面から孔部内にわたって第1導電膜を形成して孔部内を埋め込むことで、孔部内で可変抵抗膜に接触し、かつ、可変抵抗膜を介して第1導電プラグに電気的に接続するように第1導電膜を形成する工程と、を含む半導体装置の製造方法が提供される。

【0013】

本発明の第2視点によれば、基板上に形成された第1導電プラグと、第1導電プラグの上面を覆い、基板上に形成された可変抵抗膜と、基板上に形成され、第1導電プラグの上部が開口した孔部を有する第1絶縁膜と、第1絶縁膜上に形成され、孔部内から第1絶縁膜上に渡って延在することで、孔部内で可変抵抗膜に接触し、かつ、可変抵抗膜を介して第1導電プラグに電気的に接続するように形成された第1導電膜と、を有する半導体装置が提供される。

【発明の効果】

【0014】

本発明は、以下の効果のうち少なくとも1つを有する。

【0015】

本発明の半導体装置の製造方法によれば、第1絶縁膜の孔部内に、可変抵抗膜と直接接触する第1導電膜を形成することにより、少なくとも、第1導電膜のうち記憶素子(抵抗可変メモリ)を構成する部分にエッチング処理を施す必要がない。すなわち、第1導電膜のうち記憶素子(抵抗可変メモリ)を構成する部分が酸化されることを抑制することができる。これにより、記憶素子の実効面積の縮小を抑制することができる。また、フォーミング電圧の上昇による消費電力の増大も抑制することができる。

【0016】

本発明の半導体装置においては、第1導電膜が、第1絶縁膜上から孔部内に渡って延在し、可変抵抗膜と直接接触している。すなわち、少なくとも、第1導電膜のうち記憶素子(抵抗可変メモリ)を構成する部分は、エッチング処理を施すことなく形成されており、エッチング処理によって酸化されていない。これにより、孔部の大きさに応じた記憶素子の実効面積を維持することができる。また、フォーミング電圧の上昇による消費電力の増大も抑制することができる。

【図面の簡単な説明】

【0017】

【図1】第1実施形態に係る半導体装置の概略断面図。

【図2】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図3】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図4】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図5】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図6】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図7】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図8】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図9】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図10】第2実施形態に係る半導体装置の概略断面図。

【図11】第2実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図12】第2実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図13】第2実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図14】第2実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図15】第3実施形態に係る半導体装置の概略断面図。

【図16】第3実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図17】第3実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図18】第3実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【発明を実施するための形態】

【0018】

以下に上記第1視点及び第2視点の好ましい形態について記載する。

【0019】

上記第1視点の好ましい形態によれば、第1絶縁膜を形成する工程において、第1導電膜に対する酸化力が化学量論組成の二酸化シリコンよりも低い絶縁膜によって第1絶縁膜を形成する。

【0020】

上記第1視点の好ましい形態によれば、第1絶縁膜を形成する工程において、窒化シリコン及び炭素のうち少なくとも一方を含む絶縁膜によって第1絶縁膜を形成する。

【0021】

上記第1視点の好ましい形態によれば、半導体装置の製造方法は、第1絶縁膜上に形成された部分の第1導電膜を加工する工程を、更に含む。

【0022】

上記第1視点の好ましい形態によれば、可変抵抗膜を形成する工程の後、第1導電膜を加工する工程の前には、可変抵抗膜には加工を施さない。

【0023】

上記第1視点の好ましい形態によれば、可変抵抗膜を形成する工程は、第1絶縁膜を形成する工程よりも前に施す。

【0024】

上記第1視点の好ましい形態によれば、半導体装置の製造方法は、第1絶縁膜に孔部を形成する工程よりも後であって、第1導電膜を形成する工程よりも前に、孔部を所定の高さまで埋める第2導電プラグを形成する工程を更に含む。可変抵抗膜を形成する工程は、第2導電プラグを形成する工程よりも後であって、第1導電膜を形成する工程よりも前に施す。可変抵抗膜を形成する工程において、第2導電プラグを介して第1導電プラグの上面を覆うように可変抵抗膜を形成する。第1導電膜を形成する工程において、第2導電プラグおよび可変抵抗膜を介して第1導電プラグに電気的に接続するように第1導電膜を形成する。

【0025】

上記第1視点の好ましい形態によれば、第2導電プラグを形成する工程において、第1絶縁膜の孔部を埋め込むように第2導電プラグを堆積した後、これをエッチバックすることで、孔部を所定の高さまで埋める第2導電プラグを形成する。

【0026】

上記第1視点の好ましい形態によれば、半導体装置の製造方法は、孔部を所定の高さまで埋める第2導電プラグを形成した後であって、可変抵抗膜を形成する工程よりも前に、第2導電プラグの上面の酸化膜を除去する工程を更に含む。

【0027】

上記第1視点の好ましい形態によれば、第2導電プラグを形成する工程において、第1導電プラグと同じ材料によって第2導電プラグを形成する。

【0028】

上記第1視点の好ましい形態によれば、可変抵抗膜を形成する工程は、第1絶縁膜に孔部を形成する工程よりも後であって、第1導電膜を形成する工程よりも前に施す。

【0029】

上記第1視点の好ましい形態によれば、半導体装置の製造方法は、第1導電プラグを形成する工程よりも後であって、可変抵抗膜を形成する工程よりも前に、第1導電プラグの上面の酸化膜を除去する工程を更に含む。

【0030】

上記第2視点の好ましい形態によれば、第1絶縁膜は、第1導電膜に対する酸化力が化学量論組成の二酸化シリコンよりも低い絶縁膜である。

【0031】

上記第2視点の好ましい形態によれば、可変抵抗膜は基板上全面に形成されている。

【0032】

上記第2視点の好ましい形態によれば、可変抵抗膜は、第1導電プラグの上面を覆い、第1絶縁膜の下層に形成されている。

【0033】

上記第2視点の好ましい形態によれば、可変抵抗膜は、第1絶縁膜の上面から孔部の内壁および底部に渡って形成され、孔部の底部において第1導電プラグの上面を覆っている。

【0034】

以下、図面を参照しながら、本発明の実施形態の例について説明する。

【0035】

[第1実施形態]

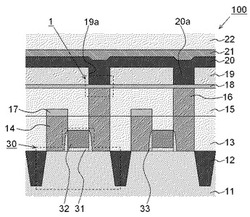

本発明の第1実施形態に係る半導体装置の製造方法について説明する。まず、本発明の半導体装置の製造方法によって製造可能な半導体装置の一例について説明する。図1に、第1実施形態に係る、抵抗可変メモリ(記憶素子)を有する半導体装置の概略断面図を示す。

【0036】

半導体装置100は、半導体基板(特許請求の範囲にいう「基板」)11と、半導体基板11に形成された素子分離領域12と、半導体基板11に形成された不純物拡散領域(不図示)と、半導体基板11上に形成されたゲート絶縁膜31と、ゲート絶縁膜31上に形成されたゲート電極32と、ゲート電極32の側面に形成されたサイドウォール33と、半導体基板11上に形成された第1層間絶縁膜13、第2層間絶縁膜15、第3層間絶縁膜(特許請求の範囲にいう「第1絶縁膜」)19及び第4層間絶縁膜22と、第2層間絶縁膜15と第3層間絶縁膜19との間に形成された可変抵抗膜(特許請求の範囲にいう「可変抵抗膜」)18と、第2層間絶縁膜15に形成され、可変抵抗膜18と電気的に接続されている下部電極プラグ(特許請求の範囲にいう「第1導電プラグ」)16と、第3層間絶縁膜19に形成され、可変抵抗膜18に電気的に接続されている上部電極(特許請求の範囲にいう「第1導電膜」)20と、第1層間絶縁膜13上に形成されたソース配線17と、第1層間絶縁膜13に形成され、不純物拡散領域と下部電極プラグ16又はソース配線17とを電気的に接続するソース/ドレインプラグ14と、第4層間絶縁膜22下に形成され、上部電極20と電気的に接続されているビット線配線21と、を備える。

【0037】

不純物拡散領域を含む半導体基板11と、ゲート絶縁膜31及びゲート電極32はトランジスタ30を構成する。

【0038】

可変抵抗膜18は、半導体基板11の上面に沿って延在するように、第2層間絶縁膜15上全面に形成され、第2層間絶縁膜15の上面から露出した下部電極プラグ16と電気的に接続されている。第3層間絶縁膜19には貫通孔(特許請求の範囲にいう「孔部」)19aが形成されている。上部電極20は、貫通孔19aに充填されたプラグ部20aを有し、貫通孔19aから第3層間絶縁膜19の上に渡って延在している。プラグ部20aは、貫通孔19aの底面に露出している可変抵抗膜18と直接接触している。下部電極プラグ16と、上部電極20のプラグ部20aとは、可変抵抗膜18を介して対向するように配置されていると共に、可変抵抗膜18を介して電気的に接続されている。下部電極プラグ16、可変抵抗膜18及び上部電極20は、可変抵抗メモリの記憶素子1を構成する。

【0039】

可変抵抗膜18及び上部電極20のプラグ部20aは、エッチング処理されておらず、少なくともエッチング処理によって酸化されていない。これにより、記憶素子1の実効面積の縮小を抑制することができる。

【0040】

上部電極20のうち、第3層間絶縁膜19上にある部分はなくてもよい。すなわち、上部電極20は、貫通孔19a内にあるプラグ部20aのみであってもよい。

【0041】

可変抵抗膜18の材料は、電圧の印加や加熱(発熱)により高抵抗状態と低抵抗状態とを切り替えることができるものであればよい。可変抵抗膜18の材料としては、例えば、HfO2、ZrO2,Al2O3、TiO2、Ta3O5、NiO、CoO、CuO等を使用することができる。上部電極20及び下部電極プラグ16の材料としては、例えば、Hf、Zr、Ti、TiN、Ni、Co、W、又はこれらの材料のうちの2以上の積層体等を使用することができる。

【0042】

ソース/ドレインプラグ14と下部電極プラグ16とは同じ材料で形成することができる。

【0043】

第3層間絶縁膜19の材料は、上部電極20の材料に対する酸化力が二酸化ケイ素(二酸化シリコン;SiO2)よりも低い絶縁材料であると好ましい。例えば、第3層間絶縁膜19の材料は、二酸化ケイ素よりも酸素の含有率の低い材料が好ましく、不純物を除く化学量論組成において酸素を含有しない材料であるとより好ましい。第3層間絶縁膜19の好ましい材料としては、例えば、窒化シリコン、アモルファスカーボン等を含む材料を使用することができる。第3層間絶縁膜19に酸化力の低い材料を用いることにより、記憶素子1の酸化、特に上部電極20(特にプラグ部20a)の酸化を抑制することができる。第1、第2及び第4層間絶縁膜13,15,22の材料は、二酸化シリコンであってもよい。

【0044】

次に、図1に示す半導体装置を用いて、第1実施形態に係る本発明の半導体装置の製造方法について説明する。図2〜図9に、第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図を示す。図2〜図9においては、下図((b)図)に概略断面図を示し、上図((a)図)に下図の概略上面図を示す。各上図においては、層間絶縁膜の図示は省略している。

【0045】

まず、半導体基板11を準備し、半導体基板11上に、トランジスタ30、ソース/ドレインプラグ14、ソース配線17及び第1層間絶縁膜13を形成する(図2)。これらは一般的な方法で作製することができる。ソース/ドレインプラグ14の上面は、CMP(Chemical Mechanical Polishing)等の方法による表面の平坦化により、第1層間絶縁膜13から露出させる。

【0046】

次に、第1層間絶縁膜13上に第2層間絶縁膜15を形成する(図3)。

【0047】

次に、エッチング等により第2層間絶縁膜15に、ソース/ドレインプラグ14の上面が露出する貫通孔を形成する。第2層間絶縁膜15の貫通孔に導電体を充填し、当該導電体の上面が第2層間絶縁膜15から露出するように、CMP等で表面を平坦化する。これにより、下部電極プラグ16を形成する(図4)。

【0048】

次に、下部電極プラグ16の上面と電気的に接続するように、第2層間絶縁膜15の上面及び下部電極プラグ16上面上を延在する可変抵抗膜18を形成する(図5)。可変抵抗膜18は、エッチング処理等をすることなく、第2層間絶縁膜15の上面の全面にわたって形成すると好ましい。

【0049】

次に、可変抵抗膜18上に、可変抵抗膜18に沿って第3層間絶縁膜19を形成する(図6)。

【0050】

次に、可変抵抗膜18が露出するように、エッチング等により、第3層間絶縁膜19に貫通孔19aを形成する(図7)。貫通孔19aは、図2〜図9の(a)図に示すような平面投影図において、下部電極プラグ16の少なくとも一部と重複するような位置に形成すると好ましい。

【0051】

次に、貫通孔19aを充填すると共に、第3層間絶縁膜19から露出した可変抵抗膜18と直接接触するように、貫通孔19aから第3層間絶縁膜19の上面にわたる導電体を形成する。次に、第3層間絶縁膜19上において当該導電体をエッチング等により線状に成形する。このとき、貫通孔19a内の当該導電体はエッチング処理されない。これにより、貫通孔19aにプラグ部20aを有する上部電極20を形成する(図8)。可変抵抗膜18を介して下部電極プラグ16と上部電極20のプラグ部20aとが対向すると共に電気的に接続されることにより記憶素子1が構成される。必要であれば、上部電極20は、CMP法等によってプラグ部20aのみが残存するように成形してもよい。

【0052】

次に、上部電極20の一部の上にビット線配線21を形成する。次に、第3層間絶縁膜19、上部電極20及びビット線配線21上に、第4層間絶縁膜22を形成する。これにより、半導体装置100を製造することができる(図9)。

【0053】

本発明によれば、上部電極20のプラグ部20aは、異方性エッチング等を施すことなく形成することができる。これにより、上部電極20のプラグ部20aの酸化を抑制することができる。すなわち、実効的な素子面積の縮小を抑制することができる。

【0054】

また、第1実施形態によれば、第3層間絶縁膜19の貫通孔19aの開口面積全体を記憶素子1として活用することができる。これにより、無駄なスペースが生じることを抑制して、素子面積を有効に活用することができる。

【0055】

[第2実施形態]

本発明の第2実施形態に係る半導体装置の製造方法について説明する。まず、本発明の半導体装置の製造方法によって製造可能な半導体装置の一例について説明する。図10に、第2実施形態に係る、抵抗可変メモリを有する半導体装置の概略断面図を示す。図10において、第1実施形態と同じ要素には同じ符号を付してある。

【0056】

第1実施形態に係る半導体装置においては、可変抵抗膜は第2層間絶縁膜上に平板状に形成されていたが、第2実施形態に係る半導体装置200においては、可変抵抗膜38は、第2層間絶縁膜19上から貫通孔19aの内壁に沿って下部電極プラグ16の上面に延在している。すなわち、可変抵抗膜38は、複数の凹部38aを有するように形成されている。上部電極40は第3層間絶縁膜19とは接しておらず、プラグ部40aは可変抵抗膜38の凹部38aに充填され、可変抵抗膜38のうち少なくとも凹部38aの底部と接触している。

【0057】

次に、図10に示す半導体装置200を用いて、第2実施形態に係る本発明の半導体装置の製造方法について説明する。図11〜図14に、第2実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図を示す。図2〜図4に示す工程までは第1実施形態と同様である。

【0058】

下部電極プラグ16を形成した後(図4)、第2層間絶縁膜15及び下部電極プラグ16上に、第3層間絶縁膜19を形成する(図11)。

【0059】

次に、下部電極プラグ16の上面が露出するように、エッチング等により、第3層間絶縁膜19に下部電極プラグ16の上面の少なくとも一部が露出するように貫通孔19aを形成する(図12)。

【0060】

次に、第3層間絶縁膜19及び下部電極プラグ16上に可変抵抗膜38を形成する(図13)。可変抵抗膜38は、第3層間絶縁膜19上から貫通孔19aの内壁に沿って延在し、下部電極プラグ16の上面と接触している。これにより、可変抵抗膜38は、下部電極プラグ16上に凹部38aを有することになる。

【0061】

次に、可変抵抗膜38上に、貫通孔19aを充填するように、すなわち可変抵抗膜38の凹部38aを充填するように上部電極40を形成する(図14)。これにより、可変抵抗膜38を介して下部電極プラグ16と上部電極40のプラグ部40aとが対向すると共に電気的に接続されることにより記憶素子1が構成される。

【0062】

ビット線配線21及び第4層間絶縁膜22は、第1実施形態と同様に形成することができる(図9)。

【0063】

第2実施形態においても上部電極40のプラグ部40aにはエッチング加工等を施す必要がなく、プラグ部40aの酸化を抑制することができる。これにより、第2実施形態によっても第1実施形態と同様の効果を得ることができる。

【0064】

また、第2実施形態に係る半導体装置200においては、図10に示すように、記憶素子1の端部は、可変抵抗膜38の膜厚tの分だけ貫通孔19aの内壁から離れることになる。エッチング加工により形成した貫通孔19aの内壁と記憶素子とが接している場合、フォーミング時に記憶素子端部で電流経路が形成されるなど、電流経路の分散によって特性のばらつきが生じるおそれがある。第2実施形態によれば、このような電流経路の分散が生じにくくなり、記憶素子1の動作の安定化を図ることができる。

【0065】

第2実施形態における上記以外の形態は第1実施形態と同様である。

【0066】

[第3実施形態]

本発明の第3実施形態に係る半導体装置の製造方法について説明する。まず、本発明の半導体装置の製造方法によって製造可能な半導体装置の一例について説明する。図15に、第3実施形態に係る、抵抗可変メモリを有する半導体装置の概略断面図を示す。図15において、第1実施形態と同じ要素には同じ符号を付してある。

【0067】

第1実施形態及び第2実施形態に係る半導体装置においては、第2層間絶縁膜の高さ(膜厚)と下部電極プラグの高さとは同じであり、可変抵抗膜は第2層間絶縁膜の上面より上に形成されていたが、第3実施形態に係る半導体装置300においては、下部電極プラグ46の高さは第2層間絶縁膜(第3実施形態においては、これが特許請求の範囲にいう「第1絶縁膜」に該当する。)45の高さより低く、可変抵抗膜48の記憶素子1となる領域は第2層間絶縁膜45の上面より下に形成されている。また、第3実施形態に係る半導体装置300は、第1実施形態及び第2実施形態に係る半導体装置における第3層間絶縁膜に相当する絶縁膜を有していない。第3実施形態においては、記憶素子1は第2層間絶縁膜45に形成されるので、第2層間絶縁膜45の材料は、第1実施形態の第3層間絶縁膜の材料と同様である、すなわち窒化シリコン、アモルファスカーボン等の酸化力の低い材料であると好ましい。

【0068】

次に、図15に示す半導体装置300を用いて、第3実施形態に係る本発明の半導体装置の製造方法について説明する。図16〜図18に、第3実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図を示す。図2〜図4に示す工程までは第1実施形態と同様である。

【0069】

図4に示すように、第1層間絶縁膜13の上面から露出したソース/ドレインプラグ14(第3実施形態においては、これが特許請求の範囲にいう「第1導電プラグ」に該当する。)の一部の上面と接触するように、下部電極プラグ46の前駆体となる導体を第2層間絶縁膜45の開口45aに充填した後(当該前駆体は図4にいう下部電極プラグ16に相当する。)、当該前駆体の上部の一部をエッチバックして、当該前駆体の上面を第2層間絶縁膜45の上面より低くする(図16)。これにより、下部電極プラグ46(第3実施形態においては、これが特許請求の範囲にいう「第2導電プラグ」に該当する。)を形成すると共に、第2層間絶縁膜45に開口45a(第3実施形態においては、これが特許請求の範囲にいう「孔部」に該当する。)を形成する。

【0070】

次に、第2層間絶縁膜45の開口45aから露出した下部電極プラグ46の上面に形成された酸化膜を除去する。

【0071】

次に、第2層間絶縁膜45及び下部電極プラグ46上に可変抵抗膜48を形成する(図17)。可変抵抗膜48は、第2層間絶縁膜45上から開口45aの内壁に沿って延在し、下部電極プラグ46の上面に直接接触(電気的に接続)している。これにより、可変抵抗膜48は、下部電極プラグ46上に凹部48aを有することになる。

【0072】

次に、可変抵抗膜48上に、開口45aを充填するように、すなわち可変抵抗膜48の凹部48aを充填するように上部電極50(第3実施形態においては、これが特許請求の範囲にいう「第1導電膜」に該当する。)を形成する(図18)。これにより、可変抵抗膜48を介して下部電極プラグ46と上部電極50のプラグ部50aとが対向すると共に電気的に接続されることにより記憶素子1が構成される。

【0073】

第3実施形態においては、第1実施形態における第3層間絶縁膜に相当する絶縁膜は形成しない。ビット線配線21及び第3層間絶縁膜52は、第1実施形態と同様に形成することができる(図9)。

【0074】

第3実施形態においても上部電極50のプラグ部50aにはエッチング加工等を施す必要がなく、プラグ部50aの酸化を抑制することができる。これにより、第3実施形態によっても第1実施形態と同様の効果を得ることができる。

【0075】

また、第3実施形態に係る半導体装置300においては、層間絶縁膜の形成工程、マスクを形成するフォトリソグラフィ工程、及び貫通孔を形成するエッチング工程を削減することができる。これにより、半導体装置300の製造工程を簡略化することができる。

【0076】

第3実施形態における上記以外の形態は第1実施形態と同様である。

【0077】

本発明の半導体装置及びその製造方法は、上記実施形態に基づいて説明されているが、上記実施形態に限定されることなく、本発明の範囲内において、かつ本発明の基本的技術思想に基づいて、種々の開示要素(各請求項の各要素、各実施例の各要素、各図面の各要素等を含む)に対し種々の変形、変更及び改良を含むことができることはいうまでもない。また、本発明の請求の範囲の枠内において、種々の開示要素(各請求項の各要素、各実施例の各要素、各図面の各要素等を含む)の多様な組み合わせ・置換ないし選択が可能である。

【0078】

本発明のさらなる課題、目的及び展開形態は、請求の範囲を含む本発明の全開示事項からも明らかにされる。

【符号の説明】

【0079】

100,200,300 半導体装置

1 記憶素子

11 半導体基板

12 素子分離領域

13 第1層間絶縁膜

14 ソース/ドレインプラグ

15,45 第2層間絶縁膜

16,46 下部電極プラグ

17 ソース配線

18,38,48 可変抵抗膜

19,52 第3層間絶縁膜

19a 貫通孔

20,40,50 上部電極

20a,40a,50a プラグ部

21 ビット線配線

22 第4層間絶縁膜

30 トランジスタ

31 ゲート絶縁膜

32 ゲート電極

33 サイドウォール

38a,48a 凹部

45a 開口

【技術分野】

【0001】

本発明は、抵抗可変素子を有する半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、次世代の不揮発性メモリとして、抵抗可変メモリ(ReRAM;Resistance Random Access Memory)と呼ばれる半導体装置が注目されている。抵抗可変メモリは、一般的には、上部電極と、下部電極と、上部電極と下部電極との間に配された可変抵抗膜とを有する(例えば、特許文献1、非特許文献1及び非特許文献2参照)。

【0003】

例えば、特許文献1に記載の抵抗素子は、第1の電極と、第1の電極上に形成された酸化白金膜と、酸化白金膜上に形成された抵抗変化膜と、抵抗変化膜上に形成された第2の電極と、を有する。特許文献1に記載の抵抗素子は、層間絶縁膜上に、電極等の各膜を積層した後にドライエッチングによってパターニングされている。(特許文献1の段落0027〜0029及び図5C〜5E参照)。

【0004】

また、非特許文献2に記載の抵抗可変メモリは、上部電極及び下部電極であるTiN膜間に形成されたHfO2膜/Ti膜の積層体と、当該積層体及び上部電極の側面を覆う被覆層(Capping Layer)と、を有する。非特許文献2に記載の抵抗可変メモリにおいても、下部電極であるTiN電極上に、HfO2膜、Ti膜及びTiN膜を積層した後、eビームリソグラフィによって積層体のパターニングを行っている(非特許文献2のExperiment欄及びFig.1参照)。

【0005】

抵抗可変メモリにおいては、電圧印加による可変抵抗膜の電気抵抗の大きな変化(CER(Colossal Electron-Reistance)効果)を利用し、可変抵抗膜の低抵抗(SET)状態と高抵抗(RESET)状態の切り替えにより情報を記録する。

【0006】

抵抗可変メモリの動作原理について説明する。上部電極と下部電極間が高抵抗状態において、上部電極及び下部電極間に高電圧(フォーミング電圧)を印加すると、可変抵抗膜に上部電極と下部電極間を低抵抗化する電流経路(導電性フィラメント)が形成される(SET)。一方、上部電極と下部電極間が低抵抗状態において、上部電極及び下部電極間にある電圧を印加すると、当該電流経路は破断され、上部電極と下部電極間は高抵抗状態となる(RESET)。高抵抗状態と低抵抗状態の切り替えは上部電極と下部電極間に印加する電圧の大きさによって制御する。そして、上部電極と下部電極間が高抵抗状態にあるか低抵抗状態にあるかによって記録されている情報が読み込まれる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2010−10582号公報

【非特許文献】

【0008】

【非特許文献1】Akihito Sawa,"Resistive switching in transition metal oxides",materialstoday,11巻6号,2008年6月

【非特許文献2】Pei-Yiら,"Scalability with silicon nitride encapsulation layer for Ti/HfOx pillar PRAM",VLSI2010,146頁

【発明の概要】

【発明が解決しようとする課題】

【0009】

以下の分析は、本発明の観点から与えられる。

【0010】

特許文献1及び非特許文献2に記載の背景技術においては、可変抵抗メモリは、抵抗可変メモリの各要素の膜を積層した後に、ドライエッチング等の異方性エッチングによるパターニングによって形成されている。しかしながら、この場合、抵抗可変メモリを構成する積層体は、エッチング工程中の大気暴露等により酸化されてしまう。特に、上部電極の側壁が酸化を受けやすい。上部電極等の金属は酸化すると高抵抗化することになる。したがって、上部電極等が酸化されると、高抵抗化により素子面積の実効値が低下することになり、これにより所望の抵抗値を実現するためには素子面積を増大させなければならなくなる。すなわち、微細化による高集積化が阻害されてしまうことになる。

【0011】

また、実効的な素子面積が縮小すると、フォーミングを誘発する欠陥因子の数が減少することになるので、フォーミング電圧が大きくなってしまう。この場合、抵抗可変メモリの消費電力が大きくならざるを得ない。

【課題を解決するための手段】

【0012】

本発明の第1視点によれば、基板上に第1導電プラグを形成する工程と、基板上に第1導電プラグの上面を覆う可変抵抗膜を形成する工程と、基板上に第1導電プラグの上面を覆う第1絶縁膜を形成する工程と、第1絶縁膜のうち第1導電プラグ上の部分を除去して、第1絶縁膜に孔部を形成する工程と、第1絶縁膜の上面から孔部内にわたって第1導電膜を形成して孔部内を埋め込むことで、孔部内で可変抵抗膜に接触し、かつ、可変抵抗膜を介して第1導電プラグに電気的に接続するように第1導電膜を形成する工程と、を含む半導体装置の製造方法が提供される。

【0013】

本発明の第2視点によれば、基板上に形成された第1導電プラグと、第1導電プラグの上面を覆い、基板上に形成された可変抵抗膜と、基板上に形成され、第1導電プラグの上部が開口した孔部を有する第1絶縁膜と、第1絶縁膜上に形成され、孔部内から第1絶縁膜上に渡って延在することで、孔部内で可変抵抗膜に接触し、かつ、可変抵抗膜を介して第1導電プラグに電気的に接続するように形成された第1導電膜と、を有する半導体装置が提供される。

【発明の効果】

【0014】

本発明は、以下の効果のうち少なくとも1つを有する。

【0015】

本発明の半導体装置の製造方法によれば、第1絶縁膜の孔部内に、可変抵抗膜と直接接触する第1導電膜を形成することにより、少なくとも、第1導電膜のうち記憶素子(抵抗可変メモリ)を構成する部分にエッチング処理を施す必要がない。すなわち、第1導電膜のうち記憶素子(抵抗可変メモリ)を構成する部分が酸化されることを抑制することができる。これにより、記憶素子の実効面積の縮小を抑制することができる。また、フォーミング電圧の上昇による消費電力の増大も抑制することができる。

【0016】

本発明の半導体装置においては、第1導電膜が、第1絶縁膜上から孔部内に渡って延在し、可変抵抗膜と直接接触している。すなわち、少なくとも、第1導電膜のうち記憶素子(抵抗可変メモリ)を構成する部分は、エッチング処理を施すことなく形成されており、エッチング処理によって酸化されていない。これにより、孔部の大きさに応じた記憶素子の実効面積を維持することができる。また、フォーミング電圧の上昇による消費電力の増大も抑制することができる。

【図面の簡単な説明】

【0017】

【図1】第1実施形態に係る半導体装置の概略断面図。

【図2】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図3】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図4】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図5】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図6】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図7】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図8】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図9】第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図10】第2実施形態に係る半導体装置の概略断面図。

【図11】第2実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図12】第2実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図13】第2実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図14】第2実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図15】第3実施形態に係る半導体装置の概略断面図。

【図16】第3実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図17】第3実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【図18】第3実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図。

【発明を実施するための形態】

【0018】

以下に上記第1視点及び第2視点の好ましい形態について記載する。

【0019】

上記第1視点の好ましい形態によれば、第1絶縁膜を形成する工程において、第1導電膜に対する酸化力が化学量論組成の二酸化シリコンよりも低い絶縁膜によって第1絶縁膜を形成する。

【0020】

上記第1視点の好ましい形態によれば、第1絶縁膜を形成する工程において、窒化シリコン及び炭素のうち少なくとも一方を含む絶縁膜によって第1絶縁膜を形成する。

【0021】

上記第1視点の好ましい形態によれば、半導体装置の製造方法は、第1絶縁膜上に形成された部分の第1導電膜を加工する工程を、更に含む。

【0022】

上記第1視点の好ましい形態によれば、可変抵抗膜を形成する工程の後、第1導電膜を加工する工程の前には、可変抵抗膜には加工を施さない。

【0023】

上記第1視点の好ましい形態によれば、可変抵抗膜を形成する工程は、第1絶縁膜を形成する工程よりも前に施す。

【0024】

上記第1視点の好ましい形態によれば、半導体装置の製造方法は、第1絶縁膜に孔部を形成する工程よりも後であって、第1導電膜を形成する工程よりも前に、孔部を所定の高さまで埋める第2導電プラグを形成する工程を更に含む。可変抵抗膜を形成する工程は、第2導電プラグを形成する工程よりも後であって、第1導電膜を形成する工程よりも前に施す。可変抵抗膜を形成する工程において、第2導電プラグを介して第1導電プラグの上面を覆うように可変抵抗膜を形成する。第1導電膜を形成する工程において、第2導電プラグおよび可変抵抗膜を介して第1導電プラグに電気的に接続するように第1導電膜を形成する。

【0025】

上記第1視点の好ましい形態によれば、第2導電プラグを形成する工程において、第1絶縁膜の孔部を埋め込むように第2導電プラグを堆積した後、これをエッチバックすることで、孔部を所定の高さまで埋める第2導電プラグを形成する。

【0026】

上記第1視点の好ましい形態によれば、半導体装置の製造方法は、孔部を所定の高さまで埋める第2導電プラグを形成した後であって、可変抵抗膜を形成する工程よりも前に、第2導電プラグの上面の酸化膜を除去する工程を更に含む。

【0027】

上記第1視点の好ましい形態によれば、第2導電プラグを形成する工程において、第1導電プラグと同じ材料によって第2導電プラグを形成する。

【0028】

上記第1視点の好ましい形態によれば、可変抵抗膜を形成する工程は、第1絶縁膜に孔部を形成する工程よりも後であって、第1導電膜を形成する工程よりも前に施す。

【0029】

上記第1視点の好ましい形態によれば、半導体装置の製造方法は、第1導電プラグを形成する工程よりも後であって、可変抵抗膜を形成する工程よりも前に、第1導電プラグの上面の酸化膜を除去する工程を更に含む。

【0030】

上記第2視点の好ましい形態によれば、第1絶縁膜は、第1導電膜に対する酸化力が化学量論組成の二酸化シリコンよりも低い絶縁膜である。

【0031】

上記第2視点の好ましい形態によれば、可変抵抗膜は基板上全面に形成されている。

【0032】

上記第2視点の好ましい形態によれば、可変抵抗膜は、第1導電プラグの上面を覆い、第1絶縁膜の下層に形成されている。

【0033】

上記第2視点の好ましい形態によれば、可変抵抗膜は、第1絶縁膜の上面から孔部の内壁および底部に渡って形成され、孔部の底部において第1導電プラグの上面を覆っている。

【0034】

以下、図面を参照しながら、本発明の実施形態の例について説明する。

【0035】

[第1実施形態]

本発明の第1実施形態に係る半導体装置の製造方法について説明する。まず、本発明の半導体装置の製造方法によって製造可能な半導体装置の一例について説明する。図1に、第1実施形態に係る、抵抗可変メモリ(記憶素子)を有する半導体装置の概略断面図を示す。

【0036】

半導体装置100は、半導体基板(特許請求の範囲にいう「基板」)11と、半導体基板11に形成された素子分離領域12と、半導体基板11に形成された不純物拡散領域(不図示)と、半導体基板11上に形成されたゲート絶縁膜31と、ゲート絶縁膜31上に形成されたゲート電極32と、ゲート電極32の側面に形成されたサイドウォール33と、半導体基板11上に形成された第1層間絶縁膜13、第2層間絶縁膜15、第3層間絶縁膜(特許請求の範囲にいう「第1絶縁膜」)19及び第4層間絶縁膜22と、第2層間絶縁膜15と第3層間絶縁膜19との間に形成された可変抵抗膜(特許請求の範囲にいう「可変抵抗膜」)18と、第2層間絶縁膜15に形成され、可変抵抗膜18と電気的に接続されている下部電極プラグ(特許請求の範囲にいう「第1導電プラグ」)16と、第3層間絶縁膜19に形成され、可変抵抗膜18に電気的に接続されている上部電極(特許請求の範囲にいう「第1導電膜」)20と、第1層間絶縁膜13上に形成されたソース配線17と、第1層間絶縁膜13に形成され、不純物拡散領域と下部電極プラグ16又はソース配線17とを電気的に接続するソース/ドレインプラグ14と、第4層間絶縁膜22下に形成され、上部電極20と電気的に接続されているビット線配線21と、を備える。

【0037】

不純物拡散領域を含む半導体基板11と、ゲート絶縁膜31及びゲート電極32はトランジスタ30を構成する。

【0038】

可変抵抗膜18は、半導体基板11の上面に沿って延在するように、第2層間絶縁膜15上全面に形成され、第2層間絶縁膜15の上面から露出した下部電極プラグ16と電気的に接続されている。第3層間絶縁膜19には貫通孔(特許請求の範囲にいう「孔部」)19aが形成されている。上部電極20は、貫通孔19aに充填されたプラグ部20aを有し、貫通孔19aから第3層間絶縁膜19の上に渡って延在している。プラグ部20aは、貫通孔19aの底面に露出している可変抵抗膜18と直接接触している。下部電極プラグ16と、上部電極20のプラグ部20aとは、可変抵抗膜18を介して対向するように配置されていると共に、可変抵抗膜18を介して電気的に接続されている。下部電極プラグ16、可変抵抗膜18及び上部電極20は、可変抵抗メモリの記憶素子1を構成する。

【0039】

可変抵抗膜18及び上部電極20のプラグ部20aは、エッチング処理されておらず、少なくともエッチング処理によって酸化されていない。これにより、記憶素子1の実効面積の縮小を抑制することができる。

【0040】

上部電極20のうち、第3層間絶縁膜19上にある部分はなくてもよい。すなわち、上部電極20は、貫通孔19a内にあるプラグ部20aのみであってもよい。

【0041】

可変抵抗膜18の材料は、電圧の印加や加熱(発熱)により高抵抗状態と低抵抗状態とを切り替えることができるものであればよい。可変抵抗膜18の材料としては、例えば、HfO2、ZrO2,Al2O3、TiO2、Ta3O5、NiO、CoO、CuO等を使用することができる。上部電極20及び下部電極プラグ16の材料としては、例えば、Hf、Zr、Ti、TiN、Ni、Co、W、又はこれらの材料のうちの2以上の積層体等を使用することができる。

【0042】

ソース/ドレインプラグ14と下部電極プラグ16とは同じ材料で形成することができる。

【0043】

第3層間絶縁膜19の材料は、上部電極20の材料に対する酸化力が二酸化ケイ素(二酸化シリコン;SiO2)よりも低い絶縁材料であると好ましい。例えば、第3層間絶縁膜19の材料は、二酸化ケイ素よりも酸素の含有率の低い材料が好ましく、不純物を除く化学量論組成において酸素を含有しない材料であるとより好ましい。第3層間絶縁膜19の好ましい材料としては、例えば、窒化シリコン、アモルファスカーボン等を含む材料を使用することができる。第3層間絶縁膜19に酸化力の低い材料を用いることにより、記憶素子1の酸化、特に上部電極20(特にプラグ部20a)の酸化を抑制することができる。第1、第2及び第4層間絶縁膜13,15,22の材料は、二酸化シリコンであってもよい。

【0044】

次に、図1に示す半導体装置を用いて、第1実施形態に係る本発明の半導体装置の製造方法について説明する。図2〜図9に、第1実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図を示す。図2〜図9においては、下図((b)図)に概略断面図を示し、上図((a)図)に下図の概略上面図を示す。各上図においては、層間絶縁膜の図示は省略している。

【0045】

まず、半導体基板11を準備し、半導体基板11上に、トランジスタ30、ソース/ドレインプラグ14、ソース配線17及び第1層間絶縁膜13を形成する(図2)。これらは一般的な方法で作製することができる。ソース/ドレインプラグ14の上面は、CMP(Chemical Mechanical Polishing)等の方法による表面の平坦化により、第1層間絶縁膜13から露出させる。

【0046】

次に、第1層間絶縁膜13上に第2層間絶縁膜15を形成する(図3)。

【0047】

次に、エッチング等により第2層間絶縁膜15に、ソース/ドレインプラグ14の上面が露出する貫通孔を形成する。第2層間絶縁膜15の貫通孔に導電体を充填し、当該導電体の上面が第2層間絶縁膜15から露出するように、CMP等で表面を平坦化する。これにより、下部電極プラグ16を形成する(図4)。

【0048】

次に、下部電極プラグ16の上面と電気的に接続するように、第2層間絶縁膜15の上面及び下部電極プラグ16上面上を延在する可変抵抗膜18を形成する(図5)。可変抵抗膜18は、エッチング処理等をすることなく、第2層間絶縁膜15の上面の全面にわたって形成すると好ましい。

【0049】

次に、可変抵抗膜18上に、可変抵抗膜18に沿って第3層間絶縁膜19を形成する(図6)。

【0050】

次に、可変抵抗膜18が露出するように、エッチング等により、第3層間絶縁膜19に貫通孔19aを形成する(図7)。貫通孔19aは、図2〜図9の(a)図に示すような平面投影図において、下部電極プラグ16の少なくとも一部と重複するような位置に形成すると好ましい。

【0051】

次に、貫通孔19aを充填すると共に、第3層間絶縁膜19から露出した可変抵抗膜18と直接接触するように、貫通孔19aから第3層間絶縁膜19の上面にわたる導電体を形成する。次に、第3層間絶縁膜19上において当該導電体をエッチング等により線状に成形する。このとき、貫通孔19a内の当該導電体はエッチング処理されない。これにより、貫通孔19aにプラグ部20aを有する上部電極20を形成する(図8)。可変抵抗膜18を介して下部電極プラグ16と上部電極20のプラグ部20aとが対向すると共に電気的に接続されることにより記憶素子1が構成される。必要であれば、上部電極20は、CMP法等によってプラグ部20aのみが残存するように成形してもよい。

【0052】

次に、上部電極20の一部の上にビット線配線21を形成する。次に、第3層間絶縁膜19、上部電極20及びビット線配線21上に、第4層間絶縁膜22を形成する。これにより、半導体装置100を製造することができる(図9)。

【0053】

本発明によれば、上部電極20のプラグ部20aは、異方性エッチング等を施すことなく形成することができる。これにより、上部電極20のプラグ部20aの酸化を抑制することができる。すなわち、実効的な素子面積の縮小を抑制することができる。

【0054】

また、第1実施形態によれば、第3層間絶縁膜19の貫通孔19aの開口面積全体を記憶素子1として活用することができる。これにより、無駄なスペースが生じることを抑制して、素子面積を有効に活用することができる。

【0055】

[第2実施形態]

本発明の第2実施形態に係る半導体装置の製造方法について説明する。まず、本発明の半導体装置の製造方法によって製造可能な半導体装置の一例について説明する。図10に、第2実施形態に係る、抵抗可変メモリを有する半導体装置の概略断面図を示す。図10において、第1実施形態と同じ要素には同じ符号を付してある。

【0056】

第1実施形態に係る半導体装置においては、可変抵抗膜は第2層間絶縁膜上に平板状に形成されていたが、第2実施形態に係る半導体装置200においては、可変抵抗膜38は、第2層間絶縁膜19上から貫通孔19aの内壁に沿って下部電極プラグ16の上面に延在している。すなわち、可変抵抗膜38は、複数の凹部38aを有するように形成されている。上部電極40は第3層間絶縁膜19とは接しておらず、プラグ部40aは可変抵抗膜38の凹部38aに充填され、可変抵抗膜38のうち少なくとも凹部38aの底部と接触している。

【0057】

次に、図10に示す半導体装置200を用いて、第2実施形態に係る本発明の半導体装置の製造方法について説明する。図11〜図14に、第2実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図を示す。図2〜図4に示す工程までは第1実施形態と同様である。

【0058】

下部電極プラグ16を形成した後(図4)、第2層間絶縁膜15及び下部電極プラグ16上に、第3層間絶縁膜19を形成する(図11)。

【0059】

次に、下部電極プラグ16の上面が露出するように、エッチング等により、第3層間絶縁膜19に下部電極プラグ16の上面の少なくとも一部が露出するように貫通孔19aを形成する(図12)。

【0060】

次に、第3層間絶縁膜19及び下部電極プラグ16上に可変抵抗膜38を形成する(図13)。可変抵抗膜38は、第3層間絶縁膜19上から貫通孔19aの内壁に沿って延在し、下部電極プラグ16の上面と接触している。これにより、可変抵抗膜38は、下部電極プラグ16上に凹部38aを有することになる。

【0061】

次に、可変抵抗膜38上に、貫通孔19aを充填するように、すなわち可変抵抗膜38の凹部38aを充填するように上部電極40を形成する(図14)。これにより、可変抵抗膜38を介して下部電極プラグ16と上部電極40のプラグ部40aとが対向すると共に電気的に接続されることにより記憶素子1が構成される。

【0062】

ビット線配線21及び第4層間絶縁膜22は、第1実施形態と同様に形成することができる(図9)。

【0063】

第2実施形態においても上部電極40のプラグ部40aにはエッチング加工等を施す必要がなく、プラグ部40aの酸化を抑制することができる。これにより、第2実施形態によっても第1実施形態と同様の効果を得ることができる。

【0064】

また、第2実施形態に係る半導体装置200においては、図10に示すように、記憶素子1の端部は、可変抵抗膜38の膜厚tの分だけ貫通孔19aの内壁から離れることになる。エッチング加工により形成した貫通孔19aの内壁と記憶素子とが接している場合、フォーミング時に記憶素子端部で電流経路が形成されるなど、電流経路の分散によって特性のばらつきが生じるおそれがある。第2実施形態によれば、このような電流経路の分散が生じにくくなり、記憶素子1の動作の安定化を図ることができる。

【0065】

第2実施形態における上記以外の形態は第1実施形態と同様である。

【0066】

[第3実施形態]

本発明の第3実施形態に係る半導体装置の製造方法について説明する。まず、本発明の半導体装置の製造方法によって製造可能な半導体装置の一例について説明する。図15に、第3実施形態に係る、抵抗可変メモリを有する半導体装置の概略断面図を示す。図15において、第1実施形態と同じ要素には同じ符号を付してある。

【0067】

第1実施形態及び第2実施形態に係る半導体装置においては、第2層間絶縁膜の高さ(膜厚)と下部電極プラグの高さとは同じであり、可変抵抗膜は第2層間絶縁膜の上面より上に形成されていたが、第3実施形態に係る半導体装置300においては、下部電極プラグ46の高さは第2層間絶縁膜(第3実施形態においては、これが特許請求の範囲にいう「第1絶縁膜」に該当する。)45の高さより低く、可変抵抗膜48の記憶素子1となる領域は第2層間絶縁膜45の上面より下に形成されている。また、第3実施形態に係る半導体装置300は、第1実施形態及び第2実施形態に係る半導体装置における第3層間絶縁膜に相当する絶縁膜を有していない。第3実施形態においては、記憶素子1は第2層間絶縁膜45に形成されるので、第2層間絶縁膜45の材料は、第1実施形態の第3層間絶縁膜の材料と同様である、すなわち窒化シリコン、アモルファスカーボン等の酸化力の低い材料であると好ましい。

【0068】

次に、図15に示す半導体装置300を用いて、第3実施形態に係る本発明の半導体装置の製造方法について説明する。図16〜図18に、第3実施形態に係る本発明の半導体装置の製造方法を説明するための概略工程図を示す。図2〜図4に示す工程までは第1実施形態と同様である。

【0069】

図4に示すように、第1層間絶縁膜13の上面から露出したソース/ドレインプラグ14(第3実施形態においては、これが特許請求の範囲にいう「第1導電プラグ」に該当する。)の一部の上面と接触するように、下部電極プラグ46の前駆体となる導体を第2層間絶縁膜45の開口45aに充填した後(当該前駆体は図4にいう下部電極プラグ16に相当する。)、当該前駆体の上部の一部をエッチバックして、当該前駆体の上面を第2層間絶縁膜45の上面より低くする(図16)。これにより、下部電極プラグ46(第3実施形態においては、これが特許請求の範囲にいう「第2導電プラグ」に該当する。)を形成すると共に、第2層間絶縁膜45に開口45a(第3実施形態においては、これが特許請求の範囲にいう「孔部」に該当する。)を形成する。

【0070】

次に、第2層間絶縁膜45の開口45aから露出した下部電極プラグ46の上面に形成された酸化膜を除去する。

【0071】

次に、第2層間絶縁膜45及び下部電極プラグ46上に可変抵抗膜48を形成する(図17)。可変抵抗膜48は、第2層間絶縁膜45上から開口45aの内壁に沿って延在し、下部電極プラグ46の上面に直接接触(電気的に接続)している。これにより、可変抵抗膜48は、下部電極プラグ46上に凹部48aを有することになる。

【0072】

次に、可変抵抗膜48上に、開口45aを充填するように、すなわち可変抵抗膜48の凹部48aを充填するように上部電極50(第3実施形態においては、これが特許請求の範囲にいう「第1導電膜」に該当する。)を形成する(図18)。これにより、可変抵抗膜48を介して下部電極プラグ46と上部電極50のプラグ部50aとが対向すると共に電気的に接続されることにより記憶素子1が構成される。

【0073】

第3実施形態においては、第1実施形態における第3層間絶縁膜に相当する絶縁膜は形成しない。ビット線配線21及び第3層間絶縁膜52は、第1実施形態と同様に形成することができる(図9)。

【0074】

第3実施形態においても上部電極50のプラグ部50aにはエッチング加工等を施す必要がなく、プラグ部50aの酸化を抑制することができる。これにより、第3実施形態によっても第1実施形態と同様の効果を得ることができる。

【0075】

また、第3実施形態に係る半導体装置300においては、層間絶縁膜の形成工程、マスクを形成するフォトリソグラフィ工程、及び貫通孔を形成するエッチング工程を削減することができる。これにより、半導体装置300の製造工程を簡略化することができる。

【0076】

第3実施形態における上記以外の形態は第1実施形態と同様である。

【0077】

本発明の半導体装置及びその製造方法は、上記実施形態に基づいて説明されているが、上記実施形態に限定されることなく、本発明の範囲内において、かつ本発明の基本的技術思想に基づいて、種々の開示要素(各請求項の各要素、各実施例の各要素、各図面の各要素等を含む)に対し種々の変形、変更及び改良を含むことができることはいうまでもない。また、本発明の請求の範囲の枠内において、種々の開示要素(各請求項の各要素、各実施例の各要素、各図面の各要素等を含む)の多様な組み合わせ・置換ないし選択が可能である。

【0078】

本発明のさらなる課題、目的及び展開形態は、請求の範囲を含む本発明の全開示事項からも明らかにされる。

【符号の説明】

【0079】

100,200,300 半導体装置

1 記憶素子

11 半導体基板

12 素子分離領域

13 第1層間絶縁膜

14 ソース/ドレインプラグ

15,45 第2層間絶縁膜

16,46 下部電極プラグ

17 ソース配線

18,38,48 可変抵抗膜

19,52 第3層間絶縁膜

19a 貫通孔

20,40,50 上部電極

20a,40a,50a プラグ部

21 ビット線配線

22 第4層間絶縁膜

30 トランジスタ

31 ゲート絶縁膜

32 ゲート電極

33 サイドウォール

38a,48a 凹部

45a 開口

【特許請求の範囲】

【請求項1】

基板上に第1導電プラグを形成する工程と、

前記基板上に前記第1導電プラグの上面を覆う可変抵抗膜を形成する工程と、

前記基板上に前記第1導電プラグの上面を覆う第1絶縁膜を形成する工程と、

前記第1絶縁膜のうち前記第1導電プラグ上の部分を除去して、前記第1絶縁膜に孔部を形成する工程と、

前記第1絶縁膜の上面から前記孔部内にわたって第1導電膜を形成して前記孔部内を埋め込むことで、前記孔部内で前記可変抵抗膜に接触し、かつ、前記可変抵抗膜を介して前記第1導電プラグに電気的に接続するように前記第1導電膜を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記第1絶縁膜を形成する工程において、前記第1導電膜に対する酸化力が化学量論組成の二酸化シリコンよりも低い絶縁膜によって前記第1絶縁膜を形成することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1絶縁膜を形成する工程において、窒化シリコン及び炭素のうち少なくとも一方を含む絶縁膜によって前記第1絶縁膜を形成することを特徴とする請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第1絶縁膜上に形成された部分の前記第1導電膜を加工する工程を、更に含むことを特徴とする請求項1〜3のいずれか一項に記載の半導体装置の製造方法。

【請求項5】

前記可変抵抗膜を形成する工程の後、前記第1導電膜を加工する工程の前には、前記可変抵抗膜には加工を施さないことを特徴とする請求項1〜4のいずれか一項に記載の半導体装置の製造方法。

【請求項6】

前記可変抵抗膜を形成する工程は、前記第1絶縁膜を形成する工程よりも前に施すことを特徴とする請求項1〜5のいずれか一項に記載の半導体装置の製造方法。

【請求項7】

前記第1絶縁膜に前記孔部を形成する工程よりも後であって、前記第1導電膜を形成する工程よりも前に、前記孔部を所定の高さまで埋める第2導電プラグを形成する工程を更に含み、

前記可変抵抗膜を形成する工程は、前記第2導電プラグを形成する工程よりも後であって、前記第1導電膜を形成する工程よりも前に施し、

前記可変抵抗膜を形成する工程において、前記第2導電プラグを介して前記第1導電プラグの上面を覆うように前記可変抵抗膜を形成し、

前記第1導電膜を形成する工程において、前記第2導電プラグおよび前記可変抵抗膜を介して前記第1導電プラグに電気的に接続するように前記第1導電膜を形成することを特徴とする請求項1〜5のいずれか一項に記載の半導体装置の製造方法。

【請求項8】

前記第2導電プラグを形成する工程において、前記第1絶縁膜の前記孔部を埋め込むように前記第2導電プラグを堆積した後、これをエッチバックすることで、前記孔部を所定の高さまで埋める前記第2導電プラグを形成することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記孔部を所定の高さまで埋める前記第2導電プラグを形成した後であって、前記可変抵抗膜を形成する工程よりも前に、前記第2導電プラグの上面の酸化膜を除去する工程を更に含むことを特徴とする請求項7又は8に記載の半導体装置の製造方法。

【請求項10】

前記第2導電プラグを形成する工程において、前記第1導電プラグと同じ材料によって前記第2導電プラグを形成することを特徴とする請求項7〜9のいずれか一項に記載の半導体装置の製造方法。

【請求項11】

前記可変抵抗膜を形成する工程は、前記第1絶縁膜に前記孔部を形成する工程よりも後であって、前記第1導電膜を形成する工程よりも前に施すことを特徴とする請求項1〜5のいずれか一項に記載の半導体装置の製造方法。

【請求項12】

前記第1導電プラグを形成する工程よりも後であって、前記可変抵抗膜を形成する工程よりも前に、前記第1導電プラグの上面の酸化膜を除去する工程を更に含むことを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項13】

基板上に形成された第1導電プラグと、

前記第1導電プラグの上面を覆い、前記基板上に形成された可変抵抗膜と、

前記基板上に形成され、前記第1導電プラグの上部が開口した孔部を有する第1絶縁膜と、

前記第1絶縁膜上に形成され、前記孔部内から前記第1絶縁膜上に渡って延在することで、前記孔部内で前記可変抵抗膜に接触し、かつ、前記可変抵抗膜を介して前記第1導電プラグに電気的に接続するように形成された第1導電膜と、

を有することを特徴とする半導体装置。

【請求項14】

前記第1絶縁膜は、前記第1導電膜に対する酸化力が化学量論組成の二酸化シリコンよりも低い絶縁膜であることを特徴とする請求項13に記載の半導体装置。

【請求項15】

前記可変抵抗膜は前記基板上全面に形成されていることを特徴とする請求項13又は14に記載の半導体装置。

【請求項16】

前記可変抵抗膜は、前記第1導電プラグの上面を覆い、前記第1絶縁膜の下層に形成されていることを特徴とする請求項13〜15のいずれか一項に記載の半導体装置。

【請求項17】

前記可変抵抗膜は、前記第1絶縁膜の上面から前記孔部の内壁および底部に渡って形成され、前記孔部の底部において前記第1導電プラグの上面を覆っていることを特徴とする請求項13〜16のいずれか一項に記載の半導体装置。

【請求項1】

基板上に第1導電プラグを形成する工程と、

前記基板上に前記第1導電プラグの上面を覆う可変抵抗膜を形成する工程と、

前記基板上に前記第1導電プラグの上面を覆う第1絶縁膜を形成する工程と、

前記第1絶縁膜のうち前記第1導電プラグ上の部分を除去して、前記第1絶縁膜に孔部を形成する工程と、

前記第1絶縁膜の上面から前記孔部内にわたって第1導電膜を形成して前記孔部内を埋め込むことで、前記孔部内で前記可変抵抗膜に接触し、かつ、前記可変抵抗膜を介して前記第1導電プラグに電気的に接続するように前記第1導電膜を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記第1絶縁膜を形成する工程において、前記第1導電膜に対する酸化力が化学量論組成の二酸化シリコンよりも低い絶縁膜によって前記第1絶縁膜を形成することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1絶縁膜を形成する工程において、窒化シリコン及び炭素のうち少なくとも一方を含む絶縁膜によって前記第1絶縁膜を形成することを特徴とする請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第1絶縁膜上に形成された部分の前記第1導電膜を加工する工程を、更に含むことを特徴とする請求項1〜3のいずれか一項に記載の半導体装置の製造方法。

【請求項5】

前記可変抵抗膜を形成する工程の後、前記第1導電膜を加工する工程の前には、前記可変抵抗膜には加工を施さないことを特徴とする請求項1〜4のいずれか一項に記載の半導体装置の製造方法。

【請求項6】

前記可変抵抗膜を形成する工程は、前記第1絶縁膜を形成する工程よりも前に施すことを特徴とする請求項1〜5のいずれか一項に記載の半導体装置の製造方法。

【請求項7】

前記第1絶縁膜に前記孔部を形成する工程よりも後であって、前記第1導電膜を形成する工程よりも前に、前記孔部を所定の高さまで埋める第2導電プラグを形成する工程を更に含み、

前記可変抵抗膜を形成する工程は、前記第2導電プラグを形成する工程よりも後であって、前記第1導電膜を形成する工程よりも前に施し、

前記可変抵抗膜を形成する工程において、前記第2導電プラグを介して前記第1導電プラグの上面を覆うように前記可変抵抗膜を形成し、

前記第1導電膜を形成する工程において、前記第2導電プラグおよび前記可変抵抗膜を介して前記第1導電プラグに電気的に接続するように前記第1導電膜を形成することを特徴とする請求項1〜5のいずれか一項に記載の半導体装置の製造方法。

【請求項8】

前記第2導電プラグを形成する工程において、前記第1絶縁膜の前記孔部を埋め込むように前記第2導電プラグを堆積した後、これをエッチバックすることで、前記孔部を所定の高さまで埋める前記第2導電プラグを形成することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記孔部を所定の高さまで埋める前記第2導電プラグを形成した後であって、前記可変抵抗膜を形成する工程よりも前に、前記第2導電プラグの上面の酸化膜を除去する工程を更に含むことを特徴とする請求項7又は8に記載の半導体装置の製造方法。

【請求項10】

前記第2導電プラグを形成する工程において、前記第1導電プラグと同じ材料によって前記第2導電プラグを形成することを特徴とする請求項7〜9のいずれか一項に記載の半導体装置の製造方法。

【請求項11】

前記可変抵抗膜を形成する工程は、前記第1絶縁膜に前記孔部を形成する工程よりも後であって、前記第1導電膜を形成する工程よりも前に施すことを特徴とする請求項1〜5のいずれか一項に記載の半導体装置の製造方法。

【請求項12】

前記第1導電プラグを形成する工程よりも後であって、前記可変抵抗膜を形成する工程よりも前に、前記第1導電プラグの上面の酸化膜を除去する工程を更に含むことを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項13】

基板上に形成された第1導電プラグと、

前記第1導電プラグの上面を覆い、前記基板上に形成された可変抵抗膜と、

前記基板上に形成され、前記第1導電プラグの上部が開口した孔部を有する第1絶縁膜と、

前記第1絶縁膜上に形成され、前記孔部内から前記第1絶縁膜上に渡って延在することで、前記孔部内で前記可変抵抗膜に接触し、かつ、前記可変抵抗膜を介して前記第1導電プラグに電気的に接続するように形成された第1導電膜と、

を有することを特徴とする半導体装置。

【請求項14】

前記第1絶縁膜は、前記第1導電膜に対する酸化力が化学量論組成の二酸化シリコンよりも低い絶縁膜であることを特徴とする請求項13に記載の半導体装置。

【請求項15】

前記可変抵抗膜は前記基板上全面に形成されていることを特徴とする請求項13又は14に記載の半導体装置。

【請求項16】

前記可変抵抗膜は、前記第1導電プラグの上面を覆い、前記第1絶縁膜の下層に形成されていることを特徴とする請求項13〜15のいずれか一項に記載の半導体装置。

【請求項17】

前記可変抵抗膜は、前記第1絶縁膜の上面から前記孔部の内壁および底部に渡って形成され、前記孔部の底部において前記第1導電プラグの上面を覆っていることを特徴とする請求項13〜16のいずれか一項に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2013−84850(P2013−84850A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2011−225006(P2011−225006)

【出願日】平成23年10月12日(2011.10.12)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成22年度 独立行政法人新エネルギー・産業技術総合開発機構「高速不揮発メモリ機能技術開発/高速不揮発メモリの開発」委託研究、産業技術強化法第19条の適用を受ける特許出願

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【出願人】(301021533)独立行政法人産業技術総合研究所 (6,529)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成23年10月12日(2011.10.12)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成22年度 独立行政法人新エネルギー・産業技術総合開発機構「高速不揮発メモリ機能技術開発/高速不揮発メモリの開発」委託研究、産業技術強化法第19条の適用を受ける特許出願

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【出願人】(301021533)独立行政法人産業技術総合研究所 (6,529)

【Fターム(参考)】

[ Back to top ]