半導体装置及びその製造方法

【課題】低周波雑音が低減されるとともに、素子面積の小さい半導体装置及びその製造方法を製造コストを増大させずに提供する。

【解決手段】半導体装置は、第1導電型の下部ゲート領域4と、第2導電型のチャネル領域3と、第1導電型の上部ゲート領域2と、チャネル領域3の両側に位置する第2導電型のソース及びドレイン領域8と、上部ゲート領域2上に形成されたゲート電極6と、ゲート電極6の両側面上に形成されたサイドウォールスペーサ7とを有するJFET70を備える。上部ゲート領域2とソース及びドレイン領域8とは、チャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間しており、ソース及びドレイン領域8は、ゲート長方向におけるゲート電極6の両側方であってサイドウォールスペーサ7の外側を含む領域に形成されている。

【解決手段】半導体装置は、第1導電型の下部ゲート領域4と、第2導電型のチャネル領域3と、第1導電型の上部ゲート領域2と、チャネル領域3の両側に位置する第2導電型のソース及びドレイン領域8と、上部ゲート領域2上に形成されたゲート電極6と、ゲート電極6の両側面上に形成されたサイドウォールスペーサ7とを有するJFET70を備える。上部ゲート領域2とソース及びドレイン領域8とは、チャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間しており、ソース及びドレイン領域8は、ゲート長方向におけるゲート電極6の両側方であってサイドウォールスペーサ7の外側を含む領域に形成されている。

【発明の詳細な説明】

【技術分野】

【0001】

本明細書に記載された技術は、半導体装置及びその製造方法に係り、特に、微小信号を増幅するアナログ回路、又はアナログ回路とデジタル回路等との混載LSI等として用いられる半導体装置及びその製造方法に関するものである。

【背景技術】

【0002】

従来、アナログ回路やLSIに用いられる半導体装置は、半導体基板上に絶縁膜を介してゲート電極が形成され、半導体基板の上面近傍のうちゲート電極下に位置する部分にチャネルが形成される構成、すなわちmetal-inasulator-semiconductor(MIS)構造を有していた。

【0003】

このような構成を有する半導体装置について、図面を参照しながら以下に説明する(例えば、特許文献1参照)。

【0004】

図22は、従来の半導体装置を示す断面図である。同図において、従来の半導体装置は、半導体基板200上にゲート絶縁膜201を挟んで形成されたゲート電極202と、半導体基板200のうちゲート電極202の両端部の下に位置する領域にそれぞれ形成されたlightly doped drain(LDD)領域203と、半導体基板200のうちゲート電極202の両側方に位置する領域であってLDD領域203の外側に形成されたソース及びドレイン領域204とを備えている。

【0005】

半導体基板200の上面部分のうちゲート電極202の直下に位置し、2つのLDD領域203に挟まれた領域にチャネルが形成される。

【0006】

ここで、微細なサブミクロンチャネルを有する半導体装置では、一般的に短チャネル効果といわれる閾値電圧の低下が顕著になる。このため、閾値電圧の低下を防止する目的で、LDD領域203に隣接するチャネルの一部またはチャネルの下部に、Halo注入領域205と呼ばれる、チャネル領域と同一導電型でチャネル領域よりも不純物濃度が濃い領域を形成することが多い。

【0007】

しかしながら、Halo注入領域205を形成する場合、電流ミラー回路などのアナログ回路の特性に影響を及ぼすアーリー電圧の低下が問題となる。そのため、従来はHalo注入領域205を設けない半導体装置でアナログ回路を構成することで、アーリー電圧の低下を抑制していた。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特表2003−509863号公報

【特許文献2】特開平03−142843号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、従来の半導体装置である表面ゲート型電界効果トランジスタ(具体的にはMISFET)においては、チャネルが半導体基板の上面近くに形成される。このため、従来の半導体装置では、半導体基板とゲ−ト酸化膜との間に生じる界面準位によって電子の捕獲や放出が起こり、その結果、低周波雑音が大きくなりやすい。そこで、素子面積当りの電流密度の増加を抑制して雑音を低減しようとすると、微小な電気信号を増幅するようなアナログ回路に従来の半導体装置を用いた場合、素子面積を大きくしなければならず、ひいてはチップ面積が増大するという不具合が生じる。

【0010】

一方、低周波雑音が小さい素子として接合型電界効果トランジスタが知られているが、接合型電界効果トランジスタは素子面積が比較的大きい。例えば、ゲートがPN接合でなく、ショットキー接合を用いる点で、接合型電界効果トランジスタの一種と考えられるMESFET(Metal-Semiconductor Field Effect Transistor)を縮小化した従来例として、特許文献2に開示された構成があるが、半導体基板上面における実効ゲート寸法(実際にゲートとして機能する部分の寸法)は小さいものの、ゲート電極自体の平面寸法は大きく、ゲート電極とソース及びドレイン電極との間隔を確保すると素子としての面積縮小効果は小さくなる。

【0011】

また、この従来例では、接合型電界効果トランジスタの製造工程と、論理回路を構成する表面ゲート型電界効果トランジスタの製造工程とで共通化できる工程が少ないので、アナログ回路と論理回路とを混載する場合には製造コストが増大するおそれがある。

【0012】

そこで、本発明は、上記の課題に鑑みて、PN接合型電界効果トランジスタ(JFET)において、低周波雑音が低減されるとともに、素子面積の小さい半導体装置及びその製造方法を製造コストを増大させずに提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明の一例に係る半導体装置は、半導体基板における第1の素子領域上に設けられたJFETを備えた半導体装置であって、前記JFETは、前記半導体基板内に形成された第1導電型の下部ゲート領域と、前記下部ゲート領域上に形成された第2導電型のチャネル領域と、前記チャネル領域とPN接合を形成するように前記チャネル領域上に形成された第1導電型の上部ゲート領域と、前記下部ゲート領域上であって前記チャネル領域の両側に位置する第2導電型の第1のソース及びドレイン領域と、前記上部ゲート領域上に形成された第1のゲート電極と、前記第1のゲート電極の両側面上に形成された第1のサイドウォールスペーサとを有しており、前記上部ゲート領域と前記第1のソース及びドレイン領域とは、前記チャネル領域のうち前記第1のサイドウォールスペーサの下に位置する部分を挟んで互いに離間しており、前記第1のソース及びドレイン領域は、ゲート長方向における前記第1のゲート電極の両側方であって前記第1のサイドウォールスペーサの外側を含む領域に形成されている。

【0014】

この構成によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。また、ゲート電極を形成する際やソース及びドレイン領域を形成する際に位置合わせズレを考慮したマージンを取る必要がないので、従来の半導体装置に比べてJFETで構成された回路の面積を大幅に縮小することができる。また、上部ゲート領域がチャネル領域と第1のゲート電極との間に設けられているので、半導体基板の上面近傍にチャネルが形成されるMISFETよりも同じ動作電流密度で比較した場合の低周波雑音を低減することができる。このように、当該半導体装置によれば、低周波雑音が低減され、MISFETと同程度まで素子面積が縮小できるので、アナログ回路等に好ましく用いることができる。

【0015】

また、前記半導体基板における第2の素子領域上に設けられたMISFETをさらに備え、前記MISFETは、前記半導体基板内に形成された第1導電型の半導体領域と、前記半導体領域上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された第2のゲート電極と、前記第2のゲート電極の両側面上に形成された第2のサイドウォールスペーサと、ゲート長方向における前記第2のゲート電極の両側方に位置する領域に形成された第2導電型の第2のソース及びドレイン領域とを有していてもよい。

【0016】

この場合、JFETの素子面積を縮小できることにより、半導体装置全体の面積を縮小することができる。さらに、JFETとMISFETの製造工程の一部を共通化することができるので、JFETで構成された回路とMISFETで構成された回路との混載LSIを、両素子を別々に作製する場合に比べて低コストで製造することができる。

【0017】

また、本発明の半導体基板の製造方法は、第1の素子領域上に設けられたJFETを備えた半導体装置の製造方法であって、前記第1の素子領域において第1導電型の下部ゲート領域を形成する工程(a)と、前記第1の素子領域において前記下部ゲート領域の上に第2導電型のチャネル領域を形成する工程(b)と、前記第1の素子領域において、第1導電型の不純物を導入することによって前記チャネル領域上に、前記チャネル領域とPN接合を形成する第1導電型の上部ゲート領域を形成する工程(c)と、前記チャネル領域上に第1のゲート電極を形成する工程(d)と、前記第1のゲート電極の両側面上に第1のサイドウォールスペーサを形成する工程(e)と、前記チャネル領域のうち、ゲート長方向における前記第1のゲート電極の両側方であって前記第1のサイドウォールスペーサの外側を含む領域に、前記上部ゲート領域と離間した第2導電型の第1のソース及びドレイン領域を形成する工程(f)とを備えている。

【0018】

この方法によれば、工程(f)でチャネル領域内に第1のソース及びドレイン領域を自己整合的に形成することができる。このため、第1のソース及びドレイン領域を形成する際にマージンを取る必要がなく、素子面積が縮小されたJFETを形成することができる。また、チャネル領域上に上部ゲート領域を形成するので、チャネル領域を半導体基板の上面から離れた位置に形成することができ、低周波雑音が低減されたJFETを作製することが可能となる。

【0019】

また、このJFETとMISFETとを混載する場合には、第1のソース及びドレイン領域と第2のソース及びドレイン領域とを同一工程で形成する等、JFETとMISFETとを共通の工程により作製することができるので、JFETとMISFETとを別々に形成する場合に比べて製造コストを低減することができる。

【発明の効果】

【0020】

本発明の半導体装置及びその製造方法によれば、アナログ回路等を構成するJFETの素子面積を低減することができる。さらに、JFETで構成された回路とMISFETで構成された回路との混載を容易にし、製造コストの低減も併せて図ることができる。

【図面の簡単な説明】

【0021】

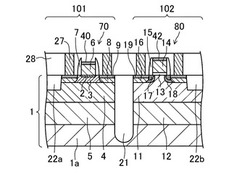

【図1】図1は、本発明の第1の実施形態に係る半導体装置を示す断面図である。

【図2】図2(a)〜(e)は、第1の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図3】図3(a)〜(c)は、第1の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図4】図4は、本発明の第1の実施形態に係る半導体装置の変形例を示す断面図である。

【図5】図5(a)〜(e)は、第1の実施形態に係る半導体装置の変形例の製造方法の一例を示す断面図である。

【図6】図6(a)〜(c)は、第1の実施形態に係る半導体装置の変形例の製造方法の一例を示す断面図である。

【図7】図7は、本発明の第2の実施形態に係る半導体装置を示す断面図である。

【図8】図8(a)〜(d)は、第2の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図9】図9(a)〜(c)は、第2の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図10】図10は、本発明の第2の実施形態に係る半導体装置の変形例を示す断面図である。

【図11】図11(a)〜(d)は、第2の実施形態に係る半導体装置の変形例の製造方法の一例を示す断面図である。

【図12】図12(a)〜(c)は、第2の実施形態に係る半導体装置の変形例の製造方法の一例を示す断面図である。

【図13】図13は、本発明の第3の実施形態に係る半導体装置を示す断面図である。

【図14】図14(a)〜(d)は、第3の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図15】図15(a)〜(c)は、第3の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図16】図16は、本発明の第4の実施形態に係る半導体装置を示す断面図である。

【図17】図17(a)〜(d)は、第4の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図18】図18(a)〜(c)は、第4の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図19】図19は、本発明の第4の実施形態に係る半導体装置の変形例を示す断面図である。

【図20】図20(a)〜(d)は、第4の実施形態に係る半導体装置の変形例の製造方法の一例を示す断面図である。

【図21】図21(a)〜(c)は、第4の実施形態に係る半導体装置の変形例の製造方法の一例を示す断面図である。

【図22】図22は、従来の半導体装置を示す断面図である。

【発明を実施するための形態】

【0022】

以下、本発明の実施形態における半導体装置及びその製造方法について、図面を参照しながら説明する。

【0023】

(第1の実施形態)

−半導体装置の構成−

図1は、本発明の第1の実施形態に係る半導体装置を示す断面図である。同図に示すように、本実施形態の半導体装置においては、例えばシリコン等からなる半導体基板1に、第1の素子領域101と第2の素子領域102とが形成されている。第1の素子領域101上にはJFETである第1のトランジスタ70が形成され、第2の素子領域102上にはMISFETである第2のトランジスタ80が形成されている。

【0024】

なお、本明細書において、第1の素子領域101とは、半導体基板1の上部であって、第1のトランジスタ70を形成するための領域内に形成された部分を指し、第2の素子領域102とは、半導体基板1の上部であって、第2のトランジスタ80を形成するための領域内に形成された部分を指すものとする。

【0025】

半導体基板1内には、P型の基板部分1a、基板部分1a上のN型埋め込み領域5、N型埋め込み領域5上のP型の下部ゲート領域4、下部ゲート領域4上のN型のチャネル領域3、チャネル領域3上のP型の上部ゲート領域2、及び下部ゲート領域4上のN型のソース及びドレイン領域8が形成されている。

【0026】

第1のトランジスタ70は、第1の素子領域101内にそれぞれ形成された上述の下部ゲート領域4、チャネル領域3、上部ゲート領域2、及びソース及びドレイン領域8と、上部ゲート領域2上に形成されたP型ポリシリコン等からなるゲート電極6と、ソース及びドレイン領域8上とゲート電極6上とにそれぞれ形成されたシリサイド層9、40と、ゲート電極6及びシリサイド層9の側面上に形成されたサイドウォールスペーサ7とを有している。

【0027】

ゲート電極6のゲート長方向の幅は、例えば数10nm〜数μm程度である。また、サイドウォールスペーサ7は、シリコン酸化物等の絶縁体で構成され、そのゲート長方向の幅は、例えば数10nm〜100nm程度である。

【0028】

ソース及びドレイン領域8はゲート長方向においてゲート電極6両側方であって、サイドウォールスペーサ7の外側を含む領域に形成されている。ソース及びドレイン領域8のN型不純物濃度は、1×1018atoms/cm3〜1×1021atoms/cm3程度である。各々に印加される電圧に応じて、ソース及びドレイン領域8の一方がソース領域となり、他方がドレイン領域となる。また、チャネル領域3は2つのソース及びドレイン領域8に挟まれており、上部ゲート領域2の側面及び底面はチャネル領域3に囲まれている。

【0029】

チャネル領域3に含まれるN型不純物の濃度はソース及びドレイン領域8のN型不純物の濃度よりも低く、例えば1×1016atoms/cm3〜1×1019atoms/cm3程度である。

【0030】

上部ゲート領域2は、チャネル領域3とPN接合するようにチャネル領域3上に形成されている。上部ゲート領域2に含まれるP型不純物の濃度は、例えば1×1019atoms/cm3〜1×1021atoms/cm3程度である。

【0031】

また、半導体基板1の第2の素子領域102内には、基板部分1a上のN型埋め込み領域12、N型埋め込み領域12上のP型のウェル領域(半導体領域)11、ウェル領域11上のN型のソース及びドレイン領域16、N型の低濃度ドレイン領域17、低濃度ドレイン領域17の一部を覆うP型のHalo注入領域18がそれぞれ形成されている。

【0032】

第2のトランジスタ80は、ウェル領域11上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成されたポリシリコン等からなるゲート電極14と、上述のソース及びドレイン領域16、低濃度ドレイン領域17、及びHalo注入領域18と、ソース及びドレイン領域16上とゲート電極14上とにそれぞれ形成されたシリサイド層19、42と、ゲート電極14の側面上に形成されたサイドウォールスペーサ15とを有している。

【0033】

ゲート電極14のゲート長方向の幅(すなわちゲート長)は、例えば数10nm〜数μm程度である。ゲート電極14は、N型不純物を含んでいてもよい。ゲート電極14とゲート電極6とはポリシリコン等、互いに同じ材料で構成されている。

【0034】

また、後述のように、サイドウォールスペーサ15とサイドウォールスペーサ7とは同一の絶縁膜を加工することで形成される。このため、サイドウォールスペーサ15の構成材料は、サイドウォールスペーサ7と同様である。また、サイドウォールスペーサ7、15のゲート長方向断面の形状は共に上方から下方に向かって厚みがやや厚くなるI字型である。

【0035】

ソース及びドレイン領域16は、ゲート長方向においてゲート電極14の両側方であって、サイドウォールスペーサ15の外側を含む領域に形成されており、そのN型不純物濃度は1×1018atoms/cm3〜1×1021atoms/cm3程度である。後述するように、ソース及びドレイン領域8、16を同時に形成する場合、ソース及びドレイン領域8、16の深さ及び不純物濃度とはほぼ等しくなる。各々に印加される電圧に応じて、ソース及びドレイン領域16の一方がソース領域となり、他方がドレイン領域となる。

【0036】

低濃度ドレイン領域17は、ゲート電極14の両側方下に位置し、各ソース及びドレイン領域16の内側(ゲート電極14側)側面に接している。低濃度ドレイン領域17は、ソース及びドレイン領域16よりも低濃度でN型不純物を含んでおり、その不純物濃度は例えば1×1017atoms/cm3〜1×1019atoms/cm3程度である。

【0037】

Halo注入領域18は、いわゆる短チャネル効果を防止するために設けられており、ゲート電極14直下のチャネル領域と同じ導電型で、且つチャネル領域(及びウェル領域11)よりも高濃度のP型不純物を含んでいる。このHalo注入領域18は、各低濃度ドレイン領域17の内側面(ゲート電極側面)を覆うように設けられている。Halo注入領域18が含むP型不純物の濃度は例えば1×1017atoms/cm3〜1×1019atoms/cm3程度である。

【0038】

半導体基板1の第1の素子領域101と第2の素子領域102との間は、基板部分1aの上部に達する深い素子分離領域21によって分離されている。また、第1の素子領域101及び第2の素子領域102は、それぞれ他の同じ素子(図示せず)と浅い素子分離領域22a、22bにより分離されている。深い素子分離領域21及び浅い素子分離領域22a、22bはそれぞれ半導体基板1に形成された溝内に埋め込まれたシリコン酸化物等により構成されている。

【0039】

また、半導体基板1の全面上には層間絶縁膜28が形成されている。シリサイド層9、19上(ソース及びドレイン領域8、16上)には、層間絶縁膜28を貫通するコンタクトプラグ27が形成されている。

【0040】

なお、以上で説明した半導体装置において、N型埋め込み領域5、12は、第1のトランジスタ70及び第2のトランジスタ80をそれぞれ基板部分1aと電気的に分離するためのものである。上述の素子分離領域21は、必ずしもN型埋め込み領域5を貫通していなくてもよい。また、N型埋め込み領域5、12を同時に形成してもよい。さらに、各シリサイド層9、19及び第2の素子領域102のHalo注入領域18は必ずしも形成されていなくてもよい。

【0041】

第1のトランジスタ70では、通常のアナログ回路で使用する場合、特に、上部ゲート領域2、及び下部ゲート領域4とチャネル領域3のPN接合間には、常に逆バイアスになるよう電圧が与えられており、ゲート電極6にはほとんど電流が流れない。さらにゲート−ソース間に所定の負の電圧を印加して、上部ゲート領域2、及び下部ゲート領域4に挟まれたチャネル領域3を空乏化することにより、ソース及びドレイン領域8間に所定の電圧を印加しても電流が流れなくなり、半導体装置はオフ状態となる。

【0042】

一方、ゲート−ソース間に負の電圧で、かつ、半導体装置をオフ状態にする所定のゲート電圧よりも大きい電圧、すなわち絶対値としては上記のオフ状態にするための所定のゲート電圧より小さい電圧、をゲート電極6に印加すると、ソース及びドレイン領域8の一方(ドレイン領域)から他方(ソース領域)へとチャネル領域3を介して電流が流れ、オン状態となる。

【0043】

第2のトランジスタ80では、2つのソース及びドレイン領域16間に所定の電圧を印加した状態でゲート電極14に正の電圧を印加することでオン状態となり、ソース及びドレイン領域16間に電流が流れる。ウェル領域11のうち、2つのソース及びドレイン領域16に挟まれた、ゲート電極14の直下に位置する部分はキャリア(ここでは電子)が走行するチャネル領域となる。

【0044】

−半導体装置の製造方法−

次に、以上のように構成された本実施形態に係る半導体装置の製造方法について説明する。図2(a)〜(e)、図3(a)〜(c)は、本実施形態の半導体装置の製造方法の一例を示す断面図である。

【0045】

まず、図2(a)に示す工程では、P型シリコン等からなる半導体基板1の所定の領域にそれぞれ浅い溝及び深い溝を形成する。次いで、第1の素子領域101と第2の素子領域102との間に形成された深い溝内にシリコン酸化物等からなる誘電体膜を埋め込んで素子分離領域21を形成するとともに、浅い溝内にシリコン酸化物等からなる誘電体膜を埋め込んで素子分離領域22a、22bを形成する。これらの誘電体膜は堆積後、chemical mechanical polishing(CMP)法等の方法によって平坦化される。

【0046】

次に、図2(b)に示す工程では、イオン注入等の公知の方法によって半導体基板1の第1の素子領域101にN型不純物を導入することでN型埋め込み領域5を形成した後、N型埋め込み領域5の上部にP型不純物を導入することで下部ゲート領域4を形成する。また、半導体基板1の第2の素子領域102にN型埋め込み領域12を形成した後、N型埋め込み領域12の上部にP型不純物を導入することで、P型のウェル領域11を形成する。

【0047】

本工程で、N型埋め込み領域5とN型埋め込み領域12とは同時に形成することもでき、下部ゲート領域4とウェル領域11とは同時に形成することもできる。

【0048】

なお、半導体基板1のうちN型埋め込み領域5、12の下に位置する領域は、便宜的に基板部分1aと呼ぶものとする。

【0049】

次いで、イオン注入等によって下部ゲート領域4の上部に選択的にN型不純物を導入することで、N型のチャネル領域3を形成する。

【0050】

次に、図2(c)に示す工程では、chemichal vapor deposition(CVD)法等を用いて、半導体基板1の上面全体にシリコン酸化物等からなり、膜厚が例えば0.数nm〜数nm程度の絶縁膜13aと、ポリシリコン等の導電体からなり、膜厚が例えば数nm〜数10nm程度の導電膜117とを順次形成する。次いで、公知のエッチング等により絶縁膜13a及び導電膜117のうち第1の素子領域101上に形成された部分を除去し、絶縁膜13a及び導電膜117を半導体基板1の第2の素子領域102上に残す。

【0051】

次に、図2(d)に示す工程では、CVD法等により、再びポリシリコン等からなり、膜厚が数10nm〜数100nm程度の導電膜118を半導体基板1の上面上及び導電膜117上に形成する。その後、イオン注入等により、導電膜118のうち、第1の素子領域101上に形成された部分にはP型不純物を導入し、導電膜117、118のうち第2の素子領域102上に形成された部分にはN型不純物を導入する(図示せず)。

【0052】

次に、図2(e)に示す工程では、ドライエッチング法などにより、第1の素子領域101上において導電膜118を、第2の素子領域102上において導電膜117、118及び絶縁膜13aをそれぞれ選択的に除去することで、チャネル領域3上にゲート電極6を形成するとともに、ウェル領域11上にゲート絶縁膜13及びゲート電極14を形成する。

【0053】

次に、図3(a)に示す工程では、第2の素子領域102(ウェル領域11)に必要に応じてゲート電極14をマスクとして用いた不純物イオンの注入を行うことにより、P型のHalo注入領域18、N型の低濃度ドレイン領域17をそれぞれ形成する。続いて、半導体基板1上及びゲート電極6、14上にシリコン窒化膜等を形成してから当該シリコン窒化膜等を異方性エッチングによりエッチバックすることにより、サイドウォールスペーサ7をゲート電極6の両側面上に形成するとともに、サイドウォールスペーサ15をゲート電極14の両側面上に形成する。

【0054】

続いて、ゲート電極6、14及びサイドウォールスペーサ7、15をマスクとして半導体基板1内にN型不純物をイオン注入する。これにより、半導体基板1(具体的にはチャネル領域3)のうち、ゲート電極6の両側方であってサイドウォールスペーサ7の外側を含む領域にソース及びドレイン領域8を形成するとともに、半導体基板1(具体的には低濃度ドレイン領域17及びウェル領域11)のうち、ゲート電極14の両側方であってサイドウォールスペーサ15の外側を含む領域にソース及びドレイン領域16を形成する。

【0055】

次に、熱処理を行って半導体基板1内及びゲート電極6、14内に含まれる不純物を活性化する。この活性化の際に、ゲート電極6に接触したチャネル領域3の上面近傍部分に、ゲート電極6に添加されたP型不純物が拡散されることによって、P型の上部ゲート領域2が形成される。チャネル領域3へのP型不純物の拡散は、ゲート電極6の形成後、別個に行ってもよい。

【0056】

次に、図3(b)に示す工程で、半導体基板1上にゲート電極6、14を埋め込むように絶縁膜(シリコン酸化膜26)を形成した後、公知の方法によってゲート電極6、14の上面が露出するまでシリコン酸化膜26を研磨する。

【0057】

さらに、第2の素子領域102の上方のみをマスク(図示せず)で覆った状態でゲート電極6の上部を選択的に除去した後、当該マスク及び残存するシリコン酸化膜26を除去する。ここで、露出したゲート電極6の上部には図3(a)に示す工程でソース及びドレイン領域8、16の形成時にN型不純物が導入されるので、必要に応じて当該部分を除去することで、上部ゲート電極3に安定して電圧を印加することができるようになる。

【0058】

次に、図3(c)に示す工程で、ゲート電極6、14上にシリサイド層40、42をそれぞれ形成するとともに、ソース及びドレイン領域8、16上にシリサイド層9、19をそれぞれ形成する。次いで、半導体基板1の上面全体に層間絶縁膜28を形成した後、層間絶縁膜28を貫通し、シリサイド層9、19にそれぞれ接続するコンタクトプラグ27を形成する。その後は図示しないが、周知技術を用いて、表面保護膜、電極等との接続を取るための配線層、及び外部接続用端子等を形成することにより、半導体装置を作製できる。

【0059】

なお、図2(c)、(d)に示す工程において、絶縁膜13aを形成した直後に絶縁膜13aの一部を選択的に除去する際には、絶縁膜13a上に保護膜として導電膜117を設ける例を説明したが、エッチングによるダメージがゲート絶縁膜となる絶縁膜13aの信頼性に影響を与えない場合には、導電膜117を設けなくてもよい。この場合、ゲート電極6、14形成用のポリシリコンを第1の素子領域101上及び第2の素子領域102上に堆積等することによってゲート電極6、14を同時に形成できる。

【0060】

また、図3(b)に示す工程では、上記したように、ゲート電極6のうち、ソース及びドレイン領域8の形成時にN型不純物が導入された部分を除去しているが、両導電型不純物の濃度が十分濃く、両導電型不純物間のリーク電流のために整流特性が無視できる場合には、必ずしもゲート電極6の上部を除去しなくてもよい。

【0061】

なお、上記で説明した各層の導電型を、全て反対の導電型にしても第1のトランジスタ70をJFETとして、第2のトランジスタ80をMISFETとして問題なく動作させることができる。

【0062】

−本実施形態の半導体装置及び製造方法の効果−

以上で説明した本実施形態の半導体装置では、JFET(第1のトランジスタ70)において、上部ゲート領域2とソース及びドレイン領域8、及び上部ゲート領域2とシリサイド層9とは、それぞれチャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間している。

【0063】

この構成によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。また、ゲート電極6が平面的に見てソース及びドレイン領域8と重なることがない。なお、サイドウォールスペーサ7の断面形状はI字状であれば好ましいが、平面的に見てソース及びドレイン領域8と大きく重なっていなければ、L字状等であってもよい。

【0064】

これに対し、特許文献2に記載された従来の半導体装置では、JFETにおいて、ゲート電極を形成するために、スペーサ端との位置合わせズレを考慮した間隔を取る必要があり、ソース及びドレイン電極とゲート電極との間隔を取る必要もある。

【0065】

このため、本実施形態の半導体装置では、特許文献2に記載された従来の半導体装置のJFETと実効ゲート寸法が同じ場合であっても、ゲート電極6のゲート長方向の幅を大幅に縮小することができる。特に、JFETである第1のトランジスタ70をMISFETと同様の寸法で形成することができる。

【0066】

さらに、N型のチャネル領域3はゲート電極6の直下において半導体基板1の上面から離れたところにある。そのため、第1のトランジスタ70においては、半導体基板1の上面近傍にチャネルが形成されるMISFETよりも、同じ動作電流密度で比較した場合の低周波雑音を10分の1以下にすることができる。その結果、微小な電気信号を扱うアナログ回路等を本実施形態のJFETで構成することにより、当該アナログ回路をMISFETで構成する場合と同等の低周波雑音性能を実現するのに、10分の1以下程度まで回路面積を縮小することができる。このように、アナログ回路と論理回路等を半導体基板上に混載した半導体装置全体のチップサイズを従来よりも大幅に縮小することができる。

【0067】

また、本実施形態の半導体装置において、上述のJFETと、論理回路等に用いられるMISFET(第2のトランジスタ80)とが同一の半導体基板1上に形成される場合、チップ全体の面積を従来技術に比べて大幅に縮小できる。また、後述のように、JFETとMISFETとが共通の工程で形成できる構成となっているので、両素子を別々に形成する場合に比べて製造コストを大幅に低減することができる。

【0068】

また、本実施形態に係る半導体装置の製造方法では、ゲート電極6、14の形成工程、サイドウォールスペーサ7、15の形成工程、ソース及びドレイン領域8、16の形成工程、各シリサイド層の形成工程等、第1のトランジスタ70の形成工程と第2のトランジスタ80の形成工程とを共通化している。そのため、本実施形態の方法によれば、それぞれのトランジスタを別個の工程により形成するのに比べて半導体装置を安価に製造することができる。

【0069】

また、本実施形態の方法によれば、P型の上部ゲート領域2を形成するための専用の工程が不要となることによっても工程数の削減が図られている。

【0070】

以上のように、本実施形態の半導体装置及びその製造方法によれば、低周波雑音が低減されたアナログ回路を小さい面積で作製できるとともに、アナログ回路と論理回路とが混載された半導体装置をより安価に、且つ、より小さい面積で実現することができる。

【0071】

−第1の実施形態の変形例−

図4は、本発明の第1の実施形態に係る半導体装置の変形例を示す断面図である。同図において、図1に示す第1の実施形態に係る半導体装置と同様の部分には同一符号を付している。

【0072】

第1の実施形態に係る半導体装置では、上述のように、第1の素子領域101において、N型のチャネル領域3上にP型のゲート電極6を形成し、このゲート電極6からチャネル領域3へP型不純物を拡散させることによってチャネル領域3の上部にP型の上部ゲート領域2が形成される。

【0073】

これに対し、本変形例に係る半導体装置では、半導体基板1の第1の素子領域101の上面部分に予めP型の上部ゲート領域131(図5(b)参照)を形成しておき、ゲート電極6の形成の際に上部ゲート領域131の一部を除去することで、上部ゲート領域2が形成される。

【0074】

このため、図4に示すように、本変形例に係る半導体装置では、第1の素子領域101上に形成された第1のトランジスタ70において、ゲート電極6と上部ゲート領域2との界面の位置よりもサイドウォールスペーサ7と半導体基板1(チャネル領域3)との界面の位置の方が低くなっている。また、第2の素子領域102上に形成された第2のトランジスタ80において、ゲート絶縁膜13とウェル領域11との界面の位置よりもサイドウォールスペーサ15と半導体基板1(低濃度ドレイン領域17)との界面の位置の方が低くなっている。なお、上部ゲート領域2の厚さは数10nm以下程度であり、上部ゲート領域2は、単結晶シリコン等からなる半導体基板1と、ゲート電極6を構成するポリシリコン膜との界面の上下両側に広がっている。

【0075】

次に、以上のように構成された本変形例に係る半導体装置の製造方法について説明する。図5(a)〜(e)、図6(a)〜(c)は、本変形例に係る半導体装置の製造方法の一例を示す断面図である。

【0076】

まず、図5(a)に示す工程では、図2(a)に示す工程と同様にして、半導体基板1内に素子分離領域21、22a、22bを形成する。

【0077】

次に、図5(b)に示す工程では、イオン注入等の方法により半導体基板1内にN型埋め込み領域5、下部ゲート領域4、N型埋め込み領域12、及びP型のウェル領域11を形成する。

【0078】

次いで、イオン注入等によって下部ゲート領域4の上部に選択的にN型不純物を導入することで、N型のチャネル領域3を形成する。続いて、P型不純物のイオン注入により、チャネル領域3の上部に、P型の上部ゲート領域131を形成する。

【0079】

次に、図5(c)に示す工程では、図2(c)に示す工程と同様の方法により、半導体基板1の上面全体にシリコン酸化物等からなり、膜厚が例えば0.数nm〜数nm程度の絶縁膜13aと、ポリシリコン等の導電体からなり、膜厚が例えば数nm〜数10nm程度の導電膜117とを順次形成する。次いで、絶縁膜13a及び導電膜117のうち第1の素子領域101上に形成された部分を除去し、絶縁膜13a及び導電膜117を半導体基板1の第2の素子領域102上に残す。

【0080】

次に、図5(d)に示す工程で、再びポリシリコン等からなり、膜厚が数10nm〜数100nm程度の導電膜118を半導体基板1の上面上及び導電膜117(図示省略)上に形成する。その後、イオン注入等により、導電膜118のうち、第1の素子領域101上に形成された部分にはP型不純物を導入し、導電膜117、118のうち第2の素子領域102上に形成された部分にはN型不純物を導入する(図示せず)。

【0081】

なお、本変形例では、上部ゲート領域131を絶縁膜13aの形成前に形成したが、これに代えて、図5(c)に示す工程において、第1の素子領域101上の導電膜117及び絶縁膜13aを除去後、イオン注入法などを用いて、第1の素子領域101の半導体基板1の上面部にP型の上部ゲート領域131’を形成してもよい。

【0082】

あるいは、図5(d)に示す工程において、ポリシリコンからなる導電膜118の形成後、イオン注入法などを用いて、第1の素子領域101上の導電膜118の下部から半導体基板1(チャネル領域3)の上面部に亘ってP型の上部ゲート領域131''を形成してもよい。

【0083】

次に、図5(e)に示す工程では、ドライエッチング法などにより導電膜117、118をパターンニングしてゲート電極6、14を形成する。これに引き続いて、上部ゲート領域131(及び場合によってはチャネル領域3の上面部)のうちゲート電極6の直下に位置する領域を除く部分と、絶縁膜13a及びウェル領域11上面部のうちゲート電極14の直下に位置する領域を除く部分とを除去する。上部ゲート領域131及びウェル領域11の除去量(すなわち、半導体基板1における除去深さ)は、例えば10nm〜100nm程度とすることが好ましい。なお、上部ゲート領域131のうちゲート電極6下に残された部分を便宜的に上部ゲート領域2と表記する。

【0084】

次に、図6(a)に示す工程で、第2の素子領域102に必要に応じてP型のHalo注入領域18、N型の低濃度ドレイン領域17をそれぞれ形成する。続いて、半導体基板1上及びゲート電極6、14上にシリコン窒化膜等を形成してから当該シリコン窒化膜等を異方性エッチングによりエッチバックすることにより、サイドウォールスペーサ7をゲート電極6の両側面上に形成するとともに、サイドウォールスペーサ15をゲート電極14の両側面上に形成する。

【0085】

続いて、ゲート電極6、14及びサイドウォールスペーサ7、15をマスクとして半導体基板1内にN型不純物をイオン注入する。これにより、半導体基板1(具体的にはチャネル領域3)のうち、ゲート電極6の両側方であってサイドウォールスペーサ7の外側に位置する領域にソース及びドレイン領域8を形成するとともに、半導体基板1(具体的にはウェル領域11)のうち、ゲート電極14の両側方であってサイドウォールスペーサ15の外側に位置する領域にソース及びドレイン領域16を形成する。

【0086】

次に、熱処理を行って半導体基板1内及びゲート電極6、14内に含まれる不純物を活性化する。この活性化の際に、P型の上部ゲート領域2中のP型不純物がN型のチャネル領域3の上部、及びゲート電極6の下面近傍部に拡散する。

【0087】

次に、図6(b)に示す工程で、半導体基板1上にゲート電極6、14を埋め込むようにシリコン酸化膜26を形成した後、公知の方法によってゲート電極6、14の上面が露出するまでシリコン酸化膜26を研磨する。次いで、第1の実施形態に係る方法と同様に、ゲート電極6の上部を選択的に除去した後、シリコン酸化膜26を除去する。

【0088】

次に、図6(c)に示す工程で、ゲート電極6、14上にシリサイド層40、42をそれぞれ形成するとともに、ソース及びドレイン領域8、16上にシリサイド層9、19をそれぞれ形成する。次いで、半導体基板1の上面全体に層間絶縁膜28を形成した後、層間絶縁膜28を貫通し、シリサイド層9、19にそれぞれ接続するコンタクトプラグ27を形成する。その後は図示しないが、周知技術を用いて、表面保護膜、電極等との接続を取るための配線層、及び外部接続用端子等を形成することにより、本変形例に係る半導体装置を作製できる。

【0089】

なお、図5(c)、(d)に示す工程において、絶縁膜13aを形成した直後に絶縁膜13aの一部を選択的に除去する際には、絶縁膜13a上に保護膜として導電膜117を設ける例を説明したが、エッチングによるダメージがゲート絶縁膜となる絶縁膜13aの信頼性に影響を与えない場合には、導電膜117を設けなくてもよい。この場合、ゲート電極6、14形成用のポリシリコンを第1の素子領域101上及び第2の素子領域102上に堆積等することによってゲート電極6、14を同時に形成できる。

【0090】

また、図6(b)に示す工程では、上記したように、ソース及びドレイン領域8の形成時にN型不純物が導入された、ゲート電極6の上部を除去しているが、両導電型不純物の濃度が十分濃く、両導電型不純物間のリーク電流のために整流特性が無視できる場合には、必ずしもゲート電極6の上部を除去しなくてもよい。

【0091】

なお、上記で説明した各層の導電型を、全て反対の導電型にしても第1のトランジスタ70をJFETとして問題なく動作させることができる。

【0092】

以上で説明した本実施形態の半導体装置では、論理回路等に用いられるMISFET(第2のトランジスタ80)と同一の半導体基板1上に形成されたJFET(第1のトランジスタ70)において、上部ゲート領域2とソース及びドレイン領域8、及び上部ゲート領域2とシリサイド層9とは、それぞれチャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間している。

【0093】

この構成によれば、上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の厚さ程度まで小さくすることができる。また、ゲート電極6が平面的に見てソース及びドレイン領域8と重なることがない。なお、サイドウォールスペーサ7の断面形状はI字状であれば好ましいが、平面的に見てソース及びドレイン領域8と大きく重なっていなければ、L字状等であってもよい。

【0094】

これに対し、特許文献2に記載された従来の半導体装置では、JFETにおいて、ゲート電極を形成するために、スペーサ端との位置合わせズレを考慮した間隔を取る必要があり、ソース及びドレイン電極とゲート電極との間隔を取る必要もある。

【0095】

このため、本変形例に係る半導体装置では、特許文献2に記載された従来の半導体装置のJFETと実効ゲート寸法が同じ場合であっても、ゲート電極6のゲート長方向の幅を大幅に縮小することができる。特に、JFETである第1のトランジスタ70をMISFETと同様の寸法で形成することができる。

【0096】

さらに、N型のチャネル領域3はゲート電極6の直下において半導体基板1の上面から離れたところにある。そのため、第1のトランジスタ70においては、半導体基板1の上面近傍にチャネルが形成されるMISFETよりも、同じ動作電流密度で比較した場合の低周波雑音を10分の1以下にすることができる。その結果、アナログ回路等をMISFETで構成する場合に比べて低周波雑音が大幅に抑制されたアナログ等の回路を、従来のJFETを用いた場合に比べてより小さいチップ面積で実現することが可能となる。

【0097】

また、本変形例の製造方法においても、ゲート電極6、14の形成工程、サイドウォールスペーサ7、15の形成工程、ソース及びドレイン領域8、16の形成工程等、第1のトランジスタ70の形成工程と第2のトランジスタ80の形成工程とを共通化している。そのため、本変形例の方法によれば、それぞれのトランジスタを別個の工程により形成するのに比べて半導体装置を安価に製造することができる。

【0098】

以上のように、本変形例の半導体装置及びその製造方法によっても、第1の実施形態に係る半導体装置及びその製造方法と同様に、低周波雑音が低減されたアナログ回路と、論理回路とが混載された半導体装置をより安価に、且つ、より小さい面積で実現することができる。

【0099】

また、本変形例に係る方法によれば、第1の実施形態に係る方法と異なり、ゲート電極6、14を形成用の導電膜118を形成する前に予めP型の上部ゲート領域131を形成している。このため、図5(d)に示す工程で導電膜118にP型不純物を導入する際に製造上のバラツキ等によって、意図しないP型不純物の半導体基板1への拡散が生じた場合であっても、当該拡散による素子特性への影響を第1の実施形態に係る方法に比べて小さくすることができる。

【0100】

なお、図5(b)に示す工程では、上部ゲート領域131は第1の素子領域101上全体に形成されるが、ゲート電極6の形成時に上部ゲート領域131のうちゲート電極6下に設けられた部分以外の部分は除去されるので、その後の熱処理によって余分なP型不純物がチャネル領域3等に導入されることはない。このため、本変形例に係る方法によれば、第1のトランジスタ70の素子特性をより安定化させることができる。

【0101】

(第2の実施形態)

図7は、本発明の第2の実施形態に係る半導体装置を示す断面図である。同図において、図1に示す第1の実施形態に係る半導体装置と同様の部分については同一の符号を付し、その部分の説明は一部簡略化する。

【0102】

図1に示す第1の実施形態に係る半導体装置では、ゲート電極6とP型の上部ゲート領域2とが直接接しているのに対し、図7に示す本実施形態に係る半導体装置では、ゲート電極6と上部ゲート領域2とが絶縁膜31を介して接している。このため、本実施形態の半導体装置では、第1のトランジスタ70においてゲート電極6と半導体基板1(上部ゲート領域2)とが直流的に絶縁されている。

【0103】

この絶縁膜31は、例えばゲート絶縁膜13と同じ材料で構成され、ゲート絶縁膜13と同じ厚さであってもよい。この場合、後述のように絶縁膜31をゲート絶縁膜13と同時に形成できるので、好ましい。その他の構成は、本実施形態の半導体装置と第1の実施形態の半導体装置とでほぼ同様である。

【0104】

以上の相違点があるものの、絶縁膜31が容量絶縁膜となり、半導体基板1(上部ゲート領域2及びチャネル領域3)には容量を介してゲート電極6により電位が与えられるので、本実施形態の半導体装置は第1の実施形態の半導体装置と同様な動作を示す。

【0105】

すなわち、第1のトランジスタ70では、ソース及びドレイン領域8間に所定の電圧を印加し、ゲート−ソース間に所定の負の電圧を印加した場合、チャネル領域3内に上部ゲート領域2から空乏層が拡がり、ソース及びドレイン領域8の一方(ドレイン領域)から他方(ソース領域)に電流が流れなくなる。

【0106】

一方、ゲート−ソース間に負の電圧で、かつ、半導体装置をオフ状態にする所定のゲート電圧よりも大きい電圧、すなわち絶対値としては上記のオフ状態にするための所定のゲート電圧より小さい電圧、をゲート電極6に印加すると、ソース及びドレイン領域8の一方(ドレイン領域)から他方(ソース領域)へとチャネル領域3を介して電流が流れ、オン状態となる。

【0107】

以上の構成によれば、P型の上部ゲート領域2の電位がN型のチャネル領域3の電位より高くなった場合でも、ゲート電極6から半導体基板1へと大電流が漏れ出ることがなく、回路設計の自由度を大きくすることができる。

【0108】

次に、以上のように構成された本実施形態に係る半導体装置の製造方法について説明する。

【0109】

図8(a)〜(d)、図9(a)〜(c)は、本実施形態の半導体装置の製造方法の一例を示す断面図である。これらの図において、第1の実施形態に係る半導体装置と同様の部分については図2(a)〜(e)、図3(a)〜(c)と同一の符号を付している。

【0110】

まず、図8(a)に示す工程では、図2(a)に示す工程と同様にして、半導体基板1内に素子分離領域21、22a、22bを形成する。次に、図8(b)に示す工程では、イオン注入等の方法により半導体基板1内にN型埋め込み領域5、下部ゲート領域4、N型埋め込み領域12、及びP型のウェル領域11を形成する。次に、イオン注入等によって下部ゲート領域4の上部に選択的にN型不純物を導入することで、N型のチャネル領域3を形成する。

【0111】

次に、図8(c)に示す工程では、半導体基板1の上面全体にシリコン酸化物等からなり、膜厚が例えば0.数nm〜数nm程度の絶縁膜13aと、ポリシリコン等の導電体からなり、膜厚が例えば数10nm〜数100nm程度の導電膜118とを順次形成する。その後、イオン注入等により、導電膜118のうち、第1の素子領域101上に形成された部分にはP型不純物を導入し、導電膜118のうち第2の素子領域102上に形成された部分にはN型不純物を導入する(図示せず)。

【0112】

次に、図8(d)に示す工程では、ドライエッチング法などにより導電膜118及び絶縁膜13aをパターンニングすることで、絶縁膜31を間に挟んでチャネル領域3上にゲート電極6を形成するとともに、ゲート絶縁膜13を間に挟んでウェル領域11上にゲート電極14を形成する。

【0113】

その後、図3(a)〜(c)に示す第1の実施形態に係る方法と同様の工程を経ることにより、半導体装置を作製できる。

【0114】

ここで、図9(a)に示す工程では、ソース及びドレイン領域8、16形成後の熱処理、あるいはゲート電極6、14の形成後からソース及びドレイン領域8、16の形成前までにする熱処理によって、ゲート電極6に含まれるP型不純物がゲート絶縁膜13を通過して、チャネル領域3の上部に拡散される。これにより、チャネル領域3上に上部ゲート領域2が形成される。

【0115】

また、図9(b)に示す工程では、ゲート電極6のうち、ソース及びドレイン領域8の形成時にN型不純物が導入された部分を除去しているが、両導電型不純物の濃度が十分濃く、両導電型不純物間のリーク電流のために整流特性が無視できる場合には、必ずしもゲート電極6の上部を除去しなくてもよい。

【0116】

なお、上記で説明した各層の導電型を、全て反対の導電型にしても第1のトランジスタ70をJFETとして、第2のトランジスタ80をMISFETとして問題なく動作させることができる。

【0117】

以上で説明した本実施形態の半導体装置では、JFET(第1のトランジスタ70)において、上部ゲート領域2とソース及びドレイン領域8、及び上部ゲート領域2とシリサイド層9とは、それぞれチャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間している。

【0118】

この構成によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。また、ゲート電極6が平面的に見てソース及びドレイン領域8と重なることがない。なお、サイドウォールスペーサ7の断面形状はI字状であれば好ましいが、平面的に見てソース及びドレイン領域8と大きく重なっていなければ、L字状等であってもよい。

【0119】

これに対し、特許文献2に記載された従来の半導体装置では、JFETにおいて、ゲート電極を形成するために、スペーサ端との位置合わせズレを考慮した間隔を取る必要があり、ソース及びドレイン電極とゲート電極との間隔も取る必要もある。

【0120】

このため、本実施形態の半導体装置では、特許文献2に記載された従来の半導体装置のJFETと実効ゲート寸法が同じ場合であっても、ゲート電極6のゲート長方向の幅を大幅に縮小することができる。特に、JFETである第1のトランジスタ70をMISFETと同様の寸法で形成することができる。

【0121】

さらに、N型のチャネル領域3はゲート電極6の直下において半導体基板1の上面から離れたところにある。そのため、第1のトランジスタ70においては、半導体基板1の上面近傍にチャネルが形成されるMISFETよりも、同じ動作電流密度で比較した場合の低周波雑音を10分の1以下にすることができる。その結果、アナログ回路等を本実施形態のJFETで構成することにより、当該アナログ回路をMISFETで構成する場合と同等の低周波雑音性能を実現するのに、10分の1以下程度まで回路面積を縮小することができる。

【0122】

また、本実施形態の半導体装置において、上述のJFETと、論理回路等に用いられるMISFET(第2のトランジスタ80)とが同一の半導体基板1上に形成される場合、チップ全体の面積を従来技術に比べて大幅に縮小できる。また、JFETとMISFETとが共通の工程で形成できる構成となっているので、両素子を別々に形成する場合に比べて製造コストを大幅に低減することができる。

【0123】

また、本実施形態に係る半導体装置の製造方法では、ゲート電極6、14の形成工程、サイドウォールスペーサ7、15の形成工程、ソース及びドレイン領域8、16の形成工程、各シリサイド層の形成工程等、第1のトランジスタ70の形成工程と第2のトランジスタ80の形成工程とを共通化している。そのため、本実施形態の方法によれば、それぞれのトランジスタを別個の工程により形成するのに比べて半導体装置を安価に製造することができる。

【0124】

また、本実施形態の方法によれば、P型の上部ゲート領域2を形成するための専用の工程が不要となることによっても工程数の削減が図られている。

【0125】

−第2の実施形態の変形例−

図10は、本発明の第2の実施形態に係る半導体装置の変形例を示す断面図である。同図において、図1に示す第1の実施形態に係る半導体装置と同様の部分には同一符号を付している。

【0126】

図4に示す第1の実施形態の変形例に係る半導体装置では、第1のトランジスタ70において、ゲート電極6と上部ゲート領域2とが直接接しているのに対し、図10に示す本変形例に係る半導体装置では、ゲート電極6と上部ゲート領域2とが絶縁膜31を介して接している。このため、本変形例に係る半導体装置では、第1のトランジスタ70においてゲート電極6と上部ゲート領域2とが直流的に絶縁されている。

【0127】

この絶縁膜31は、例えばゲート絶縁膜13と同じ材料で構成され、ゲート絶縁膜13と同じ厚さであってもよい。この場合、後述のように絶縁膜31をゲート絶縁膜13と同時に形成できるので、好ましい。その他の構成は、第1の実施形態の変形例に係る半導体装置と本変形例に係る半導体装置とでほぼ同様である。

【0128】

以上の相違点があるものの、絶縁膜31が容量絶縁膜となり、半導体基板1(上部ゲート領域2及びチャネル領域3)には容量を介してゲート電極6により電位が与えられるので、本変形例に係る半導体装置は第1の実施形態及びその変形例に係る半導体装置と同様な動作を示す。

【0129】

以上の構成によれば、P型の上部ゲート領域2の電位がN型のチャネル領域3の電位より高くなった場合でも、ゲート電極6から半導体基板1へと大電流が漏れ出ることがなく、回路設計の自由度を大きくすることができる。

【0130】

次に、以上のように構成された本変形例に係る半導体装置の製造方法について説明する。図11(a)〜(d)、図12(a)〜(c)は、本変形例に係る半導体装置の製造方法の一例を示す断面図である。

【0131】

まず、図11(a)に示す工程で、図5(a)に示す工程と同様にして素子分離領域21、22a、22bを形成する。次に、図11(b)に示す工程で、注入法などによりN型のチャネル領域3上部にP型の上部ゲート領域131を形成する。

【0132】

次に、図11(c)に示す工程では、CVD法等により、半導体基板1の上面全体にシリコン酸化物等からなる絶縁膜13aと、ポリシリコン等からなる導電膜118とを順次形成する。絶縁膜13aの膜厚は、例えば0.数nm〜数nm程度とし、導電膜118の膜厚は、例えば数10nm〜数100nm程度とする。その後、イオン注入等により、導電膜118のうち、第1の素子領域101上に形成された部分にはP型不純物を導入し、導電膜118のうち第2の素子領域102上に形成された部分にはN型不純物を導入する。

【0133】

なお、ここではP型の上部ゲート領域131を後にゲート絶縁膜となる絶縁膜13aの形成前に形成したが、これに代えて、絶縁膜13a及び導電膜118の形成後にイオン注入法等を用いて、チャネル領域3の上面部にP型不純物を導入することにより、チャネル領域3上に上部ゲート領域131’を形成してもよい。

【0134】

次に、図11(d)に示す工程では、ドライエッチング法などにより導電膜118をパターンニングしてゲート電極6、14を形成する。これに引き続いて、絶縁膜13a及び上部ゲート領域131(及び場合によってはチャネル領域3の上面部)のうちゲート電極6の直下に位置する領域を除く部分と、絶縁膜13a及びウェル領域11上面部のうちゲート電極14の直下に位置する領域を除く部分とを除去する。これにより、チャネル領域3上の上部ゲート領域2と、上部ゲート領域2上の絶縁膜31とが形成される。

【0135】

本工程において、上部ゲート領域131及びウェル領域11の除去量(すなわち、半導体基板1における除去深さ)は、例えば10nm〜100nm程度とすることが好ましい。

【0136】

これ以降は、図9(a)〜(c)に示す第2の実施形態に係る方法と同様の工程を経ることにより、半導体装置を作製できる(図12(a)〜(c)参照)。

【0137】

図12(b)に示す工程では、ゲート電極6のうち、ソース及びドレイン領域8の形成時にN型不純物が導入された部分を除去しているが、両導電型不純物の濃度が十分濃く、両導電型不純物間のリーク電流のために整流特性が無視できる場合には、必ずしもゲート電極6の上部を除去しなくてもよい。

【0138】

なお、上記で説明した各層の導電型を、全て反対の導電型にしても第1のトランジスタ70をJFETとして、第2のトランジスタ80をMISFETとして問題なく動作させることができる。

【0139】

以上で説明した本変形例の半導体装置では、JFET(第1のトランジスタ70)において、上部ゲート領域2とソース及びドレイン領域8、及び上部ゲート領域2とシリサイド層9とは、それぞれチャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間している。

【0140】

この構成によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。

【0141】

これに対し、特許文献2に記載された従来の半導体装置では、JFETにおいて、ゲート電極を形成するために、スペーサ端との位置合わせズレを考慮した間隔を取る必要があり、ソース及びドレイン電極とゲート電極との間隔を取る必要もある。

【0142】

このため、本変形例の半導体装置では、特許文献2に記載された従来の半導体装置のJFETと実効ゲート寸法が同じ場合であっても、ゲート電極6のゲート長方向の幅を大幅に縮小することができる。特に、JFETである第1のトランジスタ70をMISFETと同様の寸法で形成することができる。

【0143】

さらに、N型のチャネル領域3はゲート電極6の直下において半導体基板1の上面から離れたところにある。そのため、第1のトランジスタ70においては、半導体基板1の上面近傍にチャネルが形成されるMISFETよりも、同じ動作電流密度で比較した場合の低周波雑音を10分の1以下にすることができる。その結果、アナログ回路等を本変形例のJFETで構成することにより、当該アナログ回路をMISFETで構成する場合と同等程度まで素子面積を縮小することができ、且つMISFETを用いた場合よりも低周波雑音を大きく低減することができる。

【0144】

また、本変形例に係る半導体装置の製造方法では、ゲート電極6、14の形成工程、サイドウォールスペーサ7、15の形成工程、ソース及びドレイン領域8、16の形成工程、各シリサイド層の形成工程等、第1のトランジスタ70の形成工程と第2のトランジスタ80の形成工程とを共通化している。そのため、本実施形態の方法によれば、それぞれのトランジスタを別個の工程により形成するのに比べて半導体装置を安価に製造することができる。

【0145】

また、本変形例に係る方法においても、図5(a)〜(e)、図6(a)〜(c)に示す方法と同様に、ゲート電極6の形成前に上部ゲート領域131を形成するので、上部ゲート領域2を形成するための専用の拡散工程が不要となる。

【0146】

また、本変形例に係る方法によれば、第2の実施形態に係る方法と異なり、ゲート電極6、14を形成用の導電膜118を形成する前に予めP型の上部ゲート領域131を形成している。このため、図11(c)に示す工程で導電膜118にP型不純物を導入する際に製造上のバラツキ等によって、意図しないP型不純物の半導体基板1への拡散が生じた場合であっても、当該拡散による素子特性への影響を第2の実施形態に係る方法に比べて小さくすることができる。

【0147】

(第3の実施形態)

図13は、本発明の第3の実施形態に係る半導体装置を示す断面図である。同図において、図7に示す第2の実施形態に係る半導体装置と同様の部分については同一の符号を付し、その部分の説明は一部簡略化する。

【0148】

図7に示す半導体装置では、第1のトランジスタ70において、上部ゲート領域2上には絶縁膜31を間に挟んでポリシリコン等からなるゲート電極6が形成されていたが、本実施形態の半導体装置では、上部ゲート領域2上にはゲート電極として機能するシリサイド層9aが直接形成されている。このシリサイド層9aは、側方をサイドウォールスペーサ7に囲まれている。また、サイドウォールスペーサ7とシリサイド層9aとで構成される凹部には、層間絶縁膜28が埋め込まれている。

【0149】

この構成の違いに応じて、本実施形態の半導体装置の製造方法では、サイドウォールスペーサ7、ソース及びドレイン領域8、及び上部ゲート領域2の形成後にポリシリコンからなるゲート電極6を除去し、上部ゲート領域2の上面を直接合金化(具体的にはシリサイド化)してシリサイド層9aを形成する。

【0150】

このような構成の違いにより、上部ゲート領域2を配線層の形成直前に形成することができるので、上部ゲート領域2に印加される熱処理の回数等がより少なくなり、上部ゲート領域2中の不純物分布のバラツキを一層少なくすることができる。

【0151】

次に、以上のように構成された本実施形態に係る半導体装置の製造方法について説明する。図14(a)〜(d)、図15(a)〜(c)は、本実施形態の半導体装置の製造方法の一例を示す断面図である。これらの図において、図8(a)〜(d)及び図9(a)〜(c)と同様の部分については同一の符号を付し、その説明を一部簡略化する。

【0152】

まず、図14(a)〜(d)に示す工程では、第2の実施形態に係る半導体装置の製造方法における図8(a)〜(d)に示す工程と同様にして、絶縁膜31を間に挟んでチャネル領域3上にポリシリコン等からなるゲート電極119を形成するとともに、ゲート絶縁膜13を間に挟んでウェル領域11上にポリシリコン等からなるゲート電極14を形成する。ただし、第2の実施形態の方法と異なり、図14(c)に示す工程では、ポリシリコンからなる導電膜118の形成後に、導電膜118のうち第1の素子領域101上に形成された部分に不純物の導入を行わない。

【0153】

次に、図15(a)に示す工程では、イオン注入法等により、P型のHalo注入領域18、N型の低濃度ドレイン領域17をウェル領域11内に形成する。次いで、サイドウォールスペーサ7をゲート電極119の側面上に形成するとともにサイドウォールスペーサ15をゲート電極14の側面上に形成する。続いて、ゲート電極119、14及びサイドウォールスペーサ7、15をマスクとして半導体基板1(チャネル領域3)内にN型不純物をイオン注入することにより、ソース及びドレイン領域8、16をそれぞれ形成する。

【0154】

次に、図15(b)に示す工程では、半導体基板1の上面全体にシリコン酸化膜26等の絶縁膜を形成した後、CMP法等によりゲート電極119、14の上面が露出するまでシリコン酸化膜26の上部を除去する。さらに、第1の素子領域101上に設けられたゲート電極119及び絶縁膜31を除去してチャネル領域3を露出させ、この露出したチャネル領域3の上部にイオン注入法などを用いてP型不純物を導入することで、上部ゲート領域2を形成する。

【0155】

次に、図15(c)に示す工程で、シリコン酸化膜26を除去した後、ゲート電極14の上面上、ソース及びドレイン領域8、16上にシリサイド層9を形成するとともに、上部ゲート領域2上に第1のトランジスタ70のゲート電極として機能するシリサイド層9aを形成する。続いて、半導体基板1の上面全体、及びサイドウォールスペーサ7とシリサイド層9aとで構成された凹部内に層間絶縁膜28を形成した後、ソース及びドレイン領域8上のシリサイド層9又はソース及びドレイン領域16上のシリサイド層9に接続されるコンタクトプラグ27をそれぞれ形成する。その後は図示しないが、公知技術を用いて、表面保護膜、電極接続のための配線層、及び外部接続用端子等を形成することにより、本実施形態の半導体装置を作製することができる。

【0156】

なお、上記で説明した各層の導電型を、全て反対の導電型にしても第1のトランジスタ70をJFETとして問題なく動作させることができる。

【0157】

特許文献2に開示された従来の半導体装置では、上部ゲート領域上に形成されるゲート電極が、スペーサ端との位置合わせズレを考慮した間隔を取るとともに、ゲート電極とソース及びドレイン電極との間隔を取る必要がある。これに対し、本実施形態の半導体装置によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。このため、JFETである第1のトランジスタ70をMISFETと同様な寸法で形成することができる。

【0158】

さらに、N型のチャネル領域3はシリサイド層9aの直下において半導体基板1の上面から離れたところにある。そのため、第1のトランジスタ70においては、半導体基板1の上面近傍にチャネルが形成されるMISFETよりも、同じ動作電流密度で比較した場合の低周波雑音を10分の1以下にすることができる。その結果、アナログ回路等を本実施形態のJFETで構成することにより、当該アナログ回路をMISFETで構成する場合と同等の低周波雑音性能を実現するのに、10分の1以下程度まで回路面積を縮小することができる。

【0159】

また、本実施形態に係る半導体装置の製造方法では、シリサイド層9a、9、42の形成工程、サイドウォールスペーサ7、15の形成工程、ソース及びドレイン領域8、16の形成工程等、第1のトランジスタ70の形成工程と第2のトランジスタ80の形成工程とを共通化している。そのため、本実施形態の方法によれば、それぞれのトランジスタを別個の工程により形成するのに比べて半導体装置を安価に製造することができる。

【0160】

(第4の実施形態)

図16は、本発明の第4の実施形態に係る半導体装置を示す断面図である。同図において、図7に示す第2の実施形態に係る半導体装置と同様の部分については同一の符号を付し、その部分の説明は一部簡略化する。

【0161】

図7に示す第2の実施形態に係る半導体装置では、第1のトランジスタ70において、上部ゲート領域2上に絶縁膜31を間に挟んでP型ポリシリコンからなるゲート電極6が形成され、ウェル領域11上にはゲート絶縁膜13を間に挟んでN型ポリシリコンからなるゲート電極14が形成される。また、ゲート電極6から絶縁膜31を介してN型のチャネル領域3へP型不純物を拡散させることによって上部ゲート領域2が形成される。

【0162】

これに対し、本実施形態の半導体装置では、金属又は導電性の金属化合物からなるゲート電極65が上部ゲート領域2上に直接形成されており、ウェル領域11上にはゲート絶縁膜13を間に挟んで金属又は導電性の金属化合物からなるゲート電極66が形成されている。また、上部ゲート領域2はゲート電極65の形成前にイオン注入等により形成される。ゲート電極65、66は互いに同じ材料で構成されており、例えばタングステン等の金属や金属シリサイドやTiN、TaN等の導電性の金属化合物等で構成される。

【0163】

ゲート絶縁膜13の構成材料は特に限定されないが、ハフニウム酸化物等の高誘電率材料で構成されることが好ましい。

【0164】

また、シリサイド層9はソース及びドレイン領域8、16上に形成されている。しかし、ゲート電極65、66は金属等で構成されているので、ゲート電極65、66上にはシリサイド層は設けられていない。

【0165】

以上の構成により、いわゆるメタルゲート電極を有するJFETを、ゲート長数10nm以下のメタルゲート電極を有するMISFETと同一基板上に混載することができる。

【0166】

次に、以上のように構成された本実施形態に係る半導体装置の製造方法について説明する。

【0167】

図17(a)〜(d)、図18(a)〜(c)は、本実施形態の半導体装置の製造方法の一例を示す断面図である。これらの図において、図8(a)〜(d)及び図9(a)〜(c)、並びに図14(a)〜(d)、図15(a)〜(c)と同様の部分については同一の符号を付し、その説明を一部簡略化する。

【0168】

まず、図17(a)〜(d)に示す工程では、第2の実施形態に係る半導体装置の製造方法における図8(a)〜(d)に示す工程と同様にして、絶縁膜31を間に挟んでチャネル領域3上にポリシリコン等からなるゲート電極119を形成するとともに、ゲート絶縁膜13を間に挟んでウェル領域11上にポリシリコン等からなるゲート電極120を形成する。ただし、第2の実施形態の方法と異なり、図17(c)に示す工程では、ポリシリコンからなる導電膜118の形成後に、導電膜118に不純物の導入を行わない。

【0169】

次に、図18(a)に示す工程では、イオン注入法等により、P型のHalo注入領域18、N型の低濃度ドレイン領域17をウェル領域11内に形成する。次いで、サイドウォールスペーサ7をゲート電極119の側面上に形成するとともにサイドウォールスペーサ15をゲート電極120の側面上に形成する。続いて、ゲート電極119、120及びサイドウォールスペーサ7、15をマスクとして半導体基板1(チャネル領域3)内にN型不純物をイオン注入することにより、ソース及びドレイン領域8、16をそれぞれ形成する。

【0170】

次に、図18(b)に示す工程では、半導体基板1の上面全体にシリコン酸化膜26等の絶縁膜を形成した後、CMP法等によりゲート電極119、120の上面が露出するまでシリコン酸化膜26の上部を除去する。さらに、第1の素子領域101上に設けられたゲート電極119及び絶縁膜31を除去してチャネル領域3を露出させ、この露出したチャネル領域3の上部にイオン注入法などを用いて選択的にP型不純物を導入することで、上部ゲート領域2を形成する。この一方で、ゲート電極120を除去し、第2の素子領域102上にゲート絶縁膜13を露出させる。ゲート電極119とゲート電極120の除去とは、同時に行うことができる。

【0171】

次に、図18(c)に示す工程では、サイドウォールスペーサ7で囲まれた凹部内、及びサイドウォールスペーサ15で囲まれた凹部内に公知の方法により金属又は導電性の金属化合物を埋め込む。次いで、余剰の金属又は導電性の金属化合物をCMP法等により除去した後、シリコン酸化膜26をエッチングにより除去することで、上部ゲート領域2上にゲート電極65を形成するとともに、ゲート絶縁膜13上にゲート電極66を形成する。

【0172】

次に、ソース及びドレイン領域8、16上にシリサイド層9を形成する。続いて、半導体基板1の上面全体にゲート電極65、66を埋め込むように層間絶縁膜28を形成する。次いで、ソース及びドレイン領域8上のシリサイド層9又はソース及びドレイン領域16上のシリサイド層9に接続されるコンタクトプラグ27をそれぞれ形成する。その後は図示しないが、公知技術を用いて、表面保護膜、電極接続のための配線層、及び外部接続用端子等を形成することにより、本実施形態の半導体装置を作製することができる。

【0173】

なお、上記で説明した各層の導電型を、全て反対の導電型にしても第1のトランジスタ70及び第2のトランジスタ80を問題なく動作させることができる。

【0174】

以上で説明した本実施形態の半導体装置では、JFET(第1のトランジスタ70)において、上部ゲート領域2とソース及びドレイン領域8、及び上部ゲート領域2とシリサイド層9とは、それぞれチャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間している。

【0175】

この構成によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。

【0176】

これに対し、特許文献2に記載された従来の半導体装置では、JFETにおいて、ゲート電極を形成するためには、スペーサ端との位置合わせズレを考慮した間隔を取る必要があり、ソース及びドレイン電極とゲート電極との間隔を取る必要もある。

【0177】

このため、本実施形態の半導体装置では、特許文献2に記載された従来の半導体装置のJFETと実効ゲート寸法が同じ場合であっても、ゲート電極6のゲート長方向の幅を大幅に縮小することができる。特に、JFETである第1のトランジスタ70をMISFETと同様の寸法で形成することができる。

【0178】

さらに、N型のチャネル領域3はゲート電極65の直下において半導体基板1の上面から離れたところにある。そのため、第1のトランジスタ70においては、半導体基板1の上面近傍にチャネルが形成されるMISFETよりも、同じ動作電流密度で比較した場合の低周波雑音を10分の1以下にすることができる。その結果、アナログ回路等を本実施形態のJFETで構成することにより、当該アナログ回路をMISFETで構成する場合と同等の低周波雑音性能を実現するのに、10分の1以下程度まで回路面積を縮小することができる。

【0179】

また、本実施形態に係る半導体装置の製造方法では、ゲート電極6、14の形成工程、サイドウォールスペーサ7、15の形成工程、ソース及びドレイン領域8、16の形成工程、ゲート電極65、66の形成工程、シリサイド層9の形成工程等、第1のトランジスタ70の形成工程と第2のトランジスタ80の形成工程とを共通化している。そのため、本実施形態の方法によれば、それぞれのトランジスタを別個の工程により形成するのに比べて安価に半導体装置を製造することができる。

【0180】

−第4の実施形態の変形例−

図19は、本発明の第4の実施形態に係る半導体装置の変形例を示す断面図である。同図において、図16に示す第4の実施形態に係る半導体装置と同様の部分には同一符号を付している。

【0181】

第4の実施形態に係る半導体装置では、第1のトランジスタ70においてP型の上部ゲート領域2と金属等からなるゲート電極65とが直接接しているが、本変形例の半導体装置では、図19に示すように、上部ゲート領域2とゲート電極65とは間に絶縁膜31を挟んで接している。このため、本変形例の半導体装置では、ゲート電極65と上部ゲート領域2とが直流的に絶縁されている。

【0182】

しかしながら、絶縁膜31が容量絶縁膜となり、半導体基板1には容量を介してゲート電極65から所望の電位を与えることができるので、本変形例の半導体装置は、第4の実施形態に係る半導体装置と同様に動作する。

【0183】

以上のような構成によれば、P型の上部ゲート領域2の電位がN型のチャネル領域3の電位より高くなった場合でも、ゲート電極65からチャネル領域3へと大電流が漏れ出ることがなくなるので、回路設計の自由度を大きくすることができる。

【0184】

次に、以上のように構成された本変形例に係る半導体装置の製造方法について説明する。

【0185】

図20(a)〜(d)、図21(a)〜(c)は、本変形例の半導体装置の製造方法の一例を示す工程断面図である。これらの図において、図17(a)〜(d)、図18(a)〜(c)と同様の部分については同一の符号を付し、その説明を一部簡略化する。

【0186】

まず、図20(a)〜(d)、図21(a)に示す工程では、第4の実施形態に係る半導体装置の製造方法における図17(a)〜(d)、図18(a)に示す工程と同様の処理を行う。

【0187】

次に、図21(b)に示す工程では、半導体基板1の上面全体にシリコン酸化膜26等の絶縁膜を形成した後、CMP法等によりゲート電極119、120の上面が露出するまでシリコン酸化膜26の上部を除去する。

【0188】

次いで、第1の素子領域101上のゲート電極119を除去するとともに、第2の素子領域102上のゲート電極120を除去する。この際、絶縁膜31、ゲート絶縁膜13は除去されないので、絶縁膜31及びゲート絶縁膜13は露出することになる。次に、イオン注入法等を用いて絶縁膜31を通してチャネル領域3の上部にP型不純物を選択的に導入することで、上部ゲート領域2を形成する。

【0189】

次に、図21(c)に示す工程では、ゲート電極119、120が形成されていた領域、すなわちサイドウォールスペーサ7で囲まれた凹部内、及びサイドウォールスペーサ15で囲まれた凹部内に、公知の方法により金属又は導電性の金属化合物を埋め込む。次いで、余剰の金属又は導電性の金属化合物及びシリコン酸化膜26を除去することで、絶縁膜31上にゲート電極65を形成するとともに、ゲート絶縁膜13上にゲート電極66を形成する。

【0190】

次に、ソース及びドレイン領域8、16上にシリサイド層9を形成する。続いて、半導体基板1の上面全体にゲート電極65、66を埋め込むように層間絶縁膜28を形成する。次いで、ソース及びドレイン領域8上のシリサイド層9又はソース及びドレイン領域16上のシリサイド層9に接続されるコンタクトプラグ27をそれぞれ形成する。その後は図示しないが、公知技術を用いて、表面保護膜、電極接続のための配線層、及び外部接続用端子等を形成することにより、本変形例の半導体装置を作製することができる。

【0191】

なお、上記で説明した各層の導電型を、全て反対の導電型にしても第1のトランジスタ70及び第2のトランジスタ80を問題なく動作させることができる。

【0192】

以上で説明した本変形例の半導体装置では、JFET(第1のトランジスタ70)において、上部ゲート領域2とソース及びドレイン領域8、及び上部ゲート領域2とシリサイド層9とは、それぞれチャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間している。

【0193】

この構成によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。

【0194】

以上で説明した本変形例の半導体装置では、JFET(第1のトランジスタ70)において、上部ゲート領域2とソース及びドレイン領域8、及び上部ゲート領域2とシリサイド層9とは、それぞれチャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間している。

【0195】

この構成によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。

【0196】

これに対し、特許文献2に記載された従来の半導体装置では、JFETにおいて、ゲート電極を形成するために、スペーサ端との位置合わせズレを考慮した間隔を取る必要があり、ソース及びドレイン電極とゲート電極との間隔を取る必要もある。

【0197】

このため、本変形例の半導体装置では、特許文献2に記載された従来の半導体装置のJFETと実効ゲート寸法が同じ場合であっても、ゲート電極6のゲート長方向の幅を大幅に縮小することができる。

【0198】

特に、JFETである第1のトランジスタ70をMISFETと同様の寸法で形成することができる。

【0199】

さらに、N型のチャネル領域3はゲート電極65の直下において半導体基板1の上面から離れたところにある。そのため、第1のトランジスタ70においては、半導体基板1の上面近傍にチャネルが形成されるMISFETよりも、同じ動作電流密度で比較した場合の低周波雑音を10分の1以下にすることができる。その結果、アナログ回路等を本変形例のJFETで構成することにより、当該アナログ回路をMISFETで構成する場合と同等の低周波雑音性能を実現するのに、10分の1以下程度まで回路面積を縮小することができる。

【0200】

また、本変形例の半導体装置において、上述のJFETと、論理回路等に用いられるMISFET(第2のトランジスタ80)とが同一の半導体基板1上に形成される場合、チップ全体の面積を従来技術に比べて大幅に縮小できる。また、JFETとMISFETとが共通の工程で形成できる構成となっているので、両素子を別々に形成する場合に比べて製造コストを大幅に低減することができる。

【0201】

したがって、低周波雑音のアナログ回路及び論理回路を混載した半導体装置をより安価に、かつより小さい面積で実現することができる。

【0202】

本発明は、以上で説明した実施形態及びその変形例に限定されず、本発明の趣旨を逸脱しない範囲でこれらの半導体装置の構成を変更したものも含む。例えば、半導体基板1上にMISFET(第2のトランジスタ80)が形成されず、上述のJFET(第1のトランジスタ70)で構成された回路のみが設けられていてもよい。この場合でも、従来の半導体装置に比べて低周波雑音が低減され、且つ面積が小さいという効果を発揮することができる。

【0203】

また、各実施形態及びそれらの変形例に係る半導体装置では、ソース及びドレイン領域8、16等は半導体基板1内にイオン注入等によって不純物を導入することで形成されているが、不純物がin-situドーピングされた半導体層をCVD法等によって形成することで、ソース及びドレイン領域等を形成してもよい。

【0204】

また、本発明の趣旨を逸脱しない範囲で各実施形態及びそれらの変形例に係る半導体装置の構成要素を任意に組み合わせてもよい。

【産業上の利用可能性】

【0205】

本発明の半導体装置及びその製造方法は、アナログ回路と論理回路とを混載したLSI等に適用され、当該LSIは種々の電子機器に用いられる。

【符号の説明】

【0206】

1 半導体基板

1a 基板部分

2 上部ゲート領域

3 チャネル領域

4 下部ゲート領域

5、12 N型埋め込み領域

6、14、119、120 ゲート電極

7、15 サイドウォールスペーサ

8、16 ソース及びドレイン領域

9、9a、19、40、42 シリサイド層

11 ウェル領域

13 ゲート絶縁膜

13a、31 絶縁膜

17 低濃度ドレイン領域

18 Halo注入領域

21、22a、22b 素子分離領域

26 シリコン酸化膜

27 コンタクトプラグ

28 層間絶縁膜

65、66 ゲート電極

70 第1のトランジスタ

80 第2のトランジスタ

101 第1の素子領域

102 第2の素子領域

117、118 導電膜

131、131’、131'' 上部ゲート領域

【技術分野】

【0001】

本明細書に記載された技術は、半導体装置及びその製造方法に係り、特に、微小信号を増幅するアナログ回路、又はアナログ回路とデジタル回路等との混載LSI等として用いられる半導体装置及びその製造方法に関するものである。

【背景技術】

【0002】

従来、アナログ回路やLSIに用いられる半導体装置は、半導体基板上に絶縁膜を介してゲート電極が形成され、半導体基板の上面近傍のうちゲート電極下に位置する部分にチャネルが形成される構成、すなわちmetal-inasulator-semiconductor(MIS)構造を有していた。

【0003】

このような構成を有する半導体装置について、図面を参照しながら以下に説明する(例えば、特許文献1参照)。

【0004】

図22は、従来の半導体装置を示す断面図である。同図において、従来の半導体装置は、半導体基板200上にゲート絶縁膜201を挟んで形成されたゲート電極202と、半導体基板200のうちゲート電極202の両端部の下に位置する領域にそれぞれ形成されたlightly doped drain(LDD)領域203と、半導体基板200のうちゲート電極202の両側方に位置する領域であってLDD領域203の外側に形成されたソース及びドレイン領域204とを備えている。

【0005】

半導体基板200の上面部分のうちゲート電極202の直下に位置し、2つのLDD領域203に挟まれた領域にチャネルが形成される。

【0006】

ここで、微細なサブミクロンチャネルを有する半導体装置では、一般的に短チャネル効果といわれる閾値電圧の低下が顕著になる。このため、閾値電圧の低下を防止する目的で、LDD領域203に隣接するチャネルの一部またはチャネルの下部に、Halo注入領域205と呼ばれる、チャネル領域と同一導電型でチャネル領域よりも不純物濃度が濃い領域を形成することが多い。

【0007】

しかしながら、Halo注入領域205を形成する場合、電流ミラー回路などのアナログ回路の特性に影響を及ぼすアーリー電圧の低下が問題となる。そのため、従来はHalo注入領域205を設けない半導体装置でアナログ回路を構成することで、アーリー電圧の低下を抑制していた。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特表2003−509863号公報

【特許文献2】特開平03−142843号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、従来の半導体装置である表面ゲート型電界効果トランジスタ(具体的にはMISFET)においては、チャネルが半導体基板の上面近くに形成される。このため、従来の半導体装置では、半導体基板とゲ−ト酸化膜との間に生じる界面準位によって電子の捕獲や放出が起こり、その結果、低周波雑音が大きくなりやすい。そこで、素子面積当りの電流密度の増加を抑制して雑音を低減しようとすると、微小な電気信号を増幅するようなアナログ回路に従来の半導体装置を用いた場合、素子面積を大きくしなければならず、ひいてはチップ面積が増大するという不具合が生じる。

【0010】

一方、低周波雑音が小さい素子として接合型電界効果トランジスタが知られているが、接合型電界効果トランジスタは素子面積が比較的大きい。例えば、ゲートがPN接合でなく、ショットキー接合を用いる点で、接合型電界効果トランジスタの一種と考えられるMESFET(Metal-Semiconductor Field Effect Transistor)を縮小化した従来例として、特許文献2に開示された構成があるが、半導体基板上面における実効ゲート寸法(実際にゲートとして機能する部分の寸法)は小さいものの、ゲート電極自体の平面寸法は大きく、ゲート電極とソース及びドレイン電極との間隔を確保すると素子としての面積縮小効果は小さくなる。

【0011】

また、この従来例では、接合型電界効果トランジスタの製造工程と、論理回路を構成する表面ゲート型電界効果トランジスタの製造工程とで共通化できる工程が少ないので、アナログ回路と論理回路とを混載する場合には製造コストが増大するおそれがある。

【0012】

そこで、本発明は、上記の課題に鑑みて、PN接合型電界効果トランジスタ(JFET)において、低周波雑音が低減されるとともに、素子面積の小さい半導体装置及びその製造方法を製造コストを増大させずに提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明の一例に係る半導体装置は、半導体基板における第1の素子領域上に設けられたJFETを備えた半導体装置であって、前記JFETは、前記半導体基板内に形成された第1導電型の下部ゲート領域と、前記下部ゲート領域上に形成された第2導電型のチャネル領域と、前記チャネル領域とPN接合を形成するように前記チャネル領域上に形成された第1導電型の上部ゲート領域と、前記下部ゲート領域上であって前記チャネル領域の両側に位置する第2導電型の第1のソース及びドレイン領域と、前記上部ゲート領域上に形成された第1のゲート電極と、前記第1のゲート電極の両側面上に形成された第1のサイドウォールスペーサとを有しており、前記上部ゲート領域と前記第1のソース及びドレイン領域とは、前記チャネル領域のうち前記第1のサイドウォールスペーサの下に位置する部分を挟んで互いに離間しており、前記第1のソース及びドレイン領域は、ゲート長方向における前記第1のゲート電極の両側方であって前記第1のサイドウォールスペーサの外側を含む領域に形成されている。

【0014】

この構成によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。また、ゲート電極を形成する際やソース及びドレイン領域を形成する際に位置合わせズレを考慮したマージンを取る必要がないので、従来の半導体装置に比べてJFETで構成された回路の面積を大幅に縮小することができる。また、上部ゲート領域がチャネル領域と第1のゲート電極との間に設けられているので、半導体基板の上面近傍にチャネルが形成されるMISFETよりも同じ動作電流密度で比較した場合の低周波雑音を低減することができる。このように、当該半導体装置によれば、低周波雑音が低減され、MISFETと同程度まで素子面積が縮小できるので、アナログ回路等に好ましく用いることができる。

【0015】

また、前記半導体基板における第2の素子領域上に設けられたMISFETをさらに備え、前記MISFETは、前記半導体基板内に形成された第1導電型の半導体領域と、前記半導体領域上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された第2のゲート電極と、前記第2のゲート電極の両側面上に形成された第2のサイドウォールスペーサと、ゲート長方向における前記第2のゲート電極の両側方に位置する領域に形成された第2導電型の第2のソース及びドレイン領域とを有していてもよい。

【0016】

この場合、JFETの素子面積を縮小できることにより、半導体装置全体の面積を縮小することができる。さらに、JFETとMISFETの製造工程の一部を共通化することができるので、JFETで構成された回路とMISFETで構成された回路との混載LSIを、両素子を別々に作製する場合に比べて低コストで製造することができる。

【0017】

また、本発明の半導体基板の製造方法は、第1の素子領域上に設けられたJFETを備えた半導体装置の製造方法であって、前記第1の素子領域において第1導電型の下部ゲート領域を形成する工程(a)と、前記第1の素子領域において前記下部ゲート領域の上に第2導電型のチャネル領域を形成する工程(b)と、前記第1の素子領域において、第1導電型の不純物を導入することによって前記チャネル領域上に、前記チャネル領域とPN接合を形成する第1導電型の上部ゲート領域を形成する工程(c)と、前記チャネル領域上に第1のゲート電極を形成する工程(d)と、前記第1のゲート電極の両側面上に第1のサイドウォールスペーサを形成する工程(e)と、前記チャネル領域のうち、ゲート長方向における前記第1のゲート電極の両側方であって前記第1のサイドウォールスペーサの外側を含む領域に、前記上部ゲート領域と離間した第2導電型の第1のソース及びドレイン領域を形成する工程(f)とを備えている。

【0018】

この方法によれば、工程(f)でチャネル領域内に第1のソース及びドレイン領域を自己整合的に形成することができる。このため、第1のソース及びドレイン領域を形成する際にマージンを取る必要がなく、素子面積が縮小されたJFETを形成することができる。また、チャネル領域上に上部ゲート領域を形成するので、チャネル領域を半導体基板の上面から離れた位置に形成することができ、低周波雑音が低減されたJFETを作製することが可能となる。

【0019】

また、このJFETとMISFETとを混載する場合には、第1のソース及びドレイン領域と第2のソース及びドレイン領域とを同一工程で形成する等、JFETとMISFETとを共通の工程により作製することができるので、JFETとMISFETとを別々に形成する場合に比べて製造コストを低減することができる。

【発明の効果】

【0020】

本発明の半導体装置及びその製造方法によれば、アナログ回路等を構成するJFETの素子面積を低減することができる。さらに、JFETで構成された回路とMISFETで構成された回路との混載を容易にし、製造コストの低減も併せて図ることができる。

【図面の簡単な説明】

【0021】

【図1】図1は、本発明の第1の実施形態に係る半導体装置を示す断面図である。

【図2】図2(a)〜(e)は、第1の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図3】図3(a)〜(c)は、第1の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図4】図4は、本発明の第1の実施形態に係る半導体装置の変形例を示す断面図である。

【図5】図5(a)〜(e)は、第1の実施形態に係る半導体装置の変形例の製造方法の一例を示す断面図である。

【図6】図6(a)〜(c)は、第1の実施形態に係る半導体装置の変形例の製造方法の一例を示す断面図である。

【図7】図7は、本発明の第2の実施形態に係る半導体装置を示す断面図である。

【図8】図8(a)〜(d)は、第2の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図9】図9(a)〜(c)は、第2の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図10】図10は、本発明の第2の実施形態に係る半導体装置の変形例を示す断面図である。

【図11】図11(a)〜(d)は、第2の実施形態に係る半導体装置の変形例の製造方法の一例を示す断面図である。

【図12】図12(a)〜(c)は、第2の実施形態に係る半導体装置の変形例の製造方法の一例を示す断面図である。

【図13】図13は、本発明の第3の実施形態に係る半導体装置を示す断面図である。

【図14】図14(a)〜(d)は、第3の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図15】図15(a)〜(c)は、第3の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図16】図16は、本発明の第4の実施形態に係る半導体装置を示す断面図である。

【図17】図17(a)〜(d)は、第4の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図18】図18(a)〜(c)は、第4の実施形態に係る半導体装置の製造方法の一例を示す断面図である。

【図19】図19は、本発明の第4の実施形態に係る半導体装置の変形例を示す断面図である。

【図20】図20(a)〜(d)は、第4の実施形態に係る半導体装置の変形例の製造方法の一例を示す断面図である。

【図21】図21(a)〜(c)は、第4の実施形態に係る半導体装置の変形例の製造方法の一例を示す断面図である。

【図22】図22は、従来の半導体装置を示す断面図である。

【発明を実施するための形態】

【0022】

以下、本発明の実施形態における半導体装置及びその製造方法について、図面を参照しながら説明する。

【0023】

(第1の実施形態)

−半導体装置の構成−

図1は、本発明の第1の実施形態に係る半導体装置を示す断面図である。同図に示すように、本実施形態の半導体装置においては、例えばシリコン等からなる半導体基板1に、第1の素子領域101と第2の素子領域102とが形成されている。第1の素子領域101上にはJFETである第1のトランジスタ70が形成され、第2の素子領域102上にはMISFETである第2のトランジスタ80が形成されている。

【0024】

なお、本明細書において、第1の素子領域101とは、半導体基板1の上部であって、第1のトランジスタ70を形成するための領域内に形成された部分を指し、第2の素子領域102とは、半導体基板1の上部であって、第2のトランジスタ80を形成するための領域内に形成された部分を指すものとする。

【0025】

半導体基板1内には、P型の基板部分1a、基板部分1a上のN型埋め込み領域5、N型埋め込み領域5上のP型の下部ゲート領域4、下部ゲート領域4上のN型のチャネル領域3、チャネル領域3上のP型の上部ゲート領域2、及び下部ゲート領域4上のN型のソース及びドレイン領域8が形成されている。

【0026】

第1のトランジスタ70は、第1の素子領域101内にそれぞれ形成された上述の下部ゲート領域4、チャネル領域3、上部ゲート領域2、及びソース及びドレイン領域8と、上部ゲート領域2上に形成されたP型ポリシリコン等からなるゲート電極6と、ソース及びドレイン領域8上とゲート電極6上とにそれぞれ形成されたシリサイド層9、40と、ゲート電極6及びシリサイド層9の側面上に形成されたサイドウォールスペーサ7とを有している。

【0027】

ゲート電極6のゲート長方向の幅は、例えば数10nm〜数μm程度である。また、サイドウォールスペーサ7は、シリコン酸化物等の絶縁体で構成され、そのゲート長方向の幅は、例えば数10nm〜100nm程度である。

【0028】

ソース及びドレイン領域8はゲート長方向においてゲート電極6両側方であって、サイドウォールスペーサ7の外側を含む領域に形成されている。ソース及びドレイン領域8のN型不純物濃度は、1×1018atoms/cm3〜1×1021atoms/cm3程度である。各々に印加される電圧に応じて、ソース及びドレイン領域8の一方がソース領域となり、他方がドレイン領域となる。また、チャネル領域3は2つのソース及びドレイン領域8に挟まれており、上部ゲート領域2の側面及び底面はチャネル領域3に囲まれている。

【0029】

チャネル領域3に含まれるN型不純物の濃度はソース及びドレイン領域8のN型不純物の濃度よりも低く、例えば1×1016atoms/cm3〜1×1019atoms/cm3程度である。

【0030】

上部ゲート領域2は、チャネル領域3とPN接合するようにチャネル領域3上に形成されている。上部ゲート領域2に含まれるP型不純物の濃度は、例えば1×1019atoms/cm3〜1×1021atoms/cm3程度である。

【0031】

また、半導体基板1の第2の素子領域102内には、基板部分1a上のN型埋め込み領域12、N型埋め込み領域12上のP型のウェル領域(半導体領域)11、ウェル領域11上のN型のソース及びドレイン領域16、N型の低濃度ドレイン領域17、低濃度ドレイン領域17の一部を覆うP型のHalo注入領域18がそれぞれ形成されている。

【0032】

第2のトランジスタ80は、ウェル領域11上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成されたポリシリコン等からなるゲート電極14と、上述のソース及びドレイン領域16、低濃度ドレイン領域17、及びHalo注入領域18と、ソース及びドレイン領域16上とゲート電極14上とにそれぞれ形成されたシリサイド層19、42と、ゲート電極14の側面上に形成されたサイドウォールスペーサ15とを有している。

【0033】

ゲート電極14のゲート長方向の幅(すなわちゲート長)は、例えば数10nm〜数μm程度である。ゲート電極14は、N型不純物を含んでいてもよい。ゲート電極14とゲート電極6とはポリシリコン等、互いに同じ材料で構成されている。

【0034】

また、後述のように、サイドウォールスペーサ15とサイドウォールスペーサ7とは同一の絶縁膜を加工することで形成される。このため、サイドウォールスペーサ15の構成材料は、サイドウォールスペーサ7と同様である。また、サイドウォールスペーサ7、15のゲート長方向断面の形状は共に上方から下方に向かって厚みがやや厚くなるI字型である。

【0035】

ソース及びドレイン領域16は、ゲート長方向においてゲート電極14の両側方であって、サイドウォールスペーサ15の外側を含む領域に形成されており、そのN型不純物濃度は1×1018atoms/cm3〜1×1021atoms/cm3程度である。後述するように、ソース及びドレイン領域8、16を同時に形成する場合、ソース及びドレイン領域8、16の深さ及び不純物濃度とはほぼ等しくなる。各々に印加される電圧に応じて、ソース及びドレイン領域16の一方がソース領域となり、他方がドレイン領域となる。

【0036】

低濃度ドレイン領域17は、ゲート電極14の両側方下に位置し、各ソース及びドレイン領域16の内側(ゲート電極14側)側面に接している。低濃度ドレイン領域17は、ソース及びドレイン領域16よりも低濃度でN型不純物を含んでおり、その不純物濃度は例えば1×1017atoms/cm3〜1×1019atoms/cm3程度である。

【0037】

Halo注入領域18は、いわゆる短チャネル効果を防止するために設けられており、ゲート電極14直下のチャネル領域と同じ導電型で、且つチャネル領域(及びウェル領域11)よりも高濃度のP型不純物を含んでいる。このHalo注入領域18は、各低濃度ドレイン領域17の内側面(ゲート電極側面)を覆うように設けられている。Halo注入領域18が含むP型不純物の濃度は例えば1×1017atoms/cm3〜1×1019atoms/cm3程度である。

【0038】

半導体基板1の第1の素子領域101と第2の素子領域102との間は、基板部分1aの上部に達する深い素子分離領域21によって分離されている。また、第1の素子領域101及び第2の素子領域102は、それぞれ他の同じ素子(図示せず)と浅い素子分離領域22a、22bにより分離されている。深い素子分離領域21及び浅い素子分離領域22a、22bはそれぞれ半導体基板1に形成された溝内に埋め込まれたシリコン酸化物等により構成されている。

【0039】

また、半導体基板1の全面上には層間絶縁膜28が形成されている。シリサイド層9、19上(ソース及びドレイン領域8、16上)には、層間絶縁膜28を貫通するコンタクトプラグ27が形成されている。

【0040】

なお、以上で説明した半導体装置において、N型埋め込み領域5、12は、第1のトランジスタ70及び第2のトランジスタ80をそれぞれ基板部分1aと電気的に分離するためのものである。上述の素子分離領域21は、必ずしもN型埋め込み領域5を貫通していなくてもよい。また、N型埋め込み領域5、12を同時に形成してもよい。さらに、各シリサイド層9、19及び第2の素子領域102のHalo注入領域18は必ずしも形成されていなくてもよい。

【0041】

第1のトランジスタ70では、通常のアナログ回路で使用する場合、特に、上部ゲート領域2、及び下部ゲート領域4とチャネル領域3のPN接合間には、常に逆バイアスになるよう電圧が与えられており、ゲート電極6にはほとんど電流が流れない。さらにゲート−ソース間に所定の負の電圧を印加して、上部ゲート領域2、及び下部ゲート領域4に挟まれたチャネル領域3を空乏化することにより、ソース及びドレイン領域8間に所定の電圧を印加しても電流が流れなくなり、半導体装置はオフ状態となる。

【0042】

一方、ゲート−ソース間に負の電圧で、かつ、半導体装置をオフ状態にする所定のゲート電圧よりも大きい電圧、すなわち絶対値としては上記のオフ状態にするための所定のゲート電圧より小さい電圧、をゲート電極6に印加すると、ソース及びドレイン領域8の一方(ドレイン領域)から他方(ソース領域)へとチャネル領域3を介して電流が流れ、オン状態となる。

【0043】

第2のトランジスタ80では、2つのソース及びドレイン領域16間に所定の電圧を印加した状態でゲート電極14に正の電圧を印加することでオン状態となり、ソース及びドレイン領域16間に電流が流れる。ウェル領域11のうち、2つのソース及びドレイン領域16に挟まれた、ゲート電極14の直下に位置する部分はキャリア(ここでは電子)が走行するチャネル領域となる。

【0044】

−半導体装置の製造方法−

次に、以上のように構成された本実施形態に係る半導体装置の製造方法について説明する。図2(a)〜(e)、図3(a)〜(c)は、本実施形態の半導体装置の製造方法の一例を示す断面図である。

【0045】

まず、図2(a)に示す工程では、P型シリコン等からなる半導体基板1の所定の領域にそれぞれ浅い溝及び深い溝を形成する。次いで、第1の素子領域101と第2の素子領域102との間に形成された深い溝内にシリコン酸化物等からなる誘電体膜を埋め込んで素子分離領域21を形成するとともに、浅い溝内にシリコン酸化物等からなる誘電体膜を埋め込んで素子分離領域22a、22bを形成する。これらの誘電体膜は堆積後、chemical mechanical polishing(CMP)法等の方法によって平坦化される。

【0046】

次に、図2(b)に示す工程では、イオン注入等の公知の方法によって半導体基板1の第1の素子領域101にN型不純物を導入することでN型埋め込み領域5を形成した後、N型埋め込み領域5の上部にP型不純物を導入することで下部ゲート領域4を形成する。また、半導体基板1の第2の素子領域102にN型埋め込み領域12を形成した後、N型埋め込み領域12の上部にP型不純物を導入することで、P型のウェル領域11を形成する。

【0047】

本工程で、N型埋め込み領域5とN型埋め込み領域12とは同時に形成することもでき、下部ゲート領域4とウェル領域11とは同時に形成することもできる。

【0048】

なお、半導体基板1のうちN型埋め込み領域5、12の下に位置する領域は、便宜的に基板部分1aと呼ぶものとする。

【0049】

次いで、イオン注入等によって下部ゲート領域4の上部に選択的にN型不純物を導入することで、N型のチャネル領域3を形成する。

【0050】

次に、図2(c)に示す工程では、chemichal vapor deposition(CVD)法等を用いて、半導体基板1の上面全体にシリコン酸化物等からなり、膜厚が例えば0.数nm〜数nm程度の絶縁膜13aと、ポリシリコン等の導電体からなり、膜厚が例えば数nm〜数10nm程度の導電膜117とを順次形成する。次いで、公知のエッチング等により絶縁膜13a及び導電膜117のうち第1の素子領域101上に形成された部分を除去し、絶縁膜13a及び導電膜117を半導体基板1の第2の素子領域102上に残す。

【0051】

次に、図2(d)に示す工程では、CVD法等により、再びポリシリコン等からなり、膜厚が数10nm〜数100nm程度の導電膜118を半導体基板1の上面上及び導電膜117上に形成する。その後、イオン注入等により、導電膜118のうち、第1の素子領域101上に形成された部分にはP型不純物を導入し、導電膜117、118のうち第2の素子領域102上に形成された部分にはN型不純物を導入する(図示せず)。

【0052】

次に、図2(e)に示す工程では、ドライエッチング法などにより、第1の素子領域101上において導電膜118を、第2の素子領域102上において導電膜117、118及び絶縁膜13aをそれぞれ選択的に除去することで、チャネル領域3上にゲート電極6を形成するとともに、ウェル領域11上にゲート絶縁膜13及びゲート電極14を形成する。

【0053】

次に、図3(a)に示す工程では、第2の素子領域102(ウェル領域11)に必要に応じてゲート電極14をマスクとして用いた不純物イオンの注入を行うことにより、P型のHalo注入領域18、N型の低濃度ドレイン領域17をそれぞれ形成する。続いて、半導体基板1上及びゲート電極6、14上にシリコン窒化膜等を形成してから当該シリコン窒化膜等を異方性エッチングによりエッチバックすることにより、サイドウォールスペーサ7をゲート電極6の両側面上に形成するとともに、サイドウォールスペーサ15をゲート電極14の両側面上に形成する。

【0054】

続いて、ゲート電極6、14及びサイドウォールスペーサ7、15をマスクとして半導体基板1内にN型不純物をイオン注入する。これにより、半導体基板1(具体的にはチャネル領域3)のうち、ゲート電極6の両側方であってサイドウォールスペーサ7の外側を含む領域にソース及びドレイン領域8を形成するとともに、半導体基板1(具体的には低濃度ドレイン領域17及びウェル領域11)のうち、ゲート電極14の両側方であってサイドウォールスペーサ15の外側を含む領域にソース及びドレイン領域16を形成する。

【0055】

次に、熱処理を行って半導体基板1内及びゲート電極6、14内に含まれる不純物を活性化する。この活性化の際に、ゲート電極6に接触したチャネル領域3の上面近傍部分に、ゲート電極6に添加されたP型不純物が拡散されることによって、P型の上部ゲート領域2が形成される。チャネル領域3へのP型不純物の拡散は、ゲート電極6の形成後、別個に行ってもよい。

【0056】

次に、図3(b)に示す工程で、半導体基板1上にゲート電極6、14を埋め込むように絶縁膜(シリコン酸化膜26)を形成した後、公知の方法によってゲート電極6、14の上面が露出するまでシリコン酸化膜26を研磨する。

【0057】

さらに、第2の素子領域102の上方のみをマスク(図示せず)で覆った状態でゲート電極6の上部を選択的に除去した後、当該マスク及び残存するシリコン酸化膜26を除去する。ここで、露出したゲート電極6の上部には図3(a)に示す工程でソース及びドレイン領域8、16の形成時にN型不純物が導入されるので、必要に応じて当該部分を除去することで、上部ゲート電極3に安定して電圧を印加することができるようになる。

【0058】

次に、図3(c)に示す工程で、ゲート電極6、14上にシリサイド層40、42をそれぞれ形成するとともに、ソース及びドレイン領域8、16上にシリサイド層9、19をそれぞれ形成する。次いで、半導体基板1の上面全体に層間絶縁膜28を形成した後、層間絶縁膜28を貫通し、シリサイド層9、19にそれぞれ接続するコンタクトプラグ27を形成する。その後は図示しないが、周知技術を用いて、表面保護膜、電極等との接続を取るための配線層、及び外部接続用端子等を形成することにより、半導体装置を作製できる。

【0059】

なお、図2(c)、(d)に示す工程において、絶縁膜13aを形成した直後に絶縁膜13aの一部を選択的に除去する際には、絶縁膜13a上に保護膜として導電膜117を設ける例を説明したが、エッチングによるダメージがゲート絶縁膜となる絶縁膜13aの信頼性に影響を与えない場合には、導電膜117を設けなくてもよい。この場合、ゲート電極6、14形成用のポリシリコンを第1の素子領域101上及び第2の素子領域102上に堆積等することによってゲート電極6、14を同時に形成できる。

【0060】

また、図3(b)に示す工程では、上記したように、ゲート電極6のうち、ソース及びドレイン領域8の形成時にN型不純物が導入された部分を除去しているが、両導電型不純物の濃度が十分濃く、両導電型不純物間のリーク電流のために整流特性が無視できる場合には、必ずしもゲート電極6の上部を除去しなくてもよい。

【0061】

なお、上記で説明した各層の導電型を、全て反対の導電型にしても第1のトランジスタ70をJFETとして、第2のトランジスタ80をMISFETとして問題なく動作させることができる。

【0062】

−本実施形態の半導体装置及び製造方法の効果−

以上で説明した本実施形態の半導体装置では、JFET(第1のトランジスタ70)において、上部ゲート領域2とソース及びドレイン領域8、及び上部ゲート領域2とシリサイド層9とは、それぞれチャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間している。

【0063】

この構成によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。また、ゲート電極6が平面的に見てソース及びドレイン領域8と重なることがない。なお、サイドウォールスペーサ7の断面形状はI字状であれば好ましいが、平面的に見てソース及びドレイン領域8と大きく重なっていなければ、L字状等であってもよい。

【0064】

これに対し、特許文献2に記載された従来の半導体装置では、JFETにおいて、ゲート電極を形成するために、スペーサ端との位置合わせズレを考慮した間隔を取る必要があり、ソース及びドレイン電極とゲート電極との間隔を取る必要もある。

【0065】

このため、本実施形態の半導体装置では、特許文献2に記載された従来の半導体装置のJFETと実効ゲート寸法が同じ場合であっても、ゲート電極6のゲート長方向の幅を大幅に縮小することができる。特に、JFETである第1のトランジスタ70をMISFETと同様の寸法で形成することができる。

【0066】

さらに、N型のチャネル領域3はゲート電極6の直下において半導体基板1の上面から離れたところにある。そのため、第1のトランジスタ70においては、半導体基板1の上面近傍にチャネルが形成されるMISFETよりも、同じ動作電流密度で比較した場合の低周波雑音を10分の1以下にすることができる。その結果、微小な電気信号を扱うアナログ回路等を本実施形態のJFETで構成することにより、当該アナログ回路をMISFETで構成する場合と同等の低周波雑音性能を実現するのに、10分の1以下程度まで回路面積を縮小することができる。このように、アナログ回路と論理回路等を半導体基板上に混載した半導体装置全体のチップサイズを従来よりも大幅に縮小することができる。

【0067】

また、本実施形態の半導体装置において、上述のJFETと、論理回路等に用いられるMISFET(第2のトランジスタ80)とが同一の半導体基板1上に形成される場合、チップ全体の面積を従来技術に比べて大幅に縮小できる。また、後述のように、JFETとMISFETとが共通の工程で形成できる構成となっているので、両素子を別々に形成する場合に比べて製造コストを大幅に低減することができる。

【0068】

また、本実施形態に係る半導体装置の製造方法では、ゲート電極6、14の形成工程、サイドウォールスペーサ7、15の形成工程、ソース及びドレイン領域8、16の形成工程、各シリサイド層の形成工程等、第1のトランジスタ70の形成工程と第2のトランジスタ80の形成工程とを共通化している。そのため、本実施形態の方法によれば、それぞれのトランジスタを別個の工程により形成するのに比べて半導体装置を安価に製造することができる。

【0069】

また、本実施形態の方法によれば、P型の上部ゲート領域2を形成するための専用の工程が不要となることによっても工程数の削減が図られている。

【0070】

以上のように、本実施形態の半導体装置及びその製造方法によれば、低周波雑音が低減されたアナログ回路を小さい面積で作製できるとともに、アナログ回路と論理回路とが混載された半導体装置をより安価に、且つ、より小さい面積で実現することができる。

【0071】

−第1の実施形態の変形例−

図4は、本発明の第1の実施形態に係る半導体装置の変形例を示す断面図である。同図において、図1に示す第1の実施形態に係る半導体装置と同様の部分には同一符号を付している。

【0072】

第1の実施形態に係る半導体装置では、上述のように、第1の素子領域101において、N型のチャネル領域3上にP型のゲート電極6を形成し、このゲート電極6からチャネル領域3へP型不純物を拡散させることによってチャネル領域3の上部にP型の上部ゲート領域2が形成される。

【0073】

これに対し、本変形例に係る半導体装置では、半導体基板1の第1の素子領域101の上面部分に予めP型の上部ゲート領域131(図5(b)参照)を形成しておき、ゲート電極6の形成の際に上部ゲート領域131の一部を除去することで、上部ゲート領域2が形成される。

【0074】

このため、図4に示すように、本変形例に係る半導体装置では、第1の素子領域101上に形成された第1のトランジスタ70において、ゲート電極6と上部ゲート領域2との界面の位置よりもサイドウォールスペーサ7と半導体基板1(チャネル領域3)との界面の位置の方が低くなっている。また、第2の素子領域102上に形成された第2のトランジスタ80において、ゲート絶縁膜13とウェル領域11との界面の位置よりもサイドウォールスペーサ15と半導体基板1(低濃度ドレイン領域17)との界面の位置の方が低くなっている。なお、上部ゲート領域2の厚さは数10nm以下程度であり、上部ゲート領域2は、単結晶シリコン等からなる半導体基板1と、ゲート電極6を構成するポリシリコン膜との界面の上下両側に広がっている。

【0075】

次に、以上のように構成された本変形例に係る半導体装置の製造方法について説明する。図5(a)〜(e)、図6(a)〜(c)は、本変形例に係る半導体装置の製造方法の一例を示す断面図である。

【0076】

まず、図5(a)に示す工程では、図2(a)に示す工程と同様にして、半導体基板1内に素子分離領域21、22a、22bを形成する。

【0077】

次に、図5(b)に示す工程では、イオン注入等の方法により半導体基板1内にN型埋め込み領域5、下部ゲート領域4、N型埋め込み領域12、及びP型のウェル領域11を形成する。

【0078】

次いで、イオン注入等によって下部ゲート領域4の上部に選択的にN型不純物を導入することで、N型のチャネル領域3を形成する。続いて、P型不純物のイオン注入により、チャネル領域3の上部に、P型の上部ゲート領域131を形成する。

【0079】

次に、図5(c)に示す工程では、図2(c)に示す工程と同様の方法により、半導体基板1の上面全体にシリコン酸化物等からなり、膜厚が例えば0.数nm〜数nm程度の絶縁膜13aと、ポリシリコン等の導電体からなり、膜厚が例えば数nm〜数10nm程度の導電膜117とを順次形成する。次いで、絶縁膜13a及び導電膜117のうち第1の素子領域101上に形成された部分を除去し、絶縁膜13a及び導電膜117を半導体基板1の第2の素子領域102上に残す。

【0080】

次に、図5(d)に示す工程で、再びポリシリコン等からなり、膜厚が数10nm〜数100nm程度の導電膜118を半導体基板1の上面上及び導電膜117(図示省略)上に形成する。その後、イオン注入等により、導電膜118のうち、第1の素子領域101上に形成された部分にはP型不純物を導入し、導電膜117、118のうち第2の素子領域102上に形成された部分にはN型不純物を導入する(図示せず)。

【0081】

なお、本変形例では、上部ゲート領域131を絶縁膜13aの形成前に形成したが、これに代えて、図5(c)に示す工程において、第1の素子領域101上の導電膜117及び絶縁膜13aを除去後、イオン注入法などを用いて、第1の素子領域101の半導体基板1の上面部にP型の上部ゲート領域131’を形成してもよい。

【0082】

あるいは、図5(d)に示す工程において、ポリシリコンからなる導電膜118の形成後、イオン注入法などを用いて、第1の素子領域101上の導電膜118の下部から半導体基板1(チャネル領域3)の上面部に亘ってP型の上部ゲート領域131''を形成してもよい。

【0083】

次に、図5(e)に示す工程では、ドライエッチング法などにより導電膜117、118をパターンニングしてゲート電極6、14を形成する。これに引き続いて、上部ゲート領域131(及び場合によってはチャネル領域3の上面部)のうちゲート電極6の直下に位置する領域を除く部分と、絶縁膜13a及びウェル領域11上面部のうちゲート電極14の直下に位置する領域を除く部分とを除去する。上部ゲート領域131及びウェル領域11の除去量(すなわち、半導体基板1における除去深さ)は、例えば10nm〜100nm程度とすることが好ましい。なお、上部ゲート領域131のうちゲート電極6下に残された部分を便宜的に上部ゲート領域2と表記する。

【0084】

次に、図6(a)に示す工程で、第2の素子領域102に必要に応じてP型のHalo注入領域18、N型の低濃度ドレイン領域17をそれぞれ形成する。続いて、半導体基板1上及びゲート電極6、14上にシリコン窒化膜等を形成してから当該シリコン窒化膜等を異方性エッチングによりエッチバックすることにより、サイドウォールスペーサ7をゲート電極6の両側面上に形成するとともに、サイドウォールスペーサ15をゲート電極14の両側面上に形成する。

【0085】

続いて、ゲート電極6、14及びサイドウォールスペーサ7、15をマスクとして半導体基板1内にN型不純物をイオン注入する。これにより、半導体基板1(具体的にはチャネル領域3)のうち、ゲート電極6の両側方であってサイドウォールスペーサ7の外側に位置する領域にソース及びドレイン領域8を形成するとともに、半導体基板1(具体的にはウェル領域11)のうち、ゲート電極14の両側方であってサイドウォールスペーサ15の外側に位置する領域にソース及びドレイン領域16を形成する。

【0086】

次に、熱処理を行って半導体基板1内及びゲート電極6、14内に含まれる不純物を活性化する。この活性化の際に、P型の上部ゲート領域2中のP型不純物がN型のチャネル領域3の上部、及びゲート電極6の下面近傍部に拡散する。

【0087】

次に、図6(b)に示す工程で、半導体基板1上にゲート電極6、14を埋め込むようにシリコン酸化膜26を形成した後、公知の方法によってゲート電極6、14の上面が露出するまでシリコン酸化膜26を研磨する。次いで、第1の実施形態に係る方法と同様に、ゲート電極6の上部を選択的に除去した後、シリコン酸化膜26を除去する。

【0088】

次に、図6(c)に示す工程で、ゲート電極6、14上にシリサイド層40、42をそれぞれ形成するとともに、ソース及びドレイン領域8、16上にシリサイド層9、19をそれぞれ形成する。次いで、半導体基板1の上面全体に層間絶縁膜28を形成した後、層間絶縁膜28を貫通し、シリサイド層9、19にそれぞれ接続するコンタクトプラグ27を形成する。その後は図示しないが、周知技術を用いて、表面保護膜、電極等との接続を取るための配線層、及び外部接続用端子等を形成することにより、本変形例に係る半導体装置を作製できる。

【0089】

なお、図5(c)、(d)に示す工程において、絶縁膜13aを形成した直後に絶縁膜13aの一部を選択的に除去する際には、絶縁膜13a上に保護膜として導電膜117を設ける例を説明したが、エッチングによるダメージがゲート絶縁膜となる絶縁膜13aの信頼性に影響を与えない場合には、導電膜117を設けなくてもよい。この場合、ゲート電極6、14形成用のポリシリコンを第1の素子領域101上及び第2の素子領域102上に堆積等することによってゲート電極6、14を同時に形成できる。

【0090】

また、図6(b)に示す工程では、上記したように、ソース及びドレイン領域8の形成時にN型不純物が導入された、ゲート電極6の上部を除去しているが、両導電型不純物の濃度が十分濃く、両導電型不純物間のリーク電流のために整流特性が無視できる場合には、必ずしもゲート電極6の上部を除去しなくてもよい。

【0091】

なお、上記で説明した各層の導電型を、全て反対の導電型にしても第1のトランジスタ70をJFETとして問題なく動作させることができる。

【0092】

以上で説明した本実施形態の半導体装置では、論理回路等に用いられるMISFET(第2のトランジスタ80)と同一の半導体基板1上に形成されたJFET(第1のトランジスタ70)において、上部ゲート領域2とソース及びドレイン領域8、及び上部ゲート領域2とシリサイド層9とは、それぞれチャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間している。

【0093】

この構成によれば、上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の厚さ程度まで小さくすることができる。また、ゲート電極6が平面的に見てソース及びドレイン領域8と重なることがない。なお、サイドウォールスペーサ7の断面形状はI字状であれば好ましいが、平面的に見てソース及びドレイン領域8と大きく重なっていなければ、L字状等であってもよい。

【0094】

これに対し、特許文献2に記載された従来の半導体装置では、JFETにおいて、ゲート電極を形成するために、スペーサ端との位置合わせズレを考慮した間隔を取る必要があり、ソース及びドレイン電極とゲート電極との間隔を取る必要もある。

【0095】

このため、本変形例に係る半導体装置では、特許文献2に記載された従来の半導体装置のJFETと実効ゲート寸法が同じ場合であっても、ゲート電極6のゲート長方向の幅を大幅に縮小することができる。特に、JFETである第1のトランジスタ70をMISFETと同様の寸法で形成することができる。

【0096】

さらに、N型のチャネル領域3はゲート電極6の直下において半導体基板1の上面から離れたところにある。そのため、第1のトランジスタ70においては、半導体基板1の上面近傍にチャネルが形成されるMISFETよりも、同じ動作電流密度で比較した場合の低周波雑音を10分の1以下にすることができる。その結果、アナログ回路等をMISFETで構成する場合に比べて低周波雑音が大幅に抑制されたアナログ等の回路を、従来のJFETを用いた場合に比べてより小さいチップ面積で実現することが可能となる。

【0097】

また、本変形例の製造方法においても、ゲート電極6、14の形成工程、サイドウォールスペーサ7、15の形成工程、ソース及びドレイン領域8、16の形成工程等、第1のトランジスタ70の形成工程と第2のトランジスタ80の形成工程とを共通化している。そのため、本変形例の方法によれば、それぞれのトランジスタを別個の工程により形成するのに比べて半導体装置を安価に製造することができる。

【0098】

以上のように、本変形例の半導体装置及びその製造方法によっても、第1の実施形態に係る半導体装置及びその製造方法と同様に、低周波雑音が低減されたアナログ回路と、論理回路とが混載された半導体装置をより安価に、且つ、より小さい面積で実現することができる。

【0099】

また、本変形例に係る方法によれば、第1の実施形態に係る方法と異なり、ゲート電極6、14を形成用の導電膜118を形成する前に予めP型の上部ゲート領域131を形成している。このため、図5(d)に示す工程で導電膜118にP型不純物を導入する際に製造上のバラツキ等によって、意図しないP型不純物の半導体基板1への拡散が生じた場合であっても、当該拡散による素子特性への影響を第1の実施形態に係る方法に比べて小さくすることができる。

【0100】

なお、図5(b)に示す工程では、上部ゲート領域131は第1の素子領域101上全体に形成されるが、ゲート電極6の形成時に上部ゲート領域131のうちゲート電極6下に設けられた部分以外の部分は除去されるので、その後の熱処理によって余分なP型不純物がチャネル領域3等に導入されることはない。このため、本変形例に係る方法によれば、第1のトランジスタ70の素子特性をより安定化させることができる。

【0101】

(第2の実施形態)

図7は、本発明の第2の実施形態に係る半導体装置を示す断面図である。同図において、図1に示す第1の実施形態に係る半導体装置と同様の部分については同一の符号を付し、その部分の説明は一部簡略化する。

【0102】

図1に示す第1の実施形態に係る半導体装置では、ゲート電極6とP型の上部ゲート領域2とが直接接しているのに対し、図7に示す本実施形態に係る半導体装置では、ゲート電極6と上部ゲート領域2とが絶縁膜31を介して接している。このため、本実施形態の半導体装置では、第1のトランジスタ70においてゲート電極6と半導体基板1(上部ゲート領域2)とが直流的に絶縁されている。

【0103】

この絶縁膜31は、例えばゲート絶縁膜13と同じ材料で構成され、ゲート絶縁膜13と同じ厚さであってもよい。この場合、後述のように絶縁膜31をゲート絶縁膜13と同時に形成できるので、好ましい。その他の構成は、本実施形態の半導体装置と第1の実施形態の半導体装置とでほぼ同様である。

【0104】

以上の相違点があるものの、絶縁膜31が容量絶縁膜となり、半導体基板1(上部ゲート領域2及びチャネル領域3)には容量を介してゲート電極6により電位が与えられるので、本実施形態の半導体装置は第1の実施形態の半導体装置と同様な動作を示す。

【0105】

すなわち、第1のトランジスタ70では、ソース及びドレイン領域8間に所定の電圧を印加し、ゲート−ソース間に所定の負の電圧を印加した場合、チャネル領域3内に上部ゲート領域2から空乏層が拡がり、ソース及びドレイン領域8の一方(ドレイン領域)から他方(ソース領域)に電流が流れなくなる。

【0106】

一方、ゲート−ソース間に負の電圧で、かつ、半導体装置をオフ状態にする所定のゲート電圧よりも大きい電圧、すなわち絶対値としては上記のオフ状態にするための所定のゲート電圧より小さい電圧、をゲート電極6に印加すると、ソース及びドレイン領域8の一方(ドレイン領域)から他方(ソース領域)へとチャネル領域3を介して電流が流れ、オン状態となる。

【0107】

以上の構成によれば、P型の上部ゲート領域2の電位がN型のチャネル領域3の電位より高くなった場合でも、ゲート電極6から半導体基板1へと大電流が漏れ出ることがなく、回路設計の自由度を大きくすることができる。

【0108】

次に、以上のように構成された本実施形態に係る半導体装置の製造方法について説明する。

【0109】

図8(a)〜(d)、図9(a)〜(c)は、本実施形態の半導体装置の製造方法の一例を示す断面図である。これらの図において、第1の実施形態に係る半導体装置と同様の部分については図2(a)〜(e)、図3(a)〜(c)と同一の符号を付している。

【0110】

まず、図8(a)に示す工程では、図2(a)に示す工程と同様にして、半導体基板1内に素子分離領域21、22a、22bを形成する。次に、図8(b)に示す工程では、イオン注入等の方法により半導体基板1内にN型埋め込み領域5、下部ゲート領域4、N型埋め込み領域12、及びP型のウェル領域11を形成する。次に、イオン注入等によって下部ゲート領域4の上部に選択的にN型不純物を導入することで、N型のチャネル領域3を形成する。

【0111】

次に、図8(c)に示す工程では、半導体基板1の上面全体にシリコン酸化物等からなり、膜厚が例えば0.数nm〜数nm程度の絶縁膜13aと、ポリシリコン等の導電体からなり、膜厚が例えば数10nm〜数100nm程度の導電膜118とを順次形成する。その後、イオン注入等により、導電膜118のうち、第1の素子領域101上に形成された部分にはP型不純物を導入し、導電膜118のうち第2の素子領域102上に形成された部分にはN型不純物を導入する(図示せず)。

【0112】

次に、図8(d)に示す工程では、ドライエッチング法などにより導電膜118及び絶縁膜13aをパターンニングすることで、絶縁膜31を間に挟んでチャネル領域3上にゲート電極6を形成するとともに、ゲート絶縁膜13を間に挟んでウェル領域11上にゲート電極14を形成する。

【0113】

その後、図3(a)〜(c)に示す第1の実施形態に係る方法と同様の工程を経ることにより、半導体装置を作製できる。

【0114】

ここで、図9(a)に示す工程では、ソース及びドレイン領域8、16形成後の熱処理、あるいはゲート電極6、14の形成後からソース及びドレイン領域8、16の形成前までにする熱処理によって、ゲート電極6に含まれるP型不純物がゲート絶縁膜13を通過して、チャネル領域3の上部に拡散される。これにより、チャネル領域3上に上部ゲート領域2が形成される。

【0115】

また、図9(b)に示す工程では、ゲート電極6のうち、ソース及びドレイン領域8の形成時にN型不純物が導入された部分を除去しているが、両導電型不純物の濃度が十分濃く、両導電型不純物間のリーク電流のために整流特性が無視できる場合には、必ずしもゲート電極6の上部を除去しなくてもよい。

【0116】

なお、上記で説明した各層の導電型を、全て反対の導電型にしても第1のトランジスタ70をJFETとして、第2のトランジスタ80をMISFETとして問題なく動作させることができる。

【0117】

以上で説明した本実施形態の半導体装置では、JFET(第1のトランジスタ70)において、上部ゲート領域2とソース及びドレイン領域8、及び上部ゲート領域2とシリサイド層9とは、それぞれチャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間している。

【0118】

この構成によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。また、ゲート電極6が平面的に見てソース及びドレイン領域8と重なることがない。なお、サイドウォールスペーサ7の断面形状はI字状であれば好ましいが、平面的に見てソース及びドレイン領域8と大きく重なっていなければ、L字状等であってもよい。

【0119】

これに対し、特許文献2に記載された従来の半導体装置では、JFETにおいて、ゲート電極を形成するために、スペーサ端との位置合わせズレを考慮した間隔を取る必要があり、ソース及びドレイン電極とゲート電極との間隔も取る必要もある。

【0120】

このため、本実施形態の半導体装置では、特許文献2に記載された従来の半導体装置のJFETと実効ゲート寸法が同じ場合であっても、ゲート電極6のゲート長方向の幅を大幅に縮小することができる。特に、JFETである第1のトランジスタ70をMISFETと同様の寸法で形成することができる。

【0121】

さらに、N型のチャネル領域3はゲート電極6の直下において半導体基板1の上面から離れたところにある。そのため、第1のトランジスタ70においては、半導体基板1の上面近傍にチャネルが形成されるMISFETよりも、同じ動作電流密度で比較した場合の低周波雑音を10分の1以下にすることができる。その結果、アナログ回路等を本実施形態のJFETで構成することにより、当該アナログ回路をMISFETで構成する場合と同等の低周波雑音性能を実現するのに、10分の1以下程度まで回路面積を縮小することができる。

【0122】

また、本実施形態の半導体装置において、上述のJFETと、論理回路等に用いられるMISFET(第2のトランジスタ80)とが同一の半導体基板1上に形成される場合、チップ全体の面積を従来技術に比べて大幅に縮小できる。また、JFETとMISFETとが共通の工程で形成できる構成となっているので、両素子を別々に形成する場合に比べて製造コストを大幅に低減することができる。

【0123】

また、本実施形態に係る半導体装置の製造方法では、ゲート電極6、14の形成工程、サイドウォールスペーサ7、15の形成工程、ソース及びドレイン領域8、16の形成工程、各シリサイド層の形成工程等、第1のトランジスタ70の形成工程と第2のトランジスタ80の形成工程とを共通化している。そのため、本実施形態の方法によれば、それぞれのトランジスタを別個の工程により形成するのに比べて半導体装置を安価に製造することができる。

【0124】

また、本実施形態の方法によれば、P型の上部ゲート領域2を形成するための専用の工程が不要となることによっても工程数の削減が図られている。

【0125】

−第2の実施形態の変形例−

図10は、本発明の第2の実施形態に係る半導体装置の変形例を示す断面図である。同図において、図1に示す第1の実施形態に係る半導体装置と同様の部分には同一符号を付している。

【0126】

図4に示す第1の実施形態の変形例に係る半導体装置では、第1のトランジスタ70において、ゲート電極6と上部ゲート領域2とが直接接しているのに対し、図10に示す本変形例に係る半導体装置では、ゲート電極6と上部ゲート領域2とが絶縁膜31を介して接している。このため、本変形例に係る半導体装置では、第1のトランジスタ70においてゲート電極6と上部ゲート領域2とが直流的に絶縁されている。

【0127】

この絶縁膜31は、例えばゲート絶縁膜13と同じ材料で構成され、ゲート絶縁膜13と同じ厚さであってもよい。この場合、後述のように絶縁膜31をゲート絶縁膜13と同時に形成できるので、好ましい。その他の構成は、第1の実施形態の変形例に係る半導体装置と本変形例に係る半導体装置とでほぼ同様である。

【0128】

以上の相違点があるものの、絶縁膜31が容量絶縁膜となり、半導体基板1(上部ゲート領域2及びチャネル領域3)には容量を介してゲート電極6により電位が与えられるので、本変形例に係る半導体装置は第1の実施形態及びその変形例に係る半導体装置と同様な動作を示す。

【0129】

以上の構成によれば、P型の上部ゲート領域2の電位がN型のチャネル領域3の電位より高くなった場合でも、ゲート電極6から半導体基板1へと大電流が漏れ出ることがなく、回路設計の自由度を大きくすることができる。

【0130】

次に、以上のように構成された本変形例に係る半導体装置の製造方法について説明する。図11(a)〜(d)、図12(a)〜(c)は、本変形例に係る半導体装置の製造方法の一例を示す断面図である。

【0131】

まず、図11(a)に示す工程で、図5(a)に示す工程と同様にして素子分離領域21、22a、22bを形成する。次に、図11(b)に示す工程で、注入法などによりN型のチャネル領域3上部にP型の上部ゲート領域131を形成する。

【0132】

次に、図11(c)に示す工程では、CVD法等により、半導体基板1の上面全体にシリコン酸化物等からなる絶縁膜13aと、ポリシリコン等からなる導電膜118とを順次形成する。絶縁膜13aの膜厚は、例えば0.数nm〜数nm程度とし、導電膜118の膜厚は、例えば数10nm〜数100nm程度とする。その後、イオン注入等により、導電膜118のうち、第1の素子領域101上に形成された部分にはP型不純物を導入し、導電膜118のうち第2の素子領域102上に形成された部分にはN型不純物を導入する。

【0133】

なお、ここではP型の上部ゲート領域131を後にゲート絶縁膜となる絶縁膜13aの形成前に形成したが、これに代えて、絶縁膜13a及び導電膜118の形成後にイオン注入法等を用いて、チャネル領域3の上面部にP型不純物を導入することにより、チャネル領域3上に上部ゲート領域131’を形成してもよい。

【0134】

次に、図11(d)に示す工程では、ドライエッチング法などにより導電膜118をパターンニングしてゲート電極6、14を形成する。これに引き続いて、絶縁膜13a及び上部ゲート領域131(及び場合によってはチャネル領域3の上面部)のうちゲート電極6の直下に位置する領域を除く部分と、絶縁膜13a及びウェル領域11上面部のうちゲート電極14の直下に位置する領域を除く部分とを除去する。これにより、チャネル領域3上の上部ゲート領域2と、上部ゲート領域2上の絶縁膜31とが形成される。

【0135】

本工程において、上部ゲート領域131及びウェル領域11の除去量(すなわち、半導体基板1における除去深さ)は、例えば10nm〜100nm程度とすることが好ましい。

【0136】

これ以降は、図9(a)〜(c)に示す第2の実施形態に係る方法と同様の工程を経ることにより、半導体装置を作製できる(図12(a)〜(c)参照)。

【0137】

図12(b)に示す工程では、ゲート電極6のうち、ソース及びドレイン領域8の形成時にN型不純物が導入された部分を除去しているが、両導電型不純物の濃度が十分濃く、両導電型不純物間のリーク電流のために整流特性が無視できる場合には、必ずしもゲート電極6の上部を除去しなくてもよい。

【0138】

なお、上記で説明した各層の導電型を、全て反対の導電型にしても第1のトランジスタ70をJFETとして、第2のトランジスタ80をMISFETとして問題なく動作させることができる。

【0139】

以上で説明した本変形例の半導体装置では、JFET(第1のトランジスタ70)において、上部ゲート領域2とソース及びドレイン領域8、及び上部ゲート領域2とシリサイド層9とは、それぞれチャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間している。

【0140】

この構成によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。

【0141】

これに対し、特許文献2に記載された従来の半導体装置では、JFETにおいて、ゲート電極を形成するために、スペーサ端との位置合わせズレを考慮した間隔を取る必要があり、ソース及びドレイン電極とゲート電極との間隔を取る必要もある。

【0142】

このため、本変形例の半導体装置では、特許文献2に記載された従来の半導体装置のJFETと実効ゲート寸法が同じ場合であっても、ゲート電極6のゲート長方向の幅を大幅に縮小することができる。特に、JFETである第1のトランジスタ70をMISFETと同様の寸法で形成することができる。

【0143】

さらに、N型のチャネル領域3はゲート電極6の直下において半導体基板1の上面から離れたところにある。そのため、第1のトランジスタ70においては、半導体基板1の上面近傍にチャネルが形成されるMISFETよりも、同じ動作電流密度で比較した場合の低周波雑音を10分の1以下にすることができる。その結果、アナログ回路等を本変形例のJFETで構成することにより、当該アナログ回路をMISFETで構成する場合と同等程度まで素子面積を縮小することができ、且つMISFETを用いた場合よりも低周波雑音を大きく低減することができる。

【0144】

また、本変形例に係る半導体装置の製造方法では、ゲート電極6、14の形成工程、サイドウォールスペーサ7、15の形成工程、ソース及びドレイン領域8、16の形成工程、各シリサイド層の形成工程等、第1のトランジスタ70の形成工程と第2のトランジスタ80の形成工程とを共通化している。そのため、本実施形態の方法によれば、それぞれのトランジスタを別個の工程により形成するのに比べて半導体装置を安価に製造することができる。

【0145】

また、本変形例に係る方法においても、図5(a)〜(e)、図6(a)〜(c)に示す方法と同様に、ゲート電極6の形成前に上部ゲート領域131を形成するので、上部ゲート領域2を形成するための専用の拡散工程が不要となる。

【0146】

また、本変形例に係る方法によれば、第2の実施形態に係る方法と異なり、ゲート電極6、14を形成用の導電膜118を形成する前に予めP型の上部ゲート領域131を形成している。このため、図11(c)に示す工程で導電膜118にP型不純物を導入する際に製造上のバラツキ等によって、意図しないP型不純物の半導体基板1への拡散が生じた場合であっても、当該拡散による素子特性への影響を第2の実施形態に係る方法に比べて小さくすることができる。

【0147】

(第3の実施形態)

図13は、本発明の第3の実施形態に係る半導体装置を示す断面図である。同図において、図7に示す第2の実施形態に係る半導体装置と同様の部分については同一の符号を付し、その部分の説明は一部簡略化する。

【0148】

図7に示す半導体装置では、第1のトランジスタ70において、上部ゲート領域2上には絶縁膜31を間に挟んでポリシリコン等からなるゲート電極6が形成されていたが、本実施形態の半導体装置では、上部ゲート領域2上にはゲート電極として機能するシリサイド層9aが直接形成されている。このシリサイド層9aは、側方をサイドウォールスペーサ7に囲まれている。また、サイドウォールスペーサ7とシリサイド層9aとで構成される凹部には、層間絶縁膜28が埋め込まれている。

【0149】

この構成の違いに応じて、本実施形態の半導体装置の製造方法では、サイドウォールスペーサ7、ソース及びドレイン領域8、及び上部ゲート領域2の形成後にポリシリコンからなるゲート電極6を除去し、上部ゲート領域2の上面を直接合金化(具体的にはシリサイド化)してシリサイド層9aを形成する。

【0150】

このような構成の違いにより、上部ゲート領域2を配線層の形成直前に形成することができるので、上部ゲート領域2に印加される熱処理の回数等がより少なくなり、上部ゲート領域2中の不純物分布のバラツキを一層少なくすることができる。

【0151】

次に、以上のように構成された本実施形態に係る半導体装置の製造方法について説明する。図14(a)〜(d)、図15(a)〜(c)は、本実施形態の半導体装置の製造方法の一例を示す断面図である。これらの図において、図8(a)〜(d)及び図9(a)〜(c)と同様の部分については同一の符号を付し、その説明を一部簡略化する。

【0152】

まず、図14(a)〜(d)に示す工程では、第2の実施形態に係る半導体装置の製造方法における図8(a)〜(d)に示す工程と同様にして、絶縁膜31を間に挟んでチャネル領域3上にポリシリコン等からなるゲート電極119を形成するとともに、ゲート絶縁膜13を間に挟んでウェル領域11上にポリシリコン等からなるゲート電極14を形成する。ただし、第2の実施形態の方法と異なり、図14(c)に示す工程では、ポリシリコンからなる導電膜118の形成後に、導電膜118のうち第1の素子領域101上に形成された部分に不純物の導入を行わない。

【0153】

次に、図15(a)に示す工程では、イオン注入法等により、P型のHalo注入領域18、N型の低濃度ドレイン領域17をウェル領域11内に形成する。次いで、サイドウォールスペーサ7をゲート電極119の側面上に形成するとともにサイドウォールスペーサ15をゲート電極14の側面上に形成する。続いて、ゲート電極119、14及びサイドウォールスペーサ7、15をマスクとして半導体基板1(チャネル領域3)内にN型不純物をイオン注入することにより、ソース及びドレイン領域8、16をそれぞれ形成する。

【0154】

次に、図15(b)に示す工程では、半導体基板1の上面全体にシリコン酸化膜26等の絶縁膜を形成した後、CMP法等によりゲート電極119、14の上面が露出するまでシリコン酸化膜26の上部を除去する。さらに、第1の素子領域101上に設けられたゲート電極119及び絶縁膜31を除去してチャネル領域3を露出させ、この露出したチャネル領域3の上部にイオン注入法などを用いてP型不純物を導入することで、上部ゲート領域2を形成する。

【0155】

次に、図15(c)に示す工程で、シリコン酸化膜26を除去した後、ゲート電極14の上面上、ソース及びドレイン領域8、16上にシリサイド層9を形成するとともに、上部ゲート領域2上に第1のトランジスタ70のゲート電極として機能するシリサイド層9aを形成する。続いて、半導体基板1の上面全体、及びサイドウォールスペーサ7とシリサイド層9aとで構成された凹部内に層間絶縁膜28を形成した後、ソース及びドレイン領域8上のシリサイド層9又はソース及びドレイン領域16上のシリサイド層9に接続されるコンタクトプラグ27をそれぞれ形成する。その後は図示しないが、公知技術を用いて、表面保護膜、電極接続のための配線層、及び外部接続用端子等を形成することにより、本実施形態の半導体装置を作製することができる。

【0156】

なお、上記で説明した各層の導電型を、全て反対の導電型にしても第1のトランジスタ70をJFETとして問題なく動作させることができる。

【0157】

特許文献2に開示された従来の半導体装置では、上部ゲート領域上に形成されるゲート電極が、スペーサ端との位置合わせズレを考慮した間隔を取るとともに、ゲート電極とソース及びドレイン電極との間隔を取る必要がある。これに対し、本実施形態の半導体装置によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。このため、JFETである第1のトランジスタ70をMISFETと同様な寸法で形成することができる。

【0158】

さらに、N型のチャネル領域3はシリサイド層9aの直下において半導体基板1の上面から離れたところにある。そのため、第1のトランジスタ70においては、半導体基板1の上面近傍にチャネルが形成されるMISFETよりも、同じ動作電流密度で比較した場合の低周波雑音を10分の1以下にすることができる。その結果、アナログ回路等を本実施形態のJFETで構成することにより、当該アナログ回路をMISFETで構成する場合と同等の低周波雑音性能を実現するのに、10分の1以下程度まで回路面積を縮小することができる。

【0159】

また、本実施形態に係る半導体装置の製造方法では、シリサイド層9a、9、42の形成工程、サイドウォールスペーサ7、15の形成工程、ソース及びドレイン領域8、16の形成工程等、第1のトランジスタ70の形成工程と第2のトランジスタ80の形成工程とを共通化している。そのため、本実施形態の方法によれば、それぞれのトランジスタを別個の工程により形成するのに比べて半導体装置を安価に製造することができる。

【0160】

(第4の実施形態)

図16は、本発明の第4の実施形態に係る半導体装置を示す断面図である。同図において、図7に示す第2の実施形態に係る半導体装置と同様の部分については同一の符号を付し、その部分の説明は一部簡略化する。

【0161】

図7に示す第2の実施形態に係る半導体装置では、第1のトランジスタ70において、上部ゲート領域2上に絶縁膜31を間に挟んでP型ポリシリコンからなるゲート電極6が形成され、ウェル領域11上にはゲート絶縁膜13を間に挟んでN型ポリシリコンからなるゲート電極14が形成される。また、ゲート電極6から絶縁膜31を介してN型のチャネル領域3へP型不純物を拡散させることによって上部ゲート領域2が形成される。

【0162】

これに対し、本実施形態の半導体装置では、金属又は導電性の金属化合物からなるゲート電極65が上部ゲート領域2上に直接形成されており、ウェル領域11上にはゲート絶縁膜13を間に挟んで金属又は導電性の金属化合物からなるゲート電極66が形成されている。また、上部ゲート領域2はゲート電極65の形成前にイオン注入等により形成される。ゲート電極65、66は互いに同じ材料で構成されており、例えばタングステン等の金属や金属シリサイドやTiN、TaN等の導電性の金属化合物等で構成される。

【0163】

ゲート絶縁膜13の構成材料は特に限定されないが、ハフニウム酸化物等の高誘電率材料で構成されることが好ましい。

【0164】

また、シリサイド層9はソース及びドレイン領域8、16上に形成されている。しかし、ゲート電極65、66は金属等で構成されているので、ゲート電極65、66上にはシリサイド層は設けられていない。

【0165】

以上の構成により、いわゆるメタルゲート電極を有するJFETを、ゲート長数10nm以下のメタルゲート電極を有するMISFETと同一基板上に混載することができる。

【0166】

次に、以上のように構成された本実施形態に係る半導体装置の製造方法について説明する。

【0167】

図17(a)〜(d)、図18(a)〜(c)は、本実施形態の半導体装置の製造方法の一例を示す断面図である。これらの図において、図8(a)〜(d)及び図9(a)〜(c)、並びに図14(a)〜(d)、図15(a)〜(c)と同様の部分については同一の符号を付し、その説明を一部簡略化する。

【0168】

まず、図17(a)〜(d)に示す工程では、第2の実施形態に係る半導体装置の製造方法における図8(a)〜(d)に示す工程と同様にして、絶縁膜31を間に挟んでチャネル領域3上にポリシリコン等からなるゲート電極119を形成するとともに、ゲート絶縁膜13を間に挟んでウェル領域11上にポリシリコン等からなるゲート電極120を形成する。ただし、第2の実施形態の方法と異なり、図17(c)に示す工程では、ポリシリコンからなる導電膜118の形成後に、導電膜118に不純物の導入を行わない。

【0169】

次に、図18(a)に示す工程では、イオン注入法等により、P型のHalo注入領域18、N型の低濃度ドレイン領域17をウェル領域11内に形成する。次いで、サイドウォールスペーサ7をゲート電極119の側面上に形成するとともにサイドウォールスペーサ15をゲート電極120の側面上に形成する。続いて、ゲート電極119、120及びサイドウォールスペーサ7、15をマスクとして半導体基板1(チャネル領域3)内にN型不純物をイオン注入することにより、ソース及びドレイン領域8、16をそれぞれ形成する。

【0170】

次に、図18(b)に示す工程では、半導体基板1の上面全体にシリコン酸化膜26等の絶縁膜を形成した後、CMP法等によりゲート電極119、120の上面が露出するまでシリコン酸化膜26の上部を除去する。さらに、第1の素子領域101上に設けられたゲート電極119及び絶縁膜31を除去してチャネル領域3を露出させ、この露出したチャネル領域3の上部にイオン注入法などを用いて選択的にP型不純物を導入することで、上部ゲート領域2を形成する。この一方で、ゲート電極120を除去し、第2の素子領域102上にゲート絶縁膜13を露出させる。ゲート電極119とゲート電極120の除去とは、同時に行うことができる。

【0171】

次に、図18(c)に示す工程では、サイドウォールスペーサ7で囲まれた凹部内、及びサイドウォールスペーサ15で囲まれた凹部内に公知の方法により金属又は導電性の金属化合物を埋め込む。次いで、余剰の金属又は導電性の金属化合物をCMP法等により除去した後、シリコン酸化膜26をエッチングにより除去することで、上部ゲート領域2上にゲート電極65を形成するとともに、ゲート絶縁膜13上にゲート電極66を形成する。

【0172】

次に、ソース及びドレイン領域8、16上にシリサイド層9を形成する。続いて、半導体基板1の上面全体にゲート電極65、66を埋め込むように層間絶縁膜28を形成する。次いで、ソース及びドレイン領域8上のシリサイド層9又はソース及びドレイン領域16上のシリサイド層9に接続されるコンタクトプラグ27をそれぞれ形成する。その後は図示しないが、公知技術を用いて、表面保護膜、電極接続のための配線層、及び外部接続用端子等を形成することにより、本実施形態の半導体装置を作製することができる。

【0173】

なお、上記で説明した各層の導電型を、全て反対の導電型にしても第1のトランジスタ70及び第2のトランジスタ80を問題なく動作させることができる。

【0174】

以上で説明した本実施形態の半導体装置では、JFET(第1のトランジスタ70)において、上部ゲート領域2とソース及びドレイン領域8、及び上部ゲート領域2とシリサイド層9とは、それぞれチャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間している。

【0175】

この構成によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。

【0176】

これに対し、特許文献2に記載された従来の半導体装置では、JFETにおいて、ゲート電極を形成するためには、スペーサ端との位置合わせズレを考慮した間隔を取る必要があり、ソース及びドレイン電極とゲート電極との間隔を取る必要もある。

【0177】

このため、本実施形態の半導体装置では、特許文献2に記載された従来の半導体装置のJFETと実効ゲート寸法が同じ場合であっても、ゲート電極6のゲート長方向の幅を大幅に縮小することができる。特に、JFETである第1のトランジスタ70をMISFETと同様の寸法で形成することができる。

【0178】

さらに、N型のチャネル領域3はゲート電極65の直下において半導体基板1の上面から離れたところにある。そのため、第1のトランジスタ70においては、半導体基板1の上面近傍にチャネルが形成されるMISFETよりも、同じ動作電流密度で比較した場合の低周波雑音を10分の1以下にすることができる。その結果、アナログ回路等を本実施形態のJFETで構成することにより、当該アナログ回路をMISFETで構成する場合と同等の低周波雑音性能を実現するのに、10分の1以下程度まで回路面積を縮小することができる。

【0179】

また、本実施形態に係る半導体装置の製造方法では、ゲート電極6、14の形成工程、サイドウォールスペーサ7、15の形成工程、ソース及びドレイン領域8、16の形成工程、ゲート電極65、66の形成工程、シリサイド層9の形成工程等、第1のトランジスタ70の形成工程と第2のトランジスタ80の形成工程とを共通化している。そのため、本実施形態の方法によれば、それぞれのトランジスタを別個の工程により形成するのに比べて安価に半導体装置を製造することができる。

【0180】

−第4の実施形態の変形例−

図19は、本発明の第4の実施形態に係る半導体装置の変形例を示す断面図である。同図において、図16に示す第4の実施形態に係る半導体装置と同様の部分には同一符号を付している。

【0181】

第4の実施形態に係る半導体装置では、第1のトランジスタ70においてP型の上部ゲート領域2と金属等からなるゲート電極65とが直接接しているが、本変形例の半導体装置では、図19に示すように、上部ゲート領域2とゲート電極65とは間に絶縁膜31を挟んで接している。このため、本変形例の半導体装置では、ゲート電極65と上部ゲート領域2とが直流的に絶縁されている。

【0182】

しかしながら、絶縁膜31が容量絶縁膜となり、半導体基板1には容量を介してゲート電極65から所望の電位を与えることができるので、本変形例の半導体装置は、第4の実施形態に係る半導体装置と同様に動作する。

【0183】

以上のような構成によれば、P型の上部ゲート領域2の電位がN型のチャネル領域3の電位より高くなった場合でも、ゲート電極65からチャネル領域3へと大電流が漏れ出ることがなくなるので、回路設計の自由度を大きくすることができる。

【0184】

次に、以上のように構成された本変形例に係る半導体装置の製造方法について説明する。

【0185】

図20(a)〜(d)、図21(a)〜(c)は、本変形例の半導体装置の製造方法の一例を示す工程断面図である。これらの図において、図17(a)〜(d)、図18(a)〜(c)と同様の部分については同一の符号を付し、その説明を一部簡略化する。

【0186】

まず、図20(a)〜(d)、図21(a)に示す工程では、第4の実施形態に係る半導体装置の製造方法における図17(a)〜(d)、図18(a)に示す工程と同様の処理を行う。

【0187】

次に、図21(b)に示す工程では、半導体基板1の上面全体にシリコン酸化膜26等の絶縁膜を形成した後、CMP法等によりゲート電極119、120の上面が露出するまでシリコン酸化膜26の上部を除去する。

【0188】

次いで、第1の素子領域101上のゲート電極119を除去するとともに、第2の素子領域102上のゲート電極120を除去する。この際、絶縁膜31、ゲート絶縁膜13は除去されないので、絶縁膜31及びゲート絶縁膜13は露出することになる。次に、イオン注入法等を用いて絶縁膜31を通してチャネル領域3の上部にP型不純物を選択的に導入することで、上部ゲート領域2を形成する。

【0189】

次に、図21(c)に示す工程では、ゲート電極119、120が形成されていた領域、すなわちサイドウォールスペーサ7で囲まれた凹部内、及びサイドウォールスペーサ15で囲まれた凹部内に、公知の方法により金属又は導電性の金属化合物を埋め込む。次いで、余剰の金属又は導電性の金属化合物及びシリコン酸化膜26を除去することで、絶縁膜31上にゲート電極65を形成するとともに、ゲート絶縁膜13上にゲート電極66を形成する。

【0190】

次に、ソース及びドレイン領域8、16上にシリサイド層9を形成する。続いて、半導体基板1の上面全体にゲート電極65、66を埋め込むように層間絶縁膜28を形成する。次いで、ソース及びドレイン領域8上のシリサイド層9又はソース及びドレイン領域16上のシリサイド層9に接続されるコンタクトプラグ27をそれぞれ形成する。その後は図示しないが、公知技術を用いて、表面保護膜、電極接続のための配線層、及び外部接続用端子等を形成することにより、本変形例の半導体装置を作製することができる。

【0191】

なお、上記で説明した各層の導電型を、全て反対の導電型にしても第1のトランジスタ70及び第2のトランジスタ80を問題なく動作させることができる。

【0192】

以上で説明した本変形例の半導体装置では、JFET(第1のトランジスタ70)において、上部ゲート領域2とソース及びドレイン領域8、及び上部ゲート領域2とシリサイド層9とは、それぞれチャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間している。

【0193】

この構成によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。

【0194】

以上で説明した本変形例の半導体装置では、JFET(第1のトランジスタ70)において、上部ゲート領域2とソース及びドレイン領域8、及び上部ゲート領域2とシリサイド層9とは、それぞれチャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間している。

【0195】

この構成によれば、イオン注入等によりソース及びドレイン領域8を自己整合的に形成できるので、上部ゲート領域2とソース及びドレイン領域8との間隔、及び上部ゲート領域2とシリサイド層9との間隔を、サイドウォールスペーサ7のゲート長方向の幅程度まで小さくすることができる。

【0196】

これに対し、特許文献2に記載された従来の半導体装置では、JFETにおいて、ゲート電極を形成するために、スペーサ端との位置合わせズレを考慮した間隔を取る必要があり、ソース及びドレイン電極とゲート電極との間隔を取る必要もある。

【0197】

このため、本変形例の半導体装置では、特許文献2に記載された従来の半導体装置のJFETと実効ゲート寸法が同じ場合であっても、ゲート電極6のゲート長方向の幅を大幅に縮小することができる。

【0198】

特に、JFETである第1のトランジスタ70をMISFETと同様の寸法で形成することができる。

【0199】

さらに、N型のチャネル領域3はゲート電極65の直下において半導体基板1の上面から離れたところにある。そのため、第1のトランジスタ70においては、半導体基板1の上面近傍にチャネルが形成されるMISFETよりも、同じ動作電流密度で比較した場合の低周波雑音を10分の1以下にすることができる。その結果、アナログ回路等を本変形例のJFETで構成することにより、当該アナログ回路をMISFETで構成する場合と同等の低周波雑音性能を実現するのに、10分の1以下程度まで回路面積を縮小することができる。

【0200】

また、本変形例の半導体装置において、上述のJFETと、論理回路等に用いられるMISFET(第2のトランジスタ80)とが同一の半導体基板1上に形成される場合、チップ全体の面積を従来技術に比べて大幅に縮小できる。また、JFETとMISFETとが共通の工程で形成できる構成となっているので、両素子を別々に形成する場合に比べて製造コストを大幅に低減することができる。

【0201】

したがって、低周波雑音のアナログ回路及び論理回路を混載した半導体装置をより安価に、かつより小さい面積で実現することができる。

【0202】

本発明は、以上で説明した実施形態及びその変形例に限定されず、本発明の趣旨を逸脱しない範囲でこれらの半導体装置の構成を変更したものも含む。例えば、半導体基板1上にMISFET(第2のトランジスタ80)が形成されず、上述のJFET(第1のトランジスタ70)で構成された回路のみが設けられていてもよい。この場合でも、従来の半導体装置に比べて低周波雑音が低減され、且つ面積が小さいという効果を発揮することができる。

【0203】

また、各実施形態及びそれらの変形例に係る半導体装置では、ソース及びドレイン領域8、16等は半導体基板1内にイオン注入等によって不純物を導入することで形成されているが、不純物がin-situドーピングされた半導体層をCVD法等によって形成することで、ソース及びドレイン領域等を形成してもよい。

【0204】

また、本発明の趣旨を逸脱しない範囲で各実施形態及びそれらの変形例に係る半導体装置の構成要素を任意に組み合わせてもよい。

【産業上の利用可能性】

【0205】

本発明の半導体装置及びその製造方法は、アナログ回路と論理回路とを混載したLSI等に適用され、当該LSIは種々の電子機器に用いられる。

【符号の説明】

【0206】

1 半導体基板

1a 基板部分

2 上部ゲート領域

3 チャネル領域

4 下部ゲート領域

5、12 N型埋め込み領域

6、14、119、120 ゲート電極

7、15 サイドウォールスペーサ

8、16 ソース及びドレイン領域

9、9a、19、40、42 シリサイド層

11 ウェル領域

13 ゲート絶縁膜

13a、31 絶縁膜

17 低濃度ドレイン領域

18 Halo注入領域

21、22a、22b 素子分離領域

26 シリコン酸化膜

27 コンタクトプラグ

28 層間絶縁膜

65、66 ゲート電極

70 第1のトランジスタ

80 第2のトランジスタ

101 第1の素子領域

102 第2の素子領域

117、118 導電膜

131、131’、131'' 上部ゲート領域

【特許請求の範囲】

【請求項1】

半導体基板における第1の素子領域上に設けられたJFETを備えた半導体装置であって、

前記JFETは、前記半導体基板内に形成された第1導電型の下部ゲート領域と、前記下部ゲート領域上に形成された第2導電型のチャネル領域と、前記チャネル領域とPN接合を形成するように前記チャネル領域上に形成された第1導電型の上部ゲート領域と、前記下部ゲート領域上であって前記チャネル領域の両側に位置する第2導電型の第1のソース及びドレイン領域と、前記上部ゲート領域上に形成された第1のゲート電極と、前記第1のゲート電極の両側面上に形成された第1のサイドウォールスペーサとを有しており、

前記上部ゲート領域と前記第1のソース及びドレイン領域とは、前記チャネル領域のうち前記第1のサイドウォールスペーサの下に位置する部分を挟んで互いに離間しており、

前記第1のソース及びドレイン領域は、ゲート長方向における前記第1のゲート電極の両側方であって前記第1のサイドウォールスペーサの外側を含む領域に形成されている半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記半導体基板における第2の素子領域上に設けられたMISFETをさらに備え、

前記MISFETは、前記半導体基板内に形成された第1導電型の半導体領域と、前記半導体領域上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された第2のゲート電極と、前記第2のゲート電極の両側面上に形成された第2のサイドウォールスペーサと、ゲート長方向における前記第2のゲート電極の両側方に位置する領域に形成された第2導電型の第2のソース及びドレイン領域とを有していることを特徴とする半導体装置。

【請求項3】

請求項2に記載の半導体装置において、

前記第1のサイドウォールスペーサと前記第2のサイドウォールスペーサとは同一の膜を加工することで形成されることを特徴とする半導体装置。

【請求項4】

請求項2又は3に記載の半導体装置において、

前記第1のゲート電極は、前記上部ゲート領域と直接接していることを特徴とする半導体装置。

【請求項5】

請求項2又は3に記載の半導体装置において、

前記第1のゲート電極は、絶縁膜を介して前記上部ゲート領域と接していることを特徴とする半導体装置。

【請求項6】

請求項5に記載の半導体装置において、

前記絶縁膜と前記ゲート絶縁膜とは互いに同一の材料で構成されていることを特徴とする半導体装置。

【請求項7】

請求項2〜6のうちいずれか1つに記載の半導体装置において、

前記第1のサイドウォールスペーサと前記チャネル領域との界面位置は、前記第1のゲート電極と前記上部ゲート領域との界面位置よりも低いことを特徴とする半導体装置。

【請求項8】

請求項2〜6のうちいずれか1つに記載の半導体装置において、

前記第1のゲート電極及び前記第2のゲート電極は、共に金属又は導電性の金属化合物で構成されていることを特徴とする半導体装置。

【請求項9】

請求項8に記載の半導体装置において、

前記第1のゲート電極と前記第2のゲート電極とは互いに同じ材料で構成されていることを特徴とする半導体装置。

【請求項10】

請求項2〜8のうちいずれか1つに記載の半導体装置において、

前記第1のゲート電極と前記第2のゲート電極とは互いに同じ材料で構成されており、

前記第1のソース及びドレイン領域と前記第2のソース及びドレイン領域とは、互いに同じ深さで形成されており、且つ前記第1のソース及びドレイン領域の不純物濃度と前記第2のソース及びドレイン領域の不純物濃度とは実質的に等しいことを特徴とする半導体装置。

【請求項11】

請求項2〜7のうちいずれか1つに記載の半導体装置において、

前記第1のソース及びドレイン領域上、前記第2のソース及びドレイン領域上、前記第1のゲート電極上、及び前記第2のゲート電極上にはそれぞれシリサイド層が形成されており、

前記第1のソース及びドレイン領域上に形成された前記シリサイド層は、前記チャネル領域のうち前記第1のサイドウォールスペーサの下に位置する部分を挟んで前記上部ゲート領域と互いに離間していることを特徴とする半導体装置。

【請求項12】