半導体装置及びその製造方法

【課題】放射線耐性能力をさらに向上することができる半導体装置を提供する。

【解決手段】半導体基板1の上方に形成された第1絶縁膜12と、第1絶縁膜12の上方に形成され、下部電極17と上部電極19に挟まれる強誘電体膜18を有するキャパシタQと、キャパシタの上に形成される第2絶縁膜26と、を有し、第1絶縁膜12と下部電極17の間に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第3絶縁膜16、38と、

を有する。

【解決手段】半導体基板1の上方に形成された第1絶縁膜12と、第1絶縁膜12の上方に形成され、下部電極17と上部電極19に挟まれる強誘電体膜18を有するキャパシタQと、キャパシタの上に形成される第2絶縁膜26と、を有し、第1絶縁膜12と下部電極17の間に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第3絶縁膜16、38と、

を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、デジタル技術の進展に伴い、大容量のデータを高速に処理又は保存する傾向が高まっている。このため、電子機器に使用される半導体装置の高集積化及び高性能化が要求されている。

【0003】

そこで、半導体記憶装置、例えばDRAMの高集積化を実現するため、DRAMを構成する容量素子の容量誘電体膜として、従来の珪素酸化物又は珪素窒化物に代えて、強誘電体材料又は高誘電率材料を用いる技術が広く研究開発され始めている。

【0004】

また、より低電圧で且つ高速での書き込み動作及び読み出し動作が可能な不揮発性RAMを実現するため、容量誘電体膜として、自発分極特性を有する強誘電体膜を用いる技術も盛んに研究開発されている。このような半導体記憶装置は、強誘電体メモリ(FeRAM)とよばれる。

【0005】

FeRAMは、強誘電体のヒステリシス特性を利用して情報を記憶する。強誘電体膜を1対の電極間のキャパシタ誘電体膜として有する強誘電体キャパシタは、電極間の印加電圧に応じて分極を生じ、印加電圧を取り去っても自発分極を有する。印加電圧の極性を反転すれば、自発分極の極性も反転する。この自発分極を検出すれば情報を読み出すことが出来る。FeRAMは、高速動作が可能であり、低消費電力であり、書き込み/読み出し耐久性に優れている等の特徴を有する不揮発性メモリであり、今後の更なる発展が見込まれている。

【0006】

一方、近年の宇宙開発では日進月歩で開発が進む民生半導体部品の宇宙転用が進んでいる。また、RFIDや半導体メモリは、医療・ヘルスケア分野に応用へ目指している。そのような分野では、例えば、衛生品にICタグ(TAG)を付けてγ(ガンマ)線で滅菌する。しかしながら、ほとんどの民生部品は、耐放射線性を考慮していないので、放射線試験を行うと、ICタグの信頼性が失われてしまう。

【0007】

信頼性の高いシステムを構築するためには、システム設計段階において考慮すべきことがある。それは半導体メモリにおけるソフトエラーである。例えば、地球にやさしい放射線(ガンマ線、電子線)滅菌方法は、高圧蒸気滅菌法と比べて常温処理であって温度上昇がなく、最終梱包(密閉状態)で滅菌可能であり、また、エチレンオキシド滅菌法と比べて有害な残留物や副生成物などが一切残らない。従って、多数のメリットを持つ放射線(ガンマ線や電子線)による滅菌方法は、広く使用される。従って、滅菌される物品に搭載するFRタグ(RF−TAG)は、放射線照射によるチップのソフトエラーを解決できれば、製品の履歴管理など広く使用できる。

【0008】

高性能通信用半導体メモリの分野では、ソフトエラーやシングルイベント・アップセット(Single-event upset:SEU)に影響されない設計が重要である。ソフトエラーは、ほかの信頼性メカニズムのすべてを含めたものの中でも、最も高い不良率を引き起こしている。半導体技術が進化するにつれて、プロセッサーのパイプライン段数は増加し、メモリセルの有効面積は減少している。その結果、シングルイベント・アップセットに対する素子固有の耐性が低下している。シングルイベント効果は、高エネルギーの外部放射線粒子が引き起こす素子内部の状態の変化、あるいは過渡現象に関係しており、ソフトエラー

とハードエラーに分類できる。

【0009】

ソフトエラーは、メモリ素子をリセットしたりリライトしたりすることによって正常な動作に戻すことができるため、非破壊的なエラーといえる。これに対して、ハードエラーは永久的なもので、ハードエラーの代表的な例はシングルイベント・ラッチアップ(single-event latch-up:SEL)である。

【0010】

主に外部放射線に起因するソフトエラーは、またの名をシングルイベント・アップセットともいう。シングルビット・アップセットは、単一の高エネルギー放射線粒子の通過による1ビットの反転を指し、ほかの反転ビットからは物理的にメモリセル2個分以上、離れているものである。それに対してマルチビット・アップセットは、1つ以上の放射線粒子の通過による数エレメントの反転を指している。

【0011】

シングルイベント・アップセットはランダムに発生するが、破滅的なエラーであることは非常に珍しく、通常は素子を破壊することはない。そして、多くのシステムはある程度のソフトエラー、つまりここでいうシングルイベント・アップセットには耐えることができる。

【0012】

半導体の微細化は、産業界での生き残りのための主要な原動力となっており、また、高集積化や性能の向上およびコスト低減のための原動力ともなっている。半導体技術の進化により、ゲート長をディープサブミクロンのレベルまで縮小するにつれて、メモリ製品のセル寸法も減少し続け、駆動電圧も低下し、そしてセル内部の容量も減少している。例えば、駆動電圧は、5Vから3.3V、1.8Vからさらに低電圧へと変化している。また、容量は、10fFから5fF、そしてさらに低容量へと変化している。低容量化が進むにつれてメモリセルの臨界電荷量は縮小を続け、それによってメモリセルのシングルイベント・アップセットに対する耐性も低下している。それに従い、低エネルギー・アルファ線、あるいは宇宙線粒子もセルを妨害する要因となっている。

【0013】

半導体での空乏領域の電界は、その通った跡に電子・正孔対を一直線に生成し、電荷が浮遊する。その結果、トランジスタには電流の乱れが生じる。電界の影響下にある空乏領域は自由電子を捕捉する。わずかな過剰電荷がデバイスノードに浮遊し、これがある臨界電荷量を超えるとメモリセルの状態を反転させることになる。臨界電荷量が小さければ小さいほどソフトエラーレートは高くなる。アルファ線は低エネルギーを有しているため通常はシングルビット・アップセットを引き起こすが、低い供給電圧のメモリではマルチビット・アップセットを引き起こすこともある。

【0014】

高エネルギー宇宙線粒子は地球の高層大気と反応し、それらの衝突が太陽フレアーや銀河宇宙線粒子により変調され、高エネルギー陽子や中性子を生成する。高エネルギー中性子は10MeV〜800MeVのエネルギーを持っている。一方、陽子は30MeV以上のエネルギーを持っている。高エネルギー中性子は電荷を持たない。従って、これらはクーロン力による半導体材料との相互作用はない。そのためシリコンとの相互作用は、低エネルギー・アルファ線の場合とは異なる。

【0015】

高エネルギー中性子がソフトエラーを引き起こすためには、シリコンの原子核と衝突し、シリコン原子核のイオン化の衝撃を受けることにより、イオン化された粒子を生成しなくてはならない。この衝突はアルファ線や、より重いイオンを生成することがある。衝突によって生まれたものは、プラスチックモールド材からの通常のアルファ線よりも、高エネルギーを持つ電子・正孔対を生成する。

【0016】

一般に高性能メモリは、例えばSRAMセル、組み合わせ論理、ラッチ回路などで構成

されている。高性能通信用メモリでは、通常、チップの面積効率は低い。過去の学術研究では、組み合わせ論理はマスキングによる自然の耐性のために、通常のメモリセルに比べソフトエラーの影響を受けにくいということが示されている。しかしながら、素子の大きさとプロセッサーのパイプラインの段数を増やせば、この自然の耐性を低下させることになる。

【0017】

素子のシングルイベント・アップセットに対する耐性を向上させる別の方法は、メモリセル内に蓄える臨界電荷量を増やし、そのしきい値を増加させることである。

【0018】

その他に、絶縁物上にシリコン結晶を成長させ、その上にトランジスタなどを集積するSOI技術(Silicon On Insulator)を使用し、電荷の深さを減少させることにより素子の信頼性を向上させる方法がある。p型MOSトランジスタの閾値電圧はセルのリカバリー時間に影響し、これは間接的にシングルイベント・アップセットに対する耐性にも影響を与える。

【0019】

半導体装置の封入に用いるパッケージの材料として、Pb、Hf、Ir、Mo、Os、Pd、Pt、Re、Ta、Tb、Tl、W、Uのうちの少なくとも1種類の元素を重量比で1%以上含ませたセラミツクあるいは樹脂を用いることにより、有効に放射線を遮蔽するパッケージを得ることが知られている(特許文献1)。

【0020】

また、鉛またはタリウムの化合物を、半導体チップ上に塗布または添付し、あるいは樹脂材料に含有させて封止することにより、α線による影響を低減しメモリ等のソフトエラーを防止することが知られている(特許文献2)。

【先行技術文献】

【特許文献】

【0021】

【特許文献1】特開昭60−134448号公報

【特許文献2】特開昭57−090966号公報

【発明の概要】

【発明が解決しようとする課題】

【0022】

しかしながら、封入用パッケージを改善しても、EEPROMのように放射線に対する半導体装置の耐性が低いものも存在するし、放射線耐性能力が比較的高い半導体装置であってもさらなる耐性能力の向上が要求されるものもある。

【0023】

本発明の目的は、放射線耐性能力をさらに向上することができる半導体装置及びその製造方法を提供することにある。

【課題を解決するための手段】

【0024】

本実施形態の1つの観点によれば、半導体基板の上方に形成された第1絶縁膜と、

前記第1絶縁膜の上方に形成され、下部電極と上部電極に挟まれる強誘電体膜を有するキャパシタと、前記キャパシタの上に形成される第2絶縁膜と、を有し、前記第1絶縁膜と前記下部電極の間に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第3絶縁膜と、を有する半導体装置が提供される。

発明の目的および利点は、請求の範囲に具体的に記載された構成要素および組み合わせによって実現され達成される。前述の一般的な説明および以下の詳細な説明は、典型例および説明のためのものであって、本発明を限定するためのものではない、と理解される。

【発明の効果】

【0025】

本実施形態によれば、キャパシタ下部電極の下に、Pb又はBiが添加された結晶を持

つ第3絶縁膜を形成している。Pb又はBiが添加された結晶を有する第3絶縁膜は、例えば200nm以下に薄く形成しても高い放射線耐性能力を有することが本発明者によって確認された。また、第3絶縁膜は、その上のキャパシタの強誘電体膜の結晶性を改善するための加熱の際に同時に加熱されるので、加熱処理を追加することなくその結晶性を改善することができる。

従って、外部から半導体装置内に向けて放射線が照射されても、放射線は第3絶縁膜により部分吸収されて、キャパシタの誘電体膜に到達する放射線の輻射が軽減される。さらに、Pb又はBiが添加された絶縁膜は、成膜当初においてアモルファスに形成することにより平坦性を良好にできるので、その上に形成されるキャパシタの下部電極とその上の強誘電体膜の結晶性を良好にすることができる。これらにより、キャパシタのメモリ書き込み能力、メモリ保持能力を高めることができる。

【図面の簡単な説明】

【0026】

【図1A】図1A、図1Bは、第1実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図1C】図1C、図1Dは、第1実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図1E】図1E、図1Fは、第1実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図1G】図1G、図1Hは、第1実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

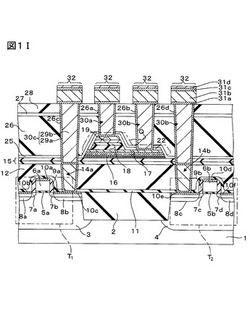

【図1I】図1Iは、第1実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図2】図2A、図2B及び図2Cは、第1実施形態に係る半導体装置に書き込まれるデータのガンマ線照射量依存特性を例示する図である。

【図3】図3は、第2実施形態に係る半導体装置を例示する断面図である。

【図4】図4は、第3実施形態に係る半導体装置を例示する断面図である。

【図5】図5は、第3実施形態に係る半導体装置の別の例を示す断面図である。

【図6】図6は、第3実施形態に係る半導体装置をさらに別の例を示す断面図である。

【図7A】図7A、図7Bは、第4実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図7C】図7C、図7Dは、第4実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図7E】図7Eは、第4実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図8】図8は、強誘電体の典型であるPZTの結晶構造の一例を示す図である。

【図9】図9は、PZTから誘電体膜を形成した構造を有する強誘電体キャパシタのヒステリシス曲線を示す。

【発明を実施するための形態】

【0027】

まず、不揮発性メモリであるFeRAM及びEEPROMのガンマ線照射後のデータの状況を表1に示す。評価サンプル(タグ形状)は、2KバイトのFeRAMを搭載した第1のRFID−LSIと、128バイトのEEPROMを搭載した第2のRFID−LSIであり、それぞれ10個用意した。評価内容は次の(1)〜(3)の処理を行い、評価により正常であったサンプルの数をPASSとして示している。

(1)メモリ領域、指定ブロックに右記データパターンを書き込む。

(2)20kGy、50kGy、100kGyのガンマ線を照射する。

(3)メモリ領域のデータを読み出し、照射前後のデータを比較する。

【表1】

【0028】

評価結果によれば、EEPROMは最低の20kGyのガンマ線照射量であってもデータが全滅する。つまり、EEPROMなどの電子の蓄積によりデータを保持する構成のメモリの場合、ガンマ線照射により電子が励起され、データが破壊される。これに対し、3VのReRAM品は、最大の100kGyのガンマ線照射量であってもデータが保持されることを確認した。

【0029】

次に、1.8VのFeRAM品(スタンダードセル、ゲートアレイ)をガンマ線照射後データの状況を表2、表3に示す。表2、表3の結果により、SS(Same State)/OS(Opposite State)共に照射量増加に伴って誤り(FAIL)数が増加する。即ち、規格値である照射量50kGyでも厳しい結果となっている。

なお、SSは、ガンマ線の照射前の書込みと同じ分極状態での読取りを表し、OSは、ガンマ線照射前の書込みと逆の分極状態での読取りを表しています。

【表2】

【表3】

【0030】

図8には、強誘電体の典型であるPZT(チタン酸ジルコン酸鉛)の結晶構造を示し、図9には、PZTから誘電体膜を形成した構造の強誘電体キャパシタのヒステリシス曲線を示す。鉛(Pb)、ジルコニウム(Zr)、チタン(Ti)、酸素(O)を含むPZT

(Pb(ZrTi)O3)は、図8に示すようなペロブスカイト構造(ABO3型)の代表的な強誘電体材料であり、正方体の各頂点にPbが、体心にZrやTiが配置され、そしてZrやTiを中心としてOは正方晶の各面心に配置している。

【0031】

酸素と金属ZrやTiから成る八面体の向きは、Pbとの相互作用により容易に歪みが発生する。格子の中にZr/Tiイオンが置かれているが、このイオンは二つの安定点を持ち、外部の電界によってその位置を変える性質、即ち分極作用がある。さらに、一度どちらの点に位置すると電界を取り去ってもその位置が変わることはない。つまり、分極状態が記憶される。従って、強誘電体膜の上下に電極を設けてキャパシタを構成し、電極電圧と分極方向と分極量をプロットすればヒステリシス(履歴)が得られ、“1”、“0”を記憶できることになる。

【0032】

このような分極による記憶状態は安定であり、その原理を利用すると、外部電界を印加すると分極が発生し、Zr/Tiイオンが結晶内部で上下する。さらに、電界をかけるのを止めても分極はそのままの状態で残り、残留分極が生じる。2つの安定点をデータ“1”とデータ“0”として記憶する。

【0033】

従って、FeRAMではデータの保持は結晶の原子配置によってなされるため、ガンマ線に照射されても、原則として上記の問題は起こらない。しかしながら、分極反転特性の劣化は照射量に応じて生じるため、データ読み出し精度が低下し、ミスリードを引き起こすことがある。従って、従来のFeRAMの構造では、耐放射線照射能力は不十分であり、特に低電圧動作メモリの耐放射線能力を向上させる必要がある。

【0034】

以上のことから、強誘電体キャパシタを有する半導体装置は、キャパシタの誘電体膜に放射線の被爆量を低減させ、キャパシタを低電圧で動作させ、耐インプリント特性及び耐放射線照射能力を向上させ、信頼性を高くすることが要求される。

【0035】

以下に、図面を参照して本発明の実施形態を説明する。図面において、同様の構成要素には同じ参照番号が付されている。

(第1の実施の形態)

図1A〜図1Iは、第1実施形態に係る半導体装置及びその製造方法を示す断面図である。本実施形態による半導体装置は、メモリセルのキャパシタがプレーナ型となる構造を有している。次に、図1Aに示す構造を形成するまでの工程を説明する。

【0036】

まず、半導体基板であるシリコン基板1の活性領域の周囲に素子分離用溝1uを形成した後に、その中に絶縁膜として例えばシリコン酸化膜を埋込む。素子分離用溝1uの中の絶縁膜は、素子分離絶縁構造であるSTI(Shallow Trench Isolation)2として使用される。なお、素子分離絶縁構造は、STI2に限られるものではなく、LOCOS法により形成されてもよい。

【0037】

ついで、シリコン基板1の一部の活性領域にp型不純物をイオン注入して第1、第2のPウェル3、4を形成し、さらに、別の活性領域にn型不純物を導入してNウェル(不図示)を形成する。第1のPウェル3と第2のPウェル4は、STI2を介して隣接している。なお、p型不純物、n型不純物のいずれかイオン注入する際には、不純物を注入しない領域をレジストパターン(不図示)で覆う。

【0038】

さらに、シリコン基板1の活性領域の表面を熱酸化することによりシリコン酸化膜を形成し、そのシリコン酸化膜をゲート絶縁膜5a、5bとして使用する。ゲート絶縁膜5a、5bの膜厚は、例えば6〜7nm程度とする。

【0039】

続いて、シリコン基板1の主面の上方にポリシリコン膜をCVD法により例えば約200nmの厚さに形成した後に、フォトリソグラフィ技術を用いてポリシリコン膜をパターニングしてPウェル3、4の上に第1、第2のゲート電極6a、6bを形成する。第1、第2のゲート電極6a、6bは、STI2の上にも形成されるワード線の一部である。また、第1、第2のゲート電極6a、6bは、第1、第2のPウェル3、4上に複数形成されてもよい。

【0040】

次に、第1、第2のゲート電極6a、6bをマスクに使用して第1、第2のPウェル3、4内にn型不純物、例えばリン(P)をイオン注入法により導入する。これにより、第1、第2のPウェル3、4のうち第1、第2のゲート電極6a、6bの両側に浅いn型エクステンション領域7a、7b、7c、7dを形成する。

【0041】

その後に、シリコン基板1の上側全面に絶縁膜を形成し、その絶縁膜をエッチバックして第1、第2のゲート電極6a、6bの側面に絶縁性のサイドウォール9a、9bとして残存させる。その絶縁膜として、例えばCVD法により酸化シリコン膜を例えば約300nmの厚さに形成する。

【0042】

続いて、サイドウォール9a、9bとゲート電極6a、6bをマスクに使用し、シリコン基板1内にn型不純物、例えば砒素(As)をイオン注入する。これにより、第1、第2のゲート電極6a、6bの両側方の第1、第2のPウェル3、4内にエクステンション領域7a、7b、7c、7dよりも深く且つ高不純物濃度の不純物拡散領域を形成する。それらの不純物拡散領域は、エクステンション領域7a、7b、7c、7dに一部が接続されるソース/ドレイン領域8a、8b、8c、8dとして使用される。

【0043】

次に、シリコン基板1の上の全体に、例えばスパッタリング法により、高融点金属膜、例えばコバルト膜を形成する。続いて、露出しているソース/ドレイン領域8a、8b、8c、8dとゲート電極6a、6bのそれぞれの上層と高融点金属膜とを熱処理により反応させる。これにより、ソース/ドレイン領域8a、8b、8c、8dとゲート電極6a、6bの上にそれぞれシリサイド層10a〜10f、例えばコバルトシリサイド層が形成される。その後に、例えばウエットエッチングにより、残された高融点金属膜をエッチング除去する。

【0044】

以上のような方法により形成された第1のPウェル3、ゲート絶縁膜5a、第1のゲート電極6a、ソース/ドレイン領域8a、8b等により第1のNMOSトランジスタT1が形成される。また、第2のPウェル4、ゲート絶縁膜5b、第1のゲート電極6b、ソース/ドレイン領域8c、8d等により第2のNMOSトランジスタT2が形成される。

【0045】

その後に、シリコン基板1上の全面に、第1、第2のNMOSトランジスタT1、T2を覆うカバー絶縁膜11として例えばシリコン窒化酸化膜をプラズマCVD法により例えば約200nmの厚さに形成する。さらに、カバー絶縁膜11上に、第1層間絶縁膜12として、例えばTEOS(Tetra Ethoxy Silane)ガスを用いるプラズマCVD法によりシリコン酸化膜を例えば約1μmの厚さに形成する。続いて、例えば化学機械研磨(CMP)法により第1層間絶縁膜12の上面を平坦化する。これにより、半導体基板1の主面から第1層間絶縁膜12の上面までの高さは、例えば785nm程度となる。

【0046】

次に、図1Bに示す構造を形成するまでの工程を説明する。

まず、フォトリソグラフィ技術を用い、第1層間絶縁膜12のうち第1、第2のPウェル3、4内のうち互いに近いそれぞれの一方のソース/ドレイン領域8b、8cの上をエッチングし、シリサイド層10d、10eに達する第1、第2のコンタクトホール12a、12bを形成する。第1、第2のコンタクトホール12a、12bの径を例えば約0.

25μmとする。

【0047】

次に、第1層間絶縁膜12の上面と第1、第2のコンタクトホール12a、12bの内面に、例えば、スパッタリング法により厚さ30nmのTi膜と厚さ20nmのTiN膜を順に形成する。Ti膜とTiN膜は、密着膜13aとなる。続いて、密着膜13aの上に、コンタクトホール12a、12b内を完全に充填する厚さに主導体膜13bとしてタングステン(W)をCVD法により形成する。主導電膜13bの膜厚は、例えば300nm程度とする。

【0048】

その後に、例えばCMP法により、第1層間絶縁膜12の上面が露出するまで主導電膜13b及び密着膜13aを研磨する。こうして、第1、第2のコンタクトホール12a、12b内に残された主導体膜13b及び密着膜13aを第1、第2の導電プラグ14a、14bとして使用する。

【0049】

次に、図1Cに例示する構造を形成するまでの工程について説明する。

まず、第1層間絶縁膜12及び第1、第2の導電プラグ14a、14bの上に、例えば、シリコン窒化酸化膜15aをプラズマCVD法により例えば約100nmの厚さに形成する。シリコン窒化酸化膜15aは、後述するキャパシタからの水分の移動を抑制するとともに、第1、第2の導電プラグ14a、14bの上面の酸化を防止するために形成される。

【0050】

次に、シリコン窒化酸化膜15a上に、例えば、TEOSガスを使用し、プラズマCVD法によって後述の密着絶縁膜16とともに密着性を向上するための絶縁膜としてシリコン酸化膜15bを形成する。シリコン酸化膜15bの膜厚を例えば約130nmとする。

【0051】

シリコン窒化酸化膜15bとシリコン酸化膜15aとにより第2層間絶縁膜15が形成される。なお、第2層間絶縁膜15は、シリコン窒化酸化膜15aとシリコン酸化膜15bとの積層膜に限定されるものではない。例えば、酸化防止膜として、シリコン窒化酸化膜15aの代わりにシリコン窒化膜や酸化アルミニウム膜を形成してもよい。

【0052】

続いて、例えば窒素雰囲気中にて、熱処理を行う。かかる熱処理は、第2層間絶縁膜15中に含まれているガスを放出するため、即ち脱ガスのためである。この熱処理を行う際の基板温度は、例えば約650℃とし、熱処理時間は、例えば約30分とする。

【0053】

次に、第2層間絶縁膜15上に、例えば、高周波スパッタリング法によりアモルファスの密着絶縁膜16を形成する。密着絶縁膜16は、後述するキャパシア下部電極17に対する密着性を確保するとともに、放射線を遮断するために形成される。

【0054】

密着絶縁膜16としては、Pb又はBi(ビスマス)添加した絶縁膜、例えば、強誘電体膜であるチタン酸ジルコン酸鉛(PZT:(PbZrxTi1−xO3))膜(0≦x≦1)、又はCa、Sr、Laが少なくともに一つ元素添加されたチタン酸ジルコン酸鉛、又はビスマス層状結晶構造を持つ(Bi,Sr)TiO3、(Bi,La)4Ti3O12膜等が用いられている。その以外に、Pb又はBi添加したPbAl2O4、PbAl2O5、PbZrO3、PbTiO3、PbSiO3、Pb(Zr,Ti)O3、BiAlO3、BiGaO3、SrBi2Ta2O9、Bi4Ti2O12膜などでもよい。密着絶縁膜16は、それらの材料から選択した二つ膜を積層した構造であってもよい。

【0055】

密着絶縁膜16としてPZT膜を用いる場合には、その膜厚は、例えば、10nm〜50nm程度、より好ましくは、20nm〜30nm程度に形成される。PZTを高周波スパッタリング法により形成する際の成膜条件は、例えば次の通りとする。まず、ターゲッ

トとしてジルコニウムチタン酸鉛からなるPZT系ターゲットを使用する。また、基板温度は、例えば約50℃に設定される。さらに、成膜室内に導入するガスとしては、例えばArガスを用いる。成膜室内の圧力は、例えば約1Paとする。印加電力は、例えば1.0kWとする。ここでは、密着絶縁膜16の膜厚を、例えば約20nmとする。

【0056】

次に、密着絶縁膜16上に、第1の導電膜17aとして貴金属膜を例えばスパッタリング法により形成する。第1の導電膜17aは、後述するキャパシタQの下部電極17の一部となるものである。第1の導電膜17aとして、例えば50nm〜150nm程度のPt膜を形成する。第1の導電膜17aを形成する際の成膜条件は、例えば次の通りとする。ターゲットとしてPtを使用する。また、基板温度は、例えば350℃に設定される。成膜室内に導入するガスとして例えばArガスを用いる。成膜室内の圧力は、例えば約1Paとする。また、印加電力を例えば約0.3kWに設定する。

【0057】

ここでは、第1の導電膜17aとして、プラチナ膜を形成する場合を例に説明したが、第1の導電膜17aはプラチナ膜に限定されるものではなく、Ir膜、Ru膜、酸化ルテニウム(RuO2)膜、SrRuO3膜等を形成してもよい。また、それらのうちいずれかを選択した積層膜により第1の導電膜17aを形成してもよい。

【0058】

次に、第1の導電膜17aの上に第2の導電膜17bを形成する。第2の導電膜17bとして、例えば厚さ0.1〜3nmの酸化プラチナ膜(PtOx膜)を形成する。第1の導電膜17aとして例えばIr膜やRu膜を用いる場合には、第2の導電膜17bとして下とは異なる例えばIr膜やRu膜を用いてもよい。この場合、第2の導電膜17bとしてIr膜を形成する場合には、Ir膜を例えば10〜30nm程度の厚さに形成する。

【0059】

また、第1の導電膜17aとして、Pt膜、Ir膜、Ru膜を用いる場合には、第2の導電膜17bとして、SrRuO3膜、LaSrMnO3膜、LaSrCoO3膜等を用いてもよい。この場合には、SrRuO3膜、LaSrMnO3膜又はLaSrCoO3のそれぞれの膜厚は、例えば1〜5nm程度であることが好ましい。

【0060】

次に、第2の導電膜17aの上に、第1の誘電体膜18aを形成する。第1の誘電体膜18aは、スパッタリング法により形成される。第1の誘電体膜18aとして、例えば、強誘電体膜を形成する。第1の誘電体膜18aは、ペロブスカイト型結晶構造又はビスマス層状化粧構造であってABOx型の結晶構造を持つ。この場合、金属種AがLi、Na、Ca、Sr、Ba、Laから選ばれる一種類以上の金属であり、金属種BがTi、Zr、Ta、Nbから選ばれる一種類以上の金属であり、酸素Oはx(正の数)の組成比を有する。

【0061】

第1の誘電体膜18aとして、例えば、チタン酸ジルコン酸鉛(PZT:PbZrxTi1−xO3)膜(0≦x≦1)、またはCa、Sr、Laが少なくともに一つ元素添加されたチタン酸ジルコン酸鉛が用いられる。または、ビスマス層状結晶構造を持つ(Bi,Sr)TiO3、チタン酸ビスマスランタン酸化物(BLT:(Bi,La)4Ti3O12)膜、ストロンチウム・ビスマス・タンタル酸化物(SBT:SrBi2Ta2O9)等が用いられる。

【0062】

PZT膜を用いる場合には、第1の誘電体膜18aの膜厚を例えば30nm〜90nm程度とする。より好ましくは、第1の誘電体膜18aの膜厚を、例えば50nm〜70nm程度とし、ここでは、例えば約60nmとする。

【0063】

第1の誘電体膜18aの成膜温度を例えば30℃以上、100℃以下とすることが好ましい。第1の誘電体膜18aの成膜温度を30℃より低く設定する場合には、ウェハ面内

において膜厚及び結晶性が不均一となってしまう場合がある。これに対し、第1の誘電体膜18aの成膜温度を100℃より高く設定する場合には、第1の誘電体膜18aにおいて、(101)配向及び(100)配向が多くなり、(111)配向が少なくなるので、良好な電気的特性のキャパシタの誘電体膜を得ることが困難となることがある。従って、本実施形態では、第1の誘電体膜18aの成膜温度を、例えば50℃に設定する。

【0064】

また、第1の誘電体膜18aを形成する方法はスパッタリング法に限られるものではない。例えば、MOCVD(Metal Organic Chemical Vapor Deposition、有機金属化学気相成長)法、ゾル・ゲル法、有機金属分解(MOD、Metal Organic Deposition)法、化学溶液堆積(CSD、Chemical Solution Deposition)法、CVD法、等により、アモルファスの第1の誘電体膜18aを形成してもよい。

【0065】

次に、例えばRTA法により、酸素を含む雰囲気中にて、第1の誘電体膜18aを結晶化する。より具体的には、不活性ガス、例えばアルゴンと酸素ガスとを含む混合ガスの雰囲気中にて、第1の誘電体膜18aを熱処理する。熱処理時間は、例えば90秒とする。第1の誘電体膜18aの結晶性を向上するためには酸素ガス流量を10〜70sccm、例えば25sccmとすることが好ましい。

【0066】

第1の誘電体膜18aの材料としてPZTが用いられている場合には、熱処理温度、即ち基板温度は、例えば550℃〜650℃に設定される。ここでは、第1の誘電体膜18aを結晶化する際の熱処理温度を、例えば600℃とする。適切な熱処理温度は、強誘電体材料の種類により異なる。例えば、PZTや、その他の元素を微量添加するPZTの熱処理温度は630℃以下、BLTは700℃以下、SBTは800℃以下が望ましい。この熱処理により第1の誘電体膜18aは結晶化される。同時に、第1の誘電体膜18aと第2の導電膜17bの界面も密着性が高く制御されている。さらに、密着絶縁膜16の少なくとも一部も同時に結晶化され、その一部はPb又はBi(ビスマス)添加した正方体の結晶絶縁膜となる。

【0067】

次に、第1の誘電体膜18aの上に、アモルファスの第2の誘電体膜18bを例えばスパッタ法により形成する。第2の誘電体膜18bとしては、例えば膜厚が1nm〜30nm、例えば約10nmの強誘電体膜を形成する。第2の誘電体膜18bの材料としては、PZT、PLZT、或いはLaとCaとSrとが添加されたチタン酸ジルコン酸鉛が用いられる。

【0068】

次に、第2の誘電体膜18bの上に第1の導電性酸化膜19aを形成する。第1の導電性酸化膜19aは、Pt、Ir、Ru、Rh、Re、Os、Pdからなる群から選択された少なくとも1種の元素の酸化物から形成される。例えば、第1の導電性酸化膜19aの形成に当たっては、先ず、第2の誘電体膜18b上に、厚さが20〜70nm、例えば約25nmで成膜の時点で結晶化したIrOx膜をスパッタ法により形成する。このときの成膜温度を例えば約300℃とし、成膜ガスとしてAr及びO2を用い、これらの流量Ar=140sccm、O2=60Sccmとする。また、スパッタパワーは、例えば1kW程度とする。

【0069】

ついで、RTA法でシリコン基板1を加熱する。その加熱条件は、温度を725℃に設定し、酸素を流量20Sccm、Arを流量2000Sccmで雰囲気中に導入するとともに、熱処理時間を60秒間とする。この熱処理は第1の誘電体膜18aの結晶性を更に向上し、非晶質の第2の誘電体膜18bを結晶化する。同時に、密着絶縁膜16の結晶性も向上する。

【0070】

第1、第2の誘電体膜18a、18bを完全に結晶化させる同時に、第1の導電性酸化

膜19aのプラズマダメージも回復でき、第1、第2の誘電体膜18a、18bは、連続的な柱状結晶を持つ誘電体膜になる。同時に、第1、第2の誘電体膜18a、18b中の酸素欠損を補償する。第1、第2の誘電体膜18bは、ペロブスカイト型結晶構造、ビスマス層状結晶構造のいずれかのABOx型結晶構造を持つことが好ましい。

【0071】

次に、第1の導電性酸化膜19aの上に、例えばスパッタリング法により、第2の導電性酸化膜19bを形成する。第第1、第2の導電性酸化膜19a、19bは、パターニングにより後述するキャパシタQの上部電極19となるものである。第2の導電性酸化膜19bとしては、例えば酸化イリジウム膜を形成する。

【0072】

第2の導電性酸化膜19bとして形成される酸化イリジウム膜(IrOy膜)における酸素の組成比yは、例えば0<y≦2とする。第2の導電性酸化膜19bとして形成される酸化イリジウム膜(IrOy膜)における酸素の組成比yは、第1の導電性酸化膜19aとして形成される酸化イリジウム膜(IrOx膜)における酸素の組成比xより大きいことが好ましい。

【0073】

第2の導電性酸化膜19bにおける酸素の組成比を第1の導電性酸化膜19aにおける酸素の組成比より大きく設定する理由は、酸素の組成比を大きく設定すると水素の拡散を防止する機能が大きくなるからである。第2の導電性酸化膜19bが水素バリア膜としても十分に機能し得るため、第1、第2の誘電体膜18a、18bが水素により還元されるのを防止しできる。第2の導電性酸化膜19bの膜厚は、例えば70〜200nm程度に形成されることが好ましく、より具体的には例えば約150nm程度とする。

【0074】

第2の導電性酸化膜19bを成膜する際のスパッタリングによる成膜条件は、例えば次の通りとする。成膜室内に導入するガスは、例えばアルゴンガスを例えば100sccm、酸素ガスを例えば100sccmで導入して混合ガスとする。成膜室内の圧力は、例えば0.8Paとする。スパッタパワーは、例えば1.0kWとする。成膜時間は、例えば59秒間程度とする。このような成膜条件で第2の導電性酸化膜19bを成膜すると、第2の導電性酸化膜19bの膜厚は、例えば約150nm程度となる。

【0075】

その後に、ウェハ状のシリコン基板1の主面と反対側の下面(裏面)を洗浄する。このような背面洗浄は、一般のウェハ洗浄とは異なるものであり、シリコン基板1の裏面に付着した誘電体膜18a、18bを除去するためのものである。

【0076】

次に、第2の導電性酸化膜19b上に、保護膜20を例えばスパッタリング法により形成する。保護膜20として、例えば34nm程度の厚さを有するTiN膜を形成する。保護膜20を形成する際には、例えばTiのターゲットを用いる。保護膜20を形成する際の基板温度は、例えば150℃とする。成膜室内における雰囲気は、例えば流量50sccmのArガスと流量90sccmのN2ガスとの混合ガスの雰囲気とする。保護膜20は、還元性物質をバリアする機能を有するものであり、第1、第2の導電性酸化膜19a、19bをパターニングする際のハードマスクとしても機能する。

【0077】

ここでは、保護膜20としてTiN膜を形成する場合を例に説明したが、TiN膜に限定されるものではない。保護膜20として、例えば、TaN膜、TiON膜、TiOx膜、TaOx膜、TaON膜、TiAlOx膜、TaAlOx膜、TiAlON膜、TaAlON膜、TiSiON膜、TaSiON膜、TiSiOx膜、TaSiOx膜、AlOx膜、ZrOx膜等を形成してもよい。

【0078】

次に、保護膜20上に、例えばフォトレジスト膜(不図示)をスピンコート法により形成する。続いて、フォトリソグラフィ技術を用い、上部電極となるパターンの長さ方向に

ある2つの対向辺を区画するストライプ平面形状にフォトレジスト膜(不図示)をパターニングする。

【0079】

続いて、フォトレジスト膜(不図示)をマスクとして使用し、保護膜20及び第1、第2の導電性酸化膜19a、19bをエッチングする。その後に、アッシング、溶剤等を使用してフォトレジスト膜(不図示)を除去する。さらに、保護膜20を例えばドライエッチングにより除去する。

【0080】

その後に、酸素を含む雰囲気中にシリコン基板1を置いて熱処理を行う。この熱処理は、第1、第2の誘電体膜18a、18bに加わったダメージを回復するための回復アニールである。熱処理温度は、例えば600〜700℃とする。ここでは、熱処理温度は、650℃とし、また、熱処理時間は、例えば40分とする。

【0081】

次に、図1Dに例示する構造を形成するまでの工程を説明する。

まず、既にストライプ状に成形された第1、第2の導電性酸化膜19a、19bとそれらの隙間から露出した第2の誘電体膜18bの上に、フォトレジスト膜21を例えばスピンコート法により形成する。続いて、フォトリソグラフィ技術を用いてフォトレジスト膜21をパターニングする。この場合のフォトレジスト膜21のパターンには、複数のストライプ状の第1、第2の導電性酸化膜19a、19bを跨ぐパターンが間隔をおいて複数形成されている。

【0082】

続いて、図1Eに例示するように、パターニングされたフォトレジスト膜21をマスクとして、第1、第2の導電膜19a、19bと第1、第2の誘電体膜18a、18bをエッチングする。この後、フォトレジスト膜21を除去する。このパターニングによって、第1、第2の導電膜19a、19bから複数のキャパシタ上部電極19が形成される。同時に、第1、第2の誘電体膜18a、18bから複数のキャパシタ誘電体膜18が形成される。キャパシタ誘電体膜18のそれぞれの上には、複数の上部電極19が形成されている。

【0083】

その後に、酸素雰囲気中にて、キャパシタ上部電極19、キャパシタ誘電体膜18等を熱処理する。熱処理条件を例えば300〜650℃とし、熱処理時間を例えば30分〜120分とする。

【0084】

次に、図1Fに示す構造を形成するまでの工程を説明する。

まず、キャパシタ上部電極19、キャパシタ誘電体膜18及び第2の導電膜17bの上に第1保護絶縁膜22を例えばスパッタリング法又はCVD法により形成する。第1保護絶縁膜22としては、例えば酸化アルミニウム膜を形成する。第1保護絶縁膜22の膜厚は、例えば20〜50nm程度とする。

【0085】

第1保護絶縁膜22を形成するための成膜装置としては、反応性RFスパッタリング装置を用いる。ターゲットとしては、直径300mmの酸化アルミニウムセラミックターゲットを用いる。酸化アルミニウム膜の成膜条件は、例えば次の通りとする。アルゴンガス雰囲気中でRFマグネトロンスパッタを行い、40〜100秒の性膜時間で膜厚が20〜50nmの酸化アルミニウム膜を形成する。その際、スパッタパワーを2.0kWに、温度を室温にそれぞれ設定し、また、反応室内の圧力を1.0Paに設定する。

【0086】

第1保護絶縁膜22は、水素や水分等によりキャパシタ誘電体膜18が還元されるのを防止するためのものである。従って、第1保護絶縁膜22の材料は、酸化アルミニウムに限られるものではなく、酸化チタン、酸化タンタル、酸化ジルコニウム、窒化タンタル、窒化アルミニウム、酸窒化アルミニウムのいずれかから選択して膜を形成してもよい。

【0087】

次に、酸素雰囲気中にシリコン基板1を置いて熱処理を行う。熱処理条件は、温度を例えば400〜600℃とし、また、熱処理時間を例えば30分〜120分とする。

【0088】

その後に、第1保護絶縁膜22の上に、例えば、フォトレジスト膜23をスピンコート法により形成する。次に、フォトリソグラフィ技術を用い、フォトレジスト膜23をキャパシタの下部電極の平面形状にパターニングする。即ち、フォトレジスト膜23のパターンは、キャパシタ誘電体膜18とその上のキャパシタ上部電極19を含むとともにキャパシタ誘電体膜18から突出する領域を有している。

【0089】

次に、図1Gに例示するように、フォトレジスト膜23をマスクとして使用し、第1保護絶縁膜22、第1、第2の導電膜17a、17b及び密着絶縁膜16をエッチングする。これによりパターニングされた第1、第2の導電膜17a、17bはキャパシタ下部電極17として使用される。その後、フォトレジスト膜23を除去する。

【0090】

以上のキャパシタ下部電極17、キャパシタ誘電体膜18及びキャパシタ上部電極19によりキャパシタQが形成される。第1保護絶縁膜22は、キャパシタ上部電極19及びキャパシタ誘電体膜18、キャパシタ下部電極17を覆うように残存する。

【0091】

次に、酸素を含有する雰囲気にシリコン基板1を置いて熱処理を行う。熱処理の温度を例えば200〜400℃とする。また、熱処理の時間を例えば30〜120分間とする。この熱処理によれば、キャパシタQをパターニング工程に吸着した水分や不純物を飛ばし、第1保護絶縁膜22の成膜後に熱処理する時に蒸し焼きを防げ、さらに、キャパシタの第1保護絶縁膜22が剥がれにくくなる。酸素を含有する雰囲気としては、酸素のみの雰囲気、アルゴン及び酸素を含有する雰囲気、並びに、窒素及び酸素を含有する雰囲気等が挙げられる。

【0092】

次に、図1Hに示す構造を形成するまでの工程について説明する。

まず、第1保護絶縁膜22及び第2層間絶縁膜15の上に、例えばスパッタリング法又はCVD法により、非晶質な第2保護絶縁膜25を形成する。第2保護絶縁膜25は、水素や水分等によりキャパシタ誘電体膜18が還元されるのを防止するためのものである。非晶質の第2保護絶縁膜25として、例えば酸化アルミニウム膜を形成する。また、第2保護絶縁膜25の材料は、酸化チタン、酸化タンタル、酸化ジルコニウム、窒化タンタル、窒化アルミニウム及び酸窒化アルミニウムのうちから選択する膜でもよい。第2保護絶縁膜25の膜厚は、スパッタリング法で形成する場合は、10nm以上、30nm以下が望ましく、例えば20nm程度とする。また、第2保護絶縁膜25の膜厚は、CVD法で形成する場合は、1nm以上、3nm以下が望ましく、例えば2nm程度とする。

【0093】

酸化アルミニウム膜の成膜条件は、例えば次の通りとする。例えば、アルゴンガス雰囲気中でRFマグネトロンスパッタを行い、成膜時間を40秒として、緻密性が高い非晶質の酸化アルミニウム膜を20nmの厚さに形成する。この場合、スパッタパワー2を.0kWに、温度を室温に、圧力を1.0Paに設定する。

【0094】

次に、酸素を含有する雰囲気にシリコン基板1を置いて熱処理を行う。この熱処理は、キャパシタ誘電体膜18に酸素を供給し、スパッタリングにより損傷しているキャパシタQのダメージを回復させてキャパシタQの電気的特性を向上するためのものである。熱処理条件として、例えば、温度を500〜700℃、時間を30分〜120分とする。この結果、キャパシタ誘電体膜18に酸素が供給され、誘電体キャパシタQの電気的特性が回復する。

【0095】

次に、第2保護絶縁膜25上に第3層間絶縁膜26を形成する。第3層間絶縁膜26として、例えば、TEOSガスを使用するプラズマCVD法によりシリコン酸化膜を形成する。第3層間絶縁膜26の膜厚は、例えば1.4μm程度とする。続いて、例えば、CMP法により第3層間絶縁膜68の上面を平坦化する。

【0096】

続いて、N2Oガス又はN2ガスを用いて発生させたプラズマ雰囲気にシリコン基板1を置いて、熱処理を行う。この熱処理は、第3層間絶縁膜26中の水分を除去するとともに、第3層間絶縁膜26の膜質を変化させ、第3層間絶縁膜26中に水分を入りにくくさせるためのものである。熱処理は、例えば、温度を約350℃、時間を約2分間とする。

【0097】

次に、第3層間絶縁膜26上に、例えばスパッタリング法又はCVD法により第3保護絶縁膜27を形成する。第3保護絶縁膜27としては、例えば酸化アルミニウム膜を形成する。第3保護絶縁膜27の膜厚は、例えば20〜50nm程度である。

【0098】

続いて、第3保護絶縁膜27上に、例えばプラズマTEOSCVD法により、第4層間絶縁膜28を形成する。第4層間絶縁膜28として、例えばシリコン酸化膜をCVD法により例えば300nm程度の厚さに形成する。

【0099】

次に、図1Iに例示する構造を形成するまでの工程について説明する。

フォトリソグラフィ技術を用い、キャパシタ下部電極17のうちキャパシタ誘電体膜18からはみ出したコンタクト領域の上とキャパシタ上部電極19の上の第4層間絶縁膜28から第1保護絶縁膜23までの連続した層を部分的にエッチングする。これにより、キャパシタ上部電極19に達する第3のコンタクトホール26aと、キャパシタ下部電極17のコンタクト領域に達する第4のコンタクトホール26bとを形成する。

【0100】

続いて、酸素雰囲気中にシリコン基板1を置いて熱処理を行う。この熱処理は、キャパシタ誘電体膜18に酸素を供給し、キャパシタQの電気的特性を向上させるためのものである。熱処理条件は、例えば400〜600℃、例えば450℃程度とする。その熱処理時間は、例えば30分〜120分とする。

【0101】

次に、フォトリソグラフィ技術を用い、第1、第2の導電プラグ14a、14bの上の第4層間絶縁膜28から第2層間絶縁膜15までの連続した絶縁膜をエッチングする。これにより、第1、第2の導電性プラグ14a、14bに達するビアホール26c、26dを形成する。

【0102】

続いて、不活性ガス雰囲気中又は真空中にシリコン基板1を置いて熱処理を行う。この熱処理は、第4、第3及び第2層間絶縁膜28、26、15中からガスを放出する、即ち脱ガスのためである。

【0103】

次に、高周波エッチングにより、第3、第4のコンタクトホール26a、26b、及び第1、第2のビアホール26c、26dの内壁面に対して表面処理を行う。続いて、第4層間絶縁膜28の上面の上と第3、第4のコンタクトホール26a、26b及び第1、第2のビアホール26c、26dの内壁面の上に、例えばスパッタリング法により、密着膜29aを形成する。密着膜29aとして、例えばTiN膜を形成する。密着膜29aは、例えば50〜150nm程度の厚さに形成される。密着膜29aとしてTiN膜を形成する場合には、ターゲットの材料としてTiを用い、成膜室内の雰囲気は、ArガスとN2ガスとの混合雰囲気とする。Arガスの流量は50sccm、N2ガスの流量は例えば90sccmとする。また、成膜温度は、例えば150℃とする。

【0104】

続いて、密着膜29aの上に、例えばCVD法により、主導電膜29bを形成する。主

導電膜29bとしては、例えばタングステン膜を形成する。主導電膜29bの膜厚は、例えば300nm程度とする。

【0105】

さらに、第4層間絶縁膜28の上面が露出するまで、例えばCMP法により、主導電膜29b及び密着膜29aを研磨する。こうして、第3、第4のコンタクトホール26a、26b及び第1、第2のビアホール26c、26d内にそれぞれ残された主導電膜29b及び密着膜29aを第3、第4、第5及び第6の導電プラグ30a、30b、30c、30dとして使用する。

【0106】

次に、プラズマ洗浄を行う。プラズマ洗浄を行う際に用いるガスは、例えばArガスとする。これにより、第3〜第6の導電プラグ30a〜30dの表面に存在する自然酸化膜等が除去される。

【0107】

続いて、導電膜として、例えば、TiN膜31a、AlCu合金膜31b、Ti膜31c、TiN膜31dを順次積層することにより、積層導電膜を形成する。TiN膜31aの膜厚は、例えば50nmとする。AlCu合金膜31bの膜厚は、例えば膜厚550nmとする。Ti膜13cの膜厚は、例えば5nmとする。TiN膜31dの膜厚は、例えば膜厚50nmとする。

【0108】

次に、フォトリソグラフィ技術を用い、積層導電膜をエッチングする。こうして、積層膜により第3〜第6の導電プラグ31a〜31dに接続される配線32が形成される。この後、更に、層間絶縁膜、導電プラグ、配線等を複数層に亘って形成する。配線層(金属配線層)は、5層に亘って形成される(不図示)。

以上により、半導体装置内のメモリセルの基本的な構造が形成される。

【0109】

上記の半導体装置によれば、キャパシタQの下地としてアモルファスで正方体結晶を持つ密着絶縁膜16を形成している。密着絶縁膜16は、例えば、Pb又はBi添加した正方体の結晶を持つ絶縁膜、例えばPbAl2O4、PbAl2O5、PbZrO3、PbTiO3、PbSiO3、Pb(Zr,Ti)O3、BiAlO3、BiGaO3、SrBi2Ta2O9、Bi4Ti2O12、(BiLa)4Ti3O12のいずれかを用いて形成されている。

【0110】

従って、密着絶縁膜16の上に形成されるキャパシタQに外部から放射線が照射されても、放射線は密着絶縁膜16により部分吸収されて、キャパシタ誘電体膜18に至る輻射が軽減される。さらに、放射線は、密着絶縁膜16とキャパシタ誘電体膜18を構成する上記材料の誘電体膜結晶(正方体)の各頂点のPbに吸収され、結晶中心のZr/Tiへの放射線の影響が更に小さくなる。

【0111】

これにより、上記構造のMOSトランジスタT1、T2とキャパシタQを有するメモリ素子は、外部放射線に照射されてもソフトエラーが起きにくくなるので、医療、衛生品のTAGとして、一緒に放射線(ガンマ線、電子線)滅菌しても、データが保持できる。

【0112】

また、キャパシタ下部電極17の下の密着絶縁膜16は、上記のようなアモルファス強誘電体材料、例えばPZTから形成されているので、表面の平坦性が非常に良い。このため、密着絶縁膜16の上に成膜した形成されるキャパシタ下部電極17、例えばPt膜は、自己配向非常に良い膜となり、単一な(111)面を得やすい。従って、その後に、キャパシタ下部電極17の熱処理を行うと、密着絶縁膜16のPZTも結晶化され、PZT/Ptの結晶配向ともに(111)面となるので、その上に形成したキャパシタ誘電体膜18、例えばPZT膜の結晶性も向上できる。

【0113】

ところで、上記の方法で形成した半導体メモリ素子について、密着絶縁膜16として形成される上記材料のうちPZTを一例として選択し、PZT膜のガンマ線に対する耐性を調べるために次のような試験を行った。

【0114】

まず、キャパシタ誘電体膜18としてPZT膜を形成するとともに、その下の密着膜をアルミナから形成し、それ以外の構造を図1Iと同様に形成した複数の試料を用意した。そして、キャパシタ誘電体膜18のPZT膜の厚さを140nmとした構造のキャパシタを有する半導体装置を第1の試料とする。また、キャパシタ誘電体膜18のPZT膜の厚さを105nmとした構造のキャパシタを有する半導体装置を第2の試料とする。第1、第2の試料は、それぞれパッケージにより封入されている。そして、第1、第2の試料にガンマ線を照射したところ、第1、第2の試料のそれぞれのSSマージン及びOSマージンとガンマ線照射量の関係は、図2A、図2Bに例示するようになった。ガンマ線の照射量は、0kGy、20kGy、50kGy、100kGyである。

【0115】

図2Aにおいて、PSSは、ガンマ線の照射前の書込みデータの読み出し量であり、USSは、ガンマ線照射前と同じ書き込み状態のデータの読み出し量である。PSS−USSは、SSマージンであり、ガンマ線照射前後の読み出し量の違いを示している。図2Aでは、ガンマ線照射が無い場合、即ち0kGyの場合のSSマージンを1としてSSマージンが規格化して示されている。

【0116】

また、図2Bにおいて、POSは、ガンマ線の照射前の書込みデータの読み出し量であり、UOSは、ガンマ線照射前と異なる書き込み状態のデータの読み出し量である。そして、POS−UOSは、OSマージンであり、ガンマ線照射前後の読み出し量の違いを示している。図2Bでは、ガンマ線照射が無い場合、即ち0kGyの場合のOSマージンを1として規格化してOSマージンが示されている。

【0117】

図2Aによれば、各サンプルのSSマージンは、誘電体膜PZTの膜厚及びガンマ線照射量に依存せず、劣化が発生しない。これに対し、図2Bによれば、140nmPZT及び105nmPZTのメモリ素子の双方のOSマージンは、ガンマ線照射量に依存し、ガンマ線照射量が増えると低くなる。さらに、厚さ140nmのPZT膜のOSマージンの低減量は、厚さ105nmのPZT膜のOSマージンの低減量よりも小さくなる。

【0118】

図2Cは、図2Bにおけるガンマ線の照射量が50kGyの場合に、厚さが140nmと105nmのPZT膜のOSマージン量を示す。140nmの厚さのPZT膜のOSマージンは、照射前の量の59%程度になり、また、105nmの厚さのPZT膜のOSマージンは照射前の量の46%程度になる。

【0119】

従って、PZTの膜が薄くなると、放射線照射の影響を受けやすい結果となる。ただし、PZTは、薄くしても、ある程度放射線照射を遮断できる。また、キャパシタの容量を考慮すると、誘電体膜は薄い方が好ましい。従って、キャパシタ誘電体膜18を厚くする代わりに、上記のように、キャパシタ下部電極17の下地となる密着絶縁膜16として結晶化されたPZT膜等を使用すると、メモリセル領域の耐放射線能力を向上させることができる。

【0120】

(第2の実施の形態)

図3は、第2実施形態に係る半導体装置の断面図である。

図3に示す半導体装置では、第1実施形態と同様に、シリコン基板1にMOSトランジスタT1、T2が形成され、その上には第1、第2層間絶縁膜12、15が形成されている。さらに、第1層間絶縁膜12内には第1、第2の導電プラグ14a、14bが形成される。また、第2層間絶縁膜15上には、密着絶縁膜16が形成され、その上にはキャパ

シタQが形成されている。また、キャパシタQのキャパシタ上部電極19、キャパシタ誘電体膜18は第1保護絶縁膜22に覆われている。さらに、第1保護絶縁膜22とキャパシタ下部電極17は、第2保護絶縁膜25により覆われている。

【0121】

第2保護絶縁膜25の上には、第1実施形態では形成されていないステップカバレッジが良好なアルミニウム酸鉛膜(PbAl2O4)が第3保護絶縁膜35として形成されている。本実施形態では、バッチ式の成膜装置を用いた原子層堆積(ALD:Atomic Layer

Deposition)法により、アルミニウム酸鉛膜を厚さ20nm程度で形成する。

【0122】

このALD法を用いたアルミニウム酸鉛膜の形成にあたっては、TMA(Tri-Methyl Aluminum)、Pb(DPM)2及びH2Oを用いたALD法により行うことも可能であるが、アルミニウム酸鉛膜をより緻密化した膜にするという観点から、本実施形態においては、TMA、Pb(DPM)2及びオゾン(O3)を用いたALD法により行うことにする。

【0123】

具体的に、本実施形態では、Al原料として常温で液体のTMA、Pbの液体原料におけるPb(DPM)2を用いて堆積工程と、酸素(O2)及びオゾン(O3)の雰囲気中での酸化工程とを、工程間に真空パージ工程を入れて交互に切り替え、これを210サイクル程度繰り返してアルミニウム酸鉛膜の形成を行う。

【0124】

より詳細には、成膜室内において、オゾンを供給して被堆積膜表面、即ち第2保護絶縁膜25表面を酸化した後、余分なオゾンを真空排気してパージする。次いで、TMA及びPb(DPM)2を流して被堆積膜表面の酸素群と反応させて原子層のアルミニウム酸鉛膜を形成した後、余分なTMA、Pb(DPM)2を真空排気してパージする。この一連のサイクルを繰り返すことにより、アルミニウム酸鉛膜が形成される。

【0125】

TMAを用いた堆積工程では、例えば、基板温度を300℃、ガス圧力を40Pa(0.3Torr)、TMAガス流量を100sccm、Pb(DPM)2流量を50Sccm、5秒間の条件で行う。また、オゾンを用いた酸化工程は、例えば、基板温度を300℃、ガス圧力を133Pa(1.0Torr)、O2+O3ガス流量を10slm、O3濃度を200g/Nm3、15秒間の条件で行う。また、TMAは温度40℃に加温して、Pb(DPM)2は蒸気圧が比較的高いので、温度200℃に加温して蒸気圧によりガス化した状態で当該バッチ式の成膜装置へ導入する。

【0126】

第3保護絶縁膜35としてアルミニウム酸鉛膜の形成が終了した後、酸素及びオゾンの雰囲気中において、同一装置内(in−situ)で昇温して緻密化アニールを行う。この際、昇温は10℃/分程度で行い、また、温度を安定させるため、昇温後30分間は保持する。この緻密化アニールは、例えば、基板温度を500℃、ガス圧力を133Pa(1.0Torr)、O2+O3ガス流量を10slm、O3濃度を200g/Nm3、30分間の条件で行う。

【0127】

なお、本実施形態では、第3保護絶縁膜35であるアルミニウム酸鉛膜の形成後の緻密化アニールの温度を500℃程度としているが、本実施形態の効果を得るためのアニール温度は、400℃以上700℃以下の範囲とすることができる。これは、アニール温度が400℃未満になるとアルミニウム酸鉛膜の緻密化が不十分になるという不具合が生じ、また、アニール温度が700℃を超えるとキャパシタ誘電体膜18を構成するPZTからPbが脱離して疲労特性が悪化するという不具合が生じるためである。

【0128】

また、本実施形態では、第3保護絶縁膜35であるアルミニウム酸鉛膜の形成後の緻密化アニールの時間を30分程度としているが、本実施形態の効果を得るためのアニール時

間は、10分以上120分以下の範囲とすることができる。これは、アニール時間が10分未満になると当該緻密化アニールを行うバッチ式装置内でウェハ位置による依存が現れるという不具合が生じ、また、アニール温度が120分を超えると、アルミニウム酸鉛膜の緻密化は十分であるがスループットが低下するという不具合が生じるためである。

【0129】

この強酸化性を有するオゾン(O3)を含む雰囲気中でのアニール処理により、アルミニウム酸鉛膜は、緻密化された膜となる。これにより、例えば層間絶縁膜の成膜等の後工程において水素が生じた際においても、キャパシタ誘電体膜18への水素の侵入を阻止することができ、キャパシタ誘電体膜18の劣化を防止することができる。さらに、第3保護絶縁膜35であるアルミニウム酸鉛膜の成膜を、TMA及びH2Oを用いたALD法により行った場合には、アルミニウム酸鉛膜中に存在するOH基を一括して除去することができ、所謂蒸し焼き状態によるキャパシタ誘電体膜18の劣化を回避することができる。

【0130】

ここでは、第3保護絶縁膜35としてALD法でアルミニウム酸鉛膜35を形成することについて説明している。第3保護絶縁膜35の他の材料としては、Pb又はBiを添加した絶縁膜であってPbAl2O5、PbZrO3、PbTiO3、PbSiO3、Pb(Zr,Ti)O3、BiAlO3、BiGaO3、SrBi2Ta2O9、Bi4Ti2O12、(BiLa)4Ti3O12のいずれか一つ材料を使用してもよい。また、第3保護絶縁膜35の成膜方法としては、ALD法以外に、カバレッジの良い有機金属分解法、化学気相蒸着法、MOCVD法、スパッタ法を使用してもよい。

【0131】

次に、酸素を含有する雰囲気にシリコン基板1を置いて熱処理を行う。この熱処理は、第3保護絶縁膜35であるアルミニウム酸鉛膜の成膜過程中に残留する有機物を蒸発させる。これらの残留有機物が、アルミニウム酸鉛膜中残ると、その以後のプロセスに第1、第2保護絶縁膜22、25に拡散し、キャパシタ誘電体膜18へ浸入する可能性がある。熱処理条件は、例えば500〜600℃とする。熱処理時間は、例えば30分〜90分とする。この結果、第1及び第2保護絶縁膜22、25及び、アルミニウム酸鉛膜は、緻密性が非常に良い膜となり、キャパシタ誘電体膜18を完全に保護する。

【0132】

一方、上記の第1、第2保護絶縁膜22、25の厚さが厚すぎると、その後の工程でコンタクトホール26a、26bを完全に開けられないので、第1、第2保護絶縁膜22、25の厚さは100nm以下に望ましい。また、第2保護絶縁膜25を省いてもよい。コンタクトホール26a、26bをよりきれいに開くためには、それらの厚さは50nm以下が望ましい。また、これらの厚さが薄すぎると、キャパシタQへの保護機能がなくなるので、キャパシタQの側面での第1、第2保護絶縁膜の厚さは10nm以上が望ましい。また、第3保護絶縁膜35となる薄いアルミニウム酸鉛膜は、アルゴンガスで容易にスパッタエッチングすることが可能であるので、本実施形態では、所望の形状のコンタクトホール26a、26bを容易に形成することができる。

【0133】

次に、第1実施形態と同じ条件で、第3保護絶縁膜35上に第3層間絶縁膜26を形成する。その以後の構造及びプロセスも第1実行形態と同じ方法で形成して半導体装置のメモリセル領域の基本構造を形成する。

【0134】

以上のように、キャパシタQを有する本実施形態に係る半導体装置が形成されている。こうした半導体メモリは、外部から放射線に照射されると、キャパシタQを挟む密着絶縁膜16及び第3保護絶縁膜35により部分吸収されて、キャパシタ誘電体膜18に至る輻射が軽減される。さらに、正方体の誘電体膜結晶の各頂点にPbに吸収され、結晶中心のZr/Tiへの影響を更に小さくなる。従って、第1実施形態と同様に、上記構造のメモリ素子は、外部放射線に照射されても、ソフトエラーが起きにくくなるので、医療、衛生品のTAGとして、一緒に放射線(ガンマ線、電子線)滅菌しても、データが保持できる

。

【0135】

ところで、第3保護絶縁膜35の上に形成される第3層間絶縁膜26として、第3保護絶縁膜35を熱処理した後に、例えばTEOS(Si(OC2H5)4)と次のソースを用いてプラズマCVD法により形成してもよい。そのソースとして、Pb(C11H19O2)2、Pb(DPM)2、Pb(TMHPD)、Bi(DPM)3、Bi(Ot−Bu)3、Bi(p−Tol)3のいずれか一つを使用する。これにより形成された第3層間膜26は、PbやBiを添加したシリコン化合物の絶縁膜であるPbSiO3あるいはBi2Si2O9である。PbやBiが添加されたシリコン化合物の第3層間絶縁膜26の膜厚は、例えば約1.2μm程度とする。第3層間絶縁膜26の形成方法として、上記のプラズマCVD法以外、ゾル−ゲル法、有機金属分解法、CSD法、化学気相蒸着法、MOCVD法などを使用してもよい。第3層間絶縁膜26の形成後には上記と同様にその表面は、例えばCMP法により平坦化される。そのようなPb、Biのいずれかを添加したシリコン酸化膜は、第1実施形態、又は、以下の実施形態において、キャパシタQ、Q0の上方の層間絶縁膜に適用してもよい。

【0136】

そのような材料により形成された第3層間絶縁膜26は、外部から照射される放射線を吸収するので、キャパシタ誘電体膜18に達する放射線の輻射が軽減する。さらに、放射線は、PbやBiが添加された誘電体膜の結晶(正方体)の各頂点のPbに吸収されるので、結晶中心のZr/Tiへの影響を更に小さくなる。従って、上記構造のメモリ素子は、外部放射線に照射されても、ソフトエラーが更に起きにくくなるので、医療、衛生品のTAGとして、一緒に放射線(ガンマ線、電子線)滅菌しても、データが保持できる。

【0137】

(第3の実施の形態)

図4は、第3実施形態に係る半導体装置の断面図である。

図4に示す半導体装置は、第1実施形態と同様に、シリコン基板にMOSトランジスタT1、T2が形成され、MOSトランジスタを覆う第1、第2層間絶縁膜12、15が形成される。また、第1層間絶縁膜12内には第1、第2の導電プラグ14a、14bが形成され、さらに、第1、第2の導電プラグ14a、14bと第1層間絶縁膜12の上に、第1実施形態と同様に、シリコン窒化酸化膜15aが形成される。この場合、シリコン窒化酸化膜15aは、例えば約100nmの厚さに形成される。

【0138】

また、シリコン窒化酸化膜15aの上には、例えばスパッタリング法により第1ガンマ線遮断膜38を形成する。第1ガンマ線遮断膜38は、第1実施形態の密着絶縁膜16と同様に絶縁膜であり、外部から放射線照射されてもそれを遮断できる機能を確保するためのものである。第1ガンマ線遮断膜38としては、Pb又はBiを含む絶縁膜、強誘電体膜、例えば、チタン酸ジルコン酸鉛(PZT:(PbZrxTi1−xO3)(0≦x≦1))膜を形成する。第1ガンマ線遮断膜38の形成方法として、例えば、高周波スパッタリング法を採用する。

【0139】

第1ガンマ線遮断膜38として、PZTの他の材料、例えば、Ca、Sr、Laが少なくともに一つ元素添加されたチタン酸ジルコン酸鉛またはビスマス層状結晶構造を持つ(Bi,Sr)TiO3や(Bi,La)4Ti3O12膜が用いられる。または、Pb又はBi添加したPbAl2O4、PbAl2O5、PbZrO3、PbTiO3、PbSiO3、Pb(Zr,Ti)O3、BiAlO3、BiGaO3、SrBi2Ta2O9、Bi4Ti2O12膜などでもよい。

【0140】

第1ガンマ線遮断膜38の膜厚は、例えば、20nm〜200nm程度、より好ましくは、50nm〜100nm程度、例えば約50nmとする。第1ガンマ線遮断膜38を形成する際の成膜条件は、例えば次の通りとする。

【0141】

スパッタリングにおける基板温度は例えば50℃である。また、成膜室内に導入するガスとしては、例えばArガスを用いる。さらに、成膜室内の圧力は例えば1Paとする。印加電力は例えば1.0kWとする。第1ガンマ線遮断膜38は、上記の材料から選択される二つ膜の積層を使用してもよい。

【0142】

第1ガンマ線遮断膜38の形成方法としては、スパッタ法以外、例えばゾル−ゲル法、有機金属分解法、化学溶液法(CSD)法、化学気相蒸着法、エピタキシャル成長法又は有機金属成長(MOCVD)法を採用してもよい。

【0143】

次に、第1ガンマ線遮断膜38の上に、例えばTEOSを使用するプラズマCVD法により、シリコン酸化膜15bを形成する。シリコン酸化膜15bの膜厚は、例えば約100nmとする。

【0144】

ここで、シリコン窒化酸化膜15a、第1ガンマ線遮断膜38及びシリコン酸化膜15bにより第2層間絶縁膜15が形成される。第2層間絶縁膜15は、第1層間絶縁膜12内の第1、第2の導電プラグ14a、14bの上面が酸化されるのを防止することを目的の1つとして形成される。

【0145】

第2層間絶縁膜15上には密着膜39が形成される。密着膜39は、キャパシタ下部電極17に対する密着性を確保するための絶縁膜である。密着膜39としては、例えば酸化アルミニウム(Al2O3)膜が形成されている。密着膜39の膜厚は例えば約20nmである。密着膜39は、第1実施形態の図1Fに示すと同様に、キャパシタ下部電極17のパターニングの際に同じレジストマスク23を使用してパターニングされる。密着膜39は、水又は水分の拡散を防止できる材料から形成されることが好ましい。

【0146】

その後、第1実施形態と同様な方法により、キャパシタ下部電極17、キャパシタ誘電体膜18、キャパシタ上部電極19を形成し、これらによりキャパシタQを形成する。なお、キャパシタ下部電極17のパターンを形成する前にキャパシタ下部電極17、キャパシタ誘電体膜18の上に第1保護絶縁膜22を形成する。なお、第1実施形態と同じ条件で、キャパシタ誘電体膜18となる第1、第2の誘電体膜18a、18bがRTA法により加熱される際に、第1ガンマ線遮断膜38も加熱されて結晶性が改善し、Pb又はBiを含有して正方体の結晶を持つ。

【0147】

その後に、第1実施形態と同様に、キャパシタQ上に第2保護絶縁膜25、第3層間絶縁膜26を形成する。即ち、第3層間絶縁膜26として例えばTEOSを使用するプラズマCVD法によりシリコン酸化膜を形成する。続いて、例えばCMP法により、第3層間絶縁膜26の上面を平坦化する。

【0148】

次に、N2Oガス又はN2ガスを用いて発生させるプラズマ雰囲気にシリコン基板1置いて熱処理を行う。この熱処理は、第3層間絶縁膜26中の水分を除去するとともに、第3層間絶縁膜26の膜質を窒素成分により変化させ、第3層間絶縁膜26中に水分を入りにくくさせるためのものである。熱処理温度は、例えば約350℃とし、熱処理時間は、例えば約2分間とする。

【0149】

次に、第3層間絶縁膜26の上に、例えばスパッタリング法又はCVD法により、第2ガンマ線遮断膜40を形成する。第2ガンマ線遮断膜40は、上記の第1ガンマ線遮断膜38の形成方法のいずれかの方法で形成される絶縁膜であり、第1ガンマ線遮断膜38に適用される材料から選択して形成される。第2ガンマ線遮断膜40の膜厚は、200nm以下、例えば約50nm程度とする。

【0150】

その後に、第2ガンマ線遮断膜40の上に、例えばTEOSを使用するプラズマCVD法により第4層間絶縁膜28を形成する。その後に、第1実施形態と同様に、第3、第4のコンタクトホール26a、26bを形成した後に、酸素雰囲気中にシリコン基板1を置いて熱処理を行う。この熱処理により、キャパシタ誘電体膜18に酸素を供給し、さらに、第2ガンマ線遮断膜40の結晶性を改善する。これにより、第2ガンマ線遮断膜40は、Pb又はBiを含有して正方体の結晶を持つ。その後のプロセスでは、第1実施例と同じ方法で導電プラグ30a〜30d、配線32等を形成し、これにより半導体装置のメモリ領域の基本構造を完成させる。

【0151】

上記の半導体装置が外部から放射線、例えばガンマ線に照射されると、放射線は、キャパシタQを挟む第1ガンマ線遮断膜38及び第2ガンマ線遮断膜40により吸収されるので、キャパシタ誘電体膜18に達する輻射が軽減される。さらに、放射線は、第1、第2ガンマ線遮断膜38、40及びキャパシタ誘電体膜18における正方体の誘電体膜結晶の各頂点にPbに吸収され、結晶中心のZr/Tiへの影響を更に小さくすることができる。なお、第1ガンマ線遮断膜38及び第2ガンマ線遮断膜40は、ともに放射線遮断膜である。

【0152】

従って、上記構造のキャパシタQ、MOSトランジスタT1、T2等を有するメモリ素子は、外部放射線に照射されても、ソフトエラーが起きにくくなるので、医療、衛生品のTAGとして、一緒に放射線(ガンマ線、電子線)で滅菌しても、データが保持できる。

【0153】

ところで、本実施形態において、キャパシタ下部電極17の密着膜39として酸化アルミニウムが形成されている。この場合、図5に例示するように、キャパシタ下部電極17の下に、第1実施形態で示したPb又はBiを含む絶縁膜から密着絶縁膜16を密着層39の代わりに形成してもよい。さらに、図6に例示するように、キャパシタQ及び第1、第2保護絶縁膜22、25の上に、第2実施形態で示した第3保護絶縁膜35としてアルミニウム酸鉛膜を形成してもよい。これらにより、メモリ素子の耐放射線性がさらに高くなる。図5、図6においては、シリコン酸化膜15bの上側と下側に、これとは材料の異なるPb又はBiを含む絶縁膜が形成された構造となる。

【0154】

なお、第3層間絶縁膜26の材料として、第2実施形態において説明したように、PbやBi添加した絶縁膜であってもよい。

【0155】

(第4の実施の形態)

図7A〜図7Eは、第4実施形態に係る半導体装置の形成工程を示す断面図である。図7A〜図7Eにおいて、図1A〜図1Iと同じ符号は同じ要素を示している。本実施形態による半導体装置は、メモリセルのキャパシタがスタック型となる構造を有している。次に、図7Aに示す構造を形成するまでの工程を説明する。

【0156】

まず、第1実施形態と同様に、半導体基板1内にSTI2に囲まれるPウェル4aを形成した後に、Pウェル4a上に例えば厚さ6〜7nmのゲート絶縁膜5cを形成する。続いて、第1実施形態と同様に、ゲート絶縁膜5c上に例えばCVD法によりポリシリコン膜を形成した後、フォトリソグラフィ技術を用いてポリシリコン膜をパターニングする。これにより、Pウェル4aの上方にワード線を兼ねた第1、第2のゲート電極6c、6dを形成する。

【0157】

次に、第1、第2のゲート電極6c、6dをマスクに使用して、例えばイオン注入法によりシリコン基板1内にn型ドーパント不純物を導入する。これにより、第1、第2のゲート電極6c、6dの両側のPウェル4a内に浅い第1〜第3のエクステンション領域7

e、7f、7gを形成する。

【0158】

次に、第1実施形態と同様な方法により、第1、第2のゲート電極6c、6dの側面に絶縁性のサイドウォール9c、9dが形成される。続いて、サイドウォール9c、9d及び第1、第2のゲート電極6c、6dをマスクに使用し、例えばイオン注入法により第1、第2のゲート電極6c、6dの両側のPウェル4a内にn型不純物を導入する。これにより、第1〜第3のエクステンション領域7e、7f、7gに接続される深い不純物拡散層を第1〜第3のソース/ドレイン領域8e、8f、8gとする。

【0159】

その後に、第1実施形態と同様な方法により、第1、第2のゲート電極6c、6dの上部と第1〜第3のソース/ドレイン領域8e、8f、8gの上部にそれぞれシリサイド層10g〜10kを形成する。

【0160】

このようして、第1、第2のゲート電極6c、6dとソース/ドレイン領域8e、8f、8g、Pウェル4a等を有する第1、第2のMOSトランジスタT3、T4が形成される。なお、第1、第2のゲート電極6c、6dの間の第2のエクステンション領域7f、第2のソース/ドレイン領域8fは、第1、第2のMOSトランジスタT3、T4により共有される。

【0161】

次に、第1実施形態と同様な方法により、第1、第2のMOSトランジスタT3、T4を覆うカバー絶縁膜11をシリコン基板1の上に形成し、さらにカバー絶縁膜11の上に厚さ約1μmの第1層間絶縁膜12を形成する。第1層間絶縁膜12の上面は例えばCMP法により平坦化される。

【0162】

その後に、フォトリソグラフィ技術を用い、第1〜第3のソース/ドレイン領域8e〜8g上のシリサイド層10i〜10kに達する第1、第2、第3のコンタクトホール12c、12d、12eをカバー絶縁膜11、第1層間絶縁膜12内に形成する。第1、第2、第3のコンタクトホール12c、12d、12eの径を例えば0.25μmとする。

【0163】

次に、第1実施形態と同様な方法により、例えば、厚さ約30nmのTi膜と厚さ約20nmのTiN膜を密着膜13cとして第1〜第3のコンタクトホール12c〜12e内に形成し、その上に厚さ約300nmのタングステン膜13dを形成する。その後に、例えばCMP法により、タングステン膜13d及び密着膜13cを第1層間絶縁膜12の上面上から除去するとともに、第1〜第3のコンタクトホール12c〜12e内に第1、第2、第3の導電プラグ14c、14d、14eとして残す。

【0164】

次に、第1、第2、第3の導電プラグ14c、14d、14e及び第1層間絶縁膜12の上に、例えば、プラズマCVD法により、シリコン窒化酸化膜15cを約130nm形成し、その上にさらに、例えばスパッタリング法により第1ガンマ線遮断膜41を形成する。第1ガンマ線遮断膜41は、外部から放射線照射されても遮断できる膜を確保する機能を有する。

【0165】

第1ガンマ線遮断膜41としては、第1実施形態で説明した密着絶縁膜16の材料、例えばPb又はBi添加した絶縁膜、強誘電体膜を形成する。第1ガンマ専遮断膜41は、第1実施形態において示された密着絶縁膜16となる材料から選択した二つ膜を積層した構造であってもよい。

【0166】

第1ガンマ線遮断膜41の膜厚は、例えば20nm〜200nm程度とし、より好ましくは、50nm〜100nm程度とする。第1ガンマ線遮断膜41をPZTから高周波スパッタリング法により形成する際の成膜条件は、例えば次の通りとする。即ち、基板温度

は、例えば50℃とする。成膜室内に導入するガスとしては、例えばArガスを用いる。成膜室内の圧力は、例えば1Paとする。印加電力は、例えば1.0kWとする。この場合、第1ガンマ線遮断膜41を約50nmの厚さに形成する。

【0167】

次に、第1ガンマ線遮断膜41の上に、例えばTEOSガスを使用するプラズマCVD法により、シリコン酸化膜15dを例えば約100nmの厚さに形成する。シリコン窒化酸化膜15c、第1ガンマ線遮断膜41及びシリコン酸化膜15dにより層間絶縁膜15が形成される。

【0168】

次に、フォトリソグラフィ技術を用い、第1、第3の導電プラグ14c、14eの上に開口42a、42bを有するレジストパターン42をシリコン酸化膜15d上に形成する。続いて、開口42a、42bを通して第2層間絶縁膜15をエッチングして第1、第2のビアホール41a、41bを第1、第3の導電プラグ14c、14d上に形成する。その後に、レジストパターン42を除去する。

【0169】

次に、図7Bに示す構造を形成するまでの工程を説明する。

まず、第1、第2のビアホール41a、41b内面と第2層間絶縁膜15上に、例えばスパッタリング法により、Ti膜を30nm程度とTiN膜を20nm程度の厚さに形成する。こうして、Ti膜とTiN膜とにより密着膜43aが形成される。

次に、密着膜43a上に、例えばCVD法により、主導電膜43bとして例えばタングステン膜を300nm程度の厚さに形成する。

【0170】

続いて、例えばCMP法により、第2層間絶縁膜15の表面が露出するまで主導電膜43b及び密着膜43aを研磨し、第1、第2のビアホール41a、42b内に残されたそれらの導電膜を第1、第2のビアプラグ44a、44bとして使用する。研磨により、第1、第2のビアプラグ44a、44bの上面の高さが第2層間絶縁膜15の上面の高さより低くなる場合がある。かかる場合には、第1、第2のビアプラグ44a、44bが埋め込まれた箇所に凹部41cが形成されることとなる。かかる凹部の深さは、例えば20〜50nm程度である。

【0171】

次に、図7Cに示す構造を形成するまでの工程を説明する。

まず、第2層間絶縁膜15の上と第1、第2のビアプラグ44a、44bの上に、例えばスパッタリング法により、下地導電膜45としてTi膜を形成する。Ti膜の膜厚は、例えば100〜300nm程度とする。

【0172】

続いて、例えばRTA法により、窒素雰囲気中にシリコン基板1を置いて熱処理を行う。熱処理温度は、例えば650℃とする。熱処理時間は、例えば60秒とする。この熱処理により、上述したTi膜がTiN膜45となる。例えば、TiN膜の膜厚を例えば100nm程度の厚さに形成する。また、Pb又はBiを含有して正方体の結晶を持つ第1ガンマ線遮断膜41の結晶性が向上する。

【0173】

さらに、CMP法により、下地導電膜45の表面を研磨して平坦化層として機能させる。研磨後における下地導電膜45の膜厚は、例えば50〜100nm程度、例えば50nm程度の厚さとする。続いて、例えばNH3ガスを用いて発生させたプラズマ雰囲気に下地導電膜(平坦化層)45の表面を暴露することにより、下地導電膜45の表面をプラズマ処理する。

【0174】

次に、下地導電膜45の上に、例えばスパッタリング法により、Ti膜を形成する。Ti膜の膜厚は、例えば20nm程度とする。この場合、プラズマ処理が行われた下地導電膜45上に形成されるTi膜は良質である。続いて、例えばRTA法により、650℃の

窒素雰囲気中にシリコン基板1を置いて60秒の熱処理を行うことにより、Ti膜は(111)配向のTiN膜となる。こうして、(111)配向のTiN膜により導電性の密着膜46aが形成される。

【0175】

次に、密着膜46aの上に、例えば反応性スパッタリング法により、導電性の酸素バリア膜(酸素拡散防止膜)46bとして、例えば100nm程度TiAlN膜を形成する。かかる酸素バリア膜46bは、第2層間絶縁膜15内に導電性の第1、第2のビアプラグ44a、44bを形成した後に、第1、第2のビアプラグ44a、44bの上面が酸化されるのを防止するためのものである。

【0176】

次に、酸素バリア膜46bの上に、例えばスパッタリング法により、第1の導電膜47aとして貴金属膜を形成する。第1の導電膜47aは、後述するキャパシタQ0のキャパシタ下部電極47の一部となるものである。第1の導電膜47aとしては、例えば100nm程度のイリジウム膜を形成する。次に、例えばRTA法により、650℃のアルゴン雰囲気中にシリコン基板1を置いて60秒の熱処理を行う。この熱処理は、第1の導電膜47a中の結晶粒を成長させるとともに、第1の導電膜47a中の結晶粒のサイズを均一化するためのものである。

【0177】

続いて、第1の導電膜47aの上に、例えばスパッタリング法により、非晶質(アモルファス状態)貴金属酸化物の第2導電膜47bを形成する。非晶質貴金属酸化物の膜として、例えば25nm程度の酸化イリジウム膜(IrOx膜:xはIrに対する組成比)を形成する。貴金属酸化物膜は、後工程において還元され、貴金属膜となる。貴金属酸化物の第2の導電膜47bが還元されることにより形成される貴金属膜は、キャパシタQ0のキャパシタ下部電極47の一部となる。

【0178】

次に、貴金属酸化物の第2導電膜47bの上に、例えばMOCVD法により、第1の誘電体膜48aを形成する。誘電体膜48aとしては、例えばPZT膜を形成する。第1の誘電体膜48aの膜厚は、例えば30nm〜150nm程度とする。より好ましくは、誘電体膜48aの膜厚を、例えば50nm〜120nm程度とする。

【0179】

第1の誘電体膜48aとなるPZT膜をMOCVD法により形成する際には、Pb、Zr、Tiの各液体原料を気化することにより原料ガスを生成し、かかる原料ガスを用いてPZT膜を形成する。Pb、Zr、Tiの各液体原料は次のようにして形成される。

【0180】

Pbの液体原料は、例えばPb(DPM)2を溶媒中に溶解することにより形成される。溶媒としては、例えばTHF(テトラヒドロフラン)が用いられる。Pbの液体原料におけるPb(DPM)2の濃度は、例えば0.3mol/l程度とする。Zrの液体原料は、例えばZr(dmhd)4を溶媒中に溶解することにより形成される。溶媒としては、例えばTHFが用いられる。Zrの液体原料におけるZr(dmhd)4の濃度は、例えば0.3mol/l程度とする。Tiの液体原料は、例えば[Ti(O−iOr)2(DPM)2]を溶媒中に溶解することにより形成される。溶媒としては、例えばTHFが用いられる。Tiの液体原料における[Ti(O−iOr)2(DPM)2]の濃度は、例えば0.3mol/l程度とする。溶媒としては、例えばTHFが用いられる。Laの液体原料におけるLa(DPM)3の濃度は、例えば0.3mol/l程度とする。

【0181】

PZTの原料ガスは、上記のようなPbの液体原料、Zrの液体原料及びTiの液体原料を、溶媒とともに気化器に導入し、かかる液体原料を気化器により気化させることにより生成される。溶媒としては、例えばTHFが用いられる。溶媒の供給量は、例えば約0.474ml/分とする。Pbの液体原料の供給量は、例えば約0.326ml/分とする。Zrの液体原料の供給量は、例えば約0.200ml/分とする。Tiの液体原料の

供給量は、例えば約0.200ml/分とする。さらに、Laの液体原料を使用してPLZTを形成する場合、その供給量は、例えば約0.020ml/分とする。

【0182】

第1の誘電体膜48aをMOCVD法により形成する際のその他の条件は、次の通りとする。即ち、成膜室内の圧力は、例えば665Pa(5Torr)とする。基板温度は、例えば620℃とする。成膜時間は、例えば490秒とする。このような条件で形成すると、例えば膜厚70nm程度のPLZT膜である第1の誘電体膜48aが形成される。第1の誘電体膜48aは、ペロブスカイト型結晶構造、ビスマス層状結晶構造のいずれかのABOx型結晶構造を持つことが好ましい。

【0183】

また、ここでは、第1の誘電体膜48aをMOCVD法により形成する場合を例に説明したが、MOCVD法に限定されるものではなく、例えば、第1実施形態と同様に、スパッタリング法により第1の誘電体膜48aを形成してもよい。

【0184】

次に、第1の誘電体膜48aの上に、例えばスパッタ法により、第2の誘電体膜48bとしてアモルファス誘電体膜を例えば、1nm〜30nm、例えば10nmの厚さに形成する。

【0185】

次に、第2の誘電体膜48b上に第1の導電性酸化膜49aを形成する。第1の導電性酸化膜49aは、Pt、Ir、Ru、Rh、Re、Os、Pdからなる群から選択された少なくとも1種の元素の酸化物から形成される。例えば、第1の導電性酸化膜49aの形成に当たっては、先ず、第2の誘電体膜48bの上に20〜70nm、例えば25nmの厚さで成膜の時点で結晶化したIrOx膜をスパッタ法により形成する。例えば、このときの成膜温度を300℃とし、成膜ガスとしてAr及びO2を用い、これらのArを140sccm、O2を60Sccmの流量とする。また、スパッタパワーは、例えば1kW程度とする。

【0186】

ついで、O2を20sccm、Arを2000sccmの流量で導入する雰囲気中にシリコン基板を置き、温度を725℃、熱処理時間を60秒間とするRTA法で加熱する。この場合、第1、第2の誘電体膜18a、18bの少なくとも一方は、ペロブスカイト型結晶構造、ビスマス層状結晶構造のいずれかのABOx型結晶構造を持つことが好ましい。

【0187】

この熱処理により、第1の誘電体膜48aの結晶性を更に向上し、非晶質の第2の誘電体膜48bも結晶化する。第1、第2の誘電体膜48a、48bを完全に結晶化させると同時に、第1の導電性酸化膜成膜49aのプラズマダメージも回復でき、拡散せしめた第1、第2の誘電体48a、48bは、連続的な柱状結晶を持つ誘電体膜48になる。また、その熱処理により第1、第2の誘電体膜48a、48b中の酸素欠損が補償される。さらに、第1ガンマ線遮断膜41の結晶性がさらに向上する。

【0188】

次に、第1の導電性酸化膜49aの上に、例えばスパッタリング法により、第2の導電性酸化膜49bを形成する。第2の導電性酸化膜49bは、後述するキャパシタQ0のキャパシタ上部電極49の一部となる。第2の導電性酸化膜49bとして、例えば酸化イリジウム(IrOy)膜(0<y≦2)を形成する。この場合、酸化イリジウム膜(IrOy膜)における酸素の組成比yは、第2の導電性酸化膜49aとして形成される酸化イリジウム膜(IrOx膜)における酸素の組成比xより大きいことが好ましい。第2の導電性酸化膜49bの膜厚は、例えば75nm〜200nm程度、例えば150nm程度とする。

【0189】

次に、第2の導電性酸化膜49bの上に導電性の水素バリア膜49cとして第2の例え

ばスパッタリング法により、50nm程度のイリジウム膜を形成する。なお、水素バリア膜49cとして、イリジウム膜の代わりに、SrRuO3膜等を形成してもよい。

【0190】

次に、半導体基板1の下面(裏面)のPbなどを洗浄して除去する。その後に、水素バリア膜49cの上に、スパッタリング法により、第1保護膜51a、例えばTiN膜を形成する。第1保護膜51aは、ハードマスクの一部として機能するものである。ここでは、第1保護膜51aとしてTiN膜を形成する場合を例に説明したが、第1保護膜51aは、TiN膜に限定されるものではなく、例えば、TiAlN膜、TaAlN膜、TaN膜等により形成されてもよい。また、第1保護膜51aは、それらの積層膜により形成されてもよい。

【0191】

次に、第1保護膜51aの上に、例えばTEOSガスを使用するプラズマCVD法により、第2保護膜51bを形成する。第2保護膜51bは、第1保護膜51aと相俟ってハードマスク51として機能するものである。

【0192】

続いて、第2保護膜51b上に、例えばスピンコート法により、フォトレジスト膜52を形成する。その後に、フォトリソグラフィ技術を用い、フォトレジスト膜52を第1、第3の導電プラグ14a、14bのそれぞれの上方でキャパシタ平面形状にパターニングする。

【0193】

次に、図7Dに例示する構造を形成するまでの工程について説明する。

まず、フォトレジスト膜52をマスクとして、第2保護膜51bをエッチングし、パターニングする。続いて、パターニングされた第2保護膜51bをマスクに使用して、第1保護膜51aをエッチングする。こうして、エッチングされた第1、第2保護膜51a、51bによりハードマスク51が形成される。

【0194】

その後に、ハードマスク51をマスクとして、例えばプラズマエッチングにより、水素バリア膜49c、第2、第1の導電性酸化膜49b、49a、第2、第1の誘電体膜48b、48a及び第2、第1の導電膜47b、47aをエッチングする。エッチングガスとしては、例えばHBrガスとO2ガスとArガスとC4F8ガスとの混合ガスを用いる。

【0195】

こうして、第1、第2の導電膜47a、47bによりキャパシタ下部電極47が形成される。また、第1、第2の誘電体膜48、48baによりキャパシタ誘電体膜48が形成される。また、第1、第2の導電性酸化膜49a、49b及び水素バリア膜49cによりキャパシタ上部電極49が形成される。

【0196】

キャパシタ下部電極47とキャパシタ誘電体膜48とキャパシタ上部電極49によりキャパシタQ0が形成される。その後に、例えばドライエッチング又はウエットエッチングにより、第2の保護膜51bを除去する。

【0197】

次に、第1保護膜51aをマスクに使用し、例えばドライエッチングにより、酸化バリア膜46b、密着膜46a及び下地導電膜45をエッチングし、第2層間絶縁膜15の上面を露出させる。この際、第1保護膜51aも最終的にエッチング除去される。そのエッチングを行う際には、例えばダウンフロー型のプラズマエッチング装置を用いる。エッチングチャンバ内に導入するガスは、例えばCF4ガスを5流量%、O2ガスを95流量%で含む混合ガスとする。エッチングチャンバ内の上部電極に印加する高周波電力は、例えば2.45GHz、1400Wとし、基板温度は、例えば200℃とする。これにより、キャパシタ下部電極47は、導電性の酸化バリア膜46b、密着膜46a及び下地導電膜45、ビアプラグ44a、44b、導電プラグ14c、14e等を介してソース/ドレイン領域8e、8gに接続される。

【0198】

図7Eに示す構造を形成するまでの工程を説明する。

まず、キャパシタQ0及び第2層間絶縁膜15の上に、例えばスパッタリング法により、非晶質な第1保護絶縁膜53を形成する。第1保護絶縁膜53は、水素や水分等によりキャパシタ誘電体膜48が還元されるのを防止するためのものである。第1保護絶縁膜53としては、例えば酸化アルミニウム膜を形成する。第1保護絶縁膜53の膜厚は、スパッタリング法で形成する場合は、10nm以上、30nm以下が望ましい、例えば20nm程度とする。また、CVD法で形成する場合は、1nm以上、3nm以下に望ましく、例えば2nm程度とする。

【0199】

次に、酸素を含有する雰囲気にて熱処理を行う。この熱処理は、キャパシタ誘電体膜48に酸素を供給し、スパッタリングにより損傷しているキャパシタQ0のダメージを回復させ、キャパシタQ0の電気的特性を向上するためのものである。熱処理条件は、例えば500〜700℃とする。熱処理時間は、例えば30分〜120分とする。

【0200】

続いて、第1保護絶縁膜53を覆うように、第2保護絶縁膜54として第1実施例の第2保護絶縁膜25と同じ形成方法でステップカバレッジが良好な酸化アルミニウム膜を形成し、その後に、オゾンを含む雰囲気中熱処理及び酸素を含む雰囲気中熱処理を行う。

【0201】

次に、第2保護絶縁膜54の上に、例えば、プラズマTEOSCVD法により例えば約1.5μm程度のシリコン酸化膜を第3層間絶縁膜55として形成する。続いて、例えばCMP法により、第3層間絶縁膜55の上面を平坦化する。

【0202】

さらに、例えばN2Oガス又はN2ガスを用いて発生させたプラズマ雰囲気にシリコン基板1を置いて、熱処理を行う。この熱処理は、第3層間絶縁膜55中の水分を除去するとともに、第4層間絶縁膜55の膜質を変化させ、第3層間絶縁膜55中に水分を入りにくくさせるためのものである。熱処理温度は、例えば350℃とする。熱処理時間は、例えば2分間とする。この熱処理の際に第3層間絶縁膜55の表面が窒化され、その表面にはシリコン窒化酸化膜が形成される。

【0203】

次に、第3層間絶縁膜55の上に、例えばスパッタリング法により第2ガンマ線遮断膜56を形成する。第2ガンマ線遮断膜56は、外部から放射線照射されても遮断できる膜を確保するための絶縁膜である。第2ガンマ線遮断膜56としては、例えば、厚さ50nm〜100nmのPZT膜を形成する。より具体的には、高周波スパッタリング法により、第2ガンマ線遮断膜56を形成する。第2ガンマ線遮断膜56は、表面が平坦化された第3層間絶縁膜55上に形成されるので、平坦となる。

【0204】

第2ガンマ線遮断膜56としては、例えば、第3実施形態における第2ガンマ線遮断膜40と同じ材料、同じ形成方法を適用し、ここでは、PZT膜を形成する。第2ガンマ線遮断膜56の膜厚は、例えば20nm〜200nm程度とする。より好ましくは、第2ガンマ線遮断膜56の膜厚を、例えば50nm〜100nm程度、本実施形態でPZT膜を形成する場合には例えば50nmとする。

【0205】

次に、第2ガンマ線遮断膜56の上に、例えばプラズマTEOSCVD法により、厚さ200nm〜300nm程度のシリコン酸化膜を第5層間絶縁膜57として形成する。

【0206】

続いて、フォトリソグラフィ技術を用い、第5層間絶縁膜57、第2ガンマ線遮断膜56、第3層間絶縁膜55、第1、第2保護絶縁膜53、54及び第2層間絶縁膜15をエッチングする。これにより、Pウェル4aの中央の第2の導電プラグ14dに達する深さの第3のビアホール55aを形成する。また、フォトリソグラフィ技術を用い、第4層間

絶縁膜57、第2ガンマ線遮断膜56、第3層間絶縁膜55、第1、第2保護絶縁膜53、54をエッチングすることにより、キャパシタ上部電極49に達する第3、第4のコンタクトホール55b、55cを形成する。

【0207】

次に、酸素雰囲気中にシリコン基板1を置いて熱処理を行う。この熱処理は、キャパシタ誘電体膜48に酸素を供給し、キャパシタ誘電体膜48における酸素欠損を補償し、キャパシタQ0の電気的特性を回復するためのものである。また、Pb又はBiを含有して正方体の結晶を持つ第2ガンマ線遮断膜56の結晶性が向上する。熱処理を行う際の基板温度は、例えば450℃とする。続いて、不活性ガス雰囲気中又は真空中にて熱処理を行う。この熱処理は、第2、第3及び第4層間絶縁膜15、55、57中からガスを放出、即ち脱ガスするためのものである。

【0208】

さらに、高周波エッチングにより、第3のビアホール55aと第3、第4のコンタクトホール55b、55cの内壁面に対して表面処理を行う。続いて、第3のビアホール55aと第3、第4のコンタクトホール55b、55cの内面と第4層層間絶縁膜57上に、例えばスパッタリング法により、導電性密着膜を形成する。導電性密着膜として、例えばTiN膜が例えば100nm程度の厚さに形成される。

【0209】

続いて、導電性密着膜の上に、例えばCVD法により、主導電膜を形成する。主導電膜としては、例えばタングステン膜が例えば300nm程度の厚さに形成される。さらに、例えばCMP法により、第4層間絶縁膜57の表面が露出するまで、主導電膜及び導電性密着膜を研磨する。こうして、第3のビアホール55aと第3、第4のコンタクトホール55b、55c内に残された主導電膜、導電性密着膜により第3のビアプラグ58a、第3、第4の導電プラグ58b、58cが形成される。

【0210】

次に、シリコン基板1をプラズマ雰囲気においてプラズマ洗浄を行う。プラズマ洗浄を行う際に用いるガスは、例えばArガスとする。これにより、第3のビアプラグ58a、第3、第4の導電プラグ58b、58cの表面に存在する自然酸化膜等が除去される。

【0211】

続いて、例えばスパッタリング法により、例えばTiN膜59a、AlCu合金膜59b、Ti膜59c及びTiN膜59dを順次積層することにより、積層導電膜を形成する。TiN膜59aの膜厚は、例えば50nmとする。AlCu合金膜59bの膜厚は、例えば膜厚550nmとする。Ti膜59cの膜厚は、例えば5nmとする。TiN膜59dの膜厚は、例えば膜厚50nmとする。

【0212】

次に、フォトリソグラフィ技術を用い、積層導電膜をパターニングする。こうして、積層導電膜により配線60が形成される。この後、更に、層間絶縁膜、導電プラグ、配線等を複数層に亘って形成する。以上の工程により本実施形態に係る半導体装置のメモリ領域の基本構造が形成される。

なお、第2保護絶縁膜53の上に、第1実施形態に示した第3保護絶縁膜35と同じように、Pb又はBi添加した保護絶縁膜を形成してもよい。

【0213】

上記のような構造半導体のメモリ領域では、外部から照射される放射線が第1ガンマ線遮断膜41及び第2ガンマ線遮断膜56により吸収され、キャパシタ誘電体膜48に到達する輻射を軽減する。即ち、放射線は、第1ガンマ線遮断膜41及び第2ガンマ線遮断膜56として形成される例えばPZTの誘電体膜結晶(正方体)の各頂点のPbに吸収され、結晶中心のZr/Tiへの影響を更に小さくなる。従って、上記構造のメモリ素子は、外部放射線が照射されても、ソフトエラーが起きにくくなるので、医療、衛生品のTAGとして、一緒に放射線(ガンマ線、電子線)滅菌しても、データが保持できる。また、第1ガンマ線遮断41は平坦に形成し易く、その上に形成される金属膜の結晶性を良くする

ことができる。なお、第1ガンマ線遮断膜41及び第2ガンマ線遮断膜56は、ともに放射線遮断膜である。

【0214】

一方、より外部放射線を遮断するために、上記の第1、第2ガンマ線(放射線)遮断膜41、56、下部電極密着膜15d、第2保護絶縁膜54の少なくともいずれかの1つの膜は、屈折率が異なる少なくとも二つ以上の膜の積層構造の1つの層である。これは、光学の原理を利用し、上記の膜に透過する放射線強度を低減するためでもあり、二層以上の屈折率異なる複数層構造を形成している上記の他の実施形態でも同様である。典型的な材料の屈折率の一例は次の通りである。

【0215】

膜の屈折率について、アルミナは1.4〜1.8、TiO2は2.5〜2.9である。また、PZTは2.4〜2.6、PbTiO3は2.7、PbZrO3は2.35、PbSiO3は2.01、PbAl2O4は1.65である。さらに、BiAlO3は2.8、BiGaO3は3.0、SrBi2Ta2O9は2.10〜2.37、Bi4Ti3O12は2.38、(BiLa)4Ti3O12は2.2〜2.35である。

なお、上記の各実施形態において、Pb、Ti、O、Bi、Ga、Sr等は元素記号を示している。

【0216】

ここで挙げた全ての例および条件的表現は、発明者が技術促進に貢献した発明および概念を読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例および条件に限定することなく解釈され、また、明細書におけるそのような例の編成は本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の精神および範囲から逸脱することなく、それに対して種々の変更、置換および変形を施すことができると理解される。

【0217】

次に、本発明の実施形態について特徴を付記する。

(付記1) 半導体基板の上方に形成された第1絶縁膜と、前記第1絶縁膜の上方に形成され、下部電極と上部電極に挟まれる強誘電体膜を有するキャパシタと、前記キャパシタの上に形成される第2絶縁膜と、を有し、前記第1絶縁膜と前記下部電極の間に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第3絶縁膜と、を有する半導体装置。

(付記2) 前記第2絶縁膜の上に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第4絶縁膜を有することを特徴とする付記1に記載の半導体装置。

(付記3) 前記キャパシタと前記第2絶縁膜の間に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第5絶縁膜を有することを特徴とする付記1又は付記2に記載の半導体装置。

(付記4) 前記第3絶縁膜は上側層と下側層を有し、前記上側層は、前記下部電極の下地として形成される密着絶縁膜であり、前記下側層は、前記密着絶縁膜の下に、中間絶縁膜を介して形成される放射線遮断膜であることを特徴とする付記1乃至付記3のいずれか1つに記載の半導体装置。

(付記5) 前記Pb又は前記Biが添加された前記結晶を持つ前記絶縁材料膜は、PbAl2O4、PbAl2O5、PbZrO3、PbTiO3、PbSiO3、Pb(Zr,Ti)O3、BiAlO3、BiGaO3、SrBi2Ta2O9、Bi4Ti2O12、(BiLa)4Ti3O12のいずれかの材料から形成されることを特徴とする付記1乃至付記4のいずれか1つに記載の半導体装置。

(付記6) 前記Pb又は前記Biが添加された前記結晶を持つ前記絶縁材料膜は、前記半導体基板の上方に形成され、屈折率が異なる二つ以上の膜からなる積層構造のうちの一つの膜であることを特徴とする付記1乃至付記5のいずれか1つに記載の半導体装置。

(付記7) 前記第2絶縁膜は、Pb又はBiが添加されたシリコン化合物であることを特徴とする付記1乃至付記6のいずれかに記載の半導体装置。

(付記8) 前記シリコン化合物は、PbSiO3又はBi2Si2O9であることを特徴とする付記7に記載の半導体装置。

(付記9) 前記第2絶縁膜内に形成され、前記上部電極に達する第1の導電性プラグと、前記第2絶縁膜内に形成され、前記下部電極のうち前記上部電極からはみ出したコンタクト領域に達する第2導電性プラグとを有することを特徴とする付記1乃至付記8のいずれか1つに記載の半導体装置。

(付記10) 前記第2絶縁膜内に形成され、前記上部電極に達する第3の導電性プラグと、前記第1絶縁膜及び第3絶縁膜内に形成される第4導電性プラグとを有することを特徴とする付記1乃至付記8のいずれか1つに記載の半導体装置。

(付記11) 半導体基板の上に第1絶縁膜を形成する工程と、前記第1絶縁膜の上に、第2絶縁膜としてPb又はBiが添加された絶縁材料膜を形成する工程と、前記第2絶縁膜の上に、下部電極と上部電極に挟まれるキャパシタ誘電体膜を有するキャパシタを形成する工程と、前記キャパシタ誘電体膜及び前記第2絶縁膜を加熱する工程と、前記キャパシタの上部に第3絶縁膜を形成する工程と、を有する半導体装置の製造方法。

(付記12) 前記第2絶縁膜と前記下部電極の間に、前記第2絶縁膜とは異なる材料の第4絶縁膜を形成する工程を有する付記11に記載の半導体装置の製造方法。

(付記13) 前記第2絶縁膜を形成する前に、前記第1絶縁膜の上に第4絶縁膜としてPb又はBiが添加された絶縁材料膜を形成する工程と、前記第4絶縁膜上に、前記第4絶縁膜及び前記第2絶縁膜の材料とは異なる他の材料から第5絶縁膜を形成する工程と、

前記第2絶縁膜とともに前記第4絶縁膜を加熱する工程と、

を有することを特徴とする付記11に記載の半導体装置の製造方法。

(付記14) 前記第3絶縁膜を形成する前に、前記キャパシタの上に、水素、水の拡散を防止する第1保護絶縁膜を形成する工程と、前記第1保護絶縁膜の上に、第2保護絶縁膜としてPb又はBiが添加された絶縁材料膜を形成する工程と、前記第3絶縁膜、前記第1保護絶縁膜及び前記第2保護絶縁膜内に前記上部電極に達するホールを形成する工程と、酸素含有雰囲気において、前記ホール内を通して前記キャパシタを加熱するとともに前記第2保護絶縁膜を加熱する工程と、前記ホール内に導電プラグを形成する工程と、を有することを特徴とする付記11乃至付記13のいずれか1つに記載の半導体装置の製造方法。

(付記15) 第2保護絶縁膜は、原子層堆積法、有機金属分解法、化学気相蒸着法、有機金属化学気相成長法のいずれかにより形成される膜であることを特徴とする付記11乃至付記14のいずれか1つに記載の半導体装置の製造方法。

(付記16) 前記第3絶縁膜の上に、第6絶縁膜としてPb又はBiが添加された絶縁材料膜を形成する工程と、前記第6絶縁膜、前記第3絶縁膜内に前記上部電極に達するホールを形成する工程と、酸素含有雰囲気において、前記ホール内を通して前記キャパシタを加熱するとともに前記第6絶縁膜を加熱する工程と、前記ホール内に導電プラグを形成する工程と、を有することを特徴とする付記11乃至付記13のいずれか1つに記載の半導体装置の製造方法。

(付記17) 前記第3絶縁膜は、Pb又はBiが添加されたシリコン化合物であることを特徴とする付記6乃至付記9のいずれかに記載の半導体装置の製造方法。

(付記18) 前記シリコン化合物は、PbSiO3又はBi2Si2O9であることを特徴とする付記17に記載の半導体装置の製造方法。

(付記19) 前記Pb又は前記Biが添加された前記絶縁材料膜は、PbAl2O4、PbAl2O5、PbZrO3、PbTiO3、PbSiO3、Pb(Zr,Ti)O3、BiAlO3、BiGaO3、SrBi2Ta2O9、Bi4Ti2O12、(BiLa)4Ti3O12のいずれかの材料から形成されることを特徴とする付記11乃至付記18のいずれか1つに記載の半導体装置の製造方法。

(付記20) 前記Pb又は前記Biが添加された前記絶縁材料膜は、ゾル−ゲル法、有機金属分解法、CSD法、化学気相蒸着法、エピタキシャル成長法、スパッタ法又はMOCVD法のいずれかにより形成される膜であることを特徴とする付記11乃至付記19の

いずれか1つに記載の半導体装置の製造方法。

【符号の説明】

【0218】

T1、T2 MOSトランジスタ

Q、Q0 キャパシタ

1 シリコン基板

12 層間絶縁膜

14a、14b 導電プラグ

15 層間絶縁膜

16 密着絶縁膜

17 キャパシタ下部電極

18 キャパシタ誘電体膜

19 キャパシタ上部電極

22、25 保護絶縁膜

26 層間絶縁膜

27 保護絶縁膜

28 層間絶縁膜

30a、30b 導電プラグ

35 保護絶縁膜

38、40 ガンマ線遮断膜

39 密着膜

44a、44b ビアプラグ(導電プラグ)

45 下地導電膜

46a 密着膜

46b 酸素バリア膜

47 キャパシタ下部電極

48 キャパシタ誘電体膜

49 キャパシタ上部電極

55 層間絶縁膜

56 ガンマ線遮断膜

58b、58c 導電プラグ

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、デジタル技術の進展に伴い、大容量のデータを高速に処理又は保存する傾向が高まっている。このため、電子機器に使用される半導体装置の高集積化及び高性能化が要求されている。

【0003】

そこで、半導体記憶装置、例えばDRAMの高集積化を実現するため、DRAMを構成する容量素子の容量誘電体膜として、従来の珪素酸化物又は珪素窒化物に代えて、強誘電体材料又は高誘電率材料を用いる技術が広く研究開発され始めている。

【0004】

また、より低電圧で且つ高速での書き込み動作及び読み出し動作が可能な不揮発性RAMを実現するため、容量誘電体膜として、自発分極特性を有する強誘電体膜を用いる技術も盛んに研究開発されている。このような半導体記憶装置は、強誘電体メモリ(FeRAM)とよばれる。

【0005】

FeRAMは、強誘電体のヒステリシス特性を利用して情報を記憶する。強誘電体膜を1対の電極間のキャパシタ誘電体膜として有する強誘電体キャパシタは、電極間の印加電圧に応じて分極を生じ、印加電圧を取り去っても自発分極を有する。印加電圧の極性を反転すれば、自発分極の極性も反転する。この自発分極を検出すれば情報を読み出すことが出来る。FeRAMは、高速動作が可能であり、低消費電力であり、書き込み/読み出し耐久性に優れている等の特徴を有する不揮発性メモリであり、今後の更なる発展が見込まれている。

【0006】

一方、近年の宇宙開発では日進月歩で開発が進む民生半導体部品の宇宙転用が進んでいる。また、RFIDや半導体メモリは、医療・ヘルスケア分野に応用へ目指している。そのような分野では、例えば、衛生品にICタグ(TAG)を付けてγ(ガンマ)線で滅菌する。しかしながら、ほとんどの民生部品は、耐放射線性を考慮していないので、放射線試験を行うと、ICタグの信頼性が失われてしまう。

【0007】

信頼性の高いシステムを構築するためには、システム設計段階において考慮すべきことがある。それは半導体メモリにおけるソフトエラーである。例えば、地球にやさしい放射線(ガンマ線、電子線)滅菌方法は、高圧蒸気滅菌法と比べて常温処理であって温度上昇がなく、最終梱包(密閉状態)で滅菌可能であり、また、エチレンオキシド滅菌法と比べて有害な残留物や副生成物などが一切残らない。従って、多数のメリットを持つ放射線(ガンマ線や電子線)による滅菌方法は、広く使用される。従って、滅菌される物品に搭載するFRタグ(RF−TAG)は、放射線照射によるチップのソフトエラーを解決できれば、製品の履歴管理など広く使用できる。

【0008】

高性能通信用半導体メモリの分野では、ソフトエラーやシングルイベント・アップセット(Single-event upset:SEU)に影響されない設計が重要である。ソフトエラーは、ほかの信頼性メカニズムのすべてを含めたものの中でも、最も高い不良率を引き起こしている。半導体技術が進化するにつれて、プロセッサーのパイプライン段数は増加し、メモリセルの有効面積は減少している。その結果、シングルイベント・アップセットに対する素子固有の耐性が低下している。シングルイベント効果は、高エネルギーの外部放射線粒子が引き起こす素子内部の状態の変化、あるいは過渡現象に関係しており、ソフトエラー

とハードエラーに分類できる。

【0009】

ソフトエラーは、メモリ素子をリセットしたりリライトしたりすることによって正常な動作に戻すことができるため、非破壊的なエラーといえる。これに対して、ハードエラーは永久的なもので、ハードエラーの代表的な例はシングルイベント・ラッチアップ(single-event latch-up:SEL)である。

【0010】

主に外部放射線に起因するソフトエラーは、またの名をシングルイベント・アップセットともいう。シングルビット・アップセットは、単一の高エネルギー放射線粒子の通過による1ビットの反転を指し、ほかの反転ビットからは物理的にメモリセル2個分以上、離れているものである。それに対してマルチビット・アップセットは、1つ以上の放射線粒子の通過による数エレメントの反転を指している。

【0011】

シングルイベント・アップセットはランダムに発生するが、破滅的なエラーであることは非常に珍しく、通常は素子を破壊することはない。そして、多くのシステムはある程度のソフトエラー、つまりここでいうシングルイベント・アップセットには耐えることができる。

【0012】

半導体の微細化は、産業界での生き残りのための主要な原動力となっており、また、高集積化や性能の向上およびコスト低減のための原動力ともなっている。半導体技術の進化により、ゲート長をディープサブミクロンのレベルまで縮小するにつれて、メモリ製品のセル寸法も減少し続け、駆動電圧も低下し、そしてセル内部の容量も減少している。例えば、駆動電圧は、5Vから3.3V、1.8Vからさらに低電圧へと変化している。また、容量は、10fFから5fF、そしてさらに低容量へと変化している。低容量化が進むにつれてメモリセルの臨界電荷量は縮小を続け、それによってメモリセルのシングルイベント・アップセットに対する耐性も低下している。それに従い、低エネルギー・アルファ線、あるいは宇宙線粒子もセルを妨害する要因となっている。

【0013】

半導体での空乏領域の電界は、その通った跡に電子・正孔対を一直線に生成し、電荷が浮遊する。その結果、トランジスタには電流の乱れが生じる。電界の影響下にある空乏領域は自由電子を捕捉する。わずかな過剰電荷がデバイスノードに浮遊し、これがある臨界電荷量を超えるとメモリセルの状態を反転させることになる。臨界電荷量が小さければ小さいほどソフトエラーレートは高くなる。アルファ線は低エネルギーを有しているため通常はシングルビット・アップセットを引き起こすが、低い供給電圧のメモリではマルチビット・アップセットを引き起こすこともある。

【0014】

高エネルギー宇宙線粒子は地球の高層大気と反応し、それらの衝突が太陽フレアーや銀河宇宙線粒子により変調され、高エネルギー陽子や中性子を生成する。高エネルギー中性子は10MeV〜800MeVのエネルギーを持っている。一方、陽子は30MeV以上のエネルギーを持っている。高エネルギー中性子は電荷を持たない。従って、これらはクーロン力による半導体材料との相互作用はない。そのためシリコンとの相互作用は、低エネルギー・アルファ線の場合とは異なる。

【0015】

高エネルギー中性子がソフトエラーを引き起こすためには、シリコンの原子核と衝突し、シリコン原子核のイオン化の衝撃を受けることにより、イオン化された粒子を生成しなくてはならない。この衝突はアルファ線や、より重いイオンを生成することがある。衝突によって生まれたものは、プラスチックモールド材からの通常のアルファ線よりも、高エネルギーを持つ電子・正孔対を生成する。

【0016】

一般に高性能メモリは、例えばSRAMセル、組み合わせ論理、ラッチ回路などで構成

されている。高性能通信用メモリでは、通常、チップの面積効率は低い。過去の学術研究では、組み合わせ論理はマスキングによる自然の耐性のために、通常のメモリセルに比べソフトエラーの影響を受けにくいということが示されている。しかしながら、素子の大きさとプロセッサーのパイプラインの段数を増やせば、この自然の耐性を低下させることになる。

【0017】

素子のシングルイベント・アップセットに対する耐性を向上させる別の方法は、メモリセル内に蓄える臨界電荷量を増やし、そのしきい値を増加させることである。

【0018】

その他に、絶縁物上にシリコン結晶を成長させ、その上にトランジスタなどを集積するSOI技術(Silicon On Insulator)を使用し、電荷の深さを減少させることにより素子の信頼性を向上させる方法がある。p型MOSトランジスタの閾値電圧はセルのリカバリー時間に影響し、これは間接的にシングルイベント・アップセットに対する耐性にも影響を与える。

【0019】

半導体装置の封入に用いるパッケージの材料として、Pb、Hf、Ir、Mo、Os、Pd、Pt、Re、Ta、Tb、Tl、W、Uのうちの少なくとも1種類の元素を重量比で1%以上含ませたセラミツクあるいは樹脂を用いることにより、有効に放射線を遮蔽するパッケージを得ることが知られている(特許文献1)。

【0020】

また、鉛またはタリウムの化合物を、半導体チップ上に塗布または添付し、あるいは樹脂材料に含有させて封止することにより、α線による影響を低減しメモリ等のソフトエラーを防止することが知られている(特許文献2)。

【先行技術文献】

【特許文献】

【0021】

【特許文献1】特開昭60−134448号公報

【特許文献2】特開昭57−090966号公報

【発明の概要】

【発明が解決しようとする課題】

【0022】

しかしながら、封入用パッケージを改善しても、EEPROMのように放射線に対する半導体装置の耐性が低いものも存在するし、放射線耐性能力が比較的高い半導体装置であってもさらなる耐性能力の向上が要求されるものもある。

【0023】

本発明の目的は、放射線耐性能力をさらに向上することができる半導体装置及びその製造方法を提供することにある。

【課題を解決するための手段】

【0024】

本実施形態の1つの観点によれば、半導体基板の上方に形成された第1絶縁膜と、

前記第1絶縁膜の上方に形成され、下部電極と上部電極に挟まれる強誘電体膜を有するキャパシタと、前記キャパシタの上に形成される第2絶縁膜と、を有し、前記第1絶縁膜と前記下部電極の間に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第3絶縁膜と、を有する半導体装置が提供される。

発明の目的および利点は、請求の範囲に具体的に記載された構成要素および組み合わせによって実現され達成される。前述の一般的な説明および以下の詳細な説明は、典型例および説明のためのものであって、本発明を限定するためのものではない、と理解される。

【発明の効果】

【0025】

本実施形態によれば、キャパシタ下部電極の下に、Pb又はBiが添加された結晶を持

つ第3絶縁膜を形成している。Pb又はBiが添加された結晶を有する第3絶縁膜は、例えば200nm以下に薄く形成しても高い放射線耐性能力を有することが本発明者によって確認された。また、第3絶縁膜は、その上のキャパシタの強誘電体膜の結晶性を改善するための加熱の際に同時に加熱されるので、加熱処理を追加することなくその結晶性を改善することができる。

従って、外部から半導体装置内に向けて放射線が照射されても、放射線は第3絶縁膜により部分吸収されて、キャパシタの誘電体膜に到達する放射線の輻射が軽減される。さらに、Pb又はBiが添加された絶縁膜は、成膜当初においてアモルファスに形成することにより平坦性を良好にできるので、その上に形成されるキャパシタの下部電極とその上の強誘電体膜の結晶性を良好にすることができる。これらにより、キャパシタのメモリ書き込み能力、メモリ保持能力を高めることができる。

【図面の簡単な説明】

【0026】

【図1A】図1A、図1Bは、第1実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図1C】図1C、図1Dは、第1実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図1E】図1E、図1Fは、第1実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図1G】図1G、図1Hは、第1実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図1I】図1Iは、第1実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図2】図2A、図2B及び図2Cは、第1実施形態に係る半導体装置に書き込まれるデータのガンマ線照射量依存特性を例示する図である。

【図3】図3は、第2実施形態に係る半導体装置を例示する断面図である。

【図4】図4は、第3実施形態に係る半導体装置を例示する断面図である。

【図5】図5は、第3実施形態に係る半導体装置の別の例を示す断面図である。

【図6】図6は、第3実施形態に係る半導体装置をさらに別の例を示す断面図である。

【図7A】図7A、図7Bは、第4実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図7C】図7C、図7Dは、第4実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図7E】図7Eは、第4実施形態に係る半導体装置の製造工程の一部を例示する断面図である。

【図8】図8は、強誘電体の典型であるPZTの結晶構造の一例を示す図である。

【図9】図9は、PZTから誘電体膜を形成した構造を有する強誘電体キャパシタのヒステリシス曲線を示す。

【発明を実施するための形態】

【0027】

まず、不揮発性メモリであるFeRAM及びEEPROMのガンマ線照射後のデータの状況を表1に示す。評価サンプル(タグ形状)は、2KバイトのFeRAMを搭載した第1のRFID−LSIと、128バイトのEEPROMを搭載した第2のRFID−LSIであり、それぞれ10個用意した。評価内容は次の(1)〜(3)の処理を行い、評価により正常であったサンプルの数をPASSとして示している。

(1)メモリ領域、指定ブロックに右記データパターンを書き込む。

(2)20kGy、50kGy、100kGyのガンマ線を照射する。

(3)メモリ領域のデータを読み出し、照射前後のデータを比較する。

【表1】

【0028】

評価結果によれば、EEPROMは最低の20kGyのガンマ線照射量であってもデータが全滅する。つまり、EEPROMなどの電子の蓄積によりデータを保持する構成のメモリの場合、ガンマ線照射により電子が励起され、データが破壊される。これに対し、3VのReRAM品は、最大の100kGyのガンマ線照射量であってもデータが保持されることを確認した。

【0029】

次に、1.8VのFeRAM品(スタンダードセル、ゲートアレイ)をガンマ線照射後データの状況を表2、表3に示す。表2、表3の結果により、SS(Same State)/OS(Opposite State)共に照射量増加に伴って誤り(FAIL)数が増加する。即ち、規格値である照射量50kGyでも厳しい結果となっている。

なお、SSは、ガンマ線の照射前の書込みと同じ分極状態での読取りを表し、OSは、ガンマ線照射前の書込みと逆の分極状態での読取りを表しています。

【表2】

【表3】

【0030】

図8には、強誘電体の典型であるPZT(チタン酸ジルコン酸鉛)の結晶構造を示し、図9には、PZTから誘電体膜を形成した構造の強誘電体キャパシタのヒステリシス曲線を示す。鉛(Pb)、ジルコニウム(Zr)、チタン(Ti)、酸素(O)を含むPZT

(Pb(ZrTi)O3)は、図8に示すようなペロブスカイト構造(ABO3型)の代表的な強誘電体材料であり、正方体の各頂点にPbが、体心にZrやTiが配置され、そしてZrやTiを中心としてOは正方晶の各面心に配置している。

【0031】

酸素と金属ZrやTiから成る八面体の向きは、Pbとの相互作用により容易に歪みが発生する。格子の中にZr/Tiイオンが置かれているが、このイオンは二つの安定点を持ち、外部の電界によってその位置を変える性質、即ち分極作用がある。さらに、一度どちらの点に位置すると電界を取り去ってもその位置が変わることはない。つまり、分極状態が記憶される。従って、強誘電体膜の上下に電極を設けてキャパシタを構成し、電極電圧と分極方向と分極量をプロットすればヒステリシス(履歴)が得られ、“1”、“0”を記憶できることになる。

【0032】

このような分極による記憶状態は安定であり、その原理を利用すると、外部電界を印加すると分極が発生し、Zr/Tiイオンが結晶内部で上下する。さらに、電界をかけるのを止めても分極はそのままの状態で残り、残留分極が生じる。2つの安定点をデータ“1”とデータ“0”として記憶する。

【0033】

従って、FeRAMではデータの保持は結晶の原子配置によってなされるため、ガンマ線に照射されても、原則として上記の問題は起こらない。しかしながら、分極反転特性の劣化は照射量に応じて生じるため、データ読み出し精度が低下し、ミスリードを引き起こすことがある。従って、従来のFeRAMの構造では、耐放射線照射能力は不十分であり、特に低電圧動作メモリの耐放射線能力を向上させる必要がある。

【0034】

以上のことから、強誘電体キャパシタを有する半導体装置は、キャパシタの誘電体膜に放射線の被爆量を低減させ、キャパシタを低電圧で動作させ、耐インプリント特性及び耐放射線照射能力を向上させ、信頼性を高くすることが要求される。

【0035】

以下に、図面を参照して本発明の実施形態を説明する。図面において、同様の構成要素には同じ参照番号が付されている。

(第1の実施の形態)

図1A〜図1Iは、第1実施形態に係る半導体装置及びその製造方法を示す断面図である。本実施形態による半導体装置は、メモリセルのキャパシタがプレーナ型となる構造を有している。次に、図1Aに示す構造を形成するまでの工程を説明する。

【0036】

まず、半導体基板であるシリコン基板1の活性領域の周囲に素子分離用溝1uを形成した後に、その中に絶縁膜として例えばシリコン酸化膜を埋込む。素子分離用溝1uの中の絶縁膜は、素子分離絶縁構造であるSTI(Shallow Trench Isolation)2として使用される。なお、素子分離絶縁構造は、STI2に限られるものではなく、LOCOS法により形成されてもよい。

【0037】

ついで、シリコン基板1の一部の活性領域にp型不純物をイオン注入して第1、第2のPウェル3、4を形成し、さらに、別の活性領域にn型不純物を導入してNウェル(不図示)を形成する。第1のPウェル3と第2のPウェル4は、STI2を介して隣接している。なお、p型不純物、n型不純物のいずれかイオン注入する際には、不純物を注入しない領域をレジストパターン(不図示)で覆う。

【0038】

さらに、シリコン基板1の活性領域の表面を熱酸化することによりシリコン酸化膜を形成し、そのシリコン酸化膜をゲート絶縁膜5a、5bとして使用する。ゲート絶縁膜5a、5bの膜厚は、例えば6〜7nm程度とする。

【0039】

続いて、シリコン基板1の主面の上方にポリシリコン膜をCVD法により例えば約200nmの厚さに形成した後に、フォトリソグラフィ技術を用いてポリシリコン膜をパターニングしてPウェル3、4の上に第1、第2のゲート電極6a、6bを形成する。第1、第2のゲート電極6a、6bは、STI2の上にも形成されるワード線の一部である。また、第1、第2のゲート電極6a、6bは、第1、第2のPウェル3、4上に複数形成されてもよい。

【0040】

次に、第1、第2のゲート電極6a、6bをマスクに使用して第1、第2のPウェル3、4内にn型不純物、例えばリン(P)をイオン注入法により導入する。これにより、第1、第2のPウェル3、4のうち第1、第2のゲート電極6a、6bの両側に浅いn型エクステンション領域7a、7b、7c、7dを形成する。

【0041】

その後に、シリコン基板1の上側全面に絶縁膜を形成し、その絶縁膜をエッチバックして第1、第2のゲート電極6a、6bの側面に絶縁性のサイドウォール9a、9bとして残存させる。その絶縁膜として、例えばCVD法により酸化シリコン膜を例えば約300nmの厚さに形成する。

【0042】

続いて、サイドウォール9a、9bとゲート電極6a、6bをマスクに使用し、シリコン基板1内にn型不純物、例えば砒素(As)をイオン注入する。これにより、第1、第2のゲート電極6a、6bの両側方の第1、第2のPウェル3、4内にエクステンション領域7a、7b、7c、7dよりも深く且つ高不純物濃度の不純物拡散領域を形成する。それらの不純物拡散領域は、エクステンション領域7a、7b、7c、7dに一部が接続されるソース/ドレイン領域8a、8b、8c、8dとして使用される。

【0043】

次に、シリコン基板1の上の全体に、例えばスパッタリング法により、高融点金属膜、例えばコバルト膜を形成する。続いて、露出しているソース/ドレイン領域8a、8b、8c、8dとゲート電極6a、6bのそれぞれの上層と高融点金属膜とを熱処理により反応させる。これにより、ソース/ドレイン領域8a、8b、8c、8dとゲート電極6a、6bの上にそれぞれシリサイド層10a〜10f、例えばコバルトシリサイド層が形成される。その後に、例えばウエットエッチングにより、残された高融点金属膜をエッチング除去する。

【0044】

以上のような方法により形成された第1のPウェル3、ゲート絶縁膜5a、第1のゲート電極6a、ソース/ドレイン領域8a、8b等により第1のNMOSトランジスタT1が形成される。また、第2のPウェル4、ゲート絶縁膜5b、第1のゲート電極6b、ソース/ドレイン領域8c、8d等により第2のNMOSトランジスタT2が形成される。

【0045】

その後に、シリコン基板1上の全面に、第1、第2のNMOSトランジスタT1、T2を覆うカバー絶縁膜11として例えばシリコン窒化酸化膜をプラズマCVD法により例えば約200nmの厚さに形成する。さらに、カバー絶縁膜11上に、第1層間絶縁膜12として、例えばTEOS(Tetra Ethoxy Silane)ガスを用いるプラズマCVD法によりシリコン酸化膜を例えば約1μmの厚さに形成する。続いて、例えば化学機械研磨(CMP)法により第1層間絶縁膜12の上面を平坦化する。これにより、半導体基板1の主面から第1層間絶縁膜12の上面までの高さは、例えば785nm程度となる。

【0046】

次に、図1Bに示す構造を形成するまでの工程を説明する。

まず、フォトリソグラフィ技術を用い、第1層間絶縁膜12のうち第1、第2のPウェル3、4内のうち互いに近いそれぞれの一方のソース/ドレイン領域8b、8cの上をエッチングし、シリサイド層10d、10eに達する第1、第2のコンタクトホール12a、12bを形成する。第1、第2のコンタクトホール12a、12bの径を例えば約0.

25μmとする。

【0047】

次に、第1層間絶縁膜12の上面と第1、第2のコンタクトホール12a、12bの内面に、例えば、スパッタリング法により厚さ30nmのTi膜と厚さ20nmのTiN膜を順に形成する。Ti膜とTiN膜は、密着膜13aとなる。続いて、密着膜13aの上に、コンタクトホール12a、12b内を完全に充填する厚さに主導体膜13bとしてタングステン(W)をCVD法により形成する。主導電膜13bの膜厚は、例えば300nm程度とする。

【0048】

その後に、例えばCMP法により、第1層間絶縁膜12の上面が露出するまで主導電膜13b及び密着膜13aを研磨する。こうして、第1、第2のコンタクトホール12a、12b内に残された主導体膜13b及び密着膜13aを第1、第2の導電プラグ14a、14bとして使用する。

【0049】

次に、図1Cに例示する構造を形成するまでの工程について説明する。

まず、第1層間絶縁膜12及び第1、第2の導電プラグ14a、14bの上に、例えば、シリコン窒化酸化膜15aをプラズマCVD法により例えば約100nmの厚さに形成する。シリコン窒化酸化膜15aは、後述するキャパシタからの水分の移動を抑制するとともに、第1、第2の導電プラグ14a、14bの上面の酸化を防止するために形成される。

【0050】

次に、シリコン窒化酸化膜15a上に、例えば、TEOSガスを使用し、プラズマCVD法によって後述の密着絶縁膜16とともに密着性を向上するための絶縁膜としてシリコン酸化膜15bを形成する。シリコン酸化膜15bの膜厚を例えば約130nmとする。

【0051】

シリコン窒化酸化膜15bとシリコン酸化膜15aとにより第2層間絶縁膜15が形成される。なお、第2層間絶縁膜15は、シリコン窒化酸化膜15aとシリコン酸化膜15bとの積層膜に限定されるものではない。例えば、酸化防止膜として、シリコン窒化酸化膜15aの代わりにシリコン窒化膜や酸化アルミニウム膜を形成してもよい。

【0052】

続いて、例えば窒素雰囲気中にて、熱処理を行う。かかる熱処理は、第2層間絶縁膜15中に含まれているガスを放出するため、即ち脱ガスのためである。この熱処理を行う際の基板温度は、例えば約650℃とし、熱処理時間は、例えば約30分とする。

【0053】

次に、第2層間絶縁膜15上に、例えば、高周波スパッタリング法によりアモルファスの密着絶縁膜16を形成する。密着絶縁膜16は、後述するキャパシア下部電極17に対する密着性を確保するとともに、放射線を遮断するために形成される。

【0054】

密着絶縁膜16としては、Pb又はBi(ビスマス)添加した絶縁膜、例えば、強誘電体膜であるチタン酸ジルコン酸鉛(PZT:(PbZrxTi1−xO3))膜(0≦x≦1)、又はCa、Sr、Laが少なくともに一つ元素添加されたチタン酸ジルコン酸鉛、又はビスマス層状結晶構造を持つ(Bi,Sr)TiO3、(Bi,La)4Ti3O12膜等が用いられている。その以外に、Pb又はBi添加したPbAl2O4、PbAl2O5、PbZrO3、PbTiO3、PbSiO3、Pb(Zr,Ti)O3、BiAlO3、BiGaO3、SrBi2Ta2O9、Bi4Ti2O12膜などでもよい。密着絶縁膜16は、それらの材料から選択した二つ膜を積層した構造であってもよい。

【0055】

密着絶縁膜16としてPZT膜を用いる場合には、その膜厚は、例えば、10nm〜50nm程度、より好ましくは、20nm〜30nm程度に形成される。PZTを高周波スパッタリング法により形成する際の成膜条件は、例えば次の通りとする。まず、ターゲッ

トとしてジルコニウムチタン酸鉛からなるPZT系ターゲットを使用する。また、基板温度は、例えば約50℃に設定される。さらに、成膜室内に導入するガスとしては、例えばArガスを用いる。成膜室内の圧力は、例えば約1Paとする。印加電力は、例えば1.0kWとする。ここでは、密着絶縁膜16の膜厚を、例えば約20nmとする。

【0056】

次に、密着絶縁膜16上に、第1の導電膜17aとして貴金属膜を例えばスパッタリング法により形成する。第1の導電膜17aは、後述するキャパシタQの下部電極17の一部となるものである。第1の導電膜17aとして、例えば50nm〜150nm程度のPt膜を形成する。第1の導電膜17aを形成する際の成膜条件は、例えば次の通りとする。ターゲットとしてPtを使用する。また、基板温度は、例えば350℃に設定される。成膜室内に導入するガスとして例えばArガスを用いる。成膜室内の圧力は、例えば約1Paとする。また、印加電力を例えば約0.3kWに設定する。

【0057】

ここでは、第1の導電膜17aとして、プラチナ膜を形成する場合を例に説明したが、第1の導電膜17aはプラチナ膜に限定されるものではなく、Ir膜、Ru膜、酸化ルテニウム(RuO2)膜、SrRuO3膜等を形成してもよい。また、それらのうちいずれかを選択した積層膜により第1の導電膜17aを形成してもよい。

【0058】

次に、第1の導電膜17aの上に第2の導電膜17bを形成する。第2の導電膜17bとして、例えば厚さ0.1〜3nmの酸化プラチナ膜(PtOx膜)を形成する。第1の導電膜17aとして例えばIr膜やRu膜を用いる場合には、第2の導電膜17bとして下とは異なる例えばIr膜やRu膜を用いてもよい。この場合、第2の導電膜17bとしてIr膜を形成する場合には、Ir膜を例えば10〜30nm程度の厚さに形成する。

【0059】

また、第1の導電膜17aとして、Pt膜、Ir膜、Ru膜を用いる場合には、第2の導電膜17bとして、SrRuO3膜、LaSrMnO3膜、LaSrCoO3膜等を用いてもよい。この場合には、SrRuO3膜、LaSrMnO3膜又はLaSrCoO3のそれぞれの膜厚は、例えば1〜5nm程度であることが好ましい。

【0060】

次に、第2の導電膜17aの上に、第1の誘電体膜18aを形成する。第1の誘電体膜18aは、スパッタリング法により形成される。第1の誘電体膜18aとして、例えば、強誘電体膜を形成する。第1の誘電体膜18aは、ペロブスカイト型結晶構造又はビスマス層状化粧構造であってABOx型の結晶構造を持つ。この場合、金属種AがLi、Na、Ca、Sr、Ba、Laから選ばれる一種類以上の金属であり、金属種BがTi、Zr、Ta、Nbから選ばれる一種類以上の金属であり、酸素Oはx(正の数)の組成比を有する。

【0061】

第1の誘電体膜18aとして、例えば、チタン酸ジルコン酸鉛(PZT:PbZrxTi1−xO3)膜(0≦x≦1)、またはCa、Sr、Laが少なくともに一つ元素添加されたチタン酸ジルコン酸鉛が用いられる。または、ビスマス層状結晶構造を持つ(Bi,Sr)TiO3、チタン酸ビスマスランタン酸化物(BLT:(Bi,La)4Ti3O12)膜、ストロンチウム・ビスマス・タンタル酸化物(SBT:SrBi2Ta2O9)等が用いられる。

【0062】

PZT膜を用いる場合には、第1の誘電体膜18aの膜厚を例えば30nm〜90nm程度とする。より好ましくは、第1の誘電体膜18aの膜厚を、例えば50nm〜70nm程度とし、ここでは、例えば約60nmとする。

【0063】

第1の誘電体膜18aの成膜温度を例えば30℃以上、100℃以下とすることが好ましい。第1の誘電体膜18aの成膜温度を30℃より低く設定する場合には、ウェハ面内

において膜厚及び結晶性が不均一となってしまう場合がある。これに対し、第1の誘電体膜18aの成膜温度を100℃より高く設定する場合には、第1の誘電体膜18aにおいて、(101)配向及び(100)配向が多くなり、(111)配向が少なくなるので、良好な電気的特性のキャパシタの誘電体膜を得ることが困難となることがある。従って、本実施形態では、第1の誘電体膜18aの成膜温度を、例えば50℃に設定する。

【0064】

また、第1の誘電体膜18aを形成する方法はスパッタリング法に限られるものではない。例えば、MOCVD(Metal Organic Chemical Vapor Deposition、有機金属化学気相成長)法、ゾル・ゲル法、有機金属分解(MOD、Metal Organic Deposition)法、化学溶液堆積(CSD、Chemical Solution Deposition)法、CVD法、等により、アモルファスの第1の誘電体膜18aを形成してもよい。

【0065】

次に、例えばRTA法により、酸素を含む雰囲気中にて、第1の誘電体膜18aを結晶化する。より具体的には、不活性ガス、例えばアルゴンと酸素ガスとを含む混合ガスの雰囲気中にて、第1の誘電体膜18aを熱処理する。熱処理時間は、例えば90秒とする。第1の誘電体膜18aの結晶性を向上するためには酸素ガス流量を10〜70sccm、例えば25sccmとすることが好ましい。

【0066】

第1の誘電体膜18aの材料としてPZTが用いられている場合には、熱処理温度、即ち基板温度は、例えば550℃〜650℃に設定される。ここでは、第1の誘電体膜18aを結晶化する際の熱処理温度を、例えば600℃とする。適切な熱処理温度は、強誘電体材料の種類により異なる。例えば、PZTや、その他の元素を微量添加するPZTの熱処理温度は630℃以下、BLTは700℃以下、SBTは800℃以下が望ましい。この熱処理により第1の誘電体膜18aは結晶化される。同時に、第1の誘電体膜18aと第2の導電膜17bの界面も密着性が高く制御されている。さらに、密着絶縁膜16の少なくとも一部も同時に結晶化され、その一部はPb又はBi(ビスマス)添加した正方体の結晶絶縁膜となる。

【0067】

次に、第1の誘電体膜18aの上に、アモルファスの第2の誘電体膜18bを例えばスパッタ法により形成する。第2の誘電体膜18bとしては、例えば膜厚が1nm〜30nm、例えば約10nmの強誘電体膜を形成する。第2の誘電体膜18bの材料としては、PZT、PLZT、或いはLaとCaとSrとが添加されたチタン酸ジルコン酸鉛が用いられる。

【0068】

次に、第2の誘電体膜18bの上に第1の導電性酸化膜19aを形成する。第1の導電性酸化膜19aは、Pt、Ir、Ru、Rh、Re、Os、Pdからなる群から選択された少なくとも1種の元素の酸化物から形成される。例えば、第1の導電性酸化膜19aの形成に当たっては、先ず、第2の誘電体膜18b上に、厚さが20〜70nm、例えば約25nmで成膜の時点で結晶化したIrOx膜をスパッタ法により形成する。このときの成膜温度を例えば約300℃とし、成膜ガスとしてAr及びO2を用い、これらの流量Ar=140sccm、O2=60Sccmとする。また、スパッタパワーは、例えば1kW程度とする。

【0069】

ついで、RTA法でシリコン基板1を加熱する。その加熱条件は、温度を725℃に設定し、酸素を流量20Sccm、Arを流量2000Sccmで雰囲気中に導入するとともに、熱処理時間を60秒間とする。この熱処理は第1の誘電体膜18aの結晶性を更に向上し、非晶質の第2の誘電体膜18bを結晶化する。同時に、密着絶縁膜16の結晶性も向上する。

【0070】

第1、第2の誘電体膜18a、18bを完全に結晶化させる同時に、第1の導電性酸化

膜19aのプラズマダメージも回復でき、第1、第2の誘電体膜18a、18bは、連続的な柱状結晶を持つ誘電体膜になる。同時に、第1、第2の誘電体膜18a、18b中の酸素欠損を補償する。第1、第2の誘電体膜18bは、ペロブスカイト型結晶構造、ビスマス層状結晶構造のいずれかのABOx型結晶構造を持つことが好ましい。

【0071】

次に、第1の導電性酸化膜19aの上に、例えばスパッタリング法により、第2の導電性酸化膜19bを形成する。第第1、第2の導電性酸化膜19a、19bは、パターニングにより後述するキャパシタQの上部電極19となるものである。第2の導電性酸化膜19bとしては、例えば酸化イリジウム膜を形成する。

【0072】

第2の導電性酸化膜19bとして形成される酸化イリジウム膜(IrOy膜)における酸素の組成比yは、例えば0<y≦2とする。第2の導電性酸化膜19bとして形成される酸化イリジウム膜(IrOy膜)における酸素の組成比yは、第1の導電性酸化膜19aとして形成される酸化イリジウム膜(IrOx膜)における酸素の組成比xより大きいことが好ましい。

【0073】

第2の導電性酸化膜19bにおける酸素の組成比を第1の導電性酸化膜19aにおける酸素の組成比より大きく設定する理由は、酸素の組成比を大きく設定すると水素の拡散を防止する機能が大きくなるからである。第2の導電性酸化膜19bが水素バリア膜としても十分に機能し得るため、第1、第2の誘電体膜18a、18bが水素により還元されるのを防止しできる。第2の導電性酸化膜19bの膜厚は、例えば70〜200nm程度に形成されることが好ましく、より具体的には例えば約150nm程度とする。

【0074】

第2の導電性酸化膜19bを成膜する際のスパッタリングによる成膜条件は、例えば次の通りとする。成膜室内に導入するガスは、例えばアルゴンガスを例えば100sccm、酸素ガスを例えば100sccmで導入して混合ガスとする。成膜室内の圧力は、例えば0.8Paとする。スパッタパワーは、例えば1.0kWとする。成膜時間は、例えば59秒間程度とする。このような成膜条件で第2の導電性酸化膜19bを成膜すると、第2の導電性酸化膜19bの膜厚は、例えば約150nm程度となる。

【0075】

その後に、ウェハ状のシリコン基板1の主面と反対側の下面(裏面)を洗浄する。このような背面洗浄は、一般のウェハ洗浄とは異なるものであり、シリコン基板1の裏面に付着した誘電体膜18a、18bを除去するためのものである。

【0076】

次に、第2の導電性酸化膜19b上に、保護膜20を例えばスパッタリング法により形成する。保護膜20として、例えば34nm程度の厚さを有するTiN膜を形成する。保護膜20を形成する際には、例えばTiのターゲットを用いる。保護膜20を形成する際の基板温度は、例えば150℃とする。成膜室内における雰囲気は、例えば流量50sccmのArガスと流量90sccmのN2ガスとの混合ガスの雰囲気とする。保護膜20は、還元性物質をバリアする機能を有するものであり、第1、第2の導電性酸化膜19a、19bをパターニングする際のハードマスクとしても機能する。

【0077】

ここでは、保護膜20としてTiN膜を形成する場合を例に説明したが、TiN膜に限定されるものではない。保護膜20として、例えば、TaN膜、TiON膜、TiOx膜、TaOx膜、TaON膜、TiAlOx膜、TaAlOx膜、TiAlON膜、TaAlON膜、TiSiON膜、TaSiON膜、TiSiOx膜、TaSiOx膜、AlOx膜、ZrOx膜等を形成してもよい。

【0078】

次に、保護膜20上に、例えばフォトレジスト膜(不図示)をスピンコート法により形成する。続いて、フォトリソグラフィ技術を用い、上部電極となるパターンの長さ方向に

ある2つの対向辺を区画するストライプ平面形状にフォトレジスト膜(不図示)をパターニングする。

【0079】

続いて、フォトレジスト膜(不図示)をマスクとして使用し、保護膜20及び第1、第2の導電性酸化膜19a、19bをエッチングする。その後に、アッシング、溶剤等を使用してフォトレジスト膜(不図示)を除去する。さらに、保護膜20を例えばドライエッチングにより除去する。

【0080】

その後に、酸素を含む雰囲気中にシリコン基板1を置いて熱処理を行う。この熱処理は、第1、第2の誘電体膜18a、18bに加わったダメージを回復するための回復アニールである。熱処理温度は、例えば600〜700℃とする。ここでは、熱処理温度は、650℃とし、また、熱処理時間は、例えば40分とする。

【0081】

次に、図1Dに例示する構造を形成するまでの工程を説明する。

まず、既にストライプ状に成形された第1、第2の導電性酸化膜19a、19bとそれらの隙間から露出した第2の誘電体膜18bの上に、フォトレジスト膜21を例えばスピンコート法により形成する。続いて、フォトリソグラフィ技術を用いてフォトレジスト膜21をパターニングする。この場合のフォトレジスト膜21のパターンには、複数のストライプ状の第1、第2の導電性酸化膜19a、19bを跨ぐパターンが間隔をおいて複数形成されている。

【0082】

続いて、図1Eに例示するように、パターニングされたフォトレジスト膜21をマスクとして、第1、第2の導電膜19a、19bと第1、第2の誘電体膜18a、18bをエッチングする。この後、フォトレジスト膜21を除去する。このパターニングによって、第1、第2の導電膜19a、19bから複数のキャパシタ上部電極19が形成される。同時に、第1、第2の誘電体膜18a、18bから複数のキャパシタ誘電体膜18が形成される。キャパシタ誘電体膜18のそれぞれの上には、複数の上部電極19が形成されている。

【0083】

その後に、酸素雰囲気中にて、キャパシタ上部電極19、キャパシタ誘電体膜18等を熱処理する。熱処理条件を例えば300〜650℃とし、熱処理時間を例えば30分〜120分とする。

【0084】

次に、図1Fに示す構造を形成するまでの工程を説明する。

まず、キャパシタ上部電極19、キャパシタ誘電体膜18及び第2の導電膜17bの上に第1保護絶縁膜22を例えばスパッタリング法又はCVD法により形成する。第1保護絶縁膜22としては、例えば酸化アルミニウム膜を形成する。第1保護絶縁膜22の膜厚は、例えば20〜50nm程度とする。

【0085】

第1保護絶縁膜22を形成するための成膜装置としては、反応性RFスパッタリング装置を用いる。ターゲットとしては、直径300mmの酸化アルミニウムセラミックターゲットを用いる。酸化アルミニウム膜の成膜条件は、例えば次の通りとする。アルゴンガス雰囲気中でRFマグネトロンスパッタを行い、40〜100秒の性膜時間で膜厚が20〜50nmの酸化アルミニウム膜を形成する。その際、スパッタパワーを2.0kWに、温度を室温にそれぞれ設定し、また、反応室内の圧力を1.0Paに設定する。

【0086】

第1保護絶縁膜22は、水素や水分等によりキャパシタ誘電体膜18が還元されるのを防止するためのものである。従って、第1保護絶縁膜22の材料は、酸化アルミニウムに限られるものではなく、酸化チタン、酸化タンタル、酸化ジルコニウム、窒化タンタル、窒化アルミニウム、酸窒化アルミニウムのいずれかから選択して膜を形成してもよい。

【0087】

次に、酸素雰囲気中にシリコン基板1を置いて熱処理を行う。熱処理条件は、温度を例えば400〜600℃とし、また、熱処理時間を例えば30分〜120分とする。

【0088】

その後に、第1保護絶縁膜22の上に、例えば、フォトレジスト膜23をスピンコート法により形成する。次に、フォトリソグラフィ技術を用い、フォトレジスト膜23をキャパシタの下部電極の平面形状にパターニングする。即ち、フォトレジスト膜23のパターンは、キャパシタ誘電体膜18とその上のキャパシタ上部電極19を含むとともにキャパシタ誘電体膜18から突出する領域を有している。

【0089】

次に、図1Gに例示するように、フォトレジスト膜23をマスクとして使用し、第1保護絶縁膜22、第1、第2の導電膜17a、17b及び密着絶縁膜16をエッチングする。これによりパターニングされた第1、第2の導電膜17a、17bはキャパシタ下部電極17として使用される。その後、フォトレジスト膜23を除去する。

【0090】

以上のキャパシタ下部電極17、キャパシタ誘電体膜18及びキャパシタ上部電極19によりキャパシタQが形成される。第1保護絶縁膜22は、キャパシタ上部電極19及びキャパシタ誘電体膜18、キャパシタ下部電極17を覆うように残存する。

【0091】

次に、酸素を含有する雰囲気にシリコン基板1を置いて熱処理を行う。熱処理の温度を例えば200〜400℃とする。また、熱処理の時間を例えば30〜120分間とする。この熱処理によれば、キャパシタQをパターニング工程に吸着した水分や不純物を飛ばし、第1保護絶縁膜22の成膜後に熱処理する時に蒸し焼きを防げ、さらに、キャパシタの第1保護絶縁膜22が剥がれにくくなる。酸素を含有する雰囲気としては、酸素のみの雰囲気、アルゴン及び酸素を含有する雰囲気、並びに、窒素及び酸素を含有する雰囲気等が挙げられる。

【0092】

次に、図1Hに示す構造を形成するまでの工程について説明する。

まず、第1保護絶縁膜22及び第2層間絶縁膜15の上に、例えばスパッタリング法又はCVD法により、非晶質な第2保護絶縁膜25を形成する。第2保護絶縁膜25は、水素や水分等によりキャパシタ誘電体膜18が還元されるのを防止するためのものである。非晶質の第2保護絶縁膜25として、例えば酸化アルミニウム膜を形成する。また、第2保護絶縁膜25の材料は、酸化チタン、酸化タンタル、酸化ジルコニウム、窒化タンタル、窒化アルミニウム及び酸窒化アルミニウムのうちから選択する膜でもよい。第2保護絶縁膜25の膜厚は、スパッタリング法で形成する場合は、10nm以上、30nm以下が望ましく、例えば20nm程度とする。また、第2保護絶縁膜25の膜厚は、CVD法で形成する場合は、1nm以上、3nm以下が望ましく、例えば2nm程度とする。

【0093】

酸化アルミニウム膜の成膜条件は、例えば次の通りとする。例えば、アルゴンガス雰囲気中でRFマグネトロンスパッタを行い、成膜時間を40秒として、緻密性が高い非晶質の酸化アルミニウム膜を20nmの厚さに形成する。この場合、スパッタパワー2を.0kWに、温度を室温に、圧力を1.0Paに設定する。

【0094】

次に、酸素を含有する雰囲気にシリコン基板1を置いて熱処理を行う。この熱処理は、キャパシタ誘電体膜18に酸素を供給し、スパッタリングにより損傷しているキャパシタQのダメージを回復させてキャパシタQの電気的特性を向上するためのものである。熱処理条件として、例えば、温度を500〜700℃、時間を30分〜120分とする。この結果、キャパシタ誘電体膜18に酸素が供給され、誘電体キャパシタQの電気的特性が回復する。

【0095】

次に、第2保護絶縁膜25上に第3層間絶縁膜26を形成する。第3層間絶縁膜26として、例えば、TEOSガスを使用するプラズマCVD法によりシリコン酸化膜を形成する。第3層間絶縁膜26の膜厚は、例えば1.4μm程度とする。続いて、例えば、CMP法により第3層間絶縁膜68の上面を平坦化する。

【0096】

続いて、N2Oガス又はN2ガスを用いて発生させたプラズマ雰囲気にシリコン基板1を置いて、熱処理を行う。この熱処理は、第3層間絶縁膜26中の水分を除去するとともに、第3層間絶縁膜26の膜質を変化させ、第3層間絶縁膜26中に水分を入りにくくさせるためのものである。熱処理は、例えば、温度を約350℃、時間を約2分間とする。

【0097】

次に、第3層間絶縁膜26上に、例えばスパッタリング法又はCVD法により第3保護絶縁膜27を形成する。第3保護絶縁膜27としては、例えば酸化アルミニウム膜を形成する。第3保護絶縁膜27の膜厚は、例えば20〜50nm程度である。

【0098】

続いて、第3保護絶縁膜27上に、例えばプラズマTEOSCVD法により、第4層間絶縁膜28を形成する。第4層間絶縁膜28として、例えばシリコン酸化膜をCVD法により例えば300nm程度の厚さに形成する。

【0099】

次に、図1Iに例示する構造を形成するまでの工程について説明する。

フォトリソグラフィ技術を用い、キャパシタ下部電極17のうちキャパシタ誘電体膜18からはみ出したコンタクト領域の上とキャパシタ上部電極19の上の第4層間絶縁膜28から第1保護絶縁膜23までの連続した層を部分的にエッチングする。これにより、キャパシタ上部電極19に達する第3のコンタクトホール26aと、キャパシタ下部電極17のコンタクト領域に達する第4のコンタクトホール26bとを形成する。

【0100】

続いて、酸素雰囲気中にシリコン基板1を置いて熱処理を行う。この熱処理は、キャパシタ誘電体膜18に酸素を供給し、キャパシタQの電気的特性を向上させるためのものである。熱処理条件は、例えば400〜600℃、例えば450℃程度とする。その熱処理時間は、例えば30分〜120分とする。

【0101】

次に、フォトリソグラフィ技術を用い、第1、第2の導電プラグ14a、14bの上の第4層間絶縁膜28から第2層間絶縁膜15までの連続した絶縁膜をエッチングする。これにより、第1、第2の導電性プラグ14a、14bに達するビアホール26c、26dを形成する。

【0102】

続いて、不活性ガス雰囲気中又は真空中にシリコン基板1を置いて熱処理を行う。この熱処理は、第4、第3及び第2層間絶縁膜28、26、15中からガスを放出する、即ち脱ガスのためである。

【0103】

次に、高周波エッチングにより、第3、第4のコンタクトホール26a、26b、及び第1、第2のビアホール26c、26dの内壁面に対して表面処理を行う。続いて、第4層間絶縁膜28の上面の上と第3、第4のコンタクトホール26a、26b及び第1、第2のビアホール26c、26dの内壁面の上に、例えばスパッタリング法により、密着膜29aを形成する。密着膜29aとして、例えばTiN膜を形成する。密着膜29aは、例えば50〜150nm程度の厚さに形成される。密着膜29aとしてTiN膜を形成する場合には、ターゲットの材料としてTiを用い、成膜室内の雰囲気は、ArガスとN2ガスとの混合雰囲気とする。Arガスの流量は50sccm、N2ガスの流量は例えば90sccmとする。また、成膜温度は、例えば150℃とする。

【0104】

続いて、密着膜29aの上に、例えばCVD法により、主導電膜29bを形成する。主

導電膜29bとしては、例えばタングステン膜を形成する。主導電膜29bの膜厚は、例えば300nm程度とする。

【0105】

さらに、第4層間絶縁膜28の上面が露出するまで、例えばCMP法により、主導電膜29b及び密着膜29aを研磨する。こうして、第3、第4のコンタクトホール26a、26b及び第1、第2のビアホール26c、26d内にそれぞれ残された主導電膜29b及び密着膜29aを第3、第4、第5及び第6の導電プラグ30a、30b、30c、30dとして使用する。

【0106】

次に、プラズマ洗浄を行う。プラズマ洗浄を行う際に用いるガスは、例えばArガスとする。これにより、第3〜第6の導電プラグ30a〜30dの表面に存在する自然酸化膜等が除去される。

【0107】

続いて、導電膜として、例えば、TiN膜31a、AlCu合金膜31b、Ti膜31c、TiN膜31dを順次積層することにより、積層導電膜を形成する。TiN膜31aの膜厚は、例えば50nmとする。AlCu合金膜31bの膜厚は、例えば膜厚550nmとする。Ti膜13cの膜厚は、例えば5nmとする。TiN膜31dの膜厚は、例えば膜厚50nmとする。

【0108】

次に、フォトリソグラフィ技術を用い、積層導電膜をエッチングする。こうして、積層膜により第3〜第6の導電プラグ31a〜31dに接続される配線32が形成される。この後、更に、層間絶縁膜、導電プラグ、配線等を複数層に亘って形成する。配線層(金属配線層)は、5層に亘って形成される(不図示)。

以上により、半導体装置内のメモリセルの基本的な構造が形成される。

【0109】

上記の半導体装置によれば、キャパシタQの下地としてアモルファスで正方体結晶を持つ密着絶縁膜16を形成している。密着絶縁膜16は、例えば、Pb又はBi添加した正方体の結晶を持つ絶縁膜、例えばPbAl2O4、PbAl2O5、PbZrO3、PbTiO3、PbSiO3、Pb(Zr,Ti)O3、BiAlO3、BiGaO3、SrBi2Ta2O9、Bi4Ti2O12、(BiLa)4Ti3O12のいずれかを用いて形成されている。

【0110】

従って、密着絶縁膜16の上に形成されるキャパシタQに外部から放射線が照射されても、放射線は密着絶縁膜16により部分吸収されて、キャパシタ誘電体膜18に至る輻射が軽減される。さらに、放射線は、密着絶縁膜16とキャパシタ誘電体膜18を構成する上記材料の誘電体膜結晶(正方体)の各頂点のPbに吸収され、結晶中心のZr/Tiへの放射線の影響が更に小さくなる。

【0111】

これにより、上記構造のMOSトランジスタT1、T2とキャパシタQを有するメモリ素子は、外部放射線に照射されてもソフトエラーが起きにくくなるので、医療、衛生品のTAGとして、一緒に放射線(ガンマ線、電子線)滅菌しても、データが保持できる。

【0112】

また、キャパシタ下部電極17の下の密着絶縁膜16は、上記のようなアモルファス強誘電体材料、例えばPZTから形成されているので、表面の平坦性が非常に良い。このため、密着絶縁膜16の上に成膜した形成されるキャパシタ下部電極17、例えばPt膜は、自己配向非常に良い膜となり、単一な(111)面を得やすい。従って、その後に、キャパシタ下部電極17の熱処理を行うと、密着絶縁膜16のPZTも結晶化され、PZT/Ptの結晶配向ともに(111)面となるので、その上に形成したキャパシタ誘電体膜18、例えばPZT膜の結晶性も向上できる。

【0113】

ところで、上記の方法で形成した半導体メモリ素子について、密着絶縁膜16として形成される上記材料のうちPZTを一例として選択し、PZT膜のガンマ線に対する耐性を調べるために次のような試験を行った。

【0114】

まず、キャパシタ誘電体膜18としてPZT膜を形成するとともに、その下の密着膜をアルミナから形成し、それ以外の構造を図1Iと同様に形成した複数の試料を用意した。そして、キャパシタ誘電体膜18のPZT膜の厚さを140nmとした構造のキャパシタを有する半導体装置を第1の試料とする。また、キャパシタ誘電体膜18のPZT膜の厚さを105nmとした構造のキャパシタを有する半導体装置を第2の試料とする。第1、第2の試料は、それぞれパッケージにより封入されている。そして、第1、第2の試料にガンマ線を照射したところ、第1、第2の試料のそれぞれのSSマージン及びOSマージンとガンマ線照射量の関係は、図2A、図2Bに例示するようになった。ガンマ線の照射量は、0kGy、20kGy、50kGy、100kGyである。

【0115】

図2Aにおいて、PSSは、ガンマ線の照射前の書込みデータの読み出し量であり、USSは、ガンマ線照射前と同じ書き込み状態のデータの読み出し量である。PSS−USSは、SSマージンであり、ガンマ線照射前後の読み出し量の違いを示している。図2Aでは、ガンマ線照射が無い場合、即ち0kGyの場合のSSマージンを1としてSSマージンが規格化して示されている。

【0116】

また、図2Bにおいて、POSは、ガンマ線の照射前の書込みデータの読み出し量であり、UOSは、ガンマ線照射前と異なる書き込み状態のデータの読み出し量である。そして、POS−UOSは、OSマージンであり、ガンマ線照射前後の読み出し量の違いを示している。図2Bでは、ガンマ線照射が無い場合、即ち0kGyの場合のOSマージンを1として規格化してOSマージンが示されている。

【0117】

図2Aによれば、各サンプルのSSマージンは、誘電体膜PZTの膜厚及びガンマ線照射量に依存せず、劣化が発生しない。これに対し、図2Bによれば、140nmPZT及び105nmPZTのメモリ素子の双方のOSマージンは、ガンマ線照射量に依存し、ガンマ線照射量が増えると低くなる。さらに、厚さ140nmのPZT膜のOSマージンの低減量は、厚さ105nmのPZT膜のOSマージンの低減量よりも小さくなる。

【0118】

図2Cは、図2Bにおけるガンマ線の照射量が50kGyの場合に、厚さが140nmと105nmのPZT膜のOSマージン量を示す。140nmの厚さのPZT膜のOSマージンは、照射前の量の59%程度になり、また、105nmの厚さのPZT膜のOSマージンは照射前の量の46%程度になる。

【0119】

従って、PZTの膜が薄くなると、放射線照射の影響を受けやすい結果となる。ただし、PZTは、薄くしても、ある程度放射線照射を遮断できる。また、キャパシタの容量を考慮すると、誘電体膜は薄い方が好ましい。従って、キャパシタ誘電体膜18を厚くする代わりに、上記のように、キャパシタ下部電極17の下地となる密着絶縁膜16として結晶化されたPZT膜等を使用すると、メモリセル領域の耐放射線能力を向上させることができる。

【0120】

(第2の実施の形態)

図3は、第2実施形態に係る半導体装置の断面図である。

図3に示す半導体装置では、第1実施形態と同様に、シリコン基板1にMOSトランジスタT1、T2が形成され、その上には第1、第2層間絶縁膜12、15が形成されている。さらに、第1層間絶縁膜12内には第1、第2の導電プラグ14a、14bが形成される。また、第2層間絶縁膜15上には、密着絶縁膜16が形成され、その上にはキャパ

シタQが形成されている。また、キャパシタQのキャパシタ上部電極19、キャパシタ誘電体膜18は第1保護絶縁膜22に覆われている。さらに、第1保護絶縁膜22とキャパシタ下部電極17は、第2保護絶縁膜25により覆われている。

【0121】

第2保護絶縁膜25の上には、第1実施形態では形成されていないステップカバレッジが良好なアルミニウム酸鉛膜(PbAl2O4)が第3保護絶縁膜35として形成されている。本実施形態では、バッチ式の成膜装置を用いた原子層堆積(ALD:Atomic Layer

Deposition)法により、アルミニウム酸鉛膜を厚さ20nm程度で形成する。

【0122】

このALD法を用いたアルミニウム酸鉛膜の形成にあたっては、TMA(Tri-Methyl Aluminum)、Pb(DPM)2及びH2Oを用いたALD法により行うことも可能であるが、アルミニウム酸鉛膜をより緻密化した膜にするという観点から、本実施形態においては、TMA、Pb(DPM)2及びオゾン(O3)を用いたALD法により行うことにする。

【0123】

具体的に、本実施形態では、Al原料として常温で液体のTMA、Pbの液体原料におけるPb(DPM)2を用いて堆積工程と、酸素(O2)及びオゾン(O3)の雰囲気中での酸化工程とを、工程間に真空パージ工程を入れて交互に切り替え、これを210サイクル程度繰り返してアルミニウム酸鉛膜の形成を行う。

【0124】

より詳細には、成膜室内において、オゾンを供給して被堆積膜表面、即ち第2保護絶縁膜25表面を酸化した後、余分なオゾンを真空排気してパージする。次いで、TMA及びPb(DPM)2を流して被堆積膜表面の酸素群と反応させて原子層のアルミニウム酸鉛膜を形成した後、余分なTMA、Pb(DPM)2を真空排気してパージする。この一連のサイクルを繰り返すことにより、アルミニウム酸鉛膜が形成される。

【0125】

TMAを用いた堆積工程では、例えば、基板温度を300℃、ガス圧力を40Pa(0.3Torr)、TMAガス流量を100sccm、Pb(DPM)2流量を50Sccm、5秒間の条件で行う。また、オゾンを用いた酸化工程は、例えば、基板温度を300℃、ガス圧力を133Pa(1.0Torr)、O2+O3ガス流量を10slm、O3濃度を200g/Nm3、15秒間の条件で行う。また、TMAは温度40℃に加温して、Pb(DPM)2は蒸気圧が比較的高いので、温度200℃に加温して蒸気圧によりガス化した状態で当該バッチ式の成膜装置へ導入する。

【0126】

第3保護絶縁膜35としてアルミニウム酸鉛膜の形成が終了した後、酸素及びオゾンの雰囲気中において、同一装置内(in−situ)で昇温して緻密化アニールを行う。この際、昇温は10℃/分程度で行い、また、温度を安定させるため、昇温後30分間は保持する。この緻密化アニールは、例えば、基板温度を500℃、ガス圧力を133Pa(1.0Torr)、O2+O3ガス流量を10slm、O3濃度を200g/Nm3、30分間の条件で行う。

【0127】

なお、本実施形態では、第3保護絶縁膜35であるアルミニウム酸鉛膜の形成後の緻密化アニールの温度を500℃程度としているが、本実施形態の効果を得るためのアニール温度は、400℃以上700℃以下の範囲とすることができる。これは、アニール温度が400℃未満になるとアルミニウム酸鉛膜の緻密化が不十分になるという不具合が生じ、また、アニール温度が700℃を超えるとキャパシタ誘電体膜18を構成するPZTからPbが脱離して疲労特性が悪化するという不具合が生じるためである。

【0128】

また、本実施形態では、第3保護絶縁膜35であるアルミニウム酸鉛膜の形成後の緻密化アニールの時間を30分程度としているが、本実施形態の効果を得るためのアニール時

間は、10分以上120分以下の範囲とすることができる。これは、アニール時間が10分未満になると当該緻密化アニールを行うバッチ式装置内でウェハ位置による依存が現れるという不具合が生じ、また、アニール温度が120分を超えると、アルミニウム酸鉛膜の緻密化は十分であるがスループットが低下するという不具合が生じるためである。

【0129】

この強酸化性を有するオゾン(O3)を含む雰囲気中でのアニール処理により、アルミニウム酸鉛膜は、緻密化された膜となる。これにより、例えば層間絶縁膜の成膜等の後工程において水素が生じた際においても、キャパシタ誘電体膜18への水素の侵入を阻止することができ、キャパシタ誘電体膜18の劣化を防止することができる。さらに、第3保護絶縁膜35であるアルミニウム酸鉛膜の成膜を、TMA及びH2Oを用いたALD法により行った場合には、アルミニウム酸鉛膜中に存在するOH基を一括して除去することができ、所謂蒸し焼き状態によるキャパシタ誘電体膜18の劣化を回避することができる。

【0130】

ここでは、第3保護絶縁膜35としてALD法でアルミニウム酸鉛膜35を形成することについて説明している。第3保護絶縁膜35の他の材料としては、Pb又はBiを添加した絶縁膜であってPbAl2O5、PbZrO3、PbTiO3、PbSiO3、Pb(Zr,Ti)O3、BiAlO3、BiGaO3、SrBi2Ta2O9、Bi4Ti2O12、(BiLa)4Ti3O12のいずれか一つ材料を使用してもよい。また、第3保護絶縁膜35の成膜方法としては、ALD法以外に、カバレッジの良い有機金属分解法、化学気相蒸着法、MOCVD法、スパッタ法を使用してもよい。

【0131】

次に、酸素を含有する雰囲気にシリコン基板1を置いて熱処理を行う。この熱処理は、第3保護絶縁膜35であるアルミニウム酸鉛膜の成膜過程中に残留する有機物を蒸発させる。これらの残留有機物が、アルミニウム酸鉛膜中残ると、その以後のプロセスに第1、第2保護絶縁膜22、25に拡散し、キャパシタ誘電体膜18へ浸入する可能性がある。熱処理条件は、例えば500〜600℃とする。熱処理時間は、例えば30分〜90分とする。この結果、第1及び第2保護絶縁膜22、25及び、アルミニウム酸鉛膜は、緻密性が非常に良い膜となり、キャパシタ誘電体膜18を完全に保護する。

【0132】

一方、上記の第1、第2保護絶縁膜22、25の厚さが厚すぎると、その後の工程でコンタクトホール26a、26bを完全に開けられないので、第1、第2保護絶縁膜22、25の厚さは100nm以下に望ましい。また、第2保護絶縁膜25を省いてもよい。コンタクトホール26a、26bをよりきれいに開くためには、それらの厚さは50nm以下が望ましい。また、これらの厚さが薄すぎると、キャパシタQへの保護機能がなくなるので、キャパシタQの側面での第1、第2保護絶縁膜の厚さは10nm以上が望ましい。また、第3保護絶縁膜35となる薄いアルミニウム酸鉛膜は、アルゴンガスで容易にスパッタエッチングすることが可能であるので、本実施形態では、所望の形状のコンタクトホール26a、26bを容易に形成することができる。

【0133】

次に、第1実施形態と同じ条件で、第3保護絶縁膜35上に第3層間絶縁膜26を形成する。その以後の構造及びプロセスも第1実行形態と同じ方法で形成して半導体装置のメモリセル領域の基本構造を形成する。

【0134】

以上のように、キャパシタQを有する本実施形態に係る半導体装置が形成されている。こうした半導体メモリは、外部から放射線に照射されると、キャパシタQを挟む密着絶縁膜16及び第3保護絶縁膜35により部分吸収されて、キャパシタ誘電体膜18に至る輻射が軽減される。さらに、正方体の誘電体膜結晶の各頂点にPbに吸収され、結晶中心のZr/Tiへの影響を更に小さくなる。従って、第1実施形態と同様に、上記構造のメモリ素子は、外部放射線に照射されても、ソフトエラーが起きにくくなるので、医療、衛生品のTAGとして、一緒に放射線(ガンマ線、電子線)滅菌しても、データが保持できる

。

【0135】

ところで、第3保護絶縁膜35の上に形成される第3層間絶縁膜26として、第3保護絶縁膜35を熱処理した後に、例えばTEOS(Si(OC2H5)4)と次のソースを用いてプラズマCVD法により形成してもよい。そのソースとして、Pb(C11H19O2)2、Pb(DPM)2、Pb(TMHPD)、Bi(DPM)3、Bi(Ot−Bu)3、Bi(p−Tol)3のいずれか一つを使用する。これにより形成された第3層間膜26は、PbやBiを添加したシリコン化合物の絶縁膜であるPbSiO3あるいはBi2Si2O9である。PbやBiが添加されたシリコン化合物の第3層間絶縁膜26の膜厚は、例えば約1.2μm程度とする。第3層間絶縁膜26の形成方法として、上記のプラズマCVD法以外、ゾル−ゲル法、有機金属分解法、CSD法、化学気相蒸着法、MOCVD法などを使用してもよい。第3層間絶縁膜26の形成後には上記と同様にその表面は、例えばCMP法により平坦化される。そのようなPb、Biのいずれかを添加したシリコン酸化膜は、第1実施形態、又は、以下の実施形態において、キャパシタQ、Q0の上方の層間絶縁膜に適用してもよい。

【0136】

そのような材料により形成された第3層間絶縁膜26は、外部から照射される放射線を吸収するので、キャパシタ誘電体膜18に達する放射線の輻射が軽減する。さらに、放射線は、PbやBiが添加された誘電体膜の結晶(正方体)の各頂点のPbに吸収されるので、結晶中心のZr/Tiへの影響を更に小さくなる。従って、上記構造のメモリ素子は、外部放射線に照射されても、ソフトエラーが更に起きにくくなるので、医療、衛生品のTAGとして、一緒に放射線(ガンマ線、電子線)滅菌しても、データが保持できる。

【0137】

(第3の実施の形態)

図4は、第3実施形態に係る半導体装置の断面図である。