半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置及びその製造方法に関する。

【背景技術】

【0002】

多くの半導体装置には、nチャネル型MIS(Metal Insulator Semiconductor)トランジスタ(n型トランジスタ)とpチャネル型MISトランジスタ(p型トランジスタ)の相補的な動作特性を利用したCMIS(Complementary MIS)型の回路が搭載されている。このCMIS型の回路では、n型トランジスタのゲート電極とp型トランジスタのゲート電極とが共通のゲート配線で接続される場合がある(例えば、特許文献1〜3参照)。

【0003】

また、半導体装置で用いられるトランジスタは、用途毎に要求される特性が異なり、特性に応じてゲートスタック(ゲート絶縁膜、ゲート電極)構造を変えることがある。ゲートスタック構造による特性調整は、同じ極性のトランジスタで異なる特性を実現する場合だけでなく、n型トランジスタとp型トランジスタとで特性の対称性を向上させる場合にも用いられる。

【0004】

ところで、近年の半導体装置では、トランジスタの微細化に伴ってゲート絶縁膜からのリーク電流が増大し、該ゲート・リーク電流の増大が半導体装置の低消費電力化を阻害する要因となっている。そのようなリーク電流を抑制する手法として、ゲート絶縁膜に高誘電率(High−k)の絶縁体を用い、ゲート電極に金属材料(メタルゲート)を用いるHKMG(High-k Metal Gate)スタック構造が知られている。

【0005】

通常、MISトランジスタではチャネル領域の不純物濃度によってトランジスタの閾値電圧を調整する。一方、上記HKMGスタック構造を採用したトランジスタ(以下、HKMGトランジスタと称す)では、チャネル領域の不純物濃度だけでなく、ゲート絶縁膜の材料や厚さ、並びにゲート電極の材料や厚さも閾値電圧を調整するパラメータとして用いられる。すなわち、HKMGトランジスタでは、要求される特性に応じて異なる材料や厚さのHKMGスタック構造が採用される。例えば特許文献4や5には、金属膜とシリコン(ポリシリコン)膜とを積層してゲート電極を形成すると共に、特性が異なるトランジスタ毎に個別の工程でゲート電極及びゲート絶縁膜をそれぞれ形成する手法が記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平5−121734号公報

【特許文献2】特開平8−125029号公報

【特許文献3】特開2006−245390号公報

【特許文献4】特開2008−219006号公報

【特許文献5】特開2011−003664号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上述したHKMGトランジスタのように、ゲートスタック構造が異なり、また各ゲート電極がゲート配線で接続される構成では、個別の工程で形成されることで分離して配置された電極(トランジスタのゲート電極)どうしを断線することなく接続することが重要になる。

【課題を解決するための手段】

【0008】

本発明の半導体装置は、半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、

前記半導体基板の主面に第2の絶縁膜を介して形成された第2の電極と、

前記半導体基板の主面上の、前記第1の電極と前記第2の電極との間に埋設された補償膜と、

前記第1の電極の上面及び前記第2の電極の上面と接触する、前記第1の電極の上面から前記補償膜の上面を経由して前記第2の電極の上面まで形成された配線と、

を有することを特徴とする。

【0009】

一方、本発明の半導体装置の製造方法は、半導体基板の主面に第1の絶縁膜を介して第1の電極を形成し、

前記半導体基板の主面に第2の絶縁膜を介して第2の電極を形成し、

前記半導体基板の主面上の、前記第1の電極と前記第2の電極との間に補償膜を埋設し、

前記第1の電極の上面及び前記第2の電極の上面と接触する、前記第1の電極の上面から前記補償膜の上面を経由して前記第2の電極の上面まで到達する配線を形成することを特徴とする。

【0010】

上記のような半導体装置及びその製造方法では、第1の電極及び第2の電極の上面と、第1の電極と第2の電極との隙間で露出していた半導体基板の主面との段差が補償膜によって低減される。そのため、分離して配置された第1の電極と第2の電極とを接続する配線のカバレッジが改善される。

【発明の効果】

【0011】

本発明によれば、個別の工程で形成されることで分離して配置された各電極どうしを断線することなく接続できる。

【図面の簡単な説明】

【0012】

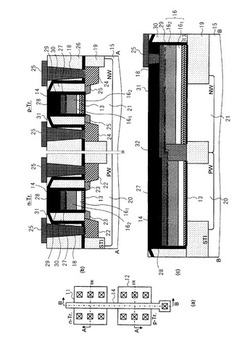

【図1】図1は、ゲート電極どうしを接続するゲート配線の構造を検討した一例を示す図であり、同図(a)は平面図、同図(b)は断面図である。

【図2】図2は、ゲート電極どうしを接続するゲート配線の構造を検討した他の例を示す図であり、同図(a)は平面図、同図(b)は断面図である。

【図3】図3は、各ゲート電極に直接接触することで接続するゲート配線の問題点を示す図であり、同図(a)は平面図、同図(b)は断面図である。

【図4】図4は、第1の実施の形態の半導体装置の一構成例を示す図であり、同図(a)は平面図、同図(b)はA−A線から見た断面図、同図(c)はB−B線から見た断面図である。

【図5】図5は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図6】図6は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図7】図7は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図8】図8は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図9】図9は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図10】図10は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図11】図11は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図12】図12は、第2の実施の形態の半導体装置の一構成例を示す図であり、同図(a)はメモリセルアレイの平面図、同図(b)は周辺回路の平面図である。

【図13】図13は、第2の実施の形態の半導体装置の一構成例を示す図であり、同図(a)はメモリセルアレイの断面図、同図(b)は周辺回路の断面図である。

【図14】図14は、第2の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図15】図15は、第2の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図16】図16は、第2の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図17】図17は、第2の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図18】図18は、第2の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【発明を実施するための形態】

【0013】

トランジスタは、例えば絶縁体が埋め込まれた溝であるSTI(Shallow Trench Isolation)によって、ソース、ドレイン及びチャネル領域となる各素子形成領域を分離し、それぞれのチャネル領域上にゲート絶縁膜及びゲート電極を成膜することで形成される。ここで、各トランジスタのゲート電極どうしをゲート配線で接続する場合、図1(a)、(b)で示すようにゲート絶縁膜及びSTI(以下、分離層と称す)を含む半導体基板5上に第1のトランジスタ1及び第2のトランジスタ2のゲート電極として用いられるゲート配線4を設ける構成が一般的である。但し、図1(a)、(b)は第1のトランジスタ1と第2のトランジスタ2のゲート絶縁膜3及びゲート電極の材料や厚さが同一である場合の構成例を示している。

【0014】

本出願人は、上記HKMGトランジスタのように、ゲートスタック構造が異なり、個別の工程で形成されることで分離して配置された各トランジスタのゲート電極どうしをゲート配線で接続する方法について検討した。

【0015】

そのような方法としては、例えば、図2(a)、(b)に示すように、半導体基板5上に第1のトランジスタ1及び第2のトランジスタ2の各ゲート電極6を覆う絶縁層7を設け、該絶縁層7上にゲート配線4を形成すると共に、絶縁層7に設けた開口に導電体(コンタクト8)を埋設し、該コンタクト8を介して各ゲート電極6と絶縁層7上のゲート配線4とを接続する方法が考えられる。

【0016】

しかしながら、図2に示す構造では、上記コンタクト8の加工寸法によって第1のトランジスタ1と第2のトランジスタ2の配置距離が制限される問題がある。すなわち、隣接する2つのトランジスタを、少なくとも2つのコンタクト8を直列に形成できる距離だけ離して配置する必要があるため、トランジスタの集積密度が低下してしまう。

【0017】

そこで、本出願人は、第1のトランジスタ1及び第2のトランジスタ2のゲート電極上面にそれぞれ直接接触するゲート配線4を設ける構造を検討した。そのような構造であれば、個別の工程で形成されることで分離して配置された各トランジスタのゲート電極6どうしを絶縁層7やコンタクト8を介さずに電気的に接続できる。

【0018】

しかしながら、図3(a)、(b)で示すように、分離して配置されたゲート電極6の上面どうしを接続する場合、該ゲート電極6の上面と、該ゲート電極6間の半導体基板5の主面との段差によってゲート配線4が断線するおそれがある。特にゲート絶縁膜3及びゲート電極6が厚くなり(段差が大きくなり)、ゲートスタックどうしの間隔が狭くなると、導体膜であるゲート配線4が段差部位の側壁や半導体基板5の主面上に均一に成膜されずに断線する可能性が高くなる(配線カバレッジが低下する)。

【0019】

本発明では、このようなゲート配線4の断線を防止するための構成及びその製造方法について提案する。

(第1の実施の形態)

図4は、第1の実施の形態の半導体装置の一構成例を示す図であり、同図(a)は平面図、同図(b)はA−A線から見た断面図、同図(c)はB−B線から見た断面図である。

【0020】

図4(a)〜(c)に示すように、第1の実施の形態の半導体装置は、n型トランジスタ(n−Tr.)11及びp型トランジスタ(p−Tr.)12を備え、該n型トランジスタ11及びp型トランジスタ12のゲート電極16どうしがゲート配線14で接続された構成である。なお、本発明は、n型トランジスタ11とp型トランジスタ12の組み合わせに適用するだけでなく、n型トランジスタ11とn型トランジスタ11の組み合わせに適用してもよく、p型トランジスタ12とp型トランジスタ12の組み合わせに適用してもよい。また、ゲート配線14で接続するトランジスタ数は、2つに限定されるものではなく、3つ以上であってもよい。

【0021】

半導体基板15は、分離層(STI)19によってn型トランジスタ11の素子形成領域となるPウエル領域(PW)20とp型トランジスタ12の素子形成領域となるNウエル領域(NW)21とに分離されている。n型トランジスタ11の素子形成領域には、例えばソース・ドレインとなる高濃度n型不純物拡散層22が形成され、該高濃度n型不純物拡散層22の内側に低濃度p型不純物拡散層23が形成されている。一方、p型トランジスタ12の素子形成領域には、例えばソース・ドレインとなる高濃度p型不純物拡散層24が形成され、該高濃度p型不純物拡散層24の内側に低濃度n型不純物拡散層25が形成されている。高濃度n型不純物拡散層22または高濃度p型不純物拡散層24から成るソース・ドレインと外部配線25とは、半導体基板上の層間絶縁膜26内に設けられたコンタクト18を介して接続される。

【0022】

n型トランジスタ11及びp型トランジスタ12のソース・ドレイン間には、高誘電率(High−k)絶縁膜から成るゲート絶縁膜13が形成され、その上に金属膜161とSi膜162とが積層された積層膜から成るゲート電極16が形成され、さらにその上に金属シリサイド膜27を介してゲート配線14が形成されている。High−k絶縁膜とは、従来からトランジスタのゲート絶縁膜に用いられてきた二酸化シリコン(SiO2)よりも誘電率が高い絶縁体(例えばHfO2、Al2O3等)を指す。

【0023】

ゲート配線14上には、絶縁体から成るキャップ層28が堆積されている。また、キャップ層28を含むゲート電極16及びゲート配線14の側面は、絶縁体から成るオフセットスペーサ29及びサイドウォールスペーサ30で覆われ、さらにオフセットスペーサ29及びサイドウォールスペーサ30を含むゲートスタック全体が絶縁体から成るライナー膜31で覆われている。

【0024】

なお、n型トランジスタ11とp型トランジスタ12は、図4(a)〜(c)に示す構成に限定されるものではなく、ゲートスタック構造が異なっていれば、どのような構成でもよい。

【0025】

このような構成において、本実施形態の半導体装置は、図4(b)に示すように、半導体基板15の主面上の、分離して配置されたn型トランジスタ11とp型トランジスタ12との間にゲート補償膜32が埋設された構成を特徴とする。ゲート配線14は、n型トランジスタ11のゲート電極16上面からゲート補償膜32の上面を経由してp型トランジスタ12のゲート電極16上面まで形成される。

【0026】

ゲート補償膜32は、例えば、隣接するn型トランジスタ11またはp型トランジスタ12の少なくともいずれか一方のゲート電極16と上面どうしが一致する厚さで形成すればよい。このような構成では、個別の工程で形成されることで分離して配置されたn型トランジスタ11及びp型トランジスタ12のゲート電極16の上面と、該ゲート電極16間の露出していた半導体基板15の主面との段差がゲート補償膜32によって低減される。そのため、各トランジスタの各ゲート電極16どうしを接続するゲート配線14の配線カバレッジが改善され、ゲート配線14の断線が抑制される。

【0027】

ゲート補償膜32は、ゲート電極16上面と半導体基板15の主面との段差を低減できる構成であればよく、その材料を限定するものではない。ゲート補償膜32には、金属や導電性半導体などの導体を用いてもよく、絶縁体を用いてもよい。本実施例ではゲート補償膜32としてシリコンを含む膜(例えば、不純物がドープされた多結晶シリコン膜)を形成する例を示す。特に、本実施形態で示す構成では、補間の対象となる複数の積層膜間は、後に配線(ゲート配線14)により電気的に接続される。ゲート補償膜32として導体を適用することは、これら両積層膜間の電気的な接続が補強されるので、より好ましい。さらに、多結晶シリコン膜のようにシリコンを含む膜は加工性に優れているため、より好ましい。

【0028】

なお、図4(a)〜(c)に示す例では、ゲート補償膜32の上面が、高さが異なるトランジスタのゲート電極16の上面とそれぞれ一致するように形成されている。図4(b)及び(c)に示すように、p型トランジスタのゲート絶縁膜13は、n型トランジスタのゲート絶縁膜13よりも厚く形成されているため、ゲート補償膜32の上面にはゲート絶縁膜13の膜厚差に相当する段差が発生する。しかしながら、該膜厚差による段差は、ゲート絶縁膜13及びゲート電極16の厚さに相当する段差に比べて十分に低く、また図3に示したように段差部位がゲート電極16で挟まれる構成ではないため、ゲート配線14の配線カバレッジの低下はわずかで済む。

【0029】

また、上述したように、図4(a)〜(c)に示す例では、ゲート補償膜32の上面が、高さが異なるトランジスタのゲート電極16の上面にそれぞれ一致するように形成されているが、ゲート補償膜31の上面は、隣接するn型トランジスタ11またはp型トランジスタ12のゲート電極16の上面と必ずしも一致させる必要はない。ゲート配線14は、配線カバレッジが低下しない範囲内で該ゲート電極16の上面よりも低く形成してもよく、高く形成してもよい。

【0030】

HKMGトランジスタを含む半導体装置では、トランジスタの微細化に伴ってゲート配線14が薄くなる、またはゲート電極16が高くなる(ゲートスタックが厚くなる)と、ゲート電極16どうしの間隔が狭くなるにしたがってゲートスタック間に形成する導体膜(ゲート配線14)の配線カバレッジがさらに低下することが懸念される。本実施形態はそのようなトランジスタを含む半導体装置に適用して効果的である。

【0031】

次に本実施形態の半導体装置の製造方法について図5〜図11を用いて説明する。

【0032】

図5〜図11は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。なお、図5〜図11の各図(a)は、図4(a)に示した平面図のA−A線から見た断面図を示し、図5〜図11の各図(b)は、図4(a)に示した平面図のB−B線から見た断面図を示している。

【0033】

図5(a)、(b)に示すように、まず半導体基板15上のn型トランジスタ11及びp型トランジスタ12の素子形成領域に、例えばALD(Atomic Layer Deposition)法を用いて高誘電率材料(例えばHfO2)から成るゲート絶縁膜13を成膜する。各トランジスタの素子形成領域は、周知の方法により、上記STIを形成し、該STIで分離された領域毎に不純物半導体を導入することで形成すればよい。なお、図5(a)、(b)は、p型トランジスタ12のゲート絶縁膜13として、ALD法等を用いて、HfO2膜上にさらに高誘電率材料(例えばAl2O3)の膜を積層した構成例を示している。n型トランジスタ11とp型トランジスタ12とでゲート絶縁膜13の厚さを変える方法はどのような方法を用いてもよい。また、図5(a)、(b)では、n型トランジスタ11とp型トランジスタ12とでゲート絶縁膜13の材料や膜厚が異なる例を示しているが、ゲート電極16の材料や膜厚を異なる構成にしてもよい。

【0034】

続いて、各ゲート絶縁膜13上に、例えばPVD(Physical Vapor Deposition)法を用いてTiN等から成る金属膜(メタルゲート)161を成膜し、その上に、例えばCVD(Chemical Vapor Deposition)法を用いてアモルファスシリコン等から成るSi膜(a−Siゲート)162を積層することでゲート電極16を形成する。図5(a)、(b)は、Si膜162上に、例えばSiO2から成る保護層33が成膜された例を示している。

【0035】

次に、図6(a)、(b)に示すように、ゲート電極16を含む半導体基板15全面を覆うように多結晶シリコン(poly-Si)層34を形成する。

【0036】

続いて、図7(a)、(b)に示すように、ゲート電極16上の多結晶シリコン層34を、例えばエッチバックすることで除去し、さらにウェットエッチング等により保護層33を除去する。このとき、ゲートスタック間の半導体基板15主面上に残る多結晶シリコン層が上記ゲート間補償膜32となる。

【0037】

次に、図8(a)、(b)に示すように、ゲート電極16及びゲート間補償膜32上に金属シリサイド膜(例えばWSi)27を形成し、その上にゲート配線(例えばW/WN:タングステン(W)、またはタングステン(W)と窒化タングステン(WN)の積層構造)14を形成し、さらにその上に、例えばP−CVD(Plasma CVD)法を用いてSiN等から成るキャップ層28を形成する。

【0038】

次に、図9(a)、(b)に示すように、例えばフォトリソグラフィ技術を用いて、ゲート絶縁膜13、ゲート電極16、金属シリサイド膜27、ゲート配線14及びキャップ層28を含むゲートスタックを所望の形状にパターニングする。

【0039】

次に、図10(a)、(b)に示すように、例えばイオン・インプランテーション法を用いて、ゲートスタック側面に形成したオフセットスペーサ(例えばSiN)29及びサイドウォールスペーサ(例えばSiO2)30をマスクに用いて所要の不純物イオンを半導体基板15中に拡散させ、n型トランジスタ11の素子形成領域に、ソース・ドレインとなる高濃度n型不純物拡散層22及び低濃度p型不純物拡散層23を形成し、p型トランジスタ12の素子形成領域に、ソース・ドレインとなる高濃度p型不純物拡散層24及び低濃度n型不純物拡散層25を形成する。

【0040】

続いて、オフセットスペーサ29及びサイドウォールスペーサ30を覆うように、例えばSiNから成るライナー膜31を形成した後、半導体基板上の全面に、例えばSOD(Spin On Dielectric)膜から成る層間絶縁膜26を形成し、エッチバックまたはCMP(Chemical Mechanical Polishing)法等を用いて層間絶縁膜26の上面を平坦化する。

【0041】

最後に、図11(a)、(b)に示すように、n型トランジスタ11及びp型トランジスタ12のソース・ドレイン上の層間絶縁膜26に開口を形成し、該開口内を含む層間絶縁膜26上の全面に導体膜(例えばW)を形成し、該導体膜を所要の形状にパターニングすることでソース・ドレインとコンタクト18を介して接続された外部配線25を形成する。

(第2の実施の形態)

図12は、第2の実施の形態の半導体装置の一構成例を示す図であり、同図(a)はメモリセルアレイの平面図、同図(b)は周辺回路の平面図である。図13は、第2の実施の形態の半導体装置の一構成例を示す図であり、同図(a)はメモリセルアレイの断面図、同図(b)は周辺回路の断面図である。

【0042】

図12(a)は、DRAM(Dynamic Random Access Memory)が備える、情報を保持するメモリセルアレイの一例を示し、図12(b)は、該DRAMが備える周辺回路の一例を示している。周辺回路は、第1の実施の形態と同様にn型トランジスタ11及びp型トランジスタ12を備え、該n型トランジスタ11及びp型トランジスタ12のゲート電極16どうしがゲート配線14で接続された構成である。図13(a)は、図12(a)に示したメモリセルアレイをX−X線から見た断面図であり、図13(b)は、図12(b)に示した周辺回路をY−Y線から見た断面図である。

【0043】

第2の実施の形態の半導体装置は、本発明をDRAM(Dynamic Random Access Memory)に適用した例であり、メモリセルアレイ用のビット線と周辺回路用の各トランジスタのゲート配線とを同時に形成する例である。すなわち、メモリセルアレイ用のビット線と周辺回路用の各トランジスタのゲート配線とが同じ構成となる。

【0044】

一般に、DRAMのリフレッシュ特性を改善するには、情報を保持するためのキャパシタの容量を大きくし、ビット線の容量を小さくすることが望ましい。ビット線の容量を低減するには、低抵抗材料を用いると共に膜厚を薄くすることが効果的である。しかしながら、ビット線と同時に周辺回路用のトランジスタのゲート配線を形成すると、ビット線の薄膜化に伴って周辺回路用のトランジスタのゲート配線も薄く形成される。そのため、ゲートスタック間の段差部でゲート配線が断線する懸念がより大きくなる。そこで、本実施形態では、周辺回路用のトランジスタのゲート配線に、第1の実施の形態と同様の構成を採用する。

【0045】

図13(a)に示すように、メモリセルアレイ(Cell Array)領域は複数のメモリセルを備えている。メモリセルは、電荷を蓄積することで情報を保持するキャパシタ101と、該キャパシタ101に電荷を蓄積する、または該キャパシタ101から電荷を放出させるセルトランジスタ102とを有する構成である。

【0046】

各セルトランジスタ102のゲート電極(ワード線)は、例えば半導体基板15に形成した溝(トレンチ)に導電体が埋め込まれた、周知の埋め込みワード線(buried Word Line: bWL)構造で形成される。トレンチの内壁には、セルトランジスタ102のゲート絶縁膜103となる酸化膜等が成膜され、その内側にゲート電極(ワード線)105となる導電体が埋設されている。ワード線105を含む上記トレンチ上部は、絶縁体(例えばSiN)から成るビットコンタクト層間絶縁膜104で覆われている。

【0047】

メモリセルアレイ領域では、上記ビットコンタクト層間絶縁膜104に設けられた開口内に導体膜から成るビット線108が形成され、ビット線108上には絶縁体から成るハードマスク層109が形成されている。また、上記ビットコンタクト層間絶縁膜104上面、並びにビット線108及びハードマスク層109の側面は絶縁膜(例えばSiN)107で覆われ、該絶縁膜107上にはライナー膜(例えばSiN)106及び層間絶縁膜(例えばSOD膜)110が堆積されている。さらに、層間絶縁膜110上には、シリコン層112が堆積され、該シリコン層112にキャパシタ101となる構造体(キャパシタ構造体)が形成されている。キャパシタ101は、上部電極113、容量絶縁膜114及び下部電極115を備えている。キャパシタ101の下部電極115とセルトランジスタ102とは、層間絶縁膜110に設けられた容量コンタクト111及び層間絶縁膜110上に形成された容量コンタクトパッド116を介して接続される。容量コンタクト111の側壁には、絶縁膜から成るサイドウォール膜117が形成されていてもよい。

【0048】

なお、本実施形態では、メモリセルが、セルトランジスタ102上にキャパシタ101が積載された周知のスタック構造で形成され、ワード線105が上記bWL構造で形成された例を示しているが、各メモリセルは、各ビット線108と周辺回路用のトランジスタのゲート配線14とが同時に形成される構成であればよく、図13(a)に示した構成に限定されるものではない。

【0049】

図13(b)に示す周辺回路(Periphery)用のトランジスタの構成は、図4(a)〜(c)に示した第1の実施の形態と同様であるため、その説明は省略する。

【0050】

図13(b)に示すように、周辺回路領域では、半導体基板15の主面上の、分離して配置されたn型トランジスタ11とp型トランジスタ12との間にゲート補償膜32が埋設され、n型トランジスタ11及びp型トランジスタ12のゲート電極16上面、並びにゲート補償膜32上面にゲート配線14が形成される。

【0051】

このような構成でも、第1の実施の形態と同様に、個別の工程で形成されることで分離して配置されたn型トランジスタ11及びp型トランジスタ12のゲート電極16の上面と、該ゲート電極16間の露出していた半導体基板15の主面との段差がゲート補償膜32によって低減される。そのため、各トランジスタの各ゲート電極16どうしを接続するゲート配線14の配線カバレッジが改善され、ゲート配線14の断線が抑制される。特に、メモリセルアレイのビット線と同時に形成されることで周辺回路用のトランジスタのゲート配線14が薄くなっても、ゲートスタック間の段差部で断線することが抑制される。

【0052】

次に本実施形態の半導体装置の製造方法について図14〜図18を用いて説明する。

【0053】

図14〜図18は、第2の実施の形態の半導体装置の製造手順の一例を示す断面図である。なお、図14〜図18の各図(a)は、図12(a)に示したメモリセルアレイのX−X線から見た断面図を示し、図14〜図18の各図(b)は、図12(b)に示した周辺回路のY−Y線から見た断面図を示している。但し、図14〜図18では、各々の工程における各層の関係を示しているため、図12に示す平面図は、図14〜図18に示す全ての断面図に対応しているわけではない。

【0054】

図14(a)に示すように、半導体基板15上のメモリセルアレイ領域には、上記bWL構造の複数のワード線105が形成され、該ワード線105及びトレンチ上部を含むメモリセルアレイ領域上に、例えば窒化シリコン膜からなるビットコンタクト層間絶縁膜104が成膜される。bWL構造は、周知の製造方法を用いて形成すればよい。

【0055】

図14(b)に示すように、周辺回路領域のn型トランジスタ11及びp型トランジスタ12の素子形成領域には、例えばALD法を用いて高誘電率材料(例えばHfO2)等から成るゲート絶縁膜13を成膜され、各ゲート絶縁膜13上に、例えばPVD法を用いてTiN等から成る金属膜161が成膜され、その上に、例えばCVD法を用いてアモルファスシリコン等から成るSi膜162が積層されたゲート電極16が形成されている。なお、図14(b)は、p型トランジスタ12のゲート絶縁膜13として、ALD法等を用いて、HfO2膜上にさらに高誘電率材料(例えばAl2O3)の膜を積層した構成例を示している。n型トランジスタ11とp型トランジスタ12とでゲート絶縁膜13の厚さを変える方法はどのような方法を用いてもよい。また、図14(a)、(b)では、n型トランジスタ11とp型トランジスタ12とでゲート絶縁膜13の材料や膜厚が異なる例を示しているが、ゲート電極16の材料や膜厚を異なる構成にしてもよい。図14(b)は、Si膜162上に、さらに保護層33が成膜された例を示している。

【0056】

次に、図15(a)、(b)に示すように、メモリセルアレイ領域、並びに周辺回路領域の各トランジスタのゲート電極16を覆うように、例えば多結晶シリコン(poly-Si)膜34を成膜する。

【0057】

次に、図16(a)、(b)に示すように、メモリセルアレイ領域、並びに周辺回路領域のゲート電極16上の多結晶シリコン層34を、例えばエッチバックすることで除去し、さらにウェットエッチング等により保護層33を除去する。このとき、周辺回路領域のゲートスタック間の半導体基板15主面上に残る多結晶シリコン層が上記ゲート間補償膜32となる。

【0058】

次に、図17(a)に示すように、例えばフォトリソグラフィ技術を用いて、メモリセルアレイ領域の所要部位のビットコンタクト層間絶縁膜104を除去することで、セルトランジスタ102のソース(またはドレイン)となる半導体層(半導体基板15の主面)を露出させる。また、図17(b)に示すように、周辺回路領域では、各トランジスタのゲート電極16を覆うように、例えば金属シリサイド膜(例えばWSi)114を形成した後、メモリセルアレイ領域及び周辺回路領域全面に、メモリセルアレイのビット線108及び周辺回路領域のゲート配線14となる導体膜(例えばW/WN:タングステン(W)、またはタングステン(W)と窒化タングステン(WN)の積層構造)115を形成し、さらにその上に、例えばP−CVD法を用いてメモリセルアレイのハードマスク層109及び周辺回路領域のキャップ層28となる絶縁層(例えばSiN)116を形成する。なお、メモリセルアレイ領域のビットコンタクト層間絶縁膜104を除去した領域には、周辺回路領域と同様に、金属シリサイド膜114を形成した後、その上に導体膜115及び絶縁層116を成膜してもよい。

【0059】

次に、図18(a)に示すように、例えばフォトリソグラフィ技術を用いてメモリセルアレイ領域上の導体膜115及び絶縁層116を所要の形状にパターニングすることで、ビット線108及びハードマスク層109を形成する。

【0060】

図18(b)では示していないが、このとき、周辺回路領域では、例えばフォトリソグラフィ技術を用いて、金属シリサイド膜114、導体膜115及び絶縁層116を所望の形状にパターニングすると共に、それらの下層のゲート絶縁膜13及びゲート電極16をパターニングすることでゲートスタックを形成する(図9(a)参照)。

【0061】

その後、メモリセルアレイ領域では、上記ビットコンタクト層間絶縁膜104上、並びにビット線108及びハードマスク層109の側面を、例えば窒化シリコン等から成る絶縁膜107で覆い、該絶縁膜107上にライナー膜106及び層間絶縁膜110を堆積する。さらに、層間絶縁膜110上に、シリコン層112を堆積し、該シリコン層112にキャパシタ101を形成する(図13(a)参照)。キャパシタ101は、周知の方法を用いて形成すればよく、ここでは詳細な説明を省略する。

【0062】

一方、周辺回路領域では、半導体基板15中に所要の不純物イオンを拡散させてn型トランジスタ11p型トランジスタ12のソース・ドレインを形成し、キャップ層28及びソース・ドレインを覆うように層間絶縁膜26を堆積した後、該層間絶縁膜26上に外部配線25を形成する。最後に、層間絶縁膜26にソース・ドレインと外部配線25とを接続するためのコンタクト18を形成する(図10及び11参照)。

【符号の説明】

【0063】

1 第1のトランジスタ

2 第2のトランジスタ

3、13、103 ゲート絶縁膜

4、14 ゲート配線

5、15 半導体基板

6、16、105 ゲート電極

7 絶縁層

8、18 コンタクト

11 n型トランジスタ

12 p型トランジスタ

161 金属膜

162 Si膜

19 分離層

20 Pウエル領域

21 Nウエル領域

22 高濃度n型不純物拡散層

23 低濃度p型不純物拡散層

24 高濃度p型不純物拡散層

25 低濃度n型不純物拡散層

26、110 層間絶縁膜

27、114 金属シリサイド膜

28 キャップ層

29 オフセットスペーサ

30 サイドウォールスペーサ

31、106 ライナー膜

32 ゲート補償膜

33 保護層

34 多結晶シリコン層

101 キャパシタ

102 セルトランジスタ

104 ビットコンタクト層間絶縁膜

107 絶縁膜

108 ビット線

109 ハードマスク層

111 容量コンタクト

112 シリコン層

113 上部電極

114 容量絶縁膜

115 下部電極

116 容量コンタクトパッド

117 サイドウォール膜

【技術分野】

【0001】

本発明は半導体装置及びその製造方法に関する。

【背景技術】

【0002】

多くの半導体装置には、nチャネル型MIS(Metal Insulator Semiconductor)トランジスタ(n型トランジスタ)とpチャネル型MISトランジスタ(p型トランジスタ)の相補的な動作特性を利用したCMIS(Complementary MIS)型の回路が搭載されている。このCMIS型の回路では、n型トランジスタのゲート電極とp型トランジスタのゲート電極とが共通のゲート配線で接続される場合がある(例えば、特許文献1〜3参照)。

【0003】

また、半導体装置で用いられるトランジスタは、用途毎に要求される特性が異なり、特性に応じてゲートスタック(ゲート絶縁膜、ゲート電極)構造を変えることがある。ゲートスタック構造による特性調整は、同じ極性のトランジスタで異なる特性を実現する場合だけでなく、n型トランジスタとp型トランジスタとで特性の対称性を向上させる場合にも用いられる。

【0004】

ところで、近年の半導体装置では、トランジスタの微細化に伴ってゲート絶縁膜からのリーク電流が増大し、該ゲート・リーク電流の増大が半導体装置の低消費電力化を阻害する要因となっている。そのようなリーク電流を抑制する手法として、ゲート絶縁膜に高誘電率(High−k)の絶縁体を用い、ゲート電極に金属材料(メタルゲート)を用いるHKMG(High-k Metal Gate)スタック構造が知られている。

【0005】

通常、MISトランジスタではチャネル領域の不純物濃度によってトランジスタの閾値電圧を調整する。一方、上記HKMGスタック構造を採用したトランジスタ(以下、HKMGトランジスタと称す)では、チャネル領域の不純物濃度だけでなく、ゲート絶縁膜の材料や厚さ、並びにゲート電極の材料や厚さも閾値電圧を調整するパラメータとして用いられる。すなわち、HKMGトランジスタでは、要求される特性に応じて異なる材料や厚さのHKMGスタック構造が採用される。例えば特許文献4や5には、金属膜とシリコン(ポリシリコン)膜とを積層してゲート電極を形成すると共に、特性が異なるトランジスタ毎に個別の工程でゲート電極及びゲート絶縁膜をそれぞれ形成する手法が記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平5−121734号公報

【特許文献2】特開平8−125029号公報

【特許文献3】特開2006−245390号公報

【特許文献4】特開2008−219006号公報

【特許文献5】特開2011−003664号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上述したHKMGトランジスタのように、ゲートスタック構造が異なり、また各ゲート電極がゲート配線で接続される構成では、個別の工程で形成されることで分離して配置された電極(トランジスタのゲート電極)どうしを断線することなく接続することが重要になる。

【課題を解決するための手段】

【0008】

本発明の半導体装置は、半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、

前記半導体基板の主面に第2の絶縁膜を介して形成された第2の電極と、

前記半導体基板の主面上の、前記第1の電極と前記第2の電極との間に埋設された補償膜と、

前記第1の電極の上面及び前記第2の電極の上面と接触する、前記第1の電極の上面から前記補償膜の上面を経由して前記第2の電極の上面まで形成された配線と、

を有することを特徴とする。

【0009】

一方、本発明の半導体装置の製造方法は、半導体基板の主面に第1の絶縁膜を介して第1の電極を形成し、

前記半導体基板の主面に第2の絶縁膜を介して第2の電極を形成し、

前記半導体基板の主面上の、前記第1の電極と前記第2の電極との間に補償膜を埋設し、

前記第1の電極の上面及び前記第2の電極の上面と接触する、前記第1の電極の上面から前記補償膜の上面を経由して前記第2の電極の上面まで到達する配線を形成することを特徴とする。

【0010】

上記のような半導体装置及びその製造方法では、第1の電極及び第2の電極の上面と、第1の電極と第2の電極との隙間で露出していた半導体基板の主面との段差が補償膜によって低減される。そのため、分離して配置された第1の電極と第2の電極とを接続する配線のカバレッジが改善される。

【発明の効果】

【0011】

本発明によれば、個別の工程で形成されることで分離して配置された各電極どうしを断線することなく接続できる。

【図面の簡単な説明】

【0012】

【図1】図1は、ゲート電極どうしを接続するゲート配線の構造を検討した一例を示す図であり、同図(a)は平面図、同図(b)は断面図である。

【図2】図2は、ゲート電極どうしを接続するゲート配線の構造を検討した他の例を示す図であり、同図(a)は平面図、同図(b)は断面図である。

【図3】図3は、各ゲート電極に直接接触することで接続するゲート配線の問題点を示す図であり、同図(a)は平面図、同図(b)は断面図である。

【図4】図4は、第1の実施の形態の半導体装置の一構成例を示す図であり、同図(a)は平面図、同図(b)はA−A線から見た断面図、同図(c)はB−B線から見た断面図である。

【図5】図5は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図6】図6は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図7】図7は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図8】図8は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図9】図9は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図10】図10は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図11】図11は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図12】図12は、第2の実施の形態の半導体装置の一構成例を示す図であり、同図(a)はメモリセルアレイの平面図、同図(b)は周辺回路の平面図である。

【図13】図13は、第2の実施の形態の半導体装置の一構成例を示す図であり、同図(a)はメモリセルアレイの断面図、同図(b)は周辺回路の断面図である。

【図14】図14は、第2の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図15】図15は、第2の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図16】図16は、第2の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図17】図17は、第2の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【図18】図18は、第2の実施の形態の半導体装置の製造手順の一例を示す断面図である。

【発明を実施するための形態】

【0013】

トランジスタは、例えば絶縁体が埋め込まれた溝であるSTI(Shallow Trench Isolation)によって、ソース、ドレイン及びチャネル領域となる各素子形成領域を分離し、それぞれのチャネル領域上にゲート絶縁膜及びゲート電極を成膜することで形成される。ここで、各トランジスタのゲート電極どうしをゲート配線で接続する場合、図1(a)、(b)で示すようにゲート絶縁膜及びSTI(以下、分離層と称す)を含む半導体基板5上に第1のトランジスタ1及び第2のトランジスタ2のゲート電極として用いられるゲート配線4を設ける構成が一般的である。但し、図1(a)、(b)は第1のトランジスタ1と第2のトランジスタ2のゲート絶縁膜3及びゲート電極の材料や厚さが同一である場合の構成例を示している。

【0014】

本出願人は、上記HKMGトランジスタのように、ゲートスタック構造が異なり、個別の工程で形成されることで分離して配置された各トランジスタのゲート電極どうしをゲート配線で接続する方法について検討した。

【0015】

そのような方法としては、例えば、図2(a)、(b)に示すように、半導体基板5上に第1のトランジスタ1及び第2のトランジスタ2の各ゲート電極6を覆う絶縁層7を設け、該絶縁層7上にゲート配線4を形成すると共に、絶縁層7に設けた開口に導電体(コンタクト8)を埋設し、該コンタクト8を介して各ゲート電極6と絶縁層7上のゲート配線4とを接続する方法が考えられる。

【0016】

しかしながら、図2に示す構造では、上記コンタクト8の加工寸法によって第1のトランジスタ1と第2のトランジスタ2の配置距離が制限される問題がある。すなわち、隣接する2つのトランジスタを、少なくとも2つのコンタクト8を直列に形成できる距離だけ離して配置する必要があるため、トランジスタの集積密度が低下してしまう。

【0017】

そこで、本出願人は、第1のトランジスタ1及び第2のトランジスタ2のゲート電極上面にそれぞれ直接接触するゲート配線4を設ける構造を検討した。そのような構造であれば、個別の工程で形成されることで分離して配置された各トランジスタのゲート電極6どうしを絶縁層7やコンタクト8を介さずに電気的に接続できる。

【0018】

しかしながら、図3(a)、(b)で示すように、分離して配置されたゲート電極6の上面どうしを接続する場合、該ゲート電極6の上面と、該ゲート電極6間の半導体基板5の主面との段差によってゲート配線4が断線するおそれがある。特にゲート絶縁膜3及びゲート電極6が厚くなり(段差が大きくなり)、ゲートスタックどうしの間隔が狭くなると、導体膜であるゲート配線4が段差部位の側壁や半導体基板5の主面上に均一に成膜されずに断線する可能性が高くなる(配線カバレッジが低下する)。

【0019】

本発明では、このようなゲート配線4の断線を防止するための構成及びその製造方法について提案する。

(第1の実施の形態)

図4は、第1の実施の形態の半導体装置の一構成例を示す図であり、同図(a)は平面図、同図(b)はA−A線から見た断面図、同図(c)はB−B線から見た断面図である。

【0020】

図4(a)〜(c)に示すように、第1の実施の形態の半導体装置は、n型トランジスタ(n−Tr.)11及びp型トランジスタ(p−Tr.)12を備え、該n型トランジスタ11及びp型トランジスタ12のゲート電極16どうしがゲート配線14で接続された構成である。なお、本発明は、n型トランジスタ11とp型トランジスタ12の組み合わせに適用するだけでなく、n型トランジスタ11とn型トランジスタ11の組み合わせに適用してもよく、p型トランジスタ12とp型トランジスタ12の組み合わせに適用してもよい。また、ゲート配線14で接続するトランジスタ数は、2つに限定されるものではなく、3つ以上であってもよい。

【0021】

半導体基板15は、分離層(STI)19によってn型トランジスタ11の素子形成領域となるPウエル領域(PW)20とp型トランジスタ12の素子形成領域となるNウエル領域(NW)21とに分離されている。n型トランジスタ11の素子形成領域には、例えばソース・ドレインとなる高濃度n型不純物拡散層22が形成され、該高濃度n型不純物拡散層22の内側に低濃度p型不純物拡散層23が形成されている。一方、p型トランジスタ12の素子形成領域には、例えばソース・ドレインとなる高濃度p型不純物拡散層24が形成され、該高濃度p型不純物拡散層24の内側に低濃度n型不純物拡散層25が形成されている。高濃度n型不純物拡散層22または高濃度p型不純物拡散層24から成るソース・ドレインと外部配線25とは、半導体基板上の層間絶縁膜26内に設けられたコンタクト18を介して接続される。

【0022】

n型トランジスタ11及びp型トランジスタ12のソース・ドレイン間には、高誘電率(High−k)絶縁膜から成るゲート絶縁膜13が形成され、その上に金属膜161とSi膜162とが積層された積層膜から成るゲート電極16が形成され、さらにその上に金属シリサイド膜27を介してゲート配線14が形成されている。High−k絶縁膜とは、従来からトランジスタのゲート絶縁膜に用いられてきた二酸化シリコン(SiO2)よりも誘電率が高い絶縁体(例えばHfO2、Al2O3等)を指す。

【0023】

ゲート配線14上には、絶縁体から成るキャップ層28が堆積されている。また、キャップ層28を含むゲート電極16及びゲート配線14の側面は、絶縁体から成るオフセットスペーサ29及びサイドウォールスペーサ30で覆われ、さらにオフセットスペーサ29及びサイドウォールスペーサ30を含むゲートスタック全体が絶縁体から成るライナー膜31で覆われている。

【0024】

なお、n型トランジスタ11とp型トランジスタ12は、図4(a)〜(c)に示す構成に限定されるものではなく、ゲートスタック構造が異なっていれば、どのような構成でもよい。

【0025】

このような構成において、本実施形態の半導体装置は、図4(b)に示すように、半導体基板15の主面上の、分離して配置されたn型トランジスタ11とp型トランジスタ12との間にゲート補償膜32が埋設された構成を特徴とする。ゲート配線14は、n型トランジスタ11のゲート電極16上面からゲート補償膜32の上面を経由してp型トランジスタ12のゲート電極16上面まで形成される。

【0026】

ゲート補償膜32は、例えば、隣接するn型トランジスタ11またはp型トランジスタ12の少なくともいずれか一方のゲート電極16と上面どうしが一致する厚さで形成すればよい。このような構成では、個別の工程で形成されることで分離して配置されたn型トランジスタ11及びp型トランジスタ12のゲート電極16の上面と、該ゲート電極16間の露出していた半導体基板15の主面との段差がゲート補償膜32によって低減される。そのため、各トランジスタの各ゲート電極16どうしを接続するゲート配線14の配線カバレッジが改善され、ゲート配線14の断線が抑制される。

【0027】

ゲート補償膜32は、ゲート電極16上面と半導体基板15の主面との段差を低減できる構成であればよく、その材料を限定するものではない。ゲート補償膜32には、金属や導電性半導体などの導体を用いてもよく、絶縁体を用いてもよい。本実施例ではゲート補償膜32としてシリコンを含む膜(例えば、不純物がドープされた多結晶シリコン膜)を形成する例を示す。特に、本実施形態で示す構成では、補間の対象となる複数の積層膜間は、後に配線(ゲート配線14)により電気的に接続される。ゲート補償膜32として導体を適用することは、これら両積層膜間の電気的な接続が補強されるので、より好ましい。さらに、多結晶シリコン膜のようにシリコンを含む膜は加工性に優れているため、より好ましい。

【0028】

なお、図4(a)〜(c)に示す例では、ゲート補償膜32の上面が、高さが異なるトランジスタのゲート電極16の上面とそれぞれ一致するように形成されている。図4(b)及び(c)に示すように、p型トランジスタのゲート絶縁膜13は、n型トランジスタのゲート絶縁膜13よりも厚く形成されているため、ゲート補償膜32の上面にはゲート絶縁膜13の膜厚差に相当する段差が発生する。しかしながら、該膜厚差による段差は、ゲート絶縁膜13及びゲート電極16の厚さに相当する段差に比べて十分に低く、また図3に示したように段差部位がゲート電極16で挟まれる構成ではないため、ゲート配線14の配線カバレッジの低下はわずかで済む。

【0029】

また、上述したように、図4(a)〜(c)に示す例では、ゲート補償膜32の上面が、高さが異なるトランジスタのゲート電極16の上面にそれぞれ一致するように形成されているが、ゲート補償膜31の上面は、隣接するn型トランジスタ11またはp型トランジスタ12のゲート電極16の上面と必ずしも一致させる必要はない。ゲート配線14は、配線カバレッジが低下しない範囲内で該ゲート電極16の上面よりも低く形成してもよく、高く形成してもよい。

【0030】

HKMGトランジスタを含む半導体装置では、トランジスタの微細化に伴ってゲート配線14が薄くなる、またはゲート電極16が高くなる(ゲートスタックが厚くなる)と、ゲート電極16どうしの間隔が狭くなるにしたがってゲートスタック間に形成する導体膜(ゲート配線14)の配線カバレッジがさらに低下することが懸念される。本実施形態はそのようなトランジスタを含む半導体装置に適用して効果的である。

【0031】

次に本実施形態の半導体装置の製造方法について図5〜図11を用いて説明する。

【0032】

図5〜図11は、第1の実施の形態の半導体装置の製造手順の一例を示す断面図である。なお、図5〜図11の各図(a)は、図4(a)に示した平面図のA−A線から見た断面図を示し、図5〜図11の各図(b)は、図4(a)に示した平面図のB−B線から見た断面図を示している。

【0033】

図5(a)、(b)に示すように、まず半導体基板15上のn型トランジスタ11及びp型トランジスタ12の素子形成領域に、例えばALD(Atomic Layer Deposition)法を用いて高誘電率材料(例えばHfO2)から成るゲート絶縁膜13を成膜する。各トランジスタの素子形成領域は、周知の方法により、上記STIを形成し、該STIで分離された領域毎に不純物半導体を導入することで形成すればよい。なお、図5(a)、(b)は、p型トランジスタ12のゲート絶縁膜13として、ALD法等を用いて、HfO2膜上にさらに高誘電率材料(例えばAl2O3)の膜を積層した構成例を示している。n型トランジスタ11とp型トランジスタ12とでゲート絶縁膜13の厚さを変える方法はどのような方法を用いてもよい。また、図5(a)、(b)では、n型トランジスタ11とp型トランジスタ12とでゲート絶縁膜13の材料や膜厚が異なる例を示しているが、ゲート電極16の材料や膜厚を異なる構成にしてもよい。

【0034】

続いて、各ゲート絶縁膜13上に、例えばPVD(Physical Vapor Deposition)法を用いてTiN等から成る金属膜(メタルゲート)161を成膜し、その上に、例えばCVD(Chemical Vapor Deposition)法を用いてアモルファスシリコン等から成るSi膜(a−Siゲート)162を積層することでゲート電極16を形成する。図5(a)、(b)は、Si膜162上に、例えばSiO2から成る保護層33が成膜された例を示している。

【0035】

次に、図6(a)、(b)に示すように、ゲート電極16を含む半導体基板15全面を覆うように多結晶シリコン(poly-Si)層34を形成する。

【0036】

続いて、図7(a)、(b)に示すように、ゲート電極16上の多結晶シリコン層34を、例えばエッチバックすることで除去し、さらにウェットエッチング等により保護層33を除去する。このとき、ゲートスタック間の半導体基板15主面上に残る多結晶シリコン層が上記ゲート間補償膜32となる。

【0037】

次に、図8(a)、(b)に示すように、ゲート電極16及びゲート間補償膜32上に金属シリサイド膜(例えばWSi)27を形成し、その上にゲート配線(例えばW/WN:タングステン(W)、またはタングステン(W)と窒化タングステン(WN)の積層構造)14を形成し、さらにその上に、例えばP−CVD(Plasma CVD)法を用いてSiN等から成るキャップ層28を形成する。

【0038】

次に、図9(a)、(b)に示すように、例えばフォトリソグラフィ技術を用いて、ゲート絶縁膜13、ゲート電極16、金属シリサイド膜27、ゲート配線14及びキャップ層28を含むゲートスタックを所望の形状にパターニングする。

【0039】

次に、図10(a)、(b)に示すように、例えばイオン・インプランテーション法を用いて、ゲートスタック側面に形成したオフセットスペーサ(例えばSiN)29及びサイドウォールスペーサ(例えばSiO2)30をマスクに用いて所要の不純物イオンを半導体基板15中に拡散させ、n型トランジスタ11の素子形成領域に、ソース・ドレインとなる高濃度n型不純物拡散層22及び低濃度p型不純物拡散層23を形成し、p型トランジスタ12の素子形成領域に、ソース・ドレインとなる高濃度p型不純物拡散層24及び低濃度n型不純物拡散層25を形成する。

【0040】

続いて、オフセットスペーサ29及びサイドウォールスペーサ30を覆うように、例えばSiNから成るライナー膜31を形成した後、半導体基板上の全面に、例えばSOD(Spin On Dielectric)膜から成る層間絶縁膜26を形成し、エッチバックまたはCMP(Chemical Mechanical Polishing)法等を用いて層間絶縁膜26の上面を平坦化する。

【0041】

最後に、図11(a)、(b)に示すように、n型トランジスタ11及びp型トランジスタ12のソース・ドレイン上の層間絶縁膜26に開口を形成し、該開口内を含む層間絶縁膜26上の全面に導体膜(例えばW)を形成し、該導体膜を所要の形状にパターニングすることでソース・ドレインとコンタクト18を介して接続された外部配線25を形成する。

(第2の実施の形態)

図12は、第2の実施の形態の半導体装置の一構成例を示す図であり、同図(a)はメモリセルアレイの平面図、同図(b)は周辺回路の平面図である。図13は、第2の実施の形態の半導体装置の一構成例を示す図であり、同図(a)はメモリセルアレイの断面図、同図(b)は周辺回路の断面図である。

【0042】

図12(a)は、DRAM(Dynamic Random Access Memory)が備える、情報を保持するメモリセルアレイの一例を示し、図12(b)は、該DRAMが備える周辺回路の一例を示している。周辺回路は、第1の実施の形態と同様にn型トランジスタ11及びp型トランジスタ12を備え、該n型トランジスタ11及びp型トランジスタ12のゲート電極16どうしがゲート配線14で接続された構成である。図13(a)は、図12(a)に示したメモリセルアレイをX−X線から見た断面図であり、図13(b)は、図12(b)に示した周辺回路をY−Y線から見た断面図である。

【0043】

第2の実施の形態の半導体装置は、本発明をDRAM(Dynamic Random Access Memory)に適用した例であり、メモリセルアレイ用のビット線と周辺回路用の各トランジスタのゲート配線とを同時に形成する例である。すなわち、メモリセルアレイ用のビット線と周辺回路用の各トランジスタのゲート配線とが同じ構成となる。

【0044】

一般に、DRAMのリフレッシュ特性を改善するには、情報を保持するためのキャパシタの容量を大きくし、ビット線の容量を小さくすることが望ましい。ビット線の容量を低減するには、低抵抗材料を用いると共に膜厚を薄くすることが効果的である。しかしながら、ビット線と同時に周辺回路用のトランジスタのゲート配線を形成すると、ビット線の薄膜化に伴って周辺回路用のトランジスタのゲート配線も薄く形成される。そのため、ゲートスタック間の段差部でゲート配線が断線する懸念がより大きくなる。そこで、本実施形態では、周辺回路用のトランジスタのゲート配線に、第1の実施の形態と同様の構成を採用する。

【0045】

図13(a)に示すように、メモリセルアレイ(Cell Array)領域は複数のメモリセルを備えている。メモリセルは、電荷を蓄積することで情報を保持するキャパシタ101と、該キャパシタ101に電荷を蓄積する、または該キャパシタ101から電荷を放出させるセルトランジスタ102とを有する構成である。

【0046】

各セルトランジスタ102のゲート電極(ワード線)は、例えば半導体基板15に形成した溝(トレンチ)に導電体が埋め込まれた、周知の埋め込みワード線(buried Word Line: bWL)構造で形成される。トレンチの内壁には、セルトランジスタ102のゲート絶縁膜103となる酸化膜等が成膜され、その内側にゲート電極(ワード線)105となる導電体が埋設されている。ワード線105を含む上記トレンチ上部は、絶縁体(例えばSiN)から成るビットコンタクト層間絶縁膜104で覆われている。

【0047】

メモリセルアレイ領域では、上記ビットコンタクト層間絶縁膜104に設けられた開口内に導体膜から成るビット線108が形成され、ビット線108上には絶縁体から成るハードマスク層109が形成されている。また、上記ビットコンタクト層間絶縁膜104上面、並びにビット線108及びハードマスク層109の側面は絶縁膜(例えばSiN)107で覆われ、該絶縁膜107上にはライナー膜(例えばSiN)106及び層間絶縁膜(例えばSOD膜)110が堆積されている。さらに、層間絶縁膜110上には、シリコン層112が堆積され、該シリコン層112にキャパシタ101となる構造体(キャパシタ構造体)が形成されている。キャパシタ101は、上部電極113、容量絶縁膜114及び下部電極115を備えている。キャパシタ101の下部電極115とセルトランジスタ102とは、層間絶縁膜110に設けられた容量コンタクト111及び層間絶縁膜110上に形成された容量コンタクトパッド116を介して接続される。容量コンタクト111の側壁には、絶縁膜から成るサイドウォール膜117が形成されていてもよい。

【0048】

なお、本実施形態では、メモリセルが、セルトランジスタ102上にキャパシタ101が積載された周知のスタック構造で形成され、ワード線105が上記bWL構造で形成された例を示しているが、各メモリセルは、各ビット線108と周辺回路用のトランジスタのゲート配線14とが同時に形成される構成であればよく、図13(a)に示した構成に限定されるものではない。

【0049】

図13(b)に示す周辺回路(Periphery)用のトランジスタの構成は、図4(a)〜(c)に示した第1の実施の形態と同様であるため、その説明は省略する。

【0050】

図13(b)に示すように、周辺回路領域では、半導体基板15の主面上の、分離して配置されたn型トランジスタ11とp型トランジスタ12との間にゲート補償膜32が埋設され、n型トランジスタ11及びp型トランジスタ12のゲート電極16上面、並びにゲート補償膜32上面にゲート配線14が形成される。

【0051】

このような構成でも、第1の実施の形態と同様に、個別の工程で形成されることで分離して配置されたn型トランジスタ11及びp型トランジスタ12のゲート電極16の上面と、該ゲート電極16間の露出していた半導体基板15の主面との段差がゲート補償膜32によって低減される。そのため、各トランジスタの各ゲート電極16どうしを接続するゲート配線14の配線カバレッジが改善され、ゲート配線14の断線が抑制される。特に、メモリセルアレイのビット線と同時に形成されることで周辺回路用のトランジスタのゲート配線14が薄くなっても、ゲートスタック間の段差部で断線することが抑制される。

【0052】

次に本実施形態の半導体装置の製造方法について図14〜図18を用いて説明する。

【0053】

図14〜図18は、第2の実施の形態の半導体装置の製造手順の一例を示す断面図である。なお、図14〜図18の各図(a)は、図12(a)に示したメモリセルアレイのX−X線から見た断面図を示し、図14〜図18の各図(b)は、図12(b)に示した周辺回路のY−Y線から見た断面図を示している。但し、図14〜図18では、各々の工程における各層の関係を示しているため、図12に示す平面図は、図14〜図18に示す全ての断面図に対応しているわけではない。

【0054】

図14(a)に示すように、半導体基板15上のメモリセルアレイ領域には、上記bWL構造の複数のワード線105が形成され、該ワード線105及びトレンチ上部を含むメモリセルアレイ領域上に、例えば窒化シリコン膜からなるビットコンタクト層間絶縁膜104が成膜される。bWL構造は、周知の製造方法を用いて形成すればよい。

【0055】

図14(b)に示すように、周辺回路領域のn型トランジスタ11及びp型トランジスタ12の素子形成領域には、例えばALD法を用いて高誘電率材料(例えばHfO2)等から成るゲート絶縁膜13を成膜され、各ゲート絶縁膜13上に、例えばPVD法を用いてTiN等から成る金属膜161が成膜され、その上に、例えばCVD法を用いてアモルファスシリコン等から成るSi膜162が積層されたゲート電極16が形成されている。なお、図14(b)は、p型トランジスタ12のゲート絶縁膜13として、ALD法等を用いて、HfO2膜上にさらに高誘電率材料(例えばAl2O3)の膜を積層した構成例を示している。n型トランジスタ11とp型トランジスタ12とでゲート絶縁膜13の厚さを変える方法はどのような方法を用いてもよい。また、図14(a)、(b)では、n型トランジスタ11とp型トランジスタ12とでゲート絶縁膜13の材料や膜厚が異なる例を示しているが、ゲート電極16の材料や膜厚を異なる構成にしてもよい。図14(b)は、Si膜162上に、さらに保護層33が成膜された例を示している。

【0056】

次に、図15(a)、(b)に示すように、メモリセルアレイ領域、並びに周辺回路領域の各トランジスタのゲート電極16を覆うように、例えば多結晶シリコン(poly-Si)膜34を成膜する。

【0057】

次に、図16(a)、(b)に示すように、メモリセルアレイ領域、並びに周辺回路領域のゲート電極16上の多結晶シリコン層34を、例えばエッチバックすることで除去し、さらにウェットエッチング等により保護層33を除去する。このとき、周辺回路領域のゲートスタック間の半導体基板15主面上に残る多結晶シリコン層が上記ゲート間補償膜32となる。

【0058】

次に、図17(a)に示すように、例えばフォトリソグラフィ技術を用いて、メモリセルアレイ領域の所要部位のビットコンタクト層間絶縁膜104を除去することで、セルトランジスタ102のソース(またはドレイン)となる半導体層(半導体基板15の主面)を露出させる。また、図17(b)に示すように、周辺回路領域では、各トランジスタのゲート電極16を覆うように、例えば金属シリサイド膜(例えばWSi)114を形成した後、メモリセルアレイ領域及び周辺回路領域全面に、メモリセルアレイのビット線108及び周辺回路領域のゲート配線14となる導体膜(例えばW/WN:タングステン(W)、またはタングステン(W)と窒化タングステン(WN)の積層構造)115を形成し、さらにその上に、例えばP−CVD法を用いてメモリセルアレイのハードマスク層109及び周辺回路領域のキャップ層28となる絶縁層(例えばSiN)116を形成する。なお、メモリセルアレイ領域のビットコンタクト層間絶縁膜104を除去した領域には、周辺回路領域と同様に、金属シリサイド膜114を形成した後、その上に導体膜115及び絶縁層116を成膜してもよい。

【0059】

次に、図18(a)に示すように、例えばフォトリソグラフィ技術を用いてメモリセルアレイ領域上の導体膜115及び絶縁層116を所要の形状にパターニングすることで、ビット線108及びハードマスク層109を形成する。

【0060】

図18(b)では示していないが、このとき、周辺回路領域では、例えばフォトリソグラフィ技術を用いて、金属シリサイド膜114、導体膜115及び絶縁層116を所望の形状にパターニングすると共に、それらの下層のゲート絶縁膜13及びゲート電極16をパターニングすることでゲートスタックを形成する(図9(a)参照)。

【0061】

その後、メモリセルアレイ領域では、上記ビットコンタクト層間絶縁膜104上、並びにビット線108及びハードマスク層109の側面を、例えば窒化シリコン等から成る絶縁膜107で覆い、該絶縁膜107上にライナー膜106及び層間絶縁膜110を堆積する。さらに、層間絶縁膜110上に、シリコン層112を堆積し、該シリコン層112にキャパシタ101を形成する(図13(a)参照)。キャパシタ101は、周知の方法を用いて形成すればよく、ここでは詳細な説明を省略する。

【0062】

一方、周辺回路領域では、半導体基板15中に所要の不純物イオンを拡散させてn型トランジスタ11p型トランジスタ12のソース・ドレインを形成し、キャップ層28及びソース・ドレインを覆うように層間絶縁膜26を堆積した後、該層間絶縁膜26上に外部配線25を形成する。最後に、層間絶縁膜26にソース・ドレインと外部配線25とを接続するためのコンタクト18を形成する(図10及び11参照)。

【符号の説明】

【0063】

1 第1のトランジスタ

2 第2のトランジスタ

3、13、103 ゲート絶縁膜

4、14 ゲート配線

5、15 半導体基板

6、16、105 ゲート電極

7 絶縁層

8、18 コンタクト

11 n型トランジスタ

12 p型トランジスタ

161 金属膜

162 Si膜

19 分離層

20 Pウエル領域

21 Nウエル領域

22 高濃度n型不純物拡散層

23 低濃度p型不純物拡散層

24 高濃度p型不純物拡散層

25 低濃度n型不純物拡散層

26、110 層間絶縁膜

27、114 金属シリサイド膜

28 キャップ層

29 オフセットスペーサ

30 サイドウォールスペーサ

31、106 ライナー膜

32 ゲート補償膜

33 保護層

34 多結晶シリコン層

101 キャパシタ

102 セルトランジスタ

104 ビットコンタクト層間絶縁膜

107 絶縁膜

108 ビット線

109 ハードマスク層

111 容量コンタクト

112 シリコン層

113 上部電極

114 容量絶縁膜

115 下部電極

116 容量コンタクトパッド

117 サイドウォール膜

【特許請求の範囲】

【請求項1】

半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、

前記半導体基板の主面に第2の絶縁膜を介して形成された第2の電極と、

前記半導体基板の主面上の、前記第1の電極と前記第2の電極との間に埋設された補償膜と、

前記第1の電極の上面及び前記第2の電極の上面と接触する、前記第1の電極の上面から前記補償膜の上面を経由して前記第2の電極の上面まで形成された配線と、

を有することを特徴とする半導体装置。

【請求項2】

前記第1の電極は第1のトランジスタのゲート電極であり、

前記第2の電極は第2のトランジスタのゲート電極であり、

前記第1のトランジスタと前記第2のトランジスタは導電型が互いに逆極性の電界効果トランジスタである請求項1記載の半導体装置。

【請求項3】

前記補償膜は、導体である請求項1または2記載の半導体装置。

【請求項4】

前記補償膜は、シリコンを含む膜である請求項1から3のいずれか1項記載の半導体装置。

【請求項5】

前記第1の絶縁膜と前記第2の絶縁膜とが異なる材料である請求項1から4のいずれか1項記載の半導体装置。

【請求項6】

前記第1の絶縁膜と前記第2の絶縁膜とが異なる膜厚である請求項1から5のいずれか1項記載の半導体装置。

【請求項7】

前記第1の電極と前記第2の電極とが異なる材料である請求項1から6のいずれか1項記載の半導体装置。

【請求項8】

前記第1の電極と前記第2の電極とが異なる膜厚である請求項1から7のいずれか1項記載の半導体装置。

【請求項9】

前記第1の絶縁膜及び前記第2の絶縁膜は、二酸化シリコンよりも誘電率が高い絶縁体から成るHigh−k絶縁膜である請求項1から8のいずれか1項記載の半導体装置。

【請求項10】

前記第1の電極及び前記第2の電極は、トランジスタのゲート電極であり、該ゲート電極に金属材料を用いたメタルゲートである請求項1から9のいずれか1項記載の半導体装置。

【請求項11】

前記第1の電極及び前記第2の電極は、金属材料から成る膜の上にシリコンを含む膜が積層された積層膜である請求項1から9のいずれか1項記載の半導体装置。

【請求項12】

情報を保持する複数のメモリセルからなるメモリセルアレイをさらに備え、

前記複数のメモリセルを接続するビット線は、前記配線と同じ構成である請求項1から11のいずれか1項記載の半導体装置。

【請求項13】

半導体基板の主面に第1の絶縁膜を介して第1の電極を形成し、

前記半導体基板の主面に第2の絶縁膜を介して第2の電極を形成し、

前記半導体基板の主面上の、前記第1の電極と前記第2の電極との間に補償膜を埋設し、

前記第1の電極の上面及び前記第2の電極の上面と接触する、前記第1の電極の上面から前記補償膜の上面を経由して前記第2の電極の上面まで到達する配線を形成することを特徴とする半導体装置の製造方法。

【請求項1】

半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、

前記半導体基板の主面に第2の絶縁膜を介して形成された第2の電極と、

前記半導体基板の主面上の、前記第1の電極と前記第2の電極との間に埋設された補償膜と、

前記第1の電極の上面及び前記第2の電極の上面と接触する、前記第1の電極の上面から前記補償膜の上面を経由して前記第2の電極の上面まで形成された配線と、

を有することを特徴とする半導体装置。

【請求項2】

前記第1の電極は第1のトランジスタのゲート電極であり、

前記第2の電極は第2のトランジスタのゲート電極であり、

前記第1のトランジスタと前記第2のトランジスタは導電型が互いに逆極性の電界効果トランジスタである請求項1記載の半導体装置。

【請求項3】

前記補償膜は、導体である請求項1または2記載の半導体装置。

【請求項4】

前記補償膜は、シリコンを含む膜である請求項1から3のいずれか1項記載の半導体装置。

【請求項5】

前記第1の絶縁膜と前記第2の絶縁膜とが異なる材料である請求項1から4のいずれか1項記載の半導体装置。

【請求項6】

前記第1の絶縁膜と前記第2の絶縁膜とが異なる膜厚である請求項1から5のいずれか1項記載の半導体装置。

【請求項7】

前記第1の電極と前記第2の電極とが異なる材料である請求項1から6のいずれか1項記載の半導体装置。

【請求項8】

前記第1の電極と前記第2の電極とが異なる膜厚である請求項1から7のいずれか1項記載の半導体装置。

【請求項9】

前記第1の絶縁膜及び前記第2の絶縁膜は、二酸化シリコンよりも誘電率が高い絶縁体から成るHigh−k絶縁膜である請求項1から8のいずれか1項記載の半導体装置。

【請求項10】

前記第1の電極及び前記第2の電極は、トランジスタのゲート電極であり、該ゲート電極に金属材料を用いたメタルゲートである請求項1から9のいずれか1項記載の半導体装置。

【請求項11】

前記第1の電極及び前記第2の電極は、金属材料から成る膜の上にシリコンを含む膜が積層された積層膜である請求項1から9のいずれか1項記載の半導体装置。

【請求項12】

情報を保持する複数のメモリセルからなるメモリセルアレイをさらに備え、

前記複数のメモリセルを接続するビット線は、前記配線と同じ構成である請求項1から11のいずれか1項記載の半導体装置。

【請求項13】

半導体基板の主面に第1の絶縁膜を介して第1の電極を形成し、

前記半導体基板の主面に第2の絶縁膜を介して第2の電極を形成し、

前記半導体基板の主面上の、前記第1の電極と前記第2の電極との間に補償膜を埋設し、

前記第1の電極の上面及び前記第2の電極の上面と接触する、前記第1の電極の上面から前記補償膜の上面を経由して前記第2の電極の上面まで到達する配線を形成することを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2013−98214(P2013−98214A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−237030(P2011−237030)

【出願日】平成23年10月28日(2011.10.28)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年10月28日(2011.10.28)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]