半導体装置及びその製造方法

【目的】埋め込みコンタクトを具備する半導体装置において、素子分離シリコン酸化膜のバーズビークにより、埋め込みコンタクト領域が減少することを防ぐことができる半導体装置及びその製造方法を提供する。

【構成】埋め込みコンタクト形成領域のシリコン基板1が削り取られており、その削り取られたシリコン基板の領域に多結晶シリコン層10が埋め込まれている。

【効果】埋め込みコンタクトの接続領域を制限するバーズビークをゲート酸化膜形成前に削り取るため、埋め込みコンタクトによる多結晶シリコン配線層と不純物拡散層との接続を確実なものにできる。

【構成】埋め込みコンタクト形成領域のシリコン基板1が削り取られており、その削り取られたシリコン基板の領域に多結晶シリコン層10が埋め込まれている。

【効果】埋め込みコンタクトの接続領域を制限するバーズビークをゲート酸化膜形成前に削り取るため、埋め込みコンタクトによる多結晶シリコン配線層と不純物拡散層との接続を確実なものにできる。

【発明の詳細な説明】

【0001】

【産業上の利用分野】本発明は、埋め込みコンタクトを具備する半導体装置の構造及びその製造方法に関する。

【0002】

【従来の技術】埋め込みコンタクトを具備する半導体装置、特にMOSFETの従来構造を図5に示す。

【0003】シリコン基板1上に、素子分離シリコン酸化膜2、ゲート膜3、多結晶シリコンゲート電極4、不純物拡散層5が形成され、さらに、多結晶シリコン配線層6と前記不純物拡散層の接続部に埋め込みコンタクト7が形成されている。

【0004】次に、従来の製造方法を図6の工程断面図を用いて説明する。

【0005】まず、図6(a)のように、シリコン基板1上に素子分離シリコン酸化膜2及び素子分離シリコン酸化膜形成の際に発生したホワイトリボン等を除去するために形成する犠牲シリコン酸化膜を形成する。そして、前記シリコン基板上の前記犠牲酸化膜を除去し、前記シリコン基板上にゲート酸化膜3を形成する。

【0006】そして、図6(b)のように、埋め込みコンタクト形成領域11のゲート酸化膜をフォトリソグラフィ及びエッチングにより除去する。

【0007】そして、図6(c)のように、前記半導体基板上に配線層、あるいは、ゲート電極として用いる多結晶シリコン層を形成し、前記多結晶シリコン層をフォトリソグラフィ及びエッチングによりパターニングし、ゲート電極4及び配線層6を形成する。

【0008】そして、図6(d)のように、熱アニールを行ない前記多結晶シリコン層より不純物を拡散させ、埋め込みコンタクト7を形成する。さらに、前記ゲート電極及び素子分離シリコン酸化膜をマスクとしたイオン注入法により、MOSトランジスタのソース、ドレインとなる不純物拡散層5を形成する。

【0009】以上のようにして、埋め込みコンタクトを具備する半導体装置を従来は製造していた。

【0010】

【発明が解決しようとする課題】従来の技術においては、下記のような問題点を有していた。

【0011】埋め込みコンタクト7が、図4のように3方向が素子分離シリコン酸化膜に囲まれた領域に存在した場合、素子分離シリコン酸化膜2のバーズビーク9が大きくなるため、埋め込みコンタクトによる接続の接続面積が小さくなり、埋め込みコンタクトの接続抵抗が大きくなる。

【0012】しかも、さらに素子の微細化が進んでくると、上記のような3方向が素子分離シリコン酸化膜に囲まれた領域におけるバーズビークがさらに大きくなり、埋め込みコンタクトによる接続が不可能になってくる。

【0013】そこで、本発明はこのような問題を解決しようとするもので、その目的とするところは、埋め込みコンタクトを具備する半導体装置において、素子分離シリコン酸化膜のバーズビークにより、前記埋め込みコンタクト領域が減少することを防ぐことができる半導体装置及びその製造方法を提供するところにある。

【0014】

【課題を解決するための手段】上記の目的を達成するために本発明半導体装置に関し、埋め込みコンタクトを具備する半導体装置において、埋め込みコンタクト形成領域のシリコン基板が削り取られており、その削り取られたシリコン基板の領域に多結晶シリコン層が埋め込む手段を取る。

【0015】また、本発明による半導体装置の製造方法は、埋め込みコンタクトを具備する半導体装置において、選択酸化により素子分離シリコン酸化膜を形成する工程と、犠牲シリコン酸化膜を形成する工程と、シリコン基板の埋め込みコンタクトを形成する領域をフォトリソグラフィによりパターニングし、エッチングすることにより埋め込みコンタクトを形成する領域の犠牲酸化膜、バーズビーク及びシリコン基板を削り取る工程と、前記シリコン基板上に多結晶シリコン層を形成し、前記多結晶シリコン層を削り取ることにより、前記埋め込みコンタクトを形成する領域のシリコン基板が削り取られた領域に多結晶シリコン層を埋め込む工程と、前記シリコン基板上の前記犠牲酸化膜を除去し、前記シリコン基板上にゲート酸化膜を形成する領域と、埋め込みコンタクト形成領域のゲート酸化膜をフォトリソグラフィ及びエッチングにより除去する工程と、前記半導体基板上に配線層、あるいは、ゲート電極として用いる多結晶シリコン層を形成する工程と、前記配線層、あるいは、ゲート電極として用いる多結晶シリコン層をフォトリソグラフィ及びエッチングによりパターニングする工程を具備する手段を取る。

【0016】また、本発明による半導体装置の製造方法は、埋め込みコンタクトを具備する半導体装置において、選択酸化により素子分離シリコン酸化膜を形成する工程と、犠牲シリコン酸化膜を形成する工程と、シリコン基板の埋め込みコンタクトを形成する領域をフォトリソグラフィによりパターニングし、エッチングすることにより埋め込みコンタクトを形成する領域の犠牲シリコン酸化膜及びバーズビークを削り取る工程と、前記シリコン基板上の前記犠牲酸化膜を除去し、前記シリコン基板上にゲート酸化膜を形成する領域と、埋め込みコンタクト形成領域のゲート酸化膜をフォトリソグラフィ及びエッチングにより除去する工程と、前記シリコン基板上に配線層、あるいは、ゲート電極として用いる多結晶シリコン層を形成する工程と、前記配線層、あるいは、ゲート電極として用いる多結晶シリコン層をフォトリソグラフィ及びエッチングによりパターニングする工程を具備する手段を取る。

【0017】

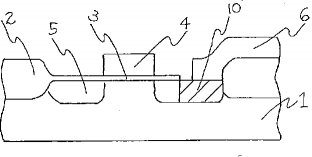

【実施例】本発明における請求項1の一実施例の断面図を図1に示す。

【0018】シリコン基板1上に、素子分離シリコン酸化膜2、ゲート膜3、多結晶シリコンゲート電極4、不純物拡散層5が形成され、さらに、多結晶シリコン配線層6と前記不純物拡散層の接続部に埋め込みコンタクト7が形成されている。なお、埋め込みコンタクト領域のシリコン基板は削り取られており、その領域に多結晶シリコン10が埋め込まれている。

【0019】次に、本発明における請求項1の一実施例の製造方法を図2(a)〜図2(f)に基づき説明する。

【0020】まず、シリコン基板1上に、150オングストローム〜250オングストロームのパッドシリコン酸化膜及び1200オングストローム〜1600オングストロームのシリコン窒化膜を用いた選択熱酸化法により4000オングストローム〜6000オングストロームの素子分離シリコン酸化膜2を形成する。選択酸化の条件として、例えば、1000℃〜1100℃の温度で、60分から90分間、ウエット雰囲気で行なう熱酸化があげられる。そして、前記シリコン窒化膜を剥離した後、素子分離シリコン酸化膜形成の際に発生したホワイトリボンを取り除くことを目的とする150オングストローム〜250オングストロームの犠牲酸化膜8を、800℃〜950℃の温度で、20分〜40分の時間、ウエット雰囲気中で熱酸化することにより形成する。この状態を示す図が図2(a)である。

【0021】そして、フォトレジストを用い、フォトリソグラフィにより埋め込みコンタクトを形成する領域11をパターニングする。そして、異方性のドライエッチングにより前記犠牲酸化膜およびバーズビークを除去するとともに、シリコン基板を1500オングストローム〜3000オングストローム削り取る。この状態を示す図が図2(b)である。

【0022】そして、前記シリコン基板上に3000オングストローム〜5000オングストロームの多結晶シリコンを化学的気相成長法により形成する。この際、前記多結晶シリコンにイオン注入法あるいは熱拡散法で不純物を導入してもよい。そして、異方性のドライエッチングによりエッチングすることにより、前記埋め込みコンタクト領域に多結晶シリコン10を埋め込む。この状態を示す図が図2(c)である。

【0023】そして、前記シリコン基板上の前記犠牲酸化膜を弗酸:水が約1:10の水溶液を用いて除去し、前記シリコン基板上に100オングストローム〜200オングストロームのゲート酸化膜3を800℃〜950℃の温度で、20分〜40分の時間、ウエット雰囲気中で熱酸化することにより形成する。この状態を示す図が図2(d)である。

【0024】そして、埋め込みコンタクト形成領域11のゲート酸化膜をフォトレジストを用いたフォトリソグラフィによりパターニングし、弗酸:水が約1:20の水溶液を用いたウエットエッチングにより前記ゲート酸化膜を除去する。この状態を示す図が図2(e)である。

【0025】そして、前記半導体基板上に配線層あるいはゲート電極として用いる4000オングストロームから6000オングストロームの多結晶シリコン層を化学的気相成長法により形成し、イオン注入法あるいは熱拡散法で不純物を前記多結晶シリコン層に導入する。そして、フォトリソグラフィ及びドライエッチングによりゲート電極4あるいは配線層6となる前記多結晶シリコン膜をパターニングする。そして、800℃〜1000℃の熱アニールにより、前記多結晶シリコン中から不純物を前記ゲート膜の開口部からシリコン基板中に導入し、埋め込みコンタクト7を形成する。そして、前記素子分離シリコン酸化膜及びゲート電極をマスクとして、イオン注入法で不純物を導入し、MOSトランジスタのソース、ドレインとなる不純物拡散層5を形成する。この状態を示す図が図2(f)である。

【0026】その後は、通常のプロセスにより埋め込みコンタクトを具備する半導体装置を製造することができる。

【0027】従来の技術においては、多結晶シリコン配線層に導入する不純物は、埋め込みコンタクトの形成を容易にするため、熱拡散しやすいもの、例えば、燐を使用していた。しかし、埋め込みコンタクト層部において、多結晶シリコン配線層より拡散された不純物層は、通常のソース、ドレイン領域の拡散層よりも深く、さらに、横方向の広がりも大きいため、埋め込みコンタクト形成領域の実効的な素子分離幅が、通常の素子分離幅よりも縮小してしまい、寄生MOSトランジスタが形成されやすくなっている。一方、熱拡散しにくい不純物、例えば、ヒ素を多結晶シリコン層に導入した場合、寄生MOSトランジスタは形成されにくくなるが、多結晶シリコン層から不純物が拡散されにくくなり、埋め込みコンタクトが高抵抗になってしまう。ところが、本発明によると、埋め込みコンタクト形成領域に埋め込んでおく多結晶シリコン層に不純物、例えば、ヒ素を導入しておくことにより、熱拡散しにくい不純物を多結晶シリコン配線層に導入することができる。

【0028】また、本発明によると、埋め込みコンタクトの接続領域を制限するバーズビークを削り取るため、埋め込みコンタクトによる多結晶シリコン配線層と不純物拡散層との接続を確実なものにすることができる。

【0029】なお、本発明による製造方法の実施例においては、埋め込みコンタクト開孔部のシリコン基板を削り取り、そこに多結晶シリコンを埋め込む方法を用いたが、前記埋め込みコンタクト開孔部に多結晶シリコンを埋め込まずに、埋め込みコンタクトを形成しても良いことは言うまでもない。

【0030】次に、本発明における他の一実施例の製造方法を図3(a)〜図3(e)に基づき説明する。

【0031】まず、シリコン基板1上に、150オングストローム〜250オングストロームのパッドシリコン酸化膜及び1200オングストローム〜1600オングストロームのシリコン窒化膜を用いた選択熱酸化法により4000オングストローム〜6000オングストロームの素子分離シリコン酸化膜2を形成する。選択酸化の条件としては、例えば、1000℃〜1100℃の温度で、60分から90分間、ウエット雰囲気中で行なう熱酸化があげられる。そして、前記シリコン窒化膜を剥離した後、素子分離シリコン酸化膜形成の際に発生したホワイトリボンを取り除くことを目的とする150オングストローム〜500オングストロームの犠牲酸化膜8を、800℃〜950℃の温度で、20分〜40分の時間、ウエット雰囲気中で熱酸化することにより形成する。この状態を示す図が図3(a)である。

【0032】そして、フォトレジストを用い、フォトリソグラフィにより埋め込みコンタクトを形成する領域11をパターニングする。そして、弗酸:水が約1:20の水溶液を用いてウエットエッチングにより前記犠牲酸化膜を除去するとともに、バーズビークも削り取る。この状態を示す図が図3(b)である。

【0033】そして、前記シリコン基板上の前記犠牲酸化膜を弗酸:水が約1:10の水溶液を用いて除去し、前記シリコン基板上に100オングストローム〜200オングストロームのゲート酸化膜3を800℃〜950℃の温度で、20分〜40分の時間、ウエット雰囲気中で熱酸化することにより形成する。この状態を示す図が図3(c)である。

【0034】そして、埋め込みコンタクト形成領域11のゲート酸化膜をフォトレジストを用いたフォトリソグラフィによりパターニングし、弗酸:水が約1:20の水溶液を用いたウエットエッチングにより前記ゲート酸化膜を除去する。この状態を示す図が図3(d)である。

【0035】そして、前記半導体基板上に配線層あるいはゲート電極として用いる4000オングストロームから6000オングストロームの多結晶シリコン層を化学的気相成長法により形成し、イオン注入法あるいは熱拡散法で不純物を前記多結晶シリコン層に導入する。そして、フォトリソグラフィ及びドライエッチングによりゲート電極4あるいは配線層6となる前記多結晶シリコン膜をパターニングする。そして、800℃〜1000℃の熱アニールにより、前記多結晶シリコン中から不純物を前記ゲート膜の開口部からシリコン基板中に導入し、埋め込みコンタクト7を形成する。そして、前記素子分離シリコン酸化膜及びゲート電極をマスクとして、イオン注入法で不純物を導入し、MOSトランジスタのソース、ドレインとなる不純物拡散層5を形成する。この状態を示す図が図3(e)である。

【0036】その後は、通常のプロセスにより埋め込みコンタクトを具備する半導体装置を製造することができる。

【0037】埋め込みコンタクトによる接続の接続面積を小さくするバーズビークを、埋め込みコンタクト形成領域のゲート酸化膜を開孔する際のエッチング量を多くすることにより減らすこともできる。しかし、ゲート酸化膜開孔の際のエッチングはウエットエッチングで行われるため、ゲート酸化膜の開孔が横方向にも広がってしまい、図4のように、ゲート電極4と埋め込みコンタクト形成のためのゲート酸化膜の開孔部11との距離12が短くなっていまい、ゲート電極とシリコン基板がゲート酸化膜の開孔部を介して短絡してしまう可能性がある。

【0038】以上に述べたように、本発明によると、埋め込みコンタクトの接続領域を制限するバーズビークをゲート酸化膜形成前に削り取るため、前述のような問題もなく、埋め込みコンタクトによる多結晶シリコン配線層と不純物拡散層との接続を確実なものにできる。

【0039】

【発明の効果】以上に述べたように本発明によると、埋め込みコンタクトの接続領域を制限するバーズビークを削り取るため、埋め込みコンタクトによる多結晶シリコン配線層と不純物拡散層との接続を確実なものにすることができる。

【図面の簡単な説明】

【図1】本発明の半導体装置の一実施例を示す断面図。

【図2】本発明の半導体装置の製造方法を示す図。

【図3】本発明の半導体装置の製造方法を示す図。

【図4】従来の半導体装置の一実施例を示す平面図。

【図5】従来の半導体装置の一実施例を示す断面図。

【図6】従来の半導体装置の製造方法を示す断面図。

【符号の説明】

1 シリコン基板

2 素子分離シリコン酸化膜

3 ゲート酸化膜

4 多結晶シリコンゲート電極

5 不純物拡散層

6 多結晶シリコン配線層

7 埋め込みコンタクト

8 犠牲シリコン酸化膜

9 バーズビーク

10 埋め込まれた多結晶シリコン

11 埋め込みコンタクト形成領域

12 埋め込みコンタクト開孔部とゲート電極の距離

【0001】

【産業上の利用分野】本発明は、埋め込みコンタクトを具備する半導体装置の構造及びその製造方法に関する。

【0002】

【従来の技術】埋め込みコンタクトを具備する半導体装置、特にMOSFETの従来構造を図5に示す。

【0003】シリコン基板1上に、素子分離シリコン酸化膜2、ゲート膜3、多結晶シリコンゲート電極4、不純物拡散層5が形成され、さらに、多結晶シリコン配線層6と前記不純物拡散層の接続部に埋め込みコンタクト7が形成されている。

【0004】次に、従来の製造方法を図6の工程断面図を用いて説明する。

【0005】まず、図6(a)のように、シリコン基板1上に素子分離シリコン酸化膜2及び素子分離シリコン酸化膜形成の際に発生したホワイトリボン等を除去するために形成する犠牲シリコン酸化膜を形成する。そして、前記シリコン基板上の前記犠牲酸化膜を除去し、前記シリコン基板上にゲート酸化膜3を形成する。

【0006】そして、図6(b)のように、埋め込みコンタクト形成領域11のゲート酸化膜をフォトリソグラフィ及びエッチングにより除去する。

【0007】そして、図6(c)のように、前記半導体基板上に配線層、あるいは、ゲート電極として用いる多結晶シリコン層を形成し、前記多結晶シリコン層をフォトリソグラフィ及びエッチングによりパターニングし、ゲート電極4及び配線層6を形成する。

【0008】そして、図6(d)のように、熱アニールを行ない前記多結晶シリコン層より不純物を拡散させ、埋め込みコンタクト7を形成する。さらに、前記ゲート電極及び素子分離シリコン酸化膜をマスクとしたイオン注入法により、MOSトランジスタのソース、ドレインとなる不純物拡散層5を形成する。

【0009】以上のようにして、埋め込みコンタクトを具備する半導体装置を従来は製造していた。

【0010】

【発明が解決しようとする課題】従来の技術においては、下記のような問題点を有していた。

【0011】埋め込みコンタクト7が、図4のように3方向が素子分離シリコン酸化膜に囲まれた領域に存在した場合、素子分離シリコン酸化膜2のバーズビーク9が大きくなるため、埋め込みコンタクトによる接続の接続面積が小さくなり、埋め込みコンタクトの接続抵抗が大きくなる。

【0012】しかも、さらに素子の微細化が進んでくると、上記のような3方向が素子分離シリコン酸化膜に囲まれた領域におけるバーズビークがさらに大きくなり、埋め込みコンタクトによる接続が不可能になってくる。

【0013】そこで、本発明はこのような問題を解決しようとするもので、その目的とするところは、埋め込みコンタクトを具備する半導体装置において、素子分離シリコン酸化膜のバーズビークにより、前記埋め込みコンタクト領域が減少することを防ぐことができる半導体装置及びその製造方法を提供するところにある。

【0014】

【課題を解決するための手段】上記の目的を達成するために本発明半導体装置に関し、埋め込みコンタクトを具備する半導体装置において、埋め込みコンタクト形成領域のシリコン基板が削り取られており、その削り取られたシリコン基板の領域に多結晶シリコン層が埋め込む手段を取る。

【0015】また、本発明による半導体装置の製造方法は、埋め込みコンタクトを具備する半導体装置において、選択酸化により素子分離シリコン酸化膜を形成する工程と、犠牲シリコン酸化膜を形成する工程と、シリコン基板の埋め込みコンタクトを形成する領域をフォトリソグラフィによりパターニングし、エッチングすることにより埋め込みコンタクトを形成する領域の犠牲酸化膜、バーズビーク及びシリコン基板を削り取る工程と、前記シリコン基板上に多結晶シリコン層を形成し、前記多結晶シリコン層を削り取ることにより、前記埋め込みコンタクトを形成する領域のシリコン基板が削り取られた領域に多結晶シリコン層を埋め込む工程と、前記シリコン基板上の前記犠牲酸化膜を除去し、前記シリコン基板上にゲート酸化膜を形成する領域と、埋め込みコンタクト形成領域のゲート酸化膜をフォトリソグラフィ及びエッチングにより除去する工程と、前記半導体基板上に配線層、あるいは、ゲート電極として用いる多結晶シリコン層を形成する工程と、前記配線層、あるいは、ゲート電極として用いる多結晶シリコン層をフォトリソグラフィ及びエッチングによりパターニングする工程を具備する手段を取る。

【0016】また、本発明による半導体装置の製造方法は、埋め込みコンタクトを具備する半導体装置において、選択酸化により素子分離シリコン酸化膜を形成する工程と、犠牲シリコン酸化膜を形成する工程と、シリコン基板の埋め込みコンタクトを形成する領域をフォトリソグラフィによりパターニングし、エッチングすることにより埋め込みコンタクトを形成する領域の犠牲シリコン酸化膜及びバーズビークを削り取る工程と、前記シリコン基板上の前記犠牲酸化膜を除去し、前記シリコン基板上にゲート酸化膜を形成する領域と、埋め込みコンタクト形成領域のゲート酸化膜をフォトリソグラフィ及びエッチングにより除去する工程と、前記シリコン基板上に配線層、あるいは、ゲート電極として用いる多結晶シリコン層を形成する工程と、前記配線層、あるいは、ゲート電極として用いる多結晶シリコン層をフォトリソグラフィ及びエッチングによりパターニングする工程を具備する手段を取る。

【0017】

【実施例】本発明における請求項1の一実施例の断面図を図1に示す。

【0018】シリコン基板1上に、素子分離シリコン酸化膜2、ゲート膜3、多結晶シリコンゲート電極4、不純物拡散層5が形成され、さらに、多結晶シリコン配線層6と前記不純物拡散層の接続部に埋め込みコンタクト7が形成されている。なお、埋め込みコンタクト領域のシリコン基板は削り取られており、その領域に多結晶シリコン10が埋め込まれている。

【0019】次に、本発明における請求項1の一実施例の製造方法を図2(a)〜図2(f)に基づき説明する。

【0020】まず、シリコン基板1上に、150オングストローム〜250オングストロームのパッドシリコン酸化膜及び1200オングストローム〜1600オングストロームのシリコン窒化膜を用いた選択熱酸化法により4000オングストローム〜6000オングストロームの素子分離シリコン酸化膜2を形成する。選択酸化の条件として、例えば、1000℃〜1100℃の温度で、60分から90分間、ウエット雰囲気で行なう熱酸化があげられる。そして、前記シリコン窒化膜を剥離した後、素子分離シリコン酸化膜形成の際に発生したホワイトリボンを取り除くことを目的とする150オングストローム〜250オングストロームの犠牲酸化膜8を、800℃〜950℃の温度で、20分〜40分の時間、ウエット雰囲気中で熱酸化することにより形成する。この状態を示す図が図2(a)である。

【0021】そして、フォトレジストを用い、フォトリソグラフィにより埋め込みコンタクトを形成する領域11をパターニングする。そして、異方性のドライエッチングにより前記犠牲酸化膜およびバーズビークを除去するとともに、シリコン基板を1500オングストローム〜3000オングストローム削り取る。この状態を示す図が図2(b)である。

【0022】そして、前記シリコン基板上に3000オングストローム〜5000オングストロームの多結晶シリコンを化学的気相成長法により形成する。この際、前記多結晶シリコンにイオン注入法あるいは熱拡散法で不純物を導入してもよい。そして、異方性のドライエッチングによりエッチングすることにより、前記埋め込みコンタクト領域に多結晶シリコン10を埋め込む。この状態を示す図が図2(c)である。

【0023】そして、前記シリコン基板上の前記犠牲酸化膜を弗酸:水が約1:10の水溶液を用いて除去し、前記シリコン基板上に100オングストローム〜200オングストロームのゲート酸化膜3を800℃〜950℃の温度で、20分〜40分の時間、ウエット雰囲気中で熱酸化することにより形成する。この状態を示す図が図2(d)である。

【0024】そして、埋め込みコンタクト形成領域11のゲート酸化膜をフォトレジストを用いたフォトリソグラフィによりパターニングし、弗酸:水が約1:20の水溶液を用いたウエットエッチングにより前記ゲート酸化膜を除去する。この状態を示す図が図2(e)である。

【0025】そして、前記半導体基板上に配線層あるいはゲート電極として用いる4000オングストロームから6000オングストロームの多結晶シリコン層を化学的気相成長法により形成し、イオン注入法あるいは熱拡散法で不純物を前記多結晶シリコン層に導入する。そして、フォトリソグラフィ及びドライエッチングによりゲート電極4あるいは配線層6となる前記多結晶シリコン膜をパターニングする。そして、800℃〜1000℃の熱アニールにより、前記多結晶シリコン中から不純物を前記ゲート膜の開口部からシリコン基板中に導入し、埋め込みコンタクト7を形成する。そして、前記素子分離シリコン酸化膜及びゲート電極をマスクとして、イオン注入法で不純物を導入し、MOSトランジスタのソース、ドレインとなる不純物拡散層5を形成する。この状態を示す図が図2(f)である。

【0026】その後は、通常のプロセスにより埋め込みコンタクトを具備する半導体装置を製造することができる。

【0027】従来の技術においては、多結晶シリコン配線層に導入する不純物は、埋め込みコンタクトの形成を容易にするため、熱拡散しやすいもの、例えば、燐を使用していた。しかし、埋め込みコンタクト層部において、多結晶シリコン配線層より拡散された不純物層は、通常のソース、ドレイン領域の拡散層よりも深く、さらに、横方向の広がりも大きいため、埋め込みコンタクト形成領域の実効的な素子分離幅が、通常の素子分離幅よりも縮小してしまい、寄生MOSトランジスタが形成されやすくなっている。一方、熱拡散しにくい不純物、例えば、ヒ素を多結晶シリコン層に導入した場合、寄生MOSトランジスタは形成されにくくなるが、多結晶シリコン層から不純物が拡散されにくくなり、埋め込みコンタクトが高抵抗になってしまう。ところが、本発明によると、埋め込みコンタクト形成領域に埋め込んでおく多結晶シリコン層に不純物、例えば、ヒ素を導入しておくことにより、熱拡散しにくい不純物を多結晶シリコン配線層に導入することができる。

【0028】また、本発明によると、埋め込みコンタクトの接続領域を制限するバーズビークを削り取るため、埋め込みコンタクトによる多結晶シリコン配線層と不純物拡散層との接続を確実なものにすることができる。

【0029】なお、本発明による製造方法の実施例においては、埋め込みコンタクト開孔部のシリコン基板を削り取り、そこに多結晶シリコンを埋め込む方法を用いたが、前記埋め込みコンタクト開孔部に多結晶シリコンを埋め込まずに、埋め込みコンタクトを形成しても良いことは言うまでもない。

【0030】次に、本発明における他の一実施例の製造方法を図3(a)〜図3(e)に基づき説明する。

【0031】まず、シリコン基板1上に、150オングストローム〜250オングストロームのパッドシリコン酸化膜及び1200オングストローム〜1600オングストロームのシリコン窒化膜を用いた選択熱酸化法により4000オングストローム〜6000オングストロームの素子分離シリコン酸化膜2を形成する。選択酸化の条件としては、例えば、1000℃〜1100℃の温度で、60分から90分間、ウエット雰囲気中で行なう熱酸化があげられる。そして、前記シリコン窒化膜を剥離した後、素子分離シリコン酸化膜形成の際に発生したホワイトリボンを取り除くことを目的とする150オングストローム〜500オングストロームの犠牲酸化膜8を、800℃〜950℃の温度で、20分〜40分の時間、ウエット雰囲気中で熱酸化することにより形成する。この状態を示す図が図3(a)である。

【0032】そして、フォトレジストを用い、フォトリソグラフィにより埋め込みコンタクトを形成する領域11をパターニングする。そして、弗酸:水が約1:20の水溶液を用いてウエットエッチングにより前記犠牲酸化膜を除去するとともに、バーズビークも削り取る。この状態を示す図が図3(b)である。

【0033】そして、前記シリコン基板上の前記犠牲酸化膜を弗酸:水が約1:10の水溶液を用いて除去し、前記シリコン基板上に100オングストローム〜200オングストロームのゲート酸化膜3を800℃〜950℃の温度で、20分〜40分の時間、ウエット雰囲気中で熱酸化することにより形成する。この状態を示す図が図3(c)である。

【0034】そして、埋め込みコンタクト形成領域11のゲート酸化膜をフォトレジストを用いたフォトリソグラフィによりパターニングし、弗酸:水が約1:20の水溶液を用いたウエットエッチングにより前記ゲート酸化膜を除去する。この状態を示す図が図3(d)である。

【0035】そして、前記半導体基板上に配線層あるいはゲート電極として用いる4000オングストロームから6000オングストロームの多結晶シリコン層を化学的気相成長法により形成し、イオン注入法あるいは熱拡散法で不純物を前記多結晶シリコン層に導入する。そして、フォトリソグラフィ及びドライエッチングによりゲート電極4あるいは配線層6となる前記多結晶シリコン膜をパターニングする。そして、800℃〜1000℃の熱アニールにより、前記多結晶シリコン中から不純物を前記ゲート膜の開口部からシリコン基板中に導入し、埋め込みコンタクト7を形成する。そして、前記素子分離シリコン酸化膜及びゲート電極をマスクとして、イオン注入法で不純物を導入し、MOSトランジスタのソース、ドレインとなる不純物拡散層5を形成する。この状態を示す図が図3(e)である。

【0036】その後は、通常のプロセスにより埋め込みコンタクトを具備する半導体装置を製造することができる。

【0037】埋め込みコンタクトによる接続の接続面積を小さくするバーズビークを、埋め込みコンタクト形成領域のゲート酸化膜を開孔する際のエッチング量を多くすることにより減らすこともできる。しかし、ゲート酸化膜開孔の際のエッチングはウエットエッチングで行われるため、ゲート酸化膜の開孔が横方向にも広がってしまい、図4のように、ゲート電極4と埋め込みコンタクト形成のためのゲート酸化膜の開孔部11との距離12が短くなっていまい、ゲート電極とシリコン基板がゲート酸化膜の開孔部を介して短絡してしまう可能性がある。

【0038】以上に述べたように、本発明によると、埋め込みコンタクトの接続領域を制限するバーズビークをゲート酸化膜形成前に削り取るため、前述のような問題もなく、埋め込みコンタクトによる多結晶シリコン配線層と不純物拡散層との接続を確実なものにできる。

【0039】

【発明の効果】以上に述べたように本発明によると、埋め込みコンタクトの接続領域を制限するバーズビークを削り取るため、埋め込みコンタクトによる多結晶シリコン配線層と不純物拡散層との接続を確実なものにすることができる。

【図面の簡単な説明】

【図1】本発明の半導体装置の一実施例を示す断面図。

【図2】本発明の半導体装置の製造方法を示す図。

【図3】本発明の半導体装置の製造方法を示す図。

【図4】従来の半導体装置の一実施例を示す平面図。

【図5】従来の半導体装置の一実施例を示す断面図。

【図6】従来の半導体装置の製造方法を示す断面図。

【符号の説明】

1 シリコン基板

2 素子分離シリコン酸化膜

3 ゲート酸化膜

4 多結晶シリコンゲート電極

5 不純物拡散層

6 多結晶シリコン配線層

7 埋め込みコンタクト

8 犠牲シリコン酸化膜

9 バーズビーク

10 埋め込まれた多結晶シリコン

11 埋め込みコンタクト形成領域

12 埋め込みコンタクト開孔部とゲート電極の距離

【特許請求の範囲】

【請求項1】 埋め込みコンタクトを具備する半導体装置において、埋め込みコンタクト形成領域のシリコン基板が削り取られており、その削り取られたシリコン基板の領域に多結晶シリコン層が埋め込まれていることを特徴とする半導体装置。

【請求項2】 埋め込みコンタクトを具備する半導体装置において、選択酸化により素子分離シリコン酸化膜を形成する工程と、犠牲シリコン酸化膜を形成する工程と、シリコン基板の埋め込みコンタクトを形成する領域をフォトリソグラフィによりパターニングし、エッチングすることにより埋め込みコンタクトを形成する領域の犠牲酸化膜、バーズビーク及びシリコン基板を削り取る工程と、前記シリコン基板上に多結晶シリコン層を形成し、前記多結晶シリコン層を削り取ることにより、前記埋め込みコンタクトを形成する領域のシリコン基板が削り取られた領域に多結晶シリコン層を埋め込む工程と、前記シリコン基板上の前記犠牲酸化膜を除去し、前記シリコン基板上にゲート酸化膜を形成する領域と、埋め込みコンタクト形成領域のゲート酸化膜をフォトリソグラフィ及びエッチングにより除去する工程と、前記半導体基板上に配線層、あるいは、ゲート電極として用いる多結晶シリコン層を形成する工程と、前記配線層、あるいは、ゲート電極として用いる多結晶シリコン層をフォトリソグラフィ及びエッチングによりパターニングする工程を具備することを特徴とする半導体装置の製造方法。

【請求項3】 埋め込みコンタクトを具備する半導体装置において、選択酸化により素子分離シリコン酸化膜を形成する工程と、犠牲シリコン酸化膜を形成する工程と、シリコン基板の埋め込みコンタクトを形成する領域をフォトリソグラフィによりパターニングし、エッチングすることにより埋め込みコンタクトを形成する領域の犠牲シリコン酸化膜及びバーズビークを削り取る工程と、前記シリコン基板上の前記犠牲酸化膜を除去し、前記シリコン基板上にゲート酸化膜を形成する領域と、埋め込みコンタクト形成領域のゲート酸化膜をフォトリソグラフィ及びエッチングにより除去する工程と、前記シリコン基板上に配線層、あるいは、ゲート電極として用いる多結晶シリコン層を形成する工程と、前記配線層、あるいは、ゲート電極として用いる多結晶シリコン層をフォトリソグラフィ及びエッチングによりパターニングする工程を具備することを特徴とする半導体装置の製造方法。

【請求項1】 埋め込みコンタクトを具備する半導体装置において、埋め込みコンタクト形成領域のシリコン基板が削り取られており、その削り取られたシリコン基板の領域に多結晶シリコン層が埋め込まれていることを特徴とする半導体装置。

【請求項2】 埋め込みコンタクトを具備する半導体装置において、選択酸化により素子分離シリコン酸化膜を形成する工程と、犠牲シリコン酸化膜を形成する工程と、シリコン基板の埋め込みコンタクトを形成する領域をフォトリソグラフィによりパターニングし、エッチングすることにより埋め込みコンタクトを形成する領域の犠牲酸化膜、バーズビーク及びシリコン基板を削り取る工程と、前記シリコン基板上に多結晶シリコン層を形成し、前記多結晶シリコン層を削り取ることにより、前記埋め込みコンタクトを形成する領域のシリコン基板が削り取られた領域に多結晶シリコン層を埋め込む工程と、前記シリコン基板上の前記犠牲酸化膜を除去し、前記シリコン基板上にゲート酸化膜を形成する領域と、埋め込みコンタクト形成領域のゲート酸化膜をフォトリソグラフィ及びエッチングにより除去する工程と、前記半導体基板上に配線層、あるいは、ゲート電極として用いる多結晶シリコン層を形成する工程と、前記配線層、あるいは、ゲート電極として用いる多結晶シリコン層をフォトリソグラフィ及びエッチングによりパターニングする工程を具備することを特徴とする半導体装置の製造方法。

【請求項3】 埋め込みコンタクトを具備する半導体装置において、選択酸化により素子分離シリコン酸化膜を形成する工程と、犠牲シリコン酸化膜を形成する工程と、シリコン基板の埋め込みコンタクトを形成する領域をフォトリソグラフィによりパターニングし、エッチングすることにより埋め込みコンタクトを形成する領域の犠牲シリコン酸化膜及びバーズビークを削り取る工程と、前記シリコン基板上の前記犠牲酸化膜を除去し、前記シリコン基板上にゲート酸化膜を形成する領域と、埋め込みコンタクト形成領域のゲート酸化膜をフォトリソグラフィ及びエッチングにより除去する工程と、前記シリコン基板上に配線層、あるいは、ゲート電極として用いる多結晶シリコン層を形成する工程と、前記配線層、あるいは、ゲート電極として用いる多結晶シリコン層をフォトリソグラフィ及びエッチングによりパターニングする工程を具備することを特徴とする半導体装置の製造方法。

【図1】

【図3】

【図4】

【図2】

【図5】

【図6】

【図3】

【図4】

【図2】

【図5】

【図6】

【公開番号】特開平6−120247

【公開日】平成6年(1994)4月28日

【国際特許分類】

【出願番号】特願平4−266278

【出願日】平成4年(1992)10月5日

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【公開日】平成6年(1994)4月28日

【国際特許分類】

【出願日】平成4年(1992)10月5日

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

[ Back to top ]