半導体装置及びその製造方法

【構成】 メイン基板2にCPU10、IOサブシステムチップ13等の主要なモジュールを搭載し、かつメインメモリ9を第1サブ基板3に搭載すると共に、メイン基板と第1サブ基板とをフレキシブル配線板4で接続した半導体装置1。CPUを搭載した第1TCP5とIOサブシステムチップを搭載した第2TCP6とをメイン基板の両面に、該基板を挟んで互いに重なり合うように実装する。フレキシブル配線板を湾曲させてメイン基板とサブ基板とを対面させ、カード形状の薄い箱体内に収容することによって、カード型コンピュータとして使用する。

【効果】 半導体装置の小型化、薄型化、高密度実装化及び高速化を図る。主要なモジュールを変更することなくサブ基板を取り替えるだけで、容易に短期間でかつ低コストで半導体装置の性能を最適に変更することができる。

【効果】 半導体装置の小型化、薄型化、高密度実装化及び高速化を図る。主要なモジュールを変更することなくサブ基板を取り替えるだけで、容易に短期間でかつ低コストで半導体装置の性能を最適に変更することができる。

【発明の詳細な説明】

【0001】

【産業上の利用分野】本発明は、プリント基板にICチップやLSI等の電子部品を搭載した半導体装置の構造及び製造方法に関し、例えばCPU、周辺装置制御用IC等を搭載したカード形状の小型コンピュータとして、様々な産業用機器及び民生用機器に組み込んで使用することができる。

【0002】

【従来の技術】従来より、マイクロコンピュータ技術の発達に伴い、自動工作機械、自動車、医療用・工業用の各種制御システムや自動販売機、自動現金支払機等の様々な産業用機器に加え、通信機器、オーディオ・ビデオ機器等の民生用機器の分野においても、コンピュータを用いた電子制御システムが広く採用されている。これらの機器に内蔵されるコンピュータシステムは、一般に専用性の高いものであり、各機器の用途、機能、デザインや周辺機器等の様々な使用条件に基づいて、それぞれ最適に設計・製造して使用される。このため、システムの開発や製造に相当の手間及び時間を要し、コストが増大するという問題があった。一方、コンピュータシステムのアーキテクチャは、例えばIBM社のPC−AT等のように特定のものが実質的な標準となっており、これに対応した周辺機器であれば、共通に利用できる場合が多い。

【0003】そこで、本願出願人による特願平5−278643号明細書に記載されるように、機器に組み込むコンピュータシステムをコンパクトなカード形状の箱体に収容してユニット化することによって、形状・構造の汎用化を図り、それにより機器毎にシステムを開発し、設計・製造するのに要する手間や労力を少なくし、コストを低減させ得る電子装置が提案されている。このような電子装置は、通例CPU(中央処理ユニット)、メモリや入出力・周辺機器制御用のIC等をプリント回路基板に実装することによって構成される。そして、プリント回路基板及びそれを収容するカード状箱体の寸法・形状等を統一することによって、ハードウェア上の汎用性を得ることができる。

【0004】他方、各種電子機器について小型・軽量・薄型化、高性能化が急速に進められ、特にコンピュータの分野では、情報量の大幅な増加に伴い情報処理の高速化が要求されている。このため、回路規模の増大、使用する電子部品の増加に対応して高密度化、高速化を図るべく、プリント基板の薄板化及びファインパターン化、多層構造の採用、電子部品の小型化等と共に、電子部品を接続するための様々な実装技術が開発されている。例えば、リフローはんだ付けによるQFP等のICパッケージの表面実装や、COBやTAB型式によるICのベアチップ実装が広く採用されている。

【0005】特にTAB型式によるTCPは、電極数やリード数に無関係に一回の動作で一括接続できるので量産性に優れ、しかもリードピッチを狭小化し、大型チップで多ピンに対応し得る特徴を有することから、高密度実装化に適している。一般にTCPをプリント基板に実装する場合、図21に示すように、プリント基板86の上に接続しようとするTCP87を載置し、その上方からボンディングツール88を用いて前記TCPのアウタリード89をプリント基板86上のランド90に加圧しかつ場合により同時に加熱して、はんだ付けや熱圧着等により接続する方法が行われている。このとき、ボンディングツールは約10kgf程度の加圧力をもって接合部を押圧するから、プリント基板は、上面の平坦な受け台91の上に載せて裏面から十分に支持する必要がある。

【0006】

【発明が解決しようとする課題】しかしながら、上述したようにユニット化された電子装置を用いてコンピュータシステムを設計・製造する場合、それを組み込む機器や設備の要求する機能、使用条件に応じて、それに搭載する半導体装置の動作速度、記憶容量等の性能を個々に適当に設定する必要がある。また、例えば自動工作機械の制御システム等の場合には、加工する対象や加工条件の変更に応じて、または使用する機種の変更に対応して、記憶されているデータを書き換える必要が生じる。このため、特に技術の進歩に対して記憶容量を切り換えるだけで対応し得る場合でも、プリント回路基板を設計し直したり基板全体を交換することになれば、ユニット化による汎用性の利益が十分に得られなくなる。

【0007】また、上述した従来の実装方法では、複数のTCPをプリント基板の両面に搭載しようとする場合、先に一方の面に実装した後にプリント基板を裏返して他方の面を実装することになるが、プリント基板8692先に接続されているTCP92を避けて受け台91に載せなければならない。このため、後から裏面に接続しようとするTCP87は、プリント基板を平面視したときに表面のTCP92と重なる位置に配置することができなかった。この結果、基板両面の面積を有効に利用することができないので、半導体装置の小型化が困難になり、十分に高密度化を図れないという問題があった。

【0008】特に、多層構造のプリント基板を用いる場合には、通例スルーホールを設けてTCPの電極端子を内層回路の配線に接続するが、上述した従来の実装方法では、動作上相互に関連する複数のICを互いに近接した位置に配置するには限界がある。このようなICが離れた位置に搭載され、それぞれ別個に設けたスルーホールを介して電源ライン、グランドラインに接続されると、搭載される位置や配線によってIC間の電源電位、接地電位に好ましくない差異や変動が生じ、そのために動作の安定性が損なわれる虞がある。しかも、スルーホールの数が多くなると、そのために使用される基板の面積が大きくなるから、基板及び半導体装置の小型化が一層困難になり、電子機器の小型化に十分対応することができない。また、配線長が必要以上に長くなって、所望の高速動作が期待できなくなる。

【0009】更に、基板の高密度実装化が進められると、搭載された各ICから発生する熱が多くなるので、これを効率よく放散させることが、基板の耐久性確保、動作の安定性等の観点から非常に重要である。そのために、従来使用されている放熱フィンやヒートシンク等の放熱手段または液体冷却装置等を使用すれば、コストが増大するだけでなく、基板全体の寸法が大きくなって、半導体装置及びこれを搭載する機器の小型化が一層困難になる。

【0010】そこで、本発明の半導体装置は、上述した問題点に鑑みてなされたものであり、その目的とするところは、装置の基本的な構成をユニット化することにより十分な汎用性を確保してコストの低減を図りつつ、異なる機能、使用条件に容易にかつ短期間で対応できる専用性を備え、特に記憶容量を容易に切り換えることができる半導体装置を提供することにある。

【0011】これに加え、装置全体のユニット化、コンパクト化に対応して、プリント回路基板の小型化・薄型化が要求されている。特にベアのICチップを用いて高密度に接続した基板にICチップ保護のための熱硬化性保護樹脂を塗布した場合、その硬化後に基板に反りが生じる等変形する虞がある。そこで、本発明の目的は、薄型基板において変形し難い構造の半導体装置を提供することにある。

【0012】また、装置全体の小型化・薄型化に伴い、現場での取扱いに対して十分な強度・耐久性を確保しなければならない。そこで、本発明の別の目的は、装置全体のコンパクト化を実現できると共に、十分な強度・耐久性を有する構造の半導体装置を提供することにある。

【0013】また、コンピュータシステムとして小型化及び高性能化が進むにつれて、基板の高密度実装化、ファインパターン化が促進され、消費電力も省力化されて少なくなる。このため、外部のノイズや回路自体の輻射ノイズの影響を受け易くなり、特にフロッピーディスクドライブ、ADコンバータ、PLL等のアナログ回路部分は、デジタル回路部分における電源電位の変動が影響して動作が不安定になる虞がある。そこで、本発明の更に別の目的は、特にアナログ部分において、ノイズの影響を少なくして誤動作の虞を解消し、動作の安定性・信頼性を確保し得る半導体装置を提供することにある。

【0014】更に、本発明の半導体装置の製造方法は、上述した汎用性と専用性との双方を備える半導体装置を、従来の工程に大幅な変更を加えたりコストを増大させることなく比較的容易に製造する方法を提供することを目的とする。

【0015】また、本発明の半導体装置は、プリント基板の両面に実装される複数のパッケージ型IC部品を、該プリント基板を挟んで互いに重なり合うように配置できるようにし、それにより基板面積の有効な利用を可能にして回路設計の自由度を増大させることができ、高密度実装化、小型化に適した半導体装置を提供することを目的とする。

【0016】これに加え、本発明の目的は、特に動作上関連が大きいICチップ間の配線長を短縮して、動作の高速化及び安定性・信頼性の向上を図ることができる半導体装置を提供することにある。

【0017】更に、本発明の半導体装置は、複数のパッケージ型IC部品をプリント基板の両面に重なり合うように配置できることに加えて、ICチップが発生する熱を、高価な放熱手段や冷却装置を用いることなく、比較的簡単な方法により効果的に放散させることができ、かつ低コストで小型化に対応し得る放熱構造を備えた半導体装置の提供を目的とする。

【0018】また、本発明の半導体装置の製造方法は、複数のパッケージ型IC部品をプリント基板の両面に重なり合うように配置した半導体装置を、従来の実装工程に大幅な変更を加えることなく、比較的簡単にかつ低コストで実現し得る方法の提供を目的とする。

【0019】

【課題を解決するための手段】本発明は、上述した目的を達成するためのものであり、以下にその内容を図面に示した実施例を用いて説明する。

【0020】請求項1記載の半導体装置は、基板に搭載されたCPUと入出力装置とメモリとを備え、該基板がメイン基板とそれに電気的に接続されたサブ基板とからなり、かつメモリが、サブ基板に搭載されたメモリ素子からなることを特徴とする。

【0021】請求項2記載の半導体装置は、上述した請求項1の特徴点に加え、CPUがメイン基板に搭載されていることを特徴とする。

【0022】これに対し、請求項3記載の半導体装置は、CPUがサブ基板に搭載されていることを特徴とする。

【0023】請求項4記載の半導体装置は、メイン基板とサブ基板とが、フレキシブル配線板を介して接続されていることを特徴とする。

【0024】これに対し、請求項5記載の半導体装置は、メイン基板とサブ基板とが、互いに対面するように1対のコネクタによって着脱可能に接続されていることを特徴とする。

【0025】請求項6記載の半導体装置は、上述した請求項4の特徴点に加え、フレキシブル配線板を湾曲させることにより、サブ基板がメイン基板と対面するように配置され、かつフレキシブル配線板が、メイン基板のサブ基板と対面する面と反対側の面に接続されていることを特徴とする。

【0026】更に請求項7記載の半導体装置は、互いに対面させたメイン基板とサブ基板とを一体的に固定するための手段を備えることを特徴とする。

【0027】請求項8記載の半導体装置は、上述した請求項1の特徴点に加え、メイン基板とサブ基板とを収容するためのカード形状の薄い箱体を備え、箱体の少なくとも一方の面が、絞り加工により外向きに膨出させた金属板からなることを特徴とする。

【0028】請求項9記載の半導体装置は、外部装置に接続するために多数の端子を配列したコネクタを更に備え、外部の液晶ディスプレイ装置(LCD)に接続されるドットクロック信号用端子が、接地端子に隣接して配置されていることを特徴とする。

【0029】請求項10記載の半導体装置は、同様に外部装置に接続するために多数の端子を複数の列に配列したコネクタを更に備えるが、外部のCRTに接続されるR、G、B信号用各端子の列が、それぞれ対応するR、G、Bリターン信号用各端子の列と平行をなし、かつ各端子が互いに対向する位置に配置されていることを特徴とする。

【0030】請求項11記載の半導体装置は、同じく外部装置に接続するために多数の端子を配列したコネクタを更に備え、該コネクタが、端子の列をその配列方向にみて左右非対称に分割するための手段を有することを特徴とする。

【0031】請求項12記載の半導体装置は、そのアナログ回路部分が、メイン基板に実装される第2のサブ基板に搭載され、かつ第2のサブ基板の電源端子が、1個所でメイン基板に接続されていることを特徴とする。

【0032】本発明の別の側面によれば、請求項13記載の半導体装置は、複数の電子部品を実装するための基板がメイン基板と電子部品をそれぞれ搭載した複数のサブ基板とからなり、少なくともいずれか2個のサブ基板が、メイン基板の両面に該基板を挟んで互いに重なり合う対称位置に実装されていることを特徴とする。

【0033】更に本発明の別の側面によれば、請求項14記載の半導体装置の製造方法は、電子部品をサブ基板に実装する過程と、このサブ基板をメイン基板上の所定位置に設置し、取外可能に仮付けした後にメイン基板に接続する過程とからなることを特徴とする。

【0034】また、請求項15記載の半導体装置は、第1ICパッケージと第2ICパッケージとをそれぞれプリント基板の第1及び第2面に実装した両面実装型であって、第1面上に形成されたランドと第1ICパッケージのリードとの接合部と、第2面上に形成されたランドと第2ICパッケージのリードとの接合部とが、互いにプリント基板を挟んで重なるように、第1及び第2ICパッケージをそれぞれ配置したことを特徴とする。

【0035】請求項16記載の半導体装置は、上述した請求項15の特徴点に加え、第1及び第2ICパッケージのリードと第1及び第2ランドとの各接合部が、互いに各ICパッケージのいずれか1辺において互いに重なり合うようにしたことを特徴とする。

【0036】また、請求項17によれば、上述した請求項15の特徴点に加えて、第1及び第2ICパッケージのリードと第1及び第2ランドとの各接合部が、互いに各ICパッケージの全4辺において重なり合うようにしたことを特徴とする半導体装置が提供される。

【0037】請求項18記載の半導体装置は、第1及び第2ICパッケージがその動作上相互に関連するICチップを搭載していることを特徴とし、更に、請求項19記載の発明によれば、第1ICパッケージがCPUを搭載し、かつ第2ICパッケージがこのCPUに対応して動作するI/Oシステムを搭載した半導体装置が提供される。

【0038】請求項20記載の発明によれば、これらの半導体装置において、少なくとも第1または第2ICパッケージがTCPからなる。

【0039】本発明の別の側面によれば、請求項21記載の半導体装置は、第1ICパッケージ及び第2ICパッケージが、プリント基板の各面に互いに該プリント基板を挟んで重なり合う位置に、それぞれダイボンディングによって接合され、かつプリント基板に貫設されたサーマルビアを介して互いに熱伝達可能に接続されていることを特徴とする。

【0040】請求項22記載の半導体装置は、上述した請求項21の特徴点に加え、プリント基板の各面に接続された第1または第2ICパッケージのリードを熱伝導性樹脂で被覆したことを特徴とする。

【0041】本発明の更に別の側面によれば、請求項23記載の半導体装置の製造方法は、複数のICパッケージをプリント基板の両面に、該プリント基板を挟んで互いに重なり合うように実装するための方法であって、先ず第1ICパッケージをプリント基板の第1面上に配置して、そのリードを第1ランドに接合することにより接続し、このプリント基板を反転させて、第1ICパッケージの接合部が支持されるように受け台の上に載置した後、第2ICパッケージをプリント基板の第2面上に、そのリードと第2面のランドとの接合部が第1ICパッケージの接合部と互いにプリント基板を挟んで重なり合うように配置し、受け台に対応する加圧手段を用いて第2ICパッケージのリードと第2ランドとを加圧することにより接合することを特徴とする。

【0042】請求項24記載の半導体装置の製造方法は、上述した請求項23の特徴点に加え、加圧手段により加圧する際に加熱し、はんだ付けによって第2ICパッケージのリードを第2ランドに接合することを特徴とする。

【0043】また、請求項25記載の半導体装置の製造方法は、上述した請求項23の特徴点に加え、加圧手段により加圧する際に加熱し、熱圧着によって第2ICパッケージのリードを第2ランドに接合することを特徴とする。

【0044】これに対し、請求項26記載の半導体装置の製造方法は、加圧手段により加圧する際に加熱し、異方性導電膜を用いて第2ICパッケージのリードを第2ランドに接合することを特徴とする。

【0045】請求項27記載の半導体装置の製造方法は、加圧手段により加圧する際に光を照射し、光硬化性樹脂を用いて第2ICパッケージのリードを第2ランドに接合することを特徴とする。

【0046】

【作用】従って、請求項1記載の半導体装置によれば、メイン基板に搭載された主要なモジュールはそのまま維持しつつ、サブ基板を取り替えるだけで、組み込む機器の機種や使用条件の変更に応じて、少なくとも記憶容量を簡単に切り換えることができる。

【0047】請求項2記載の半導体装置によれば、メイン基板の性能を維持しつつ、サブ基板を取り替えることで、半導体装置の記憶容量のみを必要に応じて容易に変更することができる。

【0048】請求項3記載の半導体装置によれば、メイン基板の基本的構成を共通化し、サブ基板を取り替えることで、半導体装置の性能及び記憶容量を必要に応じて容易に変更することができる。

【0049】請求項4記載の半導体装置によれば、フレキシブル配線板によって安価にかつ簡単に両基板を接続することができる。

【0050】請求項5記載の半導体装置によれば、コネクタによって多数の接続端子を狭ピッチで配設することができ、サブ基板に搭載されるメモリ及び/またはCPUの変更により配線が増加しても、比較的容易に対応することができる。

【0051】請求項6記載の半導体装置によれば、フレキシブル配線板をより大きな曲率で湾曲させることができる。

【0052】請求項7記載の半導体装置によれば、使用時に、例えば振動等により両基板が相対的に動かないように固定することができ、フレキシブル配線板やコネクタに不要な応力が加わらないようにして電気的接続を確保することができる。

【0053】請求項8記載の半導体装置によれば、金属板を外向きに膨出させることによって、カード形状をなす薄型の箱体に、その厚さ方向に容易に変形し難い十分な剛性を与えることができる。

【0054】請求項9記載の半導体装置によれば、外部のLCDに出力されるドットクロック用信号が安定するので、LCDによる表示を安定させることができる。

【0055】請求項10記載の半導体装置によれば、外部のCRTに出力されるアナログ信号であるR、G、B各信号を、出力側とリターン側とにおいて略同一条件にし、外部からのノイズ等の影響を少なくして、CRTによる表示を安定させることができる。

【0056】請求項11記載の半導体装置によれば、コネクタの接続に方向性を持たせることができるので、装着しようとする機器に対してコネクタを誤った向きに接続することがない。

【0057】請求項12記載の半導体装置によれば、半導体装置のアナログ回路部分を、デジタル回路部分とは別基板にして、その電源を1個所に統一することによって、デジタル回路部分における電源電位の変動による影響を少なくし、かつ基板のスペースを節約することができる。

【0058】請求項13記載の半導体装置によれば、複数のサブ基板にそれぞれ異なる電子部品を搭載し、これらを適当に選択してメイン基板に実装することによって、寸法・形状が同一で機能の異なる半導体装置を得ることができる。しかも、サブ基板が薄型化によって反りを生じても、そのような2個のサブ基板をメイン基板の両面に対称位置に接続することによって、メイン基板の変形を防止することができる。

【0059】請求項14記載の半導体装置の製造方法によれば、薄型化により反りを生じた場合でも、サブ基板を確実に位置決めしてメイン基板に接続することができる。

【0060】従って、請求項15記載の半導体装置によれば、プリント基板の両面に実装された複数のICパッケージの接合部が、プリント基板を挟んで互いに重なり合うことにより、この重なり合う部分の面積だけ基板の実装面積を小さくし、かつ基板両面の面積を有効に利用することができる。また、互いに重なり合う接合部同士においては、ICパッケージ間の配線距離を短くすることができる。

【0061】そして、請求項16記載の半導体装置によれば、ICパッケージの1辺において重なり合う接合部の部分だけ基板の実装面積を減少させることができ、更に、請求項17記載の半導体装置によれば、ICパッケージ同士が全体的に重なり合うように配置されることによって、基板の実装面積を大幅に減少させることができる。

【0062】また、請求項18記載の半導体装置によれば、各ICパッケージの例えば電源用、接地用の対応するリード同士が近接した位置に配置されるので、ICパッケージ間の配線長を短くでき、更にスルーホールを共通化することができる。特に、請求項19記載の半導体装置によれば、共有し得る信号線、アドレス線等が多いので、スルーホールの共通化によってその必要な数を大幅に減少させることができる。

【0063】更に、請求項20記載の半導体装置によれば、特にTCPの場合に、そのアウタリードとTCPに搭載したIC部品間のキャリアテープの領域において、プリント基板上では、リードとの接合部から内向きに配線を引き出し、かつスルーホールを形成することができる。

【0064】また、請求項21記載の半導体装置によれば、第1ICパッケージまたは第2ICパッケージの一方からより多く発生する熱の一部が、発熱のより少ない他方のICパッケージにサーマルビアを介して伝達されかつ放散されるので、放熱面積を実質的に増大させることができる。

【0065】更に請求項22記載の半導体装置によれば、接合部のリードを被覆する熱伝導性樹脂からも、該リードを介して伝達されるICパッケージの熱を放散させることができる。

【0066】また、請求項23記載の半導体装置の製造方法によれば、従来の実装工程と同様に、プリント基板を支持する受け台と接合部を加圧する加圧手段とを用いて、先にプリント基板の第1面に接続された第1ICパッケージと互いに重なり合うように、第2ICパッケージをプリント基板の第2面に接続することができる。

【0067】更に、請求項24乃至請求項27記載の製造方法によれば、従来より公知のはんだ付け、熱圧着、異方性導電膜、光硬化性樹脂を用いて、比較的容易に第2ICパッケージをプリント基板の第2面に、第1面に接続された第1ICパッケージと互いに重なり合うように接続することができる。

【0068】

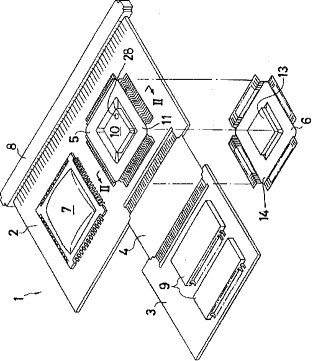

【実施例】図1は、本発明を適用した半導体装置の第1実施例を概略的に示している。この半導体装置1は、所謂ICカードやメモリカード等と略同一形状をなすカード型の小型コンピュータとして使用され、セラミック材料またはガラスエポキシ材料を基材とする2枚のプリント回路基板、即ち両面実装用の多層構造を有するメイン基板2と、それより小形の第1サブ基板3とからなる。これらの基板は、それぞれ長手方向の一辺にはんだ付けされたフレキシブル配線板4によって電気的に接続されている。メイン基板2には、第1TCP(Tape Carrier Package)5がフレキシブル配線板4を接続した面上に接続され、かつ反対側の面には、第2TCP6がメイン基板2を挟んで第1TCP5と重なる対称位置に、互いに全4辺の接続部が重なり合うように接続されている。

【0069】また、メイン基板2の両面には、後述するように薄型配線板に電子部品を予め実装した第2サブ基板7及び第3サブ基板(図示せず)が、それぞれ前記TCPの側方に互いにメイン基板2を挟んで重なり合う対称位置に接続されている。これら第2、第3サブ基板は、半導体装置1の異なる機能に対応して異なる電子部品を搭載した複数の異なるパッケージを予め用意することができる。そして、このパッケージされたサブ基板を適当に選択して組み合わせることによって、機能・用途の異なる多種類の半導体装置1を簡単に短期間でかつ低コストで設計・製造することができる。また、前記第2または第3サブ基板を別のパッケージと取り替えることによって、比較的容易に仕様の変更を実現することができる。更に、メイン基板2には、上述した電子部品以外に、図示されていないがコンピュータシステムとしてメインメモリを除く主要なモジュールを構成するために必要な電子部品類が搭載されている。また、メイン基板2のフレキシブル配線板4を接続した側と反対側の長辺に沿って、外部の装置に接続するためのコネクタ8が設けられている。

【0070】他方、第1サブ基板3には、半導体装置1のメインメモリを構成するメモリ素子として、2個のRAM9が実装されている。このため、フレキシブル配線板4は、メイン基板2の第1TCP5近傍に接続すると好都合である。本実施例では、各RAM9がそれぞれ4Mビットであって合計8Mビットの記憶容量を有するが、RAMの容量を変更しまたはその個数を増減することによって、前記メインメモリの記憶容量を適当に変更することができる。この記憶容量の変更は、第1サブ基板3のみを取り替えることによって、メイン基板2のモジュールをそのまま利用しつつ容易に短期間でかつ低コストで行うことができる。

【0071】図2に併せて示されるように、第1TCP5は、前記カード型コンピュータのCPU(中央処理ユニット)10をテープキャリア11の中央開口に組み込んでその表面を保護樹脂12で被覆した概ね正方形の薄形ICパッケージである。他方、第2TCP6は、前記カード型コンピュータの入出力を取り扱うIOサブシステムチップ13を同様にテープキャリア14の中央開口に組み込んで保護樹脂15で被覆した、前記第1TCPと略同一寸法・形状の薄形ICパッケージである。図2に良く示されるように、第1TCP5は、その4辺に沿って外向きに多数のアウタリード16が形成され、これをメイン基板2上面に形成された対応するランド17に後述するようにはんだ付けにより接合させることによって、電気的に接続されている。同様に、第2TCP6は、その4辺に沿って形成された多数のアウタリード18を、メイン基板2下面の対応するランド19にはんだ付けにより接合させることによって、接続されている。

【0072】ここで、メイン基板2の上下面において、ランド19とランド17とが平面的に略同じ位置に形成されているので、両TCP5、6は、その全4辺においてアウタリード16、18とランド17、19との各接合部がそれぞれ基板を挟んで略同じ位置に重なり合うように形成される。従って、第2TCP6は、基板を平面視したときに第1TCP5と略完全に重なり合うように配置される。このように第1、第2TCP5、6が、それぞれメイン基板2の上下両面に前記各接合部及び各チップ10、13を重ね合わせて搭載されることによって、基板上には、両TCP5、6の前記各チップの周囲と前記各接合部との間、即ちテープキャリアのみの部分に、配線可能な領域Aが得られる。この領域Aでは、前記接合部からTCP3、5の内向きに配線を引き出すことができ、かつスルーホールを形成することができる。

【0073】本実施例では、メイン基板2が6層からなる多層構造を有し、図示されるように内層にCPU10及びIOサブシステムチップ13に共通の電源ライン20及びグランドライン21や、様々な信号ラインが設けられている。そして、メイン基板2の領域Aには、共通の電源ライン20及びグランドライン21に接続された共通のスルーホール22、23が貫設されている。CPU10及びIOサブシステムチップ13は、それぞれ各電源端子が、前記接合部から内向きに延びる配線24、25を介して共通のスルーホール22により共通の電源ライン20に接続され、かつ各接地端子が、同様に前記接合部から内向きに延びる配線26、27及び共通のスルーホール23を介して、共通のグランドライン21に接続されている。また、前記両TCPの他の端子は、同様にスルーホールまたはビアホール(図示せず)を介して所定の信号ラインに適切に接続されている。

【0074】これに対し、2個のTCPが基板の上下面において部分的にのみ重なり合う位置関係、または全く重なり合わない互いにずれた位置関係にあるような場合には、それぞれのTCPのランドが形成された領域及びチップが位置する領域にはスルーホールを形成することができない。従って、基板全体としてスルーホールの形成に使用できない面積が大きくなるので、基板両面の面積を有効に利用することができず、基板全体の寸法が大きくなる。本発明によれば、いずれの前記TCPについても、その全4辺から接合部の内側に配線パターンを引き出し、スルーホールを設けて内層回路に接続することができるので、基板への電子部品の実装密度が高くなると共に、基板面積の有効利用が図られ、配線パターンの設計自由度が向上する。

【0075】また、上述したCPUとI/Oシステムチップの場合のように、その動作上互いに大きく関連する2個のICチップを同一基板の表裏面の略同じ位置に重なるように配置し、かつ電源との接続及び接地を共通化することによって、それらの電源電位及び接地電位を実質的に同一にすることができるので、動作の安定性が向上する。しかも、例えば電源用のスルーホール22は前記電源用リードとランドとの接合部近傍に、その他のスルーホールも対応するリードとランドとの接合部近傍に配設できるので、ICチップ間の配線長を短くすることができ、インダクタンス、インピーダンスを低下させてより一層の高速動作化を図ることができる。更に、隣接する配線間のキャパタンスが低下するので、ノイズの影響が少なくなり、誤動作の虞が解消される。

【0076】特に本実施例のカード型コンピュータでは、CPU10として米国インテル社製80386SLを、IOサブシステムチップ13として同社製82360SLをそれぞれ使用している。通常ICチップの上面には、印刷された製造者名、型番等の文字の向きを正面として、その左手前隅部に1番ピンの位置を示す小さなマークが付されているが、本実施例では、図1において、マーク28で示される80386SLの1番ピン及び82360SLの1番ピンの位置が、コネクタ8側から見てそれぞれ左手前にくるように、前記両チップを配置する。本実施例のように両チップが対応する場合には、それぞれ対称位置に関連するリードが出ていることがあり、特に多ビット(例えば16、32ビット)のバスが出ている場合には、対応するリードが共通の位置にくることが多い。本実施例では、上述したような配置によって、前記両チップの関連する多くのピンの位置をメイン基板2を挟んで対応させることができ、最低限必要なスルーホールの個数をその共通化によって大幅に少なくすることができた。これにより、スルーホールの形成に要する基板面積を約20%減少させることができた。また、同時に上下チップ間の配線長の短縮によって、動作の安定性及び信頼性の向上を図ることができた。

【0077】図3には、上記第1実施例の変形例が断面図示されている。この変形例では、メイン基板2の上面及び下面に、それぞれ搭載するCPU10及びIOサブシステムチップ13に対応する寸法のダイパッド29、30が所定位置に設けられている。前記両チップは、それぞれその下面全面が例えば銀ペースト等の熱伝導性樹脂31、32によってダイパッド29、30に接合されている。メイン基板2には、複数のサーマルビアホール33が貫設されており、これによって両ダイパッド29、30間が熱伝達可能に接続されている。前記カード型コンピュータを動作させると、CPU10が比較的高熱を発生するのに対し、IOサブシステムチップ13が発生する熱は比較的低い。このため、CPU10が発生した熱の一部は、熱伝導性樹脂層31からダイパッド29、サーマルビアホール33を介して反対側のダイパッド30に伝達され、IOサブシステムチップ13から放散される。また、サーマルビアホール33を介して伝達される熱の一部は、メイン基板2の内層回路を介して放散される。

【0078】更に、図3の実施例では、第1及び第2TCP5、6のアウタリード16、18とランド17、19との各接合部に保護のための絶縁性樹脂34、35が塗布されている。この絶縁性樹脂は熱伝導性を有するので、CPU10が発生する熱は、第1TCPのアウタリード16を通って絶縁性樹脂34から、及び第2TCPのアウタリード18を介して絶縁性樹脂35からも放散される。このように放熱面積を増大させることによって、高価な放熱フィンや液体冷却装置等の手段を使用しなくても、高発熱性の素子を高密度実装することが可能となり、同時に製造コストを低減させることができる。

【0079】図4を用いて、上記第1実施例のように2個のTCP5、6をメイン基板2の両面に実装する工程を説明する。先ず、第1TCP5をメイン基板2の上面に、図4Aに示す従来と同様の方法によって接続する。第1TCP5は、その全4辺のアウタリード16をそれぞれ対応する各ランド17と整合させて位置合せし、メイン基板2の所定位置に設置する。この基板を、少なくともランド17の領域を含むようにして、従来と同様に上面が平坦な受け台である第1受け台36上に載置する。ランド17の表面には、予めはんだ層が付着されている。

【0080】次に、第1TCP5の上方からボンディングツール37を下降させる。ボンディングツール37の底面は、その中央に矩形の凹所38を設けることによって、アウタリード16とランド17との接合部に対応する平面ロ字形の加圧部39を形成している。加圧部39は、4辺の全アウタリード16先端を一括して対応するランド17上面に押圧し、かつ同時に加熱する。第1TCP5は、メイン基板2の上面より相当突出するが、接合するアウタリード16先端を除く略全部が凹所38内に収容されるので、本加圧工程を妨げることはない。ボンディングツール37は、前記接合部が冷却した後に上昇させてアウタリード16から引き離され、それによってアウタリード16とランド17とがはんだ付けにより完全に接合される。

【0081】次に、図4Bに示すように、メイン基板2を上下反転させ、その上に第2TCP6を設置し、同様にその全4辺のアウタリード18をそれぞれ対応する各ランド19に整合させて位置合せする。この基板を受け台である第2受け台40上に載置する。第2受け台40は、上述したボンディングツール37の底面に略対応する平面ロ字形状の周辺支持部41を有し、それによってアウタリード16とランド17との前記接合部においてメイン基板2を支持する。前記接合部以外の第1TCP5の部分は、第2受け台40の上面中央の矩形凹所42内に収容される。ランド19の表面にも同様に、はんだ層が予め付着されている。

【0082】次に、ボンディングツール43を第2TCP6の上方から下降させる。ボンディングツール43は、ボンディングツール37と同様の形状を有し、平面ロ字形の加圧部44と中央凹所45とを底面に有する。第2TCP6の接合部の位置、形状、寸法が第1TCP5と同一であれば、ボンディングツール37をそのままボンディングツール43に使用してもよい。加圧部44により4辺の全アウタリード18先端を対応するランド19上面に押圧しかつ同時に加熱することによって、これらをはんだ付けにより一括接合する。このように第2受け台40とボンディングツール43とを用いて、互いに対応する平面ロ字形の周辺支持部41と加圧部44との間でメイン基板2を支持しつつ加圧することによって、先に接続されたTCPが妨げとならずに、基板の両面の略同じ位置に2個のTCPを実装することが可能になる。

【0083】上述した実施例では、略同一の大きさを有する2個のTCPを用いたが、大きさの異なる大小2個のTCPを重なり合う位置に搭載する場合には、当然ながら小さい方のTCPを先に基板に接続する。次に、大きい方のTCPを、その接続部をカバーし得る大きな受け台を使用して、基板の反対側の面に接続すればよい。

【0084】図5には、本発明を適用したプリント回路基板の第2実施例が概略的に示されている。第2実施例では、第1TCP5と第2TCP6とが、各1辺のアウタリード16、18の接合部においてのみ互いに重なり合うようにして、それぞれメイン基板2の上下両面に実装されている。何らかの理由により、基板のレイアウト上、前記両TCPを第1実施例のように同じ位置に完全に重なり合うように配置できない場合にも、一部の接合部において部分的に重なるようにすることによって、上記第1実施例と同様に基板両面の面積を有効に使用して実装密度を高くすることができる。特に、互いに重なり合う前記1辺のアウタリード16、18間では、双方の近接位置に共通のスルーホールをメイン基板2に設けることができるので、第1及び第2TCP5、6にそれぞれ搭載されている素子間の配線長を短くでき、高速動作化に対応することができる。同時に、この場合にも、隣接する配線パターンによるノイズの影響を少なくして、動作の安定性・信頼性を向上させ得ることはいうまでもない。

【0085】第2実施例のプリント回路基板は、図6に示す工程に従って、メイン基板2の両面に2個のTCP5、6を実装することができる。先ず、図6Aに示すように、第1TCP5をメイン基板2の表面上に、その全4辺のアウタリード16をそれぞれ対応するランド17に位置合せして設置する。このメイン基板2を、第1受け台46の上に載置する。第1受け台46は、その上面が、メイン基板2表面のランド17と重なり合うランド19に対応する段差部47を除いて平坦に形成され、ランド19の部分を含めてメイン基板2を裏面から有効に支持できるようになっている。次に、第1TCP5の上方からボンディングツール48を下降させる。ボンディングツール48の底面には、第1TCP5のアウタリード16に対応する平面ロ字形の加圧部49が形成されており、これにより全4辺のアウタリード16の先端を一括して対応するランド17に押圧し、かつ同時に加熱する。また、ランド17表面には予めはんだ層が形成されており、第1TCP5はメイン基板2表面にはんだ付けされる。そして、接合部が冷却した後、ボンディングツール48を上昇させてアウタリード16から引き離す。

【0086】次に、図6Bに示すように、上下反転させたメイン基板2の上に第2TCP6を、その全4辺のアウタリード18を対応するランド19に整合させて位置合せして設置する。このメイン基板2を第2受け台50上に載置する。第2受け台50は、その上面が、メイン基板2裏面のランド19と重なり合う第1TCP5の前記接合部に対応する段部51を除いて、平坦に形成され、メイン基板2が前記接合部を含めて確実に支持されるようになっている。次に、図示されるようにボンディングツール52を下降させ、その底面に設けられた平面ロ字形の加圧部53によって、アウタリード18先端を一括してランド19に押圧し、かつ同時に加熱する。ランド19表面には、同様に予めはんだ層が形成されているので、第2TCP6はメイン基板2裏面にはんだ付けされる。このようにして、第1実施例と同様に、2個のTCP5、6を基板の表裏両面に互いに部分的に重なり合うように実装することができる。

【0087】図7には、半導体装置1を所謂ICカードと同様のカード形状をなす箱体54内に収容したカード型コンピュータが示されている。箱体54は、図8に併せて示されるように、概ねコ字形をなす亜鉛・ダイカスト製またはアルミニウム・ダイカスト製の枠体55と、金属製の上面パネル56及び平坦な下面パネル57とから構成される。箱体54の長手方向の一方の側辺は、コネクタ8によって形成される。このようなカード形状の箱体は、樹脂ケースの一体構造が一般的であるが、本発明の場合、内部の基板に悪影響を及ぼす虞があるため、また本実施例では実際上枠体55が金属製のため、熱カシメできないので、両パネル56、57はねじ等を用いてまたは接着剤により枠体55に結合される。このように、箱体54の略全体が導電性材料で形成され、かつ枠体55、上面パネル56及び下面パネル57が導通した構造によって、メイン基板2及び第1サブ基板3に対する静電シールドの効果が発揮され、前記基板自体の輻射ノイズや外部のノイズの影響を遮断し、ノイズ干渉を有効に排除することができる。また、上面パネル56には、その周辺部から或一定の高さの膨出部58が形成されている。

【0088】図8に良く示されるように、半導体装置1は、フレキシブル配線板4を湾曲させて、第1サブ基板3をメイン基板2に対面させるような形態で、箱体54内に収容されている。メイン基板2は、例えばねじ等によって枠体55に固定される。メイン基板2と第1サブ基板3とは、それらの間に介装されたスペーサ部材59によって、互いに一定間隔で離隔しつつ対面状態で一体に結合されている。スペーサ部材59としては、ポリカーボネート樹脂のような或程度の可撓性を有する絶縁材料のブロックを使用し、これを接着剤等で前記両基板の対向面に、好ましくは基板中央付近の電子部品が接続されていない部分に、接着して固定することができる。このような固定方法によって、半導体装置1全体をより薄型にすることができる。また、スペーサ部材59が上述したように可撓性を有するため各基板2、3に余分な応力が作用しないので、振動や衝撃等に対してもその影響を受けることが少ない。そして、第1サブ基板3が概ね上面パネル56の膨出部58内に収まるようになっている。

【0089】本実施例では、メイン基板2の第1TCP5即ちCPU10を実装した面が第1サブ基板3に対面し、かつ第1サブ基板3のRAM9を実装した面がメイン基板2と対面するように配置されている。そして、上述したように、フレキシブル配線板4がメイン基板2のCPU10を実装した前記面に接続されることによって、メイン基板2にスルーホールをほとんど設ける必要がなく、CPU5と第1サブ基板3とを接続することができる。このため、メイン基板の面積をより小さくでき、基板の小型化を図り得ると共に、回路の設計・配線の自由度が増す。

【0090】図9に示す別の実施例では、フレキシブル配線板4が、メイン基板2の第1サブ基板3に対面する側と反対側の面に接続されている点において、図8の実施例と異なる。このため、メイン基板2の側縁には、フレキシブル配線板4を通すための切欠部60が形成されている。更に、メイン基板2には、CPU10がフレキシブル配線板4を接続した面と反対側に搭載されているので、これと接続するためのスルーホール61が設けられている。しかし、このような構成により、フレキシブル配線板4は、図3の実施例よりも大きい曲率で湾曲させることができるので、メイン基板2との接続部にかかる負担をより少なくし、該接続部における断線や破損を防止することができる。

【0091】また、別の実施例では、図8の構成において、第1TCP5と第2TCP6とを逆に配置することができる。この場合には、CPU10がメイン基板2のフレキシブル配線板4を接続した面と反対側になるので、図4の実施例と同様のスルーホールをメイン基板2に形成する必要がある。しかし、IOサブシステムチップ13に比して発熱の多いCPU10が、下面パネル57側にかつその近傍に配置されるので、該下面パネルからの放熱作用により、内部の温度上昇を抑制することができる。

【0092】更に別の実施例では、図9の構成において、第1TCP5と第2TCP6とを逆に配置することができる。この場合には、CPU10がメイン基板2のフレキシブル配線板4を接続した面と同じ側になるので、スルーホールを形成する必要がなく、かつフレキシブル配線板4の曲率が大きくなって前記接続部にかかる負担が少なくなり、しかも、CPU5が下面パネル57側に配置されるので、より高い放熱効果が得られるという利益がある。

【0093】図10及び図11には、それぞれ上述した図8及び図9の変形例が示されている。即ち、これらの実施例では、第1サブ基板3が、RAM9を実装した面と反対側の面をメイン基板2に対面させている。このため、図3及び図4の実施例に比して、装置全体の厚さが多少大きくなるが、RAM9が上面パネル56側にかつその近傍に配置されるので、該上面パネルからの放熱作用により、RAM9による内部の温度上昇を抑制することができる。また、フレキシブル配線板4の接続位置、CPU10の配置、及びそれらの位置関係による作用効果については、図8及び図9の場合と同一であるので、説明を省略する。

【0094】箱体54の上面パネル56は、絞り加工によって外向きの膨出部58を形成した金属板からなる。この金属板には、箱体54全体を所望の厚さに制限しつつ、使用時に図12に示すような外力による変形を防止するという観点から、例えばビッカース硬さ150〜250程度、厚さ約0.2mmのステンレス鋼板のような硬い材料を使用すると好都合である。特に、かかるカード状箱体54を手で取り扱う場合、外力は上面パネルの略中央に作用するが、そのために上面パネル56が多少凹むようなことがあっても、上述したスペーサ部材59が前記基板の略中央に配置されているので、変形による前記基板への影響が少ない。

【0095】膨出部58は、その立上り角度aを45〜90゜に設定すると、指で押しても容易に変形しない剛性が得られると共に、上述したように第1サブ基板3を、その寸法が記憶容量の増大によって大きくなっても、収容し得る十分なスペースが確保されるので好ましい。上面パネル56は、図示されるように膨出部58の立上り部を除いて全体が平坦に形成されているので、組立時に枠体55に対する位置決めが容易であり、組立性が向上し、作業が容易になる。また、本実施例では、膨出部58とコネクタ8との間を或程度離隔することによって、前記カード型コンピュータを装脱する際のコネクタ8の強度を向上させている。更に、上面パネル56の膨出部58内面には、第1サブ基板3との直接接触を防止するために、公知のレジスト材62が前記立上り部を含めて略全面に塗布されている。ここで、前記レジスト材は、膨出部58以外の上面パネル56内面には塗布されていないので、高温により変形や剥がれを生じる虞が無い。また、レジスト材62は、膨出部58内面の前記立上り部を除いた平面部分にのみ塗布することもできる。

【0096】図13には、第2サブ基板7の断面構造及び製造工程が示されている。本実施例において、第2サブ基板7は、厚さ1mm程度の4層構造の配線板63からなり、薄型化を図るために、電子部品を実装するための中央領域64が、予め約半分の厚さに削られている。配線板63には、厚さ0.3mm程度の更に薄いものを使用することもできる。配線板63の周縁には、メイン基板2のパッドにはんだ付けにより接続するための多数の端子65が設けられている。

【0097】先ず、図13Aに示すように、中央領域64の所定位置に例えばロジックIC、マイクロコンピュータ等の複数の電子部品66を設置し、ワイヤボンディングやはんだ付け等公知の方法により接続する。次に、図13Bに示すように、搭載した電子部品66及び中央領域64全体を覆うように、熱硬化性保護樹脂67を塗布する。これを加熱して保護樹脂67を硬化させた後冷却すると、配線板63、特にその中央領域64が肉薄で剛性に欠けるために、熱膨張率の差から、図13Cに示すように、その周辺部が上向きに反りを生じる。

【0098】このような上反りの第2サブ基板7は、メイン基板2上の所定位置に正確に設置しても、メイン基板2の僅かな動きで簡単に位置がずれてしまうため、正確かつ確実に接続することが困難である。また、所定位置に接続できたとしても、メイン基板も同様に薄型なために十分な剛性を有しない場合には、第2サブ基板7の反りに合わせて変形する虞がある。図14には、反りを生じたサブ基板をメイン基板の所定位置に正確に、かつメイン基板に変形を生じさせることなく実装し得る方法が工程順に示されている。

【0099】メイン基板2の表面には、第2サブ基板7の端子65を接続するために対応する多数のパッド68が予め形成されている。図14Aに示すように、第2サブ基板7を位置合せしつつ、その下面を接着剤69によってメイン基板2上に仮付けする。接着剤69は、前記下面の少なくとも2個所、または3個所以上に付着させるのが好ましいが、位置ずれを生じない限り1個所でも良い。従って、仮付け後に第2サブ基板7が正確に配置されていないことが判明すれば、簡単に取り外して位置決めし直すことができる。しかも、一旦正確に配置されれば、メイン基板2を動かしてもその位置が容易にずれることはない。次に、赤外線や温風を用いて例えば約230゜Cの温度で約10秒間加熱する周知のリフローはんだ付けによって、第2サブ基板7の各端子65を対応するメイン基板2のパッド68に接合する。図14Bに示すように、加熱中の前記第2サブ基板は、保護樹脂67が熱膨張して反りが解消し、平坦な状態になる。しかし、常温まで冷却すると、図14Cのように第2サブ基板7の反る力によって、メイン基板2にも反りが生じる。

【0100】次に、図14Dに示すようにメイン基板2を反転させ、その裏面上に第3サブ基板70を載置する。第3サブ基板70には、フロッピーディスクドライブ、ADコンバータ、PLL等のアナログ回路部分が搭載されている。第3サブ基板70は、第2サブ基板7と略同一の寸法・形状を有し、かつ熱硬化性保護樹脂の熱膨張率の差により上反りを生じている。逆にメイン基板2は、反転によって下向きに反っている。メイン基板2の裏面には、第2サブ基板7を実装した位置と該メイン基板を挟んで重なり合う対称位置に第3サブ基板70が実装されるように、予め多数のパッド71が形成されている。位置合せした第3サブ基板70は、同様にその下面を複数個所または位置ずれを起こさない限り1個所で接着剤72によりメイン基板裏面に仮付けする。この状態で正確に位置決めされていないことが判明すれば、第3サブ基板70は前記メイン基板裏面から取り外して、再度位置合せすることができる。そして、周知の手段により加熱して、リフローはんだ付けにより、図14Eのように第3サブ基板周縁の端子73を対応するパッド71に接合する。上述したように加熱中は第2、第3サブ基板7、70は反りが解消して平坦になるので、正確に位置決めされている限り、はんだ付けは容易に行われる。前記両サブ基板がメイン基板2の前記対称位置に接続されることによって、それらの反る力が均衡し、かつ互いに逆方向に作用することによって、メイン基板2は、常温に冷却した後も図14Eの真っ直ぐに平坦な状態に保持される。また、前記両サブ基板の大きさが異なる場合でも、概ね対称位置に実装することによって、メイン基板2の反りを抑制することができる。

【0101】第3サブ基板70の電源端子は、多数の端子73の中の1個所のみに設けられ、統一してメイン基板2のある電源ラインに接続されている。本発明のように回路基板が小型化すると、デジタル回路部分は動作が安定してくるのに対し、アナログ回路部分はノイズの影響を受け易くなる。特に、本実施例の第1サブ基板3のようなメモリ基板は、ノイズが発生し易く、電源電圧の変動を引き起こす虞があり、アナログ回路部分への影響も大きい。本発明によれば、アナログ回路部分をメイン基板2とは別個の基板として電源も統一することにより、デジタル回路部分の電源電位の変動の影響を少なくできるので、その動作を安定させることができる。また、電源を1個所にすることによって、第3サブ基板70及びメイン基板2のスペースを節約することができ、半導体装置全体を小型化できると共に、コストを低減させることができる。更に、必要に応じて、第3サブ基板70の電源回路にフィルタを付加することによって、ノイズをより確実に遮断することもできる。

【0102】図15A及びBには、本発明による半導体装置の第2実施例が示されている。この半導体装置は、図1に示す第1実施例のフレキシブル配線板4に代えて、1対のコネクタによって互いに電気的かつ機械的に着脱可能に接続される図15Aのメイン基板2′と図15Bの第1サブ基板3′とからなる。メイン基板2′は、第1実施例における第1TCP5即ちCPUが搭載されていない点、及びその上面に細長い雌型のコネクタ74が取り付けられている点を除いて、第1実施例のメイン基板2と全く同様の構成を有する。本実施例では、ベアチップのCPU75が、所謂COB(Chip on Board)方式で第1サブ基板3′上に直接接続され、かつ保護樹脂76で被覆されている。

【0103】更に第1サブ基板3′には、図15Bに示すように、CPU75と同一面上に半導体装置のメインメモリを構成する4個のRAM9′が搭載され、かつメイン基板2′の雌型コネクタ74に対応する細長い雄型のコネクタ77が取り付けられている。CPU75とRAM9′とは、第1サブ基板3′に配線されたデータバスを介して相互接続されているので、両者間の配線長を第1実施例の場合よりも短くできる。特に本実施例では、CPUに米国インテル社の80486マイクロプロセッサ(クロック周波数33MHz)を使用しているため、その性能を十分に発揮させてより高速で処理させることができるので、好都合である。

【0104】雌型コネクタ74は、メイン基板2′の上面に第2サブ基板7とは反対側の短辺に沿って配置され、かつ雄型コネクタ77を補完する長手方向に沿って細長い溝状の接続部78が上向きに開設されている。接続部78の内部には、その左右両側に例えば100ピンの接続端子79aが長手方向に沿って0.5mmの狭ピッチで配設されている。これに対して、雄型コネクタ77は、第1サブ基板3′の一方の辺縁に沿ってCPU75の近傍に配置され、その外面には、同じく左右両側に前記接続部の接続端子に対応する100ピンの接続端子79bが、長手方向に沿って0.5mmの狭ピッチで配設されている。この種のコネクタは一般に、フレキシブル配線板よりも狭ピッチで配線できるので、32ビットまたはそれ以上に信号線の数が増加しても、より小さいスペースで柔軟に対応することができる。

【0105】メイン基板2′と第1サブ基板3′とは、図16に良く示されるように、該第1サブ基板のCPU実装面を下向きに互いに対面させて、雄型コネクタ77を前記雌型コネクタの接続部78に強制的に嵌合させることによって、一体的に抜き差し可能に結合される。このとき、保護樹脂76で被覆したCPU75は、コネクタ74、77と第2サブ基板9との間の、第1実施例では第1TCP5が配設されていた空隙に、収納されるので、半導体装置全体の薄形化することができる。また、メイン基板2′と第1サブ基板3′とを、第1実施例の場合と同様に適当なスペーサ部材(図示せず)を用いることによって、一定の間隔を保持しつつ固定すると、両者間の電気的接続が確保されるので好都合である。当然ながら、前記スペース部材を用いることなく、コネクタのみによって両基板を機械的に固定することも可能である。また、各コネクタ74、77は、上記以外の様々な型式のものを使用することができ、かつ前記各基板の形状・寸法、配線等の設計条件によって、基板の中央部等上記実施例以外の様々な位置に設けることができる。

【0106】このように本発明によれば、第1サブ基板に搭載されるCPU及びメインメモリの記憶容量を適当に選択することによって、要求される様々な性能、条件等に対応した専用性を有する半導体装置を提供できるから、メイン基板は、搭載される主要なモジュールを統一して構成を共通化することができ、製造上有利である。特に上記第2実施例の場合、第1実施例の場合とはCPUのピン配列が異なり、かつCPUに接続される配線が多くなるが、このようなCPUの変更に対しても容易に対応することができる。更にメイン基板は、配線スペースが広くなることに加え、配線上CPUによる制限がないので、配線設計の自由度が高くなる利点がある。

【0107】図17乃至図20には、半導体装置1即ち前記カード型コンピュータのコネクタ8の端子の配列が示されている。図7に示されるように、コネクタ8は、その長手方向に沿って118ピン×上下2列の配列構造を有する。このように、半導体装置1が高性能化するにつれてコネクタ8はより多ピン化し、かつ小型化するにつれてピン配列がより狭ピッチ化している。このため、コネクタ8の開口80は、長手方向に沿って左右非対称な位置に形設された2個の補強用リブ81、82によって、それぞれ長さの異なる3つの開口部83〜85に分割されている。これに対応して、前記端子配列も図17の第1領域と、図18及び図19に連続して示す第2領域と、図20に示す第3領域とに3分割されている。非対称位置に設けたリブ81、82によってコネクタ8の接続方向が一義的に決定されるので、前記カード型コンピュータを機器に接続して使用する場合に、その装着方向を誤る虞が解消される。また、当然ながら、コネクタ8が本実施例のように雌型でなく雄型の場合には、前記リブの代わりに溝部を設けることによって、端子配列を分割することができる。

【0108】図17に示される第1領域には、ピン番号1〜28及び119〜146の28ピン×2列が上下平行に配列されている。この領域には、主に外部の周辺装置、即ちLCD(液晶ディスプレイ)、CRT、キーボード、マウス、フロッピディスクドライブ等に接続するためのピンが含まれる。図18及び図19の第2領域には、ピン番号29〜83及び147〜201の55ピン×2列が配列され、例えばシリアルインタフェース、パワーマネージメント、ATバス等に関係するピンが含まれる。図20の第3領域には、ピン番号84〜118及び202〜236の35ピン×2列が配列され、例えばシリアルインタフェース、パラレルインタフェース、ハードディスクドライブ、パワーマネージメント等に関係するピンが含まれている。これらのピンに割り当てられた信号の出力は、3.3Vまたは5Vである。このように比較的低い出力では、外部のノイズや回路内の輻射ノイズの影響を排除して信号出力を安定させることが重要である。

【0109】図17に示されるように、ピン番号121に割り当てられたLCDインタフェースのフラットパネル用データシフトクロック信号(FPDOTCLK)がピン番号120の接地ライン(GND)に隣接して配置されている。このFPDOTCLKは、フラットパネルに表示を行うための制御信号の一つで、表示用データのシフトを行うクロック信号である。これを接地ラインに隣接させることによって、その電位が安定するので、LCDの表示を安定させることができる。

【0110】また、図17のピン番号15〜17には、CRTインタフェース用信号としてCRT用RGB信号の青色(BLUE)、緑色(GREEN)、赤色(RED)信号がそれぞれ割り当てられている。そして、これらのピン番号15〜17に平行なピン配列の対向する位置に設けられたピン番号133〜135に、前記各青色、緑色、赤色信号に対するリターン信号(BRTN、GRTN、RRTN)がそれぞれ割り当てられている。このように、アナログ信号であるCRT用のR、G、B各カラー信号を出力側とリターン側とで、できる限り同一条件にすることによって、外部ノイズ等が打ち消し合ってその影響を受け難くなるので、CRTの表示を高品位にしかつ維持することができる。

【0111】以上、本発明の好適な実施例について詳細に説明したが、当業者に明らかなように、本発明はその技術的範囲内において上述した各実施例に様々な変形・変更を加えて実施することができる。例えば、上記第1実施例のメイン基板と第1サブ基板とを第2実施例のコネクタによって接続することができ、逆に第2実施例のメイン基板と第1サブ基板とをフレキシブル配線板によって接続することもできる。また、TCPを配線板に接続する方法として、はんだ付け以外に熱圧着によるリードとランドとの合金化や、シート状の異方性導電膜を用いる方法、光硬化性絶縁樹脂を用いる方法等、公知の様々な方法を用いることができる。更に、本発明は、TCPと同様にリードを有する、例えばQFPのような他のパッケージ型電子部品を実装する場合にも、同様に適用することができる。

【0112】

【発明の効果】本発明は、以上のように構成されているので、以下に記載されるような効果を奏する。

【0113】本発明の半導体装置によれば、請求項1記載のように構成することによって、サブ基板を取り替えるだけで記憶容量を簡単に変更することができるので、汎用性のあるメイン基板を同一にして、記憶容量の異なる多数の機種を容易に短期間でかつ低コストで製造することができる。しかも、技術の進歩や使用条件の変更等により記憶容量を変更する必要が生じた場合にも、簡単に切り換えができ、かつメイン基板をそのまま利用して低コストで対応することができる。特にCPUをメモリと共にサブ基板に搭載した場合には、メイン基板の共通化が図られ、かつ配線設計の自由度が向上し、製造が容易になってコストを低減化できる。更に、半導体装置の基本的性能を維持しつつ要求される特定の性能・目的に応じてCPU及びメモリを容易に設計変更できるから、半導体装置の専用性を低コストで実現することができる。

【0114】これに加え、本発明によれば、対面配置させたメイン基板とサブ基板とを一体的に固定することによって、フレキシブル配線板またはコネクタにかかる負担を少なくして、振動や衝撃等の外力に対する耐久性を向上させ、装置全体の小型化・薄型化を図ることができ、更に、これらを収容するカード状箱体の一側面を絞り加工した金属板で形成することによって、使用時の不測の取扱いに対して十分な剛性を持たせ、より一層の薄型化を達成することができる。

【0115】更に、本発明によれば、外部のLCDに接続されるドットクロック信号用端子を接地端子に隣接させ、また外部のCRTに接続されるR、G、B信号用各端子の配列を対応するR、G、Bリターン信号用端子の配列と対称に配置することによって、装置全体の小型化及び消費電力の省力化により外部から受ける電磁的な影響を少なくして画像出力を安定させ、LCD、CRTにおける表示を高品質に維持して、動作の安定性・信頼性を向上させることができる。

【0116】また、請求項13記載の本発明の半導体装置によれば、異なる電子部品を搭載したサブ基板を適当に選択することによって、異なる機能、使用条件にそれぞれ対応して多種類の半導体装置を比較的簡単に短期間でかつ低コストで製造することができ、しかも、薄型化した基板に生じ易い反りによる変形を有効に防止して、基板の薄型化を可能にし、半導体装置全体をより小型化・薄型化することができる。

【0117】請求項13記載の本発明の半導体装置の製造方法によれば、電子部品を搭載したサブ基板が、薄型化により反りを生じた場合でも、メイン基板上に正確に位置決めして接続できるので、歩留りが向上し、従来の工程を大幅に変更したり手間やコストを増加させることなく、半導体装置を製造することができる。

【0118】また、請求項15記載の半導体装置によれば、プリント基板の両面において、それぞれICパッケージのリードとプリント基板上のランドとの接合部が互いに重なり合う部分の大きさに応じて、基板面積を小さくできるので、実装密度を高くすることができ、基板両面の面積を有効に利用して回路の設計上自由度が増すと共に、半導体装置及びこれを搭載する機器の小型化を達成することができる。これに加え、特に動作上関連のあるICパッケージを重なり合うように配置すれば、共通のスルーホールを使用することにより、より一層基板面積の有効利用が図られ、高密度実装が可能になると共に、それらの間の配線長を短縮できるので、動作を高速化でき、かつ誤動作を解消して動作の安定性・信頼性の向上を図ることができる。

【0119】更に、請求項21記載の半導体装置によれば、プリント基板の両面に重なり合うように配置された一方のICパッケージから発生する熱が、プリント基板に設けたサーマルビアを介して他方のICパッケージに伝達されるので、高価な放熱手段や冷却装置を用いることなく比較的簡単な方法により、放熱面積を実質的に増大させることができ、低コストで小型化に適した放熱構造が得られる。

【0120】また、請求項23記載の半導体装置の製造方法によれば、プリント基板を支持する受け台の形状に変更を加えるだけで、従来の実装工程に大幅な変更を加えることなく、複数のICパッケージをプリント基板の両面に重なり合うように実装することができ、上述したように、高密度実装、動作の高速化、動作の安定性・信頼性の向上に適した半導体装置を比較的簡単にかつ低コストで実現することができる。

【図面の簡単な説明】

【図1】本発明を適用したカード型コンピュータ用の半導体装置の第1実施例を概略的に示す斜視図である。

【図2】図1のII−II線に於ける断面図である。

【図3】第1実施例の変形例を示す図2と同様の断面図である。

【図4】第1実施例の実装工程を示す断面図である。

【図5】本発明の第2実施例を示す断面図である。

【図6】第2実施例の実装工程を示す断面図である。

【図7】第1実施例の半導体装置を収容したカード形状の箱体を示す斜視図である。

【図8】メイン基板と第1サブ基板との接続構造を示す図7のVIII−VIII線における断面図である。

【図9】メイン基板と第1サブ基板との接続構造の別の実施例を示す断面図である。

【図10】メイン基板と第1サブ基板との接続構造の更に別の実施例を示す断面図である。

【図11】メイン基板と第1サブ基板との接続構造の更に別の実施例を示す断面図である。

【図12】カード形状の箱体の構造を説明するための断面図である。

【図13】第2サブ基板の製造工程を順に示す図A乃至図Cからなる断面図である。

【図14】第2及び第3サブ基板をメイン基板の両面に接続する工程を順に示す図A乃至図Eからなる図である。

【図15】図A及び図Bからなり、それぞれ本発明による半導体装置の第2実施例のメイン基板と第1サブ基板とを概略的に示す斜視図である。

【図16】第2実施例のメイン基板と第1サブ基板とを接続した状態を示す部分拡大図である。

【図17】コネクタのリブで分割された第1部分の端子配列を示す図である。

【図18】コネクタのリブで分割された第2部分の半分の端子配列を示す図である。

【図19】図18に示す第2部分の残りの半分の端子配列を示す図である。

【図20】コネクタのリブで分割された第3部分の端子配列を示す図である。

【図21】従来の半導体装置に於ける両面実装を示す断面図である。

【符号の説明】

1 半導体装置

2 メイン基板

3 第1サブ基板

4 フレキシブル配線板

5 第1TCP

6 第2TCP

7 第2サブ基板

8 コネクタ

9 RAM

10 CPU

11 テープキャリア

12 保護樹脂

13 IOサブシステムチップ1

14 テープキャリア

15 保護樹脂

16 アウタリード

17 ランド

18 アウタリード

19 ランド

20 電源ライン

21 グランドライン

22、23 スルーホール

24〜27 配線

28 マーク

29、30 ダイパッド

31、32 熱伝導性樹脂

33 サーマルビアホール

34、35 絶縁性樹脂

36 第1受け台

37 ボンディングツール

38 凹所

39 加圧部

40 第2受け台

41 周辺支持部

42 凹所

43 ボンディングツール

44 加圧部

45 凹所

46 第1受け台

47 段差部

48 ボンディングツール

49 加圧部

50 第2受け台

51 段部

52 ボンディングツール

53 加圧部

54 箱体

55 枠体

56 上面パネル

57 下面パネル

58 膨出部

59 スペーサ部材

60 切欠部

61 スルーホール

62 レジスト材

63 配線板

64 中央領域

65 端子

66 電子部品

67 熱硬化性保護樹脂

68 パッド

69 接着剤

70 第3サブ基板

71 パッド

72 接着剤

73 端子

74 雌型コネクタ

75 CPU

76 保護樹脂

77 雄型コネクタ

78 接続部

79 接続端子

80 開口

81、82 補強用リブ

83〜85 開口部

86 プリント基板

87 TCP

88 ボンディングツール

89 アウタリード

90 ランド

91 受け台

92 TCP

【0001】

【産業上の利用分野】本発明は、プリント基板にICチップやLSI等の電子部品を搭載した半導体装置の構造及び製造方法に関し、例えばCPU、周辺装置制御用IC等を搭載したカード形状の小型コンピュータとして、様々な産業用機器及び民生用機器に組み込んで使用することができる。

【0002】

【従来の技術】従来より、マイクロコンピュータ技術の発達に伴い、自動工作機械、自動車、医療用・工業用の各種制御システムや自動販売機、自動現金支払機等の様々な産業用機器に加え、通信機器、オーディオ・ビデオ機器等の民生用機器の分野においても、コンピュータを用いた電子制御システムが広く採用されている。これらの機器に内蔵されるコンピュータシステムは、一般に専用性の高いものであり、各機器の用途、機能、デザインや周辺機器等の様々な使用条件に基づいて、それぞれ最適に設計・製造して使用される。このため、システムの開発や製造に相当の手間及び時間を要し、コストが増大するという問題があった。一方、コンピュータシステムのアーキテクチャは、例えばIBM社のPC−AT等のように特定のものが実質的な標準となっており、これに対応した周辺機器であれば、共通に利用できる場合が多い。

【0003】そこで、本願出願人による特願平5−278643号明細書に記載されるように、機器に組み込むコンピュータシステムをコンパクトなカード形状の箱体に収容してユニット化することによって、形状・構造の汎用化を図り、それにより機器毎にシステムを開発し、設計・製造するのに要する手間や労力を少なくし、コストを低減させ得る電子装置が提案されている。このような電子装置は、通例CPU(中央処理ユニット)、メモリや入出力・周辺機器制御用のIC等をプリント回路基板に実装することによって構成される。そして、プリント回路基板及びそれを収容するカード状箱体の寸法・形状等を統一することによって、ハードウェア上の汎用性を得ることができる。

【0004】他方、各種電子機器について小型・軽量・薄型化、高性能化が急速に進められ、特にコンピュータの分野では、情報量の大幅な増加に伴い情報処理の高速化が要求されている。このため、回路規模の増大、使用する電子部品の増加に対応して高密度化、高速化を図るべく、プリント基板の薄板化及びファインパターン化、多層構造の採用、電子部品の小型化等と共に、電子部品を接続するための様々な実装技術が開発されている。例えば、リフローはんだ付けによるQFP等のICパッケージの表面実装や、COBやTAB型式によるICのベアチップ実装が広く採用されている。

【0005】特にTAB型式によるTCPは、電極数やリード数に無関係に一回の動作で一括接続できるので量産性に優れ、しかもリードピッチを狭小化し、大型チップで多ピンに対応し得る特徴を有することから、高密度実装化に適している。一般にTCPをプリント基板に実装する場合、図21に示すように、プリント基板86の上に接続しようとするTCP87を載置し、その上方からボンディングツール88を用いて前記TCPのアウタリード89をプリント基板86上のランド90に加圧しかつ場合により同時に加熱して、はんだ付けや熱圧着等により接続する方法が行われている。このとき、ボンディングツールは約10kgf程度の加圧力をもって接合部を押圧するから、プリント基板は、上面の平坦な受け台91の上に載せて裏面から十分に支持する必要がある。

【0006】

【発明が解決しようとする課題】しかしながら、上述したようにユニット化された電子装置を用いてコンピュータシステムを設計・製造する場合、それを組み込む機器や設備の要求する機能、使用条件に応じて、それに搭載する半導体装置の動作速度、記憶容量等の性能を個々に適当に設定する必要がある。また、例えば自動工作機械の制御システム等の場合には、加工する対象や加工条件の変更に応じて、または使用する機種の変更に対応して、記憶されているデータを書き換える必要が生じる。このため、特に技術の進歩に対して記憶容量を切り換えるだけで対応し得る場合でも、プリント回路基板を設計し直したり基板全体を交換することになれば、ユニット化による汎用性の利益が十分に得られなくなる。

【0007】また、上述した従来の実装方法では、複数のTCPをプリント基板の両面に搭載しようとする場合、先に一方の面に実装した後にプリント基板を裏返して他方の面を実装することになるが、プリント基板8692先に接続されているTCP92を避けて受け台91に載せなければならない。このため、後から裏面に接続しようとするTCP87は、プリント基板を平面視したときに表面のTCP92と重なる位置に配置することができなかった。この結果、基板両面の面積を有効に利用することができないので、半導体装置の小型化が困難になり、十分に高密度化を図れないという問題があった。

【0008】特に、多層構造のプリント基板を用いる場合には、通例スルーホールを設けてTCPの電極端子を内層回路の配線に接続するが、上述した従来の実装方法では、動作上相互に関連する複数のICを互いに近接した位置に配置するには限界がある。このようなICが離れた位置に搭載され、それぞれ別個に設けたスルーホールを介して電源ライン、グランドラインに接続されると、搭載される位置や配線によってIC間の電源電位、接地電位に好ましくない差異や変動が生じ、そのために動作の安定性が損なわれる虞がある。しかも、スルーホールの数が多くなると、そのために使用される基板の面積が大きくなるから、基板及び半導体装置の小型化が一層困難になり、電子機器の小型化に十分対応することができない。また、配線長が必要以上に長くなって、所望の高速動作が期待できなくなる。

【0009】更に、基板の高密度実装化が進められると、搭載された各ICから発生する熱が多くなるので、これを効率よく放散させることが、基板の耐久性確保、動作の安定性等の観点から非常に重要である。そのために、従来使用されている放熱フィンやヒートシンク等の放熱手段または液体冷却装置等を使用すれば、コストが増大するだけでなく、基板全体の寸法が大きくなって、半導体装置及びこれを搭載する機器の小型化が一層困難になる。

【0010】そこで、本発明の半導体装置は、上述した問題点に鑑みてなされたものであり、その目的とするところは、装置の基本的な構成をユニット化することにより十分な汎用性を確保してコストの低減を図りつつ、異なる機能、使用条件に容易にかつ短期間で対応できる専用性を備え、特に記憶容量を容易に切り換えることができる半導体装置を提供することにある。

【0011】これに加え、装置全体のユニット化、コンパクト化に対応して、プリント回路基板の小型化・薄型化が要求されている。特にベアのICチップを用いて高密度に接続した基板にICチップ保護のための熱硬化性保護樹脂を塗布した場合、その硬化後に基板に反りが生じる等変形する虞がある。そこで、本発明の目的は、薄型基板において変形し難い構造の半導体装置を提供することにある。

【0012】また、装置全体の小型化・薄型化に伴い、現場での取扱いに対して十分な強度・耐久性を確保しなければならない。そこで、本発明の別の目的は、装置全体のコンパクト化を実現できると共に、十分な強度・耐久性を有する構造の半導体装置を提供することにある。

【0013】また、コンピュータシステムとして小型化及び高性能化が進むにつれて、基板の高密度実装化、ファインパターン化が促進され、消費電力も省力化されて少なくなる。このため、外部のノイズや回路自体の輻射ノイズの影響を受け易くなり、特にフロッピーディスクドライブ、ADコンバータ、PLL等のアナログ回路部分は、デジタル回路部分における電源電位の変動が影響して動作が不安定になる虞がある。そこで、本発明の更に別の目的は、特にアナログ部分において、ノイズの影響を少なくして誤動作の虞を解消し、動作の安定性・信頼性を確保し得る半導体装置を提供することにある。

【0014】更に、本発明の半導体装置の製造方法は、上述した汎用性と専用性との双方を備える半導体装置を、従来の工程に大幅な変更を加えたりコストを増大させることなく比較的容易に製造する方法を提供することを目的とする。

【0015】また、本発明の半導体装置は、プリント基板の両面に実装される複数のパッケージ型IC部品を、該プリント基板を挟んで互いに重なり合うように配置できるようにし、それにより基板面積の有効な利用を可能にして回路設計の自由度を増大させることができ、高密度実装化、小型化に適した半導体装置を提供することを目的とする。

【0016】これに加え、本発明の目的は、特に動作上関連が大きいICチップ間の配線長を短縮して、動作の高速化及び安定性・信頼性の向上を図ることができる半導体装置を提供することにある。

【0017】更に、本発明の半導体装置は、複数のパッケージ型IC部品をプリント基板の両面に重なり合うように配置できることに加えて、ICチップが発生する熱を、高価な放熱手段や冷却装置を用いることなく、比較的簡単な方法により効果的に放散させることができ、かつ低コストで小型化に対応し得る放熱構造を備えた半導体装置の提供を目的とする。

【0018】また、本発明の半導体装置の製造方法は、複数のパッケージ型IC部品をプリント基板の両面に重なり合うように配置した半導体装置を、従来の実装工程に大幅な変更を加えることなく、比較的簡単にかつ低コストで実現し得る方法の提供を目的とする。

【0019】

【課題を解決するための手段】本発明は、上述した目的を達成するためのものであり、以下にその内容を図面に示した実施例を用いて説明する。

【0020】請求項1記載の半導体装置は、基板に搭載されたCPUと入出力装置とメモリとを備え、該基板がメイン基板とそれに電気的に接続されたサブ基板とからなり、かつメモリが、サブ基板に搭載されたメモリ素子からなることを特徴とする。

【0021】請求項2記載の半導体装置は、上述した請求項1の特徴点に加え、CPUがメイン基板に搭載されていることを特徴とする。

【0022】これに対し、請求項3記載の半導体装置は、CPUがサブ基板に搭載されていることを特徴とする。

【0023】請求項4記載の半導体装置は、メイン基板とサブ基板とが、フレキシブル配線板を介して接続されていることを特徴とする。

【0024】これに対し、請求項5記載の半導体装置は、メイン基板とサブ基板とが、互いに対面するように1対のコネクタによって着脱可能に接続されていることを特徴とする。

【0025】請求項6記載の半導体装置は、上述した請求項4の特徴点に加え、フレキシブル配線板を湾曲させることにより、サブ基板がメイン基板と対面するように配置され、かつフレキシブル配線板が、メイン基板のサブ基板と対面する面と反対側の面に接続されていることを特徴とする。

【0026】更に請求項7記載の半導体装置は、互いに対面させたメイン基板とサブ基板とを一体的に固定するための手段を備えることを特徴とする。

【0027】請求項8記載の半導体装置は、上述した請求項1の特徴点に加え、メイン基板とサブ基板とを収容するためのカード形状の薄い箱体を備え、箱体の少なくとも一方の面が、絞り加工により外向きに膨出させた金属板からなることを特徴とする。

【0028】請求項9記載の半導体装置は、外部装置に接続するために多数の端子を配列したコネクタを更に備え、外部の液晶ディスプレイ装置(LCD)に接続されるドットクロック信号用端子が、接地端子に隣接して配置されていることを特徴とする。

【0029】請求項10記載の半導体装置は、同様に外部装置に接続するために多数の端子を複数の列に配列したコネクタを更に備えるが、外部のCRTに接続されるR、G、B信号用各端子の列が、それぞれ対応するR、G、Bリターン信号用各端子の列と平行をなし、かつ各端子が互いに対向する位置に配置されていることを特徴とする。

【0030】請求項11記載の半導体装置は、同じく外部装置に接続するために多数の端子を配列したコネクタを更に備え、該コネクタが、端子の列をその配列方向にみて左右非対称に分割するための手段を有することを特徴とする。

【0031】請求項12記載の半導体装置は、そのアナログ回路部分が、メイン基板に実装される第2のサブ基板に搭載され、かつ第2のサブ基板の電源端子が、1個所でメイン基板に接続されていることを特徴とする。

【0032】本発明の別の側面によれば、請求項13記載の半導体装置は、複数の電子部品を実装するための基板がメイン基板と電子部品をそれぞれ搭載した複数のサブ基板とからなり、少なくともいずれか2個のサブ基板が、メイン基板の両面に該基板を挟んで互いに重なり合う対称位置に実装されていることを特徴とする。

【0033】更に本発明の別の側面によれば、請求項14記載の半導体装置の製造方法は、電子部品をサブ基板に実装する過程と、このサブ基板をメイン基板上の所定位置に設置し、取外可能に仮付けした後にメイン基板に接続する過程とからなることを特徴とする。

【0034】また、請求項15記載の半導体装置は、第1ICパッケージと第2ICパッケージとをそれぞれプリント基板の第1及び第2面に実装した両面実装型であって、第1面上に形成されたランドと第1ICパッケージのリードとの接合部と、第2面上に形成されたランドと第2ICパッケージのリードとの接合部とが、互いにプリント基板を挟んで重なるように、第1及び第2ICパッケージをそれぞれ配置したことを特徴とする。

【0035】請求項16記載の半導体装置は、上述した請求項15の特徴点に加え、第1及び第2ICパッケージのリードと第1及び第2ランドとの各接合部が、互いに各ICパッケージのいずれか1辺において互いに重なり合うようにしたことを特徴とする。

【0036】また、請求項17によれば、上述した請求項15の特徴点に加えて、第1及び第2ICパッケージのリードと第1及び第2ランドとの各接合部が、互いに各ICパッケージの全4辺において重なり合うようにしたことを特徴とする半導体装置が提供される。

【0037】請求項18記載の半導体装置は、第1及び第2ICパッケージがその動作上相互に関連するICチップを搭載していることを特徴とし、更に、請求項19記載の発明によれば、第1ICパッケージがCPUを搭載し、かつ第2ICパッケージがこのCPUに対応して動作するI/Oシステムを搭載した半導体装置が提供される。

【0038】請求項20記載の発明によれば、これらの半導体装置において、少なくとも第1または第2ICパッケージがTCPからなる。

【0039】本発明の別の側面によれば、請求項21記載の半導体装置は、第1ICパッケージ及び第2ICパッケージが、プリント基板の各面に互いに該プリント基板を挟んで重なり合う位置に、それぞれダイボンディングによって接合され、かつプリント基板に貫設されたサーマルビアを介して互いに熱伝達可能に接続されていることを特徴とする。

【0040】請求項22記載の半導体装置は、上述した請求項21の特徴点に加え、プリント基板の各面に接続された第1または第2ICパッケージのリードを熱伝導性樹脂で被覆したことを特徴とする。

【0041】本発明の更に別の側面によれば、請求項23記載の半導体装置の製造方法は、複数のICパッケージをプリント基板の両面に、該プリント基板を挟んで互いに重なり合うように実装するための方法であって、先ず第1ICパッケージをプリント基板の第1面上に配置して、そのリードを第1ランドに接合することにより接続し、このプリント基板を反転させて、第1ICパッケージの接合部が支持されるように受け台の上に載置した後、第2ICパッケージをプリント基板の第2面上に、そのリードと第2面のランドとの接合部が第1ICパッケージの接合部と互いにプリント基板を挟んで重なり合うように配置し、受け台に対応する加圧手段を用いて第2ICパッケージのリードと第2ランドとを加圧することにより接合することを特徴とする。

【0042】請求項24記載の半導体装置の製造方法は、上述した請求項23の特徴点に加え、加圧手段により加圧する際に加熱し、はんだ付けによって第2ICパッケージのリードを第2ランドに接合することを特徴とする。

【0043】また、請求項25記載の半導体装置の製造方法は、上述した請求項23の特徴点に加え、加圧手段により加圧する際に加熱し、熱圧着によって第2ICパッケージのリードを第2ランドに接合することを特徴とする。

【0044】これに対し、請求項26記載の半導体装置の製造方法は、加圧手段により加圧する際に加熱し、異方性導電膜を用いて第2ICパッケージのリードを第2ランドに接合することを特徴とする。

【0045】請求項27記載の半導体装置の製造方法は、加圧手段により加圧する際に光を照射し、光硬化性樹脂を用いて第2ICパッケージのリードを第2ランドに接合することを特徴とする。

【0046】

【作用】従って、請求項1記載の半導体装置によれば、メイン基板に搭載された主要なモジュールはそのまま維持しつつ、サブ基板を取り替えるだけで、組み込む機器の機種や使用条件の変更に応じて、少なくとも記憶容量を簡単に切り換えることができる。

【0047】請求項2記載の半導体装置によれば、メイン基板の性能を維持しつつ、サブ基板を取り替えることで、半導体装置の記憶容量のみを必要に応じて容易に変更することができる。

【0048】請求項3記載の半導体装置によれば、メイン基板の基本的構成を共通化し、サブ基板を取り替えることで、半導体装置の性能及び記憶容量を必要に応じて容易に変更することができる。

【0049】請求項4記載の半導体装置によれば、フレキシブル配線板によって安価にかつ簡単に両基板を接続することができる。

【0050】請求項5記載の半導体装置によれば、コネクタによって多数の接続端子を狭ピッチで配設することができ、サブ基板に搭載されるメモリ及び/またはCPUの変更により配線が増加しても、比較的容易に対応することができる。

【0051】請求項6記載の半導体装置によれば、フレキシブル配線板をより大きな曲率で湾曲させることができる。

【0052】請求項7記載の半導体装置によれば、使用時に、例えば振動等により両基板が相対的に動かないように固定することができ、フレキシブル配線板やコネクタに不要な応力が加わらないようにして電気的接続を確保することができる。

【0053】請求項8記載の半導体装置によれば、金属板を外向きに膨出させることによって、カード形状をなす薄型の箱体に、その厚さ方向に容易に変形し難い十分な剛性を与えることができる。

【0054】請求項9記載の半導体装置によれば、外部のLCDに出力されるドットクロック用信号が安定するので、LCDによる表示を安定させることができる。

【0055】請求項10記載の半導体装置によれば、外部のCRTに出力されるアナログ信号であるR、G、B各信号を、出力側とリターン側とにおいて略同一条件にし、外部からのノイズ等の影響を少なくして、CRTによる表示を安定させることができる。

【0056】請求項11記載の半導体装置によれば、コネクタの接続に方向性を持たせることができるので、装着しようとする機器に対してコネクタを誤った向きに接続することがない。

【0057】請求項12記載の半導体装置によれば、半導体装置のアナログ回路部分を、デジタル回路部分とは別基板にして、その電源を1個所に統一することによって、デジタル回路部分における電源電位の変動による影響を少なくし、かつ基板のスペースを節約することができる。

【0058】請求項13記載の半導体装置によれば、複数のサブ基板にそれぞれ異なる電子部品を搭載し、これらを適当に選択してメイン基板に実装することによって、寸法・形状が同一で機能の異なる半導体装置を得ることができる。しかも、サブ基板が薄型化によって反りを生じても、そのような2個のサブ基板をメイン基板の両面に対称位置に接続することによって、メイン基板の変形を防止することができる。

【0059】請求項14記載の半導体装置の製造方法によれば、薄型化により反りを生じた場合でも、サブ基板を確実に位置決めしてメイン基板に接続することができる。

【0060】従って、請求項15記載の半導体装置によれば、プリント基板の両面に実装された複数のICパッケージの接合部が、プリント基板を挟んで互いに重なり合うことにより、この重なり合う部分の面積だけ基板の実装面積を小さくし、かつ基板両面の面積を有効に利用することができる。また、互いに重なり合う接合部同士においては、ICパッケージ間の配線距離を短くすることができる。

【0061】そして、請求項16記載の半導体装置によれば、ICパッケージの1辺において重なり合う接合部の部分だけ基板の実装面積を減少させることができ、更に、請求項17記載の半導体装置によれば、ICパッケージ同士が全体的に重なり合うように配置されることによって、基板の実装面積を大幅に減少させることができる。

【0062】また、請求項18記載の半導体装置によれば、各ICパッケージの例えば電源用、接地用の対応するリード同士が近接した位置に配置されるので、ICパッケージ間の配線長を短くでき、更にスルーホールを共通化することができる。特に、請求項19記載の半導体装置によれば、共有し得る信号線、アドレス線等が多いので、スルーホールの共通化によってその必要な数を大幅に減少させることができる。

【0063】更に、請求項20記載の半導体装置によれば、特にTCPの場合に、そのアウタリードとTCPに搭載したIC部品間のキャリアテープの領域において、プリント基板上では、リードとの接合部から内向きに配線を引き出し、かつスルーホールを形成することができる。

【0064】また、請求項21記載の半導体装置によれば、第1ICパッケージまたは第2ICパッケージの一方からより多く発生する熱の一部が、発熱のより少ない他方のICパッケージにサーマルビアを介して伝達されかつ放散されるので、放熱面積を実質的に増大させることができる。

【0065】更に請求項22記載の半導体装置によれば、接合部のリードを被覆する熱伝導性樹脂からも、該リードを介して伝達されるICパッケージの熱を放散させることができる。

【0066】また、請求項23記載の半導体装置の製造方法によれば、従来の実装工程と同様に、プリント基板を支持する受け台と接合部を加圧する加圧手段とを用いて、先にプリント基板の第1面に接続された第1ICパッケージと互いに重なり合うように、第2ICパッケージをプリント基板の第2面に接続することができる。

【0067】更に、請求項24乃至請求項27記載の製造方法によれば、従来より公知のはんだ付け、熱圧着、異方性導電膜、光硬化性樹脂を用いて、比較的容易に第2ICパッケージをプリント基板の第2面に、第1面に接続された第1ICパッケージと互いに重なり合うように接続することができる。

【0068】

【実施例】図1は、本発明を適用した半導体装置の第1実施例を概略的に示している。この半導体装置1は、所謂ICカードやメモリカード等と略同一形状をなすカード型の小型コンピュータとして使用され、セラミック材料またはガラスエポキシ材料を基材とする2枚のプリント回路基板、即ち両面実装用の多層構造を有するメイン基板2と、それより小形の第1サブ基板3とからなる。これらの基板は、それぞれ長手方向の一辺にはんだ付けされたフレキシブル配線板4によって電気的に接続されている。メイン基板2には、第1TCP(Tape Carrier Package)5がフレキシブル配線板4を接続した面上に接続され、かつ反対側の面には、第2TCP6がメイン基板2を挟んで第1TCP5と重なる対称位置に、互いに全4辺の接続部が重なり合うように接続されている。

【0069】また、メイン基板2の両面には、後述するように薄型配線板に電子部品を予め実装した第2サブ基板7及び第3サブ基板(図示せず)が、それぞれ前記TCPの側方に互いにメイン基板2を挟んで重なり合う対称位置に接続されている。これら第2、第3サブ基板は、半導体装置1の異なる機能に対応して異なる電子部品を搭載した複数の異なるパッケージを予め用意することができる。そして、このパッケージされたサブ基板を適当に選択して組み合わせることによって、機能・用途の異なる多種類の半導体装置1を簡単に短期間でかつ低コストで設計・製造することができる。また、前記第2または第3サブ基板を別のパッケージと取り替えることによって、比較的容易に仕様の変更を実現することができる。更に、メイン基板2には、上述した電子部品以外に、図示されていないがコンピュータシステムとしてメインメモリを除く主要なモジュールを構成するために必要な電子部品類が搭載されている。また、メイン基板2のフレキシブル配線板4を接続した側と反対側の長辺に沿って、外部の装置に接続するためのコネクタ8が設けられている。

【0070】他方、第1サブ基板3には、半導体装置1のメインメモリを構成するメモリ素子として、2個のRAM9が実装されている。このため、フレキシブル配線板4は、メイン基板2の第1TCP5近傍に接続すると好都合である。本実施例では、各RAM9がそれぞれ4Mビットであって合計8Mビットの記憶容量を有するが、RAMの容量を変更しまたはその個数を増減することによって、前記メインメモリの記憶容量を適当に変更することができる。この記憶容量の変更は、第1サブ基板3のみを取り替えることによって、メイン基板2のモジュールをそのまま利用しつつ容易に短期間でかつ低コストで行うことができる。

【0071】図2に併せて示されるように、第1TCP5は、前記カード型コンピュータのCPU(中央処理ユニット)10をテープキャリア11の中央開口に組み込んでその表面を保護樹脂12で被覆した概ね正方形の薄形ICパッケージである。他方、第2TCP6は、前記カード型コンピュータの入出力を取り扱うIOサブシステムチップ13を同様にテープキャリア14の中央開口に組み込んで保護樹脂15で被覆した、前記第1TCPと略同一寸法・形状の薄形ICパッケージである。図2に良く示されるように、第1TCP5は、その4辺に沿って外向きに多数のアウタリード16が形成され、これをメイン基板2上面に形成された対応するランド17に後述するようにはんだ付けにより接合させることによって、電気的に接続されている。同様に、第2TCP6は、その4辺に沿って形成された多数のアウタリード18を、メイン基板2下面の対応するランド19にはんだ付けにより接合させることによって、接続されている。

【0072】ここで、メイン基板2の上下面において、ランド19とランド17とが平面的に略同じ位置に形成されているので、両TCP5、6は、その全4辺においてアウタリード16、18とランド17、19との各接合部がそれぞれ基板を挟んで略同じ位置に重なり合うように形成される。従って、第2TCP6は、基板を平面視したときに第1TCP5と略完全に重なり合うように配置される。このように第1、第2TCP5、6が、それぞれメイン基板2の上下両面に前記各接合部及び各チップ10、13を重ね合わせて搭載されることによって、基板上には、両TCP5、6の前記各チップの周囲と前記各接合部との間、即ちテープキャリアのみの部分に、配線可能な領域Aが得られる。この領域Aでは、前記接合部からTCP3、5の内向きに配線を引き出すことができ、かつスルーホールを形成することができる。

【0073】本実施例では、メイン基板2が6層からなる多層構造を有し、図示されるように内層にCPU10及びIOサブシステムチップ13に共通の電源ライン20及びグランドライン21や、様々な信号ラインが設けられている。そして、メイン基板2の領域Aには、共通の電源ライン20及びグランドライン21に接続された共通のスルーホール22、23が貫設されている。CPU10及びIOサブシステムチップ13は、それぞれ各電源端子が、前記接合部から内向きに延びる配線24、25を介して共通のスルーホール22により共通の電源ライン20に接続され、かつ各接地端子が、同様に前記接合部から内向きに延びる配線26、27及び共通のスルーホール23を介して、共通のグランドライン21に接続されている。また、前記両TCPの他の端子は、同様にスルーホールまたはビアホール(図示せず)を介して所定の信号ラインに適切に接続されている。

【0074】これに対し、2個のTCPが基板の上下面において部分的にのみ重なり合う位置関係、または全く重なり合わない互いにずれた位置関係にあるような場合には、それぞれのTCPのランドが形成された領域及びチップが位置する領域にはスルーホールを形成することができない。従って、基板全体としてスルーホールの形成に使用できない面積が大きくなるので、基板両面の面積を有効に利用することができず、基板全体の寸法が大きくなる。本発明によれば、いずれの前記TCPについても、その全4辺から接合部の内側に配線パターンを引き出し、スルーホールを設けて内層回路に接続することができるので、基板への電子部品の実装密度が高くなると共に、基板面積の有効利用が図られ、配線パターンの設計自由度が向上する。

【0075】また、上述したCPUとI/Oシステムチップの場合のように、その動作上互いに大きく関連する2個のICチップを同一基板の表裏面の略同じ位置に重なるように配置し、かつ電源との接続及び接地を共通化することによって、それらの電源電位及び接地電位を実質的に同一にすることができるので、動作の安定性が向上する。しかも、例えば電源用のスルーホール22は前記電源用リードとランドとの接合部近傍に、その他のスルーホールも対応するリードとランドとの接合部近傍に配設できるので、ICチップ間の配線長を短くすることができ、インダクタンス、インピーダンスを低下させてより一層の高速動作化を図ることができる。更に、隣接する配線間のキャパタンスが低下するので、ノイズの影響が少なくなり、誤動作の虞が解消される。

【0076】特に本実施例のカード型コンピュータでは、CPU10として米国インテル社製80386SLを、IOサブシステムチップ13として同社製82360SLをそれぞれ使用している。通常ICチップの上面には、印刷された製造者名、型番等の文字の向きを正面として、その左手前隅部に1番ピンの位置を示す小さなマークが付されているが、本実施例では、図1において、マーク28で示される80386SLの1番ピン及び82360SLの1番ピンの位置が、コネクタ8側から見てそれぞれ左手前にくるように、前記両チップを配置する。本実施例のように両チップが対応する場合には、それぞれ対称位置に関連するリードが出ていることがあり、特に多ビット(例えば16、32ビット)のバスが出ている場合には、対応するリードが共通の位置にくることが多い。本実施例では、上述したような配置によって、前記両チップの関連する多くのピンの位置をメイン基板2を挟んで対応させることができ、最低限必要なスルーホールの個数をその共通化によって大幅に少なくすることができた。これにより、スルーホールの形成に要する基板面積を約20%減少させることができた。また、同時に上下チップ間の配線長の短縮によって、動作の安定性及び信頼性の向上を図ることができた。

【0077】図3には、上記第1実施例の変形例が断面図示されている。この変形例では、メイン基板2の上面及び下面に、それぞれ搭載するCPU10及びIOサブシステムチップ13に対応する寸法のダイパッド29、30が所定位置に設けられている。前記両チップは、それぞれその下面全面が例えば銀ペースト等の熱伝導性樹脂31、32によってダイパッド29、30に接合されている。メイン基板2には、複数のサーマルビアホール33が貫設されており、これによって両ダイパッド29、30間が熱伝達可能に接続されている。前記カード型コンピュータを動作させると、CPU10が比較的高熱を発生するのに対し、IOサブシステムチップ13が発生する熱は比較的低い。このため、CPU10が発生した熱の一部は、熱伝導性樹脂層31からダイパッド29、サーマルビアホール33を介して反対側のダイパッド30に伝達され、IOサブシステムチップ13から放散される。また、サーマルビアホール33を介して伝達される熱の一部は、メイン基板2の内層回路を介して放散される。

【0078】更に、図3の実施例では、第1及び第2TCP5、6のアウタリード16、18とランド17、19との各接合部に保護のための絶縁性樹脂34、35が塗布されている。この絶縁性樹脂は熱伝導性を有するので、CPU10が発生する熱は、第1TCPのアウタリード16を通って絶縁性樹脂34から、及び第2TCPのアウタリード18を介して絶縁性樹脂35からも放散される。このように放熱面積を増大させることによって、高価な放熱フィンや液体冷却装置等の手段を使用しなくても、高発熱性の素子を高密度実装することが可能となり、同時に製造コストを低減させることができる。

【0079】図4を用いて、上記第1実施例のように2個のTCP5、6をメイン基板2の両面に実装する工程を説明する。先ず、第1TCP5をメイン基板2の上面に、図4Aに示す従来と同様の方法によって接続する。第1TCP5は、その全4辺のアウタリード16をそれぞれ対応する各ランド17と整合させて位置合せし、メイン基板2の所定位置に設置する。この基板を、少なくともランド17の領域を含むようにして、従来と同様に上面が平坦な受け台である第1受け台36上に載置する。ランド17の表面には、予めはんだ層が付着されている。

【0080】次に、第1TCP5の上方からボンディングツール37を下降させる。ボンディングツール37の底面は、その中央に矩形の凹所38を設けることによって、アウタリード16とランド17との接合部に対応する平面ロ字形の加圧部39を形成している。加圧部39は、4辺の全アウタリード16先端を一括して対応するランド17上面に押圧し、かつ同時に加熱する。第1TCP5は、メイン基板2の上面より相当突出するが、接合するアウタリード16先端を除く略全部が凹所38内に収容されるので、本加圧工程を妨げることはない。ボンディングツール37は、前記接合部が冷却した後に上昇させてアウタリード16から引き離され、それによってアウタリード16とランド17とがはんだ付けにより完全に接合される。

【0081】次に、図4Bに示すように、メイン基板2を上下反転させ、その上に第2TCP6を設置し、同様にその全4辺のアウタリード18をそれぞれ対応する各ランド19に整合させて位置合せする。この基板を受け台である第2受け台40上に載置する。第2受け台40は、上述したボンディングツール37の底面に略対応する平面ロ字形状の周辺支持部41を有し、それによってアウタリード16とランド17との前記接合部においてメイン基板2を支持する。前記接合部以外の第1TCP5の部分は、第2受け台40の上面中央の矩形凹所42内に収容される。ランド19の表面にも同様に、はんだ層が予め付着されている。

【0082】次に、ボンディングツール43を第2TCP6の上方から下降させる。ボンディングツール43は、ボンディングツール37と同様の形状を有し、平面ロ字形の加圧部44と中央凹所45とを底面に有する。第2TCP6の接合部の位置、形状、寸法が第1TCP5と同一であれば、ボンディングツール37をそのままボンディングツール43に使用してもよい。加圧部44により4辺の全アウタリード18先端を対応するランド19上面に押圧しかつ同時に加熱することによって、これらをはんだ付けにより一括接合する。このように第2受け台40とボンディングツール43とを用いて、互いに対応する平面ロ字形の周辺支持部41と加圧部44との間でメイン基板2を支持しつつ加圧することによって、先に接続されたTCPが妨げとならずに、基板の両面の略同じ位置に2個のTCPを実装することが可能になる。

【0083】上述した実施例では、略同一の大きさを有する2個のTCPを用いたが、大きさの異なる大小2個のTCPを重なり合う位置に搭載する場合には、当然ながら小さい方のTCPを先に基板に接続する。次に、大きい方のTCPを、その接続部をカバーし得る大きな受け台を使用して、基板の反対側の面に接続すればよい。

【0084】図5には、本発明を適用したプリント回路基板の第2実施例が概略的に示されている。第2実施例では、第1TCP5と第2TCP6とが、各1辺のアウタリード16、18の接合部においてのみ互いに重なり合うようにして、それぞれメイン基板2の上下両面に実装されている。何らかの理由により、基板のレイアウト上、前記両TCPを第1実施例のように同じ位置に完全に重なり合うように配置できない場合にも、一部の接合部において部分的に重なるようにすることによって、上記第1実施例と同様に基板両面の面積を有効に使用して実装密度を高くすることができる。特に、互いに重なり合う前記1辺のアウタリード16、18間では、双方の近接位置に共通のスルーホールをメイン基板2に設けることができるので、第1及び第2TCP5、6にそれぞれ搭載されている素子間の配線長を短くでき、高速動作化に対応することができる。同時に、この場合にも、隣接する配線パターンによるノイズの影響を少なくして、動作の安定性・信頼性を向上させ得ることはいうまでもない。

【0085】第2実施例のプリント回路基板は、図6に示す工程に従って、メイン基板2の両面に2個のTCP5、6を実装することができる。先ず、図6Aに示すように、第1TCP5をメイン基板2の表面上に、その全4辺のアウタリード16をそれぞれ対応するランド17に位置合せして設置する。このメイン基板2を、第1受け台46の上に載置する。第1受け台46は、その上面が、メイン基板2表面のランド17と重なり合うランド19に対応する段差部47を除いて平坦に形成され、ランド19の部分を含めてメイン基板2を裏面から有効に支持できるようになっている。次に、第1TCP5の上方からボンディングツール48を下降させる。ボンディングツール48の底面には、第1TCP5のアウタリード16に対応する平面ロ字形の加圧部49が形成されており、これにより全4辺のアウタリード16の先端を一括して対応するランド17に押圧し、かつ同時に加熱する。また、ランド17表面には予めはんだ層が形成されており、第1TCP5はメイン基板2表面にはんだ付けされる。そして、接合部が冷却した後、ボンディングツール48を上昇させてアウタリード16から引き離す。

【0086】次に、図6Bに示すように、上下反転させたメイン基板2の上に第2TCP6を、その全4辺のアウタリード18を対応するランド19に整合させて位置合せして設置する。このメイン基板2を第2受け台50上に載置する。第2受け台50は、その上面が、メイン基板2裏面のランド19と重なり合う第1TCP5の前記接合部に対応する段部51を除いて、平坦に形成され、メイン基板2が前記接合部を含めて確実に支持されるようになっている。次に、図示されるようにボンディングツール52を下降させ、その底面に設けられた平面ロ字形の加圧部53によって、アウタリード18先端を一括してランド19に押圧し、かつ同時に加熱する。ランド19表面には、同様に予めはんだ層が形成されているので、第2TCP6はメイン基板2裏面にはんだ付けされる。このようにして、第1実施例と同様に、2個のTCP5、6を基板の表裏両面に互いに部分的に重なり合うように実装することができる。

【0087】図7には、半導体装置1を所謂ICカードと同様のカード形状をなす箱体54内に収容したカード型コンピュータが示されている。箱体54は、図8に併せて示されるように、概ねコ字形をなす亜鉛・ダイカスト製またはアルミニウム・ダイカスト製の枠体55と、金属製の上面パネル56及び平坦な下面パネル57とから構成される。箱体54の長手方向の一方の側辺は、コネクタ8によって形成される。このようなカード形状の箱体は、樹脂ケースの一体構造が一般的であるが、本発明の場合、内部の基板に悪影響を及ぼす虞があるため、また本実施例では実際上枠体55が金属製のため、熱カシメできないので、両パネル56、57はねじ等を用いてまたは接着剤により枠体55に結合される。このように、箱体54の略全体が導電性材料で形成され、かつ枠体55、上面パネル56及び下面パネル57が導通した構造によって、メイン基板2及び第1サブ基板3に対する静電シールドの効果が発揮され、前記基板自体の輻射ノイズや外部のノイズの影響を遮断し、ノイズ干渉を有効に排除することができる。また、上面パネル56には、その周辺部から或一定の高さの膨出部58が形成されている。

【0088】図8に良く示されるように、半導体装置1は、フレキシブル配線板4を湾曲させて、第1サブ基板3をメイン基板2に対面させるような形態で、箱体54内に収容されている。メイン基板2は、例えばねじ等によって枠体55に固定される。メイン基板2と第1サブ基板3とは、それらの間に介装されたスペーサ部材59によって、互いに一定間隔で離隔しつつ対面状態で一体に結合されている。スペーサ部材59としては、ポリカーボネート樹脂のような或程度の可撓性を有する絶縁材料のブロックを使用し、これを接着剤等で前記両基板の対向面に、好ましくは基板中央付近の電子部品が接続されていない部分に、接着して固定することができる。このような固定方法によって、半導体装置1全体をより薄型にすることができる。また、スペーサ部材59が上述したように可撓性を有するため各基板2、3に余分な応力が作用しないので、振動や衝撃等に対してもその影響を受けることが少ない。そして、第1サブ基板3が概ね上面パネル56の膨出部58内に収まるようになっている。

【0089】本実施例では、メイン基板2の第1TCP5即ちCPU10を実装した面が第1サブ基板3に対面し、かつ第1サブ基板3のRAM9を実装した面がメイン基板2と対面するように配置されている。そして、上述したように、フレキシブル配線板4がメイン基板2のCPU10を実装した前記面に接続されることによって、メイン基板2にスルーホールをほとんど設ける必要がなく、CPU5と第1サブ基板3とを接続することができる。このため、メイン基板の面積をより小さくでき、基板の小型化を図り得ると共に、回路の設計・配線の自由度が増す。

【0090】図9に示す別の実施例では、フレキシブル配線板4が、メイン基板2の第1サブ基板3に対面する側と反対側の面に接続されている点において、図8の実施例と異なる。このため、メイン基板2の側縁には、フレキシブル配線板4を通すための切欠部60が形成されている。更に、メイン基板2には、CPU10がフレキシブル配線板4を接続した面と反対側に搭載されているので、これと接続するためのスルーホール61が設けられている。しかし、このような構成により、フレキシブル配線板4は、図3の実施例よりも大きい曲率で湾曲させることができるので、メイン基板2との接続部にかかる負担をより少なくし、該接続部における断線や破損を防止することができる。

【0091】また、別の実施例では、図8の構成において、第1TCP5と第2TCP6とを逆に配置することができる。この場合には、CPU10がメイン基板2のフレキシブル配線板4を接続した面と反対側になるので、図4の実施例と同様のスルーホールをメイン基板2に形成する必要がある。しかし、IOサブシステムチップ13に比して発熱の多いCPU10が、下面パネル57側にかつその近傍に配置されるので、該下面パネルからの放熱作用により、内部の温度上昇を抑制することができる。

【0092】更に別の実施例では、図9の構成において、第1TCP5と第2TCP6とを逆に配置することができる。この場合には、CPU10がメイン基板2のフレキシブル配線板4を接続した面と同じ側になるので、スルーホールを形成する必要がなく、かつフレキシブル配線板4の曲率が大きくなって前記接続部にかかる負担が少なくなり、しかも、CPU5が下面パネル57側に配置されるので、より高い放熱効果が得られるという利益がある。

【0093】図10及び図11には、それぞれ上述した図8及び図9の変形例が示されている。即ち、これらの実施例では、第1サブ基板3が、RAM9を実装した面と反対側の面をメイン基板2に対面させている。このため、図3及び図4の実施例に比して、装置全体の厚さが多少大きくなるが、RAM9が上面パネル56側にかつその近傍に配置されるので、該上面パネルからの放熱作用により、RAM9による内部の温度上昇を抑制することができる。また、フレキシブル配線板4の接続位置、CPU10の配置、及びそれらの位置関係による作用効果については、図8及び図9の場合と同一であるので、説明を省略する。

【0094】箱体54の上面パネル56は、絞り加工によって外向きの膨出部58を形成した金属板からなる。この金属板には、箱体54全体を所望の厚さに制限しつつ、使用時に図12に示すような外力による変形を防止するという観点から、例えばビッカース硬さ150〜250程度、厚さ約0.2mmのステンレス鋼板のような硬い材料を使用すると好都合である。特に、かかるカード状箱体54を手で取り扱う場合、外力は上面パネルの略中央に作用するが、そのために上面パネル56が多少凹むようなことがあっても、上述したスペーサ部材59が前記基板の略中央に配置されているので、変形による前記基板への影響が少ない。

【0095】膨出部58は、その立上り角度aを45〜90゜に設定すると、指で押しても容易に変形しない剛性が得られると共に、上述したように第1サブ基板3を、その寸法が記憶容量の増大によって大きくなっても、収容し得る十分なスペースが確保されるので好ましい。上面パネル56は、図示されるように膨出部58の立上り部を除いて全体が平坦に形成されているので、組立時に枠体55に対する位置決めが容易であり、組立性が向上し、作業が容易になる。また、本実施例では、膨出部58とコネクタ8との間を或程度離隔することによって、前記カード型コンピュータを装脱する際のコネクタ8の強度を向上させている。更に、上面パネル56の膨出部58内面には、第1サブ基板3との直接接触を防止するために、公知のレジスト材62が前記立上り部を含めて略全面に塗布されている。ここで、前記レジスト材は、膨出部58以外の上面パネル56内面には塗布されていないので、高温により変形や剥がれを生じる虞が無い。また、レジスト材62は、膨出部58内面の前記立上り部を除いた平面部分にのみ塗布することもできる。

【0096】図13には、第2サブ基板7の断面構造及び製造工程が示されている。本実施例において、第2サブ基板7は、厚さ1mm程度の4層構造の配線板63からなり、薄型化を図るために、電子部品を実装するための中央領域64が、予め約半分の厚さに削られている。配線板63には、厚さ0.3mm程度の更に薄いものを使用することもできる。配線板63の周縁には、メイン基板2のパッドにはんだ付けにより接続するための多数の端子65が設けられている。

【0097】先ず、図13Aに示すように、中央領域64の所定位置に例えばロジックIC、マイクロコンピュータ等の複数の電子部品66を設置し、ワイヤボンディングやはんだ付け等公知の方法により接続する。次に、図13Bに示すように、搭載した電子部品66及び中央領域64全体を覆うように、熱硬化性保護樹脂67を塗布する。これを加熱して保護樹脂67を硬化させた後冷却すると、配線板63、特にその中央領域64が肉薄で剛性に欠けるために、熱膨張率の差から、図13Cに示すように、その周辺部が上向きに反りを生じる。

【0098】このような上反りの第2サブ基板7は、メイン基板2上の所定位置に正確に設置しても、メイン基板2の僅かな動きで簡単に位置がずれてしまうため、正確かつ確実に接続することが困難である。また、所定位置に接続できたとしても、メイン基板も同様に薄型なために十分な剛性を有しない場合には、第2サブ基板7の反りに合わせて変形する虞がある。図14には、反りを生じたサブ基板をメイン基板の所定位置に正確に、かつメイン基板に変形を生じさせることなく実装し得る方法が工程順に示されている。

【0099】メイン基板2の表面には、第2サブ基板7の端子65を接続するために対応する多数のパッド68が予め形成されている。図14Aに示すように、第2サブ基板7を位置合せしつつ、その下面を接着剤69によってメイン基板2上に仮付けする。接着剤69は、前記下面の少なくとも2個所、または3個所以上に付着させるのが好ましいが、位置ずれを生じない限り1個所でも良い。従って、仮付け後に第2サブ基板7が正確に配置されていないことが判明すれば、簡単に取り外して位置決めし直すことができる。しかも、一旦正確に配置されれば、メイン基板2を動かしてもその位置が容易にずれることはない。次に、赤外線や温風を用いて例えば約230゜Cの温度で約10秒間加熱する周知のリフローはんだ付けによって、第2サブ基板7の各端子65を対応するメイン基板2のパッド68に接合する。図14Bに示すように、加熱中の前記第2サブ基板は、保護樹脂67が熱膨張して反りが解消し、平坦な状態になる。しかし、常温まで冷却すると、図14Cのように第2サブ基板7の反る力によって、メイン基板2にも反りが生じる。

【0100】次に、図14Dに示すようにメイン基板2を反転させ、その裏面上に第3サブ基板70を載置する。第3サブ基板70には、フロッピーディスクドライブ、ADコンバータ、PLL等のアナログ回路部分が搭載されている。第3サブ基板70は、第2サブ基板7と略同一の寸法・形状を有し、かつ熱硬化性保護樹脂の熱膨張率の差により上反りを生じている。逆にメイン基板2は、反転によって下向きに反っている。メイン基板2の裏面には、第2サブ基板7を実装した位置と該メイン基板を挟んで重なり合う対称位置に第3サブ基板70が実装されるように、予め多数のパッド71が形成されている。位置合せした第3サブ基板70は、同様にその下面を複数個所または位置ずれを起こさない限り1個所で接着剤72によりメイン基板裏面に仮付けする。この状態で正確に位置決めされていないことが判明すれば、第3サブ基板70は前記メイン基板裏面から取り外して、再度位置合せすることができる。そして、周知の手段により加熱して、リフローはんだ付けにより、図14Eのように第3サブ基板周縁の端子73を対応するパッド71に接合する。上述したように加熱中は第2、第3サブ基板7、70は反りが解消して平坦になるので、正確に位置決めされている限り、はんだ付けは容易に行われる。前記両サブ基板がメイン基板2の前記対称位置に接続されることによって、それらの反る力が均衡し、かつ互いに逆方向に作用することによって、メイン基板2は、常温に冷却した後も図14Eの真っ直ぐに平坦な状態に保持される。また、前記両サブ基板の大きさが異なる場合でも、概ね対称位置に実装することによって、メイン基板2の反りを抑制することができる。

【0101】第3サブ基板70の電源端子は、多数の端子73の中の1個所のみに設けられ、統一してメイン基板2のある電源ラインに接続されている。本発明のように回路基板が小型化すると、デジタル回路部分は動作が安定してくるのに対し、アナログ回路部分はノイズの影響を受け易くなる。特に、本実施例の第1サブ基板3のようなメモリ基板は、ノイズが発生し易く、電源電圧の変動を引き起こす虞があり、アナログ回路部分への影響も大きい。本発明によれば、アナログ回路部分をメイン基板2とは別個の基板として電源も統一することにより、デジタル回路部分の電源電位の変動の影響を少なくできるので、その動作を安定させることができる。また、電源を1個所にすることによって、第3サブ基板70及びメイン基板2のスペースを節約することができ、半導体装置全体を小型化できると共に、コストを低減させることができる。更に、必要に応じて、第3サブ基板70の電源回路にフィルタを付加することによって、ノイズをより確実に遮断することもできる。

【0102】図15A及びBには、本発明による半導体装置の第2実施例が示されている。この半導体装置は、図1に示す第1実施例のフレキシブル配線板4に代えて、1対のコネクタによって互いに電気的かつ機械的に着脱可能に接続される図15Aのメイン基板2′と図15Bの第1サブ基板3′とからなる。メイン基板2′は、第1実施例における第1TCP5即ちCPUが搭載されていない点、及びその上面に細長い雌型のコネクタ74が取り付けられている点を除いて、第1実施例のメイン基板2と全く同様の構成を有する。本実施例では、ベアチップのCPU75が、所謂COB(Chip on Board)方式で第1サブ基板3′上に直接接続され、かつ保護樹脂76で被覆されている。

【0103】更に第1サブ基板3′には、図15Bに示すように、CPU75と同一面上に半導体装置のメインメモリを構成する4個のRAM9′が搭載され、かつメイン基板2′の雌型コネクタ74に対応する細長い雄型のコネクタ77が取り付けられている。CPU75とRAM9′とは、第1サブ基板3′に配線されたデータバスを介して相互接続されているので、両者間の配線長を第1実施例の場合よりも短くできる。特に本実施例では、CPUに米国インテル社の80486マイクロプロセッサ(クロック周波数33MHz)を使用しているため、その性能を十分に発揮させてより高速で処理させることができるので、好都合である。

【0104】雌型コネクタ74は、メイン基板2′の上面に第2サブ基板7とは反対側の短辺に沿って配置され、かつ雄型コネクタ77を補完する長手方向に沿って細長い溝状の接続部78が上向きに開設されている。接続部78の内部には、その左右両側に例えば100ピンの接続端子79aが長手方向に沿って0.5mmの狭ピッチで配設されている。これに対して、雄型コネクタ77は、第1サブ基板3′の一方の辺縁に沿ってCPU75の近傍に配置され、その外面には、同じく左右両側に前記接続部の接続端子に対応する100ピンの接続端子79bが、長手方向に沿って0.5mmの狭ピッチで配設されている。この種のコネクタは一般に、フレキシブル配線板よりも狭ピッチで配線できるので、32ビットまたはそれ以上に信号線の数が増加しても、より小さいスペースで柔軟に対応することができる。

【0105】メイン基板2′と第1サブ基板3′とは、図16に良く示されるように、該第1サブ基板のCPU実装面を下向きに互いに対面させて、雄型コネクタ77を前記雌型コネクタの接続部78に強制的に嵌合させることによって、一体的に抜き差し可能に結合される。このとき、保護樹脂76で被覆したCPU75は、コネクタ74、77と第2サブ基板9との間の、第1実施例では第1TCP5が配設されていた空隙に、収納されるので、半導体装置全体の薄形化することができる。また、メイン基板2′と第1サブ基板3′とを、第1実施例の場合と同様に適当なスペーサ部材(図示せず)を用いることによって、一定の間隔を保持しつつ固定すると、両者間の電気的接続が確保されるので好都合である。当然ながら、前記スペース部材を用いることなく、コネクタのみによって両基板を機械的に固定することも可能である。また、各コネクタ74、77は、上記以外の様々な型式のものを使用することができ、かつ前記各基板の形状・寸法、配線等の設計条件によって、基板の中央部等上記実施例以外の様々な位置に設けることができる。

【0106】このように本発明によれば、第1サブ基板に搭載されるCPU及びメインメモリの記憶容量を適当に選択することによって、要求される様々な性能、条件等に対応した専用性を有する半導体装置を提供できるから、メイン基板は、搭載される主要なモジュールを統一して構成を共通化することができ、製造上有利である。特に上記第2実施例の場合、第1実施例の場合とはCPUのピン配列が異なり、かつCPUに接続される配線が多くなるが、このようなCPUの変更に対しても容易に対応することができる。更にメイン基板は、配線スペースが広くなることに加え、配線上CPUによる制限がないので、配線設計の自由度が高くなる利点がある。

【0107】図17乃至図20には、半導体装置1即ち前記カード型コンピュータのコネクタ8の端子の配列が示されている。図7に示されるように、コネクタ8は、その長手方向に沿って118ピン×上下2列の配列構造を有する。このように、半導体装置1が高性能化するにつれてコネクタ8はより多ピン化し、かつ小型化するにつれてピン配列がより狭ピッチ化している。このため、コネクタ8の開口80は、長手方向に沿って左右非対称な位置に形設された2個の補強用リブ81、82によって、それぞれ長さの異なる3つの開口部83〜85に分割されている。これに対応して、前記端子配列も図17の第1領域と、図18及び図19に連続して示す第2領域と、図20に示す第3領域とに3分割されている。非対称位置に設けたリブ81、82によってコネクタ8の接続方向が一義的に決定されるので、前記カード型コンピュータを機器に接続して使用する場合に、その装着方向を誤る虞が解消される。また、当然ながら、コネクタ8が本実施例のように雌型でなく雄型の場合には、前記リブの代わりに溝部を設けることによって、端子配列を分割することができる。

【0108】図17に示される第1領域には、ピン番号1〜28及び119〜146の28ピン×2列が上下平行に配列されている。この領域には、主に外部の周辺装置、即ちLCD(液晶ディスプレイ)、CRT、キーボード、マウス、フロッピディスクドライブ等に接続するためのピンが含まれる。図18及び図19の第2領域には、ピン番号29〜83及び147〜201の55ピン×2列が配列され、例えばシリアルインタフェース、パワーマネージメント、ATバス等に関係するピンが含まれる。図20の第3領域には、ピン番号84〜118及び202〜236の35ピン×2列が配列され、例えばシリアルインタフェース、パラレルインタフェース、ハードディスクドライブ、パワーマネージメント等に関係するピンが含まれている。これらのピンに割り当てられた信号の出力は、3.3Vまたは5Vである。このように比較的低い出力では、外部のノイズや回路内の輻射ノイズの影響を排除して信号出力を安定させることが重要である。

【0109】図17に示されるように、ピン番号121に割り当てられたLCDインタフェースのフラットパネル用データシフトクロック信号(FPDOTCLK)がピン番号120の接地ライン(GND)に隣接して配置されている。このFPDOTCLKは、フラットパネルに表示を行うための制御信号の一つで、表示用データのシフトを行うクロック信号である。これを接地ラインに隣接させることによって、その電位が安定するので、LCDの表示を安定させることができる。

【0110】また、図17のピン番号15〜17には、CRTインタフェース用信号としてCRT用RGB信号の青色(BLUE)、緑色(GREEN)、赤色(RED)信号がそれぞれ割り当てられている。そして、これらのピン番号15〜17に平行なピン配列の対向する位置に設けられたピン番号133〜135に、前記各青色、緑色、赤色信号に対するリターン信号(BRTN、GRTN、RRTN)がそれぞれ割り当てられている。このように、アナログ信号であるCRT用のR、G、B各カラー信号を出力側とリターン側とで、できる限り同一条件にすることによって、外部ノイズ等が打ち消し合ってその影響を受け難くなるので、CRTの表示を高品位にしかつ維持することができる。

【0111】以上、本発明の好適な実施例について詳細に説明したが、当業者に明らかなように、本発明はその技術的範囲内において上述した各実施例に様々な変形・変更を加えて実施することができる。例えば、上記第1実施例のメイン基板と第1サブ基板とを第2実施例のコネクタによって接続することができ、逆に第2実施例のメイン基板と第1サブ基板とをフレキシブル配線板によって接続することもできる。また、TCPを配線板に接続する方法として、はんだ付け以外に熱圧着によるリードとランドとの合金化や、シート状の異方性導電膜を用いる方法、光硬化性絶縁樹脂を用いる方法等、公知の様々な方法を用いることができる。更に、本発明は、TCPと同様にリードを有する、例えばQFPのような他のパッケージ型電子部品を実装する場合にも、同様に適用することができる。

【0112】

【発明の効果】本発明は、以上のように構成されているので、以下に記載されるような効果を奏する。

【0113】本発明の半導体装置によれば、請求項1記載のように構成することによって、サブ基板を取り替えるだけで記憶容量を簡単に変更することができるので、汎用性のあるメイン基板を同一にして、記憶容量の異なる多数の機種を容易に短期間でかつ低コストで製造することができる。しかも、技術の進歩や使用条件の変更等により記憶容量を変更する必要が生じた場合にも、簡単に切り換えができ、かつメイン基板をそのまま利用して低コストで対応することができる。特にCPUをメモリと共にサブ基板に搭載した場合には、メイン基板の共通化が図られ、かつ配線設計の自由度が向上し、製造が容易になってコストを低減化できる。更に、半導体装置の基本的性能を維持しつつ要求される特定の性能・目的に応じてCPU及びメモリを容易に設計変更できるから、半導体装置の専用性を低コストで実現することができる。

【0114】これに加え、本発明によれば、対面配置させたメイン基板とサブ基板とを一体的に固定することによって、フレキシブル配線板またはコネクタにかかる負担を少なくして、振動や衝撃等の外力に対する耐久性を向上させ、装置全体の小型化・薄型化を図ることができ、更に、これらを収容するカード状箱体の一側面を絞り加工した金属板で形成することによって、使用時の不測の取扱いに対して十分な剛性を持たせ、より一層の薄型化を達成することができる。

【0115】更に、本発明によれば、外部のLCDに接続されるドットクロック信号用端子を接地端子に隣接させ、また外部のCRTに接続されるR、G、B信号用各端子の配列を対応するR、G、Bリターン信号用端子の配列と対称に配置することによって、装置全体の小型化及び消費電力の省力化により外部から受ける電磁的な影響を少なくして画像出力を安定させ、LCD、CRTにおける表示を高品質に維持して、動作の安定性・信頼性を向上させることができる。

【0116】また、請求項13記載の本発明の半導体装置によれば、異なる電子部品を搭載したサブ基板を適当に選択することによって、異なる機能、使用条件にそれぞれ対応して多種類の半導体装置を比較的簡単に短期間でかつ低コストで製造することができ、しかも、薄型化した基板に生じ易い反りによる変形を有効に防止して、基板の薄型化を可能にし、半導体装置全体をより小型化・薄型化することができる。

【0117】請求項13記載の本発明の半導体装置の製造方法によれば、電子部品を搭載したサブ基板が、薄型化により反りを生じた場合でも、メイン基板上に正確に位置決めして接続できるので、歩留りが向上し、従来の工程を大幅に変更したり手間やコストを増加させることなく、半導体装置を製造することができる。

【0118】また、請求項15記載の半導体装置によれば、プリント基板の両面において、それぞれICパッケージのリードとプリント基板上のランドとの接合部が互いに重なり合う部分の大きさに応じて、基板面積を小さくできるので、実装密度を高くすることができ、基板両面の面積を有効に利用して回路の設計上自由度が増すと共に、半導体装置及びこれを搭載する機器の小型化を達成することができる。これに加え、特に動作上関連のあるICパッケージを重なり合うように配置すれば、共通のスルーホールを使用することにより、より一層基板面積の有効利用が図られ、高密度実装が可能になると共に、それらの間の配線長を短縮できるので、動作を高速化でき、かつ誤動作を解消して動作の安定性・信頼性の向上を図ることができる。

【0119】更に、請求項21記載の半導体装置によれば、プリント基板の両面に重なり合うように配置された一方のICパッケージから発生する熱が、プリント基板に設けたサーマルビアを介して他方のICパッケージに伝達されるので、高価な放熱手段や冷却装置を用いることなく比較的簡単な方法により、放熱面積を実質的に増大させることができ、低コストで小型化に適した放熱構造が得られる。

【0120】また、請求項23記載の半導体装置の製造方法によれば、プリント基板を支持する受け台の形状に変更を加えるだけで、従来の実装工程に大幅な変更を加えることなく、複数のICパッケージをプリント基板の両面に重なり合うように実装することができ、上述したように、高密度実装、動作の高速化、動作の安定性・信頼性の向上に適した半導体装置を比較的簡単にかつ低コストで実現することができる。

【図面の簡単な説明】

【図1】本発明を適用したカード型コンピュータ用の半導体装置の第1実施例を概略的に示す斜視図である。

【図2】図1のII−II線に於ける断面図である。

【図3】第1実施例の変形例を示す図2と同様の断面図である。

【図4】第1実施例の実装工程を示す断面図である。

【図5】本発明の第2実施例を示す断面図である。

【図6】第2実施例の実装工程を示す断面図である。

【図7】第1実施例の半導体装置を収容したカード形状の箱体を示す斜視図である。

【図8】メイン基板と第1サブ基板との接続構造を示す図7のVIII−VIII線における断面図である。

【図9】メイン基板と第1サブ基板との接続構造の別の実施例を示す断面図である。

【図10】メイン基板と第1サブ基板との接続構造の更に別の実施例を示す断面図である。

【図11】メイン基板と第1サブ基板との接続構造の更に別の実施例を示す断面図である。

【図12】カード形状の箱体の構造を説明するための断面図である。

【図13】第2サブ基板の製造工程を順に示す図A乃至図Cからなる断面図である。

【図14】第2及び第3サブ基板をメイン基板の両面に接続する工程を順に示す図A乃至図Eからなる図である。

【図15】図A及び図Bからなり、それぞれ本発明による半導体装置の第2実施例のメイン基板と第1サブ基板とを概略的に示す斜視図である。

【図16】第2実施例のメイン基板と第1サブ基板とを接続した状態を示す部分拡大図である。

【図17】コネクタのリブで分割された第1部分の端子配列を示す図である。

【図18】コネクタのリブで分割された第2部分の半分の端子配列を示す図である。

【図19】図18に示す第2部分の残りの半分の端子配列を示す図である。

【図20】コネクタのリブで分割された第3部分の端子配列を示す図である。

【図21】従来の半導体装置に於ける両面実装を示す断面図である。

【符号の説明】

1 半導体装置

2 メイン基板

3 第1サブ基板

4 フレキシブル配線板

5 第1TCP

6 第2TCP

7 第2サブ基板

8 コネクタ

9 RAM

10 CPU

11 テープキャリア

12 保護樹脂

13 IOサブシステムチップ1

14 テープキャリア

15 保護樹脂

16 アウタリード

17 ランド

18 アウタリード

19 ランド

20 電源ライン

21 グランドライン

22、23 スルーホール

24〜27 配線

28 マーク

29、30 ダイパッド

31、32 熱伝導性樹脂

33 サーマルビアホール

34、35 絶縁性樹脂

36 第1受け台

37 ボンディングツール

38 凹所

39 加圧部

40 第2受け台

41 周辺支持部

42 凹所

43 ボンディングツール

44 加圧部

45 凹所

46 第1受け台

47 段差部

48 ボンディングツール

49 加圧部

50 第2受け台

51 段部

52 ボンディングツール

53 加圧部

54 箱体

55 枠体

56 上面パネル

57 下面パネル

58 膨出部

59 スペーサ部材

60 切欠部

61 スルーホール

62 レジスト材

63 配線板

64 中央領域

65 端子

66 電子部品

67 熱硬化性保護樹脂

68 パッド

69 接着剤

70 第3サブ基板

71 パッド

72 接着剤

73 端子

74 雌型コネクタ

75 CPU

76 保護樹脂

77 雄型コネクタ

78 接続部

79 接続端子

80 開口

81、82 補強用リブ

83〜85 開口部

86 プリント基板

87 TCP

88 ボンディングツール

89 アウタリード

90 ランド

91 受け台

92 TCP

【特許請求の範囲】

【請求項1】 基板に搭載されたCPUと入出力装置とメモリとを備える半導体装置であって、前記基板がメイン基板と、該メイン基板に電気的に接続されたサブ基板とからなり、前記メモリが、前記サブ基板に搭載されたメモリ素子からなることを特徴とする半導体装置。

【請求項2】 前記CPUが、前記メイン基板に搭載されていることを特徴とする請求項1記載の半導体装置。

【請求項3】 前記CPUが、前記サブ基板に搭載されていることを特徴とする請求項1記載の半導体装置。

【請求項4】 前記メイン基板と前記サブ基板とが、フレキシブル配線板を介して接続されていることを特徴とする請求項1乃至請求項3のいずれか記載の半導体装置。

【請求項5】 前記メイン基板と前記サブ基板とが、互いに対面するように1対のコネクタによって着脱可能に接続されていることを特徴とする請求項1乃至請求項3のいずれか記載の半導体装置。

【請求項6】 前記サブ基板が、前記フレキシブル配線板を湾曲させて前記メイン基板と対面するように配置され、かつ前記フレキシブル配線板が、前記メイン基板の前記サブ基板と対面する面と反対側の面に接続されていることを特徴とする請求項4記載の半導体装置。

【請求項7】 互いに対面させた前記メイン基板と前記サブ基板とを一体的に固定するための手段を更に備えることを特徴とする請求項5または請求項6記載の半導体装置。

【請求項8】 前記メイン基板とサブ基板とを収容するためのカード形状の薄い箱体を備え、前記箱体の少なくとも一方の面が、絞り加工により外向きに膨出させた金属板からなることを特徴とする請求項4または請求項5記載の半導体装置。

【請求項9】 外部装置に接続するために多数の端子を配列したコネクタを更に備え、外部の液晶ディスプレイ装置に接続されるドットクロック信号用端子が、接地端子に隣接して配置されていることを特徴とする請求項1記載の半導体装置。

【請求項10】 外部装置に接続するために多数の端子を複数の列に配列したコネクタを更に備え、外部のCRTに接続されるR、G、B信号用各端子と、それらに対応するR、G、Bリターン信号用各端子とが、互いに平行な前記端子列の対向する位置にそれぞれ配置されていることを特徴とする請求項1記載の半導体装置。

【請求項11】 外部装置に接続するために多数の端子を配列したコネクタを更に備え、前記コネクタが、前記端子の列をその配列に沿って左右非対称に分割する手段を有することを特徴とする請求項1記載の半導体装置。

【請求項12】 前記メイン基板の面に実装される第2のサブ基板を有し、前記第2のサブ基板にはアナログ回路部分が搭載され、かつ前記第2のサブ基板の電源端子が、1個所で前記メイン基板に接続されていることを特徴とする請求項1記載の半導体装置。

【請求項13】 基板に実装された複数の電子部品からなる半導体装置であって、前記基板が、メイン基板とそれぞれに前記電子部品を搭載した複数のサブ基板とからなり、少なくともいずれか2個の前記サブ基板が、前記メイン基板の両面に該メイン基板を挟んで互いに重なり合う対称位置に実装されていることを特徴とする半導体装置。

【請求項14】 複数の電子部品を基板に実装した半導体装置の製造方法であって、前記電子部品をサブ基板に実装する過程と、前記サブ基板を前記メイン基板上の所定位置に設置し、取外可能に仮付けした後に前記メイン基板に接続する過程とからなることを特徴とする半導体装置の製造方法。

【請求項15】 第1ICパッケージと第2ICパッケージとをそれぞれプリント基板の第1面及び第2面に実装した半導体装置であって、前記第1ICパッケージのリードと前記第1面上に形成された第1ランドとの接合部と、前記第2ICパッケージのリードと前記第2面上に形成された第2ランドとの接合部とが、互いに前記プリント基板を挟んで重なり合うように、前記第1及び第2ICパッケージが配置されていることを特徴とする半導体装置。

【請求項16】 前記第1ICパッケージの前記リードと前記第1ランドとの前記接合部と、前記第2ICパッケージの前記リードと前記第2ランドとの前記接合部とが、前記各ICパッケージのいずれか1辺において互いに重なり合うことを特徴とする請求項15記載の半導体装置。

【請求項17】 前記第1ICパッケージの前記リードと前記第1ランドとの前記接合部と、前記第2ICパッケージの前記リードと前記第2ランドとの前記接合部とが、前記各ICパッケージの全4辺において互いに重なり合うことを特徴とする請求項15記載の半導体装置。

【請求項18】 前記第1及び第2ICパッケージが、その動作上相互に関連ICチップを搭載していることを特徴とする請求項15乃至請求項17のいずれか記載の半導体装置。

【請求項19】 前記第1ICパッケージがCPUを搭載し、かつ前記第2ICパッケージが前記CPUに対応して動作するI/Oシステムを搭載していることを特徴とする請求項18記載の半導体装置。

【請求項20】 前記第1または第2ICパッケージがTCP(Tape Carrier Package)であることを特徴とする請求項15乃至請求項19のいずれか記載の半導体装置。

【請求項21】 プリント基板の両面に第1ICパッケージと第2ICパッケージとを、前記プリント基板を挟んで互いに重なり合うように実装した半導体装置であって、前記第1及び第2ICパッケージが、それぞれ前記プリント基板の各面にダイボンディングにより接合され、かつ前記プリント基板を貫通するサーマルビアを介して互いに熱伝達可能に接続されていることを特徴とする半導体装置。

【請求項22】 前記プリント基板の各面に接続された前記第1または第2ICパッケージのリードを熱伝導性樹脂で被覆したことを特徴とする請求項21記載の半導体装置。

【請求項23】 複数のICパッケージをプリント基板の両面に実装した半導体装置の製造方法であって、第1ICパッケージを前記プリント基板の第1面上に配置して、そのリードを前記第1面上のランドに接合することにより接続する過程と、前記プリント基板を反転させ、かつ前記第1ICパッケージのリードと前記ランドとの接合部が支持されるように受け台の上に載置する過程と、第2ICパッケージを前記プリント基板の第2面上に、そのリードと前記第2面のランドとの接合部が前記第1ICパッケージの前記接合部と互いに前記プリント基板を挟んで重なり合うように配置する過程と、前記受け台に対応する加圧手段を用いて、前記第2ICパッケージのリードと前記第面のランドとを加圧することにより接合する過程とからなることを特徴とする半導体装置の製造方法。

【請求項24】 前記加圧手段により加圧する際に加熱し、はんだ付けによって前記第2ICパッケージのリードと前記第2面のランドとを接合することを特徴とする請求項23記載の半導体装置の製造方法。

【請求項25】 前記加圧手段により加圧する際に加熱し、熱圧着によって前記第2ICパッケージのリードと前記第2面のランドとを接合することを特徴とする請求項23記載の半導体装置の製造方法。

【請求項26】 前記加圧手段により加圧する際に加熱し、異方性導電膜を用いて前記第2ICパッケージのリードを前記第2面のランドに接合することを特徴とする請求項23記載の半導体装置の製造方法。

【請求項27】 前記加圧手段により加圧する際に光を照射し、光硬化性樹脂を用いて前記第2ICパッケージのリードを前記第2面のランドに接合することを特徴とする請求項23記載の半導体装置の製造方法。

【請求項1】 基板に搭載されたCPUと入出力装置とメモリとを備える半導体装置であって、前記基板がメイン基板と、該メイン基板に電気的に接続されたサブ基板とからなり、前記メモリが、前記サブ基板に搭載されたメモリ素子からなることを特徴とする半導体装置。

【請求項2】 前記CPUが、前記メイン基板に搭載されていることを特徴とする請求項1記載の半導体装置。

【請求項3】 前記CPUが、前記サブ基板に搭載されていることを特徴とする請求項1記載の半導体装置。

【請求項4】 前記メイン基板と前記サブ基板とが、フレキシブル配線板を介して接続されていることを特徴とする請求項1乃至請求項3のいずれか記載の半導体装置。

【請求項5】 前記メイン基板と前記サブ基板とが、互いに対面するように1対のコネクタによって着脱可能に接続されていることを特徴とする請求項1乃至請求項3のいずれか記載の半導体装置。

【請求項6】 前記サブ基板が、前記フレキシブル配線板を湾曲させて前記メイン基板と対面するように配置され、かつ前記フレキシブル配線板が、前記メイン基板の前記サブ基板と対面する面と反対側の面に接続されていることを特徴とする請求項4記載の半導体装置。

【請求項7】 互いに対面させた前記メイン基板と前記サブ基板とを一体的に固定するための手段を更に備えることを特徴とする請求項5または請求項6記載の半導体装置。

【請求項8】 前記メイン基板とサブ基板とを収容するためのカード形状の薄い箱体を備え、前記箱体の少なくとも一方の面が、絞り加工により外向きに膨出させた金属板からなることを特徴とする請求項4または請求項5記載の半導体装置。

【請求項9】 外部装置に接続するために多数の端子を配列したコネクタを更に備え、外部の液晶ディスプレイ装置に接続されるドットクロック信号用端子が、接地端子に隣接して配置されていることを特徴とする請求項1記載の半導体装置。

【請求項10】 外部装置に接続するために多数の端子を複数の列に配列したコネクタを更に備え、外部のCRTに接続されるR、G、B信号用各端子と、それらに対応するR、G、Bリターン信号用各端子とが、互いに平行な前記端子列の対向する位置にそれぞれ配置されていることを特徴とする請求項1記載の半導体装置。

【請求項11】 外部装置に接続するために多数の端子を配列したコネクタを更に備え、前記コネクタが、前記端子の列をその配列に沿って左右非対称に分割する手段を有することを特徴とする請求項1記載の半導体装置。

【請求項12】 前記メイン基板の面に実装される第2のサブ基板を有し、前記第2のサブ基板にはアナログ回路部分が搭載され、かつ前記第2のサブ基板の電源端子が、1個所で前記メイン基板に接続されていることを特徴とする請求項1記載の半導体装置。

【請求項13】 基板に実装された複数の電子部品からなる半導体装置であって、前記基板が、メイン基板とそれぞれに前記電子部品を搭載した複数のサブ基板とからなり、少なくともいずれか2個の前記サブ基板が、前記メイン基板の両面に該メイン基板を挟んで互いに重なり合う対称位置に実装されていることを特徴とする半導体装置。

【請求項14】 複数の電子部品を基板に実装した半導体装置の製造方法であって、前記電子部品をサブ基板に実装する過程と、前記サブ基板を前記メイン基板上の所定位置に設置し、取外可能に仮付けした後に前記メイン基板に接続する過程とからなることを特徴とする半導体装置の製造方法。

【請求項15】 第1ICパッケージと第2ICパッケージとをそれぞれプリント基板の第1面及び第2面に実装した半導体装置であって、前記第1ICパッケージのリードと前記第1面上に形成された第1ランドとの接合部と、前記第2ICパッケージのリードと前記第2面上に形成された第2ランドとの接合部とが、互いに前記プリント基板を挟んで重なり合うように、前記第1及び第2ICパッケージが配置されていることを特徴とする半導体装置。

【請求項16】 前記第1ICパッケージの前記リードと前記第1ランドとの前記接合部と、前記第2ICパッケージの前記リードと前記第2ランドとの前記接合部とが、前記各ICパッケージのいずれか1辺において互いに重なり合うことを特徴とする請求項15記載の半導体装置。

【請求項17】 前記第1ICパッケージの前記リードと前記第1ランドとの前記接合部と、前記第2ICパッケージの前記リードと前記第2ランドとの前記接合部とが、前記各ICパッケージの全4辺において互いに重なり合うことを特徴とする請求項15記載の半導体装置。

【請求項18】 前記第1及び第2ICパッケージが、その動作上相互に関連ICチップを搭載していることを特徴とする請求項15乃至請求項17のいずれか記載の半導体装置。

【請求項19】 前記第1ICパッケージがCPUを搭載し、かつ前記第2ICパッケージが前記CPUに対応して動作するI/Oシステムを搭載していることを特徴とする請求項18記載の半導体装置。

【請求項20】 前記第1または第2ICパッケージがTCP(Tape Carrier Package)であることを特徴とする請求項15乃至請求項19のいずれか記載の半導体装置。

【請求項21】 プリント基板の両面に第1ICパッケージと第2ICパッケージとを、前記プリント基板を挟んで互いに重なり合うように実装した半導体装置であって、前記第1及び第2ICパッケージが、それぞれ前記プリント基板の各面にダイボンディングにより接合され、かつ前記プリント基板を貫通するサーマルビアを介して互いに熱伝達可能に接続されていることを特徴とする半導体装置。

【請求項22】 前記プリント基板の各面に接続された前記第1または第2ICパッケージのリードを熱伝導性樹脂で被覆したことを特徴とする請求項21記載の半導体装置。

【請求項23】 複数のICパッケージをプリント基板の両面に実装した半導体装置の製造方法であって、第1ICパッケージを前記プリント基板の第1面上に配置して、そのリードを前記第1面上のランドに接合することにより接続する過程と、前記プリント基板を反転させ、かつ前記第1ICパッケージのリードと前記ランドとの接合部が支持されるように受け台の上に載置する過程と、第2ICパッケージを前記プリント基板の第2面上に、そのリードと前記第2面のランドとの接合部が前記第1ICパッケージの前記接合部と互いに前記プリント基板を挟んで重なり合うように配置する過程と、前記受け台に対応する加圧手段を用いて、前記第2ICパッケージのリードと前記第面のランドとを加圧することにより接合する過程とからなることを特徴とする半導体装置の製造方法。

【請求項24】 前記加圧手段により加圧する際に加熱し、はんだ付けによって前記第2ICパッケージのリードと前記第2面のランドとを接合することを特徴とする請求項23記載の半導体装置の製造方法。

【請求項25】 前記加圧手段により加圧する際に加熱し、熱圧着によって前記第2ICパッケージのリードと前記第2面のランドとを接合することを特徴とする請求項23記載の半導体装置の製造方法。

【請求項26】 前記加圧手段により加圧する際に加熱し、異方性導電膜を用いて前記第2ICパッケージのリードを前記第2面のランドに接合することを特徴とする請求項23記載の半導体装置の製造方法。

【請求項27】 前記加圧手段により加圧する際に光を照射し、光硬化性樹脂を用いて前記第2ICパッケージのリードを前記第2面のランドに接合することを特徴とする請求項23記載の半導体装置の製造方法。

【図1】

【図2】

【図4】

【図3】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図15】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図4】

【図3】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図15】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開平8−23149

【公開日】平成8年(1996)1月23日

【国際特許分類】

【出願番号】特願平7−55192

【出願日】平成7年(1995)2月21日

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【公開日】平成8年(1996)1月23日

【国際特許分類】

【出願日】平成7年(1995)2月21日

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

[ Back to top ]