半導体装置及びアナログスイッチの制御方法

【課題】高い電圧を有する入力信号に対して適切に動作するアナログスイッチを有する半導体装置を提供する。

【解決手段】入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチと,入力端子に印加される入力電圧に応じて,Pチャネルトランジスタの第1ゲート電圧及び第1バックゲート電圧と,Nチャネルトランジスタの第2ゲート電圧及び第2バックゲート電圧とのそれぞれの電位を可変生成する可変電圧回路と,アナログスイッチを導通または非導通に制御する制御信号を可変電圧回路に供給する制御回路とを有する。可変電圧回路は,導通に制御する制御信号に応答して,可変生成される第1ゲート電圧と第2ゲート電圧とをPチャネルトランジスタとNチャネルトランジスタのゲートにそれぞれ出力する。

【解決手段】入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチと,入力端子に印加される入力電圧に応じて,Pチャネルトランジスタの第1ゲート電圧及び第1バックゲート電圧と,Nチャネルトランジスタの第2ゲート電圧及び第2バックゲート電圧とのそれぞれの電位を可変生成する可変電圧回路と,アナログスイッチを導通または非導通に制御する制御信号を可変電圧回路に供給する制御回路とを有する。可変電圧回路は,導通に制御する制御信号に応答して,可変生成される第1ゲート電圧と第2ゲート電圧とをPチャネルトランジスタとNチャネルトランジスタのゲートにそれぞれ出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は,CMOSアナログスイッチを有する半導体装置及びアナログスイッチの制御方法に関する。

【背景技術】

【0002】

CMOSアナログスイッチは,並列に接続されたNチャネルMOSトランジスタとPチャネルMOSトランジスタを有し,逆相の制御信号をそれぞれのトランジスタのゲートに入力し,制御信号によってNMOSトランジスタとPMOSトランジスタとを導通状態(オン)と非導通状態(オフ)のいずれかに切り替えるスイッチである。入力電圧と出力電圧がグランドから電源電圧の間のいずれの電位であっても,導通状態と非導通状態を維持することができる。

【0003】

一般に,NMOSトランジスタは,ゲート・ソース間電圧が正の閾値電圧VthNを超えていれば導通状態になるが,閾値電圧VthN未満になると非導通状態になる。したがって,ゲートに電源電圧VDDを印加した場合,NMOSトランジスタは,ソースが0〜(VDD−VthN)の電圧であれば導通状態になるが,ソースが(VDD−VthN)〜VDDの電圧では非導通になる。逆に,PMOSトランジスタは,ゲート・ソース間電圧が負の閾値電圧VthPを超えていれば(ソースよりゲートがVthP以上低い場合)導通状態になるが,その閾値電圧VthP未満になると非導通状態になる。したがって,ゲートにグランド電圧VSSを印加した場合,ソースがVthP〜VDDの電圧であれば導通状態になるが,ソースが0〜VthPの電圧では非導通になる。

【0004】

そこで,NMOSトランジスタとPMOSトランジスタとを並列に接続し,NMOSトランジスタのゲートに電源電圧VDDをPMOSトランジスタのゲートにグランド電圧VSSを印加すれば,両トランジスタの両端のソース・ドレイン端子の電圧が0〜VDDのいずれの電圧であっても導通状態を維持することができる。

【0005】

また,ゲート電極の下の基板領域にはバックゲート電圧が印加され,一般に,バックゲート電圧Vbgは,NMOSトランジスタの場合は0V,PMOSトランジスタの場合は電源電圧VDDである。

【0006】

このようなCMOSアナログスイッチについては,特許文献1,2に記載されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平9−252241号公報

【特許文献2】特開平10−41798号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら,MOSトランジスタは,ゲート電極と基板との間に設けられたゲート絶縁膜の耐圧(以下ゲート耐圧)が比較的低い。それに対して,CMOSアナログスイッチの入出力端子に印加される電圧の範囲0V〜VDDが大きくなると,ゲート電圧Vgとバックゲート電圧Vbgとの間の電圧差がゲート耐圧を超える場合がある。その場合,MOSトランジスタが破壊されてしまう。

【0009】

そのため,バックゲート電圧Vbgを所定の電圧に制御してゲート電圧Vgとバックゲート電圧Vbgとの間の電圧差がゲート耐圧を超えないようにすることが必要になる。

【0010】

しかし,バックゲート電圧をグランド電圧VSS,電源電圧VDD以外の電圧にすると,CMOSアナログスイッチの入出力端子に対して基板領域が順バイアスになり,リーク電流が発生し,入力端子の電圧が出力端子に伝達されなくなる。

【0011】

そこで,本発明の目的は,広い電圧範囲の入力電圧に対しても適切に導通状態を形成することができるCMOSアナログスイッチを有する半導体装置及びアナログスイッチの制御方法を提供することにある。

【課題を解決するための手段】

【0012】

半導体装置の第1の側面は,入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチと,

前記入力端子に印加される入力電圧に応じて,前記Pチャネルトランジスタの第1ゲート電圧及び第1バックゲート電圧と,前記Nチャネルトランジスタの第2ゲート電圧及び第2バックゲート電圧とのそれぞれの電位を可変生成する可変電圧回路と,

前記アナログスイッチを導通または非導通に制御する制御信号を前記可変電圧回路に供給する制御回路とを有し,

前記可変電圧回路は,前記導通に制御する制御信号に応答して,前記可変生成される第1ゲート電圧と第2ゲート電圧とを前記PチャネルトランジスタとNチャネルトランジスタのゲートにそれぞれ出力する。

【発明の効果】

【0013】

第1の側面によれば,広い電圧範囲の入力電圧に対しても適切に導通状態を形成する半導体装置が提供される。

【図面の簡単な説明】

【0014】

【図1】試験用チップの構成図である。

【図2】CMOSアナログスイッチの回路図である。

【図3】CMOSアナログスイッチのゲート電圧とバックゲート電圧の様々な例を示す図である。

【図4】CMOSアナログスイッチのゲート電圧とバックゲート電圧の様々な例を示す図である。

【図5】CMOSアナログスイッチのゲート電圧とバックゲート電圧の様々な例を示す図である。

【図6】CMOSアナログスイッチのゲート電圧とバックゲート電圧の様々な例を示す図である。

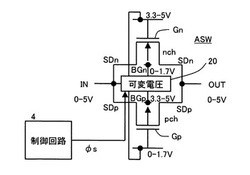

【図7】本実施の形態におけるCMOSアナログスイッチ装置の回路図である。

【図8】本実施の形態におけるCMOSアナログスイッチ装置の入力電圧に対応したゲート電圧とバックゲート電圧を示す図である。

【図9】本実施の形態におけるCMOSアナログスイッチ装置を導通するための,入力電圧に対応したゲート電圧とバックゲート電圧を示すグラフ図である。

【図10】3つの入力電圧範囲M1,M2,M3でのPMOS,NMOSトランジスタのオン抵抗を示す図である。

【図11】本実施の形態における一般化したCMOSアナログスイッチ装置の入力電圧範囲M1,M2,M3におけるゲート電圧とバックゲート電圧を示した図である。

【図12】図12は,PMOSトランジスタの入力電圧Vinに対するゲート電圧とバックゲート電圧を示した図である。

【図13】図13は,NMOSトランジスタの入力電圧Vinに対するゲート電圧とバックゲート電圧を示した図である。

【図14】図12,図13のPMOSトランジスタとNMOSトランジスタのゲート電圧とバックゲート電圧とを重ねて示した図である。

【図15】一般化したCMOSアナログスイッチ装置の場合の3つの入力電圧の範囲M1,M2,M3でのPMOS,NMOSトランジスタのオン抵抗を示す図である。

【図16】一般化したCMOSアナログスイッチ装置のPMOS,NMOSトランジスタのゲート電圧とバックゲート電圧の変型例を示す図である。

【図17】一般化したCMOSアナログスイッチ装置のPMOS,NMOSトランジスタのゲート電圧とバックゲート電圧の変型例を示す図である。

【図18】可変電圧回路の回路図である。

【図19】図18の可変電圧回路の動作を示すフローチャート図である。

【図20】入力電圧Vinが範囲M1の場合の可変電圧回路の状態を示す図である。

【図21】入力電圧Vinが範囲M2の場合の可変電圧回路の状態を示す図である。

【図22】入力電圧Vinが範囲M3の場合の可変電圧回路の状態を示す図である。

【発明を実施するための形態】

【0015】

図1は,試験用チップの構成図である。LSIテストシステム1がインターフェースとして動作する試験用チップ2に接続され,試験用チップ2の入出力端子E1〜Enには,被試験装置DUT1〜DUTnの外部端子が接続されている。

【0016】

試験用チップ2は,試験の制御を行う制御回路4を有し,制御回路4は入出力端子E1〜Enに出力信号を駆動するドライバ8と,入力信号を入力してH,Lレベルを検出するコンパレータ9とを介して入出力端子E1〜Enに接続される。また,試験用チップ2は,DC電圧測定部6を有し,ピンマトリクス10内のアナログスイッチASWを介して入力端子E1〜Enに任意の組み合わせで接続される。アナログスイッチASWには,図示しない制御信号が制御回路4から供給され,任意の組み合わせのアナログスイッチASWが導通状態にされる。それにより,任意の組み合わせの入力端子がDC電圧測定部6に接続される。

【0017】

LSIテストシステム1は,試験用チップ2を介して,被試験装置DUT1〜DUTnに所定の信号を出力し,それに応答して出力される信号を入力する。また,LSIテストシステム1は,試験用チップ2内のDC電圧測定部6により,被試験装置が出力する出力信号のDC電圧を測定する。このDC電圧測定部6は,図1に示されるとおり試験用チップ2内に設けられてもよいし,試験用チップ2とは別のチップ内に設けられても良い。

【0018】

アナログスイッチASWは,後述するとおり,入出力端子IN,OUT間にPチャネルトランジスタ(以下PMOSトランジスタ)とNチャネルトランジスタ(以下NMOSトランジスタ)のソース・ドレイン端子をそれぞれ接続し,図示しない逆相の制御信号をそれぞれのトランジスタのゲートに入力し,導通状態と非導通状態とに制御される。一般的には,PMOSトランジスタのバックゲートには入力信号の最大電圧である電源電圧が印加され,NMOSトランジスタのバックゲートには入力信号の最小電圧であるグランド電圧が印加される。そして,制御信号により,PMOSトランジスタのゲートにグランド電圧が印加され,NMOSトランジスタのゲートに電源電圧が印加されると,アナログスイッチASWは導通状態にされる。また,制御信号により,PMOSトランジスタのゲートに電源電圧が印加され,NMOSトランジスタのゲートにグランド電圧が印加されると,アナログスイッチASWは非導通状態にされる。

【0019】

近年のMOSトランジスタは,ソース・ドレイン間の耐圧が電源電圧以上あるものが開発されている。そのようなMOSトランジスタをアナログスイッチASWのCMOSトランジスタに採用することで,アナログスイッチは,試験用チップ2内の電源電圧以上のDC電圧を持つ入力信号をスイッチングすることができる。図1の例では,被試験装置DUTの出力信号のDC電圧が試験用チップ2内の電源電圧以上であっても,アナログスイッチASWがオン,オフ動作可能である。

【0020】

ところが,MOSトランジスタのゲート絶縁膜の耐圧であるゲート耐圧は,トランジスタの微細化によって低くなる傾向にある。しかし,ゲート電圧とバックゲート電圧との電圧差をゲート耐圧以下にする必要がある。したがって,従来のアナログスイッチのようなPMOSトランジスタとNMOSトランジスタのゲート電圧とバックゲート電圧がグランドと電源電圧では,電源電圧より高い電圧を有する入力信号をスイッチングすることはできない。その詳細について以下にて説明する。

【0021】

図2は,CMOSアナログスイッチの回路図である。また,図3,図4,図5,図6は,CMOSアナログスイッチのゲート電圧とバックゲート電圧の様々な例を示す図である。前提として,NMOS,PMOSトランジスタのゲート耐圧Vrが共に3.3V,入力電圧Vinが最小電圧Vminがグランド電位(0V),最大電圧Vmaxが5Vとする。また,それぞれの閾値電圧をVth(P),Vth(N)とする。

Vr=3.3V

Vmin=0V

Vmax=5V

図2のCMOSアナログスイッチASWは,入力端子INと出力端子OUTとの間に,PMOSトランジスタpchと,NMOSトランジスタnchとが並列に接続されている。両トランジスタのゲートには逆相の制御信号が印加される。一般的な方法では,アナログスイッチを導通するためには,図2に示されるとおり,PMOSトランジスタpchのゲートGに入力電圧Vinの最小電圧Vmin=0Vが,そのバックゲートBGに入力電圧Vinの最大電圧Vmax=5Vが,NMOSトランジスタnchのゲートGに最大電圧Vmax=5Vが,そのバックゲートBGに最小電圧Vmin=0Vがそれぞれ印加される。この状態では,入力電圧Vinが0V〜5VのいずれであってもPMOSトランジスタpchとNMOSトランジスタnchの少なくとも一方は導通状態になる。具体的には,アナログスイッチが導通状態では入力端子INと出力端子OUTの電圧は共に入力電圧Vinになので,入力電圧VinがVth(P)〜5VでPMOSトランジスタが導通し,入力電圧Vinが0V〜(5V−Vth(N))でNMOSトランジスタが導通する。

【0022】

しかし,前提条件としてPMOS,NMOSトランジスタのゲート耐圧Vrが3.3Vであるので,上記のように,ゲートGとバックゲートBGとの間が5Vでは,ゲート耐圧Vr以上でありトランジスタがゲート破壊を起こす。

【0023】

図3には,CMOSアナログスイッチと,入力電圧Vinに対するオン抵抗Ronの関係図とが示されている。図3に示されるように,PMOSトランジスタのバックゲートBGをゲート耐圧Vrの3.3Vに,NMOSトランジスタのゲートGをゲート耐圧Vrの3.3Vにしたとする。その場合,図3の入力電圧・オン抵抗のグラフ図に示されるとおり,入力電圧VinがVth(P)〜3.3VではPMOSトランジスタpchは導通するが,入力電圧VinがVth(P)に近づくほどオン抵抗Ronは高くなる。一方,入力電圧Vinが0V〜(3.3V-Vth(N))ではNMOSトランジスタnchは導通するが,3.3V-Vth(N)に近づくほどオン抵抗Ronは高くなる。そのため,両トランジスタの合成オン抵抗Ronは,破線で示されるとおり,入力電圧Vinが0V〜3.3Vの範囲では低くなっている。

【0024】

しかし,入力電圧Vinが3.3Vを超えると,PMOSトランジスタのP型ドレイン,ソース領域とN型のバックゲート領域とのPN接合が順バイアス状態になり,ドレイン,ソース領域からバックゲート領域に順方向リーク電流が流れる。その結果,アナログスイッチは入力電圧Vinの3.3V〜5Vの電圧を出力端子に伝達することができない。

【0025】

図4は,PMOSトランジスタpchではゲート電圧を1.7V(=5V-3.3V)にバックゲート電圧を5Vにし,NMOSトランジスタnchではゲート電圧を3.3Vにバックゲート電圧を0Vにした例である。この場合は,両トランジスタのゲートとバックゲート間電圧は共にゲート耐圧Vr=3.3Vに保たれるのでゲート破壊は生じない。この例では,PMOSトランジスタpchは,入力電圧Vinが(1.7V+Vth(P))〜5Vで導通し,NMOSトランジスタnchは,入力電圧Vinが0V〜(3.3V-Vth(N))で導通する。しかし,中間電位2.5V近辺では両トランジスタのオン抵抗Ronが大きくなり,合成オン抵抗も高くなり,双方向性のアナログスイッチとしては好ましくない。

【0026】

図5は,図4と逆に,PMOSトランジスタpchではゲート電圧を0Vにバックゲート電圧を3.3Vにし,NMOSトランジスタnchではゲート電圧を5Vにバックゲート電圧を1.7Vにした例である。この例では,PMOSトランジスタpchは,入力電圧VinがVth(P)〜5Vで導通し,NMOSトランジスタnchは,入力電圧Vinが0V〜(5V-Vth(N))で導通する。しかし,図3と同様に,入力電圧Vinが3.3V〜5Vで,PMOSトランジスタのP型ドレイン,ソース領域とN型のバックゲート領域とのPN接合が順バイアス状態になり,ドレイン,ソース領域からバックゲート領域に順方向電流が流れる。一方,入力電圧Vinが0V〜1.7Vで,NMOSトランジスタのN型ドレイン,ソース領域とP型のバックゲート領域とのPN接合が順バイアスになり,バックゲート領域からドレイン,ソース領域に順方向リーク電流が流れる。

【0027】

図6は,図3と逆に,PMOSトランジスタpchではゲート電圧を1.7Vにバックゲート電圧を5Vにし,NMOSトランジスタnchではゲート電圧を5Vにバックゲート電圧を1.7Vにした例である。この例では,PMOSトランジスタpchは,入力電圧Vinが(1.7V+Vth(P))〜5Vで導通し,NMOSトランジスタnchは,入力電圧Vinが0V〜(5V-Vth(N))で導通する。しかし,図4と同様に,入力電圧Vinが0V〜1.7Vで,NMOSトランジスタのN型ドレイン,ソース領域とP型のバックゲート領域とのPN接合が順バイアスになり,バックゲート領域からドレイン,ソース領域に順方向リーク電流が流れる。

【0028】

図7は,本実施の形態におけるCMOSアナログスイッチ装置の回路図である。このCMOSアナログスイッチ装置は,入力端子INと出力端子OUTとの間にPチャネルトランジスタpchとNチャネルトランジスタnchとを並列に接続したアナログスイッチASWと,入力端子に印加される入力電圧に応じて,PチャネルトランジスタのゲートGpの電圧及びバックゲートBGpの電圧と,NチャネルトランジスタnchのゲートGnの電圧及びバックゲートBGnの電圧のそれぞれの電位を可変生成する可変電圧回路20と,アナログスイッチASWを導通または非導通に制御する制御信号φsを可変電圧回路20に供給する制御回路4とを有する。

【0029】

そして,PMOSトランジスタでは,入力電圧Vinの0V〜5Vの範囲の電位に応じて,ゲートGpの電圧を0〜1.7Vで可変制御し,バックゲートBGpの電圧を3.3〜5Vで可変制御し,且つ,ゲート電圧とバックゲート電圧との差をゲート耐圧Vr(Pch)に維持する。一方,NMOSトランジスタでは,入力電圧Vinの0V〜5Vの範囲の電位に応じて,ゲートGnの電圧を3.3〜5Vで可変制御し,バックゲートBGnの電圧を0〜1.7Vで可変制御し,且つ,ゲート電圧とバックゲート電圧との差をゲート耐圧Vr(Nch)に維持する。このようにすることで,入力端子INに印加される入力電圧Vinが0〜5Vの電位であっても,CMOSアナログスイッチASWは,ゲート破壊を生じることなく,且つソース,ドレイン領域のリーク電流を生じることなく,正常に導通状態になることができる。

【0030】

図8は,本実施の形態におけるCMOSアナログスイッチ装置の入力電圧に対応したゲート電圧とバックゲート電圧を示す図である。また,図9は,本実施の形態におけるCMOSアナログスイッチ装置を導通するための,入力電圧に対応したゲート電圧とバックゲート電圧を示すグラフ図である。

【0031】

図8には,入力電圧Vinが0〜1.7(=5-3.3)Vの範囲M1と,1.7〜3.3(=0+3.3)Vの範囲M2と,3.3〜5Vの範囲M3それぞれについて,PMOS,NMOSトランジスタのゲート電圧とバックゲート電圧とが示されている。図9には,横軸の入力電圧Vinに対応して,縦軸のPMOS,NMOSトランジスタのゲート電圧Vg(pch),Vg(nch)と,バックゲート電圧Vbg(pch),Vbg(nch)とが示されている。破線がPMOSトランジスタのゲート電圧Vg(pch),バックゲート電圧Vbg(pch)であり,実線がNMOSトランジスタのゲート電圧Vg(nch),バックゲート電圧Vbg(nch)である。図9の横軸の0〜1.7V,1.7〜3.3V,3.3〜5Vが,図8のM1,M2,M3に対応する。

【0032】

図9の破線で示されるPMOSトランジスタの場合は,入力電圧Vinが0〜3.3(=0+Vr(pch))の場合(図8の範囲M1,M2)は,バックゲート電圧Vbg(pch)をPMOSトランジスタのゲート耐圧Vr(pch)=3.3Vにし,ゲート電圧Vg(pch)をバックゲート電圧Vbg(pch)よりゲート耐圧Vr(pch)=3.3Vだけ低い0Vにする。これにより,バックゲート電圧Vbg(pch)=3.3Vは,入力電圧Vin=0〜3.3V以上に保たれドレイン,ソース領域からバックゲート領域への順方向のリーク電流は発生せず,ゲート・バックゲート間がゲート耐圧Vr(pch)以下に保たれてゲート破壊も起きずに,導通状態にすることができる。

【0033】

そして,入力電圧Vinが3.3〜5Vの場合(図8の範囲M3)は,バックゲート電圧Vbg(pch)を入力電圧Vin(3.3〜5V)と同じにし,ゲート電圧Vg(pch)をバックゲート電圧Vbg(pch)よりゲート耐圧Vr(pch)=3.3Vだけ低くする。つまり,バックゲート電圧とゲート電圧とが入力電圧Vinに応じて上昇するように可変制御される。これにより,バックゲート電圧Vbg(pch)は入力電圧Vin以上であるので,リーク電流は発生せず,ゲート破壊も生じないで,導通状態を保つことができる。PMOSトランジスタの閾値電圧Vth(pch)は-1V未満であるので,ゲート電圧Vg(pch)の0〜1.7Vは入力電圧Vinの3.3〜5Vよりその閾値電圧Vth(pch)以上低く,PMOSトランジスタは導通状態を保つことができる。

【0034】

一方,図9の実線で示されるNMOSトランジスタの場合は,入力電圧Vinが5〜1.7(=5-Vr(nch))の場合(図8の範囲M3,M2)は,バックゲート電圧Vbg(nch)を5VよりNMOSトランジスタのゲート耐圧Vr(npch)=3.3Vだけ低い電位1.7(=5-3.3)Vにし,ゲート電圧Vg(nch)をバックゲート電圧Vbg(nch)よりゲート耐圧Vr(nch)=3.3Vだけ高い5Vにする。これにより,バックゲート電圧Vbg(nch)=1.7Vは,入力電圧Vin=5〜1.7V以下に保たれて,ドレイン,ソース領域にバックゲート領域からの順方向のリーク電流は発生せず,ゲート・バックゲート間がゲート耐圧Vr(nch)以下に保たれてゲート破壊も起きずに,導通状態にすることができる。

【0035】

そして,入力電圧Vinが1.7〜0Vの場合(図8の範囲M1)は,バックゲート電圧Vbg(nch)を入力電圧Vin(1.7〜0V)と同じにし,ゲート電圧Vg(nch)をバックゲート電圧Vbg(nch)よりゲート耐圧Vr(nch)=3.3Vだけ高くする。つまり,バックゲート電圧とゲート電圧とが入力電圧Vinに応じて下降するように可変制御される。これにより,バックゲート電圧Vbg(nch)は入力電圧Vin以下であるので,リーク電流は発生せず,ゲート破壊も生じないで,導通状態を保つことができる。NMOSトランジスタの閾値電圧Vth(nch)は+1V未満であるので,ゲート電圧Vg(nch)の5〜3.3Vは入力電圧Vinの1.7〜0Vよりその閾値電圧Vth(nch)以上高く,NMOSトランジスタは導通状態を保つことができる。

【0036】

図9では,PMOSとNMOSトランジスタの耐圧Vr(pch),Vr(nch)が共に3.3Vを前提にしているので,入力電圧Vinが5Vの場合のPMOSのゲート電圧Vg(pch)とNMOSのバックゲートVbg(nch)とが1.7Vと一致し,入力電圧Vinが0Vの場合のゲート電圧Vg(nch)とバックゲート電圧Vbg(pch)とが3.3Vと一致している。両トランジスタの耐圧が異なる場合は,一致しないことがある。

【0037】

図10は,上記の3つの入力電圧範囲M1,M2,M3でのPMOS,NMOSトランジスタのオン抵抗を示す図である。PMOSトランジスタの場合,入力電圧Vinが範囲M1(0〜1.7V)と範囲M2(1.7〜3.3V)では,ゲート電圧Vg(pch)=0V,バックゲート電圧Vbg(pch)=3.3Vと固定され,範囲M3(3.3〜5V)では,入力電圧Vinに応じて,バックゲート電圧をVbg(pch)=Vin=3.3〜5Vと可変制御し,ゲート電圧をVg(pch)=Vin-Vr(pch)=0〜1.7Vと可変制御する。この可変制御によりドレイン,ソース領域でのリーク電流が防止される。

【0038】

一方,NMOSトランジスタの場合,入力電圧Vinが範囲M3(3.3〜5V)と範囲M2(1.7〜3.3V)では,ゲート電圧Vg(nch)=5V,バックゲート電圧Vbg(nch)=1.7Vと固定され,範囲M1(0〜1.7V)では,入力電圧Vinに応じて,バックゲート電圧がVbg(nch)=Vin=0〜1.7Vと可変制御し,ゲート電圧をVg(nch)=Vin-Vr(nch)=3.3〜5Vと可変制御する。この可変制御によりドレイン,ソース領域でのリーク電流が防止される。しかも,いずれの入力電圧の範囲でも,PMOSとNMOSトランジスタの合成オン抵抗Ronを小さくすることができる。

【0039】

上記の例では,入力電圧Vinの最大電圧Vmax=5Vに対して,ゲート耐圧Vr(pch),Vr(nch)=3.3Vが最大電圧の50%を超えている。それに対して,入力電圧Vinが最小電圧Vmin=0V〜最大電圧Vmaxのいずれかであり,最大電圧Vmaxに対してゲート耐圧Vr(pch),Vr(nch)が50%未満の例について,一般化したCMOSアナログスイッチ装置を説明する。

【0040】

図11は,本実施の形態における一般化したCMOSアナログスイッチ装置の入力電圧範囲M1,M2,M3におけるゲート電圧とバックゲート電圧を示した図である。図12は,PMOSトランジスタの入力電圧Vinに対するゲート電圧とバックゲート電圧を示した図である。図13は,NMOSトランジスタの入力電圧Vinに対するゲート電圧とバックゲート電圧を示した図である。

【0041】

まず,図12のPMOSトランジスタについて説明する。入力電圧Vinが0〜Vr(pch)では,ゲート電圧Vg(pch)=Vmin=0V,バックゲート電圧Vbg(pch)=Vmin+Vr(pch)=Vr(pch)と固定電位にされる。これにより,入力電圧Vinがゲート電圧Vg(pch)=0Vより閾値電圧Vth(pch)だけ高くなると導通し,しかも,バックゲート電圧は入力電圧以上であるのでリーク電流はなく,ゲート破壊もない。さらに,入力電圧VinがVr(pch)〜Vmaxでは,バックゲート電圧はVbg(pch)=Vinにし,ゲート電圧Vg(pch)はバックゲート電圧よりVr(pch)だけ低い電圧Vg(pch)=Vin-Vr(pch)と,入力電圧Vinに応じて変動する電圧に制御される。これにより,ゲート電圧Vg(pch)は入力電圧Vinより閾値電圧Vth(pch)以上低いのでPMOSトランジスタは導通し,しかも,バックゲート電圧は入力電圧以上であるのでリーク電流はなく,ゲート破壊もない。

【0042】

次に,図13のNMOSトランジスタについて説明する。入力電圧VinがVmax〜Vmax-Vr(nch)では,ゲート電圧Vg(nch)=Vmax,バックゲート電圧Vbg(nch)=Vmax-Vr(nch)と固定電位にされる。これにより,入力電圧Vinがゲート電圧Vg(nch)=Vmaxより閾値電圧Vth(nch)だけ低くなると導通し,しかも,バックゲート電圧は入力電圧以下であるのでリーク電流はなく,ゲート破壊もない。さらに,入力電圧VinがVmax-Vr(nch)〜Vminでは,バックゲート電圧をVbg(nch)=Vinに,ゲート電圧Vg(nch)はバックゲート電圧よりVr(nch)だけ高い電圧Vg(nch)=Vin+Vr(nch)にと,入力電圧Vinに応じて変動する電圧に制御される。これにより,ゲート電圧Vg(nch)は入力電圧Vinより閾値電圧Vth(nch)以上高いのでNMOSトランジスタは導通し,しかも,バックゲート電圧は入力電圧以下であるのでリーク電流はなく,ゲート破壊もない。

【0043】

図14は,図12,図13のPMOSトランジスタとNMOSトランジスタのゲート電圧とバックゲート電圧とを重ねて示した図である。図14では,PMOSとNMOSトランジスタのゲート耐圧Vr(pch),Vr(nch)が等しいVrであることを前提にして,図12,図13のPMOSトランジスタとNMOSトランジスタのゲート電圧とバックゲート電圧とを重ねて示している。

【0044】

図15は,一般化したCMOSアナログスイッチ装置の場合の3つの入力電圧の範囲M1,M2,M3でのPMOS,NMOSトランジスタのオン抵抗を示す図である。図15の例では,Vr(pch),Vr(nch)<Vmax/2であるので,3つの入力電圧の範囲M1,M2,M3は,図11に記載されるとおりであり,図10での3つの入力電圧の範囲M1,M2,M3とは異なっている。

【0045】

入力電圧が範囲M1の場合(0〜Vr(pch))では,PMOSトランジスタのゲート電圧とバックゲート電圧とは固定されているが,NMOSトランジスタのバックゲート電圧は入力電圧Vinと等しく,ゲート電圧はそれよりゲート耐圧Vr(nch)だけ高く(Vin+Vr(nch)),入力電圧Vinに応じて変動する電位にされる。これにより,NMOSトランジスタのリーク電流が回避される。

【0046】

入力電圧が範囲M2の場合(Vr(pch)〜(Vmax-Vr(nch))では,PMOS,NMOSトランジスタのバックゲート電圧は入力電圧Vinに等しく,ゲート電圧はそれぞれVin-Vr(pch),Vin+Vr(nch)にされる。つまり,入力電圧Vinに応じて変動する電位である。これにより,PMOS,NMOSトランジスタのいずれもリーク電流が回避される。

【0047】

入力電圧が範囲M3の場合((Vmax-Vr(nch))〜Vmax)では,PMOSトランジスタのバックゲート電圧は入力電圧Vinに等しく,ゲート電圧はVin-Vr(pch)に制御される。これにより,PMOSトランジスタのリーク電流は回避される。そして,NMOSトランジスタでは,ゲート電圧はVmaxに,バックゲート電圧はVmax-Vr(nch)に固定される。

【0048】

図16,図17は,一般化したCMOSアナログスイッチ装置のPMOS,NMOSトランジスタのゲート電圧とバックゲート電圧の変型例を示す図である。図12,図13と対比して以下説明する。

【0049】

図16のPMOSトランジスタの例では,入力電圧Vinが0V近傍の場合は,ゲート電圧Vg(pch)を0Vにし,バックゲート電圧Vbg(pch)はVr(pch)にする。ただし,入力電圧Vinが0V近傍より高く最大入力電圧Vmaxまでの間では,バックゲート電圧Vbg(pch)を入力電圧Vinより高くして,ドレイン,ソース領域とバックゲート領域との間のPN接合が順バイアスにしないようにし,且つ,ゲート電圧Vg(pch)が入力電圧Vinより閾値電圧Vth(pch)だけ低くなるようにして,ゲート電圧Vg(pch)とバックゲート電圧Vbg(pch)間の電圧をゲート耐圧Vr(pch)以下になるようにする。つまり,バックゲート電圧もゲート電圧も入力電圧Vinに応じて可変制御する。

【0050】

図17のNMOSトランジスタの例では,図16と逆に,入力電圧Vinが最大電圧Vmax近傍の場合は,ゲート電圧Vg(nch)をVmaxにし,バックゲート電圧Vbg(nch)はVmax-Vr(nch)にする。ただし,入力電圧VinがVmax近傍より低く最小入力電圧Vmin=0Vまでの間では,バックゲート電圧Vbg(nch)を入力電圧Vinより低くして,ドレイン,ソース領域とバックゲート領域との間のPN接合が順バイアスにしないようにし,且つ,ゲート電圧Vg(nch)が入力電圧Vinより閾値電圧Vth(nch)だけ高くなるようにして,ゲート電圧Vg(nch)とバックゲート電圧Vbg(nch)間の電圧をゲート耐圧Vr(nch)以下にする。この場合も,PMOSと同様に,バックゲート電圧もゲート電圧も入力電圧Vinに応じて可変制御する。

【0051】

図18は,可変電圧回路の回路図である。この可変電圧回路20は,図8,9に示した入力電圧Vin=0〜5V,PMOS,NMOSトランジスタのゲート耐圧が共にVr=3.3Vの例である。可変電圧回路20は,図1でも示したとおり半導体チップ内に設けられ,その電源電圧は例えば3.3Vである。図18の可変電圧回路20は,入力電圧Vinの電圧範囲を検出する入力電圧検出回路を構成する2つのコンパレータCMP10,CMP20と,コンパレータCMP10の出力に応じてオン,オフ制御される1対の第1スイッチS10,S11と,コンパレータCMP20の出力に応じてオン,オフ制御される1対の第2スイッチS20,S21とを有する。

【0052】

コンパレータCMP10は,入力電圧Vinを抵抗2R,R,Rで分圧した電圧を負極入力端子に入力し,電圧5V(=Vmax)、電圧1.7V(=Vmax-Vr(pch))を同様の抵抗で分圧した電圧を正極入力端子に入力し,両者を比較し, Vin<3.3Vであれば出力をLレベルにし,Vin>3.3Vであれば出力をHレベルにする。つまり,Vin<3.3VであればスイッチS10が導通しS11が非導通となり,PMOSトランジスタpchのバックゲート電圧Vbg(pch)には3.3Vが印加され,一方,Vin>3.3VであればスイッチS10が非導通となりS11が導通し,PMOSトランジスタpchのバックゲート電圧Vbg(pch)には入力電圧Vinが印加される。

【0053】

コンパレータCMP20は,入力電圧Vinを抵抗2R,R,Rで降圧した電圧を負極入力端子に入力し,電圧1.7V(=Vmax-Vr(nch))を同様の抵抗で降圧した電圧を正極入力端子に入力し,両者を比較し,Vin>1.7Vであれば出力をHレベルにし,Vin<1.7Vであれば出力をLレベルにする。つまり,Vin>1.7VであればスイッチS20が導通しS21が非導通となり,NMOSトランジスタnchのバックゲート電圧Vbg(nch)には1.7Vが印加され,一方,Vin<1.7VであればスイッチS20が非導通となりS21が導通し,NMOSトランジスタnchのバックゲート電圧Vbg(nch)には入力電圧Vinが印加される。

【0054】

可変電圧回路20は,PMOSトランジスタ用の電圧シフト回路SHF1と,PMOSトランジスタpchを導通または非導通に制御する第3スイッチS30とを有し,一方,NMOSトランジスタ用の電圧シフト回路SHF2と,NMOSトランジスタnchを導通または非導通に制御する第4スイッチS40とを有する。

【0055】

電圧シフト回路SHF1は,キャパシタC1と,充電用スイッチS50,S51と,電圧シフト用スイッチS52,S53とを有し,制御信号φs11によりオンに充電用スイッチS50,S51がされるとキャパシタC1が3.3Vに充電され,充電用スイッチS50,S51が制御信号φS11によりオフにされ,電圧シフト用スイッチS52,S53がオンになると,入力inより3.3V低い電圧が出力outに生成される。

【0056】

第3スイッチS30が,制御信号φs21に応答して端子B側に接続すると,PMOSトランジスタのゲート電圧がバックゲート電圧より3.3V低くなりPMOSトランジスタは導通し,端子A側に接続すると,ゲート電圧がバックゲート電圧と同じになり非導通になる。

【0057】

電圧シフト回路SHF2は,キャパシタC2と,充電用スイッチS60,S61と,電圧シフト用スイッチS62,S63とを有し,制御信号φs12により充電用スイッチS60,S61がオンにされるとキャパシタC2が3.3Vに充電され,制御信号φS12により充電用スイッチS60,S61がオフにされ,電圧シフト用スイッチS62,S63がオンになると,入力inより3.3V高い電圧が出力outに生成される。

【0058】

第4スイッチS40が,制御信号φs22に応答して端子B側に接続すると,NMOSトランジスタのゲート電圧がバックゲート電圧より3.3V高くなりNMOSトランジスタnchは導通し,端子A側に接続すると,ゲート電圧がバックゲート電圧と同じになり非導通になる。

【0059】

図19は,図18の可変電圧回路の動作を示すフローチャート図である。図18で示されるとおり,可変電圧回路20は,制御回路4からの制御信号φs11〜φs22により制御される。まず,ゲートとバックゲート間の電圧を生成するキャパシタC1,C2の充電が制御信号φs11,φs12により行われる(S10)。具体的には,電圧シフト回路SFH1では充電用スイッチS50,S51がオンになりキャパシタC1がゲート耐圧3.3Vに充電され,電圧シフト回路SFH2では充電用スイッチS60,S61がオンになりキャパシタC2もゲート耐圧3.3Vに充電される。

【0060】

そして,入力電圧Vinの電圧範囲を検出する入力電圧検出回路を構成する2つのコンパレータCMP10,CMP20が,それぞれ,入力電圧Vinがゲート耐圧3.3Vより高いか低いかと,最大入力電圧Vmax=5Vよりゲート耐圧3.3Vだけ低い電圧1.7V(=5-3.3)より高いか低いかとを検出している(S20)。すなわち,2つのコンパレータCMP10,CMP20の出力信号の組み合わせにより,入力電圧Vinが範囲M1(0≦Vin<1.7V),M2(1.7V≦Vin<3.3V),M3(3.3V≦Vin≦Vmax(5V))を検出する(S21,S22,S23)。この検出により,1対の第1スイッチS10,S11がPMOSトランジスタのバックゲート電圧Vbg(pch)に3.3Vまたは入力Vinのいずれかを選択して出力し,1対の第2スイッチS20,S21がNMOSトランジスタのバックゲート電圧Vbg(nch)に1.7Vまたは入力Vinのいずれかを選択して出力する。

【0061】

図20は,入力電圧Vinが範囲M1の場合の可変電圧回路の状態を示す図である。入力電圧が0≦Vin<1.7Vであるので,スイッチS10がオン,S11がオフとなり,バックゲート電圧Vbg(pch)は3.3Vになり,スイッチS20がオフ,S21がオンとなり,バックゲート電圧Vbg(nch)は入力電圧Vinになる。

【0062】

図21は,入力電圧Vinが範囲M2の場合の可変電圧回路の状態を示す図である。入力電圧が1.7V≦Vin<3.3Vであるので,スイッチS10がオン,S11がオフとなり,バックゲート電圧Vbg(pch)は3.3Vになり,スイッチS20がオン,S21がオフとなり,バックゲート電圧Vbg(nch)は1.7Vになる。

【0063】

図22は,入力電圧Vinが範囲M3の場合の可変電圧回路の状態を示す図である。入力電圧が3.3V≦Vin≦Vmax(5V)であるので,スイッチS10がオフ,S11がオンとなり,バックゲート電圧Vbg(pch)は入力電圧Vinになり,スイッチS20がオン,S21がオフとなり,バックゲート電圧Vbg(nch)は1.7Vになる。

【0064】

そして,制御信号φs11,φs12により,電圧シフト回路SHF1内の充電用スイッチS50,S51をオフにし,電圧シフト用スイッチS52,S53をオンにし,電圧シフト回路SHF2内の充電用スイッチS60,S61をオフにし,電圧シフト用スイッチS62,S63をオンにする(S30)。これにより,電圧シフト回路SHF1の出力outはバックゲート電圧Vbg(pch)よりゲート耐圧3.3Vだけ低い電位になり,電圧シフト回路SHF2の出力outはバックゲート電圧Vbg(nch)よりゲート耐圧3.3Vだけ高い電位になる。

【0065】

最後に,制御回路からのアナログスイッチを導通または非導通に制御する制御信号φs21,φs22に応じて,第3スイッチS30が端子AまたはBに接続され,第4スイッチS40が端子AまたはBに接続される。両スイッチS30,S40が端子B側に接続されれば,PMOSトランジスタpchのゲート電圧はVbg(pch)-3.3Vに,NMOSトランジスタnchのゲート電圧はVbg(nch)+3.3Vになり,両トランジスタは導通状態になる。一方,両スイッチS30,S40が端子A側に接続されれば,PMOS,NOSトランジスタのゲート電圧はそれぞれのバックゲート電圧Vbg(pch),Vbg(nch)になり,両トランジスタは非導通状態になる。

【0066】

上記の工程S10とS30は,CMOSアナログスイッチのスイッチングサイクル毎に行う必要はない。少なくとも,1回のスイッチングサイクルでは,工程S20とS40とが行われる。

【0067】

以上の通り,本実施の形態のCMOSアナログスイッチ装置によれば,ゲート耐圧以上の電圧範囲の入力信号に対して適切な導通状態になることができる。したがって,電源電圧が低くゲート耐圧が低いLSIチップ内に設けられたCMOSアナログスイッチが,電源電圧を超える高い入力電圧に対して,適切にスイッチングすることができる。

【0068】

以上の実施の形態をまとめると,次の付記のとおりである。

【0069】

(付記1)

入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチと,

前記入力端子に印加される入力電圧に応じて,前記Pチャネルトランジスタの第1ゲート電圧及び第1バックゲート電圧と,前記Nチャネルトランジスタの第2ゲート電圧及び第2バックゲート電圧とのそれぞれの電位を可変生成する可変電圧回路と,

前記アナログスイッチを導通または非導通に制御する制御信号を前記可変電圧回路に供給する制御回路とを有し,

前記可変電圧回路は,前記導通に制御する制御信号に応答して,前記可変生成される第1ゲート電圧と第2ゲート電圧とを前記PチャネルトランジスタとNチャネルトランジスタのゲートにそれぞれ出力する半導体装置。

【0070】

(付記2)

付記1において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記可変電圧回路は,前記Pチャネルトランジスタに対して,前記第1バックゲート電圧を前記入力電圧以上にし,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低くし,

前記可変電圧回路は,前記Nチャネルトランジスタに対して,前記第2バックゲート電圧を前記入力電圧以下にし,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高くする半導体装置。

【0071】

(付記3)

付記1または2において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記入力電圧は最小電圧から最大電圧までの間の電位を有し,

前記可変電圧回路は,前記Pチャネルトランジスタに対して,前記入力電圧が前記最小電圧以上で且つ前記最小電圧より前記第1ゲート耐圧だけ高い第1電圧以下の第1の電圧範囲の場合に,前記第1ゲート電圧を前記最小電圧にし,前記第1バックゲート電圧を前記最小電圧より前記第1ゲート耐圧だけ高くし,前記入力電圧が前記第1電圧以上で且つ前記最大電圧以下の第2の電圧範囲の場合に,前記第1バックゲート電圧を前記入力電圧と同じにし,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低くし,

前記可変電圧回路は,前記Nチャネルトランジスタに対して,前記入力電圧が前記最大電圧以下で且つ前記最大電圧より前記第2ゲート耐圧だけ低い第2電圧以上の第3の電圧範囲の場合に,前記第2ゲート電圧を前記最大電圧にし,前記第2バックゲート電圧を前記最大電圧より前記第2ゲート耐圧だけ低くし,前記入力電圧が前記第2電圧以下で且つ前記最小電圧以上の第4の電圧範囲の場合に,前記第2バックゲート電圧を前記入力電圧と同じにし,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高くする半導体装置。

【0072】

(付記4)

付記3において,

前記可変電圧回路は,

前記入力電圧が第1乃至第4の電圧範囲か否かを検出する入力電圧検出回路と,

前記入力電圧検出回路による第1または第2の電圧範囲の検出に応じて,前記第1バックゲート電圧の出力端子を前記最小電圧より前記第1ゲート耐圧だけ高い電圧に接続または前記入力端子に接続する第1スイッチと,

前記第1ゲート電圧の出力端子に前記第1バックゲート電圧の出力端子より前記第1ゲート耐圧だけ低い電圧を供給する第1電圧シフト回路と,

前記入力電圧検出回路により第3または第4の電圧範囲の検出に応じて,前記第2バックゲート電圧の出力端子を前記最大電圧より前記第2ゲート耐圧だけ低い電圧に接続または前記入力端子に接続する第2スイッチと,

前記第2ゲート電圧の出力端子に前記第2バックゲート電圧の出力端子より前記第2ゲート耐圧だけ高い電圧を供給する第2電圧シフト回路とを有する半導体装置。

【0073】

(付記5)

付記4において,

前記可変電圧回路は,さらに,

前記導通または非導通に制御する制御信号に応答して,前記第1ゲート電圧の出力端子に,前記第1バックゲート電圧の出力端子より前記第1ゲート耐圧だけ低い電圧または前記第1バックゲート電圧をそれぞれ接続する第3スイッチと,

前記導通または非導通に制御する制御信号に応答して,前記第2ゲート電圧の出力端子に,前記前記第2バックゲート電圧の出力端子より前記第2ゲート耐圧だけ高い電圧または前記第2バックゲート電圧をそれぞれ接続する第4スイッチとを有する半導体装置。

【0074】

(付記6)

付記1乃至5のいずれかに記載の半導体装置と,

被試験装置の外部端子に接続された入力端子と,

前記入力端子に前記半導体装置を介して接続され,前記アナログスイッチが導通したときに,前記被試験装置の外部端子の電圧を測定する電圧測定部とを有する試験用半導体装置。

【0075】

(付記7)

入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチの制御方法において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記入力電圧は最小電圧から最大電圧までの間の電位を有し,

前記制御方法は,

前記入力電圧に応じて,前記Pチャネルトランジスタに対して,前記第1バックゲート電圧を前記入力電圧以上に制御し,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低く制御し,

前記入力電圧に応じて,前記Nチャネルトランジスタに対して,前記第2バックゲート電圧を前記入力電圧以下に制御し,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高く制御するアナログスイッチの制御方法。

【0076】

(付記8)

入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチの制御方法において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記入力電圧は最小電圧から最大電圧までの間の電位を有し,

前記制御方法は,

前記Pチャネルトランジスタに対して,前記入力電圧が前記最小電圧以上で且つ前記最小電圧より前記第1ゲート耐圧だけ高い第1電圧以下の第1の電圧範囲の場合に,前記第1ゲート電圧を前記最小電圧にし,前記第1バックゲート電圧を前記最小電圧より前記第1ゲート耐圧だけ高くし,前記入力電圧が前記第1電圧以上で且つ前記最大電圧以下の第2の電圧範囲の場合に,前記第1バックゲート電圧を前記入力電圧と同じにし,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低くし,

前記Nチャネルトランジスタに対して,前記入力電圧が前記最大電圧以下で且つ前記最大電圧より前記第2ゲート耐圧だけ低い第2電圧以上の第3の電圧範囲の場合に,前記第2ゲート電圧を前記最大電圧にし,前記第2バックゲート電圧を前記最大電圧より前記第2ゲート耐圧だけ低くし,前記入力電圧が前記第2電圧以下で且つ前記最小電圧以上の第4の電圧範囲の場合に,前記第2バックゲート電圧を前記入力電圧と同じにし,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高くするアナログスイッチの制御方法。

【符号の説明】

【0077】

pch:PMOSトランジスタ nch:NMOSトランジスタ

IN:入力端子 OUT:出力端子

20:可変電圧回路 4:制御回路

φs:制御信号

【技術分野】

【0001】

本発明は,CMOSアナログスイッチを有する半導体装置及びアナログスイッチの制御方法に関する。

【背景技術】

【0002】

CMOSアナログスイッチは,並列に接続されたNチャネルMOSトランジスタとPチャネルMOSトランジスタを有し,逆相の制御信号をそれぞれのトランジスタのゲートに入力し,制御信号によってNMOSトランジスタとPMOSトランジスタとを導通状態(オン)と非導通状態(オフ)のいずれかに切り替えるスイッチである。入力電圧と出力電圧がグランドから電源電圧の間のいずれの電位であっても,導通状態と非導通状態を維持することができる。

【0003】

一般に,NMOSトランジスタは,ゲート・ソース間電圧が正の閾値電圧VthNを超えていれば導通状態になるが,閾値電圧VthN未満になると非導通状態になる。したがって,ゲートに電源電圧VDDを印加した場合,NMOSトランジスタは,ソースが0〜(VDD−VthN)の電圧であれば導通状態になるが,ソースが(VDD−VthN)〜VDDの電圧では非導通になる。逆に,PMOSトランジスタは,ゲート・ソース間電圧が負の閾値電圧VthPを超えていれば(ソースよりゲートがVthP以上低い場合)導通状態になるが,その閾値電圧VthP未満になると非導通状態になる。したがって,ゲートにグランド電圧VSSを印加した場合,ソースがVthP〜VDDの電圧であれば導通状態になるが,ソースが0〜VthPの電圧では非導通になる。

【0004】

そこで,NMOSトランジスタとPMOSトランジスタとを並列に接続し,NMOSトランジスタのゲートに電源電圧VDDをPMOSトランジスタのゲートにグランド電圧VSSを印加すれば,両トランジスタの両端のソース・ドレイン端子の電圧が0〜VDDのいずれの電圧であっても導通状態を維持することができる。

【0005】

また,ゲート電極の下の基板領域にはバックゲート電圧が印加され,一般に,バックゲート電圧Vbgは,NMOSトランジスタの場合は0V,PMOSトランジスタの場合は電源電圧VDDである。

【0006】

このようなCMOSアナログスイッチについては,特許文献1,2に記載されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平9−252241号公報

【特許文献2】特開平10−41798号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら,MOSトランジスタは,ゲート電極と基板との間に設けられたゲート絶縁膜の耐圧(以下ゲート耐圧)が比較的低い。それに対して,CMOSアナログスイッチの入出力端子に印加される電圧の範囲0V〜VDDが大きくなると,ゲート電圧Vgとバックゲート電圧Vbgとの間の電圧差がゲート耐圧を超える場合がある。その場合,MOSトランジスタが破壊されてしまう。

【0009】

そのため,バックゲート電圧Vbgを所定の電圧に制御してゲート電圧Vgとバックゲート電圧Vbgとの間の電圧差がゲート耐圧を超えないようにすることが必要になる。

【0010】

しかし,バックゲート電圧をグランド電圧VSS,電源電圧VDD以外の電圧にすると,CMOSアナログスイッチの入出力端子に対して基板領域が順バイアスになり,リーク電流が発生し,入力端子の電圧が出力端子に伝達されなくなる。

【0011】

そこで,本発明の目的は,広い電圧範囲の入力電圧に対しても適切に導通状態を形成することができるCMOSアナログスイッチを有する半導体装置及びアナログスイッチの制御方法を提供することにある。

【課題を解決するための手段】

【0012】

半導体装置の第1の側面は,入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチと,

前記入力端子に印加される入力電圧に応じて,前記Pチャネルトランジスタの第1ゲート電圧及び第1バックゲート電圧と,前記Nチャネルトランジスタの第2ゲート電圧及び第2バックゲート電圧とのそれぞれの電位を可変生成する可変電圧回路と,

前記アナログスイッチを導通または非導通に制御する制御信号を前記可変電圧回路に供給する制御回路とを有し,

前記可変電圧回路は,前記導通に制御する制御信号に応答して,前記可変生成される第1ゲート電圧と第2ゲート電圧とを前記PチャネルトランジスタとNチャネルトランジスタのゲートにそれぞれ出力する。

【発明の効果】

【0013】

第1の側面によれば,広い電圧範囲の入力電圧に対しても適切に導通状態を形成する半導体装置が提供される。

【図面の簡単な説明】

【0014】

【図1】試験用チップの構成図である。

【図2】CMOSアナログスイッチの回路図である。

【図3】CMOSアナログスイッチのゲート電圧とバックゲート電圧の様々な例を示す図である。

【図4】CMOSアナログスイッチのゲート電圧とバックゲート電圧の様々な例を示す図である。

【図5】CMOSアナログスイッチのゲート電圧とバックゲート電圧の様々な例を示す図である。

【図6】CMOSアナログスイッチのゲート電圧とバックゲート電圧の様々な例を示す図である。

【図7】本実施の形態におけるCMOSアナログスイッチ装置の回路図である。

【図8】本実施の形態におけるCMOSアナログスイッチ装置の入力電圧に対応したゲート電圧とバックゲート電圧を示す図である。

【図9】本実施の形態におけるCMOSアナログスイッチ装置を導通するための,入力電圧に対応したゲート電圧とバックゲート電圧を示すグラフ図である。

【図10】3つの入力電圧範囲M1,M2,M3でのPMOS,NMOSトランジスタのオン抵抗を示す図である。

【図11】本実施の形態における一般化したCMOSアナログスイッチ装置の入力電圧範囲M1,M2,M3におけるゲート電圧とバックゲート電圧を示した図である。

【図12】図12は,PMOSトランジスタの入力電圧Vinに対するゲート電圧とバックゲート電圧を示した図である。

【図13】図13は,NMOSトランジスタの入力電圧Vinに対するゲート電圧とバックゲート電圧を示した図である。

【図14】図12,図13のPMOSトランジスタとNMOSトランジスタのゲート電圧とバックゲート電圧とを重ねて示した図である。

【図15】一般化したCMOSアナログスイッチ装置の場合の3つの入力電圧の範囲M1,M2,M3でのPMOS,NMOSトランジスタのオン抵抗を示す図である。

【図16】一般化したCMOSアナログスイッチ装置のPMOS,NMOSトランジスタのゲート電圧とバックゲート電圧の変型例を示す図である。

【図17】一般化したCMOSアナログスイッチ装置のPMOS,NMOSトランジスタのゲート電圧とバックゲート電圧の変型例を示す図である。

【図18】可変電圧回路の回路図である。

【図19】図18の可変電圧回路の動作を示すフローチャート図である。

【図20】入力電圧Vinが範囲M1の場合の可変電圧回路の状態を示す図である。

【図21】入力電圧Vinが範囲M2の場合の可変電圧回路の状態を示す図である。

【図22】入力電圧Vinが範囲M3の場合の可変電圧回路の状態を示す図である。

【発明を実施するための形態】

【0015】

図1は,試験用チップの構成図である。LSIテストシステム1がインターフェースとして動作する試験用チップ2に接続され,試験用チップ2の入出力端子E1〜Enには,被試験装置DUT1〜DUTnの外部端子が接続されている。

【0016】

試験用チップ2は,試験の制御を行う制御回路4を有し,制御回路4は入出力端子E1〜Enに出力信号を駆動するドライバ8と,入力信号を入力してH,Lレベルを検出するコンパレータ9とを介して入出力端子E1〜Enに接続される。また,試験用チップ2は,DC電圧測定部6を有し,ピンマトリクス10内のアナログスイッチASWを介して入力端子E1〜Enに任意の組み合わせで接続される。アナログスイッチASWには,図示しない制御信号が制御回路4から供給され,任意の組み合わせのアナログスイッチASWが導通状態にされる。それにより,任意の組み合わせの入力端子がDC電圧測定部6に接続される。

【0017】

LSIテストシステム1は,試験用チップ2を介して,被試験装置DUT1〜DUTnに所定の信号を出力し,それに応答して出力される信号を入力する。また,LSIテストシステム1は,試験用チップ2内のDC電圧測定部6により,被試験装置が出力する出力信号のDC電圧を測定する。このDC電圧測定部6は,図1に示されるとおり試験用チップ2内に設けられてもよいし,試験用チップ2とは別のチップ内に設けられても良い。

【0018】

アナログスイッチASWは,後述するとおり,入出力端子IN,OUT間にPチャネルトランジスタ(以下PMOSトランジスタ)とNチャネルトランジスタ(以下NMOSトランジスタ)のソース・ドレイン端子をそれぞれ接続し,図示しない逆相の制御信号をそれぞれのトランジスタのゲートに入力し,導通状態と非導通状態とに制御される。一般的には,PMOSトランジスタのバックゲートには入力信号の最大電圧である電源電圧が印加され,NMOSトランジスタのバックゲートには入力信号の最小電圧であるグランド電圧が印加される。そして,制御信号により,PMOSトランジスタのゲートにグランド電圧が印加され,NMOSトランジスタのゲートに電源電圧が印加されると,アナログスイッチASWは導通状態にされる。また,制御信号により,PMOSトランジスタのゲートに電源電圧が印加され,NMOSトランジスタのゲートにグランド電圧が印加されると,アナログスイッチASWは非導通状態にされる。

【0019】

近年のMOSトランジスタは,ソース・ドレイン間の耐圧が電源電圧以上あるものが開発されている。そのようなMOSトランジスタをアナログスイッチASWのCMOSトランジスタに採用することで,アナログスイッチは,試験用チップ2内の電源電圧以上のDC電圧を持つ入力信号をスイッチングすることができる。図1の例では,被試験装置DUTの出力信号のDC電圧が試験用チップ2内の電源電圧以上であっても,アナログスイッチASWがオン,オフ動作可能である。

【0020】

ところが,MOSトランジスタのゲート絶縁膜の耐圧であるゲート耐圧は,トランジスタの微細化によって低くなる傾向にある。しかし,ゲート電圧とバックゲート電圧との電圧差をゲート耐圧以下にする必要がある。したがって,従来のアナログスイッチのようなPMOSトランジスタとNMOSトランジスタのゲート電圧とバックゲート電圧がグランドと電源電圧では,電源電圧より高い電圧を有する入力信号をスイッチングすることはできない。その詳細について以下にて説明する。

【0021】

図2は,CMOSアナログスイッチの回路図である。また,図3,図4,図5,図6は,CMOSアナログスイッチのゲート電圧とバックゲート電圧の様々な例を示す図である。前提として,NMOS,PMOSトランジスタのゲート耐圧Vrが共に3.3V,入力電圧Vinが最小電圧Vminがグランド電位(0V),最大電圧Vmaxが5Vとする。また,それぞれの閾値電圧をVth(P),Vth(N)とする。

Vr=3.3V

Vmin=0V

Vmax=5V

図2のCMOSアナログスイッチASWは,入力端子INと出力端子OUTとの間に,PMOSトランジスタpchと,NMOSトランジスタnchとが並列に接続されている。両トランジスタのゲートには逆相の制御信号が印加される。一般的な方法では,アナログスイッチを導通するためには,図2に示されるとおり,PMOSトランジスタpchのゲートGに入力電圧Vinの最小電圧Vmin=0Vが,そのバックゲートBGに入力電圧Vinの最大電圧Vmax=5Vが,NMOSトランジスタnchのゲートGに最大電圧Vmax=5Vが,そのバックゲートBGに最小電圧Vmin=0Vがそれぞれ印加される。この状態では,入力電圧Vinが0V〜5VのいずれであってもPMOSトランジスタpchとNMOSトランジスタnchの少なくとも一方は導通状態になる。具体的には,アナログスイッチが導通状態では入力端子INと出力端子OUTの電圧は共に入力電圧Vinになので,入力電圧VinがVth(P)〜5VでPMOSトランジスタが導通し,入力電圧Vinが0V〜(5V−Vth(N))でNMOSトランジスタが導通する。

【0022】

しかし,前提条件としてPMOS,NMOSトランジスタのゲート耐圧Vrが3.3Vであるので,上記のように,ゲートGとバックゲートBGとの間が5Vでは,ゲート耐圧Vr以上でありトランジスタがゲート破壊を起こす。

【0023】

図3には,CMOSアナログスイッチと,入力電圧Vinに対するオン抵抗Ronの関係図とが示されている。図3に示されるように,PMOSトランジスタのバックゲートBGをゲート耐圧Vrの3.3Vに,NMOSトランジスタのゲートGをゲート耐圧Vrの3.3Vにしたとする。その場合,図3の入力電圧・オン抵抗のグラフ図に示されるとおり,入力電圧VinがVth(P)〜3.3VではPMOSトランジスタpchは導通するが,入力電圧VinがVth(P)に近づくほどオン抵抗Ronは高くなる。一方,入力電圧Vinが0V〜(3.3V-Vth(N))ではNMOSトランジスタnchは導通するが,3.3V-Vth(N)に近づくほどオン抵抗Ronは高くなる。そのため,両トランジスタの合成オン抵抗Ronは,破線で示されるとおり,入力電圧Vinが0V〜3.3Vの範囲では低くなっている。

【0024】

しかし,入力電圧Vinが3.3Vを超えると,PMOSトランジスタのP型ドレイン,ソース領域とN型のバックゲート領域とのPN接合が順バイアス状態になり,ドレイン,ソース領域からバックゲート領域に順方向リーク電流が流れる。その結果,アナログスイッチは入力電圧Vinの3.3V〜5Vの電圧を出力端子に伝達することができない。

【0025】

図4は,PMOSトランジスタpchではゲート電圧を1.7V(=5V-3.3V)にバックゲート電圧を5Vにし,NMOSトランジスタnchではゲート電圧を3.3Vにバックゲート電圧を0Vにした例である。この場合は,両トランジスタのゲートとバックゲート間電圧は共にゲート耐圧Vr=3.3Vに保たれるのでゲート破壊は生じない。この例では,PMOSトランジスタpchは,入力電圧Vinが(1.7V+Vth(P))〜5Vで導通し,NMOSトランジスタnchは,入力電圧Vinが0V〜(3.3V-Vth(N))で導通する。しかし,中間電位2.5V近辺では両トランジスタのオン抵抗Ronが大きくなり,合成オン抵抗も高くなり,双方向性のアナログスイッチとしては好ましくない。

【0026】

図5は,図4と逆に,PMOSトランジスタpchではゲート電圧を0Vにバックゲート電圧を3.3Vにし,NMOSトランジスタnchではゲート電圧を5Vにバックゲート電圧を1.7Vにした例である。この例では,PMOSトランジスタpchは,入力電圧VinがVth(P)〜5Vで導通し,NMOSトランジスタnchは,入力電圧Vinが0V〜(5V-Vth(N))で導通する。しかし,図3と同様に,入力電圧Vinが3.3V〜5Vで,PMOSトランジスタのP型ドレイン,ソース領域とN型のバックゲート領域とのPN接合が順バイアス状態になり,ドレイン,ソース領域からバックゲート領域に順方向電流が流れる。一方,入力電圧Vinが0V〜1.7Vで,NMOSトランジスタのN型ドレイン,ソース領域とP型のバックゲート領域とのPN接合が順バイアスになり,バックゲート領域からドレイン,ソース領域に順方向リーク電流が流れる。

【0027】

図6は,図3と逆に,PMOSトランジスタpchではゲート電圧を1.7Vにバックゲート電圧を5Vにし,NMOSトランジスタnchではゲート電圧を5Vにバックゲート電圧を1.7Vにした例である。この例では,PMOSトランジスタpchは,入力電圧Vinが(1.7V+Vth(P))〜5Vで導通し,NMOSトランジスタnchは,入力電圧Vinが0V〜(5V-Vth(N))で導通する。しかし,図4と同様に,入力電圧Vinが0V〜1.7Vで,NMOSトランジスタのN型ドレイン,ソース領域とP型のバックゲート領域とのPN接合が順バイアスになり,バックゲート領域からドレイン,ソース領域に順方向リーク電流が流れる。

【0028】

図7は,本実施の形態におけるCMOSアナログスイッチ装置の回路図である。このCMOSアナログスイッチ装置は,入力端子INと出力端子OUTとの間にPチャネルトランジスタpchとNチャネルトランジスタnchとを並列に接続したアナログスイッチASWと,入力端子に印加される入力電圧に応じて,PチャネルトランジスタのゲートGpの電圧及びバックゲートBGpの電圧と,NチャネルトランジスタnchのゲートGnの電圧及びバックゲートBGnの電圧のそれぞれの電位を可変生成する可変電圧回路20と,アナログスイッチASWを導通または非導通に制御する制御信号φsを可変電圧回路20に供給する制御回路4とを有する。

【0029】

そして,PMOSトランジスタでは,入力電圧Vinの0V〜5Vの範囲の電位に応じて,ゲートGpの電圧を0〜1.7Vで可変制御し,バックゲートBGpの電圧を3.3〜5Vで可変制御し,且つ,ゲート電圧とバックゲート電圧との差をゲート耐圧Vr(Pch)に維持する。一方,NMOSトランジスタでは,入力電圧Vinの0V〜5Vの範囲の電位に応じて,ゲートGnの電圧を3.3〜5Vで可変制御し,バックゲートBGnの電圧を0〜1.7Vで可変制御し,且つ,ゲート電圧とバックゲート電圧との差をゲート耐圧Vr(Nch)に維持する。このようにすることで,入力端子INに印加される入力電圧Vinが0〜5Vの電位であっても,CMOSアナログスイッチASWは,ゲート破壊を生じることなく,且つソース,ドレイン領域のリーク電流を生じることなく,正常に導通状態になることができる。

【0030】

図8は,本実施の形態におけるCMOSアナログスイッチ装置の入力電圧に対応したゲート電圧とバックゲート電圧を示す図である。また,図9は,本実施の形態におけるCMOSアナログスイッチ装置を導通するための,入力電圧に対応したゲート電圧とバックゲート電圧を示すグラフ図である。

【0031】

図8には,入力電圧Vinが0〜1.7(=5-3.3)Vの範囲M1と,1.7〜3.3(=0+3.3)Vの範囲M2と,3.3〜5Vの範囲M3それぞれについて,PMOS,NMOSトランジスタのゲート電圧とバックゲート電圧とが示されている。図9には,横軸の入力電圧Vinに対応して,縦軸のPMOS,NMOSトランジスタのゲート電圧Vg(pch),Vg(nch)と,バックゲート電圧Vbg(pch),Vbg(nch)とが示されている。破線がPMOSトランジスタのゲート電圧Vg(pch),バックゲート電圧Vbg(pch)であり,実線がNMOSトランジスタのゲート電圧Vg(nch),バックゲート電圧Vbg(nch)である。図9の横軸の0〜1.7V,1.7〜3.3V,3.3〜5Vが,図8のM1,M2,M3に対応する。

【0032】

図9の破線で示されるPMOSトランジスタの場合は,入力電圧Vinが0〜3.3(=0+Vr(pch))の場合(図8の範囲M1,M2)は,バックゲート電圧Vbg(pch)をPMOSトランジスタのゲート耐圧Vr(pch)=3.3Vにし,ゲート電圧Vg(pch)をバックゲート電圧Vbg(pch)よりゲート耐圧Vr(pch)=3.3Vだけ低い0Vにする。これにより,バックゲート電圧Vbg(pch)=3.3Vは,入力電圧Vin=0〜3.3V以上に保たれドレイン,ソース領域からバックゲート領域への順方向のリーク電流は発生せず,ゲート・バックゲート間がゲート耐圧Vr(pch)以下に保たれてゲート破壊も起きずに,導通状態にすることができる。

【0033】

そして,入力電圧Vinが3.3〜5Vの場合(図8の範囲M3)は,バックゲート電圧Vbg(pch)を入力電圧Vin(3.3〜5V)と同じにし,ゲート電圧Vg(pch)をバックゲート電圧Vbg(pch)よりゲート耐圧Vr(pch)=3.3Vだけ低くする。つまり,バックゲート電圧とゲート電圧とが入力電圧Vinに応じて上昇するように可変制御される。これにより,バックゲート電圧Vbg(pch)は入力電圧Vin以上であるので,リーク電流は発生せず,ゲート破壊も生じないで,導通状態を保つことができる。PMOSトランジスタの閾値電圧Vth(pch)は-1V未満であるので,ゲート電圧Vg(pch)の0〜1.7Vは入力電圧Vinの3.3〜5Vよりその閾値電圧Vth(pch)以上低く,PMOSトランジスタは導通状態を保つことができる。

【0034】

一方,図9の実線で示されるNMOSトランジスタの場合は,入力電圧Vinが5〜1.7(=5-Vr(nch))の場合(図8の範囲M3,M2)は,バックゲート電圧Vbg(nch)を5VよりNMOSトランジスタのゲート耐圧Vr(npch)=3.3Vだけ低い電位1.7(=5-3.3)Vにし,ゲート電圧Vg(nch)をバックゲート電圧Vbg(nch)よりゲート耐圧Vr(nch)=3.3Vだけ高い5Vにする。これにより,バックゲート電圧Vbg(nch)=1.7Vは,入力電圧Vin=5〜1.7V以下に保たれて,ドレイン,ソース領域にバックゲート領域からの順方向のリーク電流は発生せず,ゲート・バックゲート間がゲート耐圧Vr(nch)以下に保たれてゲート破壊も起きずに,導通状態にすることができる。

【0035】

そして,入力電圧Vinが1.7〜0Vの場合(図8の範囲M1)は,バックゲート電圧Vbg(nch)を入力電圧Vin(1.7〜0V)と同じにし,ゲート電圧Vg(nch)をバックゲート電圧Vbg(nch)よりゲート耐圧Vr(nch)=3.3Vだけ高くする。つまり,バックゲート電圧とゲート電圧とが入力電圧Vinに応じて下降するように可変制御される。これにより,バックゲート電圧Vbg(nch)は入力電圧Vin以下であるので,リーク電流は発生せず,ゲート破壊も生じないで,導通状態を保つことができる。NMOSトランジスタの閾値電圧Vth(nch)は+1V未満であるので,ゲート電圧Vg(nch)の5〜3.3Vは入力電圧Vinの1.7〜0Vよりその閾値電圧Vth(nch)以上高く,NMOSトランジスタは導通状態を保つことができる。

【0036】

図9では,PMOSとNMOSトランジスタの耐圧Vr(pch),Vr(nch)が共に3.3Vを前提にしているので,入力電圧Vinが5Vの場合のPMOSのゲート電圧Vg(pch)とNMOSのバックゲートVbg(nch)とが1.7Vと一致し,入力電圧Vinが0Vの場合のゲート電圧Vg(nch)とバックゲート電圧Vbg(pch)とが3.3Vと一致している。両トランジスタの耐圧が異なる場合は,一致しないことがある。

【0037】

図10は,上記の3つの入力電圧範囲M1,M2,M3でのPMOS,NMOSトランジスタのオン抵抗を示す図である。PMOSトランジスタの場合,入力電圧Vinが範囲M1(0〜1.7V)と範囲M2(1.7〜3.3V)では,ゲート電圧Vg(pch)=0V,バックゲート電圧Vbg(pch)=3.3Vと固定され,範囲M3(3.3〜5V)では,入力電圧Vinに応じて,バックゲート電圧をVbg(pch)=Vin=3.3〜5Vと可変制御し,ゲート電圧をVg(pch)=Vin-Vr(pch)=0〜1.7Vと可変制御する。この可変制御によりドレイン,ソース領域でのリーク電流が防止される。

【0038】

一方,NMOSトランジスタの場合,入力電圧Vinが範囲M3(3.3〜5V)と範囲M2(1.7〜3.3V)では,ゲート電圧Vg(nch)=5V,バックゲート電圧Vbg(nch)=1.7Vと固定され,範囲M1(0〜1.7V)では,入力電圧Vinに応じて,バックゲート電圧がVbg(nch)=Vin=0〜1.7Vと可変制御し,ゲート電圧をVg(nch)=Vin-Vr(nch)=3.3〜5Vと可変制御する。この可変制御によりドレイン,ソース領域でのリーク電流が防止される。しかも,いずれの入力電圧の範囲でも,PMOSとNMOSトランジスタの合成オン抵抗Ronを小さくすることができる。

【0039】

上記の例では,入力電圧Vinの最大電圧Vmax=5Vに対して,ゲート耐圧Vr(pch),Vr(nch)=3.3Vが最大電圧の50%を超えている。それに対して,入力電圧Vinが最小電圧Vmin=0V〜最大電圧Vmaxのいずれかであり,最大電圧Vmaxに対してゲート耐圧Vr(pch),Vr(nch)が50%未満の例について,一般化したCMOSアナログスイッチ装置を説明する。

【0040】

図11は,本実施の形態における一般化したCMOSアナログスイッチ装置の入力電圧範囲M1,M2,M3におけるゲート電圧とバックゲート電圧を示した図である。図12は,PMOSトランジスタの入力電圧Vinに対するゲート電圧とバックゲート電圧を示した図である。図13は,NMOSトランジスタの入力電圧Vinに対するゲート電圧とバックゲート電圧を示した図である。

【0041】

まず,図12のPMOSトランジスタについて説明する。入力電圧Vinが0〜Vr(pch)では,ゲート電圧Vg(pch)=Vmin=0V,バックゲート電圧Vbg(pch)=Vmin+Vr(pch)=Vr(pch)と固定電位にされる。これにより,入力電圧Vinがゲート電圧Vg(pch)=0Vより閾値電圧Vth(pch)だけ高くなると導通し,しかも,バックゲート電圧は入力電圧以上であるのでリーク電流はなく,ゲート破壊もない。さらに,入力電圧VinがVr(pch)〜Vmaxでは,バックゲート電圧はVbg(pch)=Vinにし,ゲート電圧Vg(pch)はバックゲート電圧よりVr(pch)だけ低い電圧Vg(pch)=Vin-Vr(pch)と,入力電圧Vinに応じて変動する電圧に制御される。これにより,ゲート電圧Vg(pch)は入力電圧Vinより閾値電圧Vth(pch)以上低いのでPMOSトランジスタは導通し,しかも,バックゲート電圧は入力電圧以上であるのでリーク電流はなく,ゲート破壊もない。

【0042】

次に,図13のNMOSトランジスタについて説明する。入力電圧VinがVmax〜Vmax-Vr(nch)では,ゲート電圧Vg(nch)=Vmax,バックゲート電圧Vbg(nch)=Vmax-Vr(nch)と固定電位にされる。これにより,入力電圧Vinがゲート電圧Vg(nch)=Vmaxより閾値電圧Vth(nch)だけ低くなると導通し,しかも,バックゲート電圧は入力電圧以下であるのでリーク電流はなく,ゲート破壊もない。さらに,入力電圧VinがVmax-Vr(nch)〜Vminでは,バックゲート電圧をVbg(nch)=Vinに,ゲート電圧Vg(nch)はバックゲート電圧よりVr(nch)だけ高い電圧Vg(nch)=Vin+Vr(nch)にと,入力電圧Vinに応じて変動する電圧に制御される。これにより,ゲート電圧Vg(nch)は入力電圧Vinより閾値電圧Vth(nch)以上高いのでNMOSトランジスタは導通し,しかも,バックゲート電圧は入力電圧以下であるのでリーク電流はなく,ゲート破壊もない。

【0043】

図14は,図12,図13のPMOSトランジスタとNMOSトランジスタのゲート電圧とバックゲート電圧とを重ねて示した図である。図14では,PMOSとNMOSトランジスタのゲート耐圧Vr(pch),Vr(nch)が等しいVrであることを前提にして,図12,図13のPMOSトランジスタとNMOSトランジスタのゲート電圧とバックゲート電圧とを重ねて示している。

【0044】

図15は,一般化したCMOSアナログスイッチ装置の場合の3つの入力電圧の範囲M1,M2,M3でのPMOS,NMOSトランジスタのオン抵抗を示す図である。図15の例では,Vr(pch),Vr(nch)<Vmax/2であるので,3つの入力電圧の範囲M1,M2,M3は,図11に記載されるとおりであり,図10での3つの入力電圧の範囲M1,M2,M3とは異なっている。

【0045】

入力電圧が範囲M1の場合(0〜Vr(pch))では,PMOSトランジスタのゲート電圧とバックゲート電圧とは固定されているが,NMOSトランジスタのバックゲート電圧は入力電圧Vinと等しく,ゲート電圧はそれよりゲート耐圧Vr(nch)だけ高く(Vin+Vr(nch)),入力電圧Vinに応じて変動する電位にされる。これにより,NMOSトランジスタのリーク電流が回避される。

【0046】

入力電圧が範囲M2の場合(Vr(pch)〜(Vmax-Vr(nch))では,PMOS,NMOSトランジスタのバックゲート電圧は入力電圧Vinに等しく,ゲート電圧はそれぞれVin-Vr(pch),Vin+Vr(nch)にされる。つまり,入力電圧Vinに応じて変動する電位である。これにより,PMOS,NMOSトランジスタのいずれもリーク電流が回避される。

【0047】

入力電圧が範囲M3の場合((Vmax-Vr(nch))〜Vmax)では,PMOSトランジスタのバックゲート電圧は入力電圧Vinに等しく,ゲート電圧はVin-Vr(pch)に制御される。これにより,PMOSトランジスタのリーク電流は回避される。そして,NMOSトランジスタでは,ゲート電圧はVmaxに,バックゲート電圧はVmax-Vr(nch)に固定される。

【0048】

図16,図17は,一般化したCMOSアナログスイッチ装置のPMOS,NMOSトランジスタのゲート電圧とバックゲート電圧の変型例を示す図である。図12,図13と対比して以下説明する。

【0049】

図16のPMOSトランジスタの例では,入力電圧Vinが0V近傍の場合は,ゲート電圧Vg(pch)を0Vにし,バックゲート電圧Vbg(pch)はVr(pch)にする。ただし,入力電圧Vinが0V近傍より高く最大入力電圧Vmaxまでの間では,バックゲート電圧Vbg(pch)を入力電圧Vinより高くして,ドレイン,ソース領域とバックゲート領域との間のPN接合が順バイアスにしないようにし,且つ,ゲート電圧Vg(pch)が入力電圧Vinより閾値電圧Vth(pch)だけ低くなるようにして,ゲート電圧Vg(pch)とバックゲート電圧Vbg(pch)間の電圧をゲート耐圧Vr(pch)以下になるようにする。つまり,バックゲート電圧もゲート電圧も入力電圧Vinに応じて可変制御する。

【0050】

図17のNMOSトランジスタの例では,図16と逆に,入力電圧Vinが最大電圧Vmax近傍の場合は,ゲート電圧Vg(nch)をVmaxにし,バックゲート電圧Vbg(nch)はVmax-Vr(nch)にする。ただし,入力電圧VinがVmax近傍より低く最小入力電圧Vmin=0Vまでの間では,バックゲート電圧Vbg(nch)を入力電圧Vinより低くして,ドレイン,ソース領域とバックゲート領域との間のPN接合が順バイアスにしないようにし,且つ,ゲート電圧Vg(nch)が入力電圧Vinより閾値電圧Vth(nch)だけ高くなるようにして,ゲート電圧Vg(nch)とバックゲート電圧Vbg(nch)間の電圧をゲート耐圧Vr(nch)以下にする。この場合も,PMOSと同様に,バックゲート電圧もゲート電圧も入力電圧Vinに応じて可変制御する。

【0051】

図18は,可変電圧回路の回路図である。この可変電圧回路20は,図8,9に示した入力電圧Vin=0〜5V,PMOS,NMOSトランジスタのゲート耐圧が共にVr=3.3Vの例である。可変電圧回路20は,図1でも示したとおり半導体チップ内に設けられ,その電源電圧は例えば3.3Vである。図18の可変電圧回路20は,入力電圧Vinの電圧範囲を検出する入力電圧検出回路を構成する2つのコンパレータCMP10,CMP20と,コンパレータCMP10の出力に応じてオン,オフ制御される1対の第1スイッチS10,S11と,コンパレータCMP20の出力に応じてオン,オフ制御される1対の第2スイッチS20,S21とを有する。

【0052】

コンパレータCMP10は,入力電圧Vinを抵抗2R,R,Rで分圧した電圧を負極入力端子に入力し,電圧5V(=Vmax)、電圧1.7V(=Vmax-Vr(pch))を同様の抵抗で分圧した電圧を正極入力端子に入力し,両者を比較し, Vin<3.3Vであれば出力をLレベルにし,Vin>3.3Vであれば出力をHレベルにする。つまり,Vin<3.3VであればスイッチS10が導通しS11が非導通となり,PMOSトランジスタpchのバックゲート電圧Vbg(pch)には3.3Vが印加され,一方,Vin>3.3VであればスイッチS10が非導通となりS11が導通し,PMOSトランジスタpchのバックゲート電圧Vbg(pch)には入力電圧Vinが印加される。

【0053】

コンパレータCMP20は,入力電圧Vinを抵抗2R,R,Rで降圧した電圧を負極入力端子に入力し,電圧1.7V(=Vmax-Vr(nch))を同様の抵抗で降圧した電圧を正極入力端子に入力し,両者を比較し,Vin>1.7Vであれば出力をHレベルにし,Vin<1.7Vであれば出力をLレベルにする。つまり,Vin>1.7VであればスイッチS20が導通しS21が非導通となり,NMOSトランジスタnchのバックゲート電圧Vbg(nch)には1.7Vが印加され,一方,Vin<1.7VであればスイッチS20が非導通となりS21が導通し,NMOSトランジスタnchのバックゲート電圧Vbg(nch)には入力電圧Vinが印加される。

【0054】

可変電圧回路20は,PMOSトランジスタ用の電圧シフト回路SHF1と,PMOSトランジスタpchを導通または非導通に制御する第3スイッチS30とを有し,一方,NMOSトランジスタ用の電圧シフト回路SHF2と,NMOSトランジスタnchを導通または非導通に制御する第4スイッチS40とを有する。

【0055】

電圧シフト回路SHF1は,キャパシタC1と,充電用スイッチS50,S51と,電圧シフト用スイッチS52,S53とを有し,制御信号φs11によりオンに充電用スイッチS50,S51がされるとキャパシタC1が3.3Vに充電され,充電用スイッチS50,S51が制御信号φS11によりオフにされ,電圧シフト用スイッチS52,S53がオンになると,入力inより3.3V低い電圧が出力outに生成される。

【0056】

第3スイッチS30が,制御信号φs21に応答して端子B側に接続すると,PMOSトランジスタのゲート電圧がバックゲート電圧より3.3V低くなりPMOSトランジスタは導通し,端子A側に接続すると,ゲート電圧がバックゲート電圧と同じになり非導通になる。

【0057】

電圧シフト回路SHF2は,キャパシタC2と,充電用スイッチS60,S61と,電圧シフト用スイッチS62,S63とを有し,制御信号φs12により充電用スイッチS60,S61がオンにされるとキャパシタC2が3.3Vに充電され,制御信号φS12により充電用スイッチS60,S61がオフにされ,電圧シフト用スイッチS62,S63がオンになると,入力inより3.3V高い電圧が出力outに生成される。

【0058】

第4スイッチS40が,制御信号φs22に応答して端子B側に接続すると,NMOSトランジスタのゲート電圧がバックゲート電圧より3.3V高くなりNMOSトランジスタnchは導通し,端子A側に接続すると,ゲート電圧がバックゲート電圧と同じになり非導通になる。

【0059】

図19は,図18の可変電圧回路の動作を示すフローチャート図である。図18で示されるとおり,可変電圧回路20は,制御回路4からの制御信号φs11〜φs22により制御される。まず,ゲートとバックゲート間の電圧を生成するキャパシタC1,C2の充電が制御信号φs11,φs12により行われる(S10)。具体的には,電圧シフト回路SFH1では充電用スイッチS50,S51がオンになりキャパシタC1がゲート耐圧3.3Vに充電され,電圧シフト回路SFH2では充電用スイッチS60,S61がオンになりキャパシタC2もゲート耐圧3.3Vに充電される。

【0060】

そして,入力電圧Vinの電圧範囲を検出する入力電圧検出回路を構成する2つのコンパレータCMP10,CMP20が,それぞれ,入力電圧Vinがゲート耐圧3.3Vより高いか低いかと,最大入力電圧Vmax=5Vよりゲート耐圧3.3Vだけ低い電圧1.7V(=5-3.3)より高いか低いかとを検出している(S20)。すなわち,2つのコンパレータCMP10,CMP20の出力信号の組み合わせにより,入力電圧Vinが範囲M1(0≦Vin<1.7V),M2(1.7V≦Vin<3.3V),M3(3.3V≦Vin≦Vmax(5V))を検出する(S21,S22,S23)。この検出により,1対の第1スイッチS10,S11がPMOSトランジスタのバックゲート電圧Vbg(pch)に3.3Vまたは入力Vinのいずれかを選択して出力し,1対の第2スイッチS20,S21がNMOSトランジスタのバックゲート電圧Vbg(nch)に1.7Vまたは入力Vinのいずれかを選択して出力する。

【0061】

図20は,入力電圧Vinが範囲M1の場合の可変電圧回路の状態を示す図である。入力電圧が0≦Vin<1.7Vであるので,スイッチS10がオン,S11がオフとなり,バックゲート電圧Vbg(pch)は3.3Vになり,スイッチS20がオフ,S21がオンとなり,バックゲート電圧Vbg(nch)は入力電圧Vinになる。

【0062】

図21は,入力電圧Vinが範囲M2の場合の可変電圧回路の状態を示す図である。入力電圧が1.7V≦Vin<3.3Vであるので,スイッチS10がオン,S11がオフとなり,バックゲート電圧Vbg(pch)は3.3Vになり,スイッチS20がオン,S21がオフとなり,バックゲート電圧Vbg(nch)は1.7Vになる。

【0063】

図22は,入力電圧Vinが範囲M3の場合の可変電圧回路の状態を示す図である。入力電圧が3.3V≦Vin≦Vmax(5V)であるので,スイッチS10がオフ,S11がオンとなり,バックゲート電圧Vbg(pch)は入力電圧Vinになり,スイッチS20がオン,S21がオフとなり,バックゲート電圧Vbg(nch)は1.7Vになる。

【0064】

そして,制御信号φs11,φs12により,電圧シフト回路SHF1内の充電用スイッチS50,S51をオフにし,電圧シフト用スイッチS52,S53をオンにし,電圧シフト回路SHF2内の充電用スイッチS60,S61をオフにし,電圧シフト用スイッチS62,S63をオンにする(S30)。これにより,電圧シフト回路SHF1の出力outはバックゲート電圧Vbg(pch)よりゲート耐圧3.3Vだけ低い電位になり,電圧シフト回路SHF2の出力outはバックゲート電圧Vbg(nch)よりゲート耐圧3.3Vだけ高い電位になる。

【0065】

最後に,制御回路からのアナログスイッチを導通または非導通に制御する制御信号φs21,φs22に応じて,第3スイッチS30が端子AまたはBに接続され,第4スイッチS40が端子AまたはBに接続される。両スイッチS30,S40が端子B側に接続されれば,PMOSトランジスタpchのゲート電圧はVbg(pch)-3.3Vに,NMOSトランジスタnchのゲート電圧はVbg(nch)+3.3Vになり,両トランジスタは導通状態になる。一方,両スイッチS30,S40が端子A側に接続されれば,PMOS,NOSトランジスタのゲート電圧はそれぞれのバックゲート電圧Vbg(pch),Vbg(nch)になり,両トランジスタは非導通状態になる。

【0066】

上記の工程S10とS30は,CMOSアナログスイッチのスイッチングサイクル毎に行う必要はない。少なくとも,1回のスイッチングサイクルでは,工程S20とS40とが行われる。

【0067】

以上の通り,本実施の形態のCMOSアナログスイッチ装置によれば,ゲート耐圧以上の電圧範囲の入力信号に対して適切な導通状態になることができる。したがって,電源電圧が低くゲート耐圧が低いLSIチップ内に設けられたCMOSアナログスイッチが,電源電圧を超える高い入力電圧に対して,適切にスイッチングすることができる。

【0068】

以上の実施の形態をまとめると,次の付記のとおりである。

【0069】

(付記1)

入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチと,

前記入力端子に印加される入力電圧に応じて,前記Pチャネルトランジスタの第1ゲート電圧及び第1バックゲート電圧と,前記Nチャネルトランジスタの第2ゲート電圧及び第2バックゲート電圧とのそれぞれの電位を可変生成する可変電圧回路と,

前記アナログスイッチを導通または非導通に制御する制御信号を前記可変電圧回路に供給する制御回路とを有し,

前記可変電圧回路は,前記導通に制御する制御信号に応答して,前記可変生成される第1ゲート電圧と第2ゲート電圧とを前記PチャネルトランジスタとNチャネルトランジスタのゲートにそれぞれ出力する半導体装置。

【0070】

(付記2)

付記1において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記可変電圧回路は,前記Pチャネルトランジスタに対して,前記第1バックゲート電圧を前記入力電圧以上にし,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低くし,

前記可変電圧回路は,前記Nチャネルトランジスタに対して,前記第2バックゲート電圧を前記入力電圧以下にし,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高くする半導体装置。

【0071】

(付記3)

付記1または2において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記入力電圧は最小電圧から最大電圧までの間の電位を有し,

前記可変電圧回路は,前記Pチャネルトランジスタに対して,前記入力電圧が前記最小電圧以上で且つ前記最小電圧より前記第1ゲート耐圧だけ高い第1電圧以下の第1の電圧範囲の場合に,前記第1ゲート電圧を前記最小電圧にし,前記第1バックゲート電圧を前記最小電圧より前記第1ゲート耐圧だけ高くし,前記入力電圧が前記第1電圧以上で且つ前記最大電圧以下の第2の電圧範囲の場合に,前記第1バックゲート電圧を前記入力電圧と同じにし,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低くし,

前記可変電圧回路は,前記Nチャネルトランジスタに対して,前記入力電圧が前記最大電圧以下で且つ前記最大電圧より前記第2ゲート耐圧だけ低い第2電圧以上の第3の電圧範囲の場合に,前記第2ゲート電圧を前記最大電圧にし,前記第2バックゲート電圧を前記最大電圧より前記第2ゲート耐圧だけ低くし,前記入力電圧が前記第2電圧以下で且つ前記最小電圧以上の第4の電圧範囲の場合に,前記第2バックゲート電圧を前記入力電圧と同じにし,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高くする半導体装置。

【0072】

(付記4)

付記3において,

前記可変電圧回路は,

前記入力電圧が第1乃至第4の電圧範囲か否かを検出する入力電圧検出回路と,

前記入力電圧検出回路による第1または第2の電圧範囲の検出に応じて,前記第1バックゲート電圧の出力端子を前記最小電圧より前記第1ゲート耐圧だけ高い電圧に接続または前記入力端子に接続する第1スイッチと,

前記第1ゲート電圧の出力端子に前記第1バックゲート電圧の出力端子より前記第1ゲート耐圧だけ低い電圧を供給する第1電圧シフト回路と,

前記入力電圧検出回路により第3または第4の電圧範囲の検出に応じて,前記第2バックゲート電圧の出力端子を前記最大電圧より前記第2ゲート耐圧だけ低い電圧に接続または前記入力端子に接続する第2スイッチと,

前記第2ゲート電圧の出力端子に前記第2バックゲート電圧の出力端子より前記第2ゲート耐圧だけ高い電圧を供給する第2電圧シフト回路とを有する半導体装置。

【0073】

(付記5)

付記4において,

前記可変電圧回路は,さらに,

前記導通または非導通に制御する制御信号に応答して,前記第1ゲート電圧の出力端子に,前記第1バックゲート電圧の出力端子より前記第1ゲート耐圧だけ低い電圧または前記第1バックゲート電圧をそれぞれ接続する第3スイッチと,

前記導通または非導通に制御する制御信号に応答して,前記第2ゲート電圧の出力端子に,前記前記第2バックゲート電圧の出力端子より前記第2ゲート耐圧だけ高い電圧または前記第2バックゲート電圧をそれぞれ接続する第4スイッチとを有する半導体装置。

【0074】

(付記6)

付記1乃至5のいずれかに記載の半導体装置と,

被試験装置の外部端子に接続された入力端子と,

前記入力端子に前記半導体装置を介して接続され,前記アナログスイッチが導通したときに,前記被試験装置の外部端子の電圧を測定する電圧測定部とを有する試験用半導体装置。

【0075】

(付記7)

入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチの制御方法において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記入力電圧は最小電圧から最大電圧までの間の電位を有し,

前記制御方法は,

前記入力電圧に応じて,前記Pチャネルトランジスタに対して,前記第1バックゲート電圧を前記入力電圧以上に制御し,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低く制御し,

前記入力電圧に応じて,前記Nチャネルトランジスタに対して,前記第2バックゲート電圧を前記入力電圧以下に制御し,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高く制御するアナログスイッチの制御方法。

【0076】

(付記8)

入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチの制御方法において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記入力電圧は最小電圧から最大電圧までの間の電位を有し,

前記制御方法は,

前記Pチャネルトランジスタに対して,前記入力電圧が前記最小電圧以上で且つ前記最小電圧より前記第1ゲート耐圧だけ高い第1電圧以下の第1の電圧範囲の場合に,前記第1ゲート電圧を前記最小電圧にし,前記第1バックゲート電圧を前記最小電圧より前記第1ゲート耐圧だけ高くし,前記入力電圧が前記第1電圧以上で且つ前記最大電圧以下の第2の電圧範囲の場合に,前記第1バックゲート電圧を前記入力電圧と同じにし,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低くし,

前記Nチャネルトランジスタに対して,前記入力電圧が前記最大電圧以下で且つ前記最大電圧より前記第2ゲート耐圧だけ低い第2電圧以上の第3の電圧範囲の場合に,前記第2ゲート電圧を前記最大電圧にし,前記第2バックゲート電圧を前記最大電圧より前記第2ゲート耐圧だけ低くし,前記入力電圧が前記第2電圧以下で且つ前記最小電圧以上の第4の電圧範囲の場合に,前記第2バックゲート電圧を前記入力電圧と同じにし,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高くするアナログスイッチの制御方法。

【符号の説明】

【0077】

pch:PMOSトランジスタ nch:NMOSトランジスタ

IN:入力端子 OUT:出力端子

20:可変電圧回路 4:制御回路

φs:制御信号

【特許請求の範囲】

【請求項1】

入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチと,

前記入力端子に印加される入力電圧に応じて,前記Pチャネルトランジスタの第1ゲート電圧及び第1バックゲート電圧と,前記Nチャネルトランジスタの第2ゲート電圧及び第2バックゲート電圧とのそれぞれの電位を可変生成する可変電圧回路と,

前記アナログスイッチを導通または非導通に制御する制御信号を前記可変電圧回路に供給する制御回路とを有し,

前記可変電圧回路は,前記導通に制御する制御信号に応答して,前記可変生成される第1ゲート電圧と第2ゲート電圧とを前記PチャネルトランジスタとNチャネルトランジスタのゲートにそれぞれ出力する半導体装置。

【請求項2】

請求項1において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記可変電圧回路は,前記Pチャネルトランジスタに対して,前記第1バックゲート電圧を前記入力電圧以上にし,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低くし,

前記可変電圧回路は,前記Nチャネルトランジスタに対して,前記第2バックゲート電圧を前記入力電圧以下にし,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高くする半導体装置。

【請求項3】

請求項1または2において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記入力電圧は最小電圧から最大電圧までの間の電位を有し,

前記可変電圧回路は,前記Pチャネルトランジスタに対して,前記入力電圧が前記最小電圧以上で且つ前記最小電圧より前記第1ゲート耐圧だけ高い第1電圧以下の第1の電圧範囲の場合に,前記第1ゲート電圧を前記最小電圧にし,前記第1バックゲート電圧を前記最小電圧より前記第1ゲート耐圧だけ高くし,前記入力電圧が前記第1電圧以上で且つ前記最大電圧以下の第2の電圧範囲の場合に,前記第1バックゲート電圧を前記入力電圧と同じにし,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低くし,

前記可変電圧回路は,前記Nチャネルトランジスタに対して,前記入力電圧が前記最大電圧以下で且つ前記最大電圧より前記第2ゲート耐圧だけ低い第2電圧以上の第3の電圧範囲の場合に,前記第2ゲート電圧を前記最大電圧にし,前記第2バックゲート電圧を前記最大電圧より前記第2ゲート耐圧だけ低くし,前記入力電圧が前記第2電圧以下で且つ前記最小電圧以上の第4の電圧範囲の場合に,前記第2バックゲート電圧を前記入力電圧と同じにし,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高くする半導体装置。

【請求項4】

請求項3において,

前記可変電圧回路は,

前記入力電圧が第1乃至第4の電圧範囲か否かを検出する入力電圧検出回路と,

前記入力電圧検出回路による第1または第2の電圧範囲の検出に応じて,前記第1バックゲート電圧の出力端子を前記最小電圧より前記第1ゲート耐圧だけ高い電圧に接続または前記入力端子に接続する第1スイッチと,

前記第1ゲート電圧の出力端子に前記第1バックゲート電圧の出力端子より前記第1ゲート耐圧だけ低い電圧を供給する第1電圧シフト回路と,

前記入力電圧検出回路により第3または第4の電圧範囲の検出に応じて,前記第2バックゲート電圧の出力端子を前記最大電圧より前記第2ゲート耐圧だけ低い電圧に接続または前記入力端子に接続する第2スイッチと,

前記第2ゲート電圧の出力端子に前記第2バックゲート電圧の出力端子より前記第2ゲート耐圧だけ高い電圧を供給する第2電圧シフト回路とを有する半導体装置。

【請求項5】

請求項4において,

前記可変電圧回路は,さらに,

前記導通または非導通に制御する制御信号に応答して,前記第1ゲート電圧の出力端子に,前記第1バックゲート電圧の出力端子より前記第1ゲート耐圧だけ低い電圧または前記第1バックゲート電圧をそれぞれ接続する第3スイッチと,

前記導通または非導通に制御する制御信号に応答して,前記第2ゲート電圧の出力端子に,前記前記第2バックゲート電圧の出力端子より前記第2ゲート耐圧だけ高い電圧または前記第2バックゲート電圧をそれぞれ接続する第4スイッチとを有する半導体装置。

【請求項6】

入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチの制御方法において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記入力電圧は最小電圧から最大電圧までの間の電位を有し,

前記制御方法は,

前記入力電圧に応じて,前記Pチャネルトランジスタに対して,前記第1バックゲート電圧を前記入力電圧以上に制御し,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低く制御し,

前記入力電圧に応じて,前記Nチャネルトランジスタに対して,前記第2バックゲート電圧を前記入力電圧以下に制御し,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高く制御するアナログスイッチの制御方法。

【請求項7】

入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチの制御方法において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記入力電圧は最小電圧から最大電圧までの間の電位を有し,

前記制御方法は,

前記Pチャネルトランジスタに対して,前記入力電圧が前記最小電圧以上で且つ前記最小電圧より前記第1ゲート耐圧だけ高い第1電圧以下の第1の電圧範囲の場合に,前記第1ゲート電圧を前記最小電圧にし,前記第1バックゲート電圧を前記最小電圧より前記第1ゲート耐圧だけ高くし,前記入力電圧が前記第1電圧以上で且つ前記最大電圧以下の第2の電圧範囲の場合に,前記第1バックゲート電圧を前記入力電圧と同じにし,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低くし,

前記Nチャネルトランジスタに対して,前記入力電圧が前記最大電圧以下で且つ前記最大電圧より前記第2ゲート耐圧だけ低い第2電圧以上の第3の電圧範囲の場合に,前記第2ゲート電圧を前記最大電圧にし,前記第2バックゲート電圧を前記最大電圧より前記第2ゲート耐圧だけ低くし,前記入力電圧が前記第2電圧以下で且つ前記最小電圧以上の第4の電圧範囲の場合に,前記第2バックゲート電圧を前記入力電圧と同じにし,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高くするアナログスイッチの制御方法。

【請求項1】

入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチと,

前記入力端子に印加される入力電圧に応じて,前記Pチャネルトランジスタの第1ゲート電圧及び第1バックゲート電圧と,前記Nチャネルトランジスタの第2ゲート電圧及び第2バックゲート電圧とのそれぞれの電位を可変生成する可変電圧回路と,

前記アナログスイッチを導通または非導通に制御する制御信号を前記可変電圧回路に供給する制御回路とを有し,

前記可変電圧回路は,前記導通に制御する制御信号に応答して,前記可変生成される第1ゲート電圧と第2ゲート電圧とを前記PチャネルトランジスタとNチャネルトランジスタのゲートにそれぞれ出力する半導体装置。

【請求項2】

請求項1において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記可変電圧回路は,前記Pチャネルトランジスタに対して,前記第1バックゲート電圧を前記入力電圧以上にし,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低くし,

前記可変電圧回路は,前記Nチャネルトランジスタに対して,前記第2バックゲート電圧を前記入力電圧以下にし,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高くする半導体装置。

【請求項3】

請求項1または2において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記入力電圧は最小電圧から最大電圧までの間の電位を有し,

前記可変電圧回路は,前記Pチャネルトランジスタに対して,前記入力電圧が前記最小電圧以上で且つ前記最小電圧より前記第1ゲート耐圧だけ高い第1電圧以下の第1の電圧範囲の場合に,前記第1ゲート電圧を前記最小電圧にし,前記第1バックゲート電圧を前記最小電圧より前記第1ゲート耐圧だけ高くし,前記入力電圧が前記第1電圧以上で且つ前記最大電圧以下の第2の電圧範囲の場合に,前記第1バックゲート電圧を前記入力電圧と同じにし,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低くし,

前記可変電圧回路は,前記Nチャネルトランジスタに対して,前記入力電圧が前記最大電圧以下で且つ前記最大電圧より前記第2ゲート耐圧だけ低い第2電圧以上の第3の電圧範囲の場合に,前記第2ゲート電圧を前記最大電圧にし,前記第2バックゲート電圧を前記最大電圧より前記第2ゲート耐圧だけ低くし,前記入力電圧が前記第2電圧以下で且つ前記最小電圧以上の第4の電圧範囲の場合に,前記第2バックゲート電圧を前記入力電圧と同じにし,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高くする半導体装置。

【請求項4】

請求項3において,

前記可変電圧回路は,

前記入力電圧が第1乃至第4の電圧範囲か否かを検出する入力電圧検出回路と,

前記入力電圧検出回路による第1または第2の電圧範囲の検出に応じて,前記第1バックゲート電圧の出力端子を前記最小電圧より前記第1ゲート耐圧だけ高い電圧に接続または前記入力端子に接続する第1スイッチと,

前記第1ゲート電圧の出力端子に前記第1バックゲート電圧の出力端子より前記第1ゲート耐圧だけ低い電圧を供給する第1電圧シフト回路と,

前記入力電圧検出回路により第3または第4の電圧範囲の検出に応じて,前記第2バックゲート電圧の出力端子を前記最大電圧より前記第2ゲート耐圧だけ低い電圧に接続または前記入力端子に接続する第2スイッチと,

前記第2ゲート電圧の出力端子に前記第2バックゲート電圧の出力端子より前記第2ゲート耐圧だけ高い電圧を供給する第2電圧シフト回路とを有する半導体装置。

【請求項5】

請求項4において,

前記可変電圧回路は,さらに,

前記導通または非導通に制御する制御信号に応答して,前記第1ゲート電圧の出力端子に,前記第1バックゲート電圧の出力端子より前記第1ゲート耐圧だけ低い電圧または前記第1バックゲート電圧をそれぞれ接続する第3スイッチと,

前記導通または非導通に制御する制御信号に応答して,前記第2ゲート電圧の出力端子に,前記前記第2バックゲート電圧の出力端子より前記第2ゲート耐圧だけ高い電圧または前記第2バックゲート電圧をそれぞれ接続する第4スイッチとを有する半導体装置。

【請求項6】

入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチの制御方法において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記入力電圧は最小電圧から最大電圧までの間の電位を有し,

前記制御方法は,

前記入力電圧に応じて,前記Pチャネルトランジスタに対して,前記第1バックゲート電圧を前記入力電圧以上に制御し,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低く制御し,

前記入力電圧に応じて,前記Nチャネルトランジスタに対して,前記第2バックゲート電圧を前記入力電圧以下に制御し,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高く制御するアナログスイッチの制御方法。

【請求項7】

入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチの制御方法において,

前記Pチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第1ゲート耐圧を有し,前記Nチャネルトランジスタはゲート絶縁膜が破壊されない最大許容電圧である第2ゲート耐圧を有し,

前記入力電圧は最小電圧から最大電圧までの間の電位を有し,

前記制御方法は,

前記Pチャネルトランジスタに対して,前記入力電圧が前記最小電圧以上で且つ前記最小電圧より前記第1ゲート耐圧だけ高い第1電圧以下の第1の電圧範囲の場合に,前記第1ゲート電圧を前記最小電圧にし,前記第1バックゲート電圧を前記最小電圧より前記第1ゲート耐圧だけ高くし,前記入力電圧が前記第1電圧以上で且つ前記最大電圧以下の第2の電圧範囲の場合に,前記第1バックゲート電圧を前記入力電圧と同じにし,前記第1ゲート電圧を前記第1バックゲート電圧より前記第1ゲート耐圧だけ低くし,

前記Nチャネルトランジスタに対して,前記入力電圧が前記最大電圧以下で且つ前記最大電圧より前記第2ゲート耐圧だけ低い第2電圧以上の第3の電圧範囲の場合に,前記第2ゲート電圧を前記最大電圧にし,前記第2バックゲート電圧を前記最大電圧より前記第2ゲート耐圧だけ低くし,前記入力電圧が前記第2電圧以下で且つ前記最小電圧以上の第4の電圧範囲の場合に,前記第2バックゲート電圧を前記入力電圧と同じにし,前記第2ゲート電圧を前記第2バックゲート電圧より前記第2ゲート耐圧だけ高くするアナログスイッチの制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【公開番号】特開2013−84761(P2013−84761A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2011−223575(P2011−223575)

【出願日】平成23年10月11日(2011.10.11)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成23年10月11日(2011.10.11)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]