半導体装置及び半導体装置の作製方法

【課題】結晶性の高い酸化物半導体をチャネル層に用いて、優れた特性を有する半導体装置を提供することを課題の一つとする。また、下地膜の平坦性を向上させた半導体装置を提供する。

【解決手段】トランジスタの下地膜に化学機械研磨処理を行い、化学機械研磨処理した後、プラズマ処理を行うことで、下地膜の中心線平均粗さRa75値を、0.1nm未満とすることができる。プラズマ処理及び化学機械研磨処理の組み合わせにより得られた平坦性を有する下地膜上に結晶性の高い酸化物半導体層を形成することで、半導体装置の特性向上を図る。

【解決手段】トランジスタの下地膜に化学機械研磨処理を行い、化学機械研磨処理した後、プラズマ処理を行うことで、下地膜の中心線平均粗さRa75値を、0.1nm未満とすることができる。プラズマ処理及び化学機械研磨処理の組み合わせにより得られた平坦性を有する下地膜上に結晶性の高い酸化物半導体層を形成することで、半導体装置の特性向上を図る。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、酸化物半導体膜を用いる半導体装置及び半導体装置の作製方法に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路及び電子機器は全て半導体装置である。

【背景技術】

【0003】

近年、携帯電話等に代表されるモバイルコミニュケーション市場は、急速に発展している。搭載部品である半導体集積回路に対する低消費電力化、高集積化、多機能化、高速化などの要求が高まるにつれて、トランジスタの特性向上が求められている。

【0004】

トランジスタの特性を示す指標の一つに、S値が用いられる。S値とは、ドレイン電圧一定下で、ドレイン電流を一桁変化させるために必要な、ゲート電圧の変化量を表す。S値が小さいほどドレイン電流の制御性に優れる。トランジスタの微細化等に起因して、現状では、S値を、80mV/dec以下にすることは難しい。

【0005】

また、シリコン系半導体材料に代わって非晶質の酸化物半導体材料を用いてトランジスタを作製し、電子デバイスなどに応用する技術が注目されている。例えば、トランジスタのチャネル層として、電子キャリア濃度が1018/cm3未満であるインジウム(In)、ガリウム(Ga)、及び亜鉛(Zn)を含む非晶質の酸化物半導体材料を用いてトランジスタを作製する技術が開示されている(特許文献1参照。)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−165529号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

トランジスタの特性向上のためには、酸化物半導体層の結晶性及び、下地膜と酸化物半導体層との界面特性を良好にすることが重要である。下地膜の平坦性を示す指標として、中心線平均粗さRa75値を用いることができる。下地膜の中心線平均粗さRa75値が大きい場合、下地膜上に形成される酸化物半導体層の結晶化が阻害され、結晶性が低減化されることで、結果的にトランジスタの電気特性の悪化や信頼性の低下を招く。

【0008】

上述した問題を鑑みて、結晶性の高い酸化物半導体をチャネル層に用いて、優れた特性を有する半導体装置を提供することを課題の一つとする。

【0009】

また、下地膜の平坦性を向上させた半導体装置を提供することを課題の一つとする。

【課題を解決するための手段】

【0010】

中心線平均粗さRa75値を小さくした下地膜上に、結晶性の高い酸化物半導体層を形成することで、半導体装置の特性向上を図る。

【0011】

本明細書で開示する本発明の一態様は、基板上に下地膜を形成し、下地膜にCMP処理を行い、CMP処理した後、プラズマ処理を行い、プラズマ処理及びCMP処理により得られた平坦な表面上に酸化物半導体層を形成する半導体装置の作製方法である。

【0012】

上記において、プラズマ処理は、希ガスを用いたプラズマ処理であることを特徴とする半導体装置の作製方法である。

【0013】

また、本明細書で開示する本発明の一態様は、基板上に下地膜を形成し、下地膜に第1のプラズマ処理を行い、第1のプラズマ処理した後、CMP処理を行い、CMP処理後、第2のプラズマ処理を行い、第1のプラズマ処理、CMP処理、及び第2のプラズマ処理により得られた平坦な表面上に酸化物半導体層を形成する半導体装置の作製方法である。

【0014】

上記において、第1のプラズマ処理及び第2のプラズマ処理は、希ガスを用いたプラズマ処理であることを特徴とする半導体装置の作製方法である。

【0015】

上記において、下地膜は、酸化シリコン膜、酸化ガリウム膜、酸化ハフニウム膜、または酸化アルミニウム膜であることを特徴とする半導体装置の作製方法である。

【0016】

また、上記において、基板は半導体基板であってもよい。

【0017】

また、上記において、基板はガラス基板であってもよい。

【0018】

また、上記において、プラズマ処理は平行平板型のプラズマ装置よりも高密度のプラズマを発生させることのできるICPエッチング装置で行うことが好ましい。

【発明の効果】

【0019】

プラズマ処理及びCMP処理を組み合わせて、下地膜の中心線平均粗さRa75値を、0.1nm未満とすることができ、半導体装置のS値を向上させることができる。

【図面の簡単な説明】

【0020】

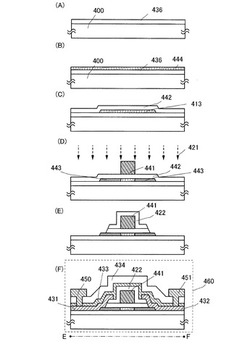

【図1】本発明のトランジスタの断面を示す図。

【図2】本発明のトランジスタの上面を示す図。

【図3】本発明のトランジスタの断面を示す図。

【図4】本発明のトランジスタのVg−Id曲線を示すグラフ。

【図5】基板中央と基板端部における下地膜表面のAFMによるサンプルの断面曲線を示すグラフ。

【図6】基板中央と基板端部における下地膜表面のAFMによるサンプルの断面曲線を示すグラフ。

【図7】半導体装置の作製工程を示す断面図。

【図8】本発明の一態様を示すブロック図及び等価回路図である。

【図9】電子機器の一態様を示す図である。

【発明を実施するための形態】

【0021】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0022】

(実施の形態1)

本実施の形態では、以下に示す手順で単結晶シリコン基板上の下地膜に平坦化処理を行い、その上に酸化物半導体層を有するトランジスタを作製し、下地膜の平坦性とトランジスタ特性、特にS値との関係を示す。なお、トランジスタの作製工程の断面図を図1に、作製したトランジスタの上面図を図2に示す。

【0023】

また、比較のため、下地膜に平坦化処理を行わないで作製したトランジスタもトランジスタ特性を測定する。

【0024】

まず、図1(A)に示すように、単結晶シリコンからなる基板400上に膜厚300nmの下地膜436を形成する。下地膜436の成膜前にアルゴンガスを導入してプラズマを発生させる逆スパッタを3分間行う。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。

【0025】

下地膜436としては、酸化シリコン層(SiOx(x>2))、酸化窒化シリコン層、窒化酸化シリコン層、酸化ガリウム層、酸化ハフニウム層、酸化アルミニウム層、珪酸ハフニウム層、珪酸ハフニウムオキシナイトライド層、ハフニウムアルミネート層を単層で又は積層して形成することができる。

【0026】

本実施の形態では、スパッタリング法を用いて酸化シリコン層を形成する。

【0027】

次いで、下地膜436表面に化学機械研磨(CMP:Chemical Mechanical Polishing)処理を行った後、Kr、Xe、Arなどの希ガスを用いたプラズマ処理を行い、露出している下地膜436の表面平坦化処理を行う。CMP処理の条件は、CMP研磨パッドとして硬質ポリウレタンパッドを用い、スラリーとしてはNP8020(ニッタ・ハース株式会社製)の原液(シリカ粒径60nm〜80nm)を用い、研磨時間0.5分、研磨圧0.001MPa、基板を固定している側のスピンドル回転数は60rpm、研磨布(研磨パッド)が固定されているテーブル回転数は56rpmとする。

【0028】

本実施の形態では、CMP処理を行った後、Arガスを用いたプラズマ処理を行い、下地膜表面の平坦性を原子間力顕微鏡(AFM:Atomic Force Microscope)を用いて測定すると中心線平均粗さRa75は0.12nmである。なお、AFMの測定領域は1μm×1μmである。

【0029】

なお、Ra75とは、JIS B 0031・JIS B 0061で定義されている中心線平均粗さを曲面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」で表現できる。

【0030】

また、上記作製方法において、Arガスを用いたプラズマ処理は、ICP(Inductively Coupled Plasma)エッチング装置を用いることが好ましい。本実施の形態では、コイル型の電極に電力を500W印加し、基板側にバイアス電力を100W(RF)印加し、流量100sccmのArガスをエッチング装置内に導入して、圧力1.35Paに設定し、基板温度を−10℃に設定してプラズマ処理を180秒行う。このプラズマ処理によって下地膜436の膜厚が約10nm程度薄くなる。

【0031】

また、コイルのインダクタンスを低下させるためにコイルを分割したマルチスパイラル方式のICPエッチング装置や、くし形コイルを円状の平板に配置したスポーク形のICPエッチング装置を用いてもよい。

【0032】

また、ICP型エッチング装置に限定されず、他のプラズマ処理装置を用いて下地膜436の平坦化を行ってもよい。

【0033】

なお、比較のため、平坦化を行わない下地膜表面をAFMで測定すると中心線平均粗さRa75は0.91nmである。また、CMP処理のみを行って下地膜表面をAFMで測定すると中心線平均粗さRa75は0.21nmである。

【0034】

次いで、図1(B)に示すように、スパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて酸化物半導体膜444を成膜する。

【0035】

酸化物半導体膜444の材料としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含む非単結晶であることが好ましい。特にInとZnを含むことが好ましい。また、該酸化物を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

【0036】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

【0037】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Ga系酸化物、三元系金属の酸化物であるIn−Ga−Zn系酸化物(IGZOとも表記する)、In−Al−Zn系酸化物、In−Sn−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物、四元系金属の酸化物であるIn−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物を用いることができる。

【0038】

なお、ここで、例えば、In−Ga−Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0039】

酸化物半導体膜は、好ましくはスパッタリング法により、基板加熱温度を100℃以上600℃以下、好ましくは150℃以上550℃以下、さらに好ましくは200℃以上500℃以下とし、酸素ガス雰囲気で成膜する。酸化物半導体膜の厚さは、1nm以上40nm以下、好ましくは3nm以上20nm以下とする。成膜時の基板加熱温度が高いほど、得られる酸化物半導体膜の不純物濃度は低くなる。また、酸化物半導体膜中の原子配列が整い、高密度化され、多結晶が形成されやすくなる。さらに、酸素ガス雰囲気で成膜することでも、希ガスなどの余分な原子が含まれないため、多結晶が形成されやすくなる。ただし、酸素ガスと希ガスの混合雰囲気としてもよく、その場合は酸素ガスの割合は30体積%以上、好ましくは50体積%以上、さらに好ましくは80体積%以上とする。

【0040】

本実施の形態では、酸化物半導体膜444であるIn−Ga−Zn−O膜を10nmの厚さで成膜する。成膜条件の一例としては、基板温度300℃、圧力0.4Pa、直流(DC)電源0.5kW、酸素とアルゴンの混合(酸素流量30sccm、アルゴン流量15sccm)雰囲気下の条件が適用される。

【0041】

そして、酸化物半導体膜444の成膜後に加熱処理を行う。この加熱処理によって酸化物半導体膜444の脱水化または脱水素化を行うことができる。加熱処理の温度は、400℃以上基板の歪み点未満とする。本実施の形態では、成膜後に、大気に触れることなく、スパッタ成膜装置内で基板を保持し、酸化物半導体膜444に対して減圧下400℃において30分間の加熱処理を行う。

【0042】

加熱処理の雰囲気は、減圧下に限定されず、水、水素などが含まれない雰囲気(露点が−40℃以下、好ましくは−60℃以下)、例えば不活性雰囲気または酸化性雰囲気で行う(図1(B)参照)。

【0043】

なお、加熱処理は成膜室内に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を用いてもよい。例えば、電気炉、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。高温のガスには、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

【0044】

次いで、図1(C)に示すように、酸化物半導体膜444を第1のフォトリソグラフィ工程により島状の酸化物半導体層413に加工する。なお、ここでの酸化物半導体膜444のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。

【0045】

次いで、ゲート絶縁層442を1nm以上200nm以下の厚さで成膜する(図1(C)参照)。ゲート絶縁層442は、スパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法を用いることができる。本実施の形態では、PCVD法を用いて酸化窒化シリコン膜を30nmの厚さで成膜する。

【0046】

次いで、ゲート電極として機能する電極を形成するための金属膜を形成する。金属膜の材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて形成することができる。また、ゲート電極を積層構造とし、その一層として窒素を含む金属酸化物、具体的には、窒素を含むIn−Ga−Zn−O膜や、窒素を含むIn−Sn−O膜や、窒素を含むIn−Ga−O膜や、窒素を含むIn−Zn−O膜や、窒素を含むSn−O膜や、窒素を含むIn−O膜や、金属窒化膜(InN、SnNなど)を用いてもよい。これらの膜は5電子ボルト、好ましくは5.5電子ボルト以上の仕事関数を有し、ゲート電極として用いた場合、トランジスタの電気特性のしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現できる。

【0047】

本実施の形態では、金属膜を積層膜として、膜厚30nmの窒化タンタル膜上に膜厚135nmのタングステン膜を形成する。

【0048】

窒化タンタル膜は、スパッタリング装置を用い、アルゴン:窒素=5:1の混合雰囲気で電力を1000W(DC)として成膜する。なお、成膜時に基板加熱は行っていない。タングステン膜は、スパッタリング装置を用い、アルゴン雰囲気で電力を4000W(DC)として成膜する。なお、成膜時の基板加熱温度は200℃とする。

【0049】

次いで、図1(D)に示すように、第2のフォトリソグラフィ工程によって窒化タンタル膜およびタングステン膜を加工して、ゲート電極441を形成する。

【0050】

次いで、ゲート電極441をマスクとして、ゲート絶縁層442を通過させて島状の酸化物半導体層413にドーパント421を選択的に導入し、低抵抗領域443を自己整合的に形成する(図1(D)参照)。

【0051】

ドーパント421は、酸化物半導体膜444の導電率を変化させる不純物である。ドーパントとしては、15族元素(代表的にはリン(P)、砒素(As)、およびアンチモン(Sb))、ホウ素(B)、アルミニウム(Al)、窒素(N)、アルゴン(Ar)、ヘリウム(He)、ネオン(Ne)、インジウム(In)、フッ素(F)、塩素(Cl)、チタン(Ti)、及び亜鉛(Zn)のいずれかから選択される一以上を用いることができる。

【0052】

本実施の形態では、ホウ素(B)をイオン注入法により注入し、加速電圧10kV、ドーズ量を3×1015atoms/cm2とする。

【0053】

次いで、ゲート電極441を覆うためのゲート保護膜を形成する。ゲート保護膜の材料としては、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜を用いて形成することができる。本実施の形態では、PCVD法を用いて保護膜となる酸化窒化シリコン膜を150nmの厚さで成膜する。

【0054】

次いで、図1(E)に示すように、第3のフォトリソグラフィ工程によってゲート保護膜及びゲート絶縁層をエッチングして酸化物半導体層413の端部を露出させる。

【0055】

次いで、酸化物半導体層413の端部と接する金属膜を形成する。本実施の形態では、膜厚100nmのタングステン膜を形成する。タングステン膜は、スパッタリング装置を用い、アルゴン雰囲気で電力を1000W(DC)として成膜する。なお、成膜時の基板加熱温度は230℃、圧力は0.8Paとする。

【0056】

次いで、第4のフォトリソグラフィ工程によって金属膜を加工してソース電極層431及びドレイン電極層432を形成する。

【0057】

次いで、ゲート電極441、ゲート保護膜422、ソース電極層431、及びドレイン電極層432を覆う第1の層間絶縁膜433及び第2の層間絶縁膜434を形成する。第1の層間絶縁膜433及び第2の層間絶縁膜434は、段差被覆性のよい絶縁膜を用いることが好ましい。第1の層間絶縁膜433及び第2の層間絶縁膜434の材料としては、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜を用いて形成することができる。本実施の形態では、スパッタリング法を用いて、層間絶縁膜の1層目(第1の層間絶縁膜433)となる酸化アルミニウム膜を50nm、PCVD法を用いて層間絶縁膜の2層目(第2の層間絶縁膜434)となる酸化窒化シリコン膜を300nmの厚さで積層成膜する。

【0058】

次に、第5のフォトリソグラフィ工程によって第1の層間絶縁膜433及び第2の層間絶縁膜434を選択的にエッチングしてソース電極層431またはドレイン電極層432に達するコンタクトホールを形成する。なお、ここでは図示しないが、ゲート電極441に達するコンタクトホールも形成する。

【0059】

次に、膜厚50nmのチタン膜と、膜厚100nmのアルミニウム膜と、膜厚50nmのチタン膜を積層成膜する。

【0060】

次に、図1(F)に示すように、第6のフォトリソグラフィ工程によってチタン膜、アルミニウム膜およびチタン膜を加工して、ソース配線450及びドレイン配線451を形成する。

【0061】

以上の工程でトランジスタ460を作製できる。

【0062】

そして、上記作製したトランジスタの電気特性を測定した。その結果が図4である。図4は、Vg−Id曲線データ(Vds=1V、Vds=10V)である。また、S値は、86.1mV/decであった。

【0063】

また、比較のため、平坦化処理を行わなかったトランジスタのS値は、95.9mV/decであった。

【0064】

また、比較のため、平坦化処理としてCMP処理のみを行ったトランジスタのS値は、86.9mV/decであった。

【0065】

これらの結果から、平坦化処理としてCMP処理の後にプラズマ処理を行って高い平坦性となった下地膜上に接して酸化物半導体層を有するトランジスタを形成するとS値の優れたトランジスタを実現することができる。

【0066】

なお、本発明は本実施の形態で示したトランジスタ460の構造に限られるものではなく、例えば、図3に示すように、下地膜上にソース電極層およびドレイン電極層を形成した後、酸化物半導体層を形成する構造のトランジスタ461としても良い。なお、トランジスタ460及びトランジスタ461の作製工程は、ほぼ同一であるため、繰り返しの説明は省略する。また、図1及び図3において同一部分又は同様な機能を有する部分には同一の符号を共通して用いることとする。

【0067】

また、ゲート電極の側面に絶縁物から成るサイドウォールを有する図3のトランジスタ構造としても良い。

【0068】

また、本実施の形態で示したトランジスタ460は、ソース電極層431およびドレイン電極層432が、一対の低抵抗領域443の上面の少なくとも一部と接する構成としているが、本発明はこれに限られるものではなく、例えば、一方の低抵抗領域443が、ソース配線450、またはドレイン配線451の少なくとも一部と接する構成としても良い。また、酸化物半導体層413に低抵抗領域443を設けなくてもよい。

【0069】

(実施の形態2)

本実施の形態では、実施の形態1と同じ条件の平坦化処理を行うことで、非常に優れた平坦性を有する下地膜のサンプルを測定して得られた平坦性データを図5に示す。図5(A)は、基板中央の断面曲線を示す図であり、図5(B)は基板端部の断面曲線を示す図である。また、再現性を確かめるため、別のサンプルを作製し、測定を行って図6に示すように、ほぼ同程度の平坦性を得ることを確認している。図5(A)及び図6(A)は、基板中央の断面曲線を示す図であり、図5(B)及び図6(B)は基板端部の断面曲線を示す図である。

【0070】

AFMで得られる中心線平均粗さRa75は、基板中央で0.07283nmであり、基板端部においては0.08241nmである。

【0071】

また、AFMで得られる中心線平均粗さRa75以外の測定値を以下に示す。なお、AFMの測定領域は1μm×1μmである。

【0072】

図5(A)の基板中央のデータにおいて、最大高低差(P−V)は0.988nm、最大山(Rp)は0.6115nm、最大谷(Rv)は−0.3765nm、自乗平均面粗さ(RMS)は、0.09209nm、n点平均粗さ(Rz)は0.7193nmである。

【0073】

また、図5(B)の基板端部のデータにおいて、最大高低差(P−V)は0.8111nm、最大山(Rp)は0.4055nm、最大谷(Rv)は−0.4055nm、自乗平均面粗さ(RMS)は、0.1032nm、n点平均粗さ(Rz)は0.6758nmである。

【0074】

また、再現性を確認するために得られたサンプルの中心線平均粗さRa75は、基板中央で0.07935nmであり、基板端部においては0.08745nmである。

【0075】

本実施の形態は、実施の形態1と自由に組み合わせることができる。

【0076】

実施の形態1に示したサンプルの中心線平均粗さRa75は0.12nmであったが、本実施の形態に示したサンプルの中心線平均粗さRa75は基板中央で0.07283nmであり、基板端部においては0.08241nmである。従って、このサンプルの下地膜を用いてトランジスタを作製すれば、実施の形態1に示したS値よりも優れたS値を期待できることはいうまでもない。

【0077】

(実施の形態3)

本実施の形態では、実施の形態1と異なる平坦化処理を行うことで、中心線平均粗さRa75を0.1nm以下にする割合を増加することができる。

【0078】

実施の形態1のCMP処理の前にプラズマ処理を行うことで、中心線平均粗さRa75を0.08nm程度にすることができる。

【0079】

即ち、第1のプラズマ処理を行った後、CMP処理を行い、第2のプラズマ処理を行うことで、確実に下地膜表面の中心線平均粗さRa75を0.1nm以下にする割合を増加できる。

【0080】

本実施の形態での第1のプラズマ処理の条件は、実施の形態1に示したプラズマ処理と同じ条件で行えばよい。

【0081】

本実施の形態は、実施の形態1と自由に組み合わせることができる。

【0082】

(実施の形態4)

本実施の形態においては、異なるトランジスタを積層し、半導体装置を作製する例を図7に示す。本実施の形態では、シリコンを半導体層とするトランジスタを形成した後、平坦化し、その上に酸化物半導体層を半導体層とするトランジスタを積層する。以下に詳細な作製方法を示す。

【0083】

まず、p型の半導体基板201に素子分離領域203を形成する。

【0084】

p型の半導体基板201としては、p型の導電型を有する単結晶シリコン基板(シリコンウェハー)、化合物半導体基板(SiC基板、サファイア基板、GaN基板等)を用いることができる。

【0085】

また、p型の半導体基板201の代わりに、SOI(Silicon On Insulator)基板として、鏡面研磨ウェハーに酸素イオンを注入した後、高温加熱することにより、表面から一定の深さに酸化層を形成させるとともに、表面層に生じた欠陥を消滅させて作られた所謂SIMOX(Separation by Implanted OXygen)基板や、水素イオン注入により形成された微小ボイドの加熱処理による成長を利用して半導体基板を劈開するスマートカット法や、ELTRAN法(Epitaxial Layer Transfer:キャノン社の登録商標)等を用いて形成したSOI基板を用いてもよい。

【0086】

素子分離領域203は、LOCOS(Local Oxidation of Silicon)法又はSTI(Shallow Trench Isolation)法等を用いて形成する。

【0087】

また、同一基板上にpチャネル型のトランジスタを形成する場合、p型の半導体基板201の一部にnウェル領域を形成してもよい。nウェル領域は、リン、ヒ素等のn型を付与する不純物元素を添加して形成される。

【0088】

なお、ここでは、p型の半導体基板を用いているが、n型の半導体基板を用いて、pチャネル型のトランジスタを形成してもよい。その場合、n型の半導体基板にp型を付与するホウ素等の不純物元素が添加されたpウェル領域を形成して、同一基板上にnチャネル型のトランジスタを形成してもよい。

【0089】

次に、半導体基板201上にゲート絶縁膜207およびゲート電極209を形成する。

【0090】

加熱処理を行い半導体基板201の表面を酸化した酸化シリコン膜を形成する。又は、熱酸化法により酸化シリコン膜を形成した後に、窒化処理を行うことによって酸化シリコン膜の表面を窒化させることにより、酸化シリコン膜と酸素と窒素を有するシリコン膜(酸化窒化シリコン膜)との積層構造で形成する。次に、酸化シリコン膜又は酸窒化シリコン膜の一部を選択的にエッチングして、ゲート絶縁膜207を形成する。若しくは、厚さ5〜50nmの酸化シリコン、酸化窒化シリコン、高誘電率物質(high−k材料ともいう)であるタンタル酸化物、酸化ハフニウム、酸化ハフニウムシリケート、酸化ジルコニウム、酸化アルミニウム、酸化チタンなどの金属酸化物、又は酸化ランタンなどの希土類酸化物等を、CVD法、スパッタリング法等を用いて形成した後、選択的に一部をエッチングして、ゲート絶縁膜207を形成する。

【0091】

ゲート電極209は、タンタル、タングステン、チタン、モリブデン、クロム、ニオブ等から選択された金属、又はこれらの金属を主成分とする合金材料若しくは化合物材料を用いることが好ましい。また、リン等の不純物を添加した多結晶シリコンを用いることができる。また、金属窒化物膜と上記の金属膜の積層構造でゲート電極209を形成してもよい。金属窒化物としては、窒化タングステン、窒化モリブデン、窒化チタンを用いることができる。金属窒化物膜を設けることにより、金属膜の密着性を向上させることができ、剥離を防止することができる。

【0092】

ゲート電極209は、導電膜をスパッタリング法、CVD法等により形成した後、該導電膜の一部を選択的にエッチングして形成される。

【0093】

ここでは、加熱処理を行い、半導体基板201上の表面を酸化した酸化シリコン膜を形成し、該酸化シリコン膜上に窒化タンタル膜及びタングステン膜が積層された導電膜をスパッタリング法により形成した後、酸化シリコン膜及び導電膜のそれぞれ一部を選択的にエッチングして、ゲート絶縁膜207およびゲート電極209を形成する。

【0094】

なお、高集積化を実現するためには、ゲート電極209の側面にサイドウォール絶縁層を有しない構成とすることが望ましい。一方で、トランジスタの特性を重視する場合には、ゲート電極209の側面にサイドウォール絶縁層を設けることもできる。

【0095】

次に、半導体基板201にn型を付与する不純物元素を添加して、n型の不純物領域211a、n型の不純物領域211bを形成する。また、同一基板上にnウェル領域を形成している場合、当該領域にp型を付与する不純物元素を添加してp型の不純物領域を形成する。n型の不純物領域211a、n型の不純物領域211bおよびp型の不純物領域におけるn型を付与する不純物元素及びp型を付与する不純物元素の濃度は、1×1019/cm3以上1×1021/cm3以下である。n型を付与する不純物元素及びp型を付与する不純物元素は、イオンドーピング法、イオン注入法等を適宜用いて、半導体基板201及びnウェル領域に添加する。

【0096】

また、ゲート電極209の側面にサイドウォール絶縁層を設ける場合、当該サイドウォール絶縁層と重畳する領域に、n型の不純物領域211a、n型の不純物領域211bおよびp型の不純物領域とは異なる不純物濃度の不純物領域を形成することができる。

【0097】

次に、半導体基板201、素子分離領域203、ゲート絶縁膜207およびゲート電極209上に、スパッタリング法、CVD法等により、絶縁膜215および絶縁膜217を形成する。

【0098】

絶縁膜215および絶縁膜217は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウムなどを用いればよく、積層又は単層で設ける。なお、絶縁膜215をCVD法により形成することで、絶縁膜215の水素含有量が高まる。このような絶縁膜215を用いて加熱処理を行うことにより、半導体基板を水素化し、水素によりダングリングボンドを終端させ、当該半導体基板中の欠陥を低減することができる。

【0099】

また、絶縁膜217として、BPSG(Boron Phosphorus Silicon Glass)などの無機材料、又は、ポリイミド、アクリルなどの有機材料を用いて形成することで、絶縁膜217の平坦性を高めることができる。

【0100】

絶縁膜215又は絶縁膜217を形成した後、n型の不純物領域211a、n型の不純物領域211bおよびp型の不純物領域に添加された不純物元素を活性化するための加熱処理を行う。

【0101】

以上の工程により、nチャネル型のトランジスタ112を作製することができる。

【0102】

次に、絶縁膜215および絶縁膜217の一部を選択的にエッチングして、開口部を形成する。次に、開口部にコンタクトプラグ219aおよびコンタクトプラグ219bを形成する。代表的には、スパッタリング法、CVD法等により導電膜を形成した後、CMP法やエッチングなどにより平坦化処理を行い、導電膜の表面の不要な部分を除去して、導電膜を形成する。

【0103】

コンタクトプラグ219aおよびコンタクトプラグ219bとなる導電膜は、WF6ガスとSiH4ガスからCVD法でタングステンシリサイドを形成し、開口部に導電膜を埋め込むことで形成される。

【0104】

次に、絶縁膜217及びコンタクトプラグ219aおよびコンタクトプラグ219b上に、スパッタリング法、CVD法等により絶縁膜を形成した後、該絶縁膜の一部を選択的にエッチングし、溝部を有する絶縁膜221を形成する。次に、スパッタリング法、CVD法等により導電膜を形成した後、CMP法やエッチングなどにより平坦化処理を行い、該導電膜の表面の不要な部分を除去して、配線223aおよび配線223bを形成する。

【0105】

ここで、配線223a及び配線223bは、それぞれトランジスタ112のソース電極又はドレイン電極として機能する。

【0106】

絶縁膜221は、絶縁膜215と同様の材料を用いて形成することができる。

【0107】

配線223aおよび配線223bとして、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、又はタングステンからなる単体金属、又はこれを主成分とする合金を単層構造又は積層構造として用いる。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、タングステン膜上にチタン膜を積層する二層構造、銅−マグネシウム−アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜と、そのチタン膜上に重ねてアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造などがある。なお、酸化インジウム、酸化錫又は酸化亜鉛を含む透明導電材料を用いてもよい。

【0108】

平坦化された絶縁膜221、配線223aおよび配線223bを用いることで、後に形成する下地膜の平坦性を向上させ、後に形成する酸化物半導体を含むトランジスタにおける電気特性のばらつきを低減することができる。また、歩留まり高く酸化物半導体層を含むトランジスタを形成することができる。

【0109】

次に、加熱処理又はプラズマ処理により、絶縁膜221、配線223aおよび配線223bに含まれる水素を脱離させることが好ましい。この結果、後の加熱処理において、後に形成される絶縁膜及び酸化物半導体膜中に水素が拡散することを防ぐことができる。なお、加熱処理は、不活性雰囲気、減圧雰囲気又は乾燥空気雰囲気にて、100℃以上基板の歪み点未満で行う。また、プラズマ処理は、希ガス、酸素、窒素又は酸化窒素(亜酸化窒素、一酸化窒素、二酸化窒素など)を用いる。

【0110】

次に、絶縁膜221、配線223a及び配線223b上に、スパッタリング法、CVD法等により、酸化物半導体層を用いたトランジスタの下地膜となる絶縁膜225を形成する。絶縁膜225としては、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム、酸化アルミニウム、酸化窒化アルミニウムを単層又は積層して形成する。また、絶縁膜225として、加熱により酸素の一部が脱離する酸化絶縁膜を用いて形成することが好ましい。加熱により酸素の一部が脱離する酸化絶縁膜としては、化学量論比を満たす酸素よりも多くの酸素を含む酸化絶縁膜を用いる。加熱により酸素の一部が脱離する酸化絶縁膜は、加熱により酸素が脱離するため、後の工程で行う加熱により酸化物半導体膜に酸素を拡散させることができる。

【0111】

次いで、絶縁膜225に平坦化処理を行う。実施の形態1に示す方法、即ちCMP処理を行った後、ICPエッチング装置を用いてプラズマ処理を行う。(図7(A)参照)この平坦化処理により絶縁膜225の表面の中心線平均粗さRa75は、0.1nm以下とすることができる。

【0112】

次に、中心線平均粗さRa75が0.1nm以下の表面を有する絶縁膜225上に、スパッタリング法、塗布法、印刷法、蒸着法、PCVD法、PLD法、ALD法又はMBE法等を用いて酸化物半導体膜を形成する。以降の工程は、実施の形態1に従ってトランジスタ460を形成する。

【0113】

本実施の形態では、トランジスタ460の酸化物半導体層として、CAAC(C Axis Aligned Crystal)を含む酸化物半導体層を用いる。CAACを含む酸化物半導体層とは、非単結晶であって、c軸に対しては結晶化した薄膜であり、そのab面に対しては必ずしも配列していない。CAACを含む酸化物半導体層は、グレインバウンダリーを有する新構造の薄膜である。

【0114】

このようなc軸配向を有する結晶を含む酸化物半導体膜を設けることにより、可視光や紫外光の照射によるトランジスタの電気特性の変化を抑制することができる。特に、上述のように、絶縁膜225の表面の中心線平均粗さRa75を、0.1nm以下とすることは有用である。これにより、S値の向上だけでなく、c軸配向を有する結晶を含む酸化物半導体膜の結晶性を向上させ、当該酸化物半導体膜を用いたトランジスタの移動度の向上を図ることもできる。

【0115】

以上の工程により、図7(B)に示すように、酸化物半導体を含んで構成されるトランジスタ460を作製することができる。なお、上記トランジスタ460は、i型(真性半導体)又はi型に限りなく近い酸化物半導体層を有するため、極めて優れた特性を示す。

【0116】

また、図7(B)においては、トランジスタ460のソース電極層431又はドレイン電極層432の一方と、トランジスタ112のゲート電極209と、がソース配線450を介して接続する構成としているが、本実施の形態はこれに限られるものではない。例えば、トランジスタ112上に設けられた絶縁膜の上面にトランジスタ112のゲート電極の上面が露出されるような構造とし、当該ゲート電極の上面に直接接するようにトランジスタ460のソース電極層又はドレイン電極層の一方を設ける構成としても良い。

【0117】

以上の工程により、nチャネル型のトランジスタ112上にトランジスタ460を作製することができる。

【0118】

nチャネル型のトランジスタ112とトランジスタ460を組み合わせることで記憶素子(以下、メモリセルとも記す)を作製することもできる。さらには、トランジスタ460を少なくとも一部に用いてCPU(Central Processing Unit)を構成することもできる。また、トランジスタ460は、DSP(Digital Signal Processor)、カスタムLSI、FPGA(Field Programmable Gate Array)等のLSIにも応用可能である。

【0119】

(実施の形態5)

本実施の形態では、同一基板上に少なくとも駆動回路の一部と、画素部に配置するトランジスタを有する表示装置を作製する例について以下に説明する。

【0120】

画素部に配置するトランジスタは、実施の形態1に従って形成する。また、実施の形態1に示すトランジスタ460はnチャネル型トランジスタであるため、駆動回路のうち、nチャネル型トランジスタで構成することができる駆動回路の一部を画素部のトランジスタと同一基板上に形成する。

【0121】

アクティブマトリクス型表示装置のブロック図の一例を図8(A)に示す。表示装置の基板5300上には、画素部5301、第1の走査線駆動回路5302、第2の走査線駆動回路5303、信号線駆動回路5304を有する。画素部5301には、複数の信号線が信号線駆動回路5304から延伸して配置され、複数の走査線が第1の走査線駆動回路5302、及び第2の走査線駆動回路5303から延伸して配置されている。なお走査線と信号線との交差領域には、各々、表示素子を有する画素がマトリクス状に配置されている。また、表示装置の基板5300はFPC(Flexible Printed Circuit)等の接続部を介して、タイミング制御回路(コントローラ、制御ICともいう)に接続されている。

【0122】

図8(A)では、第1の走査線駆動回路5302、第2の走査線駆動回路5303、信号線駆動回路5304は、画素部5301と同じ基板5300上に形成される。そのため、外部に設ける駆動回路等の部品の数が減るので、コストの低減を図ることができる。また、基板5300外部に駆動回路を設けた場合、配線を延伸させる必要が生じ、配線間の接続数が増える。同じ基板5300上に駆動回路を設けた場合、その配線間の接続数を減らすことができ、信頼性の向上、又は歩留まりの向上を図ることができる。

【0123】

また、画素部の回路構成の一例を図8(B)に示す。ここでは、VA方式の液晶表示パネルの画素構造を示す。

【0124】

この画素構造は、一つの画素に複数の画素電極層が有り、それぞれの画素電極層にトランジスタが接続されている。各トランジスタは、異なるゲート信号で駆動されるように構成されている。すなわち、マルチドメイン設計された画素において、個々の画素電極層に印加する信号を、独立して制御する構成を有している。

【0125】

トランジスタ628のゲート配線622と、トランジスタ629のゲート配線623には、異なるゲート信号を与えることができるように分離されている。一方、データ線として機能するソース電極層又はドレイン電極層626は、トランジスタ628とトランジスタ629で共通に用いられている。トランジスタ628とトランジスタ629は実施の形態1のトランジスタ460を適宜用いることができる。

【0126】

第1の画素電極層と第2の画素電極層の形状は異なっており、スリットによって分離されている。V字型に広がる第1の画素電極層の外側を囲むように第2の画素電極層が形成されている。第1の画素電極層と第2の画素電極層に印加する電圧のタイミングを、トランジスタ628及びトランジスタ629により異ならせることで、液晶の配向を制御している。トランジスタ628はゲート配線622と接続し、トランジスタ629はゲート配線623と接続している。ゲート配線622とゲート配線623は異なるゲート信号を与えることで、トランジスタ628とトランジスタ629の動作タイミングを異ならせることができる。

【0127】

また、容量配線690が設けられ、ゲート絶縁層を誘電体とし、第1の画素電極層または第2の画素電極層と電気的に接続する容量電極と保持容量を形成する。

【0128】

第1の画素電極層と液晶層と対向電極層が重なり合うことで、第1の液晶素子651が形成されている。また、第2の画素電極層と液晶層と対向電極層が重なり合うことで、第2の液晶素子652が形成されている。また、一画素に第1の液晶素子651と第2の液晶素子652が設けられたマルチドメイン構造である。

【0129】

なお、図8(B)に示す画素構成は、これに限定されない。例えば、図8(B)に示す画素に新たにスイッチ、抵抗素子、容量素子、トランジスタ、センサ、又は論理回路などを追加してもよい。

【0130】

また、本実施の形態では、VA方式の液晶表示パネルの例を示したが特に限定されず、様々な方式の液晶表示装置に応用することができる。例えば、視野角特性を改善する方法として、基板主表面に対して水平方向の電界を液晶層に印加する横電界方式(IPS方式とも呼ぶ)に応用することができる。

【0131】

例えば、IPS方式の液晶表示パネルとして、配向膜を用いないブルー相を示す液晶を用いることが好ましい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するために5重量%以上のカイラル剤を混合させた液晶組成物を用いて液晶素子の液晶層に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が1msec以下と短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい。

【0132】

また、液晶表示装置の動画特性を改善するため、バックライトとして複数のLED(発光ダイオード)光源または複数のEL光源などを用いて面光源を構成し、面光源を構成している各光源を独立して1フレーム期間内で間欠点灯駆動する駆動技術(例えばフィールドシーケンシャル方式など)もある。面光源として、3種類以上のLEDを用いてもよいし、白色発光のLEDを用いてもよい。面光源として、異なる色を呈する3種類以上の光源(例えば、R(赤)、G(緑)、B(青))を用いる場合は、カラーフィルタを用いなくともカラー表示が行える。また、面光源として、白色発光のLEDを用いる場合は、カラーフィルタを設けてカラー表示を行う。独立して複数のLEDを制御できるため、液晶層の光学変調の切り替えタイミングに合わせてLEDの発光タイミングを同期させることもできる。LEDを部分的に消灯することができるため、特に一画面を占める黒い表示領域の割合が多い映像表示の場合には、消費電力の低減効果が図れる。

【0133】

また、画素部の回路構成の一例を図8(C)に示す。ここでは、有機EL素子を用いた表示パネルの画素構造を示す。

【0134】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア(電子および正孔)が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。

【0135】

図8(C)は、半導体装置の例としてデジタル時間階調駆動を適用可能な画素構成の一例を示す図である。

【0136】

デジタル時間階調駆動を適用可能な画素の構成及び画素の動作について説明する。ここでは酸化物半導体層をチャネル形成領域に用いるnチャネル型のトランジスタを1つの画素に2つ用いる例を示す。

【0137】

画素6400は、スイッチング用トランジスタ6401、駆動用トランジスタ6402、発光素子6404及び容量素子6403を有している。スイッチング用トランジスタ6401は、ゲート電極が走査線6406に接続され、第1電極(ソース電極層及びドレイン電極層の一方)が信号線6405に接続され、第2電極(ソース電極層及びドレイン電極層の他方)が駆動用トランジスタ6402のゲート電極に接続されている。駆動用トランジスタ6402は、ゲート電極が容量素子6403を介して電源線6407に接続され、第1電極が電源線6407に接続され、第2電極が発光素子6404の第1電極(画素電極)に接続されている。発光素子6404の第2電極は共通電極6408に相当する。共通電極6408は、同一基板上に形成される共通電位線と電気的に接続される。

【0138】

なお、発光素子6404の第2電極(共通電極6408)には低電源電位が設定されている。なお、低電源電位とは、電源線6407に設定される高電源電位を基準にして低電源電位<高電源電位を満たす電位であり、低電源電位としては例えばGND、0Vなどが設定されていても良い。この高電源電位と低電源電位との電位差を発光素子6404に印加して、発光素子6404に電流を流して発光素子6404を発光させるため、高電源電位と低電源電位との電位差が発光素子6404の順方向しきい値電圧以上となるようにそれぞれの電位を設定する。

【0139】

なお、容量素子6403は駆動用トランジスタ6402のゲート容量を代用して省略することも可能である。駆動用トランジスタ6402のゲート容量については、チャネル形成領域とゲート電極との間で容量が形成されていてもよい。

【0140】

ここで、電圧入力電圧駆動方式の場合には、駆動用トランジスタ6402のゲート電極には、駆動用トランジスタ6402が十分にオンするか、オフするかの二つの状態となるようなビデオ信号を入力する。つまり、駆動用トランジスタ6402は線形領域で動作させる。駆動用トランジスタ6402は線形領域で動作させるため、電源線6407の電圧よりも高い電圧を駆動用トランジスタ6402のゲート電極にかける。なお、信号線6405には、(電源線電圧+駆動用トランジスタ6402のVth)以上の電圧をかける。

【0141】

また、デジタル時間階調駆動に代えて、アナログ階調駆動を行う場合、信号の入力を異ならせることで、図8(C)と同じ画素構成を用いることができる。

【0142】

アナログ階調駆動を行う場合、駆動用トランジスタ6402のゲート電極に発光素子6404の順方向電圧+駆動用トランジスタ6402のVth以上の電圧をかける。発光素子6404の順方向電圧とは、所望の輝度とする場合の電圧を指しており、少なくとも順方向しきい値電圧を含む。なお、駆動用トランジスタ6402が飽和領域で動作するようなビデオ信号を入力することで、発光素子6404に電流を流すことができる。駆動用トランジスタ6402を飽和領域で動作させるため、電源線6407の電位は、駆動用トランジスタ6402のゲート電位よりも高くする。ビデオ信号をアナログとすることで、発光素子6404にビデオ信号に応じた電流を流し、アナログ階調駆動を行うことができる。

【0143】

なお、図8(C)に示す画素構成は、これに限定されない。例えば、図8(C)に示す画素に新たにスイッチ、抵抗素子、容量素子、センサ、トランジスタ又は論理回路などを追加してもよい。

【0144】

(実施の形態6)

本明細書に開示する半導体装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。上記実施の形態1で説明したトランジスタ460を具備する電子機器の例について説明する。

【0145】

図9(A)は、携帯型の情報端末であり、本体3001、筐体3002、表示部3003a、3003bなどによって構成されている。この携帯型の情報端末は、少なくともバッテリーを有し、データ情報を保存するためのメモリ(Flash Memory回路、SRAM回路、DRAM回路など)、CPU(中央演算処理回路)やLogic回路を備えた構成とすることが好ましい。実施の形態1で示したトランジスタ460をCPUに用い、低消費電力化を図ってもよい。実施の形態1で示したトランジスタ460はS値が良好であり、低電圧でトランジスタのオンオフの切り換えができるため、トランジスタ460を含む回路を低電圧動作とすることができる。

【0146】

また、表示部3003bはタッチ入力機能を有するパネルとなっており、表示部3003bに表示されるキーボードボタン3004を触れることで画面操作や、文字入力を行うことができる。勿論、表示部3003aをタッチ入力機能を有するパネルとして構成してもよい。実施の形態1で示したトランジスタ460をスイッチング素子として用い、液晶パネルや有機発光パネルを作製して表示部3003a、3003bに適用することにより、携帯型の情報端末とすることができる。

【0147】

図9(A)は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子など)、記録媒体挿入部などを備える構成としてもよい。

【0148】

また、図9(A)に示す携帯型の情報端末は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

【0149】

また、図9(A)に示す携帯型の情報端末は、2つの表示部3003a、3003bのうち、一方を取り外すことができ、取り外した場合の図を図9(B)に示している。表示部3003aもタッチ入力機能を有するパネルとし、持ち運びの際、さらなる軽量化を図ることができ、片手で筐体3002をもってもう片方の手で操作することができ、便利である。

【0150】

さらに、図9(B)に示す筐体3002にアンテナやマイク機能や無線機能を持たせ、携帯電話として用いてもよい。

【0151】

図9(C)は、携帯電話の一例を示している。図9(C)に示す携帯電話機5005は、筐体に組み込まれた表示部5001の他、ヒンジ5002に取り付けられた表示パネル5003、操作ボタン5004、スピーカ、マイクなどを備えている。

【0152】

図9(C)に示す携帯電話機5005は、表示パネル5003がスライドして、表示部5001と重なるようになっており、透光性を有するカバーとしても機能する。表示パネル5003は、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子を用いた表示パネルである。

【0153】

また、両面射出構造の発光素子を用いた表示パネル5003であるため、表示部5001と重ねた状態でも表示を行うことができ、使用者はどちらも表示し、どちらの表示も視認することもできる。表示パネル5003は透光性を有し、表示パネルの向こう側が透けて見えるパネルである。例えば、地図の表示を表示部5001で行い、使用者の所在地ポイントを表示パネル5003で表示することによって現在地を認識しやすい状態を提供することができる。

【0154】

また、携帯電話機5005に撮像素子を設け、テレビ電話として使用する場合、複数の相手の顔を表示しながら、複数の相手と会話ができるため、テレビ会議なども行うことができる。例えば、表示パネル5003に一人または複数の相手の顔を表示し、さらに表示部5001にもう一人の顔を表示させることで、使用者は2人以上の顔を見ながら会話を行うことができる。

【0155】

また、表示パネル5003に表示されたタッチ入力ボタン5006を指などで触れることで、情報を入力することができる。また、電話を掛ける、或いはメールを打つなどの操作は、表示パネル5003をスライドさせて、操作ボタン5004を指などで触れることにより行うことができる。

【0156】

図9(D)は、テレビジョン装置の一例を示している。テレビジョン装置9600は、筐体9601に表示部9603が組み込まれている。表示部9603により、映像を表示することが可能である。また、ここでは、CPUを内蔵したスタンド9605により筐体9601を支持した構成を示している。実施の形態1で示したトランジスタ460を表示部9603やCPUに適用することにより、テレビジョン装置9600とすることができる。

【0157】

テレビジョン装置9600の操作は、筐体9601が備える操作スイッチや、別体のリモコン操作機により行うことができる。また、リモコン操作機に、当該リモコン操作機から出力する情報を表示する表示部を設ける構成としてもよい。

【0158】

なお、テレビジョン装置9600は、受信機やモデムなどを備えた構成とする。受信機により一般のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双方向(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。

【0159】

また、テレビジョン装置9600は、外部接続端子9604や、記憶媒体再生録画部9602、外部メモリスロットを備えている。外部接続端子9604は、USBケーブルなどの各種ケーブルと接続可能であり、パーソナルコンピュータなどとのデータ通信が可能である。記憶媒体再生録画部9602では、ディスク状の記録媒体を挿入し、記録媒体に記憶されているデータの読み出し、記録媒体への書き込みが可能である。また、外部メモリスロットに差し込まれた外部メモリ9606にデータ保存されている画像や映像などを表示部9603に映し出すことも可能である。

【0160】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【符号の説明】

【0161】

112 トランジスタ

201 半導体基板

203 素子分離領域

207 ゲート絶縁膜

209 ゲート電極

211a 不純物領域

211b 不純物領域

215 絶縁膜

217 絶縁膜

219a コンタクトプラグ

219b コンタクトプラグ

221 絶縁膜

223a 配線

223b 配線

225 絶縁膜

400 基板

413 酸化物半導体層

421 ドーパント

422 ゲート保護膜

431 ソース電極層

432 ドレイン電極層

433 層間絶縁膜

434 層間絶縁膜

436 下地膜

441 ゲート電極

442 ゲート絶縁層

443 低抵抗領域

444 酸化物半導体膜

450 ソース配線

451 ドレイン配線

460 トランジスタ

461 トランジスタ

622 ゲート配線

623 ゲート配線

626 ドレイン電極層

628 トランジスタ

629 トランジスタ

651 液晶素子

652 液晶素子

690 容量配線

3001 本体

3002 筐体

3003a 表示部

3003b 表示部

3004 キーボードボタン

5001 表示部

5002 ヒンジ

5003 表示パネル

5004 操作ボタン

5005 携帯電話機

5006 タッチ入力ボタン

5300 基板

5301 画素部

5302 走査線駆動回路

5303 走査線駆動回路

5304 信号線駆動回路

6400 画素

6401 スイッチング用トランジスタ

6402 駆動用トランジスタ

6403 容量素子

6404 発光素子

6405 信号線

6406 走査線

6407 電源線

6408 共通電極

9600 テレビジョン装置

9601 筐体

9602 記憶媒体再生録画部

9603 表示部

9604 外部接続端子

9605 スタンド

9606 外部メモリ

【技術分野】

【0001】

本発明は、酸化物半導体膜を用いる半導体装置及び半導体装置の作製方法に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路及び電子機器は全て半導体装置である。

【背景技術】

【0003】

近年、携帯電話等に代表されるモバイルコミニュケーション市場は、急速に発展している。搭載部品である半導体集積回路に対する低消費電力化、高集積化、多機能化、高速化などの要求が高まるにつれて、トランジスタの特性向上が求められている。

【0004】

トランジスタの特性を示す指標の一つに、S値が用いられる。S値とは、ドレイン電圧一定下で、ドレイン電流を一桁変化させるために必要な、ゲート電圧の変化量を表す。S値が小さいほどドレイン電流の制御性に優れる。トランジスタの微細化等に起因して、現状では、S値を、80mV/dec以下にすることは難しい。

【0005】

また、シリコン系半導体材料に代わって非晶質の酸化物半導体材料を用いてトランジスタを作製し、電子デバイスなどに応用する技術が注目されている。例えば、トランジスタのチャネル層として、電子キャリア濃度が1018/cm3未満であるインジウム(In)、ガリウム(Ga)、及び亜鉛(Zn)を含む非晶質の酸化物半導体材料を用いてトランジスタを作製する技術が開示されている(特許文献1参照。)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−165529号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

トランジスタの特性向上のためには、酸化物半導体層の結晶性及び、下地膜と酸化物半導体層との界面特性を良好にすることが重要である。下地膜の平坦性を示す指標として、中心線平均粗さRa75値を用いることができる。下地膜の中心線平均粗さRa75値が大きい場合、下地膜上に形成される酸化物半導体層の結晶化が阻害され、結晶性が低減化されることで、結果的にトランジスタの電気特性の悪化や信頼性の低下を招く。

【0008】

上述した問題を鑑みて、結晶性の高い酸化物半導体をチャネル層に用いて、優れた特性を有する半導体装置を提供することを課題の一つとする。

【0009】

また、下地膜の平坦性を向上させた半導体装置を提供することを課題の一つとする。

【課題を解決するための手段】

【0010】

中心線平均粗さRa75値を小さくした下地膜上に、結晶性の高い酸化物半導体層を形成することで、半導体装置の特性向上を図る。

【0011】

本明細書で開示する本発明の一態様は、基板上に下地膜を形成し、下地膜にCMP処理を行い、CMP処理した後、プラズマ処理を行い、プラズマ処理及びCMP処理により得られた平坦な表面上に酸化物半導体層を形成する半導体装置の作製方法である。

【0012】

上記において、プラズマ処理は、希ガスを用いたプラズマ処理であることを特徴とする半導体装置の作製方法である。

【0013】

また、本明細書で開示する本発明の一態様は、基板上に下地膜を形成し、下地膜に第1のプラズマ処理を行い、第1のプラズマ処理した後、CMP処理を行い、CMP処理後、第2のプラズマ処理を行い、第1のプラズマ処理、CMP処理、及び第2のプラズマ処理により得られた平坦な表面上に酸化物半導体層を形成する半導体装置の作製方法である。

【0014】

上記において、第1のプラズマ処理及び第2のプラズマ処理は、希ガスを用いたプラズマ処理であることを特徴とする半導体装置の作製方法である。

【0015】

上記において、下地膜は、酸化シリコン膜、酸化ガリウム膜、酸化ハフニウム膜、または酸化アルミニウム膜であることを特徴とする半導体装置の作製方法である。

【0016】

また、上記において、基板は半導体基板であってもよい。

【0017】

また、上記において、基板はガラス基板であってもよい。

【0018】

また、上記において、プラズマ処理は平行平板型のプラズマ装置よりも高密度のプラズマを発生させることのできるICPエッチング装置で行うことが好ましい。

【発明の効果】

【0019】

プラズマ処理及びCMP処理を組み合わせて、下地膜の中心線平均粗さRa75値を、0.1nm未満とすることができ、半導体装置のS値を向上させることができる。

【図面の簡単な説明】

【0020】

【図1】本発明のトランジスタの断面を示す図。

【図2】本発明のトランジスタの上面を示す図。

【図3】本発明のトランジスタの断面を示す図。

【図4】本発明のトランジスタのVg−Id曲線を示すグラフ。

【図5】基板中央と基板端部における下地膜表面のAFMによるサンプルの断面曲線を示すグラフ。

【図6】基板中央と基板端部における下地膜表面のAFMによるサンプルの断面曲線を示すグラフ。

【図7】半導体装置の作製工程を示す断面図。

【図8】本発明の一態様を示すブロック図及び等価回路図である。

【図9】電子機器の一態様を示す図である。

【発明を実施するための形態】

【0021】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0022】

(実施の形態1)

本実施の形態では、以下に示す手順で単結晶シリコン基板上の下地膜に平坦化処理を行い、その上に酸化物半導体層を有するトランジスタを作製し、下地膜の平坦性とトランジスタ特性、特にS値との関係を示す。なお、トランジスタの作製工程の断面図を図1に、作製したトランジスタの上面図を図2に示す。

【0023】

また、比較のため、下地膜に平坦化処理を行わないで作製したトランジスタもトランジスタ特性を測定する。

【0024】

まず、図1(A)に示すように、単結晶シリコンからなる基板400上に膜厚300nmの下地膜436を形成する。下地膜436の成膜前にアルゴンガスを導入してプラズマを発生させる逆スパッタを3分間行う。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。

【0025】

下地膜436としては、酸化シリコン層(SiOx(x>2))、酸化窒化シリコン層、窒化酸化シリコン層、酸化ガリウム層、酸化ハフニウム層、酸化アルミニウム層、珪酸ハフニウム層、珪酸ハフニウムオキシナイトライド層、ハフニウムアルミネート層を単層で又は積層して形成することができる。

【0026】

本実施の形態では、スパッタリング法を用いて酸化シリコン層を形成する。

【0027】

次いで、下地膜436表面に化学機械研磨(CMP:Chemical Mechanical Polishing)処理を行った後、Kr、Xe、Arなどの希ガスを用いたプラズマ処理を行い、露出している下地膜436の表面平坦化処理を行う。CMP処理の条件は、CMP研磨パッドとして硬質ポリウレタンパッドを用い、スラリーとしてはNP8020(ニッタ・ハース株式会社製)の原液(シリカ粒径60nm〜80nm)を用い、研磨時間0.5分、研磨圧0.001MPa、基板を固定している側のスピンドル回転数は60rpm、研磨布(研磨パッド)が固定されているテーブル回転数は56rpmとする。

【0028】

本実施の形態では、CMP処理を行った後、Arガスを用いたプラズマ処理を行い、下地膜表面の平坦性を原子間力顕微鏡(AFM:Atomic Force Microscope)を用いて測定すると中心線平均粗さRa75は0.12nmである。なお、AFMの測定領域は1μm×1μmである。

【0029】

なお、Ra75とは、JIS B 0031・JIS B 0061で定義されている中心線平均粗さを曲面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」で表現できる。

【0030】

また、上記作製方法において、Arガスを用いたプラズマ処理は、ICP(Inductively Coupled Plasma)エッチング装置を用いることが好ましい。本実施の形態では、コイル型の電極に電力を500W印加し、基板側にバイアス電力を100W(RF)印加し、流量100sccmのArガスをエッチング装置内に導入して、圧力1.35Paに設定し、基板温度を−10℃に設定してプラズマ処理を180秒行う。このプラズマ処理によって下地膜436の膜厚が約10nm程度薄くなる。

【0031】

また、コイルのインダクタンスを低下させるためにコイルを分割したマルチスパイラル方式のICPエッチング装置や、くし形コイルを円状の平板に配置したスポーク形のICPエッチング装置を用いてもよい。

【0032】

また、ICP型エッチング装置に限定されず、他のプラズマ処理装置を用いて下地膜436の平坦化を行ってもよい。

【0033】

なお、比較のため、平坦化を行わない下地膜表面をAFMで測定すると中心線平均粗さRa75は0.91nmである。また、CMP処理のみを行って下地膜表面をAFMで測定すると中心線平均粗さRa75は0.21nmである。

【0034】

次いで、図1(B)に示すように、スパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて酸化物半導体膜444を成膜する。

【0035】

酸化物半導体膜444の材料としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含む非単結晶であることが好ましい。特にInとZnを含むことが好ましい。また、該酸化物を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

【0036】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

【0037】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Ga系酸化物、三元系金属の酸化物であるIn−Ga−Zn系酸化物(IGZOとも表記する)、In−Al−Zn系酸化物、In−Sn−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物、四元系金属の酸化物であるIn−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物を用いることができる。

【0038】

なお、ここで、例えば、In−Ga−Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0039】

酸化物半導体膜は、好ましくはスパッタリング法により、基板加熱温度を100℃以上600℃以下、好ましくは150℃以上550℃以下、さらに好ましくは200℃以上500℃以下とし、酸素ガス雰囲気で成膜する。酸化物半導体膜の厚さは、1nm以上40nm以下、好ましくは3nm以上20nm以下とする。成膜時の基板加熱温度が高いほど、得られる酸化物半導体膜の不純物濃度は低くなる。また、酸化物半導体膜中の原子配列が整い、高密度化され、多結晶が形成されやすくなる。さらに、酸素ガス雰囲気で成膜することでも、希ガスなどの余分な原子が含まれないため、多結晶が形成されやすくなる。ただし、酸素ガスと希ガスの混合雰囲気としてもよく、その場合は酸素ガスの割合は30体積%以上、好ましくは50体積%以上、さらに好ましくは80体積%以上とする。

【0040】

本実施の形態では、酸化物半導体膜444であるIn−Ga−Zn−O膜を10nmの厚さで成膜する。成膜条件の一例としては、基板温度300℃、圧力0.4Pa、直流(DC)電源0.5kW、酸素とアルゴンの混合(酸素流量30sccm、アルゴン流量15sccm)雰囲気下の条件が適用される。

【0041】

そして、酸化物半導体膜444の成膜後に加熱処理を行う。この加熱処理によって酸化物半導体膜444の脱水化または脱水素化を行うことができる。加熱処理の温度は、400℃以上基板の歪み点未満とする。本実施の形態では、成膜後に、大気に触れることなく、スパッタ成膜装置内で基板を保持し、酸化物半導体膜444に対して減圧下400℃において30分間の加熱処理を行う。

【0042】

加熱処理の雰囲気は、減圧下に限定されず、水、水素などが含まれない雰囲気(露点が−40℃以下、好ましくは−60℃以下)、例えば不活性雰囲気または酸化性雰囲気で行う(図1(B)参照)。

【0043】

なお、加熱処理は成膜室内に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を用いてもよい。例えば、電気炉、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。高温のガスには、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

【0044】

次いで、図1(C)に示すように、酸化物半導体膜444を第1のフォトリソグラフィ工程により島状の酸化物半導体層413に加工する。なお、ここでの酸化物半導体膜444のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。

【0045】

次いで、ゲート絶縁層442を1nm以上200nm以下の厚さで成膜する(図1(C)参照)。ゲート絶縁層442は、スパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法を用いることができる。本実施の形態では、PCVD法を用いて酸化窒化シリコン膜を30nmの厚さで成膜する。

【0046】

次いで、ゲート電極として機能する電極を形成するための金属膜を形成する。金属膜の材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて形成することができる。また、ゲート電極を積層構造とし、その一層として窒素を含む金属酸化物、具体的には、窒素を含むIn−Ga−Zn−O膜や、窒素を含むIn−Sn−O膜や、窒素を含むIn−Ga−O膜や、窒素を含むIn−Zn−O膜や、窒素を含むSn−O膜や、窒素を含むIn−O膜や、金属窒化膜(InN、SnNなど)を用いてもよい。これらの膜は5電子ボルト、好ましくは5.5電子ボルト以上の仕事関数を有し、ゲート電極として用いた場合、トランジスタの電気特性のしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現できる。

【0047】

本実施の形態では、金属膜を積層膜として、膜厚30nmの窒化タンタル膜上に膜厚135nmのタングステン膜を形成する。

【0048】

窒化タンタル膜は、スパッタリング装置を用い、アルゴン:窒素=5:1の混合雰囲気で電力を1000W(DC)として成膜する。なお、成膜時に基板加熱は行っていない。タングステン膜は、スパッタリング装置を用い、アルゴン雰囲気で電力を4000W(DC)として成膜する。なお、成膜時の基板加熱温度は200℃とする。

【0049】

次いで、図1(D)に示すように、第2のフォトリソグラフィ工程によって窒化タンタル膜およびタングステン膜を加工して、ゲート電極441を形成する。

【0050】

次いで、ゲート電極441をマスクとして、ゲート絶縁層442を通過させて島状の酸化物半導体層413にドーパント421を選択的に導入し、低抵抗領域443を自己整合的に形成する(図1(D)参照)。

【0051】

ドーパント421は、酸化物半導体膜444の導電率を変化させる不純物である。ドーパントとしては、15族元素(代表的にはリン(P)、砒素(As)、およびアンチモン(Sb))、ホウ素(B)、アルミニウム(Al)、窒素(N)、アルゴン(Ar)、ヘリウム(He)、ネオン(Ne)、インジウム(In)、フッ素(F)、塩素(Cl)、チタン(Ti)、及び亜鉛(Zn)のいずれかから選択される一以上を用いることができる。

【0052】

本実施の形態では、ホウ素(B)をイオン注入法により注入し、加速電圧10kV、ドーズ量を3×1015atoms/cm2とする。

【0053】

次いで、ゲート電極441を覆うためのゲート保護膜を形成する。ゲート保護膜の材料としては、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜を用いて形成することができる。本実施の形態では、PCVD法を用いて保護膜となる酸化窒化シリコン膜を150nmの厚さで成膜する。

【0054】

次いで、図1(E)に示すように、第3のフォトリソグラフィ工程によってゲート保護膜及びゲート絶縁層をエッチングして酸化物半導体層413の端部を露出させる。

【0055】

次いで、酸化物半導体層413の端部と接する金属膜を形成する。本実施の形態では、膜厚100nmのタングステン膜を形成する。タングステン膜は、スパッタリング装置を用い、アルゴン雰囲気で電力を1000W(DC)として成膜する。なお、成膜時の基板加熱温度は230℃、圧力は0.8Paとする。

【0056】

次いで、第4のフォトリソグラフィ工程によって金属膜を加工してソース電極層431及びドレイン電極層432を形成する。

【0057】

次いで、ゲート電極441、ゲート保護膜422、ソース電極層431、及びドレイン電極層432を覆う第1の層間絶縁膜433及び第2の層間絶縁膜434を形成する。第1の層間絶縁膜433及び第2の層間絶縁膜434は、段差被覆性のよい絶縁膜を用いることが好ましい。第1の層間絶縁膜433及び第2の層間絶縁膜434の材料としては、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜を用いて形成することができる。本実施の形態では、スパッタリング法を用いて、層間絶縁膜の1層目(第1の層間絶縁膜433)となる酸化アルミニウム膜を50nm、PCVD法を用いて層間絶縁膜の2層目(第2の層間絶縁膜434)となる酸化窒化シリコン膜を300nmの厚さで積層成膜する。

【0058】

次に、第5のフォトリソグラフィ工程によって第1の層間絶縁膜433及び第2の層間絶縁膜434を選択的にエッチングしてソース電極層431またはドレイン電極層432に達するコンタクトホールを形成する。なお、ここでは図示しないが、ゲート電極441に達するコンタクトホールも形成する。

【0059】

次に、膜厚50nmのチタン膜と、膜厚100nmのアルミニウム膜と、膜厚50nmのチタン膜を積層成膜する。

【0060】

次に、図1(F)に示すように、第6のフォトリソグラフィ工程によってチタン膜、アルミニウム膜およびチタン膜を加工して、ソース配線450及びドレイン配線451を形成する。

【0061】

以上の工程でトランジスタ460を作製できる。

【0062】

そして、上記作製したトランジスタの電気特性を測定した。その結果が図4である。図4は、Vg−Id曲線データ(Vds=1V、Vds=10V)である。また、S値は、86.1mV/decであった。

【0063】

また、比較のため、平坦化処理を行わなかったトランジスタのS値は、95.9mV/decであった。

【0064】

また、比較のため、平坦化処理としてCMP処理のみを行ったトランジスタのS値は、86.9mV/decであった。

【0065】

これらの結果から、平坦化処理としてCMP処理の後にプラズマ処理を行って高い平坦性となった下地膜上に接して酸化物半導体層を有するトランジスタを形成するとS値の優れたトランジスタを実現することができる。

【0066】

なお、本発明は本実施の形態で示したトランジスタ460の構造に限られるものではなく、例えば、図3に示すように、下地膜上にソース電極層およびドレイン電極層を形成した後、酸化物半導体層を形成する構造のトランジスタ461としても良い。なお、トランジスタ460及びトランジスタ461の作製工程は、ほぼ同一であるため、繰り返しの説明は省略する。また、図1及び図3において同一部分又は同様な機能を有する部分には同一の符号を共通して用いることとする。

【0067】

また、ゲート電極の側面に絶縁物から成るサイドウォールを有する図3のトランジスタ構造としても良い。

【0068】

また、本実施の形態で示したトランジスタ460は、ソース電極層431およびドレイン電極層432が、一対の低抵抗領域443の上面の少なくとも一部と接する構成としているが、本発明はこれに限られるものではなく、例えば、一方の低抵抗領域443が、ソース配線450、またはドレイン配線451の少なくとも一部と接する構成としても良い。また、酸化物半導体層413に低抵抗領域443を設けなくてもよい。

【0069】

(実施の形態2)

本実施の形態では、実施の形態1と同じ条件の平坦化処理を行うことで、非常に優れた平坦性を有する下地膜のサンプルを測定して得られた平坦性データを図5に示す。図5(A)は、基板中央の断面曲線を示す図であり、図5(B)は基板端部の断面曲線を示す図である。また、再現性を確かめるため、別のサンプルを作製し、測定を行って図6に示すように、ほぼ同程度の平坦性を得ることを確認している。図5(A)及び図6(A)は、基板中央の断面曲線を示す図であり、図5(B)及び図6(B)は基板端部の断面曲線を示す図である。

【0070】

AFMで得られる中心線平均粗さRa75は、基板中央で0.07283nmであり、基板端部においては0.08241nmである。

【0071】

また、AFMで得られる中心線平均粗さRa75以外の測定値を以下に示す。なお、AFMの測定領域は1μm×1μmである。

【0072】

図5(A)の基板中央のデータにおいて、最大高低差(P−V)は0.988nm、最大山(Rp)は0.6115nm、最大谷(Rv)は−0.3765nm、自乗平均面粗さ(RMS)は、0.09209nm、n点平均粗さ(Rz)は0.7193nmである。

【0073】

また、図5(B)の基板端部のデータにおいて、最大高低差(P−V)は0.8111nm、最大山(Rp)は0.4055nm、最大谷(Rv)は−0.4055nm、自乗平均面粗さ(RMS)は、0.1032nm、n点平均粗さ(Rz)は0.6758nmである。

【0074】

また、再現性を確認するために得られたサンプルの中心線平均粗さRa75は、基板中央で0.07935nmであり、基板端部においては0.08745nmである。

【0075】

本実施の形態は、実施の形態1と自由に組み合わせることができる。

【0076】

実施の形態1に示したサンプルの中心線平均粗さRa75は0.12nmであったが、本実施の形態に示したサンプルの中心線平均粗さRa75は基板中央で0.07283nmであり、基板端部においては0.08241nmである。従って、このサンプルの下地膜を用いてトランジスタを作製すれば、実施の形態1に示したS値よりも優れたS値を期待できることはいうまでもない。

【0077】

(実施の形態3)

本実施の形態では、実施の形態1と異なる平坦化処理を行うことで、中心線平均粗さRa75を0.1nm以下にする割合を増加することができる。

【0078】

実施の形態1のCMP処理の前にプラズマ処理を行うことで、中心線平均粗さRa75を0.08nm程度にすることができる。

【0079】

即ち、第1のプラズマ処理を行った後、CMP処理を行い、第2のプラズマ処理を行うことで、確実に下地膜表面の中心線平均粗さRa75を0.1nm以下にする割合を増加できる。

【0080】

本実施の形態での第1のプラズマ処理の条件は、実施の形態1に示したプラズマ処理と同じ条件で行えばよい。

【0081】

本実施の形態は、実施の形態1と自由に組み合わせることができる。

【0082】

(実施の形態4)

本実施の形態においては、異なるトランジスタを積層し、半導体装置を作製する例を図7に示す。本実施の形態では、シリコンを半導体層とするトランジスタを形成した後、平坦化し、その上に酸化物半導体層を半導体層とするトランジスタを積層する。以下に詳細な作製方法を示す。

【0083】

まず、p型の半導体基板201に素子分離領域203を形成する。

【0084】

p型の半導体基板201としては、p型の導電型を有する単結晶シリコン基板(シリコンウェハー)、化合物半導体基板(SiC基板、サファイア基板、GaN基板等)を用いることができる。

【0085】

また、p型の半導体基板201の代わりに、SOI(Silicon On Insulator)基板として、鏡面研磨ウェハーに酸素イオンを注入した後、高温加熱することにより、表面から一定の深さに酸化層を形成させるとともに、表面層に生じた欠陥を消滅させて作られた所謂SIMOX(Separation by Implanted OXygen)基板や、水素イオン注入により形成された微小ボイドの加熱処理による成長を利用して半導体基板を劈開するスマートカット法や、ELTRAN法(Epitaxial Layer Transfer:キャノン社の登録商標)等を用いて形成したSOI基板を用いてもよい。

【0086】

素子分離領域203は、LOCOS(Local Oxidation of Silicon)法又はSTI(Shallow Trench Isolation)法等を用いて形成する。

【0087】

また、同一基板上にpチャネル型のトランジスタを形成する場合、p型の半導体基板201の一部にnウェル領域を形成してもよい。nウェル領域は、リン、ヒ素等のn型を付与する不純物元素を添加して形成される。

【0088】

なお、ここでは、p型の半導体基板を用いているが、n型の半導体基板を用いて、pチャネル型のトランジスタを形成してもよい。その場合、n型の半導体基板にp型を付与するホウ素等の不純物元素が添加されたpウェル領域を形成して、同一基板上にnチャネル型のトランジスタを形成してもよい。

【0089】

次に、半導体基板201上にゲート絶縁膜207およびゲート電極209を形成する。

【0090】

加熱処理を行い半導体基板201の表面を酸化した酸化シリコン膜を形成する。又は、熱酸化法により酸化シリコン膜を形成した後に、窒化処理を行うことによって酸化シリコン膜の表面を窒化させることにより、酸化シリコン膜と酸素と窒素を有するシリコン膜(酸化窒化シリコン膜)との積層構造で形成する。次に、酸化シリコン膜又は酸窒化シリコン膜の一部を選択的にエッチングして、ゲート絶縁膜207を形成する。若しくは、厚さ5〜50nmの酸化シリコン、酸化窒化シリコン、高誘電率物質(high−k材料ともいう)であるタンタル酸化物、酸化ハフニウム、酸化ハフニウムシリケート、酸化ジルコニウム、酸化アルミニウム、酸化チタンなどの金属酸化物、又は酸化ランタンなどの希土類酸化物等を、CVD法、スパッタリング法等を用いて形成した後、選択的に一部をエッチングして、ゲート絶縁膜207を形成する。

【0091】

ゲート電極209は、タンタル、タングステン、チタン、モリブデン、クロム、ニオブ等から選択された金属、又はこれらの金属を主成分とする合金材料若しくは化合物材料を用いることが好ましい。また、リン等の不純物を添加した多結晶シリコンを用いることができる。また、金属窒化物膜と上記の金属膜の積層構造でゲート電極209を形成してもよい。金属窒化物としては、窒化タングステン、窒化モリブデン、窒化チタンを用いることができる。金属窒化物膜を設けることにより、金属膜の密着性を向上させることができ、剥離を防止することができる。

【0092】

ゲート電極209は、導電膜をスパッタリング法、CVD法等により形成した後、該導電膜の一部を選択的にエッチングして形成される。

【0093】

ここでは、加熱処理を行い、半導体基板201上の表面を酸化した酸化シリコン膜を形成し、該酸化シリコン膜上に窒化タンタル膜及びタングステン膜が積層された導電膜をスパッタリング法により形成した後、酸化シリコン膜及び導電膜のそれぞれ一部を選択的にエッチングして、ゲート絶縁膜207およびゲート電極209を形成する。

【0094】

なお、高集積化を実現するためには、ゲート電極209の側面にサイドウォール絶縁層を有しない構成とすることが望ましい。一方で、トランジスタの特性を重視する場合には、ゲート電極209の側面にサイドウォール絶縁層を設けることもできる。

【0095】

次に、半導体基板201にn型を付与する不純物元素を添加して、n型の不純物領域211a、n型の不純物領域211bを形成する。また、同一基板上にnウェル領域を形成している場合、当該領域にp型を付与する不純物元素を添加してp型の不純物領域を形成する。n型の不純物領域211a、n型の不純物領域211bおよびp型の不純物領域におけるn型を付与する不純物元素及びp型を付与する不純物元素の濃度は、1×1019/cm3以上1×1021/cm3以下である。n型を付与する不純物元素及びp型を付与する不純物元素は、イオンドーピング法、イオン注入法等を適宜用いて、半導体基板201及びnウェル領域に添加する。

【0096】

また、ゲート電極209の側面にサイドウォール絶縁層を設ける場合、当該サイドウォール絶縁層と重畳する領域に、n型の不純物領域211a、n型の不純物領域211bおよびp型の不純物領域とは異なる不純物濃度の不純物領域を形成することができる。

【0097】

次に、半導体基板201、素子分離領域203、ゲート絶縁膜207およびゲート電極209上に、スパッタリング法、CVD法等により、絶縁膜215および絶縁膜217を形成する。

【0098】

絶縁膜215および絶縁膜217は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウムなどを用いればよく、積層又は単層で設ける。なお、絶縁膜215をCVD法により形成することで、絶縁膜215の水素含有量が高まる。このような絶縁膜215を用いて加熱処理を行うことにより、半導体基板を水素化し、水素によりダングリングボンドを終端させ、当該半導体基板中の欠陥を低減することができる。

【0099】

また、絶縁膜217として、BPSG(Boron Phosphorus Silicon Glass)などの無機材料、又は、ポリイミド、アクリルなどの有機材料を用いて形成することで、絶縁膜217の平坦性を高めることができる。

【0100】

絶縁膜215又は絶縁膜217を形成した後、n型の不純物領域211a、n型の不純物領域211bおよびp型の不純物領域に添加された不純物元素を活性化するための加熱処理を行う。

【0101】

以上の工程により、nチャネル型のトランジスタ112を作製することができる。

【0102】

次に、絶縁膜215および絶縁膜217の一部を選択的にエッチングして、開口部を形成する。次に、開口部にコンタクトプラグ219aおよびコンタクトプラグ219bを形成する。代表的には、スパッタリング法、CVD法等により導電膜を形成した後、CMP法やエッチングなどにより平坦化処理を行い、導電膜の表面の不要な部分を除去して、導電膜を形成する。

【0103】

コンタクトプラグ219aおよびコンタクトプラグ219bとなる導電膜は、WF6ガスとSiH4ガスからCVD法でタングステンシリサイドを形成し、開口部に導電膜を埋め込むことで形成される。

【0104】

次に、絶縁膜217及びコンタクトプラグ219aおよびコンタクトプラグ219b上に、スパッタリング法、CVD法等により絶縁膜を形成した後、該絶縁膜の一部を選択的にエッチングし、溝部を有する絶縁膜221を形成する。次に、スパッタリング法、CVD法等により導電膜を形成した後、CMP法やエッチングなどにより平坦化処理を行い、該導電膜の表面の不要な部分を除去して、配線223aおよび配線223bを形成する。

【0105】

ここで、配線223a及び配線223bは、それぞれトランジスタ112のソース電極又はドレイン電極として機能する。

【0106】

絶縁膜221は、絶縁膜215と同様の材料を用いて形成することができる。

【0107】

配線223aおよび配線223bとして、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、又はタングステンからなる単体金属、又はこれを主成分とする合金を単層構造又は積層構造として用いる。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、タングステン膜上にチタン膜を積層する二層構造、銅−マグネシウム−アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜と、そのチタン膜上に重ねてアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造などがある。なお、酸化インジウム、酸化錫又は酸化亜鉛を含む透明導電材料を用いてもよい。

【0108】

平坦化された絶縁膜221、配線223aおよび配線223bを用いることで、後に形成する下地膜の平坦性を向上させ、後に形成する酸化物半導体を含むトランジスタにおける電気特性のばらつきを低減することができる。また、歩留まり高く酸化物半導体層を含むトランジスタを形成することができる。

【0109】

次に、加熱処理又はプラズマ処理により、絶縁膜221、配線223aおよび配線223bに含まれる水素を脱離させることが好ましい。この結果、後の加熱処理において、後に形成される絶縁膜及び酸化物半導体膜中に水素が拡散することを防ぐことができる。なお、加熱処理は、不活性雰囲気、減圧雰囲気又は乾燥空気雰囲気にて、100℃以上基板の歪み点未満で行う。また、プラズマ処理は、希ガス、酸素、窒素又は酸化窒素(亜酸化窒素、一酸化窒素、二酸化窒素など)を用いる。

【0110】

次に、絶縁膜221、配線223a及び配線223b上に、スパッタリング法、CVD法等により、酸化物半導体層を用いたトランジスタの下地膜となる絶縁膜225を形成する。絶縁膜225としては、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム、酸化アルミニウム、酸化窒化アルミニウムを単層又は積層して形成する。また、絶縁膜225として、加熱により酸素の一部が脱離する酸化絶縁膜を用いて形成することが好ましい。加熱により酸素の一部が脱離する酸化絶縁膜としては、化学量論比を満たす酸素よりも多くの酸素を含む酸化絶縁膜を用いる。加熱により酸素の一部が脱離する酸化絶縁膜は、加熱により酸素が脱離するため、後の工程で行う加熱により酸化物半導体膜に酸素を拡散させることができる。

【0111】

次いで、絶縁膜225に平坦化処理を行う。実施の形態1に示す方法、即ちCMP処理を行った後、ICPエッチング装置を用いてプラズマ処理を行う。(図7(A)参照)この平坦化処理により絶縁膜225の表面の中心線平均粗さRa75は、0.1nm以下とすることができる。

【0112】

次に、中心線平均粗さRa75が0.1nm以下の表面を有する絶縁膜225上に、スパッタリング法、塗布法、印刷法、蒸着法、PCVD法、PLD法、ALD法又はMBE法等を用いて酸化物半導体膜を形成する。以降の工程は、実施の形態1に従ってトランジスタ460を形成する。

【0113】

本実施の形態では、トランジスタ460の酸化物半導体層として、CAAC(C Axis Aligned Crystal)を含む酸化物半導体層を用いる。CAACを含む酸化物半導体層とは、非単結晶であって、c軸に対しては結晶化した薄膜であり、そのab面に対しては必ずしも配列していない。CAACを含む酸化物半導体層は、グレインバウンダリーを有する新構造の薄膜である。

【0114】

このようなc軸配向を有する結晶を含む酸化物半導体膜を設けることにより、可視光や紫外光の照射によるトランジスタの電気特性の変化を抑制することができる。特に、上述のように、絶縁膜225の表面の中心線平均粗さRa75を、0.1nm以下とすることは有用である。これにより、S値の向上だけでなく、c軸配向を有する結晶を含む酸化物半導体膜の結晶性を向上させ、当該酸化物半導体膜を用いたトランジスタの移動度の向上を図ることもできる。

【0115】

以上の工程により、図7(B)に示すように、酸化物半導体を含んで構成されるトランジスタ460を作製することができる。なお、上記トランジスタ460は、i型(真性半導体)又はi型に限りなく近い酸化物半導体層を有するため、極めて優れた特性を示す。

【0116】

また、図7(B)においては、トランジスタ460のソース電極層431又はドレイン電極層432の一方と、トランジスタ112のゲート電極209と、がソース配線450を介して接続する構成としているが、本実施の形態はこれに限られるものではない。例えば、トランジスタ112上に設けられた絶縁膜の上面にトランジスタ112のゲート電極の上面が露出されるような構造とし、当該ゲート電極の上面に直接接するようにトランジスタ460のソース電極層又はドレイン電極層の一方を設ける構成としても良い。

【0117】

以上の工程により、nチャネル型のトランジスタ112上にトランジスタ460を作製することができる。

【0118】

nチャネル型のトランジスタ112とトランジスタ460を組み合わせることで記憶素子(以下、メモリセルとも記す)を作製することもできる。さらには、トランジスタ460を少なくとも一部に用いてCPU(Central Processing Unit)を構成することもできる。また、トランジスタ460は、DSP(Digital Signal Processor)、カスタムLSI、FPGA(Field Programmable Gate Array)等のLSIにも応用可能である。

【0119】

(実施の形態5)

本実施の形態では、同一基板上に少なくとも駆動回路の一部と、画素部に配置するトランジスタを有する表示装置を作製する例について以下に説明する。

【0120】

画素部に配置するトランジスタは、実施の形態1に従って形成する。また、実施の形態1に示すトランジスタ460はnチャネル型トランジスタであるため、駆動回路のうち、nチャネル型トランジスタで構成することができる駆動回路の一部を画素部のトランジスタと同一基板上に形成する。

【0121】

アクティブマトリクス型表示装置のブロック図の一例を図8(A)に示す。表示装置の基板5300上には、画素部5301、第1の走査線駆動回路5302、第2の走査線駆動回路5303、信号線駆動回路5304を有する。画素部5301には、複数の信号線が信号線駆動回路5304から延伸して配置され、複数の走査線が第1の走査線駆動回路5302、及び第2の走査線駆動回路5303から延伸して配置されている。なお走査線と信号線との交差領域には、各々、表示素子を有する画素がマトリクス状に配置されている。また、表示装置の基板5300はFPC(Flexible Printed Circuit)等の接続部を介して、タイミング制御回路(コントローラ、制御ICともいう)に接続されている。

【0122】

図8(A)では、第1の走査線駆動回路5302、第2の走査線駆動回路5303、信号線駆動回路5304は、画素部5301と同じ基板5300上に形成される。そのため、外部に設ける駆動回路等の部品の数が減るので、コストの低減を図ることができる。また、基板5300外部に駆動回路を設けた場合、配線を延伸させる必要が生じ、配線間の接続数が増える。同じ基板5300上に駆動回路を設けた場合、その配線間の接続数を減らすことができ、信頼性の向上、又は歩留まりの向上を図ることができる。

【0123】

また、画素部の回路構成の一例を図8(B)に示す。ここでは、VA方式の液晶表示パネルの画素構造を示す。

【0124】

この画素構造は、一つの画素に複数の画素電極層が有り、それぞれの画素電極層にトランジスタが接続されている。各トランジスタは、異なるゲート信号で駆動されるように構成されている。すなわち、マルチドメイン設計された画素において、個々の画素電極層に印加する信号を、独立して制御する構成を有している。

【0125】

トランジスタ628のゲート配線622と、トランジスタ629のゲート配線623には、異なるゲート信号を与えることができるように分離されている。一方、データ線として機能するソース電極層又はドレイン電極層626は、トランジスタ628とトランジスタ629で共通に用いられている。トランジスタ628とトランジスタ629は実施の形態1のトランジスタ460を適宜用いることができる。

【0126】

第1の画素電極層と第2の画素電極層の形状は異なっており、スリットによって分離されている。V字型に広がる第1の画素電極層の外側を囲むように第2の画素電極層が形成されている。第1の画素電極層と第2の画素電極層に印加する電圧のタイミングを、トランジスタ628及びトランジスタ629により異ならせることで、液晶の配向を制御している。トランジスタ628はゲート配線622と接続し、トランジスタ629はゲート配線623と接続している。ゲート配線622とゲート配線623は異なるゲート信号を与えることで、トランジスタ628とトランジスタ629の動作タイミングを異ならせることができる。

【0127】

また、容量配線690が設けられ、ゲート絶縁層を誘電体とし、第1の画素電極層または第2の画素電極層と電気的に接続する容量電極と保持容量を形成する。

【0128】

第1の画素電極層と液晶層と対向電極層が重なり合うことで、第1の液晶素子651が形成されている。また、第2の画素電極層と液晶層と対向電極層が重なり合うことで、第2の液晶素子652が形成されている。また、一画素に第1の液晶素子651と第2の液晶素子652が設けられたマルチドメイン構造である。

【0129】

なお、図8(B)に示す画素構成は、これに限定されない。例えば、図8(B)に示す画素に新たにスイッチ、抵抗素子、容量素子、トランジスタ、センサ、又は論理回路などを追加してもよい。

【0130】

また、本実施の形態では、VA方式の液晶表示パネルの例を示したが特に限定されず、様々な方式の液晶表示装置に応用することができる。例えば、視野角特性を改善する方法として、基板主表面に対して水平方向の電界を液晶層に印加する横電界方式(IPS方式とも呼ぶ)に応用することができる。

【0131】

例えば、IPS方式の液晶表示パネルとして、配向膜を用いないブルー相を示す液晶を用いることが好ましい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するために5重量%以上のカイラル剤を混合させた液晶組成物を用いて液晶素子の液晶層に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が1msec以下と短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい。

【0132】

また、液晶表示装置の動画特性を改善するため、バックライトとして複数のLED(発光ダイオード)光源または複数のEL光源などを用いて面光源を構成し、面光源を構成している各光源を独立して1フレーム期間内で間欠点灯駆動する駆動技術(例えばフィールドシーケンシャル方式など)もある。面光源として、3種類以上のLEDを用いてもよいし、白色発光のLEDを用いてもよい。面光源として、異なる色を呈する3種類以上の光源(例えば、R(赤)、G(緑)、B(青))を用いる場合は、カラーフィルタを用いなくともカラー表示が行える。また、面光源として、白色発光のLEDを用いる場合は、カラーフィルタを設けてカラー表示を行う。独立して複数のLEDを制御できるため、液晶層の光学変調の切り替えタイミングに合わせてLEDの発光タイミングを同期させることもできる。LEDを部分的に消灯することができるため、特に一画面を占める黒い表示領域の割合が多い映像表示の場合には、消費電力の低減効果が図れる。

【0133】

また、画素部の回路構成の一例を図8(C)に示す。ここでは、有機EL素子を用いた表示パネルの画素構造を示す。

【0134】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア(電子および正孔)が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。

【0135】

図8(C)は、半導体装置の例としてデジタル時間階調駆動を適用可能な画素構成の一例を示す図である。

【0136】

デジタル時間階調駆動を適用可能な画素の構成及び画素の動作について説明する。ここでは酸化物半導体層をチャネル形成領域に用いるnチャネル型のトランジスタを1つの画素に2つ用いる例を示す。

【0137】

画素6400は、スイッチング用トランジスタ6401、駆動用トランジスタ6402、発光素子6404及び容量素子6403を有している。スイッチング用トランジスタ6401は、ゲート電極が走査線6406に接続され、第1電極(ソース電極層及びドレイン電極層の一方)が信号線6405に接続され、第2電極(ソース電極層及びドレイン電極層の他方)が駆動用トランジスタ6402のゲート電極に接続されている。駆動用トランジスタ6402は、ゲート電極が容量素子6403を介して電源線6407に接続され、第1電極が電源線6407に接続され、第2電極が発光素子6404の第1電極(画素電極)に接続されている。発光素子6404の第2電極は共通電極6408に相当する。共通電極6408は、同一基板上に形成される共通電位線と電気的に接続される。

【0138】

なお、発光素子6404の第2電極(共通電極6408)には低電源電位が設定されている。なお、低電源電位とは、電源線6407に設定される高電源電位を基準にして低電源電位<高電源電位を満たす電位であり、低電源電位としては例えばGND、0Vなどが設定されていても良い。この高電源電位と低電源電位との電位差を発光素子6404に印加して、発光素子6404に電流を流して発光素子6404を発光させるため、高電源電位と低電源電位との電位差が発光素子6404の順方向しきい値電圧以上となるようにそれぞれの電位を設定する。

【0139】

なお、容量素子6403は駆動用トランジスタ6402のゲート容量を代用して省略することも可能である。駆動用トランジスタ6402のゲート容量については、チャネル形成領域とゲート電極との間で容量が形成されていてもよい。

【0140】

ここで、電圧入力電圧駆動方式の場合には、駆動用トランジスタ6402のゲート電極には、駆動用トランジスタ6402が十分にオンするか、オフするかの二つの状態となるようなビデオ信号を入力する。つまり、駆動用トランジスタ6402は線形領域で動作させる。駆動用トランジスタ6402は線形領域で動作させるため、電源線6407の電圧よりも高い電圧を駆動用トランジスタ6402のゲート電極にかける。なお、信号線6405には、(電源線電圧+駆動用トランジスタ6402のVth)以上の電圧をかける。

【0141】

また、デジタル時間階調駆動に代えて、アナログ階調駆動を行う場合、信号の入力を異ならせることで、図8(C)と同じ画素構成を用いることができる。

【0142】

アナログ階調駆動を行う場合、駆動用トランジスタ6402のゲート電極に発光素子6404の順方向電圧+駆動用トランジスタ6402のVth以上の電圧をかける。発光素子6404の順方向電圧とは、所望の輝度とする場合の電圧を指しており、少なくとも順方向しきい値電圧を含む。なお、駆動用トランジスタ6402が飽和領域で動作するようなビデオ信号を入力することで、発光素子6404に電流を流すことができる。駆動用トランジスタ6402を飽和領域で動作させるため、電源線6407の電位は、駆動用トランジスタ6402のゲート電位よりも高くする。ビデオ信号をアナログとすることで、発光素子6404にビデオ信号に応じた電流を流し、アナログ階調駆動を行うことができる。

【0143】

なお、図8(C)に示す画素構成は、これに限定されない。例えば、図8(C)に示す画素に新たにスイッチ、抵抗素子、容量素子、センサ、トランジスタ又は論理回路などを追加してもよい。

【0144】

(実施の形態6)

本明細書に開示する半導体装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。上記実施の形態1で説明したトランジスタ460を具備する電子機器の例について説明する。

【0145】

図9(A)は、携帯型の情報端末であり、本体3001、筐体3002、表示部3003a、3003bなどによって構成されている。この携帯型の情報端末は、少なくともバッテリーを有し、データ情報を保存するためのメモリ(Flash Memory回路、SRAM回路、DRAM回路など)、CPU(中央演算処理回路)やLogic回路を備えた構成とすることが好ましい。実施の形態1で示したトランジスタ460をCPUに用い、低消費電力化を図ってもよい。実施の形態1で示したトランジスタ460はS値が良好であり、低電圧でトランジスタのオンオフの切り換えができるため、トランジスタ460を含む回路を低電圧動作とすることができる。

【0146】

また、表示部3003bはタッチ入力機能を有するパネルとなっており、表示部3003bに表示されるキーボードボタン3004を触れることで画面操作や、文字入力を行うことができる。勿論、表示部3003aをタッチ入力機能を有するパネルとして構成してもよい。実施の形態1で示したトランジスタ460をスイッチング素子として用い、液晶パネルや有機発光パネルを作製して表示部3003a、3003bに適用することにより、携帯型の情報端末とすることができる。

【0147】

図9(A)は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子など)、記録媒体挿入部などを備える構成としてもよい。

【0148】

また、図9(A)に示す携帯型の情報端末は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

【0149】

また、図9(A)に示す携帯型の情報端末は、2つの表示部3003a、3003bのうち、一方を取り外すことができ、取り外した場合の図を図9(B)に示している。表示部3003aもタッチ入力機能を有するパネルとし、持ち運びの際、さらなる軽量化を図ることができ、片手で筐体3002をもってもう片方の手で操作することができ、便利である。

【0150】

さらに、図9(B)に示す筐体3002にアンテナやマイク機能や無線機能を持たせ、携帯電話として用いてもよい。

【0151】

図9(C)は、携帯電話の一例を示している。図9(C)に示す携帯電話機5005は、筐体に組み込まれた表示部5001の他、ヒンジ5002に取り付けられた表示パネル5003、操作ボタン5004、スピーカ、マイクなどを備えている。

【0152】

図9(C)に示す携帯電話機5005は、表示パネル5003がスライドして、表示部5001と重なるようになっており、透光性を有するカバーとしても機能する。表示パネル5003は、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子を用いた表示パネルである。

【0153】

また、両面射出構造の発光素子を用いた表示パネル5003であるため、表示部5001と重ねた状態でも表示を行うことができ、使用者はどちらも表示し、どちらの表示も視認することもできる。表示パネル5003は透光性を有し、表示パネルの向こう側が透けて見えるパネルである。例えば、地図の表示を表示部5001で行い、使用者の所在地ポイントを表示パネル5003で表示することによって現在地を認識しやすい状態を提供することができる。

【0154】

また、携帯電話機5005に撮像素子を設け、テレビ電話として使用する場合、複数の相手の顔を表示しながら、複数の相手と会話ができるため、テレビ会議なども行うことができる。例えば、表示パネル5003に一人または複数の相手の顔を表示し、さらに表示部5001にもう一人の顔を表示させることで、使用者は2人以上の顔を見ながら会話を行うことができる。

【0155】

また、表示パネル5003に表示されたタッチ入力ボタン5006を指などで触れることで、情報を入力することができる。また、電話を掛ける、或いはメールを打つなどの操作は、表示パネル5003をスライドさせて、操作ボタン5004を指などで触れることにより行うことができる。

【0156】

図9(D)は、テレビジョン装置の一例を示している。テレビジョン装置9600は、筐体9601に表示部9603が組み込まれている。表示部9603により、映像を表示することが可能である。また、ここでは、CPUを内蔵したスタンド9605により筐体9601を支持した構成を示している。実施の形態1で示したトランジスタ460を表示部9603やCPUに適用することにより、テレビジョン装置9600とすることができる。

【0157】

テレビジョン装置9600の操作は、筐体9601が備える操作スイッチや、別体のリモコン操作機により行うことができる。また、リモコン操作機に、当該リモコン操作機から出力する情報を表示する表示部を設ける構成としてもよい。

【0158】

なお、テレビジョン装置9600は、受信機やモデムなどを備えた構成とする。受信機により一般のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双方向(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。

【0159】

また、テレビジョン装置9600は、外部接続端子9604や、記憶媒体再生録画部9602、外部メモリスロットを備えている。外部接続端子9604は、USBケーブルなどの各種ケーブルと接続可能であり、パーソナルコンピュータなどとのデータ通信が可能である。記憶媒体再生録画部9602では、ディスク状の記録媒体を挿入し、記録媒体に記憶されているデータの読み出し、記録媒体への書き込みが可能である。また、外部メモリスロットに差し込まれた外部メモリ9606にデータ保存されている画像や映像などを表示部9603に映し出すことも可能である。

【0160】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【符号の説明】

【0161】

112 トランジスタ

201 半導体基板

203 素子分離領域

207 ゲート絶縁膜

209 ゲート電極

211a 不純物領域

211b 不純物領域

215 絶縁膜

217 絶縁膜

219a コンタクトプラグ

219b コンタクトプラグ

221 絶縁膜

223a 配線

223b 配線

225 絶縁膜

400 基板

413 酸化物半導体層

421 ドーパント

422 ゲート保護膜

431 ソース電極層

432 ドレイン電極層

433 層間絶縁膜

434 層間絶縁膜

436 下地膜

441 ゲート電極

442 ゲート絶縁層

443 低抵抗領域

444 酸化物半導体膜

450 ソース配線

451 ドレイン配線

460 トランジスタ

461 トランジスタ

622 ゲート配線

623 ゲート配線

626 ドレイン電極層

628 トランジスタ

629 トランジスタ

651 液晶素子

652 液晶素子

690 容量配線

3001 本体

3002 筐体

3003a 表示部

3003b 表示部

3004 キーボードボタン

5001 表示部

5002 ヒンジ

5003 表示パネル

5004 操作ボタン

5005 携帯電話機

5006 タッチ入力ボタン

5300 基板

5301 画素部

5302 走査線駆動回路

5303 走査線駆動回路

5304 信号線駆動回路

6400 画素

6401 スイッチング用トランジスタ

6402 駆動用トランジスタ

6403 容量素子

6404 発光素子

6405 信号線

6406 走査線

6407 電源線

6408 共通電極

9600 テレビジョン装置

9601 筐体

9602 記憶媒体再生録画部

9603 表示部

9604 外部接続端子

9605 スタンド

9606 外部メモリ

【特許請求の範囲】

【請求項1】

基板上に下地膜を形成し、

前記下地膜に化学機械研磨処理を行い、

前記化学機械研磨処理した後、プラズマ処理を行い、

前記プラズマ処理及び前記化学機械研磨処理により得られた平坦な表面上に酸化物半導体層を形成する半導体装置の作製方法。

【請求項2】

請求項1において、前記プラズマ処理は、希ガスを用いたプラズマ処理であることを特徴とする半導体装置の作製方法。

【請求項3】

基板上に下地膜を形成し、

前記下地膜に第1のプラズマ処理を行い、

前記第1のプラズマ処理した後、化学機械研磨処理を行い、

前記化学機械研磨処理後、第2のプラズマ処理を行い、

前記第1のプラズマ処理、前記化学機械研磨処理、及び前記第2のプラズマ処理により得られた平坦な表面上に酸化物半導体層を形成する半導体装置の作製方法。

【請求項4】

請求項3において、前記第1のプラズマ処理及び前記第2のプラズマ処理は、希ガスを用いたプラズマ処理であることを特徴とする半導体装置の作製方法。

【請求項5】

請求項1乃至4のいずれか一において、前記下地膜は、酸化シリコン膜、酸化ガリウム膜、酸化ハフニウム膜、または酸化アルミニウム膜であることを特徴とする半導体装置の作製方法。

【請求項6】

請求項1乃至5のいずれか一において、前記基板は半導体基板であることを特徴とする半導体装置の作製方法。

【請求項7】

請求項1乃至5のいずれか一において、前記基板はガラス基板であることを特徴とする半導体装置の作製方法。

【請求項8】

請求項1乃至7のいずれか一において、前記プラズマ処理はICPエッチング装置で行うことを特徴とする半導体装置の作製方法。

【請求項1】

基板上に下地膜を形成し、

前記下地膜に化学機械研磨処理を行い、

前記化学機械研磨処理した後、プラズマ処理を行い、

前記プラズマ処理及び前記化学機械研磨処理により得られた平坦な表面上に酸化物半導体層を形成する半導体装置の作製方法。

【請求項2】

請求項1において、前記プラズマ処理は、希ガスを用いたプラズマ処理であることを特徴とする半導体装置の作製方法。

【請求項3】

基板上に下地膜を形成し、

前記下地膜に第1のプラズマ処理を行い、

前記第1のプラズマ処理した後、化学機械研磨処理を行い、

前記化学機械研磨処理後、第2のプラズマ処理を行い、

前記第1のプラズマ処理、前記化学機械研磨処理、及び前記第2のプラズマ処理により得られた平坦な表面上に酸化物半導体層を形成する半導体装置の作製方法。

【請求項4】

請求項3において、前記第1のプラズマ処理及び前記第2のプラズマ処理は、希ガスを用いたプラズマ処理であることを特徴とする半導体装置の作製方法。

【請求項5】

請求項1乃至4のいずれか一において、前記下地膜は、酸化シリコン膜、酸化ガリウム膜、酸化ハフニウム膜、または酸化アルミニウム膜であることを特徴とする半導体装置の作製方法。

【請求項6】

請求項1乃至5のいずれか一において、前記基板は半導体基板であることを特徴とする半導体装置の作製方法。

【請求項7】

請求項1乃至5のいずれか一において、前記基板はガラス基板であることを特徴とする半導体装置の作製方法。

【請求項8】

請求項1乃至7のいずれか一において、前記プラズマ処理はICPエッチング装置で行うことを特徴とする半導体装置の作製方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−38404(P2013−38404A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2012−152279(P2012−152279)

【出願日】平成24年7月6日(2012.7.6)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成24年7月6日(2012.7.6)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]