半導体装置及び半導体装置の製造方法

【課題】半導体装置の動作を安定化できる。

【解決手段】本発明の例に関わる半導体は、半導体基板1と、半導体基板1内に設けられる2つの拡散層7と、2つの拡散層7間のチャネル領域上に設けられるゲート絶縁膜2と、ゲート絶縁膜2上に設けられる複数の導電膜3A,3B,4Aと複数の絶縁膜5A,5B,5Cとが積層された積層体6と積層体6上に設けられるシリサイド層4Bとからなるゲート電極10と、を具備し、積層体6のうち、シリサイド層4Bとは異なる構成の導電膜3Aが、ゲート絶縁膜2と接触することを特徴とする半導体装置。

【解決手段】本発明の例に関わる半導体は、半導体基板1と、半導体基板1内に設けられる2つの拡散層7と、2つの拡散層7間のチャネル領域上に設けられるゲート絶縁膜2と、ゲート絶縁膜2上に設けられる複数の導電膜3A,3B,4Aと複数の絶縁膜5A,5B,5Cとが積層された積層体6と積層体6上に設けられるシリサイド層4Bとからなるゲート電極10と、を具備し、積層体6のうち、シリサイド層4Bとは異なる構成の導電膜3Aが、ゲート絶縁膜2と接触することを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に係り、特に、MISトランジスタ及びそのMISトランジスタを用いた半導体メモリに関する。また、それらの半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体集積回路内には、構成素子の1つとして、MIS(Metal-Insulator-Semiconductor)トランジスタが、設けられている。近年では、素子特性の向上のため、高誘電体ゲート絶縁膜とメタルゲート構造を採用したMISトランジスタや、歪みSi技術を採用したMISトランジスタの開発もなされている。

【0003】

不揮発性半導体メモリ、例えば、フラッシュメモリにおいては、MISトランジスタは、メモリセルアレイ領域の動作を制御するための素子として、主に、メモリセルアレイ領域の周囲に位置する周辺回路領域内に設けられている。

【0004】

メモリセルアレイ領域内のメモリセルは、そのゲート電極がワード線としても機能するため、低抵抗化が望まれている。そのため、メモリセルのゲート電極は、ポリシリコン膜の全体をシリサイド化させた、いわゆる、FUSI(Fully-Silicide)構造が用いられる。

【0005】

フラッシュメモリはその製造工程の簡略化のため、メモリセルとMISトランジスタは、製造工程を共通化させて形成される(例えば、特許文献1参照)。そのため、周辺回路領域とメモリセルアレイ領域内に形成されるゲート電極材の膜厚はそれぞれ同じであるので、ポリシリコン膜と金属材との固相反応によるシリサイド化(シリサイド処理)を行って、メモリセルのゲート電極をFUSI構造とすると、MISトランジスタのゲート電極もFUSI構造となってしまう。

【0006】

MISトランジスタのゲート電極がFUSI構造となった場合、シリサイド層の不均一性に起因して、特性が同一であることが望ましい素子でも、しきい値電圧にばらつきが生じることがある。そのため、FUSI構造のゲート電極を有するMISトランジスタの動作及びそのMISトランジスタを用いたフラッシュメモリの動作が、不安定になる問題があった。

【特許文献1】特開平7−183411号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は、半導体装置の動作の安定化を図る技術を提案する。

【課題を解決するための手段】

【0008】

本発明の例に関わる半導体装置は、半導体基板と、前記半導体基板内に設けられ、ソース/ドレイン領域として機能する2つの拡散層と、前記2つの拡散層間のチャネル領域上に設けられるゲート絶縁膜と、前記ゲート絶縁膜上に設けられる複数の導電膜と複数の絶縁膜とが積層された積層体と前記積層体上に設けられるシリサイド層とからなるゲート電極と、を具備し、前記積層体のうち、前記シリサイド層とは異なる構成の導電膜が、前記ゲート絶縁膜と接触すること備える。

【0009】

本発明の例に関わる半導体装置の製造方法は、半導体基板上に、ゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上に、複数の導電膜と複数の絶縁膜とが積層された積層体を形成する工程と、前記積層体上に、シリコン層を形成する工程と、前記シリコン層及び前記積層体に対して、ゲート加工を施す工程と、前記シリコン層にゲート加工を施した後に、前記半導体基板内に拡散層を形成する工程と、前記シリコン層上に金属膜を形成する工程と、前記積層体が含む前記複数の導電膜のうち前記ゲート絶縁膜と接触する導電膜がシリサイド化しないように、前記シリコン層と前記金属膜との固相反応によって、前記積層体上にシリサイド層を形成する工程と、を備える。

【0010】

本発明の例に関わる半導体装置は、半導体基板と、前記半導体基板内に設けられるメモリセルアレイ領域と、前記メモリセルアレイ領域に隣接して、半導体基板内に設けられる周辺回路領域と、前記メモリセルアレイ領域内の半導体基板内に設けられ、ソース/ドレイン領域となる2つの第1拡散層と、前記第1拡散層間のチャネル領域上に設けられるトンネル絶縁膜と、前記トンネル絶縁膜上に設けられる記憶層と、前記記憶層上に設けられる中間絶縁層と、前記中間絶縁層上に設けられ、第1シリサイド層からなる第1ゲート電極とを有するメモリセルと、前記周辺領域内の半導体基板内に設けられた2つの第2拡散層と、前記第2拡散層間のチャネル領域上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられ、複数の導電膜と複数の絶縁膜とが積層された積層体と前記積層体上に設けられた第2シリサイド層とからなる第2ゲート電極とを有する周辺トランジスタと、を具備し、前記第2ゲート電極を構成している前記積層体のうち、前記第2シリサイド層とは異なる構成の導電膜が、前記ゲート絶縁膜と接触することを備える。

【0011】

本発明の例に関わる半導体装置の製造方法は、周辺回路領域内の半導体基板表面上に、ゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上に、複数の導電膜と複数の絶縁膜とが積層された積層体を形成する工程と、メモリセルアレイ領域内の半導体基板表面上に、トンネル絶縁膜を形成する工程と、前記トンネル絶縁膜上に、記憶層を形成する工程と、前記記憶層上に、中間絶縁膜を形成する工程と、前記中間絶縁膜上に、第1シリコン層を形成する工程と、前記積層体上に、第2シリコン層を形成する工程と、前記メモリセルアレイ領域内においては、前記第1シリコン層、前記中間絶縁膜及び前記記憶層に対してゲート加工を施し、前記周辺回路領域においては、前記第2シリコン層及び前記積層体に対してゲート加工を施す工程と、前記ゲート加工された第1及び第2シリコン層をマスクとして、前記メモリセルアレイ領域及び前記周辺回路領域の半導体基板内に、第1及び第2拡散層をそれぞれ形成する工程と、前記第1及び第2シリコン層上に、金属膜を形成する工程と、前記積層体が含む前記複数の導電膜のうち前記ゲート絶縁膜と接触する導電膜がシリサイド化しないように、前記第1及び第2シリコン層及び前記導電膜と前記金属膜との固相反応によって、前記中間絶縁膜上及び前記積層体上に第1及び第2シリサイド層をそれぞれ形成する工程と、を備える。

【発明の効果】

【0012】

本発明によれば、半導体装置の動作を安定化できる。

【発明を実施するための最良の形態】

【0013】

以下、図面を参照しながら、本発明の例を実施するためのいくつかの形態について詳細に説明する。

【0014】

1. 実施形態

本発明の実施形態に係る半導体装置は、MISトランジスタ及びそれを用いた半導体集積回路である。以下、本発明の実施形態においては、MISトランジスタの構造及びその製造方法について、説明する。また、本発明の実施形態では、MISトランジスタを用いた半導体回路の例として、不揮発性半導体メモリ及びその製造方法についても説明する。

【0015】

[1]第1の実施形態

図1乃至図6を参照して、本発明の第1の実施形態について説明する。

【0016】

(1) 構造

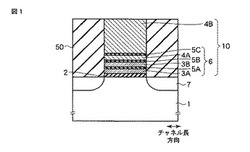

図1及び図2を用いて、本発明の実施形態に係る半導体装置(MISトランジスタ)の構造について、説明する。図1は、本実施形態に係るMISトランジスタのチャネル長方向の構造を示し、図2は、本実施形態に係るMISトランジスタのチャネル幅方向の構造を示している。

【0017】

図1及び図2に示すように、MISトランジスタは、半導体基板(例えば、シリコン基板)1内に設けられた2つの拡散層7、2つの拡散層7間の半導体基板1表面上に設けられたゲート絶縁膜2及びゲート絶縁膜2上に設けられたゲート電極10とを具備している。このゲート電極10は層間絶縁膜50で覆われている。

【0018】

2つの拡散層7は、ソース/ドレイン領域として機能する。この2つの拡散層7間がチャネル領域となり、そのチャネル領域の半導体基板1表面に、ゲート絶縁膜2が設けられている。以下、ソース/ドレイン領域として機能する拡散層のことを、ソース/ドレイン拡散層と呼ぶ。

【0019】

ゲート電極10は、ゲート絶縁膜2上に設けられ、複数の導電膜3A,3B,4Aと複数の絶縁膜5A,5B,5Cとが交互に積層された積層体6と、この積層体6上に設けられたシリサイド層4Bとから構成されている。尚、積層体6において、導電膜及び絶縁膜は、それぞれ3層ずつ図示されているがこの数に限定されるものではない。

【0020】

積層体6は、例えば、導電膜3Aがゲート絶縁膜2に直接接触するように、導電膜と絶縁膜とが順次積層されている。

【0021】

積層体6を構成する複数の絶縁膜5A,5B,5Cは、膜厚が非常に薄い絶縁膜であり、例えば、膜厚が2nm以下のシリコン酸化膜からなっている。

積層体6を構成する複数の導電膜のうち、積層体6の下端側(ゲート絶縁膜2側)の導電膜3Aは、シリサイド層4Bとは異なる導電材料、例えば、ポリシリコンからなっている。また、積層体6の上端側(シリサイド層4B側)の導電膜4Aは、導電膜3Aとは異なる導電材料からなっている。例えば、導電膜4Aはシリサイド層4Bと同じシリサイド材からなっている。導電膜3Aと導電膜4Aとの間にある導電膜3Bは、ポリシリコン膜あるいはシリサイド膜のいずれかである。以下では、導電膜3Aのことをポリシリコン膜3Aとも呼び、導電膜4Aのことシリサイド膜4Aとも呼ぶ。

【0022】

シリサイド層4Bは、例えば、ニッケルシリサイド(NiSi2)膜である。尚、それに限定されるものではなく、シリサイド層4Bは、コバルトシリサイド(CoSi2)膜、チタンシリサイド(TiSi2)膜、タングステンシリサイド(WSi2)膜及びモリブデンシリサイド(MoSi2)膜のいずれか1つであればよい。以下では、NiSi2膜を用いた例について、説明する。

【0023】

図2に示すように、半導体基板1内には、素子分離絶縁膜51が設けられている。この素子分離絶縁膜51によって、隣接する素子領域がそれぞれ電気的に分離される。素子分離絶縁膜51の上面は、例えば、積層体6の最上層に設けられた絶縁膜5Cの上面とほぼ一致するように形成されている。このように、素子分離絶縁膜51の上面の位置を絶縁膜5Cの位置と等しくすることによって、シリサイド層4Bと半導体基板1間の距離が大きく確保され、素子分離絶縁膜51の底部にチャネル(反転層)が形成されるのを防止できる。

【0024】

本発明の実施形態に係るMISトランジスタは、ゲート電極10が積層体6とシリサイド層4Bから構成され、積層体6が含む導電膜3A,3B,4Aのうち、シリサイド層4Bとは異なる材料(例えば、ポリシリコン)からなる導電膜3Aが、ゲート絶縁膜2に接触していることを特徴とする。

【0025】

図1及び図2に示されるMISトランジスタでは、ゲート電極10全体がシリサイド層4BとなるFUSI構造ではなく、ゲート絶縁膜2に接触している導電膜3Aが、例えば、ポリシリコン膜3Aなど、シリサイド層4Bとは異なった導電材からなっている。

【0026】

その具体的な形成方法についての詳細は後述するが、シリサイド層4Bの形成時に、積層体が含む絶縁膜5A,5B,5Cは、シリサイド層4Aを形成するための金属材(例えば、ニッケル(Ni))の原子に対して、その原子の拡散を抑制するストッパ膜として機能する。

【0027】

積層体6がポリシリコン膜とシリコン酸化膜とが交互に積層され、その積層体6上のポリシリコン膜とニッケル膜との固相反応により、シリサイド層4Bが形成される。この際、積層体6を構成する複数の導電膜のうち、シリサイド層4B側の導電膜4Aは、シリサイド層4Bと導電膜4Aとの間に一層の絶縁膜5Cが介在しているのみなので、金属原子の拡散は十分防止されず、導電膜4Aはシリサイド化し、シリサイド膜4Aとなる。

【0028】

その一方で、積層体6を構成する複数の導電膜のうち、ゲート絶縁膜2直上の導電膜3Aは、例えば、ポリシリコン膜3Aから構成される。これは、その導電膜3Aとシリサイド層4Bとの間に、複数の絶縁膜5A,5B,5Cが介在しているため、積層体6内を拡散するNi原子数はゲート絶縁膜2側に近づくにつれて徐々に減少し、導電膜3Aはシリサイド化されないからである。

【0029】

また、上述のように、積層体6内を拡散するNi原子数はゲート絶縁膜2側に近づくにしたがって徐々に減少するので、積層体6内の複数の導電膜は、シリサイド層4B側に位置する導電膜ほどSiに対するNi(金属)の組成比が高く、ゲート絶縁膜2側に位置する導電膜ほどSiに対するNi(金属)の組成比が低くなる。即ち、積層体6内の複数の導電膜毎にSiとNiとの組成比が異なっている。それゆえ、積層体6内に含まれているポリシリコン膜3Aとシリサイド膜4Aとの間の導電膜3Bにおいて、導電膜3BのSi原子に対するNi原子の組成比は、ポリシリコン膜3A内での組成比以上、シリサイド膜4A内での組成比以下である。尚、ゲート絶縁膜2直上の導電膜3Aは、ゲート絶縁膜2と接する部分がシリサイド膜とならなければ良く、例えば、図3に示すように、シリサイド層4B側の一部がシリサイド化されて、積層体6の最下層の導電膜がシリサイド部分4Dとポリシリコン部分3Aとのパーシャル構造となっても良い。

【0030】

これによって、半導体基板とゲート電極間の仕事関数差は、例えば、シリコン基板と均質なポリシリコン膜とによって決まり、それに基づいて、MISトランジスタのしきい値電圧が定義される。よって、ゲート絶縁膜2直上でのシリサイド層の不均一性に起因したしきい値電圧の変動は生じなくなる。それゆえ、ゲート電極が含むシリサイド層の不均一性により、MISトランジスタのしきい値電圧が素子毎にばらつくのを抑制できる。

【0031】

また、MISトランジスタのゲート電極10は、シリサイド層を含んでいるため、ゲート電極10の低抵抗化もなされている。

【0032】

本実施形態では、MISトランジスタのゲート電極10を構成している積層体6は、複数の絶縁膜5A,5B,5Cを含んでいるが、Ni原子(金属原子)の通過を抑制する絶縁膜5A,5B,5Cであっても、絶縁膜5A,5B,5Cの物理膜厚は、例えば、2nm以下と非常に薄い。そのため、本実施形態のMISトランジスタの駆動時に、ゲート電極10に印加された駆動電圧は少ない電位降下で、シリサイド層4Bとゲート絶縁膜2上面に形成されたポリシリコン膜3Aとの間に加わる。それゆえ、ゲート絶縁膜2下の半導体基板1内にチャネル(反転層)が形成されるため、複数の絶縁膜を含む積層体6によってMISトランジスタの動作が阻害されることはない。

【0033】

以上のように、本発明の第1の実施形態に係るMISトランジスタは、そのゲート電極10が複数の導電膜3A,3B,4Aと複数の絶縁膜5A,5B,5Cからなるゲート絶縁膜2上の積層体6と、積層体6上のシリサイド層4Aから構成されている。そして、その積層体6のうちゲート絶縁膜2と接する導電膜3Aは、シリサイド層4Aとは異なる材料、例えば、ポリシリコン膜からなっている。

【0034】

このように、ゲート絶縁膜2上に積層体6を設けることによって、MISトランジスタのゲート電極10はFUSI構造とはならず、ゲート絶縁膜2直上でのシリサイド層の不均一性に起因したMISトランジスタのしきい値電圧の変動を防止することができる。

【0035】

それゆえ、MISトランジスタ及び複数のMISトランジスタを有する半導体集積回路において、素子毎にしきい値電圧がばらつくのを抑制できる。

【0036】

したがって、本発明の第1の実施形態によれば、しきい値電圧のばらつきに起因する半導体装置の動作を安定化できる。

【0037】

(2) 製造方法

図1、図4乃至図7を用いて、本発明の実施形態に係るMISトランジスタの製造方法について、説明する。尚、ここでは、MISトランジスタのチャネル長方向の断面構造のみを図示して、説明する。

【0038】

はじめに、図4に示すように、半導体基板1(例えば、シリコン基板)上に、ゲート絶縁膜2として、例えば、シリコン酸化膜が、熱酸化法によって形成される。尚、ゲート絶縁膜2はシリコン酸化膜に限定されるものではなく、例えば、シリコン酸化膜とシリコン窒化膜との積層膜や、Al2O3、HfO2、Ta2O5、La2O3、LaLiO3、ZrO2、Y2O3、ZrSiO4などの高誘電体絶縁膜でもよい。

【0039】

そして、ゲート絶縁膜2上に、複数の導電膜3A,3B,3Cと複数の絶縁膜5A,5B,5Cとが交互に堆積され、積層体6が形成される。複数の導電膜3A,3B,3Cは、例えば、ポリシリコン膜であり、10nm〜15nm程度の膜厚となるように、CVD(Chemical Vapor Deposition)法を用いて形成される。複数の絶縁膜5A,5B,5Cは、例えば、熱酸化法によって形成されたシリコン酸化膜である。このシリコン酸化膜は、例えば、1nm〜2nm程度の膜厚である。尚、複数の絶縁膜5A,5B,5Cは、ポリシリコン膜上に形成された自然酸化膜でも良い。また、積層体6を形成する場合には、導電膜が、ゲート絶縁膜2に直接接触するように形成されることが好ましい。

【0040】

続いて、図5に示すように、シリコン層8(例えば、ポリシリコン層)が、例えば、CVD法を用いて、積層体6上に形成される。

【0041】

次に、図6に示すように、シリコン層8が所定のゲートパターンとなるように、例えばフォトリソグラフィー技術によってパターニングが施された後、シリコン層8及び積層体6が、例えば、RIE(Reactive Ion Etching)法を用いて、ゲート加工される。そして、ゲート加工されたシリコン層8をマスクとして、半導体基板1内にソース/ドレイン拡散層7が、例えば、イオン注入法を用いて、形成される。その後、ソース/ドレイン拡散層7内に含まれるイオン不純物がアニールによって活性化され、半導体基板1内に固定化される。

【0042】

その後、層間絶縁膜50が、例えば、CVD法を用いて、ゲート加工されたシリコン層8及び積層体6を覆うように形成される。層間絶縁膜50は、例えば、CMP(Chemical Mechanical Polishing)法によって、層間絶縁膜50の上面が、シリコン層8の上面とほぼ一致するように平坦化処理され、シリコン層8の上面が露出する。

【0043】

続いて、図7に示すように、半導体基板上の全面に、例えば、ニッケル(Ni)等の金属膜9が、例えば、スパッタ法を用いて形成される。その結果、シリコン層8の上面に金属膜9が形成されることになる。尚、金属膜9はNiに限定されず、コバルト(Co)、チタン(Ti)、タングステン(W)及びモリブデン(Mo)でも良い。

【0044】

続いて、シリコン層8と金属膜9とに加熱処理を施して、固相反応によるシリサイド化(シリサイド処理)が実行される。これによって、図1に示すように、シリサイド層4Bが積層体6上に形成される。尚、シリコン層8と固相反応しなかった金属膜は、シリサイド処理の後、除去される。

【0045】

このシリサイド処理の際、Ni原子は、シリコン(Si)原子と固相反応(シリサイド反応)を生じつつ、シリコン層8内を移動する。シリサイド層4Bと積層体6との界面まで達したNi原子は、積層体6内に拡散する。

【0046】

積層体6内に含まれる絶縁膜5A,5B,5Cは、Ni原子の拡散を防止するストッパとして機能する。但し、絶縁膜5A,5B,5Cのそれぞれは、非常に薄い膜厚(1nm〜2nm)であるため、1つの絶縁膜(例えば、絶縁膜5C)のみで、すべてのNi原子の拡散を防止できない。そのため、積層体6に含まれる複数の導電膜のうち、シリサイド層4B側に形成された導電膜4Aは、上記のシリサイド処理の際に絶縁膜5Cを通過したNi原子と反応し、シリサイド膜4Aとなる。

【0047】

このように、絶縁膜5A,5B,5Cのそれぞれは膜厚が非常に薄いため、Ni原子の一部が絶縁膜を通過し、導電膜(ポリシリコン膜)とシリサイド反応する。しかし、Ni原子がシリサイド層4B側からゲート絶縁膜2側へと拡散するにつれ、Ni原子は複数の絶縁膜5A,5B,5Cによって徐々に捕獲され、それとともに、絶縁膜5A,5B,5Cを通過したNi原子は導電膜(ポリシリコン膜)と順次反応する。そのため、積層体6内をゲート絶縁膜2側へ移動するNi原子数は減少していく。それゆえ、ゲート絶縁膜2側に形成された導電膜3A内に到達するNi原子はほとんどなく、導電膜3Aの全体がシリサイド膜となることはない。

【0048】

それゆえ、積層体6に含まれる複数の導電膜のうち、ゲート絶縁膜2側に形成された導電膜3Aは、積層体6形成時の状態、すなわち、ポリシリコン膜3Aとなっている。

【0049】

また、上述のように、Ni原子がシリサイド層4B側からゲート絶縁膜2側へと拡散するにしたがって、拡散するNi原子数は徐々に減少していく。それゆえ、積層体6内の複数の導電膜3A,3B,4A毎に、Siに対するNiの組成比がそれぞれ異なっている。

つまり、複数の導電膜のうち、シリサイド層4B側の導電膜のSi原子に対するNi原子の組成比は、ゲート絶縁膜2側の導電膜のSi原子に対するNi原子の組成比よりも高くなっている。そのため、導電膜4A(シリサイド膜)と導電膜3A(ポリシリコン膜)との間にある導電膜3BのSi原子に対するNi原子の組成比は、導電膜4A内のNi原子の組成比よりも低く、導電膜3A内のNi原子の組成比よりも高くなっている。

【0050】

尚、図4乃至図7では、積層体6を構成する導電膜及び絶縁膜は、それぞれ3層ずつ形成されているが、それに限定されるものではなく、Ni原子(メタル原子)がゲート絶縁膜2直上の導電膜(ポリシリコン膜)3Aまで拡散しない積層数で、複数の導電膜と複数の絶縁膜とが積層されていれば良い。また、ゲート絶縁膜2上の導電膜3Aは、その全体がシリサイド膜とならなければよい。つまり、その導電膜3Aのうち、ゲート絶縁膜2と直接接触する部分がシリサイド膜とならなければよく、絶縁膜5Aと直接接触する部分はシリサイド膜となってもよい。

【0051】

このように、ゲート電極を形成するためにシリサイド処理を施しても、ゲート絶縁膜2直上にはポリシリコン膜3Aが残存する。そのため、半導体基板(シリコン基板)1とゲート電極10との仕事関数差は、シリコン基板1とポリシリコン膜3Aとによって決まり、シリサイド膜の不均一性に起因して、MISトランジスタのしきい値電圧の変動が生じることはない。それゆえ、ゲート絶縁膜2直上でのシリサイド層の不均一性に起因して、MISトランジスタのしきい値電圧が素子毎にばらつくのを防止できる。

【0052】

以上の製造工程によって、本発明の実施形態のMISトランジスタが形成される。

【0053】

上述のように、本実施形態では、MISトランジスタのゲート電極10が、複数の導電膜と複数の絶縁膜が交互に積層された積層体6と、シリサイド層4Bとから構成されている。積層体6が含んでいる複数の絶縁膜5A,5B,5Cによって、シリサイド層4Bを形成する際にゲート電極内を拡散するNi原子(金属原子)は、積層体6内での拡散が妨げられる。そのため、積層体6内のいずれかの絶縁膜又は導電膜で、Ni原子の拡散は停止し、ゲート電極10全体がシリサイド化されることがない。

【0054】

それゆえ、ゲート絶縁膜2直上でのシリサイド層の不均一性に起因して、MISトランジスタのしきい値電圧は変動しない。

【0055】

また、上記の製造方法によって形成されたMISトランジスタは、積層体6内に複数の絶縁膜5A,5B,5Cを含んでいるが、それらの絶縁膜の膜厚は非常薄い。そのため、形成されたMISトランジスタの駆動時に、ゲート電極10に印加した駆動電圧は少ない電位降下で、シリサイド層4Bとゲート絶縁膜2上に形成されたポリシリコン膜3Aとの間に加わる。それゆえ、ゲート絶縁膜2下の半導体基板1内にチャネル(反転層)が形成されるため、複数の絶縁膜を含む積層体6によって、MISトランジスタの動作に支障をきたすことはない。

【0056】

したがって、本発明の第1の実施形態に係るMISトランジスタの製造方法によれば、動作が安定したMISトランジスタ及びそれを用いた半導体集積回路を提供できる。

【0057】

[2] 第2の実施形態

以下、図8乃至図20を用いて、本発明の第2の実施形態について説明する。

【0058】

本発明の第1の実施形態では、1つのMISトランジスタの構造及びその製造方法について説明した。第1の実施形態で述べたMISトランジスタは、例えば、ロジック回路やメモリ回路の構成素子として、用いられる。

【0059】

本発明の第2の実施形態は、上記のMISトランジスタを、不揮発性半導体メモリ、例えば、フラッシュメモリの構成素子として用いた例について、説明する。

【0060】

図8は、フラッシュメモリの全体構成を示す概略図である。

【0061】

図8に示すように、フラッシュメモリは、主に、メモリセルアレイ領域100とその周囲の周辺回路領域200とから構成され、それらは同一のチップ(半導体基板)上に設けられている。

【0062】

メモリセルアレイ領域100内には、複数のメモリセル及び複数の選択トランジスタが、設けられている。メモリセルは記憶素子として機能し、選択トランジスタはデータの書き込み/読み出し選択されたメモリセルに対するスイッチ素子として機能する。

【0063】

周辺回路領域200内には、ワード線・選択ゲート線ドライバ210、センスアンプ回路220及び制御回路230が設けられる。これらの回路210,220,230は、複数のMISトランジスタ(以下、周辺トランジスタとも呼ぶ)によって構成されている。周辺トランジスタは、その回路及び素子の機能に応じて、低耐圧系MISトランジスタと高耐圧系MISトランジスタとに区分されている。図1乃至図3で述べたMISトランジスタは、低耐圧系及び高耐圧系MISトランジスタとして用いられる。

【0064】

(1) 構造

図9乃至図13を用いて、本発明の実施形態の実施例に係るフラッシュメモリの構造について、説明する。

【0065】

図9は、本発明の第2の実施形態に係るフラッシュメモリの平面構造を示している。

【0066】

図9に示すように、メモリセルアレイ領域100の表面領域は、複数のアクティブ領域AAと複数の素子分離領域STIとから構成されている。アクティブ領域AA及び素子分離領域STIはY方向に延在し、1つのアクティブ領域AAは2つの素子分離領域STIに挟み込まれている。

【0067】

複数のワード線WLはX方向に延在し、アクティブ領域AAと交差している。複数のメモリセルMCは、ワード線WLとアクティブ領域AAとの交差箇所にそれぞれ設けられている。選択ゲート線SGLもワード線WLと同様にX方向に延び、選択トランジスタSTは選択ゲート線SGLとアクティブ領域AAとの交差箇所にそれぞれ設けられている。

【0068】

アクティブ領域AA内には、メモリセルMC及び選択トランジスタSTのソース/ドレイン拡散層(図示せず)が設けられている。ソース/ドレイン拡散層は、Y方向に互いに隣接するメモリセルMC及び選択トランジスタSTによって共有され、これによって、複数のメモリセルMCと選択トランジスタSTはY方向に直列接続されている。また、Y方向に互いに隣接する2つの選択トランジスタSTのソース/ドレイン拡散層上には、コンタクト80Cが設けられ、1つのコンタクトプラグ80Cが2つの選択トランジスタSTで共有される。

【0069】

以下、本実施形態においては、メモリセルアレイ領域100のうち、メモリセルが配置(形成)される領域をメモリセル形成領域101と呼び、選択トランジスタが配置(形成)される領域を選択ゲート領域102と呼ぶ。

【0070】

周辺回路領域200内には、周辺トランジスタとして、複数の高耐圧系MISトランジスタHVTrと複数の低耐圧系MISトランジスタLVTrとが設けられている。本実施形態においては、説明の簡単化のため、高耐圧系MISトランジスタHVTrと低耐圧系MISトランジスタLVTrとをそれぞれ1つずつ図示している。以下では、本実施形態において、周辺回路領域200のうち、高耐圧系MISトランジスタが配置(形成)される領域を高耐圧領域201と呼び、低耐圧系MISトランジスタが配置(形成)される領域を低耐圧領域202と呼ぶ。

【0071】

高耐圧及び低耐圧領域201,202はそれぞれ素子分離領域STIに取り囲まれ、互いに電気的に分離されたアクティブ領域AAL,AAHがそれぞれ設けられる。

【0072】

周辺トランジスタHVTr,LVTrのゲート電極101,102はアクティブ領域AAH,AALをまたがるようにX方向に延び、素子分離領域STIH,STIL上まで引き出されている。その引き出された箇所において、コンタクト82A,82Bがゲート電極101,102上にそれぞれ設けられる。また、アクティブ領域AAH,AAL内には、ソース/ドレイン拡散層71,72が設けられている。また、コンタクト80A,80Bがソース/ドレイン拡散層71,72上に接続されている。

【0073】

図10は、図9中のA−A線、B−B線及びC−C線にそれぞれ沿う断面構造を図示している。

【0074】

図10に示すように、メモリセル形成領域101内に設けられたメモリセルMCは、例えば、MONOS(Metal-Oxide-Nitride-Oxide-Semiconductor)構造のMISトランジスタである。

【0075】

メモリセルMCのゲート構造は、半導体基板1表面上のゲート絶縁膜20A上に記憶層21Aが設けられ、この記憶層21Aとゲート電極4B3との間に中間絶縁膜22Aが設けられた構造となっている。そして、メモリセルMCは、ソース/ドレイン拡散層27Aを有し、この拡散層27AはY方向(チャネル長方向)に隣接するメモリセルMCで共有されている。

【0076】

ゲート絶縁膜(第1のゲート絶縁膜)20Aは、例えば、膜厚が4nm程度のシリコン酸化膜であり、記憶層21Aへの電荷注入の際にトンネル絶縁膜として機能する。また、ゲート絶縁膜21Aに、シリコン酸化膜/シリコン窒化膜/シリコン酸化膜の積層構造を有するONO膜や、ゲート絶縁膜20A中にゲルマニウム(Ge)等の注入アシスト準位を含む層をトンネル膜の両界面に位置させた膜を用いることにより、ゲート絶縁膜の信頼性を向上でき、さらには、書き込み/消去特性を向上できる。以下では、ゲート絶縁膜20Aのことを、トンネル絶縁膜20Aと呼ぶ。

【0077】

記憶層21Aは、メモリセルMCがMONOS構造のMISトランジスタである場合には、電荷捕獲機能を有する、すなわち、電荷捕獲準位を多く含む膜が用いられ、例えば、シリコン窒化膜などの絶縁膜である。記憶層21Aがシリコン窒化膜である場合、その膜厚は3nm〜10nm程度である。

【0078】

中間絶縁膜22Aは、ゲート電極4B3に電圧が印加された際に、記憶層21Aに捕獲された電荷がゲート電極4B3に放出されるのを阻止する。以下、このような機能を有する中間絶縁膜22Aのことを、ブロック絶縁膜22Aと呼ぶ。ブロック絶縁膜22Aは、例えば、Al2O3、HfO2、Ta2O5、La2O3、LaLiO3、ZrO2、Y2O3、ZrSiO4などの高誘電体膜である。さらには、これらの複合膜や、これらの膜とSiN膜又はSiO2膜との積層膜でも良い。ブロック絶縁膜22Aがアルミナ膜である場合、その膜厚は、例えば、10nm〜30nm程度である。

【0079】

また、図11、図12及び図13は、図7中のD−D線に沿う断面構造の一例を、それぞれ図示している。メモリセルMCは、図11乃至図13のうち、いずれか1つのX方向(チャネル幅方向)に沿う断面構造を有している。

【0080】

記憶層21Aは、例えば、図11、図12又は図13に示すように、X方向(チャネル幅方向)において、素子分離領域STI内に埋め込まれた素子分離絶縁膜51によって、電気的に分離されている。尚、記憶層21AのX方向の断面構造は、図11乃至図13に示す例に限定されるものではない。例えば、記憶層21Aが絶縁膜であれば、それをX方向に隣接するメモリセルMC間で分離する必要はなく、記憶層21Aがアクティブ領域AA上及び素子分離領域STI上をX方向に延在する構造であってもよい。

【0081】

ブロック絶縁膜22Aは、図11に示すように、記憶層21A上及び素子分離絶縁膜51上をX方向に延在していてもよい。また、図12に示すように、素子分離絶縁膜51の構造が、その上面が、記憶層21Aの上面より低く、且つ、記憶層21Aの下面より高い位置まで落とし込まれる構造である場合、ブロック絶縁膜22Aは、記憶層21AのX方向の側面を覆う構造となってもよい。或いは、図13に示すように、ブロック絶縁膜22Aは、素子分離絶縁膜51によって、X方向に隣接するメモリセルMC毎に分離されてもよい。

【0082】

ゲート電極(第1のゲート電極)4B3は、図11、図12又は図13に示すようにX方向に延在し、X方向に隣接する複数のメモリセルMCで共有され、ワード線WLとして機能する。ゲート電極4B3は、例えば、シリサイド層(第1のシリサイド層)の単層構造から構成され、FUSI構造を有している。シリサイド層4B3は、例えば、NiSi2層から構成されているが、これに限定されるものではなく、他のシリサイド材から構成されても良い。

【0083】

図10に示される選択ゲート形成領域102内に設けられる選択トランジスタSTは、例えば、次のような構成を有している。選択トランジスタSTのゲート構造は、半導体基板1表面上のゲート絶縁膜20Bと、ゲート絶縁膜20B上の中間絶縁膜22Bと、中間絶縁膜22B上のゲート電極4B4とから構成されている。また、選択トランジスタSTは、半導体基板1内に設けられたソース/ドレイン拡散層27B,27Cを有している。ソース/ドレイン拡散層27Bは、Y方向に隣接するメモリセルMCと共有され、それによって、選択トランジスタSTはメモリセルMCと直列接続される。ソース/ドレイン拡散層27Cは、層間絶縁膜50内に埋めこまれたコンタクト80Cと接続され、このコンタクト80Cを介して配線層81Cに接続される。

【0084】

選択ゲート形成領域102内の半導体基板1上に設けられた絶縁膜20Bの膜厚は、メモリセルMCのトンネル絶縁膜20Aの膜厚より厚く、例えば、7nm程度である。中間絶縁膜22Bはゲート絶縁膜20B上に設けられている。中間絶縁膜22Bは、メモリセルMCのブロック絶縁膜22Aと同時に形成されるため、ブロック絶縁膜22Aと同一構成であり、例えば、10nm〜30nm程度のアルミナ膜である。

【0085】

本実施形態では、絶縁膜20Bと中間絶縁膜22Bとが、選択トランジスタSTのゲート絶縁膜として機能する。従来では、ドレイン−ソース間耐圧及びゲート耐圧の確保のため、選択トランジスタSTのゲート長は、メモリセルMCのゲート長よりも大きくされている。しかし、本実施形態では、ゲート絶縁膜を十分厚くできるため、ドレイン−ソース間耐圧及びゲート耐圧が十分確保され、選択トランジスタSTのゲート長を小さくできる。

【0086】

選択トランジスタSTのゲート電極4B4はX方向に延在している。ゲート電極4B4は、X方向に隣接する複数の選択トランジスタSTで共有され、選択ゲート線SGLとして機能する。選択ゲート線SGLとしてのゲート電極4B4は、ゲート電極4B3と同時に形成されるため、ワード線WLと同一の構成となっている。

【0087】

また、本実施形態において、選択トランジスタSTは、絶縁膜からなる記憶層21Aが設けられず、ブロック絶縁膜22Aと同一構成の中間絶縁膜22Bが、ゲート絶縁膜20Bとゲート電極4B4との間に介在するのみである。それゆえ、本実施形態の選択トランジスタSTでは、そのゲート電極4B4に電圧を印加しても、記憶層21Aに電荷が注入されることはなく、記憶層の電荷捕獲に起因する選択トランジスタSTのしきい値電圧の変動は生じない。但し、選択トランジスタSTの閾値電圧の変動特性が設計上許容される範囲内であれば、ゲート絶縁膜20Bとブロック絶縁膜22Aとの間に、記憶層と同一構成の膜があってもよい。

【0088】

図10に示される高耐圧系/低耐圧系MISトランジスタHVTr,LVTrは、ほぼ同一の構造を有している。高耐圧/低耐圧MISトランジスタHVTr,LVTrは、半導体基板1内の2つのソース/ドレイン拡散層71,72と、2つのソース/ドレイン拡散層71,72間の半導体基板1表面に設けられたゲート絶縁膜21,22と、ゲート絶縁膜21上のゲート電極101,102とを、それぞれ有している。ソース/ドレイン拡散層71,72は、層間絶縁膜50内のコンタクト80A,80Bを介して、配線層81A,81Bに接続されている。

【0089】

高耐圧領域201内に設けられる高耐圧系MISトランジスタHVTrは、例えば、書き込み電圧などの高電圧の転送を担う。そのため、そのゲート絶縁膜21の膜厚は、低耐圧系MISトランジスタLVTrのゲート絶縁膜22の膜厚よりもさらに厚くされ、それによって、高耐圧系MISトランジスタHVTrのゲート耐圧が確保されている。例えば、ゲート絶縁膜21の膜厚は、30nm以上、50nm以下程度である。

【0090】

低耐圧領域202内に設けられる低耐圧系MISトランジスタLVTrは、例えば、ロジック回路のスイッチ素子として機能する。低耐圧系MISトランジスタLVTrのゲート絶縁膜22の膜厚は、例えば、6nm〜9nm程度である。また、高耐圧系及び低耐圧系MISトランジスタHVTr,LVTrのゲート長は、ドレイン−ソース間耐圧の確保のため、選択トランジスタSTやメモリセルMCのゲート長よりも大きくされている。

【0091】

高耐圧系及び低耐圧系MISトランジスタHVTr,LVTrのゲート電極101,102は、ゲート絶縁膜21,22上の積層体61,62と、積層体61,62上のシリサイド層4B1,4B2とからそれぞれ構成されている。尚、図10において、積層体61は、2つの絶縁膜5A1,5B1と2つの導電膜3A1,4A1とから構成されているが、この積層数に限定されるものではない。積層体62についても同様である。また、積層体61と積層体62の積層数は、製造工程の簡略化の観点から同じであることが好ましい。

【0092】

積層体61,62内に含まれる複数の導電膜のうち、ゲート絶縁膜2直上の導電膜3A1,3A2は、例えば、ポリシリコン膜である。また、シリサイド層4B1,4B2側の導電膜4A1,4A2は、例えば、シリサイド膜である。

【0093】

積層体61,62内の絶縁膜5A1,5B1,5A2,5B2は、例えば、1nm〜2nm程度の膜厚を有し、シリサイド処理時に金属原子(Ni原子)が積層体61,62内全体に拡散するのを抑制する。

【0094】

このように、周辺回路領域200内に設けられた周辺トランジスタHVTr,LVTrは、第1の実施形態で述べたMISトランジスタと同様に、シリサイド層(第2のシリサイド層)4B1,4B2とゲート絶縁膜21,22との間に、複数の導電膜と複数の絶縁膜が交互に積層された積層体61,62を有している。

【0095】

フラッシュメモリにおいては、製造工程の簡略化のため、メモリセルアレイ領域100と周辺回路領域200とで、製造工程の共通化がなされている。そのため、ワード線WLの低抵抗化のためのメモリセルMCのゲート電極4B3のシリサイド処理の際に、高耐圧系及び低耐圧系MISトランジスタHVTr,LVTrのゲート電極もシリサイド処理が施される。

【0096】

しかし、本実施形態では、シリサイド処理を実行しても、メモリセルMCのゲート電極4B3はFUSI構造となるが、高耐圧系MISトランジスタHVTr,LVTrなどのMISトランジスタは、積層体61,62内に含まれる複数の導電膜のうち、ゲート絶縁膜21,22直上の導電膜3A1,3A2はシリサイド化されず、例えば、ポリシリコン膜となる。そのため、ゲート電極101,102と半導体基板1との仕事関数差は、ポリシリコン膜とシリコン基板とによって決まり、その仕事関数差によって、周辺トランジスタHVTr,LVTrのしきい値電圧が定義される。

【0097】

それゆえ、第1の実施形態と同様に、周辺トランジスタ(MISトランジスタ)HVTr,LVTrは、ゲート電極101,102が含むシリサイド層の不均一性に起因して、素子毎にしきい値電圧がばらつくのを抑制できる。

【0098】

尚、第1の実施形態と同様に、積層体61,62内に含まれる絶縁膜は非常に薄い。そのため、ゲート電極101,102に印加された駆動電圧は少ない電位降下で、シリサイド層4B1,4B2とゲート絶縁膜上に形成されたポリシリコン膜3A1,3A2との間に加わる。それゆえ、ゲート絶縁膜21,22直下の半導体基板1内に、チャネル(反転層)が形成されるため、複数の絶縁膜を含む積層体6をゲート絶縁膜21,22上に設けても、周辺トランジスタHVTr,LVTrを正常に駆動させることができる。

【0099】

したがって、本発明の第2の実施形態によれば、フラッシュメモリの動作を安定化できる。

【0100】

(2) 製造方法

(2−1) 製造方法1

図10、図14乃至図19を用いて、本発明の第2の実施形態に係るフラッシュメモリの製造方法について説明する。尚、以下では、主に、メモリセルアレイ領域100及び周辺回路領域200のY方向に沿う断面構造を用いて、各製造工程について説明し、必要に応じて、X方向に沿う断面の製造工程について説明する。

【0101】

はじめに、図14に示すように、周辺回路領域200において、高耐圧領域201内において、例えば、RIE(Reactive Ion Etching)法によって、半導体基板1がエッチングされ、凹部が半導体基板1内に形成される。即ち、高耐圧領域201の半導体基板1表面が、メモリセルアレイ領域100及び低耐圧領域202の半導体基板1表面よりも低くなる。

【0102】

そして、半導体基板1表面に犠牲酸化膜(図示せず)が形成された後、メモリセルアレイ領域100内及び周辺回路領域200内の高耐圧/低耐圧領域201,202に対し、例えば、それぞれ異なるドーズ量のイオン注入が実行され、各素子形成領域に対応した不純物濃度のウェル領域(図示せず)がそれぞれ形成される。

【0103】

犠牲酸化膜が剥離された後、半導体基板1に対して、例えば、熱酸化処理が施され、半導体基板1表面に30〜50nm程度の絶縁膜(例えば、シリコン酸化膜)が形成される。このシリコン酸化膜は、例えば、フォトリソグラフィー技術及びRIE法によって、メモリセルアレイ領域100内及び低耐圧領域202内では除去され、高耐圧領域201内の凹部内(半導体基板1表面)にのみ残存される。高耐圧領域201内に残存したシリコン酸化膜21は、高耐圧系MISトランジスタのゲート絶縁膜となる。

【0104】

続いて、半導体基板1表面に対し、例えば、熱酸化処理が再び実行され、メモリセルアレイ領域100内及び低耐圧領域202内の半導体基板1表面にシリコン酸化膜22が形成される。シリコン酸化膜22は、低耐圧系MISトランジスタのゲート絶縁膜となり、その膜厚は、6nm程度である。尚、各領域間の段差を緩和するため、シリコン酸化膜21の上端とシリコン酸化膜22の上端とがほぼ一致するように、高耐圧領域201内に凹部が形成されることが好ましい。

【0105】

そして、複数の導電膜3A1〜3A3,3B1〜3B3,3C1〜3C3と複数の絶縁膜5A1〜5A3,5B1〜5B3,5C1〜5C3が、メモリセルアレイ領域100及び周辺回路領域200内のシリコン酸化膜21,22上に交互に積層され、積層体61〜63が各領域100,200内に形成される。導電膜3A1〜3A3,3B1〜3B3,3C1〜3C3はポリシリコン膜であり、例えば、CVD法を用いて、10nm〜15nm程度の膜厚となるように形成される。また、絶縁膜5A1〜5A3,5B1〜5B3,5C1〜5C3は、例えば、熱酸化法によって、1nm〜2nm程度の膜厚となるように、形成される。尚、絶縁膜5A1〜5A3,5B1〜5B3,5C1〜5C3は、ポリシリコン膜上に形成された自然酸化膜でも良い。

【0106】

この後、例えば、メモリセルアレイ領域100及び周辺回路領域200に対して、フォトリソグラフィー技術によってパターニングが施され、メモリセルアレイ領域100内に形成された積層体63及び絶縁膜22が、例えば、RIE法によって、除去される。

そして、図15に示すように、メモリセルアレイ領域100内の半導体基板1表面に、ゲート絶縁膜20が、例えば、熱酸化法によって、形成される。このゲート絶縁膜20は、例えば、膜厚が4nm程度のシリコン酸化膜であり、メモリセルのトンネル絶縁膜となる。ゲート絶縁膜20は、ONO膜や、ゲルマニウム(Ge)等の注入アシスト準位を含む層をトンネル膜の両界面に位置させた絶縁膜を用いてもよい。

【0107】

そのゲート絶縁膜20上に、記憶層21Aが、例えば、CVD法により、4nm〜6nm程度の膜厚となるように形成される。記憶層21Aには、例えば、電荷捕獲準位を多く含むシリコン窒化膜が用いられる。そして、記憶層21Aは、フォトリソグラフィー技術及びRIE法を用いて、メモリセル形成領域101内にのみ残存するように、エッチングされ、選択ゲート形成領域102の記憶層は除去される。

【0108】

ここで、図9に示されるメモリセルのD−D線に沿う断面構造が図11に示す構造となる場合には、記憶層21Aの形成後に、フォトリソグラフィー技術及びRIE法により、半導体基板1内に溝が形成される。その溝内に素子分離絶縁膜51が埋め込まれ、アクティブ領域と素子分離領域とが形成される。この素子分離絶縁膜51によって、X方向に隣接するアクティブ領域AAが電気的に分離される。

【0109】

尚、レジストマスクではなくハードマスクを用いて、半導体基板1内に溝を形成しても良い。この場合、記憶層21Aとのエッチングの選択比を確保するため、記憶層21Aとは材質の異なる第1ハードマスク(図示せず)が記憶層21A上に成膜され、この第1ハードマスク上に、さらに、第1ハードマスクの材質と異なる第2ハードマスクが形成される。第1ハードマスクは、例えば、シリコン酸化膜などであり、第2ハードマスクは、アモルファスシリコン、或いは、シリコン窒化膜などである。

形成された溝内に素子分離絶縁膜51が埋め込まれ、ハードマスクをストッパとして、CMP法による平坦化処理を素子分離絶縁膜51に対して行う。その後、素子分離絶縁膜51の上面の高さが記憶層21Aの上面の高さと一致するように、素子分離絶縁膜51に対して、エッチバックを施す。そして、記憶層21A上に残存したハードマスクが剥離される。以上によっても、素子分離絶縁膜51によるX方向に隣接するアクティブ領域AA間の電気的な分離がなされる。

【0110】

また、図9に示されるメモリセルのD−D線に沿う断面構造が図12に示す構造となる場合には、素子分離絶縁膜51の形成後に、メモリセル形成領域101内の素子分離絶縁膜51の上面が、記憶層21Aの上面より低く、且つ、記憶層21Aの下面より高くなるように、例えば、RIE法を用いて、素子分離絶縁膜51がエッチングされる。

【0111】

続いて、中間絶縁膜22及び第1シリコン層(例えば、ポリシリコン層)23が、例えば、CVD法を用いて、メモリセルアレイ領域100内に順次形成される。

【0112】

メモリセル形成領域101内においては、記憶層21A上に、中間絶縁膜22が形成される。中間絶縁膜22は、例えば、膜厚が10nm〜30nm程度のアルミナ(Al2O3)膜である。この中間絶縁膜22は、メモリセルのブロック絶縁膜として機能する。尚、中間絶縁膜22は、アルミナ膜に限定されるものではなく、HfO2など他の高誘電体絶縁材料や、シリコン窒化膜、シリコン酸化膜などの絶縁膜の単層膜や、ONO膜など絶縁膜の積層膜でもよい。一方、セレクトゲート形成領域102においては、上記のように、記憶層が除去されているため、中間絶縁膜22がゲート絶縁膜20と直接接触した構造となっている。

この際、周辺回路領域200においては、積層体61,62上に、記憶層21Aと同一構成の絶縁膜21、中間絶縁膜22及び第1シリコン層23が形成される。

尚、選択ゲート形成領域102内の記憶層の除去の際に、その領域102内の絶縁膜20を同時に除去し、その絶縁膜20よりも膜厚が厚い絶縁膜を新たに形成しても良い。また、本実施形態では、選択ゲート形成領域102内の記憶層は除去したが、それに限定されるものではなく、選択ゲート形成領域102内に記憶層を残存させても良い。

【0113】

次に、図16に示すように、高耐圧/低耐圧領域201,202において、第1シリコン層23、中間絶縁膜22及び記憶層21が、例えば、フォトリソグラフィー技術及びRIE法を用いて、積層体61,62上から除去される。この際、例えば、積層体61,62の最上端に形成された酸化膜(自然酸化膜)は非常に薄いため除去され、これとともに、その酸化膜の直下に設けられた導電膜(ポリシリコン膜)3C1,3C2もエッチングされ、薄くなる。この膜厚の減少分を考慮するとともに、積層体61,62の上端とメモリセル形成領域101内の第1シリコン層23の上端とがほぼ一致する高さとなるように、積層体61,62が形成されることが好ましい。これは、メモリセルアレイ領域100上端と周辺回路領域200上端との段差に起因して、製造工程における加工難度が高くなってしまうのを、抑制するためである。

【0114】

次に、第1シリコン層23及び積層体61,62上に、第2シリコン層25が形成される。尚、第1シリコン層23は形成せずとも良い。即ち、中間絶縁膜22が形成された後、積層体61,62上の中間絶縁膜22のみを除去し、その後、メモリセルアレイ領域100内及び周辺回路領域200内に、第2シリコン層25を形成してもよい。その結果、第1シリコン層23の形成工程を省略することも可能となる。

【0115】

続いて、図17に示すように、例えば、シリコン窒化膜からなるマスク層26をハードマスクとして、メモリセルMC、選択トランジスタST、高耐圧系/低耐圧系MISトランジスタHVTr,LVTrがそれぞれ所定のパターンのゲートサイズとなるように、フォトリソグラフィー技術及びRIE法を用いて、メモリセルアレイ領域100内及び周辺回路領域200内にそれぞれ形成された導電膜及び絶縁膜が、ゲート加工される。

【0116】

そして、ゲート加工された第1、第2シリコン層23,25及び積層体61,62をマスクとして、ソース/ドレイン拡散層27A,27B,27C,71,72が、半導体基板1内に形成される。この後、ソース/ドレイン拡散層27A,27B,27C,71,72内に含まれる不純物イオンが、アニールによって活性化され、半導体基板1内に固定化される。

【0117】

ソース/ドレイン拡散層を形成した後、層間絶縁膜50が、メモリセルMC、各トランジスタST,HVTr,LVTrのゲートを覆うように、例えば、CVD法によって形成される。

【0118】

次に、マスク層26をストッパとして、CMP法による平坦化処理が施される。ここで、メモリセル形成領域101上端と選択ゲート形成領域102上端との間に段差が生じているが、この段差は、記憶層21Aの膜厚分(4nm〜6nm程度)である。そのため、選択ゲート形成領域102のマスク層の上部が削られ、メモリセル形成領域101上端と選択ゲート形成領域102上端はほぼ同じ高さになり、メモリセルアレイ領域100の上端は平坦になる。

【0119】

続いて、マスク層26を剥離し、図18に示すように、第2シリコン層25の上面が露出される。そして、第2シリコン層25上に、金属膜、例えば、Ni膜(金属膜)45がスパッタ法を用いて形成される。これと同時に、周辺回路200においては、第2シリコン層25上に、Ni膜45が形成される。

【0120】

そして、加熱によるシリサイド処理が実行される。これによって、メモリセルアレイ領域100では、Ni膜24に含まれるNi原子が第1及び第2シリコン層23,25内に拡散し、周辺回路領域200では、高耐圧/低耐圧領域201,202内のそれぞれに形成された第2シリコン層25及び積層体61,62内に、Ni原子が拡散する。尚、第2シリコン層25上に形成される金属膜は、Ni膜に限定されず、加熱処理によって、ポリシリコンとの間にシリサイドを形成する金属材料であれば、CoやTiなど、他の材料でも良い。尚、シリコン層及び導電膜と固相反応しなかった金属膜は、シリサイド処理の後、除去される。

【0121】

上記の加熱処理によって、図19に示すように、中間絶縁膜22上のポリシリコン層全体がシリサイド化され、メモリセルアレイ領域100内では、シリサイド(NiSi2)層4B3が形成される。これによって、メモリセルのゲート電極は、低抵抗化のため、FUSI構造のゲート電極とすることができる。同様に、選択トランジスタのゲート電極もシリサイド層4B4となる。

【0122】

一方、周辺回路領域200内では、積層体61,62のうち、Ni膜と直接接触した導電膜(ポリシリコン膜)がシリサイド化され、シリサイド膜4B1,4B2となる。また、絶縁膜5A1,5A2,5B1,5B2が1nm〜2nm程度と薄いため、Ni原子は、絶縁膜5A1,5A2,5B1,5B2を通過して、積層体61,62内を拡散する。

【0123】

Ni原子が積層体61,62内を拡散する際、第1の実施形態と同様に、Ni原子に対して絶縁膜5A1,5A2,5B1,5B2がストッパとして機能するため、Ni原子がシリサイド層4B1,4B2側からゲート絶縁膜21,22側へ移動するにつれて、拡散するNi原子数は徐々に減少する。そのため、積層体61,62内に含まれている複数の導電膜(ポリシリコン膜)毎に、Si原子に対するNi原子の組成比が異なってシリサイド化されていき、積層体61,62内に含まれている複数の導電膜の全てがシリサイド膜とはならない。それゆえ、ゲート絶縁膜21,22直上の導電膜3A1,3A2は、ポリシリコン膜とすることができる。尚、ゲート絶縁膜21,22直上の導電膜3A1,3A2がシリサイド化しないように、導電膜及び絶縁膜の積層数を考慮して積層体61及び62を形成することが好ましい。

【0124】

これによって、メモリセル形成領域101内には、シリサイド層(ゲート電極)4B3、ブロック絶縁膜(中間絶縁膜)22A及び記憶層21Aが、トンネル絶縁膜20A上に形成される。また、選択ゲート形成領域102内には、所定のゲートサイズとなる、シリサイド層(ゲート電極)4B4及びブロック絶縁膜と同一構成の中間絶縁膜22Bとが、トンネル絶縁膜20Aと同一構成の絶縁膜20B上に形成される。本実施形態においては、選択トランジスタSTにおいて、中間絶縁膜22Bと絶縁膜20Bとがゲート絶縁膜として機能する。

【0125】

高耐圧及び低耐圧領域201,202内には、シリサイド層4B1,4B2及び積層体61,62が、ゲート絶縁膜21,22上に形成される。尚、上述のように、積層体61,62内に含まれる複数の導電膜のうち、ゲート絶縁膜21,22直上の導電膜3A1,3A2はポリシリコン膜となっている。

【0126】

続いて、図10に示すように、絶縁層50上に、絶縁層55が形成される。そして、メモリセルアレイ領域100において、ソース/ドレイン拡散層27Cと接触するように、コンタクト80Cが絶縁層50,55内に埋め込まれる。そして、コンタクト80Cと電気的に接続されるように、配線層81Cが絶縁層50,55上に形成される。これと同時に、周辺回路200内の高耐圧領域201及び低耐圧領域202において、コンタクト80A,80Bが、ソース/ドレイン拡散層71,72にそれぞれ直接接触するように、絶縁層50内に埋め込まれる。さらに、配線層81A,81Bが、コンタクト80A,80Bに電気的に接続されるように、絶縁層50,55上に形成される。

【0127】

以上の製造工程によって、本発明の第2の実施形態に係るフラッシュメモリが完成する。

【0128】

本発明の第2の実施形態では、MISトランジスタ(周辺トランジスタ)が設けられる領域200内において、ゲート絶縁膜21,22上に、複数の導電膜と複数の絶縁膜とが交互に積層された積層体61,62が形成される。この積層体61,62上のシリコン層と金属膜(Ni膜)がシリサイド処理される。

【0129】

シリコン層とNi膜との固相反応によってシリサイド層が形成される際に、Ni原子はシリコン層内を拡散するとともに、積層体61,62内へも拡散する。Ni原子は積層体61,62内が含んでいる複数の絶縁膜によって拡散が妨げられる。

【0130】

これによって、シリサイド層4B1,4B2と積層体61,62とからなるMISトランジスタのゲート電極101,102は、積層体61,62内に含まれる複数の導電膜のうち、ゲート絶縁膜21,22直上の導電膜がシリサイド化するのを防止できる。そのため、MISトランジスタは、ゲート絶縁膜2直上のシリサイド層の不均一性に起因して、しきい値電圧が変動しない。

【0131】

それゆえ、MISトランジスタのしきい値電圧は、素子毎にばらつかない。

【0132】

積層体61,62は、複数の絶縁膜5A1,5B1,5A2,5B2も含んでいるが、これらの膜は非常に薄い。そのため、周辺トランジスタのゲート電極101,102に印加された駆動電圧は少ない電位降下で、シリサイド層4B1,4B2とゲート絶縁膜21,22上面に形成されたポリシリコン膜3A1,3A2との間に加わる。それゆえ、ゲート絶縁膜21,22直下の半導体基板1内にチャネル(反転層)が形成されるため、複数の絶縁膜を含む積層体をゲート絶縁膜21,22上に設けても、周辺トランジスタHVTr,LVTrの動作に支障をきたすことはない。

【0133】

また、本実施形態では、周辺トランジスタHVLr,LVTrのゲート電極101,102に積層体61,62を設けることにより、記憶層及びブロック絶縁膜の有無に起因するメモリセルアレイ領域100上端と周辺回路領域200上端との間の段差を緩和できる。それゆえ、その段差に起因して、製造工程の加工難度が高くなるのを抑制できる。

【0134】

したがって、本発明の第2の実施形態に係るフラッシュメモリの製造方法によれば、動作の安定化を図ったフラッシュメモリを提供できる。

【0135】

(2−2) 製造方法2

本発明の第2の実施形態において、メモリセルのD−D線に沿う断面構造が、図13に示す構造の場合の製造方法について、説明する。ここで、製造方法2と上記の製造方法1と異なる点は、素子分離絶縁膜51の形成方法である。

【0136】

尚、図15までの各工程は、製造方法1と同じであるため、説明を省略する。

【0137】

図15に示す工程で、例えば、選択ゲート形成領域102内の記憶層を除去した後、中間絶縁膜22及び第1シリコン層23が、メモリセルアレイ領域100内及び周辺回路領域内100内に形成される。この後、高耐圧/低耐圧領域201,202において、第1シリコン層23、中間絶縁膜22及び記憶層21が、例えば、フォトリソグラフィー技術及びRIE法を用いて、選択的に除去される。

【0138】

その後、レジストマスクを用いたフォトリソグラフィー技術及びRIE法により、半導体基板1内に溝が形成される。尚、ハードマスクを用いて、半導体基板1内に溝を形成してもよい。形成されたハードマスクが記憶層と同じ材料であれば、積層体61,62上に残存させた記憶層とを同時に除去することが可能となる。さらに、周辺回路領域100内の積層体63,63上の記憶層21は除去せずに、記憶層21をハードマスクとして用いても良いし、記憶層21上に同じ材質の材料を積層し、膜厚を厚くして、ハードマスクとして用いても良い。

【0139】

そして、溝内に素子分離絶縁層51が埋め込まれ、アクティブ領域と素子分離領域とが、メモリセルアレイ領域100内及び周辺回路領域200内の半導体基板1内に形成される。この素子分離絶縁層51によって、X方向に隣接するメモリセルアレイ領域100内のアクティブ領域AAが電気的に分離される。その後の工程は、図16乃至図19に示す工程と同様である。

【0140】

以上の工程によって、メモリセルのD−D線に沿う断面構造が、図13に示す構造となるように、メモリセルを形成することができる。

【0141】

(3) 変形例

図20を用いて、本発明の第2の実施形態に係るフラッシュメモリの変形例について、説明する。尚、図10乃至図13に示す部材と同一部材に関しては、同一符号を付し、詳細な説明は必要に応じて行う。

【0142】

図10乃至図13においては、MONOS構造のメモリセルを用いたフラッシュメモリについて、説明した。しかし、それに限定されず、絶縁層の代わりに導電層(例えば、ポリシリコン)を記憶層とした、いわゆる、積層ゲート構造のメモリセルを用いたフラッシュメモリでもよい。本変形例では、記憶層のことを、フローティングゲート電極30Aと呼ぶ。

【0143】

図20は、本変形例に係るフラッシュメモリのY方向(チャネル長方向)に沿う断面構造を示している。

【0144】

図20に示すように、メモリセルアレイ領域100内において、メモリセルMCは、フローティングゲート電極30Aとコントロールゲート電極4B3が積層されたスタックゲート構造となっている。具体的には、メモリセルMCは、以下の構成のゲート構造を有している。フローティングゲート電極30Aは、ゲート絶縁膜(トンネル絶縁膜)20A上に、設けられている。フローティングゲート電極30Aは、例えば、ポリシリコン膜からなっている。このフローティングゲート電極30Aに電荷が蓄積されることによって、メモリセルMCにデータが保持される。

【0145】

フローティングゲート電極30A上には、中間絶縁膜31Aが設けられている。中間絶縁膜31上には、コントロールゲート電極4B3設けられている。コントロールゲート電極4B3は、ワード線として機能し、シリサイド層(例えば、NiSi2層)の単層構造である。

【0146】

メモリセルがフローティングゲート電極30Aを有する場合、選択トランジスタSTのゲート構造は、ゲート絶縁膜2B上の下層ゲート電極30B上に、上層ゲート電極4B4が積層された構造となる。下層ゲート電極30Bと上層ゲート電極4B4との間には、中間絶縁膜31Aと同一構成の絶縁膜31Bが介在している。この絶縁膜31B内には、開口部が形成されており、この開口部を介して、下層ゲート電極30Bと上層ゲート電極4B4は直接接触する。

【0147】

下層ゲート電極30Bはフローティングゲート電極30Aと同時に形成され、上層ゲート電極4B4はコントロールゲート電極4B3と同時に形成される。そのため、上層ゲート電極4B4はシリサイド層となる。尚、本変形例の選択トランジスタにおいては、シリサイド層4B3,4B4の形成の際に、中間絶縁膜31Bに形成された開口部を介して、Ni原子(金属原子)が下層ゲート電極30B内にも拡散するが、中間絶縁膜31Bが介在している部分もあるため、下層ゲート電極30Bの全体がシリサイド層となることはない。

【0148】

また、本変形例においても、周辺回路領域200内に設けられる高耐圧系MISトランジスタHVTrのゲート電極101は、複数の導電膜3A1,4A1と複数の絶縁膜5A1,5B1が交互に積層された積層体61と、積層体61上に設けられたシリサイド層4B1とから構成されている。低耐圧系MISトランジスタLVTrのゲート電極102も同様に積層体61とシリサイド層4B2とから構成されている。

【0149】

それらの積層体61,62おいて、ゲート絶縁膜21,22直上の導電膜3A1,3A2は、シリサイド層4B1,4B2とは異なった導電材(例えば、ポリシリコン)からなっている。

【0150】

それゆえ、図9乃至図13に示すフラッシュメモリ内に設けられた周辺トランジスタと同様の効果が得られ、シリサイド層4B1,4B2の不均一性に起因するMISトランジスタのしきい値電圧のばらつきが生じることはない。

【0151】

したがって、本発明の第2の実施形態の変形例においても、MISトランジスタ(周辺トランジスタ)の動作を安定化できる。

【0152】

尚、図20に示す本変形例のフラッシュメモリの製造方法は、図14乃至図20を用いて説明した製造工程とほぼ同一である。相違点は以下の通りである。

【0153】

周辺領域200内のゲート絶縁膜21,22上に、複数の導電層と複数の絶縁膜からなる積層体が形成された後(図14参照)、メモリセルアレイ領域100内に形成された積層体及び絶縁膜は除去される。図15に示す工程と同様に、メモリセルアレイ領域100内の半導体基板1表面上に、ゲート絶縁膜20A,20Bが形成される。

この後、記憶層としての絶縁膜の代わりに、フローティングゲート電極30Aとなる、例えば、ポリシリコン膜30Aが、ゲート絶縁膜20A,20B上に形成される。そして、ポリシリコン膜30A上に、中間絶縁膜31A,31Bが形成される。この際、選択ゲート形成領域102内において、中間絶縁膜31Bに開口部が形成される。

【0154】

そして、図16乃至図19に示す工程と同様の工程によって、中間絶縁膜上に、第1シリコン層が形成される。そして、ゲート加工工程及びソース/ドレイン拡散層形成工程が実行され、絶縁層50が形成される。

【0155】

例えば、第2シリコン層が形成された後、金属膜が形成され、シリサイド処理(固相反応処理)が施される。シリサイド処理によって、シリサイド層4B1,4B2,4B3,4B4が形成された後、絶縁層55、コンタクト80A,80B,80C及び配線層81A,81B,81Cが形成され、本変形例のフラッシュメモリが完成する。

【0156】

フローティングゲート電極を有するメモリセルを用いた場合であっても、本変形例のフラッシュメモリは、メモリセルのゲート電極(制御ゲート電極)がFUSI構造となり、周辺トランジスタHVTr,LVTrのゲート電極101,102がゲート絶縁膜21,22直上でシリサイド膜を含まない導電膜(ポリシリコン膜)となっている。

【0157】

以上の製造工程によって、本発明の第2の実施形態の変形例に係るフラッシュメモリを作製できる。

【0158】

したがって、本発明の第2の実施形態の変形例においても、動作を安定化できるフラッシュメモリを提供できる。

【0159】

2. その他

本発明の第1及び第2の実施形態によれば、MISトランジスタの動作を安定化できる。

【0160】

尚、本発明の第2の実施形態において、フラッシュメモリを例に説明したが、例えば、MRAM(Magnetoresistive Random Access Memory)、PRAM(Phase change Random Access Memory)またはReRAM(Resistance Random Access Memory)などに用いられる周辺トランジスタ(MISトランジスタ)でもよい。その場合においても、本発明の実施形態と同様の効果が得られる。

【0161】

本発明の例は、上述の実施形態に限定されるものではなく、その要旨を逸脱しない範囲で、各構成要素を変形して具体化できる。また、上述の実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を構成できる。例えば、上述の実施形態に開示される全構成要素から幾つかの構成要素を削除してもよいし、異なる実施形態の構成要素を適宜組み合わせてもよい。

【図面の簡単な説明】

【0162】

【図1】本発明の実施形態に係るMISトランジスタの構造を示す断面図。

【図2】本発明の実施形態に係るMISトランジスタの構造を示す断面図。

【図3】本発明の実施形態に係るMISトランジスタの構造を示す断面図。

【図4】本発明の実施形態に係るMISトランジスタの製造方法の一工程を示す工程図。

【図5】本発明の実施形態に係るMISトランジスタの製造工程の一工程を示す工程図。

【図6】本発明の実施形態に係るMISトランジスタの製造工程の一工程を示す工程図。

【図7】本発明の実施形態に係るMISトランジスタの製造工程の一工程を示す工程図。

【図8】本発明の第2の実施形態に係る不揮発性半導体メモリの全体構成を示す概略図。

【図9】本発明の第2の実施形態に係るフラッシュメモリの構造を示す平面図。

【図10】本発明の第2の実施形態に係るフラッシュメモリの構造を示す断面図。

【図11】本発明の第2の実施形態に係るフラッシュメモリの構造を示す断面図。

【図12】本発明の第2の実施形態に係るフラッシュメモリの構造を示す断面図。

【図13】本発明の第2の実施形態に係るフラッシュメモリの構造を示す断面図。

【図14】本発明の第2の実施形態に係るフラッシュメモリの製造工程の一工程を示す断面図。

【図15】本発明の第2の実施形態に係るフラッシュメモリの製造工程の一工程を示す断面図。

【図16】本発明の第2の実施形態に係るフラッシュメモリの製造工程の一工程を示す断面図。

【図17】本発明の第2の実施形態に係るフラッシュメモリの製造工程の一工程を示す断面図。

【図18】本発明の第2の実施形態に係るフラッシュメモリの製造工程の一工程を示す断面図。

【図19】本発明の第2の実施形態の変形例に係るフラッシュメモリの構造を示す断面図。

【図20】本発明の第2の実施形態の変形例に係るフラッシュメモリの構造を示す断面図。

【符号の説明】

【0163】

1:半導体基板、2,21,22:ゲート絶縁膜、4B,4B1〜4B4:シリサイド層、6,61,62:積層体、3A,3A1,3A2,3B,3C:導電膜,4A,4A1,4A2:導電膜、5A,5A1,5A2,5B,5B1,5B2,5C:絶縁膜、7,71,72,27A,27B,27C:ソース/ドレイン拡散層、10,101,102,30B:ゲート電極、30A:フローティングゲート電極、50,55:絶縁層(層間絶縁膜)、51:素子分離絶縁膜、80A,80B,80C:コンタクト、81A,81B,81C:配線層、100:メモリセルアレイ領域、101:メモリセル形成領域、102:選択ゲート形成領域、200:周辺回路領域、201:高耐圧領域、202:低耐圧領域。

【技術分野】

【0001】

本発明は、半導体装置に係り、特に、MISトランジスタ及びそのMISトランジスタを用いた半導体メモリに関する。また、それらの半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体集積回路内には、構成素子の1つとして、MIS(Metal-Insulator-Semiconductor)トランジスタが、設けられている。近年では、素子特性の向上のため、高誘電体ゲート絶縁膜とメタルゲート構造を採用したMISトランジスタや、歪みSi技術を採用したMISトランジスタの開発もなされている。

【0003】

不揮発性半導体メモリ、例えば、フラッシュメモリにおいては、MISトランジスタは、メモリセルアレイ領域の動作を制御するための素子として、主に、メモリセルアレイ領域の周囲に位置する周辺回路領域内に設けられている。

【0004】

メモリセルアレイ領域内のメモリセルは、そのゲート電極がワード線としても機能するため、低抵抗化が望まれている。そのため、メモリセルのゲート電極は、ポリシリコン膜の全体をシリサイド化させた、いわゆる、FUSI(Fully-Silicide)構造が用いられる。

【0005】

フラッシュメモリはその製造工程の簡略化のため、メモリセルとMISトランジスタは、製造工程を共通化させて形成される(例えば、特許文献1参照)。そのため、周辺回路領域とメモリセルアレイ領域内に形成されるゲート電極材の膜厚はそれぞれ同じであるので、ポリシリコン膜と金属材との固相反応によるシリサイド化(シリサイド処理)を行って、メモリセルのゲート電極をFUSI構造とすると、MISトランジスタのゲート電極もFUSI構造となってしまう。

【0006】

MISトランジスタのゲート電極がFUSI構造となった場合、シリサイド層の不均一性に起因して、特性が同一であることが望ましい素子でも、しきい値電圧にばらつきが生じることがある。そのため、FUSI構造のゲート電極を有するMISトランジスタの動作及びそのMISトランジスタを用いたフラッシュメモリの動作が、不安定になる問題があった。

【特許文献1】特開平7−183411号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は、半導体装置の動作の安定化を図る技術を提案する。

【課題を解決するための手段】

【0008】

本発明の例に関わる半導体装置は、半導体基板と、前記半導体基板内に設けられ、ソース/ドレイン領域として機能する2つの拡散層と、前記2つの拡散層間のチャネル領域上に設けられるゲート絶縁膜と、前記ゲート絶縁膜上に設けられる複数の導電膜と複数の絶縁膜とが積層された積層体と前記積層体上に設けられるシリサイド層とからなるゲート電極と、を具備し、前記積層体のうち、前記シリサイド層とは異なる構成の導電膜が、前記ゲート絶縁膜と接触すること備える。

【0009】

本発明の例に関わる半導体装置の製造方法は、半導体基板上に、ゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上に、複数の導電膜と複数の絶縁膜とが積層された積層体を形成する工程と、前記積層体上に、シリコン層を形成する工程と、前記シリコン層及び前記積層体に対して、ゲート加工を施す工程と、前記シリコン層にゲート加工を施した後に、前記半導体基板内に拡散層を形成する工程と、前記シリコン層上に金属膜を形成する工程と、前記積層体が含む前記複数の導電膜のうち前記ゲート絶縁膜と接触する導電膜がシリサイド化しないように、前記シリコン層と前記金属膜との固相反応によって、前記積層体上にシリサイド層を形成する工程と、を備える。

【0010】

本発明の例に関わる半導体装置は、半導体基板と、前記半導体基板内に設けられるメモリセルアレイ領域と、前記メモリセルアレイ領域に隣接して、半導体基板内に設けられる周辺回路領域と、前記メモリセルアレイ領域内の半導体基板内に設けられ、ソース/ドレイン領域となる2つの第1拡散層と、前記第1拡散層間のチャネル領域上に設けられるトンネル絶縁膜と、前記トンネル絶縁膜上に設けられる記憶層と、前記記憶層上に設けられる中間絶縁層と、前記中間絶縁層上に設けられ、第1シリサイド層からなる第1ゲート電極とを有するメモリセルと、前記周辺領域内の半導体基板内に設けられた2つの第2拡散層と、前記第2拡散層間のチャネル領域上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられ、複数の導電膜と複数の絶縁膜とが積層された積層体と前記積層体上に設けられた第2シリサイド層とからなる第2ゲート電極とを有する周辺トランジスタと、を具備し、前記第2ゲート電極を構成している前記積層体のうち、前記第2シリサイド層とは異なる構成の導電膜が、前記ゲート絶縁膜と接触することを備える。

【0011】

本発明の例に関わる半導体装置の製造方法は、周辺回路領域内の半導体基板表面上に、ゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上に、複数の導電膜と複数の絶縁膜とが積層された積層体を形成する工程と、メモリセルアレイ領域内の半導体基板表面上に、トンネル絶縁膜を形成する工程と、前記トンネル絶縁膜上に、記憶層を形成する工程と、前記記憶層上に、中間絶縁膜を形成する工程と、前記中間絶縁膜上に、第1シリコン層を形成する工程と、前記積層体上に、第2シリコン層を形成する工程と、前記メモリセルアレイ領域内においては、前記第1シリコン層、前記中間絶縁膜及び前記記憶層に対してゲート加工を施し、前記周辺回路領域においては、前記第2シリコン層及び前記積層体に対してゲート加工を施す工程と、前記ゲート加工された第1及び第2シリコン層をマスクとして、前記メモリセルアレイ領域及び前記周辺回路領域の半導体基板内に、第1及び第2拡散層をそれぞれ形成する工程と、前記第1及び第2シリコン層上に、金属膜を形成する工程と、前記積層体が含む前記複数の導電膜のうち前記ゲート絶縁膜と接触する導電膜がシリサイド化しないように、前記第1及び第2シリコン層及び前記導電膜と前記金属膜との固相反応によって、前記中間絶縁膜上及び前記積層体上に第1及び第2シリサイド層をそれぞれ形成する工程と、を備える。

【発明の効果】

【0012】

本発明によれば、半導体装置の動作を安定化できる。

【発明を実施するための最良の形態】

【0013】

以下、図面を参照しながら、本発明の例を実施するためのいくつかの形態について詳細に説明する。

【0014】

1. 実施形態

本発明の実施形態に係る半導体装置は、MISトランジスタ及びそれを用いた半導体集積回路である。以下、本発明の実施形態においては、MISトランジスタの構造及びその製造方法について、説明する。また、本発明の実施形態では、MISトランジスタを用いた半導体回路の例として、不揮発性半導体メモリ及びその製造方法についても説明する。

【0015】

[1]第1の実施形態

図1乃至図6を参照して、本発明の第1の実施形態について説明する。

【0016】

(1) 構造

図1及び図2を用いて、本発明の実施形態に係る半導体装置(MISトランジスタ)の構造について、説明する。図1は、本実施形態に係るMISトランジスタのチャネル長方向の構造を示し、図2は、本実施形態に係るMISトランジスタのチャネル幅方向の構造を示している。

【0017】

図1及び図2に示すように、MISトランジスタは、半導体基板(例えば、シリコン基板)1内に設けられた2つの拡散層7、2つの拡散層7間の半導体基板1表面上に設けられたゲート絶縁膜2及びゲート絶縁膜2上に設けられたゲート電極10とを具備している。このゲート電極10は層間絶縁膜50で覆われている。

【0018】

2つの拡散層7は、ソース/ドレイン領域として機能する。この2つの拡散層7間がチャネル領域となり、そのチャネル領域の半導体基板1表面に、ゲート絶縁膜2が設けられている。以下、ソース/ドレイン領域として機能する拡散層のことを、ソース/ドレイン拡散層と呼ぶ。

【0019】

ゲート電極10は、ゲート絶縁膜2上に設けられ、複数の導電膜3A,3B,4Aと複数の絶縁膜5A,5B,5Cとが交互に積層された積層体6と、この積層体6上に設けられたシリサイド層4Bとから構成されている。尚、積層体6において、導電膜及び絶縁膜は、それぞれ3層ずつ図示されているがこの数に限定されるものではない。

【0020】

積層体6は、例えば、導電膜3Aがゲート絶縁膜2に直接接触するように、導電膜と絶縁膜とが順次積層されている。

【0021】

積層体6を構成する複数の絶縁膜5A,5B,5Cは、膜厚が非常に薄い絶縁膜であり、例えば、膜厚が2nm以下のシリコン酸化膜からなっている。

積層体6を構成する複数の導電膜のうち、積層体6の下端側(ゲート絶縁膜2側)の導電膜3Aは、シリサイド層4Bとは異なる導電材料、例えば、ポリシリコンからなっている。また、積層体6の上端側(シリサイド層4B側)の導電膜4Aは、導電膜3Aとは異なる導電材料からなっている。例えば、導電膜4Aはシリサイド層4Bと同じシリサイド材からなっている。導電膜3Aと導電膜4Aとの間にある導電膜3Bは、ポリシリコン膜あるいはシリサイド膜のいずれかである。以下では、導電膜3Aのことをポリシリコン膜3Aとも呼び、導電膜4Aのことシリサイド膜4Aとも呼ぶ。

【0022】

シリサイド層4Bは、例えば、ニッケルシリサイド(NiSi2)膜である。尚、それに限定されるものではなく、シリサイド層4Bは、コバルトシリサイド(CoSi2)膜、チタンシリサイド(TiSi2)膜、タングステンシリサイド(WSi2)膜及びモリブデンシリサイド(MoSi2)膜のいずれか1つであればよい。以下では、NiSi2膜を用いた例について、説明する。

【0023】

図2に示すように、半導体基板1内には、素子分離絶縁膜51が設けられている。この素子分離絶縁膜51によって、隣接する素子領域がそれぞれ電気的に分離される。素子分離絶縁膜51の上面は、例えば、積層体6の最上層に設けられた絶縁膜5Cの上面とほぼ一致するように形成されている。このように、素子分離絶縁膜51の上面の位置を絶縁膜5Cの位置と等しくすることによって、シリサイド層4Bと半導体基板1間の距離が大きく確保され、素子分離絶縁膜51の底部にチャネル(反転層)が形成されるのを防止できる。

【0024】

本発明の実施形態に係るMISトランジスタは、ゲート電極10が積層体6とシリサイド層4Bから構成され、積層体6が含む導電膜3A,3B,4Aのうち、シリサイド層4Bとは異なる材料(例えば、ポリシリコン)からなる導電膜3Aが、ゲート絶縁膜2に接触していることを特徴とする。

【0025】

図1及び図2に示されるMISトランジスタでは、ゲート電極10全体がシリサイド層4BとなるFUSI構造ではなく、ゲート絶縁膜2に接触している導電膜3Aが、例えば、ポリシリコン膜3Aなど、シリサイド層4Bとは異なった導電材からなっている。

【0026】

その具体的な形成方法についての詳細は後述するが、シリサイド層4Bの形成時に、積層体が含む絶縁膜5A,5B,5Cは、シリサイド層4Aを形成するための金属材(例えば、ニッケル(Ni))の原子に対して、その原子の拡散を抑制するストッパ膜として機能する。

【0027】

積層体6がポリシリコン膜とシリコン酸化膜とが交互に積層され、その積層体6上のポリシリコン膜とニッケル膜との固相反応により、シリサイド層4Bが形成される。この際、積層体6を構成する複数の導電膜のうち、シリサイド層4B側の導電膜4Aは、シリサイド層4Bと導電膜4Aとの間に一層の絶縁膜5Cが介在しているのみなので、金属原子の拡散は十分防止されず、導電膜4Aはシリサイド化し、シリサイド膜4Aとなる。

【0028】

その一方で、積層体6を構成する複数の導電膜のうち、ゲート絶縁膜2直上の導電膜3Aは、例えば、ポリシリコン膜3Aから構成される。これは、その導電膜3Aとシリサイド層4Bとの間に、複数の絶縁膜5A,5B,5Cが介在しているため、積層体6内を拡散するNi原子数はゲート絶縁膜2側に近づくにつれて徐々に減少し、導電膜3Aはシリサイド化されないからである。

【0029】

また、上述のように、積層体6内を拡散するNi原子数はゲート絶縁膜2側に近づくにしたがって徐々に減少するので、積層体6内の複数の導電膜は、シリサイド層4B側に位置する導電膜ほどSiに対するNi(金属)の組成比が高く、ゲート絶縁膜2側に位置する導電膜ほどSiに対するNi(金属)の組成比が低くなる。即ち、積層体6内の複数の導電膜毎にSiとNiとの組成比が異なっている。それゆえ、積層体6内に含まれているポリシリコン膜3Aとシリサイド膜4Aとの間の導電膜3Bにおいて、導電膜3BのSi原子に対するNi原子の組成比は、ポリシリコン膜3A内での組成比以上、シリサイド膜4A内での組成比以下である。尚、ゲート絶縁膜2直上の導電膜3Aは、ゲート絶縁膜2と接する部分がシリサイド膜とならなければ良く、例えば、図3に示すように、シリサイド層4B側の一部がシリサイド化されて、積層体6の最下層の導電膜がシリサイド部分4Dとポリシリコン部分3Aとのパーシャル構造となっても良い。

【0030】

これによって、半導体基板とゲート電極間の仕事関数差は、例えば、シリコン基板と均質なポリシリコン膜とによって決まり、それに基づいて、MISトランジスタのしきい値電圧が定義される。よって、ゲート絶縁膜2直上でのシリサイド層の不均一性に起因したしきい値電圧の変動は生じなくなる。それゆえ、ゲート電極が含むシリサイド層の不均一性により、MISトランジスタのしきい値電圧が素子毎にばらつくのを抑制できる。

【0031】

また、MISトランジスタのゲート電極10は、シリサイド層を含んでいるため、ゲート電極10の低抵抗化もなされている。

【0032】

本実施形態では、MISトランジスタのゲート電極10を構成している積層体6は、複数の絶縁膜5A,5B,5Cを含んでいるが、Ni原子(金属原子)の通過を抑制する絶縁膜5A,5B,5Cであっても、絶縁膜5A,5B,5Cの物理膜厚は、例えば、2nm以下と非常に薄い。そのため、本実施形態のMISトランジスタの駆動時に、ゲート電極10に印加された駆動電圧は少ない電位降下で、シリサイド層4Bとゲート絶縁膜2上面に形成されたポリシリコン膜3Aとの間に加わる。それゆえ、ゲート絶縁膜2下の半導体基板1内にチャネル(反転層)が形成されるため、複数の絶縁膜を含む積層体6によってMISトランジスタの動作が阻害されることはない。

【0033】

以上のように、本発明の第1の実施形態に係るMISトランジスタは、そのゲート電極10が複数の導電膜3A,3B,4Aと複数の絶縁膜5A,5B,5Cからなるゲート絶縁膜2上の積層体6と、積層体6上のシリサイド層4Aから構成されている。そして、その積層体6のうちゲート絶縁膜2と接する導電膜3Aは、シリサイド層4Aとは異なる材料、例えば、ポリシリコン膜からなっている。

【0034】

このように、ゲート絶縁膜2上に積層体6を設けることによって、MISトランジスタのゲート電極10はFUSI構造とはならず、ゲート絶縁膜2直上でのシリサイド層の不均一性に起因したMISトランジスタのしきい値電圧の変動を防止することができる。

【0035】

それゆえ、MISトランジスタ及び複数のMISトランジスタを有する半導体集積回路において、素子毎にしきい値電圧がばらつくのを抑制できる。

【0036】

したがって、本発明の第1の実施形態によれば、しきい値電圧のばらつきに起因する半導体装置の動作を安定化できる。

【0037】

(2) 製造方法

図1、図4乃至図7を用いて、本発明の実施形態に係るMISトランジスタの製造方法について、説明する。尚、ここでは、MISトランジスタのチャネル長方向の断面構造のみを図示して、説明する。

【0038】

はじめに、図4に示すように、半導体基板1(例えば、シリコン基板)上に、ゲート絶縁膜2として、例えば、シリコン酸化膜が、熱酸化法によって形成される。尚、ゲート絶縁膜2はシリコン酸化膜に限定されるものではなく、例えば、シリコン酸化膜とシリコン窒化膜との積層膜や、Al2O3、HfO2、Ta2O5、La2O3、LaLiO3、ZrO2、Y2O3、ZrSiO4などの高誘電体絶縁膜でもよい。

【0039】

そして、ゲート絶縁膜2上に、複数の導電膜3A,3B,3Cと複数の絶縁膜5A,5B,5Cとが交互に堆積され、積層体6が形成される。複数の導電膜3A,3B,3Cは、例えば、ポリシリコン膜であり、10nm〜15nm程度の膜厚となるように、CVD(Chemical Vapor Deposition)法を用いて形成される。複数の絶縁膜5A,5B,5Cは、例えば、熱酸化法によって形成されたシリコン酸化膜である。このシリコン酸化膜は、例えば、1nm〜2nm程度の膜厚である。尚、複数の絶縁膜5A,5B,5Cは、ポリシリコン膜上に形成された自然酸化膜でも良い。また、積層体6を形成する場合には、導電膜が、ゲート絶縁膜2に直接接触するように形成されることが好ましい。

【0040】

続いて、図5に示すように、シリコン層8(例えば、ポリシリコン層)が、例えば、CVD法を用いて、積層体6上に形成される。

【0041】

次に、図6に示すように、シリコン層8が所定のゲートパターンとなるように、例えばフォトリソグラフィー技術によってパターニングが施された後、シリコン層8及び積層体6が、例えば、RIE(Reactive Ion Etching)法を用いて、ゲート加工される。そして、ゲート加工されたシリコン層8をマスクとして、半導体基板1内にソース/ドレイン拡散層7が、例えば、イオン注入法を用いて、形成される。その後、ソース/ドレイン拡散層7内に含まれるイオン不純物がアニールによって活性化され、半導体基板1内に固定化される。

【0042】

その後、層間絶縁膜50が、例えば、CVD法を用いて、ゲート加工されたシリコン層8及び積層体6を覆うように形成される。層間絶縁膜50は、例えば、CMP(Chemical Mechanical Polishing)法によって、層間絶縁膜50の上面が、シリコン層8の上面とほぼ一致するように平坦化処理され、シリコン層8の上面が露出する。

【0043】

続いて、図7に示すように、半導体基板上の全面に、例えば、ニッケル(Ni)等の金属膜9が、例えば、スパッタ法を用いて形成される。その結果、シリコン層8の上面に金属膜9が形成されることになる。尚、金属膜9はNiに限定されず、コバルト(Co)、チタン(Ti)、タングステン(W)及びモリブデン(Mo)でも良い。

【0044】

続いて、シリコン層8と金属膜9とに加熱処理を施して、固相反応によるシリサイド化(シリサイド処理)が実行される。これによって、図1に示すように、シリサイド層4Bが積層体6上に形成される。尚、シリコン層8と固相反応しなかった金属膜は、シリサイド処理の後、除去される。

【0045】

このシリサイド処理の際、Ni原子は、シリコン(Si)原子と固相反応(シリサイド反応)を生じつつ、シリコン層8内を移動する。シリサイド層4Bと積層体6との界面まで達したNi原子は、積層体6内に拡散する。

【0046】

積層体6内に含まれる絶縁膜5A,5B,5Cは、Ni原子の拡散を防止するストッパとして機能する。但し、絶縁膜5A,5B,5Cのそれぞれは、非常に薄い膜厚(1nm〜2nm)であるため、1つの絶縁膜(例えば、絶縁膜5C)のみで、すべてのNi原子の拡散を防止できない。そのため、積層体6に含まれる複数の導電膜のうち、シリサイド層4B側に形成された導電膜4Aは、上記のシリサイド処理の際に絶縁膜5Cを通過したNi原子と反応し、シリサイド膜4Aとなる。

【0047】

このように、絶縁膜5A,5B,5Cのそれぞれは膜厚が非常に薄いため、Ni原子の一部が絶縁膜を通過し、導電膜(ポリシリコン膜)とシリサイド反応する。しかし、Ni原子がシリサイド層4B側からゲート絶縁膜2側へと拡散するにつれ、Ni原子は複数の絶縁膜5A,5B,5Cによって徐々に捕獲され、それとともに、絶縁膜5A,5B,5Cを通過したNi原子は導電膜(ポリシリコン膜)と順次反応する。そのため、積層体6内をゲート絶縁膜2側へ移動するNi原子数は減少していく。それゆえ、ゲート絶縁膜2側に形成された導電膜3A内に到達するNi原子はほとんどなく、導電膜3Aの全体がシリサイド膜となることはない。

【0048】

それゆえ、積層体6に含まれる複数の導電膜のうち、ゲート絶縁膜2側に形成された導電膜3Aは、積層体6形成時の状態、すなわち、ポリシリコン膜3Aとなっている。

【0049】

また、上述のように、Ni原子がシリサイド層4B側からゲート絶縁膜2側へと拡散するにしたがって、拡散するNi原子数は徐々に減少していく。それゆえ、積層体6内の複数の導電膜3A,3B,4A毎に、Siに対するNiの組成比がそれぞれ異なっている。

つまり、複数の導電膜のうち、シリサイド層4B側の導電膜のSi原子に対するNi原子の組成比は、ゲート絶縁膜2側の導電膜のSi原子に対するNi原子の組成比よりも高くなっている。そのため、導電膜4A(シリサイド膜)と導電膜3A(ポリシリコン膜)との間にある導電膜3BのSi原子に対するNi原子の組成比は、導電膜4A内のNi原子の組成比よりも低く、導電膜3A内のNi原子の組成比よりも高くなっている。

【0050】

尚、図4乃至図7では、積層体6を構成する導電膜及び絶縁膜は、それぞれ3層ずつ形成されているが、それに限定されるものではなく、Ni原子(メタル原子)がゲート絶縁膜2直上の導電膜(ポリシリコン膜)3Aまで拡散しない積層数で、複数の導電膜と複数の絶縁膜とが積層されていれば良い。また、ゲート絶縁膜2上の導電膜3Aは、その全体がシリサイド膜とならなければよい。つまり、その導電膜3Aのうち、ゲート絶縁膜2と直接接触する部分がシリサイド膜とならなければよく、絶縁膜5Aと直接接触する部分はシリサイド膜となってもよい。

【0051】

このように、ゲート電極を形成するためにシリサイド処理を施しても、ゲート絶縁膜2直上にはポリシリコン膜3Aが残存する。そのため、半導体基板(シリコン基板)1とゲート電極10との仕事関数差は、シリコン基板1とポリシリコン膜3Aとによって決まり、シリサイド膜の不均一性に起因して、MISトランジスタのしきい値電圧の変動が生じることはない。それゆえ、ゲート絶縁膜2直上でのシリサイド層の不均一性に起因して、MISトランジスタのしきい値電圧が素子毎にばらつくのを防止できる。

【0052】

以上の製造工程によって、本発明の実施形態のMISトランジスタが形成される。

【0053】

上述のように、本実施形態では、MISトランジスタのゲート電極10が、複数の導電膜と複数の絶縁膜が交互に積層された積層体6と、シリサイド層4Bとから構成されている。積層体6が含んでいる複数の絶縁膜5A,5B,5Cによって、シリサイド層4Bを形成する際にゲート電極内を拡散するNi原子(金属原子)は、積層体6内での拡散が妨げられる。そのため、積層体6内のいずれかの絶縁膜又は導電膜で、Ni原子の拡散は停止し、ゲート電極10全体がシリサイド化されることがない。

【0054】

それゆえ、ゲート絶縁膜2直上でのシリサイド層の不均一性に起因して、MISトランジスタのしきい値電圧は変動しない。

【0055】

また、上記の製造方法によって形成されたMISトランジスタは、積層体6内に複数の絶縁膜5A,5B,5Cを含んでいるが、それらの絶縁膜の膜厚は非常薄い。そのため、形成されたMISトランジスタの駆動時に、ゲート電極10に印加した駆動電圧は少ない電位降下で、シリサイド層4Bとゲート絶縁膜2上に形成されたポリシリコン膜3Aとの間に加わる。それゆえ、ゲート絶縁膜2下の半導体基板1内にチャネル(反転層)が形成されるため、複数の絶縁膜を含む積層体6によって、MISトランジスタの動作に支障をきたすことはない。

【0056】

したがって、本発明の第1の実施形態に係るMISトランジスタの製造方法によれば、動作が安定したMISトランジスタ及びそれを用いた半導体集積回路を提供できる。

【0057】

[2] 第2の実施形態

以下、図8乃至図20を用いて、本発明の第2の実施形態について説明する。

【0058】

本発明の第1の実施形態では、1つのMISトランジスタの構造及びその製造方法について説明した。第1の実施形態で述べたMISトランジスタは、例えば、ロジック回路やメモリ回路の構成素子として、用いられる。

【0059】

本発明の第2の実施形態は、上記のMISトランジスタを、不揮発性半導体メモリ、例えば、フラッシュメモリの構成素子として用いた例について、説明する。

【0060】

図8は、フラッシュメモリの全体構成を示す概略図である。

【0061】

図8に示すように、フラッシュメモリは、主に、メモリセルアレイ領域100とその周囲の周辺回路領域200とから構成され、それらは同一のチップ(半導体基板)上に設けられている。

【0062】

メモリセルアレイ領域100内には、複数のメモリセル及び複数の選択トランジスタが、設けられている。メモリセルは記憶素子として機能し、選択トランジスタはデータの書き込み/読み出し選択されたメモリセルに対するスイッチ素子として機能する。

【0063】

周辺回路領域200内には、ワード線・選択ゲート線ドライバ210、センスアンプ回路220及び制御回路230が設けられる。これらの回路210,220,230は、複数のMISトランジスタ(以下、周辺トランジスタとも呼ぶ)によって構成されている。周辺トランジスタは、その回路及び素子の機能に応じて、低耐圧系MISトランジスタと高耐圧系MISトランジスタとに区分されている。図1乃至図3で述べたMISトランジスタは、低耐圧系及び高耐圧系MISトランジスタとして用いられる。

【0064】

(1) 構造

図9乃至図13を用いて、本発明の実施形態の実施例に係るフラッシュメモリの構造について、説明する。

【0065】

図9は、本発明の第2の実施形態に係るフラッシュメモリの平面構造を示している。

【0066】

図9に示すように、メモリセルアレイ領域100の表面領域は、複数のアクティブ領域AAと複数の素子分離領域STIとから構成されている。アクティブ領域AA及び素子分離領域STIはY方向に延在し、1つのアクティブ領域AAは2つの素子分離領域STIに挟み込まれている。

【0067】

複数のワード線WLはX方向に延在し、アクティブ領域AAと交差している。複数のメモリセルMCは、ワード線WLとアクティブ領域AAとの交差箇所にそれぞれ設けられている。選択ゲート線SGLもワード線WLと同様にX方向に延び、選択トランジスタSTは選択ゲート線SGLとアクティブ領域AAとの交差箇所にそれぞれ設けられている。

【0068】

アクティブ領域AA内には、メモリセルMC及び選択トランジスタSTのソース/ドレイン拡散層(図示せず)が設けられている。ソース/ドレイン拡散層は、Y方向に互いに隣接するメモリセルMC及び選択トランジスタSTによって共有され、これによって、複数のメモリセルMCと選択トランジスタSTはY方向に直列接続されている。また、Y方向に互いに隣接する2つの選択トランジスタSTのソース/ドレイン拡散層上には、コンタクト80Cが設けられ、1つのコンタクトプラグ80Cが2つの選択トランジスタSTで共有される。

【0069】

以下、本実施形態においては、メモリセルアレイ領域100のうち、メモリセルが配置(形成)される領域をメモリセル形成領域101と呼び、選択トランジスタが配置(形成)される領域を選択ゲート領域102と呼ぶ。

【0070】

周辺回路領域200内には、周辺トランジスタとして、複数の高耐圧系MISトランジスタHVTrと複数の低耐圧系MISトランジスタLVTrとが設けられている。本実施形態においては、説明の簡単化のため、高耐圧系MISトランジスタHVTrと低耐圧系MISトランジスタLVTrとをそれぞれ1つずつ図示している。以下では、本実施形態において、周辺回路領域200のうち、高耐圧系MISトランジスタが配置(形成)される領域を高耐圧領域201と呼び、低耐圧系MISトランジスタが配置(形成)される領域を低耐圧領域202と呼ぶ。

【0071】

高耐圧及び低耐圧領域201,202はそれぞれ素子分離領域STIに取り囲まれ、互いに電気的に分離されたアクティブ領域AAL,AAHがそれぞれ設けられる。

【0072】

周辺トランジスタHVTr,LVTrのゲート電極101,102はアクティブ領域AAH,AALをまたがるようにX方向に延び、素子分離領域STIH,STIL上まで引き出されている。その引き出された箇所において、コンタクト82A,82Bがゲート電極101,102上にそれぞれ設けられる。また、アクティブ領域AAH,AAL内には、ソース/ドレイン拡散層71,72が設けられている。また、コンタクト80A,80Bがソース/ドレイン拡散層71,72上に接続されている。

【0073】

図10は、図9中のA−A線、B−B線及びC−C線にそれぞれ沿う断面構造を図示している。

【0074】

図10に示すように、メモリセル形成領域101内に設けられたメモリセルMCは、例えば、MONOS(Metal-Oxide-Nitride-Oxide-Semiconductor)構造のMISトランジスタである。

【0075】

メモリセルMCのゲート構造は、半導体基板1表面上のゲート絶縁膜20A上に記憶層21Aが設けられ、この記憶層21Aとゲート電極4B3との間に中間絶縁膜22Aが設けられた構造となっている。そして、メモリセルMCは、ソース/ドレイン拡散層27Aを有し、この拡散層27AはY方向(チャネル長方向)に隣接するメモリセルMCで共有されている。

【0076】

ゲート絶縁膜(第1のゲート絶縁膜)20Aは、例えば、膜厚が4nm程度のシリコン酸化膜であり、記憶層21Aへの電荷注入の際にトンネル絶縁膜として機能する。また、ゲート絶縁膜21Aに、シリコン酸化膜/シリコン窒化膜/シリコン酸化膜の積層構造を有するONO膜や、ゲート絶縁膜20A中にゲルマニウム(Ge)等の注入アシスト準位を含む層をトンネル膜の両界面に位置させた膜を用いることにより、ゲート絶縁膜の信頼性を向上でき、さらには、書き込み/消去特性を向上できる。以下では、ゲート絶縁膜20Aのことを、トンネル絶縁膜20Aと呼ぶ。

【0077】

記憶層21Aは、メモリセルMCがMONOS構造のMISトランジスタである場合には、電荷捕獲機能を有する、すなわち、電荷捕獲準位を多く含む膜が用いられ、例えば、シリコン窒化膜などの絶縁膜である。記憶層21Aがシリコン窒化膜である場合、その膜厚は3nm〜10nm程度である。

【0078】

中間絶縁膜22Aは、ゲート電極4B3に電圧が印加された際に、記憶層21Aに捕獲された電荷がゲート電極4B3に放出されるのを阻止する。以下、このような機能を有する中間絶縁膜22Aのことを、ブロック絶縁膜22Aと呼ぶ。ブロック絶縁膜22Aは、例えば、Al2O3、HfO2、Ta2O5、La2O3、LaLiO3、ZrO2、Y2O3、ZrSiO4などの高誘電体膜である。さらには、これらの複合膜や、これらの膜とSiN膜又はSiO2膜との積層膜でも良い。ブロック絶縁膜22Aがアルミナ膜である場合、その膜厚は、例えば、10nm〜30nm程度である。

【0079】

また、図11、図12及び図13は、図7中のD−D線に沿う断面構造の一例を、それぞれ図示している。メモリセルMCは、図11乃至図13のうち、いずれか1つのX方向(チャネル幅方向)に沿う断面構造を有している。

【0080】

記憶層21Aは、例えば、図11、図12又は図13に示すように、X方向(チャネル幅方向)において、素子分離領域STI内に埋め込まれた素子分離絶縁膜51によって、電気的に分離されている。尚、記憶層21AのX方向の断面構造は、図11乃至図13に示す例に限定されるものではない。例えば、記憶層21Aが絶縁膜であれば、それをX方向に隣接するメモリセルMC間で分離する必要はなく、記憶層21Aがアクティブ領域AA上及び素子分離領域STI上をX方向に延在する構造であってもよい。

【0081】

ブロック絶縁膜22Aは、図11に示すように、記憶層21A上及び素子分離絶縁膜51上をX方向に延在していてもよい。また、図12に示すように、素子分離絶縁膜51の構造が、その上面が、記憶層21Aの上面より低く、且つ、記憶層21Aの下面より高い位置まで落とし込まれる構造である場合、ブロック絶縁膜22Aは、記憶層21AのX方向の側面を覆う構造となってもよい。或いは、図13に示すように、ブロック絶縁膜22Aは、素子分離絶縁膜51によって、X方向に隣接するメモリセルMC毎に分離されてもよい。

【0082】

ゲート電極(第1のゲート電極)4B3は、図11、図12又は図13に示すようにX方向に延在し、X方向に隣接する複数のメモリセルMCで共有され、ワード線WLとして機能する。ゲート電極4B3は、例えば、シリサイド層(第1のシリサイド層)の単層構造から構成され、FUSI構造を有している。シリサイド層4B3は、例えば、NiSi2層から構成されているが、これに限定されるものではなく、他のシリサイド材から構成されても良い。

【0083】

図10に示される選択ゲート形成領域102内に設けられる選択トランジスタSTは、例えば、次のような構成を有している。選択トランジスタSTのゲート構造は、半導体基板1表面上のゲート絶縁膜20Bと、ゲート絶縁膜20B上の中間絶縁膜22Bと、中間絶縁膜22B上のゲート電極4B4とから構成されている。また、選択トランジスタSTは、半導体基板1内に設けられたソース/ドレイン拡散層27B,27Cを有している。ソース/ドレイン拡散層27Bは、Y方向に隣接するメモリセルMCと共有され、それによって、選択トランジスタSTはメモリセルMCと直列接続される。ソース/ドレイン拡散層27Cは、層間絶縁膜50内に埋めこまれたコンタクト80Cと接続され、このコンタクト80Cを介して配線層81Cに接続される。

【0084】

選択ゲート形成領域102内の半導体基板1上に設けられた絶縁膜20Bの膜厚は、メモリセルMCのトンネル絶縁膜20Aの膜厚より厚く、例えば、7nm程度である。中間絶縁膜22Bはゲート絶縁膜20B上に設けられている。中間絶縁膜22Bは、メモリセルMCのブロック絶縁膜22Aと同時に形成されるため、ブロック絶縁膜22Aと同一構成であり、例えば、10nm〜30nm程度のアルミナ膜である。

【0085】

本実施形態では、絶縁膜20Bと中間絶縁膜22Bとが、選択トランジスタSTのゲート絶縁膜として機能する。従来では、ドレイン−ソース間耐圧及びゲート耐圧の確保のため、選択トランジスタSTのゲート長は、メモリセルMCのゲート長よりも大きくされている。しかし、本実施形態では、ゲート絶縁膜を十分厚くできるため、ドレイン−ソース間耐圧及びゲート耐圧が十分確保され、選択トランジスタSTのゲート長を小さくできる。

【0086】

選択トランジスタSTのゲート電極4B4はX方向に延在している。ゲート電極4B4は、X方向に隣接する複数の選択トランジスタSTで共有され、選択ゲート線SGLとして機能する。選択ゲート線SGLとしてのゲート電極4B4は、ゲート電極4B3と同時に形成されるため、ワード線WLと同一の構成となっている。

【0087】

また、本実施形態において、選択トランジスタSTは、絶縁膜からなる記憶層21Aが設けられず、ブロック絶縁膜22Aと同一構成の中間絶縁膜22Bが、ゲート絶縁膜20Bとゲート電極4B4との間に介在するのみである。それゆえ、本実施形態の選択トランジスタSTでは、そのゲート電極4B4に電圧を印加しても、記憶層21Aに電荷が注入されることはなく、記憶層の電荷捕獲に起因する選択トランジスタSTのしきい値電圧の変動は生じない。但し、選択トランジスタSTの閾値電圧の変動特性が設計上許容される範囲内であれば、ゲート絶縁膜20Bとブロック絶縁膜22Aとの間に、記憶層と同一構成の膜があってもよい。

【0088】

図10に示される高耐圧系/低耐圧系MISトランジスタHVTr,LVTrは、ほぼ同一の構造を有している。高耐圧/低耐圧MISトランジスタHVTr,LVTrは、半導体基板1内の2つのソース/ドレイン拡散層71,72と、2つのソース/ドレイン拡散層71,72間の半導体基板1表面に設けられたゲート絶縁膜21,22と、ゲート絶縁膜21上のゲート電極101,102とを、それぞれ有している。ソース/ドレイン拡散層71,72は、層間絶縁膜50内のコンタクト80A,80Bを介して、配線層81A,81Bに接続されている。

【0089】

高耐圧領域201内に設けられる高耐圧系MISトランジスタHVTrは、例えば、書き込み電圧などの高電圧の転送を担う。そのため、そのゲート絶縁膜21の膜厚は、低耐圧系MISトランジスタLVTrのゲート絶縁膜22の膜厚よりもさらに厚くされ、それによって、高耐圧系MISトランジスタHVTrのゲート耐圧が確保されている。例えば、ゲート絶縁膜21の膜厚は、30nm以上、50nm以下程度である。

【0090】

低耐圧領域202内に設けられる低耐圧系MISトランジスタLVTrは、例えば、ロジック回路のスイッチ素子として機能する。低耐圧系MISトランジスタLVTrのゲート絶縁膜22の膜厚は、例えば、6nm〜9nm程度である。また、高耐圧系及び低耐圧系MISトランジスタHVTr,LVTrのゲート長は、ドレイン−ソース間耐圧の確保のため、選択トランジスタSTやメモリセルMCのゲート長よりも大きくされている。

【0091】

高耐圧系及び低耐圧系MISトランジスタHVTr,LVTrのゲート電極101,102は、ゲート絶縁膜21,22上の積層体61,62と、積層体61,62上のシリサイド層4B1,4B2とからそれぞれ構成されている。尚、図10において、積層体61は、2つの絶縁膜5A1,5B1と2つの導電膜3A1,4A1とから構成されているが、この積層数に限定されるものではない。積層体62についても同様である。また、積層体61と積層体62の積層数は、製造工程の簡略化の観点から同じであることが好ましい。

【0092】

積層体61,62内に含まれる複数の導電膜のうち、ゲート絶縁膜2直上の導電膜3A1,3A2は、例えば、ポリシリコン膜である。また、シリサイド層4B1,4B2側の導電膜4A1,4A2は、例えば、シリサイド膜である。

【0093】

積層体61,62内の絶縁膜5A1,5B1,5A2,5B2は、例えば、1nm〜2nm程度の膜厚を有し、シリサイド処理時に金属原子(Ni原子)が積層体61,62内全体に拡散するのを抑制する。

【0094】

このように、周辺回路領域200内に設けられた周辺トランジスタHVTr,LVTrは、第1の実施形態で述べたMISトランジスタと同様に、シリサイド層(第2のシリサイド層)4B1,4B2とゲート絶縁膜21,22との間に、複数の導電膜と複数の絶縁膜が交互に積層された積層体61,62を有している。

【0095】

フラッシュメモリにおいては、製造工程の簡略化のため、メモリセルアレイ領域100と周辺回路領域200とで、製造工程の共通化がなされている。そのため、ワード線WLの低抵抗化のためのメモリセルMCのゲート電極4B3のシリサイド処理の際に、高耐圧系及び低耐圧系MISトランジスタHVTr,LVTrのゲート電極もシリサイド処理が施される。

【0096】

しかし、本実施形態では、シリサイド処理を実行しても、メモリセルMCのゲート電極4B3はFUSI構造となるが、高耐圧系MISトランジスタHVTr,LVTrなどのMISトランジスタは、積層体61,62内に含まれる複数の導電膜のうち、ゲート絶縁膜21,22直上の導電膜3A1,3A2はシリサイド化されず、例えば、ポリシリコン膜となる。そのため、ゲート電極101,102と半導体基板1との仕事関数差は、ポリシリコン膜とシリコン基板とによって決まり、その仕事関数差によって、周辺トランジスタHVTr,LVTrのしきい値電圧が定義される。

【0097】

それゆえ、第1の実施形態と同様に、周辺トランジスタ(MISトランジスタ)HVTr,LVTrは、ゲート電極101,102が含むシリサイド層の不均一性に起因して、素子毎にしきい値電圧がばらつくのを抑制できる。

【0098】

尚、第1の実施形態と同様に、積層体61,62内に含まれる絶縁膜は非常に薄い。そのため、ゲート電極101,102に印加された駆動電圧は少ない電位降下で、シリサイド層4B1,4B2とゲート絶縁膜上に形成されたポリシリコン膜3A1,3A2との間に加わる。それゆえ、ゲート絶縁膜21,22直下の半導体基板1内に、チャネル(反転層)が形成されるため、複数の絶縁膜を含む積層体6をゲート絶縁膜21,22上に設けても、周辺トランジスタHVTr,LVTrを正常に駆動させることができる。

【0099】

したがって、本発明の第2の実施形態によれば、フラッシュメモリの動作を安定化できる。

【0100】

(2) 製造方法

(2−1) 製造方法1

図10、図14乃至図19を用いて、本発明の第2の実施形態に係るフラッシュメモリの製造方法について説明する。尚、以下では、主に、メモリセルアレイ領域100及び周辺回路領域200のY方向に沿う断面構造を用いて、各製造工程について説明し、必要に応じて、X方向に沿う断面の製造工程について説明する。

【0101】

はじめに、図14に示すように、周辺回路領域200において、高耐圧領域201内において、例えば、RIE(Reactive Ion Etching)法によって、半導体基板1がエッチングされ、凹部が半導体基板1内に形成される。即ち、高耐圧領域201の半導体基板1表面が、メモリセルアレイ領域100及び低耐圧領域202の半導体基板1表面よりも低くなる。

【0102】

そして、半導体基板1表面に犠牲酸化膜(図示せず)が形成された後、メモリセルアレイ領域100内及び周辺回路領域200内の高耐圧/低耐圧領域201,202に対し、例えば、それぞれ異なるドーズ量のイオン注入が実行され、各素子形成領域に対応した不純物濃度のウェル領域(図示せず)がそれぞれ形成される。

【0103】

犠牲酸化膜が剥離された後、半導体基板1に対して、例えば、熱酸化処理が施され、半導体基板1表面に30〜50nm程度の絶縁膜(例えば、シリコン酸化膜)が形成される。このシリコン酸化膜は、例えば、フォトリソグラフィー技術及びRIE法によって、メモリセルアレイ領域100内及び低耐圧領域202内では除去され、高耐圧領域201内の凹部内(半導体基板1表面)にのみ残存される。高耐圧領域201内に残存したシリコン酸化膜21は、高耐圧系MISトランジスタのゲート絶縁膜となる。

【0104】

続いて、半導体基板1表面に対し、例えば、熱酸化処理が再び実行され、メモリセルアレイ領域100内及び低耐圧領域202内の半導体基板1表面にシリコン酸化膜22が形成される。シリコン酸化膜22は、低耐圧系MISトランジスタのゲート絶縁膜となり、その膜厚は、6nm程度である。尚、各領域間の段差を緩和するため、シリコン酸化膜21の上端とシリコン酸化膜22の上端とがほぼ一致するように、高耐圧領域201内に凹部が形成されることが好ましい。

【0105】

そして、複数の導電膜3A1〜3A3,3B1〜3B3,3C1〜3C3と複数の絶縁膜5A1〜5A3,5B1〜5B3,5C1〜5C3が、メモリセルアレイ領域100及び周辺回路領域200内のシリコン酸化膜21,22上に交互に積層され、積層体61〜63が各領域100,200内に形成される。導電膜3A1〜3A3,3B1〜3B3,3C1〜3C3はポリシリコン膜であり、例えば、CVD法を用いて、10nm〜15nm程度の膜厚となるように形成される。また、絶縁膜5A1〜5A3,5B1〜5B3,5C1〜5C3は、例えば、熱酸化法によって、1nm〜2nm程度の膜厚となるように、形成される。尚、絶縁膜5A1〜5A3,5B1〜5B3,5C1〜5C3は、ポリシリコン膜上に形成された自然酸化膜でも良い。

【0106】

この後、例えば、メモリセルアレイ領域100及び周辺回路領域200に対して、フォトリソグラフィー技術によってパターニングが施され、メモリセルアレイ領域100内に形成された積層体63及び絶縁膜22が、例えば、RIE法によって、除去される。

そして、図15に示すように、メモリセルアレイ領域100内の半導体基板1表面に、ゲート絶縁膜20が、例えば、熱酸化法によって、形成される。このゲート絶縁膜20は、例えば、膜厚が4nm程度のシリコン酸化膜であり、メモリセルのトンネル絶縁膜となる。ゲート絶縁膜20は、ONO膜や、ゲルマニウム(Ge)等の注入アシスト準位を含む層をトンネル膜の両界面に位置させた絶縁膜を用いてもよい。

【0107】

そのゲート絶縁膜20上に、記憶層21Aが、例えば、CVD法により、4nm〜6nm程度の膜厚となるように形成される。記憶層21Aには、例えば、電荷捕獲準位を多く含むシリコン窒化膜が用いられる。そして、記憶層21Aは、フォトリソグラフィー技術及びRIE法を用いて、メモリセル形成領域101内にのみ残存するように、エッチングされ、選択ゲート形成領域102の記憶層は除去される。

【0108】

ここで、図9に示されるメモリセルのD−D線に沿う断面構造が図11に示す構造となる場合には、記憶層21Aの形成後に、フォトリソグラフィー技術及びRIE法により、半導体基板1内に溝が形成される。その溝内に素子分離絶縁膜51が埋め込まれ、アクティブ領域と素子分離領域とが形成される。この素子分離絶縁膜51によって、X方向に隣接するアクティブ領域AAが電気的に分離される。

【0109】

尚、レジストマスクではなくハードマスクを用いて、半導体基板1内に溝を形成しても良い。この場合、記憶層21Aとのエッチングの選択比を確保するため、記憶層21Aとは材質の異なる第1ハードマスク(図示せず)が記憶層21A上に成膜され、この第1ハードマスク上に、さらに、第1ハードマスクの材質と異なる第2ハードマスクが形成される。第1ハードマスクは、例えば、シリコン酸化膜などであり、第2ハードマスクは、アモルファスシリコン、或いは、シリコン窒化膜などである。

形成された溝内に素子分離絶縁膜51が埋め込まれ、ハードマスクをストッパとして、CMP法による平坦化処理を素子分離絶縁膜51に対して行う。その後、素子分離絶縁膜51の上面の高さが記憶層21Aの上面の高さと一致するように、素子分離絶縁膜51に対して、エッチバックを施す。そして、記憶層21A上に残存したハードマスクが剥離される。以上によっても、素子分離絶縁膜51によるX方向に隣接するアクティブ領域AA間の電気的な分離がなされる。

【0110】

また、図9に示されるメモリセルのD−D線に沿う断面構造が図12に示す構造となる場合には、素子分離絶縁膜51の形成後に、メモリセル形成領域101内の素子分離絶縁膜51の上面が、記憶層21Aの上面より低く、且つ、記憶層21Aの下面より高くなるように、例えば、RIE法を用いて、素子分離絶縁膜51がエッチングされる。

【0111】

続いて、中間絶縁膜22及び第1シリコン層(例えば、ポリシリコン層)23が、例えば、CVD法を用いて、メモリセルアレイ領域100内に順次形成される。

【0112】

メモリセル形成領域101内においては、記憶層21A上に、中間絶縁膜22が形成される。中間絶縁膜22は、例えば、膜厚が10nm〜30nm程度のアルミナ(Al2O3)膜である。この中間絶縁膜22は、メモリセルのブロック絶縁膜として機能する。尚、中間絶縁膜22は、アルミナ膜に限定されるものではなく、HfO2など他の高誘電体絶縁材料や、シリコン窒化膜、シリコン酸化膜などの絶縁膜の単層膜や、ONO膜など絶縁膜の積層膜でもよい。一方、セレクトゲート形成領域102においては、上記のように、記憶層が除去されているため、中間絶縁膜22がゲート絶縁膜20と直接接触した構造となっている。

この際、周辺回路領域200においては、積層体61,62上に、記憶層21Aと同一構成の絶縁膜21、中間絶縁膜22及び第1シリコン層23が形成される。

尚、選択ゲート形成領域102内の記憶層の除去の際に、その領域102内の絶縁膜20を同時に除去し、その絶縁膜20よりも膜厚が厚い絶縁膜を新たに形成しても良い。また、本実施形態では、選択ゲート形成領域102内の記憶層は除去したが、それに限定されるものではなく、選択ゲート形成領域102内に記憶層を残存させても良い。

【0113】

次に、図16に示すように、高耐圧/低耐圧領域201,202において、第1シリコン層23、中間絶縁膜22及び記憶層21が、例えば、フォトリソグラフィー技術及びRIE法を用いて、積層体61,62上から除去される。この際、例えば、積層体61,62の最上端に形成された酸化膜(自然酸化膜)は非常に薄いため除去され、これとともに、その酸化膜の直下に設けられた導電膜(ポリシリコン膜)3C1,3C2もエッチングされ、薄くなる。この膜厚の減少分を考慮するとともに、積層体61,62の上端とメモリセル形成領域101内の第1シリコン層23の上端とがほぼ一致する高さとなるように、積層体61,62が形成されることが好ましい。これは、メモリセルアレイ領域100上端と周辺回路領域200上端との段差に起因して、製造工程における加工難度が高くなってしまうのを、抑制するためである。

【0114】

次に、第1シリコン層23及び積層体61,62上に、第2シリコン層25が形成される。尚、第1シリコン層23は形成せずとも良い。即ち、中間絶縁膜22が形成された後、積層体61,62上の中間絶縁膜22のみを除去し、その後、メモリセルアレイ領域100内及び周辺回路領域200内に、第2シリコン層25を形成してもよい。その結果、第1シリコン層23の形成工程を省略することも可能となる。

【0115】

続いて、図17に示すように、例えば、シリコン窒化膜からなるマスク層26をハードマスクとして、メモリセルMC、選択トランジスタST、高耐圧系/低耐圧系MISトランジスタHVTr,LVTrがそれぞれ所定のパターンのゲートサイズとなるように、フォトリソグラフィー技術及びRIE法を用いて、メモリセルアレイ領域100内及び周辺回路領域200内にそれぞれ形成された導電膜及び絶縁膜が、ゲート加工される。

【0116】

そして、ゲート加工された第1、第2シリコン層23,25及び積層体61,62をマスクとして、ソース/ドレイン拡散層27A,27B,27C,71,72が、半導体基板1内に形成される。この後、ソース/ドレイン拡散層27A,27B,27C,71,72内に含まれる不純物イオンが、アニールによって活性化され、半導体基板1内に固定化される。

【0117】

ソース/ドレイン拡散層を形成した後、層間絶縁膜50が、メモリセルMC、各トランジスタST,HVTr,LVTrのゲートを覆うように、例えば、CVD法によって形成される。

【0118】

次に、マスク層26をストッパとして、CMP法による平坦化処理が施される。ここで、メモリセル形成領域101上端と選択ゲート形成領域102上端との間に段差が生じているが、この段差は、記憶層21Aの膜厚分(4nm〜6nm程度)である。そのため、選択ゲート形成領域102のマスク層の上部が削られ、メモリセル形成領域101上端と選択ゲート形成領域102上端はほぼ同じ高さになり、メモリセルアレイ領域100の上端は平坦になる。

【0119】

続いて、マスク層26を剥離し、図18に示すように、第2シリコン層25の上面が露出される。そして、第2シリコン層25上に、金属膜、例えば、Ni膜(金属膜)45がスパッタ法を用いて形成される。これと同時に、周辺回路200においては、第2シリコン層25上に、Ni膜45が形成される。

【0120】

そして、加熱によるシリサイド処理が実行される。これによって、メモリセルアレイ領域100では、Ni膜24に含まれるNi原子が第1及び第2シリコン層23,25内に拡散し、周辺回路領域200では、高耐圧/低耐圧領域201,202内のそれぞれに形成された第2シリコン層25及び積層体61,62内に、Ni原子が拡散する。尚、第2シリコン層25上に形成される金属膜は、Ni膜に限定されず、加熱処理によって、ポリシリコンとの間にシリサイドを形成する金属材料であれば、CoやTiなど、他の材料でも良い。尚、シリコン層及び導電膜と固相反応しなかった金属膜は、シリサイド処理の後、除去される。

【0121】

上記の加熱処理によって、図19に示すように、中間絶縁膜22上のポリシリコン層全体がシリサイド化され、メモリセルアレイ領域100内では、シリサイド(NiSi2)層4B3が形成される。これによって、メモリセルのゲート電極は、低抵抗化のため、FUSI構造のゲート電極とすることができる。同様に、選択トランジスタのゲート電極もシリサイド層4B4となる。

【0122】

一方、周辺回路領域200内では、積層体61,62のうち、Ni膜と直接接触した導電膜(ポリシリコン膜)がシリサイド化され、シリサイド膜4B1,4B2となる。また、絶縁膜5A1,5A2,5B1,5B2が1nm〜2nm程度と薄いため、Ni原子は、絶縁膜5A1,5A2,5B1,5B2を通過して、積層体61,62内を拡散する。

【0123】

Ni原子が積層体61,62内を拡散する際、第1の実施形態と同様に、Ni原子に対して絶縁膜5A1,5A2,5B1,5B2がストッパとして機能するため、Ni原子がシリサイド層4B1,4B2側からゲート絶縁膜21,22側へ移動するにつれて、拡散するNi原子数は徐々に減少する。そのため、積層体61,62内に含まれている複数の導電膜(ポリシリコン膜)毎に、Si原子に対するNi原子の組成比が異なってシリサイド化されていき、積層体61,62内に含まれている複数の導電膜の全てがシリサイド膜とはならない。それゆえ、ゲート絶縁膜21,22直上の導電膜3A1,3A2は、ポリシリコン膜とすることができる。尚、ゲート絶縁膜21,22直上の導電膜3A1,3A2がシリサイド化しないように、導電膜及び絶縁膜の積層数を考慮して積層体61及び62を形成することが好ましい。

【0124】

これによって、メモリセル形成領域101内には、シリサイド層(ゲート電極)4B3、ブロック絶縁膜(中間絶縁膜)22A及び記憶層21Aが、トンネル絶縁膜20A上に形成される。また、選択ゲート形成領域102内には、所定のゲートサイズとなる、シリサイド層(ゲート電極)4B4及びブロック絶縁膜と同一構成の中間絶縁膜22Bとが、トンネル絶縁膜20Aと同一構成の絶縁膜20B上に形成される。本実施形態においては、選択トランジスタSTにおいて、中間絶縁膜22Bと絶縁膜20Bとがゲート絶縁膜として機能する。

【0125】

高耐圧及び低耐圧領域201,202内には、シリサイド層4B1,4B2及び積層体61,62が、ゲート絶縁膜21,22上に形成される。尚、上述のように、積層体61,62内に含まれる複数の導電膜のうち、ゲート絶縁膜21,22直上の導電膜3A1,3A2はポリシリコン膜となっている。

【0126】

続いて、図10に示すように、絶縁層50上に、絶縁層55が形成される。そして、メモリセルアレイ領域100において、ソース/ドレイン拡散層27Cと接触するように、コンタクト80Cが絶縁層50,55内に埋め込まれる。そして、コンタクト80Cと電気的に接続されるように、配線層81Cが絶縁層50,55上に形成される。これと同時に、周辺回路200内の高耐圧領域201及び低耐圧領域202において、コンタクト80A,80Bが、ソース/ドレイン拡散層71,72にそれぞれ直接接触するように、絶縁層50内に埋め込まれる。さらに、配線層81A,81Bが、コンタクト80A,80Bに電気的に接続されるように、絶縁層50,55上に形成される。

【0127】

以上の製造工程によって、本発明の第2の実施形態に係るフラッシュメモリが完成する。

【0128】

本発明の第2の実施形態では、MISトランジスタ(周辺トランジスタ)が設けられる領域200内において、ゲート絶縁膜21,22上に、複数の導電膜と複数の絶縁膜とが交互に積層された積層体61,62が形成される。この積層体61,62上のシリコン層と金属膜(Ni膜)がシリサイド処理される。

【0129】

シリコン層とNi膜との固相反応によってシリサイド層が形成される際に、Ni原子はシリコン層内を拡散するとともに、積層体61,62内へも拡散する。Ni原子は積層体61,62内が含んでいる複数の絶縁膜によって拡散が妨げられる。

【0130】

これによって、シリサイド層4B1,4B2と積層体61,62とからなるMISトランジスタのゲート電極101,102は、積層体61,62内に含まれる複数の導電膜のうち、ゲート絶縁膜21,22直上の導電膜がシリサイド化するのを防止できる。そのため、MISトランジスタは、ゲート絶縁膜2直上のシリサイド層の不均一性に起因して、しきい値電圧が変動しない。

【0131】

それゆえ、MISトランジスタのしきい値電圧は、素子毎にばらつかない。

【0132】

積層体61,62は、複数の絶縁膜5A1,5B1,5A2,5B2も含んでいるが、これらの膜は非常に薄い。そのため、周辺トランジスタのゲート電極101,102に印加された駆動電圧は少ない電位降下で、シリサイド層4B1,4B2とゲート絶縁膜21,22上面に形成されたポリシリコン膜3A1,3A2との間に加わる。それゆえ、ゲート絶縁膜21,22直下の半導体基板1内にチャネル(反転層)が形成されるため、複数の絶縁膜を含む積層体をゲート絶縁膜21,22上に設けても、周辺トランジスタHVTr,LVTrの動作に支障をきたすことはない。

【0133】

また、本実施形態では、周辺トランジスタHVLr,LVTrのゲート電極101,102に積層体61,62を設けることにより、記憶層及びブロック絶縁膜の有無に起因するメモリセルアレイ領域100上端と周辺回路領域200上端との間の段差を緩和できる。それゆえ、その段差に起因して、製造工程の加工難度が高くなるのを抑制できる。

【0134】

したがって、本発明の第2の実施形態に係るフラッシュメモリの製造方法によれば、動作の安定化を図ったフラッシュメモリを提供できる。

【0135】

(2−2) 製造方法2

本発明の第2の実施形態において、メモリセルのD−D線に沿う断面構造が、図13に示す構造の場合の製造方法について、説明する。ここで、製造方法2と上記の製造方法1と異なる点は、素子分離絶縁膜51の形成方法である。

【0136】

尚、図15までの各工程は、製造方法1と同じであるため、説明を省略する。

【0137】

図15に示す工程で、例えば、選択ゲート形成領域102内の記憶層を除去した後、中間絶縁膜22及び第1シリコン層23が、メモリセルアレイ領域100内及び周辺回路領域内100内に形成される。この後、高耐圧/低耐圧領域201,202において、第1シリコン層23、中間絶縁膜22及び記憶層21が、例えば、フォトリソグラフィー技術及びRIE法を用いて、選択的に除去される。

【0138】

その後、レジストマスクを用いたフォトリソグラフィー技術及びRIE法により、半導体基板1内に溝が形成される。尚、ハードマスクを用いて、半導体基板1内に溝を形成してもよい。形成されたハードマスクが記憶層と同じ材料であれば、積層体61,62上に残存させた記憶層とを同時に除去することが可能となる。さらに、周辺回路領域100内の積層体63,63上の記憶層21は除去せずに、記憶層21をハードマスクとして用いても良いし、記憶層21上に同じ材質の材料を積層し、膜厚を厚くして、ハードマスクとして用いても良い。

【0139】

そして、溝内に素子分離絶縁層51が埋め込まれ、アクティブ領域と素子分離領域とが、メモリセルアレイ領域100内及び周辺回路領域200内の半導体基板1内に形成される。この素子分離絶縁層51によって、X方向に隣接するメモリセルアレイ領域100内のアクティブ領域AAが電気的に分離される。その後の工程は、図16乃至図19に示す工程と同様である。

【0140】

以上の工程によって、メモリセルのD−D線に沿う断面構造が、図13に示す構造となるように、メモリセルを形成することができる。

【0141】

(3) 変形例

図20を用いて、本発明の第2の実施形態に係るフラッシュメモリの変形例について、説明する。尚、図10乃至図13に示す部材と同一部材に関しては、同一符号を付し、詳細な説明は必要に応じて行う。

【0142】

図10乃至図13においては、MONOS構造のメモリセルを用いたフラッシュメモリについて、説明した。しかし、それに限定されず、絶縁層の代わりに導電層(例えば、ポリシリコン)を記憶層とした、いわゆる、積層ゲート構造のメモリセルを用いたフラッシュメモリでもよい。本変形例では、記憶層のことを、フローティングゲート電極30Aと呼ぶ。

【0143】

図20は、本変形例に係るフラッシュメモリのY方向(チャネル長方向)に沿う断面構造を示している。

【0144】

図20に示すように、メモリセルアレイ領域100内において、メモリセルMCは、フローティングゲート電極30Aとコントロールゲート電極4B3が積層されたスタックゲート構造となっている。具体的には、メモリセルMCは、以下の構成のゲート構造を有している。フローティングゲート電極30Aは、ゲート絶縁膜(トンネル絶縁膜)20A上に、設けられている。フローティングゲート電極30Aは、例えば、ポリシリコン膜からなっている。このフローティングゲート電極30Aに電荷が蓄積されることによって、メモリセルMCにデータが保持される。

【0145】

フローティングゲート電極30A上には、中間絶縁膜31Aが設けられている。中間絶縁膜31上には、コントロールゲート電極4B3設けられている。コントロールゲート電極4B3は、ワード線として機能し、シリサイド層(例えば、NiSi2層)の単層構造である。

【0146】

メモリセルがフローティングゲート電極30Aを有する場合、選択トランジスタSTのゲート構造は、ゲート絶縁膜2B上の下層ゲート電極30B上に、上層ゲート電極4B4が積層された構造となる。下層ゲート電極30Bと上層ゲート電極4B4との間には、中間絶縁膜31Aと同一構成の絶縁膜31Bが介在している。この絶縁膜31B内には、開口部が形成されており、この開口部を介して、下層ゲート電極30Bと上層ゲート電極4B4は直接接触する。

【0147】

下層ゲート電極30Bはフローティングゲート電極30Aと同時に形成され、上層ゲート電極4B4はコントロールゲート電極4B3と同時に形成される。そのため、上層ゲート電極4B4はシリサイド層となる。尚、本変形例の選択トランジスタにおいては、シリサイド層4B3,4B4の形成の際に、中間絶縁膜31Bに形成された開口部を介して、Ni原子(金属原子)が下層ゲート電極30B内にも拡散するが、中間絶縁膜31Bが介在している部分もあるため、下層ゲート電極30Bの全体がシリサイド層となることはない。

【0148】

また、本変形例においても、周辺回路領域200内に設けられる高耐圧系MISトランジスタHVTrのゲート電極101は、複数の導電膜3A1,4A1と複数の絶縁膜5A1,5B1が交互に積層された積層体61と、積層体61上に設けられたシリサイド層4B1とから構成されている。低耐圧系MISトランジスタLVTrのゲート電極102も同様に積層体61とシリサイド層4B2とから構成されている。

【0149】

それらの積層体61,62おいて、ゲート絶縁膜21,22直上の導電膜3A1,3A2は、シリサイド層4B1,4B2とは異なった導電材(例えば、ポリシリコン)からなっている。

【0150】

それゆえ、図9乃至図13に示すフラッシュメモリ内に設けられた周辺トランジスタと同様の効果が得られ、シリサイド層4B1,4B2の不均一性に起因するMISトランジスタのしきい値電圧のばらつきが生じることはない。

【0151】

したがって、本発明の第2の実施形態の変形例においても、MISトランジスタ(周辺トランジスタ)の動作を安定化できる。

【0152】

尚、図20に示す本変形例のフラッシュメモリの製造方法は、図14乃至図20を用いて説明した製造工程とほぼ同一である。相違点は以下の通りである。

【0153】

周辺領域200内のゲート絶縁膜21,22上に、複数の導電層と複数の絶縁膜からなる積層体が形成された後(図14参照)、メモリセルアレイ領域100内に形成された積層体及び絶縁膜は除去される。図15に示す工程と同様に、メモリセルアレイ領域100内の半導体基板1表面上に、ゲート絶縁膜20A,20Bが形成される。

この後、記憶層としての絶縁膜の代わりに、フローティングゲート電極30Aとなる、例えば、ポリシリコン膜30Aが、ゲート絶縁膜20A,20B上に形成される。そして、ポリシリコン膜30A上に、中間絶縁膜31A,31Bが形成される。この際、選択ゲート形成領域102内において、中間絶縁膜31Bに開口部が形成される。

【0154】

そして、図16乃至図19に示す工程と同様の工程によって、中間絶縁膜上に、第1シリコン層が形成される。そして、ゲート加工工程及びソース/ドレイン拡散層形成工程が実行され、絶縁層50が形成される。

【0155】

例えば、第2シリコン層が形成された後、金属膜が形成され、シリサイド処理(固相反応処理)が施される。シリサイド処理によって、シリサイド層4B1,4B2,4B3,4B4が形成された後、絶縁層55、コンタクト80A,80B,80C及び配線層81A,81B,81Cが形成され、本変形例のフラッシュメモリが完成する。

【0156】

フローティングゲート電極を有するメモリセルを用いた場合であっても、本変形例のフラッシュメモリは、メモリセルのゲート電極(制御ゲート電極)がFUSI構造となり、周辺トランジスタHVTr,LVTrのゲート電極101,102がゲート絶縁膜21,22直上でシリサイド膜を含まない導電膜(ポリシリコン膜)となっている。

【0157】

以上の製造工程によって、本発明の第2の実施形態の変形例に係るフラッシュメモリを作製できる。

【0158】

したがって、本発明の第2の実施形態の変形例においても、動作を安定化できるフラッシュメモリを提供できる。

【0159】

2. その他

本発明の第1及び第2の実施形態によれば、MISトランジスタの動作を安定化できる。

【0160】

尚、本発明の第2の実施形態において、フラッシュメモリを例に説明したが、例えば、MRAM(Magnetoresistive Random Access Memory)、PRAM(Phase change Random Access Memory)またはReRAM(Resistance Random Access Memory)などに用いられる周辺トランジスタ(MISトランジスタ)でもよい。その場合においても、本発明の実施形態と同様の効果が得られる。

【0161】

本発明の例は、上述の実施形態に限定されるものではなく、その要旨を逸脱しない範囲で、各構成要素を変形して具体化できる。また、上述の実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を構成できる。例えば、上述の実施形態に開示される全構成要素から幾つかの構成要素を削除してもよいし、異なる実施形態の構成要素を適宜組み合わせてもよい。

【図面の簡単な説明】

【0162】

【図1】本発明の実施形態に係るMISトランジスタの構造を示す断面図。

【図2】本発明の実施形態に係るMISトランジスタの構造を示す断面図。

【図3】本発明の実施形態に係るMISトランジスタの構造を示す断面図。

【図4】本発明の実施形態に係るMISトランジスタの製造方法の一工程を示す工程図。

【図5】本発明の実施形態に係るMISトランジスタの製造工程の一工程を示す工程図。

【図6】本発明の実施形態に係るMISトランジスタの製造工程の一工程を示す工程図。

【図7】本発明の実施形態に係るMISトランジスタの製造工程の一工程を示す工程図。

【図8】本発明の第2の実施形態に係る不揮発性半導体メモリの全体構成を示す概略図。

【図9】本発明の第2の実施形態に係るフラッシュメモリの構造を示す平面図。

【図10】本発明の第2の実施形態に係るフラッシュメモリの構造を示す断面図。

【図11】本発明の第2の実施形態に係るフラッシュメモリの構造を示す断面図。

【図12】本発明の第2の実施形態に係るフラッシュメモリの構造を示す断面図。

【図13】本発明の第2の実施形態に係るフラッシュメモリの構造を示す断面図。

【図14】本発明の第2の実施形態に係るフラッシュメモリの製造工程の一工程を示す断面図。

【図15】本発明の第2の実施形態に係るフラッシュメモリの製造工程の一工程を示す断面図。

【図16】本発明の第2の実施形態に係るフラッシュメモリの製造工程の一工程を示す断面図。

【図17】本発明の第2の実施形態に係るフラッシュメモリの製造工程の一工程を示す断面図。

【図18】本発明の第2の実施形態に係るフラッシュメモリの製造工程の一工程を示す断面図。

【図19】本発明の第2の実施形態の変形例に係るフラッシュメモリの構造を示す断面図。

【図20】本発明の第2の実施形態の変形例に係るフラッシュメモリの構造を示す断面図。

【符号の説明】

【0163】

1:半導体基板、2,21,22:ゲート絶縁膜、4B,4B1〜4B4:シリサイド層、6,61,62:積層体、3A,3A1,3A2,3B,3C:導電膜,4A,4A1,4A2:導電膜、5A,5A1,5A2,5B,5B1,5B2,5C:絶縁膜、7,71,72,27A,27B,27C:ソース/ドレイン拡散層、10,101,102,30B:ゲート電極、30A:フローティングゲート電極、50,55:絶縁層(層間絶縁膜)、51:素子分離絶縁膜、80A,80B,80C:コンタクト、81A,81B,81C:配線層、100:メモリセルアレイ領域、101:メモリセル形成領域、102:選択ゲート形成領域、200:周辺回路領域、201:高耐圧領域、202:低耐圧領域。

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板内に設けられ、ソース/ドレイン領域として機能する2つの拡散層と、

前記2つの拡散層間のチャネル領域上に設けられるゲート絶縁膜と、

前記ゲート絶縁膜上に設けられる複数の導電膜と複数の絶縁膜とが積層された積層体と前記積層体上に設けられるシリサイド層とからなるゲート電極と、を具備し、

前記積層体のうち、前記シリサイド層とは異なる構成の導電膜が、前記ゲート絶縁膜と接触することを特徴とする半導体装置。

【請求項2】

半導体基板上に、ゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、複数の導電膜と複数の絶縁膜とが積層された積層体を形成する工程と、

前記積層体上に、シリコン層を形成する工程と、

前記シリコン層及び前記積層体に対して、ゲート加工を施す工程と、

前記シリコン層にゲート加工を施した後に、前記半導体基板内に拡散層を形成する工程と、

前記シリコン層上に金属膜を形成する工程と、

前記積層体が含む前記複数の導電膜のうち前記ゲート絶縁膜と接触する導電膜がシリサイド化しないように、前記シリコン層と前記金属膜との固相反応によって、前記積層体上にシリサイド層を形成する工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項3】

半導体基板と、

前記半導体基板内に設けられるメモリセルアレイ領域と、

前記メモリセルアレイ領域に隣接して、半導体基板内に設けられる周辺回路領域と、

前記メモリセルアレイ領域内の半導体基板内に設けられ、ソース/ドレイン領域となる2つの第1拡散層と、前記第1拡散層間のチャネル領域上に設けられるトンネル絶縁膜と、前記トンネル絶縁膜上に設けられる記憶層と、前記記憶層上に設けられる中間絶縁層と、前記中間絶縁層上に設けられ、第1シリサイド層からなる第1ゲート電極とを有するメモリセルと、

前記周辺領域内の半導体基板内に設けられた2つの第2拡散層と、前記第2拡散層間のチャネル領域上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられ、複数の導電膜と複数の絶縁膜とが積層された積層体と前記積層体上に設けられた第2シリサイド層とからなる第2ゲート電極とを有する周辺トランジスタと、を具備し、

前記第2ゲート電極を構成している前記積層体のうち、前記第2シリサイド層とは異なる構成の導電膜が、前記ゲート絶縁膜と接触することを特徴とする半導体装置。

【請求項4】

前記記憶層は、電荷捕獲準位を含む絶縁膜であることを特徴とする請求項3に記載の半導体装置。

【請求項5】

周辺回路領域内の半導体基板表面上に、ゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、複数の導電膜と複数の絶縁膜とが積層された積層体を形成する工程と、

メモリセルアレイ領域内の半導体基板表面上に、トンネル絶縁膜を形成する工程と、

前記トンネル絶縁膜上に、記憶層を形成する工程と、

前記記憶層上に、中間絶縁膜を形成する工程と、

前記中間絶縁膜上に、第1シリコン層を形成する工程と、

前記積層体上に、第2シリコン層を形成する工程と、

前記メモリセルアレイ領域内においては、前記第1シリコン層、前記中間絶縁膜及び前記記憶層に対してゲート加工を施し、前記周辺回路領域においては、前記第2シリコン層及び前記積層体に対してゲート加工を施す工程と、

前記ゲート加工された第1及び第2シリコン層をマスクとして、前記メモリセルアレイ領域及び前記周辺回路領域の半導体基板内に、第1及び第2拡散層をそれぞれ形成する工程と、

前記第1及び第2シリコン層上に、金属膜を形成する工程と、

前記積層体が含む前記複数の導電膜のうち前記ゲート絶縁膜と接触する導電膜がシリサイド化しないように、前記第1及び第2のシリコン層及び前記導電膜と前記金属膜との固相反応によって、前記中間絶縁膜上及び前記積層体上に第1及び第2シリサイド層をそれぞれ形成する工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項1】

半導体基板と、

前記半導体基板内に設けられ、ソース/ドレイン領域として機能する2つの拡散層と、

前記2つの拡散層間のチャネル領域上に設けられるゲート絶縁膜と、

前記ゲート絶縁膜上に設けられる複数の導電膜と複数の絶縁膜とが積層された積層体と前記積層体上に設けられるシリサイド層とからなるゲート電極と、を具備し、

前記積層体のうち、前記シリサイド層とは異なる構成の導電膜が、前記ゲート絶縁膜と接触することを特徴とする半導体装置。

【請求項2】

半導体基板上に、ゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、複数の導電膜と複数の絶縁膜とが積層された積層体を形成する工程と、

前記積層体上に、シリコン層を形成する工程と、

前記シリコン層及び前記積層体に対して、ゲート加工を施す工程と、

前記シリコン層にゲート加工を施した後に、前記半導体基板内に拡散層を形成する工程と、

前記シリコン層上に金属膜を形成する工程と、

前記積層体が含む前記複数の導電膜のうち前記ゲート絶縁膜と接触する導電膜がシリサイド化しないように、前記シリコン層と前記金属膜との固相反応によって、前記積層体上にシリサイド層を形成する工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項3】

半導体基板と、

前記半導体基板内に設けられるメモリセルアレイ領域と、

前記メモリセルアレイ領域に隣接して、半導体基板内に設けられる周辺回路領域と、

前記メモリセルアレイ領域内の半導体基板内に設けられ、ソース/ドレイン領域となる2つの第1拡散層と、前記第1拡散層間のチャネル領域上に設けられるトンネル絶縁膜と、前記トンネル絶縁膜上に設けられる記憶層と、前記記憶層上に設けられる中間絶縁層と、前記中間絶縁層上に設けられ、第1シリサイド層からなる第1ゲート電極とを有するメモリセルと、

前記周辺領域内の半導体基板内に設けられた2つの第2拡散層と、前記第2拡散層間のチャネル領域上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられ、複数の導電膜と複数の絶縁膜とが積層された積層体と前記積層体上に設けられた第2シリサイド層とからなる第2ゲート電極とを有する周辺トランジスタと、を具備し、

前記第2ゲート電極を構成している前記積層体のうち、前記第2シリサイド層とは異なる構成の導電膜が、前記ゲート絶縁膜と接触することを特徴とする半導体装置。

【請求項4】

前記記憶層は、電荷捕獲準位を含む絶縁膜であることを特徴とする請求項3に記載の半導体装置。

【請求項5】

周辺回路領域内の半導体基板表面上に、ゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、複数の導電膜と複数の絶縁膜とが積層された積層体を形成する工程と、

メモリセルアレイ領域内の半導体基板表面上に、トンネル絶縁膜を形成する工程と、

前記トンネル絶縁膜上に、記憶層を形成する工程と、

前記記憶層上に、中間絶縁膜を形成する工程と、

前記中間絶縁膜上に、第1シリコン層を形成する工程と、

前記積層体上に、第2シリコン層を形成する工程と、

前記メモリセルアレイ領域内においては、前記第1シリコン層、前記中間絶縁膜及び前記記憶層に対してゲート加工を施し、前記周辺回路領域においては、前記第2シリコン層及び前記積層体に対してゲート加工を施す工程と、

前記ゲート加工された第1及び第2シリコン層をマスクとして、前記メモリセルアレイ領域及び前記周辺回路領域の半導体基板内に、第1及び第2拡散層をそれぞれ形成する工程と、

前記第1及び第2シリコン層上に、金属膜を形成する工程と、

前記積層体が含む前記複数の導電膜のうち前記ゲート絶縁膜と接触する導電膜がシリサイド化しないように、前記第1及び第2のシリコン層及び前記導電膜と前記金属膜との固相反応によって、前記中間絶縁膜上及び前記積層体上に第1及び第2シリサイド層をそれぞれ形成する工程と、

を具備することを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2009−272564(P2009−272564A)

【公開日】平成21年11月19日(2009.11.19)

【国際特許分類】

【出願番号】特願2008−123904(P2008−123904)

【出願日】平成20年5月9日(2008.5.9)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成21年11月19日(2009.11.19)

【国際特許分類】

【出願日】平成20年5月9日(2008.5.9)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]