半導体装置及び半導体装置の製造方法

【課題】本発明の目的は、ベアチップが高密度実装されたような半導体装置において、ベアチップの全端子を検査することを可能にした検査用パッド及びそれに付随する配線のレイアウトを提供する半導体装置を実現することである。

【解決手段】本発明に係る半導体装置は、ベアチップの全ての端子が配線基板内の特定の配線層を介して、ダミー領域に配置された検査用パッドにそれぞれ接続され、検査完了後は、そのダミー領域が切断されるものである。

【解決手段】本発明に係る半導体装置は、ベアチップの全ての端子が配線基板内の特定の配線層を介して、ダミー領域に配置された検査用パッドにそれぞれ接続され、検査完了後は、そのダミー領域が切断されるものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子(IC)を配線基板上に直接実装したベアチップ実装、特に複数のICがベアチップ実装された半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

複数の半導体素子(IC)が配線基板上に実装されたマルチチップモジュールという半導体装置が知られている。この種の半導体装置では、集積度を高め、小型化するため、ベアなIC(ベアチップ)を配線基板上に直接実装するベアチップ実装と呼ばれる高密度実装技術が用いられている。

【0003】

一方、一般的な半導体装置において、搭載されたICの電気的な検査を行うため、例えば、特許文献1及び2に示されたような提案が成されている。

【特許文献1】特開2000−77810号公報

【特許文献2】特開2001−210926号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

マルチチップモジュール等の半導体装置におけるベアチップにおいては、高密度実装のため、配線基板上のレイアウトに厳しい制限がある。そのため、ベアチップの電気的検査に用いられる検査用パッド及びそれに付随する配線等の形成領域は著しく制限を受ける。

【0005】

従って、一般のマルチチップモジュールにおけるベアチップでは、電気的検査の対象をメインクロック信号用端子、入力端子、出力端子、駆動電源用端子、グランド用端子等の主要端子に限定し、それらの端子に接続されたベアチップ内の主要機能のみを限定的に検査することにより、各端子に接続された検査用パッド及びそれに付随する配線等の占有領域を所定範囲内に限定している。

【0006】

本発明の代表的な目的は、ベアチップが高密度実装されたような半導体装置において、ベアチップの全端子を検査することを可能にした検査用パッド及びそれに付随する配線のレイアウトを提供する半導体装置を実現することである。

本発明によれば、高集積化、小型化という高密度実装を可能にしつつ、実装されたベアチップの全端子について電気的な検査を実現できるという格別の作用効果を得ることができる。このベアチップの全端子について検査することにより、検査工程という半導体装置の製造工程の途中段階でベアチップの不良を特定できるので、最終製品である半導体装置の品質が向上する。

【課題を解決するための手段】

【0007】

上記目的を達成するため、本発明は以下のような構成を備える。

請求項1記載の発明は、電子回路と、前記電子回路に電気的に接続され、その外表面上に形成された複数の端子とを有するベアチップと、

前記ベアチップが配置された搭載領域と、前記搭載領域に隣接するダミー領域とを有する積層型配線基板であって、前記複数の端子にそれぞれ電気的に接続され、前記ダミー領域に形成された複数の検査用パッドと、前記複数の端子と前記複数の検査用パッドとの間をそれぞれ電気的に接続する複数の配線が形成された検査用配線層とを備え、前記検査用パッドを用いて前記端子に接続された前記電子回路の検査を行った後、前記ダミー領域が切断される前記積層型配線基板とを備えた半導体装置である。

請求項2記載の発明は、請求項1記載の構成に加え、前記ダミー領域は前記搭載領域を包囲するように前記積層型配線基板の周辺に配置されたものである。

請求項3記載の発明は、請求項2記載の構成に加え、前記ベアチップは第1のベアチップと第2のベアチップから成り、各ベアチップは前記搭載領域内に近接して配置されると共に、前記搭載領域に対向する外表面に複数の端子が形成されたものである。

請求項4記載の発明は、請求項1乃至3のいずれかに記載の構成に加え、前記積層型配線基板は、接地電極に接続されたグランドプレーン層を有し、前記検査用配線層は前記グランドプレーン層に隣接して配置されたものである。

請求項5記載の発明は、請求項1記載の構成に加え、前記ベアチップ及び前記積層型配線基板は樹脂層で封止されたものである。

請求項6記載の発明は、請求項5記載の構成に加え、前記樹脂層に隣接して冷却手段が設けられたものである。

請求項7記載の発明は、電子回路と、前記電子回路に電気的に接続され、その外表面上に形成された複数の端子とを有するベアチップと、前記ベアチップが配置された搭載領域と、前記搭載領域に隣接するダミー領域と、前記複数の端子にそれぞれ電気的に接続され、前記ダミー領域に形成された複数の検査用パッドと、前記複数の端子と前記複数の検査用パッドとの間をそれぞれ電気的に接続する複数の配線が形成された検査用配線層とを有する積層型配線基板とを備えた半導体装置の製造方法において、

前記複数の検査用パッドの全てに検査用プローブを接触させ、各検査用パッドに電気的に接続された前記電子回路を検査する工程と、

前記検査を行った後、前記ダミー領域を切断する工程とを有する半導体装置の製造方法である。

請求項8記載の発明は、請求項7記載の構成に加え、前記ダミー領域を切断した後、前記ベアチップ及び前記積層型配線基板を樹脂層により被覆する工程を有するものである。

【発明の効果】

【0008】

請求項1記載の発明によれば、高集積化、小型化という高密度実装を可能にしつつ、実装されたベアチップの全端子について電気的な検査を実現できる。さらに、検査完了後、ダミー領域を除去することができるので、半導体装置の小型化を確保することができる。

請求項2乃至3記載の発明によれば、請求項1記載の発明により得られる効果に加え、各端子から検査パッドまでの配線距離を短くすることができるので、配線遅延が低減された精度の高い検査が実現できる。

請求項5記載の発明によれば、請求項1乃至3のいずれか記載の発明により得られる効果に加え、積層型配線基板の側面も樹脂層で封止することができるので、ベアチップ及び配線基板の気密性を高めることができると共に、周辺に配置される電子部品との短絡を防止することができる。

請求項6記載の発明によれば、請求項5記載の発明により得られる効果に加え、高熱を発生するベアチップを効果的に冷却することができる。

請求項7記載の発明によれば、ベアチップの全端子について検査することにより、検査工程という半導体装置の製造工程の途中段階でベアチップの不良を特定できるので、最終製品である半導体装置の品質が向上する。

請求項8記載の発明によれば、請求項7記載の発明により得られる効果に加え、ベアチップ及び配線基板を、配線基板の側面を含めて樹脂層で同時に封止することができる。

【発明を実施するための最良の形態】

【0009】

以下、本発明の実施の形態について図面を参照して説明する。本実施形態で参酌する図面では、発明の理解を容易にするため、各要素が模式的に示されている。本欄においては、前出の要素と同じ要素に同一符号を付すことにより、その説明が省略されることもある。

【0010】

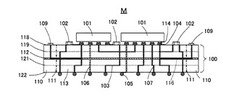

図1には本実施形態におけるマルチチップモジュールMの断面図が示され、図2にはその上面図が示されている。本実施形態では、説明の簡易化のため、2つのベアチップが配線基板上に搭載された例が示されているが、ベアチップの数はこれに限られるものではない。また、ベアチップの配線基板への実装方法、配線基板内における各配線の形成方法等については特に説明がなければ公知の手法により実現されているものと理解されたい。

【0011】

このマルチチップモジュールMは、積層型の配線基板100上に実装された2つのベアチップ101を備えている。この配線基板100はベアチップ101が搭載される搭載領域113とその周囲のダミー領域110を有する。この搭載領域113には、ベアチップ101を実装するための図示されない電極パッド、配線等が形成されると共に、電子部品102も実装されている。ダミー領域110は、後述する検査工程が完了後、切断ライン111に沿って配線基板100から切り離される。ベアチップ101は、その表面に電子回路が形成され、電子回路内の各機能ブロックに端子114が電気的に接続されている。各端子114はベアチップ101の外表面に形成されている。端子114はベアチップ101の底面に形成され、配線基板100上にはんだバンプ104を介して実装されている。端子114は配線基板100内に形成された配線103、スルーホール106もしくはビア107等の貫通孔内に形成された導電体を介してはんだボール105に接続されている。

【0012】

ダミー領域110には、複数の検査用パッド109が配置されている。本実施形態では、検査に用いる検査用パッド109は全てダミー領域110に配置している。これら検査用パッド109は配線基板100内の検査用配線層112に形成された配線116を介してベアチップ101の端子114の全てにそれぞれ接続されている。ここでベアチップ114の幾つかの端子は、図2中の実線で示される通り配線基板100上に形成された配線115により直接検査用パッド109に接続される。ベアチップ114の端子数は通常、100〜150程度あるので、全端子の内の大多数の端子は図2中の点線で示される通り配線基板100内の検査用配線層112に形成された配線116を介して検査用パッド109にそれぞれ接続される。この検査用配線層112に形成された配線116は、ベアチップの各端子114と検査用パッド109との間の接続のみを目的として設けられた、特定用途の配線層である。従って、検査が完了し、ダミー領域110が切断された後、この配線層112の配線116は、モジュールMの電気的動作に寄与しない。検査工程では、検査用パッド109のそれぞれに検査用のプローブ針を当て、ベアチップの全端子にそれぞれ接続された電子回路の機能ブロックを検査する。

【0013】

本実施形態の配線基板100の層数は図1のように4層構造に加え、検査用配線層112が形成され、5層構造となっている。第2層119は電位がゼロであるグランドプレーンに設定される。これは、第1層118においてマイクロストリップラインを構成しているため、インピーダンスコントロールのために、隣接する第2層119をグランドプレーンとする必要があるからである。ベアチップ101の端子114と電子部品もしくははんだボール105との接続には、ビアホール、スルーホール等の貫通孔を第1層から第3層121もしくは第4層122まで貫通して形成し、それらの貫通孔内に形成された導電体に接続された配線を形成して、電気的な接続を確立する。

【0014】

検査用配線層112は、配線基板100の第2層119と第3層121との間に形成されている。この検査用配線層112には、ベアチップの各端子114と検査用パッド109との間の接続のみを目的とする配線116が形成されているのみであるので、他の配線レイアウト、貫通孔等の設計への影響は最小限に留まる。すなわち、従来、用いられている4層構造の配線基板へ本実施形態の構成を適用する場合、検査用配線層に係わる配線レイアウトを追加するのみで容易に本発明を実施できる。

【0015】

ここで、配線115及び116と各端子114との接続について説明する。ベアチップ101の端子114が、第1層118のみで他方のベアチップ101の端子114もしくは電子部品102に配線を介して接続している場合は、第1層118上の配線115からダミー領域110の検査用パッド109まで、配線を引き回して接続する。

【0016】

端子114が第1層118と第2層119のみで、他方のベアチップ101の端子114もしくは電子部品102に配線を介して接続している場合は、第1層118と第2層119間に形成された貫通孔を検査用配線層112まで延在し、検査用配線層112においてこの貫通孔からダミー領域110の検査用パッド109と同平面座標まで配線116を形成する。同平面座標とは、特定の検査用パッド109の下方のことを言う。検査用パッド109の下方まで延在された配線116は、配線基板内に形成された貫通孔を介して検査用パッド109と電気的に接続される。

【0017】

端子114が配線、貫通孔を介して第4層122まで延在し、はんだボール105と接続している場合、検査用配線層112を貫通する貫通孔から検査用配線層112上でダミー領域110の検査用パッド109と同平面座標まで配線116を形成する。同様に、検査用パッド109の下方まで延在された配線116は、配線基板内に形成された貫通孔を介して検査用パッド109と電気的に接続される。

【0018】

上記の説明を参酌すれば、従来、用いられている4層構造の配線基板にダミー領域110及び検査用配線層112を設ければ、種々の設計を大きく変更せずに本実施形態を適用することが可能になる。これにより、ベアチップ101の全端子114について電気的な検査が可能になる。

【0019】

検査工程において、ベアチップの全端子にそれぞれ接続された電子回路の機能ブロックを検査した後、ダミー領域110は切断ライン111に沿って切断される。これにより配線基板100は図3のように搭載領域113のみとなり、マルチチップモジュールとしてはサイズが増大することはない。

【0020】

ベアチップ101の検査後にダミー領域110は切断され、ベアチップを搭載した回路基板はマザー基板123上にはんだボール105を介して実装される。その後、マルチチップモジュールMは図4に示されるように樹脂層108で封止される。ダミー領域110を切断後、配線基板100の側面から露出していた配線116の一部も、この樹脂封止により被覆される。

【0021】

樹脂層108上には、ベアチップ101から発生した熱を冷却するためにヒートシンク400が設けられている。

【0022】

なお、検査後にダミー領域110が切断されるため、第1層118と検査用配線層112での配線116がオープンスタブ構造となる。通常、配線を伝達する信号の周波数が高くなると、このオープンスタブ構造による信号の反射の影響が大きくなる。この場合には、配線の長さ、幅、厚み及び材料、積層基板の材料を適宜選択することにより、その影響を最大限小さくすることが可能となる。

【図面の簡単な説明】

【0023】

【図1】本発明の実施形態に係る半導体装置の断面図

【図2】本発明の実施形態に係る半導体装置の上面図

【図3】本発明の本実施形態においてダミー領域が切断された半導体装置を示す断面図

【図4】マザー基板上に搭載された本発明の実施形態に係る半導体装置を示す断面図

【符号の説明】

【0024】

100 配線基板

101 ベアチップ

102 電子部品

103 配線

109 検査用パッド

110 ダミー領域

111 切断ライン

112 検査用配線層

113 搭載領域

114 端子

115 配線基板上の配線

116 検査用配線層における配線

【技術分野】

【0001】

本発明は、半導体素子(IC)を配線基板上に直接実装したベアチップ実装、特に複数のICがベアチップ実装された半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

複数の半導体素子(IC)が配線基板上に実装されたマルチチップモジュールという半導体装置が知られている。この種の半導体装置では、集積度を高め、小型化するため、ベアなIC(ベアチップ)を配線基板上に直接実装するベアチップ実装と呼ばれる高密度実装技術が用いられている。

【0003】

一方、一般的な半導体装置において、搭載されたICの電気的な検査を行うため、例えば、特許文献1及び2に示されたような提案が成されている。

【特許文献1】特開2000−77810号公報

【特許文献2】特開2001−210926号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

マルチチップモジュール等の半導体装置におけるベアチップにおいては、高密度実装のため、配線基板上のレイアウトに厳しい制限がある。そのため、ベアチップの電気的検査に用いられる検査用パッド及びそれに付随する配線等の形成領域は著しく制限を受ける。

【0005】

従って、一般のマルチチップモジュールにおけるベアチップでは、電気的検査の対象をメインクロック信号用端子、入力端子、出力端子、駆動電源用端子、グランド用端子等の主要端子に限定し、それらの端子に接続されたベアチップ内の主要機能のみを限定的に検査することにより、各端子に接続された検査用パッド及びそれに付随する配線等の占有領域を所定範囲内に限定している。

【0006】

本発明の代表的な目的は、ベアチップが高密度実装されたような半導体装置において、ベアチップの全端子を検査することを可能にした検査用パッド及びそれに付随する配線のレイアウトを提供する半導体装置を実現することである。

本発明によれば、高集積化、小型化という高密度実装を可能にしつつ、実装されたベアチップの全端子について電気的な検査を実現できるという格別の作用効果を得ることができる。このベアチップの全端子について検査することにより、検査工程という半導体装置の製造工程の途中段階でベアチップの不良を特定できるので、最終製品である半導体装置の品質が向上する。

【課題を解決するための手段】

【0007】

上記目的を達成するため、本発明は以下のような構成を備える。

請求項1記載の発明は、電子回路と、前記電子回路に電気的に接続され、その外表面上に形成された複数の端子とを有するベアチップと、

前記ベアチップが配置された搭載領域と、前記搭載領域に隣接するダミー領域とを有する積層型配線基板であって、前記複数の端子にそれぞれ電気的に接続され、前記ダミー領域に形成された複数の検査用パッドと、前記複数の端子と前記複数の検査用パッドとの間をそれぞれ電気的に接続する複数の配線が形成された検査用配線層とを備え、前記検査用パッドを用いて前記端子に接続された前記電子回路の検査を行った後、前記ダミー領域が切断される前記積層型配線基板とを備えた半導体装置である。

請求項2記載の発明は、請求項1記載の構成に加え、前記ダミー領域は前記搭載領域を包囲するように前記積層型配線基板の周辺に配置されたものである。

請求項3記載の発明は、請求項2記載の構成に加え、前記ベアチップは第1のベアチップと第2のベアチップから成り、各ベアチップは前記搭載領域内に近接して配置されると共に、前記搭載領域に対向する外表面に複数の端子が形成されたものである。

請求項4記載の発明は、請求項1乃至3のいずれかに記載の構成に加え、前記積層型配線基板は、接地電極に接続されたグランドプレーン層を有し、前記検査用配線層は前記グランドプレーン層に隣接して配置されたものである。

請求項5記載の発明は、請求項1記載の構成に加え、前記ベアチップ及び前記積層型配線基板は樹脂層で封止されたものである。

請求項6記載の発明は、請求項5記載の構成に加え、前記樹脂層に隣接して冷却手段が設けられたものである。

請求項7記載の発明は、電子回路と、前記電子回路に電気的に接続され、その外表面上に形成された複数の端子とを有するベアチップと、前記ベアチップが配置された搭載領域と、前記搭載領域に隣接するダミー領域と、前記複数の端子にそれぞれ電気的に接続され、前記ダミー領域に形成された複数の検査用パッドと、前記複数の端子と前記複数の検査用パッドとの間をそれぞれ電気的に接続する複数の配線が形成された検査用配線層とを有する積層型配線基板とを備えた半導体装置の製造方法において、

前記複数の検査用パッドの全てに検査用プローブを接触させ、各検査用パッドに電気的に接続された前記電子回路を検査する工程と、

前記検査を行った後、前記ダミー領域を切断する工程とを有する半導体装置の製造方法である。

請求項8記載の発明は、請求項7記載の構成に加え、前記ダミー領域を切断した後、前記ベアチップ及び前記積層型配線基板を樹脂層により被覆する工程を有するものである。

【発明の効果】

【0008】

請求項1記載の発明によれば、高集積化、小型化という高密度実装を可能にしつつ、実装されたベアチップの全端子について電気的な検査を実現できる。さらに、検査完了後、ダミー領域を除去することができるので、半導体装置の小型化を確保することができる。

請求項2乃至3記載の発明によれば、請求項1記載の発明により得られる効果に加え、各端子から検査パッドまでの配線距離を短くすることができるので、配線遅延が低減された精度の高い検査が実現できる。

請求項5記載の発明によれば、請求項1乃至3のいずれか記載の発明により得られる効果に加え、積層型配線基板の側面も樹脂層で封止することができるので、ベアチップ及び配線基板の気密性を高めることができると共に、周辺に配置される電子部品との短絡を防止することができる。

請求項6記載の発明によれば、請求項5記載の発明により得られる効果に加え、高熱を発生するベアチップを効果的に冷却することができる。

請求項7記載の発明によれば、ベアチップの全端子について検査することにより、検査工程という半導体装置の製造工程の途中段階でベアチップの不良を特定できるので、最終製品である半導体装置の品質が向上する。

請求項8記載の発明によれば、請求項7記載の発明により得られる効果に加え、ベアチップ及び配線基板を、配線基板の側面を含めて樹脂層で同時に封止することができる。

【発明を実施するための最良の形態】

【0009】

以下、本発明の実施の形態について図面を参照して説明する。本実施形態で参酌する図面では、発明の理解を容易にするため、各要素が模式的に示されている。本欄においては、前出の要素と同じ要素に同一符号を付すことにより、その説明が省略されることもある。

【0010】

図1には本実施形態におけるマルチチップモジュールMの断面図が示され、図2にはその上面図が示されている。本実施形態では、説明の簡易化のため、2つのベアチップが配線基板上に搭載された例が示されているが、ベアチップの数はこれに限られるものではない。また、ベアチップの配線基板への実装方法、配線基板内における各配線の形成方法等については特に説明がなければ公知の手法により実現されているものと理解されたい。

【0011】

このマルチチップモジュールMは、積層型の配線基板100上に実装された2つのベアチップ101を備えている。この配線基板100はベアチップ101が搭載される搭載領域113とその周囲のダミー領域110を有する。この搭載領域113には、ベアチップ101を実装するための図示されない電極パッド、配線等が形成されると共に、電子部品102も実装されている。ダミー領域110は、後述する検査工程が完了後、切断ライン111に沿って配線基板100から切り離される。ベアチップ101は、その表面に電子回路が形成され、電子回路内の各機能ブロックに端子114が電気的に接続されている。各端子114はベアチップ101の外表面に形成されている。端子114はベアチップ101の底面に形成され、配線基板100上にはんだバンプ104を介して実装されている。端子114は配線基板100内に形成された配線103、スルーホール106もしくはビア107等の貫通孔内に形成された導電体を介してはんだボール105に接続されている。

【0012】

ダミー領域110には、複数の検査用パッド109が配置されている。本実施形態では、検査に用いる検査用パッド109は全てダミー領域110に配置している。これら検査用パッド109は配線基板100内の検査用配線層112に形成された配線116を介してベアチップ101の端子114の全てにそれぞれ接続されている。ここでベアチップ114の幾つかの端子は、図2中の実線で示される通り配線基板100上に形成された配線115により直接検査用パッド109に接続される。ベアチップ114の端子数は通常、100〜150程度あるので、全端子の内の大多数の端子は図2中の点線で示される通り配線基板100内の検査用配線層112に形成された配線116を介して検査用パッド109にそれぞれ接続される。この検査用配線層112に形成された配線116は、ベアチップの各端子114と検査用パッド109との間の接続のみを目的として設けられた、特定用途の配線層である。従って、検査が完了し、ダミー領域110が切断された後、この配線層112の配線116は、モジュールMの電気的動作に寄与しない。検査工程では、検査用パッド109のそれぞれに検査用のプローブ針を当て、ベアチップの全端子にそれぞれ接続された電子回路の機能ブロックを検査する。

【0013】

本実施形態の配線基板100の層数は図1のように4層構造に加え、検査用配線層112が形成され、5層構造となっている。第2層119は電位がゼロであるグランドプレーンに設定される。これは、第1層118においてマイクロストリップラインを構成しているため、インピーダンスコントロールのために、隣接する第2層119をグランドプレーンとする必要があるからである。ベアチップ101の端子114と電子部品もしくははんだボール105との接続には、ビアホール、スルーホール等の貫通孔を第1層から第3層121もしくは第4層122まで貫通して形成し、それらの貫通孔内に形成された導電体に接続された配線を形成して、電気的な接続を確立する。

【0014】

検査用配線層112は、配線基板100の第2層119と第3層121との間に形成されている。この検査用配線層112には、ベアチップの各端子114と検査用パッド109との間の接続のみを目的とする配線116が形成されているのみであるので、他の配線レイアウト、貫通孔等の設計への影響は最小限に留まる。すなわち、従来、用いられている4層構造の配線基板へ本実施形態の構成を適用する場合、検査用配線層に係わる配線レイアウトを追加するのみで容易に本発明を実施できる。

【0015】

ここで、配線115及び116と各端子114との接続について説明する。ベアチップ101の端子114が、第1層118のみで他方のベアチップ101の端子114もしくは電子部品102に配線を介して接続している場合は、第1層118上の配線115からダミー領域110の検査用パッド109まで、配線を引き回して接続する。

【0016】

端子114が第1層118と第2層119のみで、他方のベアチップ101の端子114もしくは電子部品102に配線を介して接続している場合は、第1層118と第2層119間に形成された貫通孔を検査用配線層112まで延在し、検査用配線層112においてこの貫通孔からダミー領域110の検査用パッド109と同平面座標まで配線116を形成する。同平面座標とは、特定の検査用パッド109の下方のことを言う。検査用パッド109の下方まで延在された配線116は、配線基板内に形成された貫通孔を介して検査用パッド109と電気的に接続される。

【0017】

端子114が配線、貫通孔を介して第4層122まで延在し、はんだボール105と接続している場合、検査用配線層112を貫通する貫通孔から検査用配線層112上でダミー領域110の検査用パッド109と同平面座標まで配線116を形成する。同様に、検査用パッド109の下方まで延在された配線116は、配線基板内に形成された貫通孔を介して検査用パッド109と電気的に接続される。

【0018】

上記の説明を参酌すれば、従来、用いられている4層構造の配線基板にダミー領域110及び検査用配線層112を設ければ、種々の設計を大きく変更せずに本実施形態を適用することが可能になる。これにより、ベアチップ101の全端子114について電気的な検査が可能になる。

【0019】

検査工程において、ベアチップの全端子にそれぞれ接続された電子回路の機能ブロックを検査した後、ダミー領域110は切断ライン111に沿って切断される。これにより配線基板100は図3のように搭載領域113のみとなり、マルチチップモジュールとしてはサイズが増大することはない。

【0020】

ベアチップ101の検査後にダミー領域110は切断され、ベアチップを搭載した回路基板はマザー基板123上にはんだボール105を介して実装される。その後、マルチチップモジュールMは図4に示されるように樹脂層108で封止される。ダミー領域110を切断後、配線基板100の側面から露出していた配線116の一部も、この樹脂封止により被覆される。

【0021】

樹脂層108上には、ベアチップ101から発生した熱を冷却するためにヒートシンク400が設けられている。

【0022】

なお、検査後にダミー領域110が切断されるため、第1層118と検査用配線層112での配線116がオープンスタブ構造となる。通常、配線を伝達する信号の周波数が高くなると、このオープンスタブ構造による信号の反射の影響が大きくなる。この場合には、配線の長さ、幅、厚み及び材料、積層基板の材料を適宜選択することにより、その影響を最大限小さくすることが可能となる。

【図面の簡単な説明】

【0023】

【図1】本発明の実施形態に係る半導体装置の断面図

【図2】本発明の実施形態に係る半導体装置の上面図

【図3】本発明の本実施形態においてダミー領域が切断された半導体装置を示す断面図

【図4】マザー基板上に搭載された本発明の実施形態に係る半導体装置を示す断面図

【符号の説明】

【0024】

100 配線基板

101 ベアチップ

102 電子部品

103 配線

109 検査用パッド

110 ダミー領域

111 切断ライン

112 検査用配線層

113 搭載領域

114 端子

115 配線基板上の配線

116 検査用配線層における配線

【特許請求の範囲】

【請求項1】

電子回路と、前記電子回路に電気的に接続され、その外表面上に形成された複数の端子とを有するベアチップと、

前記ベアチップが配置された搭載領域と、前記搭載領域に隣接するダミー領域とを有する積層型配線基板であって、前記複数の端子にそれぞれ電気的に接続され、前記ダミー領域に形成された複数の検査用パッドと、前記複数の端子と前記複数の検査用パッドとの間をそれぞれ電気的に接続する複数の配線が形成された検査用配線層とを備え、前記検査用パッドを用いて前記端子に接続された前記電子回路の検査を行った後、前記ダミー領域が切断される前記積層型配線基板とを備えたことを特徴とする半導体装置。

【請求項2】

前記ダミー領域は前記搭載領域を包囲するように前記積層型配線基板の周辺に配置されたことを特徴とする請求項1記載の半導体装置。

【請求項3】

前記ベアチップは第1のベアチップと第2のベアチップから成り、各ベアチップは前記搭載領域内に近接して配置されると共に、前記搭載領域に対向する外表面に複数の端子が形成されたことを特徴とする請求項2記載の半導体装置。

【請求項4】

前記積層型配線基板は、接地電極に接続されたグランドプレーン層を有し、前記検査用配線層は前記グランドプレーン層に隣接して配置されたことを特徴とする請求項1乃至3のいずれかに記載された半導体装置。

【請求項5】

前記ベアチップ及び前記積層型配線基板は樹脂層で封止されたことを特徴とする請求項1記載の半導体装置。

【請求項6】

前記樹脂層に隣接して冷却手段が設けられたことを特徴とする請求項5記載の半導体装置。

【請求項7】

電子回路と、前記電子回路に電気的に接続され、その外表面上に形成された複数の端子とを有するベアチップと、

前記ベアチップが配置された搭載領域と、前記搭載領域に隣接するダミー領域と、前記複数の端子にそれぞれ電気的に接続され、前記ダミー領域に形成された複数の検査用パッドと、前記複数の端子と前記複数の検査用パッドとの間をそれぞれ電気的に接続する複数の配線が形成された検査用配線層とを有する積層型配線基板とを備えた半導体装置の製造方法において、

前記複数の検査用パッドの全てに検査用プローブを接触させ、各検査用パッドに電気的に接続された前記電子回路を検査する工程と、

前記検査を行った後、前記ダミー領域を切断する工程とを有することを特徴とする半導体装置の製造方法。

【請求項8】

前記ダミー領域を切断した後、前記ベアチップ及び前記積層型配線基板を樹脂層により被覆する工程を有することを特徴とする請求項7記載の半導体装置の製造方法。

【請求項1】

電子回路と、前記電子回路に電気的に接続され、その外表面上に形成された複数の端子とを有するベアチップと、

前記ベアチップが配置された搭載領域と、前記搭載領域に隣接するダミー領域とを有する積層型配線基板であって、前記複数の端子にそれぞれ電気的に接続され、前記ダミー領域に形成された複数の検査用パッドと、前記複数の端子と前記複数の検査用パッドとの間をそれぞれ電気的に接続する複数の配線が形成された検査用配線層とを備え、前記検査用パッドを用いて前記端子に接続された前記電子回路の検査を行った後、前記ダミー領域が切断される前記積層型配線基板とを備えたことを特徴とする半導体装置。

【請求項2】

前記ダミー領域は前記搭載領域を包囲するように前記積層型配線基板の周辺に配置されたことを特徴とする請求項1記載の半導体装置。

【請求項3】

前記ベアチップは第1のベアチップと第2のベアチップから成り、各ベアチップは前記搭載領域内に近接して配置されると共に、前記搭載領域に対向する外表面に複数の端子が形成されたことを特徴とする請求項2記載の半導体装置。

【請求項4】

前記積層型配線基板は、接地電極に接続されたグランドプレーン層を有し、前記検査用配線層は前記グランドプレーン層に隣接して配置されたことを特徴とする請求項1乃至3のいずれかに記載された半導体装置。

【請求項5】

前記ベアチップ及び前記積層型配線基板は樹脂層で封止されたことを特徴とする請求項1記載の半導体装置。

【請求項6】

前記樹脂層に隣接して冷却手段が設けられたことを特徴とする請求項5記載の半導体装置。

【請求項7】

電子回路と、前記電子回路に電気的に接続され、その外表面上に形成された複数の端子とを有するベアチップと、

前記ベアチップが配置された搭載領域と、前記搭載領域に隣接するダミー領域と、前記複数の端子にそれぞれ電気的に接続され、前記ダミー領域に形成された複数の検査用パッドと、前記複数の端子と前記複数の検査用パッドとの間をそれぞれ電気的に接続する複数の配線が形成された検査用配線層とを有する積層型配線基板とを備えた半導体装置の製造方法において、

前記複数の検査用パッドの全てに検査用プローブを接触させ、各検査用パッドに電気的に接続された前記電子回路を検査する工程と、

前記検査を行った後、前記ダミー領域を切断する工程とを有することを特徴とする半導体装置の製造方法。

【請求項8】

前記ダミー領域を切断した後、前記ベアチップ及び前記積層型配線基板を樹脂層により被覆する工程を有することを特徴とする請求項7記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2010−123608(P2010−123608A)

【公開日】平成22年6月3日(2010.6.3)

【国際特許分類】

【出願番号】特願2008−293279(P2008−293279)

【出願日】平成20年11月17日(2008.11.17)

【出願人】(000006622)株式会社安川電機 (2,482)

【Fターム(参考)】

【公開日】平成22年6月3日(2010.6.3)

【国際特許分類】

【出願日】平成20年11月17日(2008.11.17)

【出願人】(000006622)株式会社安川電機 (2,482)

【Fターム(参考)】

[ Back to top ]