半導体装置及び半導体装置の製造方法

【課題】本発明は、比誘電率が10以上のhigh-k材料から構成されるMIMキャパシタの高誘電率膜がトランジスタや配線の設けられる箇所に形成されない半導体装置を容易に製造できる方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板上に下地電極を形成する工程と、前記下地電極上にフォトレジストを塗布する工程と、前記下地電極の外周部より中央側において前記フォトレジストに開口部を形成する工程と、比誘電率が10以上のhigh-k材料から構成される高誘電率膜を成膜する工程と、前記下地電極の外周部より中央側に前記高誘電率膜が残るように、リフトオフを行なう工程と、前記リフトオフにより残された前記高誘電率膜上に上地電極を形成する工程と、を備えることを特徴とするものである。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板上に下地電極を形成する工程と、前記下地電極上にフォトレジストを塗布する工程と、前記下地電極の外周部より中央側において前記フォトレジストに開口部を形成する工程と、比誘電率が10以上のhigh-k材料から構成される高誘電率膜を成膜する工程と、前記下地電極の外周部より中央側に前記高誘電率膜が残るように、リフトオフを行なう工程と、前記リフトオフにより残された前記高誘電率膜上に上地電極を形成する工程と、を備えることを特徴とするものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、比誘電率が10以上のhigh-k材料から構成されるMIMキャパシタの高誘電率膜がトランジスタや配線の設けられる箇所に形成されない半導体装置を容易に製造できる方法に関するものである。また、本発明は、MIMキャパシタの高誘電率膜や上地電極が剥がれることを防止できる半導体装置及び半導体装置の製造方法に関するものである。

【背景技術】

【0002】

従来、半導体基板上に大容量のMIMキャパシタを形成する場合や、より小さな面積にMIMキャパシタを形成する場合には、Ta2O5等のような、比誘電率が10以上のhigh-k材料から構成される高誘電率膜をMIMキャパシタの誘電体膜として適用している(例えば、特許文献1、2)。

【0003】

【特許文献1】特開平11−145387号公報

【特許文献2】特開2004−152796号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

比誘電率が10以上のhigh-k材料は特に化学的安定性が高く、このようなhigh-k材料から構成される高誘電率膜はエッチングにより加工することが困難である。このため、このような高誘電率膜からMIMキャパシタの誘電体膜を形成する場合には、トランジスタや配線が設けられる箇所に成膜される高誘電率膜を除去することが困難であった。この結果、トランジスタの寄生容量が増大し、配線遅延が生じるといった問題が生じていた。

【0005】

また、このような高誘電率膜を厚く形成する場合にはスパッタ法が適用される。スパッタ法を適用して高誘電率膜を成膜する場合には、成長面での反応性が高いCVD法を適用する場合よりも、MIMキャパシタの高誘電率膜と下地電極との密着性が弱くなる。このため、このような高誘電率膜が下地電極から剥がれ易くなるという問題が生じていた。さらに、MIMキャパシタの上地電極がこのような高誘電率膜上に形成される場合には、MIMキャパシタの誘電体膜として一般的に使用されるCVD絶縁膜上に形成される場合よりも、上地電極が剥がれ易くなるという問題も生じていた。

【0006】

本発明は、上述した課題を解決するためになされた。本発明の第1の目的は、比誘電率が10以上のhigh-k材料から構成されるMIMキャパシタの高誘電率膜がトランジスタや配線の設けられる箇所に形成されない半導体装置を容易に製造できる方法を提供することである。また、本発明の第2の目的は、MIMキャパシタの高誘電率膜や上地電極が剥がれることを防止できる半導体装置及び半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0007】

第1の発明に係る半導体装置の製造方法は、半導体基板上に下地電極を形成する工程と、前記下地電極上にフォトレジストを塗布する工程と、前記下地電極の外周部より中央側において前記フォトレジストに開口部を形成する工程と、前記開口部内及びフォトレジスト上に比誘電率が10以上のhigh-k材料から構成される高誘電率膜を成膜する工程と、前記下地電極の外周部より中央側に前記高誘電率膜が残るように、前記フォトレジスト及び前記フォトレジスト上の前記高誘電率膜を除去するリフトオフを行なう工程と、前記リフトオフにより残された前記高誘電率膜上に上地電極を形成する工程と、を備えることを特徴とするものである。

【0008】

第2の発明に係る半導体装置は、半導体基板と、前記半導体基板上に設けられた下地電極と、前記下地電極上に設けられた、比誘電率が10以上のhigh-k材料から構成される高誘電率膜と、前記高誘電率膜上に設けられた上地電極と、前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方と、前記高誘電率膜が設けられていない箇所において前記下地電極と前記上地電極の間と、に設けられたCVD絶縁膜と、を備え、前記CVD絶縁膜は、前記高誘電率膜よりも前記下地電極及び前記上地電極との密着性が強く、前記CVD絶縁膜の膜厚が30〜50nmであることを特徴とするものである。

【0009】

第3の発明に係る半導体装置は、半導体基板と、前記半導体基板上に設けられた下地電極と、前記下地電極上に設けられた、比誘電率が10以上のhigh-k材料から構成される高誘電率膜と、前記高誘電率膜上に設けられた上地電極と、前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方に設けられたCVD絶縁膜と、を備え、前記CVD絶縁膜は前記高誘電率膜よりも前記下地電極及び前記上地電極との密着性が強く、前記CVD絶縁膜の膜厚と、前記高誘電率膜及び前記CVD絶縁膜の合計の膜厚との比率が1:9〜1:11であることを特徴とするものである。

【0010】

第4の発明に係る半導体装置の製造方法は、半導体基板上に下地電極を形成する工程と、前記下地電極上に、比誘電率が10以上のhigh-k材料から構成される高誘電率膜をスパッタリング法により形成する工程と、前記高誘電率膜上に上地電極を形成する工程と、前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方と、前記高誘電率膜が設けられていない箇所において前記下地電極と前記上地電極の間とにCVD絶縁膜をCVD法により形成する工程と、を備え、 前記CVD絶縁膜の膜厚を30〜50nmとすることを特徴とするものである。

【0011】

第5の発明に係る半導体装置の製造方法は、半導体基板上に下地電極を形成する工程と、前記下地電極上に、比誘電率が10以上のhigh-k材料から構成される高誘電率膜をスパッタリング法により形成する工程と、前記高誘電率膜上に上地電極を形成する工程と、前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方にCVD絶縁膜をCVD法により形成する工程と、を備え、前記CVD絶縁膜の膜厚と、前記高誘電率膜及び前記CVD絶縁膜の合計の膜厚との比率を1:9〜1:11とすることを特徴とするものである。

【発明の効果】

【0012】

第1の発明により、比誘電率が10以上のhigh-k材料から構成されるMIMキャパシタの高誘電率膜がトランジスタや配線の設けられる箇所に形成されない半導体装置を容易に製造できる。また、第2〜第5の発明により、MIMキャパシタの高誘電率膜や上地電極が剥がれることを防止できる。

【発明を実施するための最良の形態】

【0013】

実施の形態1.

[実施の形態1の半導体装置]

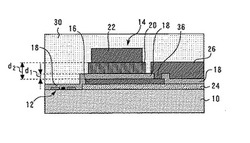

以下に、実施の形態1に係る半導体装置について説明する。図1は、実施の形態1に係る半導体装置を示す上面図である。図2は、図1のA−A´における断面図である。

【0014】

図1及び図2に示すように、半導体基板10上にGaAs高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor、以下、トランジスタと略記する)12及びMIM(Metal Insulator Metal)キャパシタ14が設けられている。トランジスタ12及びMIMキャパシタ14はMMIC(Monolithic Microwave IC)を構成する。

【0015】

MIMキャパシタ14は、下地電極16、CVD絶縁膜18、高誘電率膜20及び上地電極22を備える。下地電極16は絶縁膜24を介して半導体基板10上に設けられている。CVD絶縁膜18は下地電極16上に設けられている。高誘電率膜20はCVD絶縁膜18上において下地電極16の外周部より中央側に設けられている。上地電極22は高誘電率膜20上に設けられている。また、下地電極16にコンタクトホール36を介し接続された配線26が設けられている。上地電極22に接続された配線28が設けられている。そして、トランジスタ12及びMIMキャパシタ14を覆うように保護膜30が設けられている。

【0016】

CVD絶縁膜18はSiNから構成される。CVD絶縁膜18は、図1内の符号aで示した、高誘電率膜20が設けられていない領域においても下地電極16と上地電極22の配線28との間に設けられている。高誘電率膜20は、比誘電率が10以上のhigh-k材料(ZrO2、Ta2O5、HfO2等)から構成される。

【0017】

図2において、CVD絶縁膜18の膜厚をd1で示し、高誘電率膜20及びCVD絶縁膜18の合計の膜厚をd2で示す。ここでは、CVD絶縁膜18の膜厚d1を30nmとする。そして、高誘電率膜20の膜厚を270nmとし、高誘電率膜20及びCVD絶縁膜18の合計の膜厚d2を300nmとする。

【0018】

[実施の形態1の半導体装置の製造方法]

以下に、実施の形態1に係る半導体装置の製造方法について説明する。図3〜8は、実施の形態1に係る半導体装置の製造方法を示す工程断面図である。

【0019】

まず、図3に示すように、半導体基板10上に、トランジスタ12と下地電極16を形成する。そして、トランジスタ12及び下地電極16を覆うように、CVD絶縁膜18をCVD法により成膜する。CVD絶縁膜18としては、MIMキャパシタの誘電体膜として一般的に使用されるSiNから構成される膜を用いる。そして、CVD絶縁膜18の膜厚を30nmとする。

【0020】

次に、図4に示すように、CVD絶縁膜18上にフォトレジスト32を塗布し、露光及び現像により、下地電極16の外周部より中央側においてフォトレジスト32に開口部34を形成する。そして、開口部34の内側、及びフォトレジスト32の上に、比誘電率が10以上のhigh-k材料(ZrO2、Ta2O5、HfO2等)から構成される高誘電率膜20をスパッタリング法により成膜する。そして、高誘電率膜20の膜厚を270nmとする。

【0021】

次に、図5に示すように、下地電極16の外周部より中央側に高誘電率膜20が残るように、フォトレジスト32及びフォトレジスト32上の高誘電率膜20を除去するリフトオフを行なう。次に、図6に示すように、CVD絶縁膜18にコンタクトホール36を形成する。

【0022】

次に、図7に示すように、リフトオフにより残された高誘電率膜20上に上地電極22を形成する。この際、上地電極22とともに、下地電極16の配線26、及び上地電極22の配線(図示せず)を形成する。

【0023】

次に、図8に示すように、トランジスタ12及びMIMキャパシタ14を覆うように保護膜30を形成する。以上により、実施の形態1に係る半導体装置を製造する。

【0024】

[実施の形態1の効果]

以下に、実施の形態1の効果について説明する。

まず、リフトオフ法及びCVD法を適用したことによる効果を第1の比較例と対比しながら説明する。図9は、第1の比較例に係る半導体装置を示す上面図である。図10は、図9のA−A´における断面図である。

【0025】

図9及び図10に示すように、第1の比較例の半導体装置は、実施の形態1とは異なり、MIMキャパシタ40の誘電体膜が高誘電率膜38のみから構成されている。そして、高誘電率膜38は比誘電率が10以上のhigh-k材料(ZrO2、Ta2O5、HfO2等)から構成されている。当該high-k材料から構成された膜は化学的安定性が高く、エッチングするのが難しい。さらに、高誘電率膜38は、MIMキャパシタを100〜150Vの高耐圧にするために200〜300nmの膜厚を有する。この膜厚のため特に、高誘電率膜38は、RIE(reactive ion etching)等のエッチングにより加工することが困難である。この結果として、エッチングにより、高誘電率膜38を下地電極16の外周部より中央側にのみ残るように形成することは困難となる。

【0026】

このため第1の比較例においては、トランジスタ12や下地電極16は高誘電率膜38によって覆われ、配線26は高誘電率膜38上に形成される。また、高誘電率膜38を構成する当該high-k材料は、MIMキャパシタの誘電体膜として一般的に使用されるCVD絶縁膜(SiN等)よりも比誘電率が大きい。従って、第1の比較例に係るトランジスタ12の寄生容量は、CVD絶縁膜(SiN等)を誘電体膜として使用した場合よりも大きくなる。また、この場合には、第1の比較例に係る配線26で配線遅延が生じる。なお、エッチングにより高誘電率膜38にコンタクトホールを開口することも困難である。

【0027】

また、比誘電率が10以上のhigh-k材料から構成され、200〜300nmの厚い膜厚を有する高誘電率膜38を成膜する場合には、一般的に、スパッタリング法が用いられる。このため、高誘電率膜38は、成長面での反応性が高いCVD法を用いて成膜される場合よりも下地電極16との密着性は弱い。従って、高誘電率膜38が下地電極16から剥がれる。

【0028】

一方、実施の形態1においてはリフトオフ法を用いることにより、高誘電率膜20が下地電極16の外周部より中央側に残るように形成される。高誘電率膜20がトランジスタ12や配線26の設けられる箇所に形成されない半導体装置を容易に製造できる。この結果として、トランジスタ12は高誘電率膜20により覆われることがなくなり、トランジスタ12の寄生容量が大きくなるのを防止できる。また、高誘電率膜20が配線26の近傍に設けられなくなり、配線遅延が生じるのを防止できる。

【0029】

また、実施の形態1に係るCVD絶縁膜18は、スパッタリング法により成膜された第1の比較例に係る高誘電率膜38とは異なり、成長面での反応性が高いCVD法を用いて成膜される。このため、実施の形態1に係るCVD絶縁膜18は、第1の比較例に係る高誘電率膜38よりも下地電極16との密着性が強い。従って、実施の形態1においては、高誘電率膜20が剥がれることを防止できる。

【0030】

次に、CVD絶縁膜18の膜厚d1を30nmとしたことによる効果を説明する。CVD絶縁膜18は比誘電率が7のSiNから構成され、比誘電率が10以上のhigh-k材料から構成される高誘電率膜20よりも比誘電率が低い。このため、MIMキャパシタを大容量化するためにはCVD絶縁膜18の膜厚d1を薄くすればよい。そして、MIMキャパシタの大容量化のためには、膜厚d1を50nm以下にする必要がある。一方、図1内の符号aで示した、高誘電率膜20が設けられていない領域においては、下地電極16と上地電極22の配線28との間にCVD絶縁膜18が設けられている。そして、下地電極16と上地電極22の配線28との間のCVD絶縁膜18の絶縁耐圧として30〜50Vが必要である。そして、SiNから構成されるCVD絶縁膜18の絶縁耐圧は10MV/cmである。このため、MIMキャパシタの絶縁耐圧を得るには、膜厚d1を30nm以上にする必要がある。

【0031】

従って、CVD絶縁膜18の膜厚d1を30〜50nmの範囲に定めることにより、MIMキャパシタ14を大容量化することができ、CVD絶縁膜18の絶縁耐圧を得ることができる。実施の形態1においては、膜厚d1を30nmとしたので、膜厚d1は当該範囲に収まり、この効果が得られる。

【0032】

なお、SiO又はSiONから構成されるCVD絶縁膜18の絶縁耐圧も10MV/cmである。このため、CVD絶縁膜18をSiNではなくSiO又はSiONから構成してもよい。この場合も同様に、膜厚d1を30〜50nmの範囲に定めることにより、MIMキャパシタ14を大容量化することができ、CVD絶縁膜18の絶縁耐圧を得ることができる。これは以下の他の実施の形態においても同様である。

【0033】

次に、高誘電率膜20及びCVD絶縁膜18の合計の膜厚d2を300nmとしたことによる効果を第2の比較例と対比しながら説明する。図11は、第2の比較例に係るMIMキャパシタを有する半導体装置を示す断面図である。第2の比較例に係るMIMキャパシタ42は誘電体膜がCVD絶縁膜44のみから構成される。これ以外の第2の比較例に係る構成は、実施の形態1と同様である。第2の比較例に係るCVD絶縁膜44の膜厚は、図1に示した高誘電率膜20及びCVD絶縁膜18の合計の膜厚d2と同一である。図12は、実施の形態1に係るSiNから構成されるCVD絶縁膜を含むMIMキャパシタの面積縮小率を示した図である。面積縮小率は、同じ容量値を得る上で、実施の形態1に係るMIMキャパシタ14の面積を、第2の比較例に係るMIMキャパシタ42に対して、どれくらい縮小できるかを示す。面積縮小率は、実施の形態1に係る高誘電率膜20を含むMIMキャパシタ14及び第2の比較例に係る高誘電率膜20を含まないMIMキャパシタ42の両方を同じ面積にした上で両方の容量値を測定し、それら容量値の比率を計算することによって求められる。そして、面積縮小率は、図1に示した膜厚d1を30nmの一定値にして、図1及び図11に示した膜厚d2を30〜600nmの各値に設定して求めた。また、面積縮小率は、比誘電率(図12内でkで示す)が10〜50の高誘電率膜20のそれぞれについて求めた。

【0034】

図12に示すように、面積縮小率は、どの比誘電率においても、膜厚d2を大きくすると小さくなる。これは、膜厚d2を大きくすると、高誘電率膜20を適用したMIMキャパシタ14の面積を、高誘電率膜20を適用しない場合と比較してより小さくできることを示す。ところが、どの比誘電率の場合においても、膜厚d2を、膜厚d1と膜厚d2との比率が1:10となる厚さ(300nm)よりも大きくしても、面積縮小率は、当該比率が1:10となる場合と比較してそれほど変わらなくなる(飽和する)。

【0035】

一般に、MIMキャパシタ14を必要な絶縁耐圧が得られるまで高耐圧化するためには、膜厚d2を300nm程度まで厚くする必要がある。また、高耐圧化とともにMIMキャパシタ14を大容量化したいという要望がある。上述したように面積縮小率は、膜厚d2が300nmになるまでは小さくなっていくが、膜厚d2がそれより大きくなると飽和する。これは、膜厚d2が300nmになるまでは、高誘電率膜20の適用による大容量化の効果が顕著であるが、膜厚d2が300nmよりも大きくなると、膜厚d2が大きくなることを原因として容量が小さくなる影響が強まることを示す。

【0036】

従って、膜厚d1と膜厚d2との比率を1:10とすることにより(膜厚d1を30nmとし、膜厚d2を300nmとすることにより)、最も有利に、MIMキャパシタ14の高耐圧化と大容量化の両方を実現できる。また、面積縮小率が飽和する比率には幅があるので、膜厚d1と膜厚d2との比率が1:9〜1:11の範囲ならば、高耐圧化と大容量化の両方を実現できる効果が得られる。

【0037】

なお、成膜装置によりCVD絶縁膜18及び高誘電率膜20を成膜する場合には、膜厚に±10%の誤差が生じうる。しかし、この場合においても、高耐圧化と大容量化のために膜厚d1と膜厚d2との比率が1:10となることを目標値として成膜して構わない。誤差が生じたとしても、当該比率を1:9〜1:11の範囲に収めることができる可能性が高い。これは以下の他の実施の形態においても同様である。

【0038】

実施の形態2.

[実施の形態2の半導体装置]

以下に、実施の形態2に係る半導体装置について説明する。図13は、実施の形態2に係る半導体装置を示す断面図である。

【0039】

図13に示すように、MIMキャパシタ46は、下地電極16、第1のCVD絶縁膜48、高誘電率膜20、第2のCVD絶縁膜50及び上地電極22を備える。下地電極16は絶縁膜24を介して半導体基板10上に設けられている。第1のCVD絶縁膜48は下地電極16上に設けられている。高誘電率膜20は第1のCVD絶縁膜48上において下地電極16の外周部より中央側に設けられている。第2のCVD絶縁膜50は高誘電率膜20上に設けられている。上地電極22は第2のCVD絶縁膜50上において高誘電率膜20が下に位置する箇所に設けられている。第1のCVD絶縁膜48及び第2のCVD絶縁膜50はSiNから構成される。高誘電率膜20は、比誘電率が10以上のhigh-k材料(ZrO2、Ta2O5、HfO2等)から構成される。

【0040】

図13において、第1のCVD絶縁膜48及び第2のCVD絶縁膜50の合計の膜厚をd3で示した。また、第1のCVD絶縁膜48、高誘電率膜20及び第2のCVD絶縁膜50の合計の膜厚d4で示した。ここでは、膜厚d3を30nmとし、膜厚d4を300nmとした。以上を除き、実施の形態2に係る半導体装置の構成は実施の形態1に係る半導体装置と同一である。

【0041】

[実施の形態2の半導体装置の製造方法]

以下に、実施の形態2に係る半導体装置の製造方法について説明する。図14〜19は、実施の形態2に係る半導体装置の製造方法を示す工程断面図である。

【0042】

まず、実施の形態1と同様に、図14〜図16に示すように、トランジスタ12、MIMキャパシタ40の下地電極16、第1のCVD絶縁膜48及び高誘電率膜20を形成する。

【0043】

次に、図17に示すように、高誘電率膜20を覆うように、第2のCVD絶縁膜50を形成する。そして、第1のCVD絶縁膜48及び第2のCVD絶縁膜50を貫通するコンタクトホール52を形成する。

【0044】

次に、図18に示すように、第2のCVD絶縁膜50上に上地電極22を形成する。この際、上地電極22とともに、下地電極の配線26、及び上地電極22の配線(図示せず)を形成する。

【0045】

次に、図19に示すように、トランジスタ12及びMIMキャパシタ46を覆うように保護膜30を形成する。以上の工程により、実施の形態2に係る半導体装置を製造する。以上を除き、実施の形態2に係る半導体装置の製造方法は実施の形態1と同一である。

【0046】

[実施の形態2の効果]

以下に、実施の形態2の効果について説明する。

まず、CVD法を適用し、第2のCVD絶縁膜50を形成したことによる効果を上述した第1の比較例と対比しながら説明する。

【0047】

図9及び図10に示すように、上述した第1の比較例に係る上地電極22は、高誘電率膜38上に成膜されているため、MIMキャパシタの誘電体膜として一般的に使用されるCVD絶縁膜上に成膜される場合よりも剥がれ易くなることがある。

【0048】

一方、実施の形態2においては、第2のCVD絶縁膜50が、成長面での反応性が高いCVD法により高誘電率膜20を覆うように成膜される。上地電極22は、高誘電率膜20上ではなく第2のCVD絶縁膜50上に形成される。従って、上地電極22は、第1の比較例とは異なり高誘電率膜20上に直接形成されない。このため、上地電極22が剥がれ易くなることを防止できる。

【0049】

次に、第1のCVD絶縁膜48及び第2のCVD絶縁膜50の合計の膜厚d3を30nmとすることによる効果を説明する。膜厚d3を30〜50nmの範囲に定めることにより、実施の形態1において図1に示されたCVD絶縁膜18の膜厚d1を30〜50nmの範囲に定めることにより得られた効果と同様の効果を得られる。つまり、MIMキャパシタ46を大容量化することができ、第1のCVD絶縁膜48及び第2のCVD絶縁膜50の絶縁耐圧を得ることができる。実施の形態2においては、膜厚d3を30nmとしたので、膜厚d3はこの範囲に収まり、この効果が得られる。

【0050】

次に、第1のCVD絶縁膜48、高誘電率膜20及び第2のCVD絶縁膜50の合計の膜厚d4を300nmとしたことによる効果を説明する。上述した膜厚d3と膜厚d4との比率を1:10とすることにより(膜厚d3を30nmとし、膜厚d4を300nmとすることにより)、実施の形態1と同様に、MIMキャパシタ46の高耐圧化と大容量化の両方を最も有利に実現できる。また、膜厚d3と膜厚d4との比率が1:9〜1:11の範囲ならば、高耐圧化と大容量化の両方を実現できる効果が得られる。実施の形態2においては、膜厚d3及び膜厚d4をそれぞれ30nm、300nmとしたので、当該比率は当該範囲に収まり、この効果が得られる。

【図面の簡単な説明】

【0051】

【図1】実施の形態1に係る半導体装置を示す上面図である。

【図2】図1のA−A´における断面図である。

【図3】実施の形態1に係る半導体装置の製造方法を示す工程断面図である。

【図4】実施の形態1に係る半導体装置の製造方法を示す工程断面図である。

【図5】実施の形態1に係る半導体装置の製造方法を示す工程断面図である。

【図6】実施の形態1に係る半導体装置の製造方法を示す工程断面図である。

【図7】実施の形態1に係る半導体装置の製造方法を示す工程断面図である。

【図8】実施の形態1に係る半導体装置の製造方法を示す工程断面図である。

【図9】第1の比較例に係る半導体装置を示す上面図である。

【図10】図9のA−A´における断面図である。

【図11】第2の比較例に係るMIMキャパシタを有する半導体装置を示す断面図である。

【図12】実施の形態1に係るSiNから構成されるCVD絶縁膜を含むMIMキャパシタの面積縮小率を示した図である。

【図13】実施の形態2に係る半導体装置を示す断面図である。

【図14】実施の形態2に係る半導体装置の製造方法を示す工程断面図である。

【図15】実施の形態2に係る半導体装置の製造方法を示す工程断面図である。

【図16】実施の形態2に係る半導体装置の製造方法を示す工程断面図である。

【図17】実施の形態2に係る半導体装置の製造方法を示す工程断面図である。

【図18】実施の形態2に係る半導体装置の製造方法を示す工程断面図である。

【図19】実施の形態2に係る半導体装置の製造方法を示す工程断面図である。

【符号の説明】

【0052】

10 半導体基板

12 トランジスタ

14,40 MIMキャパシタ

16 下地電極

18 CVD絶縁膜

20,38 高誘電率膜

22 上地電極

32 フォトレジスト

36,52 コンタクトホール

48 第1のCVD絶縁膜

50 第2のCVD絶縁膜

【技術分野】

【0001】

本発明は、比誘電率が10以上のhigh-k材料から構成されるMIMキャパシタの高誘電率膜がトランジスタや配線の設けられる箇所に形成されない半導体装置を容易に製造できる方法に関するものである。また、本発明は、MIMキャパシタの高誘電率膜や上地電極が剥がれることを防止できる半導体装置及び半導体装置の製造方法に関するものである。

【背景技術】

【0002】

従来、半導体基板上に大容量のMIMキャパシタを形成する場合や、より小さな面積にMIMキャパシタを形成する場合には、Ta2O5等のような、比誘電率が10以上のhigh-k材料から構成される高誘電率膜をMIMキャパシタの誘電体膜として適用している(例えば、特許文献1、2)。

【0003】

【特許文献1】特開平11−145387号公報

【特許文献2】特開2004−152796号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

比誘電率が10以上のhigh-k材料は特に化学的安定性が高く、このようなhigh-k材料から構成される高誘電率膜はエッチングにより加工することが困難である。このため、このような高誘電率膜からMIMキャパシタの誘電体膜を形成する場合には、トランジスタや配線が設けられる箇所に成膜される高誘電率膜を除去することが困難であった。この結果、トランジスタの寄生容量が増大し、配線遅延が生じるといった問題が生じていた。

【0005】

また、このような高誘電率膜を厚く形成する場合にはスパッタ法が適用される。スパッタ法を適用して高誘電率膜を成膜する場合には、成長面での反応性が高いCVD法を適用する場合よりも、MIMキャパシタの高誘電率膜と下地電極との密着性が弱くなる。このため、このような高誘電率膜が下地電極から剥がれ易くなるという問題が生じていた。さらに、MIMキャパシタの上地電極がこのような高誘電率膜上に形成される場合には、MIMキャパシタの誘電体膜として一般的に使用されるCVD絶縁膜上に形成される場合よりも、上地電極が剥がれ易くなるという問題も生じていた。

【0006】

本発明は、上述した課題を解決するためになされた。本発明の第1の目的は、比誘電率が10以上のhigh-k材料から構成されるMIMキャパシタの高誘電率膜がトランジスタや配線の設けられる箇所に形成されない半導体装置を容易に製造できる方法を提供することである。また、本発明の第2の目的は、MIMキャパシタの高誘電率膜や上地電極が剥がれることを防止できる半導体装置及び半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0007】

第1の発明に係る半導体装置の製造方法は、半導体基板上に下地電極を形成する工程と、前記下地電極上にフォトレジストを塗布する工程と、前記下地電極の外周部より中央側において前記フォトレジストに開口部を形成する工程と、前記開口部内及びフォトレジスト上に比誘電率が10以上のhigh-k材料から構成される高誘電率膜を成膜する工程と、前記下地電極の外周部より中央側に前記高誘電率膜が残るように、前記フォトレジスト及び前記フォトレジスト上の前記高誘電率膜を除去するリフトオフを行なう工程と、前記リフトオフにより残された前記高誘電率膜上に上地電極を形成する工程と、を備えることを特徴とするものである。

【0008】

第2の発明に係る半導体装置は、半導体基板と、前記半導体基板上に設けられた下地電極と、前記下地電極上に設けられた、比誘電率が10以上のhigh-k材料から構成される高誘電率膜と、前記高誘電率膜上に設けられた上地電極と、前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方と、前記高誘電率膜が設けられていない箇所において前記下地電極と前記上地電極の間と、に設けられたCVD絶縁膜と、を備え、前記CVD絶縁膜は、前記高誘電率膜よりも前記下地電極及び前記上地電極との密着性が強く、前記CVD絶縁膜の膜厚が30〜50nmであることを特徴とするものである。

【0009】

第3の発明に係る半導体装置は、半導体基板と、前記半導体基板上に設けられた下地電極と、前記下地電極上に設けられた、比誘電率が10以上のhigh-k材料から構成される高誘電率膜と、前記高誘電率膜上に設けられた上地電極と、前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方に設けられたCVD絶縁膜と、を備え、前記CVD絶縁膜は前記高誘電率膜よりも前記下地電極及び前記上地電極との密着性が強く、前記CVD絶縁膜の膜厚と、前記高誘電率膜及び前記CVD絶縁膜の合計の膜厚との比率が1:9〜1:11であることを特徴とするものである。

【0010】

第4の発明に係る半導体装置の製造方法は、半導体基板上に下地電極を形成する工程と、前記下地電極上に、比誘電率が10以上のhigh-k材料から構成される高誘電率膜をスパッタリング法により形成する工程と、前記高誘電率膜上に上地電極を形成する工程と、前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方と、前記高誘電率膜が設けられていない箇所において前記下地電極と前記上地電極の間とにCVD絶縁膜をCVD法により形成する工程と、を備え、 前記CVD絶縁膜の膜厚を30〜50nmとすることを特徴とするものである。

【0011】

第5の発明に係る半導体装置の製造方法は、半導体基板上に下地電極を形成する工程と、前記下地電極上に、比誘電率が10以上のhigh-k材料から構成される高誘電率膜をスパッタリング法により形成する工程と、前記高誘電率膜上に上地電極を形成する工程と、前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方にCVD絶縁膜をCVD法により形成する工程と、を備え、前記CVD絶縁膜の膜厚と、前記高誘電率膜及び前記CVD絶縁膜の合計の膜厚との比率を1:9〜1:11とすることを特徴とするものである。

【発明の効果】

【0012】

第1の発明により、比誘電率が10以上のhigh-k材料から構成されるMIMキャパシタの高誘電率膜がトランジスタや配線の設けられる箇所に形成されない半導体装置を容易に製造できる。また、第2〜第5の発明により、MIMキャパシタの高誘電率膜や上地電極が剥がれることを防止できる。

【発明を実施するための最良の形態】

【0013】

実施の形態1.

[実施の形態1の半導体装置]

以下に、実施の形態1に係る半導体装置について説明する。図1は、実施の形態1に係る半導体装置を示す上面図である。図2は、図1のA−A´における断面図である。

【0014】

図1及び図2に示すように、半導体基板10上にGaAs高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor、以下、トランジスタと略記する)12及びMIM(Metal Insulator Metal)キャパシタ14が設けられている。トランジスタ12及びMIMキャパシタ14はMMIC(Monolithic Microwave IC)を構成する。

【0015】

MIMキャパシタ14は、下地電極16、CVD絶縁膜18、高誘電率膜20及び上地電極22を備える。下地電極16は絶縁膜24を介して半導体基板10上に設けられている。CVD絶縁膜18は下地電極16上に設けられている。高誘電率膜20はCVD絶縁膜18上において下地電極16の外周部より中央側に設けられている。上地電極22は高誘電率膜20上に設けられている。また、下地電極16にコンタクトホール36を介し接続された配線26が設けられている。上地電極22に接続された配線28が設けられている。そして、トランジスタ12及びMIMキャパシタ14を覆うように保護膜30が設けられている。

【0016】

CVD絶縁膜18はSiNから構成される。CVD絶縁膜18は、図1内の符号aで示した、高誘電率膜20が設けられていない領域においても下地電極16と上地電極22の配線28との間に設けられている。高誘電率膜20は、比誘電率が10以上のhigh-k材料(ZrO2、Ta2O5、HfO2等)から構成される。

【0017】

図2において、CVD絶縁膜18の膜厚をd1で示し、高誘電率膜20及びCVD絶縁膜18の合計の膜厚をd2で示す。ここでは、CVD絶縁膜18の膜厚d1を30nmとする。そして、高誘電率膜20の膜厚を270nmとし、高誘電率膜20及びCVD絶縁膜18の合計の膜厚d2を300nmとする。

【0018】

[実施の形態1の半導体装置の製造方法]

以下に、実施の形態1に係る半導体装置の製造方法について説明する。図3〜8は、実施の形態1に係る半導体装置の製造方法を示す工程断面図である。

【0019】

まず、図3に示すように、半導体基板10上に、トランジスタ12と下地電極16を形成する。そして、トランジスタ12及び下地電極16を覆うように、CVD絶縁膜18をCVD法により成膜する。CVD絶縁膜18としては、MIMキャパシタの誘電体膜として一般的に使用されるSiNから構成される膜を用いる。そして、CVD絶縁膜18の膜厚を30nmとする。

【0020】

次に、図4に示すように、CVD絶縁膜18上にフォトレジスト32を塗布し、露光及び現像により、下地電極16の外周部より中央側においてフォトレジスト32に開口部34を形成する。そして、開口部34の内側、及びフォトレジスト32の上に、比誘電率が10以上のhigh-k材料(ZrO2、Ta2O5、HfO2等)から構成される高誘電率膜20をスパッタリング法により成膜する。そして、高誘電率膜20の膜厚を270nmとする。

【0021】

次に、図5に示すように、下地電極16の外周部より中央側に高誘電率膜20が残るように、フォトレジスト32及びフォトレジスト32上の高誘電率膜20を除去するリフトオフを行なう。次に、図6に示すように、CVD絶縁膜18にコンタクトホール36を形成する。

【0022】

次に、図7に示すように、リフトオフにより残された高誘電率膜20上に上地電極22を形成する。この際、上地電極22とともに、下地電極16の配線26、及び上地電極22の配線(図示せず)を形成する。

【0023】

次に、図8に示すように、トランジスタ12及びMIMキャパシタ14を覆うように保護膜30を形成する。以上により、実施の形態1に係る半導体装置を製造する。

【0024】

[実施の形態1の効果]

以下に、実施の形態1の効果について説明する。

まず、リフトオフ法及びCVD法を適用したことによる効果を第1の比較例と対比しながら説明する。図9は、第1の比較例に係る半導体装置を示す上面図である。図10は、図9のA−A´における断面図である。

【0025】

図9及び図10に示すように、第1の比較例の半導体装置は、実施の形態1とは異なり、MIMキャパシタ40の誘電体膜が高誘電率膜38のみから構成されている。そして、高誘電率膜38は比誘電率が10以上のhigh-k材料(ZrO2、Ta2O5、HfO2等)から構成されている。当該high-k材料から構成された膜は化学的安定性が高く、エッチングするのが難しい。さらに、高誘電率膜38は、MIMキャパシタを100〜150Vの高耐圧にするために200〜300nmの膜厚を有する。この膜厚のため特に、高誘電率膜38は、RIE(reactive ion etching)等のエッチングにより加工することが困難である。この結果として、エッチングにより、高誘電率膜38を下地電極16の外周部より中央側にのみ残るように形成することは困難となる。

【0026】

このため第1の比較例においては、トランジスタ12や下地電極16は高誘電率膜38によって覆われ、配線26は高誘電率膜38上に形成される。また、高誘電率膜38を構成する当該high-k材料は、MIMキャパシタの誘電体膜として一般的に使用されるCVD絶縁膜(SiN等)よりも比誘電率が大きい。従って、第1の比較例に係るトランジスタ12の寄生容量は、CVD絶縁膜(SiN等)を誘電体膜として使用した場合よりも大きくなる。また、この場合には、第1の比較例に係る配線26で配線遅延が生じる。なお、エッチングにより高誘電率膜38にコンタクトホールを開口することも困難である。

【0027】

また、比誘電率が10以上のhigh-k材料から構成され、200〜300nmの厚い膜厚を有する高誘電率膜38を成膜する場合には、一般的に、スパッタリング法が用いられる。このため、高誘電率膜38は、成長面での反応性が高いCVD法を用いて成膜される場合よりも下地電極16との密着性は弱い。従って、高誘電率膜38が下地電極16から剥がれる。

【0028】

一方、実施の形態1においてはリフトオフ法を用いることにより、高誘電率膜20が下地電極16の外周部より中央側に残るように形成される。高誘電率膜20がトランジスタ12や配線26の設けられる箇所に形成されない半導体装置を容易に製造できる。この結果として、トランジスタ12は高誘電率膜20により覆われることがなくなり、トランジスタ12の寄生容量が大きくなるのを防止できる。また、高誘電率膜20が配線26の近傍に設けられなくなり、配線遅延が生じるのを防止できる。

【0029】

また、実施の形態1に係るCVD絶縁膜18は、スパッタリング法により成膜された第1の比較例に係る高誘電率膜38とは異なり、成長面での反応性が高いCVD法を用いて成膜される。このため、実施の形態1に係るCVD絶縁膜18は、第1の比較例に係る高誘電率膜38よりも下地電極16との密着性が強い。従って、実施の形態1においては、高誘電率膜20が剥がれることを防止できる。

【0030】

次に、CVD絶縁膜18の膜厚d1を30nmとしたことによる効果を説明する。CVD絶縁膜18は比誘電率が7のSiNから構成され、比誘電率が10以上のhigh-k材料から構成される高誘電率膜20よりも比誘電率が低い。このため、MIMキャパシタを大容量化するためにはCVD絶縁膜18の膜厚d1を薄くすればよい。そして、MIMキャパシタの大容量化のためには、膜厚d1を50nm以下にする必要がある。一方、図1内の符号aで示した、高誘電率膜20が設けられていない領域においては、下地電極16と上地電極22の配線28との間にCVD絶縁膜18が設けられている。そして、下地電極16と上地電極22の配線28との間のCVD絶縁膜18の絶縁耐圧として30〜50Vが必要である。そして、SiNから構成されるCVD絶縁膜18の絶縁耐圧は10MV/cmである。このため、MIMキャパシタの絶縁耐圧を得るには、膜厚d1を30nm以上にする必要がある。

【0031】

従って、CVD絶縁膜18の膜厚d1を30〜50nmの範囲に定めることにより、MIMキャパシタ14を大容量化することができ、CVD絶縁膜18の絶縁耐圧を得ることができる。実施の形態1においては、膜厚d1を30nmとしたので、膜厚d1は当該範囲に収まり、この効果が得られる。

【0032】

なお、SiO又はSiONから構成されるCVD絶縁膜18の絶縁耐圧も10MV/cmである。このため、CVD絶縁膜18をSiNではなくSiO又はSiONから構成してもよい。この場合も同様に、膜厚d1を30〜50nmの範囲に定めることにより、MIMキャパシタ14を大容量化することができ、CVD絶縁膜18の絶縁耐圧を得ることができる。これは以下の他の実施の形態においても同様である。

【0033】

次に、高誘電率膜20及びCVD絶縁膜18の合計の膜厚d2を300nmとしたことによる効果を第2の比較例と対比しながら説明する。図11は、第2の比較例に係るMIMキャパシタを有する半導体装置を示す断面図である。第2の比較例に係るMIMキャパシタ42は誘電体膜がCVD絶縁膜44のみから構成される。これ以外の第2の比較例に係る構成は、実施の形態1と同様である。第2の比較例に係るCVD絶縁膜44の膜厚は、図1に示した高誘電率膜20及びCVD絶縁膜18の合計の膜厚d2と同一である。図12は、実施の形態1に係るSiNから構成されるCVD絶縁膜を含むMIMキャパシタの面積縮小率を示した図である。面積縮小率は、同じ容量値を得る上で、実施の形態1に係るMIMキャパシタ14の面積を、第2の比較例に係るMIMキャパシタ42に対して、どれくらい縮小できるかを示す。面積縮小率は、実施の形態1に係る高誘電率膜20を含むMIMキャパシタ14及び第2の比較例に係る高誘電率膜20を含まないMIMキャパシタ42の両方を同じ面積にした上で両方の容量値を測定し、それら容量値の比率を計算することによって求められる。そして、面積縮小率は、図1に示した膜厚d1を30nmの一定値にして、図1及び図11に示した膜厚d2を30〜600nmの各値に設定して求めた。また、面積縮小率は、比誘電率(図12内でkで示す)が10〜50の高誘電率膜20のそれぞれについて求めた。

【0034】

図12に示すように、面積縮小率は、どの比誘電率においても、膜厚d2を大きくすると小さくなる。これは、膜厚d2を大きくすると、高誘電率膜20を適用したMIMキャパシタ14の面積を、高誘電率膜20を適用しない場合と比較してより小さくできることを示す。ところが、どの比誘電率の場合においても、膜厚d2を、膜厚d1と膜厚d2との比率が1:10となる厚さ(300nm)よりも大きくしても、面積縮小率は、当該比率が1:10となる場合と比較してそれほど変わらなくなる(飽和する)。

【0035】

一般に、MIMキャパシタ14を必要な絶縁耐圧が得られるまで高耐圧化するためには、膜厚d2を300nm程度まで厚くする必要がある。また、高耐圧化とともにMIMキャパシタ14を大容量化したいという要望がある。上述したように面積縮小率は、膜厚d2が300nmになるまでは小さくなっていくが、膜厚d2がそれより大きくなると飽和する。これは、膜厚d2が300nmになるまでは、高誘電率膜20の適用による大容量化の効果が顕著であるが、膜厚d2が300nmよりも大きくなると、膜厚d2が大きくなることを原因として容量が小さくなる影響が強まることを示す。

【0036】

従って、膜厚d1と膜厚d2との比率を1:10とすることにより(膜厚d1を30nmとし、膜厚d2を300nmとすることにより)、最も有利に、MIMキャパシタ14の高耐圧化と大容量化の両方を実現できる。また、面積縮小率が飽和する比率には幅があるので、膜厚d1と膜厚d2との比率が1:9〜1:11の範囲ならば、高耐圧化と大容量化の両方を実現できる効果が得られる。

【0037】

なお、成膜装置によりCVD絶縁膜18及び高誘電率膜20を成膜する場合には、膜厚に±10%の誤差が生じうる。しかし、この場合においても、高耐圧化と大容量化のために膜厚d1と膜厚d2との比率が1:10となることを目標値として成膜して構わない。誤差が生じたとしても、当該比率を1:9〜1:11の範囲に収めることができる可能性が高い。これは以下の他の実施の形態においても同様である。

【0038】

実施の形態2.

[実施の形態2の半導体装置]

以下に、実施の形態2に係る半導体装置について説明する。図13は、実施の形態2に係る半導体装置を示す断面図である。

【0039】

図13に示すように、MIMキャパシタ46は、下地電極16、第1のCVD絶縁膜48、高誘電率膜20、第2のCVD絶縁膜50及び上地電極22を備える。下地電極16は絶縁膜24を介して半導体基板10上に設けられている。第1のCVD絶縁膜48は下地電極16上に設けられている。高誘電率膜20は第1のCVD絶縁膜48上において下地電極16の外周部より中央側に設けられている。第2のCVD絶縁膜50は高誘電率膜20上に設けられている。上地電極22は第2のCVD絶縁膜50上において高誘電率膜20が下に位置する箇所に設けられている。第1のCVD絶縁膜48及び第2のCVD絶縁膜50はSiNから構成される。高誘電率膜20は、比誘電率が10以上のhigh-k材料(ZrO2、Ta2O5、HfO2等)から構成される。

【0040】

図13において、第1のCVD絶縁膜48及び第2のCVD絶縁膜50の合計の膜厚をd3で示した。また、第1のCVD絶縁膜48、高誘電率膜20及び第2のCVD絶縁膜50の合計の膜厚d4で示した。ここでは、膜厚d3を30nmとし、膜厚d4を300nmとした。以上を除き、実施の形態2に係る半導体装置の構成は実施の形態1に係る半導体装置と同一である。

【0041】

[実施の形態2の半導体装置の製造方法]

以下に、実施の形態2に係る半導体装置の製造方法について説明する。図14〜19は、実施の形態2に係る半導体装置の製造方法を示す工程断面図である。

【0042】

まず、実施の形態1と同様に、図14〜図16に示すように、トランジスタ12、MIMキャパシタ40の下地電極16、第1のCVD絶縁膜48及び高誘電率膜20を形成する。

【0043】

次に、図17に示すように、高誘電率膜20を覆うように、第2のCVD絶縁膜50を形成する。そして、第1のCVD絶縁膜48及び第2のCVD絶縁膜50を貫通するコンタクトホール52を形成する。

【0044】

次に、図18に示すように、第2のCVD絶縁膜50上に上地電極22を形成する。この際、上地電極22とともに、下地電極の配線26、及び上地電極22の配線(図示せず)を形成する。

【0045】

次に、図19に示すように、トランジスタ12及びMIMキャパシタ46を覆うように保護膜30を形成する。以上の工程により、実施の形態2に係る半導体装置を製造する。以上を除き、実施の形態2に係る半導体装置の製造方法は実施の形態1と同一である。

【0046】

[実施の形態2の効果]

以下に、実施の形態2の効果について説明する。

まず、CVD法を適用し、第2のCVD絶縁膜50を形成したことによる効果を上述した第1の比較例と対比しながら説明する。

【0047】

図9及び図10に示すように、上述した第1の比較例に係る上地電極22は、高誘電率膜38上に成膜されているため、MIMキャパシタの誘電体膜として一般的に使用されるCVD絶縁膜上に成膜される場合よりも剥がれ易くなることがある。

【0048】

一方、実施の形態2においては、第2のCVD絶縁膜50が、成長面での反応性が高いCVD法により高誘電率膜20を覆うように成膜される。上地電極22は、高誘電率膜20上ではなく第2のCVD絶縁膜50上に形成される。従って、上地電極22は、第1の比較例とは異なり高誘電率膜20上に直接形成されない。このため、上地電極22が剥がれ易くなることを防止できる。

【0049】

次に、第1のCVD絶縁膜48及び第2のCVD絶縁膜50の合計の膜厚d3を30nmとすることによる効果を説明する。膜厚d3を30〜50nmの範囲に定めることにより、実施の形態1において図1に示されたCVD絶縁膜18の膜厚d1を30〜50nmの範囲に定めることにより得られた効果と同様の効果を得られる。つまり、MIMキャパシタ46を大容量化することができ、第1のCVD絶縁膜48及び第2のCVD絶縁膜50の絶縁耐圧を得ることができる。実施の形態2においては、膜厚d3を30nmとしたので、膜厚d3はこの範囲に収まり、この効果が得られる。

【0050】

次に、第1のCVD絶縁膜48、高誘電率膜20及び第2のCVD絶縁膜50の合計の膜厚d4を300nmとしたことによる効果を説明する。上述した膜厚d3と膜厚d4との比率を1:10とすることにより(膜厚d3を30nmとし、膜厚d4を300nmとすることにより)、実施の形態1と同様に、MIMキャパシタ46の高耐圧化と大容量化の両方を最も有利に実現できる。また、膜厚d3と膜厚d4との比率が1:9〜1:11の範囲ならば、高耐圧化と大容量化の両方を実現できる効果が得られる。実施の形態2においては、膜厚d3及び膜厚d4をそれぞれ30nm、300nmとしたので、当該比率は当該範囲に収まり、この効果が得られる。

【図面の簡単な説明】

【0051】

【図1】実施の形態1に係る半導体装置を示す上面図である。

【図2】図1のA−A´における断面図である。

【図3】実施の形態1に係る半導体装置の製造方法を示す工程断面図である。

【図4】実施の形態1に係る半導体装置の製造方法を示す工程断面図である。

【図5】実施の形態1に係る半導体装置の製造方法を示す工程断面図である。

【図6】実施の形態1に係る半導体装置の製造方法を示す工程断面図である。

【図7】実施の形態1に係る半導体装置の製造方法を示す工程断面図である。

【図8】実施の形態1に係る半導体装置の製造方法を示す工程断面図である。

【図9】第1の比較例に係る半導体装置を示す上面図である。

【図10】図9のA−A´における断面図である。

【図11】第2の比較例に係るMIMキャパシタを有する半導体装置を示す断面図である。

【図12】実施の形態1に係るSiNから構成されるCVD絶縁膜を含むMIMキャパシタの面積縮小率を示した図である。

【図13】実施の形態2に係る半導体装置を示す断面図である。

【図14】実施の形態2に係る半導体装置の製造方法を示す工程断面図である。

【図15】実施の形態2に係る半導体装置の製造方法を示す工程断面図である。

【図16】実施の形態2に係る半導体装置の製造方法を示す工程断面図である。

【図17】実施の形態2に係る半導体装置の製造方法を示す工程断面図である。

【図18】実施の形態2に係る半導体装置の製造方法を示す工程断面図である。

【図19】実施の形態2に係る半導体装置の製造方法を示す工程断面図である。

【符号の説明】

【0052】

10 半導体基板

12 トランジスタ

14,40 MIMキャパシタ

16 下地電極

18 CVD絶縁膜

20,38 高誘電率膜

22 上地電極

32 フォトレジスト

36,52 コンタクトホール

48 第1のCVD絶縁膜

50 第2のCVD絶縁膜

【特許請求の範囲】

【請求項1】

半導体基板上に下地電極を形成する工程と、

前記下地電極上にフォトレジストを塗布する工程と、

前記下地電極の外周部より中央側において前記フォトレジストに開口部を形成する工程と、

前記開口部内及びフォトレジスト上に比誘電率が10以上のhigh-k材料から構成される高誘電率膜を成膜する工程と、

前記下地電極の外周部より中央側に前記高誘電率膜が残るように、前記フォトレジスト及び前記フォトレジスト上の前記高誘電率膜を除去するリフトオフを行なう工程と、

前記リフトオフにより残された前記高誘電率膜上に上地電極を形成する工程と、

を備えることを特徴とする半導体装置の製造方法。

【請求項2】

半導体基板と、

前記半導体基板上に設けられた下地電極と、

前記下地電極上に設けられた、比誘電率が10以上のhigh-k材料から構成される高誘電率膜と、

前記高誘電率膜上に設けられた上地電極と、

前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方と、前記高誘電率膜が設けられていない箇所において前記下地電極と前記上地電極の間と、に設けられたCVD絶縁膜と、

を備え、

前記CVD絶縁膜は、前記高誘電率膜よりも前記下地電極及び前記上地電極との密着性が強く、

前記CVD絶縁膜の膜厚が30〜50nmであることを特徴とする半導体装置。

【請求項3】

前記CVD絶縁膜は、SiN、SiO、SiONのいずれか1つから構成されることを特徴とする請求項2に記載の半導体装置。

【請求項4】

半導体基板と、

前記半導体基板上に設けられた下地電極と、

前記下地電極上に設けられた、比誘電率が10以上のhigh-k材料から構成される高誘電率膜と、

前記高誘電率膜上に設けられた上地電極と、

前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方に設けられたCVD絶縁膜と、

を備え、

前記CVD絶縁膜は前記高誘電率膜よりも前記下地電極及び前記上地電極との密着性が強く、

前記CVD絶縁膜の膜厚と、前記高誘電率膜及び前記CVD絶縁膜の合計の膜厚との比率が1:9〜1:11であることを特徴とする半導体装置。

【請求項5】

前記CVD絶縁膜は、SiNから構成されることを特徴とする請求項4に記載の半導体装置。

【請求項6】

前記高誘電率膜は、Ta2O5、ZrO2、HfO2のいずれか1つから構成されることを特徴とする請求項2〜5のいずれか1項に記載の半導体装置。

【請求項7】

半導体基板上に下地電極を形成する工程と、

前記下地電極上に、比誘電率が10以上のhigh-k材料から構成される高誘電率膜をスパッタリング法により形成する工程と、

前記高誘電率膜上に上地電極を形成する工程と、

前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方と、前記高誘電率膜が設けられていない箇所において前記下地電極と前記上地電極の間とにCVD絶縁膜をCVD法により形成する工程と、

を備え、

前記CVD絶縁膜の膜厚を30〜50nmとすることを特徴とする半導体装置の製造方法。

【請求項8】

前記CVD絶縁膜として、SiN、SiO、SiONのいずれか1つから構成される膜を用いることを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

半導体基板上に下地電極を形成する工程と、

前記下地電極上に、比誘電率が10以上のhigh-k材料から構成される高誘電率膜をスパッタリング法により形成する工程と、

前記高誘電率膜上に上地電極を形成する工程と、

前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方にCVD絶縁膜をCVD法により形成する工程と、

を備え、

前記CVD絶縁膜の膜厚と、前記高誘電率膜及び前記CVD絶縁膜の合計の膜厚との比率を1:9〜1:11とすることを特徴とする半導体装置の製造方法。

【請求項10】

前記CVD絶縁膜として、SiNから構成される膜を用いることを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

前記高誘電率膜として、Ta2O5、ZrO2、HfO2のいずれか1つから構成される膜を用いることを特徴とする請求項1、7〜10のいずれか1項に記載の半導体装置の製造方法。

【請求項1】

半導体基板上に下地電極を形成する工程と、

前記下地電極上にフォトレジストを塗布する工程と、

前記下地電極の外周部より中央側において前記フォトレジストに開口部を形成する工程と、

前記開口部内及びフォトレジスト上に比誘電率が10以上のhigh-k材料から構成される高誘電率膜を成膜する工程と、

前記下地電極の外周部より中央側に前記高誘電率膜が残るように、前記フォトレジスト及び前記フォトレジスト上の前記高誘電率膜を除去するリフトオフを行なう工程と、

前記リフトオフにより残された前記高誘電率膜上に上地電極を形成する工程と、

を備えることを特徴とする半導体装置の製造方法。

【請求項2】

半導体基板と、

前記半導体基板上に設けられた下地電極と、

前記下地電極上に設けられた、比誘電率が10以上のhigh-k材料から構成される高誘電率膜と、

前記高誘電率膜上に設けられた上地電極と、

前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方と、前記高誘電率膜が設けられていない箇所において前記下地電極と前記上地電極の間と、に設けられたCVD絶縁膜と、

を備え、

前記CVD絶縁膜は、前記高誘電率膜よりも前記下地電極及び前記上地電極との密着性が強く、

前記CVD絶縁膜の膜厚が30〜50nmであることを特徴とする半導体装置。

【請求項3】

前記CVD絶縁膜は、SiN、SiO、SiONのいずれか1つから構成されることを特徴とする請求項2に記載の半導体装置。

【請求項4】

半導体基板と、

前記半導体基板上に設けられた下地電極と、

前記下地電極上に設けられた、比誘電率が10以上のhigh-k材料から構成される高誘電率膜と、

前記高誘電率膜上に設けられた上地電極と、

前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方に設けられたCVD絶縁膜と、

を備え、

前記CVD絶縁膜は前記高誘電率膜よりも前記下地電極及び前記上地電極との密着性が強く、

前記CVD絶縁膜の膜厚と、前記高誘電率膜及び前記CVD絶縁膜の合計の膜厚との比率が1:9〜1:11であることを特徴とする半導体装置。

【請求項5】

前記CVD絶縁膜は、SiNから構成されることを特徴とする請求項4に記載の半導体装置。

【請求項6】

前記高誘電率膜は、Ta2O5、ZrO2、HfO2のいずれか1つから構成されることを特徴とする請求項2〜5のいずれか1項に記載の半導体装置。

【請求項7】

半導体基板上に下地電極を形成する工程と、

前記下地電極上に、比誘電率が10以上のhigh-k材料から構成される高誘電率膜をスパッタリング法により形成する工程と、

前記高誘電率膜上に上地電極を形成する工程と、

前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方と、前記高誘電率膜が設けられていない箇所において前記下地電極と前記上地電極の間とにCVD絶縁膜をCVD法により形成する工程と、

を備え、

前記CVD絶縁膜の膜厚を30〜50nmとすることを特徴とする半導体装置の製造方法。

【請求項8】

前記CVD絶縁膜として、SiN、SiO、SiONのいずれか1つから構成される膜を用いることを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

半導体基板上に下地電極を形成する工程と、

前記下地電極上に、比誘電率が10以上のhigh-k材料から構成される高誘電率膜をスパッタリング法により形成する工程と、

前記高誘電率膜上に上地電極を形成する工程と、

前記下地電極と前記高誘電率膜の間及び前記高誘電率膜と前記上地電極の間の少なくとも一方にCVD絶縁膜をCVD法により形成する工程と、

を備え、

前記CVD絶縁膜の膜厚と、前記高誘電率膜及び前記CVD絶縁膜の合計の膜厚との比率を1:9〜1:11とすることを特徴とする半導体装置の製造方法。

【請求項10】

前記CVD絶縁膜として、SiNから構成される膜を用いることを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

前記高誘電率膜として、Ta2O5、ZrO2、HfO2のいずれか1つから構成される膜を用いることを特徴とする請求項1、7〜10のいずれか1項に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2010−129690(P2010−129690A)

【公開日】平成22年6月10日(2010.6.10)

【国際特許分類】

【出願番号】特願2008−301313(P2008−301313)

【出願日】平成20年11月26日(2008.11.26)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成22年6月10日(2010.6.10)

【国際特許分類】

【出願日】平成20年11月26日(2008.11.26)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]