半導体装置及び半導体装置の製造方法

【課題】ビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線と配線が埋め込まれた絶縁膜の間にエアギャップを有する半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の微細化に伴い、配線の間隔が狭くなっている。配線の間隔が狭くなると配線間の容量が増大し、これによって信号の遅延が生じてしまう。配線間の容量を小さくする技術の一つに、配線と配線が埋め込まれた絶縁膜の間にエアギャップを設けることがある。

【0003】

特許文献1には、配線を埋め込むための溝を絶縁膜に形成するときに、溝の側壁に劣化層を形成し、この劣化層を配線形成後に除去することにより、配線と絶縁膜の間にエアギャップを形成する、と記載されている。

【0004】

特許文献2には、配線を埋め込むための溝の底面及び側面に触媒特性膜を形成し、この触媒特性膜上に配線となるCu膜を形成し、その後、溝の側面に位置する触媒特性膜を除去することにより、配線と絶縁膜の間にエアギャップを形成する、と記載されている。

【0005】

また特許文献3には、エアギャップを形成する技術ではないが、配線上に金属キャップを形成した後、配線が埋め込まれている絶縁膜の表面を損傷し、この損傷した表面を除去する、と記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】米国特許出願公開第2008/0076258号明細書

【特許文献2】特開2008−300652号公報

【特許文献3】特開2008−205458号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

図14(a)に示すように、エアギャップ402を有する配線層400の上の配線層420にビア421及び配線溝422を形成するときに、配線層400が有する配線404とビア421の間に位置ずれが生じることがある。この位置ずれの量によっては、ビア421の底部に、エアギャップ402の上部と繋がった開口領域424が形成される。開口領域424が形成された場合、図14(b)に示すように、ビア421及び配線溝422に拡散防止膜430及びメッキシード膜432を形成するときに、開口領域424及びその周囲において拡散防止膜430及びメッキシード膜432が形成されず、これによって、配線434にボイド426が形成されてしまう。このため、配線404とビア421の間に位置ずれが生じても、ビア421の底部にエアギャップ402と繋がった領域が形成されないようにする必要がある。

【課題を解決するための手段】

【0008】

本発明によれば、第1絶縁層と、

前記第1絶縁層に埋め込まれ、上面が前記第1絶縁層の上面より高い配線と、

前記配線と前記第1絶縁層の間に位置するエアギャップと、

少なくとも前記第1絶縁層上及び前記エアギャップ上に形成された第2絶縁層と、

少なくとも前記第2絶縁層上に形成されたエッチングストッパー膜と、

前記エッチングストッパー膜上に形成された第3絶縁層と、

少なくとも前記第3絶縁層に埋め込まれ、前記配線に接続するビアと、

を備える半導体装置が提供される。

【0009】

第3絶縁層にビアを形成するとき、第3絶縁層をエッチングして接続孔を形成した後、接続孔の底面に位置するエッチングストッパー膜をエッチングする。本発明では、配線の上面は第1絶縁層の上面より高い。このため、配線の上面はエアギャップの上端より高くなり、エッチングストッパー膜とエアギャップは厚さ方向に離間している。そして、エッチングストッパー膜とエアギャップの間には第2絶縁層が位置する。このため、第3絶縁層にビアとなる接続孔を形成するときにビアと配線の間に位置ずれが生じ、平面視において接続孔とエアギャップが重なっても、接続孔の底面に位置するエッチングストッパー膜を除去するときには第2絶縁層がエッチングストッパーとして機能する。従って、エアギャップと接続孔が繋がることを抑制できる。

【0010】

本発明によれば、第1絶縁層を形成する工程と、

前記第1絶縁層に溝を形成する工程と、

前記溝に埋め込まれた配線を形成する工程と、

前記第1絶縁層と前記配線の間にスペースを形成し、かつ前記配線の上面を前記第1絶縁層の上面より高くする工程と、

前記スペースにエアギャップを形成し、かつ少なくとも前記第1絶縁層上及び前記配線上に第2絶縁層を形成する工程と、

少なくとも前記第2絶縁層上にエッチングストッパー膜を形成する工程と、

前記エッチングストッパー膜上に第3絶縁層を形成する工程と、

少なくとも前記第3絶縁層に、前記配線上に位置するビアを埋め込む工程と、

を備える半導体装置の製造方法が提供される。

【発明の効果】

【0011】

本発明によれば、第3絶縁層にビアとなる接続孔を形成するときにビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できる。

【図面の簡単な説明】

【0012】

【図1】第1の実施形態に係る半導体装置の構成を示す断面図である。

【図2】図1に示した半導体装置の製造方法を示す断面図である。

【図3】図2の次の工程を示す断面図である。

【図4】図3の次の工程を示す断面図である。

【図5】図4の次の工程を示す断面図である。

【図6】図5の次の工程を示す断面図である。

【図7】第2の実施形態に係る半導体装置の構成を示す断面図である。

【図8】第3の実施形態に係る半導体装置の製造方法を示す断面図である。

【図9】図8の次の工程を示す断面図である。

【図10】図9の次の工程を示す断面図である。

【図11】第4の実施形態に係る半導体装置の製造方法を示す断面図である。

【図12】図11の次の工程を示す断面図である。

【図13】第5の実施形態に係る半導体装置の構成を示す断面図である。

【図14】接続孔とエアギャップが繋がったときの問題を説明するための断面図である。

【発明を実施するための形態】

【0013】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0014】

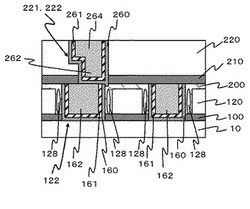

図1は、第1の実施形態に係る半導体装置の構成を示す断面図である。この半導体装置は、第1絶縁層120、配線162、エアギャップ128、第2絶縁層200、エッチングストッパー膜210、第3絶縁層220、及びビア262を備える。配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

【0015】

本図に示す例では、第2絶縁層200は、一部が配線162と第1絶縁層120の間に埋め込まれている。そしてエアギャップ128は、配線162と第1絶縁層120の間に位置する第2絶縁層200に形成されている。ただし図1に示す例と異なり、第2絶縁層200が配線162と第1絶縁層120の間に埋め込まれておらず、配線162と第1絶縁層120の間のスペースに第2絶縁層200が蓋をすることによりエアギャップ128が形成されていても良い。なお、図1に示す例においても、実際にはこのようになっている可能性がそれなりに高いと考えられる。

【0016】

配線162は、第1絶縁層120に形成された溝122に埋め込まれており、ビア262は、第3絶縁層220に形成された接続孔221に埋め込まれている。第3絶縁層220には、接続孔221の上に位置する溝222が形成されている。溝222には、ビア262に接続する配線264が埋め込まれている。本図に示す例において、ビア262と配線264は同一工程で形成されている。

【0017】

配線162、ビア262、及び配線264は、メッキ法により形成されている。詳細には、配線162は、メッキシード膜161を有している。そしてメッキシード膜161と溝122の間には、拡散防止膜160が形成されている。同様にビア262及び配線264は、メッキシード膜261を有している。そして溝222及び接続孔221とメッキシード膜261の間には、拡散防止膜260が形成されている。配線162、ビア262、及び配線264は、例えばCu膜により形成されている。拡散防止膜160,260は、例えばTaN及びTaをこの順に積層した積層膜により形成されている。

【0018】

また第1絶縁層120、第2絶縁層200、及び第3絶縁層220は、低誘電率膜により形成されている。例えば第1絶縁層120、第2絶縁層200、及び第3絶縁層220は、SiCOH膜、SiCOHN膜またはこれらのポーラス膜により形成されており、比誘電率が3.5以下、好ましくは2.7以下である。第1絶縁層120は、エッチングストッパー膜100上に形成されている。エッチングストッパー膜100は、下地絶縁膜10の上に形成されている。下地絶縁膜10は、例えば配線162の下に位置する配線層を形成する絶縁膜である。

【0019】

図2〜図6の各図は、図1に示した半導体装置の製造方法を示す断面図である。この半導体装置の製造方法では、まず第1絶縁層120を形成する。次いで第1絶縁層120に溝122を形成する。次いで、溝122に埋め込まれた配線162を形成する。次いで、第1絶縁層120と配線162の間にスペースを形成し、かつ配線162の上面を第1絶縁層120の上面より上に位置させる。次いで、上記したスペースに絶縁体を埋め込んでエアギャップ128を形成し、かつ第1絶縁層120上及び配線162上に第2絶縁層200を形成する。次いで、第2絶縁層200上にエッチングストッパー膜210を形成すし、さらにエッチングストッパー膜210上に第3絶縁層220を形成する。次いで、第3絶縁層220に、配線162上に位置するビア262を埋め込む。

以下、詳細に説明する。

【0020】

まず図2(a)に示すように、下地絶縁膜10上にエッチングストッパー膜100を形成する。エッチングストッパー膜100は、例えばSiCN膜又はSiCNH膜であるが、SiN膜、SiNH膜、又はSiCOH膜であってもよい。なお、このSiCOH膜の炭素濃度は、第1絶縁層120を形成するSiCOH膜の炭素濃度より高く、例えば20at%以上45at%以下である。次いで、エッチングストッパー膜100上に第1絶縁層120、及び酸化シリコン層140を形成する。次いで酸化シリコン層140上に反射防止膜150を形成する。次いで、反射防止膜150上にレジスト膜50を形成し、レジスト膜50を露光及び現像することにより、レジスト膜50に開口パターンを形成する。

【0021】

次いで図2(b)に示すように、レジスト膜50をマスクとして反射防止膜150、酸化シリコン層140、及び第1絶縁層120をドライエッチングする。エッチングガスには、フルオロカーボンガス(フロロカーボンガス)を用いる。これにより、第1絶縁層120には溝122が形成される。その後、レジスト膜50及び反射防止膜150を、酸素を含んだガスによるプラズマアッシングにより除去する。

【0022】

次いで図3(a)に示すように、溝122の底部に位置するエッチングストッパー膜100をドライエッチングにより除去する。この工程において、酸化シリコン層140の一部は除去される。次いで溝122を、レジスト膜の剥離液で洗浄する。この剥離液は、アミンベースである。

【0023】

図3(a)に示した状態において、溝122の側壁に位置する第1絶縁層120には、第1変質層124が形成される。第1変質層124は、第1絶縁層120の炭素濃度が低下した低炭素層である。

【0024】

次いで図3(b)に示すように、溝122に、拡散防止膜160及び配線162を埋め込む。この工程の詳細は以下の通りである。まず、溝122の底面及び側壁、並びに酸化シリコン層140上に拡散防止膜160を、例えばスパッタリング法により形成する。次いで、拡散防止膜160上に、メッキシード膜161を、例えばスパッタリング法により形成する。次いで、メッキシード膜161をシードとしてメッキを行い、導電膜を形成する。次いで、酸化シリコン層140上に位置する導電膜、メッキシード膜161、及び拡散防止膜160、並びに酸化シリコン層140を、CMP(Chemical Mechanical Polishing)法により除去する。この状態において、第1絶縁層120の表面は露出している。

【0025】

次いで図4(a)に示すように、第1絶縁層120の表面に第2変質層126を形成する。第2変質層126は、第1絶縁層120の炭素濃度が低下した低炭素層であり、例えば第1絶縁層120の表面を水素含有プラズマで処理することにより形成される。この場合、プラズマガスの少なくとも一部には、例えばアンモニアガスが用いられる。

【0026】

次いで図4(b)に示すように、第1変質層124及び第2変質層126をウェットエッチングにより除去する。エッチング液には、例えば希フッ酸液(DHF)が用いられる。この処理により、第1絶縁層120には、配線162と第1絶縁層120の間に位置するスペース125が形成される。また配線162の上面は、第1絶縁層120の上面より上に位置する。なお、第1変質層124及び第2変質層126をドライエッチングにより除去してもよい。

【0027】

次いで図5(a)に示すように、第1絶縁層120上、スペース125上、及び配線162上に、第2絶縁層200を形成する。第2絶縁層200は、例えばプラズマCVD法により形成される。この状態において、第2絶縁層200は、第1絶縁層120上に位置する部分の上面が、配線162の上面より高い。この工程により、スペース125にはエアギャップ128が形成される。また第2絶縁層200の一部は、スペース125に入り込む。ただし第2絶縁層200の形成条件によっては、第2絶縁層200がスペース125に入り込まない場合も考えられる。

【0028】

次いで図5(b)に示すように、第2絶縁層200の表層をCMP(Chemical Mechanical Polishing)法により研磨除去する。本図に示す例において、配線162上に位置する第2絶縁層200は除去されるため、配線162は第2絶縁層200から露出する。ただしエアギャップ128上には第2絶縁層200が残る。

【0029】

次いで図6(a)に示すように、第2絶縁層200上及び配線162上にエッチングストッパー膜210を形成する。エッチングストッパー膜210は、例えばSiCN膜であり、例えばプラズマCVD法により形成される。次いでエッチングストッパー膜210上に、第3絶縁層220を、例えばプラズマCVD法により形成する。第3絶縁層220は、例えばSiCOH膜である。

【0030】

次いで図6(b)に示すように、第3絶縁層220上に酸化シリコン層240を、例えばプラズマCVD法により形成する。次いで、例えばデュアルダマシン法により、第3絶縁層220に接続孔221及び溝222を形成する。接続孔221は、配線162上に位置する。

【0031】

接続孔221を形成するときのエッチングでは、まず、エッチングストッパー膜210をストッパーとして第3絶縁層220をエッチングする。これにより、まず第3絶縁層220に接続孔221が形成されるが、接続孔221の底部にはエッチングストッパー膜210が残っている。次いで、接続孔221の底部に位置するエッチングストッパー膜210をエッチングにより除去する。

【0032】

この工程において、図6(b)に示すように、接続孔221が配線162に対して位置ずれを起こし、これによって平面視において接続孔221がエアギャップ128と重なることがある。しかし本実施形態では、エアギャップ128とエッチングストッパー膜210の間には第2絶縁層200が位置している。このため、接続孔221の底面に位置するエッチングストッパー膜210を除去するときに、第2絶縁層200がエッチングストッパーとして機能し、エアギャップ128と接続孔221が繋がることを抑制する。

【0033】

その後、図1に示すように、接続孔221に拡散防止膜260及びビア262を埋め込むと共に、溝222に拡散防止膜260及び配線264を埋め込む。この工程の詳細は以下の通りである。まず、接続孔221及び溝222の底面及び側壁、並びに酸化シリコン層240(図6(b)に図示)上に、拡散防止膜260を、例えばスパッタリング法により形成する。次いで、拡散防止膜260上に、メッキシード膜261を、例えばスパッタリング法により形成する。次いで、メッキシード膜261をシードとしてメッキを行い、導電膜を形成する。次いで、酸化シリコン層240上に位置する導電膜、メッキシード膜261、拡散防止膜260、並びに酸化シリコン層240を、CMP法により除去する。

【0034】

次に、本実施形態による作用及び効果について説明する。本実施形態によれば、第2絶縁層200を形成する前に、配線162の上面を第1絶縁層120の上面より上に位置させている。このため、第2絶縁層200の表層をCMP法により研磨除去しても、第2絶縁層200のうちエアギャップ128上に位置する部分は残る。このため、接続孔221が配線162に対して位置ずれを起こし、平面視において接続孔221がエアギャップ128と重なっても、接続孔221の底面に位置するエッチングストッパー膜210を除去するときに、第2絶縁層200がエッチングストッパーとして機能し、エアギャップ128と接続孔221が繋がることを抑制する。

【0035】

このため、接続孔221の側壁及び底面において、拡散防止膜260及びメッキシード膜261が形成されない領域が発生することを抑制できる。従って、ビア262にボイドが形成されることを抑制できる。

【0036】

また本実施形態では、エアギャップ128を第2絶縁層200により形成しているため、エアギャップ128を形成するために他の膜を形成する必要がない。従って、半導体装置の製造工程数が増加することを抑制できる。

【0037】

また、第1絶縁層120の上面に第2変質層126を形成し、第2変質層126を除去することにより配線162の上面を第1絶縁層120の上面より高くしている。第2変質層126を除去する工程は、第1変質層124を除去してエアギャップ128を形成するためのスペース125を形成する工程と同一工程である。従って、半導体装置の製造工程数が増加することを抑制できる。

【0038】

また、第1絶縁層120を水素含有プラズマで処理することにより第2変質層126を形成している。このため、第2変質層126を形成するときに配線162の表面に変質層、例えば酸化層が形成されることを抑制できる。

【0039】

また、第1絶縁層120の上面を配線162の上面より低くすることにより形成されたスペース、すなわち配線162の上部の相互間のスペースには、誘電率が低い第2絶縁層200が配置される。このため、配線162において配線間容量が増大することを抑制できる。

【0040】

(第2の実施形態)

図7は、第2の実施形態に係る半導体装置の構成を示す断面図である。この半導体装置は、以下の点を除いて第1の実施形態と同様である。まず、下地絶縁膜10は、配線162に接続するビアが形成される絶縁膜である。このため、下地絶縁膜10と第1絶縁層120の間には、第1の実施形態で示したエッチングストッパー膜100が形成されていない。

【0041】

また、第3絶縁層220は、層間絶縁層224と、配線層絶縁層226により形成されている。層間絶縁層224にはビア262が埋め込まれ、配線層絶縁層226には配線264が埋め込まれている。そして配線264と配線層絶縁層226の間には、エアギャップ302が形成されており、配線層絶縁層226上には絶縁層300及びエッチングストッパー膜310が形成されている。エアギャップ302は、絶縁層300により形成されている。エアギャップ302、絶縁層300、及びエッチングストッパー膜310の形成方法は、エアギャップ128、第2絶縁層200、及びエッチングストッパー膜210の形成方法と同様である。また配線層絶縁層226の上面は配線264の上面より低くなっている。このようにするための方法は、第1絶縁層120の上面を配線162の上面より低くする方法と同様である。

【0042】

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。また、配線264と配線層絶縁層226の間にもエアギャップ302が形成されるため、配線264と同一層における配線間容量を小さくすることができる。

【0043】

(第3の実施形態)

図8〜図10の各図は、第3の実施形態に係る半導体装置の製造方法を示す断面図である。この製造方法により製造される半導体装置は、図10に示すように、配線162上に金属キャップ膜164を備えている点を除いて、第1の実施形態に係る半導体装置と同様の構成である。金属キャップ膜164は、例えばCoWP膜であるが、CoWB又はNi系メッキ膜などの他の膜であってもよい。

【0044】

まず図8(a)に示すように、下地絶縁膜10上に、エッチングストッパー膜100、第1絶縁層120、溝122、第1変質層124、拡散防止膜160、メッキシード膜161、及び配線162を形成する。これらの形成工程は、第1の実施形態と同様である。

【0045】

次いで図8(b)に示すように、無電解めっき法により、配線162上に選択的に金属キャップ膜164を形成する。この工程において、第1絶縁層120上にも選択不良の堆積物165が形成される。なお金属キャップ膜164は、選択CVD法により形成されても良い。この場合、金属キャップ膜164は、W又はCoにより形成されてもよいし、Si、Ag、Mg、Be、Zn、Pd、Cd、Au、Hg、Pt、Zr、Ti、Sn、Ni、及びFeからなる群から選ばれた少なくとも一つにより形成されてもよい。

【0046】

次いで図9(a)に示すように、第1絶縁層120の表層に第2変質層126を形成する。第2変質層126の形成方法は、第1の実施形態と同様である。

【0047】

次いで図9(b)に示すように、第1変質層124及び第2変質層126を除去する。これらの除去方法は、第1の実施形態と同様である。この工程において、選択不良の堆積物165は、第2変質層126と共に除去される。

【0048】

次いで図10に示すように、第2絶縁層200、エッチングストッパー膜210、第3絶縁層220、接続孔221、溝222、拡散防止膜260、メッキシード膜261、ビア262、及び配線264を形成する。これらの形成方法は、第1の実施形態と同様である。ただし本実施形態において、拡散防止膜260は、TaN及びTaをこの順に積層した積層膜ではなくSiCH膜などの他の膜により形成されていても良い。

【0049】

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。また、配線162の上に金属キャップ膜164を形成した後に第2絶縁層200を形成しているため、第2絶縁層200のうちエアギャップ128上に位置する部分の厚さは、第1の実施形態と比較して厚くなる。従って、平面視において接続孔221がエアギャップ128と重なっても、接続孔221の底面に位置するエッチングストッパー膜210を除去するときに、エアギャップ128と接続孔221が繋がることをさらに抑制できる。

【0050】

また、配線162上に金属キャップ膜164を形成したため、配線162のエレクトロマイグレーション耐性が向上する。また、金属キャップ膜164が配線162の拡散防止膜としても機能するため、拡散防止膜260として比誘電率が低いSiCH膜を用いることができる。

【0051】

なお本実施形態において、各層の構造を第2の実施形態と同様にしてもよい。

【0052】

(第4の実施形態)

図11及び図12の各図は、第4の実施形態に係る半導体装置の製造方法を示す断面図である。この半導体装置の製造方法は、第2絶縁層200の表層をCMP法により除去するときに、配線162上に第2絶縁層200を残す点を除いて、第1の実施形態と同様である。すなわち本実施形態によって製造される半導体装置は、配線162の上面が第2絶縁層200に被覆されており、ビア262の下部が第2絶縁層200に埋め込まれている。以下、詳細に説明する。

【0053】

まず図11(a)に示すように、下地絶縁膜10上に、エッチングストッパー膜100、第1絶縁層120、溝122、拡散防止膜160、メッキシード膜161、配線162、スペース125、エアギャップ128、及び第2絶縁層200を形成する。これらの形成工程は、第1の実施形態と同様である。また本図に示す状態において、配線162の上面は第1絶縁層120の上面より高くなっている。このようにする方法も、第1の実施形態と同様である。

【0054】

次いで図11(b)に示すように、第2絶縁層200の表層をCMP法により研磨除去する。このとき、配線162上に第2絶縁層200を残す。配線162上に位置する第2絶縁層200の厚さは、例えば5nm以上50nm以下であり、第3絶縁層220より薄い。

【0055】

次いで図12に示すように、エッチングストッパー膜210、第3絶縁層220、接続孔221、溝222、拡散防止膜260、メッキシード膜261、ビア262、及び配線264を形成する。これらの形成方法は、接続孔221を形成する工程において、エッチングストッパー膜210をエッチングした後に、さらに第2絶縁層200をエッチングして接続孔221の底部を第2絶縁層200に位置させる点を除いて、第1の実施形態と同様である。

【0056】

本実施形態においても、接続孔221の底面に位置するエッチングストッパー膜210を除去するときに、第2絶縁層200がエッチングストッパーとして機能する。そして接続孔221の底面に配線162を露出させるためには、最後にエッチングストッパー膜210を除去する必要がある。配線162の上面は第1絶縁層120の上面より高い。このため、第2絶縁層200のうちエアギャップ128上に位置する部分は、配線162上に位置する部分より厚い。このため、平面視において接続孔221がエアギャップ128と重なっても、第2絶縁層200をエッチングして接続孔221の底面に配線162を露出させるときに、エアギャップ128と接続孔221が繋がることを抑制できる。

【0057】

また、配線162上に第2絶縁層200を残しているため、第2絶縁層200の表層をCMPにより除去する工程において、配線162と第2絶縁層200の選択比を考慮しなくて良くなる。

【0058】

また、配線162は、上面も含めて第2絶縁層200で囲まれている。このため、配線162の配線間容量をさらに低くすることができる。

【0059】

なお本実施形態において、各層の構造を第2の実施形態と同様にしてもよい。

【0060】

(第5の実施形態)

図13は、第5の実施形態に係る半導体装置の構成を示す断面図である。この半導体装置は、配線162上に金属キャップ膜164を有する点を除いて、第4の実施形態によって製造される半導体装置と同様の構成である。第2絶縁層200は、金属キャップ膜164上に位置する部分に残されている。また、金属キャップ膜164の形成方法は、第3の実施形態と同様である。

【0061】

本実施形態によっても、第4の実施形態と同様の効果を得ることができる。また、第2絶縁層200のうちエアギャップ128上に位置する部分の厚さは、第4の実施形態と比較して、金属キャップ膜164の厚さ分、配線162上に位置する部分よりさらに厚くなる。従って、平面視において接続孔221がエアギャップ128と重なっても、接続孔221の底面に位置する第2絶縁層200を除去するときに、エアギャップ128と接続孔221が繋がることをさらに抑制できる。

【0062】

また、配線162は拡散防止膜160及び金属キャップ膜164によって囲まれているため、配線162を形成している金属が第2絶縁層200内に拡散することを抑制できる。

【0063】

なお本実施形態において、各層の構造を第2の実施形態と同様にしてもよい。

【0064】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【符号の説明】

【0065】

10 下地絶縁膜

50 レジスト膜

100 エッチングストッパー膜

120 第1絶縁層

122 溝

124 第1変質層

125 スペース

126 第2変質層

128 エアギャップ

140 酸化シリコン層

150 反射防止膜

160 拡散防止膜

161 メッキシード膜

162 配線

164 金属キャップ膜

165 堆積物

200 第2絶縁層

210 エッチングストッパー膜

220 第3絶縁層

221 接続孔

222 溝

224 層間絶縁層

226 配線層絶縁層

240 酸化シリコン層

260 拡散防止膜

261 メッキシード膜

262 ビア

264 配線

300 絶縁層

302 エアギャップ

310 エッチングストッパー膜

400 配線層

402 エアギャップ

404 配線

420 配線層

421 ビア

422 配線溝

424 開口領域

426 ボイド

426 ボイド

430 拡散防止膜

434 配線

【技術分野】

【0001】

本発明は、配線と配線が埋め込まれた絶縁膜の間にエアギャップを有する半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の微細化に伴い、配線の間隔が狭くなっている。配線の間隔が狭くなると配線間の容量が増大し、これによって信号の遅延が生じてしまう。配線間の容量を小さくする技術の一つに、配線と配線が埋め込まれた絶縁膜の間にエアギャップを設けることがある。

【0003】

特許文献1には、配線を埋め込むための溝を絶縁膜に形成するときに、溝の側壁に劣化層を形成し、この劣化層を配線形成後に除去することにより、配線と絶縁膜の間にエアギャップを形成する、と記載されている。

【0004】

特許文献2には、配線を埋め込むための溝の底面及び側面に触媒特性膜を形成し、この触媒特性膜上に配線となるCu膜を形成し、その後、溝の側面に位置する触媒特性膜を除去することにより、配線と絶縁膜の間にエアギャップを形成する、と記載されている。

【0005】

また特許文献3には、エアギャップを形成する技術ではないが、配線上に金属キャップを形成した後、配線が埋め込まれている絶縁膜の表面を損傷し、この損傷した表面を除去する、と記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】米国特許出願公開第2008/0076258号明細書

【特許文献2】特開2008−300652号公報

【特許文献3】特開2008−205458号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

図14(a)に示すように、エアギャップ402を有する配線層400の上の配線層420にビア421及び配線溝422を形成するときに、配線層400が有する配線404とビア421の間に位置ずれが生じることがある。この位置ずれの量によっては、ビア421の底部に、エアギャップ402の上部と繋がった開口領域424が形成される。開口領域424が形成された場合、図14(b)に示すように、ビア421及び配線溝422に拡散防止膜430及びメッキシード膜432を形成するときに、開口領域424及びその周囲において拡散防止膜430及びメッキシード膜432が形成されず、これによって、配線434にボイド426が形成されてしまう。このため、配線404とビア421の間に位置ずれが生じても、ビア421の底部にエアギャップ402と繋がった領域が形成されないようにする必要がある。

【課題を解決するための手段】

【0008】

本発明によれば、第1絶縁層と、

前記第1絶縁層に埋め込まれ、上面が前記第1絶縁層の上面より高い配線と、

前記配線と前記第1絶縁層の間に位置するエアギャップと、

少なくとも前記第1絶縁層上及び前記エアギャップ上に形成された第2絶縁層と、

少なくとも前記第2絶縁層上に形成されたエッチングストッパー膜と、

前記エッチングストッパー膜上に形成された第3絶縁層と、

少なくとも前記第3絶縁層に埋め込まれ、前記配線に接続するビアと、

を備える半導体装置が提供される。

【0009】

第3絶縁層にビアを形成するとき、第3絶縁層をエッチングして接続孔を形成した後、接続孔の底面に位置するエッチングストッパー膜をエッチングする。本発明では、配線の上面は第1絶縁層の上面より高い。このため、配線の上面はエアギャップの上端より高くなり、エッチングストッパー膜とエアギャップは厚さ方向に離間している。そして、エッチングストッパー膜とエアギャップの間には第2絶縁層が位置する。このため、第3絶縁層にビアとなる接続孔を形成するときにビアと配線の間に位置ずれが生じ、平面視において接続孔とエアギャップが重なっても、接続孔の底面に位置するエッチングストッパー膜を除去するときには第2絶縁層がエッチングストッパーとして機能する。従って、エアギャップと接続孔が繋がることを抑制できる。

【0010】

本発明によれば、第1絶縁層を形成する工程と、

前記第1絶縁層に溝を形成する工程と、

前記溝に埋め込まれた配線を形成する工程と、

前記第1絶縁層と前記配線の間にスペースを形成し、かつ前記配線の上面を前記第1絶縁層の上面より高くする工程と、

前記スペースにエアギャップを形成し、かつ少なくとも前記第1絶縁層上及び前記配線上に第2絶縁層を形成する工程と、

少なくとも前記第2絶縁層上にエッチングストッパー膜を形成する工程と、

前記エッチングストッパー膜上に第3絶縁層を形成する工程と、

少なくとも前記第3絶縁層に、前記配線上に位置するビアを埋め込む工程と、

を備える半導体装置の製造方法が提供される。

【発明の効果】

【0011】

本発明によれば、第3絶縁層にビアとなる接続孔を形成するときにビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できる。

【図面の簡単な説明】

【0012】

【図1】第1の実施形態に係る半導体装置の構成を示す断面図である。

【図2】図1に示した半導体装置の製造方法を示す断面図である。

【図3】図2の次の工程を示す断面図である。

【図4】図3の次の工程を示す断面図である。

【図5】図4の次の工程を示す断面図である。

【図6】図5の次の工程を示す断面図である。

【図7】第2の実施形態に係る半導体装置の構成を示す断面図である。

【図8】第3の実施形態に係る半導体装置の製造方法を示す断面図である。

【図9】図8の次の工程を示す断面図である。

【図10】図9の次の工程を示す断面図である。

【図11】第4の実施形態に係る半導体装置の製造方法を示す断面図である。

【図12】図11の次の工程を示す断面図である。

【図13】第5の実施形態に係る半導体装置の構成を示す断面図である。

【図14】接続孔とエアギャップが繋がったときの問題を説明するための断面図である。

【発明を実施するための形態】

【0013】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0014】

図1は、第1の実施形態に係る半導体装置の構成を示す断面図である。この半導体装置は、第1絶縁層120、配線162、エアギャップ128、第2絶縁層200、エッチングストッパー膜210、第3絶縁層220、及びビア262を備える。配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

【0015】

本図に示す例では、第2絶縁層200は、一部が配線162と第1絶縁層120の間に埋め込まれている。そしてエアギャップ128は、配線162と第1絶縁層120の間に位置する第2絶縁層200に形成されている。ただし図1に示す例と異なり、第2絶縁層200が配線162と第1絶縁層120の間に埋め込まれておらず、配線162と第1絶縁層120の間のスペースに第2絶縁層200が蓋をすることによりエアギャップ128が形成されていても良い。なお、図1に示す例においても、実際にはこのようになっている可能性がそれなりに高いと考えられる。

【0016】

配線162は、第1絶縁層120に形成された溝122に埋め込まれており、ビア262は、第3絶縁層220に形成された接続孔221に埋め込まれている。第3絶縁層220には、接続孔221の上に位置する溝222が形成されている。溝222には、ビア262に接続する配線264が埋め込まれている。本図に示す例において、ビア262と配線264は同一工程で形成されている。

【0017】

配線162、ビア262、及び配線264は、メッキ法により形成されている。詳細には、配線162は、メッキシード膜161を有している。そしてメッキシード膜161と溝122の間には、拡散防止膜160が形成されている。同様にビア262及び配線264は、メッキシード膜261を有している。そして溝222及び接続孔221とメッキシード膜261の間には、拡散防止膜260が形成されている。配線162、ビア262、及び配線264は、例えばCu膜により形成されている。拡散防止膜160,260は、例えばTaN及びTaをこの順に積層した積層膜により形成されている。

【0018】

また第1絶縁層120、第2絶縁層200、及び第3絶縁層220は、低誘電率膜により形成されている。例えば第1絶縁層120、第2絶縁層200、及び第3絶縁層220は、SiCOH膜、SiCOHN膜またはこれらのポーラス膜により形成されており、比誘電率が3.5以下、好ましくは2.7以下である。第1絶縁層120は、エッチングストッパー膜100上に形成されている。エッチングストッパー膜100は、下地絶縁膜10の上に形成されている。下地絶縁膜10は、例えば配線162の下に位置する配線層を形成する絶縁膜である。

【0019】

図2〜図6の各図は、図1に示した半導体装置の製造方法を示す断面図である。この半導体装置の製造方法では、まず第1絶縁層120を形成する。次いで第1絶縁層120に溝122を形成する。次いで、溝122に埋め込まれた配線162を形成する。次いで、第1絶縁層120と配線162の間にスペースを形成し、かつ配線162の上面を第1絶縁層120の上面より上に位置させる。次いで、上記したスペースに絶縁体を埋め込んでエアギャップ128を形成し、かつ第1絶縁層120上及び配線162上に第2絶縁層200を形成する。次いで、第2絶縁層200上にエッチングストッパー膜210を形成すし、さらにエッチングストッパー膜210上に第3絶縁層220を形成する。次いで、第3絶縁層220に、配線162上に位置するビア262を埋め込む。

以下、詳細に説明する。

【0020】

まず図2(a)に示すように、下地絶縁膜10上にエッチングストッパー膜100を形成する。エッチングストッパー膜100は、例えばSiCN膜又はSiCNH膜であるが、SiN膜、SiNH膜、又はSiCOH膜であってもよい。なお、このSiCOH膜の炭素濃度は、第1絶縁層120を形成するSiCOH膜の炭素濃度より高く、例えば20at%以上45at%以下である。次いで、エッチングストッパー膜100上に第1絶縁層120、及び酸化シリコン層140を形成する。次いで酸化シリコン層140上に反射防止膜150を形成する。次いで、反射防止膜150上にレジスト膜50を形成し、レジスト膜50を露光及び現像することにより、レジスト膜50に開口パターンを形成する。

【0021】

次いで図2(b)に示すように、レジスト膜50をマスクとして反射防止膜150、酸化シリコン層140、及び第1絶縁層120をドライエッチングする。エッチングガスには、フルオロカーボンガス(フロロカーボンガス)を用いる。これにより、第1絶縁層120には溝122が形成される。その後、レジスト膜50及び反射防止膜150を、酸素を含んだガスによるプラズマアッシングにより除去する。

【0022】

次いで図3(a)に示すように、溝122の底部に位置するエッチングストッパー膜100をドライエッチングにより除去する。この工程において、酸化シリコン層140の一部は除去される。次いで溝122を、レジスト膜の剥離液で洗浄する。この剥離液は、アミンベースである。

【0023】

図3(a)に示した状態において、溝122の側壁に位置する第1絶縁層120には、第1変質層124が形成される。第1変質層124は、第1絶縁層120の炭素濃度が低下した低炭素層である。

【0024】

次いで図3(b)に示すように、溝122に、拡散防止膜160及び配線162を埋め込む。この工程の詳細は以下の通りである。まず、溝122の底面及び側壁、並びに酸化シリコン層140上に拡散防止膜160を、例えばスパッタリング法により形成する。次いで、拡散防止膜160上に、メッキシード膜161を、例えばスパッタリング法により形成する。次いで、メッキシード膜161をシードとしてメッキを行い、導電膜を形成する。次いで、酸化シリコン層140上に位置する導電膜、メッキシード膜161、及び拡散防止膜160、並びに酸化シリコン層140を、CMP(Chemical Mechanical Polishing)法により除去する。この状態において、第1絶縁層120の表面は露出している。

【0025】

次いで図4(a)に示すように、第1絶縁層120の表面に第2変質層126を形成する。第2変質層126は、第1絶縁層120の炭素濃度が低下した低炭素層であり、例えば第1絶縁層120の表面を水素含有プラズマで処理することにより形成される。この場合、プラズマガスの少なくとも一部には、例えばアンモニアガスが用いられる。

【0026】

次いで図4(b)に示すように、第1変質層124及び第2変質層126をウェットエッチングにより除去する。エッチング液には、例えば希フッ酸液(DHF)が用いられる。この処理により、第1絶縁層120には、配線162と第1絶縁層120の間に位置するスペース125が形成される。また配線162の上面は、第1絶縁層120の上面より上に位置する。なお、第1変質層124及び第2変質層126をドライエッチングにより除去してもよい。

【0027】

次いで図5(a)に示すように、第1絶縁層120上、スペース125上、及び配線162上に、第2絶縁層200を形成する。第2絶縁層200は、例えばプラズマCVD法により形成される。この状態において、第2絶縁層200は、第1絶縁層120上に位置する部分の上面が、配線162の上面より高い。この工程により、スペース125にはエアギャップ128が形成される。また第2絶縁層200の一部は、スペース125に入り込む。ただし第2絶縁層200の形成条件によっては、第2絶縁層200がスペース125に入り込まない場合も考えられる。

【0028】

次いで図5(b)に示すように、第2絶縁層200の表層をCMP(Chemical Mechanical Polishing)法により研磨除去する。本図に示す例において、配線162上に位置する第2絶縁層200は除去されるため、配線162は第2絶縁層200から露出する。ただしエアギャップ128上には第2絶縁層200が残る。

【0029】

次いで図6(a)に示すように、第2絶縁層200上及び配線162上にエッチングストッパー膜210を形成する。エッチングストッパー膜210は、例えばSiCN膜であり、例えばプラズマCVD法により形成される。次いでエッチングストッパー膜210上に、第3絶縁層220を、例えばプラズマCVD法により形成する。第3絶縁層220は、例えばSiCOH膜である。

【0030】

次いで図6(b)に示すように、第3絶縁層220上に酸化シリコン層240を、例えばプラズマCVD法により形成する。次いで、例えばデュアルダマシン法により、第3絶縁層220に接続孔221及び溝222を形成する。接続孔221は、配線162上に位置する。

【0031】

接続孔221を形成するときのエッチングでは、まず、エッチングストッパー膜210をストッパーとして第3絶縁層220をエッチングする。これにより、まず第3絶縁層220に接続孔221が形成されるが、接続孔221の底部にはエッチングストッパー膜210が残っている。次いで、接続孔221の底部に位置するエッチングストッパー膜210をエッチングにより除去する。

【0032】

この工程において、図6(b)に示すように、接続孔221が配線162に対して位置ずれを起こし、これによって平面視において接続孔221がエアギャップ128と重なることがある。しかし本実施形態では、エアギャップ128とエッチングストッパー膜210の間には第2絶縁層200が位置している。このため、接続孔221の底面に位置するエッチングストッパー膜210を除去するときに、第2絶縁層200がエッチングストッパーとして機能し、エアギャップ128と接続孔221が繋がることを抑制する。

【0033】

その後、図1に示すように、接続孔221に拡散防止膜260及びビア262を埋め込むと共に、溝222に拡散防止膜260及び配線264を埋め込む。この工程の詳細は以下の通りである。まず、接続孔221及び溝222の底面及び側壁、並びに酸化シリコン層240(図6(b)に図示)上に、拡散防止膜260を、例えばスパッタリング法により形成する。次いで、拡散防止膜260上に、メッキシード膜261を、例えばスパッタリング法により形成する。次いで、メッキシード膜261をシードとしてメッキを行い、導電膜を形成する。次いで、酸化シリコン層240上に位置する導電膜、メッキシード膜261、拡散防止膜260、並びに酸化シリコン層240を、CMP法により除去する。

【0034】

次に、本実施形態による作用及び効果について説明する。本実施形態によれば、第2絶縁層200を形成する前に、配線162の上面を第1絶縁層120の上面より上に位置させている。このため、第2絶縁層200の表層をCMP法により研磨除去しても、第2絶縁層200のうちエアギャップ128上に位置する部分は残る。このため、接続孔221が配線162に対して位置ずれを起こし、平面視において接続孔221がエアギャップ128と重なっても、接続孔221の底面に位置するエッチングストッパー膜210を除去するときに、第2絶縁層200がエッチングストッパーとして機能し、エアギャップ128と接続孔221が繋がることを抑制する。

【0035】

このため、接続孔221の側壁及び底面において、拡散防止膜260及びメッキシード膜261が形成されない領域が発生することを抑制できる。従って、ビア262にボイドが形成されることを抑制できる。

【0036】

また本実施形態では、エアギャップ128を第2絶縁層200により形成しているため、エアギャップ128を形成するために他の膜を形成する必要がない。従って、半導体装置の製造工程数が増加することを抑制できる。

【0037】

また、第1絶縁層120の上面に第2変質層126を形成し、第2変質層126を除去することにより配線162の上面を第1絶縁層120の上面より高くしている。第2変質層126を除去する工程は、第1変質層124を除去してエアギャップ128を形成するためのスペース125を形成する工程と同一工程である。従って、半導体装置の製造工程数が増加することを抑制できる。

【0038】

また、第1絶縁層120を水素含有プラズマで処理することにより第2変質層126を形成している。このため、第2変質層126を形成するときに配線162の表面に変質層、例えば酸化層が形成されることを抑制できる。

【0039】

また、第1絶縁層120の上面を配線162の上面より低くすることにより形成されたスペース、すなわち配線162の上部の相互間のスペースには、誘電率が低い第2絶縁層200が配置される。このため、配線162において配線間容量が増大することを抑制できる。

【0040】

(第2の実施形態)

図7は、第2の実施形態に係る半導体装置の構成を示す断面図である。この半導体装置は、以下の点を除いて第1の実施形態と同様である。まず、下地絶縁膜10は、配線162に接続するビアが形成される絶縁膜である。このため、下地絶縁膜10と第1絶縁層120の間には、第1の実施形態で示したエッチングストッパー膜100が形成されていない。

【0041】

また、第3絶縁層220は、層間絶縁層224と、配線層絶縁層226により形成されている。層間絶縁層224にはビア262が埋め込まれ、配線層絶縁層226には配線264が埋め込まれている。そして配線264と配線層絶縁層226の間には、エアギャップ302が形成されており、配線層絶縁層226上には絶縁層300及びエッチングストッパー膜310が形成されている。エアギャップ302は、絶縁層300により形成されている。エアギャップ302、絶縁層300、及びエッチングストッパー膜310の形成方法は、エアギャップ128、第2絶縁層200、及びエッチングストッパー膜210の形成方法と同様である。また配線層絶縁層226の上面は配線264の上面より低くなっている。このようにするための方法は、第1絶縁層120の上面を配線162の上面より低くする方法と同様である。

【0042】

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。また、配線264と配線層絶縁層226の間にもエアギャップ302が形成されるため、配線264と同一層における配線間容量を小さくすることができる。

【0043】

(第3の実施形態)

図8〜図10の各図は、第3の実施形態に係る半導体装置の製造方法を示す断面図である。この製造方法により製造される半導体装置は、図10に示すように、配線162上に金属キャップ膜164を備えている点を除いて、第1の実施形態に係る半導体装置と同様の構成である。金属キャップ膜164は、例えばCoWP膜であるが、CoWB又はNi系メッキ膜などの他の膜であってもよい。

【0044】

まず図8(a)に示すように、下地絶縁膜10上に、エッチングストッパー膜100、第1絶縁層120、溝122、第1変質層124、拡散防止膜160、メッキシード膜161、及び配線162を形成する。これらの形成工程は、第1の実施形態と同様である。

【0045】

次いで図8(b)に示すように、無電解めっき法により、配線162上に選択的に金属キャップ膜164を形成する。この工程において、第1絶縁層120上にも選択不良の堆積物165が形成される。なお金属キャップ膜164は、選択CVD法により形成されても良い。この場合、金属キャップ膜164は、W又はCoにより形成されてもよいし、Si、Ag、Mg、Be、Zn、Pd、Cd、Au、Hg、Pt、Zr、Ti、Sn、Ni、及びFeからなる群から選ばれた少なくとも一つにより形成されてもよい。

【0046】

次いで図9(a)に示すように、第1絶縁層120の表層に第2変質層126を形成する。第2変質層126の形成方法は、第1の実施形態と同様である。

【0047】

次いで図9(b)に示すように、第1変質層124及び第2変質層126を除去する。これらの除去方法は、第1の実施形態と同様である。この工程において、選択不良の堆積物165は、第2変質層126と共に除去される。

【0048】

次いで図10に示すように、第2絶縁層200、エッチングストッパー膜210、第3絶縁層220、接続孔221、溝222、拡散防止膜260、メッキシード膜261、ビア262、及び配線264を形成する。これらの形成方法は、第1の実施形態と同様である。ただし本実施形態において、拡散防止膜260は、TaN及びTaをこの順に積層した積層膜ではなくSiCH膜などの他の膜により形成されていても良い。

【0049】

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。また、配線162の上に金属キャップ膜164を形成した後に第2絶縁層200を形成しているため、第2絶縁層200のうちエアギャップ128上に位置する部分の厚さは、第1の実施形態と比較して厚くなる。従って、平面視において接続孔221がエアギャップ128と重なっても、接続孔221の底面に位置するエッチングストッパー膜210を除去するときに、エアギャップ128と接続孔221が繋がることをさらに抑制できる。

【0050】

また、配線162上に金属キャップ膜164を形成したため、配線162のエレクトロマイグレーション耐性が向上する。また、金属キャップ膜164が配線162の拡散防止膜としても機能するため、拡散防止膜260として比誘電率が低いSiCH膜を用いることができる。

【0051】

なお本実施形態において、各層の構造を第2の実施形態と同様にしてもよい。

【0052】

(第4の実施形態)

図11及び図12の各図は、第4の実施形態に係る半導体装置の製造方法を示す断面図である。この半導体装置の製造方法は、第2絶縁層200の表層をCMP法により除去するときに、配線162上に第2絶縁層200を残す点を除いて、第1の実施形態と同様である。すなわち本実施形態によって製造される半導体装置は、配線162の上面が第2絶縁層200に被覆されており、ビア262の下部が第2絶縁層200に埋め込まれている。以下、詳細に説明する。

【0053】

まず図11(a)に示すように、下地絶縁膜10上に、エッチングストッパー膜100、第1絶縁層120、溝122、拡散防止膜160、メッキシード膜161、配線162、スペース125、エアギャップ128、及び第2絶縁層200を形成する。これらの形成工程は、第1の実施形態と同様である。また本図に示す状態において、配線162の上面は第1絶縁層120の上面より高くなっている。このようにする方法も、第1の実施形態と同様である。

【0054】

次いで図11(b)に示すように、第2絶縁層200の表層をCMP法により研磨除去する。このとき、配線162上に第2絶縁層200を残す。配線162上に位置する第2絶縁層200の厚さは、例えば5nm以上50nm以下であり、第3絶縁層220より薄い。

【0055】

次いで図12に示すように、エッチングストッパー膜210、第3絶縁層220、接続孔221、溝222、拡散防止膜260、メッキシード膜261、ビア262、及び配線264を形成する。これらの形成方法は、接続孔221を形成する工程において、エッチングストッパー膜210をエッチングした後に、さらに第2絶縁層200をエッチングして接続孔221の底部を第2絶縁層200に位置させる点を除いて、第1の実施形態と同様である。

【0056】

本実施形態においても、接続孔221の底面に位置するエッチングストッパー膜210を除去するときに、第2絶縁層200がエッチングストッパーとして機能する。そして接続孔221の底面に配線162を露出させるためには、最後にエッチングストッパー膜210を除去する必要がある。配線162の上面は第1絶縁層120の上面より高い。このため、第2絶縁層200のうちエアギャップ128上に位置する部分は、配線162上に位置する部分より厚い。このため、平面視において接続孔221がエアギャップ128と重なっても、第2絶縁層200をエッチングして接続孔221の底面に配線162を露出させるときに、エアギャップ128と接続孔221が繋がることを抑制できる。

【0057】

また、配線162上に第2絶縁層200を残しているため、第2絶縁層200の表層をCMPにより除去する工程において、配線162と第2絶縁層200の選択比を考慮しなくて良くなる。

【0058】

また、配線162は、上面も含めて第2絶縁層200で囲まれている。このため、配線162の配線間容量をさらに低くすることができる。

【0059】

なお本実施形態において、各層の構造を第2の実施形態と同様にしてもよい。

【0060】

(第5の実施形態)

図13は、第5の実施形態に係る半導体装置の構成を示す断面図である。この半導体装置は、配線162上に金属キャップ膜164を有する点を除いて、第4の実施形態によって製造される半導体装置と同様の構成である。第2絶縁層200は、金属キャップ膜164上に位置する部分に残されている。また、金属キャップ膜164の形成方法は、第3の実施形態と同様である。

【0061】

本実施形態によっても、第4の実施形態と同様の効果を得ることができる。また、第2絶縁層200のうちエアギャップ128上に位置する部分の厚さは、第4の実施形態と比較して、金属キャップ膜164の厚さ分、配線162上に位置する部分よりさらに厚くなる。従って、平面視において接続孔221がエアギャップ128と重なっても、接続孔221の底面に位置する第2絶縁層200を除去するときに、エアギャップ128と接続孔221が繋がることをさらに抑制できる。

【0062】

また、配線162は拡散防止膜160及び金属キャップ膜164によって囲まれているため、配線162を形成している金属が第2絶縁層200内に拡散することを抑制できる。

【0063】

なお本実施形態において、各層の構造を第2の実施形態と同様にしてもよい。

【0064】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【符号の説明】

【0065】

10 下地絶縁膜

50 レジスト膜

100 エッチングストッパー膜

120 第1絶縁層

122 溝

124 第1変質層

125 スペース

126 第2変質層

128 エアギャップ

140 酸化シリコン層

150 反射防止膜

160 拡散防止膜

161 メッキシード膜

162 配線

164 金属キャップ膜

165 堆積物

200 第2絶縁層

210 エッチングストッパー膜

220 第3絶縁層

221 接続孔

222 溝

224 層間絶縁層

226 配線層絶縁層

240 酸化シリコン層

260 拡散防止膜

261 メッキシード膜

262 ビア

264 配線

300 絶縁層

302 エアギャップ

310 エッチングストッパー膜

400 配線層

402 エアギャップ

404 配線

420 配線層

421 ビア

422 配線溝

424 開口領域

426 ボイド

426 ボイド

430 拡散防止膜

434 配線

【特許請求の範囲】

【請求項1】

第1絶縁層と、

前記第1絶縁層に埋め込まれ、上面が前記第1絶縁層の上面より高い配線と、

前記配線と前記第1絶縁層の間に位置するエアギャップと、

少なくとも前記第1絶縁層上及び前記エアギャップ上に形成された第2絶縁層と、

少なくとも前記第2絶縁層上に形成されたエッチングストッパー膜と、

前記エッチングストッパー膜上に形成された第3絶縁層と、

少なくとも前記第3絶縁層に埋め込まれ、前記配線に接続するビアと、

を備える半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記エアギャップは、前記第2絶縁層により形成されている半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、

前記第2絶縁層は、比誘電率が3.5以下である半導体装置。

【請求項4】

請求項1〜3のいずれか一つに記載の半導体装置において、

前記配線は、上面が前記第2絶縁層に被覆されておらず、

前記エッチングストッパー膜は、前記配線上にも形成されている半導体装置。

【請求項5】

請求項1〜3のいずれか一つに記載の半導体装置において、

前記配線は、上面が前記第2絶縁層に被覆されており、

前記ビアは、下部が前記第2絶縁層に埋め込まれている半導体装置。

【請求項6】

請求項1〜5のいずれか一つに記載の半導体装置において、

前記配線上に位置する金属キャップ膜を備える半導体装置。

【請求項7】

請求項1〜6のいずれか一つに記載の半導体装置において、

前記ビアは、メッキ法により形成されている半導体装置。

【請求項8】

請求項1〜7のいずれか一つに記載の半導体装置において、

前記第1絶縁層は、SiCOH膜、SiCOHN膜、またはSiCOH膜若しくはSiCOHN膜のポーラス膜である半導体装置。

【請求項9】

第1絶縁層を形成する工程と、

前記第1絶縁層に溝を形成する工程と、

前記溝に埋め込まれた配線を形成する工程と、

前記第1絶縁層と前記配線の間にスペースを形成し、かつ前記配線の上面を前記第1絶縁層の上面より高くする工程と、

前記スペースにエアギャップを形成し、かつ少なくとも前記第1絶縁層上及び前記配線上に第2絶縁層を形成する工程と、

少なくとも前記第2絶縁層上にエッチングストッパー膜を形成する工程と、

前記エッチングストッパー膜上に第3絶縁層を形成する工程と、

少なくとも前記第3絶縁層に、前記配線上に位置するビアを埋め込む工程と、

を備える半導体装置の製造方法。

【請求項10】

請求項9に記載の半導体装置の製造方法において、

前記エアギャップ及び前記第2絶縁層を形成する工程において、前記第2絶縁層によって前記エアギャップを形成する半導体装置の製造方法。

【請求項11】

請求項10に記載の半導体装置の製造方法において、

前記エアギャップ及び前記第2絶縁層を形成する工程は、

前記スペース上、前記第1配線層上、及び前記配線上に前記第2絶縁層を成膜する工程と、

前記第2絶縁層の表層をCMP法により除去する工程と、

を備える半導体装置の製造方法。

【請求項12】

請求項11に記載の半導体装置の製造方法において、

前記第2絶縁層の表層をCMP法により除去する工程において、前記配線を前記第2絶縁層から露出させる半導体装置の製造方法。

【請求項13】

請求項11に記載の半導体装置の製造方法において、

前記第2絶縁層の表層をCMP法により除去する工程において、前記第2絶縁層を前記配線上に残す半導体装置の製造方法。

【請求項14】

請求項9〜13のいずれか一つに記載の半導体装置の製造方法において、

前記第2絶縁層は比誘電率が3.5以下である半導体装置の製造方法。

【請求項15】

請求項9〜14のいずれか一つに記載の半導体装置の製造方法において、

前記溝を形成する工程において、前記溝の側壁に前記第1絶縁層が変質した第1変質層を形成し、

前記配線を形成する工程と、前記スペースを形成して前記配線の上面を前記第1絶縁層の上面より高くする工程の間に、前記第1絶縁層の表層に、前記第1絶縁層が変質した第2変質層を形成する工程を有し、

前記第1絶縁層と前記配線の間にスペースを形成し、かつ前記配線の上面を前記第1絶縁層の上面より高くする工程は、前記第1変質層及び前記第2変質層を除去する工程である半導体装置の製造方法。

【請求項16】

請求項15に記載の半導体装置の製造方法において、

前記第1絶縁層は、SiCOH膜、SiCOHN膜、またはSiCOH膜若しくはSiCOHN膜のポーラス膜であり、

前記第1変質層、及び前記第2変質層は、前記第1絶縁層の炭素濃度が低下した低炭素層である半導体装置の製造方法。

【請求項17】

請求項16に記載の半導体装置の製造方法において、

前記第2変質層を形成する工程は、前記第1絶縁層を水素含有プラズマで処理する工程である半導体装置の製造方法。

【請求項18】

請求項9〜17のいずれか一つに記載の半導体装置の製造方法において、

前記ビアを形成する工程は、

少なくとも前記第3絶縁層に接続孔を形成する工程と、

前記接続孔の底面及び側壁に拡散防止膜を形成する工程と、

前記拡散防止膜上にメッキシード膜を形成する工程と、

前記メッキシード膜を用いてメッキ処理を行うことにより、前記接続孔内に導電膜を埋め込む工程と、

を含む半導体装置の製造方法。

【請求項19】

請求項9〜18のいずれか一つに記載の半導体装置の製造方法において、

前記配線を形成する工程の後、前記第2絶縁層及び前記エアギャップを形成する工程の前に、前記配線上に金属キャップ膜を形成する工程を有する半導体装置の製造方法。

【請求項20】

請求項19に記載の半導体装置の製造方法において、

前記金属キャップ膜を形成する工程は、無電解メッキ法又は選択CVD法である半導体装置の製造方法。

【請求項1】

第1絶縁層と、

前記第1絶縁層に埋め込まれ、上面が前記第1絶縁層の上面より高い配線と、

前記配線と前記第1絶縁層の間に位置するエアギャップと、

少なくとも前記第1絶縁層上及び前記エアギャップ上に形成された第2絶縁層と、

少なくとも前記第2絶縁層上に形成されたエッチングストッパー膜と、

前記エッチングストッパー膜上に形成された第3絶縁層と、

少なくとも前記第3絶縁層に埋め込まれ、前記配線に接続するビアと、

を備える半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記エアギャップは、前記第2絶縁層により形成されている半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、

前記第2絶縁層は、比誘電率が3.5以下である半導体装置。

【請求項4】

請求項1〜3のいずれか一つに記載の半導体装置において、

前記配線は、上面が前記第2絶縁層に被覆されておらず、

前記エッチングストッパー膜は、前記配線上にも形成されている半導体装置。

【請求項5】

請求項1〜3のいずれか一つに記載の半導体装置において、

前記配線は、上面が前記第2絶縁層に被覆されており、

前記ビアは、下部が前記第2絶縁層に埋め込まれている半導体装置。

【請求項6】

請求項1〜5のいずれか一つに記載の半導体装置において、

前記配線上に位置する金属キャップ膜を備える半導体装置。

【請求項7】

請求項1〜6のいずれか一つに記載の半導体装置において、

前記ビアは、メッキ法により形成されている半導体装置。

【請求項8】

請求項1〜7のいずれか一つに記載の半導体装置において、

前記第1絶縁層は、SiCOH膜、SiCOHN膜、またはSiCOH膜若しくはSiCOHN膜のポーラス膜である半導体装置。

【請求項9】

第1絶縁層を形成する工程と、

前記第1絶縁層に溝を形成する工程と、

前記溝に埋め込まれた配線を形成する工程と、

前記第1絶縁層と前記配線の間にスペースを形成し、かつ前記配線の上面を前記第1絶縁層の上面より高くする工程と、

前記スペースにエアギャップを形成し、かつ少なくとも前記第1絶縁層上及び前記配線上に第2絶縁層を形成する工程と、

少なくとも前記第2絶縁層上にエッチングストッパー膜を形成する工程と、

前記エッチングストッパー膜上に第3絶縁層を形成する工程と、

少なくとも前記第3絶縁層に、前記配線上に位置するビアを埋め込む工程と、

を備える半導体装置の製造方法。

【請求項10】

請求項9に記載の半導体装置の製造方法において、

前記エアギャップ及び前記第2絶縁層を形成する工程において、前記第2絶縁層によって前記エアギャップを形成する半導体装置の製造方法。

【請求項11】

請求項10に記載の半導体装置の製造方法において、

前記エアギャップ及び前記第2絶縁層を形成する工程は、

前記スペース上、前記第1配線層上、及び前記配線上に前記第2絶縁層を成膜する工程と、

前記第2絶縁層の表層をCMP法により除去する工程と、

を備える半導体装置の製造方法。

【請求項12】

請求項11に記載の半導体装置の製造方法において、

前記第2絶縁層の表層をCMP法により除去する工程において、前記配線を前記第2絶縁層から露出させる半導体装置の製造方法。

【請求項13】

請求項11に記載の半導体装置の製造方法において、

前記第2絶縁層の表層をCMP法により除去する工程において、前記第2絶縁層を前記配線上に残す半導体装置の製造方法。

【請求項14】

請求項9〜13のいずれか一つに記載の半導体装置の製造方法において、

前記第2絶縁層は比誘電率が3.5以下である半導体装置の製造方法。

【請求項15】

請求項9〜14のいずれか一つに記載の半導体装置の製造方法において、

前記溝を形成する工程において、前記溝の側壁に前記第1絶縁層が変質した第1変質層を形成し、

前記配線を形成する工程と、前記スペースを形成して前記配線の上面を前記第1絶縁層の上面より高くする工程の間に、前記第1絶縁層の表層に、前記第1絶縁層が変質した第2変質層を形成する工程を有し、

前記第1絶縁層と前記配線の間にスペースを形成し、かつ前記配線の上面を前記第1絶縁層の上面より高くする工程は、前記第1変質層及び前記第2変質層を除去する工程である半導体装置の製造方法。

【請求項16】

請求項15に記載の半導体装置の製造方法において、

前記第1絶縁層は、SiCOH膜、SiCOHN膜、またはSiCOH膜若しくはSiCOHN膜のポーラス膜であり、

前記第1変質層、及び前記第2変質層は、前記第1絶縁層の炭素濃度が低下した低炭素層である半導体装置の製造方法。

【請求項17】

請求項16に記載の半導体装置の製造方法において、

前記第2変質層を形成する工程は、前記第1絶縁層を水素含有プラズマで処理する工程である半導体装置の製造方法。

【請求項18】

請求項9〜17のいずれか一つに記載の半導体装置の製造方法において、

前記ビアを形成する工程は、

少なくとも前記第3絶縁層に接続孔を形成する工程と、

前記接続孔の底面及び側壁に拡散防止膜を形成する工程と、

前記拡散防止膜上にメッキシード膜を形成する工程と、

前記メッキシード膜を用いてメッキ処理を行うことにより、前記接続孔内に導電膜を埋め込む工程と、

を含む半導体装置の製造方法。

【請求項19】

請求項9〜18のいずれか一つに記載の半導体装置の製造方法において、

前記配線を形成する工程の後、前記第2絶縁層及び前記エアギャップを形成する工程の前に、前記配線上に金属キャップ膜を形成する工程を有する半導体装置の製造方法。

【請求項20】

請求項19に記載の半導体装置の製造方法において、

前記金属キャップ膜を形成する工程は、無電解メッキ法又は選択CVD法である半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2010−258215(P2010−258215A)

【公開日】平成22年11月11日(2010.11.11)

【国際特許分類】

【出願番号】特願2009−106389(P2009−106389)

【出願日】平成21年4月24日(2009.4.24)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成22年11月11日(2010.11.11)

【国際特許分類】

【出願日】平成21年4月24日(2009.4.24)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]