半導体装置及び半導体装置の製造方法

【課題】電源端子及びグランド端子をより少なくして、信号端子をより多く備えることができる半導体装置を提供する。

【解決手段】複数の第1電極パッド11を第1面に有する半導体チップ10と、第1面上で、複数の第1電極パッド11の各々と接触し、複数の第1電極パッド11の各々を電気的に接続する第1配線テープ20とを具備する。

【解決手段】複数の第1電極パッド11を第1面に有する半導体チップ10と、第1面上で、複数の第1電極パッド11の各々と接触し、複数の第1電極パッド11の各々を電気的に接続する第1配線テープ20とを具備する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、デジタルテレビやデジタルカメラ等のデジタル電子機器は急速に普及し、高性能化、多機能化が進んでいる。デジタル電子機器は、小型化、薄型化、軽量化、及び低消費電力化への要求が高いため、機器に使用される半導体装置もまた、小型化、多ピン化及び低消費電力化等が進んでいる。こうした機器類の製品ラインナップは非常に多く、頻繁にモデルチェンジもすることから、開発当初から可能な限りのコストダウンを行うことが重要である。コストダウン手法としての小型化は、前述したデジタル電子機器に対する要求に合致するため有効な方法である。しかし、小型化された半導体装置は、十分な数の信号端子を確保することが難しく、様々な検討がなされている。

【0003】

特許文献1には、電源用リードを少なくし、パッケージ本体のサイズを小型化できる半導体装置が開示されている。この半導体装置は、多数の電極を有する半導体チップと、ワイヤを介して電極と接続し、装置外に出る複数のリードと、半導体チップ上に延びて絶縁材を介して積層されると共にワイヤを介して電極と接続される導体板と、これらを樹脂封止するパッケージ本体とを備えることを特徴とする。このような半導体装置は、半導体チップ上に大きな断面積を確保し得る電源用リードや接地用リードを形成しているため、半導体装置の電源系を低インダクタンスにでき、電気特性を改善することができるというものである。その結果、この半導体装置は、パッケージ本体外に導出させる電源用リードを少なくでき、小型化することが可能となる。

【0004】

特許文献2には、高周波特性のような電気特性に優れる半導体装置が開示されている。この半導体装置は、デバイスホールを有するフィルム状の絶縁基材と、デバイスホールに突出するように配設されたインナーリードと、デバイスホール内に配置され、インナーリードと接続する半導体素子と、半導体素子の接続領域を被覆する封止樹脂層とを備えている。半導体装置は、インナーリードより内側のデバイスホール領域に、リング状の電源系もしくはグランド系の配線部が配設されている。これらの配設面において、樹脂封止層より外側の領域に、電源系もしくはグランド系の接続パッドが配設され、配線部と引出し用配線を介して接続されている。このような半導体装置は、半導体素子の電源系あるいはグランド系の電極端子から、電源系もしくはグランド系の配線部を経て、極めて短い距離で接続パッドまで接続できるというものである。

【0005】

特許文献3には、TAB(Tape Automated Bonding)方式の半導体装置が開示されている。この半導体装置は、半導体チップ及びリードフレームの表裏が絶縁フィルムを用いて封止されており、リードフレームのどちらか一方の面の一部のみが絶縁性フィルムより露出していることを特徴としている。このような半導体装置は、リードフレームのどちらか一方の面を含んで半導体チップの周囲を簡単に封止できるため、製造プロセスを簡素化できるというものである。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平05−021694号公報

【特許文献2】特開2000−77559号公報

【特許文献3】特開平08−288323号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

コストダウンのために半導体装置を小型化する際には、小型化してもより多くの信号端子を備えられるように、主に半導体パッケージの電源端子及びグランド端子が削減対象となる。しかし、電源端子及びグランド端子を削減し過ぎると、IRドロップ(I:電流、R:配線抵抗)、すなわち電圧降下が発生し、その結果として、半導体装置が動作不良を起こしやすくなる問題がある。

【課題を解決するための手段】

【0008】

以下に、発明を実施するための形態で使用される符号を括弧付きで用いて、課題を解決するための手段を記載する。この符号は、特許請求の範囲の記載と発明を実施するための形態の記載との対応を明らかにするために付加されたものであり、特許請求の範囲に記載されている発明の技術的範囲の解釈に用いてはならない。

【0009】

本発明の半導体装置(1)は、複数の第1電極パッド(11、12)を第1面に有する半導体チップ(10)と、第1面上で、複数の第1電極パッド(11、12)の各々と接触し、複数の第1電極パッド(11、12)の各々を電気的に接続する第1配線テープ(20、30)とを具備する。

【0010】

本発明の半導体装置(1)の製造方法は、半導体チップ(10)の第1面に形成された複数の第1電極パッド(11、12)の各々と電気的に接続するように、第1配線テープ(20、30)を接着する工程と、外部と接続する第1パッケージ端子(41、42)と、第1配線テープ(20、30)とを第1接続部(50、60、70b、70c)で電気的に接続する工程とを具備する。

【発明の効果】

【0011】

本発明の半導体装置は、電源端子及びグランド端子をより少なく、信号端子をより多く備えることができる。

【図面の簡単な説明】

【0012】

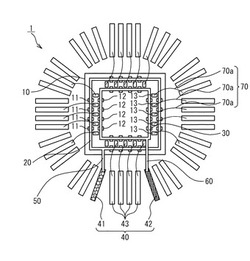

【図1】図1は、本発明の第1の実施の形態の半導体装置1を示す平面図である。

【図2】図2は、半導体チップ10の表面を示す平面図である。

【図3】図3は、半導体チップ10に配線テープ20と配線テープ30とが接着されたことを示す平面図である。

【図4】図4は、本発明の第2の実施の形態の半導体装置1を示す平面図である。

【発明を実施するための形態】

【0013】

以下に、添付図面を参照しながら、本発明の実施形態による半導体装置を説明する。

【0014】

(第1の実施の形態)

本発明の第1の実施の形態による半導体装置1を説明する。図1は、本発明の第1の実施の形態の半導体装置1を示す平面図である。図1を参照すると、半導体装置1は、半導体チップ10と、配線テープ20と、配線テープ30と、パッケージ端子部40と、接続リード50と、接続リード60と、ワイヤ部70とを具備する。尚、本発明の半導体装置1は、パッケージ端子部40の外端を残して、半導体チップ10等を保護するために樹脂によって封止されるが、図1では封止樹脂は省略されている。

【0015】

半導体チップ10は、各種機能を実現するための回路を含み、回路と接続する複数の電極パッドを表面の外周部に有する。詳細には、半導体チップ10は、複数のGND用パッド11と、複数のVDD用パッド12と、複数の信号用パッド13とを有する。複数のGND用パッド11と複数のVDD用パッド12とは、電源が供給される電極パッドである。複数の信号用パッド13は、信号が入出力される電極パッドである。平面視したときの半導体チップ10の輪郭線となる4つの各辺の近傍において、複数のGND用パッド11、複数のVDD用パッド12及び複数の信号用パッド13は、平行に並んで配置される。言い換えると、複数のGND用パッド11と、複数のVDD用パッド12及び複数の信号用パッド13は、半導体チップ10の外周のある一辺に対して平行な三列に配置される。

【0016】

配線テープ20は、半導体チップ10の表面上で、複数のGND用パッド11の各々と接触し、複数のGND用パッド11の各々を電気的に接続するリング状のテープである。リング状とは直線や曲線で形成される閉曲線状であることを表し、配線テープ20は半導体チップ10の表面上で閉曲線状に配置される。配線テープ20は、樹脂フィルムの片面にのみ、銅箔などの配線パタンを備えたものである。即ち、配線テープ20は、複数のGND用パッド11の各々と接触する銅箔などの配線パタンと、配線パタンの上に形成され、配線テープ20の表面に位置する樹脂フィルムとを備える。配線テープ20が複数のGND用パッド11を覆うように接着しているため、配線テープの配線パタンと複数のGND用パッド11の各々とは面接触し、確実に導通される構造である。接触箇所の断面は、半導体チップ10のGND用パッド11と、配線テープ20の配線パタンと、配線テープ20の樹脂フィルムとの積層構造となる。尚、配線テープ20で囲まれた半導体チップ10の表面に、複数のVDD用パッド12及び複数の信号用パッド13が配置されている。

【0017】

配線テープ30は、配線テープ20と同様であり、半導体チップ10の表面上で、複数のVDD用パッド12の各々と接触し、複数のVDD用パッド12の各々を電気的に接続するリング状のテープである。配線テープ30は、樹脂フィルムの片面にのみ、銅箔などの配線パタンを備えている。従って、接触箇所の断面は、半導体チップ10のVDD用パッド12と、配線テープ30の配線パタンと、配線テープ30の樹脂フィルムとの積層構造となる。配線テープ20と配線テープ30とは、半導体チップ10の表面上で重ならないように配置される。尚、配線テープ30で囲まれた外側の半導体チップ10の表面に、複数のGND用パッド11及び複数のVDD用パッド12が配置されている。特に、配線テープ20と配線テープ30とで囲まれた領域には、複数の信号用パッド13が配置されている。

【0018】

パッケージ端子部40は、半導体装置1が外部と接続するためのパッケージ端子であり、半導体チップ10の外側で半導体チップ10を取り囲むように放射状に配置されている。パッケージ端子部40は、GND用パッケージ端子41と、VDD用パッケージ端子42と、信号用パッケージ端子43とを備える。GND用パッケージ端子41とVDD用パッケージ端子42とには、電源として異なる電圧が供給される。GND用パッケージ端子41はグランド電圧が供給されるパッケージ端子であり、VDD用パッケージ端子42は電源電圧が供給されるパッケージ端子である。信号用パッケージ端子43は、信号が入出力されるパッケージ端子である。尚、GND用パッケージ端子41、VDD用パッケージ端子42及び信号用パッケージ端子43は、図1に示した位置や数に限定するものではなく、他の位置や複数配置されていてもよい。但し、GND用パッケージ端子41及びVDD用パッケージ端子42は、接続リード50及び接続リード60ができるだけ短くなる位置であることが好ましい。また、半導体装置1は、信号用パッケージ端子43をより多く備えられるように、GND用パッケージ端子41及びVDD用パッケージ端子42の数は少ないことが好ましい。

【0019】

接続リード50は、配線テープ20と、GND用パッケージ端子41とを電気的に接続する。接続リード50は、配線テープ20と同様であり、樹脂フィルムの片面にのみ、銅箔などの配線パタンを備えたものである。即ち、接続リード50は、配線テープ20とGND用パッケージ端子41とを電気的に接続する配線パタンと、配線パタンの上に形成され、接続リード50表面に位置する樹脂フィルムとを備える。

【0020】

接続リード60は、配線テープ30と、VDD用パッケージ端子42とを電気的に接続する。接続リード60は、接続リード50と同様であり、樹脂フィルムの片面にのみ、銅箔などの配線パタンを備えている。即ち、接続リード60は、配線テープ30とVDD用パッケージ端子42とを電気的に接続する配線パタンと、配線パタンの上に形成され、接続リード60表面に位置する樹脂フィルムとを備える。接続リード60は配線テープ20と接触するが、配線テープ20の表面は絶縁性の樹脂フィルムであるため、接続リード60と配線テープ20とはショートすることなく交差できる。即ち、交差した箇所の断面は、半導体チップ10と、配線テープ20の配線パタンと、配線テープ20の樹脂フィルムと、接続リード60の配線パタンと、接続リード60の樹脂フィルムとの積層構造となる。尚、配線テープ20と接続リード60とは、上下が逆に交差していてもよい。配線テープ20と接続リード60とが交差できることで、ワイヤ部70が形成されるための空間を確保しやくなる。また、接続リード50及び接続リード60は、1本のワイヤ70aよりも広い断面積を有し、確実に電源を供給できる効果を奏する。

【0021】

ワイヤ部70は、半導体チップ10と、パッケージ端子部40とを電気的に接続する。ワイヤ部70は、複数のワイヤ70aを含む。ワイヤ70aは、信号用パッド13と、当該信号用パッド13に対応した信号用パッケージ端子43とを1対1で電気的に接続する。

【0022】

このような構造の半導体装置1は、GND用パッケージ端子41及びVDD用パッケージ端子42を介して供給された電源を、リング状の配線テープ20及びリング状の配線テープ30を介して、複数のGND用パッド11及び複数のVDD用パッド12に供給することができる。つまり、本発明の半導体装置1は、より少ないGND用パッケージ端子41及びVDD用パッケージ端子42でも、電源を供給することが可能となる。特に、配線テープ20及び配線テープ30がリング状であると電圧降下を補い易く、電源電圧及びグランド電圧を安定させることができる。

【0023】

本発明の第1の実施の形態による半導体装置1の製造方法を説明する。図2は、半導体チップ10の表面を示す平面図である。図2を参照すると、半導体チップ10の表面には、複数のGND用パッド11と、複数のVDD用パッド12と、複数の信号用パッド13とが形成されている。平面視したときの半導体チップ10の輪郭線となる4つの各辺の近傍において、複数のGND用パッド11、複数のVDD用パッド12及び複数の信号用パッド13は、平行に並んで配置される。

【0024】

図3は、図2の半導体チップ10に配線テープ20と配線テープ30とが接着されたことを示す平面図である。図3を参照すると、配線テープ20は、複数のGND用パッド11の各々と電気的に接続するように、半導体チップ10の表面上へリング状に接着される。また、配線テープ30は、半導体チップ10の表面に形成された、配線テープ20で囲まれた複数のVDD用パッド12の各々と電気的に接続するように、半導体チップ10の表面上へリング状に接着される。尚、配線テープ20と配線テープ30とを形成する順番は逆であってもよい。

【0025】

配線テープ20と配線テープ30とが接着された半導体チップ10は、パッケージ端子部40と接続される。図1を参照すると、配線テープ20とGND用パッケージ端子41とは、接続リード50によって電気的に接続される。また、配線テープ30とVDD用パッケージ端子42とは、接続リード60によって電気的に接続される。更に、信号用パッケージ端子43は、ワイヤ70aによって信号用パッド13と接続される。この様にして、本発明の第1の実施の形態の半導体装置1は製造される。

【0026】

本発明の第1の実施の形態による半導体装置1は、GND用パッケージ端子41及びVDD用パッケージ端子42を介して供給された電源を、リング状の配線テープ20及びリング状の配線テープ30を介して、複数のGND用パッド11及び複数のVDD用パッド12に供給することができる。つまり、本発明の半導体装置1は、より少ないGND用パッケージ端子41及びVDD用パッケージ端子42でも、電源を供給することが可能となる。特に、配線テープ20及び配線テープ30がリング状であると電圧降下を補い易く、電源電圧及びグランド電圧を安定させることができるため、小型化してもより多くの信号端子を備えることができる。尚、本発明の半導体装置1は、配線テープ20と配線テープ30とが二重のリング状構造として説明したが、その数を二重に限定するものではない。

【0027】

(第2の実施の形態)

本発明の第2の実施の形態による半導体装置1を説明する。本発明の第2の実施の形態による半導体装置1は、第1の実施の形態の接続リード50と接続リード60とをワイヤに変更したものである。図4は、本発明の第2の実施の形態の半導体装置1を示す平面図である。図4を参照すると、半導体装置1は、半導体チップ10と、配線テープ20と、配線テープ30と、パッケージ端子部40と、ワイヤ部70とを具備する。尚、本発明の第2の実施の形態では、第1の実施の形態と同様の構成には同じ符号を用いて説明する。

【0028】

ワイヤ部70は、半導体チップ10と、パッケージ端子部40とを電気的に接続する。ワイヤ部70は、複数のワイヤ70aと、複数のワイヤ70bと、複数のワイヤ70cとを備える。ワイヤ70aは、1つの信号用パッド13と、当該信号用パッド13に対応した1つの信号用パッケージ端子43とを電気的に接続する。ワイヤ70bは、配線テープ20の任意の部位と、1つのGND用パッケージ端子41を電気的に接続する。ワイヤ70cは、配線テープ30の任意の部位と、1つのVDD用パッケージ端子42とを電気的に接続する。尚、複数のワイヤ70a、複数のワイヤ70b、及び複数のワイヤ70cの各々は、ワイヤ長ができるだけ短いことが好ましい。

【0029】

本発明の第2の実施の形態によるパッケージ端子部40は、複数のGND用パッケージ端子41と、複数のVDD用パッケージ用端子42とを備える。従って、配線テープ20は、複数のワイヤ70bを介して複数のGND用パッケージ端子41と接続され、配線テープ30は、複数のワイヤ70cを介して複数のVDD用パッケージ端子42と接続される。尚、GND用パッケージ端子41、VDD用パッケージ端子42及び信号用パッケージ端子43は、図4に示した位置や数に限定するものではない。但し、GND用パッケージ端子41及びVDD用パッケージ端子42は、ワイヤ70b及びワイヤ70cができるだけ短くなる位置であることが好ましい。また、半導体装置1は、信号用パッケージ端子43をより多く備えられるように、GND用パッケージ端子41及びVDD用パッケージ端子42の数は少ないことが好ましい。

【0030】

本発明の第2の実施の形態による半導体装置1の製造方法を説明する。本発明の第2の実施の形態による半導体装置1の製造方法は、図2及び図3に示した製造工程までは第1の実施の形態と同様である。従って、図3以降の製造工程を説明する。

【0031】

図3に示した状態の配線テープ20と配線テープ30とが接着された半導体チップ10は、次に、ワイヤボンディングによってパッケージ端子部40と接続される。図4を参照すると、ワイヤ部70は、半導体チップ10と、パッケージ端子部40とを電気的に接続する。詳細には、ワイヤ70aは、1つの信号用パッド13と、当該信号用パッド13に対応した1つの信号用パッケージ端子43とを電気的に接続する。ワイヤ70bは、配線テープ20の任意の部位と、GND用パッケージ端子41を電気的に接続する。ワイヤ70cは、配線テープ30の任意の部位と、VDD用パッケージ端子42とを電気的に接続する。配線テープ20及び配線テープ30は、そのテープ上のいずれの位置においてワイヤボンディングが行われても電気的な接続が可能である。この様にして、本発明の第2の実施の形態の半導体装置1は製造される。

【0032】

本発明の第2の実施の形態による半導体装置1は、第1の実施の形態による効果に加え、更に、配線テープ20及び配線テープ30のどの位置にもワイヤを接続することができるため、半導体装置1の設計の自由度を高める効果を奏する。

【0033】

以上のように、本発明の半導体装置1は、半導体チップ10上の複数の電極パッド11、12にリング状の配線テープ20、30を接着させることで、各電極パッド11、12に供給される電源電圧又はグランド電圧を共通化させることができる。これによって、本発明の半導体装置1は、電源端子及びグランド端子をより少なくし、より多くの信号端子を備えることが可能となる。特に、本発明の半導体装置1は、配線テープ20、30がリング状であるため、より少ない電源端子及びグランド端子でも、電源電圧及びグランド電圧を安定させることができる効果を奏する。また、本発明の半導体装置1は、全ての電極パッドにワイヤボンディングを行わないため、ワイヤの数や使用量を削減することもできる。ワイヤの数や使用量が減少すると、ワイヤ間で発生するショートを抑えることに繋がり、コストダウン効果に加え、信頼性及び歩留まりを向上させる効果も奏する。更に、本発明の半導体装置1は、搭載されるマザーボード側の電源端子及びグランド端子も削減することができるため、マザーボードを設計し易くする効果も奏する。尚、説明した実施の形態は矛盾のない範囲で組み合わせることが可能である。

【符号の説明】

【0034】

1 半導体装置

10 半導体チップ

11 GND用パッド

12 VDD用パッド

13 信号用パッド

20 配線テープ

30 配線テープ

40 パッケージ端子部

41 GND用パッケージ端子

42 VDD用パッケージ端子

43 信号用パッケージ端子

50 接続リード

60 接続リード

70 ワイヤ部

70a ワイヤ

70b ワイヤ

70c ワイヤ

【技術分野】

【0001】

本発明は、半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、デジタルテレビやデジタルカメラ等のデジタル電子機器は急速に普及し、高性能化、多機能化が進んでいる。デジタル電子機器は、小型化、薄型化、軽量化、及び低消費電力化への要求が高いため、機器に使用される半導体装置もまた、小型化、多ピン化及び低消費電力化等が進んでいる。こうした機器類の製品ラインナップは非常に多く、頻繁にモデルチェンジもすることから、開発当初から可能な限りのコストダウンを行うことが重要である。コストダウン手法としての小型化は、前述したデジタル電子機器に対する要求に合致するため有効な方法である。しかし、小型化された半導体装置は、十分な数の信号端子を確保することが難しく、様々な検討がなされている。

【0003】

特許文献1には、電源用リードを少なくし、パッケージ本体のサイズを小型化できる半導体装置が開示されている。この半導体装置は、多数の電極を有する半導体チップと、ワイヤを介して電極と接続し、装置外に出る複数のリードと、半導体チップ上に延びて絶縁材を介して積層されると共にワイヤを介して電極と接続される導体板と、これらを樹脂封止するパッケージ本体とを備えることを特徴とする。このような半導体装置は、半導体チップ上に大きな断面積を確保し得る電源用リードや接地用リードを形成しているため、半導体装置の電源系を低インダクタンスにでき、電気特性を改善することができるというものである。その結果、この半導体装置は、パッケージ本体外に導出させる電源用リードを少なくでき、小型化することが可能となる。

【0004】

特許文献2には、高周波特性のような電気特性に優れる半導体装置が開示されている。この半導体装置は、デバイスホールを有するフィルム状の絶縁基材と、デバイスホールに突出するように配設されたインナーリードと、デバイスホール内に配置され、インナーリードと接続する半導体素子と、半導体素子の接続領域を被覆する封止樹脂層とを備えている。半導体装置は、インナーリードより内側のデバイスホール領域に、リング状の電源系もしくはグランド系の配線部が配設されている。これらの配設面において、樹脂封止層より外側の領域に、電源系もしくはグランド系の接続パッドが配設され、配線部と引出し用配線を介して接続されている。このような半導体装置は、半導体素子の電源系あるいはグランド系の電極端子から、電源系もしくはグランド系の配線部を経て、極めて短い距離で接続パッドまで接続できるというものである。

【0005】

特許文献3には、TAB(Tape Automated Bonding)方式の半導体装置が開示されている。この半導体装置は、半導体チップ及びリードフレームの表裏が絶縁フィルムを用いて封止されており、リードフレームのどちらか一方の面の一部のみが絶縁性フィルムより露出していることを特徴としている。このような半導体装置は、リードフレームのどちらか一方の面を含んで半導体チップの周囲を簡単に封止できるため、製造プロセスを簡素化できるというものである。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平05−021694号公報

【特許文献2】特開2000−77559号公報

【特許文献3】特開平08−288323号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

コストダウンのために半導体装置を小型化する際には、小型化してもより多くの信号端子を備えられるように、主に半導体パッケージの電源端子及びグランド端子が削減対象となる。しかし、電源端子及びグランド端子を削減し過ぎると、IRドロップ(I:電流、R:配線抵抗)、すなわち電圧降下が発生し、その結果として、半導体装置が動作不良を起こしやすくなる問題がある。

【課題を解決するための手段】

【0008】

以下に、発明を実施するための形態で使用される符号を括弧付きで用いて、課題を解決するための手段を記載する。この符号は、特許請求の範囲の記載と発明を実施するための形態の記載との対応を明らかにするために付加されたものであり、特許請求の範囲に記載されている発明の技術的範囲の解釈に用いてはならない。

【0009】

本発明の半導体装置(1)は、複数の第1電極パッド(11、12)を第1面に有する半導体チップ(10)と、第1面上で、複数の第1電極パッド(11、12)の各々と接触し、複数の第1電極パッド(11、12)の各々を電気的に接続する第1配線テープ(20、30)とを具備する。

【0010】

本発明の半導体装置(1)の製造方法は、半導体チップ(10)の第1面に形成された複数の第1電極パッド(11、12)の各々と電気的に接続するように、第1配線テープ(20、30)を接着する工程と、外部と接続する第1パッケージ端子(41、42)と、第1配線テープ(20、30)とを第1接続部(50、60、70b、70c)で電気的に接続する工程とを具備する。

【発明の効果】

【0011】

本発明の半導体装置は、電源端子及びグランド端子をより少なく、信号端子をより多く備えることができる。

【図面の簡単な説明】

【0012】

【図1】図1は、本発明の第1の実施の形態の半導体装置1を示す平面図である。

【図2】図2は、半導体チップ10の表面を示す平面図である。

【図3】図3は、半導体チップ10に配線テープ20と配線テープ30とが接着されたことを示す平面図である。

【図4】図4は、本発明の第2の実施の形態の半導体装置1を示す平面図である。

【発明を実施するための形態】

【0013】

以下に、添付図面を参照しながら、本発明の実施形態による半導体装置を説明する。

【0014】

(第1の実施の形態)

本発明の第1の実施の形態による半導体装置1を説明する。図1は、本発明の第1の実施の形態の半導体装置1を示す平面図である。図1を参照すると、半導体装置1は、半導体チップ10と、配線テープ20と、配線テープ30と、パッケージ端子部40と、接続リード50と、接続リード60と、ワイヤ部70とを具備する。尚、本発明の半導体装置1は、パッケージ端子部40の外端を残して、半導体チップ10等を保護するために樹脂によって封止されるが、図1では封止樹脂は省略されている。

【0015】

半導体チップ10は、各種機能を実現するための回路を含み、回路と接続する複数の電極パッドを表面の外周部に有する。詳細には、半導体チップ10は、複数のGND用パッド11と、複数のVDD用パッド12と、複数の信号用パッド13とを有する。複数のGND用パッド11と複数のVDD用パッド12とは、電源が供給される電極パッドである。複数の信号用パッド13は、信号が入出力される電極パッドである。平面視したときの半導体チップ10の輪郭線となる4つの各辺の近傍において、複数のGND用パッド11、複数のVDD用パッド12及び複数の信号用パッド13は、平行に並んで配置される。言い換えると、複数のGND用パッド11と、複数のVDD用パッド12及び複数の信号用パッド13は、半導体チップ10の外周のある一辺に対して平行な三列に配置される。

【0016】

配線テープ20は、半導体チップ10の表面上で、複数のGND用パッド11の各々と接触し、複数のGND用パッド11の各々を電気的に接続するリング状のテープである。リング状とは直線や曲線で形成される閉曲線状であることを表し、配線テープ20は半導体チップ10の表面上で閉曲線状に配置される。配線テープ20は、樹脂フィルムの片面にのみ、銅箔などの配線パタンを備えたものである。即ち、配線テープ20は、複数のGND用パッド11の各々と接触する銅箔などの配線パタンと、配線パタンの上に形成され、配線テープ20の表面に位置する樹脂フィルムとを備える。配線テープ20が複数のGND用パッド11を覆うように接着しているため、配線テープの配線パタンと複数のGND用パッド11の各々とは面接触し、確実に導通される構造である。接触箇所の断面は、半導体チップ10のGND用パッド11と、配線テープ20の配線パタンと、配線テープ20の樹脂フィルムとの積層構造となる。尚、配線テープ20で囲まれた半導体チップ10の表面に、複数のVDD用パッド12及び複数の信号用パッド13が配置されている。

【0017】

配線テープ30は、配線テープ20と同様であり、半導体チップ10の表面上で、複数のVDD用パッド12の各々と接触し、複数のVDD用パッド12の各々を電気的に接続するリング状のテープである。配線テープ30は、樹脂フィルムの片面にのみ、銅箔などの配線パタンを備えている。従って、接触箇所の断面は、半導体チップ10のVDD用パッド12と、配線テープ30の配線パタンと、配線テープ30の樹脂フィルムとの積層構造となる。配線テープ20と配線テープ30とは、半導体チップ10の表面上で重ならないように配置される。尚、配線テープ30で囲まれた外側の半導体チップ10の表面に、複数のGND用パッド11及び複数のVDD用パッド12が配置されている。特に、配線テープ20と配線テープ30とで囲まれた領域には、複数の信号用パッド13が配置されている。

【0018】

パッケージ端子部40は、半導体装置1が外部と接続するためのパッケージ端子であり、半導体チップ10の外側で半導体チップ10を取り囲むように放射状に配置されている。パッケージ端子部40は、GND用パッケージ端子41と、VDD用パッケージ端子42と、信号用パッケージ端子43とを備える。GND用パッケージ端子41とVDD用パッケージ端子42とには、電源として異なる電圧が供給される。GND用パッケージ端子41はグランド電圧が供給されるパッケージ端子であり、VDD用パッケージ端子42は電源電圧が供給されるパッケージ端子である。信号用パッケージ端子43は、信号が入出力されるパッケージ端子である。尚、GND用パッケージ端子41、VDD用パッケージ端子42及び信号用パッケージ端子43は、図1に示した位置や数に限定するものではなく、他の位置や複数配置されていてもよい。但し、GND用パッケージ端子41及びVDD用パッケージ端子42は、接続リード50及び接続リード60ができるだけ短くなる位置であることが好ましい。また、半導体装置1は、信号用パッケージ端子43をより多く備えられるように、GND用パッケージ端子41及びVDD用パッケージ端子42の数は少ないことが好ましい。

【0019】

接続リード50は、配線テープ20と、GND用パッケージ端子41とを電気的に接続する。接続リード50は、配線テープ20と同様であり、樹脂フィルムの片面にのみ、銅箔などの配線パタンを備えたものである。即ち、接続リード50は、配線テープ20とGND用パッケージ端子41とを電気的に接続する配線パタンと、配線パタンの上に形成され、接続リード50表面に位置する樹脂フィルムとを備える。

【0020】

接続リード60は、配線テープ30と、VDD用パッケージ端子42とを電気的に接続する。接続リード60は、接続リード50と同様であり、樹脂フィルムの片面にのみ、銅箔などの配線パタンを備えている。即ち、接続リード60は、配線テープ30とVDD用パッケージ端子42とを電気的に接続する配線パタンと、配線パタンの上に形成され、接続リード60表面に位置する樹脂フィルムとを備える。接続リード60は配線テープ20と接触するが、配線テープ20の表面は絶縁性の樹脂フィルムであるため、接続リード60と配線テープ20とはショートすることなく交差できる。即ち、交差した箇所の断面は、半導体チップ10と、配線テープ20の配線パタンと、配線テープ20の樹脂フィルムと、接続リード60の配線パタンと、接続リード60の樹脂フィルムとの積層構造となる。尚、配線テープ20と接続リード60とは、上下が逆に交差していてもよい。配線テープ20と接続リード60とが交差できることで、ワイヤ部70が形成されるための空間を確保しやくなる。また、接続リード50及び接続リード60は、1本のワイヤ70aよりも広い断面積を有し、確実に電源を供給できる効果を奏する。

【0021】

ワイヤ部70は、半導体チップ10と、パッケージ端子部40とを電気的に接続する。ワイヤ部70は、複数のワイヤ70aを含む。ワイヤ70aは、信号用パッド13と、当該信号用パッド13に対応した信号用パッケージ端子43とを1対1で電気的に接続する。

【0022】

このような構造の半導体装置1は、GND用パッケージ端子41及びVDD用パッケージ端子42を介して供給された電源を、リング状の配線テープ20及びリング状の配線テープ30を介して、複数のGND用パッド11及び複数のVDD用パッド12に供給することができる。つまり、本発明の半導体装置1は、より少ないGND用パッケージ端子41及びVDD用パッケージ端子42でも、電源を供給することが可能となる。特に、配線テープ20及び配線テープ30がリング状であると電圧降下を補い易く、電源電圧及びグランド電圧を安定させることができる。

【0023】

本発明の第1の実施の形態による半導体装置1の製造方法を説明する。図2は、半導体チップ10の表面を示す平面図である。図2を参照すると、半導体チップ10の表面には、複数のGND用パッド11と、複数のVDD用パッド12と、複数の信号用パッド13とが形成されている。平面視したときの半導体チップ10の輪郭線となる4つの各辺の近傍において、複数のGND用パッド11、複数のVDD用パッド12及び複数の信号用パッド13は、平行に並んで配置される。

【0024】

図3は、図2の半導体チップ10に配線テープ20と配線テープ30とが接着されたことを示す平面図である。図3を参照すると、配線テープ20は、複数のGND用パッド11の各々と電気的に接続するように、半導体チップ10の表面上へリング状に接着される。また、配線テープ30は、半導体チップ10の表面に形成された、配線テープ20で囲まれた複数のVDD用パッド12の各々と電気的に接続するように、半導体チップ10の表面上へリング状に接着される。尚、配線テープ20と配線テープ30とを形成する順番は逆であってもよい。

【0025】

配線テープ20と配線テープ30とが接着された半導体チップ10は、パッケージ端子部40と接続される。図1を参照すると、配線テープ20とGND用パッケージ端子41とは、接続リード50によって電気的に接続される。また、配線テープ30とVDD用パッケージ端子42とは、接続リード60によって電気的に接続される。更に、信号用パッケージ端子43は、ワイヤ70aによって信号用パッド13と接続される。この様にして、本発明の第1の実施の形態の半導体装置1は製造される。

【0026】

本発明の第1の実施の形態による半導体装置1は、GND用パッケージ端子41及びVDD用パッケージ端子42を介して供給された電源を、リング状の配線テープ20及びリング状の配線テープ30を介して、複数のGND用パッド11及び複数のVDD用パッド12に供給することができる。つまり、本発明の半導体装置1は、より少ないGND用パッケージ端子41及びVDD用パッケージ端子42でも、電源を供給することが可能となる。特に、配線テープ20及び配線テープ30がリング状であると電圧降下を補い易く、電源電圧及びグランド電圧を安定させることができるため、小型化してもより多くの信号端子を備えることができる。尚、本発明の半導体装置1は、配線テープ20と配線テープ30とが二重のリング状構造として説明したが、その数を二重に限定するものではない。

【0027】

(第2の実施の形態)

本発明の第2の実施の形態による半導体装置1を説明する。本発明の第2の実施の形態による半導体装置1は、第1の実施の形態の接続リード50と接続リード60とをワイヤに変更したものである。図4は、本発明の第2の実施の形態の半導体装置1を示す平面図である。図4を参照すると、半導体装置1は、半導体チップ10と、配線テープ20と、配線テープ30と、パッケージ端子部40と、ワイヤ部70とを具備する。尚、本発明の第2の実施の形態では、第1の実施の形態と同様の構成には同じ符号を用いて説明する。

【0028】

ワイヤ部70は、半導体チップ10と、パッケージ端子部40とを電気的に接続する。ワイヤ部70は、複数のワイヤ70aと、複数のワイヤ70bと、複数のワイヤ70cとを備える。ワイヤ70aは、1つの信号用パッド13と、当該信号用パッド13に対応した1つの信号用パッケージ端子43とを電気的に接続する。ワイヤ70bは、配線テープ20の任意の部位と、1つのGND用パッケージ端子41を電気的に接続する。ワイヤ70cは、配線テープ30の任意の部位と、1つのVDD用パッケージ端子42とを電気的に接続する。尚、複数のワイヤ70a、複数のワイヤ70b、及び複数のワイヤ70cの各々は、ワイヤ長ができるだけ短いことが好ましい。

【0029】

本発明の第2の実施の形態によるパッケージ端子部40は、複数のGND用パッケージ端子41と、複数のVDD用パッケージ用端子42とを備える。従って、配線テープ20は、複数のワイヤ70bを介して複数のGND用パッケージ端子41と接続され、配線テープ30は、複数のワイヤ70cを介して複数のVDD用パッケージ端子42と接続される。尚、GND用パッケージ端子41、VDD用パッケージ端子42及び信号用パッケージ端子43は、図4に示した位置や数に限定するものではない。但し、GND用パッケージ端子41及びVDD用パッケージ端子42は、ワイヤ70b及びワイヤ70cができるだけ短くなる位置であることが好ましい。また、半導体装置1は、信号用パッケージ端子43をより多く備えられるように、GND用パッケージ端子41及びVDD用パッケージ端子42の数は少ないことが好ましい。

【0030】

本発明の第2の実施の形態による半導体装置1の製造方法を説明する。本発明の第2の実施の形態による半導体装置1の製造方法は、図2及び図3に示した製造工程までは第1の実施の形態と同様である。従って、図3以降の製造工程を説明する。

【0031】

図3に示した状態の配線テープ20と配線テープ30とが接着された半導体チップ10は、次に、ワイヤボンディングによってパッケージ端子部40と接続される。図4を参照すると、ワイヤ部70は、半導体チップ10と、パッケージ端子部40とを電気的に接続する。詳細には、ワイヤ70aは、1つの信号用パッド13と、当該信号用パッド13に対応した1つの信号用パッケージ端子43とを電気的に接続する。ワイヤ70bは、配線テープ20の任意の部位と、GND用パッケージ端子41を電気的に接続する。ワイヤ70cは、配線テープ30の任意の部位と、VDD用パッケージ端子42とを電気的に接続する。配線テープ20及び配線テープ30は、そのテープ上のいずれの位置においてワイヤボンディングが行われても電気的な接続が可能である。この様にして、本発明の第2の実施の形態の半導体装置1は製造される。

【0032】

本発明の第2の実施の形態による半導体装置1は、第1の実施の形態による効果に加え、更に、配線テープ20及び配線テープ30のどの位置にもワイヤを接続することができるため、半導体装置1の設計の自由度を高める効果を奏する。

【0033】

以上のように、本発明の半導体装置1は、半導体チップ10上の複数の電極パッド11、12にリング状の配線テープ20、30を接着させることで、各電極パッド11、12に供給される電源電圧又はグランド電圧を共通化させることができる。これによって、本発明の半導体装置1は、電源端子及びグランド端子をより少なくし、より多くの信号端子を備えることが可能となる。特に、本発明の半導体装置1は、配線テープ20、30がリング状であるため、より少ない電源端子及びグランド端子でも、電源電圧及びグランド電圧を安定させることができる効果を奏する。また、本発明の半導体装置1は、全ての電極パッドにワイヤボンディングを行わないため、ワイヤの数や使用量を削減することもできる。ワイヤの数や使用量が減少すると、ワイヤ間で発生するショートを抑えることに繋がり、コストダウン効果に加え、信頼性及び歩留まりを向上させる効果も奏する。更に、本発明の半導体装置1は、搭載されるマザーボード側の電源端子及びグランド端子も削減することができるため、マザーボードを設計し易くする効果も奏する。尚、説明した実施の形態は矛盾のない範囲で組み合わせることが可能である。

【符号の説明】

【0034】

1 半導体装置

10 半導体チップ

11 GND用パッド

12 VDD用パッド

13 信号用パッド

20 配線テープ

30 配線テープ

40 パッケージ端子部

41 GND用パッケージ端子

42 VDD用パッケージ端子

43 信号用パッケージ端子

50 接続リード

60 接続リード

70 ワイヤ部

70a ワイヤ

70b ワイヤ

70c ワイヤ

【特許請求の範囲】

【請求項1】

複数の第1電極パッドを第1面に有する半導体チップと、

前記第1面上で、前記複数の第1電極パッドの各々と接触し、前記複数の第1電極パッドの各々を電気的に接続する第1配線テープと

を具備する

半導体装置。

【請求項2】

請求項1に記載の半導体装置であって、

前記第1配線テープは、前記第1面上で閉曲線状に配置される

半導体装置。

【請求項3】

請求項2に記載の半導体装置であって、

前記第1面上に第2配線テープ

を更に具備し、

前記半導体チップは、

前記第1配線テープで囲まれた前記第1面に、複数の第2電極パッド

を更に有し、

前記第2配線テープは、前記複数の第2電極パッドの各々と接触し、前記複数の第2電極パッドの各々を電気的に接続する

半導体装置。

【請求項4】

請求項3に記載の半導体装置であって、

前記第2配線テープは、前記第1面上で閉曲線状に配置される

半導体装置。

【請求項5】

請求項1乃至4の何れか一項に記載の半導体装置であって、

前記第1配線テープは、

前記複数の第1電極パッドの各々と接触する第1導体層と、

前記第1導体層の上に形成され、前記第1配線テープの表面に位置する第1絶縁層と

を備える

半導体装置。

【請求項6】

請求項3又は4に記載の半導体装置であって、

前記第1配線テープは、

前記複数の第1電極パッドの各々と接触する第1導体層と、

前記第1導体層の上に形成され、前記第1配線テープの表面に位置する第1絶縁層と

を備え、

前記第2配線テープは、

前記複数の第2電極パッドの各々と接触する第2導体層と、

前記第2導体層の上に形成され、前記第2配線テープの表面に位置する第2絶縁層と

を備える

半導体装置。

【請求項7】

請求項3乃至6の何れか一項に記載の半導体装置であって、

外部と接続する第1パッケージ端子と、

外部と接続する第2パッケージ端子と、

前記第1配線テープと、前記第1パッケージ端子とを電気的に接続する第1接続部と、

前記第2配線テープと、前記第2パッケージ端子とを電気的に接続する第2接続部と

を更に具備する

半導体装置。

【請求項8】

請求項7に記載の半導体装置であって、

前記第1接続部は、

前記第1配線テープと前記第1パッケージ端子とを電気的に接続する第3導体層と、

前記第3導体層の上に形成され、前記第1接続部の表面に位置する第3絶縁層と

を備え、

前記第2接続部は、

前記第2配線テープと前記第2パッケージ端子とを電気的に接続する第4導体層と、

前記第4導体層の上に形成され、前記第2接続部の表面に位置する第4絶縁層と

を備える

半導体装置。

【請求項9】

請求項7又は8に記載の半導体装置であって、

前記第1パッケージ端子と前記第2パッケージ端子とには、異なる電圧が供給される

半導体装置。

【請求項10】

半導体チップの第1面に形成された複数の第1電極パッドの各々と電気的に接続するように、第1配線テープを接着する工程と、

外部と接続する第1パッケージ端子と、前記第1配線テープとを第1接続部で電気的に接続する工程と

を具備する

半導体装置の製造方法。

【請求項11】

請求項10に記載の半導体装置の製造方法であって、

前記第1配線テープを接着する工程は、

前記第1面上に、前記第1配線テープを閉曲線状に接着する工程

を備える

半導体装置の製造方法。

【請求項12】

請求項11に記載の半導体装置の製造方法であって、

前記第1面に形成された、前記第1配線テープで囲まれた複数の第2電極パッドの各々と電気的に接続するように、第2配線テープを接着する工程と、

外部と接続する第2パッケージ端子と、前記第2配線テープとを第2接続部で電気的に接続する工程と

を更に具備する

半導体装置の製造方法。

【請求項13】

請求項11に記載の半導体装置の製造方法であって、

前記第1面に形成された、前記第1配線テープの外側の複数の第2電極パッドの各々と電気的に接続するように、第2配線テープを接着する工程と、

外部と接続する第2パッケージ端子と、前記第2配線テープとを第2接続部で電気的に接続する工程と

を更に具備する

半導体装置の製造方法。

【請求項14】

請求項12又は13に記載の半導体装置の製造方法であって、

前記第2配線テープを接着する工程は、

前記第1面上に、前記第2配線テープを閉曲線状に接着する工程

を備える

半導体装置の製造方法。

【請求項1】

複数の第1電極パッドを第1面に有する半導体チップと、

前記第1面上で、前記複数の第1電極パッドの各々と接触し、前記複数の第1電極パッドの各々を電気的に接続する第1配線テープと

を具備する

半導体装置。

【請求項2】

請求項1に記載の半導体装置であって、

前記第1配線テープは、前記第1面上で閉曲線状に配置される

半導体装置。

【請求項3】

請求項2に記載の半導体装置であって、

前記第1面上に第2配線テープ

を更に具備し、

前記半導体チップは、

前記第1配線テープで囲まれた前記第1面に、複数の第2電極パッド

を更に有し、

前記第2配線テープは、前記複数の第2電極パッドの各々と接触し、前記複数の第2電極パッドの各々を電気的に接続する

半導体装置。

【請求項4】

請求項3に記載の半導体装置であって、

前記第2配線テープは、前記第1面上で閉曲線状に配置される

半導体装置。

【請求項5】

請求項1乃至4の何れか一項に記載の半導体装置であって、

前記第1配線テープは、

前記複数の第1電極パッドの各々と接触する第1導体層と、

前記第1導体層の上に形成され、前記第1配線テープの表面に位置する第1絶縁層と

を備える

半導体装置。

【請求項6】

請求項3又は4に記載の半導体装置であって、

前記第1配線テープは、

前記複数の第1電極パッドの各々と接触する第1導体層と、

前記第1導体層の上に形成され、前記第1配線テープの表面に位置する第1絶縁層と

を備え、

前記第2配線テープは、

前記複数の第2電極パッドの各々と接触する第2導体層と、

前記第2導体層の上に形成され、前記第2配線テープの表面に位置する第2絶縁層と

を備える

半導体装置。

【請求項7】

請求項3乃至6の何れか一項に記載の半導体装置であって、

外部と接続する第1パッケージ端子と、

外部と接続する第2パッケージ端子と、

前記第1配線テープと、前記第1パッケージ端子とを電気的に接続する第1接続部と、

前記第2配線テープと、前記第2パッケージ端子とを電気的に接続する第2接続部と

を更に具備する

半導体装置。

【請求項8】

請求項7に記載の半導体装置であって、

前記第1接続部は、

前記第1配線テープと前記第1パッケージ端子とを電気的に接続する第3導体層と、

前記第3導体層の上に形成され、前記第1接続部の表面に位置する第3絶縁層と

を備え、

前記第2接続部は、

前記第2配線テープと前記第2パッケージ端子とを電気的に接続する第4導体層と、

前記第4導体層の上に形成され、前記第2接続部の表面に位置する第4絶縁層と

を備える

半導体装置。

【請求項9】

請求項7又は8に記載の半導体装置であって、

前記第1パッケージ端子と前記第2パッケージ端子とには、異なる電圧が供給される

半導体装置。

【請求項10】

半導体チップの第1面に形成された複数の第1電極パッドの各々と電気的に接続するように、第1配線テープを接着する工程と、

外部と接続する第1パッケージ端子と、前記第1配線テープとを第1接続部で電気的に接続する工程と

を具備する

半導体装置の製造方法。

【請求項11】

請求項10に記載の半導体装置の製造方法であって、

前記第1配線テープを接着する工程は、

前記第1面上に、前記第1配線テープを閉曲線状に接着する工程

を備える

半導体装置の製造方法。

【請求項12】

請求項11に記載の半導体装置の製造方法であって、

前記第1面に形成された、前記第1配線テープで囲まれた複数の第2電極パッドの各々と電気的に接続するように、第2配線テープを接着する工程と、

外部と接続する第2パッケージ端子と、前記第2配線テープとを第2接続部で電気的に接続する工程と

を更に具備する

半導体装置の製造方法。

【請求項13】

請求項11に記載の半導体装置の製造方法であって、

前記第1面に形成された、前記第1配線テープの外側の複数の第2電極パッドの各々と電気的に接続するように、第2配線テープを接着する工程と、

外部と接続する第2パッケージ端子と、前記第2配線テープとを第2接続部で電気的に接続する工程と

を更に具備する

半導体装置の製造方法。

【請求項14】

請求項12又は13に記載の半導体装置の製造方法であって、

前記第2配線テープを接着する工程は、

前記第1面上に、前記第2配線テープを閉曲線状に接着する工程

を備える

半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2011−159661(P2011−159661A)

【公開日】平成23年8月18日(2011.8.18)

【国際特許分類】

【出願番号】特願2010−17851(P2010−17851)

【出願日】平成22年1月29日(2010.1.29)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成23年8月18日(2011.8.18)

【国際特許分類】

【出願日】平成22年1月29日(2010.1.29)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]