半導体装置及び半導体装置の製造方法

【課題】一つのTEGで複数方向の位置ずれを検出できるようにする。

【解決手段】この半導体装置は、TEG300を有している。TEG300は、プラグ及び配線のいずれか一方である第1要素と、プラグ及び配線の他方である第2要素を有している。第2要素は、互いに異なる方向から第1要素に面しており、第1要素から離間している。本実施形態において、第1要素はプラグ320であり、第2要素は配線330である。プラグ320は、コンタクトであってもよいし、ビアであってもよい。またプラグ320は、配線330の上に位置していてもよいし、下に位置していてもよい。

【解決手段】この半導体装置は、TEG300を有している。TEG300は、プラグ及び配線のいずれか一方である第1要素と、プラグ及び配線の他方である第2要素を有している。第2要素は、互いに異なる方向から第1要素に面しており、第1要素から離間している。本実施形態において、第1要素はプラグ320であり、第2要素は配線330である。プラグ320は、コンタクトであってもよいし、ビアであってもよい。またプラグ320は、配線330の上に位置していてもよいし、下に位置していてもよい。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、TEG(Test Element Group)を有する半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置には、コンタクト又はビアと、配線との間の位置ずれを評価するためにTEGが設けられている。例えば特許文献1には、配線と、この配線に対する距離が互いに異なる複数のコンタクトとを有するTEGが開示されている。また特許文献2には、互いに異なる方向の位置ずれを検出することができる複数のTEGを設けることが開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開昭62−203340号公報

【特許文献2】特開2001−176782号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献2に記載するように、互いに異なる方向の位置ずれを検出するためには、複数のTEGを準備する必要がある。しかし、このようにするとTEGの占有面積が増える。また、互いに異なる場所にTEGを配置する必要があるため、原理的に同一の場所における位置ずれを複数方向で検出することができない。このため、一つのTEGで複数方向の位置ずれを検出できるようにすることが好ましい。

【課題を解決するための手段】

【0005】

本発明によれば、TEGを備えており、

前記TEGは、

プラグ及び配線のいずれか一方である第1要素と、

互いに異なる方向から前記第1要素に面しており、前記第1要素から離間しており、前記プラグ及び前記配線の他方である複数の第2要素と、

を備える半導体装置が提供される。

【0006】

本発明において、プラグと配線の相対位置に位置ずれが生じた場合、第2要素と第1要素の間の静電容量が変化したり、導通が生じるため、位置ずれを検出することができる。ここで、複数の第2要素は、互いに異なる方向から第1要素に面している。このため、一つのTEGで複数方向の位置ずれを検出できるようにすることができる。

【0007】

本発明によれば、多層配線層のいずれかの配線層に、TEGを形成する工程と、

最表層の配線層に、前記TEGに接続する第1テスト用パッド及び第2テスト用パッドを形成する工程と、

前記第1テスト用パッド及び前記第2テスト用パッドの間に電圧を印加し、前記第1テスト用パッドおよび前記第2テスト用パッドの間の容量、又は導通の有無を測定する検査工程と、

を備え、

前記TEGは、

プラグ及び配線のいずれか一方であり、前記第1テスト用パッドに接続している第1要素と、

互いに異なる方向から前記第1要素に面しており、前記第1要素から離間しており、前記プラグ及び前記配線の他方であり、前記第2テスト用パッドに接続している複数の第2要素と、

を有する半導体装置の製造方法が提供される。

【発明の効果】

【0008】

本発明によれば、一つのTEGで複数方向の位置ずれを検出できる。

【図面の簡単な説明】

【0009】

【図1】第1の実施形態に係る半導体装置の構成を示す平面図である。

【図2】図1に示したTEGのレイアウトを示す平面図である。

【図3】半導体チップを個片化するときのダイシングブレードの位置を示す平面図である。

【図4】第2の実施形態に係る半導体装置が有するTEGの構成を示す平面図である。

【図5】第3の実施形態に係る半導体装置が有するTEGの構成を示す平面図である。

【図6】第4の実施形態に係る半導体装置が有するTEGの構成を示す平面図である。

【発明を実施するための形態】

【0010】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0011】

(第1の実施形態)

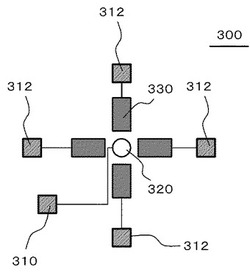

図1は、第1の実施形態に係る半導体装置の構成を示す平面図である。この半導体装置は、TEG300を有している。TEG300は、プラグ及び配線のいずれか一方である第1要素と、プラグ及び配線の他方である第2要素を有している。第2要素は、互いに異なる方向から第1要素に面しており、第1要素から離間している。本実施形態において、第1要素はプラグ320であり、第2要素は配線330である。プラグ320は、コンタクトであってもよいし、ビアであってもよい。またプラグ320は、配線330の上に位置していてもよいし、下に位置していてもよい。以下、詳細に説明する。

【0012】

本実施形態において、TEG300は配線330を4つ有している。4つの配線330は、プラグ320に対して90°間隔で配置されている。すなわちTEG300は、4方向の位置ずれを検出することができる。4つの配線330は、いずれもプラグ320からの距離が同一となるように設計されている。

【0013】

TEG300は、第1テスト用パッド310及び第2テスト用パッド312を有している。第1テスト用パッド310はプラグ320に接続しており、第2テスト用パッド312は配線330に接続している。本実施形態において、第2テスト用パッド312は複数設けられている。そして配線330は、互いに異なる第2テスト用パッド312に接続している。第1テスト用パッド310及び第2テスト用パッド312は、最上層の配線層に形成されている。

【0014】

図2は、図1に示したTEG300のレイアウトを示す平面図である。本図に示す状態において、半導体装置は複数の半導体チップが個片化されておらず、例えばウェハのままである。TEG300は、スクライブ領域20に設けられている。スクライブ領域20は、複数のチップ領域10を互いに分離する領域であり、図3に示すように、チップ領域10を個々の半導体チップに分割する際にダイシングブレード50が通る領域である。ただし図3に示すように、ダイシングブレード50の幅は、スクライブ領域20の幅より狭い。このため、個片化後の半導体チップにおいても、TEG300の少なくとも一部が残っている。

【0015】

次に、本実施形態に係る半導体装置の製造方法を説明する。まず、基板にトランジスタなどの素子を形成する。次いで、この基板上に多層配線層を形成する。このとき、少なくとも一つの配線層に、TEG300が形成される。また最上層の配線層に、第1テスト用パッド310及び第2テスト用パッド312が形成される。

【0016】

次いで、第1テスト用パッド310及び第2テスト用パッド312にプローブを接触させ、第1テスト用パッド310と第2テスト用パッド312の間の容量を測定する。プローブが接触している第2テスト用パッド312に接続している配線330と、プラグ320との距離が設計値からずれている場合、第1テスト用パッド310と第2テスト用パッド312の間の容量も設計値から変化している。そしてその変化量は、配線330とプラグ320の距離のずれに応じて変化する。従って、第1テスト用パッド310と第2テスト用パッド312の間の容量を測定し、その測定値が設計値からどの程度ずれているかを算出することにより、その第2テスト用パッド312に接続している配線330とプラグ320のずれ量を算出することができる。そして、この処理を、全ての第2テスト用パッド312に対して行う。これにより、プラグ320と配線330がどの方向にどの程度ずれているかを、算出できる。

【0017】

以上、本実施形態によれば、一つのTEG300で複数方向の位置ずれを検出できる。従って、一つのTEG300でどの方向にどの程度位置ずれが生じたかを検出することができる。このため、特定の場所における位置ずれを高い精度で検出することができる。

【0018】

(第2の実施形態)

図4は、第2の実施形態に係る半導体装置が有するTEG300の構成を示す平面図であり、第1の実施形態における図1に対応している。本実施形態に係るTEG300は、4つの配線330が同一の第2テスト用パッド312に接続している点を除いて、第1の実施形態に係るTEG300と同様である。

【0019】

本実施形態において、プラグ320と配線330の間で位置ずれが生じていた場合、第1テスト用パッド310と第2テスト用パッド312の間の容量が設計値から異なる。従って、プラグ320と配線330の間で位置ずれが生じていることを検出できる。また、測定された容量がどの程度設計値からずれているかを算出することにより、プラグ320と配線330がどの程度ずれているかを算出できる。また、第2テスト用パッド312の数を少なくすることができるため、TEG300の占有面積を小さくすることができる。

【0020】

(第3の実施形態)

図5は、第3の実施形態に係る半導体装置が有するTEG300の構成を示す平面図であり、第1の実施形態における図1に対応している。本実施形態に係るTEG300は、以下の点を除いて第1の実施形態に係るTEG300と同様の構成である。

【0021】

まず、配線330が一つ設けられており、その周囲に複数のプラグ320が形成されている。すなわち本実施形態では、配線330が第1要素であり、プラグ320が第2要素である。本図に示す例では、4つのプラグ320が90°おきに設けられている。また、第1テスト用パッド310は配線330に接続しており、複数の第2テスト用パッド312は、互いに異なるプラグ320に接続している。

【0022】

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。

【0023】

(第4の実施形態)

図6は、第4の実施形態に係る半導体装置が有するTEG300の構成を示す平面図であり、第3の実施形態における図5に対応している。本実施形態に係るTEG300は、複数のプラグ320が同一の第2テスト用パッド312に接続している点を除いて、第3の実施形態に係る半導体装置と同様である。

【0024】

本実施形態によっても、第2の実施形態と同様の効果を得ることができる。

【0025】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。例えば上記した各実施形態において、第1テスト用パッド310と第2テスト用パッド312の間での導通の有無を検出することにより、プラグ320と配線330の間の位置ずれを検出してもよい。

【符号の説明】

【0026】

10 チップ領域

20 スクライブ領域

50 ダイシングブレード

300 TEG

310 第1テスト用パッド

312 第2テスト用パッド

320 プラグ

330 配線

【技術分野】

【0001】

本発明は、TEG(Test Element Group)を有する半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置には、コンタクト又はビアと、配線との間の位置ずれを評価するためにTEGが設けられている。例えば特許文献1には、配線と、この配線に対する距離が互いに異なる複数のコンタクトとを有するTEGが開示されている。また特許文献2には、互いに異なる方向の位置ずれを検出することができる複数のTEGを設けることが開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開昭62−203340号公報

【特許文献2】特開2001−176782号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献2に記載するように、互いに異なる方向の位置ずれを検出するためには、複数のTEGを準備する必要がある。しかし、このようにするとTEGの占有面積が増える。また、互いに異なる場所にTEGを配置する必要があるため、原理的に同一の場所における位置ずれを複数方向で検出することができない。このため、一つのTEGで複数方向の位置ずれを検出できるようにすることが好ましい。

【課題を解決するための手段】

【0005】

本発明によれば、TEGを備えており、

前記TEGは、

プラグ及び配線のいずれか一方である第1要素と、

互いに異なる方向から前記第1要素に面しており、前記第1要素から離間しており、前記プラグ及び前記配線の他方である複数の第2要素と、

を備える半導体装置が提供される。

【0006】

本発明において、プラグと配線の相対位置に位置ずれが生じた場合、第2要素と第1要素の間の静電容量が変化したり、導通が生じるため、位置ずれを検出することができる。ここで、複数の第2要素は、互いに異なる方向から第1要素に面している。このため、一つのTEGで複数方向の位置ずれを検出できるようにすることができる。

【0007】

本発明によれば、多層配線層のいずれかの配線層に、TEGを形成する工程と、

最表層の配線層に、前記TEGに接続する第1テスト用パッド及び第2テスト用パッドを形成する工程と、

前記第1テスト用パッド及び前記第2テスト用パッドの間に電圧を印加し、前記第1テスト用パッドおよび前記第2テスト用パッドの間の容量、又は導通の有無を測定する検査工程と、

を備え、

前記TEGは、

プラグ及び配線のいずれか一方であり、前記第1テスト用パッドに接続している第1要素と、

互いに異なる方向から前記第1要素に面しており、前記第1要素から離間しており、前記プラグ及び前記配線の他方であり、前記第2テスト用パッドに接続している複数の第2要素と、

を有する半導体装置の製造方法が提供される。

【発明の効果】

【0008】

本発明によれば、一つのTEGで複数方向の位置ずれを検出できる。

【図面の簡単な説明】

【0009】

【図1】第1の実施形態に係る半導体装置の構成を示す平面図である。

【図2】図1に示したTEGのレイアウトを示す平面図である。

【図3】半導体チップを個片化するときのダイシングブレードの位置を示す平面図である。

【図4】第2の実施形態に係る半導体装置が有するTEGの構成を示す平面図である。

【図5】第3の実施形態に係る半導体装置が有するTEGの構成を示す平面図である。

【図6】第4の実施形態に係る半導体装置が有するTEGの構成を示す平面図である。

【発明を実施するための形態】

【0010】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0011】

(第1の実施形態)

図1は、第1の実施形態に係る半導体装置の構成を示す平面図である。この半導体装置は、TEG300を有している。TEG300は、プラグ及び配線のいずれか一方である第1要素と、プラグ及び配線の他方である第2要素を有している。第2要素は、互いに異なる方向から第1要素に面しており、第1要素から離間している。本実施形態において、第1要素はプラグ320であり、第2要素は配線330である。プラグ320は、コンタクトであってもよいし、ビアであってもよい。またプラグ320は、配線330の上に位置していてもよいし、下に位置していてもよい。以下、詳細に説明する。

【0012】

本実施形態において、TEG300は配線330を4つ有している。4つの配線330は、プラグ320に対して90°間隔で配置されている。すなわちTEG300は、4方向の位置ずれを検出することができる。4つの配線330は、いずれもプラグ320からの距離が同一となるように設計されている。

【0013】

TEG300は、第1テスト用パッド310及び第2テスト用パッド312を有している。第1テスト用パッド310はプラグ320に接続しており、第2テスト用パッド312は配線330に接続している。本実施形態において、第2テスト用パッド312は複数設けられている。そして配線330は、互いに異なる第2テスト用パッド312に接続している。第1テスト用パッド310及び第2テスト用パッド312は、最上層の配線層に形成されている。

【0014】

図2は、図1に示したTEG300のレイアウトを示す平面図である。本図に示す状態において、半導体装置は複数の半導体チップが個片化されておらず、例えばウェハのままである。TEG300は、スクライブ領域20に設けられている。スクライブ領域20は、複数のチップ領域10を互いに分離する領域であり、図3に示すように、チップ領域10を個々の半導体チップに分割する際にダイシングブレード50が通る領域である。ただし図3に示すように、ダイシングブレード50の幅は、スクライブ領域20の幅より狭い。このため、個片化後の半導体チップにおいても、TEG300の少なくとも一部が残っている。

【0015】

次に、本実施形態に係る半導体装置の製造方法を説明する。まず、基板にトランジスタなどの素子を形成する。次いで、この基板上に多層配線層を形成する。このとき、少なくとも一つの配線層に、TEG300が形成される。また最上層の配線層に、第1テスト用パッド310及び第2テスト用パッド312が形成される。

【0016】

次いで、第1テスト用パッド310及び第2テスト用パッド312にプローブを接触させ、第1テスト用パッド310と第2テスト用パッド312の間の容量を測定する。プローブが接触している第2テスト用パッド312に接続している配線330と、プラグ320との距離が設計値からずれている場合、第1テスト用パッド310と第2テスト用パッド312の間の容量も設計値から変化している。そしてその変化量は、配線330とプラグ320の距離のずれに応じて変化する。従って、第1テスト用パッド310と第2テスト用パッド312の間の容量を測定し、その測定値が設計値からどの程度ずれているかを算出することにより、その第2テスト用パッド312に接続している配線330とプラグ320のずれ量を算出することができる。そして、この処理を、全ての第2テスト用パッド312に対して行う。これにより、プラグ320と配線330がどの方向にどの程度ずれているかを、算出できる。

【0017】

以上、本実施形態によれば、一つのTEG300で複数方向の位置ずれを検出できる。従って、一つのTEG300でどの方向にどの程度位置ずれが生じたかを検出することができる。このため、特定の場所における位置ずれを高い精度で検出することができる。

【0018】

(第2の実施形態)

図4は、第2の実施形態に係る半導体装置が有するTEG300の構成を示す平面図であり、第1の実施形態における図1に対応している。本実施形態に係るTEG300は、4つの配線330が同一の第2テスト用パッド312に接続している点を除いて、第1の実施形態に係るTEG300と同様である。

【0019】

本実施形態において、プラグ320と配線330の間で位置ずれが生じていた場合、第1テスト用パッド310と第2テスト用パッド312の間の容量が設計値から異なる。従って、プラグ320と配線330の間で位置ずれが生じていることを検出できる。また、測定された容量がどの程度設計値からずれているかを算出することにより、プラグ320と配線330がどの程度ずれているかを算出できる。また、第2テスト用パッド312の数を少なくすることができるため、TEG300の占有面積を小さくすることができる。

【0020】

(第3の実施形態)

図5は、第3の実施形態に係る半導体装置が有するTEG300の構成を示す平面図であり、第1の実施形態における図1に対応している。本実施形態に係るTEG300は、以下の点を除いて第1の実施形態に係るTEG300と同様の構成である。

【0021】

まず、配線330が一つ設けられており、その周囲に複数のプラグ320が形成されている。すなわち本実施形態では、配線330が第1要素であり、プラグ320が第2要素である。本図に示す例では、4つのプラグ320が90°おきに設けられている。また、第1テスト用パッド310は配線330に接続しており、複数の第2テスト用パッド312は、互いに異なるプラグ320に接続している。

【0022】

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。

【0023】

(第4の実施形態)

図6は、第4の実施形態に係る半導体装置が有するTEG300の構成を示す平面図であり、第3の実施形態における図5に対応している。本実施形態に係るTEG300は、複数のプラグ320が同一の第2テスト用パッド312に接続している点を除いて、第3の実施形態に係る半導体装置と同様である。

【0024】

本実施形態によっても、第2の実施形態と同様の効果を得ることができる。

【0025】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。例えば上記した各実施形態において、第1テスト用パッド310と第2テスト用パッド312の間での導通の有無を検出することにより、プラグ320と配線330の間の位置ずれを検出してもよい。

【符号の説明】

【0026】

10 チップ領域

20 スクライブ領域

50 ダイシングブレード

300 TEG

310 第1テスト用パッド

312 第2テスト用パッド

320 プラグ

330 配線

【特許請求の範囲】

【請求項1】

TEGを備えており、

前記TEGは、

プラグ及び配線のいずれか一方である第1要素と、

互いに異なる方向から前記第1要素に面しており、前記第1要素から離間しており、前記プラグ及び前記配線の他方である複数の第2要素と、

を備える半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

4つの前記第2要素が、前記第1要素に対して90°間隔で配置されている半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、

前記第1要素に接続している第1テスト用パッドと、

互いに異なる前記第2要素に接続している複数の第2テスト用パッドと、

を備える半導体装置。

【請求項4】

請求項1又は2に記載の半導体装置において

前記第1要素に接続している第1テスト用パッドと、

前記複数の第2要素に接続している第2テスト用パッドと、

を備える半導体装置。

【請求項5】

多層配線層のいずれかの配線層に、TEGを形成する工程と、

最表層の配線層に、前記TEGに接続する第1テスト用パッド及び第2テスト用パッドを形成する工程と、

前記第1テスト用パッド及び前記第2テスト用パッドの間に電圧を印加し、前記第1テスト用パッドおよび前記第2テスト用パッドの間の容量、又は導通の有無を測定する検査工程と、

を備え、

前記TEGは、

プラグ及び配線のいずれか一方であり、前記第1テスト用パッドに接続している第1要素と、

互いに異なる方向から前記第1要素に面しており、前記第1要素から離間しており、前記プラグ及び前記配線の他方であり、前記第2テスト用パッドに接続している複数の第2要素と、

を有する半導体装置の製造方法。

【請求項6】

請求項5に記載の半導体装置の製造方法において、

4つの前記第2要素が、前記第1要素に対して90°間隔で配置されている半導体装置の製造方法。

【請求項7】

請求項5又は6に記載の半導体装置の製造方法において、

前記第2テスト用パッドは複数形成され、

前記複数の第2テスト用パッドは、互いに異なる前記第2要素に接続しており、

前記検査工程において、前記複数の第2テスト用パッドそれぞれに対し、前記第1テスト用パッドとの間の導通の有無を検査する半導体装置の製造方法。

【請求項8】

請求項5又は6に記載の半導体装置の製造方法において、

前記複数の第2要素は、同一の前記第2テスト用パッドに接続されている半導体装置の製造方法。

【請求項1】

TEGを備えており、

前記TEGは、

プラグ及び配線のいずれか一方である第1要素と、

互いに異なる方向から前記第1要素に面しており、前記第1要素から離間しており、前記プラグ及び前記配線の他方である複数の第2要素と、

を備える半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

4つの前記第2要素が、前記第1要素に対して90°間隔で配置されている半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、

前記第1要素に接続している第1テスト用パッドと、

互いに異なる前記第2要素に接続している複数の第2テスト用パッドと、

を備える半導体装置。

【請求項4】

請求項1又は2に記載の半導体装置において

前記第1要素に接続している第1テスト用パッドと、

前記複数の第2要素に接続している第2テスト用パッドと、

を備える半導体装置。

【請求項5】

多層配線層のいずれかの配線層に、TEGを形成する工程と、

最表層の配線層に、前記TEGに接続する第1テスト用パッド及び第2テスト用パッドを形成する工程と、

前記第1テスト用パッド及び前記第2テスト用パッドの間に電圧を印加し、前記第1テスト用パッドおよび前記第2テスト用パッドの間の容量、又は導通の有無を測定する検査工程と、

を備え、

前記TEGは、

プラグ及び配線のいずれか一方であり、前記第1テスト用パッドに接続している第1要素と、

互いに異なる方向から前記第1要素に面しており、前記第1要素から離間しており、前記プラグ及び前記配線の他方であり、前記第2テスト用パッドに接続している複数の第2要素と、

を有する半導体装置の製造方法。

【請求項6】

請求項5に記載の半導体装置の製造方法において、

4つの前記第2要素が、前記第1要素に対して90°間隔で配置されている半導体装置の製造方法。

【請求項7】

請求項5又は6に記載の半導体装置の製造方法において、

前記第2テスト用パッドは複数形成され、

前記複数の第2テスト用パッドは、互いに異なる前記第2要素に接続しており、

前記検査工程において、前記複数の第2テスト用パッドそれぞれに対し、前記第1テスト用パッドとの間の導通の有無を検査する半導体装置の製造方法。

【請求項8】

請求項5又は6に記載の半導体装置の製造方法において、

前記複数の第2要素は、同一の前記第2テスト用パッドに接続されている半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−164786(P2012−164786A)

【公開日】平成24年8月30日(2012.8.30)

【国際特許分類】

【出願番号】特願2011−23547(P2011−23547)

【出願日】平成23年2月7日(2011.2.7)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年8月30日(2012.8.30)

【国際特許分類】

【出願日】平成23年2月7日(2011.2.7)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]