半導体装置及び半導体装置の製造方法

【課題】低伝導度領域ができるだけ少なくなるグラフェン配線構造が可能な半導体装置を提供する。

【解決手段】半導体装置は、触媒金属膜220と、グラフェン膜230と、コンタクトプラグ240と、調整膜250と、を備える。触媒金属膜は、基板上に形成される。グラフェン膜は、触媒金属膜上に形成される。コンタクトプラグは、グラフェン膜と接続する。調整膜は、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に形成され、ディラック点位置をフェルミ準位に対してコンタクトプラグと接続する領域と同方向に調整する。

【解決手段】半導体装置は、触媒金属膜220と、グラフェン膜230と、コンタクトプラグ240と、調整膜250と、を備える。触媒金属膜は、基板上に形成される。グラフェン膜は、触媒金属膜上に形成される。コンタクトプラグは、グラフェン膜と接続する。調整膜は、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に形成され、ディラック点位置をフェルミ準位に対してコンタクトプラグと接続する領域と同方向に調整する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

グラフェンは炭素原子でシート状に構成されている実質的に2次元相当のナノ材料である。この材料は高電流密度耐性、超高移動度、高耐熱性、及び高機械的強度等極めて優れた物性を示す。そのため、カーボンナノチューブ同様半導体デバイスの配線材料として有望視されている。例えば、幅を10nm程度まで加工したグラフェンナノリボンは銅を上回る電気伝導度を示すことが理論的に予測されている。実際にグラフェンを配線材料に用いた配線構造を作製するには、電極、絶縁膜等様々な材料と組み合わせなければならない。アルミニウム(Al)、タングステン(W)、或いは銅(Cu)といった従来の配線材料と異なり、グラフェンは数原子層程度のシートであるため接触している材料によりその特性(キャリア密度、キャリアタイプ、移動度等)が大きく変化してしまう。例えば、グラフェン膜だけで宙に浮いた架橋部分に対して、電極であるAlが接触している部分ではAlによるドーピング効果によりディラック点が−0.6eV程度低くなる。これによりn−typeにドーピングされる。その結果、Al接触部分のキャリア密度は高くなるが架橋部分では変化がないことから、印加電圧−0.6〜0Vの間はnpn接合となってしまう。そのため、低伝導度の領域が形成されてしまうといった問題があった。

【0003】

また、半導体装置における配線構造では、通常、架橋部分を作製することは難しい。そのため、上層配線と下層配線との間を絶縁膜で絶縁する構造が一般的である。しかし、上述したAlと同様、絶縁膜、例えばシリコン酸化膜が接触することでグラフェンのディラック点は+数eV以上ずれる。配線構造では、コンタクト以外の領域は絶縁膜と接触するため、電極としてAlを接触させた場合よりもさらに広い低伝導度領域が形成されてしまう。これは配線構造としては不適であり、低伝導度領域ができるだけ少なくなるグラフェン配線構造が求められる。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】Physical review letters,104,076807,(2010)

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の実施形態は、上述した問題点を克服し、低伝導度領域ができるだけ少なくなるグラフェン配線構造が可能な装置および製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

実施形態の半導体装置は、触媒金属膜と、グラフェン膜と、コンタクトプラグと、調整膜と、を備えている。触媒金属膜は、基板上に形成される。グラフェン膜は、触媒金属膜上に形成される。コンタクトプラグは、グラフェン膜と接続する。調整膜は、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に形成され、ディラック点位置をフェルミ準位に対して前記コンタクトプラグと接続する領域と同方向に調整する。

【0007】

実施形態の半導体装置の製造方法は、基板上に触媒金属膜を形成する工程と、前記触媒金属膜上にグラフェン膜を形成する工程と、前記グラフェン膜と接続するコンタクトプラグを形成する工程と、前記コンタクトプラグを形成する前に、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に、ディラック点位置をフェルミ準位に対して前記コンタクトプラグと接続する領域と同方向に調整する調整膜を形成する工程と、を備える。

【図面の簡単な説明】

【0008】

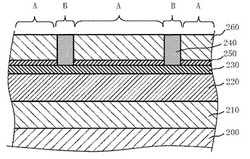

【図1】第1の実施形態における半導体装置の構成を示す図である。

【図2】第1の実施形態におけるエネルギーバンドのグラフの一例を示す図である。

【図3】第1の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図である。

【図4】第1の実施形態における半導体装置の製造方法の断面工程図である。

【図5】第1の実施形態における配線を示す上面図である。

【図6】第1の実施形態における半導体装置の製造方法の断面工程図である。

【図7】第1の実施形態における半導体装置の多層配線構成を示す図である。

【図8】第2の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図である。

【図9】第2の実施形態における半導体装置の構成を示す図である。

【発明を実施するための形態】

【0009】

(第1の実施形態)

第1の実施形態について、以下、図面を用いて説明する。

【0010】

図1は、第1の実施形態における半導体装置の構成を示す図である。図1において、基板200上に下層配線構造210が形成される。そして、下層配線構造210上にグラフェンを形成する際に触媒作用をもつ触媒金属膜220が形成される。そして、触媒金属膜220上にグラフェン膜230が形成される。グラフェン膜230上には、上層配線へと接続するコンタクトプラグ240が接続される。一方、グラフェン膜230表面のうち、コンタクトプラグ240と接続する領域B以外の領域A上には、調整膜250(ドーピング用薄膜)が形成される。そして、調整膜250上に絶縁膜260が形成される。

【0011】

第1の実施形態では、グラフェン膜230とコンタクトプラグ240と接続する領域Bでは、配線構造が触媒金属膜220とグラフェン膜230との2層構造となるが、領域B以外の領域Aでは、触媒金属膜220とグラフェン膜230と調整膜250との3層構造となる。上述したように、グラフェンは数原子層程度のシートであるため、接触している材料によりその特性(キャリア密度、キャリアタイプ、移動度等)は大きく変化してしまう。そのため、領域Aにおいて、グラフェンの表面側に調整膜250を形成せずに直接絶縁膜260と接触させてしまうと、コンタクトプラグ240と接続する領域Bと、それ以外の領域Aとの間でドーピングタイプの異なる動作領域が発生し、高抵抗な配線となってしまう。これに対して、第1の実施形態では、領域Aにおいて、グラフェン膜230の表面でまず調整膜250と接触させることで直接絶縁膜260と接触させない構造とする。調整膜250は、グラフェン膜230表面のうちの領域Aについて、コンタクトプラグ240と接続する領域Bとドーピングタイプを合わせると共にドーピングレベルの差を可能な限り抑える。言い換えれば、調整膜250は、ディラック点位置をフェルミ準位に対してコンタクトプラグ240と接続する領域Bと同方向に調整する。さらに、調整膜250は、ディラック点位置をフェルミ準位に対してコンタクトプラグ240と接続する領域Bと同程度に調整する。これにより、低抵抗なグラフェン配線構造を形成できる。

【0012】

図2は、第1の実施形態におけるエネルギーバンドのグラフの一例を示す図である。図2(a)は、コンタクトプラグ240と接続する領域Bにおけるグラフェン膜230表面でのエネルギーバンドの一例を示す。図2(b)は、調整膜250と接続する領域Aにおけるグラフェン膜230表面でのエネルギーバンドの一例を示す。各グラフにおいて、縦軸は、エネルギーEを示し、横軸は、波数Kを示す。図2(a)(b)共に、グラフェン膜230が他の膜と接触していない状態でのエネルギーバンドは点線で示される。かかるグラフェン単独の状態では、グラフが交差するディラック点C,Dの位置は、フェルミ準位Efに一致している。かかる状態からグラフェン膜230にコンタクトプラグ240を接続すると、図2(a)の実線のグラフに示すように、フェルミ準位Efに対してディラック点位置がC位置からC‘位置へと移動してしまう。図2(a)の例では、ディラック点位置がマイナス側に移動してしまう。そこで、第1の実施形態では、コンタクトプラグ240と接続しない領域Aについて、調整膜250を形成してグラフェン膜230に接触させることで、図2(b)の実線のグラフに示すように、ディラック点位置をD位置からD’位置へと移動させる。このように、調整膜250は、領域Aについて、フェルミ準位に対してコンタクトプラグ240と接続する領域Bと同方向に調整する。ここでは、コンタクトプラグ240と同様、マイナス側に移動させる。さらに、調整膜250は、ディラック点位置をフェルミ準位に対してコンタクトプラグ240と接続する領域Bと同程度に調整する。これにより、領域A,B間でのディラック点位置の差が小さくなり高抵抗領域の形成を抑制できる。ここで、グラフェン膜230表面のうちコンタクトプラグ240と接続する領域Bにおけるディラック点位置C’と、残りの調整膜250と接続する領域Aにおけるディラック点位置D’との差Δが、±0.5eV以下になるように調整すると好適である。

【0013】

調整膜250の材料としては、金(Au)、パラジウム(Pd)、銀(Ag)、タンタル(Ta)、ガリウム(Ga)等のいずれかが好適である。但し、これに限るものではない。調整膜250の材料としては、コンタクトプラグ240と接続する領域Bとドーピングタイプを合わせると共にドーピングレベルの差を抑えることが可能な材料であればよく、金属、有機化合物、或いは無機化合物のいずれであってもよい。

【0014】

さらに、調整膜250を形成することで、グラフェン膜230表面のうち調整膜250と接続する領域Aにおけるエネルギーバンド構造が、図2(b)の実線のグラフに示すように、ディラック点D‘を含むエネルギー軸方向の仮想直線(一点鎖線)に対して線対称にできる。同様に、図2(b)の実線のグラフに示すように、ディラック点D’を含む波数K軸方向の仮想直線(図示せず)に対して線対称にできる。これらのエネルギーバンド構造を維持することで、超高移動度、及び低抵抗率といったグラフェンが本来もつ特性を維持できる。

【0015】

図3は、第1の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図である。第1の実施形態における半導体装置の製造方法は、下層配線構造形成工程(S102)と、触媒金属膜形成工程(S104)と、グラフェン膜形成工程(S106)と、調整膜形成工程(S112)と、絶縁膜形成工程(S114)と、開口部形成工程(S116)と、コンタクトプラグ形成工程(S118)といった一連の工程を実施する。

【0016】

図4は、第1の実施形態における半導体装置の製造方法の断面工程図である。図4では、図3の絶縁膜形成工程(S102)から調整膜形成工程(S112)までを示している。

【0017】

図4(a)において、下層配線構造形成工程(S102)として、基板200上に下層配線構造210を形成する。基板200として、例えば、300mmのシリコンウェハが用いられると好適である。基板200内には、図示しない各種デバイス部分等が形成される。また、その他の配線等が形成されていてもよい。

【0018】

図4(b)において、触媒金属膜形成工程(S104)として、下層配線構造210上に触媒金属膜220を形成する。例えば、100nm以下の膜厚で形成するとよい。そして、リソグラフィ技術を用いて触媒金属膜220を配線幅に加工する。例えば、10nmの配線幅に加工される。触媒金属膜220は、グラフェン成長に適した触媒作用を有する材料で形成される。触媒金属膜220の材料として、コバルト(Co)と、ニッケル(Ni)と、鉄(Fe)と、銅(Cu)と、ルテニウム(Ru)と、白金(Pt)との少なくとも1つ、又はこれらの少なくとも1つが含まれた合金が用いられると好適である。特に、Co、或いはNiがより望ましい。

【0019】

図4(c)において、グラフェン膜形成工程(S106)として、触媒金属膜220上にグラフェン膜230を形成する。前工程で配線幅が10nmの触媒金属膜が形成されていれば、その部分のみにグラフェン膜230が形成される。グラフェン膜230は、CVD法で形成すればよい。成膜は、400℃〜800℃程度の温度領域でメタン、アセチレン等の炭素系ガスを熱的またはプラズマを用いて分解して炭素原子を供給することで行われる。グラフェン膜230は、触媒金属膜220を触媒として触媒金属膜220上に成長する。グラフェン膜230は、例えば、3nm〜100nmの膜厚で形成するとよい。但し、これに限るものではなく、膜厚が3nmよりも薄くなる1層の膜であってもよい。ここでは、1〜20層の層数で形成されると好適である。グラフェン膜230は、10層の膜で積層されるとより好適である。いずれの材料の触媒金属膜220であってもかかる触媒金属膜220の影響を受けずにグラフェンが本来もつ高移動度の特性を発揮できる。

【0020】

図5は、第1の実施形態における配線を示す上面図である。図5において、絶縁膜210上に、触媒金属膜220とグラフェン膜230とが配線幅で形成される。ここでは、1:1のラインアンドスペースパターンで配線が形成された例を示している。なお、図5では、配線パターンの一例を説明するために、下層配線構造210、触媒金属膜220、及びグラフェン膜230だけが示されているが、上述した各図及び以降の各図における半導体装置の断面は、それぞれ、図5におけるA−A断面に相当する位置での構成を示している。

【0021】

ここで、グラフェン膜230の結晶性(結晶方位、結晶品質、平坦性等)を制御するために、触媒金属膜220の直下に下地層を挿入しても良い。下地層の材料は、例えば、チタン(Ti)、窒化チタン(TiN)、窒化タンタル(TaN)、或いはタンタル(Ta)等がある。

【0022】

図4(d)において、調整膜形成工程(S112)として、グラフェン膜230表面上及び露出する下層配線構造210上に調整膜250を形成する。形成方法は、CVD法、蒸着法、めっき法、或いはスパッタ法で形成すればよい。そして、リソグラフィ技術を用いて、グラフェン膜230上だけに調整膜250が残るように加工する。調整膜250は、グラフェン膜230表面の調整を行う膜であるため厚膜は必要でなく、1−10nm程度で十分である。調整膜250の材料としては、Au、Pd、Ag、Ta、Ga等のいずれかが好適である。特に、コンタクトプラグ240の材料がNiの場合には、調整膜250の材料としてAu或いはPdがより望ましく、コンタクトプラグ240の材料がTiの場合には、調整膜250の材料としてAg、Ta、或いはGaがより望ましい。

【0023】

ここで、上述した例では、触媒金属膜220/グラフェン膜230/調整膜250の3層構造において、1層ごとにかかる3層が重なるように配線幅への加工を行った例を示したが、これに限るものではない。例えば、触媒金属膜220/グラフェン膜230の2層を基板全面に形成した後にかかる2層について配線幅への加工を行い、その後、調整膜250を基板全面に形成し、それから調整膜250をグラフェン膜230の配線幅に合わせてグラフェン膜230表面上にだけ残るように加工してもよい。或いは、触媒金属膜220/グラフェン膜230/調整膜250の3層を基板全面に形成した後にかかる3層について配線幅への加工を行ってもよい。

【0024】

図6は、第1の実施形態における半導体装置の製造方法の断面工程図である。図6では、図3の絶縁膜形成工程(S114)からコンタクトプラグ形成工程(S118)までを示している。

【0025】

図6(a)において、絶縁膜形成工程(S114)として、調整膜250上及び露出した下層配線構造210上に絶縁膜260をCVD法にて形成する。絶縁膜260の材料として、例えば、SiO2、SiOC等が挙げられる。

【0026】

図6(b)において、開口部形成工程(S116)として、リソグラフィ技術を用いて、コンタクトプラグを形成するためのヴィアホールとなる開口部150を形成する。ここでは、絶縁膜260とその下の調整膜250を開口し、グラフェン膜230表面を露出させる。

【0027】

図6(c)において、コンタクトプラグ形成工程(S118)として、開口部150にコンタクト材料を埋め込み、グラフェン膜230表面のコンタクト位置上にコンタクトプラグ240を形成する。コンタクトプラグ240の材料として、金属が用いられる。コンタクト金属として、例えば、銀(Ag)と、アルミニウム(Al)と、金(Au)と、コバルト(Co)と、クロム(Cr)と、銅(Cu)と、鉄(Fe)と、ニッケル(Ni)と、タンタル(Ta)と、チタン(Ti)、タングステン(W)と、バナジウム(V)との少なくとも1つ、又はこれらの少なくとも1つが含まれた合金が用いられると好適である。上記コンタクトプラグの材料はグラフェン膜の配線材料としての特性を十分に引き出すために選択されていることから、極端にはコンタクトプラグ最下部数nm程度が上記材料であればよく、その他の部分は低抵抗な材料、例えばCu、W、で形成されていてもよい。

【0028】

そして、化学機械研磨(CMP)法にて絶縁膜260上にはみ出た余分なコンタクトプラグ240材料を研磨除去して、図1に示した配線構造を持つ半導体装置を形成する。

【0029】

以上のように第1の実施形態によれば、コンタクトプラグ240と接触しない領域Aのディラック点位置を、フェルミ準位に対してコンタクトプラグ240と接続する領域Bと同方向に調整し、さらに同程度に調整する。これにより、領域A,B間でのディラック点位置の差が小さくなり高抵抗領域の形成を抑制できる。さらに、グラフェンの特性も維持できる。よって、従来のCu配線に比べて低抵抗な配線を実現できる。

【0030】

図7は、第1の実施形態における半導体装置の多層配線構成を示す図である。図1で示した状態から、さらに、触媒金属膜形成工程(S104)からコンタクトプラグ形成工程(S118)までを繰り返すことで、図7に示すような多層配線構造を形成できる。図7に示す多層配線構造の2層目では、絶縁膜260上に触媒金属膜222が形成される。そして、触媒金属膜222上にグラフェン膜232が形成される。グラフェン膜232上には、上層配線へと接続するコンタクトプラグ242が接続される。一方、グラフェン膜232表面のうち、コンタクトプラグ242と接続する領域以外の領域上には、調整膜252(ドーピング用薄膜)が形成される。そして、調整膜252上に絶縁膜262が形成される。多層配線構造の3層目では、絶縁膜262上に触媒金属膜224が形成される。そして、触媒金属膜224上にグラフェン膜234が形成される。グラフェン膜234上には、上層配線へと接続するコンタクトプラグ244が接続される。一方、グラフェン膜234表面のうち、コンタクトプラグ244と接続する領域以外の領域上には、調整膜254(ドーピング用薄膜)が形成される。そして、調整膜254上に絶縁膜264が形成される。図7では、配線とコンタクトの組が3層の配線構造を示したが、さらに、多層化してもよい。

【0031】

(第2の実施形態)

第2の実施形態では、さらに、調整膜250と絶縁膜260と間にバリアメタル膜を形成する場合について説明する。

【0032】

図8は、第2の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図である。第2の実施形態における半導体装置の製造方法は、調整膜形成工程(S112)と絶縁膜形成工程(S114)との間に、バリアメタル膜形成工程(S113)を追加した点以外は、図3と同様である。また、以下、特に説明した内容以外の内容は第1の実施形態と同様である。

【0033】

バリアメタル膜形成工程(S113)として、図4(d)で示した状態から、調整膜250上にバリアメタル膜270を形成する。ここでは、例えば、基板全面に形成された調整膜250上にバリアメタル膜270を形成し、リソグラフィ技術を用いて、調整膜250とバリアメタル膜270の2層を一緒に配線幅へと加工する。或いは、配線幅に加工済みの調整膜250上にバリアメタル膜270を基板全面に形成し、その後にリソグラフィ技術を用いてバリアメタル膜270を配線幅へと加工してもよい。そして、絶縁膜形成工程(S114)において、バリアメタル膜270上及び露出した下層配線構造210上に絶縁膜260を形成する。そして、開口部形成工程(S116)及びコンタクトプラグ形成工程(S118)を行えばよい。バリアメタル膜270の材料として、Ti、TiN、TaN、或いはRu等が好適である。形成方法は、スパッタ法等で形成すればよい。

【0034】

図9は、第2の実施形態における半導体装置の構成を示す図である。図9において、調整膜250と絶縁膜260との間にバリアメタル膜270が形成される。その他の構成は、図1と同様である。バリアメタル膜270を形成することで、調整膜250の材料が絶縁膜260へと拡散することを防止できる。

【0035】

以上、具体例を参照しつつ実施形態について説明した。しかし、本発明は、これらの具体例に限定されるものではない。また、上述した半導体装置の構成は、各種用途の半導体装置に適用可能である。いずれの用途でも高速配線を実現できる。例えば、メモリ装置、特に、NAND型のメモリ装置等に有効である。

【0036】

また、各層(膜)の膜厚や、開口部のサイズ、形状、数などについても、半導体集積回路や各種の半導体素子において必要とされるものを適宜選択して用いることができる。

【0037】

その他、本発明の要素を具備し、当業者が適宜設計変更しうる全ての半導体装置の製造方法は、本発明の範囲に包含される。

【0038】

また、説明の簡便化のために、半導体産業で通常用いられる手法、例えば、フォトリソグラフィプロセス、処理前後のクリーニング等は省略しているが、それらの手法が含まれ得ることは言うまでもない。

【符号の説明】

【0039】

200 基板、210,260 絶縁膜、220,222.224 触媒金属膜、230,232,234 グラフェン膜、240,242,244 コンタクトプラグ、250,252,254 調整膜

【技術分野】

【0001】

本発明の実施形態は、半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

グラフェンは炭素原子でシート状に構成されている実質的に2次元相当のナノ材料である。この材料は高電流密度耐性、超高移動度、高耐熱性、及び高機械的強度等極めて優れた物性を示す。そのため、カーボンナノチューブ同様半導体デバイスの配線材料として有望視されている。例えば、幅を10nm程度まで加工したグラフェンナノリボンは銅を上回る電気伝導度を示すことが理論的に予測されている。実際にグラフェンを配線材料に用いた配線構造を作製するには、電極、絶縁膜等様々な材料と組み合わせなければならない。アルミニウム(Al)、タングステン(W)、或いは銅(Cu)といった従来の配線材料と異なり、グラフェンは数原子層程度のシートであるため接触している材料によりその特性(キャリア密度、キャリアタイプ、移動度等)が大きく変化してしまう。例えば、グラフェン膜だけで宙に浮いた架橋部分に対して、電極であるAlが接触している部分ではAlによるドーピング効果によりディラック点が−0.6eV程度低くなる。これによりn−typeにドーピングされる。その結果、Al接触部分のキャリア密度は高くなるが架橋部分では変化がないことから、印加電圧−0.6〜0Vの間はnpn接合となってしまう。そのため、低伝導度の領域が形成されてしまうといった問題があった。

【0003】

また、半導体装置における配線構造では、通常、架橋部分を作製することは難しい。そのため、上層配線と下層配線との間を絶縁膜で絶縁する構造が一般的である。しかし、上述したAlと同様、絶縁膜、例えばシリコン酸化膜が接触することでグラフェンのディラック点は+数eV以上ずれる。配線構造では、コンタクト以外の領域は絶縁膜と接触するため、電極としてAlを接触させた場合よりもさらに広い低伝導度領域が形成されてしまう。これは配線構造としては不適であり、低伝導度領域ができるだけ少なくなるグラフェン配線構造が求められる。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】Physical review letters,104,076807,(2010)

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の実施形態は、上述した問題点を克服し、低伝導度領域ができるだけ少なくなるグラフェン配線構造が可能な装置および製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

実施形態の半導体装置は、触媒金属膜と、グラフェン膜と、コンタクトプラグと、調整膜と、を備えている。触媒金属膜は、基板上に形成される。グラフェン膜は、触媒金属膜上に形成される。コンタクトプラグは、グラフェン膜と接続する。調整膜は、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に形成され、ディラック点位置をフェルミ準位に対して前記コンタクトプラグと接続する領域と同方向に調整する。

【0007】

実施形態の半導体装置の製造方法は、基板上に触媒金属膜を形成する工程と、前記触媒金属膜上にグラフェン膜を形成する工程と、前記グラフェン膜と接続するコンタクトプラグを形成する工程と、前記コンタクトプラグを形成する前に、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に、ディラック点位置をフェルミ準位に対して前記コンタクトプラグと接続する領域と同方向に調整する調整膜を形成する工程と、を備える。

【図面の簡単な説明】

【0008】

【図1】第1の実施形態における半導体装置の構成を示す図である。

【図2】第1の実施形態におけるエネルギーバンドのグラフの一例を示す図である。

【図3】第1の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図である。

【図4】第1の実施形態における半導体装置の製造方法の断面工程図である。

【図5】第1の実施形態における配線を示す上面図である。

【図6】第1の実施形態における半導体装置の製造方法の断面工程図である。

【図7】第1の実施形態における半導体装置の多層配線構成を示す図である。

【図8】第2の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図である。

【図9】第2の実施形態における半導体装置の構成を示す図である。

【発明を実施するための形態】

【0009】

(第1の実施形態)

第1の実施形態について、以下、図面を用いて説明する。

【0010】

図1は、第1の実施形態における半導体装置の構成を示す図である。図1において、基板200上に下層配線構造210が形成される。そして、下層配線構造210上にグラフェンを形成する際に触媒作用をもつ触媒金属膜220が形成される。そして、触媒金属膜220上にグラフェン膜230が形成される。グラフェン膜230上には、上層配線へと接続するコンタクトプラグ240が接続される。一方、グラフェン膜230表面のうち、コンタクトプラグ240と接続する領域B以外の領域A上には、調整膜250(ドーピング用薄膜)が形成される。そして、調整膜250上に絶縁膜260が形成される。

【0011】

第1の実施形態では、グラフェン膜230とコンタクトプラグ240と接続する領域Bでは、配線構造が触媒金属膜220とグラフェン膜230との2層構造となるが、領域B以外の領域Aでは、触媒金属膜220とグラフェン膜230と調整膜250との3層構造となる。上述したように、グラフェンは数原子層程度のシートであるため、接触している材料によりその特性(キャリア密度、キャリアタイプ、移動度等)は大きく変化してしまう。そのため、領域Aにおいて、グラフェンの表面側に調整膜250を形成せずに直接絶縁膜260と接触させてしまうと、コンタクトプラグ240と接続する領域Bと、それ以外の領域Aとの間でドーピングタイプの異なる動作領域が発生し、高抵抗な配線となってしまう。これに対して、第1の実施形態では、領域Aにおいて、グラフェン膜230の表面でまず調整膜250と接触させることで直接絶縁膜260と接触させない構造とする。調整膜250は、グラフェン膜230表面のうちの領域Aについて、コンタクトプラグ240と接続する領域Bとドーピングタイプを合わせると共にドーピングレベルの差を可能な限り抑える。言い換えれば、調整膜250は、ディラック点位置をフェルミ準位に対してコンタクトプラグ240と接続する領域Bと同方向に調整する。さらに、調整膜250は、ディラック点位置をフェルミ準位に対してコンタクトプラグ240と接続する領域Bと同程度に調整する。これにより、低抵抗なグラフェン配線構造を形成できる。

【0012】

図2は、第1の実施形態におけるエネルギーバンドのグラフの一例を示す図である。図2(a)は、コンタクトプラグ240と接続する領域Bにおけるグラフェン膜230表面でのエネルギーバンドの一例を示す。図2(b)は、調整膜250と接続する領域Aにおけるグラフェン膜230表面でのエネルギーバンドの一例を示す。各グラフにおいて、縦軸は、エネルギーEを示し、横軸は、波数Kを示す。図2(a)(b)共に、グラフェン膜230が他の膜と接触していない状態でのエネルギーバンドは点線で示される。かかるグラフェン単独の状態では、グラフが交差するディラック点C,Dの位置は、フェルミ準位Efに一致している。かかる状態からグラフェン膜230にコンタクトプラグ240を接続すると、図2(a)の実線のグラフに示すように、フェルミ準位Efに対してディラック点位置がC位置からC‘位置へと移動してしまう。図2(a)の例では、ディラック点位置がマイナス側に移動してしまう。そこで、第1の実施形態では、コンタクトプラグ240と接続しない領域Aについて、調整膜250を形成してグラフェン膜230に接触させることで、図2(b)の実線のグラフに示すように、ディラック点位置をD位置からD’位置へと移動させる。このように、調整膜250は、領域Aについて、フェルミ準位に対してコンタクトプラグ240と接続する領域Bと同方向に調整する。ここでは、コンタクトプラグ240と同様、マイナス側に移動させる。さらに、調整膜250は、ディラック点位置をフェルミ準位に対してコンタクトプラグ240と接続する領域Bと同程度に調整する。これにより、領域A,B間でのディラック点位置の差が小さくなり高抵抗領域の形成を抑制できる。ここで、グラフェン膜230表面のうちコンタクトプラグ240と接続する領域Bにおけるディラック点位置C’と、残りの調整膜250と接続する領域Aにおけるディラック点位置D’との差Δが、±0.5eV以下になるように調整すると好適である。

【0013】

調整膜250の材料としては、金(Au)、パラジウム(Pd)、銀(Ag)、タンタル(Ta)、ガリウム(Ga)等のいずれかが好適である。但し、これに限るものではない。調整膜250の材料としては、コンタクトプラグ240と接続する領域Bとドーピングタイプを合わせると共にドーピングレベルの差を抑えることが可能な材料であればよく、金属、有機化合物、或いは無機化合物のいずれであってもよい。

【0014】

さらに、調整膜250を形成することで、グラフェン膜230表面のうち調整膜250と接続する領域Aにおけるエネルギーバンド構造が、図2(b)の実線のグラフに示すように、ディラック点D‘を含むエネルギー軸方向の仮想直線(一点鎖線)に対して線対称にできる。同様に、図2(b)の実線のグラフに示すように、ディラック点D’を含む波数K軸方向の仮想直線(図示せず)に対して線対称にできる。これらのエネルギーバンド構造を維持することで、超高移動度、及び低抵抗率といったグラフェンが本来もつ特性を維持できる。

【0015】

図3は、第1の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図である。第1の実施形態における半導体装置の製造方法は、下層配線構造形成工程(S102)と、触媒金属膜形成工程(S104)と、グラフェン膜形成工程(S106)と、調整膜形成工程(S112)と、絶縁膜形成工程(S114)と、開口部形成工程(S116)と、コンタクトプラグ形成工程(S118)といった一連の工程を実施する。

【0016】

図4は、第1の実施形態における半導体装置の製造方法の断面工程図である。図4では、図3の絶縁膜形成工程(S102)から調整膜形成工程(S112)までを示している。

【0017】

図4(a)において、下層配線構造形成工程(S102)として、基板200上に下層配線構造210を形成する。基板200として、例えば、300mmのシリコンウェハが用いられると好適である。基板200内には、図示しない各種デバイス部分等が形成される。また、その他の配線等が形成されていてもよい。

【0018】

図4(b)において、触媒金属膜形成工程(S104)として、下層配線構造210上に触媒金属膜220を形成する。例えば、100nm以下の膜厚で形成するとよい。そして、リソグラフィ技術を用いて触媒金属膜220を配線幅に加工する。例えば、10nmの配線幅に加工される。触媒金属膜220は、グラフェン成長に適した触媒作用を有する材料で形成される。触媒金属膜220の材料として、コバルト(Co)と、ニッケル(Ni)と、鉄(Fe)と、銅(Cu)と、ルテニウム(Ru)と、白金(Pt)との少なくとも1つ、又はこれらの少なくとも1つが含まれた合金が用いられると好適である。特に、Co、或いはNiがより望ましい。

【0019】

図4(c)において、グラフェン膜形成工程(S106)として、触媒金属膜220上にグラフェン膜230を形成する。前工程で配線幅が10nmの触媒金属膜が形成されていれば、その部分のみにグラフェン膜230が形成される。グラフェン膜230は、CVD法で形成すればよい。成膜は、400℃〜800℃程度の温度領域でメタン、アセチレン等の炭素系ガスを熱的またはプラズマを用いて分解して炭素原子を供給することで行われる。グラフェン膜230は、触媒金属膜220を触媒として触媒金属膜220上に成長する。グラフェン膜230は、例えば、3nm〜100nmの膜厚で形成するとよい。但し、これに限るものではなく、膜厚が3nmよりも薄くなる1層の膜であってもよい。ここでは、1〜20層の層数で形成されると好適である。グラフェン膜230は、10層の膜で積層されるとより好適である。いずれの材料の触媒金属膜220であってもかかる触媒金属膜220の影響を受けずにグラフェンが本来もつ高移動度の特性を発揮できる。

【0020】

図5は、第1の実施形態における配線を示す上面図である。図5において、絶縁膜210上に、触媒金属膜220とグラフェン膜230とが配線幅で形成される。ここでは、1:1のラインアンドスペースパターンで配線が形成された例を示している。なお、図5では、配線パターンの一例を説明するために、下層配線構造210、触媒金属膜220、及びグラフェン膜230だけが示されているが、上述した各図及び以降の各図における半導体装置の断面は、それぞれ、図5におけるA−A断面に相当する位置での構成を示している。

【0021】

ここで、グラフェン膜230の結晶性(結晶方位、結晶品質、平坦性等)を制御するために、触媒金属膜220の直下に下地層を挿入しても良い。下地層の材料は、例えば、チタン(Ti)、窒化チタン(TiN)、窒化タンタル(TaN)、或いはタンタル(Ta)等がある。

【0022】

図4(d)において、調整膜形成工程(S112)として、グラフェン膜230表面上及び露出する下層配線構造210上に調整膜250を形成する。形成方法は、CVD法、蒸着法、めっき法、或いはスパッタ法で形成すればよい。そして、リソグラフィ技術を用いて、グラフェン膜230上だけに調整膜250が残るように加工する。調整膜250は、グラフェン膜230表面の調整を行う膜であるため厚膜は必要でなく、1−10nm程度で十分である。調整膜250の材料としては、Au、Pd、Ag、Ta、Ga等のいずれかが好適である。特に、コンタクトプラグ240の材料がNiの場合には、調整膜250の材料としてAu或いはPdがより望ましく、コンタクトプラグ240の材料がTiの場合には、調整膜250の材料としてAg、Ta、或いはGaがより望ましい。

【0023】

ここで、上述した例では、触媒金属膜220/グラフェン膜230/調整膜250の3層構造において、1層ごとにかかる3層が重なるように配線幅への加工を行った例を示したが、これに限るものではない。例えば、触媒金属膜220/グラフェン膜230の2層を基板全面に形成した後にかかる2層について配線幅への加工を行い、その後、調整膜250を基板全面に形成し、それから調整膜250をグラフェン膜230の配線幅に合わせてグラフェン膜230表面上にだけ残るように加工してもよい。或いは、触媒金属膜220/グラフェン膜230/調整膜250の3層を基板全面に形成した後にかかる3層について配線幅への加工を行ってもよい。

【0024】

図6は、第1の実施形態における半導体装置の製造方法の断面工程図である。図6では、図3の絶縁膜形成工程(S114)からコンタクトプラグ形成工程(S118)までを示している。

【0025】

図6(a)において、絶縁膜形成工程(S114)として、調整膜250上及び露出した下層配線構造210上に絶縁膜260をCVD法にて形成する。絶縁膜260の材料として、例えば、SiO2、SiOC等が挙げられる。

【0026】

図6(b)において、開口部形成工程(S116)として、リソグラフィ技術を用いて、コンタクトプラグを形成するためのヴィアホールとなる開口部150を形成する。ここでは、絶縁膜260とその下の調整膜250を開口し、グラフェン膜230表面を露出させる。

【0027】

図6(c)において、コンタクトプラグ形成工程(S118)として、開口部150にコンタクト材料を埋め込み、グラフェン膜230表面のコンタクト位置上にコンタクトプラグ240を形成する。コンタクトプラグ240の材料として、金属が用いられる。コンタクト金属として、例えば、銀(Ag)と、アルミニウム(Al)と、金(Au)と、コバルト(Co)と、クロム(Cr)と、銅(Cu)と、鉄(Fe)と、ニッケル(Ni)と、タンタル(Ta)と、チタン(Ti)、タングステン(W)と、バナジウム(V)との少なくとも1つ、又はこれらの少なくとも1つが含まれた合金が用いられると好適である。上記コンタクトプラグの材料はグラフェン膜の配線材料としての特性を十分に引き出すために選択されていることから、極端にはコンタクトプラグ最下部数nm程度が上記材料であればよく、その他の部分は低抵抗な材料、例えばCu、W、で形成されていてもよい。

【0028】

そして、化学機械研磨(CMP)法にて絶縁膜260上にはみ出た余分なコンタクトプラグ240材料を研磨除去して、図1に示した配線構造を持つ半導体装置を形成する。

【0029】

以上のように第1の実施形態によれば、コンタクトプラグ240と接触しない領域Aのディラック点位置を、フェルミ準位に対してコンタクトプラグ240と接続する領域Bと同方向に調整し、さらに同程度に調整する。これにより、領域A,B間でのディラック点位置の差が小さくなり高抵抗領域の形成を抑制できる。さらに、グラフェンの特性も維持できる。よって、従来のCu配線に比べて低抵抗な配線を実現できる。

【0030】

図7は、第1の実施形態における半導体装置の多層配線構成を示す図である。図1で示した状態から、さらに、触媒金属膜形成工程(S104)からコンタクトプラグ形成工程(S118)までを繰り返すことで、図7に示すような多層配線構造を形成できる。図7に示す多層配線構造の2層目では、絶縁膜260上に触媒金属膜222が形成される。そして、触媒金属膜222上にグラフェン膜232が形成される。グラフェン膜232上には、上層配線へと接続するコンタクトプラグ242が接続される。一方、グラフェン膜232表面のうち、コンタクトプラグ242と接続する領域以外の領域上には、調整膜252(ドーピング用薄膜)が形成される。そして、調整膜252上に絶縁膜262が形成される。多層配線構造の3層目では、絶縁膜262上に触媒金属膜224が形成される。そして、触媒金属膜224上にグラフェン膜234が形成される。グラフェン膜234上には、上層配線へと接続するコンタクトプラグ244が接続される。一方、グラフェン膜234表面のうち、コンタクトプラグ244と接続する領域以外の領域上には、調整膜254(ドーピング用薄膜)が形成される。そして、調整膜254上に絶縁膜264が形成される。図7では、配線とコンタクトの組が3層の配線構造を示したが、さらに、多層化してもよい。

【0031】

(第2の実施形態)

第2の実施形態では、さらに、調整膜250と絶縁膜260と間にバリアメタル膜を形成する場合について説明する。

【0032】

図8は、第2の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図である。第2の実施形態における半導体装置の製造方法は、調整膜形成工程(S112)と絶縁膜形成工程(S114)との間に、バリアメタル膜形成工程(S113)を追加した点以外は、図3と同様である。また、以下、特に説明した内容以外の内容は第1の実施形態と同様である。

【0033】

バリアメタル膜形成工程(S113)として、図4(d)で示した状態から、調整膜250上にバリアメタル膜270を形成する。ここでは、例えば、基板全面に形成された調整膜250上にバリアメタル膜270を形成し、リソグラフィ技術を用いて、調整膜250とバリアメタル膜270の2層を一緒に配線幅へと加工する。或いは、配線幅に加工済みの調整膜250上にバリアメタル膜270を基板全面に形成し、その後にリソグラフィ技術を用いてバリアメタル膜270を配線幅へと加工してもよい。そして、絶縁膜形成工程(S114)において、バリアメタル膜270上及び露出した下層配線構造210上に絶縁膜260を形成する。そして、開口部形成工程(S116)及びコンタクトプラグ形成工程(S118)を行えばよい。バリアメタル膜270の材料として、Ti、TiN、TaN、或いはRu等が好適である。形成方法は、スパッタ法等で形成すればよい。

【0034】

図9は、第2の実施形態における半導体装置の構成を示す図である。図9において、調整膜250と絶縁膜260との間にバリアメタル膜270が形成される。その他の構成は、図1と同様である。バリアメタル膜270を形成することで、調整膜250の材料が絶縁膜260へと拡散することを防止できる。

【0035】

以上、具体例を参照しつつ実施形態について説明した。しかし、本発明は、これらの具体例に限定されるものではない。また、上述した半導体装置の構成は、各種用途の半導体装置に適用可能である。いずれの用途でも高速配線を実現できる。例えば、メモリ装置、特に、NAND型のメモリ装置等に有効である。

【0036】

また、各層(膜)の膜厚や、開口部のサイズ、形状、数などについても、半導体集積回路や各種の半導体素子において必要とされるものを適宜選択して用いることができる。

【0037】

その他、本発明の要素を具備し、当業者が適宜設計変更しうる全ての半導体装置の製造方法は、本発明の範囲に包含される。

【0038】

また、説明の簡便化のために、半導体産業で通常用いられる手法、例えば、フォトリソグラフィプロセス、処理前後のクリーニング等は省略しているが、それらの手法が含まれ得ることは言うまでもない。

【符号の説明】

【0039】

200 基板、210,260 絶縁膜、220,222.224 触媒金属膜、230,232,234 グラフェン膜、240,242,244 コンタクトプラグ、250,252,254 調整膜

【特許請求の範囲】

【請求項1】

基板上に形成された触媒金属膜と、

前記触媒金属膜上に形成されたグラフェン膜と、

前記グラフェン膜と接続するコンタクトプラグと、

前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に形成された、ディラック点位置をフェルミ準位に対して前記コンタクトプラグと接続する領域と同方向に調整する調整膜と、

を備えたことを特徴とする半導体装置。

【請求項2】

前記グラフェン膜表面のうち前記調整膜と接続する領域におけるエネルギーバンド構造が、ディラック点を含むエネルギー軸および波数方向の直線に対して線対称になることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記グラフェン膜表面のうち前記コンタクトプラグと接続する領域におけるディラック点位置と、残りの前記調整膜と接続する領域におけるディラック点位置との差が、±0.5eV以下になることを特徴とする請求項1又は2記載の半導体装置。

【請求項4】

前記調整膜の材料として、金属と、有機化合物と、無機化合物とのいずれかが用いられることを特徴とする請求項1〜3いずれか記載の半導体装置。

【請求項5】

前記コンタクトプラグの材料として、銀(Ag)と、アルミニウム(Al)と、金(Au)と、コバルト(Co)と、クロム(Cr)と、銅(Cu)と、鉄(Fe)と、ニッケル(Ni)と、タンタル(Ta)と、チタン(Ti)、タングステン(W)と、バナジウム(V)との少なくとも1つ、又は前記少なくとも1つが含まれた合金が用いられることを特徴とする請求項1〜4いずれか記載の半導体装置。

【請求項6】

前記触媒金属膜の材料として、コバルト(Co)と、ニッケル(Ni)と、鉄(Fe)と、銅(Cu)と、ルテニウム(Ru)と、白金(Pt)との少なくとも1つ、又は前記少なくとも1つが含まれた合金が用いられることを特徴とする請求項1〜5いずれか記載の半導体装置。

【請求項7】

前記グラフェン膜は、1〜20層の層数で形成されることを特徴とする請求項1〜6いずれか記載の半導体装置。

【請求項8】

基板上に触媒金属膜を形成する工程と、

前記触媒金属膜上にグラフェン膜を形成する工程と、

前記グラフェン膜と接続するコンタクトプラグを形成する工程と、

前記コンタクトプラグを形成する前に、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に、ディラック点位置をフェルミ準位に対して前記コンタクトプラグと接続する領域と同方向に調整する調整膜を形成する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項1】

基板上に形成された触媒金属膜と、

前記触媒金属膜上に形成されたグラフェン膜と、

前記グラフェン膜と接続するコンタクトプラグと、

前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に形成された、ディラック点位置をフェルミ準位に対して前記コンタクトプラグと接続する領域と同方向に調整する調整膜と、

を備えたことを特徴とする半導体装置。

【請求項2】

前記グラフェン膜表面のうち前記調整膜と接続する領域におけるエネルギーバンド構造が、ディラック点を含むエネルギー軸および波数方向の直線に対して線対称になることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記グラフェン膜表面のうち前記コンタクトプラグと接続する領域におけるディラック点位置と、残りの前記調整膜と接続する領域におけるディラック点位置との差が、±0.5eV以下になることを特徴とする請求項1又は2記載の半導体装置。

【請求項4】

前記調整膜の材料として、金属と、有機化合物と、無機化合物とのいずれかが用いられることを特徴とする請求項1〜3いずれか記載の半導体装置。

【請求項5】

前記コンタクトプラグの材料として、銀(Ag)と、アルミニウム(Al)と、金(Au)と、コバルト(Co)と、クロム(Cr)と、銅(Cu)と、鉄(Fe)と、ニッケル(Ni)と、タンタル(Ta)と、チタン(Ti)、タングステン(W)と、バナジウム(V)との少なくとも1つ、又は前記少なくとも1つが含まれた合金が用いられることを特徴とする請求項1〜4いずれか記載の半導体装置。

【請求項6】

前記触媒金属膜の材料として、コバルト(Co)と、ニッケル(Ni)と、鉄(Fe)と、銅(Cu)と、ルテニウム(Ru)と、白金(Pt)との少なくとも1つ、又は前記少なくとも1つが含まれた合金が用いられることを特徴とする請求項1〜5いずれか記載の半導体装置。

【請求項7】

前記グラフェン膜は、1〜20層の層数で形成されることを特徴とする請求項1〜6いずれか記載の半導体装置。

【請求項8】

基板上に触媒金属膜を形成する工程と、

前記触媒金属膜上にグラフェン膜を形成する工程と、

前記グラフェン膜と接続するコンタクトプラグを形成する工程と、

前記コンタクトプラグを形成する前に、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に、ディラック点位置をフェルミ準位に対して前記コンタクトプラグと接続する領域と同方向に調整する調整膜を形成する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2012−64784(P2012−64784A)

【公開日】平成24年3月29日(2012.3.29)

【国際特許分類】

【出願番号】特願2010−208131(P2010−208131)

【出願日】平成22年9月16日(2010.9.16)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年3月29日(2012.3.29)

【国際特許分類】

【出願日】平成22年9月16日(2010.9.16)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]