半導体装置及び半導体装置の製造方法

【課題】半導体装置を薄型化する技術を提供する。

【解決手段】半導体装置は、基板と、前記基板の上面に設けられた半導体素子と、前記基板の上面に設けられた接着剤と、を備え、前記基板の上面に、前記半導体素子の少なくとも一部を収容する凹部が形成され、前記接着剤は、前記基板と前記半導体素子との間に設けられているとともに、前記基板の凹部を覆っている。

【解決手段】半導体装置は、基板と、前記基板の上面に設けられた半導体素子と、前記基板の上面に設けられた接着剤と、を備え、前記基板の上面に、前記半導体素子の少なくとも一部を収容する凹部が形成され、前記接着剤は、前記基板と前記半導体素子との間に設けられているとともに、前記基板の凹部を覆っている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

電子機器の薄型化が進むとともに、電子機器に搭載される半導体パッケージの薄型化が要求されており、半導体チップの薄化技術の開発が行われている。半導体パッケージは、支持基板の上に半導体チップを搭載し、半導体チップを樹脂によって封止したものである。複数の半導体パッケージを積層するPoP(パッケージオンパッケージ)構造においては、上層の半導体パッケージと下層の半導体パッケージとを接続する端子のファインピッチ化によって、上下層の半導体パッケージ間の間隙は狭くなっている。PoP構造においても、下層の半導体パッケージが有する半導体チップの薄型化を行うことが求められている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】実開2004−281920号公報

【特許文献2】特開2009−302212号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

半導体チップの薄型化を行うことで、搬送や実装による半導体チップの破壊、電気特性の劣化等の様々な問題が発生する可能性がある。そのため、半導体チップの薄型化を行わずに、半導体装置の薄型化が求められている。本件は、半導体装置を薄型化する技術を提供することを目的とする。

【課題を解決するための手段】

【0005】

本件の一観点による半導体装置は、基板と、前記基板の上面に設けられた半導体素子と、前記基板の上面に設けられた接着剤と、を備え、前記基板の上面に、前記半導体素子の少なくとも一部を収容する凹部が形成され、前記接着剤は、前記基板と前記半導体素子との間に設けられているとともに、前記基板の凹部を覆っている。

【発明の効果】

【0006】

本件によれば、半導体装置を薄型化することが可能となる。

【図面の簡単な説明】

【0007】

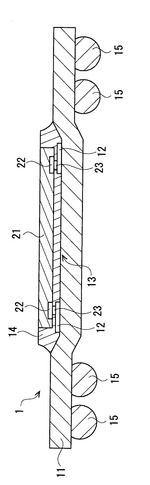

【図1A】図1Aは、本実施形態に係る半導体装置1の断面図である。

【図1B】図1Bは、本実施形態に係る半導体装置1の断面図である。

【図2A】図2Aは、半導体装置1の要部拡大断面図である。

【図2B】図2Bは、支持基板11に凹部13を形成していない場合の半導体装置1Aの要部拡大断面図である。

【図3】図3は、半導体装置1と半導体装置1Aとを、薄型の電子機器100に実装した場合の電子機器100の断面図である。

【図4】図4は、支持基板11の上面に接着剤14を形成した場合の半導体装置1の製造工程図である。

【図5】図5は、フリップチップボンダーのステージ31の上に支持基板11を設置した場合の半導体装置1の製造工程図である。

【図6】図6は、支持基板11の上方に半導体チップ21を配置した場合の半導体装置1の製造工程図である。

【図7】図7は、支持基板11の中央部分をフリップチップボンダーのステージ31の凹部32に押し込んだ場合の半導体装置1の製造工程図である。

【図8】図8は、支持基板11の中央部分をフリップチップボンダーのステージ31の凹部32に押し込んだ場合の半導体装置1の製造工程図である。

【図9A】図9Aは、接着剤14の量が少ない場合の支持基板11の断面図である。

【図9B】図9Bは、接着剤14が、支持基板11に形成された凹部13を覆っていない場合の支持基板11の断面図である。

【図9C】図9Cは、支持基板11がフラットな状態に戻った場合の支持基板11の断面図である。

【図10】図10は、支持基板11の下面に複数の半田ボール15を搭載した場合の半導体装置1の製造工程図である。

【図11】図11は、PoP(パッケージオンパッケージ)構造を有する半導体装置1の断面図である。

【図12】図12は、凹部13が形成されていない支持基板11を有する半導体パッケージ61に対して、半導体パッケージ51を実装した場合の半導体装置1Aの断面図である。

【発明を実施するための形態】

【0008】

以下、図面を参照して、発明を実施するための形態(以下、実施形態という)に係る半導体装置について説明する。以下の構成は例示であり、本実施形態は以下の構成に限定されない。

【0009】

本実施形態に係る半導体装置1の断面図を図1Aに示す。図1Aに示すように、半導体装置1は、支持基板11及び半導体チップ21を有している。支持基板11の上面(主面)に、半導体チップ(半導体集積回路チップ)21が設置されている。半導体チップ21は、半導体素子の一例である。半導体チップ21は、例えば、フリップチップ(フェイスダウン)方式により支持基板11の上面に実装される。半導体チップ21は、支持基板11の上面の中央部分に設置されてもよい。

【0010】

支持基板11は、配線基板、インターポーザ又は回路基板とも称される。支持基板11は、例えば、ビルドアップ基板、多層基板、フレキシブル基板等の有機基板である。有機基板は、例えば、ガラスエポキシ樹脂、ガラス−BT(ビスマレイミドトリアジン)及びポリイミド等を基材としてもよい。

【0011】

支持基板11の上面には、複数のパッド電極12が形成されている。パッド電極12は、例えば、銅(Cu)等の金属である。支持基板11の上面には、パッド電極12が形成されている箇所を除いて、ソルダーレジスト(図示せず)が形成されている。半導体チップ21の上面(主面)には、複数のパッド電極22が形成されている。パッド電極22は、銅(Cu)等の金属である。半導体チップ21の上面は、パッド電極22が形成された面(電極形成面)である。半導体チップ21の上面には、複数のバンプ(突起電極)23が設けられている。バンプ23は、例えば、金バンプ、半田バンプ、銅バンプ、又は、半田及び銅を含むバンプである。バンプ23は、半導体チップ21のパッド電極22に接続されているとともに、支持基板11のパッド電極12に接続されている。したがって、バンプ23を介して、支持基板11と半導体チップ21とが電気的に接続されている。

【0012】

支持基板11の上面の中央部分は、支持基板11の上面の中央部分を囲む外周部分よりも窪んでおり、支持基板11の下面(背面)の中央部分は、支持基板11の下面の外周部分よりも突出している。これにより、支持基板11の上面の中央部分には、凹部13が形成されている。すなわち、支持基板11が撓むことにより、支持基板11の上面の中央部

分に凹部13が形成されている。ただし、支持基板11の凹部13は、支持基板11の上面の中央部分に限らず、支持基板11の上面の中央部分以外の部分に形成されてもよい。また、支持基板11の凹部13は、支持基板11の上面の所定部分に形成されてもよい。支持基板11の上面の所定部分は、支持基板11の上面の中央部分であってもよい。支持基板11の所定部分は、支持基板11の上面の中央部分以外の部分であってもよい。

【0013】

図1Aに示すように、半導体チップ21の少なくとも一部分が、支持基板11の凹部13に収容される。半導体チップ21の一部分が、支持基板11の凹部13に収容されてもよいし、半導体チップ21の全体が支持基板11の凹部13に収容されてもよい。支持基板11の凹部13の底面のサイズは、半導体チップ21の外形サイズと同じ又は半導体チップ21の外形サイズよりも大きくなっている。そのため、半導体チップ21は、支持基板11の凹部13に安定した状態で収容されている。

【0014】

支持基板11の上面には、接着剤14が設けられている。接着剤14は、支持基板11と半導体チップ21との間に設けられているとともに、支持基板11の凹部13を覆っている。接着剤14の量を調整することにより、図1Bに示すように、支持基板11の上面の水平な底部とその周囲の傾斜部からなる凹部13の周囲(凹部13の傾斜部より外側)に接着剤14を設けるようにしてもよい。すなわち、支持基板11の凹部13を囲むように接着剤14を設けるようにしてもよい。接着剤14は、半導体チップ21を支持基板11に固着するとともに、支持基板11の凹部13の形状を保持する。接着剤14は、ペースト状であってもよいし、フィルム状であってもよい。ペースト状の接着剤14として、例えば、NCP(Non-Conductive Paste)及びACP(Anisotropic Conductive Paste)等を用いてもよい。フィルム状の接着剤14として、例えば、NCF(Non-Conductive Film)及びACF(Anisotropic Conductive Film)等を用いてもよい。

【0015】

支持基板11の下面には、複数の半田ボール15が設けられている。半田ボール15は、支持基板11の下面に形成されたボールパッド(図示せず)に搭載されている。

【0016】

本実施形態に係る半導体装置1によれば、半導体チップ21の一部分が、支持基板11の凹部13に収容されることにより、半導体装置1を薄型化することができる。図2Aは、半導体装置1の要部拡大断面図である。図2Bは、支持基板11に凹部13を形成していない場合の半導体装置1Aの要部拡大断面図である。図2Bに示す半導体装置1Aでは、支持基板11に凹部13が形成されていないため、半導体装置1Aの高さ(H3)及び支持基板11の上面から半導体チップ21までの高さ(H4)が低くなっていない。

【0017】

図2Aに示す半導体装置1は、半導体チップ21の一部分が、支持基板11の凹部13に収容されている。そのため、図2Aに示す半導体装置1は、図2Bに示す半導体装置1Aと比較して、半導体装置1の高さ(H1)及び支持基板11の上面から半導体チップ21までの高さ(H2)が低くなる。本実施形態では、半導体チップ21の一部分を支持基板11の凹部13に収容することにより、半導体チップ21の薄型化を行わずに半導体装置1の薄型化を行うことができる。

【0018】

図3に示すように、半導体装置1と半導体装置1Aとを、薄型の電子機器100に実装した場合、半導体装置1は、実装ボード101に設けられたケース102と接触しないが、半導体装置1Aは、ケース102と接触する。このように、本実施形態に係る半導体装置1は、半導体装置1Aと比較して、より薄型の機器に実装することが可能となる。

【0019】

図4から図8及び図10を参照して、本実施形態に係る半導体装置1の製造方法について説明する。図4に示すように、支持基板11を用意した後、支持基板11に接着剤14を塗布することにより、支持基板11の上面に接着剤14を形成する。図5に示すように

、フリップチップボンダー(接合装置)のステージ31の上に支持基板11を設置する。ステージ31の上部には、ステージ31の中央部分の上面が、ステージ31の中央部分を囲む外周部分の上面よりも窪んだ凹部32が設けられている。

【0020】

図6に示すように、フリップチップボンダーのボンディングツール33を用いて、支持基板11の上面と半導体チップ21の上面とが向かい合うように、支持基板11の上方に半導体チップ21を配置する。ボンディングツール33の吸引口34から半導体チップ21の下面(背面)を吸引することにより、ボンディングツール33は半導体チップ21を保持している。半導体チップ21の下面は、半導体チップ21の電極形成面の反対面である。

【0021】

図7に示すように、ボンディングツール33を降下させ、半導体チップ21の上面を接着剤14に押し付けるとともに、半導体チップ21のバンプ23を支持基板11のパッド電極12に押し付ける。図7に示すように、半導体チップ21に荷重(圧力)が加えられ、半導体チップ21が支持基板11に押し当てられることによって、支持基板11が撓み、支持基板11の中央部分がステージ31の凹部32に押し込まれる。支持基板11の中央部分をステージ31の凹部32に押し込むことにより、支持基板11の上面の中央部分が、支持基板11の上面の中央部分を囲む外周部分よりも窪み、支持基板11の下面の中央部分が、支持基板11の下面の外周部分よりも突出する。これにより、支持基板11の中央部分に、半導体チップ21の少なくとも一部分を収容する凹部13が形成される。また、支持基板11の中央部分以外の部分をステージ31の凹部32に押し込むことにより、支持基板11の上面の中央部分以外の部分に、凹部13を形成してもよい。また、支持基板11の所定部分をステージ31の凹部32に押し込むことにより、支持基板11の上面の所定部分に、凹部13を形成してもよい。

【0022】

支持基板11の凹部13の深さは、支持基板11の剛性、半導体チップ21の実装時の荷重(圧力)及びステージ31の凹部32の深さによって決定される。例えば、支持基板11の変形量が、ステージ31の凹部32の深さよりも大きい場合(支持基板11の変形量>ステージ31の凹部32の深さ)、図7に示すように、支持基板11の凹部13の深さは、ステージ31の凹部32の深さと同じになる。支持基板11の剛性が低い(例えば、支持基板11の板厚が薄い、支持基板11がフレキシブル基板である等)場合や、半導体チップ21の実装時の荷重(圧力)が大きい場合は、支持基板11の変形量は大きくなる。支持基板11の変形量が、ステージ31の凹部32の深さよりも大きい場合、支持基板11の変形量は、支持基板11の剛性、半導体チップ21の実装時の荷重(圧力)及びステージ31の凹部32の深さによって決定される。

【0023】

例えば、支持基板11の変形量が、ステージ31の凹部32の深さよりも小さい場合(支持基板11の変形量<ステージ31の凹部32の深さ)、図8に示すように、支持基板11の凹部13の深さは、支持基板11の変形量となる。支持基板11の剛性が高い(例えば、支持基板11の板厚が厚い等)場合や、半導体チップ21の実装時の荷重(圧力)が小さい場合は、支持基板11の変形量は小さくなる。支持基板11の変形量が、ステージ31の凹部32の深さよりも小さい場合、支持基板11の変形量は、支持基板11の剛性及び半導体チップ21の実装時の荷重(圧力)によって決定される。

【0024】

支持基板11に凹部13が形成された後、加熱処理を行うことにより、接着剤14を硬化する。例えば、ボンディングツール33を加熱し、接着剤14を150℃以上250℃以下に加熱することにより、接着剤14を硬化する。また、ボンディングツール33を加熱するとともに、ステージ31を加熱してもよい。接着剤14が硬化することにより、支持基板11に形成された凹部13の形状が保持される。

【0025】

支持基板11に凹部13を形成するために、支持基板11として、容易に変形させることが可能な有機基板を用いることが好ましい。支持基板11が有機基板である場合、支持基板11をステージ31の凹部32に押し込んだだけでは、支持基板11に形成された凹部13の形状は保持されず、支持基板11は元のフラットな状態に戻ってしまう。本実施形態では、支持基板11の凹部13を接着剤14で覆い、接着剤14を硬化することにより、支持基板11に形成された凹部13の形状を保持している。

【0026】

例えば、図9Aに示すように、支持基板11の上面に形成された接着剤14の量が少ない場合、図9Bに示すように、接着剤14は、支持基板11に形成された凹部13を覆わない。接着剤14が、支持基板11に形成された凹部13を覆っていない場合、ステージ31及びボンディングツール33を取り外すと、図9Cに示すように、支持基板11に形成された凹部13の形状が保持されず、支持基板11は元のフラットな状態に戻る。

【0027】

一方、接着剤14が、支持基板11の凹部13を覆っている場合、支持基板11の撓んでいる部分と接着剤14とが接触している。支持基板11の撓んでいる部分と接着剤14とが接触することにより、支持基板11の撓んでいる部分が元の状態に戻ることが抑制される。支持基板11の凹部13の周囲に接着剤14を設けることにより、支持基板11の撓んでいる部分が元の状態に戻ることがより抑制される。支持基板11の撓んでいる部分が元の状態に戻ることが抑制されるため、支持基板11に形成された凹部13の形状が保持される。

【0028】

支持基板11の剛性が高い場合、接着剤14が支持基板11の凹部13を覆うとともに、接着剤14が支持基板11の凹部13の周囲に設けられていることが好ましい。支持基板11の種類、厚さ等に応じて、支持基板11の凹部13の周囲に接着剤14を設けるか否かを決定してもよい。

【0029】

接着剤14が硬化した後、ステージ31及びボンディングツール33を取り外し、図10に示すように、支持基板11の下面に複数の半田ボール15を搭載する。半田ボール15は、支持基板11の下面に形成されたボールパッド(図示せず)に搭載される。

【0030】

図4から図8及び図10を参照して説明した半導体装置1の製造方法では、支持基板11の凹部13の周囲に接着剤14を設けているが、支持基板11の凹部13の周囲に接着剤14を設けないようにしてもよい。また、支持基板11の凹部13の底部全てと傾斜部の一部まで接着剤14を設けてもよい。

【0031】

半導体装置1をPoP(パッケージオンパッケージ)構造としてもよい。すなわち、図11に示すように、半導体装置1は、半導体パッケージ41と、半導体パッケージ41に実装された半導体パッケージ51とを備えてもよい。図11に示す半導体装置1は、支持基板11と、支持基板11の上面に設けられた半導体パッケージ51と、支持基板11と半導体パッケージ51との間に設けられた半導体チップ21と、を備えている。

【0032】

半導体パッケージ41は、凹部13が形成された支持基板11と、支持基板11の上面に設けられた接着剤14と、支持基板11の上面に設置された半導体チップ21と、を有している。半導体チップ21は、支持基板11の上面の中央部分に設置されてもよい。支持基板11の下面には、複数の半田ボール15が設けられている。

【0033】

半導体パッケージ51は、支持基板52と、支持基板52の上面に設けられた半導体チップ53と、半導体チップ53を封止するモールド樹脂54と、を有している。支持基板52の下面には、複数の半田ボール55が設けられている。

【0034】

半導体チップ53の上面には、複数のパッド電極56が形成されている。半導体チップ53は、パッド電極56に接続されたボンディングワイヤ57を介して、支持基板52に電気的に接続されている。支持基板52の下面に設けられた半田ボール55と、支持基板11の上面に形成された電極(図示せず)とが接合されることにより、半導体パッケージ41と半導体パッケージ51とが電気的に接続される。図11に示す半導体装置1では、支持基板11の凹部13の周囲に接着剤14を設けているが、支持基板11の凹部13の周囲に接着剤14を設けないようにしてもよい。また、支持基板11の凹部13の底部全てと傾斜部の一部まで接着剤14を設けてもよい。

【0035】

図11に示すように、半導体チップ21と、半導体パッケージ51とは接触していない。すなわち、半導体チップ21と支持基板52との間には間隙58が設けられており、半導体チップ21の下面と支持基板52の下面とは接触していない。支持基板52の下面は、半導体チップ53が設置されている面の反対面である。凹部13が形成されていない支持基板11を有する半導体パッケージ61に対して、半導体パッケージ51を実装した場合、図12に示すように、半導体チップ21と、半導体パッケージ51とが接触する。図12は、凹部13が形成されていない支持基板11を有する半導体パッケージ61に対して、半導体パッケージ51を実装した場合の半導体装置1Aの断面図である。図11に示す半導体装置1では、半導体チップ21と、半導体パッケージ51とが接触していないため、半導体チップ21の破損が抑制される。支持基板52の下面に設けられた半田ボール55を所定の高さにすることにより、半導体チップ21と支持基板52との間に間隙58を形成することが可能である。

【0036】

本実施形態によれば、半導体チップ21の一部分を支持基板11の凹部13に収容し、下層の半導体パッケージ41が有する支持基板11と上層の半導体パッケージ51との間をより狭くすることにより、半導体装置1を薄型化することができる。

【符号の説明】

【0037】

1 半導体装置

11、42 支持基板

12 パッド電極

13、32 凹部

14 接着剤

15、55 半田ボール

21、53 半導体チップ

22、57 パッド電極

23 バンプ

31 ステージ

33 ボンディングツール

41、51 半導体パッケージ

54 モールド樹脂

56 ボンディングワイヤ

58 間隙

【技術分野】

【0001】

本発明は、半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

電子機器の薄型化が進むとともに、電子機器に搭載される半導体パッケージの薄型化が要求されており、半導体チップの薄化技術の開発が行われている。半導体パッケージは、支持基板の上に半導体チップを搭載し、半導体チップを樹脂によって封止したものである。複数の半導体パッケージを積層するPoP(パッケージオンパッケージ)構造においては、上層の半導体パッケージと下層の半導体パッケージとを接続する端子のファインピッチ化によって、上下層の半導体パッケージ間の間隙は狭くなっている。PoP構造においても、下層の半導体パッケージが有する半導体チップの薄型化を行うことが求められている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】実開2004−281920号公報

【特許文献2】特開2009−302212号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

半導体チップの薄型化を行うことで、搬送や実装による半導体チップの破壊、電気特性の劣化等の様々な問題が発生する可能性がある。そのため、半導体チップの薄型化を行わずに、半導体装置の薄型化が求められている。本件は、半導体装置を薄型化する技術を提供することを目的とする。

【課題を解決するための手段】

【0005】

本件の一観点による半導体装置は、基板と、前記基板の上面に設けられた半導体素子と、前記基板の上面に設けられた接着剤と、を備え、前記基板の上面に、前記半導体素子の少なくとも一部を収容する凹部が形成され、前記接着剤は、前記基板と前記半導体素子との間に設けられているとともに、前記基板の凹部を覆っている。

【発明の効果】

【0006】

本件によれば、半導体装置を薄型化することが可能となる。

【図面の簡単な説明】

【0007】

【図1A】図1Aは、本実施形態に係る半導体装置1の断面図である。

【図1B】図1Bは、本実施形態に係る半導体装置1の断面図である。

【図2A】図2Aは、半導体装置1の要部拡大断面図である。

【図2B】図2Bは、支持基板11に凹部13を形成していない場合の半導体装置1Aの要部拡大断面図である。

【図3】図3は、半導体装置1と半導体装置1Aとを、薄型の電子機器100に実装した場合の電子機器100の断面図である。

【図4】図4は、支持基板11の上面に接着剤14を形成した場合の半導体装置1の製造工程図である。

【図5】図5は、フリップチップボンダーのステージ31の上に支持基板11を設置した場合の半導体装置1の製造工程図である。

【図6】図6は、支持基板11の上方に半導体チップ21を配置した場合の半導体装置1の製造工程図である。

【図7】図7は、支持基板11の中央部分をフリップチップボンダーのステージ31の凹部32に押し込んだ場合の半導体装置1の製造工程図である。

【図8】図8は、支持基板11の中央部分をフリップチップボンダーのステージ31の凹部32に押し込んだ場合の半導体装置1の製造工程図である。

【図9A】図9Aは、接着剤14の量が少ない場合の支持基板11の断面図である。

【図9B】図9Bは、接着剤14が、支持基板11に形成された凹部13を覆っていない場合の支持基板11の断面図である。

【図9C】図9Cは、支持基板11がフラットな状態に戻った場合の支持基板11の断面図である。

【図10】図10は、支持基板11の下面に複数の半田ボール15を搭載した場合の半導体装置1の製造工程図である。

【図11】図11は、PoP(パッケージオンパッケージ)構造を有する半導体装置1の断面図である。

【図12】図12は、凹部13が形成されていない支持基板11を有する半導体パッケージ61に対して、半導体パッケージ51を実装した場合の半導体装置1Aの断面図である。

【発明を実施するための形態】

【0008】

以下、図面を参照して、発明を実施するための形態(以下、実施形態という)に係る半導体装置について説明する。以下の構成は例示であり、本実施形態は以下の構成に限定されない。

【0009】

本実施形態に係る半導体装置1の断面図を図1Aに示す。図1Aに示すように、半導体装置1は、支持基板11及び半導体チップ21を有している。支持基板11の上面(主面)に、半導体チップ(半導体集積回路チップ)21が設置されている。半導体チップ21は、半導体素子の一例である。半導体チップ21は、例えば、フリップチップ(フェイスダウン)方式により支持基板11の上面に実装される。半導体チップ21は、支持基板11の上面の中央部分に設置されてもよい。

【0010】

支持基板11は、配線基板、インターポーザ又は回路基板とも称される。支持基板11は、例えば、ビルドアップ基板、多層基板、フレキシブル基板等の有機基板である。有機基板は、例えば、ガラスエポキシ樹脂、ガラス−BT(ビスマレイミドトリアジン)及びポリイミド等を基材としてもよい。

【0011】

支持基板11の上面には、複数のパッド電極12が形成されている。パッド電極12は、例えば、銅(Cu)等の金属である。支持基板11の上面には、パッド電極12が形成されている箇所を除いて、ソルダーレジスト(図示せず)が形成されている。半導体チップ21の上面(主面)には、複数のパッド電極22が形成されている。パッド電極22は、銅(Cu)等の金属である。半導体チップ21の上面は、パッド電極22が形成された面(電極形成面)である。半導体チップ21の上面には、複数のバンプ(突起電極)23が設けられている。バンプ23は、例えば、金バンプ、半田バンプ、銅バンプ、又は、半田及び銅を含むバンプである。バンプ23は、半導体チップ21のパッド電極22に接続されているとともに、支持基板11のパッド電極12に接続されている。したがって、バンプ23を介して、支持基板11と半導体チップ21とが電気的に接続されている。

【0012】

支持基板11の上面の中央部分は、支持基板11の上面の中央部分を囲む外周部分よりも窪んでおり、支持基板11の下面(背面)の中央部分は、支持基板11の下面の外周部分よりも突出している。これにより、支持基板11の上面の中央部分には、凹部13が形成されている。すなわち、支持基板11が撓むことにより、支持基板11の上面の中央部

分に凹部13が形成されている。ただし、支持基板11の凹部13は、支持基板11の上面の中央部分に限らず、支持基板11の上面の中央部分以外の部分に形成されてもよい。また、支持基板11の凹部13は、支持基板11の上面の所定部分に形成されてもよい。支持基板11の上面の所定部分は、支持基板11の上面の中央部分であってもよい。支持基板11の所定部分は、支持基板11の上面の中央部分以外の部分であってもよい。

【0013】

図1Aに示すように、半導体チップ21の少なくとも一部分が、支持基板11の凹部13に収容される。半導体チップ21の一部分が、支持基板11の凹部13に収容されてもよいし、半導体チップ21の全体が支持基板11の凹部13に収容されてもよい。支持基板11の凹部13の底面のサイズは、半導体チップ21の外形サイズと同じ又は半導体チップ21の外形サイズよりも大きくなっている。そのため、半導体チップ21は、支持基板11の凹部13に安定した状態で収容されている。

【0014】

支持基板11の上面には、接着剤14が設けられている。接着剤14は、支持基板11と半導体チップ21との間に設けられているとともに、支持基板11の凹部13を覆っている。接着剤14の量を調整することにより、図1Bに示すように、支持基板11の上面の水平な底部とその周囲の傾斜部からなる凹部13の周囲(凹部13の傾斜部より外側)に接着剤14を設けるようにしてもよい。すなわち、支持基板11の凹部13を囲むように接着剤14を設けるようにしてもよい。接着剤14は、半導体チップ21を支持基板11に固着するとともに、支持基板11の凹部13の形状を保持する。接着剤14は、ペースト状であってもよいし、フィルム状であってもよい。ペースト状の接着剤14として、例えば、NCP(Non-Conductive Paste)及びACP(Anisotropic Conductive Paste)等を用いてもよい。フィルム状の接着剤14として、例えば、NCF(Non-Conductive Film)及びACF(Anisotropic Conductive Film)等を用いてもよい。

【0015】

支持基板11の下面には、複数の半田ボール15が設けられている。半田ボール15は、支持基板11の下面に形成されたボールパッド(図示せず)に搭載されている。

【0016】

本実施形態に係る半導体装置1によれば、半導体チップ21の一部分が、支持基板11の凹部13に収容されることにより、半導体装置1を薄型化することができる。図2Aは、半導体装置1の要部拡大断面図である。図2Bは、支持基板11に凹部13を形成していない場合の半導体装置1Aの要部拡大断面図である。図2Bに示す半導体装置1Aでは、支持基板11に凹部13が形成されていないため、半導体装置1Aの高さ(H3)及び支持基板11の上面から半導体チップ21までの高さ(H4)が低くなっていない。

【0017】

図2Aに示す半導体装置1は、半導体チップ21の一部分が、支持基板11の凹部13に収容されている。そのため、図2Aに示す半導体装置1は、図2Bに示す半導体装置1Aと比較して、半導体装置1の高さ(H1)及び支持基板11の上面から半導体チップ21までの高さ(H2)が低くなる。本実施形態では、半導体チップ21の一部分を支持基板11の凹部13に収容することにより、半導体チップ21の薄型化を行わずに半導体装置1の薄型化を行うことができる。

【0018】

図3に示すように、半導体装置1と半導体装置1Aとを、薄型の電子機器100に実装した場合、半導体装置1は、実装ボード101に設けられたケース102と接触しないが、半導体装置1Aは、ケース102と接触する。このように、本実施形態に係る半導体装置1は、半導体装置1Aと比較して、より薄型の機器に実装することが可能となる。

【0019】

図4から図8及び図10を参照して、本実施形態に係る半導体装置1の製造方法について説明する。図4に示すように、支持基板11を用意した後、支持基板11に接着剤14を塗布することにより、支持基板11の上面に接着剤14を形成する。図5に示すように

、フリップチップボンダー(接合装置)のステージ31の上に支持基板11を設置する。ステージ31の上部には、ステージ31の中央部分の上面が、ステージ31の中央部分を囲む外周部分の上面よりも窪んだ凹部32が設けられている。

【0020】

図6に示すように、フリップチップボンダーのボンディングツール33を用いて、支持基板11の上面と半導体チップ21の上面とが向かい合うように、支持基板11の上方に半導体チップ21を配置する。ボンディングツール33の吸引口34から半導体チップ21の下面(背面)を吸引することにより、ボンディングツール33は半導体チップ21を保持している。半導体チップ21の下面は、半導体チップ21の電極形成面の反対面である。

【0021】

図7に示すように、ボンディングツール33を降下させ、半導体チップ21の上面を接着剤14に押し付けるとともに、半導体チップ21のバンプ23を支持基板11のパッド電極12に押し付ける。図7に示すように、半導体チップ21に荷重(圧力)が加えられ、半導体チップ21が支持基板11に押し当てられることによって、支持基板11が撓み、支持基板11の中央部分がステージ31の凹部32に押し込まれる。支持基板11の中央部分をステージ31の凹部32に押し込むことにより、支持基板11の上面の中央部分が、支持基板11の上面の中央部分を囲む外周部分よりも窪み、支持基板11の下面の中央部分が、支持基板11の下面の外周部分よりも突出する。これにより、支持基板11の中央部分に、半導体チップ21の少なくとも一部分を収容する凹部13が形成される。また、支持基板11の中央部分以外の部分をステージ31の凹部32に押し込むことにより、支持基板11の上面の中央部分以外の部分に、凹部13を形成してもよい。また、支持基板11の所定部分をステージ31の凹部32に押し込むことにより、支持基板11の上面の所定部分に、凹部13を形成してもよい。

【0022】

支持基板11の凹部13の深さは、支持基板11の剛性、半導体チップ21の実装時の荷重(圧力)及びステージ31の凹部32の深さによって決定される。例えば、支持基板11の変形量が、ステージ31の凹部32の深さよりも大きい場合(支持基板11の変形量>ステージ31の凹部32の深さ)、図7に示すように、支持基板11の凹部13の深さは、ステージ31の凹部32の深さと同じになる。支持基板11の剛性が低い(例えば、支持基板11の板厚が薄い、支持基板11がフレキシブル基板である等)場合や、半導体チップ21の実装時の荷重(圧力)が大きい場合は、支持基板11の変形量は大きくなる。支持基板11の変形量が、ステージ31の凹部32の深さよりも大きい場合、支持基板11の変形量は、支持基板11の剛性、半導体チップ21の実装時の荷重(圧力)及びステージ31の凹部32の深さによって決定される。

【0023】

例えば、支持基板11の変形量が、ステージ31の凹部32の深さよりも小さい場合(支持基板11の変形量<ステージ31の凹部32の深さ)、図8に示すように、支持基板11の凹部13の深さは、支持基板11の変形量となる。支持基板11の剛性が高い(例えば、支持基板11の板厚が厚い等)場合や、半導体チップ21の実装時の荷重(圧力)が小さい場合は、支持基板11の変形量は小さくなる。支持基板11の変形量が、ステージ31の凹部32の深さよりも小さい場合、支持基板11の変形量は、支持基板11の剛性及び半導体チップ21の実装時の荷重(圧力)によって決定される。

【0024】

支持基板11に凹部13が形成された後、加熱処理を行うことにより、接着剤14を硬化する。例えば、ボンディングツール33を加熱し、接着剤14を150℃以上250℃以下に加熱することにより、接着剤14を硬化する。また、ボンディングツール33を加熱するとともに、ステージ31を加熱してもよい。接着剤14が硬化することにより、支持基板11に形成された凹部13の形状が保持される。

【0025】

支持基板11に凹部13を形成するために、支持基板11として、容易に変形させることが可能な有機基板を用いることが好ましい。支持基板11が有機基板である場合、支持基板11をステージ31の凹部32に押し込んだだけでは、支持基板11に形成された凹部13の形状は保持されず、支持基板11は元のフラットな状態に戻ってしまう。本実施形態では、支持基板11の凹部13を接着剤14で覆い、接着剤14を硬化することにより、支持基板11に形成された凹部13の形状を保持している。

【0026】

例えば、図9Aに示すように、支持基板11の上面に形成された接着剤14の量が少ない場合、図9Bに示すように、接着剤14は、支持基板11に形成された凹部13を覆わない。接着剤14が、支持基板11に形成された凹部13を覆っていない場合、ステージ31及びボンディングツール33を取り外すと、図9Cに示すように、支持基板11に形成された凹部13の形状が保持されず、支持基板11は元のフラットな状態に戻る。

【0027】

一方、接着剤14が、支持基板11の凹部13を覆っている場合、支持基板11の撓んでいる部分と接着剤14とが接触している。支持基板11の撓んでいる部分と接着剤14とが接触することにより、支持基板11の撓んでいる部分が元の状態に戻ることが抑制される。支持基板11の凹部13の周囲に接着剤14を設けることにより、支持基板11の撓んでいる部分が元の状態に戻ることがより抑制される。支持基板11の撓んでいる部分が元の状態に戻ることが抑制されるため、支持基板11に形成された凹部13の形状が保持される。

【0028】

支持基板11の剛性が高い場合、接着剤14が支持基板11の凹部13を覆うとともに、接着剤14が支持基板11の凹部13の周囲に設けられていることが好ましい。支持基板11の種類、厚さ等に応じて、支持基板11の凹部13の周囲に接着剤14を設けるか否かを決定してもよい。

【0029】

接着剤14が硬化した後、ステージ31及びボンディングツール33を取り外し、図10に示すように、支持基板11の下面に複数の半田ボール15を搭載する。半田ボール15は、支持基板11の下面に形成されたボールパッド(図示せず)に搭載される。

【0030】

図4から図8及び図10を参照して説明した半導体装置1の製造方法では、支持基板11の凹部13の周囲に接着剤14を設けているが、支持基板11の凹部13の周囲に接着剤14を設けないようにしてもよい。また、支持基板11の凹部13の底部全てと傾斜部の一部まで接着剤14を設けてもよい。

【0031】

半導体装置1をPoP(パッケージオンパッケージ)構造としてもよい。すなわち、図11に示すように、半導体装置1は、半導体パッケージ41と、半導体パッケージ41に実装された半導体パッケージ51とを備えてもよい。図11に示す半導体装置1は、支持基板11と、支持基板11の上面に設けられた半導体パッケージ51と、支持基板11と半導体パッケージ51との間に設けられた半導体チップ21と、を備えている。

【0032】

半導体パッケージ41は、凹部13が形成された支持基板11と、支持基板11の上面に設けられた接着剤14と、支持基板11の上面に設置された半導体チップ21と、を有している。半導体チップ21は、支持基板11の上面の中央部分に設置されてもよい。支持基板11の下面には、複数の半田ボール15が設けられている。

【0033】

半導体パッケージ51は、支持基板52と、支持基板52の上面に設けられた半導体チップ53と、半導体チップ53を封止するモールド樹脂54と、を有している。支持基板52の下面には、複数の半田ボール55が設けられている。

【0034】

半導体チップ53の上面には、複数のパッド電極56が形成されている。半導体チップ53は、パッド電極56に接続されたボンディングワイヤ57を介して、支持基板52に電気的に接続されている。支持基板52の下面に設けられた半田ボール55と、支持基板11の上面に形成された電極(図示せず)とが接合されることにより、半導体パッケージ41と半導体パッケージ51とが電気的に接続される。図11に示す半導体装置1では、支持基板11の凹部13の周囲に接着剤14を設けているが、支持基板11の凹部13の周囲に接着剤14を設けないようにしてもよい。また、支持基板11の凹部13の底部全てと傾斜部の一部まで接着剤14を設けてもよい。

【0035】

図11に示すように、半導体チップ21と、半導体パッケージ51とは接触していない。すなわち、半導体チップ21と支持基板52との間には間隙58が設けられており、半導体チップ21の下面と支持基板52の下面とは接触していない。支持基板52の下面は、半導体チップ53が設置されている面の反対面である。凹部13が形成されていない支持基板11を有する半導体パッケージ61に対して、半導体パッケージ51を実装した場合、図12に示すように、半導体チップ21と、半導体パッケージ51とが接触する。図12は、凹部13が形成されていない支持基板11を有する半導体パッケージ61に対して、半導体パッケージ51を実装した場合の半導体装置1Aの断面図である。図11に示す半導体装置1では、半導体チップ21と、半導体パッケージ51とが接触していないため、半導体チップ21の破損が抑制される。支持基板52の下面に設けられた半田ボール55を所定の高さにすることにより、半導体チップ21と支持基板52との間に間隙58を形成することが可能である。

【0036】

本実施形態によれば、半導体チップ21の一部分を支持基板11の凹部13に収容し、下層の半導体パッケージ41が有する支持基板11と上層の半導体パッケージ51との間をより狭くすることにより、半導体装置1を薄型化することができる。

【符号の説明】

【0037】

1 半導体装置

11、42 支持基板

12 パッド電極

13、32 凹部

14 接着剤

15、55 半田ボール

21、53 半導体チップ

22、57 パッド電極

23 バンプ

31 ステージ

33 ボンディングツール

41、51 半導体パッケージ

54 モールド樹脂

56 ボンディングワイヤ

58 間隙

【特許請求の範囲】

【請求項1】

基板と、

前記基板の上面に設けられた半導体素子と、

前記基板の上面に設けられた接着剤と、

を備え、

前記基板の上面に、前記半導体素子の少なくとも一部を収容する凹部が形成され、

前記接着剤は、前記基板と前記半導体素子との間に設けられているとともに、前記基板の凹部を覆っていることを特徴とする半導体装置。

【請求項2】

前記基板の凹部は、前記基板の上面の中央部分が、前記基板の上面の中央部分を囲む外周部分よりも窪み、前記基板の下面の中央部分が、前記基板の下面の中央部分を囲む外周部分よりも突出することにより形成されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記接着剤は、前記基板の凹部の周囲に設けられていることを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記基板の上面に設けられた半導体パッケージを備え、

前記基板と前記半導体パッケージとの間に前記半導体素子が設けられており、

前記半導体素子と前記半導体パッケージとは接触していないことを特徴とする請求項1から3の何れか一項に記載の半導体装置。

【請求項5】

基板の上面に接着剤を形成する工程と、

凹部を有するステージの上に前記基板を設置する工程と、

前記基板の上面と半導体素子の電極形成面とが向かい合うように、前記接着剤の上方に前記半導体素子を配置する工程と、

前記半導体素子の電極形成面を前記接着剤に押し付けるとともに、前記半導体素子の電極を前記基板に押し付けて、前記ステージの凹部に前記基板を押し込むことにより、前記基板の上面に、前記半導体素子の少なくとも一部を収容する凹部を形成する工程と、

加熱処理により、前記接着剤を硬化する工程と、

を備え、

前記接着剤は、前記基板と前記半導体素子との間に設けられているとともに、前記基板の凹部を覆っていることを特徴とする半導体装置の製造方法。

【請求項6】

前記ステージの凹部に前記基板の中央部分を押し込み、前記基板の上面の中央部分を、前記基板の上面の中央部分を囲む外周部分よりも窪ませ、前記基板の下面の中央部分を、前記基板の下面の中央部分を囲む外周部分よりも突出させることにより、前記基板の上面に凹部を形成することを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記接着剤は、前記基板の凹部の周囲に設けられていることを特徴とする請求項5又は6に記載の半導体装置の製造方法。

【請求項8】

前記基板の上面に半導体パッケージを設置する工程を備え、

前記基板と前記半導体パッケージとの間に前記半導体素子が設けられており、

前記半導体素子と前記半導体パッケージとは接触していないことを特徴とする請求項5から7の何れか一項に記載の半導体装置の製造方法。

【請求項1】

基板と、

前記基板の上面に設けられた半導体素子と、

前記基板の上面に設けられた接着剤と、

を備え、

前記基板の上面に、前記半導体素子の少なくとも一部を収容する凹部が形成され、

前記接着剤は、前記基板と前記半導体素子との間に設けられているとともに、前記基板の凹部を覆っていることを特徴とする半導体装置。

【請求項2】

前記基板の凹部は、前記基板の上面の中央部分が、前記基板の上面の中央部分を囲む外周部分よりも窪み、前記基板の下面の中央部分が、前記基板の下面の中央部分を囲む外周部分よりも突出することにより形成されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記接着剤は、前記基板の凹部の周囲に設けられていることを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記基板の上面に設けられた半導体パッケージを備え、

前記基板と前記半導体パッケージとの間に前記半導体素子が設けられており、

前記半導体素子と前記半導体パッケージとは接触していないことを特徴とする請求項1から3の何れか一項に記載の半導体装置。

【請求項5】

基板の上面に接着剤を形成する工程と、

凹部を有するステージの上に前記基板を設置する工程と、

前記基板の上面と半導体素子の電極形成面とが向かい合うように、前記接着剤の上方に前記半導体素子を配置する工程と、

前記半導体素子の電極形成面を前記接着剤に押し付けるとともに、前記半導体素子の電極を前記基板に押し付けて、前記ステージの凹部に前記基板を押し込むことにより、前記基板の上面に、前記半導体素子の少なくとも一部を収容する凹部を形成する工程と、

加熱処理により、前記接着剤を硬化する工程と、

を備え、

前記接着剤は、前記基板と前記半導体素子との間に設けられているとともに、前記基板の凹部を覆っていることを特徴とする半導体装置の製造方法。

【請求項6】

前記ステージの凹部に前記基板の中央部分を押し込み、前記基板の上面の中央部分を、前記基板の上面の中央部分を囲む外周部分よりも窪ませ、前記基板の下面の中央部分を、前記基板の下面の中央部分を囲む外周部分よりも突出させることにより、前記基板の上面に凹部を形成することを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記接着剤は、前記基板の凹部の周囲に設けられていることを特徴とする請求項5又は6に記載の半導体装置の製造方法。

【請求項8】

前記基板の上面に半導体パッケージを設置する工程を備え、

前記基板と前記半導体パッケージとの間に前記半導体素子が設けられており、

前記半導体素子と前記半導体パッケージとは接触していないことを特徴とする請求項5から7の何れか一項に記載の半導体装置の製造方法。

【図1A】

【図1B】

【図2A】

【図2B】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9A】

【図9B】

【図9C】

【図10】

【図11】

【図12】

【図1B】

【図2A】

【図2B】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9A】

【図9B】

【図9C】

【図10】

【図11】

【図12】

【公開番号】特開2013−115290(P2013−115290A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−261348(P2011−261348)

【出願日】平成23年11月30日(2011.11.30)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月30日(2011.11.30)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

[ Back to top ]