半導体装置及び半導体装置の製造方法

【課題】大電流を流す第1ビアおよび第1配線を有し、且つ、当該第1ビアおよび第1配線が形成された第1面が平坦な半導体装置を提供する。

【解決手段】第1基板100と、第1基板100の第1面側から、当該第1基板100を貫通する第1ビア420と、第1基板100の第1面に埋設され、少なくとも一つ以上の第1ビア420の一端と接続する第1配線440と、を備えている。また、第1ビア420は、当該第1ビア420の側面と当該第1ビア420の底面とのなす角θ1が、第1配線440の側面と第1配線440の底面とのなす角θ2より大きい傾斜部を有している。

【解決手段】第1基板100と、第1基板100の第1面側から、当該第1基板100を貫通する第1ビア420と、第1基板100の第1面に埋設され、少なくとも一つ以上の第1ビア420の一端と接続する第1配線440と、を備えている。また、第1ビア420は、当該第1ビア420の側面と当該第1ビア420の底面とのなす角θ1が、第1配線440の側面と第1配線440の底面とのなす角θ2より大きい傾斜部を有している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の高集積化に伴い、大電流を流すための配線を形成するために、様々な多層配線構造が提案されている。

【0003】

特許文献1(特開2010−045371号公報)には、以下のような貫通電極(Through Silicon Via:TSV)構造体が記載されている。この貫通電極構造体の導電性ビアは、基板の上部表面から下部表面に延長されて基板を貫通している。また、導電性ビアの底部には、NiおよびCoのうちの少なくともいずれか一方を有する導電性保護膜が形成されている。さらに、導電性保護膜に接触して、基板の下部表面には、分離ポリマー絶縁膜が形成されている。これにより、半導体基板の歪みを抑制することができる貫通電極構造体を提供することができるとされている。

【0004】

また、特許文献2(特開2010−080897号公報)には、以下のような半導体装置が記載されている。第1の半導体チップと第2の半導体チップとが貼り合わされている。第1の半導体チップの表面部に電極パッドが形成されている。第2の半導体チップ中に貫通ビアが形成されている。電極パッドには掘り込み部が形成されており、当該掘り込み部内に貫通ビアの底部が埋め込まれている。これにより、貫通ビアと電極パッドとの接合強度を増大させることにより、3次元配線構造を有する半導体装置の機械的強度を増大させることができるとされている。

【0005】

また、特許文献3(特開2009−302453号公報)には、以下のような半導体装置が記載されている。半導体チップの裏面に、凹部が形成されている。この凹部内部に、貫通電極の一部である裏面配線パッドと、裏面配線とが形成されている。これにより、チップ裏面側の平坦性が確保され、チップを扱う際の吸着力の低下が起きないとされている。

【0006】

また、特許文献4(特開2009−277927号公報)には、以下のような回路基板が記載されている。回路パターンは、基板の一面に設けられている。貫通電極は、基板に設けられた貫通孔の内部に充填され、一端が回路パターンに接合されている。回路パターンおよび貫通電極は、それぞれ貴金属成分を含有する領域を有しており、当該領域を介して、互いに接合されている。これにより、回路パターンの表面における酸化膜の発生、および貫通孔内のボイドの発生を抑制することができるとされている。なお、特許文献4の図1には、深さおよび底部のアスペクト比が1以上の貫通ビアが記載されている。

【0007】

また、特許文献5(特開2009−010312号公報)には、以下のようなスタックパッケージが記載されている。第1および第2半導体チップが、ボンディングパッド形成面が向かい合うように配置されている。第1および第2半導体チップには、複数のTSVが形成されている。第1および第2半導体チップの各ボンディングパッド形成面上には、複数の配線が、TSVとボンディングパッドとを連結するように形成されている。これにより、製造過程で発生するウェハおよび半導体チップの歪みおよびクラックを抑制することができるとされている。

【0008】

また、特許文献6(特開2009−004722号公報)には、貫通ビアの底面が半導体チップから突出するように半導体チップの下面を除去する工程を含む半導体パッケージの製造方法が記載されている。これにより、スタック型半導体パッケージの製造工程を単純化して、製造コストを減少させることができるとされている。

【0009】

また、特許文献7(特開平08−255797号公報)には、以下のような半導体基板の製造方法が記載されている。まず、第1シリコン基板の一主面に溝を形成する。次いで、溝の内部に金属層を形成する。次いで、熱処理により、金属層の少なくとも一部をシリサイド化する。次いで、一主面を平坦化する。次いで、第1シリコン基板の一主面と、第2シリコン基板とを接合する。これにより、基板に低抵抗のシリサイドの埋め込み層を有する、低コストで欠陥が少ない半導体装置を提供することができるとされている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2010−045371号公報

【特許文献2】特開2010−080897号公報

【特許文献3】特開2009−302453号公報

【特許文献4】特開2009−277927号公報

【特許文献5】特開2009−010312号公報

【特許文献6】特開2009−004722号公報

【特許文献7】特開平08−255797号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

上記した特許文献1から特許文献7では、ビアホールおよび配線溝を形成した後に、ビアホールおよび配線溝に、同時にめっき法により金属を埋め込む方法に関しては検討がなされていない。

【0012】

発明者は、ビアホールおよび配線溝を形成した後の金属埋設工程において、ビアホールおよび配線溝に、同時にめっき法により金属を埋め込む場合に、以下のような課題が発生することを見出した。ビアホールはアスペクト比が高いのに対して、配線溝は浅く、アスペクト比が低い。このため、同時にめっき法により金属を埋め込む場合、ビアホールよりも配線溝の方が早く金属が埋め込まれてしまい、配線溝上の金属が盛り上がった形状になってしまう。このように、金属が埋め込まれた基板表面の平坦性が悪いため、CMP(Chemical Mechanical Polishing)工程において、均一に研磨することができないという問題があることを見出した。

【課題を解決するための手段】

【0013】

本発明によれば、

第1基板と、

前記第1基板の第1面側から、当該第1基板を貫通する第1ビアと、

前記第1基板の前記第1面に埋設され、少なくとも一つ以上の前記第1ビアの一端と接続する第1配線と、

を備え、

前記第1ビアは、当該第1ビアの前記側面と当該第1ビアの底面とのなす角が、前記第1配線の側面と前記第1配線の底面とのなす角より大きい傾斜部を有する半導体装置が提供される。

【0014】

本発明によれば、

第1基板と、

前記第1基板の第1面上に設けられた第1層間絶縁膜と、

前記第1層間絶縁膜を貫通する第1層間ビアと、

前記第1層間絶縁膜の表面に埋設され、少なくとも一つ以上の前記第1層間ビアの一端と接続する第1配線と、

を備え、

前記第1層間ビアは、当該第1層間ビアの前記側面と当該第1層間ビアの底面とのなす角が、前記第1配線の側面と前記第1配線の底面とのなす角より大きい傾斜部を有する半導体装置が提供される。

【0015】

本発明によれば、

第1基板の第1面側から、当該第1基板を貫通する第1ビアホールを形成するとともに、少なくとも一つ以上の前記第1ビアホールの一端と接続する第1配線溝を形成するエッチング工程と、

前記第1ビアホールおよび前記第1配線溝に金属を埋め込むことにより、第1ビアおよび第1配線を形成する金属埋設工程と、

を備え、

前記エッチング工程において、前記第1ビアホールに、側面と底面とのなす角が、前記第1配線溝の側面と前記第1配線溝の底面とのなす角より大きい傾斜部を形成する半導体装置の製造方法が提供される。

【0016】

本発明によれば、

第1基板の第1面上に第1層間絶縁膜を形成する工程と、

前記第1層間絶縁膜を貫通する第1層間ビアホールを形成するとともに、少なくとも一つ以上の前記第1層間ビアホールの一端と接続する第1配線溝を形成するエッチング工程と、

前記第1層間ビアホールおよび前記第1配線溝に金属を埋め込むことにより、第1層間ビアおよび第1配線を形成する金属埋設工程と、

を備え、

前記エッチング工程において、前記第1層間ビアホールに、側面と底面とのなす角が、前記第1配線溝の側面と前記第1配線溝の底面とのなす角より大きい傾斜部を形成する半導体装置の製造方法が提供される。

【0017】

本発明によれば、第1ビア(第1層間ビア)は、当該第1ビア(第1層間ビア)の側面と底面とのなす角が、第1配線の側面と底面とのなす角より大きい傾斜部を有している。これにより、その後の金属埋設工程において、第1配線溝よりも、第1ビアホールにおける金属の埋め込み速度を速くすることができる。そして、金属が埋設された後の第1基板の第1面を平坦にすることができ、さらにCMPにおいて均一に平坦化することができる。したがって、大電流を流す第1ビア(第1層間ビア)および第1配線を有し、且つ、当該第1ビア(第1層間ビア)および第1配線が形成された第1面が平坦な半導体装置を提供することができる。

【発明の効果】

【0018】

本発明によれば、大電流を流す第1ビアおよび第1配線を有し、且つ、当該第1ビアおよび第1配線が形成された第1面が平坦な半導体装置を提供することができる。

【図面の簡単な説明】

【0019】

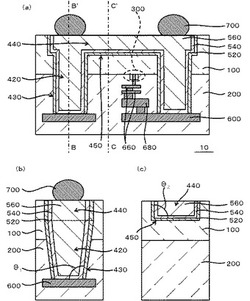

【図1】第1の実施形態に係る半導体装置の構成を示す断面図である。

【図2】第1の実施形態に係る半導体装置の構成を示す平面図である。

【図3】図1(a)における半導体素子を拡大した断面図である。

【図4】第1ビアまたは第1配線における側面と底面とのなす角と、金属の埋め込み速度の関係を示した図である。

【図5】図1(b)における第1ビアを拡大した断面図である。

【図6】第1の実施形態の効果を説明するための図である。

【図7】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図8】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図9】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図10】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図11】第2の実施形態に係る半導体装置の構成を示す断面図である。

【図12】第3の実施形態に係る半導体装置の構成を示す断面図である。

【図13】第4の実施形態に係る半導体装置の構成を示す断面図である。

【図14】第5の実施形態に係る半導体装置の構成を示す断面図である。

【図15】第6の実施形態に係る半導体装置の構成を示す断面図である。

【図16】第7の実施形態に係る半導体装置の構成を示す断面図である。

【図17】第8の実施形態に係る半導体装置の構成を示す断面図である。

【図18】第9の実施形態に係る半導体装置の構成を示す断面図である。

【発明を実施するための形態】

【0020】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0021】

(第1の実施形態)

図1から図5を用い、第1の実施形態に係る半導体装置10について説明する。まず、図1は、第1の実施形態に係る半導体装置10の構成を示す図である。図1(a)は、後述する図2のA−A'線断面図である。また、図1(b)は、図1(a)におけるB−B'線断面図である。また、図1(c)は、図1(a)におけるC−C'線断面図である。この半導体装置10は、以下のような構成を備えている。第1基板100と、第1基板100の第1面側から、当該第1基板100を貫通する第1ビア420と、第1基板100の第1面に埋設され、少なくとも一つ以上の第1ビア420の一端と接続する第1配線440と、を備えている。また、第1ビア420は、当該第1ビア420の側面と当該第1ビア420の底面とのなす角θ1が、第1配線440の側面と第1配線440の底面とのなす角θ2より大きい傾斜部を有している。以下、詳細を説明する。

【0022】

図1(a)のように、第1基板100の第1面側から、当該第1基板100を貫通する第1ビア420が形成されている。第1基板100は、たとえば、シリコン基板である。

【0023】

ここでいう「第1ビア420」とは、後述するバリアメタル層540と、バリアメタル層540内にめっきにより埋設された金属560とを含む接続孔のことである。なお、「第1ビア420」は、ライナー絶縁膜520を含まない。

【0024】

また、第1配線440は、第1基板100の第1面に埋設され、少なくとも一つ以上の第1ビア420の一端と接続している。

【0025】

ここでいう「第1配線440」とは、後述するバリアメタル層540と、バリアメタル層540内にめっきにより埋設された金属560とを含む配線のことである。なお、「第1配線440」は、ライナー絶縁膜520を含まない。

【0026】

第1配線440は、たとえば、半導体装置10をプリント配線基板(不図示)などに搭載する際に、プリント配線基板(不図示)などから供給された大電流を流すための配線である。さらに、第1配線440は、第1ビア420を介して、後述する第2配線600などの電源配線、またはグランド配線に、電流を供給する。

【0027】

ここで、第1配線440の高さ(深さ)は、5μm以上100μm以下である。これにより、第1配線440に大電流を流すことができる。

【0028】

これらの第1ビア420および第1配線440は、第1基板100に形成された第1ビアホール430および第1配線溝450に金属560を埋め込むことにより形成されている。図1において、第1ビアホール430は、製造工程において、ライナー絶縁膜520と第1基板100との界面に形成されていたものとして示している。また、第1配線溝450は、同様に、製造工程において、ライナー絶縁膜520と第1基板100との界面に形成されていたものとして示している。この金属埋設工程を含む製造方法については、詳細を後述する。

【0029】

第1ビアホール430の側面、第1配線溝450の側面および底面には、ライナー絶縁膜520が形成されている。すなわち、第1ビア420および第1配線440のうち、第1ビア420の底面を除く、第1ビア420の側面、および第1配線440の底面並びに側面と接するように、ライナー絶縁膜520が形成されている。ライナー絶縁膜520としては、たとえば、SiO2、SiN、SiCN、SiON、SiCのいずれか、またはこれらの積層膜である。また、ライナー絶縁膜520の厚さは、たとえば、20nm以上200nm以下である。

【0030】

また、第1ビア420および第1配線440のうち、内側の側面および底面には、バリアメタル層540が形成されている。バリアメタル層540としては、たとえば、Ta、TaN、Ti、TiN、Mn、CoWP、Co、NiB、W、Alなどである。また、バリアメタル層540の厚さは、たとえば、20nm以上250nm以下である。

【0031】

さらに、バリアメタル層540の内側には、めっき法により金属560が埋設されている。金属560としては、たとえば、Cu、Al、W、Ti、TiN、Ta、TaN、Mn、Coのいずれか、またはこれらの金属の合金である。

【0032】

上記のように、第1ビア420および第1配線440の境界には、バリアメタル層540が形成されておらず、第1ビア420および第1配線440内に一続きに金属560が形成されている。

【0033】

また、第1基板100の第1配線440上には、第1ビア420または第1配線440と接続する第1バンプ電極700が設けられている。第1バンプ電極700は、たとえば、第1ビア420の直上に形成されている。第1バンプ電極700の材料としては、たとえば、Sn、Sn−Ag、Sn−Ag−Cu、Auなどである。これにより、第1基板100を、第1面の第1バンプ電極700を介して、プリント配線基板などに搭載することができる。

【0034】

また、第1基板100は、第1配線440等が形成された第1面と反対の第2面上に第2配線600を備えている。また、第1ビア420の他端は、第2配線600と接続している。ここで、第2配線600は、第1基板100の第2面上に形成された配線であれば、限定されるものではない。図1では、第2配線600は、第1層間絶縁膜200中に形成された配線である。その他、第2配線600は、たとえば、第1層間絶縁膜200などの絶縁膜を介さずに、第1基板100の第2面の直上に接するように形成された配線(不図示)であってもよい。これにより、第1基板100の第1面側から、第2配線600等に電流を供給することができる。

【0035】

第1の実施形態では、第1基板100の第1面の反対の第2面側には、半導体素子300が形成されている。半導体素子300については、詳細を後述する。

【0036】

第1の実施形態では、第1基板100の第2面上には、第1層間絶縁膜200が設けられている。なお、第1層間絶縁膜200は、多層構造であってもよい。第1層間絶縁膜200としては、たとえば、SiO2、SiN、SiON、SiOC、SiOCH、SiCOHまたはSiOFなどである。上述の第2配線600は、第1層間絶縁膜200の最上層に埋設されている。

【0037】

さらに、第2面側には、半導体素子300に接続するコンタクト(たとえば後述するコンタクト620)、コンタクト620を介して半導体素子300と接続するローカル配線660が形成されている。また、ローカル配線660間、ローカル配線660並びにローカル配線680の間、およびローカル配線680並びに第2配線600の間を接続するビア(符号不図示)が形成されている。なお、第2配線600は、「グローバル配線」と呼ばれている。

【0038】

また、第1ビア420は、第1基板100を貫通するとともに、第1層間絶縁膜200の一部を貫通している。ここで、上述のように、第1ビア420の他端は、第2配線600と接続している。このように、ローカル配線660およびローカル配線680が形成された第1層間絶縁膜200を貫通して、第2配線600と接続することができる。

【0039】

ここで、第2配線600は、たとえば、第1基板100に設けられた半導体素子300等に電流を供給する電源配線、またはグランド配線である。前述のように、この第2配線600は、第1ビア420の他端と接続されていることにより、大電流の供給を受けることができる。

【0040】

また、図1(b)のように、第1ビア420は、傾斜部(符号不図示)を有している。この傾斜部は、第1ビア420に形成される位置が限定されるものではない。ただし、傾斜部は、第1ビア420のうち、少なくとも対向する一対の側面に形成されていることが好ましい。また、第1ビア420上層が先に埋め込まれ、第1ビア420下層にボイドが発生することが無いように、第1ビア420の底面に接する部分に、傾斜部が形成されていることが好ましい。なお、本実施形態では、第1ビア420のうち、第1配線440が延伸する方向と垂直の方向において、対向する側面の全体に、傾斜部が形成されている。

【0041】

ここで、上記した傾斜部は、第1ビア420の側面と第1ビア420の底面とのなす角が、第1配線440の側面と第1配線440の底面とのなす角よりも大きい。図1(b)で示されている傾斜部において、第1ビア420の側面と第1ビア420の底面とのなす角をθ1とし、一方、図1(c)のように、第1配線440の側面と第1配線440の底面とのなす角をθ2としたとき、θ1>θ2である。なお、第1ビア420の側面と底面とのなす角θ1は、後述する第1ビアホール430の側面と底面とのなす角θ1に相当する。また、第1配線440の側面と底面とのなす角θ2は、後述する第1配線溝450の側面と底面とのなす角θ2に相当する。ただし、それぞれの角度θ1およびθ2は、ライナー絶縁膜520の厚さ分だけ異なるが、角度に与える影響は微差である。これにより、後述する金属埋設工程において、第1配線溝450よりも第1ビアホール430における金属の埋め込み速度を早くすることができる。

【0042】

次に、図2を用いて、半導体装置10の平面視の構成を説明する。図2は、第1の実施形態に係る半導体装置の構成を示す平面図である。図2は、第1基板100の第1面側から見た平面図のうち、第1バンプ電極700を省略している。

【0043】

第1ビア420は、たとえば、平面視で円形状に設けられている。ここで、第1ビア420は、第1ビア420の他端が第2配線600等と接する箇所において、金属560が第2配線600等と電気的に接続するための底面を有するように形成されている。すなわち、第1ビア420が傾斜部によって先細となり、第2配線600等と接続する箇所で、ライナー絶縁膜520によって絶縁されている状態は不適である。したがって、第1基板100の第1面側における第1ビア420の直径は、当該第1ビア420の貫通する長さに応じて、最適な大きさが決定される。具体的には、第1ビア420の直径は、たとえば、1μm以上8μm以下である。

【0044】

また、第1ビア420は、一端が第1配線440と接続することなく、独立して形成されていてもよい。このような第1ビア420は、プリント配線基板(不図示)などに直接接続するために設けられている。

【0045】

第1配線440は、たとえば、大電流を流すための配線である。したがって、第1配線440は、半導体素子300などと接続するローカル配線660またはローカル配線680よりも、高さが高く、また幅も太く形成されている。具体的には、第1配線440の高さは、5μm以上50μm以下である。一方、第1配線440の幅は、第1ビア420の直径以上で、直径の4倍以下である。具体的には、1μm以上12μm以下である。これにより、第1配線440に、大電流を流すことができる。一方、第1配線440の幅が上位範囲を超える場合は、CMP工程でのディッシングが無視できなくなる。

【0046】

次に、図3を用いて、半導体素子300について説明する。図3は、図1(a)における半導体素子300を拡大した断面図である。なお、図3は、図1(a)と上下を反転させている。

【0047】

図3のように、半導体素子300は、たとえば、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)である。なお、半導体素子300は、抵抗、コンデンサ、インダクタ等であってもよい。以下では、半導体素子300は、MOSFETである場合を説明する。

【0048】

図3のように、第1基板100には、素子分離領域310が形成されている。素子分離領域310の開口部には、第1基板100の第2面の近傍に、不純物が注入されたソース領域322およびドレイン領域324が形成されている。

【0049】

ソース領域322およびドレイン領域324で挟まれたチャネル領域(不図示)上には、ゲート絶縁膜342が形成されている。また、ゲート絶縁膜342上には、ゲート電極344が形成されている。さらに、ゲート絶縁膜342およびゲート電極344の両脇には、側壁絶縁膜346が形成されている。

【0050】

また、ゲート電極344は、コンタクト620を介して、第2配線600と接続している。なお、図3では、ゲート電極344が第2配線600に接続する場合を例示したが、ソース領域322に接続されるソース電極(不図示)や、ドレイン領域324に接続されるドレイン電極(不図示)等が、コンタクト620と同様のコンタクト(不図示)、ローカル配線(不図示)、およびビア(不図示)を介して、第2配線600に接続されていてもよい。

【0051】

実際には、図1(a)で図示されていない領域に、図3と同様の半導体素子300が複数個形成されており、論理回路や記憶素子等の回路を形成している。

【0052】

次に、図4を用いて、第1ビア420の側面と第1ビア420の底面のなす角θ1、および第1配線440の側面と第1配線440の底面のなす角θ2の最適な範囲について説明する。図4は、ビアまたは配線における側面と底面のなす角と、金属の埋め込み速度の関係を示した図である。

【0053】

なお、図4において、第1ビア420や第1配線440に関わらず、第1基板100に形成された一般的なビアまたは配線溝の側面と底面とのなす角をθ(図1(b)におけるθ1、θ2に対応)とし、横軸を180−θ(図中単位「°」、以下文中では「度」と表記)としている。縦軸は、そのビアまたは配線溝に金属を埋設したときの埋め込み速度を示している。

【0054】

図4のように、金属の埋め込み速度は、180−θに対して単調減少となっている。言い換えれば、第1ビア420および第1配線440における側面と底面とのなす角θが大きくなるほど、金属の埋め込み速度が大きくなる。

【0055】

さらに、図4で示されているように、金属の埋め込み速度は、180−θが83度を境にして、二つの速度の異なる領域が存在する。一方を、金属の埋め込み速度が速いα領域とし、他方を、金属の埋め込み速度が遅いβ領域とする。α領域は、180−θが83度以下であり、β領域は、180−θが83度以上90度以下である。

【0056】

ここで、前述のように、第1ビア420は、当該第1ビア420の側面と当該第1ビア420の底面とのなす角θ1が、第1配線440の側面と第1配線440の底面とのなす角θ2より大きい傾斜部を有している。これにより、後述する金属埋設工程において、第1配線溝450よりも第1ビアホール430における金属の埋め込み速度を早くすることができる。

【0057】

したがって、傾斜部における第1ビア420の側面と第1ビア420の底面のなす角θ1はα領域であり、第1配線440の側面と第1配線440の底面のなす角θ2はβ領域であることが好ましい。この場合、第1ビア420での埋め込み速度を第1配線440での埋め込み速度よりも大きくすることができるため、第1ビア420での埋設時間と第1配線440での埋設時間を近づけることができる。これにより、第1配線440が第1ビア420よりも早く埋設されて、第1ビア420の上と比較して、第1配線440の上面が膨らんでしまうことを防ぐことができる。

【0058】

すなわち、180−θ1が、75度以上83度以下であり、180−θ2が、85度以上90度以下である。より好ましくは、180−θ1が、79度以上83度以下であり、180−θ2が、85度以上87度以下であることが好ましい。

【0059】

言い換えると、傾斜部は、第1ビア420の側面と第1ビア420の底面のなす角θ1が97度以上105度以下であり、第1配線440の側面と第1配線440の底面のなす角θ2は90度以上95度以下である。より好ましくは、傾斜部は、第1ビア420の側面と第1ビア420の底面のなす角θ1が97度以上101度以下であり、第1配線440の側面と第1配線440の底面のなす角θ2は93度以上95度以下である。

【0060】

θ1、θ2が上記範囲であることにより、第1配線溝450における金属の埋め込み速度を遅くし、第1ビアホール430における金属の埋め込み速度を早くすることができる。なお、θ1を105度以下としたのは、平面視での傾斜部の占める範囲が広くなり、結果的に第1ビア420における底面の面積が小さくなってしまうからである。一方、θ2を90度以上としたのは、逆テーパーとなると極端に金属の埋め込み速度が落ちるだけでなく、ボイドを発生させてしまう可能性があるためである。

【0061】

次に、図5を用い、ライナー絶縁膜520について説明する。図5は、図1(b)におけるビアを拡大した断面図である。

【0062】

図5のように、第1基板100とバリアメタル層540との間には、ライナー絶縁膜520が設けられている。このライナー絶縁膜520のうち、第1ビア420の一端側の膜厚をa(nm)とし、第1ビア420の他端側の膜厚をb(nm)としたとき、

b−a≧7

である。

【0063】

なお、ここでいう「第1ビア420の一端側」とは、第1ビア420が第1配線440と接続しておらず、独立している場合は、第1ビア420が第1基板100の上面と同一面を形成している部分のことをいう。一方、第1ビア420が第1配線440と接続している場合は、第1ビア420が第1配線440と接している部分のことをいう。

【0064】

また、ここでいう「第1ビア420の他端側」とは、第1ビア420が第2配線600等と接続している場合において、第1ビア420が第2配線600と接している部分のことをいう。

【0065】

ここで、第1ビア420の他端側(底面側)のライナー絶縁膜520は、ピンホールができやすい。ピンホールが発生すると、第1ビア420が第1基板100と短絡して絶縁不良を起こしてしまう。また、第1ビア420の金属560がマイグレーションするなどの絶縁不良も発生する可能性がある。このため、ライナー絶縁膜520を上記膜厚構成にすることにより、第1ビア420の他端側にピンホールのない緻密なライナー絶縁膜520を形成する。これにより、上記のような絶縁不良を抑制することができる。

【0066】

なお、第1基板100と、第1層間絶縁膜200との境界で、第1ビア420の側面の角度が変化していてもよい。第1基板100側における第1ビア420の側面と第1ビア420との底面のなす角θ1と、第1層間絶縁膜200側における第1ビア420の側面と第1ビア420との底面のなす角θ1とが、上記したように97度以上105度以下の範囲であればよい。後述するビアホール(422)を形成するためのエッチング工程において、第1基板100と、第1層間絶縁膜200とでエッチングレートが異なる可能性がある。このため、第1基板100と、第1層間絶縁膜200との境界で、θ1が変化していても、上記範囲内であることにより、本実施形態の効果を得ることができる。

【0067】

次に、図6から図10を用い、第1の実施形態に係る半導体装置の製造方法について説明する。第1の実施形態に係る半導体装置の製造方法は、下記のような工程を備えている。まず、第1基板100の第1面から、当該第1基板100を貫通する第1ビアホール430を形成するとともに、少なくとも一つ以上の第1ビアホール430の一端と接続する第1配線溝450を形成する(以降、エッチング工程)。次いで、第1ビアホール430および第1配線溝450に金属560を埋め込むことにより、第1ビア420および第1配線440を形成する(以降、金属埋設工程)。ここで、エッチング工程において、第1ビアホール430に、側面と底面とのなす角θ1が、第1配線溝450の側面と第1配線溝450の底面とのなす角θ2より大きい傾斜部を形成する。以下、詳細を説明する。

【0068】

まず、図6(a)のように、第2面側に、半導体素子300、ローカル配線660、およびローカル配線680等が形成された第1基板100を準備する。なお、以降の図では、ローカル配線660およびローカル配線680の符号を省略する。

【0069】

ここで、後述するエッチング工程の前に、第1基板100のうち、第1面と反対の第2面側に、第2配線600を形成する。図6(a)で示されているように、第2配線600を、第1層間絶縁膜200に埋設するように形成してもよい。

【0070】

次いで、第1基板100の第1面上に、レジスト膜800を成膜する。次いで、露光および現像により、レジスト膜800に、第1ビアホール430を形成するための開口を形成する。

【0071】

次いで、図6(b)のように、RIE(Reactive Ion Etching)により、第1基板100の第1面から、当該第1基板100を貫通する第1ビアホール430を形成する。このとき、第1基板100を貫通するとともに、第1層間絶縁膜200の一部をエッチングして、第1ビアホール430を形成する。このとき、エッチングとクリーニングを繰り返し行うことで、第1ビアホール430を形成する。具体的には、エッチングとクリーニングを、8回以上繰り返して行う。

【0072】

また、この段階では、第2配線600に到達しない範囲で、第1ビアホール430を形成する。これにより、レジスト膜800のアッシング工程において、第2配線600が酸化されることを抑制することができる。

【0073】

このエッチング工程において、第1ビアホール430として、側面と底面とのなす角θ1が、後述する第1配線溝450の側面と第1配線溝450の底面とのなす角θ2より大きい傾斜部の中間的な形状を形成する。なお、第1配線溝450までをエッチングした後において、上記した傾斜部の形状となっていればよい。すなわち、必ずしも、この段階で、上記した傾斜部を有している必要は無い。したがって、ここでは、後述するエッチング工程後の形状が所望の形状となるように、第1ビアホール430として、傾斜部の中間的な形状を形成しておく。

【0074】

次いで、レジスト膜800をアッシングにより除去する。

【0075】

次いで、図7(a)のように、第1ビアホール430の内部に、レジスト膜800を埋設する。ここで、実際には、図7(a)における第1基板100上にもレジスト膜800が形成されるため、エッチバックにより、レジスト膜800を平坦化する。なお、エッチバックを行わなくてもよい。

【0076】

次いで、図7(b)のように、第1基板100の第1面上に、レジスト膜800を成膜する。次いで、露光および現像により、第1基板100上のレジスト膜800に、第1配線溝450を形成するための開口を形成する。

【0077】

次いで、図8(a)のように、RIEにより、第1基板100をエッチングすることにより、第1配線溝450のうち、途中までエッチングされた中間的な溝(不図示)を形成する。次いで、レジスト膜800をアッシングにより除去する。次いで、全面エッチバックにより、第1ビアホール430を第2配線600と接するまでエッチングする。これにより、第1ビアホール430の他端を、第2配線600と接続する。また、同時に、第1配線溝450のうち、途中までエッチングされた中間的な溝(不図示)をさらにエッチングし、所望の第1配線溝450の深さまでエッチングする。

【0078】

ここで、図8(b)、図8(c)のように、このエッチング工程において、第1ビアホール430に、側面と底面とのなす角θ1が、後述する第1配線溝450の側面と第1配線溝450の底面とのなす角θ2より大きい傾斜部を形成する。

【0079】

図8(b)で示されているように、第1ビア420の側面と第1ビア420の底面のなす角θ1が、たとえば97度以上105度以下となるように、傾斜部を形成する。これにより、後述する金属埋設工程において、第1配線溝450よりも第1ビアホール430における金属560の埋め込み速度を早くすることができる。

【0080】

図8(c)で示されているように、第1配線溝450の側面と第1配線溝450の底面のなす角θ2がたとえば90度以上97度以下となるように、第1配線溝450を形成する。これにより、第1ビアホール430よりも第1配線溝450における金属560の埋め込み速度を遅くすることができる。

【0081】

以上のように、第1ビアホール430を形成した後、第1配線溝450を形成する(以上、エッチング工程)。ここで、第1配線溝450を先に形成した場合、第1ビアホール430をエッチングする際に、第1配線溝450の形状を上記した角度に保ちにくい。したがって、第1ビアホール430を先に形成することにより、上記した形状の第1ビアホール430および第1配線溝450を容易に形成することができる。

【0082】

次いで、図9(a)のように、第1ビアホール430および第1配線溝450の内側の側面および底面と、第1基板100上とに、ライナー絶縁膜520を形成する。ここでは、CVD(Chemical Vapor Deposition)、または第1基板100の熱酸化などにより、ライナー絶縁膜520を形成する。

【0083】

ここで、第1ビアホール430は、アスペクト比が大きいため、ライナー絶縁膜520は、第1ビアホール430の一端側が厚く、他端側が薄く形成される傾向にある。本実施形態では、上述したように、第1ビアホール430に、側面と底面とのなす角θ1が、第1配線溝450の側面と第1配線溝450の底面とのなす角θ2より大きい傾斜部を形成する。これにより、第1ビアホール430の他端側の側壁に対しても、ライナー絶縁膜520を厚く成膜することができる。

【0084】

次いで、エッチバックにより、第1ビアホール430の底面、すなわち、第1ビアホール430が第2配線600と接している部分のライナー絶縁膜520を除去する。これにより、第1ビアホール430内に、第2配線600を露出させる。

【0085】

ここで、図5で示したように、このライナー絶縁膜520のうち、第1ビア420の一端側の膜厚をa(nm)とし、第1ビア420の他端側の膜厚をb(nm)としたとき、

b−a≧7

となるように、ライナー絶縁膜520を形成する。

【0086】

次いで、図9(b)のように、第1ビアホール430の底面と、ライナー絶縁膜520で覆われた第1ビアホール430の側面および第1配線溝450の側面ならびに底面と、第1基板100上とに、スパッタにより、バリアメタル層540を形成する。

【0087】

次いで、図10(a)のように、めっき法により、第1ビアホール430および第1配線溝450内に、金属560を埋め込む。このとき、めっき条件は、温度が20℃以上30℃以下であり、電流値は3A以上20A以下であることが好ましい。これにより、図4に示した埋め込み速度を再現することができる。

【0088】

ここで、上記したように、第1ビアホール430および第1配線溝450の形状を調整することにより、第1ビアホール430への金属560の埋め込み速度を速くし、一方、第1配線溝450への金属560の埋め込み速度を遅くしている。したがって、めっき後の第1基板100の第1面は、第1ビアホール430の直上と第1配線溝450の直上とで凹凸に大きな差が無く、その後のCMP工程に悪影響を与えることがない。

【0089】

次いで、CMPにより、第1基板100の第1面側を平坦化する。以上により、第1ビア420および第1配線440を形成する(以上、金属埋設工程)。

【0090】

図10(b)のように、第1基板100の第1配線440上に、第1ビア420または第1配線440と接続する第1バンプ電極700を形成する。ここでは、第1バンプ電極700を、たとえば、第1ビア420の直上に形成する。

【0091】

以上のようにして、本実施形態に係る半導体装置10を得る。

【0092】

次に、第1の実施形態の効果について、説明する。

【0093】

本実施形態によれば、第1ビア420は、当該第1ビア420の側面と底面とのなす角θ1が、第1配線440の側面と底面とのなす角θ2より大きい傾斜部を有している。これにより、その後の金属埋設工程において、第1配線溝450よりも、第1ビアホール430における金属560の埋め込み速度を速くすることができる。すなわち、第1ビア420での埋設時間と第1配線440での埋設時間を近づけることができる。したがって、金属560が埋設された後の第1基板100の第1面を平坦にすることができ、さらにCMPにおいて均一に平坦化することができる。

【0094】

したがって、本実施形態によれば、大電流を流す第1ビア420および第1配線440を有し、且つ、当該第1ビア420および第1配線440が形成された第1面が平坦な半導体装置10を提供することができる。

【0095】

(第2の実施形態)

図11は、第2の実施形態に係る半導体装置10の構成を示す断面図である。第2の実施形態は、第1基板100の第2面に、第2配線600と接続する第1バンプ電極700を備えている点を除いて、第1の実施形態と同様である。以下、詳細を説明する。

【0096】

図11のように、第1基板100の第2面側には、第2配線600上に、電極パッド640が形成されている。電極パッド640としては、たとえば、Alである。

【0097】

また、電極パッド640の外周表面には、保護膜(不図示)、ポリイミド膜(不図示)などが形成されている。ここでは、いずれも第1層間絶縁膜200の一部として図示している。

【0098】

さらに、電極パッド640上には、第1バンプ電極700が形成されている。この第2面側の第1バンプ電極700は、第1面側の第1バンプ電極700と同一の材料を用いることができる。ただし、第2面側の第1バンプ電極700は、第1面側の第1バンプ電極700と実装時の温度が異なる材料で形成されていてもよい。また。第2面側の第1バンプ電極700は、ボンディングワイヤであってもよい。

【0099】

第2の実施形態によれば、第1基板の第1面と反対の第2面に、第2配線600と接続する第1バンプ電極700が形成されている。これにより、第1基板100の第1面および第2面の両側から外部接続することができる。たとえば、両側に、プリント配線基板などを実装することができる。

【0100】

(第3の実施形態)

図12は、第3の実施形態に係る半導体装置10の構成を示す断面図である。第3の実施形態は、以下の点を除いて、第1の実施形態と同様である。第1基板100の第1面と反対の第2面側には、第1基板100側の面に第3配線602を備える第2基板102が接合されている。また、第2配線600は、バンプ720(たとえば、マイクロバンプなど)を介して、第3配線602と接続している。以下、詳細を説明する。

【0101】

図12のように、第1基板100の第2面側には、第1層間絶縁膜200上に、接合層900が形成されている。接合層900のとしては、熱硬化性樹脂が用いられる。熱硬化性樹脂としては、たとえば、エポキシ樹脂やノンコンダクタフィルムなどである。また、接合層900を形成する方法としては、第1基板100と第2基板102を合わせてから熱酸化を行う方法、または第1基板100と第2基板102の表面をArビームで活性化して接続する方法なども用いられる。

【0102】

また、接合層900を介して、第1基板100の第2面側に、第2基板102が接合されている。このとき、第2基板102は、後述する第3配線602が形成された面に、第1基板100が接合されている。

【0103】

この第2基板102には、第1基板100と同様に、半導体素子300等が形成されている。また、第2基板102上には、第2層間絶縁膜202が形成されている。さらに、第2層間絶縁膜202の最上層には、第3配線602が形成されている。

【0104】

ここで、第1基板100には、第1の実施形態と同様に、第1基板100を貫通するように、第1ビア420が形成されている。この第1ビア420の他端は、第1ビア420の他端は、第2配線600と接続している。

【0105】

また、第2配線600の第2基板102側には、たとえば、第2基板102の第3配線602と接続するためのビア(符号不図示)が形成されている。一方、第2層間絶縁膜202のうち、第3配線602の第1基板100側には、たとえば、第1基板100の第2配線600と接続するためのビア(符号不図示)が形成されている。

【0106】

また、第2配線600は、バンプ720を介して、第2基板102のうち、第1基板100側の面に形成された第3配線602と接続している。これにより、第1基板100の第1面側から、第2基板102における第3配線602等に電流を供給することができる。

【0107】

バンプ720は、接合層900内に設けられている。ここでいう「バンプ720」とは、たとえば、マイクロバンプなどをいう。バンプ720の材料としては、たとえば、第1バンプ電極700等と同じ材料を用いることができる。また、バンプ720は、微細な第2配線600および第3配線602を接続するため、第1バンプ電極700等よりも小さいことが好ましい。

【0108】

なお、第2配線600の第2基板102側、および第3配線602の第1基板100側に、双方の配線を接続するためのビアが設けられている場合を説明したが、第2配線600および第3配線602が、直接、バンプ720を介して、相互に接続していてもよい。

【0109】

なお、第1の実施形態と同様に、第1ビア420は、当該第1ビア420の側面と当該第1ビア420の底面とのなす角θ1が、第1配線440の側面と第1配線440の底面とのなす角θ2より大きい傾斜部を有している。

【0110】

ここで、第3配線602は、たとえば、第2基板102に設けられた半導体素子300等に電流を供給する電源配線、またはグランド配線である。前述のように、この第3配線602は、バンプ720および第2配線600を介して、第1ビア420と接続されていることにより、第1ビア420から大電流の供給を受けることができる。

【0111】

このように、第1ビア420は、第1基板100と第2基板102の両者に対して、大電流を供給することができる。

【0112】

また、第1基板100は、たとえば、論理回路を備えている。一方、第2基板102は、たとえば、論理回路から伝達された信号を記憶する記憶素子を備えている。これにより、記憶装置を形成するために必要な素子または回路を有する各種基板を、省スペースに積層することができる。

【0113】

次に、第3の実施形態に係る半導体装置10の製造方法について説明する。第1の実施形態の製造方法に加え、第1基板100側の第1面に第3配線602を備える第2基板102を準備する。また、第1基板100の第1面と反対の第2面側に、第2基板102を接合する(接合工程)。この接合工程において、第2配線600を、バンプを介して、第3配線602と接続する。以下、第1の実施形態と同様の部分は省略しながら、詳細を説明する。

【0114】

まず、第1の実施形態と同様にして、第1基板100に、図10(b)で示されている状態の半導体装置10の中間体を形成する。

【0115】

次いで、第1層間絶縁膜200のうち、第2配線600上に、たとえば、一端が第2配線600と接続するビア(符号不図示)を形成する。なお、当該ビアを、第2基板102の第3配線と接続するように配置する。

【0116】

次いで、第1基板100側の第1面に第3配線602を備える第2基板102を準備する。そのほか、たとえば、第1基板100には、半導体素子300が形成されている。また、第3配線602は、第2層間絶縁膜202に埋設されていてもよい。

【0117】

次いで、第2層間絶縁膜202のうち、第3配線602上に、たとえば、一端が第3配線602と接続するビア(符号不図示)を形成する。なお、当該ビアを、第1基板100の第2配線600と接続するように配置する。

【0118】

次いで、接合層900を介して、第1基板100の第1面と反対の第2面側に、第2基板102を接合する(接合工程)。この接合工程において、第2配線600を、バンプを介して、第3配線602と接続する。

【0119】

以上のようにして、第3の実施形態に係る半導体装置10を得る。

【0120】

第3の実施形態によれば、第1基板100の第1面と反対の第2面側には、第2基板102が接合されている。これにより、省スペースに複数の基板を積層することができる。

【0121】

(第4の実施形態)

図13は、第4の実施形態に係る半導体装置10の構成を示す断面図である。第4の実施形態は、以下の点を除いて、第1の実施形態、または第3の実施形態と同様である。第1基板100の第1面と反対の第2面側に、第2基板102が接合されている。第2基板102は、第1基板100側の第1面から、当該第2基板102を貫通するとともに、一端が第1基板100側の第1面と同一面を形成する第2ビア422と、第1基板100と反対側に設けられ、第2ビア422の他端と接続する第3配線602と、を備えている。また、第2配線600は、バンプ720(たとえば、マイクロバンプなど)を介して、第2ビア422の一端と接続している。以下、詳細を説明する。

【0122】

図13のように、第1基板100の第2面側には、第1層間絶縁膜200上に、接合層900が形成されている。

【0123】

また、接合層900を介して、第1基板100の第2面側に、第2基板102が接合されている。このとき、第4の実施形態では、第3の実施形態と異なり、第2基板102は、第3配線602が形成されている面と反対側に、第1基板100が接合されている。

【0124】

また、この第2基板102のうち、第1基板100側の第1面から、第2ビア422が、当該第2基板102を貫通している。また、第2ビア422の一端は、第1基板100側の第1面と同一面を形成している。

【0125】

さらに、第2基板102には、第1基板100と反対側に、第3配線602が設けられている。第3配線602は、第2ビア422の他端と接続している。

【0126】

また、第1基板100の第2面側に設けられた第2配線600は、バンプ720を介して、第2ビア422の一端と接続している。なお、ここでは、第3の実施形態と同様にして、たとえば、第2配線600の第2基板側に、ビア(符号不図示)が設けられている。したがって、第2配線600は、このビア、およびバンプ720を介して、第2ビア422の一端と接続している。これにより、第1基板100の第1面側から、第2基板102における第3配線602等に電流を供給することができる。なお、上記ビアを介さずに、第2配線600および第2ビア422の一端が、直接、バンプ720を介して、相互に接続していてもよい。

【0127】

バンプ720は、接合層900内に設けられている。バンプ720は、第3の実施形態と同様のものを用いることができる。

【0128】

また、第3配線602上には、たとえば、電極パッド640が形成されている。また、電極パッド640の外周表面には、たとえば、保護膜(不図示)、ポリイミド膜(不図示)などが形成されている。

【0129】

さらに、第2基板102には、第1基板100と反対側の面に設けられ、第3配線602と接続する第2バンプ電極702が設けられていてもよい。これにより、第2基板102のうち、第1基板100と反対側の面からも、プリント配線基板などに外部接続することができる。

【0130】

次に、第4の実施形態に係る半導体装置10の製造方法について説明する。第4の実施形態に係る半導体装置10の製造方法は、以下の点を除いて、第1の実施形態、または第3の実施形態と同様である。第1の実施形態の製造方法に加え、第2基板102を準備する。また、第1基板100の第1面と反対の第2面側に、第2基板102を接合する(接合工程)。この接合工程において、第2配線600を、バンプを介して、第2ビア422の一端と接続する。以下、第3の実施形態と同様の部分は省略しながら、詳細を説明する。

【0131】

まず、第3の実施形態と同様にして、第1基板100に、図10(b)で示されている状態の半導体装置10の中間体を形成する。さらに、第1層間絶縁膜200のうち、第2配線600上に、たとえば、一端が第2配線600と接続するビア(符号不図示)を形成する。

【0132】

次いで、下記のような第2基板102を準備する。第2基板102のうち、第1基板100側の第1面から、第2基板102を貫通するとともに、一端が第1基板100側の第1面と同一面を形成する第2ビア422と、第1基板100と反対側に設けられ、第2ビア422の他端と接続する第3配線602と、を備えている。

【0133】

また、あらかじめ、第2ビア422が、第2配線600と接続するように、配置されている。すなわち、第2ビア422は、平面視で、第2配線600と重なるように配置されている。そのほかの構成は、第3の実施形態における第2基板102と同様である。

【0134】

なお、第2基板102を準備する工程は、第1の実施形態において、第1配線440を形成しない点を除いて、同様である。したがって、第1ビア420の側面と第1ビア420の底面(ここでは、第3配線602と接する面)とのなす角θ1が97度以上105度以下であってもよい。

【0135】

次いで、接合層900を介して、第1基板100の第1面と反対の第2面側に、第2基板102を接合する(接合工程)。この接合工程において、第2配線600を、バンプを介して、第2ビア422の一端と接続する。

【0136】

次いで、第2基板102のうち、第1基板100と反対側の面に、第3配線602と接続する第2バンプ電極702を形成してもよい。

【0137】

以上のようにして、第4の実施形態に係る半導体装置10を得る。

【0138】

第4の実施形態によれば、第3の実施形態と同様の効果を得ることができる。

【0139】

(第5の実施形態)

図14は、第5の実施形態に係る半導体装置10の構成を示す断面図である。第5の実施形態は、以下の点を除いて、第3、第4の実施形態と同様である。第1基板100と第2基板102との間には、少なくとも一つ以上の第3基板104が接合されている。第3基板104は、当該第3基板104の第1面から、当該第3基板104を貫通するとともに、一端が第3基板104の第1面と同一面を形成する第3ビア424と、第3基板104の第1面と反対の第2面上に設けられ、第3ビア424の他端と接続する第4配線604と、を備えている。また、第3ビア424の一端、または第4配線604は、それぞれ、バンプ720を介して、第1基板100の第2配線600、または第2基板102の第2ビア422の一端と接続している。以下、詳細を説明する。

【0140】

図14のように、上下の第1基板100および第2基板102の構成は、第4の実施形態と同様である。

【0141】

第1基板100と第2基板102との間には、少なくとも一つ以上の第3基板104を備えている。第3基板104は、第1基板100および第2基板102のそれぞれとの接合面において、接合層900を介して接合されている。なお、第3基板104は、一つだけでなく、複数であってもよい。

【0142】

また、第3基板104は、第1基板100または第2基板102と同様の基板を用いることができる。ここでは、第3基板104には、半導体素子300、第3層間絶縁膜204および第4配線604が形成されている。

【0143】

また、第3基板104のうち、当該第3基板104の第1面から、第3ビア424が、当該第3基板104を貫通している。また、第3ビア424の一端は、第3基板104の第1面と同一面を形成している。

【0144】

さらに、第3基板104には、第1面と反対の第2面上に、第4配線604が設けられている。第4配線604は、第3ビア424の他端と接続している。なお、ここでは、たとえば、第4配線604の第2基板側に、ビア(符号不図示)が設けられている。

【0145】

また、第3ビア424の一端、または第4配線604は、それぞれ、バンプ720を介して、第1基板100の第2配線600、または第2基板102の第2ビア422の一端と接続している。これにより、第1基板100および第2基板102だけでなく、少なくとも一つ以上の第3基板104に対しても大電流を供給することができる。

【0146】

なお、図14では、たとえば、第3ビア424の一端が第1基板100の第2配線600と接続している。また、第4配線604は、第2基板102の第2ビア422の一端と接続している。一方、第3基板104は、上記とは逆に接合されていてもよい。

【0147】

また、その他の変形例として、第3の実施形態のように、第2基板102は、第1基板100側の第1面に第3配線602が配置されていても良い。したがって、第3ビア424の一端、または第4配線604は、それぞれ、バンプ720を介して、第1基板100の第2配線600、または第2基板102の第3配線602と接続していてもよい。

【0148】

また、第1基板100は、たとえば、論理回路を備えている。一方、第2基板102および第3基板104は、たとえば、論理回路から伝達された信号を記憶する記憶素子を備えている。これにより、第3の実施形態と同様にして、記憶装置を形成するために必要な素子または回路を有する各種基板を、省スペースに積層することができる。

【0149】

次に、第5の実施形態に係る半導体装置10の製造方法について説明する。第5の実施形態に係る半導体装置10の製造方法は、以下の点を除いて、第3の実施形態、または第4の実施形態と同様である。第5の実施形態に係る半導体装置10の製造方法は、さらに以下の工程を備えている。第2基板102と、少なくとも一つ以上の第3基板104と、を準備する。また、第1基板100の第1面と反対の第2面側に、第3基板104と、第2基板102と、を順に接合する(接合工程)。この接合工程において、第3ビア424の一端、または第4配線604を、それぞれ、バンプを介して、第1基板100の第2配線600、または第2基板102の第2ビア422の一端と接続する。以下、第3、第4の実施形態と同様の部分は省略しながら、詳細を説明する。

【0150】

まず、第4の実施形態と同様にして、第1基板100および第2基板102を準備する。

【0151】

次いで、下記のような第3基板104を準備する。第3基板104のうち、当該第3基板104の第1面から、当該第3基板104を貫通するとともに、一端が第3基板104の第1面と同一面を形成する第3ビア424と、第3基板104の第1面と反対の第2面に設けられ、第3ビア424の他端と接続する第4配線604と、を備えている。

【0152】

また、あらかじめ、第3ビア424が、第2配線600と接続するように、配置されている。そのほかの構成は、第3の実施形態における第2基板102と同様である。

【0153】

なお、第3基板104を準備する工程は、第1の実施形態において、第1配線440を形成しない点を除いて、同様である。

【0154】

次いで、第1基板100の第1面と反対の第2面側に、第3基板104と、第2基板102と、を順に接合する(接合工程)。この接合工程において、第3ビア424の一端、または第4配線604を、それぞれ、バンプを介して、第1基板100の第2配線600、または第2基板102の第2ビア422の一端と接続する。

【0155】

上述のように、この第3基板104を接合する際には、図14で示されている構成に限らず、上下逆の構成でもよい。また、複数の第3基板104を接合する際についても、それぞれの第3基板104は、任意の接合面と接合することができる。

【0156】

また、その他の変形例として、第3の実施形態のように、第2基板102を、第1基板100側の第1面に第3配線602が配置されるように接合してもよい。

【0157】

以降の工程は、第4の実施形態と同様である。

【0158】

第5の実施形態によれば、第3、第4の実施形態と同様の効果を得ることができる。さらに、第5の実施形態によれば、3以上の基板を省スペースに接合することができ、複合的な機能を有する半導体装置10を提供することができる。

【0159】

(第6の実施形態)

図15は、第6の実施形態に係る半導体装置10の構成を示す断面図である。第6の実施形態は、第1基板100上に設けられた第1層間絶縁膜220側から、第1層間ビア460および第1配線440が形成されている点を除いて、第1の実施形態と同様である。以下、詳細を説明する。

【0160】

図15のように、第1基板100の第1面には、第1の実施形態と同様に、半導体素子300、第1層間絶縁膜200および第2配線600が形成されている。なお、第6の実施形態における「第1基板100の第1面」とは、半導体素子300、第1層間絶縁膜200等が形成された面のことをいう。

【0161】

さらに、第1層間絶縁膜200上には、さらに第1層間絶縁膜220が形成されている。この第1層間絶縁膜220は、第1層間絶縁膜200と同一の材料を用いることができる。なお、第1層間絶縁膜220は、第1層間絶縁膜200と異なる材料であってもよい。

【0162】

また、第1層間ビア460は、第1層間絶縁膜220を貫通するように形成されている。さらに、第1層間ビア460は、第1層間絶縁膜220とともに、第1層間絶縁膜200の一部を貫通している。第1層間ビア460の他端は、第2配線600と接続している。

【0163】

また、第1配線440は、第1層間絶縁膜220の表面に埋設されている。さらに、第1配線440は、少なくとも一つ以上の第1層間ビア460の一端と接続している。

【0164】

また、上述の第1層間絶縁膜220中に埋設された第2配線600は、第1層間ビア460の他端と接続している。

【0165】

また、第1層間ビア460は、当該第1層間ビア460の側面と当該第1層間ビア460の底面とのなす角θ1が、第1配線440の側面と第1配線440の底面とのなす角θ2より大きい傾斜部を有している。

【0166】

次に、第6の実施形態に係る半導体装置10の製造方法について説明する。第6の実施形態に係る半導体装置10の製造方法は、第1基板100上に設けられた第1層間絶縁膜220側から、第1層間ビア460および第1配線440を形成する点を除いて、第1の実施形態と同様である。以下、第1の実施形態と同様の部分は省略しながら、詳細を説明する。

【0167】

まず、半導体素子300、第1層間絶縁膜200および第2配線600が形成された第1基板100を準備する。次いで、第1層間絶縁膜200上に、第1層間絶縁膜220を形成する。

【0168】

次いで、第1層間絶縁膜220を貫通する第1層間ビアホールを形成するとともに、少なくとも一つ以上の第1層間ビアホールの一端と接続する第1配線溝450を形成する(エッチング工程)。なお、第1層間ビアホールとは、第1の実施形態における第1ビアホール430と同様である。

【0169】

ここで、このエッチング工程において、第1層間ビアホールに、側面と底面とのなす角θ1が、第1配線溝450の側面と第1配線溝450の底面とのなす角θ2より大きい傾斜部を形成する。

【0170】

次いで、第1層間ビアホールおよび第1配線溝450に金属560を埋め込むことにより、第1層間ビア460および第1配線440を形成する(金属埋設工程)。

【0171】

以降の工程は、第1の実施形態と同様である。

【0172】

第6の実施形態によれば、第1の実施形態のように、第1面が第1基板100の基板面でなくとも、第1ビア420と同様に第1層間ビア460および第1配線440を形成することができる。これにより、第1の実施形態と同様の効果を得ることができる。

【0173】

(第7の実施形態)

図16は、第7の実施形態に係る半導体装置10の構成を示す断面図である。第7の実施形態は、以下の点を除いて、第3の実施形態、または第6の実施形態と同様である。第1基板100の第1面と反対の第2面から、第1基板100を貫通し、一端が第2配線600と接続するとともに、他端が第2面と同一面を形成する第1基板ビア420を備えている。以下、詳細を説明する。

【0174】

図16のように、第1基板100の第1面と反対の第2面から、第1基板ビア420が貫通している。第1基板ビア420の一端は、第2配線600の下面と接続している。さらに、第1基板ビア420の他端は、第1基板100の第2面(裏面のこと)と同一面を形成している。

【0175】

なお、第1基板ビア420は、第2基板102の第3配線602と接続するように配置されている。すなわち、第1基板ビア420は、平面視で、第3配線602と重なるように配置されている。

【0176】

また、接合層900を介して、第1基板100と、第2基板102のうち、第3配線602が形成された面と、が接合されている。

【0177】

また、第1基板ビア420の他端は、バンプ720を介して、第2基板102の第3配線602と接続している。

【0178】

次に、第7の実施形態に係る半導体装置10の製造方法について説明する。第7の実施形態に係る半導体装置10の製造方法は、以下の点を除いて、第3の実施形態、または第6の実施形態と同様である。

【0179】

まず、第6の実施形態と同様にして、図15で示されている状態の半導体装置10の中間体を準備する。

【0180】

次いで、第1面と反対の第2面から、第1基板100を貫通し、一端が第2配線600と接続するとともに、第2面側の他端が当該第2面と同一面を形成するように、第1基板ビア420を形成する。

【0181】

なお、上記した第1基板ビア420を形成する工程は、第1層間ビア460を形成する工程の前に行ってもよい。

【0182】

他の工程は、第3の実施形態と同様である。

【0183】

第7の実施形態によれば、第3の実施形態と同様の効果を得ることができる。

【0184】

(第8の実施形態)

図17は、第8の実施形態に係る半導体装置10の構成を示す断面図である。第8の実施形態は、第1基板100が第7の実施形態と同様である点を除いて、第4の実施形態と同様である。以下、詳細を説明する。

【0185】

図17のように、接合層900を介して、第1基板100と、第2基板102のうち、第3配線602が形成されている面と反対側の面と、が接合されている。

【0186】

第7の実施形態と同様にして、第1基板100の第1面と反対の第2面から、第1基板ビア420が形成されている。

【0187】

一方で、第4の実施形態と同様にして、第2基板102の第1基板100側から、第2ビア422が形成されている。

【0188】

第1基板ビア420および第2ビア422は、互いに接続するように配置されている。すなわち、第1基板ビア420および第2ビア422は、平面視で重なるように配置されている。

【0189】

第1基板ビア420の他端は、バンプ720を介して、第2ビア422の一端と接続している。

【0190】

他の構成、および製造方法は、第4の実施形態と同様である。

【0191】

第8の実施形態によれば、第4の実施形態と同様の効果を得ることができる。

【0192】

(第9の実施形態)

図18は、第9の実施形態に係る半導体装置10の構成を示す断面図である。第9の実施形態は、第1基板100が第7の実施形態と同様である点を除いて、第5の実施形態と同様である。以下、詳細を説明する。

【0193】

図18のように、第1基板100と第2基板102との間に、少なくとも一つ以上の第3基板104を備えている。第3基板104は、第1基板100および第2基板102のそれぞれとの接合面において、接合層900を介して接合されている。なお、第3基板104は、一つだけでなく、複数であってもよい。

【0194】

第7の実施形態と同様にして、第1基板100の第1面と反対の第2面から、第1基板ビア420が形成されている。

【0195】

一方で、第5の実施形態と同様にして、第3基板104の第1基板100側から、第3ビア424が形成されている。また、第4の実施形態と同様にして、第2基板102の第1基板100側から、第2ビア422が形成されている。

【0196】

第1基板ビア420および第3ビア424は、互いに接続するように配置されている。すなわち、第1基板ビア420および第3ビア424は、平面視で重なるように配置されている。

【0197】

また、第3ビア424の一端、または第4配線604は、それぞれ、バンプ720を介して、第1基板ビア420の他端、または第2ビア422の一端と接続している。

【0198】

上述のように、この第3基板104を接合する際には、図18で示されている構成に限らず、上下逆の構成でもよい。また、複数の第3基板104を接合する際についても、それぞれの第3基板104は、任意の接合面と接合することができる。

【0199】

また、その他の変形例として、第7の実施形態のように、第2基板102を、第1基板100側の第1面に第3配線602が配置されるように接合してもよい。

【0200】

第9の実施形態によれば、第5の実施形態と同様の効果を得ることができる。

【0201】

なお、第3、第7の実施形態では、第2基板102の基板面には、第2バンプ電極702が形成されていない場合を説明したが、第1の実施形態のように、第2基板102の基板面側から第2ビア422または第1配線440が形成されていてもよい。このとき、第2ビア422の一端は、第3配線602と接続してもよい。さらに、当該第2ビア422または第1配線440の直上に、第2バンプ電極702が設けられていても良い。

【0202】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【符号の説明】

【0203】

10 半導体装置

100 第1基板

102 第2基板

104 第3基板

200 第1層間絶縁膜

202 第2層間絶縁膜

204 第3層間絶縁膜

220 第1層間絶縁膜

300 半導体素子

310 素子分離領域

322 ソース領域

324 ドレイン領域

342 ゲート絶縁膜

344 ゲート電極

346 側壁絶縁膜

420 第1ビア(第1基板ビア)

422 第2ビア

424 第3ビア

430 第1ビアホール

440 第1配線

450 第1配線溝

460 第1層間ビア

520 ライナー絶縁膜

540 バリアメタル層

560 金属

600 第2配線

602 第3配線

604 第4配線

620 コンタクト

640 電極パッド

660 ローカル配線

680 ローカル配線

700 第1バンプ電極

702 第2バンプ電極

720 バンプ

800 レジスト膜

900 接合層

【技術分野】

【0001】

本発明は、半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の高集積化に伴い、大電流を流すための配線を形成するために、様々な多層配線構造が提案されている。

【0003】

特許文献1(特開2010−045371号公報)には、以下のような貫通電極(Through Silicon Via:TSV)構造体が記載されている。この貫通電極構造体の導電性ビアは、基板の上部表面から下部表面に延長されて基板を貫通している。また、導電性ビアの底部には、NiおよびCoのうちの少なくともいずれか一方を有する導電性保護膜が形成されている。さらに、導電性保護膜に接触して、基板の下部表面には、分離ポリマー絶縁膜が形成されている。これにより、半導体基板の歪みを抑制することができる貫通電極構造体を提供することができるとされている。

【0004】

また、特許文献2(特開2010−080897号公報)には、以下のような半導体装置が記載されている。第1の半導体チップと第2の半導体チップとが貼り合わされている。第1の半導体チップの表面部に電極パッドが形成されている。第2の半導体チップ中に貫通ビアが形成されている。電極パッドには掘り込み部が形成されており、当該掘り込み部内に貫通ビアの底部が埋め込まれている。これにより、貫通ビアと電極パッドとの接合強度を増大させることにより、3次元配線構造を有する半導体装置の機械的強度を増大させることができるとされている。

【0005】

また、特許文献3(特開2009−302453号公報)には、以下のような半導体装置が記載されている。半導体チップの裏面に、凹部が形成されている。この凹部内部に、貫通電極の一部である裏面配線パッドと、裏面配線とが形成されている。これにより、チップ裏面側の平坦性が確保され、チップを扱う際の吸着力の低下が起きないとされている。

【0006】

また、特許文献4(特開2009−277927号公報)には、以下のような回路基板が記載されている。回路パターンは、基板の一面に設けられている。貫通電極は、基板に設けられた貫通孔の内部に充填され、一端が回路パターンに接合されている。回路パターンおよび貫通電極は、それぞれ貴金属成分を含有する領域を有しており、当該領域を介して、互いに接合されている。これにより、回路パターンの表面における酸化膜の発生、および貫通孔内のボイドの発生を抑制することができるとされている。なお、特許文献4の図1には、深さおよび底部のアスペクト比が1以上の貫通ビアが記載されている。

【0007】

また、特許文献5(特開2009−010312号公報)には、以下のようなスタックパッケージが記載されている。第1および第2半導体チップが、ボンディングパッド形成面が向かい合うように配置されている。第1および第2半導体チップには、複数のTSVが形成されている。第1および第2半導体チップの各ボンディングパッド形成面上には、複数の配線が、TSVとボンディングパッドとを連結するように形成されている。これにより、製造過程で発生するウェハおよび半導体チップの歪みおよびクラックを抑制することができるとされている。

【0008】

また、特許文献6(特開2009−004722号公報)には、貫通ビアの底面が半導体チップから突出するように半導体チップの下面を除去する工程を含む半導体パッケージの製造方法が記載されている。これにより、スタック型半導体パッケージの製造工程を単純化して、製造コストを減少させることができるとされている。

【0009】

また、特許文献7(特開平08−255797号公報)には、以下のような半導体基板の製造方法が記載されている。まず、第1シリコン基板の一主面に溝を形成する。次いで、溝の内部に金属層を形成する。次いで、熱処理により、金属層の少なくとも一部をシリサイド化する。次いで、一主面を平坦化する。次いで、第1シリコン基板の一主面と、第2シリコン基板とを接合する。これにより、基板に低抵抗のシリサイドの埋め込み層を有する、低コストで欠陥が少ない半導体装置を提供することができるとされている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2010−045371号公報

【特許文献2】特開2010−080897号公報

【特許文献3】特開2009−302453号公報

【特許文献4】特開2009−277927号公報

【特許文献5】特開2009−010312号公報

【特許文献6】特開2009−004722号公報

【特許文献7】特開平08−255797号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

上記した特許文献1から特許文献7では、ビアホールおよび配線溝を形成した後に、ビアホールおよび配線溝に、同時にめっき法により金属を埋め込む方法に関しては検討がなされていない。

【0012】

発明者は、ビアホールおよび配線溝を形成した後の金属埋設工程において、ビアホールおよび配線溝に、同時にめっき法により金属を埋め込む場合に、以下のような課題が発生することを見出した。ビアホールはアスペクト比が高いのに対して、配線溝は浅く、アスペクト比が低い。このため、同時にめっき法により金属を埋め込む場合、ビアホールよりも配線溝の方が早く金属が埋め込まれてしまい、配線溝上の金属が盛り上がった形状になってしまう。このように、金属が埋め込まれた基板表面の平坦性が悪いため、CMP(Chemical Mechanical Polishing)工程において、均一に研磨することができないという問題があることを見出した。

【課題を解決するための手段】

【0013】

本発明によれば、

第1基板と、

前記第1基板の第1面側から、当該第1基板を貫通する第1ビアと、

前記第1基板の前記第1面に埋設され、少なくとも一つ以上の前記第1ビアの一端と接続する第1配線と、

を備え、

前記第1ビアは、当該第1ビアの前記側面と当該第1ビアの底面とのなす角が、前記第1配線の側面と前記第1配線の底面とのなす角より大きい傾斜部を有する半導体装置が提供される。

【0014】

本発明によれば、

第1基板と、

前記第1基板の第1面上に設けられた第1層間絶縁膜と、

前記第1層間絶縁膜を貫通する第1層間ビアと、

前記第1層間絶縁膜の表面に埋設され、少なくとも一つ以上の前記第1層間ビアの一端と接続する第1配線と、

を備え、

前記第1層間ビアは、当該第1層間ビアの前記側面と当該第1層間ビアの底面とのなす角が、前記第1配線の側面と前記第1配線の底面とのなす角より大きい傾斜部を有する半導体装置が提供される。

【0015】

本発明によれば、

第1基板の第1面側から、当該第1基板を貫通する第1ビアホールを形成するとともに、少なくとも一つ以上の前記第1ビアホールの一端と接続する第1配線溝を形成するエッチング工程と、

前記第1ビアホールおよび前記第1配線溝に金属を埋め込むことにより、第1ビアおよび第1配線を形成する金属埋設工程と、

を備え、

前記エッチング工程において、前記第1ビアホールに、側面と底面とのなす角が、前記第1配線溝の側面と前記第1配線溝の底面とのなす角より大きい傾斜部を形成する半導体装置の製造方法が提供される。

【0016】

本発明によれば、

第1基板の第1面上に第1層間絶縁膜を形成する工程と、

前記第1層間絶縁膜を貫通する第1層間ビアホールを形成するとともに、少なくとも一つ以上の前記第1層間ビアホールの一端と接続する第1配線溝を形成するエッチング工程と、

前記第1層間ビアホールおよび前記第1配線溝に金属を埋め込むことにより、第1層間ビアおよび第1配線を形成する金属埋設工程と、

を備え、

前記エッチング工程において、前記第1層間ビアホールに、側面と底面とのなす角が、前記第1配線溝の側面と前記第1配線溝の底面とのなす角より大きい傾斜部を形成する半導体装置の製造方法が提供される。

【0017】

本発明によれば、第1ビア(第1層間ビア)は、当該第1ビア(第1層間ビア)の側面と底面とのなす角が、第1配線の側面と底面とのなす角より大きい傾斜部を有している。これにより、その後の金属埋設工程において、第1配線溝よりも、第1ビアホールにおける金属の埋め込み速度を速くすることができる。そして、金属が埋設された後の第1基板の第1面を平坦にすることができ、さらにCMPにおいて均一に平坦化することができる。したがって、大電流を流す第1ビア(第1層間ビア)および第1配線を有し、且つ、当該第1ビア(第1層間ビア)および第1配線が形成された第1面が平坦な半導体装置を提供することができる。

【発明の効果】

【0018】

本発明によれば、大電流を流す第1ビアおよび第1配線を有し、且つ、当該第1ビアおよび第1配線が形成された第1面が平坦な半導体装置を提供することができる。

【図面の簡単な説明】

【0019】

【図1】第1の実施形態に係る半導体装置の構成を示す断面図である。

【図2】第1の実施形態に係る半導体装置の構成を示す平面図である。

【図3】図1(a)における半導体素子を拡大した断面図である。

【図4】第1ビアまたは第1配線における側面と底面とのなす角と、金属の埋め込み速度の関係を示した図である。

【図5】図1(b)における第1ビアを拡大した断面図である。

【図6】第1の実施形態の効果を説明するための図である。

【図7】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図8】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図9】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図10】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図11】第2の実施形態に係る半導体装置の構成を示す断面図である。

【図12】第3の実施形態に係る半導体装置の構成を示す断面図である。

【図13】第4の実施形態に係る半導体装置の構成を示す断面図である。

【図14】第5の実施形態に係る半導体装置の構成を示す断面図である。

【図15】第6の実施形態に係る半導体装置の構成を示す断面図である。

【図16】第7の実施形態に係る半導体装置の構成を示す断面図である。

【図17】第8の実施形態に係る半導体装置の構成を示す断面図である。

【図18】第9の実施形態に係る半導体装置の構成を示す断面図である。

【発明を実施するための形態】

【0020】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0021】

(第1の実施形態)

図1から図5を用い、第1の実施形態に係る半導体装置10について説明する。まず、図1は、第1の実施形態に係る半導体装置10の構成を示す図である。図1(a)は、後述する図2のA−A'線断面図である。また、図1(b)は、図1(a)におけるB−B'線断面図である。また、図1(c)は、図1(a)におけるC−C'線断面図である。この半導体装置10は、以下のような構成を備えている。第1基板100と、第1基板100の第1面側から、当該第1基板100を貫通する第1ビア420と、第1基板100の第1面に埋設され、少なくとも一つ以上の第1ビア420の一端と接続する第1配線440と、を備えている。また、第1ビア420は、当該第1ビア420の側面と当該第1ビア420の底面とのなす角θ1が、第1配線440の側面と第1配線440の底面とのなす角θ2より大きい傾斜部を有している。以下、詳細を説明する。

【0022】

図1(a)のように、第1基板100の第1面側から、当該第1基板100を貫通する第1ビア420が形成されている。第1基板100は、たとえば、シリコン基板である。

【0023】

ここでいう「第1ビア420」とは、後述するバリアメタル層540と、バリアメタル層540内にめっきにより埋設された金属560とを含む接続孔のことである。なお、「第1ビア420」は、ライナー絶縁膜520を含まない。

【0024】

また、第1配線440は、第1基板100の第1面に埋設され、少なくとも一つ以上の第1ビア420の一端と接続している。

【0025】

ここでいう「第1配線440」とは、後述するバリアメタル層540と、バリアメタル層540内にめっきにより埋設された金属560とを含む配線のことである。なお、「第1配線440」は、ライナー絶縁膜520を含まない。

【0026】

第1配線440は、たとえば、半導体装置10をプリント配線基板(不図示)などに搭載する際に、プリント配線基板(不図示)などから供給された大電流を流すための配線である。さらに、第1配線440は、第1ビア420を介して、後述する第2配線600などの電源配線、またはグランド配線に、電流を供給する。

【0027】

ここで、第1配線440の高さ(深さ)は、5μm以上100μm以下である。これにより、第1配線440に大電流を流すことができる。

【0028】

これらの第1ビア420および第1配線440は、第1基板100に形成された第1ビアホール430および第1配線溝450に金属560を埋め込むことにより形成されている。図1において、第1ビアホール430は、製造工程において、ライナー絶縁膜520と第1基板100との界面に形成されていたものとして示している。また、第1配線溝450は、同様に、製造工程において、ライナー絶縁膜520と第1基板100との界面に形成されていたものとして示している。この金属埋設工程を含む製造方法については、詳細を後述する。

【0029】

第1ビアホール430の側面、第1配線溝450の側面および底面には、ライナー絶縁膜520が形成されている。すなわち、第1ビア420および第1配線440のうち、第1ビア420の底面を除く、第1ビア420の側面、および第1配線440の底面並びに側面と接するように、ライナー絶縁膜520が形成されている。ライナー絶縁膜520としては、たとえば、SiO2、SiN、SiCN、SiON、SiCのいずれか、またはこれらの積層膜である。また、ライナー絶縁膜520の厚さは、たとえば、20nm以上200nm以下である。

【0030】

また、第1ビア420および第1配線440のうち、内側の側面および底面には、バリアメタル層540が形成されている。バリアメタル層540としては、たとえば、Ta、TaN、Ti、TiN、Mn、CoWP、Co、NiB、W、Alなどである。また、バリアメタル層540の厚さは、たとえば、20nm以上250nm以下である。

【0031】

さらに、バリアメタル層540の内側には、めっき法により金属560が埋設されている。金属560としては、たとえば、Cu、Al、W、Ti、TiN、Ta、TaN、Mn、Coのいずれか、またはこれらの金属の合金である。

【0032】

上記のように、第1ビア420および第1配線440の境界には、バリアメタル層540が形成されておらず、第1ビア420および第1配線440内に一続きに金属560が形成されている。

【0033】

また、第1基板100の第1配線440上には、第1ビア420または第1配線440と接続する第1バンプ電極700が設けられている。第1バンプ電極700は、たとえば、第1ビア420の直上に形成されている。第1バンプ電極700の材料としては、たとえば、Sn、Sn−Ag、Sn−Ag−Cu、Auなどである。これにより、第1基板100を、第1面の第1バンプ電極700を介して、プリント配線基板などに搭載することができる。

【0034】

また、第1基板100は、第1配線440等が形成された第1面と反対の第2面上に第2配線600を備えている。また、第1ビア420の他端は、第2配線600と接続している。ここで、第2配線600は、第1基板100の第2面上に形成された配線であれば、限定されるものではない。図1では、第2配線600は、第1層間絶縁膜200中に形成された配線である。その他、第2配線600は、たとえば、第1層間絶縁膜200などの絶縁膜を介さずに、第1基板100の第2面の直上に接するように形成された配線(不図示)であってもよい。これにより、第1基板100の第1面側から、第2配線600等に電流を供給することができる。

【0035】

第1の実施形態では、第1基板100の第1面の反対の第2面側には、半導体素子300が形成されている。半導体素子300については、詳細を後述する。

【0036】

第1の実施形態では、第1基板100の第2面上には、第1層間絶縁膜200が設けられている。なお、第1層間絶縁膜200は、多層構造であってもよい。第1層間絶縁膜200としては、たとえば、SiO2、SiN、SiON、SiOC、SiOCH、SiCOHまたはSiOFなどである。上述の第2配線600は、第1層間絶縁膜200の最上層に埋設されている。

【0037】

さらに、第2面側には、半導体素子300に接続するコンタクト(たとえば後述するコンタクト620)、コンタクト620を介して半導体素子300と接続するローカル配線660が形成されている。また、ローカル配線660間、ローカル配線660並びにローカル配線680の間、およびローカル配線680並びに第2配線600の間を接続するビア(符号不図示)が形成されている。なお、第2配線600は、「グローバル配線」と呼ばれている。

【0038】

また、第1ビア420は、第1基板100を貫通するとともに、第1層間絶縁膜200の一部を貫通している。ここで、上述のように、第1ビア420の他端は、第2配線600と接続している。このように、ローカル配線660およびローカル配線680が形成された第1層間絶縁膜200を貫通して、第2配線600と接続することができる。

【0039】

ここで、第2配線600は、たとえば、第1基板100に設けられた半導体素子300等に電流を供給する電源配線、またはグランド配線である。前述のように、この第2配線600は、第1ビア420の他端と接続されていることにより、大電流の供給を受けることができる。

【0040】

また、図1(b)のように、第1ビア420は、傾斜部(符号不図示)を有している。この傾斜部は、第1ビア420に形成される位置が限定されるものではない。ただし、傾斜部は、第1ビア420のうち、少なくとも対向する一対の側面に形成されていることが好ましい。また、第1ビア420上層が先に埋め込まれ、第1ビア420下層にボイドが発生することが無いように、第1ビア420の底面に接する部分に、傾斜部が形成されていることが好ましい。なお、本実施形態では、第1ビア420のうち、第1配線440が延伸する方向と垂直の方向において、対向する側面の全体に、傾斜部が形成されている。

【0041】

ここで、上記した傾斜部は、第1ビア420の側面と第1ビア420の底面とのなす角が、第1配線440の側面と第1配線440の底面とのなす角よりも大きい。図1(b)で示されている傾斜部において、第1ビア420の側面と第1ビア420の底面とのなす角をθ1とし、一方、図1(c)のように、第1配線440の側面と第1配線440の底面とのなす角をθ2としたとき、θ1>θ2である。なお、第1ビア420の側面と底面とのなす角θ1は、後述する第1ビアホール430の側面と底面とのなす角θ1に相当する。また、第1配線440の側面と底面とのなす角θ2は、後述する第1配線溝450の側面と底面とのなす角θ2に相当する。ただし、それぞれの角度θ1およびθ2は、ライナー絶縁膜520の厚さ分だけ異なるが、角度に与える影響は微差である。これにより、後述する金属埋設工程において、第1配線溝450よりも第1ビアホール430における金属の埋め込み速度を早くすることができる。

【0042】

次に、図2を用いて、半導体装置10の平面視の構成を説明する。図2は、第1の実施形態に係る半導体装置の構成を示す平面図である。図2は、第1基板100の第1面側から見た平面図のうち、第1バンプ電極700を省略している。

【0043】

第1ビア420は、たとえば、平面視で円形状に設けられている。ここで、第1ビア420は、第1ビア420の他端が第2配線600等と接する箇所において、金属560が第2配線600等と電気的に接続するための底面を有するように形成されている。すなわち、第1ビア420が傾斜部によって先細となり、第2配線600等と接続する箇所で、ライナー絶縁膜520によって絶縁されている状態は不適である。したがって、第1基板100の第1面側における第1ビア420の直径は、当該第1ビア420の貫通する長さに応じて、最適な大きさが決定される。具体的には、第1ビア420の直径は、たとえば、1μm以上8μm以下である。

【0044】

また、第1ビア420は、一端が第1配線440と接続することなく、独立して形成されていてもよい。このような第1ビア420は、プリント配線基板(不図示)などに直接接続するために設けられている。

【0045】

第1配線440は、たとえば、大電流を流すための配線である。したがって、第1配線440は、半導体素子300などと接続するローカル配線660またはローカル配線680よりも、高さが高く、また幅も太く形成されている。具体的には、第1配線440の高さは、5μm以上50μm以下である。一方、第1配線440の幅は、第1ビア420の直径以上で、直径の4倍以下である。具体的には、1μm以上12μm以下である。これにより、第1配線440に、大電流を流すことができる。一方、第1配線440の幅が上位範囲を超える場合は、CMP工程でのディッシングが無視できなくなる。

【0046】

次に、図3を用いて、半導体素子300について説明する。図3は、図1(a)における半導体素子300を拡大した断面図である。なお、図3は、図1(a)と上下を反転させている。

【0047】

図3のように、半導体素子300は、たとえば、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)である。なお、半導体素子300は、抵抗、コンデンサ、インダクタ等であってもよい。以下では、半導体素子300は、MOSFETである場合を説明する。

【0048】

図3のように、第1基板100には、素子分離領域310が形成されている。素子分離領域310の開口部には、第1基板100の第2面の近傍に、不純物が注入されたソース領域322およびドレイン領域324が形成されている。

【0049】

ソース領域322およびドレイン領域324で挟まれたチャネル領域(不図示)上には、ゲート絶縁膜342が形成されている。また、ゲート絶縁膜342上には、ゲート電極344が形成されている。さらに、ゲート絶縁膜342およびゲート電極344の両脇には、側壁絶縁膜346が形成されている。

【0050】

また、ゲート電極344は、コンタクト620を介して、第2配線600と接続している。なお、図3では、ゲート電極344が第2配線600に接続する場合を例示したが、ソース領域322に接続されるソース電極(不図示)や、ドレイン領域324に接続されるドレイン電極(不図示)等が、コンタクト620と同様のコンタクト(不図示)、ローカル配線(不図示)、およびビア(不図示)を介して、第2配線600に接続されていてもよい。

【0051】

実際には、図1(a)で図示されていない領域に、図3と同様の半導体素子300が複数個形成されており、論理回路や記憶素子等の回路を形成している。

【0052】

次に、図4を用いて、第1ビア420の側面と第1ビア420の底面のなす角θ1、および第1配線440の側面と第1配線440の底面のなす角θ2の最適な範囲について説明する。図4は、ビアまたは配線における側面と底面のなす角と、金属の埋め込み速度の関係を示した図である。

【0053】

なお、図4において、第1ビア420や第1配線440に関わらず、第1基板100に形成された一般的なビアまたは配線溝の側面と底面とのなす角をθ(図1(b)におけるθ1、θ2に対応)とし、横軸を180−θ(図中単位「°」、以下文中では「度」と表記)としている。縦軸は、そのビアまたは配線溝に金属を埋設したときの埋め込み速度を示している。

【0054】

図4のように、金属の埋め込み速度は、180−θに対して単調減少となっている。言い換えれば、第1ビア420および第1配線440における側面と底面とのなす角θが大きくなるほど、金属の埋め込み速度が大きくなる。

【0055】

さらに、図4で示されているように、金属の埋め込み速度は、180−θが83度を境にして、二つの速度の異なる領域が存在する。一方を、金属の埋め込み速度が速いα領域とし、他方を、金属の埋め込み速度が遅いβ領域とする。α領域は、180−θが83度以下であり、β領域は、180−θが83度以上90度以下である。

【0056】

ここで、前述のように、第1ビア420は、当該第1ビア420の側面と当該第1ビア420の底面とのなす角θ1が、第1配線440の側面と第1配線440の底面とのなす角θ2より大きい傾斜部を有している。これにより、後述する金属埋設工程において、第1配線溝450よりも第1ビアホール430における金属の埋め込み速度を早くすることができる。

【0057】

したがって、傾斜部における第1ビア420の側面と第1ビア420の底面のなす角θ1はα領域であり、第1配線440の側面と第1配線440の底面のなす角θ2はβ領域であることが好ましい。この場合、第1ビア420での埋め込み速度を第1配線440での埋め込み速度よりも大きくすることができるため、第1ビア420での埋設時間と第1配線440での埋設時間を近づけることができる。これにより、第1配線440が第1ビア420よりも早く埋設されて、第1ビア420の上と比較して、第1配線440の上面が膨らんでしまうことを防ぐことができる。

【0058】

すなわち、180−θ1が、75度以上83度以下であり、180−θ2が、85度以上90度以下である。より好ましくは、180−θ1が、79度以上83度以下であり、180−θ2が、85度以上87度以下であることが好ましい。

【0059】

言い換えると、傾斜部は、第1ビア420の側面と第1ビア420の底面のなす角θ1が97度以上105度以下であり、第1配線440の側面と第1配線440の底面のなす角θ2は90度以上95度以下である。より好ましくは、傾斜部は、第1ビア420の側面と第1ビア420の底面のなす角θ1が97度以上101度以下であり、第1配線440の側面と第1配線440の底面のなす角θ2は93度以上95度以下である。

【0060】

θ1、θ2が上記範囲であることにより、第1配線溝450における金属の埋め込み速度を遅くし、第1ビアホール430における金属の埋め込み速度を早くすることができる。なお、θ1を105度以下としたのは、平面視での傾斜部の占める範囲が広くなり、結果的に第1ビア420における底面の面積が小さくなってしまうからである。一方、θ2を90度以上としたのは、逆テーパーとなると極端に金属の埋め込み速度が落ちるだけでなく、ボイドを発生させてしまう可能性があるためである。

【0061】

次に、図5を用い、ライナー絶縁膜520について説明する。図5は、図1(b)におけるビアを拡大した断面図である。

【0062】

図5のように、第1基板100とバリアメタル層540との間には、ライナー絶縁膜520が設けられている。このライナー絶縁膜520のうち、第1ビア420の一端側の膜厚をa(nm)とし、第1ビア420の他端側の膜厚をb(nm)としたとき、

b−a≧7

である。

【0063】

なお、ここでいう「第1ビア420の一端側」とは、第1ビア420が第1配線440と接続しておらず、独立している場合は、第1ビア420が第1基板100の上面と同一面を形成している部分のことをいう。一方、第1ビア420が第1配線440と接続している場合は、第1ビア420が第1配線440と接している部分のことをいう。

【0064】

また、ここでいう「第1ビア420の他端側」とは、第1ビア420が第2配線600等と接続している場合において、第1ビア420が第2配線600と接している部分のことをいう。

【0065】

ここで、第1ビア420の他端側(底面側)のライナー絶縁膜520は、ピンホールができやすい。ピンホールが発生すると、第1ビア420が第1基板100と短絡して絶縁不良を起こしてしまう。また、第1ビア420の金属560がマイグレーションするなどの絶縁不良も発生する可能性がある。このため、ライナー絶縁膜520を上記膜厚構成にすることにより、第1ビア420の他端側にピンホールのない緻密なライナー絶縁膜520を形成する。これにより、上記のような絶縁不良を抑制することができる。

【0066】

なお、第1基板100と、第1層間絶縁膜200との境界で、第1ビア420の側面の角度が変化していてもよい。第1基板100側における第1ビア420の側面と第1ビア420との底面のなす角θ1と、第1層間絶縁膜200側における第1ビア420の側面と第1ビア420との底面のなす角θ1とが、上記したように97度以上105度以下の範囲であればよい。後述するビアホール(422)を形成するためのエッチング工程において、第1基板100と、第1層間絶縁膜200とでエッチングレートが異なる可能性がある。このため、第1基板100と、第1層間絶縁膜200との境界で、θ1が変化していても、上記範囲内であることにより、本実施形態の効果を得ることができる。

【0067】

次に、図6から図10を用い、第1の実施形態に係る半導体装置の製造方法について説明する。第1の実施形態に係る半導体装置の製造方法は、下記のような工程を備えている。まず、第1基板100の第1面から、当該第1基板100を貫通する第1ビアホール430を形成するとともに、少なくとも一つ以上の第1ビアホール430の一端と接続する第1配線溝450を形成する(以降、エッチング工程)。次いで、第1ビアホール430および第1配線溝450に金属560を埋め込むことにより、第1ビア420および第1配線440を形成する(以降、金属埋設工程)。ここで、エッチング工程において、第1ビアホール430に、側面と底面とのなす角θ1が、第1配線溝450の側面と第1配線溝450の底面とのなす角θ2より大きい傾斜部を形成する。以下、詳細を説明する。

【0068】

まず、図6(a)のように、第2面側に、半導体素子300、ローカル配線660、およびローカル配線680等が形成された第1基板100を準備する。なお、以降の図では、ローカル配線660およびローカル配線680の符号を省略する。

【0069】

ここで、後述するエッチング工程の前に、第1基板100のうち、第1面と反対の第2面側に、第2配線600を形成する。図6(a)で示されているように、第2配線600を、第1層間絶縁膜200に埋設するように形成してもよい。

【0070】

次いで、第1基板100の第1面上に、レジスト膜800を成膜する。次いで、露光および現像により、レジスト膜800に、第1ビアホール430を形成するための開口を形成する。

【0071】

次いで、図6(b)のように、RIE(Reactive Ion Etching)により、第1基板100の第1面から、当該第1基板100を貫通する第1ビアホール430を形成する。このとき、第1基板100を貫通するとともに、第1層間絶縁膜200の一部をエッチングして、第1ビアホール430を形成する。このとき、エッチングとクリーニングを繰り返し行うことで、第1ビアホール430を形成する。具体的には、エッチングとクリーニングを、8回以上繰り返して行う。

【0072】

また、この段階では、第2配線600に到達しない範囲で、第1ビアホール430を形成する。これにより、レジスト膜800のアッシング工程において、第2配線600が酸化されることを抑制することができる。

【0073】

このエッチング工程において、第1ビアホール430として、側面と底面とのなす角θ1が、後述する第1配線溝450の側面と第1配線溝450の底面とのなす角θ2より大きい傾斜部の中間的な形状を形成する。なお、第1配線溝450までをエッチングした後において、上記した傾斜部の形状となっていればよい。すなわち、必ずしも、この段階で、上記した傾斜部を有している必要は無い。したがって、ここでは、後述するエッチング工程後の形状が所望の形状となるように、第1ビアホール430として、傾斜部の中間的な形状を形成しておく。

【0074】

次いで、レジスト膜800をアッシングにより除去する。

【0075】

次いで、図7(a)のように、第1ビアホール430の内部に、レジスト膜800を埋設する。ここで、実際には、図7(a)における第1基板100上にもレジスト膜800が形成されるため、エッチバックにより、レジスト膜800を平坦化する。なお、エッチバックを行わなくてもよい。

【0076】

次いで、図7(b)のように、第1基板100の第1面上に、レジスト膜800を成膜する。次いで、露光および現像により、第1基板100上のレジスト膜800に、第1配線溝450を形成するための開口を形成する。

【0077】

次いで、図8(a)のように、RIEにより、第1基板100をエッチングすることにより、第1配線溝450のうち、途中までエッチングされた中間的な溝(不図示)を形成する。次いで、レジスト膜800をアッシングにより除去する。次いで、全面エッチバックにより、第1ビアホール430を第2配線600と接するまでエッチングする。これにより、第1ビアホール430の他端を、第2配線600と接続する。また、同時に、第1配線溝450のうち、途中までエッチングされた中間的な溝(不図示)をさらにエッチングし、所望の第1配線溝450の深さまでエッチングする。

【0078】

ここで、図8(b)、図8(c)のように、このエッチング工程において、第1ビアホール430に、側面と底面とのなす角θ1が、後述する第1配線溝450の側面と第1配線溝450の底面とのなす角θ2より大きい傾斜部を形成する。

【0079】

図8(b)で示されているように、第1ビア420の側面と第1ビア420の底面のなす角θ1が、たとえば97度以上105度以下となるように、傾斜部を形成する。これにより、後述する金属埋設工程において、第1配線溝450よりも第1ビアホール430における金属560の埋め込み速度を早くすることができる。

【0080】

図8(c)で示されているように、第1配線溝450の側面と第1配線溝450の底面のなす角θ2がたとえば90度以上97度以下となるように、第1配線溝450を形成する。これにより、第1ビアホール430よりも第1配線溝450における金属560の埋め込み速度を遅くすることができる。

【0081】

以上のように、第1ビアホール430を形成した後、第1配線溝450を形成する(以上、エッチング工程)。ここで、第1配線溝450を先に形成した場合、第1ビアホール430をエッチングする際に、第1配線溝450の形状を上記した角度に保ちにくい。したがって、第1ビアホール430を先に形成することにより、上記した形状の第1ビアホール430および第1配線溝450を容易に形成することができる。

【0082】

次いで、図9(a)のように、第1ビアホール430および第1配線溝450の内側の側面および底面と、第1基板100上とに、ライナー絶縁膜520を形成する。ここでは、CVD(Chemical Vapor Deposition)、または第1基板100の熱酸化などにより、ライナー絶縁膜520を形成する。

【0083】

ここで、第1ビアホール430は、アスペクト比が大きいため、ライナー絶縁膜520は、第1ビアホール430の一端側が厚く、他端側が薄く形成される傾向にある。本実施形態では、上述したように、第1ビアホール430に、側面と底面とのなす角θ1が、第1配線溝450の側面と第1配線溝450の底面とのなす角θ2より大きい傾斜部を形成する。これにより、第1ビアホール430の他端側の側壁に対しても、ライナー絶縁膜520を厚く成膜することができる。

【0084】

次いで、エッチバックにより、第1ビアホール430の底面、すなわち、第1ビアホール430が第2配線600と接している部分のライナー絶縁膜520を除去する。これにより、第1ビアホール430内に、第2配線600を露出させる。

【0085】

ここで、図5で示したように、このライナー絶縁膜520のうち、第1ビア420の一端側の膜厚をa(nm)とし、第1ビア420の他端側の膜厚をb(nm)としたとき、

b−a≧7

となるように、ライナー絶縁膜520を形成する。

【0086】

次いで、図9(b)のように、第1ビアホール430の底面と、ライナー絶縁膜520で覆われた第1ビアホール430の側面および第1配線溝450の側面ならびに底面と、第1基板100上とに、スパッタにより、バリアメタル層540を形成する。

【0087】

次いで、図10(a)のように、めっき法により、第1ビアホール430および第1配線溝450内に、金属560を埋め込む。このとき、めっき条件は、温度が20℃以上30℃以下であり、電流値は3A以上20A以下であることが好ましい。これにより、図4に示した埋め込み速度を再現することができる。

【0088】

ここで、上記したように、第1ビアホール430および第1配線溝450の形状を調整することにより、第1ビアホール430への金属560の埋め込み速度を速くし、一方、第1配線溝450への金属560の埋め込み速度を遅くしている。したがって、めっき後の第1基板100の第1面は、第1ビアホール430の直上と第1配線溝450の直上とで凹凸に大きな差が無く、その後のCMP工程に悪影響を与えることがない。

【0089】

次いで、CMPにより、第1基板100の第1面側を平坦化する。以上により、第1ビア420および第1配線440を形成する(以上、金属埋設工程)。

【0090】

図10(b)のように、第1基板100の第1配線440上に、第1ビア420または第1配線440と接続する第1バンプ電極700を形成する。ここでは、第1バンプ電極700を、たとえば、第1ビア420の直上に形成する。

【0091】

以上のようにして、本実施形態に係る半導体装置10を得る。

【0092】

次に、第1の実施形態の効果について、説明する。

【0093】

本実施形態によれば、第1ビア420は、当該第1ビア420の側面と底面とのなす角θ1が、第1配線440の側面と底面とのなす角θ2より大きい傾斜部を有している。これにより、その後の金属埋設工程において、第1配線溝450よりも、第1ビアホール430における金属560の埋め込み速度を速くすることができる。すなわち、第1ビア420での埋設時間と第1配線440での埋設時間を近づけることができる。したがって、金属560が埋設された後の第1基板100の第1面を平坦にすることができ、さらにCMPにおいて均一に平坦化することができる。

【0094】

したがって、本実施形態によれば、大電流を流す第1ビア420および第1配線440を有し、且つ、当該第1ビア420および第1配線440が形成された第1面が平坦な半導体装置10を提供することができる。

【0095】

(第2の実施形態)

図11は、第2の実施形態に係る半導体装置10の構成を示す断面図である。第2の実施形態は、第1基板100の第2面に、第2配線600と接続する第1バンプ電極700を備えている点を除いて、第1の実施形態と同様である。以下、詳細を説明する。

【0096】

図11のように、第1基板100の第2面側には、第2配線600上に、電極パッド640が形成されている。電極パッド640としては、たとえば、Alである。

【0097】

また、電極パッド640の外周表面には、保護膜(不図示)、ポリイミド膜(不図示)などが形成されている。ここでは、いずれも第1層間絶縁膜200の一部として図示している。

【0098】

さらに、電極パッド640上には、第1バンプ電極700が形成されている。この第2面側の第1バンプ電極700は、第1面側の第1バンプ電極700と同一の材料を用いることができる。ただし、第2面側の第1バンプ電極700は、第1面側の第1バンプ電極700と実装時の温度が異なる材料で形成されていてもよい。また。第2面側の第1バンプ電極700は、ボンディングワイヤであってもよい。

【0099】

第2の実施形態によれば、第1基板の第1面と反対の第2面に、第2配線600と接続する第1バンプ電極700が形成されている。これにより、第1基板100の第1面および第2面の両側から外部接続することができる。たとえば、両側に、プリント配線基板などを実装することができる。

【0100】

(第3の実施形態)

図12は、第3の実施形態に係る半導体装置10の構成を示す断面図である。第3の実施形態は、以下の点を除いて、第1の実施形態と同様である。第1基板100の第1面と反対の第2面側には、第1基板100側の面に第3配線602を備える第2基板102が接合されている。また、第2配線600は、バンプ720(たとえば、マイクロバンプなど)を介して、第3配線602と接続している。以下、詳細を説明する。

【0101】

図12のように、第1基板100の第2面側には、第1層間絶縁膜200上に、接合層900が形成されている。接合層900のとしては、熱硬化性樹脂が用いられる。熱硬化性樹脂としては、たとえば、エポキシ樹脂やノンコンダクタフィルムなどである。また、接合層900を形成する方法としては、第1基板100と第2基板102を合わせてから熱酸化を行う方法、または第1基板100と第2基板102の表面をArビームで活性化して接続する方法なども用いられる。

【0102】

また、接合層900を介して、第1基板100の第2面側に、第2基板102が接合されている。このとき、第2基板102は、後述する第3配線602が形成された面に、第1基板100が接合されている。

【0103】

この第2基板102には、第1基板100と同様に、半導体素子300等が形成されている。また、第2基板102上には、第2層間絶縁膜202が形成されている。さらに、第2層間絶縁膜202の最上層には、第3配線602が形成されている。

【0104】

ここで、第1基板100には、第1の実施形態と同様に、第1基板100を貫通するように、第1ビア420が形成されている。この第1ビア420の他端は、第1ビア420の他端は、第2配線600と接続している。

【0105】

また、第2配線600の第2基板102側には、たとえば、第2基板102の第3配線602と接続するためのビア(符号不図示)が形成されている。一方、第2層間絶縁膜202のうち、第3配線602の第1基板100側には、たとえば、第1基板100の第2配線600と接続するためのビア(符号不図示)が形成されている。

【0106】

また、第2配線600は、バンプ720を介して、第2基板102のうち、第1基板100側の面に形成された第3配線602と接続している。これにより、第1基板100の第1面側から、第2基板102における第3配線602等に電流を供給することができる。

【0107】

バンプ720は、接合層900内に設けられている。ここでいう「バンプ720」とは、たとえば、マイクロバンプなどをいう。バンプ720の材料としては、たとえば、第1バンプ電極700等と同じ材料を用いることができる。また、バンプ720は、微細な第2配線600および第3配線602を接続するため、第1バンプ電極700等よりも小さいことが好ましい。

【0108】

なお、第2配線600の第2基板102側、および第3配線602の第1基板100側に、双方の配線を接続するためのビアが設けられている場合を説明したが、第2配線600および第3配線602が、直接、バンプ720を介して、相互に接続していてもよい。

【0109】

なお、第1の実施形態と同様に、第1ビア420は、当該第1ビア420の側面と当該第1ビア420の底面とのなす角θ1が、第1配線440の側面と第1配線440の底面とのなす角θ2より大きい傾斜部を有している。

【0110】

ここで、第3配線602は、たとえば、第2基板102に設けられた半導体素子300等に電流を供給する電源配線、またはグランド配線である。前述のように、この第3配線602は、バンプ720および第2配線600を介して、第1ビア420と接続されていることにより、第1ビア420から大電流の供給を受けることができる。

【0111】

このように、第1ビア420は、第1基板100と第2基板102の両者に対して、大電流を供給することができる。

【0112】

また、第1基板100は、たとえば、論理回路を備えている。一方、第2基板102は、たとえば、論理回路から伝達された信号を記憶する記憶素子を備えている。これにより、記憶装置を形成するために必要な素子または回路を有する各種基板を、省スペースに積層することができる。

【0113】

次に、第3の実施形態に係る半導体装置10の製造方法について説明する。第1の実施形態の製造方法に加え、第1基板100側の第1面に第3配線602を備える第2基板102を準備する。また、第1基板100の第1面と反対の第2面側に、第2基板102を接合する(接合工程)。この接合工程において、第2配線600を、バンプを介して、第3配線602と接続する。以下、第1の実施形態と同様の部分は省略しながら、詳細を説明する。

【0114】

まず、第1の実施形態と同様にして、第1基板100に、図10(b)で示されている状態の半導体装置10の中間体を形成する。

【0115】

次いで、第1層間絶縁膜200のうち、第2配線600上に、たとえば、一端が第2配線600と接続するビア(符号不図示)を形成する。なお、当該ビアを、第2基板102の第3配線と接続するように配置する。

【0116】

次いで、第1基板100側の第1面に第3配線602を備える第2基板102を準備する。そのほか、たとえば、第1基板100には、半導体素子300が形成されている。また、第3配線602は、第2層間絶縁膜202に埋設されていてもよい。

【0117】

次いで、第2層間絶縁膜202のうち、第3配線602上に、たとえば、一端が第3配線602と接続するビア(符号不図示)を形成する。なお、当該ビアを、第1基板100の第2配線600と接続するように配置する。

【0118】

次いで、接合層900を介して、第1基板100の第1面と反対の第2面側に、第2基板102を接合する(接合工程)。この接合工程において、第2配線600を、バンプを介して、第3配線602と接続する。

【0119】

以上のようにして、第3の実施形態に係る半導体装置10を得る。

【0120】

第3の実施形態によれば、第1基板100の第1面と反対の第2面側には、第2基板102が接合されている。これにより、省スペースに複数の基板を積層することができる。

【0121】

(第4の実施形態)

図13は、第4の実施形態に係る半導体装置10の構成を示す断面図である。第4の実施形態は、以下の点を除いて、第1の実施形態、または第3の実施形態と同様である。第1基板100の第1面と反対の第2面側に、第2基板102が接合されている。第2基板102は、第1基板100側の第1面から、当該第2基板102を貫通するとともに、一端が第1基板100側の第1面と同一面を形成する第2ビア422と、第1基板100と反対側に設けられ、第2ビア422の他端と接続する第3配線602と、を備えている。また、第2配線600は、バンプ720(たとえば、マイクロバンプなど)を介して、第2ビア422の一端と接続している。以下、詳細を説明する。

【0122】

図13のように、第1基板100の第2面側には、第1層間絶縁膜200上に、接合層900が形成されている。

【0123】

また、接合層900を介して、第1基板100の第2面側に、第2基板102が接合されている。このとき、第4の実施形態では、第3の実施形態と異なり、第2基板102は、第3配線602が形成されている面と反対側に、第1基板100が接合されている。

【0124】

また、この第2基板102のうち、第1基板100側の第1面から、第2ビア422が、当該第2基板102を貫通している。また、第2ビア422の一端は、第1基板100側の第1面と同一面を形成している。

【0125】

さらに、第2基板102には、第1基板100と反対側に、第3配線602が設けられている。第3配線602は、第2ビア422の他端と接続している。

【0126】

また、第1基板100の第2面側に設けられた第2配線600は、バンプ720を介して、第2ビア422の一端と接続している。なお、ここでは、第3の実施形態と同様にして、たとえば、第2配線600の第2基板側に、ビア(符号不図示)が設けられている。したがって、第2配線600は、このビア、およびバンプ720を介して、第2ビア422の一端と接続している。これにより、第1基板100の第1面側から、第2基板102における第3配線602等に電流を供給することができる。なお、上記ビアを介さずに、第2配線600および第2ビア422の一端が、直接、バンプ720を介して、相互に接続していてもよい。

【0127】

バンプ720は、接合層900内に設けられている。バンプ720は、第3の実施形態と同様のものを用いることができる。

【0128】

また、第3配線602上には、たとえば、電極パッド640が形成されている。また、電極パッド640の外周表面には、たとえば、保護膜(不図示)、ポリイミド膜(不図示)などが形成されている。

【0129】

さらに、第2基板102には、第1基板100と反対側の面に設けられ、第3配線602と接続する第2バンプ電極702が設けられていてもよい。これにより、第2基板102のうち、第1基板100と反対側の面からも、プリント配線基板などに外部接続することができる。

【0130】

次に、第4の実施形態に係る半導体装置10の製造方法について説明する。第4の実施形態に係る半導体装置10の製造方法は、以下の点を除いて、第1の実施形態、または第3の実施形態と同様である。第1の実施形態の製造方法に加え、第2基板102を準備する。また、第1基板100の第1面と反対の第2面側に、第2基板102を接合する(接合工程)。この接合工程において、第2配線600を、バンプを介して、第2ビア422の一端と接続する。以下、第3の実施形態と同様の部分は省略しながら、詳細を説明する。

【0131】

まず、第3の実施形態と同様にして、第1基板100に、図10(b)で示されている状態の半導体装置10の中間体を形成する。さらに、第1層間絶縁膜200のうち、第2配線600上に、たとえば、一端が第2配線600と接続するビア(符号不図示)を形成する。

【0132】

次いで、下記のような第2基板102を準備する。第2基板102のうち、第1基板100側の第1面から、第2基板102を貫通するとともに、一端が第1基板100側の第1面と同一面を形成する第2ビア422と、第1基板100と反対側に設けられ、第2ビア422の他端と接続する第3配線602と、を備えている。

【0133】

また、あらかじめ、第2ビア422が、第2配線600と接続するように、配置されている。すなわち、第2ビア422は、平面視で、第2配線600と重なるように配置されている。そのほかの構成は、第3の実施形態における第2基板102と同様である。

【0134】

なお、第2基板102を準備する工程は、第1の実施形態において、第1配線440を形成しない点を除いて、同様である。したがって、第1ビア420の側面と第1ビア420の底面(ここでは、第3配線602と接する面)とのなす角θ1が97度以上105度以下であってもよい。

【0135】

次いで、接合層900を介して、第1基板100の第1面と反対の第2面側に、第2基板102を接合する(接合工程)。この接合工程において、第2配線600を、バンプを介して、第2ビア422の一端と接続する。

【0136】

次いで、第2基板102のうち、第1基板100と反対側の面に、第3配線602と接続する第2バンプ電極702を形成してもよい。

【0137】

以上のようにして、第4の実施形態に係る半導体装置10を得る。

【0138】

第4の実施形態によれば、第3の実施形態と同様の効果を得ることができる。

【0139】

(第5の実施形態)

図14は、第5の実施形態に係る半導体装置10の構成を示す断面図である。第5の実施形態は、以下の点を除いて、第3、第4の実施形態と同様である。第1基板100と第2基板102との間には、少なくとも一つ以上の第3基板104が接合されている。第3基板104は、当該第3基板104の第1面から、当該第3基板104を貫通するとともに、一端が第3基板104の第1面と同一面を形成する第3ビア424と、第3基板104の第1面と反対の第2面上に設けられ、第3ビア424の他端と接続する第4配線604と、を備えている。また、第3ビア424の一端、または第4配線604は、それぞれ、バンプ720を介して、第1基板100の第2配線600、または第2基板102の第2ビア422の一端と接続している。以下、詳細を説明する。

【0140】

図14のように、上下の第1基板100および第2基板102の構成は、第4の実施形態と同様である。

【0141】

第1基板100と第2基板102との間には、少なくとも一つ以上の第3基板104を備えている。第3基板104は、第1基板100および第2基板102のそれぞれとの接合面において、接合層900を介して接合されている。なお、第3基板104は、一つだけでなく、複数であってもよい。

【0142】

また、第3基板104は、第1基板100または第2基板102と同様の基板を用いることができる。ここでは、第3基板104には、半導体素子300、第3層間絶縁膜204および第4配線604が形成されている。

【0143】

また、第3基板104のうち、当該第3基板104の第1面から、第3ビア424が、当該第3基板104を貫通している。また、第3ビア424の一端は、第3基板104の第1面と同一面を形成している。

【0144】

さらに、第3基板104には、第1面と反対の第2面上に、第4配線604が設けられている。第4配線604は、第3ビア424の他端と接続している。なお、ここでは、たとえば、第4配線604の第2基板側に、ビア(符号不図示)が設けられている。

【0145】

また、第3ビア424の一端、または第4配線604は、それぞれ、バンプ720を介して、第1基板100の第2配線600、または第2基板102の第2ビア422の一端と接続している。これにより、第1基板100および第2基板102だけでなく、少なくとも一つ以上の第3基板104に対しても大電流を供給することができる。

【0146】

なお、図14では、たとえば、第3ビア424の一端が第1基板100の第2配線600と接続している。また、第4配線604は、第2基板102の第2ビア422の一端と接続している。一方、第3基板104は、上記とは逆に接合されていてもよい。

【0147】

また、その他の変形例として、第3の実施形態のように、第2基板102は、第1基板100側の第1面に第3配線602が配置されていても良い。したがって、第3ビア424の一端、または第4配線604は、それぞれ、バンプ720を介して、第1基板100の第2配線600、または第2基板102の第3配線602と接続していてもよい。

【0148】

また、第1基板100は、たとえば、論理回路を備えている。一方、第2基板102および第3基板104は、たとえば、論理回路から伝達された信号を記憶する記憶素子を備えている。これにより、第3の実施形態と同様にして、記憶装置を形成するために必要な素子または回路を有する各種基板を、省スペースに積層することができる。

【0149】

次に、第5の実施形態に係る半導体装置10の製造方法について説明する。第5の実施形態に係る半導体装置10の製造方法は、以下の点を除いて、第3の実施形態、または第4の実施形態と同様である。第5の実施形態に係る半導体装置10の製造方法は、さらに以下の工程を備えている。第2基板102と、少なくとも一つ以上の第3基板104と、を準備する。また、第1基板100の第1面と反対の第2面側に、第3基板104と、第2基板102と、を順に接合する(接合工程)。この接合工程において、第3ビア424の一端、または第4配線604を、それぞれ、バンプを介して、第1基板100の第2配線600、または第2基板102の第2ビア422の一端と接続する。以下、第3、第4の実施形態と同様の部分は省略しながら、詳細を説明する。

【0150】

まず、第4の実施形態と同様にして、第1基板100および第2基板102を準備する。

【0151】

次いで、下記のような第3基板104を準備する。第3基板104のうち、当該第3基板104の第1面から、当該第3基板104を貫通するとともに、一端が第3基板104の第1面と同一面を形成する第3ビア424と、第3基板104の第1面と反対の第2面に設けられ、第3ビア424の他端と接続する第4配線604と、を備えている。

【0152】

また、あらかじめ、第3ビア424が、第2配線600と接続するように、配置されている。そのほかの構成は、第3の実施形態における第2基板102と同様である。

【0153】

なお、第3基板104を準備する工程は、第1の実施形態において、第1配線440を形成しない点を除いて、同様である。

【0154】

次いで、第1基板100の第1面と反対の第2面側に、第3基板104と、第2基板102と、を順に接合する(接合工程)。この接合工程において、第3ビア424の一端、または第4配線604を、それぞれ、バンプを介して、第1基板100の第2配線600、または第2基板102の第2ビア422の一端と接続する。

【0155】

上述のように、この第3基板104を接合する際には、図14で示されている構成に限らず、上下逆の構成でもよい。また、複数の第3基板104を接合する際についても、それぞれの第3基板104は、任意の接合面と接合することができる。

【0156】

また、その他の変形例として、第3の実施形態のように、第2基板102を、第1基板100側の第1面に第3配線602が配置されるように接合してもよい。

【0157】

以降の工程は、第4の実施形態と同様である。

【0158】

第5の実施形態によれば、第3、第4の実施形態と同様の効果を得ることができる。さらに、第5の実施形態によれば、3以上の基板を省スペースに接合することができ、複合的な機能を有する半導体装置10を提供することができる。

【0159】

(第6の実施形態)

図15は、第6の実施形態に係る半導体装置10の構成を示す断面図である。第6の実施形態は、第1基板100上に設けられた第1層間絶縁膜220側から、第1層間ビア460および第1配線440が形成されている点を除いて、第1の実施形態と同様である。以下、詳細を説明する。

【0160】

図15のように、第1基板100の第1面には、第1の実施形態と同様に、半導体素子300、第1層間絶縁膜200および第2配線600が形成されている。なお、第6の実施形態における「第1基板100の第1面」とは、半導体素子300、第1層間絶縁膜200等が形成された面のことをいう。

【0161】

さらに、第1層間絶縁膜200上には、さらに第1層間絶縁膜220が形成されている。この第1層間絶縁膜220は、第1層間絶縁膜200と同一の材料を用いることができる。なお、第1層間絶縁膜220は、第1層間絶縁膜200と異なる材料であってもよい。

【0162】

また、第1層間ビア460は、第1層間絶縁膜220を貫通するように形成されている。さらに、第1層間ビア460は、第1層間絶縁膜220とともに、第1層間絶縁膜200の一部を貫通している。第1層間ビア460の他端は、第2配線600と接続している。

【0163】

また、第1配線440は、第1層間絶縁膜220の表面に埋設されている。さらに、第1配線440は、少なくとも一つ以上の第1層間ビア460の一端と接続している。

【0164】

また、上述の第1層間絶縁膜220中に埋設された第2配線600は、第1層間ビア460の他端と接続している。

【0165】

また、第1層間ビア460は、当該第1層間ビア460の側面と当該第1層間ビア460の底面とのなす角θ1が、第1配線440の側面と第1配線440の底面とのなす角θ2より大きい傾斜部を有している。

【0166】

次に、第6の実施形態に係る半導体装置10の製造方法について説明する。第6の実施形態に係る半導体装置10の製造方法は、第1基板100上に設けられた第1層間絶縁膜220側から、第1層間ビア460および第1配線440を形成する点を除いて、第1の実施形態と同様である。以下、第1の実施形態と同様の部分は省略しながら、詳細を説明する。

【0167】

まず、半導体素子300、第1層間絶縁膜200および第2配線600が形成された第1基板100を準備する。次いで、第1層間絶縁膜200上に、第1層間絶縁膜220を形成する。

【0168】

次いで、第1層間絶縁膜220を貫通する第1層間ビアホールを形成するとともに、少なくとも一つ以上の第1層間ビアホールの一端と接続する第1配線溝450を形成する(エッチング工程)。なお、第1層間ビアホールとは、第1の実施形態における第1ビアホール430と同様である。

【0169】

ここで、このエッチング工程において、第1層間ビアホールに、側面と底面とのなす角θ1が、第1配線溝450の側面と第1配線溝450の底面とのなす角θ2より大きい傾斜部を形成する。

【0170】

次いで、第1層間ビアホールおよび第1配線溝450に金属560を埋め込むことにより、第1層間ビア460および第1配線440を形成する(金属埋設工程)。

【0171】

以降の工程は、第1の実施形態と同様である。

【0172】

第6の実施形態によれば、第1の実施形態のように、第1面が第1基板100の基板面でなくとも、第1ビア420と同様に第1層間ビア460および第1配線440を形成することができる。これにより、第1の実施形態と同様の効果を得ることができる。

【0173】

(第7の実施形態)

図16は、第7の実施形態に係る半導体装置10の構成を示す断面図である。第7の実施形態は、以下の点を除いて、第3の実施形態、または第6の実施形態と同様である。第1基板100の第1面と反対の第2面から、第1基板100を貫通し、一端が第2配線600と接続するとともに、他端が第2面と同一面を形成する第1基板ビア420を備えている。以下、詳細を説明する。

【0174】

図16のように、第1基板100の第1面と反対の第2面から、第1基板ビア420が貫通している。第1基板ビア420の一端は、第2配線600の下面と接続している。さらに、第1基板ビア420の他端は、第1基板100の第2面(裏面のこと)と同一面を形成している。

【0175】

なお、第1基板ビア420は、第2基板102の第3配線602と接続するように配置されている。すなわち、第1基板ビア420は、平面視で、第3配線602と重なるように配置されている。

【0176】

また、接合層900を介して、第1基板100と、第2基板102のうち、第3配線602が形成された面と、が接合されている。

【0177】

また、第1基板ビア420の他端は、バンプ720を介して、第2基板102の第3配線602と接続している。

【0178】

次に、第7の実施形態に係る半導体装置10の製造方法について説明する。第7の実施形態に係る半導体装置10の製造方法は、以下の点を除いて、第3の実施形態、または第6の実施形態と同様である。

【0179】

まず、第6の実施形態と同様にして、図15で示されている状態の半導体装置10の中間体を準備する。

【0180】

次いで、第1面と反対の第2面から、第1基板100を貫通し、一端が第2配線600と接続するとともに、第2面側の他端が当該第2面と同一面を形成するように、第1基板ビア420を形成する。

【0181】

なお、上記した第1基板ビア420を形成する工程は、第1層間ビア460を形成する工程の前に行ってもよい。

【0182】

他の工程は、第3の実施形態と同様である。

【0183】

第7の実施形態によれば、第3の実施形態と同様の効果を得ることができる。

【0184】

(第8の実施形態)

図17は、第8の実施形態に係る半導体装置10の構成を示す断面図である。第8の実施形態は、第1基板100が第7の実施形態と同様である点を除いて、第4の実施形態と同様である。以下、詳細を説明する。

【0185】

図17のように、接合層900を介して、第1基板100と、第2基板102のうち、第3配線602が形成されている面と反対側の面と、が接合されている。

【0186】

第7の実施形態と同様にして、第1基板100の第1面と反対の第2面から、第1基板ビア420が形成されている。

【0187】

一方で、第4の実施形態と同様にして、第2基板102の第1基板100側から、第2ビア422が形成されている。

【0188】

第1基板ビア420および第2ビア422は、互いに接続するように配置されている。すなわち、第1基板ビア420および第2ビア422は、平面視で重なるように配置されている。

【0189】

第1基板ビア420の他端は、バンプ720を介して、第2ビア422の一端と接続している。

【0190】

他の構成、および製造方法は、第4の実施形態と同様である。

【0191】

第8の実施形態によれば、第4の実施形態と同様の効果を得ることができる。

【0192】

(第9の実施形態)

図18は、第9の実施形態に係る半導体装置10の構成を示す断面図である。第9の実施形態は、第1基板100が第7の実施形態と同様である点を除いて、第5の実施形態と同様である。以下、詳細を説明する。

【0193】

図18のように、第1基板100と第2基板102との間に、少なくとも一つ以上の第3基板104を備えている。第3基板104は、第1基板100および第2基板102のそれぞれとの接合面において、接合層900を介して接合されている。なお、第3基板104は、一つだけでなく、複数であってもよい。

【0194】

第7の実施形態と同様にして、第1基板100の第1面と反対の第2面から、第1基板ビア420が形成されている。

【0195】

一方で、第5の実施形態と同様にして、第3基板104の第1基板100側から、第3ビア424が形成されている。また、第4の実施形態と同様にして、第2基板102の第1基板100側から、第2ビア422が形成されている。

【0196】

第1基板ビア420および第3ビア424は、互いに接続するように配置されている。すなわち、第1基板ビア420および第3ビア424は、平面視で重なるように配置されている。

【0197】

また、第3ビア424の一端、または第4配線604は、それぞれ、バンプ720を介して、第1基板ビア420の他端、または第2ビア422の一端と接続している。

【0198】

上述のように、この第3基板104を接合する際には、図18で示されている構成に限らず、上下逆の構成でもよい。また、複数の第3基板104を接合する際についても、それぞれの第3基板104は、任意の接合面と接合することができる。

【0199】

また、その他の変形例として、第7の実施形態のように、第2基板102を、第1基板100側の第1面に第3配線602が配置されるように接合してもよい。

【0200】

第9の実施形態によれば、第5の実施形態と同様の効果を得ることができる。

【0201】

なお、第3、第7の実施形態では、第2基板102の基板面には、第2バンプ電極702が形成されていない場合を説明したが、第1の実施形態のように、第2基板102の基板面側から第2ビア422または第1配線440が形成されていてもよい。このとき、第2ビア422の一端は、第3配線602と接続してもよい。さらに、当該第2ビア422または第1配線440の直上に、第2バンプ電極702が設けられていても良い。

【0202】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【符号の説明】

【0203】

10 半導体装置

100 第1基板

102 第2基板

104 第3基板

200 第1層間絶縁膜

202 第2層間絶縁膜

204 第3層間絶縁膜

220 第1層間絶縁膜

300 半導体素子

310 素子分離領域

322 ソース領域

324 ドレイン領域

342 ゲート絶縁膜

344 ゲート電極

346 側壁絶縁膜

420 第1ビア(第1基板ビア)

422 第2ビア

424 第3ビア

430 第1ビアホール

440 第1配線

450 第1配線溝

460 第1層間ビア

520 ライナー絶縁膜

540 バリアメタル層

560 金属

600 第2配線

602 第3配線

604 第4配線

620 コンタクト

640 電極パッド

660 ローカル配線

680 ローカル配線

700 第1バンプ電極

702 第2バンプ電極

720 バンプ

800 レジスト膜

900 接合層

【特許請求の範囲】

【請求項1】

第1基板と、

前記第1基板の第1面側から、当該第1基板を貫通する第1ビアと、

前記第1基板の前記第1面に埋設され、少なくとも一つ以上の前記第1ビアの一端と接続する第1配線と、

を備え、

前記第1ビアは、当該第1ビアの前記側面と当該第1ビアの底面とのなす角が、前記第1配線の側面と前記第1配線の底面とのなす角より大きい傾斜部を有する半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記第1基板は、前記第1面と反対の第2面上に第2配線を備え、

前記第1ビアの他端は、前記第2配線と接続する半導体装置。

【請求項3】

請求項2に記載の半導体装置において、

前記第1基板は、前記第2面上に設けられた第1層間絶縁膜を備え、

前記第2配線は、前記第1層間絶縁膜に埋設されており、

前記第1ビアは、前記第1基板を貫通するとともに、前記第1層間絶縁膜を貫通し、

前記第1ビアの他端は、前記第2配線と接続する半導体装置。

【請求項4】

請求項2または3に記載の半導体装置において、

前記第2配線は、電源配線またはグランド配線である半導体装置。

【請求項5】

請求項2〜4のいずれか一項に記載の半導体装置において、

前記第1基板は、前記第1面と反対の第2面に、前記第2配線と接続する第1バンプ電極を備える半導体装置。

【請求項6】

請求項2〜4のいずれか一項に記載の半導体装置において、

前記第1基板側の第1面に設けられた第3配線を備えるとともに、前記第1基板の前記第1面と反対の第2面側に接合された第2基板をさらに備え、

前記第2配線は、バンプを介して、前記第3配線と接続する半導体装置。

【請求項7】

請求項2〜4のいずれか一項に記載の半導体装置において、

前記第1基板の前記第1面と反対の第2面側に接合された第2基板と、

前記第1基板と前記第2基板との間に接合された、少なくとも一つ以上の第3基板と、

をさらに備え、

前記第2基板は、

前記第1基板側の第1面に設けられた第3配線を備え、

前記第3基板は、

当該第3基板の第1面から、当該第3基板を貫通するとともに、一端が前記第3基板の第1面と同一面を形成する第3ビアと、

前記第3基板の第1面と反対の第2面上に設けられ、前記第3ビアの他端と接続する第4配線と、

を備え、

前記第3ビアの前記一端、または前記第4配線は、それぞれ、バンプを介して、前記第1基板の前記第2配線、または前記第2基板の前記第3配線と接続する半導体装置。

【請求項8】

請求項2〜4のいずれか一項に記載の半導体装置において、

前記第1基板の前記第1面と反対の第2面側に接合された第2基板をさらに備え、

前記第2基板は、

前記第1基板側の第1面から、当該第2基板を貫通するとともに、一端が前記第1基板側の第1面と同一面を形成する第2ビアと、

前記第1基板と反対側に設けられ、前記第2ビアの他端と接続する第3配線と、

を備え、

前記第2配線は、バンプを介して、前記第2ビアの前記一端と接続する半導体装置。

【請求項9】

請求項2〜4のいずれか一項に記載の半導体装置において、

前記第1基板の前記第1面と反対の第2面側に接合された第2基板と、

前記第1基板と前記第2基板との間に接合された、少なくとも一つ以上の第3基板と、

をさらに備え、

前記第2基板は、

前記第1基板側の第1面から、当該第2基板を貫通するとともに、一端が前記第1基板側の第1面と同一面を形成する第2ビアと、

前記第1基板と反対側に設けられ、前記第2ビアの他端と接続する第3配線と、

を備え、

前記第3基板は、

当該第3基板の第1面から、当該第3基板を貫通するとともに、一端が前記第3基板の第1面と同一面を形成する第3ビアと、

前記第3基板の第1面と反対の第2面上に設けられ、前記第3ビアの他端と接続する第4配線と、

を備え、

前記第3ビアの前記一端、または前記第4配線は、それぞれ、バンプを介して、前記第1基板の前記第2配線、または前記第2基板の前記第2ビアの前記一端と接続する半導体装置。

【請求項10】

第1基板と、

前記第1基板の第1面上に設けられた第1層間絶縁膜と、

前記第1層間絶縁膜を貫通する第1層間ビアと、

前記第1層間絶縁膜の表面に埋設され、少なくとも一つ以上の前記第1層間ビアの一端と接続する第1配線と、

を備え、

前記第1層間ビアは、当該第1層間ビアの前記側面と当該第1層間ビアの底面とのなす角が、前記第1配線の側面と前記第1配線の底面とのなす角より大きい傾斜部を有する半導体装置。

【請求項11】

請求項10に記載の半導体装置において、

前記第1層間絶縁膜中に埋設され、前記第1層間ビアの他端と接続する第2配線をさらに備える半導体装置。

【請求項12】

請求項11に記載の半導体装置において、

前記第1面と反対の第2面から前記第1基板を貫通し、一端が前記第2配線と接続するとともに、他端が前記第2面と同一面を形成する第1基板ビアと、

をさらに備える半導体装置。

【請求項13】

請求項12に記載の半導体装置において、

前記第1基板側の第1面に設けられた第3配線を備えるとともに、前記第1基板の前記第1面と反対の第2面側に接合された第2基板をさらに備え、

前記第1基板ビアの前記他端は、バンプを介して、前記第3配線と接続する半導体装置。

【請求項14】

請求項12に記載の半導体装置において、

前記第1基板の前記第1面と反対の第2面側に接合された第2基板と、

前記第1基板と前記第2基板との間に、少なくとも一つ以上の第3基板と、

をさらに備え、

前記第2基板は、

前記第1基板側の第1面に設けられた第3配線を備え、

前記第3基板は、

当該第3基板の第1面から、当該第3基板を貫通するとともに、一端が前記第3基板の第1面と同一面を形成する第3ビアと、

前記第3基板の第1面と反対の第2面上に設けられ、前記第3ビアの他端と接続する第4配線と、

を備え、

前記第3ビアの前記一端、または前記第4配線は、それぞれ、バンプを介して、前記第1基板ビアの前記他端、または前記第2基板の前記第3配線と接続する半導体装置。

【請求項15】

請求項12に記載の半導体装置において、

前記第1基板の前記第1面と反対の第2面側に接合された第2基板をさらに備え、

当該第2基板は、

前記第1基板側の第1面から、当該第2基板を貫通するとともに、一端が前記第1基板側の第1面と同一面を形成する第2ビアと、

前記第1基板と反対側に設けられ、前記第2ビアの他端と接続する第3配線と、

を備え、

前記第1基板ビアの前記他端は、バンプを介して、前記第2ビアの前記一端と接続する半導体装置。

【請求項16】

請求項12に記載の半導体装置において、

前記第1基板の前記第1面と反対の第2面側に接合された第2基板と、

前記第1基板と前記第2基板との間に、少なくとも一つ以上の第3基板と、

をさらに備え、

前記第2基板は、

前記第1基板側の第1面から、当該第2基板を貫通するとともに、一端が前記第1基板側の第1面と同一面を形成する第2ビアと、

前記第1基板と反対側に設けられ、前記第2ビアの他端と接続する第3配線と、

を備え、

前記第3基板は、

前記第3基板の第1面から、当該第3基板を貫通するとともに、一端が前記第1面と同一面を形成する第3ビアと、

前記第1面と反対の第2面上に設けられ、前記第3ビアの他端と接続する第4配線と、

を備え、

前記第3ビアの前記一端、または前記第4配線は、それぞれ、バンプを介して、前記第1基板ビアの前記他端、または前記第2基板の前記第2ビアの前記一端と接続する半導体装置。

【請求項17】

請求項6〜9、13〜16のいずれか一項に記載の半導体装置において、

前記第3配線は、電源配線またはグランド配線である半導体装置。

【請求項18】

請求項6、8、13および15のいずれか一項に記載の半導体装置において、

前記第1基板は、論理回路を備え、

前記第2基板は、前記論理回路から伝達された信号を記憶する記憶素子を備える半導体装置。

【請求項19】

請求項7、9、14および16のいずれか一項に記載の半導体装置において、

前記第1基板は、論理回路を備え、

前記第2基板または前記第3基板は、前記論理回路から伝達された信号を記憶する記憶素子を備える半導体装置。

【請求項20】

請求項8、9、15および16のいずれか一項に記載の半導体装置において、

前記第2基板は、前記第1基板と反対側の面に設けられ、前記第3配線と接続する第2バンプ電極を備える半導体装置。

【請求項21】

請求項1〜20のいずれか一項に記載の半導体装置において、

前記第1基板は、前記第1面に、前記ビアまたは前記第1配線と接続する第1バンプ電極をさらに備える半導体装置。

【請求項22】

請求項1〜21のいずれか一項に記載の半導体装置において、

前記傾斜部は、前記ビアの側面と前記ビアの底面とのなす角が97度以上105度以下であり、

前記第1配線の側面と前記第1配線の底面とのなす角は、90度以上95度以下である半導体装置。

【請求項23】

請求項1〜22のいずれか一項に記載の半導体装置において、

前記ビアの内側の側面にライナー絶縁膜を備え、

前記ライナー絶縁膜のうち、前記ビアの前記一端側の膜厚をa(nm)とし、前記ビアの他端側の膜厚をb(nm)としたとき、

b−a≧7

である半導体装置。

【請求項24】

第1基板の第1面側から、当該第1基板を貫通する第1ビアホールを形成するとともに、少なくとも一つ以上の前記第1ビアホールの一端と接続する第1配線溝を形成するエッチング工程と、

前記第1ビアホールおよび前記第1配線溝に金属を埋め込むことにより、第1ビアおよび第1配線を形成する金属埋設工程と、

を備え、

前記エッチング工程において、前記第1ビアホールに、側面と底面とのなす角が、前記第1配線溝の側面と前記第1配線溝の底面とのなす角より大きい傾斜部を形成する半導体装置の製造方法。

【請求項25】

請求項24に記載の半導体装置の製造方法において、

前記エッチング工程の前に、前記第1基板のうち、前記第1面と反対の第2面側に、第2配線を形成する工程をさらに備え、

前記エッチング工程において、前記第1ビアホールの他端を前記第2配線と接続する半導体装置の製造方法。

【請求項26】

請求項25に記載の半導体装置の製造方法において、

前記第1基板側の第1面に第3配線を備える第2基板を準備する工程と、

前記第1基板の前記第1面と反対の第2面側に、前記第2基板を接合する接合工程と、

をさらに備え、

前記接合工程において、前記第2配線を、バンプを介して、前記第3配線と接続する半導体装置の製造方法。

【請求項27】

請求項25に記載の半導体装置の製造方法において、

第2基板と、少なくとも一つ以上の第3基板と、を準備する工程と、

前記第1基板の前記第1面と反対の第2面側に、前記第3基板と、前記第2基板と、を順に接合する接合工程と、

をさらに備え、

前記第2基板は、

前記第1基板側の第1面に設けられた第3配線を備え、

前記第3基板は、

当該第3基板の第1面から、当該第3基板を貫通するとともに、一端が前記第3基板の第1面と同一面を形成する第3ビアと、

前記第3基板の第1面と反対の第2面上に設けられ、前記第3ビアの他端と接続する第4配線と、

を備え、

前記接合工程において、前記第3ビアの前記一端、または前記第4配線を、それぞれ、バンプを介して、前記第1基板の前記第2配線、または前記第2基板の前記第3配線と接続する半導体装置の製造方法。

【請求項28】

請求項25に記載の半導体装置の製造方法において、

第2基板を準備する工程と、

前記第1基板の前記第1面と反対の第2面側に、前記第2基板を接合する接合工程と、

をさらに備え、

前記第2基板は、

前記第1基板側の第1面から、当該第2基板を貫通するとともに、一端が前記第1基板側の第1面と同一面を形成する第2ビアと、

前記第1基板と反対側に設けられ、前記第2ビアの他端と接続する第3配線と、

を備え、

前記接合工程において、前記第2配線を、バンプを介して、前記第2ビアの前記一端と接続する半導体装置の製造方法。

【請求項29】

請求項25に記載の半導体装置の製造方法において、

第2基板と、少なくとも一つ以上の第3基板と、を準備する工程と、

前記第1基板の前記第1面と反対の第2面側に、前記第3基板と、前記第2基板と、を順に接合する接合工程と、

をさらに備え、

前記第2基板は、

前記第1基板側の第1面から、当該第2基板を貫通するとともに、一端が前記第1基板側の第1面と同一面を形成する第2ビアと、

前記第1基板と反対側に設けられ、前記第2ビアの他端と接続する第3配線と、

を備え、

前記第3基板は、

当該第3基板の第1面から、当該第3基板を貫通するとともに、一端が前記第3基板の第1面と同一面を形成する第3ビアと、

前記第3基板の第1面と反対の第2面上に設けられ、前記第3ビアの他端と接続する第4配線と、

を備え、

前記接合工程において、前記第3ビアの前記一端、または前記第4配線を、それぞれ、バンプを介して、前記第1基板の前記第2配線、または前記第2基板の前記第2ビアの前記一端と接続する半導体装置の製造方法。

【請求項30】

第1基板の第1面上に第1層間絶縁膜を形成する工程と、

前記第1層間絶縁膜を貫通する第1層間ビアホールを形成するとともに、少なくとも一つ以上の前記第1層間ビアホールの一端と接続する第1配線溝を形成するエッチング工程と、

前記第1層間ビアホールおよび前記第1配線溝に金属を埋め込むことにより、第1層間ビアおよび第1配線を形成する金属埋設工程と、

を備え、

前記エッチング工程において、前記第1層間ビアホールに、側面と底面とのなす角が、前記第1配線溝の側面と前記第1配線溝の底面とのなす角より大きい傾斜部を形成する半導体装置の製造方法。

【請求項31】

請求項30に記載の半導体装置の製造方法において、

前記第1層間絶縁膜を形成する工程において、前記第1層間絶縁膜中に、第2配線を形成し、

前記エッチング工程において、前記第1層間ビアホールの他端を前記第2配線と接続する半導体装置の製造方法。

【請求項32】

請求項31に記載の半導体装置の製造方法において、

前記第1面と反対の第2面から前記第1基板を貫通し、一端が前記第2配線と接続するとともに、前記第2面側の他端が当該第2面と同一面を形成するように、第1基板ビアを形成する工程をさらに備える半導体装置の製造方法。

【請求項33】

請求項32に記載の半導体装置の製造方法において、

前記第1基板側の第1面に第3配線を備える第2基板を準備する工程と、

前記第1基板の前記第1面と反対の第2面側に、前記第2基板を接合する接合工程と、

をさらに備え、

前記接合工程において、前記第1基板ビアの前記他端を、バンプを介して、前記第3配線と接続する半導体装置の製造方法。

【請求項34】

請求項32に記載の半導体装置の製造方法において、

第2基板と、少なくとも一つ以上の第3基板と、を準備する工程と、

前記第1基板の前記第1面と反対の第2面側に、前記第3基板と、前記第2基板と、を順に接合する接合工程と、

をさらに備え、

前記第2基板は、

前記第1基板側の面に設けられた第3配線を備え、

前記第3基板は、

前記第3基板の第1面から、当該第3基板を貫通するとともに、一端が前記第3基板の第1面と同一面を形成する第3ビアと、

前記第3基板の第1面と反対の第2面上に設けられ、前記第3ビアの他端と接続する第4配線と、

を備え、

前記接合工程において、前記第3ビアの前記一端、または前記第4配線は、それぞれ、バンプを介して、前記第1基板ビアの前記他端、または前記第2基板の前記第3配線と接続する半導体装置の製造方法。

【請求項35】

請求項32に記載の半導体装置の製造方法において、

第2基板を準備する工程と、

前記第1基板の前記第1面と反対の第2面側に、前記第2基板を接合する接合工程と、

をさらに備え、

前記第2基板は、

前記第1基板側の第1面から、当該第2基板を貫通するとともに、一端が前記第1基板側の第1面と同一面を形成する第2ビアと、

前記第1基板と反対側に設けられ、前記第2ビアの他端と接続する第3配線と、

を備え、

前記接合工程において、前記第1基板ビアの前記他端は、バンプを介して、前記第2ビアの他端と接続する半導体装置の製造方法。

【請求項36】

請求項32に記載の半導体装置の製造方法において、

第2基板と、少なくとも一つ以上の第3基板と、を準備する工程と、

前記第1基板の前記第1面と反対の第2面側に、前記第3基板と、前記第2基板と、を順に接合する接合工程と、

をさらに備え、

前記第2基板は、

前記第1基板側の第1面から、当該第2基板を貫通するとともに、一端が前記第1基板側の第1面と同一面を形成する第2ビアと、

前記第1基板と反対側に設けられ、前記第2ビアの他端と接続する第3配線と、

を備え、

前記第3基板は、

前記第3基板の第1面から、当該第3基板を貫通するとともに、一端が前記第3基板の第1面と同一面を形成する第3ビアと、

前記第3基板の第1面と反対の第2面上に設けられ、前記第3ビアの他端と接続する第4配線と、

を備え、

前記接合工程において、前記第3ビアの前記一端、または前記第4配線は、それぞれ、バンプを介して、前記第1基板ビアの前記他端、または前記第2基板の前記第2ビアの前記一端と接続する半導体装置の製造方法。

【請求項1】

第1基板と、

前記第1基板の第1面側から、当該第1基板を貫通する第1ビアと、

前記第1基板の前記第1面に埋設され、少なくとも一つ以上の前記第1ビアの一端と接続する第1配線と、

を備え、

前記第1ビアは、当該第1ビアの前記側面と当該第1ビアの底面とのなす角が、前記第1配線の側面と前記第1配線の底面とのなす角より大きい傾斜部を有する半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記第1基板は、前記第1面と反対の第2面上に第2配線を備え、

前記第1ビアの他端は、前記第2配線と接続する半導体装置。

【請求項3】

請求項2に記載の半導体装置において、

前記第1基板は、前記第2面上に設けられた第1層間絶縁膜を備え、

前記第2配線は、前記第1層間絶縁膜に埋設されており、

前記第1ビアは、前記第1基板を貫通するとともに、前記第1層間絶縁膜を貫通し、

前記第1ビアの他端は、前記第2配線と接続する半導体装置。

【請求項4】

請求項2または3に記載の半導体装置において、

前記第2配線は、電源配線またはグランド配線である半導体装置。

【請求項5】

請求項2〜4のいずれか一項に記載の半導体装置において、

前記第1基板は、前記第1面と反対の第2面に、前記第2配線と接続する第1バンプ電極を備える半導体装置。

【請求項6】

請求項2〜4のいずれか一項に記載の半導体装置において、

前記第1基板側の第1面に設けられた第3配線を備えるとともに、前記第1基板の前記第1面と反対の第2面側に接合された第2基板をさらに備え、

前記第2配線は、バンプを介して、前記第3配線と接続する半導体装置。

【請求項7】

請求項2〜4のいずれか一項に記載の半導体装置において、

前記第1基板の前記第1面と反対の第2面側に接合された第2基板と、

前記第1基板と前記第2基板との間に接合された、少なくとも一つ以上の第3基板と、

をさらに備え、

前記第2基板は、

前記第1基板側の第1面に設けられた第3配線を備え、

前記第3基板は、

当該第3基板の第1面から、当該第3基板を貫通するとともに、一端が前記第3基板の第1面と同一面を形成する第3ビアと、

前記第3基板の第1面と反対の第2面上に設けられ、前記第3ビアの他端と接続する第4配線と、

を備え、

前記第3ビアの前記一端、または前記第4配線は、それぞれ、バンプを介して、前記第1基板の前記第2配線、または前記第2基板の前記第3配線と接続する半導体装置。

【請求項8】

請求項2〜4のいずれか一項に記載の半導体装置において、

前記第1基板の前記第1面と反対の第2面側に接合された第2基板をさらに備え、

前記第2基板は、

前記第1基板側の第1面から、当該第2基板を貫通するとともに、一端が前記第1基板側の第1面と同一面を形成する第2ビアと、

前記第1基板と反対側に設けられ、前記第2ビアの他端と接続する第3配線と、

を備え、

前記第2配線は、バンプを介して、前記第2ビアの前記一端と接続する半導体装置。

【請求項9】

請求項2〜4のいずれか一項に記載の半導体装置において、

前記第1基板の前記第1面と反対の第2面側に接合された第2基板と、

前記第1基板と前記第2基板との間に接合された、少なくとも一つ以上の第3基板と、

をさらに備え、

前記第2基板は、

前記第1基板側の第1面から、当該第2基板を貫通するとともに、一端が前記第1基板側の第1面と同一面を形成する第2ビアと、

前記第1基板と反対側に設けられ、前記第2ビアの他端と接続する第3配線と、

を備え、

前記第3基板は、

当該第3基板の第1面から、当該第3基板を貫通するとともに、一端が前記第3基板の第1面と同一面を形成する第3ビアと、

前記第3基板の第1面と反対の第2面上に設けられ、前記第3ビアの他端と接続する第4配線と、

を備え、

前記第3ビアの前記一端、または前記第4配線は、それぞれ、バンプを介して、前記第1基板の前記第2配線、または前記第2基板の前記第2ビアの前記一端と接続する半導体装置。

【請求項10】

第1基板と、

前記第1基板の第1面上に設けられた第1層間絶縁膜と、

前記第1層間絶縁膜を貫通する第1層間ビアと、

前記第1層間絶縁膜の表面に埋設され、少なくとも一つ以上の前記第1層間ビアの一端と接続する第1配線と、

を備え、

前記第1層間ビアは、当該第1層間ビアの前記側面と当該第1層間ビアの底面とのなす角が、前記第1配線の側面と前記第1配線の底面とのなす角より大きい傾斜部を有する半導体装置。

【請求項11】

請求項10に記載の半導体装置において、

前記第1層間絶縁膜中に埋設され、前記第1層間ビアの他端と接続する第2配線をさらに備える半導体装置。

【請求項12】

請求項11に記載の半導体装置において、

前記第1面と反対の第2面から前記第1基板を貫通し、一端が前記第2配線と接続するとともに、他端が前記第2面と同一面を形成する第1基板ビアと、

をさらに備える半導体装置。

【請求項13】

請求項12に記載の半導体装置において、

前記第1基板側の第1面に設けられた第3配線を備えるとともに、前記第1基板の前記第1面と反対の第2面側に接合された第2基板をさらに備え、

前記第1基板ビアの前記他端は、バンプを介して、前記第3配線と接続する半導体装置。

【請求項14】

請求項12に記載の半導体装置において、

前記第1基板の前記第1面と反対の第2面側に接合された第2基板と、

前記第1基板と前記第2基板との間に、少なくとも一つ以上の第3基板と、

をさらに備え、

前記第2基板は、

前記第1基板側の第1面に設けられた第3配線を備え、

前記第3基板は、

当該第3基板の第1面から、当該第3基板を貫通するとともに、一端が前記第3基板の第1面と同一面を形成する第3ビアと、

前記第3基板の第1面と反対の第2面上に設けられ、前記第3ビアの他端と接続する第4配線と、

を備え、

前記第3ビアの前記一端、または前記第4配線は、それぞれ、バンプを介して、前記第1基板ビアの前記他端、または前記第2基板の前記第3配線と接続する半導体装置。

【請求項15】

請求項12に記載の半導体装置において、

前記第1基板の前記第1面と反対の第2面側に接合された第2基板をさらに備え、

当該第2基板は、

前記第1基板側の第1面から、当該第2基板を貫通するとともに、一端が前記第1基板側の第1面と同一面を形成する第2ビアと、

前記第1基板と反対側に設けられ、前記第2ビアの他端と接続する第3配線と、

を備え、

前記第1基板ビアの前記他端は、バンプを介して、前記第2ビアの前記一端と接続する半導体装置。

【請求項16】

請求項12に記載の半導体装置において、

前記第1基板の前記第1面と反対の第2面側に接合された第2基板と、

前記第1基板と前記第2基板との間に、少なくとも一つ以上の第3基板と、

をさらに備え、

前記第2基板は、

前記第1基板側の第1面から、当該第2基板を貫通するとともに、一端が前記第1基板側の第1面と同一面を形成する第2ビアと、

前記第1基板と反対側に設けられ、前記第2ビアの他端と接続する第3配線と、

を備え、

前記第3基板は、

前記第3基板の第1面から、当該第3基板を貫通するとともに、一端が前記第1面と同一面を形成する第3ビアと、

前記第1面と反対の第2面上に設けられ、前記第3ビアの他端と接続する第4配線と、

を備え、

前記第3ビアの前記一端、または前記第4配線は、それぞれ、バンプを介して、前記第1基板ビアの前記他端、または前記第2基板の前記第2ビアの前記一端と接続する半導体装置。

【請求項17】

請求項6〜9、13〜16のいずれか一項に記載の半導体装置において、

前記第3配線は、電源配線またはグランド配線である半導体装置。

【請求項18】

請求項6、8、13および15のいずれか一項に記載の半導体装置において、

前記第1基板は、論理回路を備え、

前記第2基板は、前記論理回路から伝達された信号を記憶する記憶素子を備える半導体装置。

【請求項19】

請求項7、9、14および16のいずれか一項に記載の半導体装置において、

前記第1基板は、論理回路を備え、

前記第2基板または前記第3基板は、前記論理回路から伝達された信号を記憶する記憶素子を備える半導体装置。

【請求項20】

請求項8、9、15および16のいずれか一項に記載の半導体装置において、

前記第2基板は、前記第1基板と反対側の面に設けられ、前記第3配線と接続する第2バンプ電極を備える半導体装置。

【請求項21】

請求項1〜20のいずれか一項に記載の半導体装置において、

前記第1基板は、前記第1面に、前記ビアまたは前記第1配線と接続する第1バンプ電極をさらに備える半導体装置。

【請求項22】

請求項1〜21のいずれか一項に記載の半導体装置において、

前記傾斜部は、前記ビアの側面と前記ビアの底面とのなす角が97度以上105度以下であり、

前記第1配線の側面と前記第1配線の底面とのなす角は、90度以上95度以下である半導体装置。

【請求項23】

請求項1〜22のいずれか一項に記載の半導体装置において、

前記ビアの内側の側面にライナー絶縁膜を備え、

前記ライナー絶縁膜のうち、前記ビアの前記一端側の膜厚をa(nm)とし、前記ビアの他端側の膜厚をb(nm)としたとき、

b−a≧7

である半導体装置。

【請求項24】

第1基板の第1面側から、当該第1基板を貫通する第1ビアホールを形成するとともに、少なくとも一つ以上の前記第1ビアホールの一端と接続する第1配線溝を形成するエッチング工程と、

前記第1ビアホールおよび前記第1配線溝に金属を埋め込むことにより、第1ビアおよび第1配線を形成する金属埋設工程と、

を備え、