半導体装置及び半導体装置の製造方法

【課題】半導体層を用いた素子を配線層間に形成し、かつ、ゲート電極の材料を、配線の材料以外の導電体にする。

【解決手段】第1配線層150の表層には、第1配線210が埋め込まれている。第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。そしてゲート電極218上には、ゲート絶縁膜219及び半導体層220が形成されている。

【解決手段】第1配線層150の表層には、第1配線210が埋め込まれている。第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。そしてゲート電極218上には、ゲート絶縁膜219及び半導体層220が形成されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、多層配線層中に半導体素子を有する半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

特許文献1には、配線層中に半導体膜を形成し、この半導体膜及び配線層の配線を用いてトランジスタを形成することが記載されている。このトランジスタでは、半導体膜の下に位置する配線をゲート電極として使用し、かつ、配線層間の拡散防止膜をゲート絶縁膜として使用している。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−141230号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

トランジスタに求められる特性の一つに、閾値電圧がある。閾値電圧は、ゲート絶縁膜の膜厚のほかに、ゲート電極及びゲート絶縁膜の材料によっても制御できる。しかし、特許文献1に記載の技術では、多層配線層に含まれる配線をゲート電極として使用しているため、ゲート電極の材料を変えることはできなかった。

【課題を解決するための手段】

【0005】

本発明によれば、第1配線を有する第1配線層と、

前記第1配線層より上に形成され、第2配線を有する第2配線層と、

厚さ方向において前記第1配線と前記第2配線の間に位置し、前記第1配線とは異なる材料で形成され、前記第1配線に接続するゲート電極と、

前記ゲート電極上に位置するゲート絶縁膜と、

前記ゲート絶縁膜上に位置する半導体層と、

前記第2配線層に埋め込まれ、前記半導体層と前記第2配線とを接続する第1ビアと、

を備える半導体装置が提供される。

【0006】

本発明によれば、半導体層を用いた素子を配線層間に形成することができる。また、ゲート電極を、配線層の配線とは別工程で形成することができる。従って、ゲート電極の材料を、配線の材料以外の導電体にすることができる。

【0007】

本発明によれば、半導体基板上に、第1配線を有する第1配線層を形成する工程と、

前記第1配線層上に、ゲート電極、前記ゲート電極上に位置するゲート絶縁膜、及び前記ゲート絶縁膜上に位置する半導体層を形成する工程と、

前記第1配線層上及び前記半導体層上に、第2配線を有する第2配線層を形成する工程と、

を備え、

前記ゲート電極は前記第1配線に接続し、前記第2配線は前記半導体層に接続する半導体装置の製造方法が提供される。

【発明の効果】

【0008】

本発明によれば、半導体層を用いた素子を配線層間に形成することができ、かつ、ゲート電極の材料を、配線の材料以外の導電体にすることができる。

【図面の簡単な説明】

【0009】

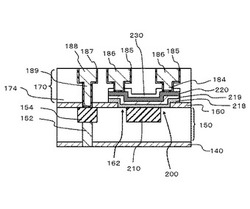

【図1】第1の実施形態に係る半導体装置の構成を示す断面図である。

【図2】図1に示したトランジスタの平面図である。

【図3】図1に示した半導体装置の製造方法を示す断面図である。

【図4】図1に示した半導体装置の製造方法を示す断面図である。

【図5】図1に示した半導体装置の製造方法を示す断面図である。

【図6】図1に示した半導体装置の製造方法を示す断面図である。

【図7】第2の実施形態に係る半導体装置の構成を示す断面図である。

【図8】図7に示した半導体装置の平面図である。

【図9】図7に示した半導体装置の製造方法を示す断面図である。

【図10】図7に示した半導体装置の製造方法を示す断面図である。

【図11】第3の実施形態に係る半導体装置の構成を示す断面図である。

【図12】図11に示した半導体装置の製造方法を示す断面図である。

【図13】図11に示した半導体装置の製造方法を示す断面図である。

【図14】図11に示した半導体装置の製造方法を示す断面図である。

【図15】第4の実施形態に係る半導体装置の構成を示す断面図である。

【図16】図15に示した半導体装置の製造方法を示す断面図である。

【図17】図15に示した半導体装置の製造方法を示す断面図である。

【図18】第5の実施形態に係る半導体装置の構成を示す断面図である。

【図19】図18に示した半導体装置の製造方法を示す断面図である。

【図20】図18に示した半導体装置の製造方法を示す断面図である。

【図21】第6の実施形態に係る半導体装置の構成を示す断面図である。

【図22】図21に示した半導体装置の製造方法を示す断面図である。

【図23】図21に示した半導体装置の製造方法を示す断面図である。

【図24】第7の実施形態に係る半導体装置の構成を示す断面図である。

【図25】図24に示した半導体装置の製造方法を示す断面図である。

【図26】図24に示した半導体装置の製造方法を示す断面図である。

【図27】第8の実施形態に係る半導体装置の構成を示す断面図である。

【図28】図27に示した半導体装置の製造方法を示す断面図である。

【図29】図27に示した半導体装置の製造方法を示す断面図である。

【図30】図27に示した半導体装置の製造方法を示す断面図である。

【図31】図27に示した半導体装置の製造方法を示す断面図である。

【図32】第9の実施形態に係る半導体装置の製造方法を示す断面図である。

【図33】第9の実施形態に係る半導体装置の製造方法を示す断面図である。

【図34】第9の実施形態に係る半導体装置の製造方法を示す断面図である。

【図35】第10の実施形態に係る半導体装置の構成を示す断面図である。

【図36】図35に示した半導体装置の平面図である。

【図37】第11の実施形態に係る半導体装置の構成を示す断面図である。

【図38】第12の実施形態に係る半導体装置の構成を示す断面図である。

【図39】第13の実施形態に係る半導体装置の構成を示す断面図である。

【図40】図39に示した半導体装置の回路図である。

【図41】図39及び図40に示した半導体装置の全体の構成を示す平面図である。

【図42】図39の変形例を示す図である。

【発明を実施するための形態】

【0010】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0011】

(第1の実施形態)

図1は、第1の実施形態に係る半導体装置の構成を示す断面図である。この半導体装置は、第1配線層150、第2配線層170、第1配線210、ゲート電極218、ゲート絶縁膜219、半導体層220、第1ビア184、及び第2配線186を備えている。第2配線層170は、第1配線層150の上に位置している。第1配線層150及び第2配線層170は、多層配線層の少なくとも一部を構成している。この多層配線層は、シリコン基板などの半導体基板(本図では図示せず)上に形成されている。この半導体基板には、例えばトランジスタなどの素子が形成されている。これら半導体基板及びトランジスタについては、後述する別の実施形態において説明する。

【0012】

第1配線層150を構成する絶縁膜、及び第2配線層170を構成する絶縁膜174は、例えば酸化シリコン又は酸化シリコンより誘電率が低い(例えば比誘電率が2.7以下)低誘電率絶縁層である。低誘電率絶縁層は、例えばSiOC膜、SiOCH膜、もしくはSiLK(登録商標)等の炭素含有膜、HSQ(ハイドロジェンシルセスキオキサン)膜、MHSQ(メチル化ハイドロジェンシルセスキオキサン)膜、MSQ(メチルシルセスキオキサン)膜、またはこれらの多孔質膜である。

【0013】

第1配線層150は、拡散防止膜140上に形成されている。拡散防止膜140は、Si、C、及びNのうち少なくとも2種の元素を含む絶縁材料により形成されている。例えば拡散防止膜140は、SiN膜、SiCN膜、又はSiC膜である。なお、拡散防止膜140は、これらの少なくとも2つを積層した積層膜であってもよい。拡散防止膜140の厚さは、例えば10nm以上150nm以下である。

【0014】

第1配線層150を構成する絶縁層の表層には、第3配線154及び第1配線210が埋め込まれている。第3配線154及び第1配線210は同一工程で形成されている。このため、第3配線154及び第1配線210は、同一の深さを有しており、かつ同一の材料、例えば銅を主成分(95%以上)とする金属材料により形成されている。

【0015】

第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。ゲート電極218は、例えばTi、Ta、W、TiN、TaN、WN膜、CoもしくはWを含む化合物、これらのいずれか一つにC及びOの少なくとも一つを導入した膜、またはこれらの膜を複数種類積層した積層膜、を有している。

【0016】

ゲート電極218上には、ゲート絶縁膜219が形成されている。ゲート絶縁膜219の厚さは、例えば0.5nm以上50nm以下である。ゲート絶縁膜219は、例えば酸化シリコン膜、窒化シリコン膜、又はHf、Zr、Al、Ti、及びTaの少なくとも一つの酸化膜を有している。その他、上記絶縁膜に窒素、炭素を添加したものや金属シリケート物であっても良い。また、ゲート絶縁膜219は、これらの2種以上の膜の積層膜であってもよい。

【0017】

ゲート絶縁膜219上には、半導体層220が形成されている。半導体層220は、厚さが例えば10nm以上300nm以下である。半導体層220は、例えば、InGaZnO(IGZO)層、InZnO層、ZnO層、ZnAlO層、ZnCuO層、NiO層、SnO層、SnO2層、CuO層、Ta2O5層、またはTiO2層などの酸化物半導体層を有している。半導体層220は、上記した酸化物半導体層の単層構造であっても良いし、上記した酸化物半導体層と他の層の積層構造であっても良い。後者の例としては、IGZO/Al2O3/IGZO/Al2O3の積層膜がある。また半導体層220はポリシリコン層又はアモルファスシリコン層であってもよい。

【0018】

半導体層220には、ソース及びドレインが設けられている。半導体層220が酸化物半導体層である場合、ソース及びドレインは、例えば酸素欠陥を導入することにより形成されるが、不純物を導入することにより形成されても良い。あるいは、コンタクト形成時に半導体層220を改質させることにより形成されても良い。半導体層220がポリシリコン層やアモルファスシリコン層である場合、ソース及びドレインは不純物を導入することにより形成される。ゲート幅方向(すなわち図1の紙面に垂直な方向)におけるソース及びドレインの幅は、例えば50nm以上10μm以下である。

【0019】

半導体層220のうちソース及びドレインに挟まれている領域は、チャネル領域となる。平面視において、このチャネル領域は、ゲート電極218及びゲート絶縁膜219と重なっている。

【0020】

半導体層220の上には、ハードマスク膜230が設けられている。ハードマスク膜230は、半導体層220をエッチングにより選択的に残す際に用いられる。このため、ハードマスク膜230と半導体層220の平面形状は同一である。ハードマスク膜230は、半導体層220に対してエッチング選択比が取れる材料であれば良い。

【0021】

第2配線層170には、第4配線188及び2つの第2配線186が形成されている。第4配線188は、ビア189を介して第3配線154に接続しており、2つの第2配線186は、それぞれ第1ビア184を介して半導体層220のソース/ドレインに接続している。第1ビア184は、平面視で、ゲート電極218の中心を介して互いに逆側に配置されている。なお、2つの第1ビア184は、ゲート電極218の中心を基準に点対称に配置されている必要はない。例えば半導体層220のドレインに接続する第1ビア184は、半導体層220のソースに接続する第1ビア184よりも、ゲート電極218から離れていても良い。

【0022】

第2配線186及び第4配線188は、互いに同一の工程で形成されている。このため、第2配線186及び第4配線188は、互いに同一の材料、例えば銅を主成分(95%以上)とする金属材料により形成されている。

【0023】

本図に示す例において、各配線及びビアは、デュアルダマシン構造を有している。ただし、少なくとも一つの層の配線及びビアは、シングルダマシン構造を有していても良い。また第2配線層170は、Al配線等、金属膜をドライエッチングにより選択的に除去した構造を有していても良い。また、第2配線層170において、各配線及びビアを埋め込むための溝又は孔の側壁には、バリアメタル膜185,187が形成されている。これらバリアメタル膜185,187は、例えば、Ti、Ta、Ru、W、これらの窒化物又は酸化物などにより形成されている。なお、バリアメタル膜185,187は、これらの材料で構成された単層であってもよいし、2つ以上の層が積層したものであってもよい。積層構造の例としては、例えば、TiN(上層)/Ti(下層)、又は、Ta(上層)/TaN(下層)の積層構造がある。

【0024】

また、第1配線層150においても、各配線及びビアを埋め込むための溝又は孔の側壁にバリアメタル膜が形成されていてもよい。このバリアメタル膜も、第2配線層170のバリアメタル膜と同様の構造を有している。

【0025】

なお、各配線の材料と、各バリアメタル膜の材料の組み合わせは、上記した例に限定されない。例えば少なくとも一つの配線層は、Alにより形成されていても良い。

【0026】

上記した構成において、ゲート電極218、ゲート絶縁膜219、及び半導体層220は、トランジスタ200(第2トランジスタ)を構成している。すなわち本実施形態では、多層配線層中に能動素子が形成されている。トランジスタ200がNチャネル型のトランジスタである場合、半導体層220はInGaZnO(IGZO)層、InZnO層、ZnO層、ZnAlO層、ZnCuO層、SnO2層、Ta2O5層、またはTiO2層で形成される。またトランジスタ200がPチャネル型のトランジスタである場合、半導体層220はNiO2層、SnO層、ZnO層、ZnAlO層、ZnCuO層、またはCuO層で形成される。またNチャネル型のトランジスタ200とPチャネル型のトランジスタ200を同一の層に形成する場合、各トランジスタ200の半導体層220と同一の材料により形成しても良い。

【0027】

本実施形態において、第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。拡散防止膜160には、開口162が形成されている。ゲート電極218は、開口162の内側、及びその周囲に位置する拡散防止膜160上に形成されている。拡散防止膜160の構成は、拡散防止膜140の構成と同様である。またゲート絶縁膜219、半導体層220、及びハードマスク膜230も、ゲート電極218と同じ平面形状を有している。本図に示す例において、ゲート電極218は、拡散防止膜160よりも薄い。ただし、ゲート電極218は、拡散防止膜160と同程度の厚さであっても良いし、拡散防止膜160よりも厚くても良い。

【0028】

なお、ハードマスク膜230は、例えば拡散防止膜160と同一材料かつ同一の厚さの層である。ただし、ハードマスク膜230は、拡散防止膜160とは異なる材料により形成されていても良い。またハードマスク膜230は、拡散防止膜160と同一材料の層と、この層の上に他の層(例えばSiO2層又はSiOCH層)をこの順に積層した積層膜であってもよい。この場合、他の層の厚さは、例えば10nm以上200nm以下である。

【0029】

図2は、図1に示したトランジスタ200の平面図である。本図に示す例において、半導体層220のうち一つのトランジスタ200を形成している領域は、長方形を有している。2つの第1ビア184は、半導体層220の2つの短辺の近傍に接続している。

【0030】

図3〜図6は、図1に示した半導体装置の製造方法を示す断面図である。まず、図3(a)に示すように、半導体基板(図示せず)にトランジスタ等を形成し、さらに半導体基板上に下層の配線層(図示せず)を形成する。ついで、この配線層の上に拡散防止膜140を形成する。次いで、拡散防止膜140上に、第1配線層150を構成する絶縁膜を形成する。次いで、この絶縁膜に、ビアホール及び配線溝を形成する。

【0031】

次いで、必要に応じて、ビアホール及び配線溝の底面及び側壁、ならびに第1配線層150となる絶縁膜上に、バリアメタル膜(図示せず)を形成する。このバリアメタル膜は、例えばスパッタリング法を用いて形成される。次いで、ビアホール及び配線溝内、ならびに第1配線層150を構成する絶縁膜上に、金属膜を例えばめっき法を用いて形成する。次いで、第1配線層150を構成する絶縁膜上の金属膜及びバリアメタル膜を、例えばCMP法を用いて除去する。これにより、第1配線層150が形成される。第1配線層150には、第3配線154、ビア152、及び第1配線210が含まれている。なお、ビア152及び第3配線154は、シングルダマシン法により形成されても良いが、デュアルダマシン法により形成されても良い。

【0032】

次いで、第1配線層150上に、拡散防止膜160を形成する。拡散防止膜160は、例えばCVD法を用いて形成される。

【0033】

次いで図3(b)に示すように、拡散防止膜160上に、ハードマスク膜240を形成する。次いで、ハードマスク膜240上にレジストパターン242を形成する。次いで、レジストパターン242をマスクとして、ハードマスク膜240をエッチングする。これにより、ハードマスク膜240には開口が形成される。この開口は、拡散防止膜160のうち開口162が形成される領域の上に位置している。

【0034】

次いで図4(a)に示すように、ハードマスク膜240をマスクとして、拡散防止膜160をエッチングする。これにより、拡散防止膜160には開口162が形成される。この段階で、開口162の底面には、第1配線210が露出する。

【0035】

その後、図4(b)に示すように、ハードマスク膜240を除去する。

【0036】

次いで図5(a)に示すように、開口162内に位置する第1配線210上、及び拡散防止膜160の全面上に、ゲート電極218を形成する。ゲート電極218は、例えばスパッタリング法により形成されるが、CVD法により形成されても良い。次いでゲート電極218上に、ゲート絶縁膜219を形成する。ゲート絶縁膜219は、例えばCVD法又はスパッタリング法により形成される。

【0037】

次いで、ゲート絶縁膜219上に、半導体層220を形成する。半導体層220がInGaZnO、InZnO、ZnO、ZnAlO、ZnCuO、NiO、SnO、CuOなどの酸化物半導体層を含んでいる場合、半導体層220は、例えばスパッタリング法により形成される。このとき半導体基板は、400℃以下の温度に加熱される。また半導体層220がポリシリコン層やアモルファスシリコン層である場合、半導体層220は、例えばプラズマCVD法により形成される。

【0038】

次いで、半導体層220上に、ハードマスク膜230を形成する。例えばハードマスク膜230が拡散防止膜160と同一層を有している場合、この層は、拡散防止膜160と同一の方法により形成される。また、ハードマスク膜230がさらに酸化シリコン層を有している場合、この酸化シリコン層は、例えばCVD法を用いて形成される。

【0039】

次いで図5(b)に示すように、ハードマスク膜230上にレジストパターン232を形成する。

【0040】

次いで図6(a)に示すように、レジストパターン232をマスクとして、ハードマスク膜230をエッチングする。これにより、ハードマスク膜230は、所定のパターンに加工される。

【0041】

その後、図6(b)に示すように、レジストパターン232を除去する。次いで、ハードマスク膜230をマスクとして、半導体層220、ゲート絶縁膜219、及びゲート電極218をエッチングする。これにより、半導体層220、ゲート絶縁膜219、及びゲート電極218は、所定の形状に加工される。半導体層220は、ゲート絶縁膜219上、及びゲート絶縁膜219の周囲に位置する拡散防止膜160上にも形成される。またこの工程において、第3配線154上に位置する半導体層220、ゲート絶縁膜219、及びゲート電極218は除去される。

【0042】

次いで、半導体層220にソース及びドレインを形成する。次いで、拡散防止膜160上及びハードマスク膜230上に、第2配線層170を構成する絶縁膜174を形成する。次いで、絶縁膜174に、ビアホール及び配線溝を形成する。絶縁膜174にビアホールを形成する工程において、ハードマスク膜230及び拡散防止膜160は、エッチングストッパーとしても機能する。特にハードマスク膜230が拡散防止膜160と同一の材料の膜を同一の厚さで有している場合、ビアの底面に位置するハードマスク膜230及び拡散防止膜160を貫通させる工程の条件出しを容易に行える。

【0043】

なお、半導体層220にソース及びドレインを形成する工程は、ここで行われても良い。例えば、半導体層220のうちビアホールの底面に露出している領域に、還元性プラズマ(例:水素プラズマ)による処理、又は窒素含有プラズマ(例:アンモニアプラズマ)による処理を行うと、半導体層220にソース及びドレインが形成される。

【0044】

次いで、ビアホール及び配線溝の底面及び側壁、ならびに絶縁膜174上に、バリアメタル膜185,187を形成する。バリアメタル膜185,187は、例えばスパッタリング法を用いて形成される。次いで、ビアホール及び配線溝内、ならびに絶縁膜174上に、金属膜を例えばめっき法を用いて形成する。次いで、絶縁膜174上の金属膜及びバリアメタル膜を、例えばCMP法を用いて除去する。これにより、第2配線層170が形成される。第2配線層170には、第2配線186及び第4配線188、並びに第1ビア184及びビア189が含まれている。なお、上記したように、第2配線層170がAl配線により形成されていてもよい。この場合、第2配線層170には、電極パッドが含まれていてもよい。

このようにして、図1に示す半導体装置が形成される。

【0045】

次に、本実施形態の作用及び効果について説明する。本実施形態によれば、第1配線210の上にゲート電極218を形成している。このため、ゲート電極218を構成する導電材料を、第1配線210を構成する導電材料と異ならせることができる。このため、ゲート電極218を構成する導電材料を適切な材料にすることにより、ゲート電極218の仕事関数を調整し、トランジスタ200の閾値電圧を所望する電圧に設定することができる。また、トランジスタ200を、ノーマリーオフ型のトランジスタ及びノーマリーオン型のトランジスタのいずれにすることもできる。

【0046】

また、第1配線210の上面をゲート電極218で覆っているため、第1配線210上から拡散防止膜160を除去しても、第1配線210を構成する導電材料が第2配線層170に拡散することを抑制できる。

【0047】

また、拡散防止膜160とは別にゲート絶縁膜219を設けているため、ゲート絶縁膜219の厚さを拡散防止膜160と異ならせることができる。このため、ゲート絶縁膜219を薄くして、トランジスタ200のゲート容量を少なくすることができる。また、ゲート絶縁膜219には第1配線210のバリア膜としての機能が求められないため、ゲート絶縁膜219として使用することができる材料の選択肢が多くなる。

【0048】

(第2の実施形態)

図7は、第2の実施形態に係る半導体装置の構成を示す断面図である。図8は、図7に示した半導体装置の平面図である。本実施形態に係る半導体装置は、トランジスタ200のゲート電極218の形状を除いて、第1の実施形態に係る半導体装置と同様の構成である。

【0049】

本実施形態においてゲート電極218は、開口162内にのみ位置している。ゲート電極218の上面は、拡散防止膜160の上面と同一面(例えば同一平面)を形成している。

【0050】

ゲート絶縁膜219及び半導体層220は、ゲート電極218上、及びゲート電極218の周囲に位置する拡散防止膜160上に形成されている。すなわち、平面視で半導体層220はゲート電極218よりも広い。そして平面視で、2つの第1ビア184は、いずれも中心がゲート電極218とは重なっていない。すなわち第1ビア184は、ゲート電極218に対してオフセットされている。本図に示す例では、2つの第1ビア184は、全体がゲート電極218と重なっていない。

【0051】

図9及び図10は、図7に示した半導体装置の製造方法を示す断面図である。まず図9(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、拡散防止膜160、及び開口162を形成する。これらの形成方法は、第1の実施形態と同様である。

【0052】

次いで図9(b)に示すように、開口162内及び拡散防止膜160上に、ゲート電極218を形成する。このとき、ゲート電極218を、拡散防止膜160よりも厚く形成する。

【0053】

次いで図10(a)に示すように、拡散防止膜160上に位置するゲート電極218を、CMP法を用いて除去する。これにより、ゲート電極218は、開口162内にのみ位置する。また、ゲート電極218の上面は、拡散防止膜160の上面と同一面となる。

【0054】

次いで図10(b)に示すように、ゲート電極218上及び拡散防止膜160の全面上に、ゲート絶縁膜219、及び半導体層220を形成する。次いで、半導体層220上にハードマスク膜230を形成する。次いで、ハードマスク膜230上にレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、ハードマスク膜230をエッチングする。これにより、ハードマスク膜230は所定のパターンを有する。次いで、必要に応じてレジストパターンを除去する。そして、ハードマスク膜230をマスクとして、半導体層220及びゲート絶縁膜219をエッチングする。これにより、半導体層220及びゲート絶縁膜219は、ゲート電極218上及びその周囲にのみ残る。

【0055】

その後の工程は、第1の実施形態と同様である。

【0056】

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。また、ゲート絶縁膜219及び半導体層220の形状と、ゲート電極218の形状とを互いに異ならせることができる。これにより、ゲート電極218の端部を、半導体層220の端部から離すことができる。従って、ゲート電極218から半導体層220に向かって流れるリーク電流を少なくすることができる。これにより、ゲート電極218の信頼性が向上する。

【0057】

また、開口162の形状を変更することにより、ゲート電極218の形状を任意の形状に設定することができる。また、ハードマスク膜230のパターンを変更することにより、ゲート絶縁膜219及び半導体層220の形状を任意の形状に設定することができる。これにより、半導体層220のうちチャネルとなる領域のうちゲート電極218とオーバーラップする領域を、所望の形状及び面積にすることができる。これにより、ソース・ドレイン間の耐圧を制御することができる。

【0058】

(第3の実施形態)

図11は、第3の実施形態に係る半導体装置の構成を示す断面図である。本実施形態に係る半導体装置は、以下の点を除いて、第2の実施形態に係る半導体装置と同様の構成である。

【0059】

まず、拡散防止膜160の上には、保護絶縁膜165が形成されている。保護絶縁膜165は、例えば第2配線層170を構成する絶縁膜と同様の材料により形成されているが、異なる材料であってもよい。例えば第2配線層170が低誘電率膜である場合、保護絶縁膜165は、酸化シリコン膜であってもよい。

【0060】

開口162は、拡散防止膜160及び保護絶縁膜165に形成されている。ゲート電極218の上面は、保護絶縁膜165の上面と同一面(例えば同一平面)を形成している。ゲート絶縁膜219、半導体層220、及びハードマスク膜230の積層体は、ゲート電極218上、及びゲート電極218の周囲に位置する保護絶縁膜165上に形成されている。

【0061】

図12〜図14は、図11に示した半導体装置の製造方法を示す断面図である。まず図12(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、及び拡散防止膜160を形成する。これらの形成方法は、第2の実施形態と同様である。次いで、拡散防止膜160上に保護絶縁膜165を形成する。

【0062】

次いで図12(b)に示すように、保護絶縁膜165上にレジストパターン242を形成する。次いで、レジストパターン242をマスクとして保護絶縁膜165をエッチングする。これにより、保護絶縁膜165に開口162が形成される。ただしこの段階では、開口162は拡散防止膜160を貫通していない。

【0063】

次いで図13(a)に示すように、レジストパターン242を除去する。次いで、保護絶縁膜165をマスクとして拡散防止膜160をエッチングする。これにより、開口162は拡散防止膜160を貫通し、開口162の底面に第1配線210が露出する。

【0064】

次いで図13(b)に示すように、開口162内及び保護絶縁膜165上に、ゲート電極218を形成する。このとき、ゲート電極218の膜厚を、拡散防止膜160と保護絶縁膜165の積層膜の膜厚よりも大きくする。

【0065】

次いで図14(a)に示すように、保護絶縁膜165上に位置するゲート電極218を、CMP法を用いて除去する。これにより、ゲート電極218は、開口162内にのみ位置する。また、ゲート電極218の上面は、保護絶縁膜165の上面と同一面となる。

【0066】

次いで図14(b)に示すように、ゲート絶縁膜219、半導体層220、及びハードマスク膜230の積層膜を、保護絶縁膜165上に形成する。これらの形成方法は、第2の実施形態と同様である。

【0067】

その後の工程は、第2の実施形態と同様である。

【0068】

本実施形態によっても、第2の実施形態と同様の効果を得ることができる。また、拡散防止膜160は保護絶縁膜165によって覆われているため、ゲート電極218のうち不要な部分は、保護絶縁膜165上に形成される。このため、ゲート電極218のうち不要な部分をCMP法で除去する際に、拡散防止膜160がダメージを受けることを抑制できる。このため、第3配線154を構成する導電材料が第2配線層170内に拡散することを抑制できる。

【0069】

また、開口162を拡散防止膜160及び保護絶縁膜165の積層膜に形成しているため、第2の実施形態と比較して、ゲート電極218を厚くすることができる。従って、半導体層220を第1配線210から離すことができる。これにより、第1配線210がトランジスタ200の閾値電圧や信頼性などのトランジスタ特性に与える影響を小さくすることができる。

【0070】

(第4の実施形態)

図15は、第4の実施形態に係る半導体装置の構成を示す断面図である。本実施形態に係る半導体装置は、以下の点を除いて、第2の実施形態に係る半導体装置と同様の構成を有している。

【0071】

まず、拡散防止膜160の開口162の中には、バリアメタル膜216が形成されている。バリアメタル膜216は、例えばTi、Ta、W、TiN、TaN、WN膜、CoもしくはWを含む化合物、これらのいずれか一つにC及びOの少なくとも一つを導入した膜、又はこれらの膜を複数種類積層した積層膜、を有している。バリアメタル膜216は、例えば拡散防止膜160と同一の厚さを有しているが、拡散防止膜160よりも薄くても良い。

【0072】

ゲート電極218は、バリアメタル膜216上、及びその周囲に位置する拡散防止膜160上に形成されている。すなわち本実施形態では、ゲート電極218は、バリアメタル膜216を介して第1配線210に接続している。そしてゲート絶縁膜219、半導体層220及びハードマスク膜230の積層体は、ゲート電極218と同一の平面形状を有している。

【0073】

図16及び図17は、図15に示した半導体装置の製造方法を示す断面図である。まず図16(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、拡散防止膜160、及び開口162を形成する。これらの形成方法は、第2の実施形態と同様である。

【0074】

次いで図16(b)に示すように、開口162内及び拡散防止膜160上に、バリアメタル膜216を形成する。このとき、バリアメタル膜216の厚さを、拡散防止膜160よりも厚くする。

【0075】

次いで図17(a)に示すように、拡散防止膜160上に位置するバリアメタル膜216を、CMP法を用いて除去する。これにより、バリアメタル膜216は、開口162内にのみ位置する。また、バリアメタル膜216の上面は、拡散防止膜160の上面と同一面となる。

【0076】

次いでバリアメタル膜216上及び拡散防止膜160の全面上に、ゲート電極218、ゲート絶縁膜219、及び半導体層220を形成する。次いで、半導体層220上にハードマスク膜230を形成する。次いで、ハードマスク膜230上にレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、ハードマスク膜230をエッチングする。これにより、ハードマスク膜230は所定のパターンを有する。次いで、必要に応じてレジストパターンを除去する。そして、ハードマスク膜230をマスクとして、半導体層220、ゲート絶縁膜219、及びゲート電極218をエッチングする。これにより、半導体層220、ゲート絶縁膜219、及びゲート電極218は、バリアメタル膜216上及びその周囲にのみ残る。

【0077】

その後の工程は、第2の実施形態と同様である。

【0078】

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。また、ゲート電極218と第1配線210の間に、バリアメタル膜216を形成している。このため、第1配線210を構成する導電材料が第2配線層170内に拡散することを、さらに抑制できる。

【0079】

また、ゲート電極218の材料を選択するときに、拡散防止能力を考慮する必要がなくなる。従って、ゲート電極218の材料の選択肢が増える。また、ゲート電極218を薄くすることも可能となる。例えばゲート電極218として、Ti、Ta、Al、Hf、W、Ni、Co、Ptおよびこれらの化合物(窒化物、炭化物、酸素添加物、複合金属およびシリサイド)を使用することができる。

【0080】

(第5の実施形態)

図18は、第5の実施形態に係る半導体装置の構成を示す断面図である。本実施形態に係る半導体装置は、保護絶縁膜165を有している点を除いて、第4の実施形態に係る半導体装置と同様の構成である。

【0081】

保護絶縁膜165の構成は、第3の実施形態と同様である。開口162は、拡散防止膜160及び保護絶縁膜165の積層体に形成されている。バリアメタル膜216の上面は、保護絶縁膜165の上面と同一面を形成されている。そして、ゲート電極218、ゲート絶縁膜219、半導体層220、及びハードマスク膜230の積層体は、バリアメタル膜216及びその周囲に位置する保護絶縁膜165上に形成されている。

【0082】

図19及び図20は、図18に示した半導体装置の製造方法を示す断面図である。まず19(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、拡散防止膜160、保護絶縁膜165、及び開口162を形成する。これらの形成方法は、第3の実施形態と同様である。

【0083】

次いで図19(b)に示すように、開口162内及び保護絶縁膜165上に、バリアメタル膜216を形成する。このとき、バリアメタル膜216の厚さを、拡散防止膜160と保護絶縁膜165の積層膜よりも厚くする。

【0084】

次いで、保護絶縁膜165上に位置するバリアメタル膜216を、CMP法を用いて除去する。これにより、バリアメタル膜216は、開口162内にのみ位置する。また、バリアメタル膜216の上面は、保護絶縁膜165の上面と同一面となる。

【0085】

次いで図20に示すように、バリアメタル膜216上及びその周囲に位置する保護絶縁膜165上に、ゲート電極218、ゲート絶縁膜219、半導体層220、及びハードマスク膜230を形成する。これらの形成方法は、第4の実施形態と同様である。

【0086】

その後の工程は、第4の実施形態と同様である。

【0087】

本実施形態によっても、第4の実施形態と同様の効果を得ることができる。また、保護絶縁膜165を形成しているため、第3の実施形態と同様の効果も得ることができる。

【0088】

(第6の実施形態)

図21は、第6の実施形態に係る半導体装置の構成を示す断面図である。本実施形態に係る半導体装置は、以下の点を除いて、第5の実施形態に係る半導体装置と同様の構成である。

【0089】

まず、バリアメタル膜216は、拡散防止膜160及び保護絶縁膜165の積層膜より薄い。またゲート電極218は、開口162内に埋め込まれている。ゲート電極218の上面は、保護絶縁膜165の上面と同一面を形成している。そしてゲート絶縁膜219、半導体層220、及びハードマスク膜230の積層体は、ゲート電極218上、及びゲート電極218の周囲に位置する保護絶縁膜165上に形成されている。ゲート電極218の厚さ、及びバリアメタル膜216の厚さは、それぞれに求められる機能に基づいて設計される。このため、拡散防止膜160と保護絶縁膜165の境界と、バリアメタル膜216とゲート電極218の境界は、互いに同じ高さに位置する場合もあるし、異なる場合もある。

【0090】

図22及び図23は、図21に示した半導体装置の製造方法を示す断面図である。まず図22(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、拡散防止膜160、保護絶縁膜165、開口162、及びバリアメタル膜216を形成する。これらの形成方法は、第5の実施形態と同様である。この段階では、バリアメタル膜216の上面は、保護絶縁膜165の上面と同一面を形成している。

【0091】

次いで図22(b)に示すように、バリアメタル膜216をエッチバックする。これにより、バリアメタル膜216の上面は、保護絶縁膜165の上面よりも低くなる。

【0092】

次いで図23(a)に示すように、バリアメタル膜216上及び保護絶縁膜165上に、ゲート電極218を形成する。次いで、バリアメタル膜216上に位置するゲート電極218を、CMP法を用いて除去する。これにより、開口162のうちバリアメタル膜216上に位置する部分には、ゲート電極218が埋め込まれる。ゲート電極218の上面は、保護絶縁膜165の上面と同一面を形成している。

【0093】

次いで図23(b)に示すように、ゲート電極218及びその周囲に位置する保護絶縁膜165上に、ゲート絶縁膜219、半導体層220、及びハードマスク膜230の積層体を形成する。これらの形成方法は、第3の実施形態と同様である。

【0094】

その後の工程は、第3の実施形態と同様である。

【0095】

本実施形態によっても、第5の実施形態と同様の効果を得ることができる。また、ゲート電極218が開口162内に埋め込まれているため、第3の実施形態と同様の効果を得ることができる。

【0096】

(第7の実施形態)

図24は、第7の実施形態に係る半導体装置の構成を示す断面図である。本実施形態に係る半導体装置は、トランジスタ200の他にトランジスタ201を有している点を除いて、第4の実施形態に係る半導体装置と同様の構成である。

【0097】

トランジスタ201は、トランジスタ200と同一層に形成されており、ゲート電極218、ゲート絶縁膜219、及び半導体層220の材料の組み合わせを除いて、トランジスタ200と同様の構成を有している。例えばトランジスタ200とトランジスタ201のチャネルの導電型が互いに同一である場合、トランジスタ200とトランジスタ201との間でゲート電極218、ゲート絶縁膜219、及び半導体層220の材料の組み合わせを異ならせることにより、トランジスタ200とトランジスタ201の閾値電圧を変えることができる。また、トランジスタ200をNチャネル型のトランジスタとして、トランジスタ201をPチャネル型のトランジスタとすることもできる。

【0098】

図25及び図26は、図24に示した半導体装置の製造方法を示す断面図である。まず図25(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、拡散防止膜160、及び開口162を形成する。これらの工程は、第1配線210及び開口162を2箇所に形成する点を除いて、第4の実施形態と同様である。

【0099】

次いで図25(b)に示すように、2箇所の開口162それぞれの中に、バリアメタル膜216を埋め込む。これらの形成方法も、第4の実施形態と同様である。

【0100】

次いで図26(a)に示すように、拡散防止膜160上及びバリアメタル膜216上に、トランジスタ200を構成するゲート電極218、ゲート絶縁膜219、及び半導体層220を形成する。次いで、半導体層220上に、トランジスタ200を構成するハードマスク膜230を形成する。次いで、このハードマスク膜230をマスクとして、半導体層220、ゲート絶縁膜219、及びゲート電極218をエッチングする。これにより、トランジスタ200のゲート電極218、ゲート絶縁膜219、及び半導体層220が形成される。

【0101】

次いで図26(b)に示すように、拡散防止膜160上、及びトランジスタ201が形成されるバリアメタル膜216上に、トランジスタ201を構成するゲート電極218、ゲート絶縁膜219、及び半導体層220を形成する。次いで、半導体層220上に、トランジスタ201を構成するハードマスク膜230を形成する。次いで、このハードマスク膜230をマスクとして、半導体層220、ゲート絶縁膜219、及びゲート電極218をエッチングする。これにより、トランジスタ201のゲート電極218、ゲート絶縁膜219、及び半導体層220が形成される。

【0102】

この後の工程は、第4の実施形態と同様である。

【0103】

本実施形態によっても、第4の実施形態と同様の効果を得ることができる。また、互いに特性が異なるトランジスタ200及びトランジスタ201を同一層に形成することができる。

【0104】

(第8の実施形態)

図27は、第8の実施形態に係る半導体装置の構成を示す断面図である。本実施形態に係る半導体装置は、トランジスタ200,201が、第6の実施形態に係るトランジスタ200と同様の構成を有している点を除いて、第7の実施形態に係る半導体装置と同様の構成である。

【0105】

図28〜図31は、図27に示した半導体装置の製造方法を示す断面図である。まず図28(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、拡散防止膜160、保護絶縁膜165、及び開口162を形成する。これらの工程は、第1配線210及び開口162を2箇所に形成する点を除いて、第6の実施形態と同様である。

【0106】

次いで図28(b)に示すように、2つの開口162内に、バリアメタル膜216を埋め込む。この工程も、第6の実施形態と同様である。この段階において、2つのバリアメタル膜216の上面は、保護絶縁膜165の上面と同一面を形成している。

【0107】

次いで図29(a)に示すように、保護絶縁膜165上及びバリアメタル膜216上にレジストパターン50を形成する。レジストパターン50は、トランジスタ200が形成されるバリアメタル膜216上に、開口を有している。次いで、レジストパターン50をマスクとしてバリアメタル膜216をエッチバックする。これにより、トランジスタ200が形成されるバリアメタル膜216の上面は、保護絶縁膜165の上面よりも低くなる。

【0108】

その後、図29(b)に示すように、レジストパターン50を除去する。次いで、トランジスタ200が形成されるバリアメタル膜216上に、トランジスタ200のゲート電極218(218a)を埋め込む。この工程は、第6の実施形態と同様である。

【0109】

次いで図30(a)に示すように、保護絶縁膜165上、トランジスタ200のゲート電極218(218a)上、及びトランジスタ201のバリアメタル膜216上に、レジストパターン52を形成する。レジストパターン52は、トランジスタ201が形成されるバリアメタル膜216上に、開口を有している。次いで、レジストパターン52をマスクとしてバリアメタル膜216をエッチバックする。これにより、トランジスタ201が形成されるバリアメタル膜216の上面は、保護絶縁膜165の上面よりも低くなる。

【0110】

その後、図30(b)に示すように、レジストパターン52を除去する。次いで、トランジスタ201が形成されるバリアメタル膜216上に、トランジスタ201のゲート電極218(218b)を埋め込む。トランジスタ200のゲート電極218aと、トランジスタ201のゲート電極218bは、別の材料により形成されていても良い。この工程は、トランジスタ200のゲート電極218(218a)を形成する工程と同様である。

【0111】

次いで図31(a)に示すように、拡散防止膜160上及びゲート電極218(218a)上に、トランジスタ200を構成するゲート絶縁膜219及び半導体層220を形成する。次いで、半導体層220上に、トランジスタ200を構成するハードマスク膜230を形成する。次いで、このハードマスク膜230をマスクとして、半導体層220及びゲート絶縁膜219をエッチングする。これにより、トランジスタ200のゲート絶縁膜219及び半導体層220が形成される。

【0112】

次いで図31(b)に示すように、拡散防止膜160上、及びトランジスタ201のゲート電極218(218b)上に、トランジスタ201を構成するゲート絶縁膜219及び半導体層220を形成する。次いで、半導体層220上に、トランジスタ201を構成するハードマスク膜230を形成する。次いで、このハードマスク膜230をマスクとして、半導体層220及びゲート絶縁膜219をエッチングする。これにより、トランジスタ201のゲート絶縁膜219及び半導体層220が形成される。

【0113】

この後の工程は、第6の実施形態と同様である。

【0114】

本実施形態によっても、第6の実施形態と同様の効果を得ることができる。また、互いに特性が異なるトランジスタ200及びトランジスタ201を同一層に形成することができる。

【0115】

なお、トランジスタ200及びトランジスタ201は、第1〜第3、第5の実施形態のいずれかと同様の構造を有していても良い。

【0116】

(第9の実施形態)

図32、図33、及び図34は、第9の実施形態に係る半導体装置の製造方法を示す断面図である。本実施形態によって製造される半導体装置の構成は、第8の実施形態に示した半導体装置の構成と同様である。

【0117】

まず、図32(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、拡散防止膜160、及び2つの開口162を形成し、さらに2つの開口162のそれぞれにバリアメタル膜216を埋め込む。これらの形成方法は、第8の実施形態と同様である。

【0118】

次いで図32(b)に示すように、2つのバリアメタル膜216を同時にエッチバックする。これにより、2つのバリアメタル膜216の上面は、いずれも保護絶縁膜165の上面よりも低くなる。

【0119】

次いで図33(a)に示すように、2つのバリアメタル膜216上及び保護絶縁膜165上に、ゲート電極218(218a)を形成する。次いで、保護絶縁膜165上に位置するゲート電極218(218a)を、CMP法を用いて除去する。これにより、2つの開口162内には、いずれもゲート電極218(218a)が埋め込まれる。

【0120】

次いで図33(b)に示すように、トランジスタ200となるゲート電極218(218a)を、レジストパターン54で覆う。ただしレジストパターン54は、トランジスタ201となるバリアメタル膜216の上方には形成されていない。次いで、レジストパターン54をマスクとして、トランジスタ201となるバリアメタル膜216上のゲート電極218(218a)を、エッチングにより除去する。

【0121】

次いで図34(a)に示すように、トランジスタ201となるバリアメタル膜216上、保護絶縁膜165上、及びトランジスタ200のゲート電極218(218a)上に、ゲート電極218(218b)を形成する。次いで図34(b)に示すように、保護絶縁膜165上、及びトランジスタ200のゲート電極218(218a)上に位置するゲート電極218(218b)を、CMP法により除去する。

【0122】

このようにして、トランジスタ200となる開口162には、バリアメタル膜216及びゲート電極218(218a)が埋め込まれ、トランジスタ201となる開口162には、バリアメタル膜216及びゲート電極218(218b)が埋め込まれる。その後の工程は、第8の実施形態と同様である。

【0123】

本実施形態によっても、第8の実施形態と同様の効果を得ることができる。また第8の実施形態と比較して、レジストパターンの形成回数を少なくすることができるため、半導体装置の製造工程数を少なくすることができる。

【0124】

(第10の実施形態)

図35は、第10の実施形態に係る半導体装置の構成を示す断面図である。図36は、図35に示した半導体装置の平面図である。この半導体装置において、トランジスタ200を構成する各層の積層構造は、第3の実施形態と同様である。ただし、ゲート電極218の平面レイアウトは櫛歯形状である。そして半導体層220のうち各ゲート電極218に挟まれている部分の上には、ソース配線となる第2配線186(186b)と、ドレイン配線となる第2配線186(186a)が、交互に延伸している。そして一つの第2配線186について、複数の第1ビア184が形成されている。これら2つの第2配線186の平面レイアウトも、櫛歯形状である。すなわち、本実施形態に係るトランジスタ200は、櫛歯型のレイアウトを有している。

【0125】

本実施形態によっても、第3の実施形態と同様の効果を得ることができる。また、トランジスタ200が櫛歯型のレイアウトを有しており、実効的なチャネル幅を広く確保できるため、トランジスタ200のオン電流を大きくすることができる。

【0126】

なお、本実施形態において、トランジスタ200を構成する各層の積層構造は、第1〜第2の実施形態、及び第4〜第6の実施形態のいずれかに示した構造であっても良い。

【0127】

(第11の実施形態)

図37は、第11の実施形態に係る半導体装置の構成を示す断面図である。この半導体装置は、トランジスタ200の代わりに容量素子202を有している点を除いて、第5の実施形態に係る半導体装置と同様の構成である。

【0128】

容量素子202はMIS型の容量素子であり、トランジスタ200におけるソース、チャネル領域、及びドレインそれぞれに接続する第1ビア184を、同一の第2配線186に接続した構成を有している。このため、容量素子202を、トランジスタ200と同一の方法により形成することができる。

【0129】

本実施形態によれば、多層配線層中に、MIS型の容量素子202を形成することができる。そして、第5の実施形態に示したトランジスタ200と、本実施形態に係る容量素子202を、同一層に、同一工程で形成することができる。

【0130】

なお、本実施形態において、容量素子202を構成する各層の積層構造は、第1〜第4の実施形態、及び第6の実施形態のいずれかに示した構造であっても良い。

【0131】

(第12の実施形態)

図38は、第12の実施形態に係る半導体装置の構成を示す断面図である。この半導体装置は、トランジスタ200の代わりにダイオード204を有している点を除いて、第5の実施形態に係る半導体装置と同様の構成である。

【0132】

ダイオード204は、第5の実施形態におけるトランジスタ200のゲート電極218と、半導体層220のソースに接続する配線182とを、ビア183を介して互いに短絡した構成を有している。ビア183は、ビア181と同一工程で形成されている。すなわちビア181,183及び配線182は、デュアルダマシン構造を有している。

【0133】

本実施形態によれば、多層配線層中に、ダイオード204を形成することができる。そして、第5の実施形態に示したトランジスタ200及び第11の実施形態に示した容量素子202の少なくとも一方と、本実施形態に係るダイオード204を、同一層に、同一工程で形成することができる。

【0134】

なお、本実施形態において、ダイオード204を構成する各層の積層構造は、第1〜第4の実施形態、及び第6の実施形態のいずれかに示した構造であっても良い。

【0135】

(第13の実施形態)

図39は、第13の実施形態に係る半導体装置の構成を示す断面図である。この半導体装置は、半導体基板10及び多層配線層100を備えている。

【0136】

半導体基板10には、素子分離膜20及びトランジスタ12,14(第1のトランジスタ)が形成されている。さらに、素子分離膜20上には、受動素子(例えば抵抗素子)16が形成されている。受動素子16は、トランジスタ12のゲート電極と同一工程で形成されている。

【0137】

多層配線層100には、第1〜第6の実施形態に示したトランジスタ200、第11の実施形態に示した容量素子202、及び第12の実施形態に示したダイオード204の少なくとも一つが形成されている。本図に示す例では、第1の実施形態(図1)に示したトランジスタ200が形成されている。トランジスタ200の平面形状は、トランジスタ12,14の平面形状よりも大きい。なお、図示していないが、この半導体装置は、トランジスタ200と同一層に、ダイオード204を有している。

【0138】

本図に示す例では、第1配線層150は、回路を形成するための配線層であるローカル配線層102の最上層に位置しており、第2配線層170は、電源配線及び接地配線を引き回すための配線であるグローバル配線層104の最下層に位置している。第2配線層170の上には、層間絶縁膜190を介して配線194が形成されている。配線194はAl配線であり、ビア192を介して第2配線層170の配線(例えば第4配線188)に接続している。配線194は、下面及び上面に、バリアメタル膜が形成されている。このバリアメタル膜は、Tiを主成分とする金属膜、この金属の窒化膜、又はこれら金属膜及び窒化膜の積層膜である。なお、配線194と同一層には、電極パッド(後述する電源パッド400、接地パッド402、及び信号用のI/Oパッド410)が形成されている。

【0139】

なお、ローカル配線層102を構成する各配線層は、グローバル配線層104を構成する配線層よりも薄い。そしてローカル配線層102の各配線も、グローバル配線層104の各配線よりも薄い。

【0140】

トランジスタ12のドレイン(又はソース)は、ローカル配線層102に形成された配線及びビアを介して、第3配線154に接続している。トランジスタ14のドレインは、ローカル配線層102に形成された配線及びビアを介して、ゲート電極218に接続している。トランジスタ12,14は、後述する内部回路300,302を構成している。なお、トランジスタ14は、平面視においてトランジスタ200の半導体層220と重なっている。

【0141】

図40は、図39に示した半導体装置の回路図である。本実施形態において、半導体装置は電源パッド400、接地パッド402、及びI/Oパッド410を有している。電源パッド400は半導体装置に電源電圧(Vdd)を供給するためのパッドであり、接地パッド402は、半導体装置に接地電位を供給するためのパッドである。I/Oパッド410は、半導体装置に対する信号の入出力を行うためのパッドである。

【0142】

半導体装置には、内部回路300,302が形成されている。内部回路300及び内部回路302は、いずれもトランジスタ200を介して電源パッド400に接続している。すなわちトランジスタ200は、電源回路の一部を構成している。本実施形態では、内部回路300,302は互いに異なる電源電圧が供給されるため、互いに異なるトランジスタ200を介して、互いに異なる電源パッド400に接続している。

【0143】

また内部回路300,302は、I/Oパッド410に接続しており、I/Oパッド410を介して外部との間で信号の入出力を行う。内部回路300,302は、いずれも接地パッド402に接続している。そしてダイオード204は、I/Oパッド410と接地パッド402の間に、I/Oパッド410から接地パッド402に向かう方向が順方向となる向きに接続されている。すなわち、ダイオード204は内部回路300をESD等から保護するための保護素子であり、内部回路300に対して並列に接続されている。

【0144】

図41は、図39及び図40に示した半導体装置の全体の構成を示す平面図である。本図に示すように、半導体装置は、矩形を有している。そして各辺に沿って、複数の電源パッドが配置されている。これら電源パッドは、電源パッド400、接地パッド402、及びI/Oパッド410のいずれかである。

【0145】

また、平面視で、内部回路300、トランジスタ200、及び容量素子202が形成されている領域は、電源パッド400、接地パッド402、及びI/Oパッド410で囲まれている領域を内側に含んでいる。すなわち、電源パッド400、接地パッド402、及びI/Oパッド410は、内部回路300、トランジスタ200、及び容量素子202と重なっている。

【0146】

図42は、図39の変形例を示す図である。この図において、第1配線層150及び第2配線層170は、いずれもグローバル配線層104に形成されている。そして第4配線188及び第2配線186は、Al配線により形成されている。電源パッド400、接地パッド402、及びI/Oパッド410は、第2配線186,188と同一層に形成されている。

【0147】

本実施形態によれば、トランジスタ200を用いて内部回路300,302の電源回路を構成し、またダイオード204を内部回路300,302の保護素子として使用している。このため、内部回路300,302と、これらの電源回路及び保護素子を、平面視で重ねることができる。従って、半導体装置をさらに小型化することができる。

【0148】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【符号の説明】

【0149】

10 半導体基板

12 トランジスタ

14 トランジスタ

16 受動素子

20 素子分離膜

50 レジストパターン

52 レジストパターン

54 レジストパターン

100 多層配線層

102 ローカル配線層

104 グローバル配線層

140 拡散防止膜

150 第1配線層

152 ビア

154 第3配線

160 拡散防止膜

162 開口

165 保護絶縁膜

170 第2配線層

174 絶縁膜

181 ビア

182 配線

183 ビア

184 第1ビア

185 バリアメタル膜

186 第2配線

187 バリアメタル膜

188 第4配線

189 ビア

190 層間絶縁膜

192 ビア

194 配線

200 トランジスタ

201 トランジスタ

202 容量素子

204 ダイオード

210 第1配線

216 バリアメタル膜

218 ゲート電極

219 ゲート絶縁膜

220 半導体層

230 ハードマスク膜

232 レジストパターン

240 ハードマスク膜

242 レジストパターン

300 内部回路

302 内部回路

400 電源パッド

402 接地パッド

410 I/Oパッド

【技術分野】

【0001】

本発明は、多層配線層中に半導体素子を有する半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

特許文献1には、配線層中に半導体膜を形成し、この半導体膜及び配線層の配線を用いてトランジスタを形成することが記載されている。このトランジスタでは、半導体膜の下に位置する配線をゲート電極として使用し、かつ、配線層間の拡散防止膜をゲート絶縁膜として使用している。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−141230号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

トランジスタに求められる特性の一つに、閾値電圧がある。閾値電圧は、ゲート絶縁膜の膜厚のほかに、ゲート電極及びゲート絶縁膜の材料によっても制御できる。しかし、特許文献1に記載の技術では、多層配線層に含まれる配線をゲート電極として使用しているため、ゲート電極の材料を変えることはできなかった。

【課題を解決するための手段】

【0005】

本発明によれば、第1配線を有する第1配線層と、

前記第1配線層より上に形成され、第2配線を有する第2配線層と、

厚さ方向において前記第1配線と前記第2配線の間に位置し、前記第1配線とは異なる材料で形成され、前記第1配線に接続するゲート電極と、

前記ゲート電極上に位置するゲート絶縁膜と、

前記ゲート絶縁膜上に位置する半導体層と、

前記第2配線層に埋め込まれ、前記半導体層と前記第2配線とを接続する第1ビアと、

を備える半導体装置が提供される。

【0006】

本発明によれば、半導体層を用いた素子を配線層間に形成することができる。また、ゲート電極を、配線層の配線とは別工程で形成することができる。従って、ゲート電極の材料を、配線の材料以外の導電体にすることができる。

【0007】

本発明によれば、半導体基板上に、第1配線を有する第1配線層を形成する工程と、

前記第1配線層上に、ゲート電極、前記ゲート電極上に位置するゲート絶縁膜、及び前記ゲート絶縁膜上に位置する半導体層を形成する工程と、

前記第1配線層上及び前記半導体層上に、第2配線を有する第2配線層を形成する工程と、

を備え、

前記ゲート電極は前記第1配線に接続し、前記第2配線は前記半導体層に接続する半導体装置の製造方法が提供される。

【発明の効果】

【0008】

本発明によれば、半導体層を用いた素子を配線層間に形成することができ、かつ、ゲート電極の材料を、配線の材料以外の導電体にすることができる。

【図面の簡単な説明】

【0009】

【図1】第1の実施形態に係る半導体装置の構成を示す断面図である。

【図2】図1に示したトランジスタの平面図である。

【図3】図1に示した半導体装置の製造方法を示す断面図である。

【図4】図1に示した半導体装置の製造方法を示す断面図である。

【図5】図1に示した半導体装置の製造方法を示す断面図である。

【図6】図1に示した半導体装置の製造方法を示す断面図である。

【図7】第2の実施形態に係る半導体装置の構成を示す断面図である。

【図8】図7に示した半導体装置の平面図である。

【図9】図7に示した半導体装置の製造方法を示す断面図である。

【図10】図7に示した半導体装置の製造方法を示す断面図である。

【図11】第3の実施形態に係る半導体装置の構成を示す断面図である。

【図12】図11に示した半導体装置の製造方法を示す断面図である。

【図13】図11に示した半導体装置の製造方法を示す断面図である。

【図14】図11に示した半導体装置の製造方法を示す断面図である。

【図15】第4の実施形態に係る半導体装置の構成を示す断面図である。

【図16】図15に示した半導体装置の製造方法を示す断面図である。

【図17】図15に示した半導体装置の製造方法を示す断面図である。

【図18】第5の実施形態に係る半導体装置の構成を示す断面図である。

【図19】図18に示した半導体装置の製造方法を示す断面図である。

【図20】図18に示した半導体装置の製造方法を示す断面図である。

【図21】第6の実施形態に係る半導体装置の構成を示す断面図である。

【図22】図21に示した半導体装置の製造方法を示す断面図である。

【図23】図21に示した半導体装置の製造方法を示す断面図である。

【図24】第7の実施形態に係る半導体装置の構成を示す断面図である。

【図25】図24に示した半導体装置の製造方法を示す断面図である。

【図26】図24に示した半導体装置の製造方法を示す断面図である。

【図27】第8の実施形態に係る半導体装置の構成を示す断面図である。

【図28】図27に示した半導体装置の製造方法を示す断面図である。

【図29】図27に示した半導体装置の製造方法を示す断面図である。

【図30】図27に示した半導体装置の製造方法を示す断面図である。

【図31】図27に示した半導体装置の製造方法を示す断面図である。

【図32】第9の実施形態に係る半導体装置の製造方法を示す断面図である。

【図33】第9の実施形態に係る半導体装置の製造方法を示す断面図である。

【図34】第9の実施形態に係る半導体装置の製造方法を示す断面図である。

【図35】第10の実施形態に係る半導体装置の構成を示す断面図である。

【図36】図35に示した半導体装置の平面図である。

【図37】第11の実施形態に係る半導体装置の構成を示す断面図である。

【図38】第12の実施形態に係る半導体装置の構成を示す断面図である。

【図39】第13の実施形態に係る半導体装置の構成を示す断面図である。

【図40】図39に示した半導体装置の回路図である。

【図41】図39及び図40に示した半導体装置の全体の構成を示す平面図である。

【図42】図39の変形例を示す図である。

【発明を実施するための形態】

【0010】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0011】

(第1の実施形態)

図1は、第1の実施形態に係る半導体装置の構成を示す断面図である。この半導体装置は、第1配線層150、第2配線層170、第1配線210、ゲート電極218、ゲート絶縁膜219、半導体層220、第1ビア184、及び第2配線186を備えている。第2配線層170は、第1配線層150の上に位置している。第1配線層150及び第2配線層170は、多層配線層の少なくとも一部を構成している。この多層配線層は、シリコン基板などの半導体基板(本図では図示せず)上に形成されている。この半導体基板には、例えばトランジスタなどの素子が形成されている。これら半導体基板及びトランジスタについては、後述する別の実施形態において説明する。

【0012】

第1配線層150を構成する絶縁膜、及び第2配線層170を構成する絶縁膜174は、例えば酸化シリコン又は酸化シリコンより誘電率が低い(例えば比誘電率が2.7以下)低誘電率絶縁層である。低誘電率絶縁層は、例えばSiOC膜、SiOCH膜、もしくはSiLK(登録商標)等の炭素含有膜、HSQ(ハイドロジェンシルセスキオキサン)膜、MHSQ(メチル化ハイドロジェンシルセスキオキサン)膜、MSQ(メチルシルセスキオキサン)膜、またはこれらの多孔質膜である。

【0013】

第1配線層150は、拡散防止膜140上に形成されている。拡散防止膜140は、Si、C、及びNのうち少なくとも2種の元素を含む絶縁材料により形成されている。例えば拡散防止膜140は、SiN膜、SiCN膜、又はSiC膜である。なお、拡散防止膜140は、これらの少なくとも2つを積層した積層膜であってもよい。拡散防止膜140の厚さは、例えば10nm以上150nm以下である。

【0014】

第1配線層150を構成する絶縁層の表層には、第3配線154及び第1配線210が埋め込まれている。第3配線154及び第1配線210は同一工程で形成されている。このため、第3配線154及び第1配線210は、同一の深さを有しており、かつ同一の材料、例えば銅を主成分(95%以上)とする金属材料により形成されている。

【0015】

第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。ゲート電極218は、例えばTi、Ta、W、TiN、TaN、WN膜、CoもしくはWを含む化合物、これらのいずれか一つにC及びOの少なくとも一つを導入した膜、またはこれらの膜を複数種類積層した積層膜、を有している。

【0016】

ゲート電極218上には、ゲート絶縁膜219が形成されている。ゲート絶縁膜219の厚さは、例えば0.5nm以上50nm以下である。ゲート絶縁膜219は、例えば酸化シリコン膜、窒化シリコン膜、又はHf、Zr、Al、Ti、及びTaの少なくとも一つの酸化膜を有している。その他、上記絶縁膜に窒素、炭素を添加したものや金属シリケート物であっても良い。また、ゲート絶縁膜219は、これらの2種以上の膜の積層膜であってもよい。

【0017】

ゲート絶縁膜219上には、半導体層220が形成されている。半導体層220は、厚さが例えば10nm以上300nm以下である。半導体層220は、例えば、InGaZnO(IGZO)層、InZnO層、ZnO層、ZnAlO層、ZnCuO層、NiO層、SnO層、SnO2層、CuO層、Ta2O5層、またはTiO2層などの酸化物半導体層を有している。半導体層220は、上記した酸化物半導体層の単層構造であっても良いし、上記した酸化物半導体層と他の層の積層構造であっても良い。後者の例としては、IGZO/Al2O3/IGZO/Al2O3の積層膜がある。また半導体層220はポリシリコン層又はアモルファスシリコン層であってもよい。

【0018】

半導体層220には、ソース及びドレインが設けられている。半導体層220が酸化物半導体層である場合、ソース及びドレインは、例えば酸素欠陥を導入することにより形成されるが、不純物を導入することにより形成されても良い。あるいは、コンタクト形成時に半導体層220を改質させることにより形成されても良い。半導体層220がポリシリコン層やアモルファスシリコン層である場合、ソース及びドレインは不純物を導入することにより形成される。ゲート幅方向(すなわち図1の紙面に垂直な方向)におけるソース及びドレインの幅は、例えば50nm以上10μm以下である。

【0019】

半導体層220のうちソース及びドレインに挟まれている領域は、チャネル領域となる。平面視において、このチャネル領域は、ゲート電極218及びゲート絶縁膜219と重なっている。

【0020】

半導体層220の上には、ハードマスク膜230が設けられている。ハードマスク膜230は、半導体層220をエッチングにより選択的に残す際に用いられる。このため、ハードマスク膜230と半導体層220の平面形状は同一である。ハードマスク膜230は、半導体層220に対してエッチング選択比が取れる材料であれば良い。

【0021】

第2配線層170には、第4配線188及び2つの第2配線186が形成されている。第4配線188は、ビア189を介して第3配線154に接続しており、2つの第2配線186は、それぞれ第1ビア184を介して半導体層220のソース/ドレインに接続している。第1ビア184は、平面視で、ゲート電極218の中心を介して互いに逆側に配置されている。なお、2つの第1ビア184は、ゲート電極218の中心を基準に点対称に配置されている必要はない。例えば半導体層220のドレインに接続する第1ビア184は、半導体層220のソースに接続する第1ビア184よりも、ゲート電極218から離れていても良い。

【0022】

第2配線186及び第4配線188は、互いに同一の工程で形成されている。このため、第2配線186及び第4配線188は、互いに同一の材料、例えば銅を主成分(95%以上)とする金属材料により形成されている。

【0023】

本図に示す例において、各配線及びビアは、デュアルダマシン構造を有している。ただし、少なくとも一つの層の配線及びビアは、シングルダマシン構造を有していても良い。また第2配線層170は、Al配線等、金属膜をドライエッチングにより選択的に除去した構造を有していても良い。また、第2配線層170において、各配線及びビアを埋め込むための溝又は孔の側壁には、バリアメタル膜185,187が形成されている。これらバリアメタル膜185,187は、例えば、Ti、Ta、Ru、W、これらの窒化物又は酸化物などにより形成されている。なお、バリアメタル膜185,187は、これらの材料で構成された単層であってもよいし、2つ以上の層が積層したものであってもよい。積層構造の例としては、例えば、TiN(上層)/Ti(下層)、又は、Ta(上層)/TaN(下層)の積層構造がある。

【0024】

また、第1配線層150においても、各配線及びビアを埋め込むための溝又は孔の側壁にバリアメタル膜が形成されていてもよい。このバリアメタル膜も、第2配線層170のバリアメタル膜と同様の構造を有している。

【0025】

なお、各配線の材料と、各バリアメタル膜の材料の組み合わせは、上記した例に限定されない。例えば少なくとも一つの配線層は、Alにより形成されていても良い。

【0026】

上記した構成において、ゲート電極218、ゲート絶縁膜219、及び半導体層220は、トランジスタ200(第2トランジスタ)を構成している。すなわち本実施形態では、多層配線層中に能動素子が形成されている。トランジスタ200がNチャネル型のトランジスタである場合、半導体層220はInGaZnO(IGZO)層、InZnO層、ZnO層、ZnAlO層、ZnCuO層、SnO2層、Ta2O5層、またはTiO2層で形成される。またトランジスタ200がPチャネル型のトランジスタである場合、半導体層220はNiO2層、SnO層、ZnO層、ZnAlO層、ZnCuO層、またはCuO層で形成される。またNチャネル型のトランジスタ200とPチャネル型のトランジスタ200を同一の層に形成する場合、各トランジスタ200の半導体層220と同一の材料により形成しても良い。

【0027】

本実施形態において、第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。拡散防止膜160には、開口162が形成されている。ゲート電極218は、開口162の内側、及びその周囲に位置する拡散防止膜160上に形成されている。拡散防止膜160の構成は、拡散防止膜140の構成と同様である。またゲート絶縁膜219、半導体層220、及びハードマスク膜230も、ゲート電極218と同じ平面形状を有している。本図に示す例において、ゲート電極218は、拡散防止膜160よりも薄い。ただし、ゲート電極218は、拡散防止膜160と同程度の厚さであっても良いし、拡散防止膜160よりも厚くても良い。

【0028】

なお、ハードマスク膜230は、例えば拡散防止膜160と同一材料かつ同一の厚さの層である。ただし、ハードマスク膜230は、拡散防止膜160とは異なる材料により形成されていても良い。またハードマスク膜230は、拡散防止膜160と同一材料の層と、この層の上に他の層(例えばSiO2層又はSiOCH層)をこの順に積層した積層膜であってもよい。この場合、他の層の厚さは、例えば10nm以上200nm以下である。

【0029】

図2は、図1に示したトランジスタ200の平面図である。本図に示す例において、半導体層220のうち一つのトランジスタ200を形成している領域は、長方形を有している。2つの第1ビア184は、半導体層220の2つの短辺の近傍に接続している。

【0030】

図3〜図6は、図1に示した半導体装置の製造方法を示す断面図である。まず、図3(a)に示すように、半導体基板(図示せず)にトランジスタ等を形成し、さらに半導体基板上に下層の配線層(図示せず)を形成する。ついで、この配線層の上に拡散防止膜140を形成する。次いで、拡散防止膜140上に、第1配線層150を構成する絶縁膜を形成する。次いで、この絶縁膜に、ビアホール及び配線溝を形成する。

【0031】

次いで、必要に応じて、ビアホール及び配線溝の底面及び側壁、ならびに第1配線層150となる絶縁膜上に、バリアメタル膜(図示せず)を形成する。このバリアメタル膜は、例えばスパッタリング法を用いて形成される。次いで、ビアホール及び配線溝内、ならびに第1配線層150を構成する絶縁膜上に、金属膜を例えばめっき法を用いて形成する。次いで、第1配線層150を構成する絶縁膜上の金属膜及びバリアメタル膜を、例えばCMP法を用いて除去する。これにより、第1配線層150が形成される。第1配線層150には、第3配線154、ビア152、及び第1配線210が含まれている。なお、ビア152及び第3配線154は、シングルダマシン法により形成されても良いが、デュアルダマシン法により形成されても良い。

【0032】

次いで、第1配線層150上に、拡散防止膜160を形成する。拡散防止膜160は、例えばCVD法を用いて形成される。

【0033】

次いで図3(b)に示すように、拡散防止膜160上に、ハードマスク膜240を形成する。次いで、ハードマスク膜240上にレジストパターン242を形成する。次いで、レジストパターン242をマスクとして、ハードマスク膜240をエッチングする。これにより、ハードマスク膜240には開口が形成される。この開口は、拡散防止膜160のうち開口162が形成される領域の上に位置している。

【0034】

次いで図4(a)に示すように、ハードマスク膜240をマスクとして、拡散防止膜160をエッチングする。これにより、拡散防止膜160には開口162が形成される。この段階で、開口162の底面には、第1配線210が露出する。

【0035】

その後、図4(b)に示すように、ハードマスク膜240を除去する。

【0036】

次いで図5(a)に示すように、開口162内に位置する第1配線210上、及び拡散防止膜160の全面上に、ゲート電極218を形成する。ゲート電極218は、例えばスパッタリング法により形成されるが、CVD法により形成されても良い。次いでゲート電極218上に、ゲート絶縁膜219を形成する。ゲート絶縁膜219は、例えばCVD法又はスパッタリング法により形成される。

【0037】

次いで、ゲート絶縁膜219上に、半導体層220を形成する。半導体層220がInGaZnO、InZnO、ZnO、ZnAlO、ZnCuO、NiO、SnO、CuOなどの酸化物半導体層を含んでいる場合、半導体層220は、例えばスパッタリング法により形成される。このとき半導体基板は、400℃以下の温度に加熱される。また半導体層220がポリシリコン層やアモルファスシリコン層である場合、半導体層220は、例えばプラズマCVD法により形成される。

【0038】

次いで、半導体層220上に、ハードマスク膜230を形成する。例えばハードマスク膜230が拡散防止膜160と同一層を有している場合、この層は、拡散防止膜160と同一の方法により形成される。また、ハードマスク膜230がさらに酸化シリコン層を有している場合、この酸化シリコン層は、例えばCVD法を用いて形成される。

【0039】

次いで図5(b)に示すように、ハードマスク膜230上にレジストパターン232を形成する。

【0040】

次いで図6(a)に示すように、レジストパターン232をマスクとして、ハードマスク膜230をエッチングする。これにより、ハードマスク膜230は、所定のパターンに加工される。

【0041】

その後、図6(b)に示すように、レジストパターン232を除去する。次いで、ハードマスク膜230をマスクとして、半導体層220、ゲート絶縁膜219、及びゲート電極218をエッチングする。これにより、半導体層220、ゲート絶縁膜219、及びゲート電極218は、所定の形状に加工される。半導体層220は、ゲート絶縁膜219上、及びゲート絶縁膜219の周囲に位置する拡散防止膜160上にも形成される。またこの工程において、第3配線154上に位置する半導体層220、ゲート絶縁膜219、及びゲート電極218は除去される。

【0042】

次いで、半導体層220にソース及びドレインを形成する。次いで、拡散防止膜160上及びハードマスク膜230上に、第2配線層170を構成する絶縁膜174を形成する。次いで、絶縁膜174に、ビアホール及び配線溝を形成する。絶縁膜174にビアホールを形成する工程において、ハードマスク膜230及び拡散防止膜160は、エッチングストッパーとしても機能する。特にハードマスク膜230が拡散防止膜160と同一の材料の膜を同一の厚さで有している場合、ビアの底面に位置するハードマスク膜230及び拡散防止膜160を貫通させる工程の条件出しを容易に行える。

【0043】

なお、半導体層220にソース及びドレインを形成する工程は、ここで行われても良い。例えば、半導体層220のうちビアホールの底面に露出している領域に、還元性プラズマ(例:水素プラズマ)による処理、又は窒素含有プラズマ(例:アンモニアプラズマ)による処理を行うと、半導体層220にソース及びドレインが形成される。

【0044】

次いで、ビアホール及び配線溝の底面及び側壁、ならびに絶縁膜174上に、バリアメタル膜185,187を形成する。バリアメタル膜185,187は、例えばスパッタリング法を用いて形成される。次いで、ビアホール及び配線溝内、ならびに絶縁膜174上に、金属膜を例えばめっき法を用いて形成する。次いで、絶縁膜174上の金属膜及びバリアメタル膜を、例えばCMP法を用いて除去する。これにより、第2配線層170が形成される。第2配線層170には、第2配線186及び第4配線188、並びに第1ビア184及びビア189が含まれている。なお、上記したように、第2配線層170がAl配線により形成されていてもよい。この場合、第2配線層170には、電極パッドが含まれていてもよい。

このようにして、図1に示す半導体装置が形成される。

【0045】

次に、本実施形態の作用及び効果について説明する。本実施形態によれば、第1配線210の上にゲート電極218を形成している。このため、ゲート電極218を構成する導電材料を、第1配線210を構成する導電材料と異ならせることができる。このため、ゲート電極218を構成する導電材料を適切な材料にすることにより、ゲート電極218の仕事関数を調整し、トランジスタ200の閾値電圧を所望する電圧に設定することができる。また、トランジスタ200を、ノーマリーオフ型のトランジスタ及びノーマリーオン型のトランジスタのいずれにすることもできる。

【0046】

また、第1配線210の上面をゲート電極218で覆っているため、第1配線210上から拡散防止膜160を除去しても、第1配線210を構成する導電材料が第2配線層170に拡散することを抑制できる。

【0047】

また、拡散防止膜160とは別にゲート絶縁膜219を設けているため、ゲート絶縁膜219の厚さを拡散防止膜160と異ならせることができる。このため、ゲート絶縁膜219を薄くして、トランジスタ200のゲート容量を少なくすることができる。また、ゲート絶縁膜219には第1配線210のバリア膜としての機能が求められないため、ゲート絶縁膜219として使用することができる材料の選択肢が多くなる。

【0048】

(第2の実施形態)

図7は、第2の実施形態に係る半導体装置の構成を示す断面図である。図8は、図7に示した半導体装置の平面図である。本実施形態に係る半導体装置は、トランジスタ200のゲート電極218の形状を除いて、第1の実施形態に係る半導体装置と同様の構成である。

【0049】

本実施形態においてゲート電極218は、開口162内にのみ位置している。ゲート電極218の上面は、拡散防止膜160の上面と同一面(例えば同一平面)を形成している。

【0050】

ゲート絶縁膜219及び半導体層220は、ゲート電極218上、及びゲート電極218の周囲に位置する拡散防止膜160上に形成されている。すなわち、平面視で半導体層220はゲート電極218よりも広い。そして平面視で、2つの第1ビア184は、いずれも中心がゲート電極218とは重なっていない。すなわち第1ビア184は、ゲート電極218に対してオフセットされている。本図に示す例では、2つの第1ビア184は、全体がゲート電極218と重なっていない。

【0051】

図9及び図10は、図7に示した半導体装置の製造方法を示す断面図である。まず図9(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、拡散防止膜160、及び開口162を形成する。これらの形成方法は、第1の実施形態と同様である。

【0052】

次いで図9(b)に示すように、開口162内及び拡散防止膜160上に、ゲート電極218を形成する。このとき、ゲート電極218を、拡散防止膜160よりも厚く形成する。

【0053】

次いで図10(a)に示すように、拡散防止膜160上に位置するゲート電極218を、CMP法を用いて除去する。これにより、ゲート電極218は、開口162内にのみ位置する。また、ゲート電極218の上面は、拡散防止膜160の上面と同一面となる。

【0054】

次いで図10(b)に示すように、ゲート電極218上及び拡散防止膜160の全面上に、ゲート絶縁膜219、及び半導体層220を形成する。次いで、半導体層220上にハードマスク膜230を形成する。次いで、ハードマスク膜230上にレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、ハードマスク膜230をエッチングする。これにより、ハードマスク膜230は所定のパターンを有する。次いで、必要に応じてレジストパターンを除去する。そして、ハードマスク膜230をマスクとして、半導体層220及びゲート絶縁膜219をエッチングする。これにより、半導体層220及びゲート絶縁膜219は、ゲート電極218上及びその周囲にのみ残る。

【0055】

その後の工程は、第1の実施形態と同様である。

【0056】

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。また、ゲート絶縁膜219及び半導体層220の形状と、ゲート電極218の形状とを互いに異ならせることができる。これにより、ゲート電極218の端部を、半導体層220の端部から離すことができる。従って、ゲート電極218から半導体層220に向かって流れるリーク電流を少なくすることができる。これにより、ゲート電極218の信頼性が向上する。

【0057】

また、開口162の形状を変更することにより、ゲート電極218の形状を任意の形状に設定することができる。また、ハードマスク膜230のパターンを変更することにより、ゲート絶縁膜219及び半導体層220の形状を任意の形状に設定することができる。これにより、半導体層220のうちチャネルとなる領域のうちゲート電極218とオーバーラップする領域を、所望の形状及び面積にすることができる。これにより、ソース・ドレイン間の耐圧を制御することができる。

【0058】

(第3の実施形態)

図11は、第3の実施形態に係る半導体装置の構成を示す断面図である。本実施形態に係る半導体装置は、以下の点を除いて、第2の実施形態に係る半導体装置と同様の構成である。

【0059】

まず、拡散防止膜160の上には、保護絶縁膜165が形成されている。保護絶縁膜165は、例えば第2配線層170を構成する絶縁膜と同様の材料により形成されているが、異なる材料であってもよい。例えば第2配線層170が低誘電率膜である場合、保護絶縁膜165は、酸化シリコン膜であってもよい。

【0060】

開口162は、拡散防止膜160及び保護絶縁膜165に形成されている。ゲート電極218の上面は、保護絶縁膜165の上面と同一面(例えば同一平面)を形成している。ゲート絶縁膜219、半導体層220、及びハードマスク膜230の積層体は、ゲート電極218上、及びゲート電極218の周囲に位置する保護絶縁膜165上に形成されている。

【0061】

図12〜図14は、図11に示した半導体装置の製造方法を示す断面図である。まず図12(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、及び拡散防止膜160を形成する。これらの形成方法は、第2の実施形態と同様である。次いで、拡散防止膜160上に保護絶縁膜165を形成する。

【0062】

次いで図12(b)に示すように、保護絶縁膜165上にレジストパターン242を形成する。次いで、レジストパターン242をマスクとして保護絶縁膜165をエッチングする。これにより、保護絶縁膜165に開口162が形成される。ただしこの段階では、開口162は拡散防止膜160を貫通していない。

【0063】

次いで図13(a)に示すように、レジストパターン242を除去する。次いで、保護絶縁膜165をマスクとして拡散防止膜160をエッチングする。これにより、開口162は拡散防止膜160を貫通し、開口162の底面に第1配線210が露出する。

【0064】

次いで図13(b)に示すように、開口162内及び保護絶縁膜165上に、ゲート電極218を形成する。このとき、ゲート電極218の膜厚を、拡散防止膜160と保護絶縁膜165の積層膜の膜厚よりも大きくする。

【0065】

次いで図14(a)に示すように、保護絶縁膜165上に位置するゲート電極218を、CMP法を用いて除去する。これにより、ゲート電極218は、開口162内にのみ位置する。また、ゲート電極218の上面は、保護絶縁膜165の上面と同一面となる。

【0066】

次いで図14(b)に示すように、ゲート絶縁膜219、半導体層220、及びハードマスク膜230の積層膜を、保護絶縁膜165上に形成する。これらの形成方法は、第2の実施形態と同様である。

【0067】

その後の工程は、第2の実施形態と同様である。

【0068】

本実施形態によっても、第2の実施形態と同様の効果を得ることができる。また、拡散防止膜160は保護絶縁膜165によって覆われているため、ゲート電極218のうち不要な部分は、保護絶縁膜165上に形成される。このため、ゲート電極218のうち不要な部分をCMP法で除去する際に、拡散防止膜160がダメージを受けることを抑制できる。このため、第3配線154を構成する導電材料が第2配線層170内に拡散することを抑制できる。

【0069】

また、開口162を拡散防止膜160及び保護絶縁膜165の積層膜に形成しているため、第2の実施形態と比較して、ゲート電極218を厚くすることができる。従って、半導体層220を第1配線210から離すことができる。これにより、第1配線210がトランジスタ200の閾値電圧や信頼性などのトランジスタ特性に与える影響を小さくすることができる。

【0070】

(第4の実施形態)

図15は、第4の実施形態に係る半導体装置の構成を示す断面図である。本実施形態に係る半導体装置は、以下の点を除いて、第2の実施形態に係る半導体装置と同様の構成を有している。

【0071】

まず、拡散防止膜160の開口162の中には、バリアメタル膜216が形成されている。バリアメタル膜216は、例えばTi、Ta、W、TiN、TaN、WN膜、CoもしくはWを含む化合物、これらのいずれか一つにC及びOの少なくとも一つを導入した膜、又はこれらの膜を複数種類積層した積層膜、を有している。バリアメタル膜216は、例えば拡散防止膜160と同一の厚さを有しているが、拡散防止膜160よりも薄くても良い。

【0072】

ゲート電極218は、バリアメタル膜216上、及びその周囲に位置する拡散防止膜160上に形成されている。すなわち本実施形態では、ゲート電極218は、バリアメタル膜216を介して第1配線210に接続している。そしてゲート絶縁膜219、半導体層220及びハードマスク膜230の積層体は、ゲート電極218と同一の平面形状を有している。

【0073】

図16及び図17は、図15に示した半導体装置の製造方法を示す断面図である。まず図16(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、拡散防止膜160、及び開口162を形成する。これらの形成方法は、第2の実施形態と同様である。

【0074】

次いで図16(b)に示すように、開口162内及び拡散防止膜160上に、バリアメタル膜216を形成する。このとき、バリアメタル膜216の厚さを、拡散防止膜160よりも厚くする。

【0075】

次いで図17(a)に示すように、拡散防止膜160上に位置するバリアメタル膜216を、CMP法を用いて除去する。これにより、バリアメタル膜216は、開口162内にのみ位置する。また、バリアメタル膜216の上面は、拡散防止膜160の上面と同一面となる。

【0076】

次いでバリアメタル膜216上及び拡散防止膜160の全面上に、ゲート電極218、ゲート絶縁膜219、及び半導体層220を形成する。次いで、半導体層220上にハードマスク膜230を形成する。次いで、ハードマスク膜230上にレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、ハードマスク膜230をエッチングする。これにより、ハードマスク膜230は所定のパターンを有する。次いで、必要に応じてレジストパターンを除去する。そして、ハードマスク膜230をマスクとして、半導体層220、ゲート絶縁膜219、及びゲート電極218をエッチングする。これにより、半導体層220、ゲート絶縁膜219、及びゲート電極218は、バリアメタル膜216上及びその周囲にのみ残る。

【0077】

その後の工程は、第2の実施形態と同様である。

【0078】

本実施形態によっても、第1の実施形態と同様の効果を得ることができる。また、ゲート電極218と第1配線210の間に、バリアメタル膜216を形成している。このため、第1配線210を構成する導電材料が第2配線層170内に拡散することを、さらに抑制できる。

【0079】

また、ゲート電極218の材料を選択するときに、拡散防止能力を考慮する必要がなくなる。従って、ゲート電極218の材料の選択肢が増える。また、ゲート電極218を薄くすることも可能となる。例えばゲート電極218として、Ti、Ta、Al、Hf、W、Ni、Co、Ptおよびこれらの化合物(窒化物、炭化物、酸素添加物、複合金属およびシリサイド)を使用することができる。

【0080】

(第5の実施形態)

図18は、第5の実施形態に係る半導体装置の構成を示す断面図である。本実施形態に係る半導体装置は、保護絶縁膜165を有している点を除いて、第4の実施形態に係る半導体装置と同様の構成である。

【0081】

保護絶縁膜165の構成は、第3の実施形態と同様である。開口162は、拡散防止膜160及び保護絶縁膜165の積層体に形成されている。バリアメタル膜216の上面は、保護絶縁膜165の上面と同一面を形成されている。そして、ゲート電極218、ゲート絶縁膜219、半導体層220、及びハードマスク膜230の積層体は、バリアメタル膜216及びその周囲に位置する保護絶縁膜165上に形成されている。

【0082】

図19及び図20は、図18に示した半導体装置の製造方法を示す断面図である。まず19(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、拡散防止膜160、保護絶縁膜165、及び開口162を形成する。これらの形成方法は、第3の実施形態と同様である。

【0083】

次いで図19(b)に示すように、開口162内及び保護絶縁膜165上に、バリアメタル膜216を形成する。このとき、バリアメタル膜216の厚さを、拡散防止膜160と保護絶縁膜165の積層膜よりも厚くする。

【0084】

次いで、保護絶縁膜165上に位置するバリアメタル膜216を、CMP法を用いて除去する。これにより、バリアメタル膜216は、開口162内にのみ位置する。また、バリアメタル膜216の上面は、保護絶縁膜165の上面と同一面となる。

【0085】

次いで図20に示すように、バリアメタル膜216上及びその周囲に位置する保護絶縁膜165上に、ゲート電極218、ゲート絶縁膜219、半導体層220、及びハードマスク膜230を形成する。これらの形成方法は、第4の実施形態と同様である。

【0086】

その後の工程は、第4の実施形態と同様である。

【0087】

本実施形態によっても、第4の実施形態と同様の効果を得ることができる。また、保護絶縁膜165を形成しているため、第3の実施形態と同様の効果も得ることができる。

【0088】

(第6の実施形態)

図21は、第6の実施形態に係る半導体装置の構成を示す断面図である。本実施形態に係る半導体装置は、以下の点を除いて、第5の実施形態に係る半導体装置と同様の構成である。

【0089】

まず、バリアメタル膜216は、拡散防止膜160及び保護絶縁膜165の積層膜より薄い。またゲート電極218は、開口162内に埋め込まれている。ゲート電極218の上面は、保護絶縁膜165の上面と同一面を形成している。そしてゲート絶縁膜219、半導体層220、及びハードマスク膜230の積層体は、ゲート電極218上、及びゲート電極218の周囲に位置する保護絶縁膜165上に形成されている。ゲート電極218の厚さ、及びバリアメタル膜216の厚さは、それぞれに求められる機能に基づいて設計される。このため、拡散防止膜160と保護絶縁膜165の境界と、バリアメタル膜216とゲート電極218の境界は、互いに同じ高さに位置する場合もあるし、異なる場合もある。

【0090】

図22及び図23は、図21に示した半導体装置の製造方法を示す断面図である。まず図22(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、拡散防止膜160、保護絶縁膜165、開口162、及びバリアメタル膜216を形成する。これらの形成方法は、第5の実施形態と同様である。この段階では、バリアメタル膜216の上面は、保護絶縁膜165の上面と同一面を形成している。

【0091】

次いで図22(b)に示すように、バリアメタル膜216をエッチバックする。これにより、バリアメタル膜216の上面は、保護絶縁膜165の上面よりも低くなる。

【0092】

次いで図23(a)に示すように、バリアメタル膜216上及び保護絶縁膜165上に、ゲート電極218を形成する。次いで、バリアメタル膜216上に位置するゲート電極218を、CMP法を用いて除去する。これにより、開口162のうちバリアメタル膜216上に位置する部分には、ゲート電極218が埋め込まれる。ゲート電極218の上面は、保護絶縁膜165の上面と同一面を形成している。

【0093】

次いで図23(b)に示すように、ゲート電極218及びその周囲に位置する保護絶縁膜165上に、ゲート絶縁膜219、半導体層220、及びハードマスク膜230の積層体を形成する。これらの形成方法は、第3の実施形態と同様である。

【0094】

その後の工程は、第3の実施形態と同様である。

【0095】

本実施形態によっても、第5の実施形態と同様の効果を得ることができる。また、ゲート電極218が開口162内に埋め込まれているため、第3の実施形態と同様の効果を得ることができる。

【0096】

(第7の実施形態)

図24は、第7の実施形態に係る半導体装置の構成を示す断面図である。本実施形態に係る半導体装置は、トランジスタ200の他にトランジスタ201を有している点を除いて、第4の実施形態に係る半導体装置と同様の構成である。

【0097】

トランジスタ201は、トランジスタ200と同一層に形成されており、ゲート電極218、ゲート絶縁膜219、及び半導体層220の材料の組み合わせを除いて、トランジスタ200と同様の構成を有している。例えばトランジスタ200とトランジスタ201のチャネルの導電型が互いに同一である場合、トランジスタ200とトランジスタ201との間でゲート電極218、ゲート絶縁膜219、及び半導体層220の材料の組み合わせを異ならせることにより、トランジスタ200とトランジスタ201の閾値電圧を変えることができる。また、トランジスタ200をNチャネル型のトランジスタとして、トランジスタ201をPチャネル型のトランジスタとすることもできる。

【0098】

図25及び図26は、図24に示した半導体装置の製造方法を示す断面図である。まず図25(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、拡散防止膜160、及び開口162を形成する。これらの工程は、第1配線210及び開口162を2箇所に形成する点を除いて、第4の実施形態と同様である。

【0099】

次いで図25(b)に示すように、2箇所の開口162それぞれの中に、バリアメタル膜216を埋め込む。これらの形成方法も、第4の実施形態と同様である。

【0100】

次いで図26(a)に示すように、拡散防止膜160上及びバリアメタル膜216上に、トランジスタ200を構成するゲート電極218、ゲート絶縁膜219、及び半導体層220を形成する。次いで、半導体層220上に、トランジスタ200を構成するハードマスク膜230を形成する。次いで、このハードマスク膜230をマスクとして、半導体層220、ゲート絶縁膜219、及びゲート電極218をエッチングする。これにより、トランジスタ200のゲート電極218、ゲート絶縁膜219、及び半導体層220が形成される。

【0101】

次いで図26(b)に示すように、拡散防止膜160上、及びトランジスタ201が形成されるバリアメタル膜216上に、トランジスタ201を構成するゲート電極218、ゲート絶縁膜219、及び半導体層220を形成する。次いで、半導体層220上に、トランジスタ201を構成するハードマスク膜230を形成する。次いで、このハードマスク膜230をマスクとして、半導体層220、ゲート絶縁膜219、及びゲート電極218をエッチングする。これにより、トランジスタ201のゲート電極218、ゲート絶縁膜219、及び半導体層220が形成される。

【0102】

この後の工程は、第4の実施形態と同様である。

【0103】

本実施形態によっても、第4の実施形態と同様の効果を得ることができる。また、互いに特性が異なるトランジスタ200及びトランジスタ201を同一層に形成することができる。

【0104】

(第8の実施形態)

図27は、第8の実施形態に係る半導体装置の構成を示す断面図である。本実施形態に係る半導体装置は、トランジスタ200,201が、第6の実施形態に係るトランジスタ200と同様の構成を有している点を除いて、第7の実施形態に係る半導体装置と同様の構成である。

【0105】

図28〜図31は、図27に示した半導体装置の製造方法を示す断面図である。まず図28(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、拡散防止膜160、保護絶縁膜165、及び開口162を形成する。これらの工程は、第1配線210及び開口162を2箇所に形成する点を除いて、第6の実施形態と同様である。

【0106】

次いで図28(b)に示すように、2つの開口162内に、バリアメタル膜216を埋め込む。この工程も、第6の実施形態と同様である。この段階において、2つのバリアメタル膜216の上面は、保護絶縁膜165の上面と同一面を形成している。

【0107】

次いで図29(a)に示すように、保護絶縁膜165上及びバリアメタル膜216上にレジストパターン50を形成する。レジストパターン50は、トランジスタ200が形成されるバリアメタル膜216上に、開口を有している。次いで、レジストパターン50をマスクとしてバリアメタル膜216をエッチバックする。これにより、トランジスタ200が形成されるバリアメタル膜216の上面は、保護絶縁膜165の上面よりも低くなる。

【0108】

その後、図29(b)に示すように、レジストパターン50を除去する。次いで、トランジスタ200が形成されるバリアメタル膜216上に、トランジスタ200のゲート電極218(218a)を埋め込む。この工程は、第6の実施形態と同様である。

【0109】

次いで図30(a)に示すように、保護絶縁膜165上、トランジスタ200のゲート電極218(218a)上、及びトランジスタ201のバリアメタル膜216上に、レジストパターン52を形成する。レジストパターン52は、トランジスタ201が形成されるバリアメタル膜216上に、開口を有している。次いで、レジストパターン52をマスクとしてバリアメタル膜216をエッチバックする。これにより、トランジスタ201が形成されるバリアメタル膜216の上面は、保護絶縁膜165の上面よりも低くなる。

【0110】

その後、図30(b)に示すように、レジストパターン52を除去する。次いで、トランジスタ201が形成されるバリアメタル膜216上に、トランジスタ201のゲート電極218(218b)を埋め込む。トランジスタ200のゲート電極218aと、トランジスタ201のゲート電極218bは、別の材料により形成されていても良い。この工程は、トランジスタ200のゲート電極218(218a)を形成する工程と同様である。

【0111】

次いで図31(a)に示すように、拡散防止膜160上及びゲート電極218(218a)上に、トランジスタ200を構成するゲート絶縁膜219及び半導体層220を形成する。次いで、半導体層220上に、トランジスタ200を構成するハードマスク膜230を形成する。次いで、このハードマスク膜230をマスクとして、半導体層220及びゲート絶縁膜219をエッチングする。これにより、トランジスタ200のゲート絶縁膜219及び半導体層220が形成される。

【0112】

次いで図31(b)に示すように、拡散防止膜160上、及びトランジスタ201のゲート電極218(218b)上に、トランジスタ201を構成するゲート絶縁膜219及び半導体層220を形成する。次いで、半導体層220上に、トランジスタ201を構成するハードマスク膜230を形成する。次いで、このハードマスク膜230をマスクとして、半導体層220及びゲート絶縁膜219をエッチングする。これにより、トランジスタ201のゲート絶縁膜219及び半導体層220が形成される。

【0113】

この後の工程は、第6の実施形態と同様である。

【0114】

本実施形態によっても、第6の実施形態と同様の効果を得ることができる。また、互いに特性が異なるトランジスタ200及びトランジスタ201を同一層に形成することができる。

【0115】

なお、トランジスタ200及びトランジスタ201は、第1〜第3、第5の実施形態のいずれかと同様の構造を有していても良い。

【0116】

(第9の実施形態)

図32、図33、及び図34は、第9の実施形態に係る半導体装置の製造方法を示す断面図である。本実施形態によって製造される半導体装置の構成は、第8の実施形態に示した半導体装置の構成と同様である。

【0117】

まず、図32(a)に示すように、拡散防止膜140、第1配線層150、ビア152、第3配線154、第1配線210、拡散防止膜160、及び2つの開口162を形成し、さらに2つの開口162のそれぞれにバリアメタル膜216を埋め込む。これらの形成方法は、第8の実施形態と同様である。

【0118】

次いで図32(b)に示すように、2つのバリアメタル膜216を同時にエッチバックする。これにより、2つのバリアメタル膜216の上面は、いずれも保護絶縁膜165の上面よりも低くなる。

【0119】

次いで図33(a)に示すように、2つのバリアメタル膜216上及び保護絶縁膜165上に、ゲート電極218(218a)を形成する。次いで、保護絶縁膜165上に位置するゲート電極218(218a)を、CMP法を用いて除去する。これにより、2つの開口162内には、いずれもゲート電極218(218a)が埋め込まれる。

【0120】

次いで図33(b)に示すように、トランジスタ200となるゲート電極218(218a)を、レジストパターン54で覆う。ただしレジストパターン54は、トランジスタ201となるバリアメタル膜216の上方には形成されていない。次いで、レジストパターン54をマスクとして、トランジスタ201となるバリアメタル膜216上のゲート電極218(218a)を、エッチングにより除去する。

【0121】

次いで図34(a)に示すように、トランジスタ201となるバリアメタル膜216上、保護絶縁膜165上、及びトランジスタ200のゲート電極218(218a)上に、ゲート電極218(218b)を形成する。次いで図34(b)に示すように、保護絶縁膜165上、及びトランジスタ200のゲート電極218(218a)上に位置するゲート電極218(218b)を、CMP法により除去する。

【0122】

このようにして、トランジスタ200となる開口162には、バリアメタル膜216及びゲート電極218(218a)が埋め込まれ、トランジスタ201となる開口162には、バリアメタル膜216及びゲート電極218(218b)が埋め込まれる。その後の工程は、第8の実施形態と同様である。

【0123】

本実施形態によっても、第8の実施形態と同様の効果を得ることができる。また第8の実施形態と比較して、レジストパターンの形成回数を少なくすることができるため、半導体装置の製造工程数を少なくすることができる。

【0124】

(第10の実施形態)

図35は、第10の実施形態に係る半導体装置の構成を示す断面図である。図36は、図35に示した半導体装置の平面図である。この半導体装置において、トランジスタ200を構成する各層の積層構造は、第3の実施形態と同様である。ただし、ゲート電極218の平面レイアウトは櫛歯形状である。そして半導体層220のうち各ゲート電極218に挟まれている部分の上には、ソース配線となる第2配線186(186b)と、ドレイン配線となる第2配線186(186a)が、交互に延伸している。そして一つの第2配線186について、複数の第1ビア184が形成されている。これら2つの第2配線186の平面レイアウトも、櫛歯形状である。すなわち、本実施形態に係るトランジスタ200は、櫛歯型のレイアウトを有している。

【0125】

本実施形態によっても、第3の実施形態と同様の効果を得ることができる。また、トランジスタ200が櫛歯型のレイアウトを有しており、実効的なチャネル幅を広く確保できるため、トランジスタ200のオン電流を大きくすることができる。

【0126】

なお、本実施形態において、トランジスタ200を構成する各層の積層構造は、第1〜第2の実施形態、及び第4〜第6の実施形態のいずれかに示した構造であっても良い。

【0127】

(第11の実施形態)

図37は、第11の実施形態に係る半導体装置の構成を示す断面図である。この半導体装置は、トランジスタ200の代わりに容量素子202を有している点を除いて、第5の実施形態に係る半導体装置と同様の構成である。

【0128】

容量素子202はMIS型の容量素子であり、トランジスタ200におけるソース、チャネル領域、及びドレインそれぞれに接続する第1ビア184を、同一の第2配線186に接続した構成を有している。このため、容量素子202を、トランジスタ200と同一の方法により形成することができる。

【0129】

本実施形態によれば、多層配線層中に、MIS型の容量素子202を形成することができる。そして、第5の実施形態に示したトランジスタ200と、本実施形態に係る容量素子202を、同一層に、同一工程で形成することができる。

【0130】

なお、本実施形態において、容量素子202を構成する各層の積層構造は、第1〜第4の実施形態、及び第6の実施形態のいずれかに示した構造であっても良い。

【0131】

(第12の実施形態)

図38は、第12の実施形態に係る半導体装置の構成を示す断面図である。この半導体装置は、トランジスタ200の代わりにダイオード204を有している点を除いて、第5の実施形態に係る半導体装置と同様の構成である。

【0132】

ダイオード204は、第5の実施形態におけるトランジスタ200のゲート電極218と、半導体層220のソースに接続する配線182とを、ビア183を介して互いに短絡した構成を有している。ビア183は、ビア181と同一工程で形成されている。すなわちビア181,183及び配線182は、デュアルダマシン構造を有している。

【0133】

本実施形態によれば、多層配線層中に、ダイオード204を形成することができる。そして、第5の実施形態に示したトランジスタ200及び第11の実施形態に示した容量素子202の少なくとも一方と、本実施形態に係るダイオード204を、同一層に、同一工程で形成することができる。

【0134】

なお、本実施形態において、ダイオード204を構成する各層の積層構造は、第1〜第4の実施形態、及び第6の実施形態のいずれかに示した構造であっても良い。

【0135】

(第13の実施形態)

図39は、第13の実施形態に係る半導体装置の構成を示す断面図である。この半導体装置は、半導体基板10及び多層配線層100を備えている。

【0136】

半導体基板10には、素子分離膜20及びトランジスタ12,14(第1のトランジスタ)が形成されている。さらに、素子分離膜20上には、受動素子(例えば抵抗素子)16が形成されている。受動素子16は、トランジスタ12のゲート電極と同一工程で形成されている。

【0137】

多層配線層100には、第1〜第6の実施形態に示したトランジスタ200、第11の実施形態に示した容量素子202、及び第12の実施形態に示したダイオード204の少なくとも一つが形成されている。本図に示す例では、第1の実施形態(図1)に示したトランジスタ200が形成されている。トランジスタ200の平面形状は、トランジスタ12,14の平面形状よりも大きい。なお、図示していないが、この半導体装置は、トランジスタ200と同一層に、ダイオード204を有している。

【0138】

本図に示す例では、第1配線層150は、回路を形成するための配線層であるローカル配線層102の最上層に位置しており、第2配線層170は、電源配線及び接地配線を引き回すための配線であるグローバル配線層104の最下層に位置している。第2配線層170の上には、層間絶縁膜190を介して配線194が形成されている。配線194はAl配線であり、ビア192を介して第2配線層170の配線(例えば第4配線188)に接続している。配線194は、下面及び上面に、バリアメタル膜が形成されている。このバリアメタル膜は、Tiを主成分とする金属膜、この金属の窒化膜、又はこれら金属膜及び窒化膜の積層膜である。なお、配線194と同一層には、電極パッド(後述する電源パッド400、接地パッド402、及び信号用のI/Oパッド410)が形成されている。

【0139】

なお、ローカル配線層102を構成する各配線層は、グローバル配線層104を構成する配線層よりも薄い。そしてローカル配線層102の各配線も、グローバル配線層104の各配線よりも薄い。

【0140】

トランジスタ12のドレイン(又はソース)は、ローカル配線層102に形成された配線及びビアを介して、第3配線154に接続している。トランジスタ14のドレインは、ローカル配線層102に形成された配線及びビアを介して、ゲート電極218に接続している。トランジスタ12,14は、後述する内部回路300,302を構成している。なお、トランジスタ14は、平面視においてトランジスタ200の半導体層220と重なっている。

【0141】

図40は、図39に示した半導体装置の回路図である。本実施形態において、半導体装置は電源パッド400、接地パッド402、及びI/Oパッド410を有している。電源パッド400は半導体装置に電源電圧(Vdd)を供給するためのパッドであり、接地パッド402は、半導体装置に接地電位を供給するためのパッドである。I/Oパッド410は、半導体装置に対する信号の入出力を行うためのパッドである。

【0142】

半導体装置には、内部回路300,302が形成されている。内部回路300及び内部回路302は、いずれもトランジスタ200を介して電源パッド400に接続している。すなわちトランジスタ200は、電源回路の一部を構成している。本実施形態では、内部回路300,302は互いに異なる電源電圧が供給されるため、互いに異なるトランジスタ200を介して、互いに異なる電源パッド400に接続している。

【0143】

また内部回路300,302は、I/Oパッド410に接続しており、I/Oパッド410を介して外部との間で信号の入出力を行う。内部回路300,302は、いずれも接地パッド402に接続している。そしてダイオード204は、I/Oパッド410と接地パッド402の間に、I/Oパッド410から接地パッド402に向かう方向が順方向となる向きに接続されている。すなわち、ダイオード204は内部回路300をESD等から保護するための保護素子であり、内部回路300に対して並列に接続されている。

【0144】

図41は、図39及び図40に示した半導体装置の全体の構成を示す平面図である。本図に示すように、半導体装置は、矩形を有している。そして各辺に沿って、複数の電源パッドが配置されている。これら電源パッドは、電源パッド400、接地パッド402、及びI/Oパッド410のいずれかである。

【0145】

また、平面視で、内部回路300、トランジスタ200、及び容量素子202が形成されている領域は、電源パッド400、接地パッド402、及びI/Oパッド410で囲まれている領域を内側に含んでいる。すなわち、電源パッド400、接地パッド402、及びI/Oパッド410は、内部回路300、トランジスタ200、及び容量素子202と重なっている。

【0146】

図42は、図39の変形例を示す図である。この図において、第1配線層150及び第2配線層170は、いずれもグローバル配線層104に形成されている。そして第4配線188及び第2配線186は、Al配線により形成されている。電源パッド400、接地パッド402、及びI/Oパッド410は、第2配線186,188と同一層に形成されている。

【0147】

本実施形態によれば、トランジスタ200を用いて内部回路300,302の電源回路を構成し、またダイオード204を内部回路300,302の保護素子として使用している。このため、内部回路300,302と、これらの電源回路及び保護素子を、平面視で重ねることができる。従って、半導体装置をさらに小型化することができる。

【0148】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【符号の説明】

【0149】

10 半導体基板

12 トランジスタ

14 トランジスタ

16 受動素子

20 素子分離膜

50 レジストパターン

52 レジストパターン

54 レジストパターン

100 多層配線層

102 ローカル配線層

104 グローバル配線層

140 拡散防止膜

150 第1配線層

152 ビア

154 第3配線

160 拡散防止膜

162 開口

165 保護絶縁膜

170 第2配線層

174 絶縁膜

181 ビア

182 配線

183 ビア

184 第1ビア

185 バリアメタル膜

186 第2配線

187 バリアメタル膜

188 第4配線

189 ビア

190 層間絶縁膜

192 ビア

194 配線

200 トランジスタ

201 トランジスタ

202 容量素子

204 ダイオード

210 第1配線

216 バリアメタル膜

218 ゲート電極

219 ゲート絶縁膜

220 半導体層

230 ハードマスク膜

232 レジストパターン

240 ハードマスク膜

242 レジストパターン

300 内部回路

302 内部回路

400 電源パッド

402 接地パッド

410 I/Oパッド

【特許請求の範囲】

【請求項1】

第1配線を有する第1配線層と、

前記第1配線層より上に形成され、第2配線を有する第2配線層と、

厚さ方向において前記第1配線と前記第2配線の間に位置し、前記第1配線とは異なる材料で形成され、前記第1配線に接続するゲート電極と、

前記ゲート電極上に位置するゲート絶縁膜と、

前記ゲート絶縁膜上に位置する半導体層と、

前記第2配線層に埋め込まれ、前記半導体層と前記第2配線とを接続する第1ビアと、

を備える半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

2つの前記第2配線を備え、

前記2つの第2配線は、互いに異なる前記第1ビアを介して、前記半導体層に接続しており、

前記2つの第1ビアは、平面視で前記ゲート電極の中心を介して互いに逆側に配置されている半導体装置。

【請求項3】

請求項2に記載の半導体装置において、

平面視で、前記半導体層は前記ゲート電極よりも広く、

前記2つの第1ビアの中心は、前記ゲート電極と重なっていない半導体装置。

【請求項4】

請求項1〜3のいずれか一項に記載の半導体装置において、

前記第1配線層に形成された第3配線と、

前記第2配線層に形成された第4配線と、

前記第2配線層に埋め込まれ、前記第3配線及び前記第4配線を接続する第2ビアと、

を備える半導体装置。

【請求項5】

請求項4に記載の半導体装置において、

前記第3配線は、前記第1配線と同一構造を有しており、

前記第4配線は、前記第2配線と同一構造を有しており、

前記第2ビアは、前記第1ビアと同一構造を有している半導体装置。

【請求項6】

請求項1〜5のいずれか一項に記載の半導体装置において、

前記第1配線層上に形成された拡散防止膜と、

前記拡散防止膜に形成され、前記第1配線上に位置する開口と、

前記開口内に位置し、前記ゲート電極と前記第1配線とを接続するバリアメタル膜と、

を備える半導体装置。

【請求項7】

請求項1〜5のいずれか一項に記載の半導体装置において、

前記第1配線層と前記第2配線層の間に形成された拡散防止膜と、

前記拡散防止膜に形成され、前記第1配線上に位置する開口と、

を備え、

前記ゲート電極は、少なくとも前記開口内に形成されている半導体装置。

【請求項8】

請求項7に記載の半導体装置において、

前記ゲート電極は、前記開口内、及び前記開口の周囲に位置する前記拡散防止膜上に形成されている半導体装置。

【請求項9】

請求項7に記載の半導体装置において、

前記ゲート電極は、前記開口内にのみ位置している半導体装置。

【請求項10】

請求項9に記載の半導体装置において、

前記ゲート電極の上面は、前記拡散防止膜の上面と同一面を形成している半導体装置。

【請求項11】

請求項7〜10のいずれか一項に記載の半導体装置において、

前記開口内に位置し、前記ゲート電極と前記第1配線とを接続するバリアメタル膜を備える半導体装置。

【請求項12】

請求項6〜11のいずれか一項に記載の半導体装置において、

前記拡散防止膜の上に位置する保護絶縁膜を備え、

前記開口は、前記保護絶縁膜及び前記拡散防止膜に形成されている半導体装置。

【請求項13】

請求項12に記載の半導体装置において、

前記保護絶縁膜は、酸化シリコンよりも誘電率が低い材料、またはこの材料の多孔質膜により形成されている半導体装置。

【請求項14】

請求項1〜13のいずれか一項に記載の半導体装置において、

前記第1配線層及び前記第2配線層は、基板上に形成されており、

前記基板に形成された第1トランジスタを備える半導体装置。

【請求項15】

請求項14に記載の半導体装置において、

平面視において、前記第1トランジスタは、前記半導体層と重なっている半導体装置。

【請求項16】

請求項2に記載の半導体装置において、

前記ゲート電極、前記ゲート絶縁膜、及び前記半導体層は第2トランジスタを形成している半導体装置。

【請求項17】

請求項16に記載の半導体装置において、

少なくとも2つの前記第2トランジスタを備え、

前記少なくとも2つの第2トランジスタは、前記ゲート電極、前記ゲート絶縁膜、及び前記半導体層の材料の組み合わせが互いに異なる半導体装置。

【請求項18】

請求項17に記載の半導体装置において、

前記少なくとも2つの第2トランジスタは、チャネルの導電型が互いに同一であり、閾値電圧が互いに異なる半導体装置。

【請求項19】

請求項16〜18のいずれか一項に記載の半導体装置において、

内部回路と、

前記多層配線層の最上層の配線層に形成され、前記内部回路に電源電圧を供給する電源パッドと、

を備え、

前記内部回路は、前記第2トランジスタを介して前記電源パッドに接続している半導体装置。

【請求項20】

請求項1〜15のいずれか一項に記載の半導体装置において、

前記半導体層は、ソース及びドレインを有しており、

前記ソースは、前記ゲート電極に短絡しており、

前記ソース、前記ドレイン、前記ゲート絶縁膜、及び前記ゲート電極は、ダイオードを形成している半導体装置。

【請求項21】

請求項20に記載の半導体装置において、

内部回路と、

前記多層配線層の最上層の配線層に形成され、前記内部回路に信号を供給するI/Oパッドと、

前記最上層の配線層に形成され、前記内部回路に接地電位を供給する接地パッドと、

を備え、

前記ダイオードは、前記I/Oパッドと前記接地パッドの間に、前記I/Oパッドから前記接地パッドに向かう方向が順方向となる向きに接続されている半導体装置。

【請求項22】

請求項1〜15のいずれか一項に記載の半導体装置において、

前記ゲート電極、前記ゲート絶縁膜、及び前記半導体層は容量素子を形成している半導体装置。

【請求項23】

請求項1〜22のいずれか一項に記載の半導体装置において、

前記第1配線はCu配線であり、

前記ゲート電極は、Ti、Ta、W、TiN、TaN、WN膜、CoもしくはWを含む化合物、これらのいずれか一つにC及びOの少なくとも一つを導入した膜、またはこれらの膜を複数種類積層した積層膜を有している半導体装置。

【請求項24】

請求項1〜23のいずれか一項に記載の半導体装置において、

前記ゲート絶縁膜は、酸化シリコン膜、窒化シリコン膜、またはHf、Zr、Al、Ti、並びにTaの少なくとも一つの酸化膜を有している半導体装置。

【請求項25】

請求項1〜24のいずれか一項に記載の半導体装置において、

前記半導体層は、酸化物半導体層である半導体装置。

【請求項26】

請求項25に記載の半導体装置において、

前記酸化物半導体層は、InGaZnO層、InZnO層、ZnO層、ZnAlO層、ZnCuO層、NiO、NiO2、SnO、またはCuOである半導体装置。

【請求項27】

請求項1〜26のいずれか一項に記載の半導体装置において、

前記半導体層上に形成され、平面形状が前記半導体層と同一であるハードマスク膜を備える半導体装置。

【請求項28】

請求項27に記載の半導体装置において、

前記ハードマスク膜は、前記拡散防止膜と同一材料であり、かつ前記拡散防止膜と同一の厚さの層を有している半導体装置。

【請求項29】

半導体基板上に、第1配線を有する第1配線層を形成する工程と、

前記第1配線層上に、第1ゲート電極、前記第1ゲート電極上に位置する第1ゲート絶縁膜、及び前記第1ゲート絶縁膜上に位置する第1半導体層を形成する工程と、

前記第1配線層上及び前記第1半導体層上に、第2配線を有する第2配線層を形成する工程と、

を備え、

前記第1ゲート電極は前記第1配線に接続し、前記第2配線は前記第1半導体層に接続する半導体装置の製造方法。

【請求項30】

請求項29に記載の半導体装置の製造方法において、

前記第1配線層を形成する工程と、前記第1ゲート電極、前記第1ゲート絶縁膜、及び前記第1半導体層を形成する工程の間に、

前記第1配線層上に拡散防止膜を形成する工程と、

前記拡散防止膜に、前記第1配線上に位置する第1開口を形成する工程と、

を備え、

前記第1ゲート電極を形成する工程において、前記第1ゲート電極を、平面視で前記第1開口と重ねることにより、前記第1ゲート電極と前記第1配線とを接続する半導体装置の製造方法。

【請求項31】

請求項30に記載の半導体装置の製造方法において、

前記第1開口を形成する工程と、前記第1ゲート電極を形成する工程の間に、前記第1開口内にバリアメタル膜を形成する工程を有する半導体装置の製造方法。

【請求項32】

請求項31に記載の半導体装置の製造方法において、

前記第1開口内に前記バリアメタル膜を埋め込む工程は、

前記第1開口内及び前記拡散防止膜上にバリアメタル膜を形成する工程と、

前記拡散防止膜上に位置するバリアメタル膜を、CMP法を用いて除去する工程と、

を有する半導体装置の製造方法。

【請求項33】

請求項32に記載の半導体装置の製造方法において、

前記第1開口内に前記バリアメタル膜を埋め込む工程の後に、

前記第1開口内の前記バリアメタル膜をエッチバックすることにより、前記バリアメタル膜の上面を前記第1開口の上端よりも下に位置させる工程と、

前記第1開口内に前記第1ゲート電極を埋め込む工程と、

を有する半導体装置の製造方法。

【請求項34】

請求項33に記載の半導体装置の製造方法において、

前記第1配線層を形成する工程において、複数の前記第1配線を形成し、

前記第1開口を形成する工程において、第1の前記第1配線上に前記第1開口を形成するとともに、前記拡散防止膜に、第2の前記第2配線上に位置する第2開口を形成し、

前記第1開口内に前記バリアメタル膜を埋め込む工程において、前記第2開口内にも前記バリアメタル膜を埋め込み、

前記第1開口内に前記第1ゲート電極を埋め込む工程の後に、

前記第2開口内の前記バリアメタル膜をエッチバックすることにより、前記第2開口内の前記バリアメタル膜の上面を前記第2開口の上端よりも下に位置させる工程と、

前記第2開口内に第2ゲート電極を埋め込む工程と、

前記第2ゲート電極上に、第2ゲート絶縁膜及び第2半導体層を形成する工程と、

を備える半導体装置の製造方法。

【請求項35】

請求項33に記載の半導体装置の製造方法において、

前記第1配線層を形成する工程において、複数の前記第1配線を形成し、

前記第1開口を形成する工程において、第1の前記第1配線上に前記第1開口を形成するとともに、前記拡散防止膜に、第2の前記第2配線上に位置する第2開口を形成し、

前記第1開口内に前記バリアメタル膜を埋め込む工程において、前記第2開口内にも前記バリアメタル膜を埋め込み、

前記バリアメタル膜の上面を前記第1開口の上端よりも下に位置させる工程において、前記第2開口内の前記バリアメタル膜もエッチバックすることにより、前記第2開口内の前記バリアメタル膜の上面も前記第2開口の上端よりも下に位置させ、

前記第1開口内に前記第1ゲート電極を埋め込む工程において、前記第2開口内にも前記第1ゲート電極と同一の材料が埋め込まれ、

前記第1開口内に前記第1ゲート電極を埋め込む工程の後に、

前記第2開口内の前記第1ゲート電極と同一の材料を除去する工程と、

前記第2開口内に、第2ゲート電極を埋め込む工程と、

前記第2ゲート電極上に、第2ゲート絶縁膜及び第2半導体層を形成する工程と、

を備える半導体装置の製造方法。

【請求項36】

請求項30〜35のいずれか一項に記載の半導体装置の製造方法において、

前記拡散防止膜を形成する工程と、前記開口を形成する工程の間に、

前記拡散防止膜上に、保護絶縁膜を形成する工程を備え、

前記開口を形成する工程において、前記拡散防止膜及び前記保護絶縁膜に前記開口を形成する半導体装置の製造方法。

【請求項1】

第1配線を有する第1配線層と、

前記第1配線層より上に形成され、第2配線を有する第2配線層と、

厚さ方向において前記第1配線と前記第2配線の間に位置し、前記第1配線とは異なる材料で形成され、前記第1配線に接続するゲート電極と、

前記ゲート電極上に位置するゲート絶縁膜と、

前記ゲート絶縁膜上に位置する半導体層と、

前記第2配線層に埋め込まれ、前記半導体層と前記第2配線とを接続する第1ビアと、

を備える半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

2つの前記第2配線を備え、

前記2つの第2配線は、互いに異なる前記第1ビアを介して、前記半導体層に接続しており、

前記2つの第1ビアは、平面視で前記ゲート電極の中心を介して互いに逆側に配置されている半導体装置。

【請求項3】

請求項2に記載の半導体装置において、

平面視で、前記半導体層は前記ゲート電極よりも広く、

前記2つの第1ビアの中心は、前記ゲート電極と重なっていない半導体装置。

【請求項4】

請求項1〜3のいずれか一項に記載の半導体装置において、

前記第1配線層に形成された第3配線と、

前記第2配線層に形成された第4配線と、

前記第2配線層に埋め込まれ、前記第3配線及び前記第4配線を接続する第2ビアと、

を備える半導体装置。

【請求項5】

請求項4に記載の半導体装置において、

前記第3配線は、前記第1配線と同一構造を有しており、

前記第4配線は、前記第2配線と同一構造を有しており、

前記第2ビアは、前記第1ビアと同一構造を有している半導体装置。

【請求項6】

請求項1〜5のいずれか一項に記載の半導体装置において、

前記第1配線層上に形成された拡散防止膜と、

前記拡散防止膜に形成され、前記第1配線上に位置する開口と、

前記開口内に位置し、前記ゲート電極と前記第1配線とを接続するバリアメタル膜と、

を備える半導体装置。

【請求項7】

請求項1〜5のいずれか一項に記載の半導体装置において、

前記第1配線層と前記第2配線層の間に形成された拡散防止膜と、

前記拡散防止膜に形成され、前記第1配線上に位置する開口と、

を備え、

前記ゲート電極は、少なくとも前記開口内に形成されている半導体装置。

【請求項8】

請求項7に記載の半導体装置において、

前記ゲート電極は、前記開口内、及び前記開口の周囲に位置する前記拡散防止膜上に形成されている半導体装置。

【請求項9】

請求項7に記載の半導体装置において、

前記ゲート電極は、前記開口内にのみ位置している半導体装置。

【請求項10】

請求項9に記載の半導体装置において、

前記ゲート電極の上面は、前記拡散防止膜の上面と同一面を形成している半導体装置。

【請求項11】

請求項7〜10のいずれか一項に記載の半導体装置において、

前記開口内に位置し、前記ゲート電極と前記第1配線とを接続するバリアメタル膜を備える半導体装置。

【請求項12】

請求項6〜11のいずれか一項に記載の半導体装置において、

前記拡散防止膜の上に位置する保護絶縁膜を備え、

前記開口は、前記保護絶縁膜及び前記拡散防止膜に形成されている半導体装置。

【請求項13】

請求項12に記載の半導体装置において、

前記保護絶縁膜は、酸化シリコンよりも誘電率が低い材料、またはこの材料の多孔質膜により形成されている半導体装置。

【請求項14】

請求項1〜13のいずれか一項に記載の半導体装置において、

前記第1配線層及び前記第2配線層は、基板上に形成されており、

前記基板に形成された第1トランジスタを備える半導体装置。

【請求項15】

請求項14に記載の半導体装置において、

平面視において、前記第1トランジスタは、前記半導体層と重なっている半導体装置。

【請求項16】

請求項2に記載の半導体装置において、

前記ゲート電極、前記ゲート絶縁膜、及び前記半導体層は第2トランジスタを形成している半導体装置。

【請求項17】

請求項16に記載の半導体装置において、

少なくとも2つの前記第2トランジスタを備え、

前記少なくとも2つの第2トランジスタは、前記ゲート電極、前記ゲート絶縁膜、及び前記半導体層の材料の組み合わせが互いに異なる半導体装置。

【請求項18】

請求項17に記載の半導体装置において、

前記少なくとも2つの第2トランジスタは、チャネルの導電型が互いに同一であり、閾値電圧が互いに異なる半導体装置。

【請求項19】

請求項16〜18のいずれか一項に記載の半導体装置において、

内部回路と、

前記多層配線層の最上層の配線層に形成され、前記内部回路に電源電圧を供給する電源パッドと、

を備え、

前記内部回路は、前記第2トランジスタを介して前記電源パッドに接続している半導体装置。

【請求項20】

請求項1〜15のいずれか一項に記載の半導体装置において、

前記半導体層は、ソース及びドレインを有しており、

前記ソースは、前記ゲート電極に短絡しており、

前記ソース、前記ドレイン、前記ゲート絶縁膜、及び前記ゲート電極は、ダイオードを形成している半導体装置。

【請求項21】

請求項20に記載の半導体装置において、

内部回路と、

前記多層配線層の最上層の配線層に形成され、前記内部回路に信号を供給するI/Oパッドと、

前記最上層の配線層に形成され、前記内部回路に接地電位を供給する接地パッドと、

を備え、

前記ダイオードは、前記I/Oパッドと前記接地パッドの間に、前記I/Oパッドから前記接地パッドに向かう方向が順方向となる向きに接続されている半導体装置。

【請求項22】

請求項1〜15のいずれか一項に記載の半導体装置において、

前記ゲート電極、前記ゲート絶縁膜、及び前記半導体層は容量素子を形成している半導体装置。

【請求項23】

請求項1〜22のいずれか一項に記載の半導体装置において、

前記第1配線はCu配線であり、

前記ゲート電極は、Ti、Ta、W、TiN、TaN、WN膜、CoもしくはWを含む化合物、これらのいずれか一つにC及びOの少なくとも一つを導入した膜、またはこれらの膜を複数種類積層した積層膜を有している半導体装置。

【請求項24】

請求項1〜23のいずれか一項に記載の半導体装置において、

前記ゲート絶縁膜は、酸化シリコン膜、窒化シリコン膜、またはHf、Zr、Al、Ti、並びにTaの少なくとも一つの酸化膜を有している半導体装置。

【請求項25】

請求項1〜24のいずれか一項に記載の半導体装置において、

前記半導体層は、酸化物半導体層である半導体装置。

【請求項26】

請求項25に記載の半導体装置において、

前記酸化物半導体層は、InGaZnO層、InZnO層、ZnO層、ZnAlO層、ZnCuO層、NiO、NiO2、SnO、またはCuOである半導体装置。

【請求項27】

請求項1〜26のいずれか一項に記載の半導体装置において、

前記半導体層上に形成され、平面形状が前記半導体層と同一であるハードマスク膜を備える半導体装置。

【請求項28】

請求項27に記載の半導体装置において、

前記ハードマスク膜は、前記拡散防止膜と同一材料であり、かつ前記拡散防止膜と同一の厚さの層を有している半導体装置。

【請求項29】

半導体基板上に、第1配線を有する第1配線層を形成する工程と、

前記第1配線層上に、第1ゲート電極、前記第1ゲート電極上に位置する第1ゲート絶縁膜、及び前記第1ゲート絶縁膜上に位置する第1半導体層を形成する工程と、

前記第1配線層上及び前記第1半導体層上に、第2配線を有する第2配線層を形成する工程と、

を備え、

前記第1ゲート電極は前記第1配線に接続し、前記第2配線は前記第1半導体層に接続する半導体装置の製造方法。

【請求項30】

請求項29に記載の半導体装置の製造方法において、

前記第1配線層を形成する工程と、前記第1ゲート電極、前記第1ゲート絶縁膜、及び前記第1半導体層を形成する工程の間に、

前記第1配線層上に拡散防止膜を形成する工程と、

前記拡散防止膜に、前記第1配線上に位置する第1開口を形成する工程と、

を備え、

前記第1ゲート電極を形成する工程において、前記第1ゲート電極を、平面視で前記第1開口と重ねることにより、前記第1ゲート電極と前記第1配線とを接続する半導体装置の製造方法。

【請求項31】

請求項30に記載の半導体装置の製造方法において、

前記第1開口を形成する工程と、前記第1ゲート電極を形成する工程の間に、前記第1開口内にバリアメタル膜を形成する工程を有する半導体装置の製造方法。

【請求項32】

請求項31に記載の半導体装置の製造方法において、

前記第1開口内に前記バリアメタル膜を埋め込む工程は、

前記第1開口内及び前記拡散防止膜上にバリアメタル膜を形成する工程と、

前記拡散防止膜上に位置するバリアメタル膜を、CMP法を用いて除去する工程と、

を有する半導体装置の製造方法。

【請求項33】

請求項32に記載の半導体装置の製造方法において、

前記第1開口内に前記バリアメタル膜を埋め込む工程の後に、

前記第1開口内の前記バリアメタル膜をエッチバックすることにより、前記バリアメタル膜の上面を前記第1開口の上端よりも下に位置させる工程と、

前記第1開口内に前記第1ゲート電極を埋め込む工程と、

を有する半導体装置の製造方法。

【請求項34】

請求項33に記載の半導体装置の製造方法において、

前記第1配線層を形成する工程において、複数の前記第1配線を形成し、

前記第1開口を形成する工程において、第1の前記第1配線上に前記第1開口を形成するとともに、前記拡散防止膜に、第2の前記第2配線上に位置する第2開口を形成し、

前記第1開口内に前記バリアメタル膜を埋め込む工程において、前記第2開口内にも前記バリアメタル膜を埋め込み、

前記第1開口内に前記第1ゲート電極を埋め込む工程の後に、

前記第2開口内の前記バリアメタル膜をエッチバックすることにより、前記第2開口内の前記バリアメタル膜の上面を前記第2開口の上端よりも下に位置させる工程と、

前記第2開口内に第2ゲート電極を埋め込む工程と、

前記第2ゲート電極上に、第2ゲート絶縁膜及び第2半導体層を形成する工程と、

を備える半導体装置の製造方法。

【請求項35】

請求項33に記載の半導体装置の製造方法において、

前記第1配線層を形成する工程において、複数の前記第1配線を形成し、

前記第1開口を形成する工程において、第1の前記第1配線上に前記第1開口を形成するとともに、前記拡散防止膜に、第2の前記第2配線上に位置する第2開口を形成し、

前記第1開口内に前記バリアメタル膜を埋め込む工程において、前記第2開口内にも前記バリアメタル膜を埋め込み、

前記バリアメタル膜の上面を前記第1開口の上端よりも下に位置させる工程において、前記第2開口内の前記バリアメタル膜もエッチバックすることにより、前記第2開口内の前記バリアメタル膜の上面も前記第2開口の上端よりも下に位置させ、

前記第1開口内に前記第1ゲート電極を埋め込む工程において、前記第2開口内にも前記第1ゲート電極と同一の材料が埋め込まれ、

前記第1開口内に前記第1ゲート電極を埋め込む工程の後に、

前記第2開口内の前記第1ゲート電極と同一の材料を除去する工程と、

前記第2開口内に、第2ゲート電極を埋め込む工程と、

前記第2ゲート電極上に、第2ゲート絶縁膜及び第2半導体層を形成する工程と、

を備える半導体装置の製造方法。

【請求項36】

請求項30〜35のいずれか一項に記載の半導体装置の製造方法において、

前記拡散防止膜を形成する工程と、前記開口を形成する工程の間に、

前記拡散防止膜上に、保護絶縁膜を形成する工程を備え、

前記開口を形成する工程において、前記拡散防止膜及び前記保護絶縁膜に前記開口を形成する半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【公開番号】特開2013−38349(P2013−38349A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2011−175391(P2011−175391)

【出願日】平成23年8月10日(2011.8.10)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成23年8月10日(2011.8.10)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]