半導体装置及び半導体装置の製造方法

【課題】ドレイン−ソース間のリーク電流が少なく、かつ、ノーマリーオフの半導体装置を提供する。

【解決手段】基板11の上に形成された不純物元素を含む第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層16と、第2の半導体層16の上に形成された第3の半導体層17と、第3の半導体層17の上に形成されたゲート電極21、ソース電極22及びドレイン電極23と、を有し、第2の半導体層16において、ゲート電極21の直下には、第1の半導体層13と接し、第1の半導体層13に含まれる不純物元素が拡散している不純物拡散領域15が形成されており、不純物元素は、不純物拡散領域がp型となる元素であることを特徴とする半導体装置。

【解決手段】基板11の上に形成された不純物元素を含む第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層16と、第2の半導体層16の上に形成された第3の半導体層17と、第3の半導体層17の上に形成されたゲート電極21、ソース電極22及びドレイン電極23と、を有し、第2の半導体層16において、ゲート電極21の直下には、第1の半導体層13と接し、第1の半導体層13に含まれる不純物元素が拡散している不純物拡散領域15が形成されており、不純物元素は、不純物拡散領域がp型となる元素であることを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及び半導体装置の製造方法に関するものである。

【背景技術】

【0002】

窒化物半導体であるGaN、AlN、InN等または、これらの混晶である材料は、広いバンドギャップを有しており、高出力電子デバイスまたは短波長発光デバイス等として用いられている。このうち、高出力デバイスとしては、電界効果型トランジスタ(FET:Field-Effect Transistor)、特に、高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor)に関する技術が開発されている(例えば、特許文献1)。このような窒化物半導体を用いたHEMTは、高出力・高効率増幅器、大電力スイッチングデバイス等に用いられる。

【0003】

このような窒化物半導体を用いたHEMTは、基板上に、窒化アルミニウムガリウム/窒化ガリウム(AlGaN/GaN)ヘテロ構造が形成されており、GaN層を電子走行層とするものである。尚、基板としては、サファイア、シリコンカーバイド(SiC)、窒化ガリウム(GaN)、シリコン(Si)等の基板が用いられる。

【0004】

窒化物半導体において、GaNは、高い飽和電子速度や広いバンドギャップを有しており、高い耐圧特性を得ることができるため、優れた電気的特性を有している。また、GaNは、結晶構造がウルツ鉱型であるため、c軸に平行な<0001>方向に極性を有しており、更に、AlGaN/GaNのヘテロ構造を形成した場合には、AlGaN層には、AlGaNとGaNとの格子歪みによるピエゾ分極が励起される。このため、チャネルとなる界面には、高濃度の2DEG(Two-Dimensional Electron Gas:2次元電子ガス)が生じる。よって、このようなGaNを用いたHEMTは、高周波・電力用デバイスとして有望とされている。

【0005】

ところで、GaNを用いたHEMTでは、ピンチオフ電圧以下のオフ状態においては、ゲート電極の直下における電子走行層の下部を通り、ドレイン側からソース側にリーク電流が発生しやすいといった問題点を有している。具体的には、図1に示すように、GaNを用いたHEMTは、基板911上に、バッファ層912、電子走行層913、電子供給層914が形成されており、電子供給層914の上に、ゲート電極921、ソース電極922及びドレイン電極923が形成されている。尚、電子走行層913はGaNにより形成されており、電子供給層914はAlGaNにより形成されており、これにより、電子走行層913において、電子走行層913と電子供給層914との界面近傍には、2DEG913aが形成される。

【0006】

一般的には、電子走行層913は、結晶性を確保するため厚く形成されるが、電子走行層913を厚く形成すると、ゲート電極921の直下には、ゲート電極921に印加された電圧による電界が及ばず、電子走行層913の下部にリーク電流が流れやすくなる。即ち、ゲート電極921にゲート電圧を印加した場合等に形成される空乏領域919が電子走行層913の下部にまで広がらないため、電子走行層913の下部において矢印に示す方向にリーク電流が流れやすくなる。GaNを用いたHEMTを高出力増幅器に用いた場合において、このようなリーク電流が増加すると、増幅効率が低下してしまう。

【0007】

また、GaNを用いたHEMTは、一般的には、高濃度の2DEGによりノーマリーオンになりやすく、ノーマリーオフの特性を得ることが難しいといった問題点もあった。現在のパワーエレクトロニクス市場において用いられている半導体装置の多くは、ノーマリーオフであるため、既存の半導体装置との親和性等より、GaNを用いたHEMTにおいても、ノーマリーオフであることが強く求められている。

【0008】

このため、リーク電流を抑制する方法としては、GaN等により形成される電子走行層913の厚さを薄くする方法や、電子走行層913の下部にMgやFe等のアクセプタとなる不純物をドープし、電子走行層913の下部を高抵抗化する方法が開示されている(例えば、非特許文献1)。また、ノーマリーオフについては、Mgをドーピングした低抵抗p型GaN層を電子供給層とゲート電極との間に形成し、低抵抗p型GaN層から供給されるホールによりゲート電極の直下における2DEGの発生を抑制する方法等が開示されている(例えば、特許文献2)。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2002−359256号公報

【特許文献2】特開2010−135641号公報

【非特許文献】

【0010】

【非特許文献1】Journal of Crystal Growth 248 (2003) 513

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかしながら、所望の結晶性を確保しつつ、電子走行層913の厚さを薄くすることは極めて困難であり、逆に、オン抵抗を増大させてしまうという問題点を有している。また、図2に示すように、電子走行層913の下に、p型となる不純物元素であるMg等をドープしたp−GaN層931を形成した場合では、Mg等はGaN内を拡散しやすいため、p−GaN層931にドープされているMgが電子走行層913内を拡散する。このように電子走行層913内をMgが拡散することにより、電子走行層913内にはMgが拡散した拡散領域913bが形成されるため、電子走行層913における2DEGの濃度や、移動度が低下し、HEMTにおける特性が低下してしまう。尚、図2は、電子走行層913内をMgが拡散することにより、2DEGが消失している状態のものを示している。

【0012】

このため、半導体材料としてGaN等の窒化物半導体を用いた半導体装置において、ドレイン−ソース間におけるリーク電流を抑制することができ、ノーマリーオフにすることのできる半導体装置及び半導体装置の製造方法が求められている。

【課題を解決するための手段】

【0013】

本実施の形態の一観点によれば、基板の上に形成された不純物元素を含む第1の半導体層と、前記第1の半導体層の上に形成された第2の半導体層と、前記第2の半導体層の上に形成された第3の半導体層と、前記第3の半導体層の上に形成されたゲート電極、ソース電極及びドレイン電極と、を有し、前記第2の半導体層において、前記ゲート電極の直下には、前記第1の半導体層と接し、前記第1の半導体層に含まれる不純物元素が拡散している不純物拡散領域が形成されており、前記不純物元素は、前記不純物拡散領域がp型となる元素であることを特徴とする。

【0014】

また、本実施の形態の他の一観点によれば、基板の上に、不純物元素を含む第1の半導体層を形成する工程と、前記第1の半導体層の上に、開口部を有する成長制御層を形成する工程と、前記開口部において露出している前記第1の半導体層及び前記成長制御層の上に、第2の半導体層を形成する工程と、前記第2の半導体層の上に、第3の半導体層を形成する工程と、前記第3の半導体層の上に、ゲート電極、ソース電極及びドレイン電極を形成する工程と、を有し、前記成長制御層における前記開口部は、前記ゲート電極の直下に形成されるものであって、前記不純物元素は、前記第2の半導体層がp型となる元素であることを特徴とする。

【発明の効果】

【0015】

開示の半導体装置及び半導体装置の製造方法によれば、半導体材料としてGaN等の窒化物半導体を用いた半導体装置において、ドレイン−ソース間におけるリーク電流を抑制することができ、ノーマリーオフにすることができる。

【図面の簡単な説明】

【0016】

【図1】従来のGaNを用いたHEMTの説明図(1)

【図2】従来のGaNを用いたHEMTの説明図(2)

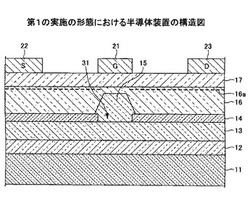

【図3】第1の実施の形態における半導体装置の構造図

【図4】第1の実施の形態における半導体装置の製造方法の工程図(1)

【図5】第1の実施の形態における半導体装置の製造方法の工程図(2)

【図6】第1の実施の形態における半導体装置の製造方法の工程図(3)

【図7】第2の実施の形態における半導体装置の構造図

【図8】第2の実施の形態における半導体装置の製造方法の説明図

【図9】第3の実施の形態における半導体装置の構造図

【図10】第4の実施の形態におけるディスクリートパッケージされた半導体デバイスの説明図

【図11】第4の実施の形態における電源装置の回路図

【図12】第4の実施の形態における高出力増幅器の構造図

【発明を実施するための形態】

【0017】

実施するための形態について、以下に説明する。尚、同じ部材等については、同一の符号を付して説明を省略する。

【0018】

〔第1の実施の形態〕

(半導体装置)

第1の実施の形態における半導体装置について、図1に基づき説明する。本実施の形態における半導体装置は、Si等の基板11上に、AlN等により形成されるバッファ層12、第1の半導体層であるp型となる不純物元素がドープされているp型層13が形成されている。p型層13上には、ゲート電極21の直下に開口部31を有するAlN等により形成される成長制御層14が形成されており、p型層13及び成長制御層14の上には、第2の半導体層となるp型拡散領域15及び電子走行層16が形成されている。即ち、ゲート電極21の直下に形成される開口部31において露出しているp型層13上には、p型拡散領域15が形成され、p型拡散領域15及び成長制御層14上は、電子走行層16が形成されている。尚、本実施の形態において、ゲート電極21の直下とは、電子供給層17または電子走行層16等を介したゲート電極21が形成される領域の下の領域を含むものである。更に、電子走行層16の上には、第3の半導体層となる電子供給層17が形成されており、電子供給層17の上には、ゲート電極21、ソース電極22及びドレイン電極23が形成されている。電子走行層16はGaNにより形成されており、電子供給層17はAlGaNにより形成されており、これにより、電子走行層16において、電子走行層16と電子供給層17との界面近傍には2DEG16aが形成される。p型層13にはGaNにp型となる不純物元素としてMgがドープされており、この上にGaNを結晶成長させることにより、p型層13が露出している成長制御層14の開口部31より、p型層13に含まれているMgが取り込まれp型拡散領域15が形成される。このため、p型拡散領域15を不純物拡散領域と記載する場合がある。尚、電子走行層16は、成長制御層14の上に形成されるため、Mgが取り込まれることはない。よって電子走行層16は、Mgを含まないGaNにより形成される。また、p型層13は、AlGaNにp型となる不純物元素がドープされたものであってもよい。

【0019】

このように、ゲート電極21の直下となるp型層13の上にp型拡散領域15を形成することにより、p型拡散領域15の直上、即ち、ゲート電極21の直下においては、2DEG16aにおける電子は殆ど存在しなくなり、ノーマリーオフにすることができる。更に、p型拡散領域15は高抵抗化しているため、ゲート電極21の直下となる電子走行層16の下層にp型拡散領域15を形成することにより、ドレイン電極23からソース電極22に流れるリーク電流を抑制することができる。尚、成長制御層14は、AlGaN、InAlN、SiOx、SiN等の他の窒化物により形成してもよい。

【0020】

(半導体装置の製造方法)

次に、図4〜図6に基づき、第1の実施の形態における半導体装置の製造方法について説明する。

【0021】

最初に、図4(a)に示すように、基板11上に、バッファ層12及びp型層13をMOVPE(Metal Organic Vapor Phase Epitaxy)法によりエピタキシャル成長させることにより形成する。この際、Alの原料ガスにはTMA(トリメチルアルミニウム)が用いられ、Gaの原料ガスにはTMG(トリメチルガリウム)が用いられ、Nの原料ガスにはNH3(アンモニア)が用いられる。また、不純物元素としてドープされるMgの原料ガスにはCp2Mg(シクロペンタジエニルマグネシウム)が用いられる。尚、これらの原料ガスは、水素(H2)をキャリアガスとしてMOVPE装置の反応炉に供給される。

【0022】

基板11は、サファイア、Si、SiC等により形成されており、基板11へのリーク電流を防ぐためには、抵抗の高い材料により形成された基板を用いることが好ましい。尚、本実施の形態では、基板11は、Siにより形成された基板が用いられている。

【0023】

基板11を数分間、水素雰囲気中で熱処理を行なった後に、バッファ層12を形成する。バッファ層12は、最初にAlNにより形成される層を形成し、この後、AlGaNにより形成される層を形成する。基板11に起因する転位を低減するためには、バッファ層12の膜厚は厚いほど好ましいが、クラックの発生を防ぐためには、あまり厚く形成しない方が好ましい。よって、バッファ層12の膜厚は、200〜1000nmが好ましい。また、このような構造以外にも、GaN/AlNを交互に形成した周期構造を有する超格子バッファや、AlNからGaNに至るまでAlの組成比を変化させた組成傾斜構造により形成してもよい。尚、バッファ層12を形成する際の温度は、約1000℃である。

【0024】

バッファ層12の上には、p型層13を形成する。p型層13は、GaNに不純物元素としてMgがドープされたものであり、膜厚が100〜300nmとなるように形成されている。尚、過剰にMgをドープした場合、p型層13及びp型層13上に形成される電子走行層16等において結晶性が劣化するため、Mgがドーピングされる濃度は、5×1017〜5×1019cm−3が好ましい。本実施の形態では、1×1019cm−3の濃度のMgがドープされている。また、本実施の形態では、p型不純物としてMgの場合について説明しているが、p型となるものであれば他の不純物元素であってもよい。

【0025】

次に、図4(b)に示すように、p型層13の上に成長制御層14を形成するためのAlN膜14aを形成する。具体的には、MOVPE、スパッタリング等により、AlN膜14aを形成する。MOVPEによりAlN膜14aを形成する際、500〜800℃の成長温度でAlN膜14aを形成する。一般的に、p型層13及び後述する電子走行層16及び電子供給層17をMOVPEにより形成する場合には、成長温度が約1000℃、または、それ以上の温度で形成されるが、AlN膜14aは、この温度よりも低い温度で形成される。このように、AlN膜14aは、通常の成膜温度よりも低い温度で形成されるため、特に、低温成長AlN(LT−AlN:Low Temperature AlN)とも呼ばれている。このように低温でAlN膜14aを形成することにより、形成されるAlN膜14aは多結晶状態の膜となる。尚、形成されるAlN膜14aは、多結晶状態の膜であってもアモルファス状態の膜であってもよい。また、形成されるAlN膜14aの膜厚は、5〜50nmである。

【0026】

次に、図5(a)に示すように、AlN膜14aに開口部31を形成することにより、成長制御層14を形成する。具体的には、AlN膜14aの全面にフォトレジストを塗布し、露光装置による露光、現像を行なうことにより、開口部31に開口を有する不図示のレジストパターンを形成する。この後、RIE(Reactive Ion Etching)等により、レジストパターンの形成されていない領域のAlN膜14aを除去し、更に、有機溶剤等によりレジストパターンを除去する。これにより、AlNにより形成される成長制御層14を形成することができる。

【0027】

次に、図5(b)に示すように、成長制御層14が形成されている面に、MOVPEによりp型拡散領域15及び電子走行層16を形成し、更に、電子走行層16上に電子供給層17を形成する。p型拡散領域15及び電子走行層16は、ともにGaNを結晶成長させることにより形成されている。p型拡散領域15及び電子走行層16を形成しているGaNは、最初に、成長制御層14が形成されていないp型層13が露出している開口部31において、p型層13における不純物元素であるMgを取り込みながら成長し、p型拡散領域15が形成される。一般に、GaNは成長モードが2次元的になりやすく、厚く成膜するほど平坦な膜が得られやすいことが知られている。しかしながら、形成されるp型拡散領域15は成長制御層14が形成されていない領域にのみ形成されていることが好ましいため、3次元成長が支配的となる条件、例えば、圧力の高い条件等により形成する。p型拡散領域15が所望の膜厚となるように形成した後は、GaNが2次元的に成長する条件により電子走行層16を形成する。この際、転位等に起因した2DEG16aにおける電子密度の低下や、移動度の低下を避けるため、電子走行層16は、膜厚が500〜1000nmとなるように形成する。これにより、ゲート電極21の直下となる成長制御層14の開口部31において露出しているp型層13上にはp型拡散領域15が形成され、p型拡散領域15及び成長制御層14上には、GaNによる電子走行層16が形成される。尚、本実施の形態においては、p型拡散領域15は、電子走行層16の表面より数100nm下に、p型拡散領域15と電子走行層16との界面が位置するように形成されている。また、成長制御層14は、上述したMgの拡散を防ぐとともに、成長制御層14上に形成される電子走行層16を形成する際の成長核形成層としての機能も有している。

【0028】

この後、電子走行層16の上には、電子供給層17が形成されるが、電子供給層17は、AlGaNの膜厚が約20nmとなるように形成する。電子供給層17は、格子不整合による結晶性の劣化を避けるため、電子供給層17をAlXGa1−XNと表わした場合に、Xの値が0.3以下となるように形成されている。

【0029】

次に、図6に示すように、電子供給層17上に、ゲート電極21、ソース電極22及びドレイン電極23を形成する。具体的には、電子供給層17上にフォトレジストを塗布し、露光装置による露光、現像を行なうことにより、ソース電極22及びドレイン電極23が形成される領域に開口を有する不図示のレジストパターンを形成する。この後、真空蒸着等の成膜方法により金属膜を成膜した後、有機溶剤等に浸漬させることによりレジストパターンの上に形成されている金属膜をレジストパターンとともに除去する。これにより、ソース電極22及びドレイン電極23を形成する。次に、再度、電子供給層17上にフォトレジストを塗布し、露光装置による露光、現像を行なうことにより、ゲート電極21が形成される領域に開口を有する不図示のレジストパターンを形成する。この後、真空蒸着等の成膜方法により金属膜を成膜した後、有機溶剤等に浸漬させることによりレジストパターンの上に形成されている金属膜をレジストパターンとともに除去する。これにより、ゲート電極21を形成する。

【0030】

以上により、本実施の形態における半導体装置であるGaNを用いたHEMTを製造することができる。

【0031】

〔第2の実施の形態〕

(半導体装置)

次に、第2の実施の形態における半導体装置について、図7に基づき説明する。本実施の形態における半導体装置は、ゲート電極近傍にゲートリセスを形成した構造のものである。

【0032】

具体的には、本実施の形態における半導体装置は、Si等の基板11上に、AlN等により形成されるバッファ層12、第1の半導体層であるp型となる不純物元素がドープされているp型層13が形成されている。p型層13上には、ゲート電極21の直下に開口部31を有するAlN等により形成される成長制御層14が形成されており、p型層13及び成長制御層14の上には、第2の半導体層となるp型拡散領域15及び電子走行層16が形成されている。即ち、ゲート電極21の直下となる開口部31において露出しているp型層13上には、p型拡散領域15が形成され、p型拡散領域15及び成長制御層14上は、電子走行層16が形成されている。更に、電子走行層16の上には、第3の半導体層となる電子供給層17が形成されており、電子供給層17の表面には、ゲート電極21が形成される領域に凹形状のゲートリセス131が形成されている。ゲート電極21は、ゲートリセス131の内部を含む領域の電子走行層17等の上に形成されており、ソース電極22及びドレイン電極23は電子供給層17の上に形成されている。電子走行層16はGaNにより形成されており、電子供給層17はAlGaNにより形成されており、これにより、電子走行層16において、電子走行層16と電子供給層17との界面近傍には2DEG16aが形成される。p型層13にはGaNにp型となる不純物元素としてMgがドープされており、この上にGaNを結晶成長させることにより、p型層13が露出している成長制御層14の開口部31より、p型層13に含まれるMgが取り込まれp型拡散領域15が形成される。このため、p型拡散領域15を不純物拡散領域と記載する場合がある。尚、電子走行層16は、成長制御層14の上に形成されるため、Mgが取り込まれることはない。よって、電子走行層16は、Mgを含まないGaNにより形成することができる。

【0033】

このように、ゲート電極21の直下となるp型層13の上にp型拡散領域15を形成することにより、p型拡散領域15の直上、即ち、ゲート電極21の直下においては、2DEG16aにおける電子は殆ど存在しなくなり、ノーマリーオフにすることができる。更に、本実施の形態では、ゲートリセス131が形成されているため、より一層ノーマリーオフになりやすい。更に、p型拡散領域15は高抵抗化しているため、ゲート電極21の直下となる電子走行層16の下層にp型拡散領域15を形成することにより、ドレイン電極23からソース電極22に流れるリーク電流を抑制することができる。

【0034】

(半導体装置の製造方法)

次に、第2の実施の形態における半導体装置の製造方法について説明する。本実施の形態における半導体装置の製造方法は、第1の実施の形態における図5(b)まで形成した後、ゲートリセス131を形成する。

【0035】

具体的には、第1の実施の形態における半導体装置の製造方法の図4(a)〜図5(b)に示される工程と同様の工程により、図5(b)に示すものを作製した後、図8(a)に示されるように、電子供給層17の表面に凹形状のゲートリセス131を形成する。ゲートリセス131は、電子供給層17の表面において、ゲート電極21が形成される領域に形成される。具体的には、電子供給層17の表面にフォトレジストを塗布し、露光装置による露光、現像を行なうことにより、ゲートリセス131が形成される領域に開口を有する不図示のレジストパターンを形成する。この後、RIE等により、レジストパターンの形成されていない領域の電子走行層17を所望の深さまで除去することによりゲートリセス131を形成する。この後、有機溶剤等によりレジストパターンを除去する。

【0036】

次に、図8(b)に示すように、電子供給層17上にゲート電極21、ソース電極22及びドレイン電極23を形成する。具体的には、電子供給層17上にフォトレジストを塗布し、露光装置による露光、現像を行なうことにより、ソース電極22及びドレイン電極23が形成される領域に開口を有する不図示のレジストパターンを形成する。この後、真空蒸着等の成膜方法により金属膜を成膜した後、有機溶剤等に浸漬させることによりレジストパターンの上に形成されている金属膜をレジストパターンとともに除去する。これにより、ソース電極22及びドレイン電極23を形成する。次に、再度、電子供給層17上にフォトレジストを塗布し、露光装置による露光、現像を行なうことにより、ゲート電極21が形成される領域に開口を有する不図示のレジストパターンを形成する。この際、ゲート電極21が電子供給層17の表面に形成されているゲートリセス131の内部等に形成されるように位置合せを行なう。即ち、ゲート電極21が形成されるレジストパターンの開口には、ゲートリセス131が露出するように位置合せを行いレジストパターンを形成する。この後、真空蒸着等の成膜方法により金属膜を成膜した後、有機溶剤等に浸漬させることによりレジストパターンの上に形成されている金属膜をレジストパターンとともに除去する。これにより、ゲート電極21を形成する。

【0037】

以上により、本実施の形態における半導体装置であるGaNを用いたHEMTを製造することができる。尚、上記以外の内容については、第1の実施の形態と同様である。

【0038】

〔第3の実施の形態〕

次に、第3の実施の形態における半導体装置について、図9に基づき説明する。本実施の形態における半導体装置は、電子供給層17上にゲート絶縁膜となる絶縁膜140が形成されている構造のものである。このような絶縁膜140を形成することにより、ゲートリーク電流を減らすことができる。絶縁膜140としては、例えば、Al2O3(酸化アルミニウム)等が用いられる。

【0039】

本実施の形態における半導体装置は、第1の実施の形態における図5(b)まで形成したものの電子供給層17上に、ソース電極22及びドレイン電極23を形成し、この後、ゲート絶縁膜となる絶縁膜140を形成する。絶縁膜140の形成方法としては、CVD(Chemical Vapor Deposition)、ALD(Atomic Layer Deposition)、スパッタリング等が挙げられる。

【0040】

この後、絶縁膜140上の所定の領域、即ち、絶縁膜140上であって、p型拡散領域15が形成されている領域の上に、ゲート電極21を形成する。

【0041】

これにより、本実施の形態における半導体装置を製造することができる。

【0042】

尚、上記以外の内容は、第1の実施の形態と同様である。また、本実施の形態は、第2の実施の形態における半導体装置においても適用することができる。

【0043】

〔第4の実施の形態〕

次に、第4の実施の形態について説明する。本実施の形態は、半導体デバイス、電源装置及び高周波増幅器である。

【0044】

本実施の形態における半導体デバイスは、第1から第3の実施の形態におけるいずれかの半導体装置をディスクリートパッケージしたものであり、このようにディスクリートパッケージされた半導体デバイスについて、図10に基づき説明する。尚、図10は、ディスクリートパッケージされた半導体装置の内部を模式的に示すものであり、電極の配置等については、第1から第3の実施の形態に示されているものとは、異なっている。

【0045】

最初に、第1から第3の実施の形態において製造された半導体装置をダイシング等により切断することにより、GaN系の半導体材料のHEMTの半導体チップ410を形成する。この半導体チップ410をリードフレーム420上に、ハンダ等のダイアタッチ剤430により固定する。尚、この半導体チップ410は、第1から第3の実施の形態における半導体装置に相当するものである。

【0046】

次に、ゲート電極411をゲートリード421にボンディングワイヤ431により接続し、ソース電極412をソースリード422にボンディングワイヤ432により接続し、ドレイン電極413をドレインリード423にボンディングワイヤ433により接続する。尚、ボンディングワイヤ431、432、433はAl等の金属材料により形成されている。また、本実施の形態においては、ゲート電極411はゲート電極パッドであり、第1から第3の実施の形態における半導体装置のゲート電極21と接続されている。また、ソース電極412はソース電極パッドであり、第1から第3の実施の形態における半導体装置のソース電極22と接続されている。また、ドレイン電極413はドレイン電極パッドであり、第1から第3の実施の形態における半導体装置のドレイン電極23と接続されている。

【0047】

次に、トランスファーモールド法によりモールド樹脂440による樹脂封止を行なう。このようにして、GaN系の半導体材料を用いたHEMTのディスクリートパッケージされている半導体デバイスを作製することができる。

【0048】

次に、本実施の形態における電源装置及び高周波増幅器について説明する。本実施の形態における電源装置及び高周波増幅器は、第1から第3の実施の形態における半導体装置のいずれかを用いた電源装置及び高周波増幅器である。

【0049】

最初に、図11に基づき、本実施の形態における電源装置について説明する。本実施の形態における電源装置460は、高圧の一次側回路461、低圧の二次側回路462及び一次側回路461と二次側回路462との間に配設されるトランス463を備えている。一次側回路461は、交流電源464、いわゆるブリッジ整流回路465、複数のスイッチング素子(図11に示す例では4つ)466及び一つのスイッチング素子467等を備えている。二次側回路462は、複数のスイッチング素子(図11に示す例では3つ)468を備えている。図11に示す例では、第1から第3の実施の形態における半導体装置を一次側回路461のスイッチング素子466及び467として用いている。尚、一次側回路461のスイッチング素子466及び467は、ノーマリーオフの半導体装置であることが好ましい。また、二次側回路462において用いられているスイッチング素子468はシリコンにより形成される通常のMISFET(metal insulator semiconductor field effect transistor)を用いている。

【0050】

次に、図12に基づき、本実施の形態における高周波増幅器について説明する。本実施の形態における高周波増幅器470は、例えば、携帯電話の基地局用パワーアンプに適用してもよい。この高周波増幅器470は、ディジタル・プレディストーション回路471、ミキサー472、パワーアンプ473及び方向性結合器474を備えている。ディジタル・プレディストーション回路471は、入力信号の非線形歪みを補償する。ミキサー472は、非線形歪みが補償された入力信号と交流信号とをミキシングする。パワーアンプ473は、交流信号とミキシングされた入力信号を増幅する。図12に示す例では、パワーアンプ473は、第1から第3の実施の形態における半導体装置を有している。方向性結合器474は、入力信号や出力信号のモニタリング等を行なう。図12に示す回路では、例えば、スイッチの切り替えにより、ミキサー472により出力信号を交流信号とミキシングしてディジタル・プレディストーション回路471に送出することが可能である。

【0051】

以上、実施の形態について詳述したが、特定の実施形態に限定されるものではなく、特許請求の範囲に記載された範囲内において、種々の変形及び変更が可能である。

【0052】

上記の説明に関し、更に以下の付記を開示する。

(付記1)

基板の上に形成された不純物元素を含む第1の半導体層と、

前記第1の半導体層の上に形成された第2の半導体層と、

前記第2の半導体層の上に形成された第3の半導体層と、

前記第3の半導体層の上に形成されたゲート電極、ソース電極及びドレイン電極と、

を有し、

前記第2の半導体層において、前記ゲート電極の直下には、前記第1の半導体層と接し、前記第1の半導体層に含まれる不純物元素が拡散している不純物拡散領域が形成されており、

前記不純物元素は、前記不純物拡散領域がp型となる元素であることを特徴とする半導体装置。

(付記2)

前記不純物元素は、Mgであることを特徴とする付記1に記載の半導体装置。

(付記3)

前記不純物拡散領域は、前記第3の半導体層とは接していないことを特徴とする付記1または2に記載の半導体装置。

(付記4)

前記第1の半導体層と前記第2の半導体層との間には、前記ゲート電極の形成される領域の直下に開口部を有する成長制御層が形成されていることを特徴とする付記1から3のいずれかに記載の半導体装置。

(付記5)

前記成長制御層は、AlN、AlGaN、InAlN、SiOx、SiNのいずれかを含むものにより形成されていることを特徴とする付記4に記載の半導体装置。

(付記6)

前記成長制御層は、多結晶又はアモルファスであることを特徴とする付記4または5に記載の半導体装置。

(付記7)

前記成長制御層の膜厚は、5〜50nmであることを特徴とする付記4から6のいずれかに記載の半導体装置。

(付記8)

前記第1の半導体層にドープされているp型となる不純物元素の濃度は、5×1017〜5×1019cm−3であることを特徴とする付記1から7のいずれかに記載の半導体装置。

(付記9)

前記第1の半導体層は、p型となる不純物元素を含むGaNまたはAlGaNにより形成されているものであることを特徴とする付記1から8のいずれかに記載の半導体装置。

(付記10)

前記第2の半導体層は、GaNを含む材料により形成されていることを特徴とする付記1から9のいずれかに記載の半導体装置。

(付記11)

前記第3の半導体層は、AlGaNを含む材料により形成されていることを特徴とする付記1から10のいずれかに記載の半導体装置。

(付記12)

前記第3の半導体層において、前記ゲート電極が形成される領域には凹形状のゲートリセスが設けられており、前記ゲート電極は、前記ゲートリセスの内部を含む領域に形成されていることを特徴とする付記1から11のいずれかに記載の半導体装置。

(付記13)

前記第3の半導体層と前記ゲート電極との間には、絶縁膜が設けられていることを特徴とする付記1から12のいずれかに記載の半導体装置。

(付記14)

付記1から13のいずれかに記載の半導体装置を有することを特徴とする電源装置。

(付記15)

付記1から13のいずれかに記載の半導体装置を有することを特徴とする増幅器。

(付記16)

基板の上に、不純物元素を含む第1の半導体層を形成する工程と、

前記第1の半導体層の上に、開口部を有する成長制御層を形成する工程と、

前記開口部において露出している前記第1の半導体層及び前記成長制御層の上に、第2の半導体層を形成する工程と、

前記第2の半導体層の上に、第3の半導体層を形成する工程と、

前記第3の半導体層の上に、ゲート電極、ソース電極及びドレイン電極を形成する工程と、

を有し、前記成長制御層における前記開口部は、前記ゲート電極の直下に形成されるものであって、

前記不純物元素は、前記第2の半導体層がp型となる元素であることを特徴とする半導体装置の製造方法。

(付記17)

前記不純物元素は、Mgであることを特徴とする付記16に記載の半導体装置の製造方法。

(付記18)

前記第1の半導体層、前記第2の半導体層及び前記第3の半導体層は、MOVPEにより形成されるものであることを特徴とする付記16または17に記載の半導体装置の製造方法。

(付記19)

前記成長制御層は、前記第1の半導体層、前記第2の半導体層及び前記第3の半導体層を形成する際の温度よりも低い温度により形成されることを特徴とする付記16から18のいずれかに記載の半導体装置の製造方法。

(付記20)

前記第2の半導体層は、前記成長制御層の前記開口部において露出している前記第1の半導体層上より、最初に結晶成長するものであることを特徴とする付記16から19のいずれかに記載の半導体装置の製造方法。

【符号の説明】

【0053】

11 基板

12 バッファ層

13 p型層(第1の半導体層)

14 成長制御層

15 p型拡散領域

16 電子走行層(第2の半導体層)

16a 2DEG

17 電子供給層(第3の半導体層)

21 ゲート電極

22 ソース電極

23 ドレイン電極

31 開口部

【技術分野】

【0001】

本発明は、半導体装置及び半導体装置の製造方法に関するものである。

【背景技術】

【0002】

窒化物半導体であるGaN、AlN、InN等または、これらの混晶である材料は、広いバンドギャップを有しており、高出力電子デバイスまたは短波長発光デバイス等として用いられている。このうち、高出力デバイスとしては、電界効果型トランジスタ(FET:Field-Effect Transistor)、特に、高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor)に関する技術が開発されている(例えば、特許文献1)。このような窒化物半導体を用いたHEMTは、高出力・高効率増幅器、大電力スイッチングデバイス等に用いられる。

【0003】

このような窒化物半導体を用いたHEMTは、基板上に、窒化アルミニウムガリウム/窒化ガリウム(AlGaN/GaN)ヘテロ構造が形成されており、GaN層を電子走行層とするものである。尚、基板としては、サファイア、シリコンカーバイド(SiC)、窒化ガリウム(GaN)、シリコン(Si)等の基板が用いられる。

【0004】

窒化物半導体において、GaNは、高い飽和電子速度や広いバンドギャップを有しており、高い耐圧特性を得ることができるため、優れた電気的特性を有している。また、GaNは、結晶構造がウルツ鉱型であるため、c軸に平行な<0001>方向に極性を有しており、更に、AlGaN/GaNのヘテロ構造を形成した場合には、AlGaN層には、AlGaNとGaNとの格子歪みによるピエゾ分極が励起される。このため、チャネルとなる界面には、高濃度の2DEG(Two-Dimensional Electron Gas:2次元電子ガス)が生じる。よって、このようなGaNを用いたHEMTは、高周波・電力用デバイスとして有望とされている。

【0005】

ところで、GaNを用いたHEMTでは、ピンチオフ電圧以下のオフ状態においては、ゲート電極の直下における電子走行層の下部を通り、ドレイン側からソース側にリーク電流が発生しやすいといった問題点を有している。具体的には、図1に示すように、GaNを用いたHEMTは、基板911上に、バッファ層912、電子走行層913、電子供給層914が形成されており、電子供給層914の上に、ゲート電極921、ソース電極922及びドレイン電極923が形成されている。尚、電子走行層913はGaNにより形成されており、電子供給層914はAlGaNにより形成されており、これにより、電子走行層913において、電子走行層913と電子供給層914との界面近傍には、2DEG913aが形成される。

【0006】

一般的には、電子走行層913は、結晶性を確保するため厚く形成されるが、電子走行層913を厚く形成すると、ゲート電極921の直下には、ゲート電極921に印加された電圧による電界が及ばず、電子走行層913の下部にリーク電流が流れやすくなる。即ち、ゲート電極921にゲート電圧を印加した場合等に形成される空乏領域919が電子走行層913の下部にまで広がらないため、電子走行層913の下部において矢印に示す方向にリーク電流が流れやすくなる。GaNを用いたHEMTを高出力増幅器に用いた場合において、このようなリーク電流が増加すると、増幅効率が低下してしまう。

【0007】

また、GaNを用いたHEMTは、一般的には、高濃度の2DEGによりノーマリーオンになりやすく、ノーマリーオフの特性を得ることが難しいといった問題点もあった。現在のパワーエレクトロニクス市場において用いられている半導体装置の多くは、ノーマリーオフであるため、既存の半導体装置との親和性等より、GaNを用いたHEMTにおいても、ノーマリーオフであることが強く求められている。

【0008】

このため、リーク電流を抑制する方法としては、GaN等により形成される電子走行層913の厚さを薄くする方法や、電子走行層913の下部にMgやFe等のアクセプタとなる不純物をドープし、電子走行層913の下部を高抵抗化する方法が開示されている(例えば、非特許文献1)。また、ノーマリーオフについては、Mgをドーピングした低抵抗p型GaN層を電子供給層とゲート電極との間に形成し、低抵抗p型GaN層から供給されるホールによりゲート電極の直下における2DEGの発生を抑制する方法等が開示されている(例えば、特許文献2)。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2002−359256号公報

【特許文献2】特開2010−135641号公報

【非特許文献】

【0010】

【非特許文献1】Journal of Crystal Growth 248 (2003) 513

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかしながら、所望の結晶性を確保しつつ、電子走行層913の厚さを薄くすることは極めて困難であり、逆に、オン抵抗を増大させてしまうという問題点を有している。また、図2に示すように、電子走行層913の下に、p型となる不純物元素であるMg等をドープしたp−GaN層931を形成した場合では、Mg等はGaN内を拡散しやすいため、p−GaN層931にドープされているMgが電子走行層913内を拡散する。このように電子走行層913内をMgが拡散することにより、電子走行層913内にはMgが拡散した拡散領域913bが形成されるため、電子走行層913における2DEGの濃度や、移動度が低下し、HEMTにおける特性が低下してしまう。尚、図2は、電子走行層913内をMgが拡散することにより、2DEGが消失している状態のものを示している。

【0012】

このため、半導体材料としてGaN等の窒化物半導体を用いた半導体装置において、ドレイン−ソース間におけるリーク電流を抑制することができ、ノーマリーオフにすることのできる半導体装置及び半導体装置の製造方法が求められている。

【課題を解決するための手段】

【0013】

本実施の形態の一観点によれば、基板の上に形成された不純物元素を含む第1の半導体層と、前記第1の半導体層の上に形成された第2の半導体層と、前記第2の半導体層の上に形成された第3の半導体層と、前記第3の半導体層の上に形成されたゲート電極、ソース電極及びドレイン電極と、を有し、前記第2の半導体層において、前記ゲート電極の直下には、前記第1の半導体層と接し、前記第1の半導体層に含まれる不純物元素が拡散している不純物拡散領域が形成されており、前記不純物元素は、前記不純物拡散領域がp型となる元素であることを特徴とする。

【0014】

また、本実施の形態の他の一観点によれば、基板の上に、不純物元素を含む第1の半導体層を形成する工程と、前記第1の半導体層の上に、開口部を有する成長制御層を形成する工程と、前記開口部において露出している前記第1の半導体層及び前記成長制御層の上に、第2の半導体層を形成する工程と、前記第2の半導体層の上に、第3の半導体層を形成する工程と、前記第3の半導体層の上に、ゲート電極、ソース電極及びドレイン電極を形成する工程と、を有し、前記成長制御層における前記開口部は、前記ゲート電極の直下に形成されるものであって、前記不純物元素は、前記第2の半導体層がp型となる元素であることを特徴とする。

【発明の効果】

【0015】

開示の半導体装置及び半導体装置の製造方法によれば、半導体材料としてGaN等の窒化物半導体を用いた半導体装置において、ドレイン−ソース間におけるリーク電流を抑制することができ、ノーマリーオフにすることができる。

【図面の簡単な説明】

【0016】

【図1】従来のGaNを用いたHEMTの説明図(1)

【図2】従来のGaNを用いたHEMTの説明図(2)

【図3】第1の実施の形態における半導体装置の構造図

【図4】第1の実施の形態における半導体装置の製造方法の工程図(1)

【図5】第1の実施の形態における半導体装置の製造方法の工程図(2)

【図6】第1の実施の形態における半導体装置の製造方法の工程図(3)

【図7】第2の実施の形態における半導体装置の構造図

【図8】第2の実施の形態における半導体装置の製造方法の説明図

【図9】第3の実施の形態における半導体装置の構造図

【図10】第4の実施の形態におけるディスクリートパッケージされた半導体デバイスの説明図

【図11】第4の実施の形態における電源装置の回路図

【図12】第4の実施の形態における高出力増幅器の構造図

【発明を実施するための形態】

【0017】

実施するための形態について、以下に説明する。尚、同じ部材等については、同一の符号を付して説明を省略する。

【0018】

〔第1の実施の形態〕

(半導体装置)

第1の実施の形態における半導体装置について、図1に基づき説明する。本実施の形態における半導体装置は、Si等の基板11上に、AlN等により形成されるバッファ層12、第1の半導体層であるp型となる不純物元素がドープされているp型層13が形成されている。p型層13上には、ゲート電極21の直下に開口部31を有するAlN等により形成される成長制御層14が形成されており、p型層13及び成長制御層14の上には、第2の半導体層となるp型拡散領域15及び電子走行層16が形成されている。即ち、ゲート電極21の直下に形成される開口部31において露出しているp型層13上には、p型拡散領域15が形成され、p型拡散領域15及び成長制御層14上は、電子走行層16が形成されている。尚、本実施の形態において、ゲート電極21の直下とは、電子供給層17または電子走行層16等を介したゲート電極21が形成される領域の下の領域を含むものである。更に、電子走行層16の上には、第3の半導体層となる電子供給層17が形成されており、電子供給層17の上には、ゲート電極21、ソース電極22及びドレイン電極23が形成されている。電子走行層16はGaNにより形成されており、電子供給層17はAlGaNにより形成されており、これにより、電子走行層16において、電子走行層16と電子供給層17との界面近傍には2DEG16aが形成される。p型層13にはGaNにp型となる不純物元素としてMgがドープされており、この上にGaNを結晶成長させることにより、p型層13が露出している成長制御層14の開口部31より、p型層13に含まれているMgが取り込まれp型拡散領域15が形成される。このため、p型拡散領域15を不純物拡散領域と記載する場合がある。尚、電子走行層16は、成長制御層14の上に形成されるため、Mgが取り込まれることはない。よって電子走行層16は、Mgを含まないGaNにより形成される。また、p型層13は、AlGaNにp型となる不純物元素がドープされたものであってもよい。

【0019】

このように、ゲート電極21の直下となるp型層13の上にp型拡散領域15を形成することにより、p型拡散領域15の直上、即ち、ゲート電極21の直下においては、2DEG16aにおける電子は殆ど存在しなくなり、ノーマリーオフにすることができる。更に、p型拡散領域15は高抵抗化しているため、ゲート電極21の直下となる電子走行層16の下層にp型拡散領域15を形成することにより、ドレイン電極23からソース電極22に流れるリーク電流を抑制することができる。尚、成長制御層14は、AlGaN、InAlN、SiOx、SiN等の他の窒化物により形成してもよい。

【0020】

(半導体装置の製造方法)

次に、図4〜図6に基づき、第1の実施の形態における半導体装置の製造方法について説明する。

【0021】

最初に、図4(a)に示すように、基板11上に、バッファ層12及びp型層13をMOVPE(Metal Organic Vapor Phase Epitaxy)法によりエピタキシャル成長させることにより形成する。この際、Alの原料ガスにはTMA(トリメチルアルミニウム)が用いられ、Gaの原料ガスにはTMG(トリメチルガリウム)が用いられ、Nの原料ガスにはNH3(アンモニア)が用いられる。また、不純物元素としてドープされるMgの原料ガスにはCp2Mg(シクロペンタジエニルマグネシウム)が用いられる。尚、これらの原料ガスは、水素(H2)をキャリアガスとしてMOVPE装置の反応炉に供給される。

【0022】

基板11は、サファイア、Si、SiC等により形成されており、基板11へのリーク電流を防ぐためには、抵抗の高い材料により形成された基板を用いることが好ましい。尚、本実施の形態では、基板11は、Siにより形成された基板が用いられている。

【0023】

基板11を数分間、水素雰囲気中で熱処理を行なった後に、バッファ層12を形成する。バッファ層12は、最初にAlNにより形成される層を形成し、この後、AlGaNにより形成される層を形成する。基板11に起因する転位を低減するためには、バッファ層12の膜厚は厚いほど好ましいが、クラックの発生を防ぐためには、あまり厚く形成しない方が好ましい。よって、バッファ層12の膜厚は、200〜1000nmが好ましい。また、このような構造以外にも、GaN/AlNを交互に形成した周期構造を有する超格子バッファや、AlNからGaNに至るまでAlの組成比を変化させた組成傾斜構造により形成してもよい。尚、バッファ層12を形成する際の温度は、約1000℃である。

【0024】

バッファ層12の上には、p型層13を形成する。p型層13は、GaNに不純物元素としてMgがドープされたものであり、膜厚が100〜300nmとなるように形成されている。尚、過剰にMgをドープした場合、p型層13及びp型層13上に形成される電子走行層16等において結晶性が劣化するため、Mgがドーピングされる濃度は、5×1017〜5×1019cm−3が好ましい。本実施の形態では、1×1019cm−3の濃度のMgがドープされている。また、本実施の形態では、p型不純物としてMgの場合について説明しているが、p型となるものであれば他の不純物元素であってもよい。

【0025】

次に、図4(b)に示すように、p型層13の上に成長制御層14を形成するためのAlN膜14aを形成する。具体的には、MOVPE、スパッタリング等により、AlN膜14aを形成する。MOVPEによりAlN膜14aを形成する際、500〜800℃の成長温度でAlN膜14aを形成する。一般的に、p型層13及び後述する電子走行層16及び電子供給層17をMOVPEにより形成する場合には、成長温度が約1000℃、または、それ以上の温度で形成されるが、AlN膜14aは、この温度よりも低い温度で形成される。このように、AlN膜14aは、通常の成膜温度よりも低い温度で形成されるため、特に、低温成長AlN(LT−AlN:Low Temperature AlN)とも呼ばれている。このように低温でAlN膜14aを形成することにより、形成されるAlN膜14aは多結晶状態の膜となる。尚、形成されるAlN膜14aは、多結晶状態の膜であってもアモルファス状態の膜であってもよい。また、形成されるAlN膜14aの膜厚は、5〜50nmである。

【0026】

次に、図5(a)に示すように、AlN膜14aに開口部31を形成することにより、成長制御層14を形成する。具体的には、AlN膜14aの全面にフォトレジストを塗布し、露光装置による露光、現像を行なうことにより、開口部31に開口を有する不図示のレジストパターンを形成する。この後、RIE(Reactive Ion Etching)等により、レジストパターンの形成されていない領域のAlN膜14aを除去し、更に、有機溶剤等によりレジストパターンを除去する。これにより、AlNにより形成される成長制御層14を形成することができる。

【0027】

次に、図5(b)に示すように、成長制御層14が形成されている面に、MOVPEによりp型拡散領域15及び電子走行層16を形成し、更に、電子走行層16上に電子供給層17を形成する。p型拡散領域15及び電子走行層16は、ともにGaNを結晶成長させることにより形成されている。p型拡散領域15及び電子走行層16を形成しているGaNは、最初に、成長制御層14が形成されていないp型層13が露出している開口部31において、p型層13における不純物元素であるMgを取り込みながら成長し、p型拡散領域15が形成される。一般に、GaNは成長モードが2次元的になりやすく、厚く成膜するほど平坦な膜が得られやすいことが知られている。しかしながら、形成されるp型拡散領域15は成長制御層14が形成されていない領域にのみ形成されていることが好ましいため、3次元成長が支配的となる条件、例えば、圧力の高い条件等により形成する。p型拡散領域15が所望の膜厚となるように形成した後は、GaNが2次元的に成長する条件により電子走行層16を形成する。この際、転位等に起因した2DEG16aにおける電子密度の低下や、移動度の低下を避けるため、電子走行層16は、膜厚が500〜1000nmとなるように形成する。これにより、ゲート電極21の直下となる成長制御層14の開口部31において露出しているp型層13上にはp型拡散領域15が形成され、p型拡散領域15及び成長制御層14上には、GaNによる電子走行層16が形成される。尚、本実施の形態においては、p型拡散領域15は、電子走行層16の表面より数100nm下に、p型拡散領域15と電子走行層16との界面が位置するように形成されている。また、成長制御層14は、上述したMgの拡散を防ぐとともに、成長制御層14上に形成される電子走行層16を形成する際の成長核形成層としての機能も有している。

【0028】

この後、電子走行層16の上には、電子供給層17が形成されるが、電子供給層17は、AlGaNの膜厚が約20nmとなるように形成する。電子供給層17は、格子不整合による結晶性の劣化を避けるため、電子供給層17をAlXGa1−XNと表わした場合に、Xの値が0.3以下となるように形成されている。

【0029】

次に、図6に示すように、電子供給層17上に、ゲート電極21、ソース電極22及びドレイン電極23を形成する。具体的には、電子供給層17上にフォトレジストを塗布し、露光装置による露光、現像を行なうことにより、ソース電極22及びドレイン電極23が形成される領域に開口を有する不図示のレジストパターンを形成する。この後、真空蒸着等の成膜方法により金属膜を成膜した後、有機溶剤等に浸漬させることによりレジストパターンの上に形成されている金属膜をレジストパターンとともに除去する。これにより、ソース電極22及びドレイン電極23を形成する。次に、再度、電子供給層17上にフォトレジストを塗布し、露光装置による露光、現像を行なうことにより、ゲート電極21が形成される領域に開口を有する不図示のレジストパターンを形成する。この後、真空蒸着等の成膜方法により金属膜を成膜した後、有機溶剤等に浸漬させることによりレジストパターンの上に形成されている金属膜をレジストパターンとともに除去する。これにより、ゲート電極21を形成する。

【0030】

以上により、本実施の形態における半導体装置であるGaNを用いたHEMTを製造することができる。

【0031】

〔第2の実施の形態〕

(半導体装置)

次に、第2の実施の形態における半導体装置について、図7に基づき説明する。本実施の形態における半導体装置は、ゲート電極近傍にゲートリセスを形成した構造のものである。

【0032】

具体的には、本実施の形態における半導体装置は、Si等の基板11上に、AlN等により形成されるバッファ層12、第1の半導体層であるp型となる不純物元素がドープされているp型層13が形成されている。p型層13上には、ゲート電極21の直下に開口部31を有するAlN等により形成される成長制御層14が形成されており、p型層13及び成長制御層14の上には、第2の半導体層となるp型拡散領域15及び電子走行層16が形成されている。即ち、ゲート電極21の直下となる開口部31において露出しているp型層13上には、p型拡散領域15が形成され、p型拡散領域15及び成長制御層14上は、電子走行層16が形成されている。更に、電子走行層16の上には、第3の半導体層となる電子供給層17が形成されており、電子供給層17の表面には、ゲート電極21が形成される領域に凹形状のゲートリセス131が形成されている。ゲート電極21は、ゲートリセス131の内部を含む領域の電子走行層17等の上に形成されており、ソース電極22及びドレイン電極23は電子供給層17の上に形成されている。電子走行層16はGaNにより形成されており、電子供給層17はAlGaNにより形成されており、これにより、電子走行層16において、電子走行層16と電子供給層17との界面近傍には2DEG16aが形成される。p型層13にはGaNにp型となる不純物元素としてMgがドープされており、この上にGaNを結晶成長させることにより、p型層13が露出している成長制御層14の開口部31より、p型層13に含まれるMgが取り込まれp型拡散領域15が形成される。このため、p型拡散領域15を不純物拡散領域と記載する場合がある。尚、電子走行層16は、成長制御層14の上に形成されるため、Mgが取り込まれることはない。よって、電子走行層16は、Mgを含まないGaNにより形成することができる。

【0033】

このように、ゲート電極21の直下となるp型層13の上にp型拡散領域15を形成することにより、p型拡散領域15の直上、即ち、ゲート電極21の直下においては、2DEG16aにおける電子は殆ど存在しなくなり、ノーマリーオフにすることができる。更に、本実施の形態では、ゲートリセス131が形成されているため、より一層ノーマリーオフになりやすい。更に、p型拡散領域15は高抵抗化しているため、ゲート電極21の直下となる電子走行層16の下層にp型拡散領域15を形成することにより、ドレイン電極23からソース電極22に流れるリーク電流を抑制することができる。

【0034】

(半導体装置の製造方法)

次に、第2の実施の形態における半導体装置の製造方法について説明する。本実施の形態における半導体装置の製造方法は、第1の実施の形態における図5(b)まで形成した後、ゲートリセス131を形成する。

【0035】

具体的には、第1の実施の形態における半導体装置の製造方法の図4(a)〜図5(b)に示される工程と同様の工程により、図5(b)に示すものを作製した後、図8(a)に示されるように、電子供給層17の表面に凹形状のゲートリセス131を形成する。ゲートリセス131は、電子供給層17の表面において、ゲート電極21が形成される領域に形成される。具体的には、電子供給層17の表面にフォトレジストを塗布し、露光装置による露光、現像を行なうことにより、ゲートリセス131が形成される領域に開口を有する不図示のレジストパターンを形成する。この後、RIE等により、レジストパターンの形成されていない領域の電子走行層17を所望の深さまで除去することによりゲートリセス131を形成する。この後、有機溶剤等によりレジストパターンを除去する。

【0036】

次に、図8(b)に示すように、電子供給層17上にゲート電極21、ソース電極22及びドレイン電極23を形成する。具体的には、電子供給層17上にフォトレジストを塗布し、露光装置による露光、現像を行なうことにより、ソース電極22及びドレイン電極23が形成される領域に開口を有する不図示のレジストパターンを形成する。この後、真空蒸着等の成膜方法により金属膜を成膜した後、有機溶剤等に浸漬させることによりレジストパターンの上に形成されている金属膜をレジストパターンとともに除去する。これにより、ソース電極22及びドレイン電極23を形成する。次に、再度、電子供給層17上にフォトレジストを塗布し、露光装置による露光、現像を行なうことにより、ゲート電極21が形成される領域に開口を有する不図示のレジストパターンを形成する。この際、ゲート電極21が電子供給層17の表面に形成されているゲートリセス131の内部等に形成されるように位置合せを行なう。即ち、ゲート電極21が形成されるレジストパターンの開口には、ゲートリセス131が露出するように位置合せを行いレジストパターンを形成する。この後、真空蒸着等の成膜方法により金属膜を成膜した後、有機溶剤等に浸漬させることによりレジストパターンの上に形成されている金属膜をレジストパターンとともに除去する。これにより、ゲート電極21を形成する。

【0037】

以上により、本実施の形態における半導体装置であるGaNを用いたHEMTを製造することができる。尚、上記以外の内容については、第1の実施の形態と同様である。

【0038】

〔第3の実施の形態〕

次に、第3の実施の形態における半導体装置について、図9に基づき説明する。本実施の形態における半導体装置は、電子供給層17上にゲート絶縁膜となる絶縁膜140が形成されている構造のものである。このような絶縁膜140を形成することにより、ゲートリーク電流を減らすことができる。絶縁膜140としては、例えば、Al2O3(酸化アルミニウム)等が用いられる。

【0039】

本実施の形態における半導体装置は、第1の実施の形態における図5(b)まで形成したものの電子供給層17上に、ソース電極22及びドレイン電極23を形成し、この後、ゲート絶縁膜となる絶縁膜140を形成する。絶縁膜140の形成方法としては、CVD(Chemical Vapor Deposition)、ALD(Atomic Layer Deposition)、スパッタリング等が挙げられる。

【0040】

この後、絶縁膜140上の所定の領域、即ち、絶縁膜140上であって、p型拡散領域15が形成されている領域の上に、ゲート電極21を形成する。

【0041】

これにより、本実施の形態における半導体装置を製造することができる。

【0042】

尚、上記以外の内容は、第1の実施の形態と同様である。また、本実施の形態は、第2の実施の形態における半導体装置においても適用することができる。

【0043】

〔第4の実施の形態〕

次に、第4の実施の形態について説明する。本実施の形態は、半導体デバイス、電源装置及び高周波増幅器である。

【0044】

本実施の形態における半導体デバイスは、第1から第3の実施の形態におけるいずれかの半導体装置をディスクリートパッケージしたものであり、このようにディスクリートパッケージされた半導体デバイスについて、図10に基づき説明する。尚、図10は、ディスクリートパッケージされた半導体装置の内部を模式的に示すものであり、電極の配置等については、第1から第3の実施の形態に示されているものとは、異なっている。

【0045】

最初に、第1から第3の実施の形態において製造された半導体装置をダイシング等により切断することにより、GaN系の半導体材料のHEMTの半導体チップ410を形成する。この半導体チップ410をリードフレーム420上に、ハンダ等のダイアタッチ剤430により固定する。尚、この半導体チップ410は、第1から第3の実施の形態における半導体装置に相当するものである。

【0046】

次に、ゲート電極411をゲートリード421にボンディングワイヤ431により接続し、ソース電極412をソースリード422にボンディングワイヤ432により接続し、ドレイン電極413をドレインリード423にボンディングワイヤ433により接続する。尚、ボンディングワイヤ431、432、433はAl等の金属材料により形成されている。また、本実施の形態においては、ゲート電極411はゲート電極パッドであり、第1から第3の実施の形態における半導体装置のゲート電極21と接続されている。また、ソース電極412はソース電極パッドであり、第1から第3の実施の形態における半導体装置のソース電極22と接続されている。また、ドレイン電極413はドレイン電極パッドであり、第1から第3の実施の形態における半導体装置のドレイン電極23と接続されている。

【0047】

次に、トランスファーモールド法によりモールド樹脂440による樹脂封止を行なう。このようにして、GaN系の半導体材料を用いたHEMTのディスクリートパッケージされている半導体デバイスを作製することができる。

【0048】

次に、本実施の形態における電源装置及び高周波増幅器について説明する。本実施の形態における電源装置及び高周波増幅器は、第1から第3の実施の形態における半導体装置のいずれかを用いた電源装置及び高周波増幅器である。

【0049】

最初に、図11に基づき、本実施の形態における電源装置について説明する。本実施の形態における電源装置460は、高圧の一次側回路461、低圧の二次側回路462及び一次側回路461と二次側回路462との間に配設されるトランス463を備えている。一次側回路461は、交流電源464、いわゆるブリッジ整流回路465、複数のスイッチング素子(図11に示す例では4つ)466及び一つのスイッチング素子467等を備えている。二次側回路462は、複数のスイッチング素子(図11に示す例では3つ)468を備えている。図11に示す例では、第1から第3の実施の形態における半導体装置を一次側回路461のスイッチング素子466及び467として用いている。尚、一次側回路461のスイッチング素子466及び467は、ノーマリーオフの半導体装置であることが好ましい。また、二次側回路462において用いられているスイッチング素子468はシリコンにより形成される通常のMISFET(metal insulator semiconductor field effect transistor)を用いている。

【0050】

次に、図12に基づき、本実施の形態における高周波増幅器について説明する。本実施の形態における高周波増幅器470は、例えば、携帯電話の基地局用パワーアンプに適用してもよい。この高周波増幅器470は、ディジタル・プレディストーション回路471、ミキサー472、パワーアンプ473及び方向性結合器474を備えている。ディジタル・プレディストーション回路471は、入力信号の非線形歪みを補償する。ミキサー472は、非線形歪みが補償された入力信号と交流信号とをミキシングする。パワーアンプ473は、交流信号とミキシングされた入力信号を増幅する。図12に示す例では、パワーアンプ473は、第1から第3の実施の形態における半導体装置を有している。方向性結合器474は、入力信号や出力信号のモニタリング等を行なう。図12に示す回路では、例えば、スイッチの切り替えにより、ミキサー472により出力信号を交流信号とミキシングしてディジタル・プレディストーション回路471に送出することが可能である。

【0051】

以上、実施の形態について詳述したが、特定の実施形態に限定されるものではなく、特許請求の範囲に記載された範囲内において、種々の変形及び変更が可能である。

【0052】

上記の説明に関し、更に以下の付記を開示する。

(付記1)

基板の上に形成された不純物元素を含む第1の半導体層と、

前記第1の半導体層の上に形成された第2の半導体層と、

前記第2の半導体層の上に形成された第3の半導体層と、

前記第3の半導体層の上に形成されたゲート電極、ソース電極及びドレイン電極と、

を有し、

前記第2の半導体層において、前記ゲート電極の直下には、前記第1の半導体層と接し、前記第1の半導体層に含まれる不純物元素が拡散している不純物拡散領域が形成されており、

前記不純物元素は、前記不純物拡散領域がp型となる元素であることを特徴とする半導体装置。

(付記2)

前記不純物元素は、Mgであることを特徴とする付記1に記載の半導体装置。

(付記3)

前記不純物拡散領域は、前記第3の半導体層とは接していないことを特徴とする付記1または2に記載の半導体装置。

(付記4)

前記第1の半導体層と前記第2の半導体層との間には、前記ゲート電極の形成される領域の直下に開口部を有する成長制御層が形成されていることを特徴とする付記1から3のいずれかに記載の半導体装置。

(付記5)

前記成長制御層は、AlN、AlGaN、InAlN、SiOx、SiNのいずれかを含むものにより形成されていることを特徴とする付記4に記載の半導体装置。

(付記6)

前記成長制御層は、多結晶又はアモルファスであることを特徴とする付記4または5に記載の半導体装置。

(付記7)

前記成長制御層の膜厚は、5〜50nmであることを特徴とする付記4から6のいずれかに記載の半導体装置。

(付記8)

前記第1の半導体層にドープされているp型となる不純物元素の濃度は、5×1017〜5×1019cm−3であることを特徴とする付記1から7のいずれかに記載の半導体装置。

(付記9)

前記第1の半導体層は、p型となる不純物元素を含むGaNまたはAlGaNにより形成されているものであることを特徴とする付記1から8のいずれかに記載の半導体装置。

(付記10)

前記第2の半導体層は、GaNを含む材料により形成されていることを特徴とする付記1から9のいずれかに記載の半導体装置。

(付記11)

前記第3の半導体層は、AlGaNを含む材料により形成されていることを特徴とする付記1から10のいずれかに記載の半導体装置。

(付記12)

前記第3の半導体層において、前記ゲート電極が形成される領域には凹形状のゲートリセスが設けられており、前記ゲート電極は、前記ゲートリセスの内部を含む領域に形成されていることを特徴とする付記1から11のいずれかに記載の半導体装置。

(付記13)

前記第3の半導体層と前記ゲート電極との間には、絶縁膜が設けられていることを特徴とする付記1から12のいずれかに記載の半導体装置。

(付記14)

付記1から13のいずれかに記載の半導体装置を有することを特徴とする電源装置。

(付記15)

付記1から13のいずれかに記載の半導体装置を有することを特徴とする増幅器。

(付記16)

基板の上に、不純物元素を含む第1の半導体層を形成する工程と、

前記第1の半導体層の上に、開口部を有する成長制御層を形成する工程と、

前記開口部において露出している前記第1の半導体層及び前記成長制御層の上に、第2の半導体層を形成する工程と、

前記第2の半導体層の上に、第3の半導体層を形成する工程と、

前記第3の半導体層の上に、ゲート電極、ソース電極及びドレイン電極を形成する工程と、

を有し、前記成長制御層における前記開口部は、前記ゲート電極の直下に形成されるものであって、

前記不純物元素は、前記第2の半導体層がp型となる元素であることを特徴とする半導体装置の製造方法。

(付記17)

前記不純物元素は、Mgであることを特徴とする付記16に記載の半導体装置の製造方法。

(付記18)

前記第1の半導体層、前記第2の半導体層及び前記第3の半導体層は、MOVPEにより形成されるものであることを特徴とする付記16または17に記載の半導体装置の製造方法。

(付記19)

前記成長制御層は、前記第1の半導体層、前記第2の半導体層及び前記第3の半導体層を形成する際の温度よりも低い温度により形成されることを特徴とする付記16から18のいずれかに記載の半導体装置の製造方法。

(付記20)

前記第2の半導体層は、前記成長制御層の前記開口部において露出している前記第1の半導体層上より、最初に結晶成長するものであることを特徴とする付記16から19のいずれかに記載の半導体装置の製造方法。

【符号の説明】

【0053】

11 基板

12 バッファ層

13 p型層(第1の半導体層)

14 成長制御層

15 p型拡散領域

16 電子走行層(第2の半導体層)

16a 2DEG

17 電子供給層(第3の半導体層)

21 ゲート電極

22 ソース電極

23 ドレイン電極

31 開口部

【特許請求の範囲】

【請求項1】

基板の上に形成された不純物元素を含む第1の半導体層と、

前記第1の半導体層の上に形成された第2の半導体層と、

前記第2の半導体層の上に形成された第3の半導体層と、

前記第3の半導体層の上に形成されたゲート電極、ソース電極及びドレイン電極と、

を有し、

前記第2の半導体層において、前記ゲート電極の直下には、前記第1の半導体層と接し、前記第1の半導体層に含まれる不純物元素が拡散している不純物拡散領域が形成されており、

前記不純物元素は、前記不純物拡散領域がp型となる元素であることを特徴とする半導体装置。

【請求項2】

前記不純物元素は、Mgであることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第1の半導体層と前記第2の半導体層との間には、前記ゲート電極の形成される領域の直下に開口部を有する成長制御層が形成されていることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

前記成長制御層は、AlN、AlGaN、InAlN、SiOx、SiNのいずれかを含むものにより形成されていることを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記第1の半導体層は、p型となる不純物元素を含むGaNまたはAlGaNにより形成されているものであることを特徴とする請求項1から4のいずれかに記載の半導体装置。

【請求項6】

前記第2の半導体層は、GaNを含む材料により形成されていることを特徴とする請求項1から5のいずれかに記載の半導体装置。

【請求項7】

前記第3の半導体層において、前記ゲート電極が形成される領域には凹形状のゲートリセスが設けられており、前記ゲート電極は、前記ゲートリセスの内部を含む領域に形成されていることを特徴とする請求項1から6のいずれかに記載の半導体装置。

【請求項8】

基板の上に、不純物元素を含む第1の半導体層を形成する工程と、

前記第1の半導体層の上に、開口部を有する成長制御層を形成する工程と、

前記開口部において露出している前記第1の半導体層及び前記成長制御層の上に、第2の半導体層を形成する工程と、

前記第2の半導体層の上に、第3の半導体層を形成する工程と、

前記第3の半導体層の上に、ゲート電極、ソース電極及びドレイン電極を形成する工程と、

を有し、前記成長制御層における前記開口部は、前記ゲート電極の直下に形成されるものであって、

前記不純物元素は、前記第2の半導体層がp型となる元素であることを特徴とする半導体装置の製造方法。

【請求項9】

前記不純物元素は、Mgであることを特徴とする請求項8に記載の半導体装置の製造方法。

【請求項10】

前記第1の半導体層、前記第2の半導体層及び前記第3の半導体層は、MOVPEにより形成されるものであることを特徴とする請求項8または9に記載の半導体装置の製造方法。

【請求項1】

基板の上に形成された不純物元素を含む第1の半導体層と、

前記第1の半導体層の上に形成された第2の半導体層と、

前記第2の半導体層の上に形成された第3の半導体層と、

前記第3の半導体層の上に形成されたゲート電極、ソース電極及びドレイン電極と、

を有し、

前記第2の半導体層において、前記ゲート電極の直下には、前記第1の半導体層と接し、前記第1の半導体層に含まれる不純物元素が拡散している不純物拡散領域が形成されており、

前記不純物元素は、前記不純物拡散領域がp型となる元素であることを特徴とする半導体装置。

【請求項2】

前記不純物元素は、Mgであることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第1の半導体層と前記第2の半導体層との間には、前記ゲート電極の形成される領域の直下に開口部を有する成長制御層が形成されていることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

前記成長制御層は、AlN、AlGaN、InAlN、SiOx、SiNのいずれかを含むものにより形成されていることを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記第1の半導体層は、p型となる不純物元素を含むGaNまたはAlGaNにより形成されているものであることを特徴とする請求項1から4のいずれかに記載の半導体装置。

【請求項6】

前記第2の半導体層は、GaNを含む材料により形成されていることを特徴とする請求項1から5のいずれかに記載の半導体装置。

【請求項7】

前記第3の半導体層において、前記ゲート電極が形成される領域には凹形状のゲートリセスが設けられており、前記ゲート電極は、前記ゲートリセスの内部を含む領域に形成されていることを特徴とする請求項1から6のいずれかに記載の半導体装置。

【請求項8】

基板の上に、不純物元素を含む第1の半導体層を形成する工程と、

前記第1の半導体層の上に、開口部を有する成長制御層を形成する工程と、

前記開口部において露出している前記第1の半導体層及び前記成長制御層の上に、第2の半導体層を形成する工程と、

前記第2の半導体層の上に、第3の半導体層を形成する工程と、

前記第3の半導体層の上に、ゲート電極、ソース電極及びドレイン電極を形成する工程と、

を有し、前記成長制御層における前記開口部は、前記ゲート電極の直下に形成されるものであって、

前記不純物元素は、前記第2の半導体層がp型となる元素であることを特徴とする半導体装置の製造方法。

【請求項9】

前記不純物元素は、Mgであることを特徴とする請求項8に記載の半導体装置の製造方法。

【請求項10】

前記第1の半導体層、前記第2の半導体層及び前記第3の半導体層は、MOVPEにより形成されるものであることを特徴とする請求項8または9に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−74210(P2013−74210A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−213472(P2011−213472)

【出願日】平成23年9月28日(2011.9.28)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月28日(2011.9.28)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]