半導体装置及び半導体装置を実装した回路装置

【課題】 アンダーフィルの未充填部分が生じない半導体装置を提案するとともに、この半導体装置を用いて、応力によるバンプやポスト電極のクラックを防止することができる回路装置を提案する。

【解決手段】 半導体装置2は半導体装置2aと、該半導体装置2aの下面に所定の端子間ピッチPで形成された端子3と、該端子3上に形成された柱状の金属のポスト電極6と、を有している。ポスト電極6は、互いに異なる2つの金属で構成されており、端子3に接合されている側が第一の金属部分6aで構成され、半田バンプ7が形成されている側が第二の金属部分6bで構成されている。第一の金属部分6aの幅方向の寸法W1は、第二の金属部分6bの幅方向の寸法W2よりも小さく形成されている。

【解決手段】 半導体装置2は半導体装置2aと、該半導体装置2aの下面に所定の端子間ピッチPで形成された端子3と、該端子3上に形成された柱状の金属のポスト電極6と、を有している。ポスト電極6は、互いに異なる2つの金属で構成されており、端子3に接合されている側が第一の金属部分6aで構成され、半田バンプ7が形成されている側が第二の金属部分6bで構成されている。第一の金属部分6aの幅方向の寸法W1は、第二の金属部分6bの幅方向の寸法W2よりも小さく形成されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線基板上に実装される半導体装置と、この半導体装置が実装された回路装置に関するものである。

【背景技術】

【0002】

電子機器に搭載される無線モジュールや電源モジュール等の回路装置は、集積回路(IC)等の半導体装置及びその他の受動部品をセラミック配線基板や樹脂製のプリント配線基板上に実装して形成される。近年は、電子機器の小型化が進んでおり、回路装置にも小型化の要求がなされている。回路装置において半導体装置が占める実装面積は比較的大きいので、その実装面積を小さくするために、フリップチップ実装による半導体装置の実装が用いられている。

【0003】

フリップチップ実装は、図13に示すように、半導体チップ12aの下面(配線基板14と向かい合う面)に端子間ピッチP1で設けられた端子13に直接または該端子に形成された柱状電極(ポスト電極)16にバンプ17を形成した半導体装置12を、バンプ17と配線基板14上のランド(電子部品等の端子電極を接合する導体)15とを接合するようにして配線基板14上に実装するものである。

【0004】

半導体装置12を実装した配線基板14は、半導体チップ12aと配線基板14との熱膨張係数の差に起因する応力を受ける。また、曲げやたわみなどの機械的な応力も受ける。これらの応力がバンプ17やポスト電極16に集中してクラックが発生することがある。このような応力を緩和するため、特開2002−313993号公報に開示されているように、半導体装置と配線基板との間に形成された空間に樹脂を充填して、アンダーフィルを充填する手法が広く行われている。このようなアンダーフィルは通常次のようにして充填される。まず配線基板上に実装した半導体装置の周囲にエポキシ樹脂等の硬化性樹脂をシリンジ等で吐出させて塗布する。このとき硬化性樹脂がバンプとバンプの間またはポスト電極とポスト電極の間を通って半導体装置と配線基板との間の空間に引き込まれて充填される。そして充填された樹脂を硬化させることによりアンダーフィルが充填される。

【0005】

【特許文献1】特開2002−313993号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

近年、半導体装置のデザインルールの微細化が進んでいる。その結果半導体チップのサイズが小さくなり、図13に示す端子間のピッチP1が狭くなる傾向にある。端子間のピッチが図14に示す端子間ピッチP2のように狭くなると、図13に示すバンプ間またはポスト電極間の距離PLXが、図14に示すバンプ間またはポスト電極間の距離PLYのように狭くなるので、硬化性樹脂が半導体装置22と配線基板24との間の空間に引き込まれにくくなる。その結果、半導体装置22と配線基板24との間の空間にアンダーフィルが充填されない部分が発生することがあった。

【0007】

本発明は、このような問題を解決して、アンダーフィルの未充填部分が生じない半導体装置を提案するとともに、この半導体装置を用いて、応力によるバンプやポスト電極のクラックを防止することができる回路装置を提案するものである。

【課題を解決するための手段】

【0008】

本発明では第一の解決手段として、半導体チップと、該半導体チップの下面に複数個並べて設けられた端子と、前記端子に一方の端部が接合された柱状の金属で形成されたポスト電極と、前記ポスト電極の他方の端部に形成された半田バンプと、を有する半導体装置において、前記ポスト電極は、前記端子に接合された側の第一の金属部分と、前記半田バンプが形成された側の第二の金属部分と、で構成され、前記第一の金属部分の幅方向の寸法が、前記第二の金属部分の幅方向の寸法よりも小さい半導体装置を提案する。

【0009】

上記第一の解決手段によれば、半導体装置のポスト電極間の距離が、第一の金属部分で端子間のピッチより広くなるので、この部分からアンダーフィルが入り込みやすくなる。その結果、半導体装置のデザインルールの微細化によって端子間のピッチが狭くなっても、半導体装置と配線基板との間の空間にアンダーフィルが充填されやすくなり、未充填部分が生じないようにできる。なお、配線基板側に接合される第二の金属部分は第一の金属部分よりも幅方向の寸法が広いので、ランドとの接合面積を大きく確保することができる。その結果、接合強度が充分に得られる。

【0010】

また、本発明では第二の解決手段として、上記第一の解決手段に加えて、前記第一の金属部分の長さが、前記第二の金属部分の長さよりも長い半導体装置を提案する。この第二の解決手段によれば、ポスト電極間の距離が半導体装置の端子間のピッチよりも広い第一の金属部分が多くなる。これによって、アンダーフィルが入り込みやすい部分を大きく確保できる。

【0011】

また、本発明では第三の解決手段として、半導体チップと、該半導体チップの下面に複数個並べて設けられた端子と、前記端子に一方の端部が接合された柱状の金属で形成されたポスト電極と、前記ポスト電極の他方の端部に形成された半田バンプと、を有する半導体装置が配線基板上にフリップチップ実装されており、前記配線基板と前記半導体装置との間に形成された空間にアンダーフィルが充填されている回路装置において、前記ポスト電極は、前記端子に接合された側の第一の金属部分と、前記半田バンプが形成された側の第二の金属部分と、で構成され、前記第一の金属部分の幅方向の寸法が、前記第二の金属部分の幅方向の寸法よりも小さい回路装置を提案する。

【0012】

上記第三の解決手段によれば、半導体装置と配線基板との間の空間に硬化性樹脂が充填されて、アンダーフィルが未充填の部分が発生しにくい回路装置が得られる。このような回路装置は応力によるバンプやポスト電極のクラックを防止する効果が高いので、信頼性が高くなる。

【発明の効果】

【0013】

本発明によれば、アンダーフィルの未充填部分が生じない半導体装置が得られるとともに、応力によるバンプやポスト電極のクラックを防止して信頼性の高い回路装置を得ることができる。

【発明を実施するための最良の形態】

【0014】

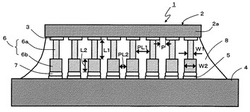

本発明の半導体装置及び回路装置に係る実施の形態について、図1に基づいて説明する。図1は本発明の回路装置の半導体装置を実装した部分を模式的に示す断面図である。回路装置1は配線基板4上にフリップチップ実装された半導体装置2を有している。なお、その他の配線導体や電子部品はここでは省略している。

【0015】

半導体装置2は、下面に所定の端子間ピッチPで形成された端子3を備えた半導体チップと、この半導体チップの端子3に接合されている柱状の金属で形成されたポスト電極6と、このポスト電極6の、端子3と接合されている側と反対側の先端に形成されている半田バンプ7と、を有している。半田バンプ7は、配線基板4上に形成されたランド5に接合されている。そして、半導体装置2と配線基板4との間の空間は、エポキシ樹脂等のアンダーフィル8が充填されている。

【0016】

ポスト電極6は、互いに異なる2つの金属で構成されており、端子3に接合されている側が第一の金属部分6aで構成され、半田バンプ7が形成されている側が第二の金属部分6bで構成されている。第一の金属部分6a及び第二の金属部分6bに用いられる金属としては、Cu、Ni、Cr、Au等がある。ポスト電極6の形状は円柱形状または角柱形状等がある。

【0017】

第一の金属部分6aの幅方向の寸法W1は、第二の金属部分6bの幅方向の寸法W2よりも小さく形成されている。幅方向の寸法は、円柱であればその直径、角柱であれば一辺の長さもしくは対角線の長さである。このようにW1<W2であれば、隣接するポスト電極6間の、第一の金属部分6aにおける距離PL1が、半導体装置2の端子3の端子間ピッチPよりも大きくなる。そのため、デザインルールの微細化によって端子間ピッチPが狭くなっても、第一の金属部分6aの形成部分からアンダーフィルが入り込みやすくなる。その結果、アンダーフィル8の未充填部分が生じないように、半導体装置2と配線基板4との間の空間に充填することができるようになる。

【0018】

なお、第一の金属部分6aの長さL1が、第二の金属部分6bの長さL2よりも長く形成されていると好ましい。第ニの金属部分6bにおける距離PL2は第一の金属部分6aにおける距離PL1よりも小さいので、第二の金属部分6bはできるだけ少ない方が好ましい。しかしながら、第ニの金属部分6bは配線基板4との接合を確保する役目を持っており、充分な接合強度を得るための接合面積を備える必要がある。よってL1>L2とすることで、アンダーフィルの入り込みやすさと配線基板4との接合強度とを両立させることができる。

【0019】

次に本発明の半導体装置2を形成するプロセスを図2〜図12に基づいて説明する。なお、半導体装置2は、Al金属で構成された端子3が端子ピッチ60μmで形成されている半導体チップ2aと、第一の金属部分6aがW1=直径20μm、L1=40μmのCuの円柱であり第二の金属部分6bがW2=直径40μm、L2=20μmのNiの円柱であるポスト電極6を有しているものを例にとって説明する。

【0020】

まず、半導体チップ2aを用意する。図2に示すように、半導体チップ2aを、端子3が形成されている方すなわち下面を上に向けて用意する。次に図3に示すように、半導体チップ2aの上に、スパッタまたは蒸着法によって、端子3を覆うようにしてシード層9を形成する。このシード層9は、後に形成するポスト電極6の第一の金属部分6aを構成する金属と略同じ種類の金属またはその合金で形成される。ここでは第一の金属部分6aがCuなので、シード層9はCuが用いられる。

【0021】

次に図4に示すように、シード層9上にメッキレジスト膜REを塗布形成する。このメッキレジスト膜REにはフォトレジストが用いられる。このメッキレジスト膜REに、半導体装置2上の端子3に対応するパターンを備えたフォトマスク(図示せず)を通して光を当てて感光し、その後現像して、図5に示すように、半導体チップ2a上の端子3に対応する位置に開口部OPを形成する。フォトレジストには光が当った部分が除去されるポジ型フォトレジストを用いても良いし、光が当った部分が不溶化するネガ型フォトレジスを用いても良い。ポジ型フォトレジストを用いる場合は開口部OPのパターン形状で光を通すフォトマスクを用い、ネガ型フォトレジストを用いる場合は開口部OPのパターン形状で光を遮断するフォトマスクを用いる。開口部OPの大きさは、第二の金属部分6bの幅方向の寸法W2と略同じすなわち直径40μmになるように形成される。

【0022】

次に図6に示すように、電解Cuメッキによって第一の金属部分6aを形成する。電流がシード層9を通じて流れるので、Cuは開口部OP内のシード層9上に析出する。第一の金属部分6aの長さL1は、電解Cuメッキの電流密度や通電時間によって調節が可能である。ここではL1が40μmになるように調節する。次に図7に示すように、電解Niメッキによって第二の金属部分6bを形成する。このときも電流がシード層9及び第一の金属部分6aを通じて流れるので、Niは開口部OP内のCu上に析出する。なお、第ニの金属部分6bの長さL2についても、電解Cuメッキの電流密度や通電時間によって調節が可能である。ここではL2が20μmになるように調節する。次に図8に示すように、電解半田メッキによって半田バンプ7となる半田層を形成する。半田バンプ7の材質は、Sn−Ag、Sn−Cu、Sn−Pb、Sn−Zn等のSn合金が用いられる。半田層は開口部OP内に形成されるので、この段階ではポスト電極6と略同じ直径40μmの円柱状に形成される。

【0023】

次に図9に示すように、メッキレジスト膜REを除去する。このようにして、シード層9上の、半導体チップ2a上の端子3に対応する位置に、第一の金属部分6a、第二の金属部分6b及び半田層で形成された直径40μmの柱状の金属が現れる。次に図10に示すように、エッチングによってシード層9を除去する。エッチング液はCuを選択的にエッチングするものを用いる。このようにして端子3上にポスト電極6及び半田バンプ7となる金属の柱が形成された状態となる。

【0024】

次に図11に示すように、第一の金属部分6aをエッチングして、第一の金属部分6aの幅方向の寸法W1を第二の金属部分の幅方向の寸法W2より細くする。第一の金属部分6aを構成する金属は、シード層9を構成する金属と略同じなので、同じエッチング液を用いることができる。この場合、シード層9を除去する工程に続けて第一の金属部分6aのエッチングを行っても良いし、同じエッチング液で濃度の違うものに換えて第一の金属部分6aのエッチングを行っても良い。幅方向の寸法はエッチングの処理時間によって調節が可能である。ここでは第一の金属部分6aの直径を20μmにする。このようにして本発明のポスト電極6が形成される。

【0025】

次に半導体装置2をリフロー炉に投入して半田層を溶融し、図12に示すように、第二の金属部分6bの端部に半田バンプ7を形成する。このようにして本発明の半導体装置2を得ることができる。

【0026】

以上、本発明の半導体装置および回路装置について説明したが、半導体チップ2aの端子ピッチ、ポスト電極の直径等は任意であり、適宜変更可能である。また、金属材料等やプロセスの条件についても、適宜変更可能であり、用いるエッチング液等も、それに合わせて適宜選択が可能である。

【図面の簡単な説明】

【0027】

【図1】本発明の回路装置を模式的に示す断面図である。

【図2】本発明の半導体装置の形成プロセスを示す図である。

【図3】本発明の半導体装置の形成プロセスを示す図である。

【図4】本発明の半導体装置の形成プロセスを示す図である。

【図5】本発明の半導体装置の形成プロセスを示す図である。

【図6】本発明の半導体装置の形成プロセスを示す図である。

【図7】本発明の半導体装置の形成プロセスを示す図である。

【図8】本発明の半導体装置の形成プロセスを示す図である。

【図9】本発明の半導体装置の形成プロセスを示す図である。

【図10】本発明の半導体装置の形成プロセスを示す図である。

【図11】本発明の半導体装置の形成プロセスを示す図である。

【図12】本発明の半導体装置の形成プロセスを示す図である。

【図13】従来の回路装置を模式的に示す断面図である。

【図14】従来の回路装置を模式的に示す断面図である。

【符号の説明】

【0028】

1、11、21 回路装置

2、12、22 半導体装置

2a、12a、22a 半導体チップ

3、13、23 端子

4、14、24 配線基板

5、15、25 ランド

6、16、26 ポスト電極

6a 第一の金属部分

6b 第ニの金属部分

7、17、27 バンプ

8 アンダーフィル

9 シード層

【技術分野】

【0001】

本発明は、配線基板上に実装される半導体装置と、この半導体装置が実装された回路装置に関するものである。

【背景技術】

【0002】

電子機器に搭載される無線モジュールや電源モジュール等の回路装置は、集積回路(IC)等の半導体装置及びその他の受動部品をセラミック配線基板や樹脂製のプリント配線基板上に実装して形成される。近年は、電子機器の小型化が進んでおり、回路装置にも小型化の要求がなされている。回路装置において半導体装置が占める実装面積は比較的大きいので、その実装面積を小さくするために、フリップチップ実装による半導体装置の実装が用いられている。

【0003】

フリップチップ実装は、図13に示すように、半導体チップ12aの下面(配線基板14と向かい合う面)に端子間ピッチP1で設けられた端子13に直接または該端子に形成された柱状電極(ポスト電極)16にバンプ17を形成した半導体装置12を、バンプ17と配線基板14上のランド(電子部品等の端子電極を接合する導体)15とを接合するようにして配線基板14上に実装するものである。

【0004】

半導体装置12を実装した配線基板14は、半導体チップ12aと配線基板14との熱膨張係数の差に起因する応力を受ける。また、曲げやたわみなどの機械的な応力も受ける。これらの応力がバンプ17やポスト電極16に集中してクラックが発生することがある。このような応力を緩和するため、特開2002−313993号公報に開示されているように、半導体装置と配線基板との間に形成された空間に樹脂を充填して、アンダーフィルを充填する手法が広く行われている。このようなアンダーフィルは通常次のようにして充填される。まず配線基板上に実装した半導体装置の周囲にエポキシ樹脂等の硬化性樹脂をシリンジ等で吐出させて塗布する。このとき硬化性樹脂がバンプとバンプの間またはポスト電極とポスト電極の間を通って半導体装置と配線基板との間の空間に引き込まれて充填される。そして充填された樹脂を硬化させることによりアンダーフィルが充填される。

【0005】

【特許文献1】特開2002−313993号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

近年、半導体装置のデザインルールの微細化が進んでいる。その結果半導体チップのサイズが小さくなり、図13に示す端子間のピッチP1が狭くなる傾向にある。端子間のピッチが図14に示す端子間ピッチP2のように狭くなると、図13に示すバンプ間またはポスト電極間の距離PLXが、図14に示すバンプ間またはポスト電極間の距離PLYのように狭くなるので、硬化性樹脂が半導体装置22と配線基板24との間の空間に引き込まれにくくなる。その結果、半導体装置22と配線基板24との間の空間にアンダーフィルが充填されない部分が発生することがあった。

【0007】

本発明は、このような問題を解決して、アンダーフィルの未充填部分が生じない半導体装置を提案するとともに、この半導体装置を用いて、応力によるバンプやポスト電極のクラックを防止することができる回路装置を提案するものである。

【課題を解決するための手段】

【0008】

本発明では第一の解決手段として、半導体チップと、該半導体チップの下面に複数個並べて設けられた端子と、前記端子に一方の端部が接合された柱状の金属で形成されたポスト電極と、前記ポスト電極の他方の端部に形成された半田バンプと、を有する半導体装置において、前記ポスト電極は、前記端子に接合された側の第一の金属部分と、前記半田バンプが形成された側の第二の金属部分と、で構成され、前記第一の金属部分の幅方向の寸法が、前記第二の金属部分の幅方向の寸法よりも小さい半導体装置を提案する。

【0009】

上記第一の解決手段によれば、半導体装置のポスト電極間の距離が、第一の金属部分で端子間のピッチより広くなるので、この部分からアンダーフィルが入り込みやすくなる。その結果、半導体装置のデザインルールの微細化によって端子間のピッチが狭くなっても、半導体装置と配線基板との間の空間にアンダーフィルが充填されやすくなり、未充填部分が生じないようにできる。なお、配線基板側に接合される第二の金属部分は第一の金属部分よりも幅方向の寸法が広いので、ランドとの接合面積を大きく確保することができる。その結果、接合強度が充分に得られる。

【0010】

また、本発明では第二の解決手段として、上記第一の解決手段に加えて、前記第一の金属部分の長さが、前記第二の金属部分の長さよりも長い半導体装置を提案する。この第二の解決手段によれば、ポスト電極間の距離が半導体装置の端子間のピッチよりも広い第一の金属部分が多くなる。これによって、アンダーフィルが入り込みやすい部分を大きく確保できる。

【0011】

また、本発明では第三の解決手段として、半導体チップと、該半導体チップの下面に複数個並べて設けられた端子と、前記端子に一方の端部が接合された柱状の金属で形成されたポスト電極と、前記ポスト電極の他方の端部に形成された半田バンプと、を有する半導体装置が配線基板上にフリップチップ実装されており、前記配線基板と前記半導体装置との間に形成された空間にアンダーフィルが充填されている回路装置において、前記ポスト電極は、前記端子に接合された側の第一の金属部分と、前記半田バンプが形成された側の第二の金属部分と、で構成され、前記第一の金属部分の幅方向の寸法が、前記第二の金属部分の幅方向の寸法よりも小さい回路装置を提案する。

【0012】

上記第三の解決手段によれば、半導体装置と配線基板との間の空間に硬化性樹脂が充填されて、アンダーフィルが未充填の部分が発生しにくい回路装置が得られる。このような回路装置は応力によるバンプやポスト電極のクラックを防止する効果が高いので、信頼性が高くなる。

【発明の効果】

【0013】

本発明によれば、アンダーフィルの未充填部分が生じない半導体装置が得られるとともに、応力によるバンプやポスト電極のクラックを防止して信頼性の高い回路装置を得ることができる。

【発明を実施するための最良の形態】

【0014】

本発明の半導体装置及び回路装置に係る実施の形態について、図1に基づいて説明する。図1は本発明の回路装置の半導体装置を実装した部分を模式的に示す断面図である。回路装置1は配線基板4上にフリップチップ実装された半導体装置2を有している。なお、その他の配線導体や電子部品はここでは省略している。

【0015】

半導体装置2は、下面に所定の端子間ピッチPで形成された端子3を備えた半導体チップと、この半導体チップの端子3に接合されている柱状の金属で形成されたポスト電極6と、このポスト電極6の、端子3と接合されている側と反対側の先端に形成されている半田バンプ7と、を有している。半田バンプ7は、配線基板4上に形成されたランド5に接合されている。そして、半導体装置2と配線基板4との間の空間は、エポキシ樹脂等のアンダーフィル8が充填されている。

【0016】

ポスト電極6は、互いに異なる2つの金属で構成されており、端子3に接合されている側が第一の金属部分6aで構成され、半田バンプ7が形成されている側が第二の金属部分6bで構成されている。第一の金属部分6a及び第二の金属部分6bに用いられる金属としては、Cu、Ni、Cr、Au等がある。ポスト電極6の形状は円柱形状または角柱形状等がある。

【0017】

第一の金属部分6aの幅方向の寸法W1は、第二の金属部分6bの幅方向の寸法W2よりも小さく形成されている。幅方向の寸法は、円柱であればその直径、角柱であれば一辺の長さもしくは対角線の長さである。このようにW1<W2であれば、隣接するポスト電極6間の、第一の金属部分6aにおける距離PL1が、半導体装置2の端子3の端子間ピッチPよりも大きくなる。そのため、デザインルールの微細化によって端子間ピッチPが狭くなっても、第一の金属部分6aの形成部分からアンダーフィルが入り込みやすくなる。その結果、アンダーフィル8の未充填部分が生じないように、半導体装置2と配線基板4との間の空間に充填することができるようになる。

【0018】

なお、第一の金属部分6aの長さL1が、第二の金属部分6bの長さL2よりも長く形成されていると好ましい。第ニの金属部分6bにおける距離PL2は第一の金属部分6aにおける距離PL1よりも小さいので、第二の金属部分6bはできるだけ少ない方が好ましい。しかしながら、第ニの金属部分6bは配線基板4との接合を確保する役目を持っており、充分な接合強度を得るための接合面積を備える必要がある。よってL1>L2とすることで、アンダーフィルの入り込みやすさと配線基板4との接合強度とを両立させることができる。

【0019】

次に本発明の半導体装置2を形成するプロセスを図2〜図12に基づいて説明する。なお、半導体装置2は、Al金属で構成された端子3が端子ピッチ60μmで形成されている半導体チップ2aと、第一の金属部分6aがW1=直径20μm、L1=40μmのCuの円柱であり第二の金属部分6bがW2=直径40μm、L2=20μmのNiの円柱であるポスト電極6を有しているものを例にとって説明する。

【0020】

まず、半導体チップ2aを用意する。図2に示すように、半導体チップ2aを、端子3が形成されている方すなわち下面を上に向けて用意する。次に図3に示すように、半導体チップ2aの上に、スパッタまたは蒸着法によって、端子3を覆うようにしてシード層9を形成する。このシード層9は、後に形成するポスト電極6の第一の金属部分6aを構成する金属と略同じ種類の金属またはその合金で形成される。ここでは第一の金属部分6aがCuなので、シード層9はCuが用いられる。

【0021】

次に図4に示すように、シード層9上にメッキレジスト膜REを塗布形成する。このメッキレジスト膜REにはフォトレジストが用いられる。このメッキレジスト膜REに、半導体装置2上の端子3に対応するパターンを備えたフォトマスク(図示せず)を通して光を当てて感光し、その後現像して、図5に示すように、半導体チップ2a上の端子3に対応する位置に開口部OPを形成する。フォトレジストには光が当った部分が除去されるポジ型フォトレジストを用いても良いし、光が当った部分が不溶化するネガ型フォトレジスを用いても良い。ポジ型フォトレジストを用いる場合は開口部OPのパターン形状で光を通すフォトマスクを用い、ネガ型フォトレジストを用いる場合は開口部OPのパターン形状で光を遮断するフォトマスクを用いる。開口部OPの大きさは、第二の金属部分6bの幅方向の寸法W2と略同じすなわち直径40μmになるように形成される。

【0022】

次に図6に示すように、電解Cuメッキによって第一の金属部分6aを形成する。電流がシード層9を通じて流れるので、Cuは開口部OP内のシード層9上に析出する。第一の金属部分6aの長さL1は、電解Cuメッキの電流密度や通電時間によって調節が可能である。ここではL1が40μmになるように調節する。次に図7に示すように、電解Niメッキによって第二の金属部分6bを形成する。このときも電流がシード層9及び第一の金属部分6aを通じて流れるので、Niは開口部OP内のCu上に析出する。なお、第ニの金属部分6bの長さL2についても、電解Cuメッキの電流密度や通電時間によって調節が可能である。ここではL2が20μmになるように調節する。次に図8に示すように、電解半田メッキによって半田バンプ7となる半田層を形成する。半田バンプ7の材質は、Sn−Ag、Sn−Cu、Sn−Pb、Sn−Zn等のSn合金が用いられる。半田層は開口部OP内に形成されるので、この段階ではポスト電極6と略同じ直径40μmの円柱状に形成される。

【0023】

次に図9に示すように、メッキレジスト膜REを除去する。このようにして、シード層9上の、半導体チップ2a上の端子3に対応する位置に、第一の金属部分6a、第二の金属部分6b及び半田層で形成された直径40μmの柱状の金属が現れる。次に図10に示すように、エッチングによってシード層9を除去する。エッチング液はCuを選択的にエッチングするものを用いる。このようにして端子3上にポスト電極6及び半田バンプ7となる金属の柱が形成された状態となる。

【0024】

次に図11に示すように、第一の金属部分6aをエッチングして、第一の金属部分6aの幅方向の寸法W1を第二の金属部分の幅方向の寸法W2より細くする。第一の金属部分6aを構成する金属は、シード層9を構成する金属と略同じなので、同じエッチング液を用いることができる。この場合、シード層9を除去する工程に続けて第一の金属部分6aのエッチングを行っても良いし、同じエッチング液で濃度の違うものに換えて第一の金属部分6aのエッチングを行っても良い。幅方向の寸法はエッチングの処理時間によって調節が可能である。ここでは第一の金属部分6aの直径を20μmにする。このようにして本発明のポスト電極6が形成される。

【0025】

次に半導体装置2をリフロー炉に投入して半田層を溶融し、図12に示すように、第二の金属部分6bの端部に半田バンプ7を形成する。このようにして本発明の半導体装置2を得ることができる。

【0026】

以上、本発明の半導体装置および回路装置について説明したが、半導体チップ2aの端子ピッチ、ポスト電極の直径等は任意であり、適宜変更可能である。また、金属材料等やプロセスの条件についても、適宜変更可能であり、用いるエッチング液等も、それに合わせて適宜選択が可能である。

【図面の簡単な説明】

【0027】

【図1】本発明の回路装置を模式的に示す断面図である。

【図2】本発明の半導体装置の形成プロセスを示す図である。

【図3】本発明の半導体装置の形成プロセスを示す図である。

【図4】本発明の半導体装置の形成プロセスを示す図である。

【図5】本発明の半導体装置の形成プロセスを示す図である。

【図6】本発明の半導体装置の形成プロセスを示す図である。

【図7】本発明の半導体装置の形成プロセスを示す図である。

【図8】本発明の半導体装置の形成プロセスを示す図である。

【図9】本発明の半導体装置の形成プロセスを示す図である。

【図10】本発明の半導体装置の形成プロセスを示す図である。

【図11】本発明の半導体装置の形成プロセスを示す図である。

【図12】本発明の半導体装置の形成プロセスを示す図である。

【図13】従来の回路装置を模式的に示す断面図である。

【図14】従来の回路装置を模式的に示す断面図である。

【符号の説明】

【0028】

1、11、21 回路装置

2、12、22 半導体装置

2a、12a、22a 半導体チップ

3、13、23 端子

4、14、24 配線基板

5、15、25 ランド

6、16、26 ポスト電極

6a 第一の金属部分

6b 第ニの金属部分

7、17、27 バンプ

8 アンダーフィル

9 シード層

【特許請求の範囲】

【請求項1】

半導体チップと、該半導体チップの下面に複数個並べて設けられた端子と、前記端子に一方の端部が接合された柱状の金属で形成されたポスト電極と、前記ポスト電極の他方の端部に形成された半田バンプと、を有する半導体装置において、

前記ポスト電極は、前記端子に接合された側の第一の金属部分と、前記半田バンプが形成された側の第二の金属部分と、で構成され、

前記第一の金属部分の幅方向の寸法が、前記第二の金属部分の幅方向の寸法よりも小さい

ことを特徴とする半導体装置。

【請求項2】

前記第一の金属部分の長さが、前記第二の金属部分の長さよりも長いことを特徴とする請求項1に記載の半導体装置。

【請求項3】

半導体チップと、該半導体チップの下面に複数個並べて設けられた端子と、前記端子に一方の端部が接合された柱状の金属で形成されたポスト電極と、前記ポスト電極の他方の端部に形成された半田バンプと、を有する半導体装置が配線基板上にフリップチップ実装されており、前記配線基板と前記半導体装置との間に形成された空間にアンダーフィルが充填されている回路装置において、

前記ポスト電極は、前記端子に接合された側の第一の金属部分と、前記半田バンプが形成された側の第二の金属部分と、で構成され、

前記第一の金属部分の幅方向の寸法が、前記第二の金属部分の幅方向の寸法よりも小さい

ことを特徴とする回路装置。

【請求項1】

半導体チップと、該半導体チップの下面に複数個並べて設けられた端子と、前記端子に一方の端部が接合された柱状の金属で形成されたポスト電極と、前記ポスト電極の他方の端部に形成された半田バンプと、を有する半導体装置において、

前記ポスト電極は、前記端子に接合された側の第一の金属部分と、前記半田バンプが形成された側の第二の金属部分と、で構成され、

前記第一の金属部分の幅方向の寸法が、前記第二の金属部分の幅方向の寸法よりも小さい

ことを特徴とする半導体装置。

【請求項2】

前記第一の金属部分の長さが、前記第二の金属部分の長さよりも長いことを特徴とする請求項1に記載の半導体装置。

【請求項3】

半導体チップと、該半導体チップの下面に複数個並べて設けられた端子と、前記端子に一方の端部が接合された柱状の金属で形成されたポスト電極と、前記ポスト電極の他方の端部に形成された半田バンプと、を有する半導体装置が配線基板上にフリップチップ実装されており、前記配線基板と前記半導体装置との間に形成された空間にアンダーフィルが充填されている回路装置において、

前記ポスト電極は、前記端子に接合された側の第一の金属部分と、前記半田バンプが形成された側の第二の金属部分と、で構成され、

前記第一の金属部分の幅方向の寸法が、前記第二の金属部分の幅方向の寸法よりも小さい

ことを特徴とする回路装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2009−81153(P2009−81153A)

【公開日】平成21年4月16日(2009.4.16)

【国際特許分類】

【出願番号】特願2007−247032(P2007−247032)

【出願日】平成19年9月25日(2007.9.25)

【出願人】(000204284)太陽誘電株式会社 (964)

【Fターム(参考)】

【公開日】平成21年4月16日(2009.4.16)

【国際特許分類】

【出願日】平成19年9月25日(2007.9.25)

【出願人】(000204284)太陽誘電株式会社 (964)

【Fターム(参考)】

[ Back to top ]