半導体装置及び無線通信システム

【課題】無線通信によりデータの交信が可能な半導体装置において、半導体装置内の回路が過電圧により破壊されることを防止する。

【解決手段】半導体装置内のアナログ回路部、特に高周波回路、電源回路及びデータ復調回路で使用しているトランジスタと、デジタル回路部(ロジック回路部)で使用しているトランジスタとにおいて、アナログ回路部内のトランジスタのゲート長をデジタル回路部内のトランジスタのゲート長以上とする。こうして、過電圧が供給された際にゲート長の長いアナログ回路で電圧を緩和し、当該アナログ回路から出力された信号が入力されるデジタル回路部において、トランジスタ等の回路内の素子が破壊されるのを防止する。また、アナログ回路部、特に電源回路及びデータ復調回路は周波数の速い動作は必要がなく、一方、デジタル回路部等は周波数の速い動作が必要とされるので、それぞれの目的にあった無駄のない動作が実現できる。

【解決手段】半導体装置内のアナログ回路部、特に高周波回路、電源回路及びデータ復調回路で使用しているトランジスタと、デジタル回路部(ロジック回路部)で使用しているトランジスタとにおいて、アナログ回路部内のトランジスタのゲート長をデジタル回路部内のトランジスタのゲート長以上とする。こうして、過電圧が供給された際にゲート長の長いアナログ回路で電圧を緩和し、当該アナログ回路から出力された信号が入力されるデジタル回路部において、トランジスタ等の回路内の素子が破壊されるのを防止する。また、アナログ回路部、特に電源回路及びデータ復調回路は周波数の速い動作は必要がなく、一方、デジタル回路部等は周波数の速い動作が必要とされるので、それぞれの目的にあった無駄のない動作が実現できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は無線通信によりデータの交信が可能な半導体装置に関する。データの受信のみ、またはデータの送信のみを行う半導体装置に関する。また、前記半導体装置と、無線通信によって情報の交信を行うリーダ/ライタとを有する無線通信システムに関する。

【背景技術】

【0002】

個々の対象物にID(個体識別番号)を与えることで、その対象物の履歴を明確にし、生産、管理等に役立てるといった個体認識技術が注目されている。その中でも、RFIDタグ(ICタグ、ICチップ、RF(Radio Frequency)タグ、無線タグ、電子タグ、トランスポンダとも呼ばれる)等の無線通信によりデータの交信が可能な半導体装置を用いたRFID(Radio Friquency Identification)技術が利用され始めている。

【0003】

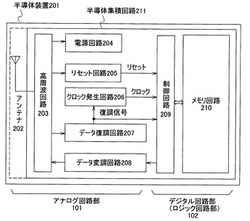

無線通信によりデータの交信が可能な半導体装置の一般的な構成について、図2を用いて説明する。

【0004】

無線通信によりデータの交信が可能な半導体装置301は、アンテナ302及び半導体集積回路309を有する。

【0005】

また、無線通信によりデータの交信が可能な半導体装置301は、主にアナログ回路部1101及びデジタル回路部(ロジック回路部)1102に分けられる。

【0006】

アナログ回路部1101は、アンテナ302、高周波回路303、電源回路304a、リミッタ回路304b、リセット回路304c、クロック発生回路304d、データ復調回路305、データ変調回路306等を有し、デジタル回路部(ロジック回路部)1102は、制御回路307及びメモリ回路308等を有する。

【0007】

次に、無線通信によりデータの交信が可能な半導体装置301の一般的な動作について、図2を用いて説明する。

【0008】

はじめに、アンテナ302により無線信号が受信される。無線信号は高周波回路303を介して電源回路304aに入力され、高電源電位(以下、VDD)が生成される。VDDはリミッタ回路304bにより所定の電位以下となるように制御され、各回路に供給される。また、無線信号は高周波回路303を介してデータ復調回路305に入力され、復調される(以下、復調信号)。さらに、無線信号は高周波回路303を介して、リセット回路304cに入力される。復調信号はクロック発生回路304dに入力される。リセット回路304cの出力信号(以下、リセット)及びクロック発生回路304dの出力信号(以下、クロック)と、復調信号とは制御回路307に入力される。制御回路307に入力された復調信号は、制御回路307によって解析される。そして、解析された信号にしたがって、メモリ回路308内に記憶されている半導体装置の情報が出力される。出力された半導体装置の情報は制御回路307によって符号化される。さらに、符号化された半導体装置の情報に基づき、データ変調回路306は搬送波を変調する。こうして、半導体装置の情報はアンテナ302により無線信号に載せて送信される。なお、図示していないが、半導体集積回路309を構成する複数の回路においては、低電源電位(以下、VSS)は共通である。VSSは例えばGNDとすることができる。VSSとVDDの電位差が半導体集積回路309を構成する複数の回路に供給され、それらの回路の電源電圧となる。

【0009】

無線信号を送受信するリーダ/ライタと半導体装置の距離によって、半導体装置内のアンテナが受信する無線信号の振幅は変化する。リーダ/ライタと半導体装置の距離が近い場合は半導体装置内のアンテナが受信する無線信号の振幅は大きく、リーダ/ライタと半導体装置の距離が遠い場合は半導体装置内のアンテナが受信する無線信号の振幅は小さい。

【0010】

無線信号を送受信するリーダ/ライタと半導体装置の距離が近い場合には、電源回路によって生成されるVDDが高くなり、半導体装置内に必要以上の電圧(以下、過電圧)が供給されることになる。そのため、半導体装置内の素子(トランジスタ、容量素子、抵抗素子等)が破壊される可能性がある。

【0011】

そこで、半導体装置は、図2のようにリミッタ回路304b等を設け、所定の電位より大きい高電源電位は内部回路に供給されないような構成となっている。このようなリミッタ回路を用いた半導体装置は例えば特許文献1に記載されている。なお、特許文献1では、リミッタ回路はレギュレータ回路と表記している。

【特許文献1】特開2001−125653号公報

【発明の開示】

【発明が解決しようとする課題】

【0012】

従来のようにリミッタ回路を設けた半導体装置では、半導体装置内の回路構成が複雑となり、半導体装置のサイズが大きくなるという問題点がある。

【0013】

上記の実情を鑑み、無線通信によりデータの交信が可能な半導体装置において、過電圧による半導体装置内の素子(トランジスタ、容量素子、抵抗素子等)の破壊を防止し、且つ回路構成を単純にしてサイズを小さくすることを課題とする。

【課題を解決するための手段】

【0014】

本発明は、前述した課題を解決するために、以下の構成を有することを特徴とする。

【0015】

本発明の半導体装置は、アナログ回路部とデジタル回路部(ロジック回路部)を有する。半導体装置内のアナログ回路部とデジタル回路部(ロジック回路部)で使用するトランジスタにおいて、アナログ回路部内、特に電源回路及びデータ復調回路のトランジスタのゲート長(チャネル長)をデジタル回路部(ロジック回路部)内のトランジスタのゲート長(チャネル長)以上とすることを特徴とする。

【0016】

好ましくは、アナログ回路部内、特に、電源回路、データ復調回路で使用されるトランジスタのゲート長(チャネル長)をデジタル回路部(ロジック回路部)で使用されるトランジスタのゲート長(チャネル長)の2倍以上とする。

【0017】

本発明の半導体装置は、アナログ回路部を有する。アナログ回路部には無線信号が入力される。アナログ回路部は、無線信号を用いて直流電圧を発生する電源回路と、無線信号を復調するデータ復調回路と、データ復調回路の出力を用いてクロックを生成するクロック発生回路とを有する。電源回路及びデータ復調回路が有するトランジスタのゲート長(チャネル長)は、クロック発生回路が有するトランジスタのゲート長(チャネル長)以上とすることを特徴とする。

【0018】

好ましくは、電源回路及びデータ復調回路で使用されるトランジスタのゲート長(チャネル長)をクロック発生回路で使用されるトランジスタのゲート長(チャネル長)の2倍以上とする。

【0019】

なお、マルチゲート型のトランジスタ(複数のトランジスタが直列に接続された構成)の場合、マルチゲート型のトランジスタのゲート長(チャネル長)とは当該トランジスタを構成する複数のトランジスタの各々に対するゲート長(チャネル長)であるとする。

【0020】

本発明において、ゲート電極の幅が異なることにより、複数の異なるゲート長を有するゲート電極を用いてもよい。この場合、アナログ回路部内のトランジスタのゲート電極において最も短いゲート長は、デジタル回路部内のトランジスタのゲート長において最も長いゲート長よりも長ければよい。

【発明の効果】

【0021】

アナログ回路部内、特に電源回路及びデータ復調回路のトランジスタのゲート長をデジタル回路部(ロジック回路部)内のトランジスタのゲート長以上とすることで、リミッタ回路等の特別な回路を設けることなく、過電圧が供給された際にゲート長の長いアナログ回路部で電圧を緩和することができる。さらに、アナログ回路部からの信号が入力されるデジタル回路部(ロジック回路部)において、トランジスタ等の回路内の素子が破壊されるのを防止することができる。

【0022】

また、アナログ回路部、特に電源回路及びデータ復調回路は、受信した無線信号から定電位(VDD)を生成したり、受信した無線信号よりも周波数の遅い復調信号を生成したりする。つまり、アナログ回路部、特に電源回路及びデータ復調回路は、受信した無線信号を加工することを主目的とするため、周波数の速い動作は必要がない。一方、デジタル回路部(ロジック回路部)及びアナログ回路部内のクロック発生回路等は、アナログ回路部で生成された復調信号、VDD等を用いて演算処理などを行うため、周波数の速い動作が必要とされる。したがって、半導体装置内のアナログ回路部とデジタル回路部(ロジック回路部)で使用するトランジスタにおいて、アナログ回路部内、特に電源回路及びデータ復調回路のトランジスタのゲート長をデジタル回路部(ロジック回路部)内のトランジスタのゲート長以上とすることで、無駄のないそれぞれの目的にあった動作が実現できる。

【発明を実施するための最良の形態】

【0023】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更しうることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じ物を指し示す符号は異なる図面間において共通とする。

【0024】

また、本発明において、接続されているとは電気的に接続されていることと同義である。したがって、間に、別の素子などが配置されていてもよい。

【0025】

(実施の形態1)

本実施の形態1では、本発明の無線通信によりデータの交信が可能な半導体装置の構成と当該半導体装置の動作について、図1を用いて説明する。

【0026】

はじめに、本発明の無線通信によりデータの交信が可能な半導体装置の構成について説明する。半導体装置201は、主にアナログ回路部101及びデジタル回路部(ロジック回路部)102を有する。そして、アナログ回路部101は、アンテナ202、高周波回路203、電源回路204、リセット回路205、クロック発生回路206、データ復調回路207、データ変調回路208等を有し、デジタル回路部(ロジック回路部)102は制御回路209及びメモリ回路210等を有する。

【0027】

次に、本発明の無線通信によりデータの交信が可能な半導体装置の動作について説明する。アンテナ202により無線信号が受信される。無線信号は高周波回路203を介して電源回路204に入力され、高電源電位(以下、VDD)が生成される。ここで、図示していないが、VDDは半導体集積回路211が有する各回路に供給される。また、高周波回路203を介してデータ復調回路207に入力された信号は復調される(以下、復調信号)。さらに、無線信号は高周波回路203を介してリセット回路205に入力され、リセット回路205の出力信号(リセット)は制御回路209に入力される。また、復調信号はクロック発生回路206に入力され、クロック発生回路206の出力信号(クロック)は制御回路209に入力される。更に、復調信号は制御回路209に入力される。制御回路209に入力された信号は、制御回路209によって解析される。そして、解析された信号にしたがって、メモリ回路210内に記憶されている半導体装置の情報が出力される。出力された半導体装置の情報は制御回路209によって符号化される。さらに、符号化された半導体装置の情報に基づき、データ変調回路208は搬送波を変調する。こうして、半導体装置の情報はアンテナ202により無線信号に載せて送信される。なお、図示していないが、半導体集積回路211を構成する複数の回路においては、低電源電位(以下、VSS)は共通である。VSSは例えばGND(接地電位)とすることができる。

【0028】

ここで、アナログ回路部101、特に、電源回路204、データ復調回路207で使用するトランジスタのゲート長は制御回路209及びメモリ回路210等を有するデジタル回路部(ロジック回路部)102で使用するトランジスタのゲート長以上である。

【0029】

そうすることで、リミッタ回路のような特別な回路を設けることなく、過電圧が供給された際にゲート長の長いアナログ回路部で電圧を緩和することができる。さらに、アナログ回路部101から出力された信号が入力されるデジタル回路部(ロジック回路部)102において、回路内の素子であるトランジスタ等が破壊されるのを防止することが出来る。

【0030】

また、アナログ回路部101、特に電源回路204及びデータ復調回路207は、受信した無線信号から定電位(VDD)を生成したり、受信した無線信号よりも周波数の遅い復調信号を生成したりする。つまり、アナログ回路部101、特に電源回路204及びデータ復調回路207は、受信した無線信号を加工することを主目的とする。よって、周波数の速い動作は必要がない。一方、デジタル回路部(ロジック回路部)102及びアナログ回路部101内のクロック発生回路206等は、アナログ回路部101で生成された復調信号、VDD等を用いて、演算処理を行うなど、周波数の速い動作が必要とされる。従って、半導体装置内のアナログ回路部101とデジタル回路部(ロジック回路部)102で使用するトランジスタにおいて、アナログ回路部101内、特に電源回路204及びデータ復調回路207のトランジスタのゲート長をデジタル回路部(ロジック回路部)102内のトランジスタのゲート長以上とする。こうして、それぞれの目的にあった無駄のない動作が実現できる。

【0031】

本発明の半導体装置のアンテナ202が受信する無線信号は、搬送波を変調した信号である。搬送波の変調方式は、アナログ変調またはデジタル変調であって、振幅変調、位相変調、周波数変調、及びスペクトラム拡散のいずれであってもよい。

【0032】

また、搬送波の周波数は、サブミリ波である300GHz以上3THz以下、ミリ波である30GHz以上300GHz未満、マイクロ波である3GHz以上30GHz未満、極超短波である300MHz以上3GHz未満、超短波である30MHz以上300MHz未満、短波である3MHz以上30MHz未満、中波である300KHz以上3MHz未満、長波である30KHz以上300KHz未満、及び超長波である3KHz以上30KHz未満のいずれの周波数も用いることができる。望ましくは、1GHz以下にすると良い。

【0033】

また、VSSと電源回路204が生成するVDDとの電位差、つまり、本発明の半導体装置の電源電圧(動作電圧)は1V〜6V、望ましくは3V以下にするとよい。本発明の半導体装置の電源電圧は、アナログ回路部101及びデジタル回路部(ロジック回路部)102で同じとすることができる。

【0034】

メモリ回路210は、DRAM(Dynamic Random Access Memory)、SRAM(Static Random Access Memory)、FeRAM(Ferroelectric Random Access Memory)、マスクROM(Read Only Memory)、EPROM(Electrically Programmable Read Only Memory)、EEPROM(Electrically Erasable and Programmable Read Only Memory)、フラッシュメモリを用いることができる。

【0035】

上記構成により本発明の無線通信によりデータの交信が可能な半導体装置は、リミッタ回路を設けることなく回路内の素子が破壊されるのを防止することができる。こうして、半導体装置のサイズを小さく抑え、且つ信頼性の高い半導体装置を提供することができる。

【0036】

(実施の形態2)

本実施の形態2では、実際に設計した回路の一部である図3を用いて動作の説明を行う。なお、図3では、動作の説明をするための最低限の回路構成しか図示していない。図示しない部分については図1と同様である。

【0037】

高周波回路203は、共振容量220、第一の帯域フィルタ221及び第二の帯域フィルタ222を有する。ここで、共振容量220はアンテナ202が受信したい周波数の信号を最も効率よく受信するために設けられる。また、第一の帯域フィルタ221及び第二の帯域フィルタ222はノイズを除去するために設けられる。第一の帯域フィルタ221及び第二の帯域フィルタ222は、共有化して1つの帯域フィルタとしても構わないが、2つに分けることが望ましい。

【0038】

ここで、ノイズを除去するために設けられている第一の帯域フィルタ221及び第二の帯域フィルタ222は、主に、抵抗素子と容量素子の接続により構成される。そして、高周波ノイズを遮断したい場合と低周波ノイズを遮断したい場合で、抵抗素子と容量素子の接続の仕方がかわる。たとえば、低周波ノイズを除去したい場合は容量素子と抵抗素子を直列に接続し、ハイパスフィルタを構成すればよい。どの帯域のノイズを除去するかは、本発明の半導体装置が使用される目的に即した設計仕様によって決定される。遮断したい周波数が十分に遮断できるように、容量素子の容量値または抵抗素子の抵抗値、抵抗素子の抵抗値と容量素子の容量値の両方を大きくしておくことが望ましい。なお、上記帯域フィルタにおいては、抵抗素子と容量素子の接続により構成しているが、抵抗素子や容量素子の代わりにトランジスタを用いても良いし、遮断したい周波数が遮断できる構成であれば、上記構成に限定されずにどのような構成を用いても良い。なお、抵抗素子及び容量素子を設ける代わりに、または、抵抗素子及び容量素子に加えて、配線や電極等の寄生抵抗や、複数の配線の重なりや複数の電極の重なりによる寄生容量を積極的に利用してもよい。

【0039】

第一の帯域フィルタ221を通った無線信号(交流信号)は電源回路204に入力する。そして、入力された無線信号(交流信号)は電源回路204内の第一の整流回路223により整流される。さらに、整流された信号は保持容量224により平滑化され、高電源電位(VDD)が生成される。VDDは本発明の半導体装置内の複数の回路ブロックに供給される。

【0040】

ここで、第一の整流回路223は2個のN型トランジスタを有する。N型トランジスタ234のゲートとソースは接続されており、ドレインにはVDDが与えられている。N型トランジスタ235のゲートとソースにはVSS(GND)が与えられており、ドレインはN型トランジスタ234のゲート及びソースに接続されている。こうすることで、受信した無線信号を整流することができる。

【0041】

なお、第一の整流回路223は、図3において示した回路構成に限定されず、図3とは異なる構成の半波整流回路を用いても良いし、全波整流回路を用いても良いし、交流信号を直流信号に変えることができる回路構成であれば、どのような回路を用いても良い。

【0042】

第二の帯域フィルタ222を通った無線信号(交流信号)は、データ復調回路207に入力する。そして、入力した無線信号(交流信号)はデータ復調回路207内の第二の整流回路225により整流される。さらに、第一の抵抗素子228、第一の容量素子230、第二の抵抗素子229及び第二の容量素子231により復調される(以下、復調信号)。復調信号は半導体装置201内の複数の回路ブロックに入力される。

【0043】

ここで、第二の整流回路225は2個のN型トランジスタを有する。N型トランジスタ232のゲートとソースは接続されており、ドレインは第一の抵抗素子228の一方、第一の容量素子230の一方及び第二の抵抗素子229の一方に接続されている。N型トランジスタ233のゲートとソースにはVSS(GND)が与えられており、ドレインはN型トランジスタ232のゲート及びソースに接続されている。

【0044】

また、第一の抵抗素子228の他方及び第一の容量素子230の他方はVSS(GND)が与えられている。さらに、第二の抵抗素子229の他方は第二の容量素子231の一方に接続されており、第二の容量素子231の他方にはVSS(GND)が与えられている。第二の抵抗素子229の他方及び第二の容量素子231の一方はデータ復調回路207の出力である。

【0045】

こうすることで、データ復調回路207は受信した交流信号を整流し、復調することができる。

【0046】

なお、第二の整流回路225は、図3において示した回路構成に限定されず、図3とは異なる構成の半波整流回路を用いても良いし、全波整流回路を用いても良いし、交流信号を直流信号に変えることができる回路構成であれば、どのような回路を用いても良い。

【0047】

また、第二の整流回路225により直流信号に変えられた信号を復調するための複数の抵抗素子及び容量素子の接続の仕方及び構成は、図3において示した接続の仕方及び構成に限定されない。抵抗素子及び容量素子以外にトランジスタを用いても良いし、直流信号に変えられた信号を復調することができる回路構成であれば、どのような回路を用いても良い。

【0048】

図3では、このようにして出力された復調信号が制御回路209に入力される場合を、一例として示す。なお、図3では、制御回路209内のインバータ227に復調信号が入力する例を示しているが、復調信号が入力する回路は設計によって様々に変えられるので、図3において示した構成に限定されない。前述のようにインバータでもよいし、その他の論理回路でもよいし、容量素子、抵抗素子及びインダクタンスなどの素子でもよいし、それらの組み合わせでもよい。なお、抵抗素子及び容量素子を設ける代わりに、または、抵抗素子及び容量素子に加えて、配線や電極等の寄生抵抗や、複数の配線の重なりや複数の電極の重なりによる寄生容量を積極的に利用してもよい。

【0049】

こうして、復調信号が制御回路209内のインバータ227に入力して得られた出力信号は、制御回路内回路226に入力される。

【0050】

ここで、制御回路内回路226は、本発明の半導体装置が使用される目的に即した設計仕様に基づき設計される。

【0051】

図3において、アナログ回路部に相当するのは、アンテナ202、高周波回路203、電源回路204、データ復調回路207である。また、電源回路204内の第一の整流回路223及びデータ復調回路207内の第二の整流回路225でトランジスタが使用される。さらに、デジタル回路部(ロジック回路部)に相当するのは、制御回路209である。さらにまた、制御回路209内でトランジスタが使用される一例として制御回路内のインバータ227があげられる。

【0052】

本実施の形態2においては、前述のアナログ回路部に相当する電源回路204内の第一の整流回路223及びデータ復調回路207内の第二の整流回路225で使用するN型トランジスタ234、N型トランジスタ235、N型トランジスタ232及びN型トランジスタ233のゲート長は3.3μmで設計する。また、前述のデジタル回路部(ロジック回路部)に相当する制御回路209内のインバータ227で使用するトランジスタのゲート長は1.3μmで設計する。さらに、制御回路内回路226、及び図示していないが、メモリ回路210等内で使用するトランジスタのゲート長も1.3μmで設計することができる。

【0053】

アナログ回路部、特に、電源回路204及びデータ復調回路207で使用するトランジスタのゲート長は制御回路209及びメモリ回路210等を有するデジタル回路部(ロジック回路部)で使用するトランジスタのゲート長以上とする。好ましくは、アナログ回路部、特に、電源回路204及びデータ復調回路207で使用するトランジスタのゲート長を制御回路209及びメモリ回路210等を有するデジタル回路部(ロジック回路部)で使用するトランジスタのゲート長の2倍以上とする。

【0054】

そうすることで、リミッタ回路のような特別な回路を設けることなく、過電圧が供給された際にゲート長の長いアナログ回路部で電圧を緩和することができる。さらに、アナログ回路部から出力された信号が入力されるデジタル回路部(ロジック回路部)において、回路内の素子であるトランジスタ等が破壊されるのを防止することが出来る。

【0055】

また、アナログ回路部、特に電源回路204及びデータ復調回路207は、受信した無線信号から高電源電位(VDD)を生成したり、受信した無線信号よりも周波数の遅い復調信号を生成したりといった、受信した無線信号を加工することを主目的とするため、周波数の速い動作は必要がない。一方、デジタル回路部(ロジック回路部)及びアナログ回路部内のクロック発生回路206等は、アナログ回路部で生成された復調信号、VDD等を用いて、演算処理を行うなど、周波数の速い動作が必要とされる。従って、半導体装置内のアナログ回路部とデジタル回路部(ロジック回路部)で使用するトランジスタにおいて、アナログ回路部内、特に電源回路204及びデータ復調回路207のトランジスタのゲート長をデジタル回路部(ロジック回路部)内のトランジスタのゲート長以上とすることで、それぞれの目的にあった無駄のない動作が実現できる。

【0056】

上記構成により本発明の無線通信によりデータの交信が可能な半導体装置は、リミッタ回路を設けることなく回路内の素子が破壊されるのを防止することができる。こうして、半導体装置のサイズを小さく抑え、且つ信頼性の高い半導体装置を提供することができる。

【0057】

本実施の形態2は、実施の形態1と自由に組み合わせて実施することが可能である。

【0058】

(実施の形態3)

本実施の形態3では、本発明の半導体装置の図3の回路の一部にあたるマスク図面について、図4を用いて説明する。図4において、5001aはN型半導体層であり、5001bはP型半導体層であり、5003は第1の配線であり、5004は第2の配線である。5002はコンタクトホールである。

【0059】

図4(A)は、図3のデータ復調回路207で用いられている第二の整流回路225及び第一の抵抗素子228である。第二の整流回路225の有するN型トランジスタ232及びN型トランジスタ233は各々、N型半導体層5001aと、N型半導体層5001aに接する絶縁膜と、N型半導体層5001aと当該絶縁膜を介して重なる第1の配線5003とによって構成される。N型トランジスタ232及びN型トランジスタ233において、第1の配線5003がゲート電極となり、当該絶縁膜がゲート絶縁膜となる。図4(A)では、N型トランジスタ232及びN型トランジスタ233は各々、5個のダイオード接続(ゲートとドレインが接続)されたトランジスタを2組有し、この2組が並列に接続された構成となっている。即ち、10個のダイオード接続されたトランジスタが並列に接続された構成となっている。図16に、N型トランジスタ232を拡大した図(図16(A))と、その等価回路(図16(B))を示す。N型トランジスタ232は10個のN型トランジスタ5550が端子5000aと端子5000bの間に並列に接続された構成となっている。並列に接続した複数のN型トランジスタ5550によってN型トランジスタ232を構成することによって、N型トランジスタ232のチャネル幅を大きくし、且つそのレイアウトの自由度を高くすることができる。図16ではN型トランジスタ232を代表で示したが、N型トランジスタ233についても同様である。こうして、N型トランジスタ232及びN型トランジスタ233を有する第二の整流回路225の占める面積を小さくすることができる。

【0060】

なお、図4及び図16では、第二の整流回路225の例を示したが、電源回路204が有する第一の整流回路223についても同様な構成とすることができる。

【0061】

第一の抵抗素子228は、島状に加工された複数のN型半導体層5001aと、これら複数のN型半導体層5001aを接続する第2の配線5004によって構成される。複数のN型半導体層5001aと第2の配線5004とはコンタクトホール5002によって接続されている。

【0062】

図4(B)は、図3の制御回路内のインバータ227である。制御回路内のインバータ227は、P型トランジスタ5501とN型トランジスタ5502より構成される。P型トランジスタ5501は、P型半導体層5001bと、P型半導体層5001bに接する絶縁膜と、P型半導体層5001bと当該絶縁膜を介して重なる第1の配線5003とによって構成される。P型トランジスタ5501において、第1の配線5003がゲート電極となり、当該絶縁膜がゲート絶縁膜となる。N型トランジスタ5502は、N型半導体層5001aと、N型半導体層5001aに接する絶縁膜と、N型半導体層5001aと当該絶縁膜を介して重なる第1の配線5003とによって構成される。N型トランジスタ5502において、第1の配線5003がゲート電極となり、当該絶縁膜がゲート絶縁膜となる。

【0063】

ここで、アナログ回路部の一部である第二の整流回路225で使用するN型トランジスタ232及びN型トランジスタ233のゲート長は3.3μmで設計する。また、デジタル回路部(ロジック回路部)に相当する制御回路内のインバータ227で使用するトランジスタのゲート長は1.3μmで設計する。

【0064】

つまり、アナログ回路部に相当するデータ復調回路207で使用するトランジスタのゲート長はデジタル回路部(ロジック回路部)で使用するトランジスタのゲート長以上である。

【0065】

そうすることで、リミッタ回路のような特別な回路を設けることなく、過電圧が供給された際にゲート長の長いアナログ回路部で電圧を緩和する。さらに、アナログ回路部から出力された信号が入力されるデジタル回路部(ロジック回路部)において、回路内の素子であるトランジスタ等が破壊されるのを防止することが出来る。

【0066】

また、アナログ回路部に相当するデータ復調回路207は、無線信号(受信した無線信号)よりも周波数の遅い復調信号を生成するため、周波数の速い動作は必要がない。一方、デジタル回路部(ロジック回路部)に相当する制御回路内のインバータ227は、アナログ回路部で生成された復調信号、VDD等を用いて、演算処理を行うなど、周波数の速い動作が必要とされる。したがって、半導体装置内のアナログ回路部とデジタル回路部(ロジック回路部)で使用するトランジスタにおいて、アナログ回路部内のトランジスタのゲート長をデジタル回路部(ロジック回路部)内のトランジスタのゲート長以上とすることで、無駄のないそれぞれの目的にあった動作が実現できる。

【0067】

上記構成により本発明の無線通信によりデータの交信が可能な半導体装置は、リミッタ回路を設けることなく回路内の素子が破壊されるのを防止することができる。こうして、半導体装置のサイズを小さく抑え、且つ信頼性の高い半導体装置を提供することができる。

【0068】

本実施の形態3は、実施の形態1または実施の形態2と自由に組み合わせて実施することが可能である。

【実施例1】

【0069】

本実施例では、本発明の半導体装置の具体的な構成について、図5及び図6を用いて説明する。

【0070】

図1や図3で示した本発明の半導体装置201におけるアンテナ202の構成例を図5(A)乃至図5(D)に示す。アンテナ202は2通りの設け方があり、一方(以下、第1のアンテナ設置法という)を図5(A)及び図5(C)に示す。もう一方(以下、第2のアンテナ設置法という)を図5(B)及び図5(D)に示す。図5(C)は図5(A)のA〜A’の断面図に相当し、図5(D)は図5(B)のB〜B’の断面図に相当する。

【0071】

第1のアンテナ設置法では、複数の素子(以下、素子群601と呼ぶ)が設けられた基板600上にアンテナ202を設ける(図5(A)及び図5(C)参照)。素子群601によって、本発明の半導体装置のアンテナ以外の回路が構成される。素子群601は複数の薄膜トランジスタを有する。図示する構成では、アンテナ202として機能する導電膜は、素子群601の有する薄膜トランジスタのソースやドレインと接続される配線と同じ層に設けられている。しかしながら、アンテナ202として機能する導電膜は、素子群601の有する薄膜トランジスタのゲート電極664と同じ層に設けてもよいし、素子群601を覆うように更に絶縁膜を設け当該絶縁膜上に設けてもよい。

【0072】

第2のアンテナ設置法では、素子群601が設けられた基板600上に端子部602を設ける。そして、当該端子部602に接続するように、基板600とは別の基板610上に設けられたアンテナ202を接続する(図5(B)及び図5(D)参照)。図示する構成では、素子群601の有する薄膜トランジスタのソースやドレインと接続される配線の一部を端子部602として用いる。そして、端子部602に接続するように、基板600と、アンテナ202が設けられた基板610とを貼り合わせている。基板600と基板610の間には、導電性粒子603と樹脂604が設けられている。導電性粒子603によって、アンテナ202と端子部602とは電気的に接続されている。

【0073】

素子群601の構成及び作製方法について説明する。素子群601は、大面積の基板上に複数形成し、その後、分断することで完成させれば、安価なものを提供することができる。基板600としては、例えばバリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板等を用いることができる。また、半導体基板の表面に絶縁膜を形成したものを用いても良い。プラスチック等の可撓性を有する合成樹脂からなる基板を用いても良い。基板の表面を、CMP(Chemical Mechanical Polishing)法などの研磨により平坦化しておいても良い。また、ガラス基板、石英基板や、半導体基板を研磨して薄くした基板を用いてもよい。

【0074】

基板600上に設けられている下地層661としては、酸化珪素や、窒化珪素または窒化酸化珪素などの絶縁膜を用いることができる。下地層661によって、基板600に含まれるNaなどのアルカリ金属やアルカリ土類金属が半導体層662に拡散し薄膜トランジスタの特性に悪影響をおよぼすのを防ぐことができる。図5では、下地層661を単層の構造としているが、2層あるいはそれ以上の複数層で形成してもよい。なお、石英基板など不純物の拡散がさして問題とならない場合は、下地層661を必ずしも設ける必要はない。

【0075】

なお、高密度プラズマによって基板600の表面を直接処理してもよい。高密度プラズマは、高周波(例えば2.45GHz)を使うことによって生成される。なお、高密度プラズマとしては電子密度が1011〜1013/cm3かつ電子温度が2eV以下、イオンエネルギーが5eV以下であるものを用いる。このように低電子温度が特徴である高密度プラズマは、活性種の運動エネルギーが低いため、従来のプラズマ処理に比べプラズマダメージが少なく欠陥が少ない膜を形成することができる。プラズマの生成はラジアルスロットアンテナを用いた高周波励起のプラズマ処理装置を用いることができる。高周波を発生するアンテナから基板600までの距離を20〜80mm(好ましくは20〜60mm)とする。

【0076】

窒化性雰囲気、例えば、窒素(N)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下、または窒素と水素(H)と希ガス雰囲気下、またはアンモニア(NH3)と希ガス雰囲気下において、上記高密度プラズマ処理を行うことによって、基板600表面を窒化することができる。基板600としてガラスや石英、シリコンウエハ等を用いた場合、基板600の表面に形成された窒化物層は窒化珪素を主成分とするので、基板600側から拡散してくる不純物のブロッキング層として利用することができる。この窒化物層の上に酸化珪素膜または酸窒化珪素膜をプラズマCVD法で形成して下地層661としても良い。

【0077】

また、酸化珪素や酸窒化珪素などからなる下地層661の表面に対し同様な高密度プラズマ処理を行うことにより、その表面及び表面から1〜10nmの深さの領域を窒化処理をすることができる。このきわめて薄い窒化珪素の層は、ブロッキング層として機能し、且つその上に形成する半導体層662へ与える応力の影響が少ないので好ましい。

【0078】

半導体層662としては、所定の形状に加工された結晶性半導体膜や非晶質半導体膜を用いることができる。また、有機半導体膜を用いてもよい。結晶性半導体膜は非晶質半導体膜を結晶化して得ることができる。結晶化方法としては、レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法等を用いることができる。半導体層662は、チャネル形成領域662aと、導電型を付与する不純物元素が添加された一対の不純物領域662bとを有する。なお、チャネル形成領域662aと一対の不純物領域662bとの間に、不純物領域662bよりも低濃度で前記不純物元素が添加された低濃度不純物領域662cを有する構成を示したがこれに限定されない。低濃度不純物領域662cを設けない構成であってもよい。

【0079】

なお、半導体層662と同時に形成される配線は、基板600の上面に垂直な方向3005から見た場合に角部が丸くなるよう引き回すのが好ましい。上記配線の引き回し方法について図7に模式的に示す。半導体層と同時に形成される配線を図中配線3011で示す。図7(A)は従来の配線の引き回し方法である。図7(B)は本発明の配線の引き回し方法である。従来の配線3011の角部1201aに対して本発明の配線3011の角部1202aは丸くなっている。角部を丸くすることによって、ゴミ等が配線の角部に残るのを防止することができる。こうして、半導体装置のゴミによる不良を低減し歩留まりを高めることができる。

【0080】

薄膜トランジスタのチャネル形成領域662aにおいて、導電型を付与する不純物元素が添加されていてもよい。こうして、薄膜トランジスタのしきい値電圧を制御することができる。

【0081】

第1の絶縁層663としては、酸化珪素、窒化珪素または窒化酸化珪素等を用い、単層または複数の膜を積層させて形成することができる。この場合において、第1の絶縁層663の表面を酸化雰囲気又は窒化雰囲気で高密度プラズマによって処理し、酸化又は窒化処理して緻密化しても良い。高密度プラズマは、前述と同様に、高周波(例えば2.45GHz)を使うことによって生成される。なお、高密度プラズマとしては電子密度が1011〜1013/cm3かつ電子温度が2eV以下、イオンエネルギーが5eV以下であるものを用いる。プラズマの生成はラジアルスロットアンテナを用いた高周波励起のプラズマ処理装置を用いることができる。また、高密度プラズマを発生させる装置において、高周波を発生するアンテナから基板600までの距離を20〜80mm(好ましくは20〜60mm)とする。

【0082】

なお、第1の絶縁層663を成膜する前に、半導体層662の表面に対して上記高密度プラズマ処理を行って、半導体層の表面を酸化又は窒化処理してもよい。このとき、基板600の温度を300〜450℃とし、酸化雰囲気又は窒化雰囲気で処理することにより、その上に堆積する第1の絶縁層663と良好な界面を形成することができる。

【0083】

窒化雰囲気としては、窒素(N)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下、または窒素と水素(H)と希ガス雰囲気下、またはアンモニア(NH3)と希ガス雰囲気を用いることができる。酸化雰囲気としては、酸素(O)と希ガス雰囲気下、または酸素と水素(H)と希ガス雰囲気下、または一酸化二窒素(N2O)と希ガス雰囲気を用いることができる。

【0084】

ゲート電極664としては、Ta、W、Ti、Mo、Al、Cu、Cr、Ndから選ばれた一種の元素または該元素を複数含む合金若しくは化合物を用いることができる。更に、これらの元素、合金、化合物からなる単層または積層構造を用いることができる。図では、2層構造のゲート電極664を示した。なお、ゲート電極664やゲート電極664と同時に形成される配線は、基板600の上面に垂直な方向3005から見た場合に角部が丸くなるよう引き回すのが好ましい。引き回しの方法は図7(B)に示した方法と同様とすることができる。ゲート電極664やゲート電極664と同時に形成される配線を図中配線3012で示す。従来の配線3012の角部1201bに対して本発明の配線3012の角部1202bの様に角部を丸くすることによって、ゴミ等が配線の角部に残るのを防止することができる。こうして、半導体装置のゴミによる不良を低減し歩留まりを高めることができる。

【0085】

薄膜トランジスタは、半導体層662と、ゲート電極664と、半導体層662とゲート電極664との間のゲート絶縁膜として機能する第1の絶縁層663とによって構成される。本実施例では、薄膜トランジスタをトップゲート型のトランジスタとして示したが、半導体層の下方にゲート電極を有するボトムゲート型のトランジスタであっても良いし、半導体層の上下にゲート電極を有するデュアルゲート型のトランジスタであっても良い。

【0086】

第2の絶縁層667は窒化珪素膜などイオン性不純物をブロッキングするバリア性の絶縁膜であることが望ましい。第2の絶縁層667は窒化珪素または酸窒化珪素で形成する。この第2の絶縁層667は、半導体層662の汚染を防ぐ保護膜としての機能を有している。第2の絶縁層667を堆積した後に、水素ガスを導入して前述のような高密度プラズマ処理をすることで、第2の絶縁層667の水素化を行っても良い。または、アンモニア(NH3)ガスを導入して、第2の絶縁層667の窒化と水素化を行っても良い。または、酸素、一酸化二窒素(N2O)ガスなどと水素ガスを導入して、酸化窒化処理と水素化処理を行っても良い。この方法により、窒化処理、酸化処置若しくは酸化窒化処理を行うことにより第2の絶縁層667の表面を緻密化することができる。こうして第2の絶縁層667の保護膜としての機能を強化することができる。第2の絶縁層667に導入された水素は、その後400〜450℃の熱処理をすることにより放出されて、半導体層662の水素化をすることができる。なお当該水素化処理は、第1の絶縁層663を用いた水素化処理と組み合わせてもよい。

【0087】

第3の絶縁層665としては、無機絶縁膜や有機絶縁膜の単層または積層構造を用いることができる。無機絶縁膜としては、CVD法により形成された酸化珪素膜や、SOG(Spin On Glass)法により形成された酸化珪素膜などを用いることができ、有機絶縁膜としてはポリイミド、ポリアミド、BCB(ベンゾシクロブテン)、アクリルまたはポジ型感光性有機樹脂、ネガ型感光性有機樹脂等の膜を用いることができる。

【0088】

また、第3の絶縁層665として、珪素(Si)と酸素(O)との結合で骨格構造が構成される材料を用いることもできる。この材料の置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

【0089】

配線666としては、Al、Ni、W、Mo、Ti、Pt、Cu、Ta、Au、Mnから選ばれた一種の元素または該元素を複数含む合金を用いることができる。更に、これらの元素、合金からなる単層または積層構造を用いることができる。図では、単層構造の例を示した。なお、配線666は、基板600の上面に垂直な方向3005から見た場合に角部が丸くなるよう引き回すのが好ましい。引き回しの方法は図7(B)に示した方法と同様とすることができる。配線666を図中配線3013で示す。従来の配線3013の角部1201cに対して本発明の配線3013の角部1202cの様に角部を丸くすることによって、ゴミ等が配線の角部に残るのを防止することができる。こうして、半導体装置のゴミによる不良を低減し歩留まりを高めることができる。図5(A)及び図5(C)に示した構成では、配線666は、薄膜トランジスタのソースやドレインと接続される配線となると共に、アンテナ202となる。図5(B)及び図5(D)に示した構成では、配線666は、薄膜トランジスタのソースやドレインと接続される配線となると共に、端子部602となる。図7において、配線666と薄膜トランジスタのソースやドレインとを接続するコンタクトホール3014を示す。

【0090】

なお、アンテナ202は、Au、Ag、Cuなどのナノ粒子を含む導電性ペーストを用いて、液滴吐出法により形成することもできる。液滴吐出法は、インクジェット法やディスペンサ方式等の液滴を吐出してパターンを形成する方式の総称であり、材料の利用効率の向上等の利点を有する。

【0091】

図5(A)及び図5(C)に示した構成では、配線666上に第4の絶縁層668を形成する。第4の絶縁層668としては、無機絶縁膜や有機絶縁膜の単層または積層構造を用いることができる。第4の絶縁層668はアンテナ202の保護層として機能する。

【0092】

また、素子群601は基板600上に形成されたもの(図6(A)参照)をそのまま使用してもよいが、基板600上の素子群601を剥離し(図6(B)参照)、当該素子群601をフレキシブル基板701に貼り合わせてもよい(図6(C)参照)。フレキシブル基板701は、可撓性を有し、例えば、ポリカーボネート、ポリアリレート、ポリエーテルスルフォン等のプラスチック基板またはセラミック基板等を用いることができる。

【0093】

基板600からの素子群601の剥離は、(A)あらかじめ基板600と素子群601との間に剥離層を設けておいて、剥離層をエッチング剤により除去することで行う方法を用いることができる。または、(B)剥離層をエッチング剤により部分的に除去し、その後、基板600と素子群601とを物理的に剥離する方法を用いることができる。または、(C)素子群601が形成された耐熱性の高い基板600を機械的に削除又は溶液やガスによるエッチングで除去することで、当該素子群601を切り離す方法を用いることができる。なお、物理的手段によって剥離されるとは、外部からストレスが与えられて剥離されることを指し、例えば、ノズルから吹き付けられるガスの風圧や超音波等からストレスを与えられて剥離することである。

【0094】

上記(A)や(B)のより具体例な方法としては、耐熱性の高い基板600と素子群601の間に金属酸化膜を設け、当該金属酸化膜を結晶化により脆弱化して、当該素子群601を剥離する方法がある。また上記(A)や(B)のより具体例な方法として、耐熱性の高い基板600と素子群601の間に水素を含む非晶質珪素膜を設け、レーザ−光の照射またはエッチングにより当該非晶質珪素膜を除去することで、当該素子群601を剥離する方法を用いることもできる。

【0095】

また、剥離した素子群601のフレキシブル基板701への貼り付けは、市販の接着剤を用いればよく、例えば、エポキシ樹脂系接着剤や樹脂添加剤等の接着材を用いればよい。

【0096】

素子群601をアンテナが形成されたフレキシブル基板701に貼り合わせ当該アンテナとの電気的接続をとると、厚さが薄く、軽く、落下しても割れにくい半導体装置が完成する(図6(C)参照)。安価なフレキシブル基板701を用いると、安価な半導体装置を提供することができる。さらに、フレキシブル基板701は可撓性を有するため、曲面や異形の形状上に貼り合わせることが可能となり、多種多様の用途が実現する。例えば、薬の瓶のような曲面上に、本発明の半導体装置の一形態である無線タグ720を密着して貼り合わせることができる(図6(D)参照)。さらに、基板600を再利用すれば、低コストで半導体装置を作製することができる。

【0097】

素子群601は、フィルムで覆うことによって封止することができる。該フイルムの表面は、二酸化珪素(シリカ)の粉末により、コーティングされていてもよい。コーティングにより、高温で高湿度の環境下においても防水性を保つことができる。つまり、耐湿性の機能を持たせることができる。また、該フイルムの表面に帯電防止の機能を持たせてもよい。また、該フイルムの表面は、炭素を主成分とする材料(例えば、ダイヤモンドライクカーボン)によりコーティングされていてもよい。コーティングにより強度が増し、半導体装置の劣化や破壊を抑制することができる。また、フィルムは、基材の材料(例えば樹脂)と、二酸化珪素や導電性材料や炭素を主成分とする材料とを混ぜ合わせた材料により形成してもよい。また、フィルムの表面に界面活性剤を設ける、もしくはフィルムに界面活性剤を直接練り込むことで帯電防止の機能を持たせることができる。

【0098】

本実施例は、上記の実施の形態と自由に組み合わせることができる。

【実施例2】

【0099】

本実施例では、本発明の半導体装置をフレキシブルな構成にした例について説明する。説明には図8を用いる。図8(A)において、本発明の半導体装置は、フレキシブルな保護層901と、アンテナ902を含むフレキシブルな保護層903と、剥離プロセスや基板の薄膜化により形成された素子群904とを有する。素子群904は、実施例1で素子群601として示した構成と同様の構成とすることができる。保護層903上に形成されたアンテナ902は、素子群904と電気的に接続する。図8では、アンテナ902は保護層903上にのみ形成されているが、本発明はこの構成に制約されず、アンテナ902を保護層901上にも形成してもよい。なお、素子群904と、保護層901及び保護層903との間には、窒化珪素膜等からなるバリア膜を形成するとよい。そうすると、素子群904が汚染されることなく、信頼性を向上させた半導体装置を提供することができる。

【0100】

アンテナ902は、Ag、Cu、またはそれらでメッキされた金属で形成することができる。素子群904とアンテナ902とは、異方性導電膜を用い、紫外線処理又は超音波処理を行うことで接続することができる。なお、素子群904とアンテナ902とは、導電性ペースト等を用いて接着してもよい。

【0101】

保護層901及び保護層903によって素子群904を挟むことによって半導体装置が完成する(図8(A)中、矢印参照)。

【0102】

こうして形成された半導体装置の断面構造を図8(B)に示す。挟まれた素子群904の厚さ3003は、5μm以下、好ましくは0.1μm〜3μmの厚さとなるようにするとよい。また、保護層901及び保護層903を重ねたときの厚さをdとしたとき、保護層901及び保護層903の厚さは、好ましくは(d/2)±30μm、さらに好ましくは(d/2)±10μmとする。また、保護層901及び保護層903の厚さは10μm〜200μmであることが望ましい。さらに、素子群904の面積は10mm角(100mm2)以下であり、望ましくは0.3mm角〜4mm角(0.09mm2〜16mm2)の面積とするとよい。

【0103】

保護層901及び保護層903は、有機樹脂材料で形成されているため、折り曲げに対して強い特性を有する。また、剥離プロセスや基板の薄膜化により形成した素子群904自体も、単結晶半導体に比べて、折り曲げに対して強い特性を有する。そして、素子群904と、保護層901及び保護層903とは空隙がないように、密着させることができるため、完成した半導体装置自体も折り曲げに対して強い特性を有する。このような保護層901及び保護層903で囲われた素子群904は、他の個体物の表面または内部に配置しても良いし、紙の中に埋め込んでも良い。

【0104】

素子群904を有する半導体装置を曲面を有する基板に貼る場合について説明する。説明には図8(C)を用いる。図面では、素子群904から選択された1つのトランジスタ981を図示する。トランジスタ981は、ゲート電極907の電位に応じて、ソース及びドレインの一方905からソース及びドレインの他方906に電流を流す。トランジスタ981の電流が流れる方向(キャリアの移動方向3004)と、基板980が弧を描く方向が直交するように、トランジスタ981は配置される。このような配置にすれば、基板980が折り曲げられて弧を描いても、トランジスタ981に与えられる応力の影響が少なく、素子群904が含むトランジスタ981の特性の変動を抑制することができる。

【0105】

本実施例は、上記の実施の形態、実施例1と自由に組み合わせることができる。

【実施例3】

【0106】

本実施例では、本発明の半導体装置201を構成する回路が有するトランジスタの構成例を示す。トランジスタは単結晶基板に形成されるMOSトランジスタの他、薄膜トランジスタ(TFT)で構成することもできる。図11はこれらの回路を構成するトランジスタの断面構造を示す図である。図11は、Nチャネル型のトランジスタ2001、Nチャネル型のトランジスタ2002、容量素子2004、抵抗素子2005、Pチャネル型のトランジスタ2003が示されている。各トランジスタは半導体層405、絶縁層408、ゲート電極409を備えている。ゲート電極409は、第1導電層403と第2導電層402の積層構造で形成されている。また、図12(A)〜(D)は、図11で示すトランジスタ、容量素子、抵抗素子に対応する上面図であり合わせて参照することができる。

【0107】

図11において、Nチャネル型のトランジスタ2001の半導体層405には、ゲート電極409と重なる領域を挟んでチャネル長方向(キャリアの流れる方向)に並ぶように一対の不純物領域407が形成されている。不純物領域407は低濃度ドレイン(LDD)領域であり、配線404とコンタクトを形成するソース領域及びドレイン領域を形成する不純物領域406の導電型を付与する不純物元素の濃度よりも低濃度に当該不純物元素がドープされた領域である。不純物領域406と不純物領域407には、Nチャネル型のトランジスタ2001を構成する場合、N型を付与する不純物としてリンなどが添加されている。LDD領域はホットエレクトロン劣化や短チャネル効果を抑制する手段として形成される。

【0108】

図12(A)で示すように、Nチャネル型のトランジスタ2001のゲート電極409において、第1導電層403は第2導電層402の両側に広がって形成されている。この場合において、第1導電層403の膜厚は第2導電層402の膜厚よりも薄く形成されている。第1導電層403の厚さは、10〜100kVの電界で加速されたイオン種を通過させることが可能な厚さに形成されている。不純物領域407はゲート電極409の第1導電層403と重なるように形成されている。すなわち、ゲート電極409とオーバーラップするLDD領域を形成している。この構造は、ゲート電極409において、第2導電層402をマスクとして第1導電層403を通して一導電型の不純物を添加することにより、自己整合的に不純物領域407を形成している。すなわち、ゲート電極とオーバーラップするLDD領域を自己整合的に形成している。

【0109】

ゲート電極の両側にLDD領域を有するトランジスタは、図3における電源回路204中の第一の整流回路223及び第二の整流回路225に用いられる整流用のトランジスタや、論理回路に用いられるトランスミッションゲート(アナログスイッチとも呼ぶ)を構成するトランジスタに適用される。これらのトランジスタは、ソース電極及びドレイン電極に正負両方の電圧が印加されるため、ゲート電極の両側にLDD領域を設けることが好ましい。

【0110】

図11において、Nチャネル型のトランジスタ2002の半導体層405には、チャネル形成領域の片側に不純物領域407が形成されている。不純物領域407は、不純物領域406の不純物濃度よりも低濃度に不純物元素がドープされた低濃度ドレイン(LDD)領域である。図12(B)で示すように、Nチャネル型のトランジスタ2002のゲート電極409において、第1導電層403は、第2導電層402の片側に広がって形成されている。この場合も同様に、第2導電層402をマスクとして、第1導電層403を通して一導電型の不純物を添加することにより、自己整合的にLDD領域を形成することができる。

【0111】

ゲート電極の片側にLDD領域を有するトランジスタは、ソース電極及びドレイン電極間に正電圧のみ、もしくは負電圧のみが印加されるトランジスタに適用すればよい。具体的には、インバータ回路、NAND回路、NOR回路、ラッチ回路といった論理ゲートを構成するトランジスタや、センスアンプ、定電圧発生回路、VCO(Voltage Controlled Oscillator)といったアナログ回路を構成するトランジスタに適用すればよい。

【0112】

図11において、容量素子2004は、第1導電層403と半導体層405とで絶縁層408を挟んで形成されている。容量素子2004を形成する半導体層405には、不純物領域410と不純物領域411を備えている。不純物領域411は、半導体層405において第1導電層403と重なる位置に形成される。また、不純物領域410は配線404とコンタクトを形成する。不純物領域411は、第1導電層403を通して一導電型の不純物を添加することができるので、不純物領域410と不純物領域411に含まれる不純物濃度は同じにすることもできるし、異ならせることも可能である。いずれにしても、容量素子2004において、半導体層405は電極として機能させるので、一導電型の不純物を添加して低抵抗化しておくことが好ましい。また、第1導電層403は、図12(C)に示すように、第2導電層402を補助的な電極として利用することにより、第1導電層403及び第2導電層402は容量素子2004の電極として十分に機能させることができる。このように、第1導電層403と第2導電層402を組み合わせた複合的な電極構造とすることにより、容量素子2004を自己整合的に形成することができる。

【0113】

容量素子2004は、図3に示す電源回路204の保持容量224、あるいは高周波回路203が有する共振容量220、データ復調回路が有する第一の容量素子230及び第二の容量素子231として用いることができる。特に、共振容量は、容量素子の2端子間に正負両方の電圧が印加されるため、2端子間の電圧の正負によらず容量として機能することが必要である。

【0114】

図11において、抵抗素子2005は、第1導電層403によって形成されている(図12(D)も参照)。第1導電層403は30〜150nm程度の厚さに形成されるので、その幅や長さを適宜設定して抵抗素子を構成することができる。

【0115】

抵抗素子は、図1に示すデータ変調回路208が有する抵抗負荷として用いることができる。また、図3に示すデータ復調回路207が有する第一の抵抗素子228及び第二の抵抗素子229としても用いることができる。さらに、VCOなどで電流を制御する場合の負荷としても用いることができる。抵抗素子は、導電型を付与する不純物元素を高濃度に含む半導体層や、膜厚の薄い金属層によって構成すればよい。抵抗値が膜厚、膜質、不純物濃度、活性化率などに依存する半導体層に対して、金属層は、膜厚、膜質で抵抗値が決定するため、ばらつきが小さく好ましい。

【0116】

図11において、Pチャネル型のトランジスタ2003は、半導体層405に不純物領域412を備えている。この不純物領域412は、配線404とコンタクトを形成するソース領域及びドレイン領域として機能する。ゲート電極409の構成は第1導電層403と第2導電層402が重畳した構成となっている(図12(E)も参照)。Pチャネル型のトランジスタ2003はLDD領域を設けないシングルドレイン構造のトランジスタである。Pチャネル型のトランジスタ2003を形成する場合、不純物領域412にはP型を付与する不純物として硼素などが添加される。一方、不純物領域412にN型を付与する不純物としてリンなどを添加すればシングルドレイン構造のnチャネル型トランジスタとすることもできる。

【0117】

半導体層405及びゲート絶縁層408の一方若しくは双方に対して、高密度プラズマ処理によって酸化又は窒化処理しても良い。この処理は、実施例1で示した手法と同様にすることができる。

【0118】

上記処理によって、半導体層405とゲート絶縁層408の界面の欠陥準位を低減することができる。ゲート絶縁層408対してこの処理を行うことにより、この絶縁層の緻密化を図ることができる。すなわち、荷電欠陥の生成を抑えトランジスタのしきい値電圧の変動を抑えることができる。また、トランジスタを3V以下の電圧で駆動させる場合には、このプラズマ処理により酸化若しくは窒化された絶縁層をゲート絶縁層408として適用することができる。また、トランジスタの駆動電圧が3V以上の場合には、このプラズマ処理で半導体層405の表面に形成した絶縁層とCVD法(プラズマCVD法若しくは熱CVD法)で堆積した絶縁層とを組み合わせてゲート絶縁層408を形成することができる。また、同様に、この絶縁層は、容量素子2004の誘電体層としても利用することができる。この場合、このプラズマ処理で形成された絶縁層は、1〜10nmの厚さで形成され、緻密な膜であるので、大きな電荷容量を持つ容量素子を形成することができる。

【0119】

図11及び図12を参照して説明したように、膜厚の異なる導電層を組み合わせることにより、さまざまな構成の素子を形成することができる。第1導電層のみが形成される領域と、第1導電層と第2導電層が積層されている領域は、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いて形成することができる。すなわち、フォトリソグラフィー工程において、フォトレジストを露光する際に、フォトマスクの透過光量を調節して、現像されるレジストマスクの厚さを異ならせる。この場合、フォトマスクまたはレチクルに解像度限界以下の間隔を有する複数のスリットを設けて上記複雑な形状を有するレジストを形成してもよい。また、現像後に約200℃のベークを行ってフォトレジスト材料で形成されるマスクパターンを変形させてもよい。

【0120】

また、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いることにより、第1導電層のみが形成される領域と、第1導電層と第2導電層が積層されている領域を連続して形成することができる。図12(A)に示すように、第1導電層のみが形成される領域を半導体層上に選択的に形成することができる。半導体層上において第1導電層のみが形成される領域を設けることは、LDD領域を自己整合的に作製することができる等の点で有効であるが、半導体層上以外の領域(ゲート電極と連続する配線領域)では第1導電層のみが形成される領域は必要がない。このフォトマスク若しくはレチクルを用いることにより、配線部分は、第1導電層のみの領域を作らないで済むので、配線密度を実質的に高めることができる。

【0121】

図11及び図12の場合には、第1導電層はタングステン(W)、クロム(Cr)、タンタル(Ta)、窒化タンタル(TaN)またはモリブデン(Mo)などの高融点金属、又は高融点金属を主成分とする合金もしくは化合物を30〜50nmの厚さで形成する。また、第2導電層はタングステン(W)、クロム(Cr)、タンタル(Ta)、窒化タンタル(TaN)またはモリブデン(Mo)などの高融点金属、又は高融点金属を主成分とする合金もしくは化合物で300〜600nmの厚さに形成する。例えば、第1導電層と第2導電層をそれぞれ異なる導電材料を用い、後に行うエッチング工程でエッチングレートの差が生じるようにする。一例として、第1導電層をTaNを用い、第2導電層としてタングステン膜を用いることができる。

【0122】

本実施例では、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いて、電極構造の異なるトランジスタ、容量素子、抵抗素子を、同じフォトマスクまたはレチクルを用いたエッチング工程によって作り分ける方法を示した。これにより、回路の特性に応じて、形態の異なる素子を、工程を増やすことなく作り込み、集積化することができる。

【0123】

本実施例は、上記の実施の形態、実施例1及び実施例2と自由に組み合わせることができる。

【実施例4】

【0124】

本実施例では、半導体装置201のメモリ回路210等として用いることができるスタティックRAM(SRAM)の一例について、図13〜図15を参照して説明する。

【0125】

図13(A)で示す半導体層10、半導体層11はシリコン若しくはシリコンを成分とする結晶性の半導体で形成することが好ましい。例えば、半導体層10、半導体層11として、シリコン膜をレーザアニールなどによって結晶化された多結晶シリコン、単結晶シリコンなどが適用される。その他にも半導体特性を示す、金属酸化物半導体、アモルファスシリコン、有機半導体を適用することも可能である。

【0126】

いずれにしても、最初に形成する半導体層は絶縁表面を有する基板の全面若しくは一部(トランジスタの半導体領域として確定されるよりも広い面積を有する領域)に形成する。そして、フォトリソグラフィー技術によって、半導体層上にマスクパターンを形成する。そのマスクパターンを利用して半導体層をエッチング処理することにより、トランジスタのソース領域及びドレイン領域及びチャネル形成領域を含む特定形状の島状の半導体層10、半導体層11を形成する。

【0127】

図13(A)で示す半導体層10、半導体層11を形成するためのフォトマスクは、図13(B)に示すマスクパターン2000を備えている。このマスクパターン2000は、フォトリソグラフィー工程で用いるレジストがポジ型かネガ型かで異なる。ポジ型レジストを用いる場合には、図13(B)で示すマスクパターン2000は、遮光部として作製される。マスクパターン2000は、多角形の頂部Aを削除した形状となっている。このフォトマスクのパターンは、例えば、角部において一辺が10μm以下の直角三角形を切り取るように面取りされている。また、屈曲部Bにおいては、その角部が直角とならないように屈曲する形状となっている。屈曲部Bを拡大すると、複数段に渡って屈曲する形状(実施例1で図7を用いて示した構成参照)となっている。

【0128】

図13(B)で示すマスクパターン2000は、その形状が、図13(A)で示す半導体層10、半導体層11に反映される。その場合、マスクパターン2000と相似の形状が転写されても良いが、マスクパターン2000の角部がさらに丸みを帯びるように転写されていても良い。すなわち、マスクパターン2000よりもさらにパターン形状をなめらかにした丸め部を設けても良い。

【0129】

半導体層10、半導体層11の上には、酸化シリコン若しくは窒化シリコンを少なくとも一部に含む絶縁層が形成される。この絶縁層を形成する目的の一つはゲート絶縁層である。そして、図14(A)で示すように、半導体層と一部が重なるようにゲート配線12、ゲート配線13、ゲート配線14を形成する。ゲート配線12は半導体層10に対応して形成される。ゲート配線13は半導体層10、半導体層11に対応して形成される。また、ゲート配線14は半導体層10、半導体層11に対応して形成される。ゲート配線は、金属層又は導電性の高い半導体層を成膜し、フォトリソグラフィー技術によってその形状を絶縁層上に作り込まれる。

【0130】

このゲート配線を形成するためのフォトマスクは、図14(B)に示すマスクパターン2100を備えている。このマスクパターン2100は、角部において一辺が10μm以下または配線の線幅の1/2以下で線幅の1/5以上の大きさの直角三角形を切り取るように面取りされている。図14(B)で示すマスクパターン2100は、その形状が、図14(A)で示すゲート配線12、ゲート配線13、ゲート配線14に反映される。その場合、マスクパターン2100と相似の形状が転写されても良いが、マスクパターン2100の角部がさらに丸みを帯びるように転写されていても良い。すなわち、マスクパターン2100よりもさらにパターン形状をなめらかにした、丸め部を設けても良い。すなわち、ゲート配線12、ゲート配線13、ゲート配線14の角部は、丸みをおびていてもよい。角部の外側はプラズマによるドライエッチの際、異常放電による微粉の発生を抑え、角部の内側では、たとえ洗浄のときにできた微粉であっても、それが角に集まりやすいのを洗い流す。その結果、歩留まり向上が非常に期待できるという効果を有する。

【0131】

層間絶縁層はゲート配線12、ゲート配線13、ゲート配線14の次に形成される層である。層間絶縁層は酸化シリコンなどの無機絶縁材料若しくポリイミドやアクリル樹脂などを使った有機絶材料を使って形成する。この層間絶縁層とゲート配線12、ゲート配線13、ゲート配線14の間には窒化シリコン若しくは窒化酸化シリコンなどの絶縁層を介在させても良い。また、層間絶縁層上にも窒化シリコン若しくは窒化酸化シリコンなどの絶縁層を設けても良い。この絶縁層は、外因性の金属イオンや水分など薄膜トランジスタ(TFT)にとっては良くない不純物により半導体層やゲート絶縁層を汚染するのを防ぐことができる。

【0132】

層間絶縁層には所定の位置に開孔が形成されている。例えば、下層にあるゲート配線や半導体層に対応して設けられる。金属若しくは金属化合物の一層若しくは複数層で形成される配線層は、フォトリソグラフィー技術によってマスクパターンが形成され、エッチング加工により所定のパターンに形成される。そして、図15(A)で示すように、半導体層10や半導体層11と一部が重なるように配線15、配線16、配線17、配線18、配線19、配線20を形成する。配線はある特定の素子間を連結する。配線は特定の素子と素子の間を直線で結ぶのではなく、レイアウトの制約上屈曲部が含まれる。また、他の配線とのコンタクト部やその他の領域において配線幅が変化する。コンタクト部では、コンタクトホールが配線幅と同等若しくは大きい場合には、その部分で配線幅が広がるように変化する。

【0133】

この配線15乃至配線20を形成するためのフォトマスクは、図15(B)に示すマスクパターン2200を備えている。この場合においても、マスクパターンは、角部において一辺が10μm以下または配線の線幅の1/2以下で線幅の1/5以上の大きさの直角三角形を切り取るように面取りされる。更に、角部に丸みをおびさせてもよい。このような配線は、角部の外側はプラズマによるドライエッチの際、異常放電による微粉の発生を抑え、角部の内側では、たとえ洗浄のときにできた微粉であっても、それが角に集まりやすいのを洗い流す。その結果、歩留まり向上が非常に期待できるという効果を有する。配線の角部が丸みをおびることにより、配線の電気伝導を良好にする効果が期待できる。また、多数の配線を平行に設けた構造において、角部が丸みをおびた配線を用いることは、ゴミを洗い流すのにきわめて好都合である。

【0134】

図15(A)には、Nチャネル型のトランジスタ21、Nチャネル型のトランジスタ22、Nチャネル型のトランジスタ23、Nチャネル型のトランジスタ24、Pチャネル型のトランジスタ25、Pチャネル型のトランジスタ26が形成されている。Nチャネル型のトランジスタ23とPチャネル型のトランジスタ25はインバータ27を構成している。Nチャネル型のトランジスタ24とPチャネル型のトランジスタ26はインバータ28を構成している。この6つのトランジスタを含む回路はSRAMを形成している。これらのトランジスタの上層には、窒化シリコンや酸化シリコンなどの絶縁層が形成されていても良い。

【0135】

本実施例は、上記の実施の形態、実施例1乃至実施例3と自由に組み合わせることができる。

【実施例5】

【0136】

本発明の半導体装置201の一実施例を図17に示す。図17(A)は半導体装置201の展開図であり、図17(B)は図17(A)のA−Bにおける断面図である。本実施例では、複数のアンテナを有する半導体装置201において、特に薄膜トランジスタを有する層上に形成されたアンテナと、パッチアンテナとを有する半導体装置201の構造について説明する。

【0137】

実施例1で示した素子群601の作製方法と同様に、絶縁性基板7101上に薄膜トランジスタを有する層7102が形成される。薄膜トランジスタを有する層7102上に層間絶縁層7182が形成される。層間絶縁層7182上に第1のアンテナ7181が形成される。第1のアンテナ7181上には絶縁層7183が形成され、絶縁層7183の表面に接続端子7184が形成される。

【0138】

一部に接続端子7184が露出した絶縁層7183と第2のアンテナであるパッチアンテナ7103とが、異方性導電接着材7104により固着される。また、接続端子7184とパッチアンテナの給電体層7113とが、異方性導電接着材7104に分散される導電性粒子で電気的に接続される。接続端子7184と薄膜トランジスタを有する層7102に形成される第1の薄膜トランジスタ7185とが電気的に接続される。また、薄膜トランジスタを有する層7102に形成される第2の薄膜トランジスタ7186と第1のアンテナ7181とが電気的に接続される。なお、異方性導電接着材の代わりに、導電性ペーストを硬化した導電層を用いてもよい。

【0139】

第1のアンテナ7181は、アルミニウム、銅、銀を含む金属材料で形成する。例えば、銅又は銀のペースト状組成物を、スクリーン印刷、オフセット印刷、インクジェット方式の印刷法で形成することができる。また、スパッタリングなどでアルミニウム膜を形成し、エッチング加工により形成しても良い。その他、電解メッキ法、無電解メッキ法を用いて形成しても良い。

【0140】

なお、第1のアンテナ7181を省略することも可能である。

【0141】

ここでは、第1のアンテナ7181の形状は、図18(A)に示すように方形コイル状である。

【0142】

第1のアンテナ7181の形状について図18を用いて説明する。図18は、層間絶縁層7182及びその上に形成されたアンテナを示す上面図である。本実施例では、図17(A)及び図18(A)に示すように、第1のアンテナ7181は方形コイル状7181aであるがこの形状に限定されるものではない。円形コイル状としてもよい。また、図18(B)に示すように方形ループ状7181bのアンテナとすることができる。また、円形ループ状アンテナとすることができる。また、図18(C)に示すように直線型ダイポール状7181cのアンテナとすることができる。また、曲線型ダイポール状のアンテナとすることができる。

【0143】

このように複数のアンテナを設けることで、一つの半導体装置で複数の異なる周波数の電波を受信することが可能なマルチバンド対応の半導体装置を形成することができる。

【0144】

本実施例は、上記の実施の形態、実施例1乃至実施例4と自由に組み合わせることができる。

【実施例6】

【0145】

本実施例では、本発明の半導体装置201の用途について図9及び図10を用いて説明する。半導体装置201は、例えば、紙幣、硬貨、有価証券、無記名債券類、証書類(運転免許証や住民票等、図10(A)参照)に設けて使用することができる。また、包装用容器類(包装紙やボトル等、図10(B)参照)、DVDソフトやCDやビデオテープ等の記録媒体(図10(C)参照)に設けて使用することができる。また、車やバイクや自転車等の乗物類(図10(D)参照)、鞄や眼鏡等の身の回り品(図10(E)参照)、食品類、衣類、生活用品類、電子機器等に設けて使用することができる。電子機器とは、液晶表示装置、EL(エレクトロルミネッセンス)表示装置、テレビジョン装置(単にテレビまたはテレビ受像器とも呼ぶ)および携帯電話機等を指す。

【0146】

半導体装置201は、物品の表面に貼り付けたり、物品に埋め込んだりして物品に固定することができる。例えば、本なら紙に埋め込んだり、有機樹脂からなるパッケージなら当該有機樹脂に埋め込んだりするとよい。紙幣、硬貨、有価証券類、無記名債券類、証書類等に半導体装置201を設けることにより、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に半導体装置201を設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。また乗物類に半導体装置201を設けることにより、偽造や盗難を防止することができる。また、動物等の生き物に埋め込むことによって、個々の生き物の識別を容易に行うことができる。例えば、家畜等の生き物に無線タグを埋め込むことによって、生まれた年や性別または種類等を容易に識別することが可能となる。

【0147】

以上のように、本発明の半導体装置201は物品(生き物を含む)であればどのようなものにでも設けて使用することができる。

【0148】

半導体装置201は、無線通信によるデータの送受信が可能である点、様々な形状に加工可能である点、選択する周波数によっては、指向性が広く、認識範囲が広い点等の様々な利点を有する。

【0149】

次に、半導体装置201を用いたシステムの一形態について、図9を用いて説明する。表示部521を含む携帯端末の側面には、リーダ/ライタ520が設けられ、物品A522の側面には本発明の半導体装置523が設けられ、物品B532の上面には本発明の半導体装置531が設けられている(図9(A)参照)。物品A522が含む半導体装置523にリーダ/ライタ520をかざすと、表示部521に物品A522の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴、商品の説明等の商品に関する情報が表示される。物品B532が含む半導体装置531にリーダ/ライタ520をかざすと、表示部521に物品B532の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴、商品の説明等の商品に関する情報が表示される。

【0150】

図9(A)に示すシステムを利用したビジネスモデルの一例を示す。説明には図9(B)のフローチャートを用いる。携帯端末において、食物アレルギーの情報を入力しておく(ステップ1)。食物アレルギーの情報とは、所定の人物が食物アレルギー反応を起こす原材料等の情報である。携帯端末に設けられたリーダ/ライタ520によって、前述のとおり物品A522の情報を取得する(ステップ2)。ここで、物品A522は食品であるとする。物品A522の情報には物品A522の原材料の情報が含まれる。食物アレルギーの情報と取得した物品A522の原材料の情報とを比較し、一致する材料があるか否かを判断する(ステップ3)。一致する材料がある場合、所定の人物は物品Aに対してアレルギー反応を起こす危険性があるとし、携帯端末の使用者に注意を呼びかける(ステップ4)。一致する材料がない場合、所定の人物は物品Aに対してアレルギー反応を起こす危険性が少ないとし、携帯端末の使用者にその旨(安全である旨)を知らせる(ステップ5)。ステップ4やステップ5において、携帯端末の使用者に情報を知らせる方法は、携帯端末の表示部521に表示を行う方法であっても良いし、携帯端末のアラーム等を鳴らす方法であっても良い。

【0151】

本発明の半導体装置201は過電圧を防止するため信頼性が高く、且つサイズを小さくすることができる。よって、本発明により、半導体装置201を搭載することができるものの範囲が広がり、多様なシステムを実現することができる。こうして、高機能化と高付加価値化を実現したシステムを提供することができる。

【0152】

本実施例は、上記の実施の形態、実施例1乃至実施例5と自由に組み合わせることができる。

【図面の簡単な説明】

【0153】

【図1】本発明の半導体装置の構成を示す図。

【図2】従来の半導体装置の構成を示す図。

【図3】本発明の半導体装置の構成を示す図。

【図4】本発明の半導体装置のマスク図面の一部を示す図。

【図5】本発明の半導体装置のアンテナの構成を示す図。

【図6】本発明の半導体装置の作製方法を示す図。

【図7】半導体装置の配線の引き回し方法を示す図。

【図8】本発明の半導体装置の作製方法を示す図。

【図9】本発明の半導体装置の用途を示す図。

【図10】本発明の半導体装置の用途を示す図。

【図11】本発明の半導体装置の作製方法を示す図。

【図12】本発明の半導体装置の作製方法を示す図。

【図13】本発明の半導体装置の作製方法を示す図。

【図14】本発明の半導体装置の作製方法を示す図。

【図15】本発明の半導体装置の作製方法を示す図。

【図16】本発明の半導体装置のマスク図面の一部及び等価回路を示す図。

【図17】本発明の半導体装置の構成を示す図。

【図18】本発明の半導体装置のアンテナの構成を示す図。

【符号の説明】

【0154】

10 半導体層

11 半導体層

12 ゲート配線

13 ゲート配線

14 ゲート配線

15 配線

16 配線

17 配線

18 配線

19 配線

20 配線

21 トランジスタ

22 トランジスタ

23 トランジスタ

24 トランジスタ

25 トランジスタ

26 トランジスタ

27 インバータ

28 インバータ

101 アナログ回路部

102 デジタル回路部(ロジック回路部)

201 半導体装置

202 アンテナ

203 高周波回路

204 電源回路

205 リセット回路

206 クロック発生回路

207 データ復調回路

208 データ変調回路

209 制御回路

210 メモリ回路

211 半導体集積回路

220 共振容量

221 第一の帯域フィルタ

222 第二の帯域フィルタ

223 第一の整流回路

224 保持容量

225 第二の整流回路

226 制御回路内回路

227 インバータ

228 第一の抵抗素子

229 第二の抵抗素子

230 第一の容量素子

231 第二の容量素子

232 N型トランジスタ

233 N型トランジスタ

234 N型トランジスタ

235 N型トランジスタ

301 半導体装置

302 アンテナ

303 高周波回路

304a 電源回路

304b リミッタ回路

304c リセット回路

304d クロック発生回路

305 データ復調回路

306 データ変調回路

307 制御回路

308 メモリ回路

309 半導体集積回路

402 第2導電層

403 第1導電層

404 配線

405 半導体層

406 不純物領域

407 不純物領域

408 絶縁層

409 ゲート電極

410 不純物領域

411 不純物領域

412 不純物領域

520 リーダ/ライタ

521 表示部

522 物品A

523 半導体装置

531 半導体装置

532 物品B

600 基板

601 素子群

602 端子部

603 導電性粒子

604 樹脂

610 基板

661 下地層

662 半導体層

662a チャネル形成領域

662b 不純物領域

662c 低濃度不純物領域

663 第1の絶縁層

664 ゲート電極

665 第3の絶縁層

666 配線

667 第2の絶縁層

668 第4の絶縁層

701 フレキシブル基板

720 無線タグ

901 保護層

902 アンテナ

903 保護層

904 素子群

905 ソース及びドレインの一方

906 ソース及びドレインの他方

907 ゲート電極

980 基板

981 トランジスタ

1101 アナログ回路部

1102 デジタル回路部(ロジック回路部)

1201a 角部

1201b 角部

1201c 角部

1202a 角部

1202b 角部

1202c 角部

2000 マスクパターン

2100 マスクパターン

2200 マスクパターン

2001 トランジスタ

2002 トランジスタ

2003 トランジスタ

2004 容量素子

2005 抵抗素子

3003 厚さ

3004 キャリアの移動方向

3005 方向

3011 配線

3012 配線

3013 配線

3014 コンタクトホール

5000a 端子

5000b 端子

5001a N型半導体層

5001b P型半導体層

5002 コンタクトホール

5003 第1の配線

5004 第2の配線

5501 P型トランジスタ

5502 N型トランジスタ

5550 N型トランジスタ

7101 絶縁性基板

7102 層

7103 パッチアンテナ

7104 異方性導電接着材

7113 給電体層

7181 第1のアンテナ

7181a 方形コイル状

7181b 方形ループ状

7181c 直線型ダイポール状

7182 層間絶縁層

7183 絶縁層

7184 接続端子

7185 第1の薄膜トランジスタ

7186 第2の薄膜トランジスタ

【技術分野】

【0001】

本発明は無線通信によりデータの交信が可能な半導体装置に関する。データの受信のみ、またはデータの送信のみを行う半導体装置に関する。また、前記半導体装置と、無線通信によって情報の交信を行うリーダ/ライタとを有する無線通信システムに関する。

【背景技術】

【0002】

個々の対象物にID(個体識別番号)を与えることで、その対象物の履歴を明確にし、生産、管理等に役立てるといった個体認識技術が注目されている。その中でも、RFIDタグ(ICタグ、ICチップ、RF(Radio Frequency)タグ、無線タグ、電子タグ、トランスポンダとも呼ばれる)等の無線通信によりデータの交信が可能な半導体装置を用いたRFID(Radio Friquency Identification)技術が利用され始めている。

【0003】

無線通信によりデータの交信が可能な半導体装置の一般的な構成について、図2を用いて説明する。

【0004】

無線通信によりデータの交信が可能な半導体装置301は、アンテナ302及び半導体集積回路309を有する。

【0005】

また、無線通信によりデータの交信が可能な半導体装置301は、主にアナログ回路部1101及びデジタル回路部(ロジック回路部)1102に分けられる。

【0006】

アナログ回路部1101は、アンテナ302、高周波回路303、電源回路304a、リミッタ回路304b、リセット回路304c、クロック発生回路304d、データ復調回路305、データ変調回路306等を有し、デジタル回路部(ロジック回路部)1102は、制御回路307及びメモリ回路308等を有する。

【0007】

次に、無線通信によりデータの交信が可能な半導体装置301の一般的な動作について、図2を用いて説明する。

【0008】

はじめに、アンテナ302により無線信号が受信される。無線信号は高周波回路303を介して電源回路304aに入力され、高電源電位(以下、VDD)が生成される。VDDはリミッタ回路304bにより所定の電位以下となるように制御され、各回路に供給される。また、無線信号は高周波回路303を介してデータ復調回路305に入力され、復調される(以下、復調信号)。さらに、無線信号は高周波回路303を介して、リセット回路304cに入力される。復調信号はクロック発生回路304dに入力される。リセット回路304cの出力信号(以下、リセット)及びクロック発生回路304dの出力信号(以下、クロック)と、復調信号とは制御回路307に入力される。制御回路307に入力された復調信号は、制御回路307によって解析される。そして、解析された信号にしたがって、メモリ回路308内に記憶されている半導体装置の情報が出力される。出力された半導体装置の情報は制御回路307によって符号化される。さらに、符号化された半導体装置の情報に基づき、データ変調回路306は搬送波を変調する。こうして、半導体装置の情報はアンテナ302により無線信号に載せて送信される。なお、図示していないが、半導体集積回路309を構成する複数の回路においては、低電源電位(以下、VSS)は共通である。VSSは例えばGNDとすることができる。VSSとVDDの電位差が半導体集積回路309を構成する複数の回路に供給され、それらの回路の電源電圧となる。

【0009】

無線信号を送受信するリーダ/ライタと半導体装置の距離によって、半導体装置内のアンテナが受信する無線信号の振幅は変化する。リーダ/ライタと半導体装置の距離が近い場合は半導体装置内のアンテナが受信する無線信号の振幅は大きく、リーダ/ライタと半導体装置の距離が遠い場合は半導体装置内のアンテナが受信する無線信号の振幅は小さい。

【0010】

無線信号を送受信するリーダ/ライタと半導体装置の距離が近い場合には、電源回路によって生成されるVDDが高くなり、半導体装置内に必要以上の電圧(以下、過電圧)が供給されることになる。そのため、半導体装置内の素子(トランジスタ、容量素子、抵抗素子等)が破壊される可能性がある。

【0011】

そこで、半導体装置は、図2のようにリミッタ回路304b等を設け、所定の電位より大きい高電源電位は内部回路に供給されないような構成となっている。このようなリミッタ回路を用いた半導体装置は例えば特許文献1に記載されている。なお、特許文献1では、リミッタ回路はレギュレータ回路と表記している。

【特許文献1】特開2001−125653号公報

【発明の開示】

【発明が解決しようとする課題】

【0012】

従来のようにリミッタ回路を設けた半導体装置では、半導体装置内の回路構成が複雑となり、半導体装置のサイズが大きくなるという問題点がある。

【0013】

上記の実情を鑑み、無線通信によりデータの交信が可能な半導体装置において、過電圧による半導体装置内の素子(トランジスタ、容量素子、抵抗素子等)の破壊を防止し、且つ回路構成を単純にしてサイズを小さくすることを課題とする。

【課題を解決するための手段】

【0014】

本発明は、前述した課題を解決するために、以下の構成を有することを特徴とする。

【0015】

本発明の半導体装置は、アナログ回路部とデジタル回路部(ロジック回路部)を有する。半導体装置内のアナログ回路部とデジタル回路部(ロジック回路部)で使用するトランジスタにおいて、アナログ回路部内、特に電源回路及びデータ復調回路のトランジスタのゲート長(チャネル長)をデジタル回路部(ロジック回路部)内のトランジスタのゲート長(チャネル長)以上とすることを特徴とする。

【0016】

好ましくは、アナログ回路部内、特に、電源回路、データ復調回路で使用されるトランジスタのゲート長(チャネル長)をデジタル回路部(ロジック回路部)で使用されるトランジスタのゲート長(チャネル長)の2倍以上とする。

【0017】

本発明の半導体装置は、アナログ回路部を有する。アナログ回路部には無線信号が入力される。アナログ回路部は、無線信号を用いて直流電圧を発生する電源回路と、無線信号を復調するデータ復調回路と、データ復調回路の出力を用いてクロックを生成するクロック発生回路とを有する。電源回路及びデータ復調回路が有するトランジスタのゲート長(チャネル長)は、クロック発生回路が有するトランジスタのゲート長(チャネル長)以上とすることを特徴とする。

【0018】

好ましくは、電源回路及びデータ復調回路で使用されるトランジスタのゲート長(チャネル長)をクロック発生回路で使用されるトランジスタのゲート長(チャネル長)の2倍以上とする。

【0019】

なお、マルチゲート型のトランジスタ(複数のトランジスタが直列に接続された構成)の場合、マルチゲート型のトランジスタのゲート長(チャネル長)とは当該トランジスタを構成する複数のトランジスタの各々に対するゲート長(チャネル長)であるとする。

【0020】

本発明において、ゲート電極の幅が異なることにより、複数の異なるゲート長を有するゲート電極を用いてもよい。この場合、アナログ回路部内のトランジスタのゲート電極において最も短いゲート長は、デジタル回路部内のトランジスタのゲート長において最も長いゲート長よりも長ければよい。

【発明の効果】

【0021】

アナログ回路部内、特に電源回路及びデータ復調回路のトランジスタのゲート長をデジタル回路部(ロジック回路部)内のトランジスタのゲート長以上とすることで、リミッタ回路等の特別な回路を設けることなく、過電圧が供給された際にゲート長の長いアナログ回路部で電圧を緩和することができる。さらに、アナログ回路部からの信号が入力されるデジタル回路部(ロジック回路部)において、トランジスタ等の回路内の素子が破壊されるのを防止することができる。

【0022】

また、アナログ回路部、特に電源回路及びデータ復調回路は、受信した無線信号から定電位(VDD)を生成したり、受信した無線信号よりも周波数の遅い復調信号を生成したりする。つまり、アナログ回路部、特に電源回路及びデータ復調回路は、受信した無線信号を加工することを主目的とするため、周波数の速い動作は必要がない。一方、デジタル回路部(ロジック回路部)及びアナログ回路部内のクロック発生回路等は、アナログ回路部で生成された復調信号、VDD等を用いて演算処理などを行うため、周波数の速い動作が必要とされる。したがって、半導体装置内のアナログ回路部とデジタル回路部(ロジック回路部)で使用するトランジスタにおいて、アナログ回路部内、特に電源回路及びデータ復調回路のトランジスタのゲート長をデジタル回路部(ロジック回路部)内のトランジスタのゲート長以上とすることで、無駄のないそれぞれの目的にあった動作が実現できる。

【発明を実施するための最良の形態】

【0023】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更しうることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じ物を指し示す符号は異なる図面間において共通とする。

【0024】

また、本発明において、接続されているとは電気的に接続されていることと同義である。したがって、間に、別の素子などが配置されていてもよい。

【0025】

(実施の形態1)

本実施の形態1では、本発明の無線通信によりデータの交信が可能な半導体装置の構成と当該半導体装置の動作について、図1を用いて説明する。

【0026】

はじめに、本発明の無線通信によりデータの交信が可能な半導体装置の構成について説明する。半導体装置201は、主にアナログ回路部101及びデジタル回路部(ロジック回路部)102を有する。そして、アナログ回路部101は、アンテナ202、高周波回路203、電源回路204、リセット回路205、クロック発生回路206、データ復調回路207、データ変調回路208等を有し、デジタル回路部(ロジック回路部)102は制御回路209及びメモリ回路210等を有する。

【0027】

次に、本発明の無線通信によりデータの交信が可能な半導体装置の動作について説明する。アンテナ202により無線信号が受信される。無線信号は高周波回路203を介して電源回路204に入力され、高電源電位(以下、VDD)が生成される。ここで、図示していないが、VDDは半導体集積回路211が有する各回路に供給される。また、高周波回路203を介してデータ復調回路207に入力された信号は復調される(以下、復調信号)。さらに、無線信号は高周波回路203を介してリセット回路205に入力され、リセット回路205の出力信号(リセット)は制御回路209に入力される。また、復調信号はクロック発生回路206に入力され、クロック発生回路206の出力信号(クロック)は制御回路209に入力される。更に、復調信号は制御回路209に入力される。制御回路209に入力された信号は、制御回路209によって解析される。そして、解析された信号にしたがって、メモリ回路210内に記憶されている半導体装置の情報が出力される。出力された半導体装置の情報は制御回路209によって符号化される。さらに、符号化された半導体装置の情報に基づき、データ変調回路208は搬送波を変調する。こうして、半導体装置の情報はアンテナ202により無線信号に載せて送信される。なお、図示していないが、半導体集積回路211を構成する複数の回路においては、低電源電位(以下、VSS)は共通である。VSSは例えばGND(接地電位)とすることができる。

【0028】

ここで、アナログ回路部101、特に、電源回路204、データ復調回路207で使用するトランジスタのゲート長は制御回路209及びメモリ回路210等を有するデジタル回路部(ロジック回路部)102で使用するトランジスタのゲート長以上である。

【0029】

そうすることで、リミッタ回路のような特別な回路を設けることなく、過電圧が供給された際にゲート長の長いアナログ回路部で電圧を緩和することができる。さらに、アナログ回路部101から出力された信号が入力されるデジタル回路部(ロジック回路部)102において、回路内の素子であるトランジスタ等が破壊されるのを防止することが出来る。

【0030】

また、アナログ回路部101、特に電源回路204及びデータ復調回路207は、受信した無線信号から定電位(VDD)を生成したり、受信した無線信号よりも周波数の遅い復調信号を生成したりする。つまり、アナログ回路部101、特に電源回路204及びデータ復調回路207は、受信した無線信号を加工することを主目的とする。よって、周波数の速い動作は必要がない。一方、デジタル回路部(ロジック回路部)102及びアナログ回路部101内のクロック発生回路206等は、アナログ回路部101で生成された復調信号、VDD等を用いて、演算処理を行うなど、周波数の速い動作が必要とされる。従って、半導体装置内のアナログ回路部101とデジタル回路部(ロジック回路部)102で使用するトランジスタにおいて、アナログ回路部101内、特に電源回路204及びデータ復調回路207のトランジスタのゲート長をデジタル回路部(ロジック回路部)102内のトランジスタのゲート長以上とする。こうして、それぞれの目的にあった無駄のない動作が実現できる。

【0031】

本発明の半導体装置のアンテナ202が受信する無線信号は、搬送波を変調した信号である。搬送波の変調方式は、アナログ変調またはデジタル変調であって、振幅変調、位相変調、周波数変調、及びスペクトラム拡散のいずれであってもよい。

【0032】

また、搬送波の周波数は、サブミリ波である300GHz以上3THz以下、ミリ波である30GHz以上300GHz未満、マイクロ波である3GHz以上30GHz未満、極超短波である300MHz以上3GHz未満、超短波である30MHz以上300MHz未満、短波である3MHz以上30MHz未満、中波である300KHz以上3MHz未満、長波である30KHz以上300KHz未満、及び超長波である3KHz以上30KHz未満のいずれの周波数も用いることができる。望ましくは、1GHz以下にすると良い。

【0033】

また、VSSと電源回路204が生成するVDDとの電位差、つまり、本発明の半導体装置の電源電圧(動作電圧)は1V〜6V、望ましくは3V以下にするとよい。本発明の半導体装置の電源電圧は、アナログ回路部101及びデジタル回路部(ロジック回路部)102で同じとすることができる。

【0034】

メモリ回路210は、DRAM(Dynamic Random Access Memory)、SRAM(Static Random Access Memory)、FeRAM(Ferroelectric Random Access Memory)、マスクROM(Read Only Memory)、EPROM(Electrically Programmable Read Only Memory)、EEPROM(Electrically Erasable and Programmable Read Only Memory)、フラッシュメモリを用いることができる。

【0035】

上記構成により本発明の無線通信によりデータの交信が可能な半導体装置は、リミッタ回路を設けることなく回路内の素子が破壊されるのを防止することができる。こうして、半導体装置のサイズを小さく抑え、且つ信頼性の高い半導体装置を提供することができる。

【0036】

(実施の形態2)

本実施の形態2では、実際に設計した回路の一部である図3を用いて動作の説明を行う。なお、図3では、動作の説明をするための最低限の回路構成しか図示していない。図示しない部分については図1と同様である。

【0037】

高周波回路203は、共振容量220、第一の帯域フィルタ221及び第二の帯域フィルタ222を有する。ここで、共振容量220はアンテナ202が受信したい周波数の信号を最も効率よく受信するために設けられる。また、第一の帯域フィルタ221及び第二の帯域フィルタ222はノイズを除去するために設けられる。第一の帯域フィルタ221及び第二の帯域フィルタ222は、共有化して1つの帯域フィルタとしても構わないが、2つに分けることが望ましい。

【0038】

ここで、ノイズを除去するために設けられている第一の帯域フィルタ221及び第二の帯域フィルタ222は、主に、抵抗素子と容量素子の接続により構成される。そして、高周波ノイズを遮断したい場合と低周波ノイズを遮断したい場合で、抵抗素子と容量素子の接続の仕方がかわる。たとえば、低周波ノイズを除去したい場合は容量素子と抵抗素子を直列に接続し、ハイパスフィルタを構成すればよい。どの帯域のノイズを除去するかは、本発明の半導体装置が使用される目的に即した設計仕様によって決定される。遮断したい周波数が十分に遮断できるように、容量素子の容量値または抵抗素子の抵抗値、抵抗素子の抵抗値と容量素子の容量値の両方を大きくしておくことが望ましい。なお、上記帯域フィルタにおいては、抵抗素子と容量素子の接続により構成しているが、抵抗素子や容量素子の代わりにトランジスタを用いても良いし、遮断したい周波数が遮断できる構成であれば、上記構成に限定されずにどのような構成を用いても良い。なお、抵抗素子及び容量素子を設ける代わりに、または、抵抗素子及び容量素子に加えて、配線や電極等の寄生抵抗や、複数の配線の重なりや複数の電極の重なりによる寄生容量を積極的に利用してもよい。

【0039】

第一の帯域フィルタ221を通った無線信号(交流信号)は電源回路204に入力する。そして、入力された無線信号(交流信号)は電源回路204内の第一の整流回路223により整流される。さらに、整流された信号は保持容量224により平滑化され、高電源電位(VDD)が生成される。VDDは本発明の半導体装置内の複数の回路ブロックに供給される。

【0040】

ここで、第一の整流回路223は2個のN型トランジスタを有する。N型トランジスタ234のゲートとソースは接続されており、ドレインにはVDDが与えられている。N型トランジスタ235のゲートとソースにはVSS(GND)が与えられており、ドレインはN型トランジスタ234のゲート及びソースに接続されている。こうすることで、受信した無線信号を整流することができる。

【0041】

なお、第一の整流回路223は、図3において示した回路構成に限定されず、図3とは異なる構成の半波整流回路を用いても良いし、全波整流回路を用いても良いし、交流信号を直流信号に変えることができる回路構成であれば、どのような回路を用いても良い。

【0042】

第二の帯域フィルタ222を通った無線信号(交流信号)は、データ復調回路207に入力する。そして、入力した無線信号(交流信号)はデータ復調回路207内の第二の整流回路225により整流される。さらに、第一の抵抗素子228、第一の容量素子230、第二の抵抗素子229及び第二の容量素子231により復調される(以下、復調信号)。復調信号は半導体装置201内の複数の回路ブロックに入力される。

【0043】

ここで、第二の整流回路225は2個のN型トランジスタを有する。N型トランジスタ232のゲートとソースは接続されており、ドレインは第一の抵抗素子228の一方、第一の容量素子230の一方及び第二の抵抗素子229の一方に接続されている。N型トランジスタ233のゲートとソースにはVSS(GND)が与えられており、ドレインはN型トランジスタ232のゲート及びソースに接続されている。

【0044】

また、第一の抵抗素子228の他方及び第一の容量素子230の他方はVSS(GND)が与えられている。さらに、第二の抵抗素子229の他方は第二の容量素子231の一方に接続されており、第二の容量素子231の他方にはVSS(GND)が与えられている。第二の抵抗素子229の他方及び第二の容量素子231の一方はデータ復調回路207の出力である。

【0045】

こうすることで、データ復調回路207は受信した交流信号を整流し、復調することができる。

【0046】

なお、第二の整流回路225は、図3において示した回路構成に限定されず、図3とは異なる構成の半波整流回路を用いても良いし、全波整流回路を用いても良いし、交流信号を直流信号に変えることができる回路構成であれば、どのような回路を用いても良い。

【0047】

また、第二の整流回路225により直流信号に変えられた信号を復調するための複数の抵抗素子及び容量素子の接続の仕方及び構成は、図3において示した接続の仕方及び構成に限定されない。抵抗素子及び容量素子以外にトランジスタを用いても良いし、直流信号に変えられた信号を復調することができる回路構成であれば、どのような回路を用いても良い。

【0048】

図3では、このようにして出力された復調信号が制御回路209に入力される場合を、一例として示す。なお、図3では、制御回路209内のインバータ227に復調信号が入力する例を示しているが、復調信号が入力する回路は設計によって様々に変えられるので、図3において示した構成に限定されない。前述のようにインバータでもよいし、その他の論理回路でもよいし、容量素子、抵抗素子及びインダクタンスなどの素子でもよいし、それらの組み合わせでもよい。なお、抵抗素子及び容量素子を設ける代わりに、または、抵抗素子及び容量素子に加えて、配線や電極等の寄生抵抗や、複数の配線の重なりや複数の電極の重なりによる寄生容量を積極的に利用してもよい。

【0049】

こうして、復調信号が制御回路209内のインバータ227に入力して得られた出力信号は、制御回路内回路226に入力される。

【0050】

ここで、制御回路内回路226は、本発明の半導体装置が使用される目的に即した設計仕様に基づき設計される。

【0051】

図3において、アナログ回路部に相当するのは、アンテナ202、高周波回路203、電源回路204、データ復調回路207である。また、電源回路204内の第一の整流回路223及びデータ復調回路207内の第二の整流回路225でトランジスタが使用される。さらに、デジタル回路部(ロジック回路部)に相当するのは、制御回路209である。さらにまた、制御回路209内でトランジスタが使用される一例として制御回路内のインバータ227があげられる。

【0052】

本実施の形態2においては、前述のアナログ回路部に相当する電源回路204内の第一の整流回路223及びデータ復調回路207内の第二の整流回路225で使用するN型トランジスタ234、N型トランジスタ235、N型トランジスタ232及びN型トランジスタ233のゲート長は3.3μmで設計する。また、前述のデジタル回路部(ロジック回路部)に相当する制御回路209内のインバータ227で使用するトランジスタのゲート長は1.3μmで設計する。さらに、制御回路内回路226、及び図示していないが、メモリ回路210等内で使用するトランジスタのゲート長も1.3μmで設計することができる。

【0053】

アナログ回路部、特に、電源回路204及びデータ復調回路207で使用するトランジスタのゲート長は制御回路209及びメモリ回路210等を有するデジタル回路部(ロジック回路部)で使用するトランジスタのゲート長以上とする。好ましくは、アナログ回路部、特に、電源回路204及びデータ復調回路207で使用するトランジスタのゲート長を制御回路209及びメモリ回路210等を有するデジタル回路部(ロジック回路部)で使用するトランジスタのゲート長の2倍以上とする。

【0054】

そうすることで、リミッタ回路のような特別な回路を設けることなく、過電圧が供給された際にゲート長の長いアナログ回路部で電圧を緩和することができる。さらに、アナログ回路部から出力された信号が入力されるデジタル回路部(ロジック回路部)において、回路内の素子であるトランジスタ等が破壊されるのを防止することが出来る。

【0055】

また、アナログ回路部、特に電源回路204及びデータ復調回路207は、受信した無線信号から高電源電位(VDD)を生成したり、受信した無線信号よりも周波数の遅い復調信号を生成したりといった、受信した無線信号を加工することを主目的とするため、周波数の速い動作は必要がない。一方、デジタル回路部(ロジック回路部)及びアナログ回路部内のクロック発生回路206等は、アナログ回路部で生成された復調信号、VDD等を用いて、演算処理を行うなど、周波数の速い動作が必要とされる。従って、半導体装置内のアナログ回路部とデジタル回路部(ロジック回路部)で使用するトランジスタにおいて、アナログ回路部内、特に電源回路204及びデータ復調回路207のトランジスタのゲート長をデジタル回路部(ロジック回路部)内のトランジスタのゲート長以上とすることで、それぞれの目的にあった無駄のない動作が実現できる。

【0056】

上記構成により本発明の無線通信によりデータの交信が可能な半導体装置は、リミッタ回路を設けることなく回路内の素子が破壊されるのを防止することができる。こうして、半導体装置のサイズを小さく抑え、且つ信頼性の高い半導体装置を提供することができる。

【0057】

本実施の形態2は、実施の形態1と自由に組み合わせて実施することが可能である。

【0058】

(実施の形態3)

本実施の形態3では、本発明の半導体装置の図3の回路の一部にあたるマスク図面について、図4を用いて説明する。図4において、5001aはN型半導体層であり、5001bはP型半導体層であり、5003は第1の配線であり、5004は第2の配線である。5002はコンタクトホールである。

【0059】

図4(A)は、図3のデータ復調回路207で用いられている第二の整流回路225及び第一の抵抗素子228である。第二の整流回路225の有するN型トランジスタ232及びN型トランジスタ233は各々、N型半導体層5001aと、N型半導体層5001aに接する絶縁膜と、N型半導体層5001aと当該絶縁膜を介して重なる第1の配線5003とによって構成される。N型トランジスタ232及びN型トランジスタ233において、第1の配線5003がゲート電極となり、当該絶縁膜がゲート絶縁膜となる。図4(A)では、N型トランジスタ232及びN型トランジスタ233は各々、5個のダイオード接続(ゲートとドレインが接続)されたトランジスタを2組有し、この2組が並列に接続された構成となっている。即ち、10個のダイオード接続されたトランジスタが並列に接続された構成となっている。図16に、N型トランジスタ232を拡大した図(図16(A))と、その等価回路(図16(B))を示す。N型トランジスタ232は10個のN型トランジスタ5550が端子5000aと端子5000bの間に並列に接続された構成となっている。並列に接続した複数のN型トランジスタ5550によってN型トランジスタ232を構成することによって、N型トランジスタ232のチャネル幅を大きくし、且つそのレイアウトの自由度を高くすることができる。図16ではN型トランジスタ232を代表で示したが、N型トランジスタ233についても同様である。こうして、N型トランジスタ232及びN型トランジスタ233を有する第二の整流回路225の占める面積を小さくすることができる。

【0060】

なお、図4及び図16では、第二の整流回路225の例を示したが、電源回路204が有する第一の整流回路223についても同様な構成とすることができる。

【0061】

第一の抵抗素子228は、島状に加工された複数のN型半導体層5001aと、これら複数のN型半導体層5001aを接続する第2の配線5004によって構成される。複数のN型半導体層5001aと第2の配線5004とはコンタクトホール5002によって接続されている。

【0062】

図4(B)は、図3の制御回路内のインバータ227である。制御回路内のインバータ227は、P型トランジスタ5501とN型トランジスタ5502より構成される。P型トランジスタ5501は、P型半導体層5001bと、P型半導体層5001bに接する絶縁膜と、P型半導体層5001bと当該絶縁膜を介して重なる第1の配線5003とによって構成される。P型トランジスタ5501において、第1の配線5003がゲート電極となり、当該絶縁膜がゲート絶縁膜となる。N型トランジスタ5502は、N型半導体層5001aと、N型半導体層5001aに接する絶縁膜と、N型半導体層5001aと当該絶縁膜を介して重なる第1の配線5003とによって構成される。N型トランジスタ5502において、第1の配線5003がゲート電極となり、当該絶縁膜がゲート絶縁膜となる。

【0063】

ここで、アナログ回路部の一部である第二の整流回路225で使用するN型トランジスタ232及びN型トランジスタ233のゲート長は3.3μmで設計する。また、デジタル回路部(ロジック回路部)に相当する制御回路内のインバータ227で使用するトランジスタのゲート長は1.3μmで設計する。

【0064】

つまり、アナログ回路部に相当するデータ復調回路207で使用するトランジスタのゲート長はデジタル回路部(ロジック回路部)で使用するトランジスタのゲート長以上である。

【0065】

そうすることで、リミッタ回路のような特別な回路を設けることなく、過電圧が供給された際にゲート長の長いアナログ回路部で電圧を緩和する。さらに、アナログ回路部から出力された信号が入力されるデジタル回路部(ロジック回路部)において、回路内の素子であるトランジスタ等が破壊されるのを防止することが出来る。

【0066】

また、アナログ回路部に相当するデータ復調回路207は、無線信号(受信した無線信号)よりも周波数の遅い復調信号を生成するため、周波数の速い動作は必要がない。一方、デジタル回路部(ロジック回路部)に相当する制御回路内のインバータ227は、アナログ回路部で生成された復調信号、VDD等を用いて、演算処理を行うなど、周波数の速い動作が必要とされる。したがって、半導体装置内のアナログ回路部とデジタル回路部(ロジック回路部)で使用するトランジスタにおいて、アナログ回路部内のトランジスタのゲート長をデジタル回路部(ロジック回路部)内のトランジスタのゲート長以上とすることで、無駄のないそれぞれの目的にあった動作が実現できる。

【0067】

上記構成により本発明の無線通信によりデータの交信が可能な半導体装置は、リミッタ回路を設けることなく回路内の素子が破壊されるのを防止することができる。こうして、半導体装置のサイズを小さく抑え、且つ信頼性の高い半導体装置を提供することができる。

【0068】

本実施の形態3は、実施の形態1または実施の形態2と自由に組み合わせて実施することが可能である。

【実施例1】

【0069】

本実施例では、本発明の半導体装置の具体的な構成について、図5及び図6を用いて説明する。

【0070】

図1や図3で示した本発明の半導体装置201におけるアンテナ202の構成例を図5(A)乃至図5(D)に示す。アンテナ202は2通りの設け方があり、一方(以下、第1のアンテナ設置法という)を図5(A)及び図5(C)に示す。もう一方(以下、第2のアンテナ設置法という)を図5(B)及び図5(D)に示す。図5(C)は図5(A)のA〜A’の断面図に相当し、図5(D)は図5(B)のB〜B’の断面図に相当する。

【0071】

第1のアンテナ設置法では、複数の素子(以下、素子群601と呼ぶ)が設けられた基板600上にアンテナ202を設ける(図5(A)及び図5(C)参照)。素子群601によって、本発明の半導体装置のアンテナ以外の回路が構成される。素子群601は複数の薄膜トランジスタを有する。図示する構成では、アンテナ202として機能する導電膜は、素子群601の有する薄膜トランジスタのソースやドレインと接続される配線と同じ層に設けられている。しかしながら、アンテナ202として機能する導電膜は、素子群601の有する薄膜トランジスタのゲート電極664と同じ層に設けてもよいし、素子群601を覆うように更に絶縁膜を設け当該絶縁膜上に設けてもよい。

【0072】

第2のアンテナ設置法では、素子群601が設けられた基板600上に端子部602を設ける。そして、当該端子部602に接続するように、基板600とは別の基板610上に設けられたアンテナ202を接続する(図5(B)及び図5(D)参照)。図示する構成では、素子群601の有する薄膜トランジスタのソースやドレインと接続される配線の一部を端子部602として用いる。そして、端子部602に接続するように、基板600と、アンテナ202が設けられた基板610とを貼り合わせている。基板600と基板610の間には、導電性粒子603と樹脂604が設けられている。導電性粒子603によって、アンテナ202と端子部602とは電気的に接続されている。

【0073】

素子群601の構成及び作製方法について説明する。素子群601は、大面積の基板上に複数形成し、その後、分断することで完成させれば、安価なものを提供することができる。基板600としては、例えばバリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板等を用いることができる。また、半導体基板の表面に絶縁膜を形成したものを用いても良い。プラスチック等の可撓性を有する合成樹脂からなる基板を用いても良い。基板の表面を、CMP(Chemical Mechanical Polishing)法などの研磨により平坦化しておいても良い。また、ガラス基板、石英基板や、半導体基板を研磨して薄くした基板を用いてもよい。

【0074】

基板600上に設けられている下地層661としては、酸化珪素や、窒化珪素または窒化酸化珪素などの絶縁膜を用いることができる。下地層661によって、基板600に含まれるNaなどのアルカリ金属やアルカリ土類金属が半導体層662に拡散し薄膜トランジスタの特性に悪影響をおよぼすのを防ぐことができる。図5では、下地層661を単層の構造としているが、2層あるいはそれ以上の複数層で形成してもよい。なお、石英基板など不純物の拡散がさして問題とならない場合は、下地層661を必ずしも設ける必要はない。

【0075】

なお、高密度プラズマによって基板600の表面を直接処理してもよい。高密度プラズマは、高周波(例えば2.45GHz)を使うことによって生成される。なお、高密度プラズマとしては電子密度が1011〜1013/cm3かつ電子温度が2eV以下、イオンエネルギーが5eV以下であるものを用いる。このように低電子温度が特徴である高密度プラズマは、活性種の運動エネルギーが低いため、従来のプラズマ処理に比べプラズマダメージが少なく欠陥が少ない膜を形成することができる。プラズマの生成はラジアルスロットアンテナを用いた高周波励起のプラズマ処理装置を用いることができる。高周波を発生するアンテナから基板600までの距離を20〜80mm(好ましくは20〜60mm)とする。

【0076】

窒化性雰囲気、例えば、窒素(N)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下、または窒素と水素(H)と希ガス雰囲気下、またはアンモニア(NH3)と希ガス雰囲気下において、上記高密度プラズマ処理を行うことによって、基板600表面を窒化することができる。基板600としてガラスや石英、シリコンウエハ等を用いた場合、基板600の表面に形成された窒化物層は窒化珪素を主成分とするので、基板600側から拡散してくる不純物のブロッキング層として利用することができる。この窒化物層の上に酸化珪素膜または酸窒化珪素膜をプラズマCVD法で形成して下地層661としても良い。

【0077】

また、酸化珪素や酸窒化珪素などからなる下地層661の表面に対し同様な高密度プラズマ処理を行うことにより、その表面及び表面から1〜10nmの深さの領域を窒化処理をすることができる。このきわめて薄い窒化珪素の層は、ブロッキング層として機能し、且つその上に形成する半導体層662へ与える応力の影響が少ないので好ましい。

【0078】

半導体層662としては、所定の形状に加工された結晶性半導体膜や非晶質半導体膜を用いることができる。また、有機半導体膜を用いてもよい。結晶性半導体膜は非晶質半導体膜を結晶化して得ることができる。結晶化方法としては、レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法等を用いることができる。半導体層662は、チャネル形成領域662aと、導電型を付与する不純物元素が添加された一対の不純物領域662bとを有する。なお、チャネル形成領域662aと一対の不純物領域662bとの間に、不純物領域662bよりも低濃度で前記不純物元素が添加された低濃度不純物領域662cを有する構成を示したがこれに限定されない。低濃度不純物領域662cを設けない構成であってもよい。

【0079】

なお、半導体層662と同時に形成される配線は、基板600の上面に垂直な方向3005から見た場合に角部が丸くなるよう引き回すのが好ましい。上記配線の引き回し方法について図7に模式的に示す。半導体層と同時に形成される配線を図中配線3011で示す。図7(A)は従来の配線の引き回し方法である。図7(B)は本発明の配線の引き回し方法である。従来の配線3011の角部1201aに対して本発明の配線3011の角部1202aは丸くなっている。角部を丸くすることによって、ゴミ等が配線の角部に残るのを防止することができる。こうして、半導体装置のゴミによる不良を低減し歩留まりを高めることができる。

【0080】

薄膜トランジスタのチャネル形成領域662aにおいて、導電型を付与する不純物元素が添加されていてもよい。こうして、薄膜トランジスタのしきい値電圧を制御することができる。

【0081】

第1の絶縁層663としては、酸化珪素、窒化珪素または窒化酸化珪素等を用い、単層または複数の膜を積層させて形成することができる。この場合において、第1の絶縁層663の表面を酸化雰囲気又は窒化雰囲気で高密度プラズマによって処理し、酸化又は窒化処理して緻密化しても良い。高密度プラズマは、前述と同様に、高周波(例えば2.45GHz)を使うことによって生成される。なお、高密度プラズマとしては電子密度が1011〜1013/cm3かつ電子温度が2eV以下、イオンエネルギーが5eV以下であるものを用いる。プラズマの生成はラジアルスロットアンテナを用いた高周波励起のプラズマ処理装置を用いることができる。また、高密度プラズマを発生させる装置において、高周波を発生するアンテナから基板600までの距離を20〜80mm(好ましくは20〜60mm)とする。

【0082】

なお、第1の絶縁層663を成膜する前に、半導体層662の表面に対して上記高密度プラズマ処理を行って、半導体層の表面を酸化又は窒化処理してもよい。このとき、基板600の温度を300〜450℃とし、酸化雰囲気又は窒化雰囲気で処理することにより、その上に堆積する第1の絶縁層663と良好な界面を形成することができる。

【0083】

窒化雰囲気としては、窒素(N)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下、または窒素と水素(H)と希ガス雰囲気下、またはアンモニア(NH3)と希ガス雰囲気を用いることができる。酸化雰囲気としては、酸素(O)と希ガス雰囲気下、または酸素と水素(H)と希ガス雰囲気下、または一酸化二窒素(N2O)と希ガス雰囲気を用いることができる。

【0084】

ゲート電極664としては、Ta、W、Ti、Mo、Al、Cu、Cr、Ndから選ばれた一種の元素または該元素を複数含む合金若しくは化合物を用いることができる。更に、これらの元素、合金、化合物からなる単層または積層構造を用いることができる。図では、2層構造のゲート電極664を示した。なお、ゲート電極664やゲート電極664と同時に形成される配線は、基板600の上面に垂直な方向3005から見た場合に角部が丸くなるよう引き回すのが好ましい。引き回しの方法は図7(B)に示した方法と同様とすることができる。ゲート電極664やゲート電極664と同時に形成される配線を図中配線3012で示す。従来の配線3012の角部1201bに対して本発明の配線3012の角部1202bの様に角部を丸くすることによって、ゴミ等が配線の角部に残るのを防止することができる。こうして、半導体装置のゴミによる不良を低減し歩留まりを高めることができる。

【0085】

薄膜トランジスタは、半導体層662と、ゲート電極664と、半導体層662とゲート電極664との間のゲート絶縁膜として機能する第1の絶縁層663とによって構成される。本実施例では、薄膜トランジスタをトップゲート型のトランジスタとして示したが、半導体層の下方にゲート電極を有するボトムゲート型のトランジスタであっても良いし、半導体層の上下にゲート電極を有するデュアルゲート型のトランジスタであっても良い。

【0086】

第2の絶縁層667は窒化珪素膜などイオン性不純物をブロッキングするバリア性の絶縁膜であることが望ましい。第2の絶縁層667は窒化珪素または酸窒化珪素で形成する。この第2の絶縁層667は、半導体層662の汚染を防ぐ保護膜としての機能を有している。第2の絶縁層667を堆積した後に、水素ガスを導入して前述のような高密度プラズマ処理をすることで、第2の絶縁層667の水素化を行っても良い。または、アンモニア(NH3)ガスを導入して、第2の絶縁層667の窒化と水素化を行っても良い。または、酸素、一酸化二窒素(N2O)ガスなどと水素ガスを導入して、酸化窒化処理と水素化処理を行っても良い。この方法により、窒化処理、酸化処置若しくは酸化窒化処理を行うことにより第2の絶縁層667の表面を緻密化することができる。こうして第2の絶縁層667の保護膜としての機能を強化することができる。第2の絶縁層667に導入された水素は、その後400〜450℃の熱処理をすることにより放出されて、半導体層662の水素化をすることができる。なお当該水素化処理は、第1の絶縁層663を用いた水素化処理と組み合わせてもよい。

【0087】

第3の絶縁層665としては、無機絶縁膜や有機絶縁膜の単層または積層構造を用いることができる。無機絶縁膜としては、CVD法により形成された酸化珪素膜や、SOG(Spin On Glass)法により形成された酸化珪素膜などを用いることができ、有機絶縁膜としてはポリイミド、ポリアミド、BCB(ベンゾシクロブテン)、アクリルまたはポジ型感光性有機樹脂、ネガ型感光性有機樹脂等の膜を用いることができる。

【0088】

また、第3の絶縁層665として、珪素(Si)と酸素(O)との結合で骨格構造が構成される材料を用いることもできる。この材料の置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

【0089】

配線666としては、Al、Ni、W、Mo、Ti、Pt、Cu、Ta、Au、Mnから選ばれた一種の元素または該元素を複数含む合金を用いることができる。更に、これらの元素、合金からなる単層または積層構造を用いることができる。図では、単層構造の例を示した。なお、配線666は、基板600の上面に垂直な方向3005から見た場合に角部が丸くなるよう引き回すのが好ましい。引き回しの方法は図7(B)に示した方法と同様とすることができる。配線666を図中配線3013で示す。従来の配線3013の角部1201cに対して本発明の配線3013の角部1202cの様に角部を丸くすることによって、ゴミ等が配線の角部に残るのを防止することができる。こうして、半導体装置のゴミによる不良を低減し歩留まりを高めることができる。図5(A)及び図5(C)に示した構成では、配線666は、薄膜トランジスタのソースやドレインと接続される配線となると共に、アンテナ202となる。図5(B)及び図5(D)に示した構成では、配線666は、薄膜トランジスタのソースやドレインと接続される配線となると共に、端子部602となる。図7において、配線666と薄膜トランジスタのソースやドレインとを接続するコンタクトホール3014を示す。

【0090】

なお、アンテナ202は、Au、Ag、Cuなどのナノ粒子を含む導電性ペーストを用いて、液滴吐出法により形成することもできる。液滴吐出法は、インクジェット法やディスペンサ方式等の液滴を吐出してパターンを形成する方式の総称であり、材料の利用効率の向上等の利点を有する。

【0091】

図5(A)及び図5(C)に示した構成では、配線666上に第4の絶縁層668を形成する。第4の絶縁層668としては、無機絶縁膜や有機絶縁膜の単層または積層構造を用いることができる。第4の絶縁層668はアンテナ202の保護層として機能する。

【0092】

また、素子群601は基板600上に形成されたもの(図6(A)参照)をそのまま使用してもよいが、基板600上の素子群601を剥離し(図6(B)参照)、当該素子群601をフレキシブル基板701に貼り合わせてもよい(図6(C)参照)。フレキシブル基板701は、可撓性を有し、例えば、ポリカーボネート、ポリアリレート、ポリエーテルスルフォン等のプラスチック基板またはセラミック基板等を用いることができる。

【0093】

基板600からの素子群601の剥離は、(A)あらかじめ基板600と素子群601との間に剥離層を設けておいて、剥離層をエッチング剤により除去することで行う方法を用いることができる。または、(B)剥離層をエッチング剤により部分的に除去し、その後、基板600と素子群601とを物理的に剥離する方法を用いることができる。または、(C)素子群601が形成された耐熱性の高い基板600を機械的に削除又は溶液やガスによるエッチングで除去することで、当該素子群601を切り離す方法を用いることができる。なお、物理的手段によって剥離されるとは、外部からストレスが与えられて剥離されることを指し、例えば、ノズルから吹き付けられるガスの風圧や超音波等からストレスを与えられて剥離することである。

【0094】

上記(A)や(B)のより具体例な方法としては、耐熱性の高い基板600と素子群601の間に金属酸化膜を設け、当該金属酸化膜を結晶化により脆弱化して、当該素子群601を剥離する方法がある。また上記(A)や(B)のより具体例な方法として、耐熱性の高い基板600と素子群601の間に水素を含む非晶質珪素膜を設け、レーザ−光の照射またはエッチングにより当該非晶質珪素膜を除去することで、当該素子群601を剥離する方法を用いることもできる。

【0095】

また、剥離した素子群601のフレキシブル基板701への貼り付けは、市販の接着剤を用いればよく、例えば、エポキシ樹脂系接着剤や樹脂添加剤等の接着材を用いればよい。

【0096】

素子群601をアンテナが形成されたフレキシブル基板701に貼り合わせ当該アンテナとの電気的接続をとると、厚さが薄く、軽く、落下しても割れにくい半導体装置が完成する(図6(C)参照)。安価なフレキシブル基板701を用いると、安価な半導体装置を提供することができる。さらに、フレキシブル基板701は可撓性を有するため、曲面や異形の形状上に貼り合わせることが可能となり、多種多様の用途が実現する。例えば、薬の瓶のような曲面上に、本発明の半導体装置の一形態である無線タグ720を密着して貼り合わせることができる(図6(D)参照)。さらに、基板600を再利用すれば、低コストで半導体装置を作製することができる。

【0097】

素子群601は、フィルムで覆うことによって封止することができる。該フイルムの表面は、二酸化珪素(シリカ)の粉末により、コーティングされていてもよい。コーティングにより、高温で高湿度の環境下においても防水性を保つことができる。つまり、耐湿性の機能を持たせることができる。また、該フイルムの表面に帯電防止の機能を持たせてもよい。また、該フイルムの表面は、炭素を主成分とする材料(例えば、ダイヤモンドライクカーボン)によりコーティングされていてもよい。コーティングにより強度が増し、半導体装置の劣化や破壊を抑制することができる。また、フィルムは、基材の材料(例えば樹脂)と、二酸化珪素や導電性材料や炭素を主成分とする材料とを混ぜ合わせた材料により形成してもよい。また、フィルムの表面に界面活性剤を設ける、もしくはフィルムに界面活性剤を直接練り込むことで帯電防止の機能を持たせることができる。

【0098】

本実施例は、上記の実施の形態と自由に組み合わせることができる。

【実施例2】

【0099】

本実施例では、本発明の半導体装置をフレキシブルな構成にした例について説明する。説明には図8を用いる。図8(A)において、本発明の半導体装置は、フレキシブルな保護層901と、アンテナ902を含むフレキシブルな保護層903と、剥離プロセスや基板の薄膜化により形成された素子群904とを有する。素子群904は、実施例1で素子群601として示した構成と同様の構成とすることができる。保護層903上に形成されたアンテナ902は、素子群904と電気的に接続する。図8では、アンテナ902は保護層903上にのみ形成されているが、本発明はこの構成に制約されず、アンテナ902を保護層901上にも形成してもよい。なお、素子群904と、保護層901及び保護層903との間には、窒化珪素膜等からなるバリア膜を形成するとよい。そうすると、素子群904が汚染されることなく、信頼性を向上させた半導体装置を提供することができる。

【0100】

アンテナ902は、Ag、Cu、またはそれらでメッキされた金属で形成することができる。素子群904とアンテナ902とは、異方性導電膜を用い、紫外線処理又は超音波処理を行うことで接続することができる。なお、素子群904とアンテナ902とは、導電性ペースト等を用いて接着してもよい。

【0101】

保護層901及び保護層903によって素子群904を挟むことによって半導体装置が完成する(図8(A)中、矢印参照)。

【0102】

こうして形成された半導体装置の断面構造を図8(B)に示す。挟まれた素子群904の厚さ3003は、5μm以下、好ましくは0.1μm〜3μmの厚さとなるようにするとよい。また、保護層901及び保護層903を重ねたときの厚さをdとしたとき、保護層901及び保護層903の厚さは、好ましくは(d/2)±30μm、さらに好ましくは(d/2)±10μmとする。また、保護層901及び保護層903の厚さは10μm〜200μmであることが望ましい。さらに、素子群904の面積は10mm角(100mm2)以下であり、望ましくは0.3mm角〜4mm角(0.09mm2〜16mm2)の面積とするとよい。

【0103】

保護層901及び保護層903は、有機樹脂材料で形成されているため、折り曲げに対して強い特性を有する。また、剥離プロセスや基板の薄膜化により形成した素子群904自体も、単結晶半導体に比べて、折り曲げに対して強い特性を有する。そして、素子群904と、保護層901及び保護層903とは空隙がないように、密着させることができるため、完成した半導体装置自体も折り曲げに対して強い特性を有する。このような保護層901及び保護層903で囲われた素子群904は、他の個体物の表面または内部に配置しても良いし、紙の中に埋め込んでも良い。

【0104】

素子群904を有する半導体装置を曲面を有する基板に貼る場合について説明する。説明には図8(C)を用いる。図面では、素子群904から選択された1つのトランジスタ981を図示する。トランジスタ981は、ゲート電極907の電位に応じて、ソース及びドレインの一方905からソース及びドレインの他方906に電流を流す。トランジスタ981の電流が流れる方向(キャリアの移動方向3004)と、基板980が弧を描く方向が直交するように、トランジスタ981は配置される。このような配置にすれば、基板980が折り曲げられて弧を描いても、トランジスタ981に与えられる応力の影響が少なく、素子群904が含むトランジスタ981の特性の変動を抑制することができる。

【0105】

本実施例は、上記の実施の形態、実施例1と自由に組み合わせることができる。

【実施例3】

【0106】

本実施例では、本発明の半導体装置201を構成する回路が有するトランジスタの構成例を示す。トランジスタは単結晶基板に形成されるMOSトランジスタの他、薄膜トランジスタ(TFT)で構成することもできる。図11はこれらの回路を構成するトランジスタの断面構造を示す図である。図11は、Nチャネル型のトランジスタ2001、Nチャネル型のトランジスタ2002、容量素子2004、抵抗素子2005、Pチャネル型のトランジスタ2003が示されている。各トランジスタは半導体層405、絶縁層408、ゲート電極409を備えている。ゲート電極409は、第1導電層403と第2導電層402の積層構造で形成されている。また、図12(A)〜(D)は、図11で示すトランジスタ、容量素子、抵抗素子に対応する上面図であり合わせて参照することができる。

【0107】

図11において、Nチャネル型のトランジスタ2001の半導体層405には、ゲート電極409と重なる領域を挟んでチャネル長方向(キャリアの流れる方向)に並ぶように一対の不純物領域407が形成されている。不純物領域407は低濃度ドレイン(LDD)領域であり、配線404とコンタクトを形成するソース領域及びドレイン領域を形成する不純物領域406の導電型を付与する不純物元素の濃度よりも低濃度に当該不純物元素がドープされた領域である。不純物領域406と不純物領域407には、Nチャネル型のトランジスタ2001を構成する場合、N型を付与する不純物としてリンなどが添加されている。LDD領域はホットエレクトロン劣化や短チャネル効果を抑制する手段として形成される。

【0108】

図12(A)で示すように、Nチャネル型のトランジスタ2001のゲート電極409において、第1導電層403は第2導電層402の両側に広がって形成されている。この場合において、第1導電層403の膜厚は第2導電層402の膜厚よりも薄く形成されている。第1導電層403の厚さは、10〜100kVの電界で加速されたイオン種を通過させることが可能な厚さに形成されている。不純物領域407はゲート電極409の第1導電層403と重なるように形成されている。すなわち、ゲート電極409とオーバーラップするLDD領域を形成している。この構造は、ゲート電極409において、第2導電層402をマスクとして第1導電層403を通して一導電型の不純物を添加することにより、自己整合的に不純物領域407を形成している。すなわち、ゲート電極とオーバーラップするLDD領域を自己整合的に形成している。

【0109】

ゲート電極の両側にLDD領域を有するトランジスタは、図3における電源回路204中の第一の整流回路223及び第二の整流回路225に用いられる整流用のトランジスタや、論理回路に用いられるトランスミッションゲート(アナログスイッチとも呼ぶ)を構成するトランジスタに適用される。これらのトランジスタは、ソース電極及びドレイン電極に正負両方の電圧が印加されるため、ゲート電極の両側にLDD領域を設けることが好ましい。

【0110】

図11において、Nチャネル型のトランジスタ2002の半導体層405には、チャネル形成領域の片側に不純物領域407が形成されている。不純物領域407は、不純物領域406の不純物濃度よりも低濃度に不純物元素がドープされた低濃度ドレイン(LDD)領域である。図12(B)で示すように、Nチャネル型のトランジスタ2002のゲート電極409において、第1導電層403は、第2導電層402の片側に広がって形成されている。この場合も同様に、第2導電層402をマスクとして、第1導電層403を通して一導電型の不純物を添加することにより、自己整合的にLDD領域を形成することができる。

【0111】

ゲート電極の片側にLDD領域を有するトランジスタは、ソース電極及びドレイン電極間に正電圧のみ、もしくは負電圧のみが印加されるトランジスタに適用すればよい。具体的には、インバータ回路、NAND回路、NOR回路、ラッチ回路といった論理ゲートを構成するトランジスタや、センスアンプ、定電圧発生回路、VCO(Voltage Controlled Oscillator)といったアナログ回路を構成するトランジスタに適用すればよい。

【0112】

図11において、容量素子2004は、第1導電層403と半導体層405とで絶縁層408を挟んで形成されている。容量素子2004を形成する半導体層405には、不純物領域410と不純物領域411を備えている。不純物領域411は、半導体層405において第1導電層403と重なる位置に形成される。また、不純物領域410は配線404とコンタクトを形成する。不純物領域411は、第1導電層403を通して一導電型の不純物を添加することができるので、不純物領域410と不純物領域411に含まれる不純物濃度は同じにすることもできるし、異ならせることも可能である。いずれにしても、容量素子2004において、半導体層405は電極として機能させるので、一導電型の不純物を添加して低抵抗化しておくことが好ましい。また、第1導電層403は、図12(C)に示すように、第2導電層402を補助的な電極として利用することにより、第1導電層403及び第2導電層402は容量素子2004の電極として十分に機能させることができる。このように、第1導電層403と第2導電層402を組み合わせた複合的な電極構造とすることにより、容量素子2004を自己整合的に形成することができる。

【0113】

容量素子2004は、図3に示す電源回路204の保持容量224、あるいは高周波回路203が有する共振容量220、データ復調回路が有する第一の容量素子230及び第二の容量素子231として用いることができる。特に、共振容量は、容量素子の2端子間に正負両方の電圧が印加されるため、2端子間の電圧の正負によらず容量として機能することが必要である。

【0114】

図11において、抵抗素子2005は、第1導電層403によって形成されている(図12(D)も参照)。第1導電層403は30〜150nm程度の厚さに形成されるので、その幅や長さを適宜設定して抵抗素子を構成することができる。

【0115】

抵抗素子は、図1に示すデータ変調回路208が有する抵抗負荷として用いることができる。また、図3に示すデータ復調回路207が有する第一の抵抗素子228及び第二の抵抗素子229としても用いることができる。さらに、VCOなどで電流を制御する場合の負荷としても用いることができる。抵抗素子は、導電型を付与する不純物元素を高濃度に含む半導体層や、膜厚の薄い金属層によって構成すればよい。抵抗値が膜厚、膜質、不純物濃度、活性化率などに依存する半導体層に対して、金属層は、膜厚、膜質で抵抗値が決定するため、ばらつきが小さく好ましい。

【0116】

図11において、Pチャネル型のトランジスタ2003は、半導体層405に不純物領域412を備えている。この不純物領域412は、配線404とコンタクトを形成するソース領域及びドレイン領域として機能する。ゲート電極409の構成は第1導電層403と第2導電層402が重畳した構成となっている(図12(E)も参照)。Pチャネル型のトランジスタ2003はLDD領域を設けないシングルドレイン構造のトランジスタである。Pチャネル型のトランジスタ2003を形成する場合、不純物領域412にはP型を付与する不純物として硼素などが添加される。一方、不純物領域412にN型を付与する不純物としてリンなどを添加すればシングルドレイン構造のnチャネル型トランジスタとすることもできる。

【0117】

半導体層405及びゲート絶縁層408の一方若しくは双方に対して、高密度プラズマ処理によって酸化又は窒化処理しても良い。この処理は、実施例1で示した手法と同様にすることができる。

【0118】

上記処理によって、半導体層405とゲート絶縁層408の界面の欠陥準位を低減することができる。ゲート絶縁層408対してこの処理を行うことにより、この絶縁層の緻密化を図ることができる。すなわち、荷電欠陥の生成を抑えトランジスタのしきい値電圧の変動を抑えることができる。また、トランジスタを3V以下の電圧で駆動させる場合には、このプラズマ処理により酸化若しくは窒化された絶縁層をゲート絶縁層408として適用することができる。また、トランジスタの駆動電圧が3V以上の場合には、このプラズマ処理で半導体層405の表面に形成した絶縁層とCVD法(プラズマCVD法若しくは熱CVD法)で堆積した絶縁層とを組み合わせてゲート絶縁層408を形成することができる。また、同様に、この絶縁層は、容量素子2004の誘電体層としても利用することができる。この場合、このプラズマ処理で形成された絶縁層は、1〜10nmの厚さで形成され、緻密な膜であるので、大きな電荷容量を持つ容量素子を形成することができる。

【0119】

図11及び図12を参照して説明したように、膜厚の異なる導電層を組み合わせることにより、さまざまな構成の素子を形成することができる。第1導電層のみが形成される領域と、第1導電層と第2導電層が積層されている領域は、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いて形成することができる。すなわち、フォトリソグラフィー工程において、フォトレジストを露光する際に、フォトマスクの透過光量を調節して、現像されるレジストマスクの厚さを異ならせる。この場合、フォトマスクまたはレチクルに解像度限界以下の間隔を有する複数のスリットを設けて上記複雑な形状を有するレジストを形成してもよい。また、現像後に約200℃のベークを行ってフォトレジスト材料で形成されるマスクパターンを変形させてもよい。

【0120】

また、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いることにより、第1導電層のみが形成される領域と、第1導電層と第2導電層が積層されている領域を連続して形成することができる。図12(A)に示すように、第1導電層のみが形成される領域を半導体層上に選択的に形成することができる。半導体層上において第1導電層のみが形成される領域を設けることは、LDD領域を自己整合的に作製することができる等の点で有効であるが、半導体層上以外の領域(ゲート電極と連続する配線領域)では第1導電層のみが形成される領域は必要がない。このフォトマスク若しくはレチクルを用いることにより、配線部分は、第1導電層のみの領域を作らないで済むので、配線密度を実質的に高めることができる。

【0121】

図11及び図12の場合には、第1導電層はタングステン(W)、クロム(Cr)、タンタル(Ta)、窒化タンタル(TaN)またはモリブデン(Mo)などの高融点金属、又は高融点金属を主成分とする合金もしくは化合物を30〜50nmの厚さで形成する。また、第2導電層はタングステン(W)、クロム(Cr)、タンタル(Ta)、窒化タンタル(TaN)またはモリブデン(Mo)などの高融点金属、又は高融点金属を主成分とする合金もしくは化合物で300〜600nmの厚さに形成する。例えば、第1導電層と第2導電層をそれぞれ異なる導電材料を用い、後に行うエッチング工程でエッチングレートの差が生じるようにする。一例として、第1導電層をTaNを用い、第2導電層としてタングステン膜を用いることができる。

【0122】

本実施例では、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いて、電極構造の異なるトランジスタ、容量素子、抵抗素子を、同じフォトマスクまたはレチクルを用いたエッチング工程によって作り分ける方法を示した。これにより、回路の特性に応じて、形態の異なる素子を、工程を増やすことなく作り込み、集積化することができる。

【0123】

本実施例は、上記の実施の形態、実施例1及び実施例2と自由に組み合わせることができる。

【実施例4】

【0124】

本実施例では、半導体装置201のメモリ回路210等として用いることができるスタティックRAM(SRAM)の一例について、図13〜図15を参照して説明する。

【0125】

図13(A)で示す半導体層10、半導体層11はシリコン若しくはシリコンを成分とする結晶性の半導体で形成することが好ましい。例えば、半導体層10、半導体層11として、シリコン膜をレーザアニールなどによって結晶化された多結晶シリコン、単結晶シリコンなどが適用される。その他にも半導体特性を示す、金属酸化物半導体、アモルファスシリコン、有機半導体を適用することも可能である。

【0126】

いずれにしても、最初に形成する半導体層は絶縁表面を有する基板の全面若しくは一部(トランジスタの半導体領域として確定されるよりも広い面積を有する領域)に形成する。そして、フォトリソグラフィー技術によって、半導体層上にマスクパターンを形成する。そのマスクパターンを利用して半導体層をエッチング処理することにより、トランジスタのソース領域及びドレイン領域及びチャネル形成領域を含む特定形状の島状の半導体層10、半導体層11を形成する。

【0127】

図13(A)で示す半導体層10、半導体層11を形成するためのフォトマスクは、図13(B)に示すマスクパターン2000を備えている。このマスクパターン2000は、フォトリソグラフィー工程で用いるレジストがポジ型かネガ型かで異なる。ポジ型レジストを用いる場合には、図13(B)で示すマスクパターン2000は、遮光部として作製される。マスクパターン2000は、多角形の頂部Aを削除した形状となっている。このフォトマスクのパターンは、例えば、角部において一辺が10μm以下の直角三角形を切り取るように面取りされている。また、屈曲部Bにおいては、その角部が直角とならないように屈曲する形状となっている。屈曲部Bを拡大すると、複数段に渡って屈曲する形状(実施例1で図7を用いて示した構成参照)となっている。

【0128】

図13(B)で示すマスクパターン2000は、その形状が、図13(A)で示す半導体層10、半導体層11に反映される。その場合、マスクパターン2000と相似の形状が転写されても良いが、マスクパターン2000の角部がさらに丸みを帯びるように転写されていても良い。すなわち、マスクパターン2000よりもさらにパターン形状をなめらかにした丸め部を設けても良い。

【0129】

半導体層10、半導体層11の上には、酸化シリコン若しくは窒化シリコンを少なくとも一部に含む絶縁層が形成される。この絶縁層を形成する目的の一つはゲート絶縁層である。そして、図14(A)で示すように、半導体層と一部が重なるようにゲート配線12、ゲート配線13、ゲート配線14を形成する。ゲート配線12は半導体層10に対応して形成される。ゲート配線13は半導体層10、半導体層11に対応して形成される。また、ゲート配線14は半導体層10、半導体層11に対応して形成される。ゲート配線は、金属層又は導電性の高い半導体層を成膜し、フォトリソグラフィー技術によってその形状を絶縁層上に作り込まれる。

【0130】

このゲート配線を形成するためのフォトマスクは、図14(B)に示すマスクパターン2100を備えている。このマスクパターン2100は、角部において一辺が10μm以下または配線の線幅の1/2以下で線幅の1/5以上の大きさの直角三角形を切り取るように面取りされている。図14(B)で示すマスクパターン2100は、その形状が、図14(A)で示すゲート配線12、ゲート配線13、ゲート配線14に反映される。その場合、マスクパターン2100と相似の形状が転写されても良いが、マスクパターン2100の角部がさらに丸みを帯びるように転写されていても良い。すなわち、マスクパターン2100よりもさらにパターン形状をなめらかにした、丸め部を設けても良い。すなわち、ゲート配線12、ゲート配線13、ゲート配線14の角部は、丸みをおびていてもよい。角部の外側はプラズマによるドライエッチの際、異常放電による微粉の発生を抑え、角部の内側では、たとえ洗浄のときにできた微粉であっても、それが角に集まりやすいのを洗い流す。その結果、歩留まり向上が非常に期待できるという効果を有する。

【0131】

層間絶縁層はゲート配線12、ゲート配線13、ゲート配線14の次に形成される層である。層間絶縁層は酸化シリコンなどの無機絶縁材料若しくポリイミドやアクリル樹脂などを使った有機絶材料を使って形成する。この層間絶縁層とゲート配線12、ゲート配線13、ゲート配線14の間には窒化シリコン若しくは窒化酸化シリコンなどの絶縁層を介在させても良い。また、層間絶縁層上にも窒化シリコン若しくは窒化酸化シリコンなどの絶縁層を設けても良い。この絶縁層は、外因性の金属イオンや水分など薄膜トランジスタ(TFT)にとっては良くない不純物により半導体層やゲート絶縁層を汚染するのを防ぐことができる。

【0132】

層間絶縁層には所定の位置に開孔が形成されている。例えば、下層にあるゲート配線や半導体層に対応して設けられる。金属若しくは金属化合物の一層若しくは複数層で形成される配線層は、フォトリソグラフィー技術によってマスクパターンが形成され、エッチング加工により所定のパターンに形成される。そして、図15(A)で示すように、半導体層10や半導体層11と一部が重なるように配線15、配線16、配線17、配線18、配線19、配線20を形成する。配線はある特定の素子間を連結する。配線は特定の素子と素子の間を直線で結ぶのではなく、レイアウトの制約上屈曲部が含まれる。また、他の配線とのコンタクト部やその他の領域において配線幅が変化する。コンタクト部では、コンタクトホールが配線幅と同等若しくは大きい場合には、その部分で配線幅が広がるように変化する。

【0133】

この配線15乃至配線20を形成するためのフォトマスクは、図15(B)に示すマスクパターン2200を備えている。この場合においても、マスクパターンは、角部において一辺が10μm以下または配線の線幅の1/2以下で線幅の1/5以上の大きさの直角三角形を切り取るように面取りされる。更に、角部に丸みをおびさせてもよい。このような配線は、角部の外側はプラズマによるドライエッチの際、異常放電による微粉の発生を抑え、角部の内側では、たとえ洗浄のときにできた微粉であっても、それが角に集まりやすいのを洗い流す。その結果、歩留まり向上が非常に期待できるという効果を有する。配線の角部が丸みをおびることにより、配線の電気伝導を良好にする効果が期待できる。また、多数の配線を平行に設けた構造において、角部が丸みをおびた配線を用いることは、ゴミを洗い流すのにきわめて好都合である。

【0134】

図15(A)には、Nチャネル型のトランジスタ21、Nチャネル型のトランジスタ22、Nチャネル型のトランジスタ23、Nチャネル型のトランジスタ24、Pチャネル型のトランジスタ25、Pチャネル型のトランジスタ26が形成されている。Nチャネル型のトランジスタ23とPチャネル型のトランジスタ25はインバータ27を構成している。Nチャネル型のトランジスタ24とPチャネル型のトランジスタ26はインバータ28を構成している。この6つのトランジスタを含む回路はSRAMを形成している。これらのトランジスタの上層には、窒化シリコンや酸化シリコンなどの絶縁層が形成されていても良い。

【0135】

本実施例は、上記の実施の形態、実施例1乃至実施例3と自由に組み合わせることができる。

【実施例5】

【0136】

本発明の半導体装置201の一実施例を図17に示す。図17(A)は半導体装置201の展開図であり、図17(B)は図17(A)のA−Bにおける断面図である。本実施例では、複数のアンテナを有する半導体装置201において、特に薄膜トランジスタを有する層上に形成されたアンテナと、パッチアンテナとを有する半導体装置201の構造について説明する。

【0137】

実施例1で示した素子群601の作製方法と同様に、絶縁性基板7101上に薄膜トランジスタを有する層7102が形成される。薄膜トランジスタを有する層7102上に層間絶縁層7182が形成される。層間絶縁層7182上に第1のアンテナ7181が形成される。第1のアンテナ7181上には絶縁層7183が形成され、絶縁層7183の表面に接続端子7184が形成される。

【0138】

一部に接続端子7184が露出した絶縁層7183と第2のアンテナであるパッチアンテナ7103とが、異方性導電接着材7104により固着される。また、接続端子7184とパッチアンテナの給電体層7113とが、異方性導電接着材7104に分散される導電性粒子で電気的に接続される。接続端子7184と薄膜トランジスタを有する層7102に形成される第1の薄膜トランジスタ7185とが電気的に接続される。また、薄膜トランジスタを有する層7102に形成される第2の薄膜トランジスタ7186と第1のアンテナ7181とが電気的に接続される。なお、異方性導電接着材の代わりに、導電性ペーストを硬化した導電層を用いてもよい。

【0139】

第1のアンテナ7181は、アルミニウム、銅、銀を含む金属材料で形成する。例えば、銅又は銀のペースト状組成物を、スクリーン印刷、オフセット印刷、インクジェット方式の印刷法で形成することができる。また、スパッタリングなどでアルミニウム膜を形成し、エッチング加工により形成しても良い。その他、電解メッキ法、無電解メッキ法を用いて形成しても良い。

【0140】

なお、第1のアンテナ7181を省略することも可能である。

【0141】

ここでは、第1のアンテナ7181の形状は、図18(A)に示すように方形コイル状である。

【0142】

第1のアンテナ7181の形状について図18を用いて説明する。図18は、層間絶縁層7182及びその上に形成されたアンテナを示す上面図である。本実施例では、図17(A)及び図18(A)に示すように、第1のアンテナ7181は方形コイル状7181aであるがこの形状に限定されるものではない。円形コイル状としてもよい。また、図18(B)に示すように方形ループ状7181bのアンテナとすることができる。また、円形ループ状アンテナとすることができる。また、図18(C)に示すように直線型ダイポール状7181cのアンテナとすることができる。また、曲線型ダイポール状のアンテナとすることができる。

【0143】

このように複数のアンテナを設けることで、一つの半導体装置で複数の異なる周波数の電波を受信することが可能なマルチバンド対応の半導体装置を形成することができる。

【0144】

本実施例は、上記の実施の形態、実施例1乃至実施例4と自由に組み合わせることができる。

【実施例6】

【0145】

本実施例では、本発明の半導体装置201の用途について図9及び図10を用いて説明する。半導体装置201は、例えば、紙幣、硬貨、有価証券、無記名債券類、証書類(運転免許証や住民票等、図10(A)参照)に設けて使用することができる。また、包装用容器類(包装紙やボトル等、図10(B)参照)、DVDソフトやCDやビデオテープ等の記録媒体(図10(C)参照)に設けて使用することができる。また、車やバイクや自転車等の乗物類(図10(D)参照)、鞄や眼鏡等の身の回り品(図10(E)参照)、食品類、衣類、生活用品類、電子機器等に設けて使用することができる。電子機器とは、液晶表示装置、EL(エレクトロルミネッセンス)表示装置、テレビジョン装置(単にテレビまたはテレビ受像器とも呼ぶ)および携帯電話機等を指す。

【0146】

半導体装置201は、物品の表面に貼り付けたり、物品に埋め込んだりして物品に固定することができる。例えば、本なら紙に埋め込んだり、有機樹脂からなるパッケージなら当該有機樹脂に埋め込んだりするとよい。紙幣、硬貨、有価証券類、無記名債券類、証書類等に半導体装置201を設けることにより、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に半導体装置201を設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。また乗物類に半導体装置201を設けることにより、偽造や盗難を防止することができる。また、動物等の生き物に埋め込むことによって、個々の生き物の識別を容易に行うことができる。例えば、家畜等の生き物に無線タグを埋め込むことによって、生まれた年や性別または種類等を容易に識別することが可能となる。

【0147】

以上のように、本発明の半導体装置201は物品(生き物を含む)であればどのようなものにでも設けて使用することができる。

【0148】

半導体装置201は、無線通信によるデータの送受信が可能である点、様々な形状に加工可能である点、選択する周波数によっては、指向性が広く、認識範囲が広い点等の様々な利点を有する。

【0149】

次に、半導体装置201を用いたシステムの一形態について、図9を用いて説明する。表示部521を含む携帯端末の側面には、リーダ/ライタ520が設けられ、物品A522の側面には本発明の半導体装置523が設けられ、物品B532の上面には本発明の半導体装置531が設けられている(図9(A)参照)。物品A522が含む半導体装置523にリーダ/ライタ520をかざすと、表示部521に物品A522の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴、商品の説明等の商品に関する情報が表示される。物品B532が含む半導体装置531にリーダ/ライタ520をかざすと、表示部521に物品B532の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴、商品の説明等の商品に関する情報が表示される。

【0150】

図9(A)に示すシステムを利用したビジネスモデルの一例を示す。説明には図9(B)のフローチャートを用いる。携帯端末において、食物アレルギーの情報を入力しておく(ステップ1)。食物アレルギーの情報とは、所定の人物が食物アレルギー反応を起こす原材料等の情報である。携帯端末に設けられたリーダ/ライタ520によって、前述のとおり物品A522の情報を取得する(ステップ2)。ここで、物品A522は食品であるとする。物品A522の情報には物品A522の原材料の情報が含まれる。食物アレルギーの情報と取得した物品A522の原材料の情報とを比較し、一致する材料があるか否かを判断する(ステップ3)。一致する材料がある場合、所定の人物は物品Aに対してアレルギー反応を起こす危険性があるとし、携帯端末の使用者に注意を呼びかける(ステップ4)。一致する材料がない場合、所定の人物は物品Aに対してアレルギー反応を起こす危険性が少ないとし、携帯端末の使用者にその旨(安全である旨)を知らせる(ステップ5)。ステップ4やステップ5において、携帯端末の使用者に情報を知らせる方法は、携帯端末の表示部521に表示を行う方法であっても良いし、携帯端末のアラーム等を鳴らす方法であっても良い。

【0151】

本発明の半導体装置201は過電圧を防止するため信頼性が高く、且つサイズを小さくすることができる。よって、本発明により、半導体装置201を搭載することができるものの範囲が広がり、多様なシステムを実現することができる。こうして、高機能化と高付加価値化を実現したシステムを提供することができる。

【0152】

本実施例は、上記の実施の形態、実施例1乃至実施例5と自由に組み合わせることができる。

【図面の簡単な説明】

【0153】

【図1】本発明の半導体装置の構成を示す図。

【図2】従来の半導体装置の構成を示す図。

【図3】本発明の半導体装置の構成を示す図。

【図4】本発明の半導体装置のマスク図面の一部を示す図。

【図5】本発明の半導体装置のアンテナの構成を示す図。

【図6】本発明の半導体装置の作製方法を示す図。

【図7】半導体装置の配線の引き回し方法を示す図。

【図8】本発明の半導体装置の作製方法を示す図。

【図9】本発明の半導体装置の用途を示す図。

【図10】本発明の半導体装置の用途を示す図。

【図11】本発明の半導体装置の作製方法を示す図。

【図12】本発明の半導体装置の作製方法を示す図。

【図13】本発明の半導体装置の作製方法を示す図。

【図14】本発明の半導体装置の作製方法を示す図。

【図15】本発明の半導体装置の作製方法を示す図。

【図16】本発明の半導体装置のマスク図面の一部及び等価回路を示す図。

【図17】本発明の半導体装置の構成を示す図。

【図18】本発明の半導体装置のアンテナの構成を示す図。

【符号の説明】

【0154】

10 半導体層

11 半導体層

12 ゲート配線

13 ゲート配線

14 ゲート配線

15 配線

16 配線

17 配線

18 配線

19 配線

20 配線

21 トランジスタ

22 トランジスタ

23 トランジスタ

24 トランジスタ

25 トランジスタ

26 トランジスタ

27 インバータ

28 インバータ

101 アナログ回路部

102 デジタル回路部(ロジック回路部)

201 半導体装置

202 アンテナ

203 高周波回路

204 電源回路

205 リセット回路

206 クロック発生回路

207 データ復調回路

208 データ変調回路

209 制御回路

210 メモリ回路

211 半導体集積回路

220 共振容量

221 第一の帯域フィルタ

222 第二の帯域フィルタ

223 第一の整流回路

224 保持容量

225 第二の整流回路

226 制御回路内回路

227 インバータ

228 第一の抵抗素子

229 第二の抵抗素子

230 第一の容量素子

231 第二の容量素子

232 N型トランジスタ

233 N型トランジスタ

234 N型トランジスタ

235 N型トランジスタ

301 半導体装置

302 アンテナ

303 高周波回路

304a 電源回路

304b リミッタ回路

304c リセット回路

304d クロック発生回路

305 データ復調回路

306 データ変調回路

307 制御回路

308 メモリ回路

309 半導体集積回路

402 第2導電層

403 第1導電層

404 配線

405 半導体層

406 不純物領域

407 不純物領域

408 絶縁層

409 ゲート電極

410 不純物領域

411 不純物領域

412 不純物領域

520 リーダ/ライタ

521 表示部

522 物品A

523 半導体装置

531 半導体装置

532 物品B

600 基板

601 素子群

602 端子部

603 導電性粒子

604 樹脂

610 基板

661 下地層

662 半導体層

662a チャネル形成領域

662b 不純物領域

662c 低濃度不純物領域

663 第1の絶縁層

664 ゲート電極

665 第3の絶縁層

666 配線

667 第2の絶縁層

668 第4の絶縁層

701 フレキシブル基板

720 無線タグ

901 保護層

902 アンテナ

903 保護層

904 素子群

905 ソース及びドレインの一方

906 ソース及びドレインの他方

907 ゲート電極

980 基板

981 トランジスタ

1101 アナログ回路部

1102 デジタル回路部(ロジック回路部)

1201a 角部

1201b 角部

1201c 角部

1202a 角部

1202b 角部

1202c 角部

2000 マスクパターン

2100 マスクパターン

2200 マスクパターン

2001 トランジスタ

2002 トランジスタ

2003 トランジスタ

2004 容量素子

2005 抵抗素子

3003 厚さ

3004 キャリアの移動方向

3005 方向

3011 配線

3012 配線

3013 配線

3014 コンタクトホール

5000a 端子

5000b 端子

5001a N型半導体層

5001b P型半導体層

5002 コンタクトホール

5003 第1の配線

5004 第2の配線

5501 P型トランジスタ

5502 N型トランジスタ

5550 N型トランジスタ

7101 絶縁性基板

7102 層

7103 パッチアンテナ

7104 異方性導電接着材

7113 給電体層

7181 第1のアンテナ

7181a 方形コイル状

7181b 方形ループ状

7181c 直線型ダイポール状

7182 層間絶縁層

7183 絶縁層

7184 接続端子

7185 第1の薄膜トランジスタ

7186 第2の薄膜トランジスタ

【特許請求の範囲】

【請求項1】

無線通信によりデータの交信を行う半導体装置において、

アナログ回路部とデジタル回路部とを有し、

前記アナログ回路部には無線信号が入力され、

前記デジタル回路部には前記アナログ回路部からの出力信号が入力され、

前記アナログ回路部に含まれるトランジスタのゲート長は、前記デジタル回路部に含まれるトランジスタのゲート長以上であることを特徴とする半導体装置。

【請求項2】

無線通信によりデータの交信を行う半導体装置において、

アナログ回路部とデジタル回路部とを有し、

前記アナログ回路部には無線信号が入力され、

前記デジタル回路部には前記アナログ回路部からの出力信号が入力され、

前記アナログ回路部は、前記無線信号を用いて直流電圧を発生する電源回路と、前記無線信号を復調するデータ復調回路とを有し、

前記電源回路及び前記データ復調回路に含まれるトランジスタのゲート長は、前記デジタル回路部に含まれるトランジスタのゲート長以上であることを特徴とする半導体装置。

【請求項3】

無線通信によりデータの交信を行う半導体装置において、

アナログ回路部とデジタル回路部とを有し、

前記アナログ回路部には無線信号が入力され、

前記デジタル回路部には前記アナログ回路部からの出力信号が入力され、

前記アナログ回路部は、前記無線信号を用いて直流電圧を発生する電源回路と、前記無線信号を復調するデータ復調回路とを有し、

前記電源回路及び前記データ復調回路に含まれるトランジスタのうち、前記電源回路の入力に接続されたトランジスタ及び前記データ復調回路の入力に接続されたトランジスタのゲート長は、前記デジタル回路部に含まれるトランジスタのゲート長以上であることを特徴とする半導体装置。

【請求項4】

無線通信によりデータの交信を行う半導体装置において、

アナログ回路部を有し、

前記アナログ回路部には無線信号が入力され、