半導体装置用テープキャリア、半導体装置の製造方法、半導体装置、および半導体モジュール装置

【課題】テープキャリア型半導体装置において、製品外形に含まれない無形領域を削減できる半導体装置用テープキャリア、半導体装置の製造方法、半導体装置、および半導体モジュール装置を提供する。

【解決手段】表面に複数配置した配線パターン11と半導体素子21のバンプ23とを電気的に接続し、絶縁性の樹脂22で封止することで半導体装置となる薄膜の絶縁テープ1であって、絶縁テープ1の搬送方向における半導体装置の外形サイズが、絶縁テープ1を搬送する為に開口されたスプロケットホール2のピッチ間隔の整数倍Xピッチ(X=1,2,3,4,5,・・・)より大きく、尚かつ整数倍X+小数Yピッチ(0<Y<1)以下である半導体装置用テープキャリアにおいて、半導体装置1デバイスのテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、半導体装置の外形サイズに関与しない絶縁テープ1の無形領域を削減している。

【解決手段】表面に複数配置した配線パターン11と半導体素子21のバンプ23とを電気的に接続し、絶縁性の樹脂22で封止することで半導体装置となる薄膜の絶縁テープ1であって、絶縁テープ1の搬送方向における半導体装置の外形サイズが、絶縁テープ1を搬送する為に開口されたスプロケットホール2のピッチ間隔の整数倍Xピッチ(X=1,2,3,4,5,・・・)より大きく、尚かつ整数倍X+小数Yピッチ(0<Y<1)以下である半導体装置用テープキャリアにおいて、半導体装置1デバイスのテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、半導体装置の外形サイズに関与しない絶縁テープ1の無形領域を削減している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、フレキシブル配線基板上に半導体素子が接合・搭載された半導体装置に用いるテープキャリア、半導体装置、半導体モジュール及び半導体装置の製造方法に関するものである。

【背景技術】

【0002】

本発明は、COF(Chip On Film)、及びTCP(Tape Carrier Package)と呼ばれるフレキシブル配線基板上に半導体素子が接合・搭載された半導体装置(以下COF、及びTCPと称する)用のテープキャリア、半導体装置、半導体モジュール及び半導体装置の製造方法に関するものである。

【0003】

図15は、従来のテープキャリア500上でのCOF半導体装置用テープキャリアについて示した平面図であり、図16は、従来のテープキャリア500上でのCOF半導体装置について示した平面図である。

【0004】

また、図17は、従来のテープキャリア600上でのTCP半導体装置用テープキャリアについて示した平面図であり、図18は、従来のテープキャリア600上でのTCP半導体装置について示した平面図である。

【0005】

TCPとCOFの異なる点は、TCPでは絶縁テープ501の半導体素子521が搭載される部分にあらかじめ貫通した開口部516が開けられ、配線パターン511が片持ち梁状に突き出した状態で配線パターン511の先端部分と半導体素子521が接合されるのに対して、COFでは半導体素子521を搭載するための搭載用の開口部を有しておらず、半導体素子521が薄膜の絶縁テープ501の表面上に形成された配線パターン511に接合・搭載されていること、TCPでは配線パターン511が片持ち梁状に突き出した状態である為に、配線パターン511の厚みは18μm以上を使用しており、配線パターン511の配線ピッチが45μm未満の製造が困難であるのに対して、COFでは薄膜の絶縁テープ501の表面上に配線パターン511が形成されている為に、配線パターン511の厚みは8μm以下も使用でき、配線パターン511の配線ピッチが35μm以下の製造も容易であること、TCPでは液晶パネル等への実装後の折り曲げ部分にあらかじめスリット517が設けられているのに対して、COFでは折り曲げ用のスリットを有しておらず、薄膜の絶縁テープ501のどこでも自由に折り曲げられること、及びTCPではポリイミドから成る絶縁テープ501上に、接着剤を用いて銅箔をラミネートして形成しているのに対して、COFでは銅箔裏面にポリイミド等を塗布、硬化して形成(キャスティング法)、あるいはポリイミド等から成る絶縁テープ501上に銅をスパッタで積層して形成(メタライジング法)していることである。

【0006】

COFは、その使用目的から自由に折り曲げることが可能な薄膜の絶縁テープ501が使用され、薄膜の絶縁テープ501の表面上に配置された配線パターン511の各配線は、半導体素子521の対応する端子と電気的に接続され、外部接続用コネクタ部512には、液晶パネルやプリント基板などに接続される。上記以外の配線パターン露出部は、ソルダーレジスト513が塗布され、絶縁状態が確保される。半導体素子521が搭載される搭載領域515にはソルダーレジスト513は塗布されず、ソルダーレジスト開口部514が形成されている。半導体素子521は薄膜の絶縁テープ501上の搭載領域515に搭載された後、樹脂522によって封止される。

【0007】

COF、TCP共に、多くの場合は、薄膜の絶縁テープ501にスプロケットホール502と呼ばれる搬送用の開口が4.75mm間隔で設置されており、通常、製品の外形に連動したテープピッチはスプロケットホール502の整数倍のピッチで設計されている。各工程の製造設備内では、スプロケットホール502を使用して1ピッチずつ搬送され、1工程(1デバイスの処理・搬送)では、製品の外形ピッチ(整数倍)分が搬送される。

【0008】

薄膜の絶縁テープ501上への製品の配置方法や、搬送を含めた製造方法に関する従来技術としては、TCPでの公開公報・文献、等は無く、COFでは、特許文献1に示されている。

【特許文献1】特開2000−323533号公報(平成12年(2000年)11月24日公開、特許第3558921号、平成16年(2004年)5月28日登録)

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかしながら、前記従来の半導体装置用テープキャリア、半導体装置の製造方法、半導体装置、および半導体モジュール装置では、COF、又はTCPの製品外形サイズやテープピッチが拡大することによる材料費、加工費の増加、および製造能力が低下するという問題点を有している。

【0010】

COF、TCP共に、通常、製品の外形サイズに連動したテープピッチはスプロケットホール502の整数倍のピッチで設計されており、使用用途によっても異なるが、平均的には5ピッチ前後となっている。しかし、製品自体の外形は、スプロケットホール502の整数倍ピッチ(平均的には5ピッチ)に丁度一致したサイズの場合は少なく、製品外形に含まれない無形領域(不要領域)503が存在している場合が多くなっている。この場合、材料コスト、加工費、製造工程の能力、等に無駄が生じることになり、例えば1/2ピッチ(ハーフピッチ)分の無形領域(不要領域)が存在する場合には、材料コストとしては約10%の増加となってしまうことがある。

【0011】

解決方法として、製品外形サイズの縮小、及びテープピッチの小数ピッチ化がある。製品外形サイズの縮小については、外形形状・サイズや配線パターン511の引き回し自由度によって大きく変化するが、ユーザ仕様であることからユーザとの調整が最も重要かつ難題となっており、外形サイズ縮小は非常に困難となっている。

【0012】

そのため、例えば上記の特許文献1では、製品外形の配置を工夫することによって製品の形成に寄与しないテープキャリア700の無形領域503を削減する技術について開示している。

【0013】

図19は、上記特許文献1に開示されている従来技術の一例を示す平面図である。

【0014】

図19に示す例では、COF半導体装置の製造方法について記載している。上記特許文献1の方法はCOF半導体装置およびTCP半導体装置などに適用できる方法であるが、ここではCOF半導体装置について記載することにする。

【0015】

特許文献1の方法では、外部接続用コネクタ部512を含む製品外形の一部が突起形状を有している製品において、突起部同士を互いに隣接するように向かい合わせて配置することで、突起部周辺の不要な領域を削減する。

【0016】

このように配置することによって、使用するテープキャリア700の長さを短く調整している。

【0017】

上記の例では、外部接続用コネクタ部512の向きを向かい合わせることによって無形領域503を削減し、使用するテープキャリア700のテープピッチを削減することができた。しかしながら、さまざまな形状のCOFに対しては、常に外部接続用コネクタ部512を向かい合わせることで使用するテープキャリア700のテープピッチを最小化することができるとは限らず、COFの形状に合わせてテープキャリア700に配置する向きを設計する必要がある。

【0018】

また、上記のように製品の配置方向を複数の方向に配置しているため、各製造工程ではテープキャリア700への部品の実装方向をCOFの配置方向に合わせて切り替える必要がある。このため、テープキャリア700のテープピッチを削減することと、製造工程を簡略化することとを考慮して設計をおこなう必要がある。

【0019】

本発明は、COF、又はTCPの製品外形サイズやテープピッチの拡大による材料費、加工費の増加、製造能力の低下という問題点を解決するものであり、COF、又はTCPにおいて、製品外形に含まれない無形領域(不要領域)を削減でき、材料コストを約10%程度低減できる半導体装置用テープキャリア、半導体装置の製造方法、半導体装置、および半導体モジュール装置を提供することにある。

【課題を解決するための手段】

【0020】

本発明のCOF、又はTCP半導体装置用テープキャリアは、上記課題を解決するために、表面に複数配置した配線パターンと半導体素子の突起電極とを電気的に接続し、絶縁性樹脂で封止することでCOF、又はTCP半導体装置となる薄膜の絶縁テープであって、前記絶縁テープの搬送方向における前記COF、又はTCP半導体装置の外形サイズが、前記絶縁テープを搬送する為に開口されたスプロケットホールのピッチ間隔の整数倍Xピッチ(X=1,2,3,4,5,・・・)より大きく、尚かつ整数倍X+小数Yピッチ(0<Y<1)以下であり、通常はテープピッチを整数倍X+1ピッチに設定する前記COF、又はTCP半導体装置となる前記絶縁テープにおいて、前記COF、又はTCP半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、前記半導体装置の外形サイズに関与しない前記絶縁テープの無形領域を削減していることを特徴としている。

【0021】

また、本発明のCOF、又はTCP半導体装置用テープキャリアでは、前記絶縁テープの搬送方向における前記COF、又はTCP半導体装置の外形サイズを前記配線パターンの設計面で縮小した場合においても、小数Yピッチ(0<Y<1)化を同時に行い、前記COF、又はTCP半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定していることが好ましい。

【0022】

上記の発明によれば、半導体装置の外形サイズに関与しない前記絶縁テープの無形領域(不要領域)を削減し、材料コストを低減することができる。

【0023】

本発明のCOF、又はTCP半導体装置の製造方法は、上記課題を解決するために、前記半導体素子の実装、樹脂封止、テスト、他、アセンブリ工程での搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定した前記半導体装置を製造していることを特徴としている。

【0024】

製造設備の搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施できるように、必要に応じてソフトや搬送機構を変更している。

【0025】

また、本発明のCOF、又はTCP半導体装置の製造方法では、前記半導体素子の実装、樹脂封止、テスト、他、アセンブリ工程が、前記半導体装置を複数個 同時に処理し、前記半導体装置の製品処理ピッチが整数倍となるようにしてもよい。

【0026】

前記半導体装置を処理する処理機構を複数個保有している製造設備を使用して、複数個の半導体装置を同時に処理してもよい。

【0027】

また、本発明のCOF、又はTCP半導体装置の製造方法では、前記半導体装置の前記絶縁テープからの打ち抜き工程が、前記半導体装置を複数個同時に打ち抜く工程であり、前記半導体装置の製品打ち抜きの外形、及び搬送ピッチが前記スプロケットホールの前記ピッチ間隔の整数倍となるようにしてもよい。

【0028】

1セットの打ち抜き金型によって、複数個の前記半導体装置を同時に打ち抜いている。

【0029】

上記の発明によれば、COF、又はTCP半導体装置の製造における搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、COF、又はTCP半導体装置用テープキャリアのテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定することができるので、半導体装置の外形サイズに関与しない前記絶縁テープの無形領域(不要領域)を削減し、材料コストを低減することができる。

【0030】

上記の発明によれば、COF、又はTCP半導体装置の外形サイズに関与しない前記絶縁テープの無形領域(不要領域)を削減し、材料コストを低減した半導体装置または半導体モジュール装置を製造することができる。

【発明の効果】

【0031】

本発明のCOF、又はTCP半導体装置用テープキャリアは、以上のように、前記絶縁テープの搬送方向における前記COF、又はTCP半導体装置の外形サイズが、前記絶縁テープを搬送する為に開口されたスプロケットホールのピッチ間隔の整数倍Xピッチ(X=1,2,3,4,5,・・・)より大きく、尚かつ整数倍X+小数Yピッチ(0<Y<1)以下であり、通常はテープピッチを整数倍X+1ピッチに設定する前記COF、又はTCP半導体装置となる前記絶縁テープにおいて、前記半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、前記半導体装置の外形サイズに関与しない前記絶縁テープの無形領域を削減している。

【0032】

また、本発明のCOF、又はTCP半導体装置の製造方法は、以上のように、前記半導体素子の実装、樹脂封止、テスト、他、アセンブリ工程での搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定した前記半導体装置を製造する方法である。

【0033】

また、本発明のCOF、又はTCP半導体装置の製造方法は、前記半導体素子の実装、樹脂封止、テスト、他、アセンブリ工程において、前記半導体装置を複数個 同時に処理し、前記半導体装置の製品処理ピッチを整数倍とする製造方法でもある。

【0034】

また、本発明の半導体装置、又は半導体モジュール装置は、上記のCOF、又はTCP半導体装置用テープキャリア、または半導体装置の製造方法を用いて、製造されたものである。

【0035】

それゆえ、COF、又はTCP半導体装置用テープキャリアにおいて、半導体装置の製品外形に含まれない無形領域(不要領域)を削減でき、材料コストを約10%程度低減できる半導体装置用テープキャリア、半導体装置の製造方法、半導体装置、および半導体モジュール装置を提供することができるという効果を奏する。

【0036】

即ち、前記COF、又はTCP半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、前記COF、又はTCP半導体装置の外形サイズに関与しない前記絶縁テープの無形領域(不要領域)を削減していること、前記半導体素子のアセンブリ工程での搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定した前記COF、又はTCP半導体装置を製造していること、製造設備の搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施していること、必要に応じて、ソフトや搬送機構を変更していること、前記半導体素子のアセンブリ工程が、前記COF、又はTCP半導体装置を複数個同時に処理し、前記COF、又はTCP半導体装置の製品処理ピッチが整数倍となっていること、処理機構を複数個 保有している製造設備を使用して、複数個を同時に処理していること、前記COF、又はTCP半導体装置の前記絶縁テープからの打ち抜き工程が、前記COF、又はTCP半導体装置を複数個同時に打ち抜き、前記COF、又はTCP半導体装置の製品打ち抜きの外形、及び搬送ピッチが整数倍となっていることによって、本発明によるCOF、又はTCP半導体装置用テープキャリア、及び半導体装置の製造方法は、従来のCOF、又はTCP半導体装置用テープキャリア、及び半導体装置の製造方法と比較して、前記COF、又はTCPの製品外形に含まれない無形領域(不要領域)を削減することが可能となり、材料コストを約10%程度低減できる。

【発明を実施するための最良の形態】

【0037】

〔実施の形態1〕

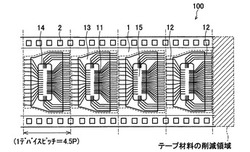

図1〜図4に本発明でのCOF、TCP用テープキャリア、及び半導体装置の実施の形態を示し、図5〜図8にCOF、TCP半導体装置、及びモジュールの断面図を示す。

【0038】

本COFに使用されるテープキャリア100は、自由に折り曲げることが可能な柔軟性の高い厚さ15〜40μmの薄膜のポリイミド系の絶縁テープ1を基材とし、絶縁テープ1の表面に厚さ8〜18μmの銅箔又はスパッタ銅(配線パターン)がキャスティング法、スパッタ法(メタライジング法)、等により形成されている。

【0039】

本TCPに使用されるテープキャリア200は、ポリイミドから成る絶縁テープ1上に、接着剤18を用いて銅箔をラミネートして形成しており、絶縁テープ1の半導体素子21が搭載される部分にあらかじめ貫通した開口部16が開けられ、配線パターン11が片持ち梁状に突き出した状態である為、配線パターン11の厚みは18μm以上を使用しており、液晶パネル等への実装後の折り曲げ部分にはあらかじめスリット17が設けられている。

【0040】

COF、TCP共に、配線パターン11の表面には、錫メッキや金メッキが施されている。配線パターン11と半導体素子21との接続部、及び外部接続用コネクタ部12以外のパターン露出部には、ソルダーレジスト13が塗布され、絶縁状態が確保される。半導体素子21が搭載される搭載領域15にはソルダーレジスト13は塗布されず、ソルダーレジスト開口部14が形成されている。尚、図中には、メッキは記載していない。

【0041】

COF、TCP共に、多くの場合は、薄膜の絶縁テープ1にスプロケットホール2と呼ばれる搬送用の開口が4.75mm間隔で設置されており、通常、製品の外形に連動したテープピッチはスプロケットホール2の整数倍のピッチで設計されている。各工程の製造設備内では、スプロケットホール2を使用して1ピッチずつ搬送され、1工程(1デバイスの処理・搬送)では、製品の外形ピッチ(整数倍)分が搬送される。

【0042】

半導体素子21には、バンプ23と呼ばれる突起電極が形成されており、絶縁テープ1の表面上に形成されている(COF)、又は絶縁テープ1の半導体素子21が搭載される部分にあらかじめ貫通した開口部16が開けられ、配線パターン11が片持ち梁状に突き出した状態である(TCP)配線パターン11に接合・搭載され、配線パターン11の各配線が半導体素子21の対応する端子のバンプ23と電気的に接続される。半導体素子21が接合・搭載された後に半導体素子21とテープキャリア100または200に出来る隙間(COF)、又は半導体素子21の表面(TCP)は、樹脂22が注入(COF)、又は塗布(TCP)され封止される。配線パターン11の外部接続用コネクタ部12には、液晶パネル24やプリント基板25などが接続される。

【0043】

本発明のCOF、及びTCP用のテープキャリア(100、200)は、配線パターン11と半導体素子21とを電気的に接続し、絶縁性の樹脂22で封止することでCOF、又はTCP半導体装置となる絶縁テープ1の搬送方向におけるCOF、又はTCP半導体装置の外形サイズが、絶縁テープ1を搬送する為に開口されたスプロケットホール2のピッチ間隔(4.75mm)の整数倍4ピッチより大きく、尚かつ整数倍4+1/2ピッチ(ハーフピッチ)以下であり、通常はテープピッチを整数倍4+1=5ピッチに設定するCOF、又はTCP半導体装置となる絶縁テープ1において、COF、又はTCP半導体装置のテープピッチを整数倍4+1/2=4.5ピッチに設定し、COF、又はTCP半導体装置の外形サイズに関与しない絶縁テープ1の無形領域(不要領域)を削減し、材料コストを低減している。

【0044】

図15〜図18に従来のCOF、及びTCP用のテープキャリア(500、600)を示す。

【0045】

従来のCOF、及びTCP用のテープキャリア(500、600)では、絶縁テープ501の搬送方向におけるCOF、又はTCP半導体装置の外形サイズが、絶縁テープ501を搬送する為に開口されたスプロケットホール502のピッチ間隔(4.75mm)の整数倍4ピッチより大きく、尚かつ整数倍4+1/2ピッチ(ハーフピッチ)以下の場合でも、テープピッチを整数倍4+1=5ピッチに設定されており、COF、又はTCP半導体装置の外形サイズに関与しない絶縁テープ501の無形領域(不要領域)503が存在している為、材料コスト、加工費、製造工程の能力、等に無駄が生じている。

【0046】

本発明を実施したCOF、及びTCP用のテープキャリア(100、200)では、COF、又はTCP半導体装置の外形サイズに関与しない絶縁テープ1の無形領域(不要領域)を削減していることによって、従来のCOF、又はTCP半導体装置用のテープキャリア(500、600)と比較して、COF、又はTCPのテープピッチ拡大による材料費、加工費の増加、製造能力の低下という問題点の解決が可能となり、COF、又はTCP半導体装置用のテープキャリアの材料コストを従来(平均的には5ピッチ)の約90%に低減できる。

【0047】

図19に別の従来例として、COF用のテープキャリア700を示す。

【0048】

従来のCOF用のテープキャリア700では、外部接続用コネクタ部512の向きを向かい合わせることによって無形領域503を削減し、使用するテープキャリア700のテープピッチを削減することができた。しかしながら、さまざまな形状のCOFに対しては、常に外部接続用コネクタ部512を向かい合わせることで使用するテープキャリア700のテープピッチを最小化することができるとは限らず、COFの形状に合わせてテープキャリア700に配置する向きを設計する必要がある。

【0049】

また、上記のように製品の配置方向を複数の方向に配置しているため、各製造工程ではテープキャリア700への部品の実装方向をCOFの配置方向に合わせて切り替える必要がある。このため、テープキャリア700のテープピッチを削減することと、製造工程を簡略化することとを考慮して設計をおこなう必要がある。

【0050】

本発明では、上記の従来例のように、COFの形状に合わせてテープキャリアに配置する向きを設計する必要がない。

【0051】

〔実施の形態2〕

図9、図10に本発明でのCOF用のテープキャリア100、及び半導体装置の実施の形態を示す。

【0052】

本発明を実施したCOF用のテープキャリア100では、絶縁テープ1の搬送方向におけるCOF半導体装置の外形サイズが、絶縁テープ1を搬送する為に開口されたスプロケットホール2のピッチ間隔(4.75mm)の整数倍4ピッチより大きく、尚かつ整数倍4+1/4ピッチ以下であり、通常はテープピッチを整数倍4+1=5ピッチに設定するCOF半導体装置となる絶縁テープ1において、COF半導体装置のテープピッチを整数倍4+1/4=4.25ピッチに設定し、COF半導体装置の外形サイズに関与しない絶縁テープ1の無形領域(不要領域)を削減していることによって、従来のCOF、又はTCP半導体装置用のテープキャリア(500,600)と比較して、COFのテープピッチ拡大による材料費、加工費の増加、製造能力の低下という問題点の解決が可能となり、COF半導体装置用のテープキャリア100の材料コストを従来(平均的には5ピッチ)の約85%に低減できる。

【0053】

〔実施の形態3〕

図11に本発明のCOF半導体装置の実施の形態を示す。

【0054】

絶縁テープ1の搬送方向におけるCOF半導体装置の外形サイズを配線パターン11の設計面で縮小した場合の実施の形態を示す。本実施の形態においても実施の形態1と同様に、1/2ピッチ(ハーフピッチ)化を同時に行い、COF半導体装置のテープピッチを整数倍3+1/2=3.5ピッチに設定している。

【0055】

設計面での外形サイズ縮小の方法としては、配線パターン間のピッチ縮小、配線パターンの引き回し変更、ユーザ外形仕様の変更、等がある。

【0056】

本実施の形態のCOF用のテープキャリア100では、実施の形態1のCOF用のテープキャリア100を超える効果(約70%に低減)を得ることができる。

【0057】

〔実施の形態4〕

図12に本発明のCOF半導体装置の実施の形態を示す。

【0058】

実施の形態3と同様に、絶縁テープ1の搬送方向におけるCOF半導体装置の外形サイズを配線パターン11の設計面で縮小した場合の実施の形態を示す。本実施の形態においては、実施の形態3よりもCOF半導体装置の外形サイズの配線パターン設計面での縮小が大きく、実施の形態1、及び実施の形態3と同様に、1/2ピッチ(ハーフピッチ)化も同時に行い、COF半導体装置のテープピッチを整数倍2+1/2=2.5ピッチに設定している。

【0059】

本実施の形態のCOF用のテープキャリア100では、実施の形態1、及び実施の形態3のCOF用のテープキャリア100を超える効果(約50%に低減)を得ることができる。

【0060】

〔実施の形態5〕

図13に本発明のCOF半導体装置の実施の形態として製造工程(半導体素子実装工程)を示す。

【0061】

従来のCOF半導体装置の製造工程では、図20に示すように、製造装置の搬送ピッチが1ピッチで実施され、テープピッチを整数倍に設定したCOF半導体装置を製造していた。この時、1デバイスの製品処理のピッチは、例えば1ピッチ×5=5ピッチとなっている。

【0062】

本発明のCOF半導体装置の製造工程(半導体素子実装工程)では、ソフトや搬送機構を変更していることで、製造装置の搬送ピッチを1/2ピッチ(ハーフピッチ)で実施し、テープピッチを整数倍4+1/2ピッチ=4.5ピッチに設定したCOF半導体装置を製造している。この時、1デバイスの製品処理のピッチは、例えば0.5ピッチ×9=4.5ピッチとなっている。

【0063】

すなわち、本実施の形態の半導体装置用テープキャリアにおける1デバイスのテープピッチは、スプロケットホールのピッチ間隔の整数倍X+小数Y=4+0.5=4.5ピッチであり、半導体装置の製造工程(半導体素子実装工程)における1デバイスの製品処理ピッチも同じ4.5ピッチとなるが、製造工程における搬送ピッチである小数Z(0<Z<1、Z=0.05の整数倍)は、いくつかのピッチが考えられ、例えば0.05×5=0.25ピッチ、0.05×10=0.5ピッチ、0.05×30=1.5ピッチ、等で搬送することができる。

【0064】

本実施の形態のCOF半導体装置の製造工程(半導体素子実装工程)は、実施の形態1のCOF用のテープキャリア100を使用した製造工程を示しているが、実施の形態3、及び実施の形態4においても同様の製造工程(半導体素子実装工程)によって製造することが可能である。

【0065】

〔実施の形態6〕

図14に本発明のCOF半導体装置の実施の形態として製造工程(半導体装置打ち抜き工程)を示す。

【0066】

従来のCOF半導体装置の製造工程では、図21に示すように、COF半導体装置の絶縁テープ1からの打ち抜き工程において、COF半導体装置を1デバイスずつ打ち抜いていた。

【0067】

本発明のCOF半導体素子の製造工程では、COF半導体装置を複数個同時に処理することで、COF半導体装置の製品処理ピッチを整数倍としている。COF半導体装置の絶縁テープ1からの打ち抜き工程において、COF半導体装置を複数個(2個)同時に打ち抜き、COF半導体装置の製品打ち抜きの処理ピッチをスプロケットホール2のピッチ間隔(4.75mm)の整数倍(9ピッチ)としている。

【0068】

本実施の形態のCOF半導体装置の製造工程(半導体装置打ち抜き工程)は、実施の形態1のCOF用のテープキャリア100を使用した製造工程を示しているが、実施の形態3、及び実施の形態4においても同様の製造工程によって製造することが可能である。

【0069】

以上のように、テープピッチの小数ピッチ化は、製品外形サイズがスプロケットホールの整数倍Xピッチ(X=1,2,3,4,5,・・・)より大きく、尚かつ整数倍X+小数Yピッチ(0<Y<1)以下である場合(通常、テープピッチを整数倍X+1ピッチに設定している)には、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に縮小することが可能であり、例えば4ピッチ+1/2ピッチ(ハーフピッチ)の場合には、通常は4+1=5ピッチに設定しているが、4+0.5=4.5ピッチに縮小することが可能であり、10%の縮小が容易となってくる。勿論、製品外形サイズの縮小も可能な場合には更なる縮小が可能となる。

【0070】

しかし、COF、又はTCPの製造工程や製品の打ち抜き工程も、製品ピッチ、すなわち整数倍X+小数Yピッチ(0<Y<1)で対応する必要があるが、製造設備の搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施できるように、例えば4+0.5=4.5ピッチの場合は、搬送ピッチを0.5ピッチで実施できるように、製造設備のソフトや搬送機構を変更すること、絶縁テープからの製品打ち抜き工程では、複数個を同時に打ち抜くことで、容易に対応することが可能となる。

【0071】

すなわち、本発明によるCOF、又はTCP半導体装置用テープキャリア、及び半導体装置の製造方法は、上記の課題を解決する為に、表面に複数配置した配線パターンと半導体素子の突起電極とを電気的に接続し、絶縁性の樹脂で封止することでCOF、又はTCP半導体装置となる薄膜の絶縁テープであり、前記絶縁テープの搬送方向における前記COF、又はTCP半導体装置の外形サイズが、前記絶縁テープを搬送する為に開口されたスプロケットホールのピッチ間隔(4.75mm)の整数倍Xより大きく、尚かつ整数倍X+小数Yピッチ(0<Y<1)以下であり、通常はテープピッチを整数倍X+1ピッチに設定する前記COF、又はTCP半導体装置となる前記絶縁テープにおいて、前記COF、又はTCP半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、前記COF、又はTCP半導体装置の外形サイズに関与しない前記絶縁テープの無形領域(不要領域)を削減している。また、前記半導体素子のアセンブリ工程での搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定した前記COF、又はTCP半導体装置を製造していること、製造設備の搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施できるように、ソフトや搬送機構を変更していること、前記半導体素子のアセンブリ工程が、前記COF、又はTCP半導体装置を複数個 同時に処理し、前記COF、又はTCP半導体装置の製品処理ピッチが整数倍となっていること、処理機構を複数個 保有している製造設備を使用して、複数個を同時に処理していること、前記COF、又はTCP半導体装置の前記絶縁テープからの打ち抜き工程が、前記COF、又はTCP半導体装置を複数個 同時に打ち抜き、前記COF、又はTCP半導体装置の製品打ち抜き処理ピッチが整数倍となっていることで、前記COF、又はTCPの製品外形に含まれない無形領域(不要領域)を削減し、材料コストを低減したことを特徴としている。

【0072】

また、本発明によるCOF、又はTCP半導体装置用テープキャリア、及び半導体装置の製造方法と従来のCOF、又はTCP半導体装置用テープキャリア、及び半導体装置の製造方法との違いは、前記COF、又はTCP半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、前記COF、又はTCP半導体装置の外形サイズに関与しない前記絶縁テープの無形領域(不要領域)を削減していること、前記半導体素子のアセンブリ工程での搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定した前記COF、又はTCP半導体装置を製造していること、製造設備の搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施できるように、ソフトや搬送機構を変更していること、前記半導体素子のアセンブリ工程が、前記COF、又はTCP半導体装置を複数個 同時に処理し、前記COF、又はTCP半導体装置の製品処理ピッチが整数倍となっていること、処理機構を複数個 保有している製造設備を使用して、複数個を同時に処理していること、前記COF、又はTCP半導体装置の前記絶縁テープからの打ち抜き工程が、前記COF、又はTCP半導体装置を複数個 同時に打ち抜き、前記COF、又はTCP半導体装置の製品打ち抜きの処理ピッチが整数倍となっていることのみであり、一部、ソフトや搬送機構の変更は必要となるものの、従来の製造設備・手法での製造が可能である。

【0073】

これによって、前記COF、又はTCP半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、前記COF、又はTCP半導体装置の外形サイズに関与しない前記絶縁テープの無形領域(不要領域)を削減していること、前記半導体素子のアセンブリ工程での搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定した前記COF、又はTCP半導体装置を製造していること、製造設備の搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施できるように、ソフトや搬送機構を変更していること、前記半導体素子のアセンブリ工程が、前記COF、又はTCP半導体装置を複数個同時に処理し、前記COF、又はTCP半導体装置の製品処理ピッチが整数倍となっていること、処理機構を複数個 保有している製造設備を使用して、複数個を同時に処理していること、前記COF、又はTCP半導体装置の前記絶縁テープからの打ち抜き工程が、前記COF、又はTCP半導体装置を複数個 同時に打ち抜き、前記COF、又はTCP半導体装置の製品打ち抜きの処理ピッチが整数倍となっていることによって、本発明によるCOF、又はTCP半導体装置用テープキャリア、及び半導体装置の製造方法は、従来のCOF、又はTCP半導体装置用テープキャリア、及び半導体装置の製造方法と比較して、前記COF、又はTCPの製品外形に含まれない無形領域(不要領域)を削減することが可能となり、材料コストを約10%程度低減できる。

【産業上の利用可能性】

【0074】

以上のように、本発明では、フレキシブル配線基板上に半導体素子が接合・搭載された半導体装置の製造方法において、半導体装置の外形サイズにあわせて半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)とすることができ、半導体装置の外形サイズに関与しない絶縁テープの無形領域を削減することができる。そのため、本発明は、COF半導体装置やTCP半導体装置に代表されるテープ状の材料から形成される半導体装置やその部品を製造する分野に利用することができるだけでなく、さらには、ロール状に形成されている材料から定められた長さの製品を製造することに関わる分野に広く応用することが可能である。

【図面の簡単な説明】

【0075】

【図1】本発明の実施の形態として、COF半導体装置用テープキャリア(半導体素子実装前)を示す平面図である。

【図2】本発明の実施の形態として、図1の半導体素子実装後(半導体装置)を示す平面図である。

【図3】図1、図2とは異なる本発明の実施の形態として、TCP半導体装置用テープキャリア(半導体素子実装前)を示す平面図である。

【図4】図1、図2とは異なる本発明の実施の形態として、図3の半導体素子実装後(半導体装置)を示す平面図である。

【図5】本発明の実施の形態として、図1、図2の実施の形態によるCOF半導体装置を示す断面図である。

【図6】本発明の実施の形態として、図3、図4の実施の形態によるTCP半導体装置を示す断面図である。

【図7】本発明の実施の形態として、図5の実施の形態による半導体モジュール装置を示す断面図である。

【図8】本発明の実施の形態として、図6の実施の形態による半導体モジュール装置を示す断面図である。

【図9】図1〜図4とは異なる本発明の実施の形態として、COF半導体装置用テープキャリア(半導体素子実装前)を示す平面図である。

【図10】図1〜図4とは異なる本発明の実施の形態として、図9の半導体素子実装後(半導体装置)を示す平面図である。

【図11】図1〜図4、図9、図10とは異なる本発明の実施の形態として、COF半導体装置を示す平面図である。

【図12】図1〜図4、図9〜図11とは異なる本発明の実施の形態として、COF半導体装置を示す平面図である。

【図13】本発明の実施の形態として、半導体素子の実装工程を示す平面図である。

【図14】本発明の実施の形態として、COF半導体装置の打ち抜き工程を示す平面図である。

【図15】従来例のCOF半導体装置用テープキャリア(半導体素子実装前)を示す平面図である。

【図16】従来例のCOF半導体装置を示す平面図である。

【図17】従来例のTCP半導体装置用テープキャリア(半導体素子実装前)を示す平面図である。

【図18】従来例のTCP半導体装置を示す平面図である。

【図19】図15〜図18とは異なる従来例のCOF半導体装置用テープキャリア(半導体素子実装前)を示す平面図である。

【図20】従来例の半導体素子実装工程を示す平面図である。

【図21】従来例のCOF半導体装置打ち抜き工程を示す平面図である。

【符号の説明】

【0076】

1,501 絶縁テープ

2,502 スプロケットホール

11、511 配線パターン

12、512 外部接続用コネクタ部

13、513 ソルダーレジスト

14、514 ソルダーレジスト開口部

15、515 搭載領域

16、516 開口部

17、517 スリット

18、 接着剤

21、521 半導体素子

22、522 樹脂(絶縁性樹脂)

23 バンプ(突起電極)

24 液晶パネル

25 プリント基板

100 テープキャリア(半導体装置用テープキャリア)

200 テープキャリア(半導体装置用テープキャリア)

500 テープキャリア(半導体装置用テープキャリア)

503 無形領域(不要領域)

600 テープキャリア(半導体装置用テープキャリア)

700 テープキャリア(半導体装置用テープキャリア)

【技術分野】

【0001】

本発明は、フレキシブル配線基板上に半導体素子が接合・搭載された半導体装置に用いるテープキャリア、半導体装置、半導体モジュール及び半導体装置の製造方法に関するものである。

【背景技術】

【0002】

本発明は、COF(Chip On Film)、及びTCP(Tape Carrier Package)と呼ばれるフレキシブル配線基板上に半導体素子が接合・搭載された半導体装置(以下COF、及びTCPと称する)用のテープキャリア、半導体装置、半導体モジュール及び半導体装置の製造方法に関するものである。

【0003】

図15は、従来のテープキャリア500上でのCOF半導体装置用テープキャリアについて示した平面図であり、図16は、従来のテープキャリア500上でのCOF半導体装置について示した平面図である。

【0004】

また、図17は、従来のテープキャリア600上でのTCP半導体装置用テープキャリアについて示した平面図であり、図18は、従来のテープキャリア600上でのTCP半導体装置について示した平面図である。

【0005】

TCPとCOFの異なる点は、TCPでは絶縁テープ501の半導体素子521が搭載される部分にあらかじめ貫通した開口部516が開けられ、配線パターン511が片持ち梁状に突き出した状態で配線パターン511の先端部分と半導体素子521が接合されるのに対して、COFでは半導体素子521を搭載するための搭載用の開口部を有しておらず、半導体素子521が薄膜の絶縁テープ501の表面上に形成された配線パターン511に接合・搭載されていること、TCPでは配線パターン511が片持ち梁状に突き出した状態である為に、配線パターン511の厚みは18μm以上を使用しており、配線パターン511の配線ピッチが45μm未満の製造が困難であるのに対して、COFでは薄膜の絶縁テープ501の表面上に配線パターン511が形成されている為に、配線パターン511の厚みは8μm以下も使用でき、配線パターン511の配線ピッチが35μm以下の製造も容易であること、TCPでは液晶パネル等への実装後の折り曲げ部分にあらかじめスリット517が設けられているのに対して、COFでは折り曲げ用のスリットを有しておらず、薄膜の絶縁テープ501のどこでも自由に折り曲げられること、及びTCPではポリイミドから成る絶縁テープ501上に、接着剤を用いて銅箔をラミネートして形成しているのに対して、COFでは銅箔裏面にポリイミド等を塗布、硬化して形成(キャスティング法)、あるいはポリイミド等から成る絶縁テープ501上に銅をスパッタで積層して形成(メタライジング法)していることである。

【0006】

COFは、その使用目的から自由に折り曲げることが可能な薄膜の絶縁テープ501が使用され、薄膜の絶縁テープ501の表面上に配置された配線パターン511の各配線は、半導体素子521の対応する端子と電気的に接続され、外部接続用コネクタ部512には、液晶パネルやプリント基板などに接続される。上記以外の配線パターン露出部は、ソルダーレジスト513が塗布され、絶縁状態が確保される。半導体素子521が搭載される搭載領域515にはソルダーレジスト513は塗布されず、ソルダーレジスト開口部514が形成されている。半導体素子521は薄膜の絶縁テープ501上の搭載領域515に搭載された後、樹脂522によって封止される。

【0007】

COF、TCP共に、多くの場合は、薄膜の絶縁テープ501にスプロケットホール502と呼ばれる搬送用の開口が4.75mm間隔で設置されており、通常、製品の外形に連動したテープピッチはスプロケットホール502の整数倍のピッチで設計されている。各工程の製造設備内では、スプロケットホール502を使用して1ピッチずつ搬送され、1工程(1デバイスの処理・搬送)では、製品の外形ピッチ(整数倍)分が搬送される。

【0008】

薄膜の絶縁テープ501上への製品の配置方法や、搬送を含めた製造方法に関する従来技術としては、TCPでの公開公報・文献、等は無く、COFでは、特許文献1に示されている。

【特許文献1】特開2000−323533号公報(平成12年(2000年)11月24日公開、特許第3558921号、平成16年(2004年)5月28日登録)

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかしながら、前記従来の半導体装置用テープキャリア、半導体装置の製造方法、半導体装置、および半導体モジュール装置では、COF、又はTCPの製品外形サイズやテープピッチが拡大することによる材料費、加工費の増加、および製造能力が低下するという問題点を有している。

【0010】

COF、TCP共に、通常、製品の外形サイズに連動したテープピッチはスプロケットホール502の整数倍のピッチで設計されており、使用用途によっても異なるが、平均的には5ピッチ前後となっている。しかし、製品自体の外形は、スプロケットホール502の整数倍ピッチ(平均的には5ピッチ)に丁度一致したサイズの場合は少なく、製品外形に含まれない無形領域(不要領域)503が存在している場合が多くなっている。この場合、材料コスト、加工費、製造工程の能力、等に無駄が生じることになり、例えば1/2ピッチ(ハーフピッチ)分の無形領域(不要領域)が存在する場合には、材料コストとしては約10%の増加となってしまうことがある。

【0011】

解決方法として、製品外形サイズの縮小、及びテープピッチの小数ピッチ化がある。製品外形サイズの縮小については、外形形状・サイズや配線パターン511の引き回し自由度によって大きく変化するが、ユーザ仕様であることからユーザとの調整が最も重要かつ難題となっており、外形サイズ縮小は非常に困難となっている。

【0012】

そのため、例えば上記の特許文献1では、製品外形の配置を工夫することによって製品の形成に寄与しないテープキャリア700の無形領域503を削減する技術について開示している。

【0013】

図19は、上記特許文献1に開示されている従来技術の一例を示す平面図である。

【0014】

図19に示す例では、COF半導体装置の製造方法について記載している。上記特許文献1の方法はCOF半導体装置およびTCP半導体装置などに適用できる方法であるが、ここではCOF半導体装置について記載することにする。

【0015】

特許文献1の方法では、外部接続用コネクタ部512を含む製品外形の一部が突起形状を有している製品において、突起部同士を互いに隣接するように向かい合わせて配置することで、突起部周辺の不要な領域を削減する。

【0016】

このように配置することによって、使用するテープキャリア700の長さを短く調整している。

【0017】

上記の例では、外部接続用コネクタ部512の向きを向かい合わせることによって無形領域503を削減し、使用するテープキャリア700のテープピッチを削減することができた。しかしながら、さまざまな形状のCOFに対しては、常に外部接続用コネクタ部512を向かい合わせることで使用するテープキャリア700のテープピッチを最小化することができるとは限らず、COFの形状に合わせてテープキャリア700に配置する向きを設計する必要がある。

【0018】

また、上記のように製品の配置方向を複数の方向に配置しているため、各製造工程ではテープキャリア700への部品の実装方向をCOFの配置方向に合わせて切り替える必要がある。このため、テープキャリア700のテープピッチを削減することと、製造工程を簡略化することとを考慮して設計をおこなう必要がある。

【0019】

本発明は、COF、又はTCPの製品外形サイズやテープピッチの拡大による材料費、加工費の増加、製造能力の低下という問題点を解決するものであり、COF、又はTCPにおいて、製品外形に含まれない無形領域(不要領域)を削減でき、材料コストを約10%程度低減できる半導体装置用テープキャリア、半導体装置の製造方法、半導体装置、および半導体モジュール装置を提供することにある。

【課題を解決するための手段】

【0020】

本発明のCOF、又はTCP半導体装置用テープキャリアは、上記課題を解決するために、表面に複数配置した配線パターンと半導体素子の突起電極とを電気的に接続し、絶縁性樹脂で封止することでCOF、又はTCP半導体装置となる薄膜の絶縁テープであって、前記絶縁テープの搬送方向における前記COF、又はTCP半導体装置の外形サイズが、前記絶縁テープを搬送する為に開口されたスプロケットホールのピッチ間隔の整数倍Xピッチ(X=1,2,3,4,5,・・・)より大きく、尚かつ整数倍X+小数Yピッチ(0<Y<1)以下であり、通常はテープピッチを整数倍X+1ピッチに設定する前記COF、又はTCP半導体装置となる前記絶縁テープにおいて、前記COF、又はTCP半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、前記半導体装置の外形サイズに関与しない前記絶縁テープの無形領域を削減していることを特徴としている。

【0021】

また、本発明のCOF、又はTCP半導体装置用テープキャリアでは、前記絶縁テープの搬送方向における前記COF、又はTCP半導体装置の外形サイズを前記配線パターンの設計面で縮小した場合においても、小数Yピッチ(0<Y<1)化を同時に行い、前記COF、又はTCP半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定していることが好ましい。

【0022】

上記の発明によれば、半導体装置の外形サイズに関与しない前記絶縁テープの無形領域(不要領域)を削減し、材料コストを低減することができる。

【0023】

本発明のCOF、又はTCP半導体装置の製造方法は、上記課題を解決するために、前記半導体素子の実装、樹脂封止、テスト、他、アセンブリ工程での搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定した前記半導体装置を製造していることを特徴としている。

【0024】

製造設備の搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施できるように、必要に応じてソフトや搬送機構を変更している。

【0025】

また、本発明のCOF、又はTCP半導体装置の製造方法では、前記半導体素子の実装、樹脂封止、テスト、他、アセンブリ工程が、前記半導体装置を複数個 同時に処理し、前記半導体装置の製品処理ピッチが整数倍となるようにしてもよい。

【0026】

前記半導体装置を処理する処理機構を複数個保有している製造設備を使用して、複数個の半導体装置を同時に処理してもよい。

【0027】

また、本発明のCOF、又はTCP半導体装置の製造方法では、前記半導体装置の前記絶縁テープからの打ち抜き工程が、前記半導体装置を複数個同時に打ち抜く工程であり、前記半導体装置の製品打ち抜きの外形、及び搬送ピッチが前記スプロケットホールの前記ピッチ間隔の整数倍となるようにしてもよい。

【0028】

1セットの打ち抜き金型によって、複数個の前記半導体装置を同時に打ち抜いている。

【0029】

上記の発明によれば、COF、又はTCP半導体装置の製造における搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、COF、又はTCP半導体装置用テープキャリアのテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定することができるので、半導体装置の外形サイズに関与しない前記絶縁テープの無形領域(不要領域)を削減し、材料コストを低減することができる。

【0030】

上記の発明によれば、COF、又はTCP半導体装置の外形サイズに関与しない前記絶縁テープの無形領域(不要領域)を削減し、材料コストを低減した半導体装置または半導体モジュール装置を製造することができる。

【発明の効果】

【0031】

本発明のCOF、又はTCP半導体装置用テープキャリアは、以上のように、前記絶縁テープの搬送方向における前記COF、又はTCP半導体装置の外形サイズが、前記絶縁テープを搬送する為に開口されたスプロケットホールのピッチ間隔の整数倍Xピッチ(X=1,2,3,4,5,・・・)より大きく、尚かつ整数倍X+小数Yピッチ(0<Y<1)以下であり、通常はテープピッチを整数倍X+1ピッチに設定する前記COF、又はTCP半導体装置となる前記絶縁テープにおいて、前記半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、前記半導体装置の外形サイズに関与しない前記絶縁テープの無形領域を削減している。

【0032】

また、本発明のCOF、又はTCP半導体装置の製造方法は、以上のように、前記半導体素子の実装、樹脂封止、テスト、他、アセンブリ工程での搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定した前記半導体装置を製造する方法である。

【0033】

また、本発明のCOF、又はTCP半導体装置の製造方法は、前記半導体素子の実装、樹脂封止、テスト、他、アセンブリ工程において、前記半導体装置を複数個 同時に処理し、前記半導体装置の製品処理ピッチを整数倍とする製造方法でもある。

【0034】

また、本発明の半導体装置、又は半導体モジュール装置は、上記のCOF、又はTCP半導体装置用テープキャリア、または半導体装置の製造方法を用いて、製造されたものである。

【0035】

それゆえ、COF、又はTCP半導体装置用テープキャリアにおいて、半導体装置の製品外形に含まれない無形領域(不要領域)を削減でき、材料コストを約10%程度低減できる半導体装置用テープキャリア、半導体装置の製造方法、半導体装置、および半導体モジュール装置を提供することができるという効果を奏する。

【0036】

即ち、前記COF、又はTCP半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、前記COF、又はTCP半導体装置の外形サイズに関与しない前記絶縁テープの無形領域(不要領域)を削減していること、前記半導体素子のアセンブリ工程での搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定した前記COF、又はTCP半導体装置を製造していること、製造設備の搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施していること、必要に応じて、ソフトや搬送機構を変更していること、前記半導体素子のアセンブリ工程が、前記COF、又はTCP半導体装置を複数個同時に処理し、前記COF、又はTCP半導体装置の製品処理ピッチが整数倍となっていること、処理機構を複数個 保有している製造設備を使用して、複数個を同時に処理していること、前記COF、又はTCP半導体装置の前記絶縁テープからの打ち抜き工程が、前記COF、又はTCP半導体装置を複数個同時に打ち抜き、前記COF、又はTCP半導体装置の製品打ち抜きの外形、及び搬送ピッチが整数倍となっていることによって、本発明によるCOF、又はTCP半導体装置用テープキャリア、及び半導体装置の製造方法は、従来のCOF、又はTCP半導体装置用テープキャリア、及び半導体装置の製造方法と比較して、前記COF、又はTCPの製品外形に含まれない無形領域(不要領域)を削減することが可能となり、材料コストを約10%程度低減できる。

【発明を実施するための最良の形態】

【0037】

〔実施の形態1〕

図1〜図4に本発明でのCOF、TCP用テープキャリア、及び半導体装置の実施の形態を示し、図5〜図8にCOF、TCP半導体装置、及びモジュールの断面図を示す。

【0038】

本COFに使用されるテープキャリア100は、自由に折り曲げることが可能な柔軟性の高い厚さ15〜40μmの薄膜のポリイミド系の絶縁テープ1を基材とし、絶縁テープ1の表面に厚さ8〜18μmの銅箔又はスパッタ銅(配線パターン)がキャスティング法、スパッタ法(メタライジング法)、等により形成されている。

【0039】

本TCPに使用されるテープキャリア200は、ポリイミドから成る絶縁テープ1上に、接着剤18を用いて銅箔をラミネートして形成しており、絶縁テープ1の半導体素子21が搭載される部分にあらかじめ貫通した開口部16が開けられ、配線パターン11が片持ち梁状に突き出した状態である為、配線パターン11の厚みは18μm以上を使用しており、液晶パネル等への実装後の折り曲げ部分にはあらかじめスリット17が設けられている。

【0040】

COF、TCP共に、配線パターン11の表面には、錫メッキや金メッキが施されている。配線パターン11と半導体素子21との接続部、及び外部接続用コネクタ部12以外のパターン露出部には、ソルダーレジスト13が塗布され、絶縁状態が確保される。半導体素子21が搭載される搭載領域15にはソルダーレジスト13は塗布されず、ソルダーレジスト開口部14が形成されている。尚、図中には、メッキは記載していない。

【0041】

COF、TCP共に、多くの場合は、薄膜の絶縁テープ1にスプロケットホール2と呼ばれる搬送用の開口が4.75mm間隔で設置されており、通常、製品の外形に連動したテープピッチはスプロケットホール2の整数倍のピッチで設計されている。各工程の製造設備内では、スプロケットホール2を使用して1ピッチずつ搬送され、1工程(1デバイスの処理・搬送)では、製品の外形ピッチ(整数倍)分が搬送される。

【0042】

半導体素子21には、バンプ23と呼ばれる突起電極が形成されており、絶縁テープ1の表面上に形成されている(COF)、又は絶縁テープ1の半導体素子21が搭載される部分にあらかじめ貫通した開口部16が開けられ、配線パターン11が片持ち梁状に突き出した状態である(TCP)配線パターン11に接合・搭載され、配線パターン11の各配線が半導体素子21の対応する端子のバンプ23と電気的に接続される。半導体素子21が接合・搭載された後に半導体素子21とテープキャリア100または200に出来る隙間(COF)、又は半導体素子21の表面(TCP)は、樹脂22が注入(COF)、又は塗布(TCP)され封止される。配線パターン11の外部接続用コネクタ部12には、液晶パネル24やプリント基板25などが接続される。

【0043】

本発明のCOF、及びTCP用のテープキャリア(100、200)は、配線パターン11と半導体素子21とを電気的に接続し、絶縁性の樹脂22で封止することでCOF、又はTCP半導体装置となる絶縁テープ1の搬送方向におけるCOF、又はTCP半導体装置の外形サイズが、絶縁テープ1を搬送する為に開口されたスプロケットホール2のピッチ間隔(4.75mm)の整数倍4ピッチより大きく、尚かつ整数倍4+1/2ピッチ(ハーフピッチ)以下であり、通常はテープピッチを整数倍4+1=5ピッチに設定するCOF、又はTCP半導体装置となる絶縁テープ1において、COF、又はTCP半導体装置のテープピッチを整数倍4+1/2=4.5ピッチに設定し、COF、又はTCP半導体装置の外形サイズに関与しない絶縁テープ1の無形領域(不要領域)を削減し、材料コストを低減している。

【0044】

図15〜図18に従来のCOF、及びTCP用のテープキャリア(500、600)を示す。

【0045】

従来のCOF、及びTCP用のテープキャリア(500、600)では、絶縁テープ501の搬送方向におけるCOF、又はTCP半導体装置の外形サイズが、絶縁テープ501を搬送する為に開口されたスプロケットホール502のピッチ間隔(4.75mm)の整数倍4ピッチより大きく、尚かつ整数倍4+1/2ピッチ(ハーフピッチ)以下の場合でも、テープピッチを整数倍4+1=5ピッチに設定されており、COF、又はTCP半導体装置の外形サイズに関与しない絶縁テープ501の無形領域(不要領域)503が存在している為、材料コスト、加工費、製造工程の能力、等に無駄が生じている。

【0046】

本発明を実施したCOF、及びTCP用のテープキャリア(100、200)では、COF、又はTCP半導体装置の外形サイズに関与しない絶縁テープ1の無形領域(不要領域)を削減していることによって、従来のCOF、又はTCP半導体装置用のテープキャリア(500、600)と比較して、COF、又はTCPのテープピッチ拡大による材料費、加工費の増加、製造能力の低下という問題点の解決が可能となり、COF、又はTCP半導体装置用のテープキャリアの材料コストを従来(平均的には5ピッチ)の約90%に低減できる。

【0047】

図19に別の従来例として、COF用のテープキャリア700を示す。

【0048】

従来のCOF用のテープキャリア700では、外部接続用コネクタ部512の向きを向かい合わせることによって無形領域503を削減し、使用するテープキャリア700のテープピッチを削減することができた。しかしながら、さまざまな形状のCOFに対しては、常に外部接続用コネクタ部512を向かい合わせることで使用するテープキャリア700のテープピッチを最小化することができるとは限らず、COFの形状に合わせてテープキャリア700に配置する向きを設計する必要がある。

【0049】

また、上記のように製品の配置方向を複数の方向に配置しているため、各製造工程ではテープキャリア700への部品の実装方向をCOFの配置方向に合わせて切り替える必要がある。このため、テープキャリア700のテープピッチを削減することと、製造工程を簡略化することとを考慮して設計をおこなう必要がある。

【0050】

本発明では、上記の従来例のように、COFの形状に合わせてテープキャリアに配置する向きを設計する必要がない。

【0051】

〔実施の形態2〕

図9、図10に本発明でのCOF用のテープキャリア100、及び半導体装置の実施の形態を示す。

【0052】

本発明を実施したCOF用のテープキャリア100では、絶縁テープ1の搬送方向におけるCOF半導体装置の外形サイズが、絶縁テープ1を搬送する為に開口されたスプロケットホール2のピッチ間隔(4.75mm)の整数倍4ピッチより大きく、尚かつ整数倍4+1/4ピッチ以下であり、通常はテープピッチを整数倍4+1=5ピッチに設定するCOF半導体装置となる絶縁テープ1において、COF半導体装置のテープピッチを整数倍4+1/4=4.25ピッチに設定し、COF半導体装置の外形サイズに関与しない絶縁テープ1の無形領域(不要領域)を削減していることによって、従来のCOF、又はTCP半導体装置用のテープキャリア(500,600)と比較して、COFのテープピッチ拡大による材料費、加工費の増加、製造能力の低下という問題点の解決が可能となり、COF半導体装置用のテープキャリア100の材料コストを従来(平均的には5ピッチ)の約85%に低減できる。

【0053】

〔実施の形態3〕

図11に本発明のCOF半導体装置の実施の形態を示す。

【0054】

絶縁テープ1の搬送方向におけるCOF半導体装置の外形サイズを配線パターン11の設計面で縮小した場合の実施の形態を示す。本実施の形態においても実施の形態1と同様に、1/2ピッチ(ハーフピッチ)化を同時に行い、COF半導体装置のテープピッチを整数倍3+1/2=3.5ピッチに設定している。

【0055】

設計面での外形サイズ縮小の方法としては、配線パターン間のピッチ縮小、配線パターンの引き回し変更、ユーザ外形仕様の変更、等がある。

【0056】

本実施の形態のCOF用のテープキャリア100では、実施の形態1のCOF用のテープキャリア100を超える効果(約70%に低減)を得ることができる。

【0057】

〔実施の形態4〕

図12に本発明のCOF半導体装置の実施の形態を示す。

【0058】

実施の形態3と同様に、絶縁テープ1の搬送方向におけるCOF半導体装置の外形サイズを配線パターン11の設計面で縮小した場合の実施の形態を示す。本実施の形態においては、実施の形態3よりもCOF半導体装置の外形サイズの配線パターン設計面での縮小が大きく、実施の形態1、及び実施の形態3と同様に、1/2ピッチ(ハーフピッチ)化も同時に行い、COF半導体装置のテープピッチを整数倍2+1/2=2.5ピッチに設定している。

【0059】

本実施の形態のCOF用のテープキャリア100では、実施の形態1、及び実施の形態3のCOF用のテープキャリア100を超える効果(約50%に低減)を得ることができる。

【0060】

〔実施の形態5〕

図13に本発明のCOF半導体装置の実施の形態として製造工程(半導体素子実装工程)を示す。

【0061】

従来のCOF半導体装置の製造工程では、図20に示すように、製造装置の搬送ピッチが1ピッチで実施され、テープピッチを整数倍に設定したCOF半導体装置を製造していた。この時、1デバイスの製品処理のピッチは、例えば1ピッチ×5=5ピッチとなっている。

【0062】

本発明のCOF半導体装置の製造工程(半導体素子実装工程)では、ソフトや搬送機構を変更していることで、製造装置の搬送ピッチを1/2ピッチ(ハーフピッチ)で実施し、テープピッチを整数倍4+1/2ピッチ=4.5ピッチに設定したCOF半導体装置を製造している。この時、1デバイスの製品処理のピッチは、例えば0.5ピッチ×9=4.5ピッチとなっている。

【0063】

すなわち、本実施の形態の半導体装置用テープキャリアにおける1デバイスのテープピッチは、スプロケットホールのピッチ間隔の整数倍X+小数Y=4+0.5=4.5ピッチであり、半導体装置の製造工程(半導体素子実装工程)における1デバイスの製品処理ピッチも同じ4.5ピッチとなるが、製造工程における搬送ピッチである小数Z(0<Z<1、Z=0.05の整数倍)は、いくつかのピッチが考えられ、例えば0.05×5=0.25ピッチ、0.05×10=0.5ピッチ、0.05×30=1.5ピッチ、等で搬送することができる。

【0064】

本実施の形態のCOF半導体装置の製造工程(半導体素子実装工程)は、実施の形態1のCOF用のテープキャリア100を使用した製造工程を示しているが、実施の形態3、及び実施の形態4においても同様の製造工程(半導体素子実装工程)によって製造することが可能である。

【0065】

〔実施の形態6〕

図14に本発明のCOF半導体装置の実施の形態として製造工程(半導体装置打ち抜き工程)を示す。

【0066】

従来のCOF半導体装置の製造工程では、図21に示すように、COF半導体装置の絶縁テープ1からの打ち抜き工程において、COF半導体装置を1デバイスずつ打ち抜いていた。

【0067】

本発明のCOF半導体素子の製造工程では、COF半導体装置を複数個同時に処理することで、COF半導体装置の製品処理ピッチを整数倍としている。COF半導体装置の絶縁テープ1からの打ち抜き工程において、COF半導体装置を複数個(2個)同時に打ち抜き、COF半導体装置の製品打ち抜きの処理ピッチをスプロケットホール2のピッチ間隔(4.75mm)の整数倍(9ピッチ)としている。

【0068】

本実施の形態のCOF半導体装置の製造工程(半導体装置打ち抜き工程)は、実施の形態1のCOF用のテープキャリア100を使用した製造工程を示しているが、実施の形態3、及び実施の形態4においても同様の製造工程によって製造することが可能である。

【0069】

以上のように、テープピッチの小数ピッチ化は、製品外形サイズがスプロケットホールの整数倍Xピッチ(X=1,2,3,4,5,・・・)より大きく、尚かつ整数倍X+小数Yピッチ(0<Y<1)以下である場合(通常、テープピッチを整数倍X+1ピッチに設定している)には、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に縮小することが可能であり、例えば4ピッチ+1/2ピッチ(ハーフピッチ)の場合には、通常は4+1=5ピッチに設定しているが、4+0.5=4.5ピッチに縮小することが可能であり、10%の縮小が容易となってくる。勿論、製品外形サイズの縮小も可能な場合には更なる縮小が可能となる。

【0070】

しかし、COF、又はTCPの製造工程や製品の打ち抜き工程も、製品ピッチ、すなわち整数倍X+小数Yピッチ(0<Y<1)で対応する必要があるが、製造設備の搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施できるように、例えば4+0.5=4.5ピッチの場合は、搬送ピッチを0.5ピッチで実施できるように、製造設備のソフトや搬送機構を変更すること、絶縁テープからの製品打ち抜き工程では、複数個を同時に打ち抜くことで、容易に対応することが可能となる。

【0071】

すなわち、本発明によるCOF、又はTCP半導体装置用テープキャリア、及び半導体装置の製造方法は、上記の課題を解決する為に、表面に複数配置した配線パターンと半導体素子の突起電極とを電気的に接続し、絶縁性の樹脂で封止することでCOF、又はTCP半導体装置となる薄膜の絶縁テープであり、前記絶縁テープの搬送方向における前記COF、又はTCP半導体装置の外形サイズが、前記絶縁テープを搬送する為に開口されたスプロケットホールのピッチ間隔(4.75mm)の整数倍Xより大きく、尚かつ整数倍X+小数Yピッチ(0<Y<1)以下であり、通常はテープピッチを整数倍X+1ピッチに設定する前記COF、又はTCP半導体装置となる前記絶縁テープにおいて、前記COF、又はTCP半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、前記COF、又はTCP半導体装置の外形サイズに関与しない前記絶縁テープの無形領域(不要領域)を削減している。また、前記半導体素子のアセンブリ工程での搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定した前記COF、又はTCP半導体装置を製造していること、製造設備の搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施できるように、ソフトや搬送機構を変更していること、前記半導体素子のアセンブリ工程が、前記COF、又はTCP半導体装置を複数個 同時に処理し、前記COF、又はTCP半導体装置の製品処理ピッチが整数倍となっていること、処理機構を複数個 保有している製造設備を使用して、複数個を同時に処理していること、前記COF、又はTCP半導体装置の前記絶縁テープからの打ち抜き工程が、前記COF、又はTCP半導体装置を複数個 同時に打ち抜き、前記COF、又はTCP半導体装置の製品打ち抜き処理ピッチが整数倍となっていることで、前記COF、又はTCPの製品外形に含まれない無形領域(不要領域)を削減し、材料コストを低減したことを特徴としている。

【0072】

また、本発明によるCOF、又はTCP半導体装置用テープキャリア、及び半導体装置の製造方法と従来のCOF、又はTCP半導体装置用テープキャリア、及び半導体装置の製造方法との違いは、前記COF、又はTCP半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、前記COF、又はTCP半導体装置の外形サイズに関与しない前記絶縁テープの無形領域(不要領域)を削減していること、前記半導体素子のアセンブリ工程での搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定した前記COF、又はTCP半導体装置を製造していること、製造設備の搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施できるように、ソフトや搬送機構を変更していること、前記半導体素子のアセンブリ工程が、前記COF、又はTCP半導体装置を複数個 同時に処理し、前記COF、又はTCP半導体装置の製品処理ピッチが整数倍となっていること、処理機構を複数個 保有している製造設備を使用して、複数個を同時に処理していること、前記COF、又はTCP半導体装置の前記絶縁テープからの打ち抜き工程が、前記COF、又はTCP半導体装置を複数個 同時に打ち抜き、前記COF、又はTCP半導体装置の製品打ち抜きの処理ピッチが整数倍となっていることのみであり、一部、ソフトや搬送機構の変更は必要となるものの、従来の製造設備・手法での製造が可能である。

【0073】

これによって、前記COF、又はTCP半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、前記COF、又はTCP半導体装置の外形サイズに関与しない前記絶縁テープの無形領域(不要領域)を削減していること、前記半導体素子のアセンブリ工程での搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定した前記COF、又はTCP半導体装置を製造していること、製造設備の搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施できるように、ソフトや搬送機構を変更していること、前記半導体素子のアセンブリ工程が、前記COF、又はTCP半導体装置を複数個同時に処理し、前記COF、又はTCP半導体装置の製品処理ピッチが整数倍となっていること、処理機構を複数個 保有している製造設備を使用して、複数個を同時に処理していること、前記COF、又はTCP半導体装置の前記絶縁テープからの打ち抜き工程が、前記COF、又はTCP半導体装置を複数個 同時に打ち抜き、前記COF、又はTCP半導体装置の製品打ち抜きの処理ピッチが整数倍となっていることによって、本発明によるCOF、又はTCP半導体装置用テープキャリア、及び半導体装置の製造方法は、従来のCOF、又はTCP半導体装置用テープキャリア、及び半導体装置の製造方法と比較して、前記COF、又はTCPの製品外形に含まれない無形領域(不要領域)を削減することが可能となり、材料コストを約10%程度低減できる。

【産業上の利用可能性】

【0074】

以上のように、本発明では、フレキシブル配線基板上に半導体素子が接合・搭載された半導体装置の製造方法において、半導体装置の外形サイズにあわせて半導体装置のテープピッチを整数倍X+小数Yピッチ(0<Y<1)とすることができ、半導体装置の外形サイズに関与しない絶縁テープの無形領域を削減することができる。そのため、本発明は、COF半導体装置やTCP半導体装置に代表されるテープ状の材料から形成される半導体装置やその部品を製造する分野に利用することができるだけでなく、さらには、ロール状に形成されている材料から定められた長さの製品を製造することに関わる分野に広く応用することが可能である。

【図面の簡単な説明】

【0075】

【図1】本発明の実施の形態として、COF半導体装置用テープキャリア(半導体素子実装前)を示す平面図である。

【図2】本発明の実施の形態として、図1の半導体素子実装後(半導体装置)を示す平面図である。

【図3】図1、図2とは異なる本発明の実施の形態として、TCP半導体装置用テープキャリア(半導体素子実装前)を示す平面図である。

【図4】図1、図2とは異なる本発明の実施の形態として、図3の半導体素子実装後(半導体装置)を示す平面図である。

【図5】本発明の実施の形態として、図1、図2の実施の形態によるCOF半導体装置を示す断面図である。

【図6】本発明の実施の形態として、図3、図4の実施の形態によるTCP半導体装置を示す断面図である。

【図7】本発明の実施の形態として、図5の実施の形態による半導体モジュール装置を示す断面図である。

【図8】本発明の実施の形態として、図6の実施の形態による半導体モジュール装置を示す断面図である。

【図9】図1〜図4とは異なる本発明の実施の形態として、COF半導体装置用テープキャリア(半導体素子実装前)を示す平面図である。

【図10】図1〜図4とは異なる本発明の実施の形態として、図9の半導体素子実装後(半導体装置)を示す平面図である。

【図11】図1〜図4、図9、図10とは異なる本発明の実施の形態として、COF半導体装置を示す平面図である。

【図12】図1〜図4、図9〜図11とは異なる本発明の実施の形態として、COF半導体装置を示す平面図である。

【図13】本発明の実施の形態として、半導体素子の実装工程を示す平面図である。

【図14】本発明の実施の形態として、COF半導体装置の打ち抜き工程を示す平面図である。

【図15】従来例のCOF半導体装置用テープキャリア(半導体素子実装前)を示す平面図である。

【図16】従来例のCOF半導体装置を示す平面図である。

【図17】従来例のTCP半導体装置用テープキャリア(半導体素子実装前)を示す平面図である。

【図18】従来例のTCP半導体装置を示す平面図である。

【図19】図15〜図18とは異なる従来例のCOF半導体装置用テープキャリア(半導体素子実装前)を示す平面図である。

【図20】従来例の半導体素子実装工程を示す平面図である。

【図21】従来例のCOF半導体装置打ち抜き工程を示す平面図である。

【符号の説明】

【0076】

1,501 絶縁テープ

2,502 スプロケットホール

11、511 配線パターン

12、512 外部接続用コネクタ部

13、513 ソルダーレジスト

14、514 ソルダーレジスト開口部

15、515 搭載領域

16、516 開口部

17、517 スリット

18、 接着剤

21、521 半導体素子

22、522 樹脂(絶縁性樹脂)

23 バンプ(突起電極)

24 液晶パネル

25 プリント基板

100 テープキャリア(半導体装置用テープキャリア)

200 テープキャリア(半導体装置用テープキャリア)

500 テープキャリア(半導体装置用テープキャリア)

503 無形領域(不要領域)

600 テープキャリア(半導体装置用テープキャリア)

700 テープキャリア(半導体装置用テープキャリア)

【特許請求の範囲】

【請求項1】

表面に複数配置した配線パターンと半導体素子の突起電極とを電気的に接続し、絶縁性樹脂で封止することで半導体装置となる薄膜の絶縁テープからなる半導体装置用テープキャリアであって、

前記絶縁テープの搬送方向における前記半導体装置の外形サイズが、

前記絶縁テープを搬送する為に開口されたスプロケットホールのピッチ間隔の整数倍Xピッチ(X=1,2,3,4,5,・・・)より大きく、尚かつ整数倍X+小数Yピッチ(0<Y<1)以下であり、

前記半導体装置1デバイスのテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、前記半導体装置の外形サイズに関与しない前記絶縁テープの無形領域を削減していることを特徴とする半導体装置用テープキャリア。

【請求項2】

前記半導体装置がCOFまたはTCPであることを特徴とする請求項1に記載の半導体装置用テープキャリア。

【請求項3】

前記絶縁テープの搬送方向における前記半導体装置の外形サイズを前記配線パターンの設計面で縮小した場合において、

小数Yピッチ(0<Y<1)化を同時に行い、前記COF、又はTCP半導体装置用テープキャリアのテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定していることを特徴とする請求項1または2に記載の半導体装置用テープキャリア。

【請求項4】

小数Yが、0.05の整数倍(1,2,3,4,5,・・・)であることを特徴とする請求項1〜3の何れか1項に記載の半導体装置用テープキャリア。

【請求項5】

前記半導体素子の実装、樹脂封止、テスト、他、アセンブリ工程での搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定した前記半導体装置を製造していることを特徴とする請求項1〜4の何れか1項に記載の半導体装置の製造方法。

【請求項6】

製造設備の搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施できるように、ソフトや搬送機構を変更していることを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記半導体素子の実装、樹脂封止、テスト、他、アセンブリ工程が、

前記半導体装置を複数個 同時に処理し、前記半導体装置の製品処理ピッチが整数倍となっていることを特徴とする請求項1〜4の何れか1項に記載の半導体装置の製造方法。

【請求項8】

前記半導体装置を処理する処理機構を複数個保有している製造設備を使用して、複数個の半導体装置を同時に処理していることを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記半導体装置の前記絶縁テープからの打ち抜き工程が、前記半導体装置を複数個同時に打ち抜く工程であり、

前記半導体装置の製品打ち抜きの外形、及び搬送ピッチが前記スプロケットホールの前記ピッチ間隔の整数倍となっていることを特徴とする請求項1〜8の何れか1項に記載の半導体装置の製造方法。

【請求項10】

1セットの打ち抜き金型によって、複数個の前記半導体装置を同時に打ち抜いていることを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

請求項1〜4の何れか1項に記載の半導体装置用テープキャリア、または請求項5〜10の何れか1項に記載の半導体装置の製造方法を用いて、製造された半導体装置。

【請求項12】

請求項11に記載の半導体装置を用いて製造された半導体モジュール装置。

【請求項1】

表面に複数配置した配線パターンと半導体素子の突起電極とを電気的に接続し、絶縁性樹脂で封止することで半導体装置となる薄膜の絶縁テープからなる半導体装置用テープキャリアであって、

前記絶縁テープの搬送方向における前記半導体装置の外形サイズが、

前記絶縁テープを搬送する為に開口されたスプロケットホールのピッチ間隔の整数倍Xピッチ(X=1,2,3,4,5,・・・)より大きく、尚かつ整数倍X+小数Yピッチ(0<Y<1)以下であり、

前記半導体装置1デバイスのテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定し、前記半導体装置の外形サイズに関与しない前記絶縁テープの無形領域を削減していることを特徴とする半導体装置用テープキャリア。

【請求項2】

前記半導体装置がCOFまたはTCPであることを特徴とする請求項1に記載の半導体装置用テープキャリア。

【請求項3】

前記絶縁テープの搬送方向における前記半導体装置の外形サイズを前記配線パターンの設計面で縮小した場合において、

小数Yピッチ(0<Y<1)化を同時に行い、前記COF、又はTCP半導体装置用テープキャリアのテープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定していることを特徴とする請求項1または2に記載の半導体装置用テープキャリア。

【請求項4】

小数Yが、0.05の整数倍(1,2,3,4,5,・・・)であることを特徴とする請求項1〜3の何れか1項に記載の半導体装置用テープキャリア。

【請求項5】

前記半導体素子の実装、樹脂封止、テスト、他、アセンブリ工程での搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施し、テープピッチを整数倍X+小数Yピッチ(0<Y<1)に設定した前記半導体装置を製造していることを特徴とする請求項1〜4の何れか1項に記載の半導体装置の製造方法。

【請求項6】

製造設備の搬送ピッチを小数Zピッチ(0<Z<1、Z=0.05の整数倍)で実施できるように、ソフトや搬送機構を変更していることを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記半導体素子の実装、樹脂封止、テスト、他、アセンブリ工程が、

前記半導体装置を複数個 同時に処理し、前記半導体装置の製品処理ピッチが整数倍となっていることを特徴とする請求項1〜4の何れか1項に記載の半導体装置の製造方法。

【請求項8】

前記半導体装置を処理する処理機構を複数個保有している製造設備を使用して、複数個の半導体装置を同時に処理していることを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記半導体装置の前記絶縁テープからの打ち抜き工程が、前記半導体装置を複数個同時に打ち抜く工程であり、

前記半導体装置の製品打ち抜きの外形、及び搬送ピッチが前記スプロケットホールの前記ピッチ間隔の整数倍となっていることを特徴とする請求項1〜8の何れか1項に記載の半導体装置の製造方法。

【請求項10】

1セットの打ち抜き金型によって、複数個の前記半導体装置を同時に打ち抜いていることを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

請求項1〜4の何れか1項に記載の半導体装置用テープキャリア、または請求項5〜10の何れか1項に記載の半導体装置の製造方法を用いて、製造された半導体装置。

【請求項12】

請求項11に記載の半導体装置を用いて製造された半導体モジュール装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2008−66605(P2008−66605A)

【公開日】平成20年3月21日(2008.3.21)

【国際特許分類】

【出願番号】特願2006−244782(P2006−244782)

【出願日】平成18年9月8日(2006.9.8)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成20年3月21日(2008.3.21)

【国際特許分類】

【出願日】平成18年9月8日(2006.9.8)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]