半導体装置

【課題】 消費電力が小さく、かつ動作速度が速い半導体装置を提供する。

【解決手段】 DRAMコアセルのリードゲート1は、各々のゲートがそれぞれノードN1,N2を介してビット線BL,/BLに接続されるNチャネルMOSトランジスタ61,63と、各々のゲートがともに列選択信号CSLRを受けるNチャネルMOSトランジスタ2,3とを含み、MOSトランジスタ2,3のゲート酸化膜はMOSトランジスタ61,63のゲート酸化膜よりも薄い。したがって、列選択信号CSLRの振幅電圧の低電圧化を図ることができる。

【解決手段】 DRAMコアセルのリードゲート1は、各々のゲートがそれぞれノードN1,N2を介してビット線BL,/BLに接続されるNチャネルMOSトランジスタ61,63と、各々のゲートがともに列選択信号CSLRを受けるNチャネルMOSトランジスタ2,3とを含み、MOSトランジスタ2,3のゲート酸化膜はMOSトランジスタ61,63のゲート酸化膜よりも薄い。したがって、列選択信号CSLRの振幅電圧の低電圧化を図ることができる。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】この発明は半導体装置に関し、特に、第1および第2の信号線と、それらを接続するためのMOSトランジスタとを備えた半導体装置に関する。

【0002】

【従来の技術】従来より、DRAMコアセルとロジック回路が混載されたシステムLSIが開発されている。DRAMコアセルとロジック回路の間では、データ転送速度の向上を図るため、同時に数百ビットのデータの入出力が可能となっている。また、複数ビットごとに1ビットのライトマスク信号の入力端子が設けられており、このライトマスク信号を制御することにより対応の複数ビットのメモリセルのデータの書換えを禁止することが可能となっている。

【0003】図12は、そのようなDRAMコアセル30の全体構成を示すブロック図である。図12において、このDRAMコアセル30は、行/列アドレスバッファ+クロック発生回路31、行/列デコード回路32、メモリマット33およびデータ入出力回路34を備える。このDRAMコアセル30では、同時に8kビット(ただし、kは1以上の整数である)のデータDQ1〜8kの入出力が可能となっており、8ビットのデータごとに1ビットのライトマスク信号WMの入力端子が設けられている。

【0004】行/列アドレスバッファ+クロック発生回路31は、外部アドレス信号A0〜Am(ただし、mは0以上の整数である)および外部制御信号/RAS,/CAS,/WEに従って、行アドレス信号RA0〜RAm、列アドレス信号CA0〜CAm、リードクロック信号CLKRおよびライトクロック信号CLKWなどを生成し、DRAMコアセル30全体を制御する。

【0005】メモリマット33は、複数(図では3つ)のセンスアンプ帯SA1〜SA3と、それらの間に配置されたメモリセルアレイMA1,MA2とを含む。メモリセルアレイMA1,MA2は、それぞれが1ビットのデータを記憶する複数のメモリセルを含む。複数のメモリセルは、予め定められた数8kずつグループ化されている。各メモリセルグループは、行アドレスおよび列アドレスによって決定される所定のアドレスに配置される。

【0006】行/列デコード回路32は、行/列アドレスバッファ+クロック発生回路31から与えられる行アドレス信号RA0〜RAmおよび列アドレス信号CA0〜CAmに従って、メモリセルアレイMA1,MA2のアドレスを指定する。センスアンプ帯SA1,SA2には、後述するセンスアンプ+入出力制御回路群が設けられている。センスアンプ+入出力制御回路群は、行/列デコード回路32によって指定されたアドレスの8k個のメモリセルをデータ入出力回路34に接続する。データ入出力回路34は、ライトドライバ+リードアンプ帯35および入出力バッファ群36を含む。ライトドライバ+リードアンプ帯35には、ライトドライバ群およびリードアンプ群が設けられている。

【0007】リードアンプ群は、リードクロック信号CLKRに同期して動作し、選択された8k個のメモリセルからの読出データQ1〜Q8kを入出力バッファ群36に与える。入出力バッファ群36は、外部制御信号/OEに応答してリードアンプ群からの読出データQ1〜Q8kを外部に出力する。ライトドライバ群は、ライトクロック信号CLKWに同期して動作し、外部からの書込データD1〜D8kを選択された8k個のメモリセルに書込む。ただし、8k個のメモリセルのうちライトマスク信号WM1〜WMkによって指定されたメモリセルにはデータは書込まれない。

【0008】メモリセルアレイMA1,MA2の各々は、それぞれがデータDQ1〜DQ8kに対応して設けられた8k個のメモリブロックMBを含む。各メモリブロックMBは、図13に示すように、複数行複数列に配置された複数のメモリセルMCと、それぞれ複数行に対応して設けられた複数のワード線WLと、それぞれ複数列に対応して設けられた複数組のビット線対BL,/BLとを含む。メモリセルMCは、アクセス用のNチャネルMOSトランジスタQと情報記憶用のキャパシタCとを含む周知のものである。

【0009】行/列デコード回路32によって行アドレス信号RA0〜RAmに対応するワード線WLが選択レベルの「H」レベルにされると、ワード線WLに対応する行のメモリセルMCのNチャネルMOSトランジスタQが導通し、メモリセルMCのデータの書込/読出が可能となる。書込動作時は、1本のワード線WLを選択レベルの「H」レベルにしてメモリセルMCを活性化させた後、書込データDに従って1組のビット線対BL,/BLのうちの一方のビット線を「H」レベルにし他方のビット線を「L」レベルにする。これにより、ビット線の電位が所望のメモリセルMCのキャパシタCに書込まれる。読出動作時は、ビット線対BL,/BLの電位をVBL(=VCC/2)にイコライズした後、1本のワード線WLを選択レベルの「H」レベルにしてメモリセルMCを活性化させる。これにより、各ビット線対BL,/BL間にメモリセルMCの記憶データに応じた微小電位差が生じる。各ビット線対間の微小電位差を電源電圧Vddsに増幅した後、1組のビット線対の電位差を検出することにより所望のメモリセルMCのデータを読出すことができる。8k個のメモリブロックMBは、ワード線WLの延在する方向に配列されており、ワード線WLは8k個のメモリブロックMBで共用されている。

【0010】図14は、データDQ1の書込/読出に関連する部分の構成を示す回路ブロック図である。図14において、データD1の書込を行なうためのライトドライバ37およびライトデータ線対GIOW,/GIOWと、データQ1の読出を行なうためのリードアンプ38およびリードデータ線対GIOR,/GIORとが設けられる。

【0011】ライトドライバ37は、図12で示したライトドライバ+リードアンプ帯35に配置され、書込動作時に書込データD1に従ってライトデータ線GIOW,/GIOWのうちの一方を「H」レベルにし他方を「L」レベルにする。リードアンプ38は、ライトドライバ+リードアンプ帯35に配置され、読出動作時にリードデータ線対GIOR,/GIOR間の電位差を検出して読出データQ1を生成し、出力バッファを介して外部に出力する。

【0012】ライトデータ線対GIOW,/GIOWは、図2で示したメモリアレイMA1,MA2およびセンスアンプ帯SA1〜SA3を横切るように配置され、その一方端はライトドライバ37に接続される。リードデータ線対GIOR,/GIORは、メモリアレイMA1,MA2およびセンスアンプ帯SA1〜SA3を横切るように配置され、その一方端はリードアンプ38に接続される。

【0013】メモリセルアレイMA1のメモリブロックMBに含まれる1組のビット線対BL1,/BL1と、メモリセルアレイMA2のメモリブロックMBに含まれる1組のビット線対BL2,/BL2とに共通にセンスアンプ+入出力制御回路40が設けられる。センスアンプ+入出力制御回路40は、メモリセルアレイMA1,MA2のたとえば各奇数番のビット線対BL,/BLに対応して設けられ、センスアンプ帯SA2に配置される。なお、メモリアレイMA1,MA2の各偶数番のビット線対BL,/BL用のセンスアンプ+入出力制御回路は、それぞれセンスアンプ帯SA1,SA3に配置される。

【0014】センスアンプ+入出力制御回路40は、NチャネルMOSトランジスタ41〜44、イコライザ45,46、センスアンプ47、ライトゲート50およびリードゲート60を含む。NチャネルMOSトランジスタ41,42は、それぞれメモリセルアレイMA1のビット線BL1,/BL1とノードN1,N2との間に接続され、各々のゲートはともに信号SHR1を受ける。NチャネルMOSトランジスタ43,44は、それぞれメモリセルアレイMA2のビット線BL2,/BL2とノードN1,N2との間に接続され、各々のゲートはともに信号SHR2を受ける。信号SHR1が活性化レベルの「H」レベルになると、NチャネルMOSトランジスタ41,42が導通してセンスアンプ+入出力制御回路40はメモリセルアレイMA1のビット線対BL1,/BL1と結合される。信号SHR2が活性化レベルの「H」レベルになると、NチャネルMOSトランジスタ43,44が導通してセンスアンプ+入出力制御回路40はメモリセルアレイMA2のビット線対BL2,/BL2と結合される。

【0015】イコライザ45は、信号BLEQ1が活性化レベルの「H」レベルの場合に活性化され、メモリセルアレイMA1のビット線対BL1,/BL1の電位をビット線電位VBL(=Vdds/2)にイコライズする。イコライザ46は、信号BLEQ2が活性化レベルの「H」レベルの場合に活性化され、メモリセルアレイMA2のビット線対BL2,/BL2の電位をビット線電位VBLにイコライズする。センスアンプ47は、信号SE,/SEがそれぞれ活性化レベルの「H」レベルおよび「L」レベルになったことに応じて活性化され、NチャネルMOSトランジスタ41,42または43,44によってノードN1,N2に接続されたビット線対BL1,/BL1またはBL2,/BL2間の電位差を電源電圧Vddsに増幅する。

【0016】ライトゲート50は、NチャネルMOSトランジスタ51〜54を含む。NチャネルMOSトランジスタ51,52は、ライトデータ線GIOWとノードN1との間に直列接続され、各々のゲートがそれぞれ信号WM1,CSLWを受ける。NチャネルMOSトランジスタ53,54は、ライトデータ線/GIOWとノードN2との間に直列接続され、各々ゲートはそれぞれ信号WM1,CSLWを受ける。

【0017】列選択信号CSLWが選択レベルの「H」レベルになると、NチャネルMOSトランジスタ52,54が導通する。ライトマスク信号WM1が「L」レベルの場合は、NチャネルMOSトランジスタ51,53が非導通になってデータD1の書込が禁止される。ライトマスク信号WM1が「H」レベルの場合は、NチャネルMOSトランジスタ51,53が導通してデータD1の書込が許容される。

【0018】リードゲート60は、NチャネルMOSトランジスタ61〜64を含む。NチャネルMOSトランジスタ61,62は接地電位GNDのラインとリードデータ線/GIORとの間に直列接続され、NチャネルMOSトランジスタ63,64は接地電位GNDのラインとリードデータ線GIORとの間に直列接続される。NチャネルMOSトランジスタ61,63はゲートがそれぞれノードN1,N2に接続され、NチャネルMOSトランジスタ62,64のゲートがともに信号CSLRを受ける。

【0019】列選択信号CSLRが選択レベルの「H」レベルになると、NチャネルMOSトランジスタ62,64が導通する。ノードN1,N2がそれぞれ「H」レベルおよび「L」レベルの場合は、NチャネルMOSトランジスタ61が導通するとともにNチャネルMOSトランジスタ63が非導通となり、「H」レベルにプリチャージされたリードデータ線GIOR,/GIORのうちのリードデータ線/GIORが接地される。ノードN1,N2がそれぞれ「L」レベルおよび「H」レベルの場合は、NチャネルMOSトランジスタ63が導通するとともにNチャネルMOSトランジスタ61が非導通となり、「H」レベルにプリチャージされたリードデータ線GIOR,/GIORのうちのリードデータ線GIORが接地される。

【0020】次に、図14で示したデータDQ1の書込/読出に関連する部分の動作について説明する。ここでは、メモリセルアレイMA1のビット線対BL1,/BL1が選択される場合について説明する。また、ライトマスク信号WM1は「H」レベルにされているものとする。

【0021】書込動作時は、まず信号SHR2が非活性化レベルの「L」レベルになってNチャネルMOSトランジスタ43,44が非導通になり、ノードN1,N2はメモリセルアレイMA2と切離される。また、ビット線イコライズ信号BLEQ1が非活性化レベルの「L」レベルになってイコライザ45が非活性化され、メモリセルアレイMA1のビット線対BL1,/BL1のイコライズが停止される。

【0022】次に、列アドレス信号CA0〜CAmに対応する列選択信号CSLWが選択レベルの「H」レベルにされてその列選択信号CSLWに対応するライトゲート50が導通し、ライトデータ線対GIOW,/GIOWがライトゲート50、ノードN1,N2、NチャネルMOSトランジスタ41,42を介してビット線対BL1,/BL1と結合される。また、ライトドライバ37は、書込データD1に従ってライトデータ線GIOW,/GIOWのうちの一方を「H」レベルにし他方を「L」レベルにする。

【0023】次いで、センスアンプ活性化信号SE,/SEがそれぞれ活性化レベルの「H」レベルおよび「L」レベルにされてセンスアンプ47が活性化され、センスアンプ47によってビット線対BL1,/BL1間の電位差が電源電圧Vddsに増幅される。また、行アドレス信号RA0〜RAmに対応するワード線WLが選択レベルの「H」レベルにされてそのワード線WLに対応するメモリセルMCが活性化され、ビット線BL1または/BL1の電位がそのメモリセルMCに書込まれる。

【0024】読出動作時は、まず信号SHR2が非活性化レベルの「L」レベルになってNチャネルMOSトランジスタ43,44が非導通になり、ノードN1,N2はメモリセルアレイMA2と切離される。また、ビット線イコライズ信号BLEQ1が非活性化レベルの「L」レベルになってイコライザ45が非活性化され、メモリセルアレイMA1のビット線対BL1,/BL1のイコライズが停止される。

【0025】次に、行アドレス信号RA0〜RAmに対応するワード線WLが選択レベルの「H」レベルにされてそのワード線WLに対応するメモリセルMCが活性化され、そのメモリセルMCの記憶データに応じてビット線対BL1,/BL1間に微小電位差が生じる。

【0026】次いで、センスアンプ活性化信号SE,/SEがそれぞれ活性化レベルの「H」レベルおよび「L」レベルにされ、センスアンプ47が活性化され、ビット線BL1,/BL1間の電位差が電源電圧Vddsに増幅される。すなわち、ビット線BL1,/BL1のうちプリチャージ電位Vdds/2よりも高い電位のビット線が電源電位Vddsにされ、他方のビット線が接地電位GNDにされる。これにより、リードゲート64のNチャネルMOSトランジスタ61,63のうちの一方が導通し他方が非導通になる。

【0027】次いで、列アドレス信号CA0〜CAmに対応する列選択信号CSLRが選択レベルの「H」レベルにされてその列選択信号CSLRに対応するリードゲート60のNチャネルMOSトランジスタ62,64が導通し、「H」レベルに予めプリチャージされたリードデータ線GIOR,/GIORのうちのいずれか一方がNチャネルMOSトランジスタ62,61または64,63を介して接地されて「L」レベルになる。リードアンプ38は、リードデータ線対GIOR,/GIORの電位差を検出し、検出結果に応じた論理のデータQ1を生成し、出力バッファを介して外部に出力する。

【0028】

【発明が解決しようとする課題】ところで従来は、ビット線BL,/BLの振幅電圧と、データ線GIOW,/GIOW,GIOR,/GIORの振幅電圧と、列選択信号CSLW,CSLRの振幅電圧とは同じ電圧であったので、ライトゲート50、リードゲート60およびセンスアンプ47のMOSトランジスタには同じ耐圧のMOSトランジスタすなわち同じ膜厚のゲート酸化膜を有するMOSトランジスタが用いられていた。

【0029】しかし、近年、DRAMコアセル30の周辺電源が低電圧化され、かつデータ線GIOW,/GIOW,GIOR,/GIORおよび列選択信号CSLW,CSLRの数が多くなってきているので、それらの振幅電圧を周辺電源電圧と同じにし、低消費電力化を図る必要がある。

【0030】しかし、単に列選択信号CSLW,CSLRの振幅電圧を小さくしただけでは、NチャネルMOSトランジスタ52,54,62,64に流れるソース−ドレイン間電流Idが小さくなって書込/読出動作が遅くなってしまう。

【0031】また、振幅電圧が小さな列選択信号CSLW,CSLRの振幅をレベル変換回路によって増幅する方法も考えられるが、レベル変換を行なうための時間が必要になって書込/読出動作が遅くなってしまう。

【0032】一方、メモリセルMCのキャパシタCにはできるだけ高い電圧を書込んでデータ保持時間を長くする必要があるので、センスアンプ47用の電源電圧Vddsを低くすることは好ましくない。したがって、ソース−ドレイン間電流Idを大きくするためにMOSトランジスタのゲート酸化膜を一律に薄くすると、センスアンプ47用の電源電圧VddsによってMOSトランジスタが破壊されてしまう。

【0033】それゆえに、この発明の主たる目的は、消費電流が小さく、かつ動作速度が速い半導体装置を提供することである。

【0034】

【課題を解決するための手段】この発明に係る半導体装置は、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線と、予め定められた第2の電位にプリチャージされる第2の信号線と、その入力電極が第1の信号線に接続され、第1の信号線の電位がそのしきい値電位を超えたことに応じて導通する第1のMOSトランジスタと、第1の信号線の信号が第2の信号線に伝達されることを許可する制御信号が入力されたことに応じて導通し、第1のMOSトランジスタを第2の信号線と基準電位のラインとの間に接続する第2のMOSトランジスタとを備え、第2のMOSトランジスタのゲート酸化膜は、第1のMOSトランジスタのゲート酸化膜よりも薄く形成されていることを特徴とするものである。

【0035】好ましくは、さらに、第1の信号線に与えられる信号の相補信号が与えられる第3の信号線と、第2の電位にプリチャージされる第4の信号線と、その入力電極が第3の信号線に接続され、第3の信号線の電位がそのしきい値電位を超えたことに応じて導通する第3のMOSトランジスタと、制御信号が入力されたことに応じて導通し、第3のMOSトランジスタを第4の信号線と基準電位のラインとの間に接続する第4のMOSトランジスタとを備え、第4のMOSトランジスタのゲート酸化膜は、第3のMOSトランジスタのゲート酸化膜よりも薄く形成されている。

【0036】また好ましくは、第1および第2のMOSトランジスタは、第2の信号線と基準電位のラインとの間に直列接続される。半導体装置は、さらに、第1の信号線に与えられる信号の相補信号が与えられる第3の信号線と、第2の電位にプリチャージされる第4の信号線と、その第1の電極が第4の信号線に接続され、その第2の電極が第1および第2のMOSトランジスタの間のノードに接続され、その入力電極が第3の信号線に接続され、第3の信号線の電位がそのしきい値電位を超えたことに応じて導通する第3のMOSトランジスタとを備え、第2のMOSトランジスタのゲート酸化膜は、第3のMOSトランジスタのゲート酸化膜よりも薄く形成されている。

【0037】また、この発明に係る他の半導体装置は、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線と、予め定められた第2の電位にプリチャージされる第2の信号線と、第2の信号線の電位と第2の電位との電位差を増幅し、その一方のレベルが第1の電位よりも高い第3の電位であり、その他方のレベルが基準電位である信号を第2の信号線に与えるセンスアンプと、その第1の電極が第1の信号線に接続され、第1の信号線の信号が第2の信号線に伝達されることを許可する第1の制御信号が入力されたことに応じて導通する第1のMOSトランジスタと、第1のMOSトランジスタの第2の電極と第2の信号線との間に接続され、第1の信号線の信号が第2の信号線に伝達されることを禁止するための第2の制御信号が入力されたことに応じて非導通になる第2のMOSトランジスタとを備え、第1のMOSトランジスタのゲート酸化膜は、第2のMOSトランジスタのゲート酸化膜よりも薄く形成されていることを特徴とするものである。

【0038】また、この発明に係るさらに他の半導体装置は、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線と、予め定められた第2の電位にプリチャージされる第2の信号線と、第2の信号線の電位と第2の電位との間の電位差を増幅し、その一方のレベルが第1の電位よりも高い第3の電位であり、その他方のレベルが基準電位である信号を第2の信号線に与えるセンスアンプと、その第1の電極が第1の信号線に接続され、第1の信号線の信号が第2の信号線に伝達されることを許可する制御信号が入力されたことに応じて導通する第1のMOSトランジスタと、第1のMOSトランジスタの第2の電極と第2の信号線との間に接続され、その入力電極が第3の電位を受けて導通する第2のMOSトランジスタとを備え、第1のMOSトランジスタのゲート酸化膜は、第2のMOSトランジスタのゲート酸化膜よりも薄く形成されていることを特徴とするものである。

【0039】好ましくは、各MOSトランジスタは、半導体基板の表面に形成されたゲート酸化膜および活性領域を含み、比較的厚いゲート酸化膜を有するMOSトランジスタの活性領域と比較的薄いゲート酸化膜を有するMOSトランジスタの活性領域とは、分離して形成されている。

【0040】

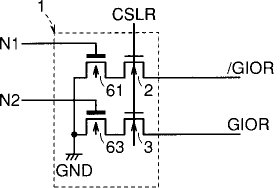

【発明の実施の形態】[実施の形態1]図1は、この発明の実施の形態1によるDRAMコアセルのリードゲート1の構成を示す回路図であって、図14のリードゲート60と対比される図である。

【0041】図1において、このリードゲート1が従来のリードゲート60と異なる点は、NチャネルMOSトランジスタ62,64がNチャネルMOSトランジスタ2,3で置換されている点である。NチャネルMOSトランジスタ2は、NチャネルMOSトランジスタ61のドレインとリードデータ線/GIORとの間に接続され、そのゲートが列選択信号CSLRを受ける。NチャネルMOSトランジスタ3は、NチャネルMOSトランジスタ63のドレインとリードデータ線GIORとの間に接続され、そのゲートが列選択信号CSLRを受ける。

【0042】列選択線CSLRの振幅電圧すなわち「H」レベルと「L」レベルの差の電圧は、周辺電源と同じ1.5Vである。リードデータ線GIOR,/GIORの振幅電圧は、周辺電源と同じ1.5Vである。ビット線BL,/BLの振幅電圧すなわちセンスアンプ47用の電圧Vddsは、2.0Vである。

【0043】NチャネルMOSトランジスタ61は、図2R>2(a)(b)に示すように、比較的大きな膜厚(たとえば7.5nm)のゲート酸化膜61aを有する。ゲート酸化膜61aは半導体基板4の表面に形成されている。ゲート酸化膜61aの上にはゲート電極61gが形成され、その一方側から他方側に渡って活性領域が形成される。ゲート酸化膜61gの一方側の活性領域はMOSトランジスタ61のソース61sとなり、他方側の活性領域はMOSトランジスタ61のドレイン61dとなる。NチャネルMOSトランジスタ63もNチャネルMOSトランジスタ61と同じ構成である。

【0044】NチャネルMOSトランジスタ2は、図2(c)(d)に示すように、比較的小さな膜厚(たとえば3.0nm)のゲート酸化膜2aを有する。ゲート酸化膜2aは半導体基板4の表面に形成されている。ゲート酸化膜2aの上にはゲート電極2gが形成され、その一方側から他方側に渡って活性領域が形成される。ゲート酸化膜2gの一方側の活性領域はMOSトランジスタ2のソース2sとなり、他方側の活性領域はMOSトランジスタ2のドレイン2dとなる。

【0045】図3は、図1に示したリードゲート1のレイアウトを示す図である。図3において、半導体基板の表面に薄いゲート絶縁膜を介して1本の電極が形成される。この電極の一方端部はNチャネルMOSトランジスタ2のゲート電極2gとなり、その他方端部はNチャネルMOSトランジスタ3のゲート電極3gとなる。ゲート電極2gの近傍の基板表面に厚いゲート絶縁膜を介してNチャネルMOSトランジスタ61のゲート電極61gが形成され、ゲート電極3gの近傍の基板表面に厚いゲート酸化膜を介してNチャネルMOSトランジスタ63のゲート電極63gが形成される。ゲート電極2g,3gは列選択信号CSLRを受ける。ゲート電極61g,63gはそれぞれノードN1,N2に接続される。

【0046】ゲート電極2g,61gの間および両側にわたって活性領域A1が形成され、ゲート電極3g,63gの間および両側にわたって活性領域A2が形成される。ゲート電極2g,61gの間の領域は、NチャネルMOSトランジスタ2のソース2sおよびNチャネルMOSトランジスタ61のドレイン61dとなる。ゲート電極3g,63gの間の領域は、NチャネルMOSトランジスタ3のソース3sおよびNチャネルMOSトランジスタ63のドレイン63dとなる。NチャネルMOSトランジスタ2,3のドレイン2d,3dは、それぞれコンタクトホールC1,C2を介して上層のリードデータ線/GIOR,GIORに接続される。NチャネルMOSトランジスタ61,63のソース61s,63sは、それぞれコンタクトホールC3,C4を介して上層の接地電位GNDのラインに接続される。

【0047】この実施の形態1では、リードゲート1に含まれる4つのNチャネルMOSトランジスタのうちの列選択信号CSLRをゲートに受ける2つのNチャネルMOSトランジスタ2,3としてゲート絶縁膜の薄いものを使用したので、列選択信号CSLRの振幅電圧を周辺電源と同じ低電圧にすることができ、低消費電力化を図ることができる。また、列選択信号CSLRの振幅電圧を低電圧化しても、その振幅電圧を昇圧するためのレベル変換回路を用いる必要がないので、読出動作が遅くなることもない。また、低電圧の列選択信号CSLRで大きなソース−ドレイン間電流を得ることができるので、NチャネルMOSトランジスタ2,3のサイズが小さくてすむ。さらに、リードデータ線対GIOR,/GIORの振幅電圧も周辺電源と同じ低電圧にするので、大幅な低消費電力化を図ることができる。

【0048】[実施の形態2]実施の形態1では、同じ活性領域(たとえばA1)にゲート酸化膜の膜厚の異なる2種類のNチャネルMOSトランジスタ2,61を形成したが、この方法ではゲート電極2g,61gの間隔を大きくする必要があり、レイアウト面積が大きくなる。また、マスクがずれた場合に2つのNチャネルMOSトランジスタ2,61の不純物濃度が変化する可能性があり、信頼性上問題がある。この実施の形態2では、この問題が解決される。

【0049】図4は、この発明の実施の形態2によるDRAMコアセルのリードゲート5のレイアウトを示す図である。リードゲート5の回路図は、図1で示したリードゲート1と同じである。

【0050】図4において、半導体基板の表面に厚いゲート酸化膜を介してNチャネルMOSトランジスタ61,63のゲート電極61g,63gが平行に形成される。また、半導体基板表面に薄いゲート酸化膜を介してNチャネルMOSトランジスタ2,3のゲート電極2g,3gが平行に形成される。ゲート電極61gと2g,63gと3gは、それぞれ所定の間隔をあけて一直線上に形成される。ゲート電極2g,3gは列選択信号CSLRを受け、ゲート電極61g,63gはそれぞれノードN1,N2に接続される。

【0051】ゲート電極2g,3g,61g,63gの両側にそれぞれ活性領域A1a,A2a,A1b,A2bが互いに分離して形成される。活性領域A1a,A2aのうちゲート電極2g,3gの間の領域がそれぞれNチャネルMOSトランジスタ2,3のソース2s,3sとなり、ゲート電極2g,3gの外側の領域がそれぞれNチャネルMOSトランジスタ2,3のドレイン2d,3dとなる。活性領域A1b,A2bのうちゲート電極61g,63gの間の領域がそれぞれNチャネルMOSトランジスタ61,63のソース61s,63sとなり、ゲート電極61g,63gの外側の領域がそれぞれNチャネルMOSトランジスタ61,63のドレイン61d,63dとなる。

【0052】NチャネルMOSトランジスタ2のソース2sとNチャネルMOSトランジスタ61のドレイン61dとが活性領域で形成された配線層L1で接続される。NチャネルMOSトランジスタ3のソース3sとNチャネルMOSトランジスタ63のドレイン63dとが活性領域で形成された配線層L2で接続される。NチャネルMOSトランジスタ2,3のドレイン2d,3dは、それぞれコンタクトホールC1,C2を介して上層のリードデータ線/GIOR,GIORに接続される。NチャネルMOSトランジスタ61,63のソース61s,63sは、それぞれコンタクトホールC3,C4を介して上層の接地電位GNDのラインに接続される。

【0053】この実施の形態2では、ゲート酸化膜の膜厚の異なる2種類のNチャネルMOSトランジスタ2と61,3と63を別の活性領域A1aとA1b,A2aとA2bで形成し、活性領域A1aとA1b,A2aとA2bをそれぞれ配線層L1,L2で接続する。したがって、活性領域A1aとA1b,A2aとA2bを分離して形成することができるので、信頼性が向上する。また、最小の面積でレイアウトすることが可能となる。

【0054】[実施の形態3]図5は、この発明の実施の形態3によるDRAMコアセルのリードゲート6の構成を示す回路図である。

【0055】図5を参照して、このリードゲート6が図1R>1で示したリードゲート1と異なる点は、NチャネルMOSトランジスタ2と61,3と63の接続順が入換えられている点である。NチャネルMOSトランジスタ2,3のソースはともに接地電位GNDのラインに接続され、各々のゲートがともに列選択信号CSLRを受ける。NチャネルMOSトランジスタ61のソースはNチャネルMOSトランジスタ2のドレインに接続され、そのドレインはリードデータ線/GIORに接続され、そのゲートはノードN1に接続される。NチャネルMOSトランジスタ63のソースはNチャネルMOSトランジスタ3のドレインに接続され、そのドレインはリードデータ線GIORに接続され、そのゲートはノードN2に接続される。

【0056】図6は、図5に示したリードゲート6のレイアウトを示す図である。図6において、半導体基板の表面に厚いゲート酸化膜を介して2本のゲート電極61g,63gが平行に形成される。また、半導体基板の表面に薄いゲート酸化膜を介して2本のゲート電極2g,3gが平行に形成される。ゲート電極61gと2g,63gと3gは、それぞれ所定の間隔をあけて一直線上に形成される。

【0057】ゲート電極2g,3g,61g,63gの両側にそれぞれ活性領域A1a,A2a,A1b,A2bが形成される。活性領域A1a,A2aのうちゲート電極2g,3gの間の領域がそれぞれNチャネルMOSトランジスタ2,3のドレイン2d,3dとなり、ゲート電極2g,3gの外側の領域がそれぞれNチャネルMOSトランジスタ2gのソース2s,3sとなる。活性領域A1b,A2bのうちゲート電極61g,63gの間の領域がそれぞれNチャネルMOSトランジスタ61,63のソース61s,63sとなり、ゲート電極61g,63gの外側の領域がそれぞれNチャネルMOSトランジスタ61,63のドレイン61d,63dとなる。

【0058】NチャネルMOSトランジスタ2のドレイン2dとNチャネルMOSトランジスタ61のソース61sとが活性領域で形成された配線層L1で接続される。NチャネルMOSトランジスタ3のドレイン3dとNチャネルMOSトランジスタ63のソース63sとが活性領域で形成された配線層L2で接続される。NチャネルMOSトランジスタ2,3のソース2s,3sは、それぞれコンタクトホールC1,C2を介して上層の接地電位GNDのラインに接続される。NチャネルMOSトランジスタ61,63のドレイン61d,63dは、それぞれコンタクトホールC3,C4を介して上層のリードデータ線/GIOR,GIORに接続される。

【0059】この実施の形態3でも、実施の形態2と同じ効果が得られる。

[実施の形態4]図7は、この発明の実施の形態4によるDRAMコアセルのリードゲート7の構成を示す回路図である。図7を参照して、このリードゲート7が図5のリードゲート6と異なる点は、NチャネルMOSトランジスタ2が削除され、NチャネルMOSトランジスタ61のソースがNチャネルMOSトランジスタ63のソースに接続されている点である。

【0060】図8は、図7に示したリードゲート7のレイアウトを示す図である。図8において、半導体基板の表面に厚いゲート酸化膜を介してNチャネルMOSトランジスタ61,63のゲート電極61g,63gが平行に形成される。また、半導体基板の表面に薄いゲート酸化膜を介してNチャネルMOSトランジスタ3の2本のゲート電極3g,3g′が平行に形成される。ゲート電極61gと3g,63gと3g′は、所定の間隔でそれぞれ一直線上に形成される。ゲート電極3g,3g′は列選択信号CSLRを受け、ゲート電極61g,63gはそれぞれノードN1,N2に接続される。

【0061】ゲート電極3g,3g′の間および両側にわたって活性領域A3が形成され、ゲート電極61g,63の間および両側にわたって活性領域A4が形成される。ゲート電極3g,3g′の間の領域はNチャネルMOSトランジスタ3のドレイン3dとなり、ゲート電極3g,3g′の外側の領域はNチャネルMOSトランジスタ3のソース3s,3s′となる。ゲート電極61g,63gの間の領域はNチャネルMOSトランジスタ61,63のソース61s,63sとなり、ゲート電極61g,63gの外側の領域はそれぞれNチャネルMOSトランジスタ61,63のドレイン61d,63dとなる。

【0062】NチャネルMOSトランジスタ3のドレイン3dとNチャネルMOSトランジスタ60,63のソース61s,63sとは活性領域で形成された配線層L3で接続される。NチャネルMOSトランジスタ3のソース3s,3s′は、それぞれコンタクトホールC1,C2を介して上層の接地電位GNDのラインに接続される。NチャネルMOSトランジスタ61,63のドレイン61d,63dは、それぞれコンタクトホールC3,C4を介してリードデータ線/GIOR,GIORに接続される。

【0063】この実施の形態4でも、実施の形態2と同じ効果が得られる。

[実施の形態5]図9は、この発明の実施の形態5によるDRAMコアセルのライトゲート10の構成を示す回路図であって、図14のライトゲート50と対比される図である。

【0064】図9において、このライトゲート10は、ノードN2とライトデータ線/GIOWとの間に直列接続されたNチャネルMOSトランジスタ11,12と、ノードN1とライトデータ線GIOWとの間に直列接続されたNチャネルMOSトランジスタ13,14とを含む。NチャネルMOSトランジスタ11,13は、比較的大きな膜厚(たとえば7.5nm)のゲート酸化膜を有する。NチャネルMOSトランジスタ12,14は、比較的小さな膜厚(たとえば3.0nm)のゲート酸化膜を有する。NチャネルMOSトランジスタ11,13のゲートは、ともにライトマスク信号WM1を受ける。NチャネルMOSトランジスタ12,14のゲートは、ともに列選択信号CSLWを受ける。

【0065】列選択信号CSLWの振幅電圧は、周辺電源と同じ1.5Vである。ライトデータ線GIOW,/GIOWの振幅電圧は、周辺電源と同じ1.5Vである。ノードN1,N2の振幅電圧すなわちセンスアンプ47用の電源電圧Vddsは、2.0Vである。ライトマスク信号WM1の振幅電圧は、2.0Vである。

【0066】ノードN2またはN1が「H」レベル(電源電位Vdds)でライトマスク信号WM1が「H」レベル(電源電圧Vdds)の場合でも、NチャネルMOSトランジスタ12または14のドレインの電位はVdds−Vth(ただし、VthはNチャネルMOSトランジスタ11,13のしきい値電圧である)になるので、NチャネルMOSトランジスタ12,14のゲート酸化膜の耐圧はVdds−Vthよりも大きければよい。

【0067】図10は、図9に示したライトゲート10のレイアウトを示す図である。図10において、半導体基板の表面に厚いゲート酸化膜を介してNチャネルMOSトランジスタ11,13のゲート電極11g,13gが平行に形成される。また、半導体基板表面に薄いゲート酸化膜を介してNチャネルMOSトランジスタ12,14のゲート電極12g,14gが平行に形成される。ゲート電極11gと12g,13gと14gは、それぞれ所定の間隔をあけて一直線上に形成される。ゲート電極11g,13gはともにライトマスク信号WM1を受け、ゲート電極12g,14gはともに列選択信号CSLWを受ける。

【0068】ゲート電極12g,14g,11g,13gの両側にそれぞれ活性領域A5〜A8が形成される。活性領域A5,A6のうちゲート電極12g,14gの間の領域がそれぞれNチャネルMOSトランジスタ12,14のドレイン12d,14dとなり、ゲート電極12g,14gの外側の領域がそれぞれNチャネルMOSトランジスタ12,14のソース13s,14sとなる。活性領域A7,A8のうちゲート電極11g,13gの間の領域がそれぞれNチャネルMOSトランジスタ11,13のソース11s,13sとなり、ゲート電極11g,13gの外側の領域がそれぞれNチャネルMOSトランジスタ12,13のドレイン11d,13dとなる。

【0069】NチャネルMOSトランジスタ12のドレイン12dとNチャネルMOSトランジスタ11のソース11sとが活性領域で形成された配線層L5で接続される。NチャネルMOSトランジスタ14のドレイン14dとNチャネルMOSトランジスタ13のソース13sとが活性領域で形成された配線層L6で接続される。NチャネルMOSトランジスタ12,14のソース12s,14sは、それぞれコンタクトホールC5,C6を介して上層のライトデータ線/GIOW,GIOWに接続される。NチャネルMOSトランジスタ11,13のドレイン11d,13dはそれぞれコンタクトホールC7,C8を介して上層のノードN2,N1に接続される。

【0070】この実施の形態5では、ライトゲート10に含まれる4つのNチャネルMOSトランジスタ11〜14のうちの列選択信号CSLWをゲートに受ける2つのNチャネルMOSトランジスタ12,14としてゲート絶縁膜の薄いものを使用したので、列選択信号CSLWの振幅電圧を周辺電源と同じ低電圧にすることができ、低消費電力化を図ることができる。また、列選択信号CSLWの振幅電圧を低電圧化しても、その振幅電圧を昇圧するためのレベル変換回路を用いる必要がないので、書込動作が遅くなることもない。また、低電圧の列選択線CSLWで大きなソース−ドレイン間電流を得ることができるので、NチャネルMOSトランジスタ12,14のサイズは小さくてすむ。さらに、ライトデータ線対GIOW,/GIOWの振幅電圧も周辺電源と同じ低電圧にするので、大幅な低消費電力化を図ることができる。

【0071】また、ゲート酸化膜の膜厚の異なる2種類のNチャネルMOSトランジスタ11と12,13と14を別の活性領域A7とA5,A8とA6で形成し、活性領域A7とA5,A8とA6をそれぞれ配線層L1,L2で接続する。したがって、活性層A7とA5,A8とA6を分離して形成することができるので、信頼性が向上する。また、最小の面積でレイアウトすることが可能となる。

【0072】なお、ライトマスク信号WM1のないDRAMコアセルにおいては、図11に示すように、信号WM1の代わりにセンスアンプ47用の電源電位VddsをNチャネルMOSトランジスタ11,13のゲートに与えるとよい。この場合も、NチャネルMOSトランジスタ12,14のドレインの電位はVdds−Vthとなるので、NチャネルMOSトランジスタ12,14のゲート酸化膜の耐圧はVdds−Vthよりも大きければよい。

【0073】今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【0074】

【発明の効果】以上のように、この発明に係る半導体装置では、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線と、予め定められた第2の電位にプリチャージされる第2の信号線と、その入力電極が第1の信号線に接続され、第1の信号線の電位がそのしきい値電位を超えたことに応じて導通する第1のMOSトランジスタと、第1の信号線の信号が第2の信号線に伝達されることを許可する制御信号が入力されたことに応じて導通し、第1のMOSトランジスタを第2の信号線と基準電位のラインとの間に接続する第2のMOSトランジスタとが設けられ、第2のMOSトランジスタのゲート酸化膜は、第1のMOSトランジスタのゲート酸化膜よりも薄く形成される。したがって、第2のMOSトランジスタのゲート酸化膜を薄く形成するので、制御信号の振幅電圧の低電圧化を図ることができ、消費電力の低減化を図ることができる。また、低電圧化した制御信号を増幅するためのレベル変換回路を設ける必要がないので、動作速度が遅くなることもない。また、第2のトランジスタのサイズを小さくすることができ、チップ面積の縮小化を図ることができる。

【0075】好ましくは、さらに、第1の信号線に与えられる信号の相補信号が与えられる第3の信号線と、第2の電位にプリチャージされる第4の信号線と、その入力電極が第3の信号線に接続され、第3の信号線の電位がそのしきい値電位を超えたことに応じて導通する第3のMOSトランジスタと、制御信号が入力されたことに応じて導通し、第3のMOSトランジスタを第4の信号線と基準電位のラインとの間に接続する第4のMOSトランジスタとが設けられ、第4のMOSトランジスタのゲート酸化膜は、第3のMOSトランジスタのゲート酸化膜よりも薄く形成される。この場合は、信号およびその相補信号を伝達することができる。

【0076】また好ましくは、第1および第2のMOSトランジスタは、第2の信号線と基準電位のラインとの間に直列接続され、さらに、第1の信号線に与えられる信号の相補信号を与える第3の信号線と、第2の電位にプリチャージされる第4の信号線と、その第1の電極が第4の信号線に接続され、その第2の電極が第1および第2のMOSトランジスタの間のノードに接続され、その入力電極が第3の信号線に接続され、第3の信号線の電位がそのしきい値電位を超えたことに応じて導通する第3のMOSトランジスタとが設けられ、第2のMOSトランジスタのゲート酸化膜は、第3のMOSトランジスタのゲート酸化膜よりも薄く形成される。この場合は、信号およびその相補信号を伝達することができる。また、第1および第3のMOSトランジスタで第2のMOSトランジスタを共用するので、トランジスタ数が少なくてすむ。

【0077】また、この発明に係る他の半導体装置では、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線と、予め定められた第2の電位にプリチャージされる第2の信号線と、第2の信号線の電位と第2の電位との電位差を増幅し、その一方のレベルが第1の電位よりも高い第3の電位であり、その他方のレベルが基準電位である信号を第2の信号線に与えるセンスアンプと、その第1の電極が第1の信号線に接続され、第1の信号線の信号が第2の信号線に伝達されることを許可する第1の制御信号が入力されたことに応じて導通する第1のMOSトランジスタと、第1のMOSトランジスタの第2の電極と第2の信号線との間に接続され、第1の信号線の信号が第2の信号線に伝達されることを禁止するための第2の制御信号が入力されたことに応じて非導通になる第2のMOSトランジスタとが設けられ、第1のMOSトランジスタのゲート酸化膜は、第2のMOSトランジスタのゲート酸化膜よりも薄く形成される。したがって、第1のMOSトランジスタのゲート酸化膜を薄く形成するので、第1の制御信号の振幅電圧の低電圧化を図ることができ、消費電力の低減化を図ることができる。また、低電圧化した第1の制御信号を増幅するためのレベル変換回路を設ける必要がないので、動作速度が遅くなることもない。また、第1のトランジスタのサイズを小さくすることができ、チップ面積の縮小化を図ることができる。

【0078】また、この発明に係るさらに他の半導体装置では、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線と、予め定められた第2の電位にプリチャージされる第2の信号線と、第2の信号線の電位と第2の電位との電位差を増幅し、その一方のレベルが第1の電位よりも高い第3の電位であり、その他方のレベルが基準電位である信号を第2の信号線に与えるセンスアンプと、その第1の電極が第1の信号線に接続され、第1の信号線の信号が第2の信号線に伝達されることを許可する制御信号が入力されたことに応じて導通する第1のMOSトランジスタと、第1のMOSトランジスタの第2の電極と第2の信号線との間に接続され、その入力電極が第3の電位を受けて導通する第2のMOSトランジスタとが設けられ、第1のMOSトランジスタのゲート酸化膜は、第2のMOSトランジスタのゲート酸化膜よりも薄く形成されている。したがって、第1のMOSトランジスタのゲート酸化膜を薄く形成したので、制御信号の振幅電圧の低電圧化を図ることができ、消費電力の低減化を図ることができる。また、第2の信号線の電位がセンスアンプによって第3の電位にされた場合でも、第3の電位よりも第2のMOSトランジスタのしきい値電圧だけ低い電位が第1のMOSトランジスタに与えられるので、第1のMOSトランジスタが絶縁破壊されるのを防止することができる。

【0079】また好ましくは、各MOSトランジスタは、半導体基板の表面に形成されたゲート酸化膜および活性領域を含み、比較的厚いゲート酸化膜を有するMOSトランジスタの活性領域と比較的薄いゲート酸化膜を有するMOSトランジスタの活性領域とは、分離して形成されている。この場合は、信頼性の向上と、レイアウト面積の縮小化を図ることができる。

【図面の簡単な説明】

【図1】 この発明の実施の形態1によるDRAMコアセルのリードゲートの構成を示す回路図である。

【図2】 図1に示した2種類のNチャネルMOSトランジスタ2,61の構成を示す図である。

【図3】 図1に示したリードゲートのレイアウトを示す図である。

【図4】 この発明の実施の形態2によるDRAMコアセルのリードゲートのレイアウトを示す図である。

【図5】 この発明の実施の形態3によるDRAMコアセルのリードゲートの構成を示す回路図である。

【図6】 図5に示したリードゲートのレイアウトを示す図である。

【図7】 この発明の実施の形態4によるDRAMコアセルのリードゲートの構成を示す回路図である。

【図8】 図7に示したリードゲートのレイアウトを示す図である。

【図9】 この発明の実施の形態5によるDRAMコアセルのライトゲートの構成を示す回路図である。

【図10】 図9に示したライトゲートのレイアウトを示す図である。

【図11】 実施の形態5の変更例を示す回路図である。

【図12】 従来のDRAMコアセルの全体構成を示すブロック図である。

【図13】 図12に示したメモリセルアレイに含まれるメモリブロックの構成を示す回路ブロック図である。

【図14】 図12に示したデータDQ1の書込/読出に関連する部分の構成を示す回路ブロック図である。

【符号の説明】

1,5〜7,60 リードゲート、2,3,11〜14,Q,41〜44,51〜54,61〜64 NチャネルMOSトランジスタ、2s,3s,11s〜14s,61s,63s ソース、2d,3d,11d〜14d,61d,64d ドレイン、2g,3g,11g〜14g,61g,63g ゲート電極、2a,61a ゲート酸化膜、4 半導体基板、10,50 ライトゲート、C1〜C8 コンタクトホール、A1〜A8,A1a,A1b,A2a,A2b 活性領域、GIOR,/GIOR リードデータ線対、GIOW,/GIOW ライトデータ線対、L1〜L5 配線層、30 DRAMコアセル、31 行/列アドレスバッファ+クロック発生回路、32 行/列デコード回路、33 メモリマット、34 データ入出力回路、35 ライトドライバ+リードアンプ帯、36 入出力バッファ群、SA1〜SA3 センスアンプ帯、MA1,MA2メモリセルアレイ、MB メモリブロック、MC メモリセル、WL ワード線、BL,/BL ビット線対、37 ライトドライバ、38 リードアンプ、45,46 イコライザ、47 センスアンプ。

【0001】

【発明の属する技術分野】この発明は半導体装置に関し、特に、第1および第2の信号線と、それらを接続するためのMOSトランジスタとを備えた半導体装置に関する。

【0002】

【従来の技術】従来より、DRAMコアセルとロジック回路が混載されたシステムLSIが開発されている。DRAMコアセルとロジック回路の間では、データ転送速度の向上を図るため、同時に数百ビットのデータの入出力が可能となっている。また、複数ビットごとに1ビットのライトマスク信号の入力端子が設けられており、このライトマスク信号を制御することにより対応の複数ビットのメモリセルのデータの書換えを禁止することが可能となっている。

【0003】図12は、そのようなDRAMコアセル30の全体構成を示すブロック図である。図12において、このDRAMコアセル30は、行/列アドレスバッファ+クロック発生回路31、行/列デコード回路32、メモリマット33およびデータ入出力回路34を備える。このDRAMコアセル30では、同時に8kビット(ただし、kは1以上の整数である)のデータDQ1〜8kの入出力が可能となっており、8ビットのデータごとに1ビットのライトマスク信号WMの入力端子が設けられている。

【0004】行/列アドレスバッファ+クロック発生回路31は、外部アドレス信号A0〜Am(ただし、mは0以上の整数である)および外部制御信号/RAS,/CAS,/WEに従って、行アドレス信号RA0〜RAm、列アドレス信号CA0〜CAm、リードクロック信号CLKRおよびライトクロック信号CLKWなどを生成し、DRAMコアセル30全体を制御する。

【0005】メモリマット33は、複数(図では3つ)のセンスアンプ帯SA1〜SA3と、それらの間に配置されたメモリセルアレイMA1,MA2とを含む。メモリセルアレイMA1,MA2は、それぞれが1ビットのデータを記憶する複数のメモリセルを含む。複数のメモリセルは、予め定められた数8kずつグループ化されている。各メモリセルグループは、行アドレスおよび列アドレスによって決定される所定のアドレスに配置される。

【0006】行/列デコード回路32は、行/列アドレスバッファ+クロック発生回路31から与えられる行アドレス信号RA0〜RAmおよび列アドレス信号CA0〜CAmに従って、メモリセルアレイMA1,MA2のアドレスを指定する。センスアンプ帯SA1,SA2には、後述するセンスアンプ+入出力制御回路群が設けられている。センスアンプ+入出力制御回路群は、行/列デコード回路32によって指定されたアドレスの8k個のメモリセルをデータ入出力回路34に接続する。データ入出力回路34は、ライトドライバ+リードアンプ帯35および入出力バッファ群36を含む。ライトドライバ+リードアンプ帯35には、ライトドライバ群およびリードアンプ群が設けられている。

【0007】リードアンプ群は、リードクロック信号CLKRに同期して動作し、選択された8k個のメモリセルからの読出データQ1〜Q8kを入出力バッファ群36に与える。入出力バッファ群36は、外部制御信号/OEに応答してリードアンプ群からの読出データQ1〜Q8kを外部に出力する。ライトドライバ群は、ライトクロック信号CLKWに同期して動作し、外部からの書込データD1〜D8kを選択された8k個のメモリセルに書込む。ただし、8k個のメモリセルのうちライトマスク信号WM1〜WMkによって指定されたメモリセルにはデータは書込まれない。

【0008】メモリセルアレイMA1,MA2の各々は、それぞれがデータDQ1〜DQ8kに対応して設けられた8k個のメモリブロックMBを含む。各メモリブロックMBは、図13に示すように、複数行複数列に配置された複数のメモリセルMCと、それぞれ複数行に対応して設けられた複数のワード線WLと、それぞれ複数列に対応して設けられた複数組のビット線対BL,/BLとを含む。メモリセルMCは、アクセス用のNチャネルMOSトランジスタQと情報記憶用のキャパシタCとを含む周知のものである。

【0009】行/列デコード回路32によって行アドレス信号RA0〜RAmに対応するワード線WLが選択レベルの「H」レベルにされると、ワード線WLに対応する行のメモリセルMCのNチャネルMOSトランジスタQが導通し、メモリセルMCのデータの書込/読出が可能となる。書込動作時は、1本のワード線WLを選択レベルの「H」レベルにしてメモリセルMCを活性化させた後、書込データDに従って1組のビット線対BL,/BLのうちの一方のビット線を「H」レベルにし他方のビット線を「L」レベルにする。これにより、ビット線の電位が所望のメモリセルMCのキャパシタCに書込まれる。読出動作時は、ビット線対BL,/BLの電位をVBL(=VCC/2)にイコライズした後、1本のワード線WLを選択レベルの「H」レベルにしてメモリセルMCを活性化させる。これにより、各ビット線対BL,/BL間にメモリセルMCの記憶データに応じた微小電位差が生じる。各ビット線対間の微小電位差を電源電圧Vddsに増幅した後、1組のビット線対の電位差を検出することにより所望のメモリセルMCのデータを読出すことができる。8k個のメモリブロックMBは、ワード線WLの延在する方向に配列されており、ワード線WLは8k個のメモリブロックMBで共用されている。

【0010】図14は、データDQ1の書込/読出に関連する部分の構成を示す回路ブロック図である。図14において、データD1の書込を行なうためのライトドライバ37およびライトデータ線対GIOW,/GIOWと、データQ1の読出を行なうためのリードアンプ38およびリードデータ線対GIOR,/GIORとが設けられる。

【0011】ライトドライバ37は、図12で示したライトドライバ+リードアンプ帯35に配置され、書込動作時に書込データD1に従ってライトデータ線GIOW,/GIOWのうちの一方を「H」レベルにし他方を「L」レベルにする。リードアンプ38は、ライトドライバ+リードアンプ帯35に配置され、読出動作時にリードデータ線対GIOR,/GIOR間の電位差を検出して読出データQ1を生成し、出力バッファを介して外部に出力する。

【0012】ライトデータ線対GIOW,/GIOWは、図2で示したメモリアレイMA1,MA2およびセンスアンプ帯SA1〜SA3を横切るように配置され、その一方端はライトドライバ37に接続される。リードデータ線対GIOR,/GIORは、メモリアレイMA1,MA2およびセンスアンプ帯SA1〜SA3を横切るように配置され、その一方端はリードアンプ38に接続される。

【0013】メモリセルアレイMA1のメモリブロックMBに含まれる1組のビット線対BL1,/BL1と、メモリセルアレイMA2のメモリブロックMBに含まれる1組のビット線対BL2,/BL2とに共通にセンスアンプ+入出力制御回路40が設けられる。センスアンプ+入出力制御回路40は、メモリセルアレイMA1,MA2のたとえば各奇数番のビット線対BL,/BLに対応して設けられ、センスアンプ帯SA2に配置される。なお、メモリアレイMA1,MA2の各偶数番のビット線対BL,/BL用のセンスアンプ+入出力制御回路は、それぞれセンスアンプ帯SA1,SA3に配置される。

【0014】センスアンプ+入出力制御回路40は、NチャネルMOSトランジスタ41〜44、イコライザ45,46、センスアンプ47、ライトゲート50およびリードゲート60を含む。NチャネルMOSトランジスタ41,42は、それぞれメモリセルアレイMA1のビット線BL1,/BL1とノードN1,N2との間に接続され、各々のゲートはともに信号SHR1を受ける。NチャネルMOSトランジスタ43,44は、それぞれメモリセルアレイMA2のビット線BL2,/BL2とノードN1,N2との間に接続され、各々のゲートはともに信号SHR2を受ける。信号SHR1が活性化レベルの「H」レベルになると、NチャネルMOSトランジスタ41,42が導通してセンスアンプ+入出力制御回路40はメモリセルアレイMA1のビット線対BL1,/BL1と結合される。信号SHR2が活性化レベルの「H」レベルになると、NチャネルMOSトランジスタ43,44が導通してセンスアンプ+入出力制御回路40はメモリセルアレイMA2のビット線対BL2,/BL2と結合される。

【0015】イコライザ45は、信号BLEQ1が活性化レベルの「H」レベルの場合に活性化され、メモリセルアレイMA1のビット線対BL1,/BL1の電位をビット線電位VBL(=Vdds/2)にイコライズする。イコライザ46は、信号BLEQ2が活性化レベルの「H」レベルの場合に活性化され、メモリセルアレイMA2のビット線対BL2,/BL2の電位をビット線電位VBLにイコライズする。センスアンプ47は、信号SE,/SEがそれぞれ活性化レベルの「H」レベルおよび「L」レベルになったことに応じて活性化され、NチャネルMOSトランジスタ41,42または43,44によってノードN1,N2に接続されたビット線対BL1,/BL1またはBL2,/BL2間の電位差を電源電圧Vddsに増幅する。

【0016】ライトゲート50は、NチャネルMOSトランジスタ51〜54を含む。NチャネルMOSトランジスタ51,52は、ライトデータ線GIOWとノードN1との間に直列接続され、各々のゲートがそれぞれ信号WM1,CSLWを受ける。NチャネルMOSトランジスタ53,54は、ライトデータ線/GIOWとノードN2との間に直列接続され、各々ゲートはそれぞれ信号WM1,CSLWを受ける。

【0017】列選択信号CSLWが選択レベルの「H」レベルになると、NチャネルMOSトランジスタ52,54が導通する。ライトマスク信号WM1が「L」レベルの場合は、NチャネルMOSトランジスタ51,53が非導通になってデータD1の書込が禁止される。ライトマスク信号WM1が「H」レベルの場合は、NチャネルMOSトランジスタ51,53が導通してデータD1の書込が許容される。

【0018】リードゲート60は、NチャネルMOSトランジスタ61〜64を含む。NチャネルMOSトランジスタ61,62は接地電位GNDのラインとリードデータ線/GIORとの間に直列接続され、NチャネルMOSトランジスタ63,64は接地電位GNDのラインとリードデータ線GIORとの間に直列接続される。NチャネルMOSトランジスタ61,63はゲートがそれぞれノードN1,N2に接続され、NチャネルMOSトランジスタ62,64のゲートがともに信号CSLRを受ける。

【0019】列選択信号CSLRが選択レベルの「H」レベルになると、NチャネルMOSトランジスタ62,64が導通する。ノードN1,N2がそれぞれ「H」レベルおよび「L」レベルの場合は、NチャネルMOSトランジスタ61が導通するとともにNチャネルMOSトランジスタ63が非導通となり、「H」レベルにプリチャージされたリードデータ線GIOR,/GIORのうちのリードデータ線/GIORが接地される。ノードN1,N2がそれぞれ「L」レベルおよび「H」レベルの場合は、NチャネルMOSトランジスタ63が導通するとともにNチャネルMOSトランジスタ61が非導通となり、「H」レベルにプリチャージされたリードデータ線GIOR,/GIORのうちのリードデータ線GIORが接地される。

【0020】次に、図14で示したデータDQ1の書込/読出に関連する部分の動作について説明する。ここでは、メモリセルアレイMA1のビット線対BL1,/BL1が選択される場合について説明する。また、ライトマスク信号WM1は「H」レベルにされているものとする。

【0021】書込動作時は、まず信号SHR2が非活性化レベルの「L」レベルになってNチャネルMOSトランジスタ43,44が非導通になり、ノードN1,N2はメモリセルアレイMA2と切離される。また、ビット線イコライズ信号BLEQ1が非活性化レベルの「L」レベルになってイコライザ45が非活性化され、メモリセルアレイMA1のビット線対BL1,/BL1のイコライズが停止される。

【0022】次に、列アドレス信号CA0〜CAmに対応する列選択信号CSLWが選択レベルの「H」レベルにされてその列選択信号CSLWに対応するライトゲート50が導通し、ライトデータ線対GIOW,/GIOWがライトゲート50、ノードN1,N2、NチャネルMOSトランジスタ41,42を介してビット線対BL1,/BL1と結合される。また、ライトドライバ37は、書込データD1に従ってライトデータ線GIOW,/GIOWのうちの一方を「H」レベルにし他方を「L」レベルにする。

【0023】次いで、センスアンプ活性化信号SE,/SEがそれぞれ活性化レベルの「H」レベルおよび「L」レベルにされてセンスアンプ47が活性化され、センスアンプ47によってビット線対BL1,/BL1間の電位差が電源電圧Vddsに増幅される。また、行アドレス信号RA0〜RAmに対応するワード線WLが選択レベルの「H」レベルにされてそのワード線WLに対応するメモリセルMCが活性化され、ビット線BL1または/BL1の電位がそのメモリセルMCに書込まれる。

【0024】読出動作時は、まず信号SHR2が非活性化レベルの「L」レベルになってNチャネルMOSトランジスタ43,44が非導通になり、ノードN1,N2はメモリセルアレイMA2と切離される。また、ビット線イコライズ信号BLEQ1が非活性化レベルの「L」レベルになってイコライザ45が非活性化され、メモリセルアレイMA1のビット線対BL1,/BL1のイコライズが停止される。

【0025】次に、行アドレス信号RA0〜RAmに対応するワード線WLが選択レベルの「H」レベルにされてそのワード線WLに対応するメモリセルMCが活性化され、そのメモリセルMCの記憶データに応じてビット線対BL1,/BL1間に微小電位差が生じる。

【0026】次いで、センスアンプ活性化信号SE,/SEがそれぞれ活性化レベルの「H」レベルおよび「L」レベルにされ、センスアンプ47が活性化され、ビット線BL1,/BL1間の電位差が電源電圧Vddsに増幅される。すなわち、ビット線BL1,/BL1のうちプリチャージ電位Vdds/2よりも高い電位のビット線が電源電位Vddsにされ、他方のビット線が接地電位GNDにされる。これにより、リードゲート64のNチャネルMOSトランジスタ61,63のうちの一方が導通し他方が非導通になる。

【0027】次いで、列アドレス信号CA0〜CAmに対応する列選択信号CSLRが選択レベルの「H」レベルにされてその列選択信号CSLRに対応するリードゲート60のNチャネルMOSトランジスタ62,64が導通し、「H」レベルに予めプリチャージされたリードデータ線GIOR,/GIORのうちのいずれか一方がNチャネルMOSトランジスタ62,61または64,63を介して接地されて「L」レベルになる。リードアンプ38は、リードデータ線対GIOR,/GIORの電位差を検出し、検出結果に応じた論理のデータQ1を生成し、出力バッファを介して外部に出力する。

【0028】

【発明が解決しようとする課題】ところで従来は、ビット線BL,/BLの振幅電圧と、データ線GIOW,/GIOW,GIOR,/GIORの振幅電圧と、列選択信号CSLW,CSLRの振幅電圧とは同じ電圧であったので、ライトゲート50、リードゲート60およびセンスアンプ47のMOSトランジスタには同じ耐圧のMOSトランジスタすなわち同じ膜厚のゲート酸化膜を有するMOSトランジスタが用いられていた。

【0029】しかし、近年、DRAMコアセル30の周辺電源が低電圧化され、かつデータ線GIOW,/GIOW,GIOR,/GIORおよび列選択信号CSLW,CSLRの数が多くなってきているので、それらの振幅電圧を周辺電源電圧と同じにし、低消費電力化を図る必要がある。

【0030】しかし、単に列選択信号CSLW,CSLRの振幅電圧を小さくしただけでは、NチャネルMOSトランジスタ52,54,62,64に流れるソース−ドレイン間電流Idが小さくなって書込/読出動作が遅くなってしまう。

【0031】また、振幅電圧が小さな列選択信号CSLW,CSLRの振幅をレベル変換回路によって増幅する方法も考えられるが、レベル変換を行なうための時間が必要になって書込/読出動作が遅くなってしまう。

【0032】一方、メモリセルMCのキャパシタCにはできるだけ高い電圧を書込んでデータ保持時間を長くする必要があるので、センスアンプ47用の電源電圧Vddsを低くすることは好ましくない。したがって、ソース−ドレイン間電流Idを大きくするためにMOSトランジスタのゲート酸化膜を一律に薄くすると、センスアンプ47用の電源電圧VddsによってMOSトランジスタが破壊されてしまう。

【0033】それゆえに、この発明の主たる目的は、消費電流が小さく、かつ動作速度が速い半導体装置を提供することである。

【0034】

【課題を解決するための手段】この発明に係る半導体装置は、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線と、予め定められた第2の電位にプリチャージされる第2の信号線と、その入力電極が第1の信号線に接続され、第1の信号線の電位がそのしきい値電位を超えたことに応じて導通する第1のMOSトランジスタと、第1の信号線の信号が第2の信号線に伝達されることを許可する制御信号が入力されたことに応じて導通し、第1のMOSトランジスタを第2の信号線と基準電位のラインとの間に接続する第2のMOSトランジスタとを備え、第2のMOSトランジスタのゲート酸化膜は、第1のMOSトランジスタのゲート酸化膜よりも薄く形成されていることを特徴とするものである。

【0035】好ましくは、さらに、第1の信号線に与えられる信号の相補信号が与えられる第3の信号線と、第2の電位にプリチャージされる第4の信号線と、その入力電極が第3の信号線に接続され、第3の信号線の電位がそのしきい値電位を超えたことに応じて導通する第3のMOSトランジスタと、制御信号が入力されたことに応じて導通し、第3のMOSトランジスタを第4の信号線と基準電位のラインとの間に接続する第4のMOSトランジスタとを備え、第4のMOSトランジスタのゲート酸化膜は、第3のMOSトランジスタのゲート酸化膜よりも薄く形成されている。

【0036】また好ましくは、第1および第2のMOSトランジスタは、第2の信号線と基準電位のラインとの間に直列接続される。半導体装置は、さらに、第1の信号線に与えられる信号の相補信号が与えられる第3の信号線と、第2の電位にプリチャージされる第4の信号線と、その第1の電極が第4の信号線に接続され、その第2の電極が第1および第2のMOSトランジスタの間のノードに接続され、その入力電極が第3の信号線に接続され、第3の信号線の電位がそのしきい値電位を超えたことに応じて導通する第3のMOSトランジスタとを備え、第2のMOSトランジスタのゲート酸化膜は、第3のMOSトランジスタのゲート酸化膜よりも薄く形成されている。

【0037】また、この発明に係る他の半導体装置は、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線と、予め定められた第2の電位にプリチャージされる第2の信号線と、第2の信号線の電位と第2の電位との電位差を増幅し、その一方のレベルが第1の電位よりも高い第3の電位であり、その他方のレベルが基準電位である信号を第2の信号線に与えるセンスアンプと、その第1の電極が第1の信号線に接続され、第1の信号線の信号が第2の信号線に伝達されることを許可する第1の制御信号が入力されたことに応じて導通する第1のMOSトランジスタと、第1のMOSトランジスタの第2の電極と第2の信号線との間に接続され、第1の信号線の信号が第2の信号線に伝達されることを禁止するための第2の制御信号が入力されたことに応じて非導通になる第2のMOSトランジスタとを備え、第1のMOSトランジスタのゲート酸化膜は、第2のMOSトランジスタのゲート酸化膜よりも薄く形成されていることを特徴とするものである。

【0038】また、この発明に係るさらに他の半導体装置は、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線と、予め定められた第2の電位にプリチャージされる第2の信号線と、第2の信号線の電位と第2の電位との間の電位差を増幅し、その一方のレベルが第1の電位よりも高い第3の電位であり、その他方のレベルが基準電位である信号を第2の信号線に与えるセンスアンプと、その第1の電極が第1の信号線に接続され、第1の信号線の信号が第2の信号線に伝達されることを許可する制御信号が入力されたことに応じて導通する第1のMOSトランジスタと、第1のMOSトランジスタの第2の電極と第2の信号線との間に接続され、その入力電極が第3の電位を受けて導通する第2のMOSトランジスタとを備え、第1のMOSトランジスタのゲート酸化膜は、第2のMOSトランジスタのゲート酸化膜よりも薄く形成されていることを特徴とするものである。

【0039】好ましくは、各MOSトランジスタは、半導体基板の表面に形成されたゲート酸化膜および活性領域を含み、比較的厚いゲート酸化膜を有するMOSトランジスタの活性領域と比較的薄いゲート酸化膜を有するMOSトランジスタの活性領域とは、分離して形成されている。

【0040】

【発明の実施の形態】[実施の形態1]図1は、この発明の実施の形態1によるDRAMコアセルのリードゲート1の構成を示す回路図であって、図14のリードゲート60と対比される図である。

【0041】図1において、このリードゲート1が従来のリードゲート60と異なる点は、NチャネルMOSトランジスタ62,64がNチャネルMOSトランジスタ2,3で置換されている点である。NチャネルMOSトランジスタ2は、NチャネルMOSトランジスタ61のドレインとリードデータ線/GIORとの間に接続され、そのゲートが列選択信号CSLRを受ける。NチャネルMOSトランジスタ3は、NチャネルMOSトランジスタ63のドレインとリードデータ線GIORとの間に接続され、そのゲートが列選択信号CSLRを受ける。

【0042】列選択線CSLRの振幅電圧すなわち「H」レベルと「L」レベルの差の電圧は、周辺電源と同じ1.5Vである。リードデータ線GIOR,/GIORの振幅電圧は、周辺電源と同じ1.5Vである。ビット線BL,/BLの振幅電圧すなわちセンスアンプ47用の電圧Vddsは、2.0Vである。

【0043】NチャネルMOSトランジスタ61は、図2R>2(a)(b)に示すように、比較的大きな膜厚(たとえば7.5nm)のゲート酸化膜61aを有する。ゲート酸化膜61aは半導体基板4の表面に形成されている。ゲート酸化膜61aの上にはゲート電極61gが形成され、その一方側から他方側に渡って活性領域が形成される。ゲート酸化膜61gの一方側の活性領域はMOSトランジスタ61のソース61sとなり、他方側の活性領域はMOSトランジスタ61のドレイン61dとなる。NチャネルMOSトランジスタ63もNチャネルMOSトランジスタ61と同じ構成である。

【0044】NチャネルMOSトランジスタ2は、図2(c)(d)に示すように、比較的小さな膜厚(たとえば3.0nm)のゲート酸化膜2aを有する。ゲート酸化膜2aは半導体基板4の表面に形成されている。ゲート酸化膜2aの上にはゲート電極2gが形成され、その一方側から他方側に渡って活性領域が形成される。ゲート酸化膜2gの一方側の活性領域はMOSトランジスタ2のソース2sとなり、他方側の活性領域はMOSトランジスタ2のドレイン2dとなる。

【0045】図3は、図1に示したリードゲート1のレイアウトを示す図である。図3において、半導体基板の表面に薄いゲート絶縁膜を介して1本の電極が形成される。この電極の一方端部はNチャネルMOSトランジスタ2のゲート電極2gとなり、その他方端部はNチャネルMOSトランジスタ3のゲート電極3gとなる。ゲート電極2gの近傍の基板表面に厚いゲート絶縁膜を介してNチャネルMOSトランジスタ61のゲート電極61gが形成され、ゲート電極3gの近傍の基板表面に厚いゲート酸化膜を介してNチャネルMOSトランジスタ63のゲート電極63gが形成される。ゲート電極2g,3gは列選択信号CSLRを受ける。ゲート電極61g,63gはそれぞれノードN1,N2に接続される。

【0046】ゲート電極2g,61gの間および両側にわたって活性領域A1が形成され、ゲート電極3g,63gの間および両側にわたって活性領域A2が形成される。ゲート電極2g,61gの間の領域は、NチャネルMOSトランジスタ2のソース2sおよびNチャネルMOSトランジスタ61のドレイン61dとなる。ゲート電極3g,63gの間の領域は、NチャネルMOSトランジスタ3のソース3sおよびNチャネルMOSトランジスタ63のドレイン63dとなる。NチャネルMOSトランジスタ2,3のドレイン2d,3dは、それぞれコンタクトホールC1,C2を介して上層のリードデータ線/GIOR,GIORに接続される。NチャネルMOSトランジスタ61,63のソース61s,63sは、それぞれコンタクトホールC3,C4を介して上層の接地電位GNDのラインに接続される。

【0047】この実施の形態1では、リードゲート1に含まれる4つのNチャネルMOSトランジスタのうちの列選択信号CSLRをゲートに受ける2つのNチャネルMOSトランジスタ2,3としてゲート絶縁膜の薄いものを使用したので、列選択信号CSLRの振幅電圧を周辺電源と同じ低電圧にすることができ、低消費電力化を図ることができる。また、列選択信号CSLRの振幅電圧を低電圧化しても、その振幅電圧を昇圧するためのレベル変換回路を用いる必要がないので、読出動作が遅くなることもない。また、低電圧の列選択信号CSLRで大きなソース−ドレイン間電流を得ることができるので、NチャネルMOSトランジスタ2,3のサイズが小さくてすむ。さらに、リードデータ線対GIOR,/GIORの振幅電圧も周辺電源と同じ低電圧にするので、大幅な低消費電力化を図ることができる。

【0048】[実施の形態2]実施の形態1では、同じ活性領域(たとえばA1)にゲート酸化膜の膜厚の異なる2種類のNチャネルMOSトランジスタ2,61を形成したが、この方法ではゲート電極2g,61gの間隔を大きくする必要があり、レイアウト面積が大きくなる。また、マスクがずれた場合に2つのNチャネルMOSトランジスタ2,61の不純物濃度が変化する可能性があり、信頼性上問題がある。この実施の形態2では、この問題が解決される。

【0049】図4は、この発明の実施の形態2によるDRAMコアセルのリードゲート5のレイアウトを示す図である。リードゲート5の回路図は、図1で示したリードゲート1と同じである。

【0050】図4において、半導体基板の表面に厚いゲート酸化膜を介してNチャネルMOSトランジスタ61,63のゲート電極61g,63gが平行に形成される。また、半導体基板表面に薄いゲート酸化膜を介してNチャネルMOSトランジスタ2,3のゲート電極2g,3gが平行に形成される。ゲート電極61gと2g,63gと3gは、それぞれ所定の間隔をあけて一直線上に形成される。ゲート電極2g,3gは列選択信号CSLRを受け、ゲート電極61g,63gはそれぞれノードN1,N2に接続される。

【0051】ゲート電極2g,3g,61g,63gの両側にそれぞれ活性領域A1a,A2a,A1b,A2bが互いに分離して形成される。活性領域A1a,A2aのうちゲート電極2g,3gの間の領域がそれぞれNチャネルMOSトランジスタ2,3のソース2s,3sとなり、ゲート電極2g,3gの外側の領域がそれぞれNチャネルMOSトランジスタ2,3のドレイン2d,3dとなる。活性領域A1b,A2bのうちゲート電極61g,63gの間の領域がそれぞれNチャネルMOSトランジスタ61,63のソース61s,63sとなり、ゲート電極61g,63gの外側の領域がそれぞれNチャネルMOSトランジスタ61,63のドレイン61d,63dとなる。

【0052】NチャネルMOSトランジスタ2のソース2sとNチャネルMOSトランジスタ61のドレイン61dとが活性領域で形成された配線層L1で接続される。NチャネルMOSトランジスタ3のソース3sとNチャネルMOSトランジスタ63のドレイン63dとが活性領域で形成された配線層L2で接続される。NチャネルMOSトランジスタ2,3のドレイン2d,3dは、それぞれコンタクトホールC1,C2を介して上層のリードデータ線/GIOR,GIORに接続される。NチャネルMOSトランジスタ61,63のソース61s,63sは、それぞれコンタクトホールC3,C4を介して上層の接地電位GNDのラインに接続される。

【0053】この実施の形態2では、ゲート酸化膜の膜厚の異なる2種類のNチャネルMOSトランジスタ2と61,3と63を別の活性領域A1aとA1b,A2aとA2bで形成し、活性領域A1aとA1b,A2aとA2bをそれぞれ配線層L1,L2で接続する。したがって、活性領域A1aとA1b,A2aとA2bを分離して形成することができるので、信頼性が向上する。また、最小の面積でレイアウトすることが可能となる。

【0054】[実施の形態3]図5は、この発明の実施の形態3によるDRAMコアセルのリードゲート6の構成を示す回路図である。

【0055】図5を参照して、このリードゲート6が図1R>1で示したリードゲート1と異なる点は、NチャネルMOSトランジスタ2と61,3と63の接続順が入換えられている点である。NチャネルMOSトランジスタ2,3のソースはともに接地電位GNDのラインに接続され、各々のゲートがともに列選択信号CSLRを受ける。NチャネルMOSトランジスタ61のソースはNチャネルMOSトランジスタ2のドレインに接続され、そのドレインはリードデータ線/GIORに接続され、そのゲートはノードN1に接続される。NチャネルMOSトランジスタ63のソースはNチャネルMOSトランジスタ3のドレインに接続され、そのドレインはリードデータ線GIORに接続され、そのゲートはノードN2に接続される。

【0056】図6は、図5に示したリードゲート6のレイアウトを示す図である。図6において、半導体基板の表面に厚いゲート酸化膜を介して2本のゲート電極61g,63gが平行に形成される。また、半導体基板の表面に薄いゲート酸化膜を介して2本のゲート電極2g,3gが平行に形成される。ゲート電極61gと2g,63gと3gは、それぞれ所定の間隔をあけて一直線上に形成される。

【0057】ゲート電極2g,3g,61g,63gの両側にそれぞれ活性領域A1a,A2a,A1b,A2bが形成される。活性領域A1a,A2aのうちゲート電極2g,3gの間の領域がそれぞれNチャネルMOSトランジスタ2,3のドレイン2d,3dとなり、ゲート電極2g,3gの外側の領域がそれぞれNチャネルMOSトランジスタ2gのソース2s,3sとなる。活性領域A1b,A2bのうちゲート電極61g,63gの間の領域がそれぞれNチャネルMOSトランジスタ61,63のソース61s,63sとなり、ゲート電極61g,63gの外側の領域がそれぞれNチャネルMOSトランジスタ61,63のドレイン61d,63dとなる。

【0058】NチャネルMOSトランジスタ2のドレイン2dとNチャネルMOSトランジスタ61のソース61sとが活性領域で形成された配線層L1で接続される。NチャネルMOSトランジスタ3のドレイン3dとNチャネルMOSトランジスタ63のソース63sとが活性領域で形成された配線層L2で接続される。NチャネルMOSトランジスタ2,3のソース2s,3sは、それぞれコンタクトホールC1,C2を介して上層の接地電位GNDのラインに接続される。NチャネルMOSトランジスタ61,63のドレイン61d,63dは、それぞれコンタクトホールC3,C4を介して上層のリードデータ線/GIOR,GIORに接続される。

【0059】この実施の形態3でも、実施の形態2と同じ効果が得られる。

[実施の形態4]図7は、この発明の実施の形態4によるDRAMコアセルのリードゲート7の構成を示す回路図である。図7を参照して、このリードゲート7が図5のリードゲート6と異なる点は、NチャネルMOSトランジスタ2が削除され、NチャネルMOSトランジスタ61のソースがNチャネルMOSトランジスタ63のソースに接続されている点である。

【0060】図8は、図7に示したリードゲート7のレイアウトを示す図である。図8において、半導体基板の表面に厚いゲート酸化膜を介してNチャネルMOSトランジスタ61,63のゲート電極61g,63gが平行に形成される。また、半導体基板の表面に薄いゲート酸化膜を介してNチャネルMOSトランジスタ3の2本のゲート電極3g,3g′が平行に形成される。ゲート電極61gと3g,63gと3g′は、所定の間隔でそれぞれ一直線上に形成される。ゲート電極3g,3g′は列選択信号CSLRを受け、ゲート電極61g,63gはそれぞれノードN1,N2に接続される。

【0061】ゲート電極3g,3g′の間および両側にわたって活性領域A3が形成され、ゲート電極61g,63の間および両側にわたって活性領域A4が形成される。ゲート電極3g,3g′の間の領域はNチャネルMOSトランジスタ3のドレイン3dとなり、ゲート電極3g,3g′の外側の領域はNチャネルMOSトランジスタ3のソース3s,3s′となる。ゲート電極61g,63gの間の領域はNチャネルMOSトランジスタ61,63のソース61s,63sとなり、ゲート電極61g,63gの外側の領域はそれぞれNチャネルMOSトランジスタ61,63のドレイン61d,63dとなる。

【0062】NチャネルMOSトランジスタ3のドレイン3dとNチャネルMOSトランジスタ60,63のソース61s,63sとは活性領域で形成された配線層L3で接続される。NチャネルMOSトランジスタ3のソース3s,3s′は、それぞれコンタクトホールC1,C2を介して上層の接地電位GNDのラインに接続される。NチャネルMOSトランジスタ61,63のドレイン61d,63dは、それぞれコンタクトホールC3,C4を介してリードデータ線/GIOR,GIORに接続される。

【0063】この実施の形態4でも、実施の形態2と同じ効果が得られる。

[実施の形態5]図9は、この発明の実施の形態5によるDRAMコアセルのライトゲート10の構成を示す回路図であって、図14のライトゲート50と対比される図である。

【0064】図9において、このライトゲート10は、ノードN2とライトデータ線/GIOWとの間に直列接続されたNチャネルMOSトランジスタ11,12と、ノードN1とライトデータ線GIOWとの間に直列接続されたNチャネルMOSトランジスタ13,14とを含む。NチャネルMOSトランジスタ11,13は、比較的大きな膜厚(たとえば7.5nm)のゲート酸化膜を有する。NチャネルMOSトランジスタ12,14は、比較的小さな膜厚(たとえば3.0nm)のゲート酸化膜を有する。NチャネルMOSトランジスタ11,13のゲートは、ともにライトマスク信号WM1を受ける。NチャネルMOSトランジスタ12,14のゲートは、ともに列選択信号CSLWを受ける。

【0065】列選択信号CSLWの振幅電圧は、周辺電源と同じ1.5Vである。ライトデータ線GIOW,/GIOWの振幅電圧は、周辺電源と同じ1.5Vである。ノードN1,N2の振幅電圧すなわちセンスアンプ47用の電源電圧Vddsは、2.0Vである。ライトマスク信号WM1の振幅電圧は、2.0Vである。

【0066】ノードN2またはN1が「H」レベル(電源電位Vdds)でライトマスク信号WM1が「H」レベル(電源電圧Vdds)の場合でも、NチャネルMOSトランジスタ12または14のドレインの電位はVdds−Vth(ただし、VthはNチャネルMOSトランジスタ11,13のしきい値電圧である)になるので、NチャネルMOSトランジスタ12,14のゲート酸化膜の耐圧はVdds−Vthよりも大きければよい。

【0067】図10は、図9に示したライトゲート10のレイアウトを示す図である。図10において、半導体基板の表面に厚いゲート酸化膜を介してNチャネルMOSトランジスタ11,13のゲート電極11g,13gが平行に形成される。また、半導体基板表面に薄いゲート酸化膜を介してNチャネルMOSトランジスタ12,14のゲート電極12g,14gが平行に形成される。ゲート電極11gと12g,13gと14gは、それぞれ所定の間隔をあけて一直線上に形成される。ゲート電極11g,13gはともにライトマスク信号WM1を受け、ゲート電極12g,14gはともに列選択信号CSLWを受ける。

【0068】ゲート電極12g,14g,11g,13gの両側にそれぞれ活性領域A5〜A8が形成される。活性領域A5,A6のうちゲート電極12g,14gの間の領域がそれぞれNチャネルMOSトランジスタ12,14のドレイン12d,14dとなり、ゲート電極12g,14gの外側の領域がそれぞれNチャネルMOSトランジスタ12,14のソース13s,14sとなる。活性領域A7,A8のうちゲート電極11g,13gの間の領域がそれぞれNチャネルMOSトランジスタ11,13のソース11s,13sとなり、ゲート電極11g,13gの外側の領域がそれぞれNチャネルMOSトランジスタ12,13のドレイン11d,13dとなる。

【0069】NチャネルMOSトランジスタ12のドレイン12dとNチャネルMOSトランジスタ11のソース11sとが活性領域で形成された配線層L5で接続される。NチャネルMOSトランジスタ14のドレイン14dとNチャネルMOSトランジスタ13のソース13sとが活性領域で形成された配線層L6で接続される。NチャネルMOSトランジスタ12,14のソース12s,14sは、それぞれコンタクトホールC5,C6を介して上層のライトデータ線/GIOW,GIOWに接続される。NチャネルMOSトランジスタ11,13のドレイン11d,13dはそれぞれコンタクトホールC7,C8を介して上層のノードN2,N1に接続される。

【0070】この実施の形態5では、ライトゲート10に含まれる4つのNチャネルMOSトランジスタ11〜14のうちの列選択信号CSLWをゲートに受ける2つのNチャネルMOSトランジスタ12,14としてゲート絶縁膜の薄いものを使用したので、列選択信号CSLWの振幅電圧を周辺電源と同じ低電圧にすることができ、低消費電力化を図ることができる。また、列選択信号CSLWの振幅電圧を低電圧化しても、その振幅電圧を昇圧するためのレベル変換回路を用いる必要がないので、書込動作が遅くなることもない。また、低電圧の列選択線CSLWで大きなソース−ドレイン間電流を得ることができるので、NチャネルMOSトランジスタ12,14のサイズは小さくてすむ。さらに、ライトデータ線対GIOW,/GIOWの振幅電圧も周辺電源と同じ低電圧にするので、大幅な低消費電力化を図ることができる。

【0071】また、ゲート酸化膜の膜厚の異なる2種類のNチャネルMOSトランジスタ11と12,13と14を別の活性領域A7とA5,A8とA6で形成し、活性領域A7とA5,A8とA6をそれぞれ配線層L1,L2で接続する。したがって、活性層A7とA5,A8とA6を分離して形成することができるので、信頼性が向上する。また、最小の面積でレイアウトすることが可能となる。

【0072】なお、ライトマスク信号WM1のないDRAMコアセルにおいては、図11に示すように、信号WM1の代わりにセンスアンプ47用の電源電位VddsをNチャネルMOSトランジスタ11,13のゲートに与えるとよい。この場合も、NチャネルMOSトランジスタ12,14のドレインの電位はVdds−Vthとなるので、NチャネルMOSトランジスタ12,14のゲート酸化膜の耐圧はVdds−Vthよりも大きければよい。

【0073】今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【0074】

【発明の効果】以上のように、この発明に係る半導体装置では、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線と、予め定められた第2の電位にプリチャージされる第2の信号線と、その入力電極が第1の信号線に接続され、第1の信号線の電位がそのしきい値電位を超えたことに応じて導通する第1のMOSトランジスタと、第1の信号線の信号が第2の信号線に伝達されることを許可する制御信号が入力されたことに応じて導通し、第1のMOSトランジスタを第2の信号線と基準電位のラインとの間に接続する第2のMOSトランジスタとが設けられ、第2のMOSトランジスタのゲート酸化膜は、第1のMOSトランジスタのゲート酸化膜よりも薄く形成される。したがって、第2のMOSトランジスタのゲート酸化膜を薄く形成するので、制御信号の振幅電圧の低電圧化を図ることができ、消費電力の低減化を図ることができる。また、低電圧化した制御信号を増幅するためのレベル変換回路を設ける必要がないので、動作速度が遅くなることもない。また、第2のトランジスタのサイズを小さくすることができ、チップ面積の縮小化を図ることができる。

【0075】好ましくは、さらに、第1の信号線に与えられる信号の相補信号が与えられる第3の信号線と、第2の電位にプリチャージされる第4の信号線と、その入力電極が第3の信号線に接続され、第3の信号線の電位がそのしきい値電位を超えたことに応じて導通する第3のMOSトランジスタと、制御信号が入力されたことに応じて導通し、第3のMOSトランジスタを第4の信号線と基準電位のラインとの間に接続する第4のMOSトランジスタとが設けられ、第4のMOSトランジスタのゲート酸化膜は、第3のMOSトランジスタのゲート酸化膜よりも薄く形成される。この場合は、信号およびその相補信号を伝達することができる。

【0076】また好ましくは、第1および第2のMOSトランジスタは、第2の信号線と基準電位のラインとの間に直列接続され、さらに、第1の信号線に与えられる信号の相補信号を与える第3の信号線と、第2の電位にプリチャージされる第4の信号線と、その第1の電極が第4の信号線に接続され、その第2の電極が第1および第2のMOSトランジスタの間のノードに接続され、その入力電極が第3の信号線に接続され、第3の信号線の電位がそのしきい値電位を超えたことに応じて導通する第3のMOSトランジスタとが設けられ、第2のMOSトランジスタのゲート酸化膜は、第3のMOSトランジスタのゲート酸化膜よりも薄く形成される。この場合は、信号およびその相補信号を伝達することができる。また、第1および第3のMOSトランジスタで第2のMOSトランジスタを共用するので、トランジスタ数が少なくてすむ。

【0077】また、この発明に係る他の半導体装置では、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線と、予め定められた第2の電位にプリチャージされる第2の信号線と、第2の信号線の電位と第2の電位との電位差を増幅し、その一方のレベルが第1の電位よりも高い第3の電位であり、その他方のレベルが基準電位である信号を第2の信号線に与えるセンスアンプと、その第1の電極が第1の信号線に接続され、第1の信号線の信号が第2の信号線に伝達されることを許可する第1の制御信号が入力されたことに応じて導通する第1のMOSトランジスタと、第1のMOSトランジスタの第2の電極と第2の信号線との間に接続され、第1の信号線の信号が第2の信号線に伝達されることを禁止するための第2の制御信号が入力されたことに応じて非導通になる第2のMOSトランジスタとが設けられ、第1のMOSトランジスタのゲート酸化膜は、第2のMOSトランジスタのゲート酸化膜よりも薄く形成される。したがって、第1のMOSトランジスタのゲート酸化膜を薄く形成するので、第1の制御信号の振幅電圧の低電圧化を図ることができ、消費電力の低減化を図ることができる。また、低電圧化した第1の制御信号を増幅するためのレベル変換回路を設ける必要がないので、動作速度が遅くなることもない。また、第1のトランジスタのサイズを小さくすることができ、チップ面積の縮小化を図ることができる。

【0078】また、この発明に係るさらに他の半導体装置では、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線と、予め定められた第2の電位にプリチャージされる第2の信号線と、第2の信号線の電位と第2の電位との電位差を増幅し、その一方のレベルが第1の電位よりも高い第3の電位であり、その他方のレベルが基準電位である信号を第2の信号線に与えるセンスアンプと、その第1の電極が第1の信号線に接続され、第1の信号線の信号が第2の信号線に伝達されることを許可する制御信号が入力されたことに応じて導通する第1のMOSトランジスタと、第1のMOSトランジスタの第2の電極と第2の信号線との間に接続され、その入力電極が第3の電位を受けて導通する第2のMOSトランジスタとが設けられ、第1のMOSトランジスタのゲート酸化膜は、第2のMOSトランジスタのゲート酸化膜よりも薄く形成されている。したがって、第1のMOSトランジスタのゲート酸化膜を薄く形成したので、制御信号の振幅電圧の低電圧化を図ることができ、消費電力の低減化を図ることができる。また、第2の信号線の電位がセンスアンプによって第3の電位にされた場合でも、第3の電位よりも第2のMOSトランジスタのしきい値電圧だけ低い電位が第1のMOSトランジスタに与えられるので、第1のMOSトランジスタが絶縁破壊されるのを防止することができる。

【0079】また好ましくは、各MOSトランジスタは、半導体基板の表面に形成されたゲート酸化膜および活性領域を含み、比較的厚いゲート酸化膜を有するMOSトランジスタの活性領域と比較的薄いゲート酸化膜を有するMOSトランジスタの活性領域とは、分離して形成されている。この場合は、信頼性の向上と、レイアウト面積の縮小化を図ることができる。

【図面の簡単な説明】

【図1】 この発明の実施の形態1によるDRAMコアセルのリードゲートの構成を示す回路図である。

【図2】 図1に示した2種類のNチャネルMOSトランジスタ2,61の構成を示す図である。

【図3】 図1に示したリードゲートのレイアウトを示す図である。

【図4】 この発明の実施の形態2によるDRAMコアセルのリードゲートのレイアウトを示す図である。

【図5】 この発明の実施の形態3によるDRAMコアセルのリードゲートの構成を示す回路図である。

【図6】 図5に示したリードゲートのレイアウトを示す図である。

【図7】 この発明の実施の形態4によるDRAMコアセルのリードゲートの構成を示す回路図である。

【図8】 図7に示したリードゲートのレイアウトを示す図である。

【図9】 この発明の実施の形態5によるDRAMコアセルのライトゲートの構成を示す回路図である。

【図10】 図9に示したライトゲートのレイアウトを示す図である。

【図11】 実施の形態5の変更例を示す回路図である。

【図12】 従来のDRAMコアセルの全体構成を示すブロック図である。

【図13】 図12に示したメモリセルアレイに含まれるメモリブロックの構成を示す回路ブロック図である。

【図14】 図12に示したデータDQ1の書込/読出に関連する部分の構成を示す回路ブロック図である。

【符号の説明】

1,5〜7,60 リードゲート、2,3,11〜14,Q,41〜44,51〜54,61〜64 NチャネルMOSトランジスタ、2s,3s,11s〜14s,61s,63s ソース、2d,3d,11d〜14d,61d,64d ドレイン、2g,3g,11g〜14g,61g,63g ゲート電極、2a,61a ゲート酸化膜、4 半導体基板、10,50 ライトゲート、C1〜C8 コンタクトホール、A1〜A8,A1a,A1b,A2a,A2b 活性領域、GIOR,/GIOR リードデータ線対、GIOW,/GIOW ライトデータ線対、L1〜L5 配線層、30 DRAMコアセル、31 行/列アドレスバッファ+クロック発生回路、32 行/列デコード回路、33 メモリマット、34 データ入出力回路、35 ライトドライバ+リードアンプ帯、36 入出力バッファ群、SA1〜SA3 センスアンプ帯、MA1,MA2メモリセルアレイ、MB メモリブロック、MC メモリセル、WL ワード線、BL,/BL ビット線対、37 ライトドライバ、38 リードアンプ、45,46 イコライザ、47 センスアンプ。

【特許請求の範囲】

【請求項1】 半導体装置であって、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線、予め定められた第2の電位にプリチャージされる第2の信号線、その入力電極が前記第1の信号線に接続され、該第1の信号線の電位がそのしきい値電位を超えたことに応じて導通する第1のMOSトランジスタ、および前記第1の信号線の信号が前記第2の信号線に伝達されることを許可する制御信号が入力されたことに応じて導通し、前記第1のMOSトランジスタを前記第2の信号線と前記基準電位のラインとの間に接続する第2のMOSトランジスタを備え、前記第2のMOSトランジスタのゲート酸化膜は、前記第1のMOSトランジスタのゲート酸化膜よりも薄く形成されている、半導体装置。

【請求項2】 さらに、前記第1の信号線に与えられる信号の相補信号が与えられる第3の信号線、前記第2の電位にプリチャージされる第4の信号線、その入力電極が前記第3の信号線に接続され、該第3の信号線の電位がそのしきい値電位を超えたことに応じて導通する第3のMOSトランジスタ、および前記制御信号が入力されたことに応じて導通し、前記第3のMOSトランジスタを前記第4の信号線と前記基準電位のラインとの間に接続する第4のMOSトランジスタを備え、前記第4のMOSトランジスタのゲート酸化膜は、前記第3のMOSトランジスタのゲート酸化膜よりも薄く形成されている、請求項1に記載の半導体装置。

【請求項3】 前記第1および第2のMOSトランジスタは、前記第2の信号線と前記基準電位のラインとの間に直列接続され、さらに、前記第1の信号線に与えられる信号の相補信号が与えられる第3の信号線、前記第2の電位にプリチャージされる第4の信号線、およびその第1の電極が前記第4の信号線に接続され、その第2の電極が前記第1および第2のMOSトランジスタの間のノードに接続され、その入力電極が前記第3の信号線に接続され、該第3の信号線の電位がそのしきい値電位を超えたことに応じて導通する第3のMOSトランジスタを備え、前記第2のMOSトランジスタのゲート酸化膜は、前記第3のMOSトランジスタのゲート酸化膜よりも薄く形成されている、請求項1に記載の半導体装置。

【請求項4】 半導体装置であって、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線、予め定められた第2の電位にプリチャージされる第2の信号線、前記第2の信号線の電位と前記第2の電位との電位差を増幅し、その一方のレベルが前記第1の電位よりも高い第3の電位であり、その他方のレベルが前記基準電位である信号を前記第2の信号線に与えるセンスアンプ、その第1の電極が前記第1の信号線に接続され、前記第1の信号線の信号が前記第2の信号線に伝達されることを許可する第1の制御信号が入力されたことに応じて導通する第1のMOSトランジスタ、および前記第1のMOSトランジスタの第2の電極と前記第2の信号線との間に接続され、前記第1の信号線の信号が前記第2の信号線に伝達されることを禁止するための第2の制御信号が入力されたことに応じて非導通になる第2のMOSトランジスタを備え、前記第1のMOSトランジスタのゲート酸化膜は、前記第2のMOSトランジスタのゲート酸化膜よりも薄く形成されている、半導体装置。

【請求項5】 半導体装置であって、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線、予め定められた第2の電位にプリチャージされる第2の信号線、前記第2の信号線の電位と前記第2の電位との電位差を増幅し、その一方のレベルが前記第1の電位よりも高い第3の電位であり、その他方のレベルが前記基準電位である信号を前記第2の信号線に与えるセンスアンプ、その第1の電極が前記第1の信号線に接続され、その第1の信号線の信号が前記第2の信号線に伝達されることを許可する制御信号が入力されたことに応じて導通する第1のMOSトランジスタ、および前記第1のMOSトランジスタの第2の電極と前記第2の信号線との間に接続され、その入力電極が前記第3の電位を受けて導通する第2のMOSトランジスタを備え、前記第1のMOSトランジスタのゲート酸化膜は、前記第2のMOSトランジスタのゲート酸化膜よりも薄く形成されている、半導体装置。

【請求項6】 各MOSトランジスタは、半導体基板の表面に形成されたゲート酸化膜および活性領域を含み、比較的厚いゲート酸化膜を有するMOSトランジスタの活性領域と比較的薄いゲート酸化膜を有するMOSトランジスタの活性領域とは、分離して形成されている、請求項1から請求項5のいずれかに記載の半導体装置。

【請求項1】 半導体装置であって、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線、予め定められた第2の電位にプリチャージされる第2の信号線、その入力電極が前記第1の信号線に接続され、該第1の信号線の電位がそのしきい値電位を超えたことに応じて導通する第1のMOSトランジスタ、および前記第1の信号線の信号が前記第2の信号線に伝達されることを許可する制御信号が入力されたことに応じて導通し、前記第1のMOSトランジスタを前記第2の信号線と前記基準電位のラインとの間に接続する第2のMOSトランジスタを備え、前記第2のMOSトランジスタのゲート酸化膜は、前記第1のMOSトランジスタのゲート酸化膜よりも薄く形成されている、半導体装置。

【請求項2】 さらに、前記第1の信号線に与えられる信号の相補信号が与えられる第3の信号線、前記第2の電位にプリチャージされる第4の信号線、その入力電極が前記第3の信号線に接続され、該第3の信号線の電位がそのしきい値電位を超えたことに応じて導通する第3のMOSトランジスタ、および前記制御信号が入力されたことに応じて導通し、前記第3のMOSトランジスタを前記第4の信号線と前記基準電位のラインとの間に接続する第4のMOSトランジスタを備え、前記第4のMOSトランジスタのゲート酸化膜は、前記第3のMOSトランジスタのゲート酸化膜よりも薄く形成されている、請求項1に記載の半導体装置。

【請求項3】 前記第1および第2のMOSトランジスタは、前記第2の信号線と前記基準電位のラインとの間に直列接続され、さらに、前記第1の信号線に与えられる信号の相補信号が与えられる第3の信号線、前記第2の電位にプリチャージされる第4の信号線、およびその第1の電極が前記第4の信号線に接続され、その第2の電極が前記第1および第2のMOSトランジスタの間のノードに接続され、その入力電極が前記第3の信号線に接続され、該第3の信号線の電位がそのしきい値電位を超えたことに応じて導通する第3のMOSトランジスタを備え、前記第2のMOSトランジスタのゲート酸化膜は、前記第3のMOSトランジスタのゲート酸化膜よりも薄く形成されている、請求項1に記載の半導体装置。

【請求項4】 半導体装置であって、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線、予め定められた第2の電位にプリチャージされる第2の信号線、前記第2の信号線の電位と前記第2の電位との電位差を増幅し、その一方のレベルが前記第1の電位よりも高い第3の電位であり、その他方のレベルが前記基準電位である信号を前記第2の信号線に与えるセンスアンプ、その第1の電極が前記第1の信号線に接続され、前記第1の信号線の信号が前記第2の信号線に伝達されることを許可する第1の制御信号が入力されたことに応じて導通する第1のMOSトランジスタ、および前記第1のMOSトランジスタの第2の電極と前記第2の信号線との間に接続され、前記第1の信号線の信号が前記第2の信号線に伝達されることを禁止するための第2の制御信号が入力されたことに応じて非導通になる第2のMOSトランジスタを備え、前記第1のMOSトランジスタのゲート酸化膜は、前記第2のMOSトランジスタのゲート酸化膜よりも薄く形成されている、半導体装置。

【請求項5】 半導体装置であって、その一方のレベルが第1の電位であり、その他方のレベルが基準電位である信号が与えられる第1の信号線、予め定められた第2の電位にプリチャージされる第2の信号線、前記第2の信号線の電位と前記第2の電位との電位差を増幅し、その一方のレベルが前記第1の電位よりも高い第3の電位であり、その他方のレベルが前記基準電位である信号を前記第2の信号線に与えるセンスアンプ、その第1の電極が前記第1の信号線に接続され、その第1の信号線の信号が前記第2の信号線に伝達されることを許可する制御信号が入力されたことに応じて導通する第1のMOSトランジスタ、および前記第1のMOSトランジスタの第2の電極と前記第2の信号線との間に接続され、その入力電極が前記第3の電位を受けて導通する第2のMOSトランジスタを備え、前記第1のMOSトランジスタのゲート酸化膜は、前記第2のMOSトランジスタのゲート酸化膜よりも薄く形成されている、半導体装置。

【請求項6】 各MOSトランジスタは、半導体基板の表面に形成されたゲート酸化膜および活性領域を含み、比較的厚いゲート酸化膜を有するMOSトランジスタの活性領域と比較的薄いゲート酸化膜を有するMOSトランジスタの活性領域とは、分離して形成されている、請求項1から請求項5のいずれかに記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2002−16238(P2002−16238A)

【公開日】平成14年1月18日(2002.1.18)

【国際特許分類】

【出願番号】特願2000−195963(P2000−195963)

【出願日】平成12年6月29日(2000.6.29)

【出願人】(000006013)三菱電機株式会社 (33,312)

【出願人】(591036457)三菱電機エンジニアリング株式会社 (419)

【Fターム(参考)】

【公開日】平成14年1月18日(2002.1.18)

【国際特許分類】

【出願日】平成12年6月29日(2000.6.29)

【出願人】(000006013)三菱電機株式会社 (33,312)

【出願人】(591036457)三菱電機エンジニアリング株式会社 (419)

【Fターム(参考)】

[ Back to top ]