半導体装置

【課題】 半導体スイッチング素子のコレクタ電流の立ち上がりおよび立下り時における電流変化の傾きを変化できないため、ノイズ発生およびスイッチング損失を最適に設定できない。

【解決手段】 半導体スイッチング素子と、入力信号に基づきこの半導体スイッチング素子の駆動制御を行う駆動制御手段(9)とからなる半導体装置において、前記駆動制御手段(9)に、駆動能力の異なる複数個の駆動デバイス(T1〜T6)を備え、その駆動デバイスの中からいずれか1つ、もしくは複数個を選択して用いることにより、半導体スイッチング素子の動作特性を補正する特性補正手段(10)を備える。

【解決手段】 半導体スイッチング素子と、入力信号に基づきこの半導体スイッチング素子の駆動制御を行う駆動制御手段(9)とからなる半導体装置において、前記駆動制御手段(9)に、駆動能力の異なる複数個の駆動デバイス(T1〜T6)を備え、その駆動デバイスの中からいずれか1つ、もしくは複数個を選択して用いることにより、半導体スイッチング素子の動作特性を補正する特性補正手段(10)を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の回路構成に関するものであり、特にIGBTなどの絶縁ゲート型半導体スイッチング素子を駆動するパワーモジュールにおいて、そのパワーモジュールの電気的特性のトリミングを行う回路に関する。

【背景技術】

【0002】

図13にインバータ回路用パワーモジュールの構成を示す。駆動制御回路は、UPin,VPin,WPin,UNin,VNin,WNinを入力信号とし、各IGBT1〜IGBT6にそれぞれ駆動信号UPout,VPout,WPout,UNout,VNout,WNout(図13ではUPout,UNoutのみ明記)を出力する。この図13では1個の駆動制御回路で6個のIGBTを駆動するパワーモジュールの例であるが、複数の駆動制御回路を搭載したものもある。

【0003】

尚、図中右上のダイオードブリッジは本モジュールにDC電源を供給するための整流回路である。又、電流検出用の抵抗Rsは、IGBT2のエミッタ回路に挿入されているが、電流損失が大きくなるため、一般には、後で参照する図15に示すように、第2のエミッタ回路に挿入される。

【0004】

図14に前記入力信号UPin,UNinに係わる入出力動作タイミングチャートを示す。t1は、入力信号UPinのハイからローへのレベル反転から、出力信号UPoutがローからハイへのレベル反転までに要する遅延時間である。そして、IGBT1の出力電流Iupからわかるように、更にtonPの遅延時間をおいてIGBT1がスイッチオンする。前者の遅延時間t1は、駆動制御回路に起因するものであり、後者の遅延時間tonPはIGBTの応答時間によるものである。したがって、入力信号UPinのハイからローへのレベル反転からtconP後にIGBT1がスイッチオンする。

【0005】

t2は、入力信号UPinのローからハイへのレベル反転から、出力信号UPoutがハイからローへのレベル反転までに要する遅延時間である。そして、IGBT1の出力電流Iupからわかるように、更にtoffPの遅延時間をおいてIGBT1がスイッチオフする。従って入力信号UPinのローからハイへのレベル反転からtcoffP後にIGBT1がスイッチオフする。

【0006】

同様に、入力信号UNinのローからハイへのレベル反転から、tcoffN(=t3+toffN)後にIGBT2がスイッチオフし、入力信号UNinのハイからローへのレベル反転から、tconN(=t4+tonN)後にIGBT2がスイッチオンする。尚、この図14でわかるように、入力信号UPin,UNinに対し、出力信号UPout、UNoutはレベルが反転している。

【発明の開示】

【発明が解決しようとする課題】

【0007】

上述したt1〜t4およびtonP、toffP、toffN、tonNの遅延時間は一定ではなく、駆動制御回路やIGBTによってバラツキがある。従って、いかなる場合でも、IGBT1とIGBT2とが同時にスイッチオンしないように、IGBT1のオン期間に対し、IGBT2のオフ期間が長くなるようにしている。

【0008】

そのためには、入力信号UPinのロー期間に対し、入力信号UNinのハイ期間を図示のごとく設定する必要があり、その結果、入力信号UNinには入力休止時間期間(Tdead)が含まれるため、高精度なインバータ制御を行う際の阻害要因となっていた。

【0009】

又、図13の駆動制御回路に含まれる過電流保護の回路を図15に示している。IGBT2に接続したセンス抵抗Rsに電流Irsが流れることにより、センス抵抗の一端にはVRs=Rs・Irsの電位が発生する。その電位VRsが所定のトリップレベルを超えると、過電流保護回路3'により、短絡が発生したと検知され、駆動制御手段4'の動作が停止され、短絡保護が機能する。しかし、センス抵抗にバラツキがあり、過電流保護回路3'で設定されているトリップレベルにもバラツキがあり、そのため短絡電流保護値にもバラツキが生じ、正確な短絡保護が困難であった。

【0010】

更に、各IGBTのコレクタ電流の立ち上がりおよび立下り時における電流変化の傾きが大きくなると、ノイズが多量に発生し、一方、前記傾きが緩やかになると、スイッチング損失が増大する。このようにノイズ発生とスイッチング損失との間にはトレードオフの関係がある。そのため、実際のIGBTの使用状態に適った駆動が行えるように、従来はIGBT毎に、最適となる駆動制御回路を必要とした。

【0011】

本発明は、上述した課題を解決するためになされたものであり、

デバイスの電気的特性をトリミングすることにより、各デバイス間でのバラツキをなくし高精度のインバータ制御を行える半導体装置と、

短絡保護および過温度保護を高精度で行える半導体装置と、

出力デバイスのコレクタ電流の立ち上がり、および立下りの傾斜を最適に設定できる半導体装置とを提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明は、半導体スイッチング素子の駆動に用いられる半導体装置において、特性補正用入力信号に基づき前記半導体スイッチング素子の特性補正を行う特性補正手段を有することを特徴とする。

【0013】

本発明の第1の態様は、半導体スイッチング素子と、入力信号に基づきこの半導体スイッチング素子の駆動制御を行う駆動制御手段と、特性補正用入力信号に基づき前記駆動制御手段に対し伝達遅延時間を随意に設定して各半導体素子における遅延時間のバラツキをなくす特性補正手段を有することを特徴とする。

【0014】

本発明の第2の態様は、半導体スイッチング素子と、この半導体スイッチング素子に流れる電流を検出する電流検出手段と、この電流検出手段からの検出信号が規定のトリップレベルを上回ったとき、前記半導体スイッチング素子の動作を停止させる過電流保護手段と、前記トリップレベルの補正を行う特性補正手段を有することを特徴とする。

【0015】

本発明の第3の態様は、半導体スイッチング素子と、この半導体スイッチング素子の動作温度を検出する温度検知手段と、この温度検知手段からの検知信号が規定のトリップレベルを上回ったとき、前記半導体スイッチング素子の動作を停止させる過温度保護手段と、前記トリップレベルの補正を行う特性補正手段を有することを特徴とする。

【0016】

本発明の第4の態様(請求項1対応)は、半導体スイッチング素子と、入力信号に基づきこの半導体スイッチング素子の駆動制御を行う駆動制御手段とからなる半導体装置において、

前記駆動制御手段に、駆動能力の異なる複数個の駆動デバイスを備え、その駆動デバイスの中からいずれか1つ、もしくは複数個を選択して用いることにより、半導体スイッチング素子の動作特性を補正する特性補正手段を備えたことを特徴とする。

【発明の効果】

【0017】

本発明は、半導体スイッチング素子の特性について補正するようにしたので、各半導体装置における種々のバラツキを補正でき、高精度なインバータ装置を提供できる。

【0018】

本発明の第1の態様は、駆動回路に適切な遅延時間を設定することにより、半導体スイッチング素子における遅延時間のバラツキをなくすようにしたので、入力休止時間期間(Tdead)の設定が不要となり、高精度のインバータ制御が可能となる。

【0019】

本発明の第2の態様は、過電流の判断基準とするトリップレベルを随意に補正できるようにしたので、短絡保護を高精度で行なうことができる。

【0020】

本発明の第3の態様は、過温度の判断基準とするトリップレベルを随意に補正できるようにしたので、過温度保護を高精度で行なうことができる。

【0021】

本発明の第4の態様は、駆動回路に電流容量の異なる複数個の駆動デバイスを備え、その中から適切なものを選択できるようにしたので、半導体スイッチング素子のコレクタ電流の立ち上がり、および立下りの傾斜を随意に設定できる。

【0022】

前記特性補正手段としては、請求項2のごとく不揮発性メモリや、請求項3のごとくワンタイムROMで簡便に実現できる。また、これらの不揮発性メモリやワンタイムROMで実現した特性補正手段は、請求項4のごとく容易に半導体装置に集積化して内蔵できる。

【発明を実施するための最良の形態】

【0023】

実施形態1

図1は、本発明の第1実施形態を示した制御ブロック図を示す。駆動制御回路1は、信号入力端子からの入力信号UPinおよび信号入力端子からの入力信号UNinの信号に基づき、当該パワーモジュールの出力端子であるP2、N2間にシリアルに接続されたU相のIGBT1、IGBT2のそれぞれのゲートに出力信号UPoutおよびUNoutを供給する。この図1では、U相についてのみ記したが、V相のIGBT3、IGBT4およびW相のIGBT5、IGBT6を駆動するための回路を含む。

【0024】

駆動制御回路1および特性補正回路2の詳しい回路図を図2に示している。駆動制御回路1において、論理回路11は、入力信号UPinを遅延挿入回路12内ラインL1にロジック信号として出力する。遅延挿入回路12内において、ラインL1とアースとの間に、キャパシタンスC1、C2、C3がそれぞれスイッチS1、S2、S3を介して接続される。また、ラインL1には電流I1が供給される。

【0025】

前記ラインL1は反転器INV1を介し、遅延挿入回路13内のラインL2に接続される。この遅延挿入回路13においても、ラインL2とアースとの間に、キャパシタンスC4、C5、C6がそれぞれスイッチS4、S5、S6を介して接続されている。また、ラインL2には電流I2が供給される。そのラインL2は反転器INV2を介して駆動回路14に接続される。この駆動回路14からIGBT1を駆動する駆動信号UPoutが出力される。

【0026】

キャパシタンスC1、C2、C3およびキャパシタンスC4、C5、C6の各容量は同一であってもよく、あるいは個別に異なる容量であってもよい。また、キャパシタンスの個数は3個に限定されない。

【0027】

特性補正回路2では、特性補正信号が書込回路21により、EPROM22に書き込まれ、そのEPROM22のデータがレジスタ23にラッチされる。このレジスタ23よりのラッチデータd1〜d6が前記スイッチS1〜S6の駆動信号として供給される。従って、特性補正信号によって、前記スイッチS1〜S6を所望の状態にスイッチオン、スイッチオフできる。

【0028】

図2の駆動制御回路1の動作を図3のタイミングチャートに従って説明する。入力信号UNinは、図14のものと異なり、入力休止時間(Tdead)は含まれず、入力信号UPinとレベルが反転しているだけで完全に同期している。遅延時間t11は、入力信号UPinのハイからローへのレベル反転から、出力信号UPoutがローからハイへのレベル反転までに要した駆動制御回路1内の遅延時間であり、スイッチS1〜S3がすべてオフのとき、遅延挿入回路12での遅延時間は0のため、この時の遅延時間t11の大きさは、図14における遅延時間t1に相当する。

【0029】

遅延時間t12は、入力信号UPinのローからハイへのレベル反転から出力信号UPoutがハイから、ローへのレベル反転までに要した駆動制御回路1内の遅延時間であり、スイッチS4〜S6がすべてオフのとき、この遅延挿入回路33での遅延時間は0のため、この時の遅延時間t12の大きさは、図14における遅延時間t2に相当する。

【0030】

図2の駆動制御回路1では、入力信号UPinのみに対する回路のみ示しており、他の入力信号UNin、VPin、VNin、WPin、WNin に対してもそれぞれ同じ回路(遅延挿入回路や特性補正回路)を備える。従って、遅延時間t13は、入力信号UNinのローからハイへのレベル反転から出力信号UNoutがハイからローへのレベル反転までの遅延時間であり、遅延時間t14は、入力信号UNinのハイからローへのレベル反転から出力信号UNoutがローからハイへのレベル反転までの遅延時間である。これらの遅延時間もt11およびt12と同様に随意に設定できる。

【0031】

IGBT1は、UPinのハイからローへの反転レベルから遅延時間t11後に、出力信号UPoutがローからハイにレベル反転し、さらにtonP(IGBT1の応答時間)後にIGBT1がスイッチオンする。従って、入力信号UPinのハイからローへのレベル反転からtconP後にIGBT1がスイッチオンする。

【0032】

そして、そのIGBT1は、UPinのローからハイへの反転レベルから遅延時間t12後に、出力信号UPoutがハイからローにレベル反転し、さらにtoffP(IGBT1の応答時間)後にIGBT1がスイッチオフする。従って、入力信号UPinのローからハイへのレベル反転からtcoffP後にIGBT1がスイッチオフする。

【0033】

同様に、IGBT2は、UNinのローからハイへの反転レベルから遅延時間t13後に、出力信号UNoutがハイからローにレベル反転し、さらにtoffN(IGBT2の応答時間)後にIGBT2がスイッチオフする。従って、入力信号UNinのローからハイへのレベル反転からtcoffN後にIGBT2がスイッチオフする。

【0034】

そして、そのIGBT2は、UNinのハイからローへの反転レベルから遅延時間t14後に、出力信号UNoutがローからハイにレベル反転し、さらにtonN(これもIGBT2の応答時間)後にIGBT2がスイッチオンする。従って、入力信号UNinのハイからローへのレベル反転からtconN後にIGBT1がスイッチオンする。

【0035】

入力信号UPinおよびUNinを図3のごとく同期させても、駆動制御回路1における遅延時間やIGBT自身の反応時間にバラツキがあるため、tconP≠tcoffNであり、IGBT1のスイッチオンとIGBT2のスイッチオフとが合致しない。同様に、tcoffP≠tconNであるため、IGBT1のスイッチオフとIGBT2のスイッチオンとが合致しない。

【0036】

しかし、特性補正信号により、

全スイッチをオフ

いずれか1つのスイッチをオン

いずれか2つのスイッチをオン

全スイッチをオン

のどれかを選択することにより、t11およびt13の遅延時間を加減でき、この操作により、図3のごとく、tconP≒tcoffNとすれば、同じタイミングでIGBT1はスイッチオンし、IGBT2はスイッチオフする。同様に、t12およびt14の遅延時間を加減して、tcoffP≒tconNとすれば、同じタイミングでIGBT1はスイッチオフし、IGBT2はスイッチオンする。

【0037】

このように、tconP≒tcoffN、tcoffP≒tconNとすれば、駆動制御手段1およびIGBT自身の応答時間を含めたデバイス全体での遅延時間のバラツキをなくせることができ、そのため、入力休止時間(Tdead)が不要であり、高精度なインバータ制御が可能となる。尚、温度変化や経年変化により、遅延時間が僅かながらドリフトするため、そのドリフトをカバーできる程度のTdeadの設定が望ましい。但し、この場合のTdeadは従来のものと比較して格段に短いため、高精度なインバータ制御を行う際に障害とならない。

【0038】

特性補正回路2のEPROM22には、不揮発性メモリもしくはワンタイムROMを用いることができ、そのような特性補正回路2を、この駆動制御回路1に集積内蔵することもできる。

【0039】

実施形態2

図4は、本発明の第2実施形態を示した制御ブロック図を示し、その詳細を図5に示している。駆動制御回路4は、入力信号Cをロジック信号として出力する論理回路41と、そのロジック信号に従って駆動信号cを出力する駆動回路42とからなる。

【0040】

過電流保護回路3は比較器31からなり、その非反転入力部には、IGBT2の第2エミッタに接続したセンス抵抗Rsの一端に生じたVsが入力される。基準電圧Vref は、4つの直列接続の抵抗で分圧され、それらの分圧された電圧Vref1〜Vref3がスイッチS1〜S3によって選択され、比較器31の反転入力部にトリップレベルとして入力される。この比較器31の出力は、前記論理回路41に遮断信号として出力される。

【0041】

特性補正回路5は前記スイッチS1〜S3のいずれか1つをオンにするための回路であり、その回路構成は、図2の特性補正回路2と同様である。この特性補正回路5もEPROMに不揮発性メモリもしくはワンタイムROMを用いることができ、本駆動制御回路4に集積内蔵することもできる。

【0042】

既述したように、従来は、センス抵抗Rs、過電流保護回路3で設定されているトリップレベルおよびエミッタの分流比に個体バラツキがあり、そのため短絡電流保護値にもバラツキが生じ、正確な短絡保護が困難であったが、本実施形態では、図6に示すように、トリップレベルをVref1、Vref2、Vref3 に変更可能とし、実測結果に基づき適切なトリップレベルを設定することにより、正確な過電流保護が可能となる。尚、変更可能なトリップレベルの個数は3個に限定されない。

【0043】

実施形態3

図7は、本発明の第3実施形態を示した制御ブロック図を示し、図7の詳細を図8に示す。図7および図8において、図4および図5と共通する要素については共通の符号を付している。過温度保護回路7自身は、過電流保護回路3と同一の回路構成であるが、比較器71の非反転入力部には温度検知手段8で検出した温度信号Vtが取り込まれる。

【0044】

IGBT1の動作温度が高くなり、前記温度信号Vtが所定のトリップレベルを上回れば、所定の遮断信号が駆動制御回路4に供給されることにより、入力信号Dに対し、その駆動信号dが遮断されるが、この過温度保護回路7においても、過温度保護トリップレベルおよび温度検知手段8のバラツキがあるため正確な過温度保護が困難であった。

【0045】

そこで本実施形態では、図9に示すように、トリップレベルをVref1、Vref2、Vref3 に変更可能とし、実測結果に基づき適切なトリップレベルを設定することにより、正確な過温度保護が可能となる。

【0046】

実施形態4

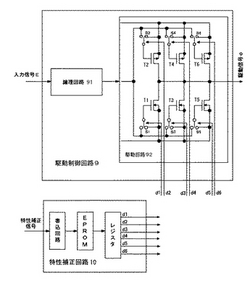

図10は、本発明の第4実施形態を示した制御ブロック図を示し、その詳細を図11に示す。駆動制御回路9は、入力信号Eをロジック信号として出力する論理回路91と、駆動回路92とからなる。NタイプのFETトランジスタT1、T3、T5の各ドレインは、当駆動制御回路9の出力端子に接続され、各ゲートは、各スイッチS1、S3、S5を介して論理回路91の出力部か、各トランジスタのソースに接続される。

【0047】

PタイプのFETトランジスタT2、T4、T6の各ドレインは、当駆動制御回路9の出力端子に接続され、各ゲートは、各スイッチS2、S4、S6を介して論理回路91の出力部か、各トランジスタのソースに接続される。各スイッチS1〜S6は、特性補正回路10のレジスタよりの信号d1〜d6により駆動される。

【0048】

入力信号Eの立ち下がりにより、トランジスタT1、T3、T5の内、論理回路91の出力部に接続されていたトランジスタが駆動され、そして、前記入力信号Eの立ち上がりにより、トランジスタT2、T4、T6の内、論理回路91の出力部に接続されていたトランジスタが駆動され、それらの駆動されたトランジスタの出力電流が駆動信号eとして出力される。

【0049】

このときのタイミングチャートを図12に示している。駆動信号e1は、トランジスタT1およびT2が駆動されたときのものであり、駆動信号e2は、トランジスタT3およびT4が駆動されたときのものである。トランジスタT1およびT2に比べ、トランジスタT3およびT4の駆動能力が大きく、それゆえ、駆動信号e2の立ち上がりおよび立ち下がりが、駆動信号e1と比較して緩くなっている。駆動信号e1およびe2におけるIGBT2のコレクタ電流をI1、I2に示している。

【0050】

従来は、IGBTの電流容量毎に駆動制御回路の駆動能力を変える必要があったが、本実施形態によれば、種々の駆動容量を持ったIGBTの中から適切なものを選択することにより、IGBT2のコレクタ(出力)電流の立ち上がり、立ち下がりの傾きを随意に選択できる。この特性補正回路10もEPROMに不揮発性メモリもしくはワンタイムROMを用いることができ、本駆動制御回路9に集積内蔵することもできる。

【0051】

駆動されるトランジスタは、T1−T2、T3−T4、T5−T6の組み合わせ以外に、T1−T4のような組み合わせであってもよく、あるいは(T1+T3)−(T2+T4)のように複数個を同時に駆動させるような組み合わせも可能である。

【図面の簡単な説明】

【0052】

【図1】本発明の第1実施形態を示した制御ブロック図

【図2】図1の詳細を示した回路図

【図3】図1における信号のタイミングチャート

【図4】本発明の第2実施形態を示した制御ブロック図

【図5】図4の詳細を示した回路図

【図6】図4における信号のタイミングチャート

【図7】本発明の第3実施形態を示した制御ブロック図

【図8】図7の詳細を示した回路図

【図9】図7における信号のタイミングチャート

【図10】本発明の第4実施形態を示した制御ブロック図

【図11】図7の詳細を示した回路図

【図12】図10における信号のタイミングチャート

【図13】従来のパワーモジュールの構成を示した回路図

【図14】図13における入出力動作を示したタイミングチャート

【図15】短絡保護動作時を示したタイミングチャート

【符号の説明】

【0053】

1 駆動制御回路、2 特性補正回路、3 過電流保護回路、4 駆動制御回路、5 特性補正回路、7 過温度保護回路、8 温度検知手段、9 駆動制御回路、10 特性補正回路、11 論理回路、12 遅延挿入回路、13 遅延挿入回路、21 書込回路、22 EPROM、23 レジスタ、91 論理回路、92 駆動回路

【技術分野】

【0001】

本発明は、半導体装置の回路構成に関するものであり、特にIGBTなどの絶縁ゲート型半導体スイッチング素子を駆動するパワーモジュールにおいて、そのパワーモジュールの電気的特性のトリミングを行う回路に関する。

【背景技術】

【0002】

図13にインバータ回路用パワーモジュールの構成を示す。駆動制御回路は、UPin,VPin,WPin,UNin,VNin,WNinを入力信号とし、各IGBT1〜IGBT6にそれぞれ駆動信号UPout,VPout,WPout,UNout,VNout,WNout(図13ではUPout,UNoutのみ明記)を出力する。この図13では1個の駆動制御回路で6個のIGBTを駆動するパワーモジュールの例であるが、複数の駆動制御回路を搭載したものもある。

【0003】

尚、図中右上のダイオードブリッジは本モジュールにDC電源を供給するための整流回路である。又、電流検出用の抵抗Rsは、IGBT2のエミッタ回路に挿入されているが、電流損失が大きくなるため、一般には、後で参照する図15に示すように、第2のエミッタ回路に挿入される。

【0004】

図14に前記入力信号UPin,UNinに係わる入出力動作タイミングチャートを示す。t1は、入力信号UPinのハイからローへのレベル反転から、出力信号UPoutがローからハイへのレベル反転までに要する遅延時間である。そして、IGBT1の出力電流Iupからわかるように、更にtonPの遅延時間をおいてIGBT1がスイッチオンする。前者の遅延時間t1は、駆動制御回路に起因するものであり、後者の遅延時間tonPはIGBTの応答時間によるものである。したがって、入力信号UPinのハイからローへのレベル反転からtconP後にIGBT1がスイッチオンする。

【0005】

t2は、入力信号UPinのローからハイへのレベル反転から、出力信号UPoutがハイからローへのレベル反転までに要する遅延時間である。そして、IGBT1の出力電流Iupからわかるように、更にtoffPの遅延時間をおいてIGBT1がスイッチオフする。従って入力信号UPinのローからハイへのレベル反転からtcoffP後にIGBT1がスイッチオフする。

【0006】

同様に、入力信号UNinのローからハイへのレベル反転から、tcoffN(=t3+toffN)後にIGBT2がスイッチオフし、入力信号UNinのハイからローへのレベル反転から、tconN(=t4+tonN)後にIGBT2がスイッチオンする。尚、この図14でわかるように、入力信号UPin,UNinに対し、出力信号UPout、UNoutはレベルが反転している。

【発明の開示】

【発明が解決しようとする課題】

【0007】

上述したt1〜t4およびtonP、toffP、toffN、tonNの遅延時間は一定ではなく、駆動制御回路やIGBTによってバラツキがある。従って、いかなる場合でも、IGBT1とIGBT2とが同時にスイッチオンしないように、IGBT1のオン期間に対し、IGBT2のオフ期間が長くなるようにしている。

【0008】

そのためには、入力信号UPinのロー期間に対し、入力信号UNinのハイ期間を図示のごとく設定する必要があり、その結果、入力信号UNinには入力休止時間期間(Tdead)が含まれるため、高精度なインバータ制御を行う際の阻害要因となっていた。

【0009】

又、図13の駆動制御回路に含まれる過電流保護の回路を図15に示している。IGBT2に接続したセンス抵抗Rsに電流Irsが流れることにより、センス抵抗の一端にはVRs=Rs・Irsの電位が発生する。その電位VRsが所定のトリップレベルを超えると、過電流保護回路3'により、短絡が発生したと検知され、駆動制御手段4'の動作が停止され、短絡保護が機能する。しかし、センス抵抗にバラツキがあり、過電流保護回路3'で設定されているトリップレベルにもバラツキがあり、そのため短絡電流保護値にもバラツキが生じ、正確な短絡保護が困難であった。

【0010】

更に、各IGBTのコレクタ電流の立ち上がりおよび立下り時における電流変化の傾きが大きくなると、ノイズが多量に発生し、一方、前記傾きが緩やかになると、スイッチング損失が増大する。このようにノイズ発生とスイッチング損失との間にはトレードオフの関係がある。そのため、実際のIGBTの使用状態に適った駆動が行えるように、従来はIGBT毎に、最適となる駆動制御回路を必要とした。

【0011】

本発明は、上述した課題を解決するためになされたものであり、

デバイスの電気的特性をトリミングすることにより、各デバイス間でのバラツキをなくし高精度のインバータ制御を行える半導体装置と、

短絡保護および過温度保護を高精度で行える半導体装置と、

出力デバイスのコレクタ電流の立ち上がり、および立下りの傾斜を最適に設定できる半導体装置とを提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明は、半導体スイッチング素子の駆動に用いられる半導体装置において、特性補正用入力信号に基づき前記半導体スイッチング素子の特性補正を行う特性補正手段を有することを特徴とする。

【0013】

本発明の第1の態様は、半導体スイッチング素子と、入力信号に基づきこの半導体スイッチング素子の駆動制御を行う駆動制御手段と、特性補正用入力信号に基づき前記駆動制御手段に対し伝達遅延時間を随意に設定して各半導体素子における遅延時間のバラツキをなくす特性補正手段を有することを特徴とする。

【0014】

本発明の第2の態様は、半導体スイッチング素子と、この半導体スイッチング素子に流れる電流を検出する電流検出手段と、この電流検出手段からの検出信号が規定のトリップレベルを上回ったとき、前記半導体スイッチング素子の動作を停止させる過電流保護手段と、前記トリップレベルの補正を行う特性補正手段を有することを特徴とする。

【0015】

本発明の第3の態様は、半導体スイッチング素子と、この半導体スイッチング素子の動作温度を検出する温度検知手段と、この温度検知手段からの検知信号が規定のトリップレベルを上回ったとき、前記半導体スイッチング素子の動作を停止させる過温度保護手段と、前記トリップレベルの補正を行う特性補正手段を有することを特徴とする。

【0016】

本発明の第4の態様(請求項1対応)は、半導体スイッチング素子と、入力信号に基づきこの半導体スイッチング素子の駆動制御を行う駆動制御手段とからなる半導体装置において、

前記駆動制御手段に、駆動能力の異なる複数個の駆動デバイスを備え、その駆動デバイスの中からいずれか1つ、もしくは複数個を選択して用いることにより、半導体スイッチング素子の動作特性を補正する特性補正手段を備えたことを特徴とする。

【発明の効果】

【0017】

本発明は、半導体スイッチング素子の特性について補正するようにしたので、各半導体装置における種々のバラツキを補正でき、高精度なインバータ装置を提供できる。

【0018】

本発明の第1の態様は、駆動回路に適切な遅延時間を設定することにより、半導体スイッチング素子における遅延時間のバラツキをなくすようにしたので、入力休止時間期間(Tdead)の設定が不要となり、高精度のインバータ制御が可能となる。

【0019】

本発明の第2の態様は、過電流の判断基準とするトリップレベルを随意に補正できるようにしたので、短絡保護を高精度で行なうことができる。

【0020】

本発明の第3の態様は、過温度の判断基準とするトリップレベルを随意に補正できるようにしたので、過温度保護を高精度で行なうことができる。

【0021】

本発明の第4の態様は、駆動回路に電流容量の異なる複数個の駆動デバイスを備え、その中から適切なものを選択できるようにしたので、半導体スイッチング素子のコレクタ電流の立ち上がり、および立下りの傾斜を随意に設定できる。

【0022】

前記特性補正手段としては、請求項2のごとく不揮発性メモリや、請求項3のごとくワンタイムROMで簡便に実現できる。また、これらの不揮発性メモリやワンタイムROMで実現した特性補正手段は、請求項4のごとく容易に半導体装置に集積化して内蔵できる。

【発明を実施するための最良の形態】

【0023】

実施形態1

図1は、本発明の第1実施形態を示した制御ブロック図を示す。駆動制御回路1は、信号入力端子からの入力信号UPinおよび信号入力端子からの入力信号UNinの信号に基づき、当該パワーモジュールの出力端子であるP2、N2間にシリアルに接続されたU相のIGBT1、IGBT2のそれぞれのゲートに出力信号UPoutおよびUNoutを供給する。この図1では、U相についてのみ記したが、V相のIGBT3、IGBT4およびW相のIGBT5、IGBT6を駆動するための回路を含む。

【0024】

駆動制御回路1および特性補正回路2の詳しい回路図を図2に示している。駆動制御回路1において、論理回路11は、入力信号UPinを遅延挿入回路12内ラインL1にロジック信号として出力する。遅延挿入回路12内において、ラインL1とアースとの間に、キャパシタンスC1、C2、C3がそれぞれスイッチS1、S2、S3を介して接続される。また、ラインL1には電流I1が供給される。

【0025】

前記ラインL1は反転器INV1を介し、遅延挿入回路13内のラインL2に接続される。この遅延挿入回路13においても、ラインL2とアースとの間に、キャパシタンスC4、C5、C6がそれぞれスイッチS4、S5、S6を介して接続されている。また、ラインL2には電流I2が供給される。そのラインL2は反転器INV2を介して駆動回路14に接続される。この駆動回路14からIGBT1を駆動する駆動信号UPoutが出力される。

【0026】

キャパシタンスC1、C2、C3およびキャパシタンスC4、C5、C6の各容量は同一であってもよく、あるいは個別に異なる容量であってもよい。また、キャパシタンスの個数は3個に限定されない。

【0027】

特性補正回路2では、特性補正信号が書込回路21により、EPROM22に書き込まれ、そのEPROM22のデータがレジスタ23にラッチされる。このレジスタ23よりのラッチデータd1〜d6が前記スイッチS1〜S6の駆動信号として供給される。従って、特性補正信号によって、前記スイッチS1〜S6を所望の状態にスイッチオン、スイッチオフできる。

【0028】

図2の駆動制御回路1の動作を図3のタイミングチャートに従って説明する。入力信号UNinは、図14のものと異なり、入力休止時間(Tdead)は含まれず、入力信号UPinとレベルが反転しているだけで完全に同期している。遅延時間t11は、入力信号UPinのハイからローへのレベル反転から、出力信号UPoutがローからハイへのレベル反転までに要した駆動制御回路1内の遅延時間であり、スイッチS1〜S3がすべてオフのとき、遅延挿入回路12での遅延時間は0のため、この時の遅延時間t11の大きさは、図14における遅延時間t1に相当する。

【0029】

遅延時間t12は、入力信号UPinのローからハイへのレベル反転から出力信号UPoutがハイから、ローへのレベル反転までに要した駆動制御回路1内の遅延時間であり、スイッチS4〜S6がすべてオフのとき、この遅延挿入回路33での遅延時間は0のため、この時の遅延時間t12の大きさは、図14における遅延時間t2に相当する。

【0030】

図2の駆動制御回路1では、入力信号UPinのみに対する回路のみ示しており、他の入力信号UNin、VPin、VNin、WPin、WNin に対してもそれぞれ同じ回路(遅延挿入回路や特性補正回路)を備える。従って、遅延時間t13は、入力信号UNinのローからハイへのレベル反転から出力信号UNoutがハイからローへのレベル反転までの遅延時間であり、遅延時間t14は、入力信号UNinのハイからローへのレベル反転から出力信号UNoutがローからハイへのレベル反転までの遅延時間である。これらの遅延時間もt11およびt12と同様に随意に設定できる。

【0031】

IGBT1は、UPinのハイからローへの反転レベルから遅延時間t11後に、出力信号UPoutがローからハイにレベル反転し、さらにtonP(IGBT1の応答時間)後にIGBT1がスイッチオンする。従って、入力信号UPinのハイからローへのレベル反転からtconP後にIGBT1がスイッチオンする。

【0032】

そして、そのIGBT1は、UPinのローからハイへの反転レベルから遅延時間t12後に、出力信号UPoutがハイからローにレベル反転し、さらにtoffP(IGBT1の応答時間)後にIGBT1がスイッチオフする。従って、入力信号UPinのローからハイへのレベル反転からtcoffP後にIGBT1がスイッチオフする。

【0033】

同様に、IGBT2は、UNinのローからハイへの反転レベルから遅延時間t13後に、出力信号UNoutがハイからローにレベル反転し、さらにtoffN(IGBT2の応答時間)後にIGBT2がスイッチオフする。従って、入力信号UNinのローからハイへのレベル反転からtcoffN後にIGBT2がスイッチオフする。

【0034】

そして、そのIGBT2は、UNinのハイからローへの反転レベルから遅延時間t14後に、出力信号UNoutがローからハイにレベル反転し、さらにtonN(これもIGBT2の応答時間)後にIGBT2がスイッチオンする。従って、入力信号UNinのハイからローへのレベル反転からtconN後にIGBT1がスイッチオンする。

【0035】

入力信号UPinおよびUNinを図3のごとく同期させても、駆動制御回路1における遅延時間やIGBT自身の反応時間にバラツキがあるため、tconP≠tcoffNであり、IGBT1のスイッチオンとIGBT2のスイッチオフとが合致しない。同様に、tcoffP≠tconNであるため、IGBT1のスイッチオフとIGBT2のスイッチオンとが合致しない。

【0036】

しかし、特性補正信号により、

全スイッチをオフ

いずれか1つのスイッチをオン

いずれか2つのスイッチをオン

全スイッチをオン

のどれかを選択することにより、t11およびt13の遅延時間を加減でき、この操作により、図3のごとく、tconP≒tcoffNとすれば、同じタイミングでIGBT1はスイッチオンし、IGBT2はスイッチオフする。同様に、t12およびt14の遅延時間を加減して、tcoffP≒tconNとすれば、同じタイミングでIGBT1はスイッチオフし、IGBT2はスイッチオンする。

【0037】

このように、tconP≒tcoffN、tcoffP≒tconNとすれば、駆動制御手段1およびIGBT自身の応答時間を含めたデバイス全体での遅延時間のバラツキをなくせることができ、そのため、入力休止時間(Tdead)が不要であり、高精度なインバータ制御が可能となる。尚、温度変化や経年変化により、遅延時間が僅かながらドリフトするため、そのドリフトをカバーできる程度のTdeadの設定が望ましい。但し、この場合のTdeadは従来のものと比較して格段に短いため、高精度なインバータ制御を行う際に障害とならない。

【0038】

特性補正回路2のEPROM22には、不揮発性メモリもしくはワンタイムROMを用いることができ、そのような特性補正回路2を、この駆動制御回路1に集積内蔵することもできる。

【0039】

実施形態2

図4は、本発明の第2実施形態を示した制御ブロック図を示し、その詳細を図5に示している。駆動制御回路4は、入力信号Cをロジック信号として出力する論理回路41と、そのロジック信号に従って駆動信号cを出力する駆動回路42とからなる。

【0040】

過電流保護回路3は比較器31からなり、その非反転入力部には、IGBT2の第2エミッタに接続したセンス抵抗Rsの一端に生じたVsが入力される。基準電圧Vref は、4つの直列接続の抵抗で分圧され、それらの分圧された電圧Vref1〜Vref3がスイッチS1〜S3によって選択され、比較器31の反転入力部にトリップレベルとして入力される。この比較器31の出力は、前記論理回路41に遮断信号として出力される。

【0041】

特性補正回路5は前記スイッチS1〜S3のいずれか1つをオンにするための回路であり、その回路構成は、図2の特性補正回路2と同様である。この特性補正回路5もEPROMに不揮発性メモリもしくはワンタイムROMを用いることができ、本駆動制御回路4に集積内蔵することもできる。

【0042】

既述したように、従来は、センス抵抗Rs、過電流保護回路3で設定されているトリップレベルおよびエミッタの分流比に個体バラツキがあり、そのため短絡電流保護値にもバラツキが生じ、正確な短絡保護が困難であったが、本実施形態では、図6に示すように、トリップレベルをVref1、Vref2、Vref3 に変更可能とし、実測結果に基づき適切なトリップレベルを設定することにより、正確な過電流保護が可能となる。尚、変更可能なトリップレベルの個数は3個に限定されない。

【0043】

実施形態3

図7は、本発明の第3実施形態を示した制御ブロック図を示し、図7の詳細を図8に示す。図7および図8において、図4および図5と共通する要素については共通の符号を付している。過温度保護回路7自身は、過電流保護回路3と同一の回路構成であるが、比較器71の非反転入力部には温度検知手段8で検出した温度信号Vtが取り込まれる。

【0044】

IGBT1の動作温度が高くなり、前記温度信号Vtが所定のトリップレベルを上回れば、所定の遮断信号が駆動制御回路4に供給されることにより、入力信号Dに対し、その駆動信号dが遮断されるが、この過温度保護回路7においても、過温度保護トリップレベルおよび温度検知手段8のバラツキがあるため正確な過温度保護が困難であった。

【0045】

そこで本実施形態では、図9に示すように、トリップレベルをVref1、Vref2、Vref3 に変更可能とし、実測結果に基づき適切なトリップレベルを設定することにより、正確な過温度保護が可能となる。

【0046】

実施形態4

図10は、本発明の第4実施形態を示した制御ブロック図を示し、その詳細を図11に示す。駆動制御回路9は、入力信号Eをロジック信号として出力する論理回路91と、駆動回路92とからなる。NタイプのFETトランジスタT1、T3、T5の各ドレインは、当駆動制御回路9の出力端子に接続され、各ゲートは、各スイッチS1、S3、S5を介して論理回路91の出力部か、各トランジスタのソースに接続される。

【0047】

PタイプのFETトランジスタT2、T4、T6の各ドレインは、当駆動制御回路9の出力端子に接続され、各ゲートは、各スイッチS2、S4、S6を介して論理回路91の出力部か、各トランジスタのソースに接続される。各スイッチS1〜S6は、特性補正回路10のレジスタよりの信号d1〜d6により駆動される。

【0048】

入力信号Eの立ち下がりにより、トランジスタT1、T3、T5の内、論理回路91の出力部に接続されていたトランジスタが駆動され、そして、前記入力信号Eの立ち上がりにより、トランジスタT2、T4、T6の内、論理回路91の出力部に接続されていたトランジスタが駆動され、それらの駆動されたトランジスタの出力電流が駆動信号eとして出力される。

【0049】

このときのタイミングチャートを図12に示している。駆動信号e1は、トランジスタT1およびT2が駆動されたときのものであり、駆動信号e2は、トランジスタT3およびT4が駆動されたときのものである。トランジスタT1およびT2に比べ、トランジスタT3およびT4の駆動能力が大きく、それゆえ、駆動信号e2の立ち上がりおよび立ち下がりが、駆動信号e1と比較して緩くなっている。駆動信号e1およびe2におけるIGBT2のコレクタ電流をI1、I2に示している。

【0050】

従来は、IGBTの電流容量毎に駆動制御回路の駆動能力を変える必要があったが、本実施形態によれば、種々の駆動容量を持ったIGBTの中から適切なものを選択することにより、IGBT2のコレクタ(出力)電流の立ち上がり、立ち下がりの傾きを随意に選択できる。この特性補正回路10もEPROMに不揮発性メモリもしくはワンタイムROMを用いることができ、本駆動制御回路9に集積内蔵することもできる。

【0051】

駆動されるトランジスタは、T1−T2、T3−T4、T5−T6の組み合わせ以外に、T1−T4のような組み合わせであってもよく、あるいは(T1+T3)−(T2+T4)のように複数個を同時に駆動させるような組み合わせも可能である。

【図面の簡単な説明】

【0052】

【図1】本発明の第1実施形態を示した制御ブロック図

【図2】図1の詳細を示した回路図

【図3】図1における信号のタイミングチャート

【図4】本発明の第2実施形態を示した制御ブロック図

【図5】図4の詳細を示した回路図

【図6】図4における信号のタイミングチャート

【図7】本発明の第3実施形態を示した制御ブロック図

【図8】図7の詳細を示した回路図

【図9】図7における信号のタイミングチャート

【図10】本発明の第4実施形態を示した制御ブロック図

【図11】図7の詳細を示した回路図

【図12】図10における信号のタイミングチャート

【図13】従来のパワーモジュールの構成を示した回路図

【図14】図13における入出力動作を示したタイミングチャート

【図15】短絡保護動作時を示したタイミングチャート

【符号の説明】

【0053】

1 駆動制御回路、2 特性補正回路、3 過電流保護回路、4 駆動制御回路、5 特性補正回路、7 過温度保護回路、8 温度検知手段、9 駆動制御回路、10 特性補正回路、11 論理回路、12 遅延挿入回路、13 遅延挿入回路、21 書込回路、22 EPROM、23 レジスタ、91 論理回路、92 駆動回路

【特許請求の範囲】

【請求項1】

半導体スイッチング素子と、入力信号に基づきこの半導体スイッチング素子の駆動制御を行う駆動制御手段とからなる半導体装置において、

前記駆動制御手段に、駆動能力の異なる複数個の駆動デバイスを備え、その駆動デバイスの中からいずれか1つ、もしくは複数個を選択して用いることにより、半導体スイッチング素子の動作特性を補正する特性補正手段を備えたことを特徴とする半導体装置。

【請求項2】

前記特性補正手段は不揮発性メモリである請求項1に記載の半導体装置。

【請求項3】

前記特性補正手段はワンタイムROMである請求項1または2に記載の半導体装置。

【請求項4】

不揮発性メモリもしくはワンタイムROMで実現される上記特性補正手段を集積内蔵したことを特徴とする請求項2または3に記載の半導体装置。

【請求項1】

半導体スイッチング素子と、入力信号に基づきこの半導体スイッチング素子の駆動制御を行う駆動制御手段とからなる半導体装置において、

前記駆動制御手段に、駆動能力の異なる複数個の駆動デバイスを備え、その駆動デバイスの中からいずれか1つ、もしくは複数個を選択して用いることにより、半導体スイッチング素子の動作特性を補正する特性補正手段を備えたことを特徴とする半導体装置。

【請求項2】

前記特性補正手段は不揮発性メモリである請求項1に記載の半導体装置。

【請求項3】

前記特性補正手段はワンタイムROMである請求項1または2に記載の半導体装置。

【請求項4】

不揮発性メモリもしくはワンタイムROMで実現される上記特性補正手段を集積内蔵したことを特徴とする請求項2または3に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2006−20336(P2006−20336A)

【公開日】平成18年1月19日(2006.1.19)

【国際特許分類】

【出願番号】特願2005−200563(P2005−200563)

【出願日】平成17年7月8日(2005.7.8)

【分割の表示】特願2002−174386(P2002−174386)の分割

【原出願日】平成14年6月14日(2002.6.14)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成18年1月19日(2006.1.19)

【国際特許分類】

【出願日】平成17年7月8日(2005.7.8)

【分割の表示】特願2002−174386(P2002−174386)の分割

【原出願日】平成14年6月14日(2002.6.14)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]