半導体装置

【課題】 寄生トランジスタのオン動作を防止し、回路消費電流を低減するブートストラップ方式の半導体装置を提供する。

【解決手段】 パワーデバイスの低圧側(112)の電力素子を駆動して高圧側駆動部(111)の電源を供給するブートストラップ回路は、少なくともブートストラップコンデンサに電源を供給する低圧半導体素子部(7)と高圧島ドリフト部(Rn,8)を備え、低圧半導体素子部と高圧島ドリフト部は接合分離され、pch−MOSトランジスタ(Tr7)のバックゲート(16)はダイオードが接続されていないオープン構成としている。

【解決手段】 パワーデバイスの低圧側(112)の電力素子を駆動して高圧側駆動部(111)の電源を供給するブートストラップ回路は、少なくともブートストラップコンデンサに電源を供給する低圧半導体素子部(7)と高圧島ドリフト部(Rn,8)を備え、低圧半導体素子部と高圧島ドリフト部は接合分離され、pch−MOSトランジスタ(Tr7)のバックゲート(16)はダイオードが接続されていないオープン構成としている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はパワーデバイスを駆動する半導体装置に関し、特に、ブートストラップ回路方式を用いたインバータ等のパワーデバイスを駆動する半導体装置に関するものである。

【背景技術】

【0002】

一般に、ブートストラップダイオード方式では、ブートストラップダイオードは高耐圧ICチップの外部側に設けられていたが、1チップ化を目的としてブートストラップダイオードを高耐圧ICチップ内に搭載したブートストラップダイオード方式が開発されている。このようなブートストラップ回路方式の高耐圧ICチップについて、図25及び図26を用いて以下に説明する。図25は従来のブートストラップダイオードの断面構造を示し、図26は従来のパワーデバイス(電力変換器)と図25に示すブートストラップダイオードを搭載した高耐圧ICとを連結した概略回路構成を示す。

【0003】

図25に示すブートストラップ方式は、高耐圧ICチップに搭載したブートストラップダイオード部101と、高圧側駆動用CMOS領域102とを備える。p−基板105上に形成されたn−半導体層106内にp−ウェル103と層間絶縁膜のp+型拡散層104とを離間させて設けられている。これにより、p−ウェル103とp+型拡散層104間に電源電圧Vccを印加でき、高圧ダイオードはブートストラップダイオード(D101)として使用可能としている。ここで、高耐圧ICチップのp−基板105は通常は接地(GND)電位に接続されている。

【0004】

図26において、C1は外部ブートストラップコンデンサ(以後、「外部コンデンサ」と略称する)であり、上側(高圧側)パワートランジスタT1と下側(低圧側)パワートランジスタT2は、高電圧端子HVと接地GND間に直列に接続され、これらのトランジスタT1とT2はそれぞれ固有の基板ダイオードD1とD2を有する。図示のように、高耐圧ICは、高圧側駆動回路111と低圧側駆動回路112とレベルシフト回路113と遅延回路114と高耐圧のブートストラップダイオードD101を備え、トランジスタT1とT2等より成るパワーデバイスを駆動するように接続されている。

【0005】

外部コンデンサC1の一端はICチップ上のブートストラップダイオードD101を介して電源電圧Vccに接続され、下側トランジスタT2が導通(オン)状態にあるときに出力端子OUTがほぼ接地電位に維持された場合に、充電電流を外部コンデンサC1に流し、外部コンデンサC1は電源電圧Vccよりも電圧降下分だけ僅かに小さい充電電圧V1を保持する。これにより、低圧側駆動回路112は比較的低い電源電圧Vccにより駆動され、高圧側駆動回路111は外部コンデンサC1に充電された電圧V1により駆動される。

【0006】

このように、図25及び図26に示す高耐圧ICでは、ブートストラップダイオードD101のアノード107を制限抵抗R1を介して電源電圧Vccに接続し、カソード108を高圧側浮遊供給絶対電圧VB端子に接続し、この高圧側浮遊供給絶対電圧VB端子と高圧側浮遊供給オフセット電圧VS端子(出力端子OUT)との間に外部コンデンサC1を接続している。このような構成において、電力変換器の出力素子の低圧側トランジスタT2がオンするときに、高圧であるブートストラップダイオードD101を通じて外部コンデンサC1を充電し、この外部コンデンサC1に充電された電圧V1により高圧側駆動回路111を駆動することにより、高圧側浮遊電源を別途設けることを必要としない方式を提供している。

【0007】

他の従来構成としては、過渡期間中における集積LDMOS構造の寄生トランジスタのON防止用のデバイスを有し、集積デバイスの破壊防止を保証する集積LDMOSトランジスタを使用し、LDMOSと下側電力素子のタイミングを同期させたブートストラップ・キャパシタンスの充電回路が開示されている(例えば、特許文献1参照)。

【0008】

【特許文献1】特開平9−65571号公報(段落0009〜0014、図3〜5)

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかし、図25及び図26に示すようなブートストラップダイオードD101を高耐圧ICに搭載したブートストラップ回路方式は、ダイオードD101のアノード107がp−基板105よりも電源電圧分だけ電位的に高く、高圧を保持するためにRESURF構造となっている。この場合、電源電圧Vccを印可すると寄生のPNPトランジスタ109がオン(ON)動作し、ベース濃度が低いため、寄生のPNPトランジスタの電流増幅率HFEが大きくなり、アノード107からp−ウェル103及びn−半導体層106を介してp−基板105方向に非常に大きな電流が流れてしまうといった問題があった。

【0010】

本発明は、上記課題を解決するためになされたもので、寄生のトランジスタのオン動作を防止し、回路の消費電流を低減することができるブートストラップ方式による高耐圧ICチップの半導体装置を提供することを目的とする。即ち、高圧保持と充電の役割を接合分離で別々の素子に行うことで、寄生のPNPトランジスタの動作を極力無くす構成とする。これは、高圧保持部はRESURF構造ではあるが、n−ドリフト層となっているため寄生のPNPトランジスタは発生しないことによる。また、充電するための半導体素子としては、ダイオード型とpch−MOSトランジスタ型の大きく2通りのものを搭載しているが、どちらの型式においても寄生のPNPトランジスタの動作を極力無くすため、埋込みn+層を追加してベース濃度を濃くし、寄生のPNPトランジスタの電流増幅率HFEを低くしている。

【課題を解決するための手段】

【0011】

上記目的を達成するために、本発明による半導体装置は、パワーデバイスを駆動する半導体装置であって、前記パワーデバイスの低圧側の電力素子を駆動して高圧側浮遊供給絶対電圧と高圧側浮遊供給オフセット電圧間に接続されたブートストラップコンデンサに高圧側駆動部の電源を供給するブートストラップ回路を有する。ブートストラップ回路は、少なくとも前記ブートストラップコンデンサに電源を供給する低圧半導体素子部と高圧保持部を備え、低圧半導体素子部と高圧保持部は接合分離されている。高圧保持部は高圧島のn−半導体内の高圧側と開口部にそれぞれn+層を設けたn−ドリフト層である。また、ブートストラップ回路の低圧半導体素子部は少なくともPch−MOSトランジスタを備え、Pch−MOSトランジスタの第1のp+層が電源電圧に接続され、第2のp+層がn−ドリフト層を介して高圧側浮遊供給絶対電圧端子に接続され、Pch−MOSトランジスタのバックゲートは、ダイオードが接続されていないオープン構成であることを特徴とする。

【発明の効果】

【0012】

本発明によれば、高圧側浮遊電源を必要とせず、電源電圧Vccから、高圧側浮遊供給絶対電圧と高圧側浮遊供給オフセット電圧間に接続されたブートストラップコンデンサに電源電圧Vccをそのまま充電することが可能となり、寄生トランジスタのオン動作を防止する。また、Pch−MOSトランジスタがオフ状態のときに、ボディ・ドレインダイオードを通じて、充電電荷が流出することを防止できるとともに、Pch−MOSトランジスタのバックゲートにはダイオードが接続されていないので、その分だけ回路面積を縮小できる。

【発明を実施するための最良の形態】

【0013】

以下、本発明の実施の形態について、図1乃至図24を用いて、ブートストラップ方式を例示して説明する。ブートストラップ方式は、充電可能な半導体素子部と高圧保持用n−ドリフト層を接合分離でモノシリック高耐圧IC(1チップ構成の高耐圧IC)チップに搭載した構成である。ただし、本発明はこれに限定されるものではなく、他のMOSトランジスタ等を備える半導体装置にも適用可能である。なお、各図において共通する要素には同一の符号を付し、重複する説明については省略している。

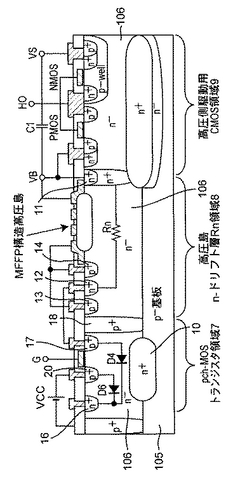

【0014】

(実施の形態1)

本実施の形態1の特徴は、ブートストラップ回路内の充電可能な半導体素子部を構成するPch−MOSトランジスタ領域(7)において、n−半導体層(106)内に第1のp+層(20)と第2のp+層(17)とバックゲートn+層(16)を埋設し、このバックゲートn+層(16)には、従来はPch−MOSトランジスタがOFFの際に電荷流出を防止するためのダイオードが接続されていたが、本実施の形態1ではこのような電荷流出防止用のダイオードを設けることなく、バックゲートn+層(16)をオープン構成としたことである。

【0015】

先ず、本発明の実施の形態1の基本構成について図1及び図2を用いて以下に説明する。図1は本発明の実施の形態1に係る半導体装置とパワーデバイスとを連結した概略回路構成、図2は本実施の形態1に係るブートストラップ回路要部の断面構造を示す。図示の構成では、Pch−MOSトランジスタTr7の領域7と高圧島を利用したn−ドリフト層Rn領域8をモノシリック高耐圧ICチップに搭載したブートストラップ方式を示す。この方式では、高電圧を保持するために設けられたn−ドリフト層Rn領域8では、端子領域12(n+層)がPch−MOSトランジスタTr7の第2のp+層17と接続され、端子領域11(n+層)が高圧側駆動回路111の高圧側浮遊供給絶対電圧VBと接続された構成である。

【0016】

図1及び図2に示すように本実施の形態1は、Pch−MOSトランジスタ領域7の第1のp+層20を電源電圧Vccに接続し、第2のp+層17と接続されたn−ドリフト層Rnを介して外部コンデンサC1に電流が流れ、外部コンデンサC1の充電を行うブートストラップ方式である。

【0017】

上記構成において、図1に示すように、遅延回路114の一端子はPch−MOSトランジスタ(Tr7)領域7のゲートに接続され、低圧側駆動回路112とレベルシフト回路113と遅延回路114の各一端子は接地電位(GND)に接続されている。このような構成により、電力変換器(パワーデバイス)の出力素子の低圧側トランジスタT2がON動作するのと同期してPch−MOSトランジスタ領域7がON動作するように駆動制御している。

【0018】

一方、VB端子とVS端子間に接続された外部コンデンサC1の一端は、モノシリック高耐圧ICチップ上のn−ドリフト層RnとPch−MOSトランジスタ領域7を介して、例えば電源電圧15VのVccに接続され、下側トランジスタT2が導通(ON)状態となり出力端子OUTがほぼ接地電位に維持されたときに、充電電流を外部コンデンサC1に流す。外部コンデンサC1は電源電圧Vccを電圧降下させずにそのまま充電電圧として保持する。これにより、低圧側駆動回路112は比較的低い電源電圧Vccにより駆動されるとともに、高圧側駆動回路111は外部コンデンサC1に充電された電圧Vccにより駆動される。

【0019】

このように、電力変換器の出力素子の低圧側トランジスタT2がONするのと同期してPch−MOSトランジスタ領域7がONするように制御することにより、Pch−MOSトランジスタ領域7がONすると、Pch−MOSトランジスタ領域7の第1のp+層20と接続されている電源電圧Vccからn−ドリフト層Rnを介して外部コンデンサC1に電流が流れ、外部コンデンサC1の充電が行われる。この充電された電圧Vccを高圧側駆動回路111の電源電圧として使用することにより、高圧側浮遊電源を別途設けることを必要としないブートストラップ方式を提供できる。

【0020】

ここで、図2に示すブートストラップ回路の断面構造では、Pch−MOSトランジスタ領域7と高圧島n−ドリフト層領域8と高圧側駆動用CMOSトランジスタ領域9とを有し、Pch−MOSトランジスタ領域7において、埋込n+層10をn−半導体層106とp−基板105との間に介在させている。また、高圧島n−ドリフト層領域8において、p−基板105と同電位のp+層13及び14は、空乏層を広げ、n+領域12の電界集中を緩和させるために設けられている。また、Pch−MOSトランジスタ領域7と高圧島状n−ドリフト層領域8とを接合分離するp+拡散領域18が層間絶縁膜として、n−半導体層106内にp−基板105に達する深さにまで形成されている。

【0021】

このように構成されたブートストラップ回路の断面構造から明らかなように、Pch−MOSトランジスタ領域7の埋込n+層10をPch−MOSトランジスタ領域7のn−半導体層106とp−基板105間に介在させたことにより、ベース濃度を濃くして寄生のPNPトランジスタ(109)の高電界HFEを下げ、寄生のPNPトランジスタのON動作を従来構成より遥かに抑制することができ、第1のp+層20からPch−MOSトランジスタ領域7のn−半導体層106を介してp−基板105方向に電流が流れることを防止している。

【0022】

さらに本実施の形態では、Pch−MOSトランジスタ領域7はPch−MOSトランジスタ領域7のn−半導体層106内に第1のp+層20及び第2のp+層17とバックゲートn+層16を埋設し、Pch−MOSトランジスタ領域7のバックゲートn+層16をオープン構成としたことを特徴としている。バックゲートn+層16をオープン構成としても、ボディ・ドレインダイオードD4を介して流れる電流と逆方向に寄生のダイオードD6が第1のp+層(20)とバックゲートn+層(16)間に生成されるため、Pch−MOSトランジスタ領域7がオンからオフに切り替わる際に、Pch−MOSトランジスタ領域7のボディ・ドレインダイオードD4を介して流れる逆方向電流を、寄生ダイオードD6により防止できる。

【0023】

このように、Pch−MOSトランジスタ領域7のバックゲートn+層16をオープン構成としたことにより、Pch−MOSトランジスタ領域7がON状態のときに、端子VBと端子VS間に電源電圧Vccをそのまま充電することができ、寄生のPNPトランジスタのON動作を従来構成より遙かに抑制すると共に、モノシリックICチップに搭載可能となる。さらに、Pch−MOSトランジスタ領域7がOFF状態のときに、ボディ・ドレインダイオードD4を介して充電電荷が流出することを防止することができる。また、Pch−MOSトランジスタのバックゲートn+層(16)には電荷流出防止用のダイオードが接続されていないため、ダイオードが設けられていない分だけ回路面積を縮小できる。

【0024】

また、Pch−MOSトランジスタTr7領域7はn−半導体層106内にアノードp+層20とカソードn+層16を設け、埋込n+層10をPch−MOSトランジスタTr7領域7のn−半導体層106とp−基板105間に介在させたことにより、ベース濃度を濃くして寄生のPNPトランジスタ従来構成における図27に示した寄生PNPトランジスタ109のHFEを下げている。これにより、寄生のPNPトランジスタのON動作を従来構成より遥かに抑制することができ、アノードp+層20からPch−MOSトランジスタTr7領域7のn−半導体層106を介してp−基板105方向に電流が流れることを防止している。

【0025】

一方、高圧島n−ドリフト層領域8は、多重浮遊フィールドプレートMFFP(Multiple Floating Field Plate)の2重埋め込み構造を採用している。即ち、高圧島n−ドリフト層Rn領域8では、高圧島のn−半導体層106内の高電位側のn+層11と、開口部のn+層12の両側をp−基板と同電位(接地電位GND)に固定された一対のp+層13と14で囲む。これにより、空乏層を広げ、開口部のn+層12の電界集中を緩和させ、高圧側の電力素子がONし低圧側の電力素子がOFFすると、開口部のn+層12はフローティング電位となるが、その電位を低電位(約40V以下)に抑制することができ、高電圧、即ち600V以上の高電圧を保持することができる。

【0026】

このように、本実施の形態1に係るブートストラップ方式では、Pch−MOSトランジスタ領域7と高圧島n−ドリフト層領域8を高耐圧ICチップに搭載した構成により、回路消費電流を効果的に低減することが可能となる。また、図2において、Pch−MOSトランジスタ領域7と高圧島n−ドリフト層Rn領域8を接合分離した構成により、モノシリック高耐圧ICチップに搭載可能となる。

【0027】

なお、本実施の形態1は種々の変形が可能であり、例えば、充電可能な半導体素子部の構造は同じで、高圧島n−ドリフト層Rn領域8の構造が異なっている変形例1〜7等、さらに、Pch−MOSトランジスタ領域7の構成を、図2に示す構造以外に、例えば、図14に示す変形例8のように構成することも可能である。以下、本実施の形態1の変形例1〜8についてそれらの要点を説明する。

【0028】

(変形例1)

図3は変形例1に係るブートストラップ回路要部の断面構造を示す。図2に示す実施の形態1の構成では、高圧島n−ドリフト層Rn領域8において、空乏層を広げ、高圧島開口部のn+層12の電界集中を緩和させるために、p−基板と同電位に固定された一対のp+層13,14を設けているが、図3に示す変形例1のように、一方のp+層13を省略し、p+層14のみを設けた構成としてもよい。

【0029】

このような一方のp+層13を取り除いた構成においても、ダイオードD3領域6と高圧島n−ドリフト層Rn領域8とを接合分離するp+拡散領域18がp+層13の機能を兼ね、上記と同様の役割、即ち、n+層12の電界集中を緩和させる役割を果たしている。従って、p+層13を取り除いた分だけ、ICチップの高圧島n−ドリフト層領域8の面積を縮小することができる。

【0030】

(変形例2)

図4及び図5は変形例2(A),(B)に係るブートストラップ回路要部の断面構造を示し、その基本構成は図1乃至図2に示す実施の形態1と同様である。実施の形態1との相違点は、図4に示すように変形例2(A)の構成では、高圧島n−ドリフト層Rn領域8において、新たな埋込p+層19を高圧島のn−半導体層106とp−基板105との間に介在させたことであり、図5に示す変形例2(B)では、高圧島n−ドリフト層Rn領域8において、埋込p+層19を高圧島のn−半導体層106内に埋め込んだ構成である。

【0031】

図4及び図5に示すように、変形例2では、埋込p+層19を高圧島のn−半導体層106とp−基板105との間に介在させるか、またはp+層19を高圧島のn−半導体層106内に埋め込むことにより、n+層12直下の実効的な空乏層を低減することができ、n+領域12が高電位となることを回避することができる。

【0032】

(変形例3)

変形例3について図6及び図7を用いて説明する。図6及び図7は変形例3(A),(B)の要部断面構造を示し、その基本構成は図4及び図5に示す変形例2と同様である。変形例2との相違点は、変形例3では、変形例1で説明した特徴を変形例2と組合せて適用したことである。

【0033】

即ち、図4及び図5に示す変形例2の構成例では、高圧島n−ドリフト層Rn領域8において、p−基板と同電位に固定された一対のp+層13,14を設けているが、図6または図7に示す変形例3の構成例では、一方のp+層13を省略し、p+層14のみを設けた構成とし、高圧島n−ドリフト層Rn領域8において、埋込p+層19を高圧島のn−半導体層106とp−基板105との間に介在(図6)、または、埋込p+層19を高圧島のn−半導体層106内に埋め込んだ(図7)ことを特徴としている。

【0034】

このような一方のp+層13を取り除いた構成においても、ダイオードD3領域6と高圧島n−ドリフト層Rn領域8とを接合分離するp+拡散領域18がp+層13の機能を兼ね、上記と同様の役割、即ち、n+層12の電界集中を緩和させる役割を果たしている。従って、p+層13を取り除いた分だけ、ICチップの高圧島n−ドリフト層領域8の面積を縮小することができる。

【0035】

なお、図4及び図5に示す変形例2と図6及び図7に示す変形例3において、高圧島n−ドリフト層領域8内に埋込p+層19を生成する方法として、高エネルギーイオン注入法により、埋込p+層19をn−半導体層106内に注入形成する方法を用いることができる。

【0036】

(変形例4)

変形例4について図8を用いて説明する。図8は変形例4に係るブートストラップ回路の要部断面構造を示し、その基本構成は例えば図2に示す実施の形態1と同様である。変形例4では、n+層12が高電位となることを回避する別の好ましい構成例を示すものであり、図8に示す高圧島n−ドリフト層Rn領域8において、n+層12の電界集中を緩和させるために、p−基板と同電位に固定された一対のp+層13,14の埋め込み下部及び側面部を囲むようにp−ウェル層23,24を埋設したことである。

【0037】

これにより、n+層12近傍の実効的な空乏層を低減することができ、n+層12が高電位となることを回避できる。なお、p−ウェル層23,24のうちいずれか一方のみを埋設することによっても、同様の効果が得られる。

【0038】

(変形例5)

変形例5について図9を用いて説明する。図9は変形例5に係るブートストラップ回路の要部断面構造を示し、その基本構成は図8に示す変形例4と同様である。図9に示す変形例5では、一方のp+層13とその下部のp−ウェル層23の対を取り除き、p+層14とその下部のp−ウェル層24の対のみを形成した構成としている。

【0039】

このような一方のp+層13とその下部のPウェル層23の対を取り除いた構成においても、ダイオードD3領域6と高圧島n−ドリフト層Rn領域8とを接合分離するp+拡散領域18がp+層13の機能を兼ね、上記と同様の役割、即ち、n+層12の電界集中を緩和させる役割を果たしている。従って、p+層13及びその下部のPウェル層23を取り除いた分だけ、ICチップの高圧島n−ドリフト層領域8の面積を縮小することができる。

【0040】

(変形例6)

変形例6について図10及び図11を用いて説明する。図10及び図11は変形例6(A),(B)の要部断面構造を示し、その基本構成は図8に示す変形例4と同様である。図10及び図11に示す変形例6の構成では、上述の図4または図5に示す変形例2の特徴と図8に示す変形例4の特徴を組合せた構成である。

【0041】

即ち、本変形例6では、p−基板と同電位に固定された一対のp+層13,14の埋め込み下部及び側面全体を囲むようにp−ウェル層23,24を埋設するとともに、埋込p+層19を高圧島のn−半導体層106とp−基板105の間に介在(図10)、または、埋込p+層19を高圧島のn−半導体層106内に埋め込んだ(図11)ことを特徴としている。

【0042】

これにより、n+層12直下及びn+層12近傍の実効的な空乏層を低減することができ、n+層12が高電位となることを回避できる。なお、p−ウェル23,24のうちのいずれか一方のみを埋設することによっても、同様の効果が得られる。

【0043】

(変形例7)

変形例7について図12及び図13を用いて説明する。図12及び図13は変形例7(A),(B)の要部断面構造を示し、その基本構成は図10及び図11に示す変形例6と同様である。図12及び図13に示す変形例7では、一方のp+層13とその下部のp−ウェル層23の対を取り除き、p+層14とその下部のp−ウェル層24の対のみを形成した構成としている。

【0044】

このような一方のp+層13とその下部のPウェル層23の対を取り除いた構成においても、ダイオードD3領域6と高圧島n−ドリフト層Rn領域8とを接合分離するp+拡散領域18がp+層13の機能を兼ね、上記と同様の役割、即ち、n+層12の電界集中を緩和させる役割を果たしている。従って、p+層13及びその下部のPウェル層23を取り除いた分だけ、ICチップの高圧島n−ドリフト層領域8の面積を縮小することができる。

【0045】

また、変形例6と同様に、埋込p+層19を高圧島のn−半導体層106とp−基板105の間に介在(図12)、または、埋込p+層19を高圧島のn−半導体層106内に埋め込んだ(図13)ことを特徴としている。これにより、n+層12直下及びn+層12近傍の実効的な空乏層を低減することができ、n+層12が高電位となることを回避できる。

【0046】

(変形例8)

変形例8について図14を用いて説明する。図14は変形例8に係るブートストラップ回路要部の断面構造を示し、その基本構成は図1及び図2に示す実施の形態1と同様である。実施の形態1との相違点は、図14に示す変形例8では、Pch−MOSトランジスタ領域7のn−半導体層106内に設けられているバックゲートn+層16を、n−半導体層106内の埋込n+層10と部分的に接する深さまで埋設した構成としている。

【0047】

これにより、ベース濃度をより濃くして寄生のPNPトランジスタ(109)の高電界HFEを下げ、寄生のPNPトランジスタのON動作を防止することができ、第1のp+層20からPch−MOSトランジスタ領域7のn−半導体層106を介してp−基板105方向に電流が流れることを防止している。

【0048】

(実施の形態2)

本発明の実施の形態2について図15及び図16を用いて説明する。図15は本発明の実施の形態2に係る半導体装置とパワーデバイスとを連結した概略回路構成、図16は本実施の形態2に係るブートストラップ回路要部の断面構造を示し、その基本構成は図1乃至図2に示す実施の形態1と同様である。実施の形態1との相違点は、図15及び図16に示す本実施の形態2の構成では、Pch−MOSトランジスタTr7のバックゲートに接続する第1のダイオードD5領域50と第2のダイオードD7領域70をさらにモノシリック高耐圧ICチップに追加搭載したことである。

【0049】

即ち、Pch−MOSトランジスタ領域7の第1のp+層20とバックゲートn+層16間に第1のダイオードD5を設けて対応するダイオード領域50を形成し、また、Pch−MOSトランジスタ領域7の第2のp+層17とバックゲートn+層16間に第2のダイオードD7を設けて対応するダイオード領域70を形成している。

【0050】

上記構成において、ダイオードD5およびD7のカソードはともにPch−MOSトランジスタ(Tr7)のバックゲート(16)に接続され、ダイオードD5及びD7のアノードは、それぞれp+層27及び32を介してPch−MOSトランジスタ領域7の第1のp+層20及び第2のp+層17に接続されている。このように、ダイオードD5(領域50)の配置方向は、Pch−MOSトランジスタ領域7のOFFに切り替え時にボディ・ドレインダイオードD4を介して流れる逆回復電流とは逆方向となるように配置されている。

【0051】

即ち、例えば、ダイオードD5領域50は、Pch−MOSトランジスタ領域7がONからOFFに切り替わる際に、Pch−MOSトランジスタ領域7のボディ・ドレインダイオードD4を介して流れる逆回復電流を防止し、Pch−MOSトランジスタ領域7の第1のp+層20とダイオードD5領域50のアノードp+層27が電源電圧Vccに接続され、Pch−MOSトランジスタ領域7のバックゲートn+層16とダイオードD5領域50のカソードn+層28が接続されている。その他の構成は実施の形態1と同じである。

【0052】

これにより、Pch−MOSトランジスタ領域7がオンからオフに切り替わる際に、Pch−MOSトランジスタ領域7のボディ・ドレインダイオードD4及びダイオードD7を介して流れる逆方向電流をダイオードD5により防止する構成としている。

【0053】

このように構成されたブートストラップ回路の断面構造から明らかなように、Pch−MOSトランジスタ領域7がオン状態のときに、端子VBと端子VS間に電源電圧Vccをそのまま充電することができ、寄生のPNPトランジスタのオン動作を従来構成より遙かに抑制すると共に、モノシリックICチップに搭載可能となる。さらに、Pch−MOSトランジスタ領域7がオフ状態のときに、ボディ・ドレインダイオードD4を介して充電電荷が流出することを防止することができる。

【0054】

なお、本実施の形態2についても種々の変形例が可能であり、例えば、実施の形態1で説明した変形例1〜8の構造に対しても、本実施の形態2は同様に適用できる。

【0055】

また、図16に示す構成では、Pch−MOSトランジスタ領域7とダイオードD5領域50は接合分離されているが、それに限定されるものではなく、同じn−半導体層106内に存在した場合も同様の効果が得られる。

【0056】

(実施の形態3)

本発明の実施の形態3について図17及び図18を用いて説明する。図17は本発明の実施の形態3に係る半導体装置とパワーデバイスとを連結した概略回路構成、図18は本実施の形態3に係るブートストラップ回路要部の断面構造を示し、その基本構成は実施の形態1及び2と同様である。

【0057】

即ち、図17及び図18に示す本実施の形態3の基本構成では、Pch−MOSトランジスタ領域7のOFFに切り替え時にボディ・ドレインダイオードD4を介して流れる逆回復電流とは逆方向にダイオードD5領域50を追加搭載し、さらに、本実施の形態3の特徴ポイントは、Pch−MOSトランジスタ(Tr77)領域77とNch−MOSトランジスタ(Tr41)領域41をモノシリック高耐圧ICチップに追加搭載したことである。ただし、本実施の形態3では、実施の形態2で記載した第2のダイオードD7領域70は設けられていない。

【0058】

図17及び図18に示すように、Nch−MOSトランジスタ領域41はPch−MOSトランジスタ領域7を駆動する駆動回路である。Pch−MOSトランジスタ領域7の第2のp+層17はPch−MOSトランジスタ領域77を介してPch−MOSトランジスタ領域7のゲートに接続され、Pch−MOSトランジスタ領域7のゲートはNch−MOSトランジスタ領域41を介して接地電位(GND)に接続され、Nch−MOSトランジスタ領域41のバックゲートp+層29とソースn+層30も接地電位(GND)に接続されている。また、Nch−MOSトランジスタ領域41のゲートとPch−MOSトランジスタ領域77のゲートは遅延回路114の一端子に接続されている。

【0059】

図17及び図18から明らかなように、高圧島状n−ドリフト層領域8の開口部のn+層(11,12)はPch−MOSトランジスタTr7の第2のp+層17と接続され、第2のp+層17はさらにスイッチ素子として機能するPch−MOSトランジスタTr77を介してPch−MOSトランジスタTr7のゲートに接続され、このPch−MOSトランジスタTr7のゲートはさらにNch−MOSトランジスタTr41のドレインに接続されている。

【0060】

これにより、Nch−MOSトランジスタTr41の駆動(ON)するタイミングと低圧側の電力素子を駆動(ON)するタイミングとPch−MOSトランジスタTr77のOFFするタイミングが同期している。(原文クレーム3)さらに、Pch−MOSトランジスタTr77のゲートとNch−MOSトランジスタTr41のゲートが接続し、Nch−MOSトランジスタTr41のソース及びバックゲートは、低圧側駆動回路112,レベルシフト回路113及び遅延回路114の接地電位(GND)端子に接続されている。

【0061】

このようにスイッチ素子としてPch−MOSトランジスタTr77を設けたことにより、Nch−MOSトランジスタTr41の駆動(ON)するタイミングでスイッチOFFさせているので、接地電位(GND)側に電流が流れることがなく、従って、消費電流を抑制することができる。

【0062】

また、Pch−MOSトランジスタTr77のゲートとNch−MOSトランジスタTr41のゲートが短絡させたことにより、回路面積を縮小できる。

【0063】

このように構成されたブートストラップ回路の断面構造から明らかなように、Nch−MOSトランジスタ領域41がON状態の時、Pch−MOSトランジスタ領域77はOFF状態となり、Pch−MOSトランジスタ領域7はON状態となるので、端子VBと端子VS間に電源電圧Vccをほぼ充電することが可能となり、Nch−MOSトランジスタ領域41を介して電流が基板に流れない。

【0064】

従って、回路消費電流をさらに抑制することができ、寄生(PNP)トランジスタのON動作を従来構成より遥かに抑制するとともに、モノシリックICチップに搭載可能となる。また、Pch−MOSトランジスタ領域7がOFF状態のときに、ボディ・ドレインダイオードD4を通じて、充電電荷が流出することを防止できる。さらに、電力変換器の高圧側の出力素子がON状態の時に、充電とは逆方向にPch−MOSトランジスタ領域7がONするのを防止できる。

【0065】

なお、図18に示す構成では、Nch−MOSトランジスタ領域41とPch−MOSトランジスタ領域77とダイオードD5領域50とPch−MOSトランジスタ領域7は接合分離されているが、それに限定されるものではなく、同じn−半導体層106内に存在した場合も同様の効果が得られる。さらに、Nch−MOSトランジスタ領域41の構造においても、図18の構造に限定されるものではない。

【0066】

また、本実施の形態3は、充電可能な半導体素子部の構造のみが実施の形態1及び2と異なっているだけである。従って、高圧島n−ドリフト層Rn領域8の構造が異なっている実施の形態1で説明した変形例1〜7に対しても、本実施の形態3は同様に適用できる。

【0067】

さらに、Pch−MOSトランジスタ領域7及びPch−MOSトランジスタ領域77において、図18に示す構造の他に、実施の形態1で述べた変形例8の構造においても、図示は省略するが、本実施の形態3のPch−MOSトランジスタ領域7及びPch−MOSトランジスタ領域77は適用できる。

【0068】

また、ダイオードD5領域50において、図18に示す構造の他に、後述する変形例9〜12のダイオード構造においても、図示は省略するが、本実施の形態3のダイオードD5領域50は適用できる。変形例9〜12について以下に要点のみ説明する。

【0069】

(変形例9)

変形例9は、ダイオードD5領域50のn−半導体層106内に設けられたn+層28が、n−半導体層106内の埋込n+層10と部分的に接する深さにまで埋設された構成としている。

【0070】

これにより、ベース濃度をより濃くして、寄生のPNPトランジスタ(109)のHFEを下げ、寄生のPNPトランジスタのON動作を抑制することができ、アノードp+層27からダイオードD5領域50のn−半導体層106を介してp−基板105方向に電流が流れることを防止している。

【0071】

(変形例10)

変形例10は、ダイオードD5領域50のn−半導体層106内にp−ウェルを設け、p−ウェル内にアノードp+層27とカソードn+層28を設け、埋込n+層10をn−半導体層106とp−基板105間に介在させた構成としている。

【0072】

これにより、実施の形態1と同等に寄生のPNPトランジスタのON動作を抑制することができ、アノードp+層27からダイオードD5領域50のn−半導体層106を介してp−基板105方向に電流が流れることを防止している。

【0073】

(変形例11)

変形例11は、ダイオードD5領域50のn−半導体層106内にさらにn+層を設け、ダイオードD5領域50のn−半導体層106内のp−ウェル内のアノードp+層27と接続した構成としている。

【0074】

これにより、寄生のPNPトランジスタ(109)の電流増幅率HFEを遥かに下げ、寄生のPNPトランジスタのON動作を防止することができ、アノードp+層27からダイオードD5領域50のn−半導体層106を介してp−基板105方向に電流が流れることを防止している。

【0075】

(変形例12)

変形例12は、前述の変形例9の特徴と変形例11の特徴とを組合せて適用したことである。即ち、ダイオードD5領域50のn−半導体層106内にp−ウェルを設け、p−ウェル内にアノードp+層27とカソードn+層28を設け、埋込n+層10をn−半導体層106とp−基板105間に介在させている。ダイオードD5領域50のn−半導体層106内にさらにn+層を設け、ダイオードD5領域50のn−半導体層106内のp−ウェル内のアノードp+層27と接続している。上記構成において、ダイオードD5領域50のn−半導体層106内に設けられているn+層を、ダイオードD5領域50のn−半導体層106内の埋込n+層10と部分的に接する深さにまで埋設した構成である。

【0076】

これにより、ベース濃度をより濃くして寄生のPNPトランジスタ(109)の電流増幅率HFEを遥かに下げ、寄生のPNPトランジスタのON動作を防止することができ、アノードp+層27からダイオードD5領域50のn−半導体層106を介してp−基板105方向に電流が流れることを防止している。

【0077】

(実施の形態4)

本発明の実施の形態4について図19を用いて説明する。図19は本実施の形態4に係るブートストラップ回路構成を示し、その基本構成は図17に示す実施の形態3と同様である。実施の形態3との相違点は、本実施の形態4では、実施の形態2で説明したダイオードD7領域70を追加搭載する特徴を、実施の形態3の構成に導入したことである。即ち、Pch−MOSトランジスタ領域77とNch−MOSトランジスタ領域41をモノシリック高耐圧ICチップに追加搭載するとともに、ダイオードD7領域70を追加搭載した構成である。これにより、実施の形態2及び3と同様の効果が得られる。

【0078】

(実施の形態5)

本発明の実施の形態5について図20を用いて説明する。図20は本実施の形態5に係るブートストラップ回路構成を示し、その基本構成は図17に示す実施の形態3と同様である。相違点は、実施の形態3の構成で設けられていたダイオードD5領域50を、本実施の形態5では除去し、Pch−MOSトランジスタ領域7のバックゲートn+層16をオープン構成としたことである。これにより、実施の形態3と同様の効果が得られるとともに、ダイオードD5領域50を取り除いた分だけ、回路面積を縮小することができる。

【0079】

(実施の形態6)

本発明の実施の形態6について図21と図22を用いて説明する。図21は本実施の形態6に係るブートストラップ回路構成、図22はその要部断面構造を示し、その基本構成は図15乃び図16に示す実施の形態2と類似し、相違点は、本実施の形態6の構成では、ダイオードD7領域70は削除され、Pch−MOSトランジスタ領域7のゲートとPch−MOSトランジスタ領域7の第2のp+層17とが接続されたことである。

【0080】

一方、VB端子とVS端子間に接続された外部コンデンサC1の一端は、高耐圧ICチップ上のn−ドリフト層RnとPch−MOSトランジスタ領域7を介して、電源電圧Vccに接続され、下側トランジスタT2が導通(ON)状態にある時に出力端子OUTが接地電位に維持されると、それによってVB端子の電位が決まる。VB端子の電位がVcc以下の場合には、Pch−MOSトランジスタ領域7はON状態となり、充電電流を外部コンデンサC1に流し、外部コンデンサC1は電源電圧VccよりもPch−MOSトランジスタ領域7の閾値分だけ小さい充電電圧V2を保持する。これにより、低圧側駆動回路112は比較的低い電源電圧Vccにより駆動され、高圧側駆動回路111は外部コンデンサC1に充電された電圧V2により駆動される。

【0081】

図21と図22に示す本実施の形態では、高圧島状n−ドリフト層領域8の開口部のn+層(12)は、Pch−MOSトランジスタTr7の第2のp+層17(ソース)と接続され、さらに、Pch−MOSトランジスタTr7の第2のp+層17は、制限抵抗を介在させることなく、直接Pch−MOSトランジスタTr7のゲートGと接続されている。このように、Pch−MOSトランジスタTr7のゲートGは高圧島状n−ドリフト層領域8の開口部のn+層(12)及びPch−MOSトランジスタTr7の第2のp+層17以外いずれにも接続されていない。

【0082】

上記構成により、Pch−MOSトランジスタ領域7と電力変換器(パワーデバイス)の出力素子の低圧側トランジスダT2がONするタイミングを同期させる必要がないため、Pch−MOSトランジスタ領域7を駆動するNch−MOSトランジスタ領域41等の駆動回路やPch−MOSトランジスタ領域7を電力変換器の出力素子の低圧側トランジスタT2がONするタイミングを同期させるために必要な遅延回路を必要としない分、大幅に回路面積を縮小することができる。

【0083】

なお、本実施の形態6についても種々の変形例が可能であり、例えば、実施の形態1で説明した変形例1〜8の構造に対しても、本実施の形態6は同様に適用できる。

【0084】

(実施の形態7)

本発明の実施の形態7について図23を用いて説明する。図23は本実施の形態7に係るブートストラップ回路構成を示し、その基本構成は図21に示す実施の形態6と同様である。実施の形態6との相違点は、本実施の形態7では、実施の形態2で説明したように、ダイオードD5領域50とダイオードD7領域70をモノシリック高耐圧ICチップに追加搭載したことである。これにより、実施の形態2及び6と同様の効果が得られる。

【0085】

(実施の形態8)

本発明の実施の形態8について図24を用いて説明する。図24は本実施の形態8に係るブートストラップ回路構成を示し、その基本構成は図21に示す実施の形態6と同様である。実施の形態6との相違点は、本実施の形態8では、ダイオードD5領域50を削除し、Pch−MOSトランジスタ領域7のバックゲートn+層16をオープン構成としたことである。これにより、実施の形態6と同様の効果が得られるとともに、ダイオードD5領域50を取り除いた分だけ、回路面積を縮小することができる。

【産業上の利用可能性】

【0086】

本発明の活用例として、ブートストラップ回路方式を用いたインバータ等のパワーデバイスを駆動する半導体装置において、寄生のPNPトランジスタの動作を極力無くすことができ、寄生のトランジスタのオン動作を防止し、回路の消費電流を低減する技術に適用できる。

【図面の簡単な説明】

【0087】

【図1】本発明の実施の形態1に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図2】本発明の実施の形態1に係る半導体装置のブートストラップ回路要部の断面図である。

【図3】本発明の実施の形態の変形例1に係る半導体装置のブートストラップ回路要部の断面図である。

【図4】本発明の実施の形態の変形例2(A)に係る半導体装置のブートストラップ回路要部の断面図である。

【図5】本発明の実施の形態の変形例2(B)に係る半導体装置のブートストラップ回路要部の断面図である。

【図6】本発明の実施の形態の変形例3(A)に係る半導体装置のブートストラップ回路要部の断面図である。

【図7】本発明の実施の形態の変形例3(B)に係る半導体装置のブートストラップ回路要部の断面図である。

【図8】本発明の実施の形態の変形例4に係る半導体装置のブートストラップ回路要部の断面図である。

【図9】本発明の実施の形態の変形例5に係る半導体装置のブートストラップ回路要部の断面図である。

【図10】本発明の実施の形態の変形例6(A)に係る半導体装置のブートストラップ回路要部の断面図である。

【図11】本発明の実施の形態の変形例6(B)に係る半導体装置のブートストラップ回路要部の断面図である。

【図12】本発明の実施の形態の変形例7(A)に係る半導体装置のブートストラップ回路要部の断面図である。

【図13】本発明の実施の形態の変形例7(B)に係る半導体装置のブートストラップ回路要部の断面図である。

【図14】本発明の実施の形態の変形例8に係る半導体装置のブートストラップ回路要部の断面図である。

【図15】本発明の実施の形態2に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図16】本発明の実施の形態2に係る半導体装置のブートストラップ回路要部の断面図である。

【図17】本発明の実施の形態3に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図18】本発明の実施の形態3に係る半導体装置のブートストラップ回路要部の断面図である。

【図19】本発明の実施の形態4に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図20】本発明の実施の形態5に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図21】本発明の実施の形態6に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図22】本発明の実施の形態6に係る半導体装置のブートストラップ回路要部の断面図である。

【図23】本発明の実施の形態7に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図24】本発明の実施の形態8に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図25】従来の半導体装置のブートストラップ回路要部断面図である。

【図26】従来の半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【符号の説明】

【0088】

6,50,70 ダイオード領域、 7,41,77 MOSトランジスタ領域、 8 高圧島n−ドリフト層、 9 高圧側駆動用CMOS領域、 10,11,12,22 n+領域、 13,14、17,19,20,21 p+領域、 18 p+型拡散層、 23,24,25 p−ウェル、 105 p−基板、 106 n−半導体層、 111 高圧側駆動部、 112 低圧側駆動部、 113 レベルシフト回路、 114 遅延回路、 Rn ドリフト抵抗、 D1,D2,D3,D4,D5,D6,D7 ダイオード、 T1,T2 電力素子、 C1 外部コンデンサ

【技術分野】

【0001】

本発明はパワーデバイスを駆動する半導体装置に関し、特に、ブートストラップ回路方式を用いたインバータ等のパワーデバイスを駆動する半導体装置に関するものである。

【背景技術】

【0002】

一般に、ブートストラップダイオード方式では、ブートストラップダイオードは高耐圧ICチップの外部側に設けられていたが、1チップ化を目的としてブートストラップダイオードを高耐圧ICチップ内に搭載したブートストラップダイオード方式が開発されている。このようなブートストラップ回路方式の高耐圧ICチップについて、図25及び図26を用いて以下に説明する。図25は従来のブートストラップダイオードの断面構造を示し、図26は従来のパワーデバイス(電力変換器)と図25に示すブートストラップダイオードを搭載した高耐圧ICとを連結した概略回路構成を示す。

【0003】

図25に示すブートストラップ方式は、高耐圧ICチップに搭載したブートストラップダイオード部101と、高圧側駆動用CMOS領域102とを備える。p−基板105上に形成されたn−半導体層106内にp−ウェル103と層間絶縁膜のp+型拡散層104とを離間させて設けられている。これにより、p−ウェル103とp+型拡散層104間に電源電圧Vccを印加でき、高圧ダイオードはブートストラップダイオード(D101)として使用可能としている。ここで、高耐圧ICチップのp−基板105は通常は接地(GND)電位に接続されている。

【0004】

図26において、C1は外部ブートストラップコンデンサ(以後、「外部コンデンサ」と略称する)であり、上側(高圧側)パワートランジスタT1と下側(低圧側)パワートランジスタT2は、高電圧端子HVと接地GND間に直列に接続され、これらのトランジスタT1とT2はそれぞれ固有の基板ダイオードD1とD2を有する。図示のように、高耐圧ICは、高圧側駆動回路111と低圧側駆動回路112とレベルシフト回路113と遅延回路114と高耐圧のブートストラップダイオードD101を備え、トランジスタT1とT2等より成るパワーデバイスを駆動するように接続されている。

【0005】

外部コンデンサC1の一端はICチップ上のブートストラップダイオードD101を介して電源電圧Vccに接続され、下側トランジスタT2が導通(オン)状態にあるときに出力端子OUTがほぼ接地電位に維持された場合に、充電電流を外部コンデンサC1に流し、外部コンデンサC1は電源電圧Vccよりも電圧降下分だけ僅かに小さい充電電圧V1を保持する。これにより、低圧側駆動回路112は比較的低い電源電圧Vccにより駆動され、高圧側駆動回路111は外部コンデンサC1に充電された電圧V1により駆動される。

【0006】

このように、図25及び図26に示す高耐圧ICでは、ブートストラップダイオードD101のアノード107を制限抵抗R1を介して電源電圧Vccに接続し、カソード108を高圧側浮遊供給絶対電圧VB端子に接続し、この高圧側浮遊供給絶対電圧VB端子と高圧側浮遊供給オフセット電圧VS端子(出力端子OUT)との間に外部コンデンサC1を接続している。このような構成において、電力変換器の出力素子の低圧側トランジスタT2がオンするときに、高圧であるブートストラップダイオードD101を通じて外部コンデンサC1を充電し、この外部コンデンサC1に充電された電圧V1により高圧側駆動回路111を駆動することにより、高圧側浮遊電源を別途設けることを必要としない方式を提供している。

【0007】

他の従来構成としては、過渡期間中における集積LDMOS構造の寄生トランジスタのON防止用のデバイスを有し、集積デバイスの破壊防止を保証する集積LDMOSトランジスタを使用し、LDMOSと下側電力素子のタイミングを同期させたブートストラップ・キャパシタンスの充電回路が開示されている(例えば、特許文献1参照)。

【0008】

【特許文献1】特開平9−65571号公報(段落0009〜0014、図3〜5)

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかし、図25及び図26に示すようなブートストラップダイオードD101を高耐圧ICに搭載したブートストラップ回路方式は、ダイオードD101のアノード107がp−基板105よりも電源電圧分だけ電位的に高く、高圧を保持するためにRESURF構造となっている。この場合、電源電圧Vccを印可すると寄生のPNPトランジスタ109がオン(ON)動作し、ベース濃度が低いため、寄生のPNPトランジスタの電流増幅率HFEが大きくなり、アノード107からp−ウェル103及びn−半導体層106を介してp−基板105方向に非常に大きな電流が流れてしまうといった問題があった。

【0010】

本発明は、上記課題を解決するためになされたもので、寄生のトランジスタのオン動作を防止し、回路の消費電流を低減することができるブートストラップ方式による高耐圧ICチップの半導体装置を提供することを目的とする。即ち、高圧保持と充電の役割を接合分離で別々の素子に行うことで、寄生のPNPトランジスタの動作を極力無くす構成とする。これは、高圧保持部はRESURF構造ではあるが、n−ドリフト層となっているため寄生のPNPトランジスタは発生しないことによる。また、充電するための半導体素子としては、ダイオード型とpch−MOSトランジスタ型の大きく2通りのものを搭載しているが、どちらの型式においても寄生のPNPトランジスタの動作を極力無くすため、埋込みn+層を追加してベース濃度を濃くし、寄生のPNPトランジスタの電流増幅率HFEを低くしている。

【課題を解決するための手段】

【0011】

上記目的を達成するために、本発明による半導体装置は、パワーデバイスを駆動する半導体装置であって、前記パワーデバイスの低圧側の電力素子を駆動して高圧側浮遊供給絶対電圧と高圧側浮遊供給オフセット電圧間に接続されたブートストラップコンデンサに高圧側駆動部の電源を供給するブートストラップ回路を有する。ブートストラップ回路は、少なくとも前記ブートストラップコンデンサに電源を供給する低圧半導体素子部と高圧保持部を備え、低圧半導体素子部と高圧保持部は接合分離されている。高圧保持部は高圧島のn−半導体内の高圧側と開口部にそれぞれn+層を設けたn−ドリフト層である。また、ブートストラップ回路の低圧半導体素子部は少なくともPch−MOSトランジスタを備え、Pch−MOSトランジスタの第1のp+層が電源電圧に接続され、第2のp+層がn−ドリフト層を介して高圧側浮遊供給絶対電圧端子に接続され、Pch−MOSトランジスタのバックゲートは、ダイオードが接続されていないオープン構成であることを特徴とする。

【発明の効果】

【0012】

本発明によれば、高圧側浮遊電源を必要とせず、電源電圧Vccから、高圧側浮遊供給絶対電圧と高圧側浮遊供給オフセット電圧間に接続されたブートストラップコンデンサに電源電圧Vccをそのまま充電することが可能となり、寄生トランジスタのオン動作を防止する。また、Pch−MOSトランジスタがオフ状態のときに、ボディ・ドレインダイオードを通じて、充電電荷が流出することを防止できるとともに、Pch−MOSトランジスタのバックゲートにはダイオードが接続されていないので、その分だけ回路面積を縮小できる。

【発明を実施するための最良の形態】

【0013】

以下、本発明の実施の形態について、図1乃至図24を用いて、ブートストラップ方式を例示して説明する。ブートストラップ方式は、充電可能な半導体素子部と高圧保持用n−ドリフト層を接合分離でモノシリック高耐圧IC(1チップ構成の高耐圧IC)チップに搭載した構成である。ただし、本発明はこれに限定されるものではなく、他のMOSトランジスタ等を備える半導体装置にも適用可能である。なお、各図において共通する要素には同一の符号を付し、重複する説明については省略している。

【0014】

(実施の形態1)

本実施の形態1の特徴は、ブートストラップ回路内の充電可能な半導体素子部を構成するPch−MOSトランジスタ領域(7)において、n−半導体層(106)内に第1のp+層(20)と第2のp+層(17)とバックゲートn+層(16)を埋設し、このバックゲートn+層(16)には、従来はPch−MOSトランジスタがOFFの際に電荷流出を防止するためのダイオードが接続されていたが、本実施の形態1ではこのような電荷流出防止用のダイオードを設けることなく、バックゲートn+層(16)をオープン構成としたことである。

【0015】

先ず、本発明の実施の形態1の基本構成について図1及び図2を用いて以下に説明する。図1は本発明の実施の形態1に係る半導体装置とパワーデバイスとを連結した概略回路構成、図2は本実施の形態1に係るブートストラップ回路要部の断面構造を示す。図示の構成では、Pch−MOSトランジスタTr7の領域7と高圧島を利用したn−ドリフト層Rn領域8をモノシリック高耐圧ICチップに搭載したブートストラップ方式を示す。この方式では、高電圧を保持するために設けられたn−ドリフト層Rn領域8では、端子領域12(n+層)がPch−MOSトランジスタTr7の第2のp+層17と接続され、端子領域11(n+層)が高圧側駆動回路111の高圧側浮遊供給絶対電圧VBと接続された構成である。

【0016】

図1及び図2に示すように本実施の形態1は、Pch−MOSトランジスタ領域7の第1のp+層20を電源電圧Vccに接続し、第2のp+層17と接続されたn−ドリフト層Rnを介して外部コンデンサC1に電流が流れ、外部コンデンサC1の充電を行うブートストラップ方式である。

【0017】

上記構成において、図1に示すように、遅延回路114の一端子はPch−MOSトランジスタ(Tr7)領域7のゲートに接続され、低圧側駆動回路112とレベルシフト回路113と遅延回路114の各一端子は接地電位(GND)に接続されている。このような構成により、電力変換器(パワーデバイス)の出力素子の低圧側トランジスタT2がON動作するのと同期してPch−MOSトランジスタ領域7がON動作するように駆動制御している。

【0018】

一方、VB端子とVS端子間に接続された外部コンデンサC1の一端は、モノシリック高耐圧ICチップ上のn−ドリフト層RnとPch−MOSトランジスタ領域7を介して、例えば電源電圧15VのVccに接続され、下側トランジスタT2が導通(ON)状態となり出力端子OUTがほぼ接地電位に維持されたときに、充電電流を外部コンデンサC1に流す。外部コンデンサC1は電源電圧Vccを電圧降下させずにそのまま充電電圧として保持する。これにより、低圧側駆動回路112は比較的低い電源電圧Vccにより駆動されるとともに、高圧側駆動回路111は外部コンデンサC1に充電された電圧Vccにより駆動される。

【0019】

このように、電力変換器の出力素子の低圧側トランジスタT2がONするのと同期してPch−MOSトランジスタ領域7がONするように制御することにより、Pch−MOSトランジスタ領域7がONすると、Pch−MOSトランジスタ領域7の第1のp+層20と接続されている電源電圧Vccからn−ドリフト層Rnを介して外部コンデンサC1に電流が流れ、外部コンデンサC1の充電が行われる。この充電された電圧Vccを高圧側駆動回路111の電源電圧として使用することにより、高圧側浮遊電源を別途設けることを必要としないブートストラップ方式を提供できる。

【0020】

ここで、図2に示すブートストラップ回路の断面構造では、Pch−MOSトランジスタ領域7と高圧島n−ドリフト層領域8と高圧側駆動用CMOSトランジスタ領域9とを有し、Pch−MOSトランジスタ領域7において、埋込n+層10をn−半導体層106とp−基板105との間に介在させている。また、高圧島n−ドリフト層領域8において、p−基板105と同電位のp+層13及び14は、空乏層を広げ、n+領域12の電界集中を緩和させるために設けられている。また、Pch−MOSトランジスタ領域7と高圧島状n−ドリフト層領域8とを接合分離するp+拡散領域18が層間絶縁膜として、n−半導体層106内にp−基板105に達する深さにまで形成されている。

【0021】

このように構成されたブートストラップ回路の断面構造から明らかなように、Pch−MOSトランジスタ領域7の埋込n+層10をPch−MOSトランジスタ領域7のn−半導体層106とp−基板105間に介在させたことにより、ベース濃度を濃くして寄生のPNPトランジスタ(109)の高電界HFEを下げ、寄生のPNPトランジスタのON動作を従来構成より遥かに抑制することができ、第1のp+層20からPch−MOSトランジスタ領域7のn−半導体層106を介してp−基板105方向に電流が流れることを防止している。

【0022】

さらに本実施の形態では、Pch−MOSトランジスタ領域7はPch−MOSトランジスタ領域7のn−半導体層106内に第1のp+層20及び第2のp+層17とバックゲートn+層16を埋設し、Pch−MOSトランジスタ領域7のバックゲートn+層16をオープン構成としたことを特徴としている。バックゲートn+層16をオープン構成としても、ボディ・ドレインダイオードD4を介して流れる電流と逆方向に寄生のダイオードD6が第1のp+層(20)とバックゲートn+層(16)間に生成されるため、Pch−MOSトランジスタ領域7がオンからオフに切り替わる際に、Pch−MOSトランジスタ領域7のボディ・ドレインダイオードD4を介して流れる逆方向電流を、寄生ダイオードD6により防止できる。

【0023】

このように、Pch−MOSトランジスタ領域7のバックゲートn+層16をオープン構成としたことにより、Pch−MOSトランジスタ領域7がON状態のときに、端子VBと端子VS間に電源電圧Vccをそのまま充電することができ、寄生のPNPトランジスタのON動作を従来構成より遙かに抑制すると共に、モノシリックICチップに搭載可能となる。さらに、Pch−MOSトランジスタ領域7がOFF状態のときに、ボディ・ドレインダイオードD4を介して充電電荷が流出することを防止することができる。また、Pch−MOSトランジスタのバックゲートn+層(16)には電荷流出防止用のダイオードが接続されていないため、ダイオードが設けられていない分だけ回路面積を縮小できる。

【0024】

また、Pch−MOSトランジスタTr7領域7はn−半導体層106内にアノードp+層20とカソードn+層16を設け、埋込n+層10をPch−MOSトランジスタTr7領域7のn−半導体層106とp−基板105間に介在させたことにより、ベース濃度を濃くして寄生のPNPトランジスタ従来構成における図27に示した寄生PNPトランジスタ109のHFEを下げている。これにより、寄生のPNPトランジスタのON動作を従来構成より遥かに抑制することができ、アノードp+層20からPch−MOSトランジスタTr7領域7のn−半導体層106を介してp−基板105方向に電流が流れることを防止している。

【0025】

一方、高圧島n−ドリフト層領域8は、多重浮遊フィールドプレートMFFP(Multiple Floating Field Plate)の2重埋め込み構造を採用している。即ち、高圧島n−ドリフト層Rn領域8では、高圧島のn−半導体層106内の高電位側のn+層11と、開口部のn+層12の両側をp−基板と同電位(接地電位GND)に固定された一対のp+層13と14で囲む。これにより、空乏層を広げ、開口部のn+層12の電界集中を緩和させ、高圧側の電力素子がONし低圧側の電力素子がOFFすると、開口部のn+層12はフローティング電位となるが、その電位を低電位(約40V以下)に抑制することができ、高電圧、即ち600V以上の高電圧を保持することができる。

【0026】

このように、本実施の形態1に係るブートストラップ方式では、Pch−MOSトランジスタ領域7と高圧島n−ドリフト層領域8を高耐圧ICチップに搭載した構成により、回路消費電流を効果的に低減することが可能となる。また、図2において、Pch−MOSトランジスタ領域7と高圧島n−ドリフト層Rn領域8を接合分離した構成により、モノシリック高耐圧ICチップに搭載可能となる。

【0027】

なお、本実施の形態1は種々の変形が可能であり、例えば、充電可能な半導体素子部の構造は同じで、高圧島n−ドリフト層Rn領域8の構造が異なっている変形例1〜7等、さらに、Pch−MOSトランジスタ領域7の構成を、図2に示す構造以外に、例えば、図14に示す変形例8のように構成することも可能である。以下、本実施の形態1の変形例1〜8についてそれらの要点を説明する。

【0028】

(変形例1)

図3は変形例1に係るブートストラップ回路要部の断面構造を示す。図2に示す実施の形態1の構成では、高圧島n−ドリフト層Rn領域8において、空乏層を広げ、高圧島開口部のn+層12の電界集中を緩和させるために、p−基板と同電位に固定された一対のp+層13,14を設けているが、図3に示す変形例1のように、一方のp+層13を省略し、p+層14のみを設けた構成としてもよい。

【0029】

このような一方のp+層13を取り除いた構成においても、ダイオードD3領域6と高圧島n−ドリフト層Rn領域8とを接合分離するp+拡散領域18がp+層13の機能を兼ね、上記と同様の役割、即ち、n+層12の電界集中を緩和させる役割を果たしている。従って、p+層13を取り除いた分だけ、ICチップの高圧島n−ドリフト層領域8の面積を縮小することができる。

【0030】

(変形例2)

図4及び図5は変形例2(A),(B)に係るブートストラップ回路要部の断面構造を示し、その基本構成は図1乃至図2に示す実施の形態1と同様である。実施の形態1との相違点は、図4に示すように変形例2(A)の構成では、高圧島n−ドリフト層Rn領域8において、新たな埋込p+層19を高圧島のn−半導体層106とp−基板105との間に介在させたことであり、図5に示す変形例2(B)では、高圧島n−ドリフト層Rn領域8において、埋込p+層19を高圧島のn−半導体層106内に埋め込んだ構成である。

【0031】

図4及び図5に示すように、変形例2では、埋込p+層19を高圧島のn−半導体層106とp−基板105との間に介在させるか、またはp+層19を高圧島のn−半導体層106内に埋め込むことにより、n+層12直下の実効的な空乏層を低減することができ、n+領域12が高電位となることを回避することができる。

【0032】

(変形例3)

変形例3について図6及び図7を用いて説明する。図6及び図7は変形例3(A),(B)の要部断面構造を示し、その基本構成は図4及び図5に示す変形例2と同様である。変形例2との相違点は、変形例3では、変形例1で説明した特徴を変形例2と組合せて適用したことである。

【0033】

即ち、図4及び図5に示す変形例2の構成例では、高圧島n−ドリフト層Rn領域8において、p−基板と同電位に固定された一対のp+層13,14を設けているが、図6または図7に示す変形例3の構成例では、一方のp+層13を省略し、p+層14のみを設けた構成とし、高圧島n−ドリフト層Rn領域8において、埋込p+層19を高圧島のn−半導体層106とp−基板105との間に介在(図6)、または、埋込p+層19を高圧島のn−半導体層106内に埋め込んだ(図7)ことを特徴としている。

【0034】

このような一方のp+層13を取り除いた構成においても、ダイオードD3領域6と高圧島n−ドリフト層Rn領域8とを接合分離するp+拡散領域18がp+層13の機能を兼ね、上記と同様の役割、即ち、n+層12の電界集中を緩和させる役割を果たしている。従って、p+層13を取り除いた分だけ、ICチップの高圧島n−ドリフト層領域8の面積を縮小することができる。

【0035】

なお、図4及び図5に示す変形例2と図6及び図7に示す変形例3において、高圧島n−ドリフト層領域8内に埋込p+層19を生成する方法として、高エネルギーイオン注入法により、埋込p+層19をn−半導体層106内に注入形成する方法を用いることができる。

【0036】

(変形例4)

変形例4について図8を用いて説明する。図8は変形例4に係るブートストラップ回路の要部断面構造を示し、その基本構成は例えば図2に示す実施の形態1と同様である。変形例4では、n+層12が高電位となることを回避する別の好ましい構成例を示すものであり、図8に示す高圧島n−ドリフト層Rn領域8において、n+層12の電界集中を緩和させるために、p−基板と同電位に固定された一対のp+層13,14の埋め込み下部及び側面部を囲むようにp−ウェル層23,24を埋設したことである。

【0037】

これにより、n+層12近傍の実効的な空乏層を低減することができ、n+層12が高電位となることを回避できる。なお、p−ウェル層23,24のうちいずれか一方のみを埋設することによっても、同様の効果が得られる。

【0038】

(変形例5)

変形例5について図9を用いて説明する。図9は変形例5に係るブートストラップ回路の要部断面構造を示し、その基本構成は図8に示す変形例4と同様である。図9に示す変形例5では、一方のp+層13とその下部のp−ウェル層23の対を取り除き、p+層14とその下部のp−ウェル層24の対のみを形成した構成としている。

【0039】

このような一方のp+層13とその下部のPウェル層23の対を取り除いた構成においても、ダイオードD3領域6と高圧島n−ドリフト層Rn領域8とを接合分離するp+拡散領域18がp+層13の機能を兼ね、上記と同様の役割、即ち、n+層12の電界集中を緩和させる役割を果たしている。従って、p+層13及びその下部のPウェル層23を取り除いた分だけ、ICチップの高圧島n−ドリフト層領域8の面積を縮小することができる。

【0040】

(変形例6)

変形例6について図10及び図11を用いて説明する。図10及び図11は変形例6(A),(B)の要部断面構造を示し、その基本構成は図8に示す変形例4と同様である。図10及び図11に示す変形例6の構成では、上述の図4または図5に示す変形例2の特徴と図8に示す変形例4の特徴を組合せた構成である。

【0041】

即ち、本変形例6では、p−基板と同電位に固定された一対のp+層13,14の埋め込み下部及び側面全体を囲むようにp−ウェル層23,24を埋設するとともに、埋込p+層19を高圧島のn−半導体層106とp−基板105の間に介在(図10)、または、埋込p+層19を高圧島のn−半導体層106内に埋め込んだ(図11)ことを特徴としている。

【0042】

これにより、n+層12直下及びn+層12近傍の実効的な空乏層を低減することができ、n+層12が高電位となることを回避できる。なお、p−ウェル23,24のうちのいずれか一方のみを埋設することによっても、同様の効果が得られる。

【0043】

(変形例7)

変形例7について図12及び図13を用いて説明する。図12及び図13は変形例7(A),(B)の要部断面構造を示し、その基本構成は図10及び図11に示す変形例6と同様である。図12及び図13に示す変形例7では、一方のp+層13とその下部のp−ウェル層23の対を取り除き、p+層14とその下部のp−ウェル層24の対のみを形成した構成としている。

【0044】

このような一方のp+層13とその下部のPウェル層23の対を取り除いた構成においても、ダイオードD3領域6と高圧島n−ドリフト層Rn領域8とを接合分離するp+拡散領域18がp+層13の機能を兼ね、上記と同様の役割、即ち、n+層12の電界集中を緩和させる役割を果たしている。従って、p+層13及びその下部のPウェル層23を取り除いた分だけ、ICチップの高圧島n−ドリフト層領域8の面積を縮小することができる。

【0045】

また、変形例6と同様に、埋込p+層19を高圧島のn−半導体層106とp−基板105の間に介在(図12)、または、埋込p+層19を高圧島のn−半導体層106内に埋め込んだ(図13)ことを特徴としている。これにより、n+層12直下及びn+層12近傍の実効的な空乏層を低減することができ、n+層12が高電位となることを回避できる。

【0046】

(変形例8)

変形例8について図14を用いて説明する。図14は変形例8に係るブートストラップ回路要部の断面構造を示し、その基本構成は図1及び図2に示す実施の形態1と同様である。実施の形態1との相違点は、図14に示す変形例8では、Pch−MOSトランジスタ領域7のn−半導体層106内に設けられているバックゲートn+層16を、n−半導体層106内の埋込n+層10と部分的に接する深さまで埋設した構成としている。

【0047】

これにより、ベース濃度をより濃くして寄生のPNPトランジスタ(109)の高電界HFEを下げ、寄生のPNPトランジスタのON動作を防止することができ、第1のp+層20からPch−MOSトランジスタ領域7のn−半導体層106を介してp−基板105方向に電流が流れることを防止している。

【0048】

(実施の形態2)

本発明の実施の形態2について図15及び図16を用いて説明する。図15は本発明の実施の形態2に係る半導体装置とパワーデバイスとを連結した概略回路構成、図16は本実施の形態2に係るブートストラップ回路要部の断面構造を示し、その基本構成は図1乃至図2に示す実施の形態1と同様である。実施の形態1との相違点は、図15及び図16に示す本実施の形態2の構成では、Pch−MOSトランジスタTr7のバックゲートに接続する第1のダイオードD5領域50と第2のダイオードD7領域70をさらにモノシリック高耐圧ICチップに追加搭載したことである。

【0049】

即ち、Pch−MOSトランジスタ領域7の第1のp+層20とバックゲートn+層16間に第1のダイオードD5を設けて対応するダイオード領域50を形成し、また、Pch−MOSトランジスタ領域7の第2のp+層17とバックゲートn+層16間に第2のダイオードD7を設けて対応するダイオード領域70を形成している。

【0050】

上記構成において、ダイオードD5およびD7のカソードはともにPch−MOSトランジスタ(Tr7)のバックゲート(16)に接続され、ダイオードD5及びD7のアノードは、それぞれp+層27及び32を介してPch−MOSトランジスタ領域7の第1のp+層20及び第2のp+層17に接続されている。このように、ダイオードD5(領域50)の配置方向は、Pch−MOSトランジスタ領域7のOFFに切り替え時にボディ・ドレインダイオードD4を介して流れる逆回復電流とは逆方向となるように配置されている。

【0051】

即ち、例えば、ダイオードD5領域50は、Pch−MOSトランジスタ領域7がONからOFFに切り替わる際に、Pch−MOSトランジスタ領域7のボディ・ドレインダイオードD4を介して流れる逆回復電流を防止し、Pch−MOSトランジスタ領域7の第1のp+層20とダイオードD5領域50のアノードp+層27が電源電圧Vccに接続され、Pch−MOSトランジスタ領域7のバックゲートn+層16とダイオードD5領域50のカソードn+層28が接続されている。その他の構成は実施の形態1と同じである。

【0052】

これにより、Pch−MOSトランジスタ領域7がオンからオフに切り替わる際に、Pch−MOSトランジスタ領域7のボディ・ドレインダイオードD4及びダイオードD7を介して流れる逆方向電流をダイオードD5により防止する構成としている。

【0053】

このように構成されたブートストラップ回路の断面構造から明らかなように、Pch−MOSトランジスタ領域7がオン状態のときに、端子VBと端子VS間に電源電圧Vccをそのまま充電することができ、寄生のPNPトランジスタのオン動作を従来構成より遙かに抑制すると共に、モノシリックICチップに搭載可能となる。さらに、Pch−MOSトランジスタ領域7がオフ状態のときに、ボディ・ドレインダイオードD4を介して充電電荷が流出することを防止することができる。

【0054】

なお、本実施の形態2についても種々の変形例が可能であり、例えば、実施の形態1で説明した変形例1〜8の構造に対しても、本実施の形態2は同様に適用できる。

【0055】

また、図16に示す構成では、Pch−MOSトランジスタ領域7とダイオードD5領域50は接合分離されているが、それに限定されるものではなく、同じn−半導体層106内に存在した場合も同様の効果が得られる。

【0056】

(実施の形態3)

本発明の実施の形態3について図17及び図18を用いて説明する。図17は本発明の実施の形態3に係る半導体装置とパワーデバイスとを連結した概略回路構成、図18は本実施の形態3に係るブートストラップ回路要部の断面構造を示し、その基本構成は実施の形態1及び2と同様である。

【0057】

即ち、図17及び図18に示す本実施の形態3の基本構成では、Pch−MOSトランジスタ領域7のOFFに切り替え時にボディ・ドレインダイオードD4を介して流れる逆回復電流とは逆方向にダイオードD5領域50を追加搭載し、さらに、本実施の形態3の特徴ポイントは、Pch−MOSトランジスタ(Tr77)領域77とNch−MOSトランジスタ(Tr41)領域41をモノシリック高耐圧ICチップに追加搭載したことである。ただし、本実施の形態3では、実施の形態2で記載した第2のダイオードD7領域70は設けられていない。

【0058】

図17及び図18に示すように、Nch−MOSトランジスタ領域41はPch−MOSトランジスタ領域7を駆動する駆動回路である。Pch−MOSトランジスタ領域7の第2のp+層17はPch−MOSトランジスタ領域77を介してPch−MOSトランジスタ領域7のゲートに接続され、Pch−MOSトランジスタ領域7のゲートはNch−MOSトランジスタ領域41を介して接地電位(GND)に接続され、Nch−MOSトランジスタ領域41のバックゲートp+層29とソースn+層30も接地電位(GND)に接続されている。また、Nch−MOSトランジスタ領域41のゲートとPch−MOSトランジスタ領域77のゲートは遅延回路114の一端子に接続されている。

【0059】

図17及び図18から明らかなように、高圧島状n−ドリフト層領域8の開口部のn+層(11,12)はPch−MOSトランジスタTr7の第2のp+層17と接続され、第2のp+層17はさらにスイッチ素子として機能するPch−MOSトランジスタTr77を介してPch−MOSトランジスタTr7のゲートに接続され、このPch−MOSトランジスタTr7のゲートはさらにNch−MOSトランジスタTr41のドレインに接続されている。

【0060】

これにより、Nch−MOSトランジスタTr41の駆動(ON)するタイミングと低圧側の電力素子を駆動(ON)するタイミングとPch−MOSトランジスタTr77のOFFするタイミングが同期している。(原文クレーム3)さらに、Pch−MOSトランジスタTr77のゲートとNch−MOSトランジスタTr41のゲートが接続し、Nch−MOSトランジスタTr41のソース及びバックゲートは、低圧側駆動回路112,レベルシフト回路113及び遅延回路114の接地電位(GND)端子に接続されている。

【0061】

このようにスイッチ素子としてPch−MOSトランジスタTr77を設けたことにより、Nch−MOSトランジスタTr41の駆動(ON)するタイミングでスイッチOFFさせているので、接地電位(GND)側に電流が流れることがなく、従って、消費電流を抑制することができる。

【0062】

また、Pch−MOSトランジスタTr77のゲートとNch−MOSトランジスタTr41のゲートが短絡させたことにより、回路面積を縮小できる。

【0063】

このように構成されたブートストラップ回路の断面構造から明らかなように、Nch−MOSトランジスタ領域41がON状態の時、Pch−MOSトランジスタ領域77はOFF状態となり、Pch−MOSトランジスタ領域7はON状態となるので、端子VBと端子VS間に電源電圧Vccをほぼ充電することが可能となり、Nch−MOSトランジスタ領域41を介して電流が基板に流れない。

【0064】

従って、回路消費電流をさらに抑制することができ、寄生(PNP)トランジスタのON動作を従来構成より遥かに抑制するとともに、モノシリックICチップに搭載可能となる。また、Pch−MOSトランジスタ領域7がOFF状態のときに、ボディ・ドレインダイオードD4を通じて、充電電荷が流出することを防止できる。さらに、電力変換器の高圧側の出力素子がON状態の時に、充電とは逆方向にPch−MOSトランジスタ領域7がONするのを防止できる。

【0065】

なお、図18に示す構成では、Nch−MOSトランジスタ領域41とPch−MOSトランジスタ領域77とダイオードD5領域50とPch−MOSトランジスタ領域7は接合分離されているが、それに限定されるものではなく、同じn−半導体層106内に存在した場合も同様の効果が得られる。さらに、Nch−MOSトランジスタ領域41の構造においても、図18の構造に限定されるものではない。

【0066】

また、本実施の形態3は、充電可能な半導体素子部の構造のみが実施の形態1及び2と異なっているだけである。従って、高圧島n−ドリフト層Rn領域8の構造が異なっている実施の形態1で説明した変形例1〜7に対しても、本実施の形態3は同様に適用できる。

【0067】

さらに、Pch−MOSトランジスタ領域7及びPch−MOSトランジスタ領域77において、図18に示す構造の他に、実施の形態1で述べた変形例8の構造においても、図示は省略するが、本実施の形態3のPch−MOSトランジスタ領域7及びPch−MOSトランジスタ領域77は適用できる。

【0068】

また、ダイオードD5領域50において、図18に示す構造の他に、後述する変形例9〜12のダイオード構造においても、図示は省略するが、本実施の形態3のダイオードD5領域50は適用できる。変形例9〜12について以下に要点のみ説明する。

【0069】

(変形例9)

変形例9は、ダイオードD5領域50のn−半導体層106内に設けられたn+層28が、n−半導体層106内の埋込n+層10と部分的に接する深さにまで埋設された構成としている。

【0070】

これにより、ベース濃度をより濃くして、寄生のPNPトランジスタ(109)のHFEを下げ、寄生のPNPトランジスタのON動作を抑制することができ、アノードp+層27からダイオードD5領域50のn−半導体層106を介してp−基板105方向に電流が流れることを防止している。

【0071】

(変形例10)

変形例10は、ダイオードD5領域50のn−半導体層106内にp−ウェルを設け、p−ウェル内にアノードp+層27とカソードn+層28を設け、埋込n+層10をn−半導体層106とp−基板105間に介在させた構成としている。

【0072】

これにより、実施の形態1と同等に寄生のPNPトランジスタのON動作を抑制することができ、アノードp+層27からダイオードD5領域50のn−半導体層106を介してp−基板105方向に電流が流れることを防止している。

【0073】

(変形例11)

変形例11は、ダイオードD5領域50のn−半導体層106内にさらにn+層を設け、ダイオードD5領域50のn−半導体層106内のp−ウェル内のアノードp+層27と接続した構成としている。

【0074】

これにより、寄生のPNPトランジスタ(109)の電流増幅率HFEを遥かに下げ、寄生のPNPトランジスタのON動作を防止することができ、アノードp+層27からダイオードD5領域50のn−半導体層106を介してp−基板105方向に電流が流れることを防止している。

【0075】

(変形例12)

変形例12は、前述の変形例9の特徴と変形例11の特徴とを組合せて適用したことである。即ち、ダイオードD5領域50のn−半導体層106内にp−ウェルを設け、p−ウェル内にアノードp+層27とカソードn+層28を設け、埋込n+層10をn−半導体層106とp−基板105間に介在させている。ダイオードD5領域50のn−半導体層106内にさらにn+層を設け、ダイオードD5領域50のn−半導体層106内のp−ウェル内のアノードp+層27と接続している。上記構成において、ダイオードD5領域50のn−半導体層106内に設けられているn+層を、ダイオードD5領域50のn−半導体層106内の埋込n+層10と部分的に接する深さにまで埋設した構成である。

【0076】

これにより、ベース濃度をより濃くして寄生のPNPトランジスタ(109)の電流増幅率HFEを遥かに下げ、寄生のPNPトランジスタのON動作を防止することができ、アノードp+層27からダイオードD5領域50のn−半導体層106を介してp−基板105方向に電流が流れることを防止している。

【0077】

(実施の形態4)

本発明の実施の形態4について図19を用いて説明する。図19は本実施の形態4に係るブートストラップ回路構成を示し、その基本構成は図17に示す実施の形態3と同様である。実施の形態3との相違点は、本実施の形態4では、実施の形態2で説明したダイオードD7領域70を追加搭載する特徴を、実施の形態3の構成に導入したことである。即ち、Pch−MOSトランジスタ領域77とNch−MOSトランジスタ領域41をモノシリック高耐圧ICチップに追加搭載するとともに、ダイオードD7領域70を追加搭載した構成である。これにより、実施の形態2及び3と同様の効果が得られる。

【0078】

(実施の形態5)

本発明の実施の形態5について図20を用いて説明する。図20は本実施の形態5に係るブートストラップ回路構成を示し、その基本構成は図17に示す実施の形態3と同様である。相違点は、実施の形態3の構成で設けられていたダイオードD5領域50を、本実施の形態5では除去し、Pch−MOSトランジスタ領域7のバックゲートn+層16をオープン構成としたことである。これにより、実施の形態3と同様の効果が得られるとともに、ダイオードD5領域50を取り除いた分だけ、回路面積を縮小することができる。

【0079】

(実施の形態6)

本発明の実施の形態6について図21と図22を用いて説明する。図21は本実施の形態6に係るブートストラップ回路構成、図22はその要部断面構造を示し、その基本構成は図15乃び図16に示す実施の形態2と類似し、相違点は、本実施の形態6の構成では、ダイオードD7領域70は削除され、Pch−MOSトランジスタ領域7のゲートとPch−MOSトランジスタ領域7の第2のp+層17とが接続されたことである。

【0080】

一方、VB端子とVS端子間に接続された外部コンデンサC1の一端は、高耐圧ICチップ上のn−ドリフト層RnとPch−MOSトランジスタ領域7を介して、電源電圧Vccに接続され、下側トランジスタT2が導通(ON)状態にある時に出力端子OUTが接地電位に維持されると、それによってVB端子の電位が決まる。VB端子の電位がVcc以下の場合には、Pch−MOSトランジスタ領域7はON状態となり、充電電流を外部コンデンサC1に流し、外部コンデンサC1は電源電圧VccよりもPch−MOSトランジスタ領域7の閾値分だけ小さい充電電圧V2を保持する。これにより、低圧側駆動回路112は比較的低い電源電圧Vccにより駆動され、高圧側駆動回路111は外部コンデンサC1に充電された電圧V2により駆動される。

【0081】

図21と図22に示す本実施の形態では、高圧島状n−ドリフト層領域8の開口部のn+層(12)は、Pch−MOSトランジスタTr7の第2のp+層17(ソース)と接続され、さらに、Pch−MOSトランジスタTr7の第2のp+層17は、制限抵抗を介在させることなく、直接Pch−MOSトランジスタTr7のゲートGと接続されている。このように、Pch−MOSトランジスタTr7のゲートGは高圧島状n−ドリフト層領域8の開口部のn+層(12)及びPch−MOSトランジスタTr7の第2のp+層17以外いずれにも接続されていない。

【0082】

上記構成により、Pch−MOSトランジスタ領域7と電力変換器(パワーデバイス)の出力素子の低圧側トランジスダT2がONするタイミングを同期させる必要がないため、Pch−MOSトランジスタ領域7を駆動するNch−MOSトランジスタ領域41等の駆動回路やPch−MOSトランジスタ領域7を電力変換器の出力素子の低圧側トランジスタT2がONするタイミングを同期させるために必要な遅延回路を必要としない分、大幅に回路面積を縮小することができる。

【0083】

なお、本実施の形態6についても種々の変形例が可能であり、例えば、実施の形態1で説明した変形例1〜8の構造に対しても、本実施の形態6は同様に適用できる。

【0084】

(実施の形態7)

本発明の実施の形態7について図23を用いて説明する。図23は本実施の形態7に係るブートストラップ回路構成を示し、その基本構成は図21に示す実施の形態6と同様である。実施の形態6との相違点は、本実施の形態7では、実施の形態2で説明したように、ダイオードD5領域50とダイオードD7領域70をモノシリック高耐圧ICチップに追加搭載したことである。これにより、実施の形態2及び6と同様の効果が得られる。

【0085】

(実施の形態8)

本発明の実施の形態8について図24を用いて説明する。図24は本実施の形態8に係るブートストラップ回路構成を示し、その基本構成は図21に示す実施の形態6と同様である。実施の形態6との相違点は、本実施の形態8では、ダイオードD5領域50を削除し、Pch−MOSトランジスタ領域7のバックゲートn+層16をオープン構成としたことである。これにより、実施の形態6と同様の効果が得られるとともに、ダイオードD5領域50を取り除いた分だけ、回路面積を縮小することができる。

【産業上の利用可能性】

【0086】

本発明の活用例として、ブートストラップ回路方式を用いたインバータ等のパワーデバイスを駆動する半導体装置において、寄生のPNPトランジスタの動作を極力無くすことができ、寄生のトランジスタのオン動作を防止し、回路の消費電流を低減する技術に適用できる。

【図面の簡単な説明】

【0087】

【図1】本発明の実施の形態1に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図2】本発明の実施の形態1に係る半導体装置のブートストラップ回路要部の断面図である。

【図3】本発明の実施の形態の変形例1に係る半導体装置のブートストラップ回路要部の断面図である。

【図4】本発明の実施の形態の変形例2(A)に係る半導体装置のブートストラップ回路要部の断面図である。

【図5】本発明の実施の形態の変形例2(B)に係る半導体装置のブートストラップ回路要部の断面図である。

【図6】本発明の実施の形態の変形例3(A)に係る半導体装置のブートストラップ回路要部の断面図である。

【図7】本発明の実施の形態の変形例3(B)に係る半導体装置のブートストラップ回路要部の断面図である。

【図8】本発明の実施の形態の変形例4に係る半導体装置のブートストラップ回路要部の断面図である。

【図9】本発明の実施の形態の変形例5に係る半導体装置のブートストラップ回路要部の断面図である。

【図10】本発明の実施の形態の変形例6(A)に係る半導体装置のブートストラップ回路要部の断面図である。

【図11】本発明の実施の形態の変形例6(B)に係る半導体装置のブートストラップ回路要部の断面図である。

【図12】本発明の実施の形態の変形例7(A)に係る半導体装置のブートストラップ回路要部の断面図である。

【図13】本発明の実施の形態の変形例7(B)に係る半導体装置のブートストラップ回路要部の断面図である。

【図14】本発明の実施の形態の変形例8に係る半導体装置のブートストラップ回路要部の断面図である。

【図15】本発明の実施の形態2に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図16】本発明の実施の形態2に係る半導体装置のブートストラップ回路要部の断面図である。

【図17】本発明の実施の形態3に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図18】本発明の実施の形態3に係る半導体装置のブートストラップ回路要部の断面図である。

【図19】本発明の実施の形態4に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図20】本発明の実施の形態5に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図21】本発明の実施の形態6に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図22】本発明の実施の形態6に係る半導体装置のブートストラップ回路要部の断面図である。

【図23】本発明の実施の形態7に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図24】本発明の実施の形態8に係る半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【図25】従来の半導体装置のブートストラップ回路要部断面図である。

【図26】従来の半導体装置とパワーデバイスとを連結した概略回路構成を示す図である。

【符号の説明】

【0088】

6,50,70 ダイオード領域、 7,41,77 MOSトランジスタ領域、 8 高圧島n−ドリフト層、 9 高圧側駆動用CMOS領域、 10,11,12,22 n+領域、 13,14、17,19,20,21 p+領域、 18 p+型拡散層、 23,24,25 p−ウェル、 105 p−基板、 106 n−半導体層、 111 高圧側駆動部、 112 低圧側駆動部、 113 レベルシフト回路、 114 遅延回路、 Rn ドリフト抵抗、 D1,D2,D3,D4,D5,D6,D7 ダイオード、 T1,T2 電力素子、 C1 外部コンデンサ

【特許請求の範囲】

【請求項1】

パワーデバイスを駆動する半導体装置であって、前記パワーデバイスの低圧側の電力素子を駆動して高圧側浮遊供給絶対電圧と高圧側浮遊供給オフセット電圧間に接続されたブートストラップコンデンサに高圧側駆動部の電源を供給するブートストラップ回路を有し、

前記ブートストラップ回路は、少なくとも前記ブートストラップコンデンサに電源を供給する低圧半導体素子部と高圧保持部を備え、

前記低圧半導体素子部と前記高圧保持部は接合分離され、前記高圧保持部は高圧島のn−半導体内の高圧側と開口部にそれぞれn+層を設けたn−ドリフト層である半導体装置において、

前記ブートストラップ回路の前記低圧半導体素子部は少なくともPch−MOSトランジスタを備え、前記Pch−MOSトランジスタの第1のp+層が電源電圧に接続され、第2のp+層が前記n−ドリフト層を介して高圧側浮遊供給絶対電圧端子に接続され、前記Pch−MOSトランジスタのバックゲートは、ダイオードが接続されていないオープン構成であることを特徴とする半導体装置。

【請求項2】

前記第2のp+層とバックゲートのn+層間に形成されるボディ・ドレインダイオードを介して流れる電流と逆方向に、寄生のダイオードが前記第1のp+層とバックゲートn+層間に形成される請求項1に記載の半導体装置。

【請求項3】

パワーデバイスを駆動する半導体装置であって、前記パワーデバイスの低圧側の電力素子を駆動して高圧側浮遊供給絶対電圧と高圧側浮遊供給オフセット電圧間に接続されたブートストラップコンデンサに高圧側駆動部の電源を供給するブートストラップ回路を有し、

前記ブートストラップ回路は、少なくとも前記ブートストラップコンデンサに電源を供給する低圧半導体素子部と高圧保持部を備え、

前記低圧半導体素子部と前記高圧保持部は接合分離され、前記高圧保持部は高圧島のn−半導体内の高圧側と開口部にそれぞれn+層を設けたn−ドリフト層である半導体装置において、

前記ブートストラップ回路の前記低圧半導体素子部は少なくともpch−MOSトランジスタを備え、前記Pch−MOSトランジスタの第1のp+層が電源電圧に接続され、第2のp+層が前記n−ドリフト層を介して高圧側浮遊供給絶対電圧端子に接続され、前記Pch−MOSトランジスタのバックゲートに接続する第1のダイオード領域と第2のダイオード領域をさらにモノシリック高耐圧ICチップに追加搭載したことを特徴とする半導体装置。

【請求項4】

前記Pch−MOSトランジスタ領域の第1のp+層とバックゲートn+層間に第1のダイオードを設けるとともに、第2のp+層とバックゲートn+層間に第2のダイオードを設け、前記第1のダイオードおよび第2のダイオードのカソードはともに前記Pch−MOSトランジスタのバックゲートに接続され、前記第1及び第2のダイオードのアノードは、前記Pch−MOSトランジスタ領域の第1のp+層及び第2のp+層にそれぞれ接続されている請求項3に記載の半導体装置。

【請求項5】

前記高圧島状n−ドリフト層領域の開口部のn+層は前記Pch−MOSトランジスタの第2のp+層と接続され、該第2のp+層はさらにスイッチを介して前記Pch−MOSトランジスタのゲートに接続され、該Pch−MOSトランジスタのゲートはさらにNch−MOSトランジスタのドレインに接続され、前記Nch−MOSトランジスタの駆動するタイミングと低圧側の電力素子を駆動するタイミングと前記スイッチのOFFするタイミングが同期することを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置。

【請求項6】

前記スイッチが第2のPch−MOSトランジスタである請求項5に記載の半導体装置。

【請求項7】

前記スイッチである第2のPch−MOSトランジスタのゲートと前記Nch−MOSトランジスタのゲートが短絡している請求項6に記載の半導体装置。

【請求項8】

前記高圧島状n−ドリフト層領域の開口部のn+層は前記Pch−MOSトランジスタの第2のp+層とゲートに接続され、前記Pch−MOSトランジスタのゲートは、前記高圧島状n−ドリフト層領域の開口部のn+層及び前記Pch−MOSトランジスタTr7の第2のp+層以外いずれにも接続されていないことを特徴とする請求項1乃至7のいずれか1項に記載の半導体装置。

【請求項9】

前記ブートストラップ回路の前記低圧半導体素子部において、埋込n+層をn−半導体層とp−基板間に介在させたことを特徴とする請求項1乃至8のいずれか1項に記載の半導体装置。

【請求項1】

パワーデバイスを駆動する半導体装置であって、前記パワーデバイスの低圧側の電力素子を駆動して高圧側浮遊供給絶対電圧と高圧側浮遊供給オフセット電圧間に接続されたブートストラップコンデンサに高圧側駆動部の電源を供給するブートストラップ回路を有し、

前記ブートストラップ回路は、少なくとも前記ブートストラップコンデンサに電源を供給する低圧半導体素子部と高圧保持部を備え、

前記低圧半導体素子部と前記高圧保持部は接合分離され、前記高圧保持部は高圧島のn−半導体内の高圧側と開口部にそれぞれn+層を設けたn−ドリフト層である半導体装置において、

前記ブートストラップ回路の前記低圧半導体素子部は少なくともPch−MOSトランジスタを備え、前記Pch−MOSトランジスタの第1のp+層が電源電圧に接続され、第2のp+層が前記n−ドリフト層を介して高圧側浮遊供給絶対電圧端子に接続され、前記Pch−MOSトランジスタのバックゲートは、ダイオードが接続されていないオープン構成であることを特徴とする半導体装置。

【請求項2】

前記第2のp+層とバックゲートのn+層間に形成されるボディ・ドレインダイオードを介して流れる電流と逆方向に、寄生のダイオードが前記第1のp+層とバックゲートn+層間に形成される請求項1に記載の半導体装置。

【請求項3】

パワーデバイスを駆動する半導体装置であって、前記パワーデバイスの低圧側の電力素子を駆動して高圧側浮遊供給絶対電圧と高圧側浮遊供給オフセット電圧間に接続されたブートストラップコンデンサに高圧側駆動部の電源を供給するブートストラップ回路を有し、

前記ブートストラップ回路は、少なくとも前記ブートストラップコンデンサに電源を供給する低圧半導体素子部と高圧保持部を備え、

前記低圧半導体素子部と前記高圧保持部は接合分離され、前記高圧保持部は高圧島のn−半導体内の高圧側と開口部にそれぞれn+層を設けたn−ドリフト層である半導体装置において、

前記ブートストラップ回路の前記低圧半導体素子部は少なくともpch−MOSトランジスタを備え、前記Pch−MOSトランジスタの第1のp+層が電源電圧に接続され、第2のp+層が前記n−ドリフト層を介して高圧側浮遊供給絶対電圧端子に接続され、前記Pch−MOSトランジスタのバックゲートに接続する第1のダイオード領域と第2のダイオード領域をさらにモノシリック高耐圧ICチップに追加搭載したことを特徴とする半導体装置。

【請求項4】

前記Pch−MOSトランジスタ領域の第1のp+層とバックゲートn+層間に第1のダイオードを設けるとともに、第2のp+層とバックゲートn+層間に第2のダイオードを設け、前記第1のダイオードおよび第2のダイオードのカソードはともに前記Pch−MOSトランジスタのバックゲートに接続され、前記第1及び第2のダイオードのアノードは、前記Pch−MOSトランジスタ領域の第1のp+層及び第2のp+層にそれぞれ接続されている請求項3に記載の半導体装置。

【請求項5】

前記高圧島状n−ドリフト層領域の開口部のn+層は前記Pch−MOSトランジスタの第2のp+層と接続され、該第2のp+層はさらにスイッチを介して前記Pch−MOSトランジスタのゲートに接続され、該Pch−MOSトランジスタのゲートはさらにNch−MOSトランジスタのドレインに接続され、前記Nch−MOSトランジスタの駆動するタイミングと低圧側の電力素子を駆動するタイミングと前記スイッチのOFFするタイミングが同期することを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置。

【請求項6】

前記スイッチが第2のPch−MOSトランジスタである請求項5に記載の半導体装置。

【請求項7】

前記スイッチである第2のPch−MOSトランジスタのゲートと前記Nch−MOSトランジスタのゲートが短絡している請求項6に記載の半導体装置。

【請求項8】

前記高圧島状n−ドリフト層領域の開口部のn+層は前記Pch−MOSトランジスタの第2のp+層とゲートに接続され、前記Pch−MOSトランジスタのゲートは、前記高圧島状n−ドリフト層領域の開口部のn+層及び前記Pch−MOSトランジスタTr7の第2のp+層以外いずれにも接続されていないことを特徴とする請求項1乃至7のいずれか1項に記載の半導体装置。

【請求項9】

前記ブートストラップ回路の前記低圧半導体素子部において、埋込n+層をn−半導体層とp−基板間に介在させたことを特徴とする請求項1乃至8のいずれか1項に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【公開番号】特開2006−5182(P2006−5182A)

【公開日】平成18年1月5日(2006.1.5)

【国際特許分類】

【出願番号】特願2004−180367(P2004−180367)

【出願日】平成16年6月18日(2004.6.18)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成18年1月5日(2006.1.5)

【国際特許分類】

【出願日】平成16年6月18日(2004.6.18)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]