半導体装置

【課題】半導体装置の保護膜にクラックが入ることを防止した半導体装置を提供すること。

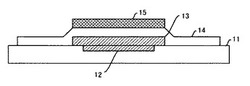

【解決手段】GaAs基板11上にキャパシタを形成予定の場所に対して、約1μmの深さを持つ凹部12を形成する。その上部にキャパシタ下部電極13としてAl配線層を形成する。この下部電極層13は凹部12の側壁に対して接続するように形成し、その上部にキャパシタとして動作させるための誘電体14としてSiNを形成する。その上部に上部電極15を形成してキャパシタが形成できる。GaAs基板11に凹部があるので、昇温降温を行うプロセスにおけるAlスライドによって誘電体14にクラックが生じない。

【解決手段】GaAs基板11上にキャパシタを形成予定の場所に対して、約1μmの深さを持つ凹部12を形成する。その上部にキャパシタ下部電極13としてAl配線層を形成する。この下部電極層13は凹部12の側壁に対して接続するように形成し、その上部にキャパシタとして動作させるための誘電体14としてSiNを形成する。その上部に上部電極15を形成してキャパシタが形成できる。GaAs基板11に凹部があるので、昇温降温を行うプロセスにおけるAlスライドによって誘電体14にクラックが生じない。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関し、特に半導体装置の保護膜にクラックが入ることを防止した半導体装置に関する。

【背景技術】

【0002】

従来、ガリウム砒素(以下GaAsと呼ぶ)を半導体基板とした電界効果トランジスタ(以下GaAsFETと呼ぶ)において、通常ゲート電極を形成した後に絶縁および素子保護の目的でシリコンナイトライド(以下SiNと呼ぶ)などの保護膜を形成する。(例えば、特許文献1参照)この保護膜を成長する工程は300℃程度の高温において行われる為に、ゲート電極配線がアルミニウム(以下Al)で形成される場合、半導体基板との熱膨張率の違いによってAlが膨張し、Alスライドなる現象を起こすことが知られている。保護膜形成後、常温に戻ったときAlが元の長さに縮小し、SiN保護膜にクラックを生じさせる。従来はこのクラックを通してGaAs界面に水分や不純物が浸入し、耐圧が変化するなどして、FET動作不良が生じるなどの信頼性問題を引き起こしていた。これを解決するためにまず、図3にAl電極線幅とSiN保護層の段切れ亀裂の長さの関係を測定し、その結果を示す。これによると、Al電極端部に生じたSiNクラックはAl電極長に比例しており、15μm以上の配線幅ではクラックが発生してしまうことを示していることが見出された。これにより、クラックが発生しないような根本的な解決が必要であることがわかった。

【特許文献1】特開平5−335345号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

したがって本発明は前記に鑑みてなされたものでその目的とするところは、半導体装置の保護膜にクラックが入ることを防止した半導体装置を提供することにある。

【課題を解決するための手段】

【0004】

前記課題を解決するために、本発明の一形態によれば、半導体基板上に形成された凹部と、前記凹部の底面と側面に接触するように形成された配線層と、前記配線層を覆うように形成された保護層を備えたことを特徴とする半導体装置が提供される。

【発明の効果】

【0005】

本発明によれば、半導体基板上に凹部を設けその凹部の側面に接続するように配線層を形成しているので、保護層形成の昇温降温プロセスにおいて、配線層が熱膨張でスライドしようとしてもこの凹部の側面で制限されているので熱膨張スライドが生じない。また、凹部の深さが、配線層厚より小さくても、熱膨張スライドを防止する効果がある。このように半導体基板上に形成された凹部の側面で配線層のスライドを抑制しているので半導体装置の保護膜にクラックのない良好な保護膜が形成され、電気絶縁性および信頼性が飛躍的に向上できる。

【発明を実施するための最良の形態】

【0006】

以下本発明の実施形態につき詳細に説明する。図1は本発明における第1の実施形態を示しており、MMIC(Monolitic Microwave Integrated Circuit)で形成されるキャパシタの断面構造を示している。MMICには受動素子として抵抗、インダクタ、キャパシタが含まれるが、このキャパシタは、Au/Pt/Ti/SiN/Al構造で形成される場合が多い。まず、GaAs基板11上にキャパシタを形成予定の場所に対して、約1μmの深さを持つ凹部12を形成する。その上部にキャパシタ下部電極13としてAlを蒸着等の方法によって形成する。この下部電極層13は凹部12の側壁に対して接続するように形成する必要がある。その上部にキャパシタとして動作させるための誘電体14としてSiNを例えばプラズマCVD(Chemical Vapor Deposition)等で形成する。そのときの成長温度は約300度と高温である。その上部に上部電極15を形成してキャパシタが形成できる。上部電極15と下部電極13に挟まれた誘電体14がキャパシタとして動作するためには電気的耐圧が必要であり、クラックが存在すると耐圧がなくなりキャパシタとして動作しなくなる。GaAs基板11に凹部がなければ、上述したように昇温降温を行うプロセスにおいてAlスライドによって誘電体14にクラックが生じてしまう。

【0007】

本実施例においてはこの問題を解決するもので、昇温降温を行うプロセスにおいてもAlがGaAsウエハ面に平行な方向に伸縮する事がないように、Al下部電極13直下のGaAs基板11上に凹部12を設けている。本実施形態では、燐酸系エッチャント(水:燐酸:過酸化水素=50:3:1)で1μm程度の深さを持つ凹部12を作製している。これにより誘電体14にクラックが生じることを防止でき、キャパシタ耐圧の低下がなくなる。図3に示したように凹部のない基板に成長したSiNクラックとAl電極長の関係から10μm程度よりも長い電極を形成する場合、本発明を適用するとクラックの発生を防止できる。この下部電極層13の厚みは凹部12の深さより薄い場合は当然Alスライドを抑制できるが、1μm程度の凹部の深さがあれば厚い場合であってもAlスライドを抑制を抑制できる。

【0008】

図2は本発明における第2の実施形態を示しており、FETのゲート電極に接続するゲートバスライン配線に本発明を適用したGaAsFETを上部から見た図である。FETはドレイン電極21a〜21cと、ソース電極22a〜22d、ゲート電極から形成される。ゲート電極は、櫛形ゲート電極23a〜23fとこれに接続された、ゲートバスライン24と、これに接続されたゲート電極パッド25a〜25cから構成される。ゲートバスライン24直下に凹部26a〜26cを形成した後、Alを成長しゲート電極が形成される。このゲート電極は凹部26a〜26cの側壁に対して接続するように形成する必要がある。ゲート電極を形成した後は、その上部に素子の保護のためパッシベーション膜を形成する。このパッシベーション膜もSiNを例えばプラズマCVD等で形成する。そのときの成長温度は約300度と高温である。ゲート電極がAlである場合、半導体基板との熱膨張率の違いによって、常温に戻ったときAlが元の長さに縮小する。櫛型ゲート電極23a〜23fにおいてはゲート幅が細いので降温時にSiN保護膜にクラックを生じさせることはないが、バスライン24はそのバスライン幅が15〜20μmのため、凹部26a〜26cを形成していなければ降温時にクラックを生じてしまう。この凹部26a〜26cは図2の例では3つ図示しているが、さらに数多くを形成しても構わない。この凹部の数を多くすることでAlスライドの防止が確実にできる。

【0009】

以上のべたように、このように構成された本発明の実施形態に係る半導体装置によれば、半導体基板上に凹部を設けその凹部の側面に接続するように配線層を形成しているので、保護層形成の昇温降温プロセスにおいて、配線層が熱膨張でスライドしようとしてもこの凹部の側面で制限されているので熱膨張スライドが生じない。また、凹部の深さが、配線層厚より小さくても、熱膨張スライドを防止する効果がある。このように半導体基板上に形成された凹部の側面で配線層のスライドを抑制しているので半導体装置の保護膜にクラックのない良好な保護膜が形成され、電気絶縁性および信頼性が飛躍的に向上できる。

【0010】

本発明は前記実施形態をそのままに限定されるものではなく、実施段階でその要旨を逸脱しない範囲で具体化できる。例えば、実施形態ではGaAs基板上のAl配線とSiN保護膜について述べたが、本発明においては、熱膨張係数の違いから生ずるクラックを防止できるので、InP基板上での素子製作や配線層としてCuや保護膜としてSiO2を使用するなど、どのような材料を用いても応用できる。

【図面の簡単な説明】

【0011】

【図1】本発明の第1の実施例におけるMMICで形成されるキャパシタの断面構造図である。

【図2】本発明の第2の実施例におけるFETのゲート電極に接続するゲートバスライン配線とFET全体を上部から見た図である。

【図3】従来のAl電極線幅とSiN保護層の段切れ亀裂の長さを測定した図である。

【符号の説明】

【0012】

11…GaAs基板

12、26a、26b、26c…凹部

13…下部電極層

14…誘電体

15…上部電極層

21a、21b、21c…ドレイン電極

22a、22b、22c、22d…ソース電極

23a、23b、23c、23d、23e、23f…櫛型ゲート電極

24・・・ゲートバスライン

25a、25b、25c・・・ゲート電極パッド

【技術分野】

【0001】

本発明は、半導体装置に関し、特に半導体装置の保護膜にクラックが入ることを防止した半導体装置に関する。

【背景技術】

【0002】

従来、ガリウム砒素(以下GaAsと呼ぶ)を半導体基板とした電界効果トランジスタ(以下GaAsFETと呼ぶ)において、通常ゲート電極を形成した後に絶縁および素子保護の目的でシリコンナイトライド(以下SiNと呼ぶ)などの保護膜を形成する。(例えば、特許文献1参照)この保護膜を成長する工程は300℃程度の高温において行われる為に、ゲート電極配線がアルミニウム(以下Al)で形成される場合、半導体基板との熱膨張率の違いによってAlが膨張し、Alスライドなる現象を起こすことが知られている。保護膜形成後、常温に戻ったときAlが元の長さに縮小し、SiN保護膜にクラックを生じさせる。従来はこのクラックを通してGaAs界面に水分や不純物が浸入し、耐圧が変化するなどして、FET動作不良が生じるなどの信頼性問題を引き起こしていた。これを解決するためにまず、図3にAl電極線幅とSiN保護層の段切れ亀裂の長さの関係を測定し、その結果を示す。これによると、Al電極端部に生じたSiNクラックはAl電極長に比例しており、15μm以上の配線幅ではクラックが発生してしまうことを示していることが見出された。これにより、クラックが発生しないような根本的な解決が必要であることがわかった。

【特許文献1】特開平5−335345号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

したがって本発明は前記に鑑みてなされたものでその目的とするところは、半導体装置の保護膜にクラックが入ることを防止した半導体装置を提供することにある。

【課題を解決するための手段】

【0004】

前記課題を解決するために、本発明の一形態によれば、半導体基板上に形成された凹部と、前記凹部の底面と側面に接触するように形成された配線層と、前記配線層を覆うように形成された保護層を備えたことを特徴とする半導体装置が提供される。

【発明の効果】

【0005】

本発明によれば、半導体基板上に凹部を設けその凹部の側面に接続するように配線層を形成しているので、保護層形成の昇温降温プロセスにおいて、配線層が熱膨張でスライドしようとしてもこの凹部の側面で制限されているので熱膨張スライドが生じない。また、凹部の深さが、配線層厚より小さくても、熱膨張スライドを防止する効果がある。このように半導体基板上に形成された凹部の側面で配線層のスライドを抑制しているので半導体装置の保護膜にクラックのない良好な保護膜が形成され、電気絶縁性および信頼性が飛躍的に向上できる。

【発明を実施するための最良の形態】

【0006】

以下本発明の実施形態につき詳細に説明する。図1は本発明における第1の実施形態を示しており、MMIC(Monolitic Microwave Integrated Circuit)で形成されるキャパシタの断面構造を示している。MMICには受動素子として抵抗、インダクタ、キャパシタが含まれるが、このキャパシタは、Au/Pt/Ti/SiN/Al構造で形成される場合が多い。まず、GaAs基板11上にキャパシタを形成予定の場所に対して、約1μmの深さを持つ凹部12を形成する。その上部にキャパシタ下部電極13としてAlを蒸着等の方法によって形成する。この下部電極層13は凹部12の側壁に対して接続するように形成する必要がある。その上部にキャパシタとして動作させるための誘電体14としてSiNを例えばプラズマCVD(Chemical Vapor Deposition)等で形成する。そのときの成長温度は約300度と高温である。その上部に上部電極15を形成してキャパシタが形成できる。上部電極15と下部電極13に挟まれた誘電体14がキャパシタとして動作するためには電気的耐圧が必要であり、クラックが存在すると耐圧がなくなりキャパシタとして動作しなくなる。GaAs基板11に凹部がなければ、上述したように昇温降温を行うプロセスにおいてAlスライドによって誘電体14にクラックが生じてしまう。

【0007】

本実施例においてはこの問題を解決するもので、昇温降温を行うプロセスにおいてもAlがGaAsウエハ面に平行な方向に伸縮する事がないように、Al下部電極13直下のGaAs基板11上に凹部12を設けている。本実施形態では、燐酸系エッチャント(水:燐酸:過酸化水素=50:3:1)で1μm程度の深さを持つ凹部12を作製している。これにより誘電体14にクラックが生じることを防止でき、キャパシタ耐圧の低下がなくなる。図3に示したように凹部のない基板に成長したSiNクラックとAl電極長の関係から10μm程度よりも長い電極を形成する場合、本発明を適用するとクラックの発生を防止できる。この下部電極層13の厚みは凹部12の深さより薄い場合は当然Alスライドを抑制できるが、1μm程度の凹部の深さがあれば厚い場合であってもAlスライドを抑制を抑制できる。

【0008】

図2は本発明における第2の実施形態を示しており、FETのゲート電極に接続するゲートバスライン配線に本発明を適用したGaAsFETを上部から見た図である。FETはドレイン電極21a〜21cと、ソース電極22a〜22d、ゲート電極から形成される。ゲート電極は、櫛形ゲート電極23a〜23fとこれに接続された、ゲートバスライン24と、これに接続されたゲート電極パッド25a〜25cから構成される。ゲートバスライン24直下に凹部26a〜26cを形成した後、Alを成長しゲート電極が形成される。このゲート電極は凹部26a〜26cの側壁に対して接続するように形成する必要がある。ゲート電極を形成した後は、その上部に素子の保護のためパッシベーション膜を形成する。このパッシベーション膜もSiNを例えばプラズマCVD等で形成する。そのときの成長温度は約300度と高温である。ゲート電極がAlである場合、半導体基板との熱膨張率の違いによって、常温に戻ったときAlが元の長さに縮小する。櫛型ゲート電極23a〜23fにおいてはゲート幅が細いので降温時にSiN保護膜にクラックを生じさせることはないが、バスライン24はそのバスライン幅が15〜20μmのため、凹部26a〜26cを形成していなければ降温時にクラックを生じてしまう。この凹部26a〜26cは図2の例では3つ図示しているが、さらに数多くを形成しても構わない。この凹部の数を多くすることでAlスライドの防止が確実にできる。

【0009】

以上のべたように、このように構成された本発明の実施形態に係る半導体装置によれば、半導体基板上に凹部を設けその凹部の側面に接続するように配線層を形成しているので、保護層形成の昇温降温プロセスにおいて、配線層が熱膨張でスライドしようとしてもこの凹部の側面で制限されているので熱膨張スライドが生じない。また、凹部の深さが、配線層厚より小さくても、熱膨張スライドを防止する効果がある。このように半導体基板上に形成された凹部の側面で配線層のスライドを抑制しているので半導体装置の保護膜にクラックのない良好な保護膜が形成され、電気絶縁性および信頼性が飛躍的に向上できる。

【0010】

本発明は前記実施形態をそのままに限定されるものではなく、実施段階でその要旨を逸脱しない範囲で具体化できる。例えば、実施形態ではGaAs基板上のAl配線とSiN保護膜について述べたが、本発明においては、熱膨張係数の違いから生ずるクラックを防止できるので、InP基板上での素子製作や配線層としてCuや保護膜としてSiO2を使用するなど、どのような材料を用いても応用できる。

【図面の簡単な説明】

【0011】

【図1】本発明の第1の実施例におけるMMICで形成されるキャパシタの断面構造図である。

【図2】本発明の第2の実施例におけるFETのゲート電極に接続するゲートバスライン配線とFET全体を上部から見た図である。

【図3】従来のAl電極線幅とSiN保護層の段切れ亀裂の長さを測定した図である。

【符号の説明】

【0012】

11…GaAs基板

12、26a、26b、26c…凹部

13…下部電極層

14…誘電体

15…上部電極層

21a、21b、21c…ドレイン電極

22a、22b、22c、22d…ソース電極

23a、23b、23c、23d、23e、23f…櫛型ゲート電極

24・・・ゲートバスライン

25a、25b、25c・・・ゲート電極パッド

【特許請求の範囲】

【請求項1】

半導体基板上に形成された凹部と、前記凹部の底面と側面に接触するように形成された配線層と、前記配線層を覆うように形成された保護層を備えた半導体装置。

【請求項2】

前記凹部の溝の深さは、前記配線層の厚みより小さいことを特徴とする請求項1記載の半導体装置。

【請求項3】

前記配線層はAlであり、前記保護層はSiNであることを特徴とする請求項1記載の半導体装置。

【請求項4】

前記凹部はFETのゲート電極に接続するゲートバスライン配線直下の半導体基板上に形成することを特徴とする請求項1記載半導体装置。

【請求項5】

前記凹部はMMICのキャパシタ下部電極直下の半導体基板上に形成することを特徴とする請求項1記載半導体装置。

【請求項1】

半導体基板上に形成された凹部と、前記凹部の底面と側面に接触するように形成された配線層と、前記配線層を覆うように形成された保護層を備えた半導体装置。

【請求項2】

前記凹部の溝の深さは、前記配線層の厚みより小さいことを特徴とする請求項1記載の半導体装置。

【請求項3】

前記配線層はAlであり、前記保護層はSiNであることを特徴とする請求項1記載の半導体装置。

【請求項4】

前記凹部はFETのゲート電極に接続するゲートバスライン配線直下の半導体基板上に形成することを特徴とする請求項1記載半導体装置。

【請求項5】

前記凹部はMMICのキャパシタ下部電極直下の半導体基板上に形成することを特徴とする請求項1記載半導体装置。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2007−243017(P2007−243017A)

【公開日】平成19年9月20日(2007.9.20)

【国際特許分類】

【出願番号】特願2006−65768(P2006−65768)

【出願日】平成18年3月10日(2006.3.10)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成19年9月20日(2007.9.20)

【国際特許分類】

【出願日】平成18年3月10日(2006.3.10)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]