半導体装置

【課題】半導体装置の高集積化された半導体チップの突起電極とテープキャリアのインナーリードとの接合工程を簡素化する手段を提供する。

【解決手段】半導体装置が、半導体チップと、絶縁性を有するベースフィルムと、半導体チップの一の面の縁部の中央側に1列に形成された第1の突起電極と、第1の突起電極の外側に第1の突起電極より低い高さで1列に形成された第2の突起電極と、ベースフィルムの半導体チップの搭載面に、第1の突起電極上に延在して形成された第1のインナーリードと、第1のインナーリードのベースフィルムの反対側に形成された絶縁膜と、絶縁膜上に第2の突起電極上に延在して形成された第2のインナーリードとを備える。

【解決手段】半導体装置が、半導体チップと、絶縁性を有するベースフィルムと、半導体チップの一の面の縁部の中央側に1列に形成された第1の突起電極と、第1の突起電極の外側に第1の突起電極より低い高さで1列に形成された第2の突起電極と、ベースフィルムの半導体チップの搭載面に、第1の突起電極上に延在して形成された第1のインナーリードと、第1のインナーリードのベースフィルムの反対側に形成された絶縁膜と、絶縁膜上に第2の突起電極上に延在して形成された第2のインナーリードとを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、テープキャリア上に半導体チップを搭載して連続的に製造されるTCP(Tape Carrier Package)型の半導体装置に関する。

【背景技術】

【0002】

近年、テープキャリア上に搭載される半導体チップの高集積化が進展し、半導体チップに形成される突起電極の数が増加傾向にあり、これに伴ってテープキャリア上に形成されるインナーリードの数が増加し、隣合うインナーリード間およびアウターリード間のショートを避けるために一定の間隔でインナーリードやアウターリードを配置すると、半導体装置が大型化するという問題が生ずる。

【0003】

このため、インナーリードやアウターリードの幅を細くすると、インナーリードやアウターリード自身の強度の低下、および半導体チップの突起電極との接合強度や実装基板の配線端子との接合強度が低下するという問題が生じる。

このような問題に対処するため、従来のTCP型の半導体装置は、ポリイミド等の絶縁性を有するベースフィルムの表裏の面に、銅箔を接着積層し、これをエッチングによりパターニングしてベースフィルムの両面にインナーリードを形成し、裏面に形成されたインナーリードは熱圧着により半導体チップの外側に1列に形成された突起電極に直接接合し、おもて面に形成されたインナーリードと半導体チップの中央側に1列に形成された突起電極とは、ワイヤボンディングにより接合して半導体チップの高集積化への要求に対応している(例えば、特許文献1参照。)。

【特許文献1】特開平3−276737号公報(主に第2頁左下欄、第1図)

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した従来の技術においては、裏面に形成されたインナーリードと半導体チップの外側に形成された突起電極とは熱圧着により直接接合し、おもて面に形成されたインナーリードと半導体チップの中央側に形成された突起電極とは、ワイヤボンディングにより接合しているため、インナーリードと半導体チップの突起電極との接合工程を、熱圧着による接合工程と、ワイヤボンディングによる接合工程とに分けてTCP型の半導体装置の製造工程を構成することが必要になり、ワイヤボンディングによる接合工程を設けるための設備の導入やその設置のためのスペースの確保しなければならないという問題がある。

【0005】

本発明は、上記の問題点を解決するためになされたもので、高集積化された半導体チップの突起電極とインナーリードとの接合工程を簡素化する手段を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明は、上記課題を解決するために、半導体装置が、半導体チップと、絶縁性を有するベースフィルムと、前記半導体チップの一の面の縁部の中央側に、1列に形成された第1の突起電極と、該第1の突起電極の外側に、該第1の突起電極より低い高さで、1列に形成された第2の突起電極と、前記ベースフィルムの前記半導体チップの搭載面に、前記第1の突起電極上に延在して形成された第1のインナーリードと、該第1のインナーリードの前記ベースフィルムの反対側に形成された絶縁膜と、該絶縁膜上に、前記第2の突起電極上に延在して形成された第2のインナーリードとを備えたことを特徴とする。

【発明の効果】

【0007】

これにより、本発明は、半導体チップの第1および第2突起電極とベースフィルム上の第1および第2のインナーリードとを位置を合わせて同時に接合することができ、接合工程を1回にして、高集積化された半導体チップを搭載した半導体装置の接合工程を簡素化することができるという効果が得られる。

【発明を実施するための最良の形態】

【0008】

以下に、図面を参照して本発明による半導体装置の実施例について説明する。

【実施例1】

【0009】

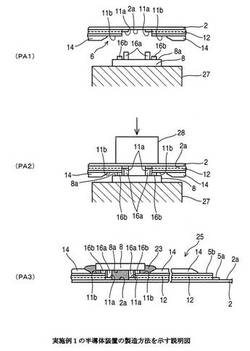

図1は実施例1のテープキャリアの上面を示す説明図、図2は実施例1のインナーリード形成領域の上面を示す説明図、図1は実施例1のテープキャリアの断面を示す説明図、図4は実施例1の半導体チップの電極形成面を示す説明図、図5は図4のC−C断面を示す説明図、図6は実施例1のテープキャリアの製造方法を示す説明図、図7は実施例1の半導体装置の製造方法を示す説明図である。

【0010】

上記の図3は図2に示すA−A断面線および図1に示すB−B断面線に沿った断面を同時に示した断面図である。また、図1、図2はソルダーレジストを除いた状態で描いてある。

図1において、1はテープキャリアである。

2はベースフィルムであり、ポリイミド等の耐熱性および絶縁性を有する樹脂材料で製作された長尺のフィルム部材であって、その両方の縁領域には、図示しない駆動装置で駆動されるスプロケットの歯に嵌合してテープキャリア1の移動や位置決めを行うために所定のピッチでそれぞれ1列に配置されたスプロケットホール3が形成されている。

【0011】

5a、5bは第1および第2のアウターリード(区別を必要としない場合は、アウターリード5という。)であり、インナーリード形成領域6を挟んで両側に設定されたアウターリード形成領域7a、7bに銅(Cu)等の導電材料で形成された配線であって、アウターリード形成領域7a側の第1および第2のアウターリード5a、5bは半導体チップ8(図4、図5参照)への入力端子として機能し、アウターリード形成領域7b側の第1および第2のアウターリード5a、5bは半導体チップ8からの出力端子として機能する。

【0012】

また、第1および第2のアウターリード5a、5bの先端部には、それぞれパッド9が形成されている。

インナーリード形成領域6には、図2に示すように、その周囲の縁部に第1および第2のインナーリード11a、11b(区別を必要としない場合は、インナーリード11という。)が、それぞれ所定の第1および第2のアウターリード5a、5bと接続した状態(図1参照)で形成されている。

【0013】

本実施例の第1および第2のインナーリード11a、11b、並びに第1および第2のアウターリード5a、5bは、図3にハッチングを付して示すポリイミド等の絶縁材料で形成された絶縁膜12(図1および図2には2点鎖線で示してある。)を挟んでベースフィルム2の半導体チップ8の搭載面(チップ搭載面2aという。)上に2層に形成されており、チップ搭載面2a上に第1のインナーリード11aおよびこれに接続する第1のアウターリード5aが形成され、これらの上に形成された絶縁膜12のチップ搭載面2aと反対側の面上に第2のインナーリード11bおよびこれに接続する第2のアウターリード5bが形成されている。

【0014】

また、第1のインナーリード11aの先端部は、その上層の第2のインナーリード11bの先端よりインナーリード形成領域6の中央側に延在(図2参照)してそれぞれ形成され、第1のアウターリード5aの先端部は、その上層の第2のアウターリード5bの先端よりインナーリード形成領域6の外側に延在(図1参照)してそれぞれ形成されており、第1のインナーリード11aと第2のインナーリード11b、および第1のアウターリード5aと第2のアウターリード5bはそれぞれ絶縁膜12を挟んで階段状に2段に配置されている。

【0015】

更に、ベースフィルム2のチップ搭載面2aに形成された第1のインナーリード11aおよび第1のアウターリード5aと、絶縁膜12上の第2のインナーリード11bおよび第2のアウターリード5bとはそれぞれ自身の強度を確保する幅で形成され、かつ隣とのショートを避けるための一定の間隔で配置されている。

更に、本実施例の第1のインナーリード11aと第2のインナーリード11bとはその長手方向の1辺同士が上下で同じ位置となるように配置(図2参照)され、第1のアウターリード5aと第2のアウターリード5bとはその長手方向の1辺同士が上下で同じ位置となるように配置(図1参照)されている。

【0016】

このように、本実施例の第1および第2のインナーリード11a、11bと、第1および第2のアウターリード5bとは、それぞれ長手方向の辺が上下で同じ位置となるように配置されているので、通常の一つの面上に同じ数のインナーリード11およびアウターリード5を配置した平面配置の場合と比較して、1段に形成されるインナーリード11およびアウターリード5の数を半分にして、その並び方向の全幅(図2に示す寸法W等)を略半分にすることができる。この場合にインナーリード11およびアウターリード5のそれぞれの隣とのショートを避けるための一定の間隔が、自身の強度を確保する幅より広いときは並び方向の全幅を半分以下にすることができる。

【0017】

図3において、14はソルダーレジストであり、半田の侵入を防止するための絶縁性を有する膜であって、隣合う第2のインナーリード11b間および隣合う第2のアウターリード5b間をそれぞれ絶縁する機能も有している。

半導体チップ8は、通常の半導体チップ8と同じ大きさで2倍に高集積化された半導体チップであって、図4、図5に示すように、その一の面に多数の突起電極の形成され、この面(電極形成面8aという。)の周囲の縁部に、2列に並べた第1の突起電極16aと第2の突起電極16b(区別を必要としない場合は、突起電極16という。)とがそれぞれ矩形に1列に並べて形成されており、半導体チップ8の中央側に1列に形成された第1の突起電極16aの電極形成面8aからの高さは、図5に示すようにその外側に1列に形成された第2の突起電極16bより高く形成されている。

【0018】

本実施例の第1の突起電極16aと第2の突起電極16bとは、図4に示すように千鳥に配置されており、ベースフィルム2のチップ搭載面2aに形成された中央側に延在している第1のインナーリード11aは第1の突起電極16a上に達し、絶縁膜12上形成された第2のインナーリード11bは第2の突起電極16b上に達するように形成され、その段差は、第1の突起電極16aと第2の突起電極16bとの高さの差と同等に形成されており、第1の突起電極16aは第1のインナーリード11aに、第2の突起電極16bは第2のインナーリード11bにそれぞれ接合される(図7参照)。

【0019】

このような、高さの異なる第1および第2の突起電極16a、16bの製造は、例えば金(Au)等で突起電極を形成するときに、その電解メッキ工程における第1の突起電極16a側への通電時間を、第2の突起電極16b側への通電時間より長く設定して形成される。

図6において、21はマスク部材としてのレジストマスクであり、フォトリソグラフィによりベースフィルム2のチップ搭載面2a側に塗布されたポジ型またはネガ型のレジストを露光および現像処理して形成されたマスクパターンであって、本実施例の絶縁膜12の形成工程におけるマスクとして機能する。

【0020】

図7において、23は封止層であり、ベースフィルム2のチップ搭載面2aと半導体チップ8の電極形成面8aとの間に注入された熱硬化性のエポキシ樹脂等の封止樹脂を加熱硬化させて形成された絶縁性を有する層であって、半導体チップ8の電極形成面8aと反対側の面(裏面という。)を露出させた状態で形成され、第1および第2のインナーリード11a、11bと第1および第2の突起電極16a、16bとの接合部を絶縁すると共に外部の湿度等から保護する機能を有している。

【0021】

本実施例のベースフィルム2上に半導体チップ8を搭載して形成される半導体装置25は以下のようにして製造される。

以下に、図6にPで示す工程に従って本実施例のテープキャリアの製造方法について説明する。

P1、スプロケットホール3が形成されたベースフィルム2のチップ搭載面2a上に銅箔を接着積層し、フォトリソグラフィにより図1、図2に示す第1のアウターリード5aおよび第1のインナーリード11aの形成領域を覆うエッチングレジストを形成し、これをマスクとして銅箔をエッチングし、その後にエッチングレジストを除去して、ベースフィルム2のチップ搭載面2a上のアウターリード形成領域7a、7bおよびインナーリード形成領域6に、それぞれ第1のアウターリード5aおよびこれに接続する第1のインナーリード11aを形成する。

【0022】

P2、フォトリソグラフィにより、第1のインナーリード11aの先端部および第1のアウターリード5aの先端部を覆う領域(図2に示す2点鎖線で囲われた領域、および図1に示す2点鎖線で囲われた領域の外側の領域)を覆うレジストマスク21、つまり絶縁膜12の形成領域を露出させたレジストマスク21を形成し、これをマスクとして絶縁材料をコーティングして絶縁膜12を形成する。

【0023】

このとき、隣合う第1のインナーリード11a間および隣合う第1のアウターリード5a間は、それぞれ絶縁膜12が埋込まれて絶縁される。

P3、工程P2で形成したレジストマスク21を除去し、上記工程P1と同様にして絶縁膜状12上に、銅箔を接着積層し、図1、図2に示す第2のアウターリード5bおよび第2のインナーリード11bの形成領域を覆うエッチングレジストを用いて、絶縁膜12上のアウターリード形成領域7a、7bおよびインナーリード形成領域6に、それぞれ第2のアウターリード5bおよびこれに接続する第2のインナーリード11bを形成する。

【0024】

P4、そして、液状のソルダーレジスト14を第2のアウターリード5bおよび第2のインナーリード11bの先端部を残して塗布し、これを硬化させて隣合う第2のインナーリード11b間および隣合う第2のアウターリード5b間、並びにそれぞれの先端部を除く第2のアウターリード5bおよび第2のインナーリード11b上にソルダーレジスト14を形成する。

【0025】

このとき、隣合う第2のインナーリード11b間および隣合う第2のアウターリード5b間は、それぞれソルダーレジスト14が埋込まれて絶縁される。

このようにして製造されたテープキャリア1に半導体チップ8を搭載した半導体装置25の製造方法について、図7にPAで示す工程に従って説明する。

PA1、ボンディングステージ27に予め製造した半導体チップ8の裏面を載置し、スプロケットホール3を用いてチップ搭載面2aを下方に向けたテープキャリア1のインナーリード形成領域6を半導体チップ8上に移動させ、第1および第2のインナーリード11a、11bと第1および第2の突起電極16a、16bとをそれぞれ対向させて停止させる。

【0026】

PA2、ボンディングツール28によりベースフィルム2のチップ搭載面2aの反対側の面を押して、第1のインナーリード11aと第1の突起電極16a、および第2のインナーリード11bと第2の突起電極16bとをそれぞれ当接させ、ボンディングツール28により加熱、押圧して第1のインナーリード11aと第1の突起電極16a、および第2のインナーリード11bと第2の突起電極16bとを同時に接合する。

【0027】

PA3、スプロケットホール3を用いてチップ搭載面2aを上方に向けたテープキャリア1のインナーリード形成領域6を封止工程へ移動させ、封止樹脂を図7にハッチングを付して示すように、ベースフィルム2のチップ搭載面2aと半導体チップ8の電極形成面8aとの間に注入し、これを加熱硬化させて封止層23を形成する。

これにより、本実施例の半導体装置25がテープキャリア1上に形成され、その後にテープキャリア1から半導体装置25の部位を切取って本実施例の半導体装置25を製造する。

【0028】

このように、本実施例のテープキャリア1は、半導体チップ8の電極形成面8aの縁部の中央側に1列に形成された高さの高い第1の突起電極と、その縁部の外側に1列に形成された高さの低い第2の突起電極とにそれぞれ接続する第1および第2のインナーリード11a、11bを絶縁膜12を挟んで2段に形成したので、ベースフィルム2のチップ搭載面2aに形成された第1のインナーリード11aと、絶縁膜12上の第2のインナーリード11bとを自身の強度を確保する幅で形成し、隣とのショートを避けるための一定の間隔で配置することができ、半導体チップ8の第1および第2突起電極16a、16bとの接合強度を確保しながら、2倍に高集積化された半導体チップ8を搭載することが可能になる。

【0029】

また、2列に形成された突起電極16を、その中央側を高く、外側を低く形成し、これらの第1および第2の突起電極16a、16bとにそれぞれ接続する第1および第2のインナーリード11a、11bを絶縁膜12を挟んで突起電極16の高低差に合わせて2段に形成したので、第1のインナーリード11aと第1の突起電極16a、および第2のインナーリード11bと第2の突起電極16bとをそれぞれ当接させて同時に接合することができ、高集積化された半導体チップ8の第1および第2突起電極16a、16bと第1および第2のインナーリード11a、11bとの接合をそれぞれの位置を合わせて1回の接合工程で容易に行うことができ、通常の熱圧着による接合工程をそのまま利用することが可能になり、高集積化された半導体チップ8を搭載したTCP型の半導体装置25の製造工程を簡素化することができる。

【0030】

更に、第1のアウターリード5aは、ベースフィルム2のチップ搭載面2aに形成された第1のインナーリード11aにチップ搭載面2a上で接続し、第2のアウターリード5bは、絶縁膜12上に形成された第2のインナーリード11bに絶縁膜12上で接続しているので、第1のインナーリード11aおよび第1のアウターリード5aと、第2のインナーリード11bおよび第2のアウターリード5bとをそれぞれ同一面上に形成することができ、2段に形成された第1および第2のインナーリード11a、11bを有するテープキャリア1の製造を容易に行うことができると共に、アウターリード5の並び方向の全幅を大幅に低減してベースフィルム2の使用量を削減することが可能になり、半導体装置25の製造コストを節減することができる。

【0031】

更に、第1のアウターリード5aの先端部が、その上段の第2のアウターリード5bの先端の外側に延在しているので、図示しない実装基板の配線端子と第1および第2のアウターリード5a、5bとの接合を容易に行うことができる。

以上説明したように、本実施例では、電極形成面の縁部の中央側に1列に形成された第1の突起電極および第1の突起電極の外側に千鳥に配置した第1の突起電極より低い高さで1列に形成された第2の突起電極とを有する半導体チップと、チップ搭載面に第1の突起電極上に延在して形成された第1のインナーリードおよび第1のインナーリード上に形成された絶縁膜を挟んで絶縁膜上に第2の突起電極上に延在して形成された第2のインナーリードとを有するベースフィルムとを設けたことによって、半導体チップの第1および第2突起電極とベースフィルム上の第1および第2のインナーリードとを位置を合わせて同時に接合することができ、接合工程を1回にして、高集積化された半導体チップを搭載した半導体装置の接合工程を簡素化することができる。

【0032】

また、ベースフィルムのチップ搭載面に、第1のインナーリードに接続する第1のアウターリードを形成し、絶縁膜上に第2のインナーリードに接続する第2のアウターリードを形成し、第1のアウターリードの先端を、第2のアウターリードの先端の外側に延在させるようにしたことによって、第1のインナーリードおよび第1のアウターリードと、第2のインナーリードおよび第2のアウターリードとをそれぞれ同一面上に形成することができ、2段に形成された第1および第2のインナーリードを有するテープキャリアの製造を容易に行うことができると共に、アウターリードの並び方向の全幅を大幅に低減することができる他、実装基板の配線端子と第1および第2のアウターリードとの接合を容易に行うことができる。

【実施例2】

【0033】

図8は実施例2のテープキャリアの上面を示す説明図、図9は実施例2のインナーリード形成領域の上面を示す説明図、図10は実施例2のテープキャリアの断面を示す説明図、図11は実施例2の半導体チップの電極形成面を示す説明図、図12は図11のF−F断面を示す説明図である。

上記の図10は図9に示すD−D断面線および図8に示すE−E断面線に沿った断面を同時に示した断面図である。また、図8、図9はソルダーレジストを除いた状態で描いてある。

【0034】

なお、上記実施例1と同様の部分は、同一の符号を付してその説明を省略する。

本実施例の第1および第2のインナーリード11a、11bと、第1および第2のアウターリード5a、5bは、上記実施例1と同様にそれぞれ絶縁膜12を挟んで階段状に2段に配置(図10参照)されているが、第1のインナーリード11aと第2のインナーリード11bとはその長手方向の2辺同士が上下で同じ位置となるように配置(図9参照)、つまり図10に示すように、同じ位置に絶縁膜12を挟んで重ね合わせて配置され、第1のアウターリード5aと第2のアウターリード5bも同様に同じ位置に絶縁膜12を挟んで重ね合わせて配置(図8参照)されている。

【0035】

このように配置しても、実施例1と同様に、平面配置の場合と比較して、1段に形成されるインナーリード11およびアウターリード5の数を半分にして、その並び方向の全幅(図9に示す寸法W等)を略半分にすることができる。この場合にインナーリード11およびアウターリード5のそれぞれの隣とのショートを避けるための一定の間隔が、自身の強度を確保する幅より広いときは並び方向の全幅を半分以下にすることができる。

【0036】

本実施例の半導体チップ8は、実施例1と同様の通常の半導体チップ8と同じ大きさで2倍に高集積化された半導体チップであるが、その第1の突起電極16aと第2の突起電極16bとは、図11に示すように、半導体チップ8の長手方向に形成された第1および第2の突起電極16a、16bは半導体チップ8の短手方向に沿って直列に配置され、半導体チップ8の短手方向に形成された第1および第2の突起電極16a、16bは半導体チップ8の長手方向に沿って直列に配置されており、これら並列に配置された第1の突起電極16aと第2の突起電極16bは実施例1と同様に、中央側に配置された第1の突起電極16aの高さが高く、外側に配置された第2の突起電極16bが低く形成され(図12参照)、第1の突起電極16aにはベースフィルム2のチップ搭載面2aに形成された半導体チップ8の中央側に延在している第1のインナーリード11aが接合され、第2の突起電極16bには、絶縁膜12を挟んで重ね合わされて形成された第2のインナーリード11bが接合される。

【0037】

本実施例のベースフィルム2上に半導体チップ8を搭載して形成される半導体装置25の製造は、図6に示すテープキャリアの製造方法および図7に示す半導体装置の製造方法と同様であるので、その説明を省略する。

この場合に、上記実施例1の工程P3における第2のアウターリード5bおよび第2のインナーリード11bの形成は、図8、図9に示す第2のアウターリード5bおよび第2のインナーリード11bの形成領域を覆うエッチングレジストを用いて形成される。

【0038】

以上説明したように、本実施例では、電極形成面の縁部に並列に形成された第1および第2の突起電極を有する半導体チップと、絶縁膜を挟んで2段に重ね合わせて形成された第1および第2のインナーリードを有するベースフィルムとを設けるようにしても、上記実施例1と同様の効果を得ることができる。

なお、上記実施例においては、半導体チップの2列の突起電極を千鳥に配置した場合と並列に配置した場合を例に、これらに対応する2段に形成された第1および第2のインナーリードを有するベースフィルムの形成について説明したが、半導体チップの2列の突起電極の配置は、千鳥と並列の中間的な配置であってもよく、規則性のない配置であってもよい。要は半導体チップの2列の突起電極の配置に合わせて2段に形成された第1および第2のインナーリードを形成すれば、上記と同様の効果を得ることができる。

【0039】

また、上記各実施例においては、絶縁膜はポリイミドであるとして説明したが、ソルダーレジストを絶縁膜として用いるようにしてもよい。

【図面の簡単な説明】

【0040】

【図1】実施例1のテープキャリアの上面を示す説明図

【図2】実施例1のインナーリード形成領域の上面を示す説明図

【図3】実施例1のテープキャリアの断面を示す説明図

【図4】実施例1の半導体チップの電極形成面を示す説明図

【図5】図4のC―C断面を示す説明図

【図6】実施例1のテープキャリアの製造方法を示す説明図

【図7】実施例1の半導体装置の製造方法を示す説明図

【図8】実施例2のテープキャリアの上面を示す説明図

【図9】実施例2のインナーリード形成領域の上面を示す説明図

【図10】実施例2のテープキャリアの断面を示す説明図

【図11】実施例2の半導体チップの電極形成面を示す説明図

【図12】図11のF−F断面を示す説明図

【符号の説明】

【0041】

1 テープキャリア

2 ベースフィルム

2a チップ搭載面

3 スプロケットホール

5 アウターリード

5a 第1のアウターリード

5b 第2のアウターリード

6 インナーリード形成領域

7a、7b アウターリード形成領域

8 半導体チップ

8a 電極形成面

11 インナーリード

11a 第1のインナーリード

11b 第2のインナーリード

12 絶縁膜

14 ソルダーレジスト

16 突起電極

16a 第1の突起電極

16b 第2の突起電極

21 レジストマスク

23 封止層

27 ボンディングステージ

28 ボンディングツール

【技術分野】

【0001】

本発明は、テープキャリア上に半導体チップを搭載して連続的に製造されるTCP(Tape Carrier Package)型の半導体装置に関する。

【背景技術】

【0002】

近年、テープキャリア上に搭載される半導体チップの高集積化が進展し、半導体チップに形成される突起電極の数が増加傾向にあり、これに伴ってテープキャリア上に形成されるインナーリードの数が増加し、隣合うインナーリード間およびアウターリード間のショートを避けるために一定の間隔でインナーリードやアウターリードを配置すると、半導体装置が大型化するという問題が生ずる。

【0003】

このため、インナーリードやアウターリードの幅を細くすると、インナーリードやアウターリード自身の強度の低下、および半導体チップの突起電極との接合強度や実装基板の配線端子との接合強度が低下するという問題が生じる。

このような問題に対処するため、従来のTCP型の半導体装置は、ポリイミド等の絶縁性を有するベースフィルムの表裏の面に、銅箔を接着積層し、これをエッチングによりパターニングしてベースフィルムの両面にインナーリードを形成し、裏面に形成されたインナーリードは熱圧着により半導体チップの外側に1列に形成された突起電極に直接接合し、おもて面に形成されたインナーリードと半導体チップの中央側に1列に形成された突起電極とは、ワイヤボンディングにより接合して半導体チップの高集積化への要求に対応している(例えば、特許文献1参照。)。

【特許文献1】特開平3−276737号公報(主に第2頁左下欄、第1図)

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した従来の技術においては、裏面に形成されたインナーリードと半導体チップの外側に形成された突起電極とは熱圧着により直接接合し、おもて面に形成されたインナーリードと半導体チップの中央側に形成された突起電極とは、ワイヤボンディングにより接合しているため、インナーリードと半導体チップの突起電極との接合工程を、熱圧着による接合工程と、ワイヤボンディングによる接合工程とに分けてTCP型の半導体装置の製造工程を構成することが必要になり、ワイヤボンディングによる接合工程を設けるための設備の導入やその設置のためのスペースの確保しなければならないという問題がある。

【0005】

本発明は、上記の問題点を解決するためになされたもので、高集積化された半導体チップの突起電極とインナーリードとの接合工程を簡素化する手段を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明は、上記課題を解決するために、半導体装置が、半導体チップと、絶縁性を有するベースフィルムと、前記半導体チップの一の面の縁部の中央側に、1列に形成された第1の突起電極と、該第1の突起電極の外側に、該第1の突起電極より低い高さで、1列に形成された第2の突起電極と、前記ベースフィルムの前記半導体チップの搭載面に、前記第1の突起電極上に延在して形成された第1のインナーリードと、該第1のインナーリードの前記ベースフィルムの反対側に形成された絶縁膜と、該絶縁膜上に、前記第2の突起電極上に延在して形成された第2のインナーリードとを備えたことを特徴とする。

【発明の効果】

【0007】

これにより、本発明は、半導体チップの第1および第2突起電極とベースフィルム上の第1および第2のインナーリードとを位置を合わせて同時に接合することができ、接合工程を1回にして、高集積化された半導体チップを搭載した半導体装置の接合工程を簡素化することができるという効果が得られる。

【発明を実施するための最良の形態】

【0008】

以下に、図面を参照して本発明による半導体装置の実施例について説明する。

【実施例1】

【0009】

図1は実施例1のテープキャリアの上面を示す説明図、図2は実施例1のインナーリード形成領域の上面を示す説明図、図1は実施例1のテープキャリアの断面を示す説明図、図4は実施例1の半導体チップの電極形成面を示す説明図、図5は図4のC−C断面を示す説明図、図6は実施例1のテープキャリアの製造方法を示す説明図、図7は実施例1の半導体装置の製造方法を示す説明図である。

【0010】

上記の図3は図2に示すA−A断面線および図1に示すB−B断面線に沿った断面を同時に示した断面図である。また、図1、図2はソルダーレジストを除いた状態で描いてある。

図1において、1はテープキャリアである。

2はベースフィルムであり、ポリイミド等の耐熱性および絶縁性を有する樹脂材料で製作された長尺のフィルム部材であって、その両方の縁領域には、図示しない駆動装置で駆動されるスプロケットの歯に嵌合してテープキャリア1の移動や位置決めを行うために所定のピッチでそれぞれ1列に配置されたスプロケットホール3が形成されている。

【0011】

5a、5bは第1および第2のアウターリード(区別を必要としない場合は、アウターリード5という。)であり、インナーリード形成領域6を挟んで両側に設定されたアウターリード形成領域7a、7bに銅(Cu)等の導電材料で形成された配線であって、アウターリード形成領域7a側の第1および第2のアウターリード5a、5bは半導体チップ8(図4、図5参照)への入力端子として機能し、アウターリード形成領域7b側の第1および第2のアウターリード5a、5bは半導体チップ8からの出力端子として機能する。

【0012】

また、第1および第2のアウターリード5a、5bの先端部には、それぞれパッド9が形成されている。

インナーリード形成領域6には、図2に示すように、その周囲の縁部に第1および第2のインナーリード11a、11b(区別を必要としない場合は、インナーリード11という。)が、それぞれ所定の第1および第2のアウターリード5a、5bと接続した状態(図1参照)で形成されている。

【0013】

本実施例の第1および第2のインナーリード11a、11b、並びに第1および第2のアウターリード5a、5bは、図3にハッチングを付して示すポリイミド等の絶縁材料で形成された絶縁膜12(図1および図2には2点鎖線で示してある。)を挟んでベースフィルム2の半導体チップ8の搭載面(チップ搭載面2aという。)上に2層に形成されており、チップ搭載面2a上に第1のインナーリード11aおよびこれに接続する第1のアウターリード5aが形成され、これらの上に形成された絶縁膜12のチップ搭載面2aと反対側の面上に第2のインナーリード11bおよびこれに接続する第2のアウターリード5bが形成されている。

【0014】

また、第1のインナーリード11aの先端部は、その上層の第2のインナーリード11bの先端よりインナーリード形成領域6の中央側に延在(図2参照)してそれぞれ形成され、第1のアウターリード5aの先端部は、その上層の第2のアウターリード5bの先端よりインナーリード形成領域6の外側に延在(図1参照)してそれぞれ形成されており、第1のインナーリード11aと第2のインナーリード11b、および第1のアウターリード5aと第2のアウターリード5bはそれぞれ絶縁膜12を挟んで階段状に2段に配置されている。

【0015】

更に、ベースフィルム2のチップ搭載面2aに形成された第1のインナーリード11aおよび第1のアウターリード5aと、絶縁膜12上の第2のインナーリード11bおよび第2のアウターリード5bとはそれぞれ自身の強度を確保する幅で形成され、かつ隣とのショートを避けるための一定の間隔で配置されている。

更に、本実施例の第1のインナーリード11aと第2のインナーリード11bとはその長手方向の1辺同士が上下で同じ位置となるように配置(図2参照)され、第1のアウターリード5aと第2のアウターリード5bとはその長手方向の1辺同士が上下で同じ位置となるように配置(図1参照)されている。

【0016】

このように、本実施例の第1および第2のインナーリード11a、11bと、第1および第2のアウターリード5bとは、それぞれ長手方向の辺が上下で同じ位置となるように配置されているので、通常の一つの面上に同じ数のインナーリード11およびアウターリード5を配置した平面配置の場合と比較して、1段に形成されるインナーリード11およびアウターリード5の数を半分にして、その並び方向の全幅(図2に示す寸法W等)を略半分にすることができる。この場合にインナーリード11およびアウターリード5のそれぞれの隣とのショートを避けるための一定の間隔が、自身の強度を確保する幅より広いときは並び方向の全幅を半分以下にすることができる。

【0017】

図3において、14はソルダーレジストであり、半田の侵入を防止するための絶縁性を有する膜であって、隣合う第2のインナーリード11b間および隣合う第2のアウターリード5b間をそれぞれ絶縁する機能も有している。

半導体チップ8は、通常の半導体チップ8と同じ大きさで2倍に高集積化された半導体チップであって、図4、図5に示すように、その一の面に多数の突起電極の形成され、この面(電極形成面8aという。)の周囲の縁部に、2列に並べた第1の突起電極16aと第2の突起電極16b(区別を必要としない場合は、突起電極16という。)とがそれぞれ矩形に1列に並べて形成されており、半導体チップ8の中央側に1列に形成された第1の突起電極16aの電極形成面8aからの高さは、図5に示すようにその外側に1列に形成された第2の突起電極16bより高く形成されている。

【0018】

本実施例の第1の突起電極16aと第2の突起電極16bとは、図4に示すように千鳥に配置されており、ベースフィルム2のチップ搭載面2aに形成された中央側に延在している第1のインナーリード11aは第1の突起電極16a上に達し、絶縁膜12上形成された第2のインナーリード11bは第2の突起電極16b上に達するように形成され、その段差は、第1の突起電極16aと第2の突起電極16bとの高さの差と同等に形成されており、第1の突起電極16aは第1のインナーリード11aに、第2の突起電極16bは第2のインナーリード11bにそれぞれ接合される(図7参照)。

【0019】

このような、高さの異なる第1および第2の突起電極16a、16bの製造は、例えば金(Au)等で突起電極を形成するときに、その電解メッキ工程における第1の突起電極16a側への通電時間を、第2の突起電極16b側への通電時間より長く設定して形成される。

図6において、21はマスク部材としてのレジストマスクであり、フォトリソグラフィによりベースフィルム2のチップ搭載面2a側に塗布されたポジ型またはネガ型のレジストを露光および現像処理して形成されたマスクパターンであって、本実施例の絶縁膜12の形成工程におけるマスクとして機能する。

【0020】

図7において、23は封止層であり、ベースフィルム2のチップ搭載面2aと半導体チップ8の電極形成面8aとの間に注入された熱硬化性のエポキシ樹脂等の封止樹脂を加熱硬化させて形成された絶縁性を有する層であって、半導体チップ8の電極形成面8aと反対側の面(裏面という。)を露出させた状態で形成され、第1および第2のインナーリード11a、11bと第1および第2の突起電極16a、16bとの接合部を絶縁すると共に外部の湿度等から保護する機能を有している。

【0021】

本実施例のベースフィルム2上に半導体チップ8を搭載して形成される半導体装置25は以下のようにして製造される。

以下に、図6にPで示す工程に従って本実施例のテープキャリアの製造方法について説明する。

P1、スプロケットホール3が形成されたベースフィルム2のチップ搭載面2a上に銅箔を接着積層し、フォトリソグラフィにより図1、図2に示す第1のアウターリード5aおよび第1のインナーリード11aの形成領域を覆うエッチングレジストを形成し、これをマスクとして銅箔をエッチングし、その後にエッチングレジストを除去して、ベースフィルム2のチップ搭載面2a上のアウターリード形成領域7a、7bおよびインナーリード形成領域6に、それぞれ第1のアウターリード5aおよびこれに接続する第1のインナーリード11aを形成する。

【0022】

P2、フォトリソグラフィにより、第1のインナーリード11aの先端部および第1のアウターリード5aの先端部を覆う領域(図2に示す2点鎖線で囲われた領域、および図1に示す2点鎖線で囲われた領域の外側の領域)を覆うレジストマスク21、つまり絶縁膜12の形成領域を露出させたレジストマスク21を形成し、これをマスクとして絶縁材料をコーティングして絶縁膜12を形成する。

【0023】

このとき、隣合う第1のインナーリード11a間および隣合う第1のアウターリード5a間は、それぞれ絶縁膜12が埋込まれて絶縁される。

P3、工程P2で形成したレジストマスク21を除去し、上記工程P1と同様にして絶縁膜状12上に、銅箔を接着積層し、図1、図2に示す第2のアウターリード5bおよび第2のインナーリード11bの形成領域を覆うエッチングレジストを用いて、絶縁膜12上のアウターリード形成領域7a、7bおよびインナーリード形成領域6に、それぞれ第2のアウターリード5bおよびこれに接続する第2のインナーリード11bを形成する。

【0024】

P4、そして、液状のソルダーレジスト14を第2のアウターリード5bおよび第2のインナーリード11bの先端部を残して塗布し、これを硬化させて隣合う第2のインナーリード11b間および隣合う第2のアウターリード5b間、並びにそれぞれの先端部を除く第2のアウターリード5bおよび第2のインナーリード11b上にソルダーレジスト14を形成する。

【0025】

このとき、隣合う第2のインナーリード11b間および隣合う第2のアウターリード5b間は、それぞれソルダーレジスト14が埋込まれて絶縁される。

このようにして製造されたテープキャリア1に半導体チップ8を搭載した半導体装置25の製造方法について、図7にPAで示す工程に従って説明する。

PA1、ボンディングステージ27に予め製造した半導体チップ8の裏面を載置し、スプロケットホール3を用いてチップ搭載面2aを下方に向けたテープキャリア1のインナーリード形成領域6を半導体チップ8上に移動させ、第1および第2のインナーリード11a、11bと第1および第2の突起電極16a、16bとをそれぞれ対向させて停止させる。

【0026】

PA2、ボンディングツール28によりベースフィルム2のチップ搭載面2aの反対側の面を押して、第1のインナーリード11aと第1の突起電極16a、および第2のインナーリード11bと第2の突起電極16bとをそれぞれ当接させ、ボンディングツール28により加熱、押圧して第1のインナーリード11aと第1の突起電極16a、および第2のインナーリード11bと第2の突起電極16bとを同時に接合する。

【0027】

PA3、スプロケットホール3を用いてチップ搭載面2aを上方に向けたテープキャリア1のインナーリード形成領域6を封止工程へ移動させ、封止樹脂を図7にハッチングを付して示すように、ベースフィルム2のチップ搭載面2aと半導体チップ8の電極形成面8aとの間に注入し、これを加熱硬化させて封止層23を形成する。

これにより、本実施例の半導体装置25がテープキャリア1上に形成され、その後にテープキャリア1から半導体装置25の部位を切取って本実施例の半導体装置25を製造する。

【0028】

このように、本実施例のテープキャリア1は、半導体チップ8の電極形成面8aの縁部の中央側に1列に形成された高さの高い第1の突起電極と、その縁部の外側に1列に形成された高さの低い第2の突起電極とにそれぞれ接続する第1および第2のインナーリード11a、11bを絶縁膜12を挟んで2段に形成したので、ベースフィルム2のチップ搭載面2aに形成された第1のインナーリード11aと、絶縁膜12上の第2のインナーリード11bとを自身の強度を確保する幅で形成し、隣とのショートを避けるための一定の間隔で配置することができ、半導体チップ8の第1および第2突起電極16a、16bとの接合強度を確保しながら、2倍に高集積化された半導体チップ8を搭載することが可能になる。

【0029】

また、2列に形成された突起電極16を、その中央側を高く、外側を低く形成し、これらの第1および第2の突起電極16a、16bとにそれぞれ接続する第1および第2のインナーリード11a、11bを絶縁膜12を挟んで突起電極16の高低差に合わせて2段に形成したので、第1のインナーリード11aと第1の突起電極16a、および第2のインナーリード11bと第2の突起電極16bとをそれぞれ当接させて同時に接合することができ、高集積化された半導体チップ8の第1および第2突起電極16a、16bと第1および第2のインナーリード11a、11bとの接合をそれぞれの位置を合わせて1回の接合工程で容易に行うことができ、通常の熱圧着による接合工程をそのまま利用することが可能になり、高集積化された半導体チップ8を搭載したTCP型の半導体装置25の製造工程を簡素化することができる。

【0030】

更に、第1のアウターリード5aは、ベースフィルム2のチップ搭載面2aに形成された第1のインナーリード11aにチップ搭載面2a上で接続し、第2のアウターリード5bは、絶縁膜12上に形成された第2のインナーリード11bに絶縁膜12上で接続しているので、第1のインナーリード11aおよび第1のアウターリード5aと、第2のインナーリード11bおよび第2のアウターリード5bとをそれぞれ同一面上に形成することができ、2段に形成された第1および第2のインナーリード11a、11bを有するテープキャリア1の製造を容易に行うことができると共に、アウターリード5の並び方向の全幅を大幅に低減してベースフィルム2の使用量を削減することが可能になり、半導体装置25の製造コストを節減することができる。

【0031】

更に、第1のアウターリード5aの先端部が、その上段の第2のアウターリード5bの先端の外側に延在しているので、図示しない実装基板の配線端子と第1および第2のアウターリード5a、5bとの接合を容易に行うことができる。

以上説明したように、本実施例では、電極形成面の縁部の中央側に1列に形成された第1の突起電極および第1の突起電極の外側に千鳥に配置した第1の突起電極より低い高さで1列に形成された第2の突起電極とを有する半導体チップと、チップ搭載面に第1の突起電極上に延在して形成された第1のインナーリードおよび第1のインナーリード上に形成された絶縁膜を挟んで絶縁膜上に第2の突起電極上に延在して形成された第2のインナーリードとを有するベースフィルムとを設けたことによって、半導体チップの第1および第2突起電極とベースフィルム上の第1および第2のインナーリードとを位置を合わせて同時に接合することができ、接合工程を1回にして、高集積化された半導体チップを搭載した半導体装置の接合工程を簡素化することができる。

【0032】

また、ベースフィルムのチップ搭載面に、第1のインナーリードに接続する第1のアウターリードを形成し、絶縁膜上に第2のインナーリードに接続する第2のアウターリードを形成し、第1のアウターリードの先端を、第2のアウターリードの先端の外側に延在させるようにしたことによって、第1のインナーリードおよび第1のアウターリードと、第2のインナーリードおよび第2のアウターリードとをそれぞれ同一面上に形成することができ、2段に形成された第1および第2のインナーリードを有するテープキャリアの製造を容易に行うことができると共に、アウターリードの並び方向の全幅を大幅に低減することができる他、実装基板の配線端子と第1および第2のアウターリードとの接合を容易に行うことができる。

【実施例2】

【0033】

図8は実施例2のテープキャリアの上面を示す説明図、図9は実施例2のインナーリード形成領域の上面を示す説明図、図10は実施例2のテープキャリアの断面を示す説明図、図11は実施例2の半導体チップの電極形成面を示す説明図、図12は図11のF−F断面を示す説明図である。

上記の図10は図9に示すD−D断面線および図8に示すE−E断面線に沿った断面を同時に示した断面図である。また、図8、図9はソルダーレジストを除いた状態で描いてある。

【0034】

なお、上記実施例1と同様の部分は、同一の符号を付してその説明を省略する。

本実施例の第1および第2のインナーリード11a、11bと、第1および第2のアウターリード5a、5bは、上記実施例1と同様にそれぞれ絶縁膜12を挟んで階段状に2段に配置(図10参照)されているが、第1のインナーリード11aと第2のインナーリード11bとはその長手方向の2辺同士が上下で同じ位置となるように配置(図9参照)、つまり図10に示すように、同じ位置に絶縁膜12を挟んで重ね合わせて配置され、第1のアウターリード5aと第2のアウターリード5bも同様に同じ位置に絶縁膜12を挟んで重ね合わせて配置(図8参照)されている。

【0035】

このように配置しても、実施例1と同様に、平面配置の場合と比較して、1段に形成されるインナーリード11およびアウターリード5の数を半分にして、その並び方向の全幅(図9に示す寸法W等)を略半分にすることができる。この場合にインナーリード11およびアウターリード5のそれぞれの隣とのショートを避けるための一定の間隔が、自身の強度を確保する幅より広いときは並び方向の全幅を半分以下にすることができる。

【0036】

本実施例の半導体チップ8は、実施例1と同様の通常の半導体チップ8と同じ大きさで2倍に高集積化された半導体チップであるが、その第1の突起電極16aと第2の突起電極16bとは、図11に示すように、半導体チップ8の長手方向に形成された第1および第2の突起電極16a、16bは半導体チップ8の短手方向に沿って直列に配置され、半導体チップ8の短手方向に形成された第1および第2の突起電極16a、16bは半導体チップ8の長手方向に沿って直列に配置されており、これら並列に配置された第1の突起電極16aと第2の突起電極16bは実施例1と同様に、中央側に配置された第1の突起電極16aの高さが高く、外側に配置された第2の突起電極16bが低く形成され(図12参照)、第1の突起電極16aにはベースフィルム2のチップ搭載面2aに形成された半導体チップ8の中央側に延在している第1のインナーリード11aが接合され、第2の突起電極16bには、絶縁膜12を挟んで重ね合わされて形成された第2のインナーリード11bが接合される。

【0037】

本実施例のベースフィルム2上に半導体チップ8を搭載して形成される半導体装置25の製造は、図6に示すテープキャリアの製造方法および図7に示す半導体装置の製造方法と同様であるので、その説明を省略する。

この場合に、上記実施例1の工程P3における第2のアウターリード5bおよび第2のインナーリード11bの形成は、図8、図9に示す第2のアウターリード5bおよび第2のインナーリード11bの形成領域を覆うエッチングレジストを用いて形成される。

【0038】

以上説明したように、本実施例では、電極形成面の縁部に並列に形成された第1および第2の突起電極を有する半導体チップと、絶縁膜を挟んで2段に重ね合わせて形成された第1および第2のインナーリードを有するベースフィルムとを設けるようにしても、上記実施例1と同様の効果を得ることができる。

なお、上記実施例においては、半導体チップの2列の突起電極を千鳥に配置した場合と並列に配置した場合を例に、これらに対応する2段に形成された第1および第2のインナーリードを有するベースフィルムの形成について説明したが、半導体チップの2列の突起電極の配置は、千鳥と並列の中間的な配置であってもよく、規則性のない配置であってもよい。要は半導体チップの2列の突起電極の配置に合わせて2段に形成された第1および第2のインナーリードを形成すれば、上記と同様の効果を得ることができる。

【0039】

また、上記各実施例においては、絶縁膜はポリイミドであるとして説明したが、ソルダーレジストを絶縁膜として用いるようにしてもよい。

【図面の簡単な説明】

【0040】

【図1】実施例1のテープキャリアの上面を示す説明図

【図2】実施例1のインナーリード形成領域の上面を示す説明図

【図3】実施例1のテープキャリアの断面を示す説明図

【図4】実施例1の半導体チップの電極形成面を示す説明図

【図5】図4のC―C断面を示す説明図

【図6】実施例1のテープキャリアの製造方法を示す説明図

【図7】実施例1の半導体装置の製造方法を示す説明図

【図8】実施例2のテープキャリアの上面を示す説明図

【図9】実施例2のインナーリード形成領域の上面を示す説明図

【図10】実施例2のテープキャリアの断面を示す説明図

【図11】実施例2の半導体チップの電極形成面を示す説明図

【図12】図11のF−F断面を示す説明図

【符号の説明】

【0041】

1 テープキャリア

2 ベースフィルム

2a チップ搭載面

3 スプロケットホール

5 アウターリード

5a 第1のアウターリード

5b 第2のアウターリード

6 インナーリード形成領域

7a、7b アウターリード形成領域

8 半導体チップ

8a 電極形成面

11 インナーリード

11a 第1のインナーリード

11b 第2のインナーリード

12 絶縁膜

14 ソルダーレジスト

16 突起電極

16a 第1の突起電極

16b 第2の突起電極

21 レジストマスク

23 封止層

27 ボンディングステージ

28 ボンディングツール

【特許請求の範囲】

【請求項1】

半導体チップと、

絶縁性を有するベースフィルムと、

前記半導体チップの一の面の縁部の中央側に、1列に形成された第1の突起電極と、

該第1の突起電極の外側に、該第1の突起電極より低い高さで、1列に形成された第2の突起電極と、

前記ベースフィルムの前記半導体チップの搭載面に、前記第1の突起電極上に延在して形成された第1のインナーリードと、

該第1のインナーリードの前記ベースフィルムの反対側に形成された絶縁膜と、

該絶縁膜上に、前記第2の突起電極上に延在して形成された第2のインナーリードとを備えたことを特徴とする半導体装置。

【請求項2】

請求項1において、

前記第1の突起電極と、前記第2の突起電極とが、千鳥に配置されていることを特徴とする半導体装置。

【請求項3】

請求項1において、

前記第1の突起電極と、前記第2の突起電極とが、並列に配置されていることを特徴とする半導体装置。

【請求項4】

請求項1ないし請求項3のいずれか一項において、

前記ベースフィルムの前記半導体チップの搭載面の、第1および第2のインナーリードの外側に形成され、前記第1のインナーリードに接続する第1のアウターリードと、

該第1のアウターリードの前記ベースフィルムの反対側に形成された前記絶縁膜上に形成され、前記第2のインナーリードに接続する第2のアウターリードとを設け、

前記第1のアウターリードの先端部を、前記第2のアウターリードの先端の外側に延在させたことを特徴とする半導体装置。

【請求項1】

半導体チップと、

絶縁性を有するベースフィルムと、

前記半導体チップの一の面の縁部の中央側に、1列に形成された第1の突起電極と、

該第1の突起電極の外側に、該第1の突起電極より低い高さで、1列に形成された第2の突起電極と、

前記ベースフィルムの前記半導体チップの搭載面に、前記第1の突起電極上に延在して形成された第1のインナーリードと、

該第1のインナーリードの前記ベースフィルムの反対側に形成された絶縁膜と、

該絶縁膜上に、前記第2の突起電極上に延在して形成された第2のインナーリードとを備えたことを特徴とする半導体装置。

【請求項2】

請求項1において、

前記第1の突起電極と、前記第2の突起電極とが、千鳥に配置されていることを特徴とする半導体装置。

【請求項3】

請求項1において、

前記第1の突起電極と、前記第2の突起電極とが、並列に配置されていることを特徴とする半導体装置。

【請求項4】

請求項1ないし請求項3のいずれか一項において、

前記ベースフィルムの前記半導体チップの搭載面の、第1および第2のインナーリードの外側に形成され、前記第1のインナーリードに接続する第1のアウターリードと、

該第1のアウターリードの前記ベースフィルムの反対側に形成された前記絶縁膜上に形成され、前記第2のインナーリードに接続する第2のアウターリードとを設け、

前記第1のアウターリードの先端部を、前記第2のアウターリードの先端の外側に延在させたことを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2007−329278(P2007−329278A)

【公開日】平成19年12月20日(2007.12.20)

【国際特許分類】

【出願番号】特願2006−158900(P2006−158900)

【出願日】平成18年6月7日(2006.6.7)

【出願人】(000000295)沖電気工業株式会社 (6,645)

【出願人】(390008855)宮崎沖電気株式会社 (151)

【Fターム(参考)】

【公開日】平成19年12月20日(2007.12.20)

【国際特許分類】

【出願日】平成18年6月7日(2006.6.7)

【出願人】(000000295)沖電気工業株式会社 (6,645)

【出願人】(390008855)宮崎沖電気株式会社 (151)

【Fターム(参考)】

[ Back to top ]