半導体装置

【課題】 製造プロセスの複雑化や製造コストの増大を招くことなく、デュアルメタルゲートCMOS構造を実現する。

【解決手段】 基板上にn,pチャネルの各MISトランジスタ100,200を有する半導体装置であって、nMISトランジスタ100は、基板10上に形成されたp型半導体領域101と、p型半導体領域101上にゲート絶縁膜104を介して形成され、1モノレイヤー以上3nm以下の下層ゲート電極111と、下層ゲート電極111上に形成され、平均的な電気陰性度が下層ゲート電極111のそれより0.1以上小さい上層ゲート電極112とを含み、pMISトランジスタ200は、基板10上に形成されたn型半導体領域201と、n型半導体領域201上にゲート絶縁膜204を介して形成され、上層ゲート電極111と同一金属材料からなるゲート電極210とを含んで形成されている。

【解決手段】 基板上にn,pチャネルの各MISトランジスタ100,200を有する半導体装置であって、nMISトランジスタ100は、基板10上に形成されたp型半導体領域101と、p型半導体領域101上にゲート絶縁膜104を介して形成され、1モノレイヤー以上3nm以下の下層ゲート電極111と、下層ゲート電極111上に形成され、平均的な電気陰性度が下層ゲート電極111のそれより0.1以上小さい上層ゲート電極112とを含み、pMISトランジスタ200は、基板10上に形成されたn型半導体領域201と、n型半導体領域201上にゲート絶縁膜204を介して形成され、上層ゲート電極111と同一金属材料からなるゲート電極210とを含んで形成されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、同一基板上に金属ゲートを有するpチャネルMISトランジスタとnチャネルMISトランジスタを形成した半導体装置に関する。

【背景技術】

【0002】

近年、同一基板上にpチャネルMISトランジスタとnチャネルMISトランジスタを形成したCMOSデバイスにおいて、ゲート電極材料として金属を用いるメタルゲート技術が注目を集めている。金属は、原子密度と同程度の高い電荷密度を持つため、金属をゲート電極として用いた場合、ゲート電極の空乏化を無視することができる。

【0003】

メタルゲート電極を用いたCMOSデバイスにおいて低い閾値電圧を実現するためには、いわゆるデュアルメタルゲートCMOS構造を成す必要がある。デュアルメタルゲートCMOS構造を成すためには、nチャネルMISトランジスタ及びpチャネルMISトランジスタの各ゲート電極は、それぞれSiの伝導帯端及び価電子帯端に近い実効仕事関数を示す必要があり、pチャネルMISトランジスタのゲート電極の実効仕事関数がnチャネルMISトランジスタの実効仕事関数より0.4eV以上高いことが求められる。現在のところ、これを実現する方法としては、nチャネルMISトランジスタ及びpチャネルMISトランジスタの各ゲート電極を全く異なる金属材料で構成するものが一般的である(例えば、特許文献1及び非特許文献1参照)。

【0004】

しかしながら、nチャネルMISトランジスタとpチャネルMISトランジスタでゲート電極に異なる金属材料を用いた場合、ゲート電極の形成及び加工共に、nチャネルMISトランジスタ及びpチャネルMISトランジスタで別々に行う必要がある。このため、製造プロセスが複雑化し、製造コストが増大するという問題が生じてしまう。ちなみに特許文献1の方法では、pMISトランジスタ及びnMISトランジスタのゲート電極材料としてモリブデンを用いながら、一方に炭素を導入することにより、各々のゲート電極の仕事関数を異ならせている。この場合、一方のゲート電極部分をマスクするためのマスクの形成、炭素の導入、炭化のための熱処理、マスクの除去等の工程が必要となり、製造プロセスが複雑になる。

【0005】

メタルゲート技術導入実現のためには、製造プロセスがなるべく煩雑化しないような、デュアルメタルゲートCMOS構造を見出す必要がある。

【特許文献1】特開2004−207481号公報

【非特許文献1】米国特許 US7,030,430

【発明の開示】

【発明が解決しようとする課題】

【0006】

このように従来、CMOSデバイスの性能向上のためにはデュアルメタルゲート技術の導入が必須であるが、その実現にはnチャネルMISトランジスタとpチャネルMISトランジスタでゲート電極として異なる金属材料を用いる必要があり、これが製造プロセスの複雑化や製造コストの増大を招く要因となっていた。

【0007】

本発明は、上記事情を考慮してなされたもので、その目的とするところは、nチャネルMISトランジスタとpチャネルMISトランジスタでゲート電極として実質的に同じ金属材料を用いることができ、製造プロセスの複雑化や製造コストの増大を招くことなく、デュアルメタルゲートCMOS構造を実現することのできる半導体装置を提供することにある。

【課題を解決するための手段】

【0008】

上記課題を解決するために本発明は、次のような構成を採用している。

【0009】

即ち、本発明の一態様は、基板上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された半導体装置であって、前記nチャネルMISトランジスタは、前記基板上に形成されたp型半導体領域と、前記p型半導体領域上に形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第1下層ゲート電極と、前記第1下層ゲート電極上に形成され、平均的な電気陰性度が第1下層ゲート電極の平均的な電気陰性度よりも0.1以上小さく、金属材料で形成された第1上層ゲート電極とを含んで形成され、前記pチャネルMISトランジスタは、前記基板上に形成されたn型半導体領域と、前記n型半導体領域上に形成された第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成され、前記金属材料で形成された第2ゲート電極とを含んで形成されていることを特徴とする。

【0010】

また、本発明の別の一態様は、基板上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された半導体装置であって、前記nチャネルMISトランジスタは、前記基板上に形成されたp型半導体領域と、前記p型半導体領域上に形成され、金属材料で形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された第1ゲート電極とを含んで形成され、前記pチャネルMISトランジスタは、前記基板上に形成されたn型半導体領域と、前記n型半導体領域上に形成された第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第2下層ゲート電極と、前記第2下層ゲート電極上に形成され、平均的な電気陰性度が第2下層ゲート電極の平均的な電気陰性度よりも0.1以上大きく、前記金属材料で形成された第2上層ゲート電極とを含んで形成されていることを特徴とする。

【0011】

また、本発明の更に別の一態様は、基板上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された半導体装置であって、前記基板上に形成されたp型半導体領域と、前記p型半導体領域上に形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第1下層ゲート電極と、前記第1下層ゲート電極上に形成され、平均的な電気陰性度が第1下層ゲート電極の平均的な電気陰性度よりも小さく、金属材料で形成された第1上層ゲート電極とを含んで形成されたnチャネルMISトランジスタと、前記基板上に形成されたn型半導体領域と、前記n型半導体領域上に形成された第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第2下層ゲート電極と、前記第2下層ゲート電極上に形成され、平均的な電気陰性度が第2下層ゲート電極の平均的な電気陰性度よりも大きく、前記金属材料で形成された第2上層ゲート電極とを含んで形成されたpチャネルMISトランジスタと、を具備し、前記第1下層ゲート電極と前記第1上層ゲート電極との平均的な電気陰性度の差の絶対値Δχ(1) と、前記第2下層ゲート電極と前記第2上層ゲート電極との平均的な電気陰性度の差の絶対値Δχ(2) と、の和が0.1以上であることを特徴とする。

【発明の効果】

【0012】

本発明によれば、nチャネルMISトランジスタとpチャネルMISトランジスタでゲート電極に実質的に同じ金属材料を用いながら、pチャネルMISトランジスタのゲート電極の実効仕事関数をnチャネルMISトランジスタの実効仕事関数よりも十分大きくすることができる。従って、nチャネルMISトランジスタ及びpチャネルMISトランジスタの各ゲート電極を一括で加工することができ、製造プロセスの複雑化及び製造コストの低減をはかることができる。

【発明を実施するための最良の形態】

【0013】

(発明の概要及び原理)

発明の実施形態について説明する前に、まず、本発明の原理について説明する。

【0014】

ゲート電極の実効仕事関数Φeff は、式(1)のように表される。

【0015】

Φeff =Φbulk+Φinterface …(1)

Φbulkは、ゲート電極のバルク部分の性質によって決定され、Φinterfaceはゲート電極/ゲート絶縁膜界面における電荷分布によって決定される項である。ここに、ゲート絶縁膜表面上に形成された下層と下層表面上に形成された上層からなる二層構造を含む積層構造のゲート電極があるとする。このとき、図1に示すように、下層の膜厚が、1モノレイヤー以上、3nm以下である場合、Φbulkは主に上層の性質によって決定される一方で、Φinterfaceは下層の性質によって決定される。

【0016】

Φinterfaceは、ゲート電極側の原子とゲート絶縁膜側の原子とが互いに結合した場合に形成するダイポールの大きさに依存する。ここで、ゲート電極が、Ta−C合金、ゲート絶縁膜が酸化物からなる場合を考える。

【0017】

図2は、ゲート電極側のTaとゲート絶縁膜側のOが互いに結合した場合のエネルギーバンド図を示したものである。TaとOの電気陰性度χは、それぞれ1.5と3.5であるため、TaとOが結合すると、電子はより電気陰性度χの高いO、即ちゲート絶縁膜側に偏る。そのとき、図2に示すように、Φinterfaceが上昇してΦeff が増加する。

【0018】

一方、ゲート電極側のCとゲート絶縁膜側のOが結合した場合を考える。このとき、Cの電気陰性度χは2.5であり、Taに比べると、電子を引き付ける力が強い。そのため、Ta−O結合が形成した場合に比べると、電子の絶縁膜側への偏りは小さく、その分Φinterfaceも小さくなる。

【0019】

以上のことを、より一般的に記述すると、ゲート絶縁膜が同一である場合、ゲート電極のゲート絶縁膜側に電気陰性度χの小さな原子が多い(即ちゲート電極のゲート絶縁膜側の平均的なχが小さい)ほどΦinterfaceは大きく、ゲート電極側のゲート絶縁膜に電気陰性度χの大きな原子が多い(即ちゲート電極の平均的なχが大きい)ほどΦinterfaceは小さいということになる。本明細書において、平均的なχとは、金属材料を構成する元素の電気陰性度の幾何平均のことを示す。例えば、TaxCy の平均的なχは、

【数1】

【0020】

と表される。χTa及びχCは、それぞれTa及びCの電気陰性度のことである。

【0021】

以上の理由により、図3(a)(b)に示すように、ゲート電極下層(B)の平均的なχが、ゲート電極上層(A)のχよりも大きい場合には、A/Bの積層構造からなるゲート電極のΦinterfaceは、A単層からなるゲート電極のΦinterfaceよりも小さい。逆に、ゲート電極下層(B)の平均的なχが、ゲート電極上層(A)の平均的なχよりも小さい場合には、図4(a)(b)に示すように、A/Bの積層構造からなるゲート電極のΦinterfaceは、A単層からなるゲート電極のΦinterfaceよりも大きい。

【0022】

ところで、一般にχが高いほどΦbulkは大きくなる。そのため、ゲート電極下層(B)がΦbulkにも影響する場合には、Φbulkが受ける影響とΦinterfaceが受ける影響が相殺してしまう。よって、ゲート電極下層(B)はΦinterfaceとしてのみ機能せねばならない。これは、上述したように、ゲート電極下層(B)の厚さが、1モノレイヤー以上3nm以下であれば実現され、そのとき、Φinterfaceの差がそのままΦeff に反映されることになる。

【0023】

本発明者らは、ゲート電極を積層構造にすることで、どれほどのΦeff 差が生じるのか検討した。その結果、ゲート電極上層(A)の平均的なχとゲート電極下層(B)の平均的なχとの差の絶対値Δχが0.1以上であれば、A単層からなるMISトランジスタとA/B積層からなるMISトランジスタのΦeff 差(Δφeff)が、デュアルメタルゲートCMOS構造の実現のために必要とされる0.4eV以上になることを見出した。さらに、Δφeff とΔχとは、

ΔΦeff = 0.4×Δχ/0.1 …(3)

の関係にあることを見出した。

【0024】

図5は、TaCx/TaCy(y>x)の積層構造からなるゲート電極と、TaCx単層からなるゲート電極の実効仕事関数の実測値を示すものである。なお、ここではゲート絶縁膜としてSiO2 を用いている。

【0025】

ゲート電極がTaCx単層の場合(M1)は、実効仕事関数は4.7eV程度であるのに対し、ゲート電極がTaCx/TaCy(y>x)の場合(M2)には、4.2eV程度の実効仕事関数を示す。ゲート電極M1及びM2のCの原子濃度を物理分析により調べたところ、ゲート絶縁膜/ゲート電極界面から3nm以上深い領域のC原子濃度は互いに同じであったが、ゲート電極のゲート絶縁膜極近傍の領域のC原子濃度は、M1では52 at.%、M2では63 at.%であった。これを平均的なχに直すと、M1では1.96、M2では2.07で、両者には0.1以上のχ差があり、前述した0.4eV以上のΦeff 差を得るための条件を満たしている。この事実は、上述した原理の妥当性を示していると云える。

【0026】

以下、図面を参照して本発明の実施形態について説明する。なお、各実施形態を通して共通の構成には同一の符号を付し、重複する説明は省略する。

【0027】

(第1の実施形態)

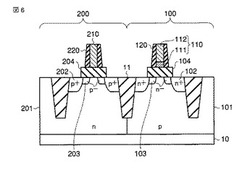

図6は、本発明の第1の実施形態に係わるデュアルメタルゲートCMOS構造の半導体装置の概略構造を示す断面図である。

【0028】

半導体基板としてのSi基板10の表面領域には、p型半導体領域101とn型半導体領域201が設けられ、それぞれの領域101,201にnチャネルMISトランジスタ100、pチャネルMISトランジスタ200が形成されている。p型半導体領域101及びn型半導体領域201は、いわゆるウエルとして形成され、各々の領域101,201の境界部にはこれらを分離するための素子分離領域11が形成されている。

【0029】

p型半導体領域101の表面上には第1のゲート絶縁膜104が形成されており、このゲート絶縁膜104上には、積層構造を成す第1のゲート電極110が形成されている。このゲート電極110の下層(第1下層ゲート電極)111は、厚さが1モノレイヤー以上3nm以下のTa−C合金からなり、上層(第1上層ゲート電極)112はTa−C合金からなる。但し、下層ゲート電極111の平均的な電気陰性度χは、上層ゲート電極112の平均的なχよりも0.1以上大きい。これは、下層ゲート電極111のC原子濃度が上層ゲート電極112のC原子濃度より10 at.%以上高いことと同義である。

【0030】

n型半導体領域201の表面上には第2のゲート絶縁膜204が形成されており、このゲート絶縁膜204の表面上にはTa−C合金からなるゲート電極(第2ゲート電極)210が形成されている。このゲート電極210は、第1上層ゲート電極212と同じ材料であり、上層ゲート電極212と同時に形成されている。

【0031】

ゲート電極210及び上層ゲート電極112の上には、さらにWやTiNといった高融点金属等が形成されていてもよい。なお、図6のその他の構成である素子分離領域11、ソース/ドレイン領域102,202、エクステンション領域103,203、ゲート側壁絶縁膜120,220は、通常の半導体プロセスより形成可能である。また、ゲート絶縁膜104,204は同じ材料であり、同時に形成されている。さらに、側壁絶縁膜120,220も同じ材料であり、同時に形成されている。

【0032】

前述した原理により、本実施形態の構造を用いることで、メタルゲートを用いたデュアルメタルゲートCMOS構造を実現することができる。また、nチャネルMISトランジスタ100のゲート電極110の下層ゲート電極111は非常に薄く、その他のゲート電極部分(上層ゲート電極112)は、pチャネルMISトランジスタ200のゲート電極210と同一である。このため、ゲートの加工を一括で行うことができ、製造プロセスの簡略化及び製造コストの低減をはかることができる。

【0033】

また、nチャネルMISトランジスタ100及びpチャネルMISトランジスタ200の閾値電圧をどちらも十分低くするためには、nチャネルMISトランジスタ100の実効仕事関数(Φeff(N))は4.3eV以下、pチャネルMISトランジスタ200の実効仕事関数(Φeff(P))は4.7eV以上であることが望ましい。本実施形態においては、pチャネルMISトランジスタ200のゲート電極210は、ゲート電極単層からなり、Φbulk及びΦinterface共に単層のTaCの性質のみで決定される。そのため、ゲート電極210は、4.7以上の実効仕事関数値を持つことが望ましい。

【0034】

一方、積層構造からなるnチャネルMISトランジスタ100のゲート電極110の実効仕事関数は、下層ゲート電極111と上層ゲート電極112の電気陰性度差Δχにより、ゲート電極210の実効仕事関数よりも低い。nチャネルMISトランジスタ100のゲート電極実効仕事関数Φeff(N) が4.3eV以下であるためには、前記式(3)より、Δχが、

Φeff(P)-0.4×Δχ/0.1 ≦ 4.3 …(4)

を満たしていればよい。

【0035】

ところで、ゲート電極のゲート絶縁膜側の構造と、その組成及び厚さは、MIS構造のSi基板を除去し、ゲート絶縁膜越しにXPS測定(裏面XPS測定)を行うことで調べることができる。XPS測定の際の光電子検出角度(TOA)が低角であるほどゲート絶縁膜/ゲート電極界面から浅い領域のゲート電極の情報が得られ、TOAを高角にすればゲート絶縁膜/ゲート電極界面から深い領域のゲート電極の情報が得られる。このため、TOAを変えることで、ゲート絶縁膜/ゲート金属界面から所望の深さのゲート電極の組成を調べることができる。また、ゲート電極/ゲート絶縁膜の断面構造は、TEM−EELS法によっても分析可能である。

【0036】

前述の原理の説明時に用いた図5に示すゲート電極M1及びM2の構造と、その組成及び厚さは、裏面XPS測定により得たものである。

【0037】

また、pチャネルMISトランジスタ200のゲート電極210としては、TaC(111)配向性の強いTaCxを用いることが有効である。それは、結晶化したTaCxの実効仕事関数はその結晶面に依存し、TaC(111)面は、特に高い実効仕事関数を示すためである。これは、絶縁膜と接している面がTaC(111)面の場合はΦinterfaceが大きいからであり、TaC(111)面の結晶配向率[TaC(111)面/{TaC(111)面+TaC(200)面}が80%以上であればこの効果が得られることが分かっている。

【0038】

つまり、pチャネルMISトランジスタ200のゲート電極210がTaC(111)面の結晶配向率[TaC(111)面/{TaC(111)面+TaC(200)面}]が80%以上であるTaCxからなれば、pチャネルMISトランジスタ200のゲート電極210の実効仕事関数は結晶化していないTa−C合金を用いた場合の実効仕事関数よりも大きくなる。そのため、nチャネルMISトランジスタ100のゲート電極110の実効仕事関数とpチャネルMISトランジスタ200のゲート電極210の実効仕事関数との差をより容易に得ることができる。

【0039】

なお、nチャネルMISトランジスタ100においては、上層ゲート電極112としてTaC(111)配向性の強いTaCxを用いたとしても、上層ゲート電極112はゲート絶縁膜104に直接接していないので、配向性の制御により実効仕事関数が大きくなることはない。

【0040】

このように、結晶配向性の制御により仕事関数を変化させられることは、本発明者らにより見出され、既に提案されている(特願2005−356951)。以下に、この提案について簡単に説明しておく。

【0041】

従来技術では、TaCx電極の仕事関数が4.18eVであったため、一般にnチャネルMISトランジスタにしかTaCx電極を用いていない。仮に、従来技術のTaCxをpチャネルMISトランジスタのゲート電極に用いたとしても、そのしきい値電圧は非常に高くなり、CMOSの正常動作は不可能になる。

【0042】

本発明者らは、TaとCとの組成比(C/Ta)を0.5〜1.5に設定し、TaCxを結晶化状態で用いた。さらに、本発明者らは、(111)配向性を強くすることで4.8eV程度のp+ シリコンに近い仕事関数が得られ、(111)配向に対し(200)配向成分を増やすことでn+ シリコンに近い仕事関数が得られることを新たに見出し、これをCMOSトランジスタのデュアルメタルゲートに適用した。

【0043】

図7はその発見を示す、膜厚100nmのTaCx薄膜の結晶性を調べた実験結果を示す図である。横軸は角度(2θ)、縦軸は強度を示している。また、pMOS用TaC電極とnMOS用TaC電極のそれぞれの特性が区別できるように、縦軸方向にオフセットして示している。TaCx膜の組成は共にC/Ta〜1であるが、成膜法の違いによって、(111)回折ピークが最も強くなるものと、(200)回折ピークが最も強くなるものに作り分けできることが示された。

【0044】

上記では、TaC膜/ゲート絶縁膜/Si基板の分析用試料を用いた結果を示した。このような実験はもちろん完成したトランジスタでも実施可能であり、その場合はトランジスタのゲート電極の部分をTEM観察などで用いられるピックアップ法で切り出し、ゲート電極の断面を電子線回折法で分析すれば、(111)配向と(200)配向の割合を確認することが可能である。この場合、TEM法の電子ビームを用いるので分析位置のポジショニング精度が高い。これにより、実際にしきい値電圧制御に強く関係する、ゲート絶縁膜と接した領域のTaC膜の配向性を確認することが容易となる。

【0045】

図8は、上記のようにして配向性を変化させたときの仕事関数の変化を示した図である。TaCxがp+ シリコン同等の4.75eV以上の仕事関数を示すために、下記の(5)式で示す(111)面の結晶配向比率は80%以上の必要があることが分かった。

【0046】

TaC(111)ピーク強度

/{TaC(111)ピーク強度+TaC(200)ピーク強度}×100 …(5)

ここで、(111)面結晶配向比率は、図9のXRDスペクトルにおいて、TaC(111)ピークとTaC(200)ピーク強度の絶対値を求め、式(5)から計算する。ここで、ピーク強度の代わりに、ピーク面積を用いても良い。また、(111)面結晶配向比率を求める際には、ゲート電極のゲート絶縁膜に隣接する面と垂直方向、即ちゲート電極の膜厚方向を基準にしている。

【0047】

このように、pチャネルMISトランジスタ200のゲート電極210としては、TaC(111)配向性の強いTaCxを用いることが有効である。

【0048】

また、本実施形態では、ゲート電極材料としてTaCを用いていることから、次のような利点もある。

【0049】

本実施形態においてゲート電極材料として用いるTaとCは、Taの電気陰性度χが1.5,Cの電気陰性度χが2.5であり、χの差が大きい。これは、TaCxのCの組成比を変えることにより平均的な電気陰性度χを大きく変化させることができることを意味する。例えば、Taの代わりにMoを用いたとすると、Moのχは2.16とCのそれと近いため、MoCxのCの組成比を変えても平均的な電気陰性度χを大きく変化させることはできない。

【0050】

また、TaCは耐熱性が優れていることからもゲート電極材料として望ましいものである。このように、TaCのようにそれぞれの原子の電気陰性度差が大きく、耐熱性に優れた材料であればゲート電極材料として用いることができ、TaC以外にTiC,TaN,TiNを用いることも可能である。

【0051】

また、nチャネルMISトランジスタ100のゲート電極110の下層ゲート電極111は、不純物原子を含んだTa−C合金であってもよい。Cよりも電気陰性度の高い不純物元素を下層ゲート電極111の部分に配することで、より容易に、下層ゲート電極111と上層ゲート電極112の平均的な電気陰性度差を0.1以上にすることができる。そのため、不純物元素としてはN,O,F,P,S,Cl,As,Se,Br,Iを用いることができ、その中でも特に、F,P,Asは半導体製造プロセスで一般的な不純物ドープとして確立されているので、望ましい。

【0052】

次に、本実施形態の半導体装置の製造方法の一例を、図10を参照して説明する。

【0053】

まず、図10(a)に示すように、Si基板10上に素子分離領域11によって分離されたp型半導体領域101及びn型半導体領域201を形成した後、基板表面にゲート絶縁膜14(104,204)を形成する。ゲート絶縁膜は、SiO2 等の酸化膜であっても良いし、酸化膜以外の高誘電体膜であっても良い。特に、ハフニウム窒化シリケート(例えば、HfSiON)、ランタンハフネート(例えば、La2 Hf2 O7 )、ランタンアルミネート(例えば、LaAlO3 )が好ましく、非晶質であることが更に好ましい。続いて、nチャネルMISトランジスタ100側のゲート絶縁膜104上にのみ選択的にC層15を堆積する。

【0054】

次いで、図10(b)に示すように、pチャネルMISトランジスタ200側のゲート絶縁膜14及びnチャネルMISトランジスタ100側のC層15上にTa−C合金16(112,210)を同時に形成する。

【0055】

ここで、Ta−C合金16として(111)面結晶配向比率80%以上のpMOS用TaC電極をより効率良く形成するためには、膜厚方向にTa層とC層を交互に存在させることが有効である。この成膜方法の原理を、図11(a)〜(c)に模式的に示す。TaCは立方晶の結晶構造をとり、その(111)面は、Taと層とC層が交互に積み重ねられた構造となっている。従って、成膜段階でTaC(111)面と同様の原子配置を意図的に形成することで、より効率的に(111)面に配向したTaC薄膜を得ることが可能になる。

【0056】

このような製造方法は、ALD的手法により実現することが可能である。即ち、Taソースの供給とCソースの供給を、図11に示すように1層ずつ、交互に行えば良い。ここで、Taソースとしてクロライド系、アミド系、イミド系などの比較的蒸気圧の高い原料を用いることができ、Cソースとしてはアセチレン、CH4 ,C2 H4 ,CCl4 ,COなどを用いることが可能である。

【0057】

また、スパッタ法を用いても、上記製造方法は実現可能である。この場合には、複数のカソードを有するマルチカソードスパッタリング装置を用い、TaターゲットとCターゲットを装着する。Taターゲット1層分のスパッタリングと、Cターゲット1層分のスパッタリングを交互に行うことにより、pMOS用TaC薄膜を成膜できる。

【0058】

ここで、ゲート絶縁膜上に成膜する順序は、Cから始めてもTaから始めても、(111)面配向性の良し悪しには大きな影響を与えない。但し、ゲート絶縁膜上にCから成膜した場合には、ゲート絶縁膜上でCがTaと結合しない状態で存在することになるから、この成膜段階においてはゲート絶縁膜中への炭素の移動がより起こりやすい状況となる。ゲート絶縁膜中におけるCは固定電荷の起源となりデバイス特性を劣化させることが知られているため、本実施形態における成膜の順序としては、Ta層を先に堆積することがより望ましい。

【0059】

次いで、前記図10(b)に示す構造に熱処理を施すことで、C層15と、C層15上のTa−C合金16を混合させ、ゲート電極下層111を形成し、図10(c)に示す構造を得る。ここで、C層15の厚さにより、ゲート電極下層111の組成を制御することができる。実際に、C層15が厚いほどゲート電極下層111の組成がCリッチになる。図12に示すように、厚さが1.5nm以上であれば、nチャネルMISトランジスタ100と、pチャネルMISトランジスタ200の実効仕事関数差が0.4eV以上になることが確認された。

【0060】

但し、C層15と上部電極のTa−C合金との混合により形成したゲート電極下層111が3nm以上になると、前述したようにゲート電極下層がΦbulkにも影響してしまう。これを回避するために、C層15の厚さは2.5nm以下であることが望ましい。C層15の堆積方法は特に限定されるものではないが、均一な薄膜を形成することができるALD(Atomic Layer Deposition)法を用いるのが望ましい。Ta−C合金16の形成方法は、特に限定されるものではないが、例えば、CVD法、蒸着法、スパッタ法等が挙げられる。

【0061】

次いで、リソグラフィー及びRIE等のエッチングにより、ゲート絶縁膜14及びTa−C合金16を、nチャネルMISトランジスタ100、pチャネルMISトランジスタ200で一括加工し、図10(d)の構造を得る。

【0062】

これ以降は周知の工程により、ゲート部分をマスクに各半導体領域101,201の表面にエクステンション領域103,203を形成したのち、ゲート側壁絶縁膜120,220を形成する。そして、ゲート部分及び側壁絶縁膜120,220をマスクに各半導体領域101,201の表面にソース/ドレイン領域102,202を形成することによって、前記図6に示す構造が得られる。

【0063】

このように本実施形態によれば、基板上にnチャネルMISトランジスタ100とpチャネルMISトランジスタ200を形成したデュアルメタルゲートCMOS構造において、ゲート電極材料としてTaCを用い、nチャネルMISトランジスタ100のゲート電極110を下層ゲート電極111と上層ゲート電極112の積層構造とし、上層ゲート電極112の平均的な電気陰性度を下層ゲート電極111の平均的な電気陰性度よりも0.1以上小さくし、pチャネルMISトランジスタ200のゲート電極210としてnチャネルMISトランジスタ100の上層ゲート電極112と同一の金属材料を用いることにより、pチャネルMISトランジスタ200のゲート電極210の実効仕事関数をnチャネルMISトランジスタ100のゲート電極110の実効仕事関数より0.4eV以上高くすることができる。

【0064】

そしてこの場合、nチャネルMISトランジスタ100の上層ゲート電極112及びpチャネルMISトランジスタ200のゲート電極210は共に同一組成のTaCで、nチャネルMISトランジスタ100の下層ゲート電極111は非常に薄いため、ゲートの加工を一括で行うことができる。更には、nチャネルMISトランジスタ100の下層電極111は、nチャネルMISトランジスタ100の上層ゲート電極112及びpチャネルMISトランジスタ200のゲート電極210と組成は異なるがTaCからなり、構成元素が同一であるため、電極形成の際に別の原料を必要としない。このため、製造プロセスの簡略化及び製造コストの低減をはかることができる。

【0065】

(第2の実施形態)

図13は、本発明の第2の実施形態に係わるデュアルメタルゲートCMOS構造の半導体装置の概略構造を示す断面図である。

【0066】

p型半導体領域101の表面上には第1のゲート絶縁膜104が形成されており、このゲート絶縁膜104の表面上にはTa−C合金からなるゲート電極(第1ゲート電極)110が形成されている。

【0067】

n型半導体領域201の表面上には第2のゲート絶縁膜204が形成されており、このゲート絶縁膜204上には、積層構造を成す第2のゲート電極210が形成されている。このゲート電極210の下層(第2下層ゲート電極)211は、厚さが1モノレイヤー以上3nm以下のTa−C合金からなり、上層(第2上層ゲート電極)212はTa−C合金からなる。但し、下層ゲート電極211の平均的な電気陰性度χは、上層ゲート電極212の平均的な電気陰性度χよりも0.1以上小さい。これは、下層ゲート電極211のC原子濃度が上層ゲート電極212のC原子濃度より10 at.%以上低いことと同義である。

【0068】

ゲート電極110及び上層ゲート電極212の上には、さらにWやTiNといった高融点金属等が形成されていてもよい。なお、図13のその他の構成である素子分離領域11、ソース/ドレイン領域102,202、エクステンション領域103,203、ゲート側壁絶縁膜120,220は、通常の半導体プロセスより形成可能である。

【0069】

本実施形態は、先に説明した第1の実施形態の場合とは逆に、pチャネルMISトランジスタ200のゲート電極210を上層/下層の積層構造を含む形にしたものであり、第1の実施形態と同じ原理によりメタルゲートを用いたデュアルメタルゲートCMOS構造を実現することができる。

【0070】

また、第1の実施形態と同様に、pチャネルMISトランジスタ200のゲート電極210の下層ゲート電極211は非常に薄く、その他のゲート電極部分(上層ゲート電極212)は、nチャネルMISトランジスタ100のゲート電極110と同一である。このため、ゲートの加工を一括で行うことができ、第1の実施形態と同様の効果を得ることができる。

【0071】

また、本実施形態では、第1の実施形態とは逆に、nチャネルMISトランジスタ100のゲート電極110はゲート電極単層からなり、Φbulk及びΦinterface共に単層のTaCの性質のみで決定される。そのため、本実施形態においては、Φeff(P)≧4.7eV及びΦeff(N)≦4.3eVの条件を満たすためには、ゲート電極110は4.3以下の実効仕事関数値を持ち、ゲート電極110とゲート電極210の平均的な電気陰性度差の絶対値Δχが

Φeff(N)+0.4×Δχ/0.1 ≧ 4.7 …(6)

を満たしていればよいことが前記式(3)より導出される。

【0072】

また、本実施形態においては、nチャネルMISトランジスタ100のゲート電極110としてTaC(100)配向性の強いTaCxを用いることが有効である。ここでは、TaC(100)面の実効仕事関数が低いことを利用する。膜厚方向のTaC(111)面の結晶配向率[TaC(111)面/{TaC(111)面+TaC(200)面}が60%以下であるときにこの実効仕事関数はTaC(100)面の影響を受けて十分に低くなることが分かっている。つまり、nチャネルMISトランジスタ100のゲート電極110がTaC(111)面の結晶配向率[TaC(111)面/{TaC(111)面+TaC(200)面}が60%以下であるTaCxからなれば、nチャネルMISトランジスタ100のゲート電極110の実効仕事関数は結晶化していないTa−C合金を用いた場合よりも小さくなる。そのため、nチャネルMISトランジスタ100のゲート電極110の実効仕事関数とpチャネルMISトランジスタ200のゲート電極210の実効仕事関数との差をより容易に得ることができる。

【0073】

また、pチャネルMISトランジスタ200のゲート電極210の下層ゲート電極211は、不純物原子を含んだTa−C合金であってもよい。Taよりも電気陰性度の小さい不純物元素を下層ゲート電極211の部分に配することで、より容易に、下層ゲート電極211と上層ゲート電極212の平均的な電気陰性度差を0.1以上にすることができる。そのため、不純物元素としてはSc,Y,La,Zr,Hfを用いるのが望ましい。さらに、ランタノイド、アクチノイドに分類されるものを用いることも可能である。

【0074】

本実施形態の製造方法としては、先の第1の実施形態と基本的に同様であるが、nチャネルMISトランジスタ100側のゲートは単層、pチャネルMISトランジスタ200側のゲートは積層にする必要がある。このためには、例えば第1の実施形態の製造方法の図10(a)に示される工程を、pチャネルMISトランジスタ200側のゲート絶縁膜204上にのみ選択的にTa層を堆積する工程に変更することで製造可能である。

【0075】

また、先にも説明したように本実施形態では、nチャネルMISトランジスタ100のゲート電極110及びpチャネルMISトランジスタ200の上層ゲート電極212の形成に際して、(111)面結晶配向比率が60%以下のnMOS用TaCx電極を形成するのが望ましい。

【0076】

(111)面結晶配向比率が60%以下のnMOS用TaCx電極を形成するためには、第1の実施形態で説明したpMOS用TaCx電極の形成とは異なり、膜厚方向にTaとCが交互に存在しないように成膜することが重要である。この成膜原理の模式図を、図14(a)〜(c)に示す。

【0077】

CVD法によりnMOS用TaCx電極を形成するためには、TaソースとCソースを同時供給することが重要である。これにより、1層にTaとCは共存しながらTaCの成膜が進行するため、(111)面が形成されにくく、むしろ(200)面が形成されやすくなる。ここで、TaソースとCソースはpMOS用TaCx電極の形成に用いたものと同様でかまわない。

【0078】

スパッタリング法を用いる場合、TaターゲットとCターゲットの同時スパッタリングを用いることが望ましい。この場合、pMOS用TaCx電極の形成法とは異なり、TaとCを同時にスパッタリングすることで、(111)面が形成されにくく、(200)面が形成されやすくなる。本実施形態においては、C/Ta=1.0のTaCx膜を、TaとCの2ターゲットの同時スパッタリングにより100nm堆積した。この膜の堆積はCVD法やMBE法などの手法を用いてもかまわない。

【0079】

このように本実施形態によれば、第1の実施形態とは逆に、pチャネルMISトランジスタ200のゲート電極210を下層ゲート電極211と上層ゲート電極212の積層構造とし、上層ゲート電極212の平均的な電気陰性度を下層ゲート電極211の平均的な電気陰性度よりも0.1以上大きくし、nチャネルMISトランジスタ100のゲート電極110としてpチャネルMISトランジスタ200の上層ゲート電極212と同一の金属材料を用いることにより、pチャネルMISトランジスタ200のゲート電極210の実効仕事関数をnチャネルMISトランジスタ100のゲート電極110の実効仕事関数より0.4eV以上高くすることができる。

【0080】

そしてこの場合、pチャネルMISトランジスタ200の上層ゲート電極212及びnチャネルMISトランジスタ100のゲート電極110は共に同一組成のTaCで、pチャネルMISトランジスタ200の下層ゲート電極211は非常に薄いため、ゲートの加工を一括で行うことができる。更には、pチャネルMISトランジスタ200の下層電極211は、pチャネルMISトランジスタ200の上層ゲート電極212及びnチャネルMISトランジスタ100のゲート電極110と組成は異なるがTaCからなり、構成元素が同一であるため、電極形成の際に別の原料を必要としない。従って、第1の実施形態と同様の効果が得られる。

【0081】

(第3の実施形態)

図15は、本発明の第3の実施形態に係わるデュアルメタルゲートCMOS構造の半導体装置の概略構造を示す断面図である。

【0082】

p型半導体領域101の表面上には第1のゲート絶縁膜104が形成されており、このゲート絶縁膜104上には、積層構造を成す第1のゲート電極110が形成されている。このゲート電極110の下層(第1下層ゲート電極)111は、厚さが1モノレイヤー以上3nm以下のTa−C合金からなり、上層(第1上層ゲート電極)112はTa−C合金からなる。但し、下層ゲート電極111の平均的な電気陰性度χは、上層ゲート電極112の平均的な電気陰性度χよりも大きい。これは、下層ゲート電極111のC原子濃度が上層ゲート電極112のC原子濃度より高いことと同義である。

【0083】

n型半導体領域201の表面上には第2のゲート絶縁膜204が形成されており、このゲート絶縁膜204の表面上には積層構造を成す第2のゲート電極210が形成されている。このゲート電極210の下層(第2下層ゲート電極)211は、厚さが1モノレイヤー以上3nm以下のTa−C合金からなり、上層(第2上層ゲート電極)212はTa−C合金からなる。下層ゲート電極211の平均的な電気陰性度χは、上層ゲート電極212の平均的な電気陰性度χよりも小さい。これは、下層ゲート電極211のC原子濃度が上層ゲート電極212のC原子濃度より低いことと同義である。また、pMOS側の上層ゲート電極212は、nMOS側の上層ゲート電極112と同じ材料であり、上層ゲート電極112と同時に形成されている。

【0084】

下層ゲート電極211と上層ゲート電極212の平均的なχの差の絶対値と、下層ゲート電極111と上層ゲート電極112の平均的なχの差の絶対値の和は0.1以上であり、これは結果的に下層ゲート電極111のCの原子密度が、下層ゲート電極211のCの原子密度より10 at.%以上高いことと同義である。

【0085】

上層ゲート電極112,212の上には、さらにWやTiNといった高融点金属等が形成されていてもよい。なお、図15のその他の構成である素子分離領域11、ソース/ドレイン領域102,202、エクステンション領域103,203、ゲート側壁絶縁膜120,220は、通常の半導体プロセスより形成可能である。

【0086】

本実施形態は、第1の実施形態のnチャネルMISトランジスタ100と、第2の実施形態のpチャネルMISトランジスタ200を組み合わせたものである。第1及び第2の実施形態と比較すると、製造工程が増えてしまう欠点があるものの、nチャネルMISトランジスタ100とpチャネルMISトランジスタ200の各ゲート電極の実効仕事関数差をより容易に得ることが可能である点で優れている。つまり、nチャネルMISトランジスタ100とpチャネルMISトランジスタ200の各ゲート電極がどちらも積層構造であるため、各ゲート電極の下層と上層のχ差は、第1及び第2の実施形態におけるゲート電極の下層と上層のχ差よりも小さくてよい。

【0087】

本実施形態において、Φeff(P)≧4.7eV及びΦeff(N)≦4.3eVの条件を満たすためには、上層ゲート電極112,212は、下層ゲート電極111と上層ゲート電極112の電気陰性度差の絶対値Δχ(1) 及び、下層ゲート電極211と上層ゲート電極212の電気陰性度差の絶対値がΔχ(2) が、

Φeff(1)−0.4×Δχ(1)/0.1 ≦ 4.3

Φeff(2)+0.4×Δχ(2)/0.1 ≧ 4.7

を満たしていればよいことが、前記式(3)から導出される。ここで、Φeff(1)及びΦeff(2)とは、それぞれ上層ゲート電極112及び上層ゲート電極212と同一の金属材料単層からなるゲート電極のΦeff である。

【0088】

また、本実施形態の構造は、第1の実施形態の製造工程と第2の実施形態の製造工程とを組み合わせることにより製造することができる。

【0089】

(変形例)

なお、本発明は上述した各実施形態に限定されるものではない。実施形態ではゲート電極としてTaCを用いたが、必ずしもTaCに限らず、TiC,TaN,TiNを用いることも可能である。また、下層ゲート電極の厚さは1モノレイヤー以上で3nm以下の範囲であれば適宜変更可能である。同様に、下層ゲート電極と上層ゲート電極との平均的な電気陰性度の差、更には下層ゲート電極のCの原子密度と上層ゲート電極のCの原子密度との関係は、実施形態で説明した範囲において、適宜変更可能である。また、ゲート絶縁膜は、シリコン酸化膜に限らずシリコン窒化膜、シリコン酸化窒化膜、更には他の高誘電体膜を用いることも可能である。

【0090】

その他、本発明の要旨を逸脱しない範囲で、種々変形して実施することができる。

【図面の簡単な説明】

【0091】

【図1】ゲート電極の構造と、その実効仕事関数との関係を示す図。

【図2】ゲート電極/ゲート絶縁膜界面にダイポールが形成した場合のエネルギーバンドを示す図。

【図3】ゲート電極の構造(単層、積層)と、その実効仕事関数との関係を示す図。

【図4】ゲート電極の構造(単層、積層)と、その実効仕事関数との関係を示す図。

【図5】TaCx電極及びTaCx/TaCy電極のSiO2 上での実効仕事関数を示す図。

【図6】第1の実施形態に係わる半導体装置の概略構造を示す断面図

【図7】成膜法の違いによるTaCx電極の配向性変化を示す特性図。

【図8】TaCx電極配向性と仕事関数との関係を示す特性図。

【図9】TaCx電極組成と結晶性の変化との関係を示す特性図。

【図10】第1の実施形態に係わる半導体装置の製造工程を示す断面図。

【図11】pMOS用TaCx電極の形成方法を説明するための模式図。

【図12】ゲート絶縁膜上に堆積するC層の膜厚と仕事関数との関係を示す特性図。

【図13】第2の実施形態に係わる半導体装置の概略構造を示す断面図。

【図14】nMOS用TaCx電極の形成方法を説明するための模式図。

【図15】第3の実施形態に係わる半導体装置の概略構造を示す断面図

【符号の説明】

【0092】

10…Si半導体基板

11…素子分離領域

15…C層

16…Ta−C合金

100…nチャネルMISトランジスタ

200…pチャネルMISトランジスタ

101…p型半導体領域

102,202…ソース/ドレイン電極

103,203…エクステンション領域

104,204…ゲート絶縁膜

110,210…ゲート電極

111,211…下層ゲート電極

112,212…上層ゲート電極

120,220…ゲート側壁

201…n型半導体領域

【技術分野】

【0001】

本発明は、同一基板上に金属ゲートを有するpチャネルMISトランジスタとnチャネルMISトランジスタを形成した半導体装置に関する。

【背景技術】

【0002】

近年、同一基板上にpチャネルMISトランジスタとnチャネルMISトランジスタを形成したCMOSデバイスにおいて、ゲート電極材料として金属を用いるメタルゲート技術が注目を集めている。金属は、原子密度と同程度の高い電荷密度を持つため、金属をゲート電極として用いた場合、ゲート電極の空乏化を無視することができる。

【0003】

メタルゲート電極を用いたCMOSデバイスにおいて低い閾値電圧を実現するためには、いわゆるデュアルメタルゲートCMOS構造を成す必要がある。デュアルメタルゲートCMOS構造を成すためには、nチャネルMISトランジスタ及びpチャネルMISトランジスタの各ゲート電極は、それぞれSiの伝導帯端及び価電子帯端に近い実効仕事関数を示す必要があり、pチャネルMISトランジスタのゲート電極の実効仕事関数がnチャネルMISトランジスタの実効仕事関数より0.4eV以上高いことが求められる。現在のところ、これを実現する方法としては、nチャネルMISトランジスタ及びpチャネルMISトランジスタの各ゲート電極を全く異なる金属材料で構成するものが一般的である(例えば、特許文献1及び非特許文献1参照)。

【0004】

しかしながら、nチャネルMISトランジスタとpチャネルMISトランジスタでゲート電極に異なる金属材料を用いた場合、ゲート電極の形成及び加工共に、nチャネルMISトランジスタ及びpチャネルMISトランジスタで別々に行う必要がある。このため、製造プロセスが複雑化し、製造コストが増大するという問題が生じてしまう。ちなみに特許文献1の方法では、pMISトランジスタ及びnMISトランジスタのゲート電極材料としてモリブデンを用いながら、一方に炭素を導入することにより、各々のゲート電極の仕事関数を異ならせている。この場合、一方のゲート電極部分をマスクするためのマスクの形成、炭素の導入、炭化のための熱処理、マスクの除去等の工程が必要となり、製造プロセスが複雑になる。

【0005】

メタルゲート技術導入実現のためには、製造プロセスがなるべく煩雑化しないような、デュアルメタルゲートCMOS構造を見出す必要がある。

【特許文献1】特開2004−207481号公報

【非特許文献1】米国特許 US7,030,430

【発明の開示】

【発明が解決しようとする課題】

【0006】

このように従来、CMOSデバイスの性能向上のためにはデュアルメタルゲート技術の導入が必須であるが、その実現にはnチャネルMISトランジスタとpチャネルMISトランジスタでゲート電極として異なる金属材料を用いる必要があり、これが製造プロセスの複雑化や製造コストの増大を招く要因となっていた。

【0007】

本発明は、上記事情を考慮してなされたもので、その目的とするところは、nチャネルMISトランジスタとpチャネルMISトランジスタでゲート電極として実質的に同じ金属材料を用いることができ、製造プロセスの複雑化や製造コストの増大を招くことなく、デュアルメタルゲートCMOS構造を実現することのできる半導体装置を提供することにある。

【課題を解決するための手段】

【0008】

上記課題を解決するために本発明は、次のような構成を採用している。

【0009】

即ち、本発明の一態様は、基板上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された半導体装置であって、前記nチャネルMISトランジスタは、前記基板上に形成されたp型半導体領域と、前記p型半導体領域上に形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第1下層ゲート電極と、前記第1下層ゲート電極上に形成され、平均的な電気陰性度が第1下層ゲート電極の平均的な電気陰性度よりも0.1以上小さく、金属材料で形成された第1上層ゲート電極とを含んで形成され、前記pチャネルMISトランジスタは、前記基板上に形成されたn型半導体領域と、前記n型半導体領域上に形成された第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成され、前記金属材料で形成された第2ゲート電極とを含んで形成されていることを特徴とする。

【0010】

また、本発明の別の一態様は、基板上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された半導体装置であって、前記nチャネルMISトランジスタは、前記基板上に形成されたp型半導体領域と、前記p型半導体領域上に形成され、金属材料で形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された第1ゲート電極とを含んで形成され、前記pチャネルMISトランジスタは、前記基板上に形成されたn型半導体領域と、前記n型半導体領域上に形成された第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第2下層ゲート電極と、前記第2下層ゲート電極上に形成され、平均的な電気陰性度が第2下層ゲート電極の平均的な電気陰性度よりも0.1以上大きく、前記金属材料で形成された第2上層ゲート電極とを含んで形成されていることを特徴とする。

【0011】

また、本発明の更に別の一態様は、基板上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された半導体装置であって、前記基板上に形成されたp型半導体領域と、前記p型半導体領域上に形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第1下層ゲート電極と、前記第1下層ゲート電極上に形成され、平均的な電気陰性度が第1下層ゲート電極の平均的な電気陰性度よりも小さく、金属材料で形成された第1上層ゲート電極とを含んで形成されたnチャネルMISトランジスタと、前記基板上に形成されたn型半導体領域と、前記n型半導体領域上に形成された第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第2下層ゲート電極と、前記第2下層ゲート電極上に形成され、平均的な電気陰性度が第2下層ゲート電極の平均的な電気陰性度よりも大きく、前記金属材料で形成された第2上層ゲート電極とを含んで形成されたpチャネルMISトランジスタと、を具備し、前記第1下層ゲート電極と前記第1上層ゲート電極との平均的な電気陰性度の差の絶対値Δχ(1) と、前記第2下層ゲート電極と前記第2上層ゲート電極との平均的な電気陰性度の差の絶対値Δχ(2) と、の和が0.1以上であることを特徴とする。

【発明の効果】

【0012】

本発明によれば、nチャネルMISトランジスタとpチャネルMISトランジスタでゲート電極に実質的に同じ金属材料を用いながら、pチャネルMISトランジスタのゲート電極の実効仕事関数をnチャネルMISトランジスタの実効仕事関数よりも十分大きくすることができる。従って、nチャネルMISトランジスタ及びpチャネルMISトランジスタの各ゲート電極を一括で加工することができ、製造プロセスの複雑化及び製造コストの低減をはかることができる。

【発明を実施するための最良の形態】

【0013】

(発明の概要及び原理)

発明の実施形態について説明する前に、まず、本発明の原理について説明する。

【0014】

ゲート電極の実効仕事関数Φeff は、式(1)のように表される。

【0015】

Φeff =Φbulk+Φinterface …(1)

Φbulkは、ゲート電極のバルク部分の性質によって決定され、Φinterfaceはゲート電極/ゲート絶縁膜界面における電荷分布によって決定される項である。ここに、ゲート絶縁膜表面上に形成された下層と下層表面上に形成された上層からなる二層構造を含む積層構造のゲート電極があるとする。このとき、図1に示すように、下層の膜厚が、1モノレイヤー以上、3nm以下である場合、Φbulkは主に上層の性質によって決定される一方で、Φinterfaceは下層の性質によって決定される。

【0016】

Φinterfaceは、ゲート電極側の原子とゲート絶縁膜側の原子とが互いに結合した場合に形成するダイポールの大きさに依存する。ここで、ゲート電極が、Ta−C合金、ゲート絶縁膜が酸化物からなる場合を考える。

【0017】

図2は、ゲート電極側のTaとゲート絶縁膜側のOが互いに結合した場合のエネルギーバンド図を示したものである。TaとOの電気陰性度χは、それぞれ1.5と3.5であるため、TaとOが結合すると、電子はより電気陰性度χの高いO、即ちゲート絶縁膜側に偏る。そのとき、図2に示すように、Φinterfaceが上昇してΦeff が増加する。

【0018】

一方、ゲート電極側のCとゲート絶縁膜側のOが結合した場合を考える。このとき、Cの電気陰性度χは2.5であり、Taに比べると、電子を引き付ける力が強い。そのため、Ta−O結合が形成した場合に比べると、電子の絶縁膜側への偏りは小さく、その分Φinterfaceも小さくなる。

【0019】

以上のことを、より一般的に記述すると、ゲート絶縁膜が同一である場合、ゲート電極のゲート絶縁膜側に電気陰性度χの小さな原子が多い(即ちゲート電極のゲート絶縁膜側の平均的なχが小さい)ほどΦinterfaceは大きく、ゲート電極側のゲート絶縁膜に電気陰性度χの大きな原子が多い(即ちゲート電極の平均的なχが大きい)ほどΦinterfaceは小さいということになる。本明細書において、平均的なχとは、金属材料を構成する元素の電気陰性度の幾何平均のことを示す。例えば、TaxCy の平均的なχは、

【数1】

【0020】

と表される。χTa及びχCは、それぞれTa及びCの電気陰性度のことである。

【0021】

以上の理由により、図3(a)(b)に示すように、ゲート電極下層(B)の平均的なχが、ゲート電極上層(A)のχよりも大きい場合には、A/Bの積層構造からなるゲート電極のΦinterfaceは、A単層からなるゲート電極のΦinterfaceよりも小さい。逆に、ゲート電極下層(B)の平均的なχが、ゲート電極上層(A)の平均的なχよりも小さい場合には、図4(a)(b)に示すように、A/Bの積層構造からなるゲート電極のΦinterfaceは、A単層からなるゲート電極のΦinterfaceよりも大きい。

【0022】

ところで、一般にχが高いほどΦbulkは大きくなる。そのため、ゲート電極下層(B)がΦbulkにも影響する場合には、Φbulkが受ける影響とΦinterfaceが受ける影響が相殺してしまう。よって、ゲート電極下層(B)はΦinterfaceとしてのみ機能せねばならない。これは、上述したように、ゲート電極下層(B)の厚さが、1モノレイヤー以上3nm以下であれば実現され、そのとき、Φinterfaceの差がそのままΦeff に反映されることになる。

【0023】

本発明者らは、ゲート電極を積層構造にすることで、どれほどのΦeff 差が生じるのか検討した。その結果、ゲート電極上層(A)の平均的なχとゲート電極下層(B)の平均的なχとの差の絶対値Δχが0.1以上であれば、A単層からなるMISトランジスタとA/B積層からなるMISトランジスタのΦeff 差(Δφeff)が、デュアルメタルゲートCMOS構造の実現のために必要とされる0.4eV以上になることを見出した。さらに、Δφeff とΔχとは、

ΔΦeff = 0.4×Δχ/0.1 …(3)

の関係にあることを見出した。

【0024】

図5は、TaCx/TaCy(y>x)の積層構造からなるゲート電極と、TaCx単層からなるゲート電極の実効仕事関数の実測値を示すものである。なお、ここではゲート絶縁膜としてSiO2 を用いている。

【0025】

ゲート電極がTaCx単層の場合(M1)は、実効仕事関数は4.7eV程度であるのに対し、ゲート電極がTaCx/TaCy(y>x)の場合(M2)には、4.2eV程度の実効仕事関数を示す。ゲート電極M1及びM2のCの原子濃度を物理分析により調べたところ、ゲート絶縁膜/ゲート電極界面から3nm以上深い領域のC原子濃度は互いに同じであったが、ゲート電極のゲート絶縁膜極近傍の領域のC原子濃度は、M1では52 at.%、M2では63 at.%であった。これを平均的なχに直すと、M1では1.96、M2では2.07で、両者には0.1以上のχ差があり、前述した0.4eV以上のΦeff 差を得るための条件を満たしている。この事実は、上述した原理の妥当性を示していると云える。

【0026】

以下、図面を参照して本発明の実施形態について説明する。なお、各実施形態を通して共通の構成には同一の符号を付し、重複する説明は省略する。

【0027】

(第1の実施形態)

図6は、本発明の第1の実施形態に係わるデュアルメタルゲートCMOS構造の半導体装置の概略構造を示す断面図である。

【0028】

半導体基板としてのSi基板10の表面領域には、p型半導体領域101とn型半導体領域201が設けられ、それぞれの領域101,201にnチャネルMISトランジスタ100、pチャネルMISトランジスタ200が形成されている。p型半導体領域101及びn型半導体領域201は、いわゆるウエルとして形成され、各々の領域101,201の境界部にはこれらを分離するための素子分離領域11が形成されている。

【0029】

p型半導体領域101の表面上には第1のゲート絶縁膜104が形成されており、このゲート絶縁膜104上には、積層構造を成す第1のゲート電極110が形成されている。このゲート電極110の下層(第1下層ゲート電極)111は、厚さが1モノレイヤー以上3nm以下のTa−C合金からなり、上層(第1上層ゲート電極)112はTa−C合金からなる。但し、下層ゲート電極111の平均的な電気陰性度χは、上層ゲート電極112の平均的なχよりも0.1以上大きい。これは、下層ゲート電極111のC原子濃度が上層ゲート電極112のC原子濃度より10 at.%以上高いことと同義である。

【0030】

n型半導体領域201の表面上には第2のゲート絶縁膜204が形成されており、このゲート絶縁膜204の表面上にはTa−C合金からなるゲート電極(第2ゲート電極)210が形成されている。このゲート電極210は、第1上層ゲート電極212と同じ材料であり、上層ゲート電極212と同時に形成されている。

【0031】

ゲート電極210及び上層ゲート電極112の上には、さらにWやTiNといった高融点金属等が形成されていてもよい。なお、図6のその他の構成である素子分離領域11、ソース/ドレイン領域102,202、エクステンション領域103,203、ゲート側壁絶縁膜120,220は、通常の半導体プロセスより形成可能である。また、ゲート絶縁膜104,204は同じ材料であり、同時に形成されている。さらに、側壁絶縁膜120,220も同じ材料であり、同時に形成されている。

【0032】

前述した原理により、本実施形態の構造を用いることで、メタルゲートを用いたデュアルメタルゲートCMOS構造を実現することができる。また、nチャネルMISトランジスタ100のゲート電極110の下層ゲート電極111は非常に薄く、その他のゲート電極部分(上層ゲート電極112)は、pチャネルMISトランジスタ200のゲート電極210と同一である。このため、ゲートの加工を一括で行うことができ、製造プロセスの簡略化及び製造コストの低減をはかることができる。

【0033】

また、nチャネルMISトランジスタ100及びpチャネルMISトランジスタ200の閾値電圧をどちらも十分低くするためには、nチャネルMISトランジスタ100の実効仕事関数(Φeff(N))は4.3eV以下、pチャネルMISトランジスタ200の実効仕事関数(Φeff(P))は4.7eV以上であることが望ましい。本実施形態においては、pチャネルMISトランジスタ200のゲート電極210は、ゲート電極単層からなり、Φbulk及びΦinterface共に単層のTaCの性質のみで決定される。そのため、ゲート電極210は、4.7以上の実効仕事関数値を持つことが望ましい。

【0034】

一方、積層構造からなるnチャネルMISトランジスタ100のゲート電極110の実効仕事関数は、下層ゲート電極111と上層ゲート電極112の電気陰性度差Δχにより、ゲート電極210の実効仕事関数よりも低い。nチャネルMISトランジスタ100のゲート電極実効仕事関数Φeff(N) が4.3eV以下であるためには、前記式(3)より、Δχが、

Φeff(P)-0.4×Δχ/0.1 ≦ 4.3 …(4)

を満たしていればよい。

【0035】

ところで、ゲート電極のゲート絶縁膜側の構造と、その組成及び厚さは、MIS構造のSi基板を除去し、ゲート絶縁膜越しにXPS測定(裏面XPS測定)を行うことで調べることができる。XPS測定の際の光電子検出角度(TOA)が低角であるほどゲート絶縁膜/ゲート電極界面から浅い領域のゲート電極の情報が得られ、TOAを高角にすればゲート絶縁膜/ゲート電極界面から深い領域のゲート電極の情報が得られる。このため、TOAを変えることで、ゲート絶縁膜/ゲート金属界面から所望の深さのゲート電極の組成を調べることができる。また、ゲート電極/ゲート絶縁膜の断面構造は、TEM−EELS法によっても分析可能である。

【0036】

前述の原理の説明時に用いた図5に示すゲート電極M1及びM2の構造と、その組成及び厚さは、裏面XPS測定により得たものである。

【0037】

また、pチャネルMISトランジスタ200のゲート電極210としては、TaC(111)配向性の強いTaCxを用いることが有効である。それは、結晶化したTaCxの実効仕事関数はその結晶面に依存し、TaC(111)面は、特に高い実効仕事関数を示すためである。これは、絶縁膜と接している面がTaC(111)面の場合はΦinterfaceが大きいからであり、TaC(111)面の結晶配向率[TaC(111)面/{TaC(111)面+TaC(200)面}が80%以上であればこの効果が得られることが分かっている。

【0038】

つまり、pチャネルMISトランジスタ200のゲート電極210がTaC(111)面の結晶配向率[TaC(111)面/{TaC(111)面+TaC(200)面}]が80%以上であるTaCxからなれば、pチャネルMISトランジスタ200のゲート電極210の実効仕事関数は結晶化していないTa−C合金を用いた場合の実効仕事関数よりも大きくなる。そのため、nチャネルMISトランジスタ100のゲート電極110の実効仕事関数とpチャネルMISトランジスタ200のゲート電極210の実効仕事関数との差をより容易に得ることができる。

【0039】

なお、nチャネルMISトランジスタ100においては、上層ゲート電極112としてTaC(111)配向性の強いTaCxを用いたとしても、上層ゲート電極112はゲート絶縁膜104に直接接していないので、配向性の制御により実効仕事関数が大きくなることはない。

【0040】

このように、結晶配向性の制御により仕事関数を変化させられることは、本発明者らにより見出され、既に提案されている(特願2005−356951)。以下に、この提案について簡単に説明しておく。

【0041】

従来技術では、TaCx電極の仕事関数が4.18eVであったため、一般にnチャネルMISトランジスタにしかTaCx電極を用いていない。仮に、従来技術のTaCxをpチャネルMISトランジスタのゲート電極に用いたとしても、そのしきい値電圧は非常に高くなり、CMOSの正常動作は不可能になる。

【0042】

本発明者らは、TaとCとの組成比(C/Ta)を0.5〜1.5に設定し、TaCxを結晶化状態で用いた。さらに、本発明者らは、(111)配向性を強くすることで4.8eV程度のp+ シリコンに近い仕事関数が得られ、(111)配向に対し(200)配向成分を増やすことでn+ シリコンに近い仕事関数が得られることを新たに見出し、これをCMOSトランジスタのデュアルメタルゲートに適用した。

【0043】

図7はその発見を示す、膜厚100nmのTaCx薄膜の結晶性を調べた実験結果を示す図である。横軸は角度(2θ)、縦軸は強度を示している。また、pMOS用TaC電極とnMOS用TaC電極のそれぞれの特性が区別できるように、縦軸方向にオフセットして示している。TaCx膜の組成は共にC/Ta〜1であるが、成膜法の違いによって、(111)回折ピークが最も強くなるものと、(200)回折ピークが最も強くなるものに作り分けできることが示された。

【0044】

上記では、TaC膜/ゲート絶縁膜/Si基板の分析用試料を用いた結果を示した。このような実験はもちろん完成したトランジスタでも実施可能であり、その場合はトランジスタのゲート電極の部分をTEM観察などで用いられるピックアップ法で切り出し、ゲート電極の断面を電子線回折法で分析すれば、(111)配向と(200)配向の割合を確認することが可能である。この場合、TEM法の電子ビームを用いるので分析位置のポジショニング精度が高い。これにより、実際にしきい値電圧制御に強く関係する、ゲート絶縁膜と接した領域のTaC膜の配向性を確認することが容易となる。

【0045】

図8は、上記のようにして配向性を変化させたときの仕事関数の変化を示した図である。TaCxがp+ シリコン同等の4.75eV以上の仕事関数を示すために、下記の(5)式で示す(111)面の結晶配向比率は80%以上の必要があることが分かった。

【0046】

TaC(111)ピーク強度

/{TaC(111)ピーク強度+TaC(200)ピーク強度}×100 …(5)

ここで、(111)面結晶配向比率は、図9のXRDスペクトルにおいて、TaC(111)ピークとTaC(200)ピーク強度の絶対値を求め、式(5)から計算する。ここで、ピーク強度の代わりに、ピーク面積を用いても良い。また、(111)面結晶配向比率を求める際には、ゲート電極のゲート絶縁膜に隣接する面と垂直方向、即ちゲート電極の膜厚方向を基準にしている。

【0047】

このように、pチャネルMISトランジスタ200のゲート電極210としては、TaC(111)配向性の強いTaCxを用いることが有効である。

【0048】

また、本実施形態では、ゲート電極材料としてTaCを用いていることから、次のような利点もある。

【0049】

本実施形態においてゲート電極材料として用いるTaとCは、Taの電気陰性度χが1.5,Cの電気陰性度χが2.5であり、χの差が大きい。これは、TaCxのCの組成比を変えることにより平均的な電気陰性度χを大きく変化させることができることを意味する。例えば、Taの代わりにMoを用いたとすると、Moのχは2.16とCのそれと近いため、MoCxのCの組成比を変えても平均的な電気陰性度χを大きく変化させることはできない。

【0050】

また、TaCは耐熱性が優れていることからもゲート電極材料として望ましいものである。このように、TaCのようにそれぞれの原子の電気陰性度差が大きく、耐熱性に優れた材料であればゲート電極材料として用いることができ、TaC以外にTiC,TaN,TiNを用いることも可能である。

【0051】

また、nチャネルMISトランジスタ100のゲート電極110の下層ゲート電極111は、不純物原子を含んだTa−C合金であってもよい。Cよりも電気陰性度の高い不純物元素を下層ゲート電極111の部分に配することで、より容易に、下層ゲート電極111と上層ゲート電極112の平均的な電気陰性度差を0.1以上にすることができる。そのため、不純物元素としてはN,O,F,P,S,Cl,As,Se,Br,Iを用いることができ、その中でも特に、F,P,Asは半導体製造プロセスで一般的な不純物ドープとして確立されているので、望ましい。

【0052】

次に、本実施形態の半導体装置の製造方法の一例を、図10を参照して説明する。

【0053】

まず、図10(a)に示すように、Si基板10上に素子分離領域11によって分離されたp型半導体領域101及びn型半導体領域201を形成した後、基板表面にゲート絶縁膜14(104,204)を形成する。ゲート絶縁膜は、SiO2 等の酸化膜であっても良いし、酸化膜以外の高誘電体膜であっても良い。特に、ハフニウム窒化シリケート(例えば、HfSiON)、ランタンハフネート(例えば、La2 Hf2 O7 )、ランタンアルミネート(例えば、LaAlO3 )が好ましく、非晶質であることが更に好ましい。続いて、nチャネルMISトランジスタ100側のゲート絶縁膜104上にのみ選択的にC層15を堆積する。

【0054】

次いで、図10(b)に示すように、pチャネルMISトランジスタ200側のゲート絶縁膜14及びnチャネルMISトランジスタ100側のC層15上にTa−C合金16(112,210)を同時に形成する。

【0055】

ここで、Ta−C合金16として(111)面結晶配向比率80%以上のpMOS用TaC電極をより効率良く形成するためには、膜厚方向にTa層とC層を交互に存在させることが有効である。この成膜方法の原理を、図11(a)〜(c)に模式的に示す。TaCは立方晶の結晶構造をとり、その(111)面は、Taと層とC層が交互に積み重ねられた構造となっている。従って、成膜段階でTaC(111)面と同様の原子配置を意図的に形成することで、より効率的に(111)面に配向したTaC薄膜を得ることが可能になる。

【0056】

このような製造方法は、ALD的手法により実現することが可能である。即ち、Taソースの供給とCソースの供給を、図11に示すように1層ずつ、交互に行えば良い。ここで、Taソースとしてクロライド系、アミド系、イミド系などの比較的蒸気圧の高い原料を用いることができ、Cソースとしてはアセチレン、CH4 ,C2 H4 ,CCl4 ,COなどを用いることが可能である。

【0057】

また、スパッタ法を用いても、上記製造方法は実現可能である。この場合には、複数のカソードを有するマルチカソードスパッタリング装置を用い、TaターゲットとCターゲットを装着する。Taターゲット1層分のスパッタリングと、Cターゲット1層分のスパッタリングを交互に行うことにより、pMOS用TaC薄膜を成膜できる。

【0058】

ここで、ゲート絶縁膜上に成膜する順序は、Cから始めてもTaから始めても、(111)面配向性の良し悪しには大きな影響を与えない。但し、ゲート絶縁膜上にCから成膜した場合には、ゲート絶縁膜上でCがTaと結合しない状態で存在することになるから、この成膜段階においてはゲート絶縁膜中への炭素の移動がより起こりやすい状況となる。ゲート絶縁膜中におけるCは固定電荷の起源となりデバイス特性を劣化させることが知られているため、本実施形態における成膜の順序としては、Ta層を先に堆積することがより望ましい。

【0059】

次いで、前記図10(b)に示す構造に熱処理を施すことで、C層15と、C層15上のTa−C合金16を混合させ、ゲート電極下層111を形成し、図10(c)に示す構造を得る。ここで、C層15の厚さにより、ゲート電極下層111の組成を制御することができる。実際に、C層15が厚いほどゲート電極下層111の組成がCリッチになる。図12に示すように、厚さが1.5nm以上であれば、nチャネルMISトランジスタ100と、pチャネルMISトランジスタ200の実効仕事関数差が0.4eV以上になることが確認された。

【0060】

但し、C層15と上部電極のTa−C合金との混合により形成したゲート電極下層111が3nm以上になると、前述したようにゲート電極下層がΦbulkにも影響してしまう。これを回避するために、C層15の厚さは2.5nm以下であることが望ましい。C層15の堆積方法は特に限定されるものではないが、均一な薄膜を形成することができるALD(Atomic Layer Deposition)法を用いるのが望ましい。Ta−C合金16の形成方法は、特に限定されるものではないが、例えば、CVD法、蒸着法、スパッタ法等が挙げられる。

【0061】

次いで、リソグラフィー及びRIE等のエッチングにより、ゲート絶縁膜14及びTa−C合金16を、nチャネルMISトランジスタ100、pチャネルMISトランジスタ200で一括加工し、図10(d)の構造を得る。

【0062】

これ以降は周知の工程により、ゲート部分をマスクに各半導体領域101,201の表面にエクステンション領域103,203を形成したのち、ゲート側壁絶縁膜120,220を形成する。そして、ゲート部分及び側壁絶縁膜120,220をマスクに各半導体領域101,201の表面にソース/ドレイン領域102,202を形成することによって、前記図6に示す構造が得られる。

【0063】

このように本実施形態によれば、基板上にnチャネルMISトランジスタ100とpチャネルMISトランジスタ200を形成したデュアルメタルゲートCMOS構造において、ゲート電極材料としてTaCを用い、nチャネルMISトランジスタ100のゲート電極110を下層ゲート電極111と上層ゲート電極112の積層構造とし、上層ゲート電極112の平均的な電気陰性度を下層ゲート電極111の平均的な電気陰性度よりも0.1以上小さくし、pチャネルMISトランジスタ200のゲート電極210としてnチャネルMISトランジスタ100の上層ゲート電極112と同一の金属材料を用いることにより、pチャネルMISトランジスタ200のゲート電極210の実効仕事関数をnチャネルMISトランジスタ100のゲート電極110の実効仕事関数より0.4eV以上高くすることができる。

【0064】

そしてこの場合、nチャネルMISトランジスタ100の上層ゲート電極112及びpチャネルMISトランジスタ200のゲート電極210は共に同一組成のTaCで、nチャネルMISトランジスタ100の下層ゲート電極111は非常に薄いため、ゲートの加工を一括で行うことができる。更には、nチャネルMISトランジスタ100の下層電極111は、nチャネルMISトランジスタ100の上層ゲート電極112及びpチャネルMISトランジスタ200のゲート電極210と組成は異なるがTaCからなり、構成元素が同一であるため、電極形成の際に別の原料を必要としない。このため、製造プロセスの簡略化及び製造コストの低減をはかることができる。

【0065】

(第2の実施形態)

図13は、本発明の第2の実施形態に係わるデュアルメタルゲートCMOS構造の半導体装置の概略構造を示す断面図である。

【0066】

p型半導体領域101の表面上には第1のゲート絶縁膜104が形成されており、このゲート絶縁膜104の表面上にはTa−C合金からなるゲート電極(第1ゲート電極)110が形成されている。

【0067】

n型半導体領域201の表面上には第2のゲート絶縁膜204が形成されており、このゲート絶縁膜204上には、積層構造を成す第2のゲート電極210が形成されている。このゲート電極210の下層(第2下層ゲート電極)211は、厚さが1モノレイヤー以上3nm以下のTa−C合金からなり、上層(第2上層ゲート電極)212はTa−C合金からなる。但し、下層ゲート電極211の平均的な電気陰性度χは、上層ゲート電極212の平均的な電気陰性度χよりも0.1以上小さい。これは、下層ゲート電極211のC原子濃度が上層ゲート電極212のC原子濃度より10 at.%以上低いことと同義である。

【0068】

ゲート電極110及び上層ゲート電極212の上には、さらにWやTiNといった高融点金属等が形成されていてもよい。なお、図13のその他の構成である素子分離領域11、ソース/ドレイン領域102,202、エクステンション領域103,203、ゲート側壁絶縁膜120,220は、通常の半導体プロセスより形成可能である。

【0069】

本実施形態は、先に説明した第1の実施形態の場合とは逆に、pチャネルMISトランジスタ200のゲート電極210を上層/下層の積層構造を含む形にしたものであり、第1の実施形態と同じ原理によりメタルゲートを用いたデュアルメタルゲートCMOS構造を実現することができる。

【0070】

また、第1の実施形態と同様に、pチャネルMISトランジスタ200のゲート電極210の下層ゲート電極211は非常に薄く、その他のゲート電極部分(上層ゲート電極212)は、nチャネルMISトランジスタ100のゲート電極110と同一である。このため、ゲートの加工を一括で行うことができ、第1の実施形態と同様の効果を得ることができる。

【0071】

また、本実施形態では、第1の実施形態とは逆に、nチャネルMISトランジスタ100のゲート電極110はゲート電極単層からなり、Φbulk及びΦinterface共に単層のTaCの性質のみで決定される。そのため、本実施形態においては、Φeff(P)≧4.7eV及びΦeff(N)≦4.3eVの条件を満たすためには、ゲート電極110は4.3以下の実効仕事関数値を持ち、ゲート電極110とゲート電極210の平均的な電気陰性度差の絶対値Δχが

Φeff(N)+0.4×Δχ/0.1 ≧ 4.7 …(6)

を満たしていればよいことが前記式(3)より導出される。

【0072】

また、本実施形態においては、nチャネルMISトランジスタ100のゲート電極110としてTaC(100)配向性の強いTaCxを用いることが有効である。ここでは、TaC(100)面の実効仕事関数が低いことを利用する。膜厚方向のTaC(111)面の結晶配向率[TaC(111)面/{TaC(111)面+TaC(200)面}が60%以下であるときにこの実効仕事関数はTaC(100)面の影響を受けて十分に低くなることが分かっている。つまり、nチャネルMISトランジスタ100のゲート電極110がTaC(111)面の結晶配向率[TaC(111)面/{TaC(111)面+TaC(200)面}が60%以下であるTaCxからなれば、nチャネルMISトランジスタ100のゲート電極110の実効仕事関数は結晶化していないTa−C合金を用いた場合よりも小さくなる。そのため、nチャネルMISトランジスタ100のゲート電極110の実効仕事関数とpチャネルMISトランジスタ200のゲート電極210の実効仕事関数との差をより容易に得ることができる。

【0073】

また、pチャネルMISトランジスタ200のゲート電極210の下層ゲート電極211は、不純物原子を含んだTa−C合金であってもよい。Taよりも電気陰性度の小さい不純物元素を下層ゲート電極211の部分に配することで、より容易に、下層ゲート電極211と上層ゲート電極212の平均的な電気陰性度差を0.1以上にすることができる。そのため、不純物元素としてはSc,Y,La,Zr,Hfを用いるのが望ましい。さらに、ランタノイド、アクチノイドに分類されるものを用いることも可能である。

【0074】

本実施形態の製造方法としては、先の第1の実施形態と基本的に同様であるが、nチャネルMISトランジスタ100側のゲートは単層、pチャネルMISトランジスタ200側のゲートは積層にする必要がある。このためには、例えば第1の実施形態の製造方法の図10(a)に示される工程を、pチャネルMISトランジスタ200側のゲート絶縁膜204上にのみ選択的にTa層を堆積する工程に変更することで製造可能である。

【0075】

また、先にも説明したように本実施形態では、nチャネルMISトランジスタ100のゲート電極110及びpチャネルMISトランジスタ200の上層ゲート電極212の形成に際して、(111)面結晶配向比率が60%以下のnMOS用TaCx電極を形成するのが望ましい。

【0076】

(111)面結晶配向比率が60%以下のnMOS用TaCx電極を形成するためには、第1の実施形態で説明したpMOS用TaCx電極の形成とは異なり、膜厚方向にTaとCが交互に存在しないように成膜することが重要である。この成膜原理の模式図を、図14(a)〜(c)に示す。

【0077】

CVD法によりnMOS用TaCx電極を形成するためには、TaソースとCソースを同時供給することが重要である。これにより、1層にTaとCは共存しながらTaCの成膜が進行するため、(111)面が形成されにくく、むしろ(200)面が形成されやすくなる。ここで、TaソースとCソースはpMOS用TaCx電極の形成に用いたものと同様でかまわない。

【0078】

スパッタリング法を用いる場合、TaターゲットとCターゲットの同時スパッタリングを用いることが望ましい。この場合、pMOS用TaCx電極の形成法とは異なり、TaとCを同時にスパッタリングすることで、(111)面が形成されにくく、(200)面が形成されやすくなる。本実施形態においては、C/Ta=1.0のTaCx膜を、TaとCの2ターゲットの同時スパッタリングにより100nm堆積した。この膜の堆積はCVD法やMBE法などの手法を用いてもかまわない。

【0079】

このように本実施形態によれば、第1の実施形態とは逆に、pチャネルMISトランジスタ200のゲート電極210を下層ゲート電極211と上層ゲート電極212の積層構造とし、上層ゲート電極212の平均的な電気陰性度を下層ゲート電極211の平均的な電気陰性度よりも0.1以上大きくし、nチャネルMISトランジスタ100のゲート電極110としてpチャネルMISトランジスタ200の上層ゲート電極212と同一の金属材料を用いることにより、pチャネルMISトランジスタ200のゲート電極210の実効仕事関数をnチャネルMISトランジスタ100のゲート電極110の実効仕事関数より0.4eV以上高くすることができる。

【0080】

そしてこの場合、pチャネルMISトランジスタ200の上層ゲート電極212及びnチャネルMISトランジスタ100のゲート電極110は共に同一組成のTaCで、pチャネルMISトランジスタ200の下層ゲート電極211は非常に薄いため、ゲートの加工を一括で行うことができる。更には、pチャネルMISトランジスタ200の下層電極211は、pチャネルMISトランジスタ200の上層ゲート電極212及びnチャネルMISトランジスタ100のゲート電極110と組成は異なるがTaCからなり、構成元素が同一であるため、電極形成の際に別の原料を必要としない。従って、第1の実施形態と同様の効果が得られる。

【0081】

(第3の実施形態)

図15は、本発明の第3の実施形態に係わるデュアルメタルゲートCMOS構造の半導体装置の概略構造を示す断面図である。

【0082】

p型半導体領域101の表面上には第1のゲート絶縁膜104が形成されており、このゲート絶縁膜104上には、積層構造を成す第1のゲート電極110が形成されている。このゲート電極110の下層(第1下層ゲート電極)111は、厚さが1モノレイヤー以上3nm以下のTa−C合金からなり、上層(第1上層ゲート電極)112はTa−C合金からなる。但し、下層ゲート電極111の平均的な電気陰性度χは、上層ゲート電極112の平均的な電気陰性度χよりも大きい。これは、下層ゲート電極111のC原子濃度が上層ゲート電極112のC原子濃度より高いことと同義である。

【0083】

n型半導体領域201の表面上には第2のゲート絶縁膜204が形成されており、このゲート絶縁膜204の表面上には積層構造を成す第2のゲート電極210が形成されている。このゲート電極210の下層(第2下層ゲート電極)211は、厚さが1モノレイヤー以上3nm以下のTa−C合金からなり、上層(第2上層ゲート電極)212はTa−C合金からなる。下層ゲート電極211の平均的な電気陰性度χは、上層ゲート電極212の平均的な電気陰性度χよりも小さい。これは、下層ゲート電極211のC原子濃度が上層ゲート電極212のC原子濃度より低いことと同義である。また、pMOS側の上層ゲート電極212は、nMOS側の上層ゲート電極112と同じ材料であり、上層ゲート電極112と同時に形成されている。

【0084】

下層ゲート電極211と上層ゲート電極212の平均的なχの差の絶対値と、下層ゲート電極111と上層ゲート電極112の平均的なχの差の絶対値の和は0.1以上であり、これは結果的に下層ゲート電極111のCの原子密度が、下層ゲート電極211のCの原子密度より10 at.%以上高いことと同義である。

【0085】

上層ゲート電極112,212の上には、さらにWやTiNといった高融点金属等が形成されていてもよい。なお、図15のその他の構成である素子分離領域11、ソース/ドレイン領域102,202、エクステンション領域103,203、ゲート側壁絶縁膜120,220は、通常の半導体プロセスより形成可能である。

【0086】

本実施形態は、第1の実施形態のnチャネルMISトランジスタ100と、第2の実施形態のpチャネルMISトランジスタ200を組み合わせたものである。第1及び第2の実施形態と比較すると、製造工程が増えてしまう欠点があるものの、nチャネルMISトランジスタ100とpチャネルMISトランジスタ200の各ゲート電極の実効仕事関数差をより容易に得ることが可能である点で優れている。つまり、nチャネルMISトランジスタ100とpチャネルMISトランジスタ200の各ゲート電極がどちらも積層構造であるため、各ゲート電極の下層と上層のχ差は、第1及び第2の実施形態におけるゲート電極の下層と上層のχ差よりも小さくてよい。

【0087】

本実施形態において、Φeff(P)≧4.7eV及びΦeff(N)≦4.3eVの条件を満たすためには、上層ゲート電極112,212は、下層ゲート電極111と上層ゲート電極112の電気陰性度差の絶対値Δχ(1) 及び、下層ゲート電極211と上層ゲート電極212の電気陰性度差の絶対値がΔχ(2) が、

Φeff(1)−0.4×Δχ(1)/0.1 ≦ 4.3

Φeff(2)+0.4×Δχ(2)/0.1 ≧ 4.7

を満たしていればよいことが、前記式(3)から導出される。ここで、Φeff(1)及びΦeff(2)とは、それぞれ上層ゲート電極112及び上層ゲート電極212と同一の金属材料単層からなるゲート電極のΦeff である。

【0088】

また、本実施形態の構造は、第1の実施形態の製造工程と第2の実施形態の製造工程とを組み合わせることにより製造することができる。

【0089】

(変形例)

なお、本発明は上述した各実施形態に限定されるものではない。実施形態ではゲート電極としてTaCを用いたが、必ずしもTaCに限らず、TiC,TaN,TiNを用いることも可能である。また、下層ゲート電極の厚さは1モノレイヤー以上で3nm以下の範囲であれば適宜変更可能である。同様に、下層ゲート電極と上層ゲート電極との平均的な電気陰性度の差、更には下層ゲート電極のCの原子密度と上層ゲート電極のCの原子密度との関係は、実施形態で説明した範囲において、適宜変更可能である。また、ゲート絶縁膜は、シリコン酸化膜に限らずシリコン窒化膜、シリコン酸化窒化膜、更には他の高誘電体膜を用いることも可能である。

【0090】

その他、本発明の要旨を逸脱しない範囲で、種々変形して実施することができる。

【図面の簡単な説明】

【0091】

【図1】ゲート電極の構造と、その実効仕事関数との関係を示す図。

【図2】ゲート電極/ゲート絶縁膜界面にダイポールが形成した場合のエネルギーバンドを示す図。

【図3】ゲート電極の構造(単層、積層)と、その実効仕事関数との関係を示す図。

【図4】ゲート電極の構造(単層、積層)と、その実効仕事関数との関係を示す図。

【図5】TaCx電極及びTaCx/TaCy電極のSiO2 上での実効仕事関数を示す図。

【図6】第1の実施形態に係わる半導体装置の概略構造を示す断面図

【図7】成膜法の違いによるTaCx電極の配向性変化を示す特性図。

【図8】TaCx電極配向性と仕事関数との関係を示す特性図。

【図9】TaCx電極組成と結晶性の変化との関係を示す特性図。

【図10】第1の実施形態に係わる半導体装置の製造工程を示す断面図。

【図11】pMOS用TaCx電極の形成方法を説明するための模式図。

【図12】ゲート絶縁膜上に堆積するC層の膜厚と仕事関数との関係を示す特性図。

【図13】第2の実施形態に係わる半導体装置の概略構造を示す断面図。

【図14】nMOS用TaCx電極の形成方法を説明するための模式図。

【図15】第3の実施形態に係わる半導体装置の概略構造を示す断面図

【符号の説明】

【0092】

10…Si半導体基板

11…素子分離領域

15…C層

16…Ta−C合金

100…nチャネルMISトランジスタ

200…pチャネルMISトランジスタ

101…p型半導体領域

102,202…ソース/ドレイン電極

103,203…エクステンション領域

104,204…ゲート絶縁膜

110,210…ゲート電極

111,211…下層ゲート電極

112,212…上層ゲート電極

120,220…ゲート側壁

201…n型半導体領域

【特許請求の範囲】

【請求項1】

基板上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された半導体装置であって、

前記nチャネルMISトランジスタは、前記基板上に形成されたp型半導体領域と、前記p型半導体領域上に形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第1下層ゲート電極と、前記第1下層ゲート電極上に形成され、平均的な電気陰性度が第1下層ゲート電極の平均的な電気陰性度よりも0.1以上小さく、金属材料で形成された第1上層ゲート電極とを含んで形成され、

前記pチャネルMISトランジスタは、前記基板上に形成されたn型半導体領域と、前記n型半導体領域上に形成された第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成され、前記金属材料で形成された第2ゲート電極とを含んで形成されていることを特徴とする半導体装置。

【請求項2】

前記第2ゲート電極の実効仕事関数Φeff(1) は4.7eV以上であり、前記第1下層ゲート電極と前記第1上層ゲート電極との平均的な電気陰性度の差Δχ(1) は、

Φeff(1)−0.4×Δχ(1)/0.1≦4.3

を満たすことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記金属材料はTa−C合金であることを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記第1下層ゲート電極はTa−C合金で形成され、前記第1下層ゲート電極のCの原子密度は、前記第1上層ゲート電極のCの原子密度より10 at.%以上高いことを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記第2ゲート電極は、該ゲート電極の膜厚方向に対するTaC(111)面の結晶配向率[TaC(111)面/{TaC(111)面+TaC(200)面}]が80%以上であることを特徴とする請求項3又は4に記載の半導体装置。

【請求項6】

基板上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された半導体装置であって、

前記nチャネルMISトランジスタは、前記基板上に形成されたp型半導体領域と、前記p型半導体領域上に形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成され、金属材料で形成された第1ゲート電極とを含んで形成され、

前記pチャネルMISトランジスタは、前記基板上に形成されたn型半導体領域と、前記n型半導体領域上に形成された第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第2下層ゲート電極と、前記第2下層ゲート電極上に形成され、平均的な電気陰性度が第2下層ゲート電極の平均的な電気陰性度よりも0.1以上大きく、前記金属材料で形成された第2上層ゲート電極とを含んで形成されていることを特徴とする半導体装置。

【請求項7】

前記第1ゲート電極の実効仕事関数Φeff(2) は4.3eV以下であり、前記第2下層ゲート電極と前記第2上層ゲート電極との平均的な電気陰性度の差Δχ(2) の絶対値は、

Φeff(2)+0.4×Δχ(2)/0.1≧4.7

を満たすことを特徴とする請求項6に記載の半導体装置。

【請求項8】

前記第2上層ゲート電極はTa−C合金で形成されていることを特徴とする請求項6又は7に記載の半導体装置。

【請求項9】

前記第2下層ゲート電極はTa−C合金で形成され、前記第2下層ゲート電極のCの原子密度は、前記第2上層ゲート電極のCの原子密度より10 at.%以上低いことを特徴とする請求項8に記載の半導体装置。

【請求項10】

前記第1ゲート電極は、該ゲート電極の膜厚方向に対するTaC(111)面の結晶配向率[TaC(111)面/{TaC(111)面+TaC(200)面}]が60%以下であることを特徴とする請求項8又は9に記載の半導体装置。

【請求項11】

基板と、

前記基板上に形成されたp型半導体領域と、前記p型半導体領域上に形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第1下層ゲート電極と、前記第1下層ゲート電極上に形成され、平均的な電気陰性度が第1下層ゲート電極の平均的な電気陰性度よりも小さく、金属材料で形成された第1上層ゲート電極とを含んで形成されたnチャネルMISトランジスタと、

前記基板上に形成されたn型半導体領域と、前記n型半導体領域上に形成された第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第2下層ゲート電極と、前記第2下層ゲート電極上に形成され、平均的な電気陰性度が第2下層ゲート電極の平均的な電気陰性度よりも大きく、前記金属材料で形成された第2上層ゲート電極とを含んで形成されたpチャネルMISトランジスタと、

を具備し、

前記第1下層ゲート電極と前記第1上層ゲート電極との平均的な電気陰性度の差の絶対値Δχ(1) と、前記第2下層ゲート電極と前記第2上層ゲート電極との平均的な電気陰性度の差の絶対値Δχ(2) と、の和が0.1以上であることを特徴とする半導体装置。

【請求項12】

前記第1上層ゲート電極と同一の金属材料で単層のゲート電極を形成した場合の該ゲート電極の実効仕事関数Φeff(1)、前記第2上層ゲート電極と同一の金属材料で単層のゲート電極を形成した場合の該ゲート電極の実効仕事関数Φeff(2)、前記Δχ(1) 及び前記Δχ(2) が、

Φeff(1)−0.4×Δχ(1)/0.1≦4.3

Φeff(2)+0.4×Δχ(2)/0.1≧4.7

を満たすことを特徴とする請求項11に記載の半導体装置。

【請求項13】

前記第1上層ゲート電極及び前記第2上層ゲート電極は、同じ組成のTa−C合金で形成されていることを特徴とする請求項11又は12に記載の半導体装置。

【請求項14】

前記第1下層ゲート電極と前記第2下層ゲート電極はTa−C合金で形成され、前記第1下層ゲート電極のCの原子密度は前記第1上層ゲート電極のCの原子密度より高く、前記第2下層ゲート電極のCの原子密度は前記第1上層ゲート電極のCの原子密度より低く、前記第1下層ゲート電極のCの原子密度は前記第2下層ゲート電極のCの原子密度より10 at.%以上高いことを特徴とする請求項11乃至13の何れかに記載の半導体装置。

【請求項15】

前記第1下層ゲート電極は、Ta−C合金にN,O,F,P,S,Cl,As,Se,Br,Iのうちの少なくとも1つが添加された金属材料で形成されていることを特徴とする請求項3,4,13,14の何れかに記載の半導体装置。

【請求項16】

前記第2下層ゲート電極は、Ta−C合金にSc,Y,La,Zr,Hfのうちの少なくとも1つが添加された金属材料で形成されていることを特徴とする請求項8,9,13,14の何れかに記載の半導体装置。

【請求項1】

基板上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された半導体装置であって、

前記nチャネルMISトランジスタは、前記基板上に形成されたp型半導体領域と、前記p型半導体領域上に形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第1下層ゲート電極と、前記第1下層ゲート電極上に形成され、平均的な電気陰性度が第1下層ゲート電極の平均的な電気陰性度よりも0.1以上小さく、金属材料で形成された第1上層ゲート電極とを含んで形成され、

前記pチャネルMISトランジスタは、前記基板上に形成されたn型半導体領域と、前記n型半導体領域上に形成された第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成され、前記金属材料で形成された第2ゲート電極とを含んで形成されていることを特徴とする半導体装置。

【請求項2】

前記第2ゲート電極の実効仕事関数Φeff(1) は4.7eV以上であり、前記第1下層ゲート電極と前記第1上層ゲート電極との平均的な電気陰性度の差Δχ(1) は、

Φeff(1)−0.4×Δχ(1)/0.1≦4.3

を満たすことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記金属材料はTa−C合金であることを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記第1下層ゲート電極はTa−C合金で形成され、前記第1下層ゲート電極のCの原子密度は、前記第1上層ゲート電極のCの原子密度より10 at.%以上高いことを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記第2ゲート電極は、該ゲート電極の膜厚方向に対するTaC(111)面の結晶配向率[TaC(111)面/{TaC(111)面+TaC(200)面}]が80%以上であることを特徴とする請求項3又は4に記載の半導体装置。

【請求項6】

基板上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された半導体装置であって、

前記nチャネルMISトランジスタは、前記基板上に形成されたp型半導体領域と、前記p型半導体領域上に形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成され、金属材料で形成された第1ゲート電極とを含んで形成され、

前記pチャネルMISトランジスタは、前記基板上に形成されたn型半導体領域と、前記n型半導体領域上に形成された第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第2下層ゲート電極と、前記第2下層ゲート電極上に形成され、平均的な電気陰性度が第2下層ゲート電極の平均的な電気陰性度よりも0.1以上大きく、前記金属材料で形成された第2上層ゲート電極とを含んで形成されていることを特徴とする半導体装置。

【請求項7】

前記第1ゲート電極の実効仕事関数Φeff(2) は4.3eV以下であり、前記第2下層ゲート電極と前記第2上層ゲート電極との平均的な電気陰性度の差Δχ(2) の絶対値は、

Φeff(2)+0.4×Δχ(2)/0.1≧4.7

を満たすことを特徴とする請求項6に記載の半導体装置。

【請求項8】

前記第2上層ゲート電極はTa−C合金で形成されていることを特徴とする請求項6又は7に記載の半導体装置。

【請求項9】

前記第2下層ゲート電極はTa−C合金で形成され、前記第2下層ゲート電極のCの原子密度は、前記第2上層ゲート電極のCの原子密度より10 at.%以上低いことを特徴とする請求項8に記載の半導体装置。

【請求項10】

前記第1ゲート電極は、該ゲート電極の膜厚方向に対するTaC(111)面の結晶配向率[TaC(111)面/{TaC(111)面+TaC(200)面}]が60%以下であることを特徴とする請求項8又は9に記載の半導体装置。

【請求項11】

基板と、

前記基板上に形成されたp型半導体領域と、前記p型半導体領域上に形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第1下層ゲート電極と、前記第1下層ゲート電極上に形成され、平均的な電気陰性度が第1下層ゲート電極の平均的な電気陰性度よりも小さく、金属材料で形成された第1上層ゲート電極とを含んで形成されたnチャネルMISトランジスタと、

前記基板上に形成されたn型半導体領域と、前記n型半導体領域上に形成された第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成され、膜厚が1モノレイヤー以上3nm以下である第2下層ゲート電極と、前記第2下層ゲート電極上に形成され、平均的な電気陰性度が第2下層ゲート電極の平均的な電気陰性度よりも大きく、前記金属材料で形成された第2上層ゲート電極とを含んで形成されたpチャネルMISトランジスタと、

を具備し、

前記第1下層ゲート電極と前記第1上層ゲート電極との平均的な電気陰性度の差の絶対値Δχ(1) と、前記第2下層ゲート電極と前記第2上層ゲート電極との平均的な電気陰性度の差の絶対値Δχ(2) と、の和が0.1以上であることを特徴とする半導体装置。

【請求項12】

前記第1上層ゲート電極と同一の金属材料で単層のゲート電極を形成した場合の該ゲート電極の実効仕事関数Φeff(1)、前記第2上層ゲート電極と同一の金属材料で単層のゲート電極を形成した場合の該ゲート電極の実効仕事関数Φeff(2)、前記Δχ(1) 及び前記Δχ(2) が、

Φeff(1)−0.4×Δχ(1)/0.1≦4.3

Φeff(2)+0.4×Δχ(2)/0.1≧4.7

を満たすことを特徴とする請求項11に記載の半導体装置。

【請求項13】

前記第1上層ゲート電極及び前記第2上層ゲート電極は、同じ組成のTa−C合金で形成されていることを特徴とする請求項11又は12に記載の半導体装置。

【請求項14】

前記第1下層ゲート電極と前記第2下層ゲート電極はTa−C合金で形成され、前記第1下層ゲート電極のCの原子密度は前記第1上層ゲート電極のCの原子密度より高く、前記第2下層ゲート電極のCの原子密度は前記第1上層ゲート電極のCの原子密度より低く、前記第1下層ゲート電極のCの原子密度は前記第2下層ゲート電極のCの原子密度より10 at.%以上高いことを特徴とする請求項11乃至13の何れかに記載の半導体装置。

【請求項15】

前記第1下層ゲート電極は、Ta−C合金にN,O,F,P,S,Cl,As,Se,Br,Iのうちの少なくとも1つが添加された金属材料で形成されていることを特徴とする請求項3,4,13,14の何れかに記載の半導体装置。

【請求項16】

前記第2下層ゲート電極は、Ta−C合金にSc,Y,La,Zr,Hfのうちの少なくとも1つが添加された金属材料で形成されていることを特徴とする請求項8,9,13,14の何れかに記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2008−147239(P2008−147239A)

【公開日】平成20年6月26日(2008.6.26)

【国際特許分類】

【出願番号】特願2006−329521(P2006−329521)

【出願日】平成18年12月6日(2006.12.6)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成20年6月26日(2008.6.26)

【国際特許分類】

【出願日】平成18年12月6日(2006.12.6)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]