半導体装置

【課題】厚いゲート絶縁膜を形成することに起因する不具合を生じさせることなく、高耐圧デバイスにも適用可能なMOSトランジスタを備えた半導体装置を提供する。

【解決手段】ドレイン領域はN−ドレイン領域3dとN+ドレイン領域11dからなる二重拡散構造を備えている。ゲート電極は、ゲート絶縁膜7上に形成された第1ゲート電極9と、第1ゲート電極上9にゲート電極間絶縁膜11を介して形成された第2ゲート電極13とからなる。第2ゲート電極13にゲート配線13gが接続され、第1ゲート電極9にはゲート配線13gは接続されていない。ゲート絶縁膜7とN+ソース領域11sの間の半導体基板1表面にフィールド絶縁膜15配置されている。第1ゲート電極9のドレイン領域側の端部はフィールド絶縁膜15上に配置されている。第2ゲート電極13に印加されるゲート電圧はゲート絶縁膜7とゲート電極間絶縁膜11で分割される。

【解決手段】ドレイン領域はN−ドレイン領域3dとN+ドレイン領域11dからなる二重拡散構造を備えている。ゲート電極は、ゲート絶縁膜7上に形成された第1ゲート電極9と、第1ゲート電極上9にゲート電極間絶縁膜11を介して形成された第2ゲート電極13とからなる。第2ゲート電極13にゲート配線13gが接続され、第1ゲート電極9にはゲート配線13gは接続されていない。ゲート絶縁膜7とN+ソース領域11sの間の半導体基板1表面にフィールド絶縁膜15配置されている。第1ゲート電極9のドレイン領域側の端部はフィールド絶縁膜15上に配置されている。第2ゲート電極13に印加されるゲート電圧はゲート絶縁膜7とゲート電極間絶縁膜11で分割される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、第1導電型の半導体基板の表面側に互いに間隔をもって配置された第2導電型のドレイン領域及びソース領域と、ソース領域とドレイン領域の間の半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とをもち、ソース領域とドレイン領域の間の半導体基板がチャネル領域となっているMOSトランジスタを備えた半導体装置に関し、特に、LOCOSオフセットトランジスタに関するものである。

【背景技術】

【0002】

近年の携帯電話器や携帯ゲーム機器の市場拡大に対応して液晶駆動用回路の需要が拡大している。液晶駆動にはバックライト電源などで高い電圧が必要とされるため、そのLSI化には高耐圧トランジスタが必要となる。CMOS(相補型Metal Oxide Semiconductor)型における高耐圧トランジスタの代表的なものとして、MOSトランジスタからなるLOCOS(LOCal Oxidation of Silicon:ロコス)オフセットトランジスタ(例えば特許文献1を参照。)とMasked−LDD(Lightly Doped Drain)トランジスタ(例えば特許文献2を参照。)がある。

【0003】

まず、LOCOSオフセットトランジスタについて説明する。

図32は従来のLOCOSオフセットトランジスタを示す断面図である。

P型の半導体基板1の表面側に互いに間隔をもってN−ドレイン領域3dとN−ソース領域3sが形成されている。N−ドレイン領域3dとN−ソース領域3sの間の半導体基板1がチャネル領域5となる。N−ドレイン領域3dとN−ソース領域3sの間の半導体基板1上にゲート絶縁膜51が形成されている。ゲート絶縁膜51上にゲート電極53が形成されている。図示は省略するが、N−ドレイン領域3d、N−ソース領域3s及びチャネル領域5が形成されている領域の半導体基板1にはP型ウエル領域が形成されている。

【0004】

N−ドレイン領域3dの表面側に、N−ドレイン領域3dの端部とは間隔をもってN+ドレイン領域11dが形成されている。N−ソース領域3sの表面側に、N−ソース領域3sの端部とは間隔をもってN+ソース領域11sが形成されている。

半導体基板1の表面に、LOCOSオフセットトランジスタの形成領域を画定するためのLOCOS酸化膜15が形成されている。LOCOS酸化膜15はゲート絶縁膜51よりも厚い膜厚をもつ。N−ドレイン領域3dのチャネル領域5側の端部とN+ドレイン領域11dの間のN−ドレイン領域3d表面、及びN−ソース領域3sのチャネル領域5側の端部とN+ソース領域11sの間のN−ソース領域3s表面にもLOCOS酸化膜15が形成されている。ゲート電極53の端部はLOCOS酸化膜15上に配置されている。

【0005】

ゲート電極53、N+ドレイン領域11d、N+ソース領域11s及びLOCOS酸化膜15上を覆って半導体基板1上に酸化シリコン膜系絶縁膜17が形成されている。酸化シリコン膜系絶縁膜17上に金属材料からなるゲート配線19g、ドレイン配線19d及びソース配線19sが形成されている。酸化シリコン膜系絶縁膜17に形成された接続孔21を介して、ゲート配線19gはゲート電極53に接続され、ドレイン配線19dはN+ドレイン領域11dに接続され、ソース配線19sはN+ソース領域11sに接続されている。

【0006】

図32〜図37を参照して従来のLOCOSオフセットトランジスタの製造工程を説明する。

P型半導体基板1に図示しないP型ウエル領域を形成した後、写真製版技術を用いてレジストパターン(図示は省略)を形成し、それをマスクとしてリンを注入エネルギーは100KeV(キロエレクトロンボルト)、ドーズ量は2.0×1013cm-2の条件でイオン注入する。レジストパターンを除去した後、温度1000℃、30分間の窒素雰囲気にさらすことで注入されたリンが拡散及び活性化し、低濃度なN−ドレイン領域3d及びN−ソース領域3sが形成される(図33参照。)。

【0007】

既存の素子分離形成技術を用いてLOCOS酸化膜15を膜厚500nm(ナノメートル)で形成する(図34参照。)。

ゲート絶縁膜51を膜厚80nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして多結晶シリコン膜及びゲート絶縁膜51を順次エッチング除去して多結晶シリコン膜からなるゲート電極53を形成し、ゲート電極53下にゲート絶縁膜51を形成する。その後、レジストパターンの除去を行なう(図35参照。)。ゲート電極53の端部はLOCOS酸化膜15上に配置されている。

【0008】

LOCOSオフセットトランジスタの形成領域に開口をもつレジストパターンを形成した後、ヒ素を注入エネルギー30KeV、ドーズ量5.0×1015cm-2の条件でイオン注入する。レジストパターンを除去した後、温度900℃、30分間の窒素雰囲気にさらすことで注入されたヒ素が拡散及び活性化し、高濃度なN+ドレイン領域11d及びN+ソース領域11sが形成される(図36参照。)。N+ドレイン領域11dとその周りを覆う低濃度なN−ドレイン領域3dがドレイン領域を構成し、N+ソース領域11sとその周りを覆う低濃度なN−ソース領域3sがソース領域を構成する。このように、LOCOSオフセットトランジスタではドレイン領域及びソース領域が二重拡散構造を備えている。

【0009】

半導体基板1上全面に酸化シリコン膜系絶縁膜17を1000nmの膜厚に堆積する。レジストパターンを形成した後、そのレジストパターンをマスクとして所定の位置の酸化シリコン膜系絶縁膜17をエッチング除去し、N+ドレイン領域11d、N+ソース領域11s、ゲート電極53に対応する位置に接続孔21を形成する(図37参照。)。

【0010】

酸化シリコン膜系絶縁膜17上にアルミニウム系金属膜を形成し、その金属膜をパターニングして、ゲート配線19g、ドレイン配線19d及びソース配線19sを形成する(図32参照。)。

【0011】

LOCOSオフセットトランジスタは、(1)ドレイン領域及びソース領域が二重拡散構造を備えていること、(2)ゲート電極53の端部がゲート絶縁膜51よりも厚いLOCOS酸化膜15上に配置されていること、の2つの特徴を備えていることで高耐圧化が可能となる。

【0012】

ドレイン領域及びソース領域の耐圧に関して、その耐圧はアバランシェブレイクダウンで決定される。図32に示したように、LOCOSオフセットトランジスタにおいては、N+ドレイン領域11dはN−ドレイン領域3dで囲まれ、N+ソース領域11sはN−ソース領域3sで囲まれているので、濃いN+ドレイン領域11d及びN+ソース領域11sがP型ウエルと直接接することがない。その結果、ドレイン領域及びソース領域のアバランシェブレイクダウン耐圧は30V程度まで向上する。なお、上記(1),(2)のLOCOSオフセットトランジスタの特徴を備えていない通常のMOSトランジスタのドレイン領域及びソース領域のアバランシェブレイクダウン耐圧は10V程度である。

【0013】

また、MOSトランジスタでは、ゲート電極の電位がGND(グラウンド)電位に固定された場合、ゲート電極直下のPN接合部は耐圧が下がることが知られている。この現象をゲート変調接合耐圧と呼び、通常のMOSトランジスタでは10V前後の低い値でブレイクダウンしてしまう。一方、LOCOSオフセットトランジスタでは、図32に示したように、ゲート電極53の端部がLOCOS酸化膜15に乗り上げているので、ゲート電極53と高濃度N+領域11d,11s間の基板垂直方向の距離を大きくすることができ、その結果、ゲート変調接合耐圧が30V程度まで向上する。

【0014】

以上のように、(1)ドレイン領域及びソース領域が高濃度N+領域11d,11sと低濃度N−領域3d,3sの2つの領域で形成されていること、(2)ゲート電極53の端部がLOCOS酸化膜15に乗り上げていること、の2つの構造的工夫を採用することで高耐圧化を実現できるのである。

【0015】

次にMasked−LDDトランジスタについて説明する。

図38はMasked−LDDトランジスタを示す断面図である。

P型の半導体基板1の表面側に互いに間隔をもってN−ドレイン領域3dとN−ソース領域3sが形成されている。N−ドレイン領域3dとN−ソース領域3sの間の半導体基板1上にゲート絶縁膜51が形成されている。ゲート絶縁膜51上にゲート電極53が形成されている。N−ドレイン領域3dとN−ソース領域3sの間の半導体基板1がチャネル領域5となる。図示は省略するが、N−ドレイン領域3d、N−ソース領域3s及びチャネル領域5が形成されている領域の半導体基板1にはP型ウエル領域が形成されている。

【0016】

N−ドレイン領域3dの表面側に、N−ドレイン領域3dの端部とは間隔をもってN+ドレイン領域11dが形成されている。N−ソース領域3sの表面側に、N−ソース領域3sの端部とは間隔をもってN+ソース領域11sが形成されている。すなわち、上方から見て、N+ドレイン領域11及びN+ソース領域11sはゲート電極53とは間隔をもって配置されている。

半導体基板1の表面に、Masked−LDDトランジスタの形成領域を画定するためのLOCOS酸化膜15が形成されている。LOCOS酸化膜15はゲート絶縁膜51よりも厚い膜厚をもつ。Masked−LDDトランジスタの形成領域内にはLOCOS酸化膜15は形成されていない。

【0017】

ゲート電極53、N+ドレイン領域11d、N+ソース領域11s及びLOCOS酸化膜15上を覆って半導体基板1上に酸化シリコン膜系絶縁膜17が形成されている。酸化シリコン膜系絶縁膜17上に金属材料からなるゲート配線19g、ドレイン配線19d及びソース配線19sが形成されている。酸化シリコン膜系絶縁膜17に形成された接続孔21を介して、ゲート配線19gはゲート電極53に接続され、ドレイン配線19dはN+ドレイン領域11dに接続され、ソース配線19sはN+ソース領域11sに接続されている。

【0018】

図38〜図43を参照してMasked−LDDトランジスタの製造工程を説明する。

P型半導体基板1に図示しないP型ウエル領域を形成した後、既存の素子分離形成技術を用いてLOCOS酸化膜15を膜厚500nmで形成する(図39参照。)。

【0019】

ゲート絶縁膜51を膜厚80nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして多結晶シリコン膜及びゲート絶縁膜51を順次エッチング除去して多結晶シリコン膜からなるゲート電極53を形成し、ゲート電極53下にゲート絶縁膜51を形成する。その後、レジストパターンの除去を行なう(図40参照。)。

【0020】

Masked−LDDトランジスタの形成領域に開口をもつレジストパターンを形成した後、リンを注入エネルギー30KeV、ドーズ量2.0×1013cm-2の条件でイオン注入する。レジストパターンを除去した後、温度900℃、30分間の窒素雰囲気にさらすことで注入されたリンが拡散及び活性化し、低濃度なN−ドレイン領域3d及びN−ソース領域3sが形成される(図41参照。)。

【0021】

ゲート電極53と、上方から見てゲート電極53に隣接しているN−ドレイン領域3d及びN−ソース領域3sの一部分を覆うレジストパターンを形成する。そのレジストパターンをマスクとしてヒ素を注入エネルギー30KeV、ドーズ量5.0×1015cm-2の条件でイオン注入する。レジストパターンを除去した後、温度900℃、30分間の窒素雰囲気にさらすことで注入されたヒ素が拡散及び活性化し、高濃度なN+ドレイン領域11d及びN+ソース領域11sが形成される(図42参照。)。N+ドレイン領域11dとその周りを覆う低濃度なN−ドレイン領域3dがドレイン領域を構成し、N+ソース領域11sとその周りを覆う低濃度なN−ソース領域3sがソース領域を構成する。このように、Masked−LDDトランジスタではドレイン領域及びソース領域が二重拡散構造を備えている。

【0022】

このように、ゲート電極53とN−ドレイン領域3d及びN−ソース領域3sの間にLOCOS酸化膜15が介在していないのがMasked−LDDトランジスタの特徴である。この製造工程からわかるように、N−ドレイン領域3d及びN−ソース領域3sの領域はレジストパターンによって確定されている。このような構造のMOSトランジスタは、レジストパターンによって高濃度なヒ素注入が部分的に遮蔽(Mask)されることによって形成されることからMasked−LDDトランジスタと呼ばれている。

【0023】

製造工程の説明を続けると、半導体基板1上全面に酸化シリコン膜系絶縁膜17を1000nmの膜厚に堆積する。レジストパターンを形成した後、そのレジストパターンをマスクとして所定の位置の酸化シリコン膜系絶縁膜17をエッチング除去し、N+ドレイン領域11d、N+ソース領域11s、ゲート電極53に対応する位置に接続孔21を形成する(図43参照。)。

【0024】

酸化シリコン膜系絶縁膜17上にアルミニウム系金属膜を形成し、その金属膜をパターニングして、ゲート配線19g、ドレイン配線19d及びソース配線19sを形成する(図38参照。)。

【0025】

Masked−LDDトランジスタとLOCOSオフセットトランジスタの相違点は、Masked−LDDトランジスタはゲート電極のドレイン領域側の端部及びソース領域側の端部がLOCOS酸化膜に乗り上げていないことである。そして、この相違点を反映して、Masked−LDDトランジスタはLOCOSオフセットトランジスタに比べて対応可能電圧(いわゆる耐圧)が低くなる。その反面、電流駆動能力はMasked−LDDトランジスタの方が大きい。つまり、中程度の高耐圧機能をもたせつつ大電流を流したいような用途にはMasked−LDDトランジスタが適しており、電流駆動能力を犠牲にしても高い電圧を扱いたい用途にはLOCOSオフセットトランジスタが適している、と言える。

【0026】

以上の説明では、ドレイン領域及びソース領域の両方が高耐圧機能をもった場合を説明したが、デバイス仕様によってはドレイン領域のみが高耐圧機能をもっている場合もあり得る。

【0027】

次に、Masked−LDDトランジスタとLOCOSオフセットトランジスタの共通点に着目する。

Masked−LDDトランジスタとLOCOSオフセットトランジスタで共通した点はゲート絶縁膜51の膜厚が80nmと厚いことが上げられる。この膜厚は耐圧30Vを想定した場合であり、要求される耐圧値が30Vよりも高い場合はこの膜厚は更に厚くなる。つまり、ゲート電極にも高い電圧が印加されるので、ゲート絶縁膜の絶縁耐性がそれに耐えうるようにその膜厚を厚くする必要があるわけである。

【0028】

そしてこの点がこれら両デバイスの重要課題となっている。すなわちゲート絶縁膜51の膜厚が80nmと厚いので成膜に必要な処理時間が長時間化してしまうのである。この結果、成膜時の熱処理の影響で、既に形成済のP型ウエルやしきい値電圧(Vth)調整のためのチャネルドープ不純物が再分布してしまう。特にゲート絶縁膜が約50nmより厚くなると酸化時間が極端に長くなるので、完成したデバイスの特性ズレを招いてしまう。このことは高耐圧トランジスタ自身の問題だけではなく、他の素子、例えば容量素子や抵抗素子、或いは、別用途のトランジスタを同一半導体基板に形成する場合は、これらの素子も同様の影響を受けてしまうことになるので、この処理時間が長時間化する問題は複合混載化の最も大きな阻害要因になっている。

【0029】

厚いゲート絶縁膜にはもう一つ大きな問題がある。その問題点を図44から図47を参照して説明する。

従来の高耐圧トランジスタの製造工程では、まず、LOCOS酸化膜15が形成されている半導体基板1上に厚いゲート絶縁膜51を形成し、さらにゲート電極53を形成するための多結晶シリコン膜をウエハ全面に形成する(図44参照。)。次に、レジストパターン(図示は省略)を用いて多結晶シリコン膜をエッチング除去してゲート電極53を形成する(図45参照。)。次に、ウェットエッチング技術を用いてゲート電極53下以外の厚いゲート絶縁膜51を除去した後、イオン注入法によりN+ドレイン領域11dとN+ソース領域11sを形成する(図46参照。)。

【0030】

上記製造工程において、ゲート電極53下以外の厚いゲート絶縁膜51を除去する理由は、図45に示したようにN+ドレイン領域11dとN+ソース領域11sの形成予定領域に厚いゲート絶縁膜51が残存している状態では、N+ドレイン領域11dとN+ソース領域11sを形成するためのイオン注入時に厚いゲート絶縁膜51が遮蔽物になってしまい、N+ドレイン領域11dとN+ソース領域11sを正常には形成できないからである。このため、図46に示したように、N+ドレイン領域11dとN+ソース領域11sの形成予定領域に残存する厚いゲート絶縁膜51をイオン注入前に除去する必要がある。

【0031】

厚いゲート絶縁膜51の除去はウェットエッチングにて実施するのであるが、厚いゲート絶縁膜51の膜厚が80nmと厚いので、厚いゲート絶縁膜51の除去に長時間の処理が必要となり、製造工程が長時間化するという不具合が生じる。

さらに、この除去処理を行なうことで、既に形成済のLOCOS酸化膜15も膜減りするため、LOCOS酸化膜15の端部(図46の破線円内)がくぼみ部55のように形状異常に陥ってしまう(図47参照。)。このことは設計寸法からのズレだけでなく電気特性異常も引き起こす虞れがある。

【0032】

以上のように、厚いゲート絶縁膜を形成することはデバイス形成の上で課題が多数あるわけで、このことが高耐圧トランジスタの形成、更には他の素子との複合混載化を困難なものにしている。

【0033】

【特許文献1】特第3275569号公報

【特許文献2】特開平09−266255号公報

【特許文献3】特開2005−303037号公報

【発明の開示】

【発明が解決しようとする課題】

【0034】

そこで本発明は、厚いゲート絶縁膜を形成することに起因する不具合を生じさせることなく、高耐圧デバイスにも適用可能なMOSトランジスタを備えた半導体装置を提供することを目的とするものである。

【課題を解決するための手段】

【0035】

本発明にかかる半導体装置は、第1導電型の半導体基板の表面側に互いに間隔をもって配置された第2導電型のドレイン領域及びソース領域と、上記ソース領域とドレイン領域の間の上記半導体基板上に形成されたゲート絶縁膜と、上記ゲート絶縁膜上に形成されたゲート電極とをもち、上記ソース領域とドレイン領域の間の上記半導体基板がチャネル領域となっているMOSトランジスタを備えた半導体装置であって、上記ドレイン領域は、上記ゲート絶縁膜及び上記チャネル領域とは間隔をもって配置された第1ドレイン領域と、上記第1ドレイン領域と上記チャネル領域の間に上記第1ドレイン領域及び上記チャネル領域に隣接して配置された第2ドレイン領域とからなり、上記ゲート電極は、上記ゲート絶縁膜上に形成された第1ゲート電極と、上記第1ゲート電極上にゲート電極間絶縁膜を介して形成された第2ゲート電極とからなり、上記第2ゲート電極にはゲート電圧を与えるためのゲート配線が接続されており、上記第1ゲート電極には上記ゲート配線は接続されておらず、上記半導体基板表面に上記ゲート絶縁膜よりも厚い厚みをもつフィールド絶縁膜を備え、上記フィールド絶縁膜は少なくとも上記ゲート絶縁膜と上記第1ドレイン領域の間の上記半導体基板表面に配置されており、上記第1ゲート電極の上記ドレイン領域側の端部は上記フィールド絶縁膜上に配置されているものである。

【0036】

本発明の半導体装置を構成するMOSトランジスタは、ゲート電極として、半導体基板上にゲート絶縁膜を介して形成された第1ゲート電極と、第1ゲート電極上にゲート電極間絶縁膜を介して形成された第2ゲート電極を備えている。そして、ゲート電極にゲート電圧を与えるためのゲート配線は、第2ゲート電極に接続され、第1ゲート電極には接続されていない。この構造において、ゲート電圧に対してゲート電極間絶縁膜にかかる電圧V2とゲート絶縁膜にかかる電圧V1は、第2ゲート電極と第1ゲート電極の間の容量値C2と、第1ゲート電極と半導体基板の間の容量値C1によって決定される。すなわち、ゲート電極に印加されるゲート電圧が高電圧であっても、上記容量値C1とC2を調整することによってゲート絶縁膜にかかる電圧V1を小さくすることができ、厚いゲート絶縁膜を用いることなく、ゲート電極に高いゲート電圧が高印加される高耐圧デバイスに適用することができる。ただし、本発明が適用される半導体装置は、一般に高耐圧と言われる、例えば15V以上の高耐圧をもつMOSトランジスタを備えた半導体装置に限定されるものではなく、低耐圧で高速動作が可能なMOSトランジスタを備えた半導体装置にも適用することができる。

【0037】

本発明の半導体装置において、上記第2ゲート電極の端部は、上方から見て、上記第1ゲート電極上のみに配置されている例を挙げることができる。

さらに、上記第1ゲート電極の端部及び側面を覆い、かつ上記第2ゲート電極とは間隔をもって配置された、上記第2ゲート電極と同一材料で同時に形成されたパターンが形成されているようにしてもよい。

【0038】

また、上方から見て、上記第2ゲート電極の端部の一部分又は全部が上記第1ゲート電極の端部よりも外側に配置されており、上記第1ゲート電極の端部よりも外側に配置されている上記第2ゲート電極部分は上記フィールド絶縁膜上に配置されており、かつ上記第1ゲート電極とは前記ゲート電極間絶縁膜を介している例を挙げることができる。

さらに、上方から見て、上記第2ゲート電極の端部の全部が上記第1ゲート電極の端部よりも外側に配置されており、上記第2ゲート電極は上記第1ゲート電極の端部及び側面を覆っているようにしてもよい。

さらに、上方から見て、上記第1ゲート電極上で上記第1ゲート電極の端部とは間隔をもつ位置に上記第2ゲート電極が形成されていない領域が存在しているようにしてもよい。

【0039】

また、上記第1ゲート電極と上記第2ゲート電極の間の容量値が互いに異なる複数の上記MOSトランジスタを備えている例を挙げることができる。

この場合、上記複数のMOSトランジスタにおいて、上記第2ゲート電極のレイアウト面積のみが互いに異なっている例を挙げることができる。

【0040】

また、アナログ回路では積層多結晶シリコンによる容量素子(2層ポリキャパシタンス)が多用されている。

そこで、上記半導体基板上に、上記第1ゲート電極と同一材料で同時に形成された第1容量素子電極と、上記第1容量素子電極上に絶縁膜を介して上記第2ゲート電極と同一材料で同時に形成された第2容量素子電極をもつ容量素子をさらに備えている例を挙げることができる。

【発明の効果】

【0041】

本発明の半導体装置では、MOSトランジスタについて、ドレイン領域は、ゲート絶縁膜及びチャネル領域とは間隔をもって配置された第1ドレイン領域と、第1ドレイン領域とチャネル領域の間に第1ドレイン領域及びチャネル領域に隣接して配置された第2ドレイン領域とからなり、ゲート電極は、ゲート絶縁膜上に形成された第1ゲート電極と、第1ゲート電極上にゲート電極間絶縁膜を介して形成された第2ゲート電極とからなり、第2ゲート電極にはゲート電圧を与えるためのゲート配線が接続されており、第1ゲート電極にはゲート配線は接続されておらず、半導体基板表面にゲート絶縁膜よりも厚い厚みをもつフィールド絶縁膜を備え、フィールド絶縁膜は少なくともゲート絶縁膜と第1ドレイン領域の間の半導体基板表面に配置されており、第1ゲート電極のドレイン領域側の端部はフィールド絶縁膜上に配置されているようにしたので、ゲート絶縁膜に印加される電圧をゲート配線に印加されるゲート電圧よりも小さくすることができるので、厚いゲート絶縁膜を用いることなく、ゲート電極に高いゲート電圧が高印加される高耐圧デバイスに適用することができる。

【0042】

また、第2ゲート電極の端部は、上方から見て、第1ゲート電極上のみに配置されており、第1ゲート電極の端部及び側面を覆い、かつ第2ゲート電極とは間隔をもって配置された、第2ゲート電極と同一材料で同時に形成されたパターンが形成されているようにすれば、第2ゲート電極を形成するための材料の加工残渣が第1ゲート電極の側面に形成されるのを防止して、その加工残渣に起因する不具合、例えば配線部の電気的ショートなどを防止することができる。

【0043】

また、上方から見て、第2ゲート電極の端部の一部分又は全部が第1ゲート電極の端部よりも外側に配置されており、第1ゲート電極の端部よりも外側に配置されている第2ゲート電極部分はフィールド絶縁膜上に配置されており、かつ第1ゲート電極とは前記ゲート電極間絶縁膜を介しているようにすれば、第1ゲート電極の側面を用いて第1ゲート電極、第2ゲート電極間の容量値を調整することができる。

【0044】

さらに、上方から見て、第2ゲート電極の端部の全部が第1ゲート電極の端部よりも外側に配置されており、第2ゲート電極は第1ゲート電極の端部及び側面を覆っているようにすれば、第2ゲート電極を形成するための材料の加工残渣が第1ゲート電極の側面に形成されるのを防止して、その加工残渣に起因する不具合、例えば配線部の電気的ショートなどを防止することができる。

【0045】

さらに、第2ゲート電極の端部の全部が第1ゲート電極の端部よりも外側に配置されている構成において、上方から見て、第1ゲート電極上で第1ゲート電極の端部とは間隔をもつ位置に第2ゲート電極が形成されていない領域が存在しているようにすれば、第2ゲート電極を形成するための材料の加工残渣が第1ゲート電極の側面に形成されるのを防止しつつ、第1ゲート電極上全面に第2ゲート電極が形成されている場合に比べて第1ゲート電極、第2ゲート電極間の容量値を大きくすることができる。

【0046】

また、第1ゲート電極と第2ゲート電極の間の容量値が互いに異なる複数のMOSトランジスタを備えているようにすれば、互いに異なる動作電圧をもつ複数のMOSトランジスタを同一半導体基板上に混載することができる。

この場合、上記複数のMOSトランジスタにおいて、第2ゲート電極のレイアウト面積のみが互いに異なっているようにすれば、製造工程を増加させることなく、互いに異なる動作電圧をもつ複数のMOSトランジスタを形成することができる。

【0047】

また、半導体基板上に、第1ゲート電極と同一材料で同時に形成された第1容量素子電極と、第1容量素子電極上に絶縁膜を介して第2ゲート電極と同一材料で同時に形成された第2容量素子電極をもつ容量素子をさらに備えているようにすれば、アナログ回路への適用が容易になる。

【発明を実施するための最良の形態】

【0048】

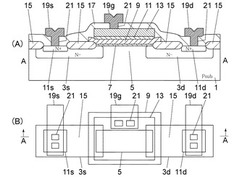

図1は一実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。(A)は(B)のA−A位置での断面である。(B)では上方から見て隠れている部分も実線で記している。(A)では模式的にゲート配線及びゲートコンタクトも図示している。

【0049】

P型の半導体基板(Psub)1の表面側に互いに間隔をもってN−ドレイン領域3dとN−ソース領域3sが形成されている。N−ドレイン領域3dとN−ソース領域3sの間の半導体基板1がチャネル領域5となる。N−ドレイン領域3dとN−ソース領域3sの間の半導体基板1上にゲート絶縁膜7が形成されている。ゲート絶縁膜7は、例えば、酸化シリコン膜からなり、その膜厚は20nmである。図示は省略するが、N−ドレイン領域3d、N−ソース領域3s及びチャネル領域5が形成されている領域の半導体基板1にはP型ウエル領域が形成されている。

【0050】

ゲート絶縁膜7上に第1ゲート電極9が形成されている。第1ゲート電極9は、例えば、多結晶シリコン膜からなり、その膜厚は300nmである。

第1ゲート電極9上にゲート電極間絶縁膜11を介して第2ゲート電極13が形成されているゲート電極間絶縁膜11は、例えば、酸化シリコン膜からなり、その膜厚は20nmである。第2ゲート電極13は、例えば、多結晶シリコン膜からなり、その膜厚は300nmである。

【0051】

N−ドレイン領域3dの表面側に、N−ドレイン領域3dの端部とは間隔をもってN+ドレイン領域11dが形成されている。N−ソース領域3sの表面側に、N−ソース領域3sの端部とは間隔をもってN+ソース領域11sが形成されている。N+ドレイン領域11d及びN+ソース領域11sはN−ドレイン領域3d及びN−ソース領域3sよりも濃いN型不純物濃度をもっている。このように、ドレイン領域及びソース領域は二重拡散構造を備えている。

【0052】

半導体基板1の表面に、LOCOSオフセットトランジスタの形成領域を画定するためのLOCOS酸化膜(フィールド絶縁膜)15が形成されている。LOCOS酸化膜15はゲート絶縁膜7よりも厚い膜厚をもち、その膜厚は例えば500nmである。LOCOS酸化膜15は、N−ドレイン領域3dのチャネル領域5側の端部とN+ドレイン領域11dの間のN−ドレイン領域3d表面、及びN−ソース領域3sのチャネル領域5側の端部とN+ソース領域11sの間のN−ソース領域3s表面にも形成されている。第1ゲート電極9の端部はLOCOS酸化膜15上に配置されている。また、第1ゲート電極9のN+ドレイン領域11d側の端部及びN+ソース領域11s側の端部は、上方から見て、それぞれN+ドレイン領域11d、N+ソース領域11sとは間隔をもって配置されている。

【0053】

第1ゲート電極9、第2ゲート電極13、N+ドレイン領域11d、N+ソース領域11s及びLOCOS酸化膜15上を覆って半導体基板1上に酸化シリコン膜系絶縁膜17が形成されている。酸化シリコン膜系絶縁膜17上に金属材料、例えばアルミニウムからなるゲート配線19g、ドレイン配線19d及びソース配線19sが形成されている。酸化シリコン膜系絶縁膜17に形成された接続孔21を介して、ゲート配線19gは第2ゲート電極13に接続され、ドレイン配線19dはN+ドレイン領域11dに接続され、ソース配線19sはN+ソース領域11sに接続されている。ゲート配線19gは第1ゲート電極9には接続されていない。

【0054】

図2〜図7は、図1に示したLOCOSオフセットトランジスタを形成するための製造工程の一例を順に示す図であり、各図において(A)は断面図、(B)は平面図を示し、(A)は(B)のA−A位置での断面である。(B)では上方から見て隠れている部分も実線で記している。図1〜図7を参照して製造工程の一例を説明する。

【0055】

P型半導体基板1に図示しないP型ウエル領域を形成した後、写真製版技術を用いてレジストパターン(図示は省略)を形成し、それをマスクとしてリンを注入エネルギーは100KeV、ドーズ量は2.0×1013cm-2の条件でイオン注入する。レジストパターンを除去した後、温度1000℃、30分間の窒素雰囲気にさらすことで注入されたリンが拡散及び活性化し、低濃度なN−ドレイン領域3d及びN−ソース領域3sが形成される(図2参照。)。

【0056】

既存の素子分離形成技術を用いてLOCOS酸化膜15を膜厚500nmで形成する(図3参照。)。

ゲート絶縁膜7を膜厚20nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして、異方性ドライエッチング技術により、多結晶シリコン膜及びゲート絶縁膜7を順次エッチング除去して多結晶シリコン膜からなる第1ゲート電極9を形成し、第1ゲート電極9下のみにゲート絶縁膜7を形成する。その後、レジストパターンの除去を行なう(図4参照。)。第1ゲート電極9の端部はLOCOS酸化膜15上に配置されている。ここで、ゲート絶縁膜7のエッチング除去はウェットエッチング技術により行なってもよい。

【0057】

第1ゲート電極9の表面にゲート電極間絶縁膜11を膜厚20nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして、異方性ドライエッチング技術により、多結晶シリコン膜及びゲート電極間絶縁膜11を順次エッチング除去して多結晶シリコン膜からなる第2ゲート電極13を形成し、第2ゲート電極13下のみにゲート電極間絶縁膜11を形成する。その後、レジストパターンの除去を行なう(図5参照。)。上方から見て、第2ゲート電極13の端部は第1ゲート電極9上に配置されている。ここで、ゲート電極間絶縁膜11のエッチング除去はウェットエッチング技術により行なってもよい。

【0058】

LOCOSオフセットトランジスタの形成領域に開口をもつレジストパターンを形成した後、ヒ素を注入エネルギー30KeV、ドーズ量5.0×1015cm-2の条件でイオン注入する。レジストパターンを除去した後、温度900℃、30分間の窒素雰囲気にさらすことで注入されたヒ素が拡散及び活性化し、高濃度なN+ドレイン領域11d及びN+ソース領域11sが形成される(図6参照。)。N+ドレイン領域11dとその周りを覆う低濃度なN−ドレイン領域3dがドレイン領域を構成し、N+ソース領域11sとその周りを覆う低濃度なN−ソース領域3sがソース領域を構成する。

【0059】

半導体基板1上全面に酸化シリコン膜系絶縁膜17、例えばNSG(Non-doped Silicate Glass)膜とBPSG(Boro-phospho Silicate Glass )膜の積層膜を1000nmの膜厚に堆積する。レジストパターンを形成した後、そのレジストパターンをマスクとして所定の位置の酸化シリコン膜系絶縁膜17をエッチング除去し、N+ドレイン領域11d、N+ソース領域11s、第2ゲート電極13に対応する位置に接続孔21を形成する(図7参照。)。

【0060】

酸化シリコン膜系絶縁膜17上に例えばアルミニウム系金属膜を形成し、その金属膜をパターニングして、ゲート配線19g、ドレイン配線19d及びソース配線19sを形成する(図1参照。)。

【0061】

この実施例では、(1)ドレイン領域及びソース領域が二重拡散構造を備えていること、(2)第1ゲート電極9の端部がゲート絶縁膜7よりも厚いLOCOS酸化膜15上に配置されていること、の2つの特徴を備えているのでドレイン領域及びソース領域は高電圧に耐えることができる。

【0062】

さらに、第1ゲート電極9上にゲート電極間絶縁膜11を介して第2ゲート電極13を備え、積層構造のゲート電極となっていることから、第2ゲート電極13に印加されるゲート電圧がゲート電極間絶縁膜11とゲート絶縁膜7に分圧される。これにより、ゲート電極も高電圧に耐えることができる。これを図1と図8を参照して説明する。

【0063】

図8は第2ゲート電極13に印加されるゲート電圧がゲート電極間絶縁膜11とゲート絶縁膜7に分圧されることを説明するための図である。(A)はゲート電極の回路図と、ゲート絶縁膜7、ゲート電極間絶縁膜11に与えられる電圧V1,V2を表す式である。(B)は第1ゲート電極9と半導体基板1との間の容量値をC1、第2ゲート電極13と第1ゲート電極9の間の容量値をC2としたときの容量値C1,C2の容量値比に対する電圧V1,V2を示す表である。

【0064】

第1ゲート電極9と半導体基板1との間の容量値をC1、第2ゲート電極13と第1ゲート電極9の間の容量値をC2とすると、ゲート絶縁膜7にかかる電圧V1とゲート電極間絶縁膜11にかかる電圧V2は図8中の式のようになる。

仮にC1=C2とすると、第2ゲート電極13にかかる電圧V1は、第2ゲート電極13に印加されるゲート電圧(Vdd)に対して半分に低減される。このことはゲート絶縁膜厚としては従来の半分ですむことを示している。すなわち厚いゲート絶縁膜を長時間の熱処理で形成することなく、ゲート電極に高耐圧機能をもたせることが可能となる。

【0065】

この実施例ではゲート電極間絶縁膜11を酸化シリコン膜から構成される単層膜としたが、ゲート電極間絶縁膜は例えば酸化シリコン膜/窒化シリコン膜/酸化シリコン膜から構成される積層膜、いわゆるONO膜であってもよい。一般的にONO膜のほうが酸化シリコン単層膜よりも絶縁耐性が高いので第2ゲート電極13に印加される電圧値の大部分を担わせることにつながる。つまり、ゲート絶縁膜7にかかる電圧を低く押さえることができるわけである。しかもこの時、ゲート絶縁膜7は酸化シリコン膜のまま形成できるので、ホットキャリアの捕獲による電気特性のシフトの問題は原理的に発生しない。

【0066】

ゲート絶縁膜7にかかる電圧V1は図8中に示した計算式から算出することができる。ここでゲート電極間絶縁膜11をONO膜にすることで絶縁耐性の向上、つまりは分圧電圧V2の増大化が可能になる。これを積極利用することを説明する。すなわち、C2をC1に対して小さく設定する。例えばC2=C1/3にすると図8の計算結果表からVdd=28Vの時、V2=21V、V1=7Vとなり、駆動電圧Vdd=28Vの高電圧環境下でありながらゲート絶縁膜7には7Vしか印加されない。

【0067】

また、図9に示すように、半導体基板1、第1ゲート電極9間のゲート絶縁膜7の面積を第1ゲート電極9、第2ゲート電極13間のゲート電極間絶縁膜9の面積よりも小さくすることにより、C2を下げることができる。このように、半導体基板1、第1ゲート電極9間のゲート絶縁膜7の面積と、第1ゲート電極9、第2ゲート電極13間のゲート電極間絶縁膜9の面積の比率を調整することにより、第2ゲート電極13に印加されるゲート電圧に対してゲート絶縁膜7にかかる電圧を制御することができる。

【0068】

また、ゲート絶縁膜7とゲート電極間絶縁膜11の膜厚を調整することによっても、容量値C1,C2を制御することができ、ゲート絶縁膜7にかかる電圧を所望の値に設定することもできる。

このように、第2ゲート電極13に印加されるゲート電圧に対してゲート絶縁膜7にかかる電圧は、ゲート絶縁膜7とゲート電極間絶縁膜11の膜の種類、ゲート絶縁膜7とゲート電極間絶縁膜11の面積、ゲート絶縁膜7とゲート電極間絶縁膜11の膜厚によって制御することができる。

【0069】

図1に示した実施例の製造工程では、第1ゲート電極9を形成した後に、半導体基板1上全面にゲート電極間絶縁膜11を介して多結晶シリコン膜を形成し、その多結晶シリコン膜を異方性ドライエッチング技術によりパターニングして第2ゲート電極13を形成するので、図10に示すように、第1ゲート電極9の側面に多結晶シリコン加工残渣23((B)ではシボで示す)が形成されることがある。多結晶シリコン加工残渣23は第1ゲート電極9及びN−領域3d,3sとはゲート電極間絶縁膜11と同一材料で同時に形成された絶縁膜パターンを介して形成される。

【0070】

この実施例では、多結晶シリコン加工残渣23はLOCOS酸化膜15上に形成され、かつ第1ゲート電極9及び第2ゲート電極13とは絶縁されているので、多結晶シリコン加工残渣23がトランジスタ動作に悪影響を与えることはない。なお、図48に示すように、本願発明の積層ゲート電極構造を通常のMOSトランジスタに適用した場合、N+領域11d,11sを形成するためのイオン注入時に多結晶シリコン加工残渣23が遮蔽物になり、図中符号Xの部分にイオンが注入されないので、上方から見てN+領域11d,11sが第1ゲート電極9とは間隔をもって形成されてしまう。したがって、通常のMOSトランジスタ構造では、本願発明の積層ゲート電極構造を採用することができない。

【0071】

図10に示した実施例において、多結晶シリコン加工残渣23はトランジスタ動作に悪影響を与えるものではないが、製造工程中に多結晶シリコン加工残渣23が剥がれて半導体基板上で移動すると、多結晶シリコン加工残渣23はいわゆる異物となり、例えば配線部の電気的ショート、ひいては歩留まりの低下を招くことが考えられる。

次に、多結晶シリコン加工残渣23が発生しない実施例を説明する。

【0072】

図11はさらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。(A)は(B)のA−A位置での断面である。(B)では上方から見て隠れている部分も実線で記している。(A)では模式的にゲート配線及びゲートコンタクトも図示している。図1と同じ機能を果たす部分には同じ符号を付す。

【0073】

この実施例では、上方から見て、第2ゲート電極13の端部の全部が第1ゲート電極9の端部よりも外側に配置されて、第2ゲート電極13は第1ゲート電極9の側面を覆っている。第1ゲート電極9の端部よりも外側に配置されている第2ゲート電極13の部分はLOCOS酸化膜15上に配置されている。第1ゲート電極9と第2ゲート電極13の間にはゲート電極間絶縁膜11が形成されている。

【0074】

第2ゲート電極13は第1ゲート電極9の側面を覆っているので、第2ゲート電極13を形成するための多結晶シリコン膜を異方性ドライエッチング技術によりパターニングする際に第2ゲート電極13の側面に多結晶シリコン加工残渣23(図10参照。)が形成されることはない。これにより、多結晶シリコン加工残渣23に起因する不具合を防止することができる。

【0075】

さらに、第1ゲート電極9の端部よりも外側に配置されている第2ゲート電極13の部分はLOCOS酸化膜15上に配置されているので、第2ゲート電極13に印加されるゲート電圧がゲート絶縁膜7に直接影響を与えることはない。すなわち、高耐圧機能を保持することができる。

【0076】

さらに、第1ゲート電極9の側面も使って第1ゲート電極9、第2ゲート電極13間の容量値を調整することができるので、設計の自由度が増す。

【0077】

図11に示した実施例では、第1ゲート電極9上全面に第2ゲート電極13が配置されているが、本発明はこれに限定されるものではない。

図12はさらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。(A)は(B)のA−A位置での断面である。(B)では上方から見て隠れている部分も実線で記している。(A)では模式的にゲート配線及びゲートコンタクトも図示している。図1、図11と同じ機能を果たす部分には同じ符号を付す。(B)では第2電極をシボで示した。

【0078】

この実施例では、図11に示した実施例と比較して、第1ゲート電極9上で第1ゲート電極9の端部とは間隔をもつ位置に第2ゲート電極13が形成されていない領域が存在している。これにより、図11に示した実施例に比べて第1ゲート電極9、第2ゲート電極13間の容量値を大きくすることができる。

また、第1ゲート電極9上で第2ゲート電極13が形成されていない領域の面積を調整することにより、第1ゲート電極9、第2ゲート電極13間の容量値を任意の値に設定することもできる。

【0079】

図12に示した実施例では、第1ゲート電極9上で第2ゲート電極13が形成されていない領域は1箇所の矩形であるが、本発明はこれに限定されるものではなく、当該領域は1ゲート電極9上で複数個所に設けられていてもよいし、当該領域の平面形状は例えば円形など、矩形以外の形状であってもよい。

【0080】

また、図11及び図12に示した各実施例では、上方から見て第2ゲート電極13の端部の全部が第1ゲート電極9の端部よりも外側に配置されているが、図13に示すように、上方から見て第2ゲート電極13の端部の一部分が第1ゲート電極9の端部よりも外側に配置されているようにしてもよい。図13(B)では第2ゲート電極13及び多結晶シリコン加工残渣23をシボで示した。

【0081】

図13に示した実施例では、多結晶シリコン加工残渣23の発生はある程度許容しながら、同時に第1ゲート電極9、第2ゲート電極13間の容量値を図11に示した実施例に比べて小さくすることができる。このような構造は、多結晶シリコン加工残渣23に起因する不具合の懸念が小さい用途であって、かつ、ゲート絶縁膜7に印加される電圧を低くしたい場合に有効である。

【0082】

図14はさらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。(A)は(B)のA−A位置での断面である。(B)では上方から見て隠れている部分も実線で記している。(A)では模式的にゲート配線及びゲートコンタクトも図示している。図1と同じ機能を果たす部分には同じ符号を付す。

【0083】

この実施例では、図1に示した実施例と同様に、第2ゲート電極13は第1ゲート電極9上のみに形成されている。そして、上方から見て第2ゲート電極13の端部は第1ゲート電極9の端部とは間隔をもって配置されている。

【0084】

この実施例が図1に示した実施例と異なる点は、絶縁膜パターン25を介して第1ゲート電極9の端部及び側面を覆い、かつ第2ゲート電極13とは間隔をもって配置された、第2ゲート電極13と同一材料で同時に形成された多結晶シリコンパターン27が形成されている点である。多結晶シリコンパターン27は、第2ゲート電極13とは間隔をもって配置されているので、第2ゲート電極13とは絶縁されている。絶縁膜パターン25はゲート電極間絶縁膜11と同一材料で同時に形成されたものである。

この実施例によれば、多結晶シリコン加工残渣23(図10参照。)を発生させることなく、第1ゲート電極9、第2ゲート電極13間の容量値を小さくすることができる。

【0085】

上記実施例では、第1ゲート電極9のドレイン領域側の端部及びソース領域側の端部の両方がLOCOS酸化膜15上に配置されているが、図15に示すように、第1ゲート電極9のドレイン領域側の端部のみがLOCOS酸化膜15上に配置されているようにしてもよい。

また、上記実施例では、ドレイン領域及びソース領域の両方が二重拡散構造を備えているが、図16に示すように、ドレイン領域のみが二重拡散構造を備えているようにしてもよい。

【0086】

図9〜図16に示した各実施例は、図1〜図7を参照して説明した製造工程例で用いるレイアウト形状(フォトマスクのCADデータ)を変更することにより形成することができる。

【0087】

ところで、従来構造のLOCOSオフセットトランジスタを用いて、複数のゲート電圧値向けのLOCOSオフセットトランジスタを1つの半導体基板に混載する場合、複数の問題点が生じる。

図49に示すように、例えば3種類のゲート電圧値に対応した3種類のLOCOSオフセットトランジスタを混載している場合、それらのLOCOSオフセットトランジスタでゲート絶縁膜51−1,51−2,51−3の膜厚をそれぞれ異ならせる必要があった。すなわち、ゲート電圧Vdd=30Vの電圧で動作可能なトランジスタ(1)ではゲート絶縁膜51−1の膜厚を80nmに、ゲート電圧Vdd=22.5Vの電圧で動作可能なトランジスタ(2)ではゲート絶縁膜51−2の膜厚を50nmに、ゲート電圧Vdd=15Vの電圧で動作可能なトランジスタ(3)ではゲート絶縁膜51−3の膜厚を30nmにするなど、各電圧帯に応じたゲート絶縁膜をそれぞれ形成する必要があった。3種類の異なる膜厚のゲート絶縁膜を一つの半導体基板に形成するためにはプロセスフローの長時間化の問題、マスクセットの作成枚数の増加の問題、前述のフィールド絶縁膜の膜減りの問題(図47参照。)など、解決すべき課題が極めて多い。これについての詳細は特許文献3を参照されたい。

【0088】

これに対して、本願発明を構成するLOCOSオフセットトランジスタでは、半導体基板、第1ゲート電極間の容量値と第1ゲート電極、第2ゲート電極間の容量値を調整することによってゲート絶縁膜にかかる電圧を制御することができるので、複数種類のゲート電圧値に対応した複数種類のLOCOSオフセットトランジスタを同一半導体基板上に混載する場合であっても、それらのトランジスタでゲート絶縁膜厚を互いに異ならせることなく、すなわち同一膜厚のゲート絶縁膜のままを用いて、動作電圧帯が互いに異なる複数種類のトランジスタを同一半導体基板上に混載することができる。図17を参照して、動作電圧帯が互いに異なる3種類のLOCOSオフセットトランジスタを同一半導体基板上に混載した実施例を説明する。

【0089】

図17はさらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図、(C)はゲート電圧に対する各トランジスタの設定例を示す表である。(A)は(B)のA−A位置での断面である。(B)では上方から見て隠れている部分も実線で記している。(A)では模式的にゲート配線及びゲートコンタクトも図示している。図1と同じ部分には同じ符号を付す。

この実施例では、ゲート電圧Vdd=30Vの電圧で動作可能なトランジスタ(1)と、ゲート電圧Vdd=22.5Vの電圧で動作可能なトランジスタ(2)と、ゲート電圧Vdd=15Vの電圧で動作可能なトランジスタ(3)を同一半導体基板1上に備えている。

【0090】

トランジスタ(1),(2),(3)において、第2ゲート電極13−1,13−2,13−3のレイアウト面積が互いに異なっている。それ以外に部分、例えば、半導体基板1に形成されたP型ウエル領域、ゲート絶縁膜7、第1ゲート電極9、ゲート電極間絶縁膜11に関しては、その形状、不純物濃度、膜厚などは3つのトランジスタ(1),(2),(3)で同じになっている。なお、ゲート電極間絶縁膜11の平面形状は、第2ゲート電極13−1,13−2,13−3の平面形状が互いに異なっているにともなって、トランジスタ(1),(2),(3)で互いに異なっている。

【0091】

つまり、トランジスタ(1),(2),(3)において、第1ゲート電極9と半導体基板1(P型ウエル領域)との間の容量値=C1は同じであり、第1ゲート電極9と第2ゲート電極13の間の容量値=C2が互いに異なっている。具体的にはゲート電圧Vdd=30Vの電圧で動作可能なトランジスタ(1)はC2=C1/3に、ゲート電圧Vdd=22.5Vの電圧で動作可能なトランジスタ(2)はC2=C1/2に、ゲート電圧Vdd=15Vの電圧で動作可能なトランジスタ(3)はC2=C1になるように調整してある。これにより、前述の図8の計算式に従うと、ゲート絶縁膜7にかかる電圧は3つのトランジスタ(1),(2),(3)で全て7.5Vとなる。すなわち、膜厚、材料及び形成時期が同一のゲート絶縁膜7を用いて印加電圧が30Vと22.5Vと15Vの3種類の動作電圧帯に対応可能なワンチップLSIを得ることができる。

【0092】

さらに、3つのトランジスタ(1),(2),(3)は第2ゲート電極13のレイアウト面積(CADデータ)を互いに異ならせるだけで形成することができるので、製造方法としては前述の図1〜図7を参照して説明した製造工程により形成できる。すなわち、図49を参照して説明したプロセスフローの長時間化の問題やマスクセットの作成枚数増加の問題、フィールド絶縁膜の膜減りの問題などを全て回避することができる。

【0093】

図17に示した実施例では、3つのトランジスタ(1),(2),(3)について、第2ゲート電極13−1,13−2,13−3のレイアウト面積のみを互いに異ならせることにより、動作電圧帯が互いに異なるトランジスタ(1),(2),(3)を形成しているが、LOCOSオフセットトランジスタの動作電圧帯を互いに異ならせる方法は、これに限定されるものではなく、ゲート絶縁膜7、第1ゲート電極9、ゲート電極間絶縁膜11及び第1ゲート電極13について、レイアウト面積、膜厚及び材料のうちの少なくとも1つを互いに異ならせることにより、LOCOSオフセットトランジスタの動作電圧帯を互いに異ならせるようにしてもよい。ただし、図49を参照して説明した上記問題点を考慮すると、複数のLOCOSオフセットトランジスタで第2ゲート電極のレイアウト面積のみを互いに異ならせることにより動作電圧帯を互いに異ならせるようにすることが有利である。

【0094】

また、図17に示した実施例では、3つのトランジスタ(1),(2),(3)は全て15V以上の高電圧に対応したものであるが、本発明を構成するLOCOSオフセットトランジスタは例えば2.5V程度の低電圧で動作可能なトランジスタにも適用することができるので、トランジスタ(1),(2),(3)のうちの1つ、2つ又は全部を、互いに動作電圧帯が異なる低電圧で動作可能なトランジスタにしてもよい。

【0095】

また、図17に示した実施例では、同一半導体基板上に混載されたトランジス(1),(2),(3)は全部LOCOSオフセットトランジスタであるが、本発明を構成するLOCOSオフセットトランジスタと通常のMOSトランジスタを同一半導体基板上に混載することもできる。その実施例を図18を参照して説明する。

【0096】

図18はさらに他の実施例を概略的に示す断面図である。図1と同じ機能を果たす部分には同じ符号を付す。LOCOSオフセットトランジスタの構造は図1に示した実施例と同じなので説明を省略する。

【0097】

半導体基板1のLOCOSオフセットトランジスタ形成領域とは異なる領域に通常のMOSトランジスタが形成されている。

通常のMOSトランジスタは、半導体基板1の表面側に形成されたP型ウエル(図示は省略)に互いに間隔をもって形成されたN+ドレイン領域29d、N+ソース領域29sを備えている。N+ドレイン領域29dとN+ソース領域29sの間の半導体基板1がチャネル領域31となる。チャネル領域31上にゲート絶縁膜33が形成されている。ゲート絶縁膜33はLOCOSオフセットトランジスタのゲート絶縁膜33と同時に形成されたものであり、例えば膜厚が20nmの酸化シリコン膜からなる。

【0098】

ゲート絶縁膜33上にゲート電極35が形成されている。ゲート電極35はLOCOSオフセットトランジスタの第1ゲート電極9と同一材料から同時に形成されたものである。

N+ドレイン領域29d上、N+ソース領域29s上及び第ゲート電極35上を覆って半導体基板1上に酸化シリコン膜系絶縁膜17が形成されている。酸化シリコン膜系絶縁膜17上に金属材料、例えばアルミニウムからなるゲート配線37g、ドレイン配線37d及びソース配線37sが形成されている。酸化シリコン膜系絶縁膜17に形成された接続孔21を介して、ゲート配線37gはゲート電極35に接続され、ドレイン配線37dはN+ドレイン領域29dに接続され、ソース配線37sはN+ソース領域29sに接続されている。

【0099】

図19〜図24は、図18に示したLOCOSオフセットトランジスタ及び通常のMOSトランジスタを形成するための製造工程の一例を順に示す概略的な断面図である。図81〜図19を参照して製造工程の一例を説明する。

【0100】

P型半導体基板1に図示しないP型ウエル領域を形成した後、写真製版技術を用いてレジストパターン(図示は省略)を形成し、それをマスクとしてリンを注入エネルギーは100KeV、ドーズ量は2.0×1013cm-2の条件でイオン注入する。レジストパターンを除去した後、温度1000℃、30分間の窒素雰囲気にさらすことで注入されたリンが拡散及び活性化し、低濃度なN−ドレイン領域3d及びN−ソース領域3sが形成される(図19参照。)。

【0101】

既存の素子分離形成技術を用いてLOCOS酸化膜15を膜厚500nmで形成する(図20参照。)。

ゲート絶縁膜7,33となる酸化シリコン膜を膜厚20nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして、異方性ドライエッチング技術により、多結晶シリコン膜及び酸化シリコン膜を順次エッチング除去して多結晶シリコン膜からなる第1ゲート電極9及びゲート電極35を形成し、第1ゲート電極9下にゲート絶縁膜7を形成し、ゲート電極35下にゲート絶縁膜33を形成する。その後、レジストパターンの除去を行なう(図21参照。)。ここで、ゲート絶縁膜7,33を形成するための酸化シリコン膜のエッチング除去はウェットエッチング技術により行なってもよい。

【0102】

ゲート電極間絶縁膜11を膜厚20nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして、異方性ドライエッチング技術により、多結晶シリコン膜及びゲート電極間絶縁膜11を順次エッチング除去して多結晶シリコン膜からなる第2ゲート電極13を形成し、第2ゲート電極13下にゲート電極間絶縁膜11を形成する。このとき、第1ゲート電極9及びゲート電極35の側面に多結晶シリコン加工残渣23が形成される。その後、レジストパターンの除去を行なう(図22参照。)。ここで、ゲート電極間絶縁膜11のエッチング除去はウェットエッチング技術により行なってもよい。

【0103】

通常のMOSトランジスタの形成領域に開口部をもつレジストパターン39を形成する。レジストパターン39をマスクにして、例えば等方性エッチング技術により、ゲート電極35側面の多結晶シリコン加工残渣23を除去する(図23参照。)。

【0104】

LOCOSオフセットトランジスタ及び通常のMOSトランジスタの形成領域に開口をもつレジストパターンを形成した後、ヒ素を注入エネルギー30KeV、ドーズ量5.0×1015cm-2の条件でイオン注入する。レジストパターンを除去した後、温度900℃、30分間の窒素雰囲気にさらすことで注入されたヒ素が拡散及び活性化し、高濃度なN+ドレイン領域11d、N+ソース領域11s、N+ドレイン領域29d及びN+ソース領域29sが形成される(図24参照。)。

【0105】

半導体基板1上全面に酸化シリコン膜系絶縁膜17を1000nmの膜厚に堆積する。レジストパターンを形成した後、そのレジストパターンをマスクとして所定の位置の酸化シリコン膜系絶縁膜17をエッチング除去し、N+ドレイン領域11d、N+ソース領域11s、第2ゲート電極13、N+ドレイン領域29d、N+ソース領域29s、ゲート電極35に対応する位置に接続孔21を形成する。酸化シリコン膜系絶縁膜17上に例えばアルミニウム系金属膜を形成し、その金属膜をパターニングして、ゲート配線19g、ドレイン配線19d、ソース配線19s、ゲート配線37g、ドレイン配線37d及びソース配線37sを形成する(図18参照。)。

【0106】

この実施例では、LOCOSオフセットランジスタについて図8に示したようにゲート電圧の分割を行なうことによりゲート絶縁膜7にかかる電圧を小さくすることができるので、ゲート絶縁膜7と通常のトランジスタのゲート絶縁膜33を同一材料で同じ膜厚で同時に形成することができる。すなわち、通常のトランジスタのゲート絶縁膜33と同じ特性のゲート絶縁膜7を用いて高電圧対応可能なLOCOSオフセットトランジスタを形成することができる。

【0107】

さらに、この実施例では、LOCOSオフセットトランジスタのゲート絶縁膜7と通常のトランジスタのゲート絶縁膜33は同時に形成されたものであるので、LOCOSオフセットトランジスタと通常のトランジスタを同一半導体基板上に混載する場合にプロセスフローの簡略化を実現できるので、プロセスフローの長時間化の上記問題点が生じない。さらにLOCOSオフセットトランジスタの第1ゲート電極9と通常のトランジスタのゲート電極35は同時に形成されたものであるのでプロセスフローの簡略化を実現できる。

【0108】

図25はさらに他の実施例を概略的に示す断面図である。この実施例は、LOCOSオフセットトランジスタの形成領域とは異なる半導体基板1の位置に、第1ゲート電極と同一材料で同時に形成された第1容量素子電極と、第1容量素子電極上に絶縁膜を介して第2ゲート電極と同一材料で同時に形成された第2容量素子電極をもつ容量素子をさらに備えているものである。図1と同じ機能を果たす部分には同じ符号を付す。LOCOSオフセットトランジスタの構造は図1に示した実施例と同じなので説明を省略する。

【0109】

LOCOSオフセットトランジスタの形成領域とは異なる半導体基板1の位置に、LOCOS酸化膜15を介して容量素子が形成されている。この容量素子は、LOCOS酸化膜15上に形成された第1容量素子電極41uと、第1容量素子電極41上に容量素子電極間絶縁膜43を介して形成された第2容量素子電極41tを備えている。第1容量素子電極41uは第1ゲート電極9と同一材料で同時に形成されたものである。容量素子電極間絶縁膜43はゲート電極間絶縁膜11と同一材料で同時に形成されたものである。第2容量素子電極41tは第2ゲート電極13と同一材料で同時に形成されたものである。

【0110】

酸化シリコン膜系絶縁膜17はた第1容量素子電極41u及び第2容量素子電極41tも覆っている。酸化シリコン膜系絶縁膜17上にゲート配線19g、ドレイン配線19d及びソース配線19sと同一材料で同時に形成された第1容量素子電極配線45uと第2容量素子電極配線45tが形成されている。酸化シリコン膜系絶縁膜17に形成された接続孔21を介して、第1容量素子電極配線45uは第1容量素子電極41uに接続され、第2容量素子電極配線45tは第2容量素子電極41tに接続されている。

【0111】

図26〜図31は、図25に示したLOCOSオフセットトランジスタ及び容量素子を形成するための製造工程の一例を順に示す断面図である。図25〜図31を参照して製造工程の一例を説明する。

【0112】

P型半導体基板1に図示しないP型ウエル領域を形成した後、写真製版技術を用いてレジストパターン(図示は省略)を形成し、それをマスクとしてリンを注入エネルギーは100KeV、ドーズ量は2.0×1013cm-2の条件でイオン注入する。レジストパターンを除去した後、温度1000℃、30分間の窒素雰囲気にさらすことで注入されたリンが拡散及び活性化し、低濃度なN−ドレイン領域3d及びN−ソース領域3sが形成される(図26参照。)。

【0113】

既存の素子分離形成技術を用いてLOCOS酸化膜15を膜厚500nmで形成する(図27参照。)。

ゲート絶縁膜7を膜厚20nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして、異方性ドライエッチング技術により、多結晶シリコン膜及びゲート絶縁膜7を順次エッチング除去して多結晶シリコン膜からなる第1ゲート電極9と第1容量素子電極41uを形成し、第1ゲート電極9下にゲート絶縁膜7を形成する。ここで第1容量素子電極41u下にゲート絶縁膜7が残存するが図示は省略している。その後、レジストパターンの除去を行なう(図28参照。)。

【0114】

ゲート電極間絶縁膜11及び容量素子電極間絶縁膜43形成するための酸化シリコン膜を膜厚20nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして、異方性ドライエッチング技術により、多結晶シリコン膜及び酸化シリコン膜を順次エッチング除去して、第1ゲート電極9上に第2ゲート電極13及びゲート電極間絶縁膜11を形成し、第1容量素子電極41u上に第2容量素子電極41t及び容量素子電極間絶縁膜43を形成する。ここで、第1ゲート電極9側面及び第1容量素子電極41u側面に多結晶シリコン加工残渣23(図10参照。)が形成されることがあるが、図示は省略する。なお、第1容量素子電極41u側面に多結晶シリコン加工残渣23が形成されても、多結晶シリコン加工残渣23はLOCOS酸化膜15上に形成されるので、容量素子の電気的特性に悪影響を与えることはない。その後、レジストパターンの除去を行なう(図29参照。)。

【0115】

LOCOSオフセットトランジスタの形成領域に開口をもつレジストパターンを形成した後、ヒ素を注入エネルギー30KeV、ドーズ量5.0×1015cm-2の条件でイオン注入する。レジストパターンを除去した後、温度900℃、30分間の窒素雰囲気にさらすことで注入されたヒ素が拡散及び活性化し、高濃度なN+ドレイン領域11d及びN+ソース領域11sが形成される(図30参照。)。

【0116】

半導体基板1上全面に酸化シリコン膜系絶縁膜17、例えばNSG膜とBPSG膜の積層膜を1000nmの膜厚に堆積する。レジストパターンを形成した後、そのレジストパターンをマスクとして所定の位置の酸化シリコン膜系絶縁膜17をエッチング除去し、N+ドレイン領域11d、N+ソース領域11s、第2ゲート電極13、第1容量素子電極41u、第2容量素子電極41tに対応する位置に接続孔21を形成する(図31参照。)。

【0117】

酸化シリコン膜系絶縁膜17上に例えばアルミニウム系金属膜を形成し、その金属膜をパターニングして、ゲート配線19g、ドレイン配線19d、ソース配線19s、第1容量素子電極配線45u、第2容量素子電極配線45tを形成する(図25参照。)。

【0118】

この実施例では、容量素子は、第1ゲート電極9と同一材料で同時に形成された第1容量素子電極41uと、ゲート電極間絶縁膜11と同一材料で同時に形成された容量素子電極間絶縁膜43と、第2ゲート電極13と同一材料で同時に形成された第2容量素子電極41tによって形成されているので、LOCOSオフセットトランジスタの製造工程を増加させることなく、同一半導体基板1上に容量素子を混載することができる。

【0119】

この実施例では、容量素子において、上方から見て第2容量素子電極41tの端部は第1容量素子電極41uの端部の内側に配置されているが、第1容量素子電極41uと第2容量素子電極41のレイアウト位置はこれに限定されるものではない。

例えば、図12や図14に示したLOCOSオフセットトランジスタの第1ゲート電極9及び第2ゲート電極13のレイアウト位置と同様に、容量素子において、上方から見て第2容量素子電極41tの端部は第1容量素子電極41uの端部の外側に配置されており、かつ第1容量素子電極41uのコンタクトを形成する位置には第2容量素子電極41tが形成されていないようにすれば、第1容量素子電極41uの側面に多結晶シリコン加工残渣23(図10参照。)が形成されるのを防止することができる。

【0120】

また、図13に示したLOCOSオフセットトランジスタの第1ゲート電極9及び第2ゲート電極13のレイアウト位置と同様に、容量素子において、上方から見て第2容量素子電極41tの端部の一部分が第1容量素子電極41uの端部の外側に配置されているようにしてもよい。

【0121】

以上、本発明の実施例を説明したが、本発明はこれらに限定されるものではなく、形状、配置、個数、材料などは一例であり、特許請求の範囲に記載された本発明の範囲内で種々の変更が可能である。

【図面の簡単な説明】

【0122】

【図1】一実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図2】図1に示したLOCOSオフセットトランジスタを形成するための製造工程の一例を説明するための最初の工程を示す図であり、(A)は断面図、(B)は平面図である。

【図3】同製造工程例の続きの工程を示す図であり、(A)は断面図、(B)は平面図である。

【図4】同製造工程例のさらに続きの工程を示す図であり、(A)は断面図、(B)は平面図である。

【図5】同製造工程例のさらに続きの工程を示す図であり、(A)は断面図、(B)は平面図である。

【図6】同製造工程例のさらに続きの工程を示す図であり、(A)は断面図、(B)は平面図である。

【図7】同製造工程例のさらに続きの工程を示す図であり、(A)は断面図、(B)は平面図である。

【図8】第2ゲート電極に印加されるゲート電圧がゲート電極間絶縁膜とゲート絶縁膜に分圧されることを説明するための図であり、(A)はゲート電極の回路図と、ゲート絶縁膜、ゲート電極間絶縁膜に与えられる電圧V1,V2を表す式であり、(B)は第1ゲート電極9半導体基板1の間の容量値をC1、第2ゲート電極131ゲート電極の間の容量値をC2としたときの容量値C1,C2の容量値比に対する電圧V1,V2を示す表である。

【図9】他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図10】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図11】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図12】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図13】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図14】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図15】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図16】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図17】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図、(C)はゲート電圧に対する各トランジスタの設定例を示す表である。

【図18】さらに他の実施例を概略的に示す断面図である。

【図19】図18に示したLOCOSオフセットトランジスタ及び通常のMOSトランジスタを形成するための製造工程の一例を説明するための最初の工程を示す断面図である。

【図20】同製造工程例の続きの工程を示す断面図である。

【図21】同製造工程例のさらに続きの工程を示す断面図である。

【図22】同製造工程例のさらに続きの工程を示す断面図である。

【図23】同製造工程例のさらに続きの工程を示す断面図である。

【図24】同製造工程例のさらに続きの工程を示す断面図である。

【図25】さらに他の実施例を概略的に示す断面図である。

【図26】図25に示したLOCOSオフセットトランジスタ及び容量素子を形成するための製造工程の一例を説明するための最初の工程を示す断面図である。

【図27】同製造工程例の続きの工程を示す断面図である。

【図28】同製造工程例のさらに続きの工程を示す断面図である。

【図29】同製造工程例のさらに続きの工程を示す断面図である。

【図30】同製造工程例のさらに続きの工程を示す断面図である。

【図31】同製造工程例のさらに続きの工程を示す断面図である。

【図32】従来のLOCOSオフセットトランジスタを概略的に示す断面図である。

【図33】図32に示した従来のLOCOSオフセットトランジスタの製造工程の一例を説明するための最初の工程を示す断面図である。

【図34】同製造工程例の続きの工程を示す断面図である。

【図35】同製造工程例のさらに続きの工程を示す断面図である。

【図36】同製造工程例のさらに続きの工程を示す断面図である。

【図37】同製造工程例のさらに続きの工程を示す断面図である。

【図38】Masked−LDDトランジスタを概略的に示す断面図である。

【図39】図38に示したMasked−LDDトランジスタの製造工程の一例を説明するための最初の工程を示す断面図である。

【図40】同製造工程例の続きの工程を示す断面図である。

【図41】同製造工程例のさらに続きの工程を示す断面図である。

【図42】同製造工程例のさらに続きの工程を示す断面図である。

【図43】同製造工程例のさらに続きの工程を示す断面図である。

【図44】厚いゲート絶縁膜を備えたLOCOSオフセットトランジスタを形成する際の不具合を説明するための工程断面図である。

【図45】図44の続きの工程を示す断面図である。

【図46】図45の続きの工程を示す断面図である。

【図47】図46の破線円で囲まれた部分を拡大して示す断面図である。

【図48】本願発明の積層ゲート電極構造を通常のMOSトランジスタに適用した場合の不具合を説明するための断面図である。

【図49】従来構造のLOCOSオフセットトランジスタを用いて、3種類のゲート電圧値に対応した3種類のLOCOSオフセットトランジスタを同一半導体基板に混載した様子を概略的に示す断面図である。

【符号の説明】

【0123】

1 半導体基板

3d N−ドレイン領域

3s N−ソース領域

5 チャネル領域

7 ゲート絶縁膜

9 第1ゲート電極

11 ゲート電極間絶縁膜

13,13−1,13−2,13−3 第2ゲート電極

15 LOCOS酸化膜(フィールド絶縁膜)

19g ゲート配線

27 多結晶シリコンパターン(第2ゲート電極と同一材料で同時形成されたパターン)

41u 第1容量素子電極

41t 第2容量素子電極

43 容量素子電極間絶縁膜

【技術分野】

【0001】

本発明は、第1導電型の半導体基板の表面側に互いに間隔をもって配置された第2導電型のドレイン領域及びソース領域と、ソース領域とドレイン領域の間の半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とをもち、ソース領域とドレイン領域の間の半導体基板がチャネル領域となっているMOSトランジスタを備えた半導体装置に関し、特に、LOCOSオフセットトランジスタに関するものである。

【背景技術】

【0002】

近年の携帯電話器や携帯ゲーム機器の市場拡大に対応して液晶駆動用回路の需要が拡大している。液晶駆動にはバックライト電源などで高い電圧が必要とされるため、そのLSI化には高耐圧トランジスタが必要となる。CMOS(相補型Metal Oxide Semiconductor)型における高耐圧トランジスタの代表的なものとして、MOSトランジスタからなるLOCOS(LOCal Oxidation of Silicon:ロコス)オフセットトランジスタ(例えば特許文献1を参照。)とMasked−LDD(Lightly Doped Drain)トランジスタ(例えば特許文献2を参照。)がある。

【0003】

まず、LOCOSオフセットトランジスタについて説明する。

図32は従来のLOCOSオフセットトランジスタを示す断面図である。

P型の半導体基板1の表面側に互いに間隔をもってN−ドレイン領域3dとN−ソース領域3sが形成されている。N−ドレイン領域3dとN−ソース領域3sの間の半導体基板1がチャネル領域5となる。N−ドレイン領域3dとN−ソース領域3sの間の半導体基板1上にゲート絶縁膜51が形成されている。ゲート絶縁膜51上にゲート電極53が形成されている。図示は省略するが、N−ドレイン領域3d、N−ソース領域3s及びチャネル領域5が形成されている領域の半導体基板1にはP型ウエル領域が形成されている。

【0004】

N−ドレイン領域3dの表面側に、N−ドレイン領域3dの端部とは間隔をもってN+ドレイン領域11dが形成されている。N−ソース領域3sの表面側に、N−ソース領域3sの端部とは間隔をもってN+ソース領域11sが形成されている。

半導体基板1の表面に、LOCOSオフセットトランジスタの形成領域を画定するためのLOCOS酸化膜15が形成されている。LOCOS酸化膜15はゲート絶縁膜51よりも厚い膜厚をもつ。N−ドレイン領域3dのチャネル領域5側の端部とN+ドレイン領域11dの間のN−ドレイン領域3d表面、及びN−ソース領域3sのチャネル領域5側の端部とN+ソース領域11sの間のN−ソース領域3s表面にもLOCOS酸化膜15が形成されている。ゲート電極53の端部はLOCOS酸化膜15上に配置されている。

【0005】

ゲート電極53、N+ドレイン領域11d、N+ソース領域11s及びLOCOS酸化膜15上を覆って半導体基板1上に酸化シリコン膜系絶縁膜17が形成されている。酸化シリコン膜系絶縁膜17上に金属材料からなるゲート配線19g、ドレイン配線19d及びソース配線19sが形成されている。酸化シリコン膜系絶縁膜17に形成された接続孔21を介して、ゲート配線19gはゲート電極53に接続され、ドレイン配線19dはN+ドレイン領域11dに接続され、ソース配線19sはN+ソース領域11sに接続されている。

【0006】

図32〜図37を参照して従来のLOCOSオフセットトランジスタの製造工程を説明する。

P型半導体基板1に図示しないP型ウエル領域を形成した後、写真製版技術を用いてレジストパターン(図示は省略)を形成し、それをマスクとしてリンを注入エネルギーは100KeV(キロエレクトロンボルト)、ドーズ量は2.0×1013cm-2の条件でイオン注入する。レジストパターンを除去した後、温度1000℃、30分間の窒素雰囲気にさらすことで注入されたリンが拡散及び活性化し、低濃度なN−ドレイン領域3d及びN−ソース領域3sが形成される(図33参照。)。

【0007】

既存の素子分離形成技術を用いてLOCOS酸化膜15を膜厚500nm(ナノメートル)で形成する(図34参照。)。

ゲート絶縁膜51を膜厚80nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして多結晶シリコン膜及びゲート絶縁膜51を順次エッチング除去して多結晶シリコン膜からなるゲート電極53を形成し、ゲート電極53下にゲート絶縁膜51を形成する。その後、レジストパターンの除去を行なう(図35参照。)。ゲート電極53の端部はLOCOS酸化膜15上に配置されている。

【0008】

LOCOSオフセットトランジスタの形成領域に開口をもつレジストパターンを形成した後、ヒ素を注入エネルギー30KeV、ドーズ量5.0×1015cm-2の条件でイオン注入する。レジストパターンを除去した後、温度900℃、30分間の窒素雰囲気にさらすことで注入されたヒ素が拡散及び活性化し、高濃度なN+ドレイン領域11d及びN+ソース領域11sが形成される(図36参照。)。N+ドレイン領域11dとその周りを覆う低濃度なN−ドレイン領域3dがドレイン領域を構成し、N+ソース領域11sとその周りを覆う低濃度なN−ソース領域3sがソース領域を構成する。このように、LOCOSオフセットトランジスタではドレイン領域及びソース領域が二重拡散構造を備えている。

【0009】

半導体基板1上全面に酸化シリコン膜系絶縁膜17を1000nmの膜厚に堆積する。レジストパターンを形成した後、そのレジストパターンをマスクとして所定の位置の酸化シリコン膜系絶縁膜17をエッチング除去し、N+ドレイン領域11d、N+ソース領域11s、ゲート電極53に対応する位置に接続孔21を形成する(図37参照。)。

【0010】

酸化シリコン膜系絶縁膜17上にアルミニウム系金属膜を形成し、その金属膜をパターニングして、ゲート配線19g、ドレイン配線19d及びソース配線19sを形成する(図32参照。)。

【0011】

LOCOSオフセットトランジスタは、(1)ドレイン領域及びソース領域が二重拡散構造を備えていること、(2)ゲート電極53の端部がゲート絶縁膜51よりも厚いLOCOS酸化膜15上に配置されていること、の2つの特徴を備えていることで高耐圧化が可能となる。

【0012】

ドレイン領域及びソース領域の耐圧に関して、その耐圧はアバランシェブレイクダウンで決定される。図32に示したように、LOCOSオフセットトランジスタにおいては、N+ドレイン領域11dはN−ドレイン領域3dで囲まれ、N+ソース領域11sはN−ソース領域3sで囲まれているので、濃いN+ドレイン領域11d及びN+ソース領域11sがP型ウエルと直接接することがない。その結果、ドレイン領域及びソース領域のアバランシェブレイクダウン耐圧は30V程度まで向上する。なお、上記(1),(2)のLOCOSオフセットトランジスタの特徴を備えていない通常のMOSトランジスタのドレイン領域及びソース領域のアバランシェブレイクダウン耐圧は10V程度である。

【0013】

また、MOSトランジスタでは、ゲート電極の電位がGND(グラウンド)電位に固定された場合、ゲート電極直下のPN接合部は耐圧が下がることが知られている。この現象をゲート変調接合耐圧と呼び、通常のMOSトランジスタでは10V前後の低い値でブレイクダウンしてしまう。一方、LOCOSオフセットトランジスタでは、図32に示したように、ゲート電極53の端部がLOCOS酸化膜15に乗り上げているので、ゲート電極53と高濃度N+領域11d,11s間の基板垂直方向の距離を大きくすることができ、その結果、ゲート変調接合耐圧が30V程度まで向上する。

【0014】

以上のように、(1)ドレイン領域及びソース領域が高濃度N+領域11d,11sと低濃度N−領域3d,3sの2つの領域で形成されていること、(2)ゲート電極53の端部がLOCOS酸化膜15に乗り上げていること、の2つの構造的工夫を採用することで高耐圧化を実現できるのである。

【0015】

次にMasked−LDDトランジスタについて説明する。

図38はMasked−LDDトランジスタを示す断面図である。

P型の半導体基板1の表面側に互いに間隔をもってN−ドレイン領域3dとN−ソース領域3sが形成されている。N−ドレイン領域3dとN−ソース領域3sの間の半導体基板1上にゲート絶縁膜51が形成されている。ゲート絶縁膜51上にゲート電極53が形成されている。N−ドレイン領域3dとN−ソース領域3sの間の半導体基板1がチャネル領域5となる。図示は省略するが、N−ドレイン領域3d、N−ソース領域3s及びチャネル領域5が形成されている領域の半導体基板1にはP型ウエル領域が形成されている。

【0016】

N−ドレイン領域3dの表面側に、N−ドレイン領域3dの端部とは間隔をもってN+ドレイン領域11dが形成されている。N−ソース領域3sの表面側に、N−ソース領域3sの端部とは間隔をもってN+ソース領域11sが形成されている。すなわち、上方から見て、N+ドレイン領域11及びN+ソース領域11sはゲート電極53とは間隔をもって配置されている。

半導体基板1の表面に、Masked−LDDトランジスタの形成領域を画定するためのLOCOS酸化膜15が形成されている。LOCOS酸化膜15はゲート絶縁膜51よりも厚い膜厚をもつ。Masked−LDDトランジスタの形成領域内にはLOCOS酸化膜15は形成されていない。

【0017】

ゲート電極53、N+ドレイン領域11d、N+ソース領域11s及びLOCOS酸化膜15上を覆って半導体基板1上に酸化シリコン膜系絶縁膜17が形成されている。酸化シリコン膜系絶縁膜17上に金属材料からなるゲート配線19g、ドレイン配線19d及びソース配線19sが形成されている。酸化シリコン膜系絶縁膜17に形成された接続孔21を介して、ゲート配線19gはゲート電極53に接続され、ドレイン配線19dはN+ドレイン領域11dに接続され、ソース配線19sはN+ソース領域11sに接続されている。

【0018】

図38〜図43を参照してMasked−LDDトランジスタの製造工程を説明する。

P型半導体基板1に図示しないP型ウエル領域を形成した後、既存の素子分離形成技術を用いてLOCOS酸化膜15を膜厚500nmで形成する(図39参照。)。

【0019】

ゲート絶縁膜51を膜厚80nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして多結晶シリコン膜及びゲート絶縁膜51を順次エッチング除去して多結晶シリコン膜からなるゲート電極53を形成し、ゲート電極53下にゲート絶縁膜51を形成する。その後、レジストパターンの除去を行なう(図40参照。)。

【0020】

Masked−LDDトランジスタの形成領域に開口をもつレジストパターンを形成した後、リンを注入エネルギー30KeV、ドーズ量2.0×1013cm-2の条件でイオン注入する。レジストパターンを除去した後、温度900℃、30分間の窒素雰囲気にさらすことで注入されたリンが拡散及び活性化し、低濃度なN−ドレイン領域3d及びN−ソース領域3sが形成される(図41参照。)。

【0021】

ゲート電極53と、上方から見てゲート電極53に隣接しているN−ドレイン領域3d及びN−ソース領域3sの一部分を覆うレジストパターンを形成する。そのレジストパターンをマスクとしてヒ素を注入エネルギー30KeV、ドーズ量5.0×1015cm-2の条件でイオン注入する。レジストパターンを除去した後、温度900℃、30分間の窒素雰囲気にさらすことで注入されたヒ素が拡散及び活性化し、高濃度なN+ドレイン領域11d及びN+ソース領域11sが形成される(図42参照。)。N+ドレイン領域11dとその周りを覆う低濃度なN−ドレイン領域3dがドレイン領域を構成し、N+ソース領域11sとその周りを覆う低濃度なN−ソース領域3sがソース領域を構成する。このように、Masked−LDDトランジスタではドレイン領域及びソース領域が二重拡散構造を備えている。

【0022】

このように、ゲート電極53とN−ドレイン領域3d及びN−ソース領域3sの間にLOCOS酸化膜15が介在していないのがMasked−LDDトランジスタの特徴である。この製造工程からわかるように、N−ドレイン領域3d及びN−ソース領域3sの領域はレジストパターンによって確定されている。このような構造のMOSトランジスタは、レジストパターンによって高濃度なヒ素注入が部分的に遮蔽(Mask)されることによって形成されることからMasked−LDDトランジスタと呼ばれている。

【0023】

製造工程の説明を続けると、半導体基板1上全面に酸化シリコン膜系絶縁膜17を1000nmの膜厚に堆積する。レジストパターンを形成した後、そのレジストパターンをマスクとして所定の位置の酸化シリコン膜系絶縁膜17をエッチング除去し、N+ドレイン領域11d、N+ソース領域11s、ゲート電極53に対応する位置に接続孔21を形成する(図43参照。)。

【0024】

酸化シリコン膜系絶縁膜17上にアルミニウム系金属膜を形成し、その金属膜をパターニングして、ゲート配線19g、ドレイン配線19d及びソース配線19sを形成する(図38参照。)。

【0025】

Masked−LDDトランジスタとLOCOSオフセットトランジスタの相違点は、Masked−LDDトランジスタはゲート電極のドレイン領域側の端部及びソース領域側の端部がLOCOS酸化膜に乗り上げていないことである。そして、この相違点を反映して、Masked−LDDトランジスタはLOCOSオフセットトランジスタに比べて対応可能電圧(いわゆる耐圧)が低くなる。その反面、電流駆動能力はMasked−LDDトランジスタの方が大きい。つまり、中程度の高耐圧機能をもたせつつ大電流を流したいような用途にはMasked−LDDトランジスタが適しており、電流駆動能力を犠牲にしても高い電圧を扱いたい用途にはLOCOSオフセットトランジスタが適している、と言える。

【0026】

以上の説明では、ドレイン領域及びソース領域の両方が高耐圧機能をもった場合を説明したが、デバイス仕様によってはドレイン領域のみが高耐圧機能をもっている場合もあり得る。

【0027】

次に、Masked−LDDトランジスタとLOCOSオフセットトランジスタの共通点に着目する。

Masked−LDDトランジスタとLOCOSオフセットトランジスタで共通した点はゲート絶縁膜51の膜厚が80nmと厚いことが上げられる。この膜厚は耐圧30Vを想定した場合であり、要求される耐圧値が30Vよりも高い場合はこの膜厚は更に厚くなる。つまり、ゲート電極にも高い電圧が印加されるので、ゲート絶縁膜の絶縁耐性がそれに耐えうるようにその膜厚を厚くする必要があるわけである。

【0028】

そしてこの点がこれら両デバイスの重要課題となっている。すなわちゲート絶縁膜51の膜厚が80nmと厚いので成膜に必要な処理時間が長時間化してしまうのである。この結果、成膜時の熱処理の影響で、既に形成済のP型ウエルやしきい値電圧(Vth)調整のためのチャネルドープ不純物が再分布してしまう。特にゲート絶縁膜が約50nmより厚くなると酸化時間が極端に長くなるので、完成したデバイスの特性ズレを招いてしまう。このことは高耐圧トランジスタ自身の問題だけではなく、他の素子、例えば容量素子や抵抗素子、或いは、別用途のトランジスタを同一半導体基板に形成する場合は、これらの素子も同様の影響を受けてしまうことになるので、この処理時間が長時間化する問題は複合混載化の最も大きな阻害要因になっている。

【0029】

厚いゲート絶縁膜にはもう一つ大きな問題がある。その問題点を図44から図47を参照して説明する。

従来の高耐圧トランジスタの製造工程では、まず、LOCOS酸化膜15が形成されている半導体基板1上に厚いゲート絶縁膜51を形成し、さらにゲート電極53を形成するための多結晶シリコン膜をウエハ全面に形成する(図44参照。)。次に、レジストパターン(図示は省略)を用いて多結晶シリコン膜をエッチング除去してゲート電極53を形成する(図45参照。)。次に、ウェットエッチング技術を用いてゲート電極53下以外の厚いゲート絶縁膜51を除去した後、イオン注入法によりN+ドレイン領域11dとN+ソース領域11sを形成する(図46参照。)。

【0030】

上記製造工程において、ゲート電極53下以外の厚いゲート絶縁膜51を除去する理由は、図45に示したようにN+ドレイン領域11dとN+ソース領域11sの形成予定領域に厚いゲート絶縁膜51が残存している状態では、N+ドレイン領域11dとN+ソース領域11sを形成するためのイオン注入時に厚いゲート絶縁膜51が遮蔽物になってしまい、N+ドレイン領域11dとN+ソース領域11sを正常には形成できないからである。このため、図46に示したように、N+ドレイン領域11dとN+ソース領域11sの形成予定領域に残存する厚いゲート絶縁膜51をイオン注入前に除去する必要がある。

【0031】

厚いゲート絶縁膜51の除去はウェットエッチングにて実施するのであるが、厚いゲート絶縁膜51の膜厚が80nmと厚いので、厚いゲート絶縁膜51の除去に長時間の処理が必要となり、製造工程が長時間化するという不具合が生じる。

さらに、この除去処理を行なうことで、既に形成済のLOCOS酸化膜15も膜減りするため、LOCOS酸化膜15の端部(図46の破線円内)がくぼみ部55のように形状異常に陥ってしまう(図47参照。)。このことは設計寸法からのズレだけでなく電気特性異常も引き起こす虞れがある。

【0032】

以上のように、厚いゲート絶縁膜を形成することはデバイス形成の上で課題が多数あるわけで、このことが高耐圧トランジスタの形成、更には他の素子との複合混載化を困難なものにしている。

【0033】

【特許文献1】特第3275569号公報

【特許文献2】特開平09−266255号公報

【特許文献3】特開2005−303037号公報

【発明の開示】

【発明が解決しようとする課題】

【0034】

そこで本発明は、厚いゲート絶縁膜を形成することに起因する不具合を生じさせることなく、高耐圧デバイスにも適用可能なMOSトランジスタを備えた半導体装置を提供することを目的とするものである。

【課題を解決するための手段】

【0035】

本発明にかかる半導体装置は、第1導電型の半導体基板の表面側に互いに間隔をもって配置された第2導電型のドレイン領域及びソース領域と、上記ソース領域とドレイン領域の間の上記半導体基板上に形成されたゲート絶縁膜と、上記ゲート絶縁膜上に形成されたゲート電極とをもち、上記ソース領域とドレイン領域の間の上記半導体基板がチャネル領域となっているMOSトランジスタを備えた半導体装置であって、上記ドレイン領域は、上記ゲート絶縁膜及び上記チャネル領域とは間隔をもって配置された第1ドレイン領域と、上記第1ドレイン領域と上記チャネル領域の間に上記第1ドレイン領域及び上記チャネル領域に隣接して配置された第2ドレイン領域とからなり、上記ゲート電極は、上記ゲート絶縁膜上に形成された第1ゲート電極と、上記第1ゲート電極上にゲート電極間絶縁膜を介して形成された第2ゲート電極とからなり、上記第2ゲート電極にはゲート電圧を与えるためのゲート配線が接続されており、上記第1ゲート電極には上記ゲート配線は接続されておらず、上記半導体基板表面に上記ゲート絶縁膜よりも厚い厚みをもつフィールド絶縁膜を備え、上記フィールド絶縁膜は少なくとも上記ゲート絶縁膜と上記第1ドレイン領域の間の上記半導体基板表面に配置されており、上記第1ゲート電極の上記ドレイン領域側の端部は上記フィールド絶縁膜上に配置されているものである。

【0036】

本発明の半導体装置を構成するMOSトランジスタは、ゲート電極として、半導体基板上にゲート絶縁膜を介して形成された第1ゲート電極と、第1ゲート電極上にゲート電極間絶縁膜を介して形成された第2ゲート電極を備えている。そして、ゲート電極にゲート電圧を与えるためのゲート配線は、第2ゲート電極に接続され、第1ゲート電極には接続されていない。この構造において、ゲート電圧に対してゲート電極間絶縁膜にかかる電圧V2とゲート絶縁膜にかかる電圧V1は、第2ゲート電極と第1ゲート電極の間の容量値C2と、第1ゲート電極と半導体基板の間の容量値C1によって決定される。すなわち、ゲート電極に印加されるゲート電圧が高電圧であっても、上記容量値C1とC2を調整することによってゲート絶縁膜にかかる電圧V1を小さくすることができ、厚いゲート絶縁膜を用いることなく、ゲート電極に高いゲート電圧が高印加される高耐圧デバイスに適用することができる。ただし、本発明が適用される半導体装置は、一般に高耐圧と言われる、例えば15V以上の高耐圧をもつMOSトランジスタを備えた半導体装置に限定されるものではなく、低耐圧で高速動作が可能なMOSトランジスタを備えた半導体装置にも適用することができる。

【0037】

本発明の半導体装置において、上記第2ゲート電極の端部は、上方から見て、上記第1ゲート電極上のみに配置されている例を挙げることができる。

さらに、上記第1ゲート電極の端部及び側面を覆い、かつ上記第2ゲート電極とは間隔をもって配置された、上記第2ゲート電極と同一材料で同時に形成されたパターンが形成されているようにしてもよい。

【0038】

また、上方から見て、上記第2ゲート電極の端部の一部分又は全部が上記第1ゲート電極の端部よりも外側に配置されており、上記第1ゲート電極の端部よりも外側に配置されている上記第2ゲート電極部分は上記フィールド絶縁膜上に配置されており、かつ上記第1ゲート電極とは前記ゲート電極間絶縁膜を介している例を挙げることができる。

さらに、上方から見て、上記第2ゲート電極の端部の全部が上記第1ゲート電極の端部よりも外側に配置されており、上記第2ゲート電極は上記第1ゲート電極の端部及び側面を覆っているようにしてもよい。

さらに、上方から見て、上記第1ゲート電極上で上記第1ゲート電極の端部とは間隔をもつ位置に上記第2ゲート電極が形成されていない領域が存在しているようにしてもよい。

【0039】

また、上記第1ゲート電極と上記第2ゲート電極の間の容量値が互いに異なる複数の上記MOSトランジスタを備えている例を挙げることができる。

この場合、上記複数のMOSトランジスタにおいて、上記第2ゲート電極のレイアウト面積のみが互いに異なっている例を挙げることができる。

【0040】

また、アナログ回路では積層多結晶シリコンによる容量素子(2層ポリキャパシタンス)が多用されている。

そこで、上記半導体基板上に、上記第1ゲート電極と同一材料で同時に形成された第1容量素子電極と、上記第1容量素子電極上に絶縁膜を介して上記第2ゲート電極と同一材料で同時に形成された第2容量素子電極をもつ容量素子をさらに備えている例を挙げることができる。

【発明の効果】

【0041】

本発明の半導体装置では、MOSトランジスタについて、ドレイン領域は、ゲート絶縁膜及びチャネル領域とは間隔をもって配置された第1ドレイン領域と、第1ドレイン領域とチャネル領域の間に第1ドレイン領域及びチャネル領域に隣接して配置された第2ドレイン領域とからなり、ゲート電極は、ゲート絶縁膜上に形成された第1ゲート電極と、第1ゲート電極上にゲート電極間絶縁膜を介して形成された第2ゲート電極とからなり、第2ゲート電極にはゲート電圧を与えるためのゲート配線が接続されており、第1ゲート電極にはゲート配線は接続されておらず、半導体基板表面にゲート絶縁膜よりも厚い厚みをもつフィールド絶縁膜を備え、フィールド絶縁膜は少なくともゲート絶縁膜と第1ドレイン領域の間の半導体基板表面に配置されており、第1ゲート電極のドレイン領域側の端部はフィールド絶縁膜上に配置されているようにしたので、ゲート絶縁膜に印加される電圧をゲート配線に印加されるゲート電圧よりも小さくすることができるので、厚いゲート絶縁膜を用いることなく、ゲート電極に高いゲート電圧が高印加される高耐圧デバイスに適用することができる。

【0042】

また、第2ゲート電極の端部は、上方から見て、第1ゲート電極上のみに配置されており、第1ゲート電極の端部及び側面を覆い、かつ第2ゲート電極とは間隔をもって配置された、第2ゲート電極と同一材料で同時に形成されたパターンが形成されているようにすれば、第2ゲート電極を形成するための材料の加工残渣が第1ゲート電極の側面に形成されるのを防止して、その加工残渣に起因する不具合、例えば配線部の電気的ショートなどを防止することができる。

【0043】

また、上方から見て、第2ゲート電極の端部の一部分又は全部が第1ゲート電極の端部よりも外側に配置されており、第1ゲート電極の端部よりも外側に配置されている第2ゲート電極部分はフィールド絶縁膜上に配置されており、かつ第1ゲート電極とは前記ゲート電極間絶縁膜を介しているようにすれば、第1ゲート電極の側面を用いて第1ゲート電極、第2ゲート電極間の容量値を調整することができる。

【0044】

さらに、上方から見て、第2ゲート電極の端部の全部が第1ゲート電極の端部よりも外側に配置されており、第2ゲート電極は第1ゲート電極の端部及び側面を覆っているようにすれば、第2ゲート電極を形成するための材料の加工残渣が第1ゲート電極の側面に形成されるのを防止して、その加工残渣に起因する不具合、例えば配線部の電気的ショートなどを防止することができる。

【0045】

さらに、第2ゲート電極の端部の全部が第1ゲート電極の端部よりも外側に配置されている構成において、上方から見て、第1ゲート電極上で第1ゲート電極の端部とは間隔をもつ位置に第2ゲート電極が形成されていない領域が存在しているようにすれば、第2ゲート電極を形成するための材料の加工残渣が第1ゲート電極の側面に形成されるのを防止しつつ、第1ゲート電極上全面に第2ゲート電極が形成されている場合に比べて第1ゲート電極、第2ゲート電極間の容量値を大きくすることができる。

【0046】

また、第1ゲート電極と第2ゲート電極の間の容量値が互いに異なる複数のMOSトランジスタを備えているようにすれば、互いに異なる動作電圧をもつ複数のMOSトランジスタを同一半導体基板上に混載することができる。

この場合、上記複数のMOSトランジスタにおいて、第2ゲート電極のレイアウト面積のみが互いに異なっているようにすれば、製造工程を増加させることなく、互いに異なる動作電圧をもつ複数のMOSトランジスタを形成することができる。

【0047】

また、半導体基板上に、第1ゲート電極と同一材料で同時に形成された第1容量素子電極と、第1容量素子電極上に絶縁膜を介して第2ゲート電極と同一材料で同時に形成された第2容量素子電極をもつ容量素子をさらに備えているようにすれば、アナログ回路への適用が容易になる。

【発明を実施するための最良の形態】

【0048】

図1は一実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。(A)は(B)のA−A位置での断面である。(B)では上方から見て隠れている部分も実線で記している。(A)では模式的にゲート配線及びゲートコンタクトも図示している。

【0049】

P型の半導体基板(Psub)1の表面側に互いに間隔をもってN−ドレイン領域3dとN−ソース領域3sが形成されている。N−ドレイン領域3dとN−ソース領域3sの間の半導体基板1がチャネル領域5となる。N−ドレイン領域3dとN−ソース領域3sの間の半導体基板1上にゲート絶縁膜7が形成されている。ゲート絶縁膜7は、例えば、酸化シリコン膜からなり、その膜厚は20nmである。図示は省略するが、N−ドレイン領域3d、N−ソース領域3s及びチャネル領域5が形成されている領域の半導体基板1にはP型ウエル領域が形成されている。

【0050】

ゲート絶縁膜7上に第1ゲート電極9が形成されている。第1ゲート電極9は、例えば、多結晶シリコン膜からなり、その膜厚は300nmである。

第1ゲート電極9上にゲート電極間絶縁膜11を介して第2ゲート電極13が形成されているゲート電極間絶縁膜11は、例えば、酸化シリコン膜からなり、その膜厚は20nmである。第2ゲート電極13は、例えば、多結晶シリコン膜からなり、その膜厚は300nmである。

【0051】

N−ドレイン領域3dの表面側に、N−ドレイン領域3dの端部とは間隔をもってN+ドレイン領域11dが形成されている。N−ソース領域3sの表面側に、N−ソース領域3sの端部とは間隔をもってN+ソース領域11sが形成されている。N+ドレイン領域11d及びN+ソース領域11sはN−ドレイン領域3d及びN−ソース領域3sよりも濃いN型不純物濃度をもっている。このように、ドレイン領域及びソース領域は二重拡散構造を備えている。

【0052】

半導体基板1の表面に、LOCOSオフセットトランジスタの形成領域を画定するためのLOCOS酸化膜(フィールド絶縁膜)15が形成されている。LOCOS酸化膜15はゲート絶縁膜7よりも厚い膜厚をもち、その膜厚は例えば500nmである。LOCOS酸化膜15は、N−ドレイン領域3dのチャネル領域5側の端部とN+ドレイン領域11dの間のN−ドレイン領域3d表面、及びN−ソース領域3sのチャネル領域5側の端部とN+ソース領域11sの間のN−ソース領域3s表面にも形成されている。第1ゲート電極9の端部はLOCOS酸化膜15上に配置されている。また、第1ゲート電極9のN+ドレイン領域11d側の端部及びN+ソース領域11s側の端部は、上方から見て、それぞれN+ドレイン領域11d、N+ソース領域11sとは間隔をもって配置されている。

【0053】

第1ゲート電極9、第2ゲート電極13、N+ドレイン領域11d、N+ソース領域11s及びLOCOS酸化膜15上を覆って半導体基板1上に酸化シリコン膜系絶縁膜17が形成されている。酸化シリコン膜系絶縁膜17上に金属材料、例えばアルミニウムからなるゲート配線19g、ドレイン配線19d及びソース配線19sが形成されている。酸化シリコン膜系絶縁膜17に形成された接続孔21を介して、ゲート配線19gは第2ゲート電極13に接続され、ドレイン配線19dはN+ドレイン領域11dに接続され、ソース配線19sはN+ソース領域11sに接続されている。ゲート配線19gは第1ゲート電極9には接続されていない。

【0054】

図2〜図7は、図1に示したLOCOSオフセットトランジスタを形成するための製造工程の一例を順に示す図であり、各図において(A)は断面図、(B)は平面図を示し、(A)は(B)のA−A位置での断面である。(B)では上方から見て隠れている部分も実線で記している。図1〜図7を参照して製造工程の一例を説明する。

【0055】

P型半導体基板1に図示しないP型ウエル領域を形成した後、写真製版技術を用いてレジストパターン(図示は省略)を形成し、それをマスクとしてリンを注入エネルギーは100KeV、ドーズ量は2.0×1013cm-2の条件でイオン注入する。レジストパターンを除去した後、温度1000℃、30分間の窒素雰囲気にさらすことで注入されたリンが拡散及び活性化し、低濃度なN−ドレイン領域3d及びN−ソース領域3sが形成される(図2参照。)。

【0056】

既存の素子分離形成技術を用いてLOCOS酸化膜15を膜厚500nmで形成する(図3参照。)。

ゲート絶縁膜7を膜厚20nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして、異方性ドライエッチング技術により、多結晶シリコン膜及びゲート絶縁膜7を順次エッチング除去して多結晶シリコン膜からなる第1ゲート電極9を形成し、第1ゲート電極9下のみにゲート絶縁膜7を形成する。その後、レジストパターンの除去を行なう(図4参照。)。第1ゲート電極9の端部はLOCOS酸化膜15上に配置されている。ここで、ゲート絶縁膜7のエッチング除去はウェットエッチング技術により行なってもよい。

【0057】

第1ゲート電極9の表面にゲート電極間絶縁膜11を膜厚20nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして、異方性ドライエッチング技術により、多結晶シリコン膜及びゲート電極間絶縁膜11を順次エッチング除去して多結晶シリコン膜からなる第2ゲート電極13を形成し、第2ゲート電極13下のみにゲート電極間絶縁膜11を形成する。その後、レジストパターンの除去を行なう(図5参照。)。上方から見て、第2ゲート電極13の端部は第1ゲート電極9上に配置されている。ここで、ゲート電極間絶縁膜11のエッチング除去はウェットエッチング技術により行なってもよい。

【0058】

LOCOSオフセットトランジスタの形成領域に開口をもつレジストパターンを形成した後、ヒ素を注入エネルギー30KeV、ドーズ量5.0×1015cm-2の条件でイオン注入する。レジストパターンを除去した後、温度900℃、30分間の窒素雰囲気にさらすことで注入されたヒ素が拡散及び活性化し、高濃度なN+ドレイン領域11d及びN+ソース領域11sが形成される(図6参照。)。N+ドレイン領域11dとその周りを覆う低濃度なN−ドレイン領域3dがドレイン領域を構成し、N+ソース領域11sとその周りを覆う低濃度なN−ソース領域3sがソース領域を構成する。

【0059】

半導体基板1上全面に酸化シリコン膜系絶縁膜17、例えばNSG(Non-doped Silicate Glass)膜とBPSG(Boro-phospho Silicate Glass )膜の積層膜を1000nmの膜厚に堆積する。レジストパターンを形成した後、そのレジストパターンをマスクとして所定の位置の酸化シリコン膜系絶縁膜17をエッチング除去し、N+ドレイン領域11d、N+ソース領域11s、第2ゲート電極13に対応する位置に接続孔21を形成する(図7参照。)。

【0060】

酸化シリコン膜系絶縁膜17上に例えばアルミニウム系金属膜を形成し、その金属膜をパターニングして、ゲート配線19g、ドレイン配線19d及びソース配線19sを形成する(図1参照。)。

【0061】

この実施例では、(1)ドレイン領域及びソース領域が二重拡散構造を備えていること、(2)第1ゲート電極9の端部がゲート絶縁膜7よりも厚いLOCOS酸化膜15上に配置されていること、の2つの特徴を備えているのでドレイン領域及びソース領域は高電圧に耐えることができる。

【0062】

さらに、第1ゲート電極9上にゲート電極間絶縁膜11を介して第2ゲート電極13を備え、積層構造のゲート電極となっていることから、第2ゲート電極13に印加されるゲート電圧がゲート電極間絶縁膜11とゲート絶縁膜7に分圧される。これにより、ゲート電極も高電圧に耐えることができる。これを図1と図8を参照して説明する。

【0063】

図8は第2ゲート電極13に印加されるゲート電圧がゲート電極間絶縁膜11とゲート絶縁膜7に分圧されることを説明するための図である。(A)はゲート電極の回路図と、ゲート絶縁膜7、ゲート電極間絶縁膜11に与えられる電圧V1,V2を表す式である。(B)は第1ゲート電極9と半導体基板1との間の容量値をC1、第2ゲート電極13と第1ゲート電極9の間の容量値をC2としたときの容量値C1,C2の容量値比に対する電圧V1,V2を示す表である。

【0064】

第1ゲート電極9と半導体基板1との間の容量値をC1、第2ゲート電極13と第1ゲート電極9の間の容量値をC2とすると、ゲート絶縁膜7にかかる電圧V1とゲート電極間絶縁膜11にかかる電圧V2は図8中の式のようになる。

仮にC1=C2とすると、第2ゲート電極13にかかる電圧V1は、第2ゲート電極13に印加されるゲート電圧(Vdd)に対して半分に低減される。このことはゲート絶縁膜厚としては従来の半分ですむことを示している。すなわち厚いゲート絶縁膜を長時間の熱処理で形成することなく、ゲート電極に高耐圧機能をもたせることが可能となる。

【0065】

この実施例ではゲート電極間絶縁膜11を酸化シリコン膜から構成される単層膜としたが、ゲート電極間絶縁膜は例えば酸化シリコン膜/窒化シリコン膜/酸化シリコン膜から構成される積層膜、いわゆるONO膜であってもよい。一般的にONO膜のほうが酸化シリコン単層膜よりも絶縁耐性が高いので第2ゲート電極13に印加される電圧値の大部分を担わせることにつながる。つまり、ゲート絶縁膜7にかかる電圧を低く押さえることができるわけである。しかもこの時、ゲート絶縁膜7は酸化シリコン膜のまま形成できるので、ホットキャリアの捕獲による電気特性のシフトの問題は原理的に発生しない。

【0066】

ゲート絶縁膜7にかかる電圧V1は図8中に示した計算式から算出することができる。ここでゲート電極間絶縁膜11をONO膜にすることで絶縁耐性の向上、つまりは分圧電圧V2の増大化が可能になる。これを積極利用することを説明する。すなわち、C2をC1に対して小さく設定する。例えばC2=C1/3にすると図8の計算結果表からVdd=28Vの時、V2=21V、V1=7Vとなり、駆動電圧Vdd=28Vの高電圧環境下でありながらゲート絶縁膜7には7Vしか印加されない。

【0067】

また、図9に示すように、半導体基板1、第1ゲート電極9間のゲート絶縁膜7の面積を第1ゲート電極9、第2ゲート電極13間のゲート電極間絶縁膜9の面積よりも小さくすることにより、C2を下げることができる。このように、半導体基板1、第1ゲート電極9間のゲート絶縁膜7の面積と、第1ゲート電極9、第2ゲート電極13間のゲート電極間絶縁膜9の面積の比率を調整することにより、第2ゲート電極13に印加されるゲート電圧に対してゲート絶縁膜7にかかる電圧を制御することができる。

【0068】

また、ゲート絶縁膜7とゲート電極間絶縁膜11の膜厚を調整することによっても、容量値C1,C2を制御することができ、ゲート絶縁膜7にかかる電圧を所望の値に設定することもできる。

このように、第2ゲート電極13に印加されるゲート電圧に対してゲート絶縁膜7にかかる電圧は、ゲート絶縁膜7とゲート電極間絶縁膜11の膜の種類、ゲート絶縁膜7とゲート電極間絶縁膜11の面積、ゲート絶縁膜7とゲート電極間絶縁膜11の膜厚によって制御することができる。

【0069】

図1に示した実施例の製造工程では、第1ゲート電極9を形成した後に、半導体基板1上全面にゲート電極間絶縁膜11を介して多結晶シリコン膜を形成し、その多結晶シリコン膜を異方性ドライエッチング技術によりパターニングして第2ゲート電極13を形成するので、図10に示すように、第1ゲート電極9の側面に多結晶シリコン加工残渣23((B)ではシボで示す)が形成されることがある。多結晶シリコン加工残渣23は第1ゲート電極9及びN−領域3d,3sとはゲート電極間絶縁膜11と同一材料で同時に形成された絶縁膜パターンを介して形成される。

【0070】

この実施例では、多結晶シリコン加工残渣23はLOCOS酸化膜15上に形成され、かつ第1ゲート電極9及び第2ゲート電極13とは絶縁されているので、多結晶シリコン加工残渣23がトランジスタ動作に悪影響を与えることはない。なお、図48に示すように、本願発明の積層ゲート電極構造を通常のMOSトランジスタに適用した場合、N+領域11d,11sを形成するためのイオン注入時に多結晶シリコン加工残渣23が遮蔽物になり、図中符号Xの部分にイオンが注入されないので、上方から見てN+領域11d,11sが第1ゲート電極9とは間隔をもって形成されてしまう。したがって、通常のMOSトランジスタ構造では、本願発明の積層ゲート電極構造を採用することができない。

【0071】

図10に示した実施例において、多結晶シリコン加工残渣23はトランジスタ動作に悪影響を与えるものではないが、製造工程中に多結晶シリコン加工残渣23が剥がれて半導体基板上で移動すると、多結晶シリコン加工残渣23はいわゆる異物となり、例えば配線部の電気的ショート、ひいては歩留まりの低下を招くことが考えられる。

次に、多結晶シリコン加工残渣23が発生しない実施例を説明する。

【0072】

図11はさらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。(A)は(B)のA−A位置での断面である。(B)では上方から見て隠れている部分も実線で記している。(A)では模式的にゲート配線及びゲートコンタクトも図示している。図1と同じ機能を果たす部分には同じ符号を付す。

【0073】

この実施例では、上方から見て、第2ゲート電極13の端部の全部が第1ゲート電極9の端部よりも外側に配置されて、第2ゲート電極13は第1ゲート電極9の側面を覆っている。第1ゲート電極9の端部よりも外側に配置されている第2ゲート電極13の部分はLOCOS酸化膜15上に配置されている。第1ゲート電極9と第2ゲート電極13の間にはゲート電極間絶縁膜11が形成されている。

【0074】

第2ゲート電極13は第1ゲート電極9の側面を覆っているので、第2ゲート電極13を形成するための多結晶シリコン膜を異方性ドライエッチング技術によりパターニングする際に第2ゲート電極13の側面に多結晶シリコン加工残渣23(図10参照。)が形成されることはない。これにより、多結晶シリコン加工残渣23に起因する不具合を防止することができる。

【0075】

さらに、第1ゲート電極9の端部よりも外側に配置されている第2ゲート電極13の部分はLOCOS酸化膜15上に配置されているので、第2ゲート電極13に印加されるゲート電圧がゲート絶縁膜7に直接影響を与えることはない。すなわち、高耐圧機能を保持することができる。

【0076】

さらに、第1ゲート電極9の側面も使って第1ゲート電極9、第2ゲート電極13間の容量値を調整することができるので、設計の自由度が増す。

【0077】

図11に示した実施例では、第1ゲート電極9上全面に第2ゲート電極13が配置されているが、本発明はこれに限定されるものではない。

図12はさらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。(A)は(B)のA−A位置での断面である。(B)では上方から見て隠れている部分も実線で記している。(A)では模式的にゲート配線及びゲートコンタクトも図示している。図1、図11と同じ機能を果たす部分には同じ符号を付す。(B)では第2電極をシボで示した。

【0078】

この実施例では、図11に示した実施例と比較して、第1ゲート電極9上で第1ゲート電極9の端部とは間隔をもつ位置に第2ゲート電極13が形成されていない領域が存在している。これにより、図11に示した実施例に比べて第1ゲート電極9、第2ゲート電極13間の容量値を大きくすることができる。

また、第1ゲート電極9上で第2ゲート電極13が形成されていない領域の面積を調整することにより、第1ゲート電極9、第2ゲート電極13間の容量値を任意の値に設定することもできる。

【0079】

図12に示した実施例では、第1ゲート電極9上で第2ゲート電極13が形成されていない領域は1箇所の矩形であるが、本発明はこれに限定されるものではなく、当該領域は1ゲート電極9上で複数個所に設けられていてもよいし、当該領域の平面形状は例えば円形など、矩形以外の形状であってもよい。

【0080】

また、図11及び図12に示した各実施例では、上方から見て第2ゲート電極13の端部の全部が第1ゲート電極9の端部よりも外側に配置されているが、図13に示すように、上方から見て第2ゲート電極13の端部の一部分が第1ゲート電極9の端部よりも外側に配置されているようにしてもよい。図13(B)では第2ゲート電極13及び多結晶シリコン加工残渣23をシボで示した。

【0081】

図13に示した実施例では、多結晶シリコン加工残渣23の発生はある程度許容しながら、同時に第1ゲート電極9、第2ゲート電極13間の容量値を図11に示した実施例に比べて小さくすることができる。このような構造は、多結晶シリコン加工残渣23に起因する不具合の懸念が小さい用途であって、かつ、ゲート絶縁膜7に印加される電圧を低くしたい場合に有効である。

【0082】

図14はさらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。(A)は(B)のA−A位置での断面である。(B)では上方から見て隠れている部分も実線で記している。(A)では模式的にゲート配線及びゲートコンタクトも図示している。図1と同じ機能を果たす部分には同じ符号を付す。

【0083】

この実施例では、図1に示した実施例と同様に、第2ゲート電極13は第1ゲート電極9上のみに形成されている。そして、上方から見て第2ゲート電極13の端部は第1ゲート電極9の端部とは間隔をもって配置されている。

【0084】

この実施例が図1に示した実施例と異なる点は、絶縁膜パターン25を介して第1ゲート電極9の端部及び側面を覆い、かつ第2ゲート電極13とは間隔をもって配置された、第2ゲート電極13と同一材料で同時に形成された多結晶シリコンパターン27が形成されている点である。多結晶シリコンパターン27は、第2ゲート電極13とは間隔をもって配置されているので、第2ゲート電極13とは絶縁されている。絶縁膜パターン25はゲート電極間絶縁膜11と同一材料で同時に形成されたものである。

この実施例によれば、多結晶シリコン加工残渣23(図10参照。)を発生させることなく、第1ゲート電極9、第2ゲート電極13間の容量値を小さくすることができる。

【0085】

上記実施例では、第1ゲート電極9のドレイン領域側の端部及びソース領域側の端部の両方がLOCOS酸化膜15上に配置されているが、図15に示すように、第1ゲート電極9のドレイン領域側の端部のみがLOCOS酸化膜15上に配置されているようにしてもよい。

また、上記実施例では、ドレイン領域及びソース領域の両方が二重拡散構造を備えているが、図16に示すように、ドレイン領域のみが二重拡散構造を備えているようにしてもよい。

【0086】

図9〜図16に示した各実施例は、図1〜図7を参照して説明した製造工程例で用いるレイアウト形状(フォトマスクのCADデータ)を変更することにより形成することができる。

【0087】

ところで、従来構造のLOCOSオフセットトランジスタを用いて、複数のゲート電圧値向けのLOCOSオフセットトランジスタを1つの半導体基板に混載する場合、複数の問題点が生じる。

図49に示すように、例えば3種類のゲート電圧値に対応した3種類のLOCOSオフセットトランジスタを混載している場合、それらのLOCOSオフセットトランジスタでゲート絶縁膜51−1,51−2,51−3の膜厚をそれぞれ異ならせる必要があった。すなわち、ゲート電圧Vdd=30Vの電圧で動作可能なトランジスタ(1)ではゲート絶縁膜51−1の膜厚を80nmに、ゲート電圧Vdd=22.5Vの電圧で動作可能なトランジスタ(2)ではゲート絶縁膜51−2の膜厚を50nmに、ゲート電圧Vdd=15Vの電圧で動作可能なトランジスタ(3)ではゲート絶縁膜51−3の膜厚を30nmにするなど、各電圧帯に応じたゲート絶縁膜をそれぞれ形成する必要があった。3種類の異なる膜厚のゲート絶縁膜を一つの半導体基板に形成するためにはプロセスフローの長時間化の問題、マスクセットの作成枚数の増加の問題、前述のフィールド絶縁膜の膜減りの問題(図47参照。)など、解決すべき課題が極めて多い。これについての詳細は特許文献3を参照されたい。

【0088】

これに対して、本願発明を構成するLOCOSオフセットトランジスタでは、半導体基板、第1ゲート電極間の容量値と第1ゲート電極、第2ゲート電極間の容量値を調整することによってゲート絶縁膜にかかる電圧を制御することができるので、複数種類のゲート電圧値に対応した複数種類のLOCOSオフセットトランジスタを同一半導体基板上に混載する場合であっても、それらのトランジスタでゲート絶縁膜厚を互いに異ならせることなく、すなわち同一膜厚のゲート絶縁膜のままを用いて、動作電圧帯が互いに異なる複数種類のトランジスタを同一半導体基板上に混載することができる。図17を参照して、動作電圧帯が互いに異なる3種類のLOCOSオフセットトランジスタを同一半導体基板上に混載した実施例を説明する。

【0089】

図17はさらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図、(C)はゲート電圧に対する各トランジスタの設定例を示す表である。(A)は(B)のA−A位置での断面である。(B)では上方から見て隠れている部分も実線で記している。(A)では模式的にゲート配線及びゲートコンタクトも図示している。図1と同じ部分には同じ符号を付す。

この実施例では、ゲート電圧Vdd=30Vの電圧で動作可能なトランジスタ(1)と、ゲート電圧Vdd=22.5Vの電圧で動作可能なトランジスタ(2)と、ゲート電圧Vdd=15Vの電圧で動作可能なトランジスタ(3)を同一半導体基板1上に備えている。

【0090】

トランジスタ(1),(2),(3)において、第2ゲート電極13−1,13−2,13−3のレイアウト面積が互いに異なっている。それ以外に部分、例えば、半導体基板1に形成されたP型ウエル領域、ゲート絶縁膜7、第1ゲート電極9、ゲート電極間絶縁膜11に関しては、その形状、不純物濃度、膜厚などは3つのトランジスタ(1),(2),(3)で同じになっている。なお、ゲート電極間絶縁膜11の平面形状は、第2ゲート電極13−1,13−2,13−3の平面形状が互いに異なっているにともなって、トランジスタ(1),(2),(3)で互いに異なっている。

【0091】

つまり、トランジスタ(1),(2),(3)において、第1ゲート電極9と半導体基板1(P型ウエル領域)との間の容量値=C1は同じであり、第1ゲート電極9と第2ゲート電極13の間の容量値=C2が互いに異なっている。具体的にはゲート電圧Vdd=30Vの電圧で動作可能なトランジスタ(1)はC2=C1/3に、ゲート電圧Vdd=22.5Vの電圧で動作可能なトランジスタ(2)はC2=C1/2に、ゲート電圧Vdd=15Vの電圧で動作可能なトランジスタ(3)はC2=C1になるように調整してある。これにより、前述の図8の計算式に従うと、ゲート絶縁膜7にかかる電圧は3つのトランジスタ(1),(2),(3)で全て7.5Vとなる。すなわち、膜厚、材料及び形成時期が同一のゲート絶縁膜7を用いて印加電圧が30Vと22.5Vと15Vの3種類の動作電圧帯に対応可能なワンチップLSIを得ることができる。

【0092】

さらに、3つのトランジスタ(1),(2),(3)は第2ゲート電極13のレイアウト面積(CADデータ)を互いに異ならせるだけで形成することができるので、製造方法としては前述の図1〜図7を参照して説明した製造工程により形成できる。すなわち、図49を参照して説明したプロセスフローの長時間化の問題やマスクセットの作成枚数増加の問題、フィールド絶縁膜の膜減りの問題などを全て回避することができる。

【0093】

図17に示した実施例では、3つのトランジスタ(1),(2),(3)について、第2ゲート電極13−1,13−2,13−3のレイアウト面積のみを互いに異ならせることにより、動作電圧帯が互いに異なるトランジスタ(1),(2),(3)を形成しているが、LOCOSオフセットトランジスタの動作電圧帯を互いに異ならせる方法は、これに限定されるものではなく、ゲート絶縁膜7、第1ゲート電極9、ゲート電極間絶縁膜11及び第1ゲート電極13について、レイアウト面積、膜厚及び材料のうちの少なくとも1つを互いに異ならせることにより、LOCOSオフセットトランジスタの動作電圧帯を互いに異ならせるようにしてもよい。ただし、図49を参照して説明した上記問題点を考慮すると、複数のLOCOSオフセットトランジスタで第2ゲート電極のレイアウト面積のみを互いに異ならせることにより動作電圧帯を互いに異ならせるようにすることが有利である。

【0094】

また、図17に示した実施例では、3つのトランジスタ(1),(2),(3)は全て15V以上の高電圧に対応したものであるが、本発明を構成するLOCOSオフセットトランジスタは例えば2.5V程度の低電圧で動作可能なトランジスタにも適用することができるので、トランジスタ(1),(2),(3)のうちの1つ、2つ又は全部を、互いに動作電圧帯が異なる低電圧で動作可能なトランジスタにしてもよい。

【0095】

また、図17に示した実施例では、同一半導体基板上に混載されたトランジス(1),(2),(3)は全部LOCOSオフセットトランジスタであるが、本発明を構成するLOCOSオフセットトランジスタと通常のMOSトランジスタを同一半導体基板上に混載することもできる。その実施例を図18を参照して説明する。

【0096】

図18はさらに他の実施例を概略的に示す断面図である。図1と同じ機能を果たす部分には同じ符号を付す。LOCOSオフセットトランジスタの構造は図1に示した実施例と同じなので説明を省略する。

【0097】

半導体基板1のLOCOSオフセットトランジスタ形成領域とは異なる領域に通常のMOSトランジスタが形成されている。

通常のMOSトランジスタは、半導体基板1の表面側に形成されたP型ウエル(図示は省略)に互いに間隔をもって形成されたN+ドレイン領域29d、N+ソース領域29sを備えている。N+ドレイン領域29dとN+ソース領域29sの間の半導体基板1がチャネル領域31となる。チャネル領域31上にゲート絶縁膜33が形成されている。ゲート絶縁膜33はLOCOSオフセットトランジスタのゲート絶縁膜33と同時に形成されたものであり、例えば膜厚が20nmの酸化シリコン膜からなる。

【0098】

ゲート絶縁膜33上にゲート電極35が形成されている。ゲート電極35はLOCOSオフセットトランジスタの第1ゲート電極9と同一材料から同時に形成されたものである。

N+ドレイン領域29d上、N+ソース領域29s上及び第ゲート電極35上を覆って半導体基板1上に酸化シリコン膜系絶縁膜17が形成されている。酸化シリコン膜系絶縁膜17上に金属材料、例えばアルミニウムからなるゲート配線37g、ドレイン配線37d及びソース配線37sが形成されている。酸化シリコン膜系絶縁膜17に形成された接続孔21を介して、ゲート配線37gはゲート電極35に接続され、ドレイン配線37dはN+ドレイン領域29dに接続され、ソース配線37sはN+ソース領域29sに接続されている。

【0099】

図19〜図24は、図18に示したLOCOSオフセットトランジスタ及び通常のMOSトランジスタを形成するための製造工程の一例を順に示す概略的な断面図である。図81〜図19を参照して製造工程の一例を説明する。

【0100】

P型半導体基板1に図示しないP型ウエル領域を形成した後、写真製版技術を用いてレジストパターン(図示は省略)を形成し、それをマスクとしてリンを注入エネルギーは100KeV、ドーズ量は2.0×1013cm-2の条件でイオン注入する。レジストパターンを除去した後、温度1000℃、30分間の窒素雰囲気にさらすことで注入されたリンが拡散及び活性化し、低濃度なN−ドレイン領域3d及びN−ソース領域3sが形成される(図19参照。)。

【0101】

既存の素子分離形成技術を用いてLOCOS酸化膜15を膜厚500nmで形成する(図20参照。)。

ゲート絶縁膜7,33となる酸化シリコン膜を膜厚20nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして、異方性ドライエッチング技術により、多結晶シリコン膜及び酸化シリコン膜を順次エッチング除去して多結晶シリコン膜からなる第1ゲート電極9及びゲート電極35を形成し、第1ゲート電極9下にゲート絶縁膜7を形成し、ゲート電極35下にゲート絶縁膜33を形成する。その後、レジストパターンの除去を行なう(図21参照。)。ここで、ゲート絶縁膜7,33を形成するための酸化シリコン膜のエッチング除去はウェットエッチング技術により行なってもよい。

【0102】

ゲート電極間絶縁膜11を膜厚20nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして、異方性ドライエッチング技術により、多結晶シリコン膜及びゲート電極間絶縁膜11を順次エッチング除去して多結晶シリコン膜からなる第2ゲート電極13を形成し、第2ゲート電極13下にゲート電極間絶縁膜11を形成する。このとき、第1ゲート電極9及びゲート電極35の側面に多結晶シリコン加工残渣23が形成される。その後、レジストパターンの除去を行なう(図22参照。)。ここで、ゲート電極間絶縁膜11のエッチング除去はウェットエッチング技術により行なってもよい。

【0103】

通常のMOSトランジスタの形成領域に開口部をもつレジストパターン39を形成する。レジストパターン39をマスクにして、例えば等方性エッチング技術により、ゲート電極35側面の多結晶シリコン加工残渣23を除去する(図23参照。)。

【0104】

LOCOSオフセットトランジスタ及び通常のMOSトランジスタの形成領域に開口をもつレジストパターンを形成した後、ヒ素を注入エネルギー30KeV、ドーズ量5.0×1015cm-2の条件でイオン注入する。レジストパターンを除去した後、温度900℃、30分間の窒素雰囲気にさらすことで注入されたヒ素が拡散及び活性化し、高濃度なN+ドレイン領域11d、N+ソース領域11s、N+ドレイン領域29d及びN+ソース領域29sが形成される(図24参照。)。

【0105】

半導体基板1上全面に酸化シリコン膜系絶縁膜17を1000nmの膜厚に堆積する。レジストパターンを形成した後、そのレジストパターンをマスクとして所定の位置の酸化シリコン膜系絶縁膜17をエッチング除去し、N+ドレイン領域11d、N+ソース領域11s、第2ゲート電極13、N+ドレイン領域29d、N+ソース領域29s、ゲート電極35に対応する位置に接続孔21を形成する。酸化シリコン膜系絶縁膜17上に例えばアルミニウム系金属膜を形成し、その金属膜をパターニングして、ゲート配線19g、ドレイン配線19d、ソース配線19s、ゲート配線37g、ドレイン配線37d及びソース配線37sを形成する(図18参照。)。

【0106】

この実施例では、LOCOSオフセットランジスタについて図8に示したようにゲート電圧の分割を行なうことによりゲート絶縁膜7にかかる電圧を小さくすることができるので、ゲート絶縁膜7と通常のトランジスタのゲート絶縁膜33を同一材料で同じ膜厚で同時に形成することができる。すなわち、通常のトランジスタのゲート絶縁膜33と同じ特性のゲート絶縁膜7を用いて高電圧対応可能なLOCOSオフセットトランジスタを形成することができる。

【0107】

さらに、この実施例では、LOCOSオフセットトランジスタのゲート絶縁膜7と通常のトランジスタのゲート絶縁膜33は同時に形成されたものであるので、LOCOSオフセットトランジスタと通常のトランジスタを同一半導体基板上に混載する場合にプロセスフローの簡略化を実現できるので、プロセスフローの長時間化の上記問題点が生じない。さらにLOCOSオフセットトランジスタの第1ゲート電極9と通常のトランジスタのゲート電極35は同時に形成されたものであるのでプロセスフローの簡略化を実現できる。

【0108】

図25はさらに他の実施例を概略的に示す断面図である。この実施例は、LOCOSオフセットトランジスタの形成領域とは異なる半導体基板1の位置に、第1ゲート電極と同一材料で同時に形成された第1容量素子電極と、第1容量素子電極上に絶縁膜を介して第2ゲート電極と同一材料で同時に形成された第2容量素子電極をもつ容量素子をさらに備えているものである。図1と同じ機能を果たす部分には同じ符号を付す。LOCOSオフセットトランジスタの構造は図1に示した実施例と同じなので説明を省略する。

【0109】

LOCOSオフセットトランジスタの形成領域とは異なる半導体基板1の位置に、LOCOS酸化膜15を介して容量素子が形成されている。この容量素子は、LOCOS酸化膜15上に形成された第1容量素子電極41uと、第1容量素子電極41上に容量素子電極間絶縁膜43を介して形成された第2容量素子電極41tを備えている。第1容量素子電極41uは第1ゲート電極9と同一材料で同時に形成されたものである。容量素子電極間絶縁膜43はゲート電極間絶縁膜11と同一材料で同時に形成されたものである。第2容量素子電極41tは第2ゲート電極13と同一材料で同時に形成されたものである。

【0110】

酸化シリコン膜系絶縁膜17はた第1容量素子電極41u及び第2容量素子電極41tも覆っている。酸化シリコン膜系絶縁膜17上にゲート配線19g、ドレイン配線19d及びソース配線19sと同一材料で同時に形成された第1容量素子電極配線45uと第2容量素子電極配線45tが形成されている。酸化シリコン膜系絶縁膜17に形成された接続孔21を介して、第1容量素子電極配線45uは第1容量素子電極41uに接続され、第2容量素子電極配線45tは第2容量素子電極41tに接続されている。

【0111】

図26〜図31は、図25に示したLOCOSオフセットトランジスタ及び容量素子を形成するための製造工程の一例を順に示す断面図である。図25〜図31を参照して製造工程の一例を説明する。

【0112】

P型半導体基板1に図示しないP型ウエル領域を形成した後、写真製版技術を用いてレジストパターン(図示は省略)を形成し、それをマスクとしてリンを注入エネルギーは100KeV、ドーズ量は2.0×1013cm-2の条件でイオン注入する。レジストパターンを除去した後、温度1000℃、30分間の窒素雰囲気にさらすことで注入されたリンが拡散及び活性化し、低濃度なN−ドレイン領域3d及びN−ソース領域3sが形成される(図26参照。)。

【0113】

既存の素子分離形成技術を用いてLOCOS酸化膜15を膜厚500nmで形成する(図27参照。)。

ゲート絶縁膜7を膜厚20nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして、異方性ドライエッチング技術により、多結晶シリコン膜及びゲート絶縁膜7を順次エッチング除去して多結晶シリコン膜からなる第1ゲート電極9と第1容量素子電極41uを形成し、第1ゲート電極9下にゲート絶縁膜7を形成する。ここで第1容量素子電極41u下にゲート絶縁膜7が残存するが図示は省略している。その後、レジストパターンの除去を行なう(図28参照。)。

【0114】

ゲート電極間絶縁膜11及び容量素子電極間絶縁膜43形成するための酸化シリコン膜を膜厚20nmで形成した後、連続して多結晶シリコン膜を300nmの厚みに堆積させる。写真製版技術を用いてレジストパターンを形成する。それをマスクにして、異方性ドライエッチング技術により、多結晶シリコン膜及び酸化シリコン膜を順次エッチング除去して、第1ゲート電極9上に第2ゲート電極13及びゲート電極間絶縁膜11を形成し、第1容量素子電極41u上に第2容量素子電極41t及び容量素子電極間絶縁膜43を形成する。ここで、第1ゲート電極9側面及び第1容量素子電極41u側面に多結晶シリコン加工残渣23(図10参照。)が形成されることがあるが、図示は省略する。なお、第1容量素子電極41u側面に多結晶シリコン加工残渣23が形成されても、多結晶シリコン加工残渣23はLOCOS酸化膜15上に形成されるので、容量素子の電気的特性に悪影響を与えることはない。その後、レジストパターンの除去を行なう(図29参照。)。

【0115】

LOCOSオフセットトランジスタの形成領域に開口をもつレジストパターンを形成した後、ヒ素を注入エネルギー30KeV、ドーズ量5.0×1015cm-2の条件でイオン注入する。レジストパターンを除去した後、温度900℃、30分間の窒素雰囲気にさらすことで注入されたヒ素が拡散及び活性化し、高濃度なN+ドレイン領域11d及びN+ソース領域11sが形成される(図30参照。)。

【0116】

半導体基板1上全面に酸化シリコン膜系絶縁膜17、例えばNSG膜とBPSG膜の積層膜を1000nmの膜厚に堆積する。レジストパターンを形成した後、そのレジストパターンをマスクとして所定の位置の酸化シリコン膜系絶縁膜17をエッチング除去し、N+ドレイン領域11d、N+ソース領域11s、第2ゲート電極13、第1容量素子電極41u、第2容量素子電極41tに対応する位置に接続孔21を形成する(図31参照。)。

【0117】

酸化シリコン膜系絶縁膜17上に例えばアルミニウム系金属膜を形成し、その金属膜をパターニングして、ゲート配線19g、ドレイン配線19d、ソース配線19s、第1容量素子電極配線45u、第2容量素子電極配線45tを形成する(図25参照。)。

【0118】

この実施例では、容量素子は、第1ゲート電極9と同一材料で同時に形成された第1容量素子電極41uと、ゲート電極間絶縁膜11と同一材料で同時に形成された容量素子電極間絶縁膜43と、第2ゲート電極13と同一材料で同時に形成された第2容量素子電極41tによって形成されているので、LOCOSオフセットトランジスタの製造工程を増加させることなく、同一半導体基板1上に容量素子を混載することができる。

【0119】

この実施例では、容量素子において、上方から見て第2容量素子電極41tの端部は第1容量素子電極41uの端部の内側に配置されているが、第1容量素子電極41uと第2容量素子電極41のレイアウト位置はこれに限定されるものではない。

例えば、図12や図14に示したLOCOSオフセットトランジスタの第1ゲート電極9及び第2ゲート電極13のレイアウト位置と同様に、容量素子において、上方から見て第2容量素子電極41tの端部は第1容量素子電極41uの端部の外側に配置されており、かつ第1容量素子電極41uのコンタクトを形成する位置には第2容量素子電極41tが形成されていないようにすれば、第1容量素子電極41uの側面に多結晶シリコン加工残渣23(図10参照。)が形成されるのを防止することができる。

【0120】

また、図13に示したLOCOSオフセットトランジスタの第1ゲート電極9及び第2ゲート電極13のレイアウト位置と同様に、容量素子において、上方から見て第2容量素子電極41tの端部の一部分が第1容量素子電極41uの端部の外側に配置されているようにしてもよい。

【0121】

以上、本発明の実施例を説明したが、本発明はこれらに限定されるものではなく、形状、配置、個数、材料などは一例であり、特許請求の範囲に記載された本発明の範囲内で種々の変更が可能である。

【図面の簡単な説明】

【0122】

【図1】一実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図2】図1に示したLOCOSオフセットトランジスタを形成するための製造工程の一例を説明するための最初の工程を示す図であり、(A)は断面図、(B)は平面図である。

【図3】同製造工程例の続きの工程を示す図であり、(A)は断面図、(B)は平面図である。

【図4】同製造工程例のさらに続きの工程を示す図であり、(A)は断面図、(B)は平面図である。

【図5】同製造工程例のさらに続きの工程を示す図であり、(A)は断面図、(B)は平面図である。

【図6】同製造工程例のさらに続きの工程を示す図であり、(A)は断面図、(B)は平面図である。

【図7】同製造工程例のさらに続きの工程を示す図であり、(A)は断面図、(B)は平面図である。

【図8】第2ゲート電極に印加されるゲート電圧がゲート電極間絶縁膜とゲート絶縁膜に分圧されることを説明するための図であり、(A)はゲート電極の回路図と、ゲート絶縁膜、ゲート電極間絶縁膜に与えられる電圧V1,V2を表す式であり、(B)は第1ゲート電極9半導体基板1の間の容量値をC1、第2ゲート電極131ゲート電極の間の容量値をC2としたときの容量値C1,C2の容量値比に対する電圧V1,V2を示す表である。

【図9】他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図10】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図11】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図12】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図13】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図14】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図15】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図16】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図である。

【図17】さらに他の実施例を概略的に示す図であり、(A)は断面図、(B)は平面図、(C)はゲート電圧に対する各トランジスタの設定例を示す表である。

【図18】さらに他の実施例を概略的に示す断面図である。

【図19】図18に示したLOCOSオフセットトランジスタ及び通常のMOSトランジスタを形成するための製造工程の一例を説明するための最初の工程を示す断面図である。

【図20】同製造工程例の続きの工程を示す断面図である。

【図21】同製造工程例のさらに続きの工程を示す断面図である。

【図22】同製造工程例のさらに続きの工程を示す断面図である。

【図23】同製造工程例のさらに続きの工程を示す断面図である。

【図24】同製造工程例のさらに続きの工程を示す断面図である。

【図25】さらに他の実施例を概略的に示す断面図である。

【図26】図25に示したLOCOSオフセットトランジスタ及び容量素子を形成するための製造工程の一例を説明するための最初の工程を示す断面図である。

【図27】同製造工程例の続きの工程を示す断面図である。

【図28】同製造工程例のさらに続きの工程を示す断面図である。

【図29】同製造工程例のさらに続きの工程を示す断面図である。

【図30】同製造工程例のさらに続きの工程を示す断面図である。

【図31】同製造工程例のさらに続きの工程を示す断面図である。

【図32】従来のLOCOSオフセットトランジスタを概略的に示す断面図である。

【図33】図32に示した従来のLOCOSオフセットトランジスタの製造工程の一例を説明するための最初の工程を示す断面図である。

【図34】同製造工程例の続きの工程を示す断面図である。

【図35】同製造工程例のさらに続きの工程を示す断面図である。

【図36】同製造工程例のさらに続きの工程を示す断面図である。

【図37】同製造工程例のさらに続きの工程を示す断面図である。

【図38】Masked−LDDトランジスタを概略的に示す断面図である。

【図39】図38に示したMasked−LDDトランジスタの製造工程の一例を説明するための最初の工程を示す断面図である。

【図40】同製造工程例の続きの工程を示す断面図である。

【図41】同製造工程例のさらに続きの工程を示す断面図である。

【図42】同製造工程例のさらに続きの工程を示す断面図である。

【図43】同製造工程例のさらに続きの工程を示す断面図である。

【図44】厚いゲート絶縁膜を備えたLOCOSオフセットトランジスタを形成する際の不具合を説明するための工程断面図である。

【図45】図44の続きの工程を示す断面図である。

【図46】図45の続きの工程を示す断面図である。

【図47】図46の破線円で囲まれた部分を拡大して示す断面図である。

【図48】本願発明の積層ゲート電極構造を通常のMOSトランジスタに適用した場合の不具合を説明するための断面図である。

【図49】従来構造のLOCOSオフセットトランジスタを用いて、3種類のゲート電圧値に対応した3種類のLOCOSオフセットトランジスタを同一半導体基板に混載した様子を概略的に示す断面図である。

【符号の説明】

【0123】

1 半導体基板

3d N−ドレイン領域

3s N−ソース領域

5 チャネル領域

7 ゲート絶縁膜

9 第1ゲート電極

11 ゲート電極間絶縁膜

13,13−1,13−2,13−3 第2ゲート電極

15 LOCOS酸化膜(フィールド絶縁膜)

19g ゲート配線

27 多結晶シリコンパターン(第2ゲート電極と同一材料で同時形成されたパターン)

41u 第1容量素子電極

41t 第2容量素子電極

43 容量素子電極間絶縁膜

【特許請求の範囲】

【請求項1】

第1導電型の半導体基板の表面側に互いに間隔をもって配置された第2導電型のドレイン領域及びソース領域と、前記ソース領域とドレイン領域の間の前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極とをもち、前記ソース領域とドレイン領域の間の前記半導体基板がチャネル領域となっているMOSトランジスタを備えた半導体装置において、

前記ドレイン領域は、前記ゲート絶縁膜及び前記チャネル領域とは間隔をもって配置された第1ドレイン領域と、前記第1ドレイン領域と前記チャネル領域の間に前記第1ドレイン領域及び前記チャネル領域に隣接して配置された第2ドレイン領域とからなり、

前記ゲート電極は、前記ゲート絶縁膜上に形成された第1ゲート電極と、前記第1ゲート電極上にゲート電極間絶縁膜を介して形成された第2ゲート電極とからなり、

前記第2ゲート電極にはゲート電圧を与えるためのゲート配線が接続されており、前記第1ゲート電極には前記ゲート配線は接続されておらず、

前記半導体基板表面に前記ゲート絶縁膜よりも厚い厚みをもつフィールド絶縁膜を備え、

前記フィールド絶縁膜は少なくとも前記ゲート絶縁膜と前記第1ドレイン領域の間の前記半導体基板表面に配置されており、

前記第1ゲート電極の前記ドレイン領域側の端部は前記フィールド絶縁膜上に配置されていることを特徴とする半導体装置。

【請求項2】

上方から見て、前記第2ゲート電極の端部は前記第1ゲート電極上のみに配置されている請求項1に記載の半導体装置。

【請求項3】

前記第1ゲート電極の端部及び側面を覆い、かつ前記第2ゲート電極とは間隔をもって配置された、前記第2ゲート電極と同一材料で同時に形成されたパターンが形成されている請求項2に記載の半導体装置。

【請求項4】

上方から見て、前記第2ゲート電極の端部の一部分又は全部が前記第1ゲート電極の端部よりも外側に配置されており、前記第1ゲート電極の端部よりも外側に配置されている前記第2ゲート電極部分は前記フィールド絶縁膜上に配置されており、かつ前記第1ゲート電極とは前記ゲート電極間絶縁膜を介している請求項1に記載の半導体装置。

【請求項5】

上方から見て、前記第2ゲート電極の端部の全部が前記第1ゲート電極の端部よりも外側に配置されており、前記第2ゲート電極は前記第1ゲート電極の端部及び側面を覆っている請求項4に記載の半導体装置。

【請求項6】

上方から見て、前記第1ゲート電極上で前記第1ゲート電極の端部とは間隔をもつ位置に前記第2ゲート電極が形成されていない領域が存在している請求項5に記載の半導体装置。

【請求項7】

前記第1ゲート電極と前記第2ゲート電極の間の容量値が互いに異なる複数の前記MOSトランジスタを備えている請求項1から6のいずれか一項に記載の半導体装置。

【請求項8】

前記複数のMOSトランジスタにおいて、前記第2ゲート電極のレイアウト面積のみが互いに異なっている請求項7に記載の半導体装置。

【請求項9】

前記半導体基板上に、前記第1ゲート電極と同一材料で同時に形成された第1容量素子電極と、前記第1容量素子電極上に絶縁膜を介して前記第2ゲート電極と同一材料で同時に形成された第2容量素子電極をもつ容量素子をさらに備えている請求項1から8のいずれか一項に記載の半導体装置。

【請求項1】

第1導電型の半導体基板の表面側に互いに間隔をもって配置された第2導電型のドレイン領域及びソース領域と、前記ソース領域とドレイン領域の間の前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極とをもち、前記ソース領域とドレイン領域の間の前記半導体基板がチャネル領域となっているMOSトランジスタを備えた半導体装置において、

前記ドレイン領域は、前記ゲート絶縁膜及び前記チャネル領域とは間隔をもって配置された第1ドレイン領域と、前記第1ドレイン領域と前記チャネル領域の間に前記第1ドレイン領域及び前記チャネル領域に隣接して配置された第2ドレイン領域とからなり、

前記ゲート電極は、前記ゲート絶縁膜上に形成された第1ゲート電極と、前記第1ゲート電極上にゲート電極間絶縁膜を介して形成された第2ゲート電極とからなり、

前記第2ゲート電極にはゲート電圧を与えるためのゲート配線が接続されており、前記第1ゲート電極には前記ゲート配線は接続されておらず、

前記半導体基板表面に前記ゲート絶縁膜よりも厚い厚みをもつフィールド絶縁膜を備え、

前記フィールド絶縁膜は少なくとも前記ゲート絶縁膜と前記第1ドレイン領域の間の前記半導体基板表面に配置されており、

前記第1ゲート電極の前記ドレイン領域側の端部は前記フィールド絶縁膜上に配置されていることを特徴とする半導体装置。

【請求項2】

上方から見て、前記第2ゲート電極の端部は前記第1ゲート電極上のみに配置されている請求項1に記載の半導体装置。

【請求項3】

前記第1ゲート電極の端部及び側面を覆い、かつ前記第2ゲート電極とは間隔をもって配置された、前記第2ゲート電極と同一材料で同時に形成されたパターンが形成されている請求項2に記載の半導体装置。

【請求項4】

上方から見て、前記第2ゲート電極の端部の一部分又は全部が前記第1ゲート電極の端部よりも外側に配置されており、前記第1ゲート電極の端部よりも外側に配置されている前記第2ゲート電極部分は前記フィールド絶縁膜上に配置されており、かつ前記第1ゲート電極とは前記ゲート電極間絶縁膜を介している請求項1に記載の半導体装置。

【請求項5】

上方から見て、前記第2ゲート電極の端部の全部が前記第1ゲート電極の端部よりも外側に配置されており、前記第2ゲート電極は前記第1ゲート電極の端部及び側面を覆っている請求項4に記載の半導体装置。

【請求項6】

上方から見て、前記第1ゲート電極上で前記第1ゲート電極の端部とは間隔をもつ位置に前記第2ゲート電極が形成されていない領域が存在している請求項5に記載の半導体装置。

【請求項7】

前記第1ゲート電極と前記第2ゲート電極の間の容量値が互いに異なる複数の前記MOSトランジスタを備えている請求項1から6のいずれか一項に記載の半導体装置。

【請求項8】

前記複数のMOSトランジスタにおいて、前記第2ゲート電極のレイアウト面積のみが互いに異なっている請求項7に記載の半導体装置。

【請求項9】

前記半導体基板上に、前記第1ゲート電極と同一材料で同時に形成された第1容量素子電極と、前記第1容量素子電極上に絶縁膜を介して前記第2ゲート電極と同一材料で同時に形成された第2容量素子電極をもつ容量素子をさらに備えている請求項1から8のいずれか一項に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図48】

【図49】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図48】

【図49】

【公開番号】特開2008−244345(P2008−244345A)

【公開日】平成20年10月9日(2008.10.9)

【国際特許分類】

【出願番号】特願2007−85868(P2007−85868)

【出願日】平成19年3月28日(2007.3.28)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成20年10月9日(2008.10.9)

【国際特許分類】

【出願日】平成19年3月28日(2007.3.28)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]