半導体装置

【課題】第三者による不正な攻撃によって故障動作を引き起こされた場合でも、故障動作を検出し、回路動作を停止することが可能となるような半導体装置を提供する。

【解決手段】複数のフリップフロップを含む信号処理回路を有する半導体装置において、前記信号処理回路は、フリップフロップの入力信号を入力としパリティデータを生成する第1のパリティ生成回路と、前記第1のパリティ生成回路の出力をラッチするための、パリティ格納回路と、フリップフロップの出力信号を入力としパリティデータを生成する第2のパリティ生成回路と、前記パリティ格納回路の出力と第2のパリティ生成回路の出力とを比較し、不一致の場合に異常検出信号を出力するパリティ比較回路を備える。

【解決手段】複数のフリップフロップを含む信号処理回路を有する半導体装置において、前記信号処理回路は、フリップフロップの入力信号を入力としパリティデータを生成する第1のパリティ生成回路と、前記第1のパリティ生成回路の出力をラッチするための、パリティ格納回路と、フリップフロップの出力信号を入力としパリティデータを生成する第2のパリティ生成回路と、前記パリティ格納回路の出力と第2のパリティ生成回路の出力とを比較し、不一致の場合に異常検出信号を出力するパリティ比較回路を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、信号処理回路を有する半導体装置に関し、より特定的には、信号処理回路の故障動作を検知することにより、故障動作を利用した秘匿データの改竄、漏洩を防止するための技術に関する。

【背景技術】

【0002】

近年、メッセージの暗号化、デジタル署名、認証等を必要とするアプリケーションに使用するシステムLSIとして、暗号処理機能を備えたシステムLSIが増加している。それに伴い、信号処理回路の故障動作を利用した秘匿データの改竄、漏洩を防止するため、このようなセキュリティに関する機能を備えたLSIにとって耐タンパ性の向上が最重要課題となる。

【0003】

LSIに対する攻撃方法としては、チップを破壊して回路の観察や波形観測、回路の改造等を行う破壊攻撃と、チップを破壊せずにLSIの消費電力や電源波形から暗号鍵等を推定する非破壊攻撃とがある。非破壊攻撃の一つとして、処理の実行中にチップに加熱、放射線照射、光照射等により故障動作を発生させて、正常動作時と故障動作時との出力の違いから暗号鍵等を推定するDFA(Differential Fault Analysis)がある。

【0004】

光照射によるDFA対策として、光を検知する光検知素子をチップ上に配置し、強い光照射を検知するとCPUをリセットするなど、チップが動作しなくなるようにする対策がある。また、別の方法として、例えば特許文献1に開示されている技術では、論理的に同じ処理を行う回路に並行して処理をさせて、それらの出力に矛盾があれば処理を停止する方法が提案されている。

【特許文献1】特開2006−229485号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、上述した光検知素子を用いた対策では、特定箇所を誤動作させるために非常に小さい範囲を照射された場合には、検出することが困難であるという問題がある。また、特許文献1に開示されている技術のように、論理的に同じ処理を行う回路に並行して処理をさせる対策では、回路面積が大幅に増大してしまうという問題がある。

【0006】

それ故に、本発明の目的は、回路面積の増大を抑制しながら、信号処理回路の故障動作を検知し、故障動作を利用した秘匿データの改竄、漏洩を防止できる半導体装置を提供することである。

【課題を解決するための手段】

【0007】

本発明は、パリティデータを生成し、生成したパリティデータを比較することによって故障動作を検出する半導体装置に向けられている。本発明の半導体装置は、信号処理回路と制御回路とを備え、信号処理回路において、パリティデータを生成するパリティ生成回路と、パリティ生成回路で生成されたパリティデータをラッチするパリティ格納回路と、パリティ生成回路で生成されたパリティデータとパリティ格納回路にラッチされたパリティデータとを比較するパリティ比較回路とを備える。上記構成により、パリティ比較回路が、故障動作を検出した場合、制御回路に異常検知信号を出力し、制御回路は、信号処理回路から異常検出信号が入力された場合、リセット信号を出力し、信号処理回路の動作をリセットすることによって上記目的を達成させる。

【0008】

好ましい信号処理回路は、フリップフロップの入力信号を入力とし、パリティデータを生成する第1のパリティ生成回路と、第1のパリティ生成回路で生成したパリティデータをラッチするためのパリティ格納回路と、フリップフロップの出力信号を入力とし、パリティデータを生成する第2のパリティ生成回路と、パリティ格納回路にラッチしたパリティデータと第2のパリティ生成回路で生成したパリティデータとを比較し、不一致の場合異常検出信号を出力するパリティ比較回路とで構成される。

【0009】

この構成の場合、第三者による不正な攻撃によって信号処理回路内のフリップフロップの出力データが反転した場合であっても、パリティ格納回路にラッチしたパリティデータと第2のパリティ生成回路で生成したパリティデータとが異なる信号波形になるために、パリティ比較回路が異常検出信号を出力することで、故障動作の検出が可能である。この異常検出信号により、例えばCPUの動作を停止させることにより、故障動作を利用したDFAを防止することが可能となる。

【0010】

また、他の好ましい信号処理回路は、フリップフロップの入力信号を入力とし、パリティデータを生成するパリティ生成回路と、パリティ生成回路で生成したパリティデータを第1のタイミングでラッチするための、第1のパリティ格納回路と、パリティ生成回路で生成したパリティデータを第1のタイミングとは異なる第2のタイミングでラッチするための、第2のパリティ格納回路と、第2のパリティ格納回路にラッチしたパリティデータを第1のタイミングでラッチするための、第3のパリティ格納回路と、第1のパリティ格納回路にラッチしたパリティデータと第3のパリティ格納回路にラッチしたパリティデータとを比較し、不一致の場合、異常検出信号を出力するパリティ比較回路とで構成される。

【0011】

この構成の場合、第三者による不正な攻撃によって信号処理回路内の組合せ回路の出力データが反転した場合であっても、第1のパリティ格納回路にラッチしたパリティデータと第3のパリティ格納回路にラッチしたパリティデータとが異なる信号波形になるために、パリティ比較回路が異常検出信号を出力することで、故障動作の検出が可能となる。

【0012】

また、他の好ましい信号処理回路は、フリップフロップの入力信号を入力とし、パリティデータを生成する第1のパリティ生成回路と、第1のパリティ生成回路で生成したパリティデータを第1のタイミングでラッチするための、第1のパリティ格納回路と、第1のパリティ生成回路で生成したパリティデータを第1のタイミングとは異なる第2のタイミングでラッチするための、第2のパリティ格納回路と、第2のパリティ格納回路にラッチしたパリティデータを第1のタイミングでラッチするための、第3のパリティ格納回路と、フリップフロップの出力信号を入力とし、パリティデータを生成する第2のパリティ生成回路と、第1のパリティ格納回路にラッチしたパリティデータと第3のパリティ格納回路にラッチしたパリティデータと第2のパリティ生成回路で生成したパリティデータとを比較し、いずれか一つでも不一致の場合、異常検出信号を出力するパリティ比較回路とで構成される。

【0013】

この構成の場合、第三者による不正な攻撃によって信号処理回路内のフリップフロップの出力データ、または組合せ回路の出力データが反転した場合であっても、第1のパリティ格納回路にラッチしたパリティデータと第3のパリティ格納回路にラッチしたパリティデータと第2のパリティ生成回路で生成したパリティデータのいずれか一つが異なる信号波形になるために、パリティ比較回路が異常検出信号を出力することで、故障動作の検出が可能となる。

【発明の効果】

【0014】

上述のように、本発明によれば、小規模の回路の追加で、信号処理回路の故障動作を検知し、故障動作を利用した秘匿データの改竄、漏洩をできないようにすることができる。

【発明を実施するための最良の形態】

【0015】

以下、本発明を実施するための最良の形態について、図面を参照しながら説明する。図1は、本発明の第1〜3の実施形態に係る半導体装置のブロック図である。本実施形態の半導体装置は、信号処理回路10と、制御回路20とから構成されている。制御回路20には、信号処理回路10からの出力信号である異常検知信号が入力される。制御回路20は、信号処理回路10からの異常検出信号を判断し、異常を検出した場合、リセット信号を出力する。このリセット信号により、信号処理回路10の動作がリセットされる。尚、このリセット信号が出力された場合の信号処理回路10の動作を制御する方法としては、信号処理回路10への入力信号の遮断、または電源供給の停止等が挙げられる。信号処理回路10の回路は、例えば暗号処理回路であったり、CPUであったり、様々な回路が考えられる。

【0016】

以下、第1〜3の実施形態で、パリティデータによって故障動作を検知し、異常検知信号を出力する信号処理回路について、さらに詳しく説明する。

【0017】

(第1の実施形態)

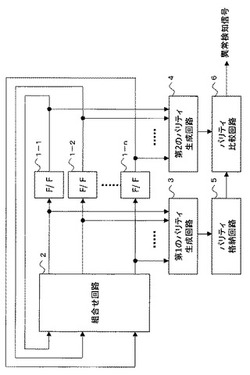

図2は、第1の実施形態に係る信号処理回路のブロック図である。本実施形態の信号処理回路は、n個のフリップフロップ(F/F)1−1〜1−nと、組合せ回路2と、第1のパリティ生成回路3と、第2のパリティ生成回路4と、パリティ格納回路5と、パリティ比較回路6とから構成されている。

【0018】

フリップフロップ1−1〜1−nは、システムクロックの立ち上がりでデータを取り込むディレイフリップフロップ(D−FF)である。また、第1のパリティ生成回路3と、第2のパリティ生成回路4とは、同じ構成の回路であり、偶数パリティを生成する回路である。パリティ格納回路5は、第1のパリティ生成回路3で生成されたパリティデータをラッチするための回路であり、システムクロックの立ち上がりのタイミングでデータを取り込むD−FFである。パリティ比較回路6は、パリティ格納回路5にラッチしたパリティデータと、第2のパリティ生成回路4で生成したパリティデータとを比較するための回路である。

【0019】

次に、図3Aおよび図3Bのタイミングチャートを参照しながら、図2の信号処理回路の動作について説明する。ここでは、本実施形態における図2の信号処理回路のうち、フリップフロップが、フリップフロップ1−1、フリップフロップ1−2、およびフリップフロップ1−3の3個の場合を例に挙げる。また、パリティ比較回路6から出力される異常検出信号のレベルを正常時はLow、異常検出時はHighとして説明する。

【0020】

図3Aおよび図3Bは、システムクロック、各フリップフロップの入力信号、出力信号、第1のパリティ生成回路3で生成されたパリティデータの出力、パリティ格納回路5にラッチされたパリティデータの出力、第2のパリティ生成回路4で生成されたパリティデータの出力、およびパリティ比較回路6から出力される異常検出信号の波形を示している。また、システムクロックの立ち上がりの時刻を順にt0、t1、t2、t3、t4、t5、およびt6とする。

【0021】

図3Aは、正常時の動作を示すタイミングチャートである。第1のパリティ生成回路3は、フリップフロップ1−1、フリップフロップ1−2、およびフリップフロップ1−3への入力信号を入力として、偶数パリティを生成している。

【0022】

また、フリップフロップ1−1、フリップフロップ1−2、およびフリップフロップ1−3は、システムクロックの立ち上がりでデータを取り込む。例えば、時刻t1と時刻t2の間で、フリップフロップ1−1の入力信号はLowからHighに変化しているが、フリップフロップ1−1の出力信号は、時刻t1と時刻t2の間では、Lowのままであり、システムクロックの立ち上がりである時刻t2でデータを取り込み、Highに変化する。

【0023】

また、第2のパリティ生成回路4は、フリップフロップ1−1、フリップフロップ1−2、およびフリップフロップ1−3から出力される出力信号を入力として、偶数パリティを生成している。

【0024】

また、第1のパリティ生成回路3の出力は、システムクロックが立ち上がるタイミングでパリティ格納回路5に取り込まれる。例えば、時刻t0と時刻t1の間で、第1のパリティ生成回路3の出力はLowからHighに変化しているが、パリティ格納回路5の出力は時刻t0とt1の間では、Lowのままであり、システムクロックの立ち上がりである時刻t1でデータを取り込み、Highに変化する。

【0025】

よって、正常時は、第2のパリティ生成回路4の出力とパリティ格納回路5の出力とは一致するので、異常検知信号はLowレベル出力となる。

【0026】

図3Bは、異常時の動作を示すタイミングチャートである。本実施形態では、時刻t4と時刻t5の間の時刻t4’において、第三者による不正な攻撃によってフリップフロップ1−1の出力信号が反転してしまった場合について説明する。なお、反転している部分を図3B中の反転部A1として示している。

【0027】

時刻t4’には、フリップフロップ1−1、フリップフロップ1−2、およびフリップフロップ1−3への入力信号は変化していないことから、第1のパリティ生成回路3の出力は変化せず、Lowのままである。また、正常時と同様、第1のパリティ生成回路3の出力は、システムクロックが立ち上がるタイミングでパリティ格納回路5に取り込まれる。

【0028】

一方、時刻t4’において、反転部A1に示すようにフリップフロップ1−1の出力信号は反転しているため、フリップフロップ1−1の出力信号を入力としてパリティデータを生成している第2のパリティ生成回路4の出力は、HighからLowへ変化する(図3B中の反転部A2)。よって、パリティ格納回路5の出力と時刻t4’に変化した第2のパリティ生成回路4の出力は不一致となり、異常検知信号がHighレベル出力となる(図3B中の反転部A3)。

【0029】

以上のように、本発明の第1の実施形態に係る半導体装置によれば、第三者による不正な攻撃によってフリップフロップの出力信号が反転してしまった場合、異常を検出し、回路動作をリセットすることで、故障動作を利用した暗号鍵の漏洩等を防止することが可能となる。また、異常検知に必要な回路は比較的小さいので、回路面積の増大を抑制しながらセキュリティを強化することが可能となる。

【0030】

(第2の実施形態)

図4は、第2の実施形態に係る信号処理回路のブロック図である。本実施形態の信号処理回路は、n個のフリップフロップ(F/F)1−1〜1−nと、組合せ回路2と、パリティ生成回路3と、第1のパリティ格納回路5と、第2のパリティ格納回路7と、第3のパリティ格納回路8と、パリティ比較回路6とから構成されている。

【0031】

フリップフロップ1−1〜1−nは、第1の実施形態と同様、システムクロックの立ち上がりでデータを取り込むディレイフリップフロップ(D−FF)であり、パリティ生成回路3は、偶数パリティを生成する回路である。また、第1のパリティ格納回路5は、パリティ生成回路3で生成したパリティデータをラッチするための回路であり、第1のタイミングでデータを取り込むD−FFである。第2のパリティ格納回路7は、パリティ生成回路3で生成したパリティデータをラッチするための回路であり、第1のタイミングとは異なる第2のタイミングでデータを取り込むD−FFである。第3のパリティ格納回路8は、第2のパリティ格納回路7にラッチしたパリティデータをラッチするための回路であり、第1のタイミングでデータを取り込むD−FFである。なお、この例では、第1のタイミングは、システムクロックの立ち上がりのタイミングとし、第1のタイミングとは異なる第2のタイミングは、システムクロックの立ち下がりのタイミングとしている。パリティ比較回路6は、第1のパリティ格納回路5にラッチしたパリティデータと、第3のパリティ格納回路8にラッチしたパリティデータとを比較するための回路である。

【0032】

次に、図5Aおよび図5Bのタイミングチャートを参照しながら、図4の信号処理回路の動作について説明する。ここでは、本実施形態における図4の信号処理回路のうち、フリップフロップが、フリップフロップ1−1、フリップフロップ1−2、およびフリップフロップ1−3の3個の場合を例に挙げる。また、パリティ比較回路6から出力される異常検出信号のレベルを正常時はLow、異常検出時はHighとして説明する。

【0033】

図5Aおよび図5Bは、システムクロック、各フリップフロップの入力信号、パリティ生成回路3で生成されたパリティデータの出力、第1のパリティ格納回路5にラッチされたパリティデータの出力、第2のパリティ格納回路7にラッチされたパリティデータの出力、第3のパリティ格納回路8にラッチされたパリティデータの出力、およびパリティ比較回路6から出力される異常検出信号の波形を示している。また、システムクロックの立ち上がりの時刻を順にt0、t1、t2、t3、t4、t5、およびt6とする。

【0034】

図5Aは、正常時の動作を示すタイミングチャートである。パリティ生成回路3は、フリップフロップ1−1、フリップフロップ1−2、およびフリップフロップ1−3への入力信号を入力として、偶数パリティを生成している。

【0035】

また、パリティ生成回路3の出力は、システムクロックの立ち上がるタイミングで第1のパリティ格納回路5に取り込まれ、システムクロックの立ち下がるタイミングで第2のパリティ格納回路7に取り込まれる。例えば、時刻t0とシステムクロックの立ち下がりである時刻t0’間で、パリティ生成回路3の出力はLowからHighに変化しているが、第1のパリティ格納回路5の出力は、システムクロックの立ち上がりである時刻t1でデータを取り込み、LowからHighに変化する。

【0036】

一方、第2のパリティ格納回路7は、システムクロックの立ち下がりである時刻t0’のタイミングでデータを取り込み、LowからHighに変化する。さらに、第3のパリティ格納回路8は、システムクロックの立ち上がるタイミングで、第2のパリティ格納回路7の出力を取り込む。つまり、上記の場合、時刻t1のタイミングでデータを取り込む。

【0037】

よって、正常時は、第1のパリティ格納回路5の出力と第3のパリティ格納回路8の出力とは一致するので、異常検知信号はLowレベル出力となる。

【0038】

図5Bは、異常時の動作を示すタイミングチャートである。本実施形態では、時刻t3と時刻t4の間の時刻t3’において、第三者による不正な攻撃によって組合せ回路2の出力信号の一つが反転してしまった場合について説明する。なお、反転している部分を図5B中の反転部B1とする。

【0039】

時刻t3’において、反転部B1に示すようにパリティ生成回路3の入力の一つであるフリップフロップ1−3への入力信号が反転しているため、パリティ生成回路3の出力は、HighからLowへ変化する(図5B中の反転部B2)。また、正常時と同様、パリティ生成回路3の出力は、システムクロックが立ち上がるタイミングである時刻t4で、第1のパリティ格納回路5に取り込まれるため、時刻t4においてパリティ格納回路5の出力も反転してしまう(図5B中の反転部B3)。

【0040】

しかし、第2のパリティ格納回路7が、パリティ生成回路3の出力を取り込むタイミング、つまり、システムクロックが立ち下がる時刻t4’において、第三者による不正な攻撃によって反転していた信号が、正常状態に戻っている。このため、第2のパリティ格納回路7は、第三者による不正な攻撃によって反転した状態から元に戻った正常状態の信号より生成されたパリティ生成回路3の出力をラッチする。さらに、第3のパリティ格納回路8は、システムクロックが立ち上がるタイミングで第2のパリティ格納回路7の出力をラッチする。つまり、時刻t5のタイミングでデータを取り込む。

【0041】

よって、第1のパリティ格納回路5の出力と第3のパリティ格納回路8の出力は、時刻t4と時刻t5の間において不一致となるため(図5B中の反転部B4)、異常検知信号がHighレベル出力となり、故障動作の検出が可能となる。

【0042】

以上のように、本発明の第2の実施形態に係る半導体装置によれば、第三者による不正な攻撃によって組合せ回路の出力信号が反転してしまった場合、異常を検出し、回路動作をリセットすることで、故障動作を利用した暗号鍵の漏洩等を防止することが可能となる。また、異常検知に必要な回路は比較的小さいので、回路面積の増大を抑制しながらセキュリティを強化することが可能となる。

【0043】

なお、本実施形態では、各D−FFがデータを取り込むタイミングとして、第1のタイミングはシステムクロックの立ち上がりとし、第2のタイミングは当該システムクロックの立ち下がりとしたが、例えば、当該システムクロックとは周波数の異なる第2のシステムクロックを生成し、第2のシステムクロックの立ち上がりのタイミングを第2のタイミングとしても構わない。

【0044】

(第3の実施形態)

図6は、第3の実施形態に係る信号処理回路のブロック図である。本実施形態の信号処理回路は、n個のフリップフロップ(F/F)1−1〜1−nと、組合せ回路2と、第1のパリティ生成回路3と、第2のパリティ生成回路4と、第1のパリティ格納回路5と、第2のパリティ格納回路7と、第3のパリティ格納回路8と、パリティ比較回路6とから構成されている。

【0045】

本実施形態は、第1の実施形態と第2の実施形態を組み合わせたものであり、各構成要素の基本的な動作は上述した実施形態で示した内容と同様である。フリップフロップ1−1〜1−nは、システムクロックの立ち上がりでデータを取り込むディレイフリップフロップ(D−FF)であり、第1のパリティ生成回路3と、第2のパリティ生成回路4とは、偶数パリティを生成する回路である。

【0046】

第1のパリティ格納回路5は、第1のパリティ生成回路3で生成したパリティデータを、システムクロックの立ち上がりのタイミングで取り込むD−FFであり、第2のパリティ格納回路7は、第1のパリティ生成回路3で生成したパリティデータを、システムクロックの立ち下がりのタイミングで取り込むD−FFであり、第3のパリティ格納回路8は、第2のパリティ格納回路7にラッチしたパリティデータを、システムクロックの立ち上がりのタイミングで取り込むD−FFである。パリティ比較回路6は、第1のパリティ格納回路5にラッチしたパリティデータと、第3のパリティ格納回路8にラッチしたパリティデータと、第2のパリティ生成回路4で生成したパリティデータとを比較するための回路である。

【0047】

本実施形態は、第1の実施形態に示したフリップフロップの出力信号の反転による故障の検出と、第2の実施形態に示した組合せ回路の出力信号の反転による故障の検出とを同時に行う構成になっている。すなわち、第三者による不正な攻撃によってフリップフロップの出力信号が反転した場合には、第1のパリティ格納回路5の出力と、第2のパリティ生成回路4の出力が異なる信号となり異常検出信号が出力され、組合せ回路の出力信号の反転した場合には、第1のパリティ格納回路5の出力と、第3のパリティ格納回路8の出力が異なる信号となり異常検出信号が出力される。

【0048】

以上のように、本発明の第3の実施形態に係る半導体装置によれば、第三者による不正な攻撃によってフリップフロップの出力信号が反転してしまった場合や、組合せ回路の出力信号が反転してしまった場合、異常を検出し、回路動作をリセットすることで、故障動作を利用した暗号鍵の漏洩等を防止することが可能となる。また、異常検知に必要な回路は比較的小さいので、回路面積の増大を抑制しながらセキュリティを強化することが可能となる。

【0049】

(第4の実施形態)

図7は、第4の実施形態に係る半導体装置のブロック図である。本実施形態の半導体装置は、n個の信号処理回路10−1〜10−nと、制御回路20とから構成されている。

【0050】

信号処理回路10−1〜10−nは、第1〜3の実施形態で示したいずれかの信号処理回路である。制御回路20は、各信号処理回路10−1〜10−nからの出力信号である異常検知信号1〜nが入力され、異常検出信号により一つでも異常を検出した場合、リセット信号を出力する。このリセット信号により、すべての信号処理回路10−1〜10−nの動作がリセットされる。

【0051】

以上のように、本発明の第4の実施形態に係る半導体装置によれば、第三者による不正な攻撃によって任意の1つの信号処理回路が異常を検知した場合、すべての信号処理回路の動作をリセットすることで、故障動作を利用した暗号鍵の漏洩等を防止することが可能となる。

【産業上の利用可能性】

【0052】

本発明に係る半導体装置は、メッセージの暗号化、デジタル署名、認証等を必要とするアプリケーションに使用される耐タンパ性の向上が要求されるシステムLSI等の半導体装置において有用である。

【図面の簡単な説明】

【0053】

【図1】第1〜3の実施形態に係る半導体装置の構成図

【図2】第1の実施形態に係る信号処理回路の構成図

【図3A】図2に示した信号処理回路の正常時の動作を示すタイミングチャート

【図3B】図2に示した信号処理回路の異常時の動作を示すタイミングチャート

【図4】第2の実施形態に係る信号処理回路の構成図

【図5A】図4に示した信号処理回路の正常時の動作を示すタイミングチャート

【図5B】図4に示した信号処理回路の異常時の動作を示すタイミングチャート

【図6】第3の実施形態に係る信号処理回路の構成図

【図7】第4の実施形態に係る半導体装置の構成図

【符号の説明】

【0054】

1−1〜1−n フリップフロップ

2 組合せ回路

3、4 パリティ生成回路

5、7、8 パリティ格納回路

6 パリティ比較回路

10、10−1〜10−n 信号処理回路

20 制御回路

【技術分野】

【0001】

本発明は、信号処理回路を有する半導体装置に関し、より特定的には、信号処理回路の故障動作を検知することにより、故障動作を利用した秘匿データの改竄、漏洩を防止するための技術に関する。

【背景技術】

【0002】

近年、メッセージの暗号化、デジタル署名、認証等を必要とするアプリケーションに使用するシステムLSIとして、暗号処理機能を備えたシステムLSIが増加している。それに伴い、信号処理回路の故障動作を利用した秘匿データの改竄、漏洩を防止するため、このようなセキュリティに関する機能を備えたLSIにとって耐タンパ性の向上が最重要課題となる。

【0003】

LSIに対する攻撃方法としては、チップを破壊して回路の観察や波形観測、回路の改造等を行う破壊攻撃と、チップを破壊せずにLSIの消費電力や電源波形から暗号鍵等を推定する非破壊攻撃とがある。非破壊攻撃の一つとして、処理の実行中にチップに加熱、放射線照射、光照射等により故障動作を発生させて、正常動作時と故障動作時との出力の違いから暗号鍵等を推定するDFA(Differential Fault Analysis)がある。

【0004】

光照射によるDFA対策として、光を検知する光検知素子をチップ上に配置し、強い光照射を検知するとCPUをリセットするなど、チップが動作しなくなるようにする対策がある。また、別の方法として、例えば特許文献1に開示されている技術では、論理的に同じ処理を行う回路に並行して処理をさせて、それらの出力に矛盾があれば処理を停止する方法が提案されている。

【特許文献1】特開2006−229485号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、上述した光検知素子を用いた対策では、特定箇所を誤動作させるために非常に小さい範囲を照射された場合には、検出することが困難であるという問題がある。また、特許文献1に開示されている技術のように、論理的に同じ処理を行う回路に並行して処理をさせる対策では、回路面積が大幅に増大してしまうという問題がある。

【0006】

それ故に、本発明の目的は、回路面積の増大を抑制しながら、信号処理回路の故障動作を検知し、故障動作を利用した秘匿データの改竄、漏洩を防止できる半導体装置を提供することである。

【課題を解決するための手段】

【0007】

本発明は、パリティデータを生成し、生成したパリティデータを比較することによって故障動作を検出する半導体装置に向けられている。本発明の半導体装置は、信号処理回路と制御回路とを備え、信号処理回路において、パリティデータを生成するパリティ生成回路と、パリティ生成回路で生成されたパリティデータをラッチするパリティ格納回路と、パリティ生成回路で生成されたパリティデータとパリティ格納回路にラッチされたパリティデータとを比較するパリティ比較回路とを備える。上記構成により、パリティ比較回路が、故障動作を検出した場合、制御回路に異常検知信号を出力し、制御回路は、信号処理回路から異常検出信号が入力された場合、リセット信号を出力し、信号処理回路の動作をリセットすることによって上記目的を達成させる。

【0008】

好ましい信号処理回路は、フリップフロップの入力信号を入力とし、パリティデータを生成する第1のパリティ生成回路と、第1のパリティ生成回路で生成したパリティデータをラッチするためのパリティ格納回路と、フリップフロップの出力信号を入力とし、パリティデータを生成する第2のパリティ生成回路と、パリティ格納回路にラッチしたパリティデータと第2のパリティ生成回路で生成したパリティデータとを比較し、不一致の場合異常検出信号を出力するパリティ比較回路とで構成される。

【0009】

この構成の場合、第三者による不正な攻撃によって信号処理回路内のフリップフロップの出力データが反転した場合であっても、パリティ格納回路にラッチしたパリティデータと第2のパリティ生成回路で生成したパリティデータとが異なる信号波形になるために、パリティ比較回路が異常検出信号を出力することで、故障動作の検出が可能である。この異常検出信号により、例えばCPUの動作を停止させることにより、故障動作を利用したDFAを防止することが可能となる。

【0010】

また、他の好ましい信号処理回路は、フリップフロップの入力信号を入力とし、パリティデータを生成するパリティ生成回路と、パリティ生成回路で生成したパリティデータを第1のタイミングでラッチするための、第1のパリティ格納回路と、パリティ生成回路で生成したパリティデータを第1のタイミングとは異なる第2のタイミングでラッチするための、第2のパリティ格納回路と、第2のパリティ格納回路にラッチしたパリティデータを第1のタイミングでラッチするための、第3のパリティ格納回路と、第1のパリティ格納回路にラッチしたパリティデータと第3のパリティ格納回路にラッチしたパリティデータとを比較し、不一致の場合、異常検出信号を出力するパリティ比較回路とで構成される。

【0011】

この構成の場合、第三者による不正な攻撃によって信号処理回路内の組合せ回路の出力データが反転した場合であっても、第1のパリティ格納回路にラッチしたパリティデータと第3のパリティ格納回路にラッチしたパリティデータとが異なる信号波形になるために、パリティ比較回路が異常検出信号を出力することで、故障動作の検出が可能となる。

【0012】

また、他の好ましい信号処理回路は、フリップフロップの入力信号を入力とし、パリティデータを生成する第1のパリティ生成回路と、第1のパリティ生成回路で生成したパリティデータを第1のタイミングでラッチするための、第1のパリティ格納回路と、第1のパリティ生成回路で生成したパリティデータを第1のタイミングとは異なる第2のタイミングでラッチするための、第2のパリティ格納回路と、第2のパリティ格納回路にラッチしたパリティデータを第1のタイミングでラッチするための、第3のパリティ格納回路と、フリップフロップの出力信号を入力とし、パリティデータを生成する第2のパリティ生成回路と、第1のパリティ格納回路にラッチしたパリティデータと第3のパリティ格納回路にラッチしたパリティデータと第2のパリティ生成回路で生成したパリティデータとを比較し、いずれか一つでも不一致の場合、異常検出信号を出力するパリティ比較回路とで構成される。

【0013】

この構成の場合、第三者による不正な攻撃によって信号処理回路内のフリップフロップの出力データ、または組合せ回路の出力データが反転した場合であっても、第1のパリティ格納回路にラッチしたパリティデータと第3のパリティ格納回路にラッチしたパリティデータと第2のパリティ生成回路で生成したパリティデータのいずれか一つが異なる信号波形になるために、パリティ比較回路が異常検出信号を出力することで、故障動作の検出が可能となる。

【発明の効果】

【0014】

上述のように、本発明によれば、小規模の回路の追加で、信号処理回路の故障動作を検知し、故障動作を利用した秘匿データの改竄、漏洩をできないようにすることができる。

【発明を実施するための最良の形態】

【0015】

以下、本発明を実施するための最良の形態について、図面を参照しながら説明する。図1は、本発明の第1〜3の実施形態に係る半導体装置のブロック図である。本実施形態の半導体装置は、信号処理回路10と、制御回路20とから構成されている。制御回路20には、信号処理回路10からの出力信号である異常検知信号が入力される。制御回路20は、信号処理回路10からの異常検出信号を判断し、異常を検出した場合、リセット信号を出力する。このリセット信号により、信号処理回路10の動作がリセットされる。尚、このリセット信号が出力された場合の信号処理回路10の動作を制御する方法としては、信号処理回路10への入力信号の遮断、または電源供給の停止等が挙げられる。信号処理回路10の回路は、例えば暗号処理回路であったり、CPUであったり、様々な回路が考えられる。

【0016】

以下、第1〜3の実施形態で、パリティデータによって故障動作を検知し、異常検知信号を出力する信号処理回路について、さらに詳しく説明する。

【0017】

(第1の実施形態)

図2は、第1の実施形態に係る信号処理回路のブロック図である。本実施形態の信号処理回路は、n個のフリップフロップ(F/F)1−1〜1−nと、組合せ回路2と、第1のパリティ生成回路3と、第2のパリティ生成回路4と、パリティ格納回路5と、パリティ比較回路6とから構成されている。

【0018】

フリップフロップ1−1〜1−nは、システムクロックの立ち上がりでデータを取り込むディレイフリップフロップ(D−FF)である。また、第1のパリティ生成回路3と、第2のパリティ生成回路4とは、同じ構成の回路であり、偶数パリティを生成する回路である。パリティ格納回路5は、第1のパリティ生成回路3で生成されたパリティデータをラッチするための回路であり、システムクロックの立ち上がりのタイミングでデータを取り込むD−FFである。パリティ比較回路6は、パリティ格納回路5にラッチしたパリティデータと、第2のパリティ生成回路4で生成したパリティデータとを比較するための回路である。

【0019】

次に、図3Aおよび図3Bのタイミングチャートを参照しながら、図2の信号処理回路の動作について説明する。ここでは、本実施形態における図2の信号処理回路のうち、フリップフロップが、フリップフロップ1−1、フリップフロップ1−2、およびフリップフロップ1−3の3個の場合を例に挙げる。また、パリティ比較回路6から出力される異常検出信号のレベルを正常時はLow、異常検出時はHighとして説明する。

【0020】

図3Aおよび図3Bは、システムクロック、各フリップフロップの入力信号、出力信号、第1のパリティ生成回路3で生成されたパリティデータの出力、パリティ格納回路5にラッチされたパリティデータの出力、第2のパリティ生成回路4で生成されたパリティデータの出力、およびパリティ比較回路6から出力される異常検出信号の波形を示している。また、システムクロックの立ち上がりの時刻を順にt0、t1、t2、t3、t4、t5、およびt6とする。

【0021】

図3Aは、正常時の動作を示すタイミングチャートである。第1のパリティ生成回路3は、フリップフロップ1−1、フリップフロップ1−2、およびフリップフロップ1−3への入力信号を入力として、偶数パリティを生成している。

【0022】

また、フリップフロップ1−1、フリップフロップ1−2、およびフリップフロップ1−3は、システムクロックの立ち上がりでデータを取り込む。例えば、時刻t1と時刻t2の間で、フリップフロップ1−1の入力信号はLowからHighに変化しているが、フリップフロップ1−1の出力信号は、時刻t1と時刻t2の間では、Lowのままであり、システムクロックの立ち上がりである時刻t2でデータを取り込み、Highに変化する。

【0023】

また、第2のパリティ生成回路4は、フリップフロップ1−1、フリップフロップ1−2、およびフリップフロップ1−3から出力される出力信号を入力として、偶数パリティを生成している。

【0024】

また、第1のパリティ生成回路3の出力は、システムクロックが立ち上がるタイミングでパリティ格納回路5に取り込まれる。例えば、時刻t0と時刻t1の間で、第1のパリティ生成回路3の出力はLowからHighに変化しているが、パリティ格納回路5の出力は時刻t0とt1の間では、Lowのままであり、システムクロックの立ち上がりである時刻t1でデータを取り込み、Highに変化する。

【0025】

よって、正常時は、第2のパリティ生成回路4の出力とパリティ格納回路5の出力とは一致するので、異常検知信号はLowレベル出力となる。

【0026】

図3Bは、異常時の動作を示すタイミングチャートである。本実施形態では、時刻t4と時刻t5の間の時刻t4’において、第三者による不正な攻撃によってフリップフロップ1−1の出力信号が反転してしまった場合について説明する。なお、反転している部分を図3B中の反転部A1として示している。

【0027】

時刻t4’には、フリップフロップ1−1、フリップフロップ1−2、およびフリップフロップ1−3への入力信号は変化していないことから、第1のパリティ生成回路3の出力は変化せず、Lowのままである。また、正常時と同様、第1のパリティ生成回路3の出力は、システムクロックが立ち上がるタイミングでパリティ格納回路5に取り込まれる。

【0028】

一方、時刻t4’において、反転部A1に示すようにフリップフロップ1−1の出力信号は反転しているため、フリップフロップ1−1の出力信号を入力としてパリティデータを生成している第2のパリティ生成回路4の出力は、HighからLowへ変化する(図3B中の反転部A2)。よって、パリティ格納回路5の出力と時刻t4’に変化した第2のパリティ生成回路4の出力は不一致となり、異常検知信号がHighレベル出力となる(図3B中の反転部A3)。

【0029】

以上のように、本発明の第1の実施形態に係る半導体装置によれば、第三者による不正な攻撃によってフリップフロップの出力信号が反転してしまった場合、異常を検出し、回路動作をリセットすることで、故障動作を利用した暗号鍵の漏洩等を防止することが可能となる。また、異常検知に必要な回路は比較的小さいので、回路面積の増大を抑制しながらセキュリティを強化することが可能となる。

【0030】

(第2の実施形態)

図4は、第2の実施形態に係る信号処理回路のブロック図である。本実施形態の信号処理回路は、n個のフリップフロップ(F/F)1−1〜1−nと、組合せ回路2と、パリティ生成回路3と、第1のパリティ格納回路5と、第2のパリティ格納回路7と、第3のパリティ格納回路8と、パリティ比較回路6とから構成されている。

【0031】

フリップフロップ1−1〜1−nは、第1の実施形態と同様、システムクロックの立ち上がりでデータを取り込むディレイフリップフロップ(D−FF)であり、パリティ生成回路3は、偶数パリティを生成する回路である。また、第1のパリティ格納回路5は、パリティ生成回路3で生成したパリティデータをラッチするための回路であり、第1のタイミングでデータを取り込むD−FFである。第2のパリティ格納回路7は、パリティ生成回路3で生成したパリティデータをラッチするための回路であり、第1のタイミングとは異なる第2のタイミングでデータを取り込むD−FFである。第3のパリティ格納回路8は、第2のパリティ格納回路7にラッチしたパリティデータをラッチするための回路であり、第1のタイミングでデータを取り込むD−FFである。なお、この例では、第1のタイミングは、システムクロックの立ち上がりのタイミングとし、第1のタイミングとは異なる第2のタイミングは、システムクロックの立ち下がりのタイミングとしている。パリティ比較回路6は、第1のパリティ格納回路5にラッチしたパリティデータと、第3のパリティ格納回路8にラッチしたパリティデータとを比較するための回路である。

【0032】

次に、図5Aおよび図5Bのタイミングチャートを参照しながら、図4の信号処理回路の動作について説明する。ここでは、本実施形態における図4の信号処理回路のうち、フリップフロップが、フリップフロップ1−1、フリップフロップ1−2、およびフリップフロップ1−3の3個の場合を例に挙げる。また、パリティ比較回路6から出力される異常検出信号のレベルを正常時はLow、異常検出時はHighとして説明する。

【0033】

図5Aおよび図5Bは、システムクロック、各フリップフロップの入力信号、パリティ生成回路3で生成されたパリティデータの出力、第1のパリティ格納回路5にラッチされたパリティデータの出力、第2のパリティ格納回路7にラッチされたパリティデータの出力、第3のパリティ格納回路8にラッチされたパリティデータの出力、およびパリティ比較回路6から出力される異常検出信号の波形を示している。また、システムクロックの立ち上がりの時刻を順にt0、t1、t2、t3、t4、t5、およびt6とする。

【0034】

図5Aは、正常時の動作を示すタイミングチャートである。パリティ生成回路3は、フリップフロップ1−1、フリップフロップ1−2、およびフリップフロップ1−3への入力信号を入力として、偶数パリティを生成している。

【0035】

また、パリティ生成回路3の出力は、システムクロックの立ち上がるタイミングで第1のパリティ格納回路5に取り込まれ、システムクロックの立ち下がるタイミングで第2のパリティ格納回路7に取り込まれる。例えば、時刻t0とシステムクロックの立ち下がりである時刻t0’間で、パリティ生成回路3の出力はLowからHighに変化しているが、第1のパリティ格納回路5の出力は、システムクロックの立ち上がりである時刻t1でデータを取り込み、LowからHighに変化する。

【0036】

一方、第2のパリティ格納回路7は、システムクロックの立ち下がりである時刻t0’のタイミングでデータを取り込み、LowからHighに変化する。さらに、第3のパリティ格納回路8は、システムクロックの立ち上がるタイミングで、第2のパリティ格納回路7の出力を取り込む。つまり、上記の場合、時刻t1のタイミングでデータを取り込む。

【0037】

よって、正常時は、第1のパリティ格納回路5の出力と第3のパリティ格納回路8の出力とは一致するので、異常検知信号はLowレベル出力となる。

【0038】

図5Bは、異常時の動作を示すタイミングチャートである。本実施形態では、時刻t3と時刻t4の間の時刻t3’において、第三者による不正な攻撃によって組合せ回路2の出力信号の一つが反転してしまった場合について説明する。なお、反転している部分を図5B中の反転部B1とする。

【0039】

時刻t3’において、反転部B1に示すようにパリティ生成回路3の入力の一つであるフリップフロップ1−3への入力信号が反転しているため、パリティ生成回路3の出力は、HighからLowへ変化する(図5B中の反転部B2)。また、正常時と同様、パリティ生成回路3の出力は、システムクロックが立ち上がるタイミングである時刻t4で、第1のパリティ格納回路5に取り込まれるため、時刻t4においてパリティ格納回路5の出力も反転してしまう(図5B中の反転部B3)。

【0040】

しかし、第2のパリティ格納回路7が、パリティ生成回路3の出力を取り込むタイミング、つまり、システムクロックが立ち下がる時刻t4’において、第三者による不正な攻撃によって反転していた信号が、正常状態に戻っている。このため、第2のパリティ格納回路7は、第三者による不正な攻撃によって反転した状態から元に戻った正常状態の信号より生成されたパリティ生成回路3の出力をラッチする。さらに、第3のパリティ格納回路8は、システムクロックが立ち上がるタイミングで第2のパリティ格納回路7の出力をラッチする。つまり、時刻t5のタイミングでデータを取り込む。

【0041】

よって、第1のパリティ格納回路5の出力と第3のパリティ格納回路8の出力は、時刻t4と時刻t5の間において不一致となるため(図5B中の反転部B4)、異常検知信号がHighレベル出力となり、故障動作の検出が可能となる。

【0042】

以上のように、本発明の第2の実施形態に係る半導体装置によれば、第三者による不正な攻撃によって組合せ回路の出力信号が反転してしまった場合、異常を検出し、回路動作をリセットすることで、故障動作を利用した暗号鍵の漏洩等を防止することが可能となる。また、異常検知に必要な回路は比較的小さいので、回路面積の増大を抑制しながらセキュリティを強化することが可能となる。

【0043】

なお、本実施形態では、各D−FFがデータを取り込むタイミングとして、第1のタイミングはシステムクロックの立ち上がりとし、第2のタイミングは当該システムクロックの立ち下がりとしたが、例えば、当該システムクロックとは周波数の異なる第2のシステムクロックを生成し、第2のシステムクロックの立ち上がりのタイミングを第2のタイミングとしても構わない。

【0044】

(第3の実施形態)

図6は、第3の実施形態に係る信号処理回路のブロック図である。本実施形態の信号処理回路は、n個のフリップフロップ(F/F)1−1〜1−nと、組合せ回路2と、第1のパリティ生成回路3と、第2のパリティ生成回路4と、第1のパリティ格納回路5と、第2のパリティ格納回路7と、第3のパリティ格納回路8と、パリティ比較回路6とから構成されている。

【0045】

本実施形態は、第1の実施形態と第2の実施形態を組み合わせたものであり、各構成要素の基本的な動作は上述した実施形態で示した内容と同様である。フリップフロップ1−1〜1−nは、システムクロックの立ち上がりでデータを取り込むディレイフリップフロップ(D−FF)であり、第1のパリティ生成回路3と、第2のパリティ生成回路4とは、偶数パリティを生成する回路である。

【0046】

第1のパリティ格納回路5は、第1のパリティ生成回路3で生成したパリティデータを、システムクロックの立ち上がりのタイミングで取り込むD−FFであり、第2のパリティ格納回路7は、第1のパリティ生成回路3で生成したパリティデータを、システムクロックの立ち下がりのタイミングで取り込むD−FFであり、第3のパリティ格納回路8は、第2のパリティ格納回路7にラッチしたパリティデータを、システムクロックの立ち上がりのタイミングで取り込むD−FFである。パリティ比較回路6は、第1のパリティ格納回路5にラッチしたパリティデータと、第3のパリティ格納回路8にラッチしたパリティデータと、第2のパリティ生成回路4で生成したパリティデータとを比較するための回路である。

【0047】

本実施形態は、第1の実施形態に示したフリップフロップの出力信号の反転による故障の検出と、第2の実施形態に示した組合せ回路の出力信号の反転による故障の検出とを同時に行う構成になっている。すなわち、第三者による不正な攻撃によってフリップフロップの出力信号が反転した場合には、第1のパリティ格納回路5の出力と、第2のパリティ生成回路4の出力が異なる信号となり異常検出信号が出力され、組合せ回路の出力信号の反転した場合には、第1のパリティ格納回路5の出力と、第3のパリティ格納回路8の出力が異なる信号となり異常検出信号が出力される。

【0048】

以上のように、本発明の第3の実施形態に係る半導体装置によれば、第三者による不正な攻撃によってフリップフロップの出力信号が反転してしまった場合や、組合せ回路の出力信号が反転してしまった場合、異常を検出し、回路動作をリセットすることで、故障動作を利用した暗号鍵の漏洩等を防止することが可能となる。また、異常検知に必要な回路は比較的小さいので、回路面積の増大を抑制しながらセキュリティを強化することが可能となる。

【0049】

(第4の実施形態)

図7は、第4の実施形態に係る半導体装置のブロック図である。本実施形態の半導体装置は、n個の信号処理回路10−1〜10−nと、制御回路20とから構成されている。

【0050】

信号処理回路10−1〜10−nは、第1〜3の実施形態で示したいずれかの信号処理回路である。制御回路20は、各信号処理回路10−1〜10−nからの出力信号である異常検知信号1〜nが入力され、異常検出信号により一つでも異常を検出した場合、リセット信号を出力する。このリセット信号により、すべての信号処理回路10−1〜10−nの動作がリセットされる。

【0051】

以上のように、本発明の第4の実施形態に係る半導体装置によれば、第三者による不正な攻撃によって任意の1つの信号処理回路が異常を検知した場合、すべての信号処理回路の動作をリセットすることで、故障動作を利用した暗号鍵の漏洩等を防止することが可能となる。

【産業上の利用可能性】

【0052】

本発明に係る半導体装置は、メッセージの暗号化、デジタル署名、認証等を必要とするアプリケーションに使用される耐タンパ性の向上が要求されるシステムLSI等の半導体装置において有用である。

【図面の簡単な説明】

【0053】

【図1】第1〜3の実施形態に係る半導体装置の構成図

【図2】第1の実施形態に係る信号処理回路の構成図

【図3A】図2に示した信号処理回路の正常時の動作を示すタイミングチャート

【図3B】図2に示した信号処理回路の異常時の動作を示すタイミングチャート

【図4】第2の実施形態に係る信号処理回路の構成図

【図5A】図4に示した信号処理回路の正常時の動作を示すタイミングチャート

【図5B】図4に示した信号処理回路の異常時の動作を示すタイミングチャート

【図6】第3の実施形態に係る信号処理回路の構成図

【図7】第4の実施形態に係る半導体装置の構成図

【符号の説明】

【0054】

1−1〜1−n フリップフロップ

2 組合せ回路

3、4 パリティ生成回路

5、7、8 パリティ格納回路

6 パリティ比較回路

10、10−1〜10−n 信号処理回路

20 制御回路

【特許請求の範囲】

【請求項1】

複数のフリップフロップを含む信号処理回路を有する半導体装置であって、

前記信号処理回路は、

前記フリップフロップの入力信号を入力とし、パリティデータを生成する第1のパリティ生成回路と、

前記第1のパリティ生成回路で生成したパリティデータをラッチするための、パリティ格納回路と、

前記フリップフロップの出力信号を入力とし、パリティデータを生成する第2のパリティ生成回路と、

前記パリティ格納回路にラッチしたパリティデータと前記第2のパリティ生成回路で生成したパリティデータとを比較し、不一致の場合に異常検出信号を出力するパリティ比較回路とを備える、半導体装置。

【請求項2】

複数のフリップフロップを含む信号処理回路を有する半導体装置であって、

前記信号処理回路は、

前記フリップフロップの入力信号を入力とし、パリティデータを生成するパリティ生成回路と、

前記パリティ生成回路で生成したパリティデータを第1のタイミングでラッチするための、第1のパリティ格納回路と、

前記パリティ生成回路で生成したパリティデータを前記第1のタイミングとは異なる第2のタイミングでラッチするための、第2のパリティ格納回路と、

前記第2のパリティ格納回路にラッチしたパリティデータを前記第1のタイミングでラッチするための、第3のパリティ格納回路と、

前記第1のパリティ格納回路にラッチしたパリティデータと前記第3のパリティ格納回路にラッチしたパリティデータとを比較し、不一致の場合に異常検出信号を出力するパリティ比較回路とを備える、半導体装置。

【請求項3】

複数のフリップフロップを含む信号処理回路を有する半導体装置であって、

前記信号処理回路は、

前記フリップフロップの入力信号を入力とし、パリティデータを生成する第1のパリティ生成回路と、

前記第1のパリティ生成回路で生成したパリティデータを第1のタイミングでラッチするための、第1のパリティ格納回路と、

前記第1のパリティ生成回路で生成したパリティデータを前記第1のタイミングとは異なる第2のタイミングでラッチするための、第2のパリティ格納回路と、

前記第2のパリティ格納回路にラッチしたパリティデータを前記第1のタイミングでラッチするための、第3のパリティ格納回路と、

前記フリップフロップの出力信号を入力とし、パリティデータを生成する第2のパリティ生成回路と、

前記第1のパリティ格納回路にラッチしたパリティデータと前記第3のパリティ格納回路にラッチしたパリティデータと前記第2のパリティ生成回路で生成したパリティデータとを比較し、いずれか一つでも不一致の場合に異常検出信号を出力するパリティ比較回路とを備える、半導体装置。

【請求項4】

前記第1のタイミングは、システムクロックの立ち上がりのタイミングであり、

前記第1のタイミングとは異なる前記第2のタイミングは、システムクロックの立ち下がりのタイミングであることを特徴とする、請求項2又は3に記載の半導体装置。

【請求項1】

複数のフリップフロップを含む信号処理回路を有する半導体装置であって、

前記信号処理回路は、

前記フリップフロップの入力信号を入力とし、パリティデータを生成する第1のパリティ生成回路と、

前記第1のパリティ生成回路で生成したパリティデータをラッチするための、パリティ格納回路と、

前記フリップフロップの出力信号を入力とし、パリティデータを生成する第2のパリティ生成回路と、

前記パリティ格納回路にラッチしたパリティデータと前記第2のパリティ生成回路で生成したパリティデータとを比較し、不一致の場合に異常検出信号を出力するパリティ比較回路とを備える、半導体装置。

【請求項2】

複数のフリップフロップを含む信号処理回路を有する半導体装置であって、

前記信号処理回路は、

前記フリップフロップの入力信号を入力とし、パリティデータを生成するパリティ生成回路と、

前記パリティ生成回路で生成したパリティデータを第1のタイミングでラッチするための、第1のパリティ格納回路と、

前記パリティ生成回路で生成したパリティデータを前記第1のタイミングとは異なる第2のタイミングでラッチするための、第2のパリティ格納回路と、

前記第2のパリティ格納回路にラッチしたパリティデータを前記第1のタイミングでラッチするための、第3のパリティ格納回路と、

前記第1のパリティ格納回路にラッチしたパリティデータと前記第3のパリティ格納回路にラッチしたパリティデータとを比較し、不一致の場合に異常検出信号を出力するパリティ比較回路とを備える、半導体装置。

【請求項3】

複数のフリップフロップを含む信号処理回路を有する半導体装置であって、

前記信号処理回路は、

前記フリップフロップの入力信号を入力とし、パリティデータを生成する第1のパリティ生成回路と、

前記第1のパリティ生成回路で生成したパリティデータを第1のタイミングでラッチするための、第1のパリティ格納回路と、

前記第1のパリティ生成回路で生成したパリティデータを前記第1のタイミングとは異なる第2のタイミングでラッチするための、第2のパリティ格納回路と、

前記第2のパリティ格納回路にラッチしたパリティデータを前記第1のタイミングでラッチするための、第3のパリティ格納回路と、

前記フリップフロップの出力信号を入力とし、パリティデータを生成する第2のパリティ生成回路と、

前記第1のパリティ格納回路にラッチしたパリティデータと前記第3のパリティ格納回路にラッチしたパリティデータと前記第2のパリティ生成回路で生成したパリティデータとを比較し、いずれか一つでも不一致の場合に異常検出信号を出力するパリティ比較回路とを備える、半導体装置。

【請求項4】

前記第1のタイミングは、システムクロックの立ち上がりのタイミングであり、

前記第1のタイミングとは異なる前記第2のタイミングは、システムクロックの立ち下がりのタイミングであることを特徴とする、請求項2又は3に記載の半導体装置。

【図1】

【図2】

【図3A】

【図3B】

【図4】

【図5A】

【図5B】

【図6】

【図7】

【図2】

【図3A】

【図3B】

【図4】

【図5A】

【図5B】

【図6】

【図7】

【公開番号】特開2008−289086(P2008−289086A)

【公開日】平成20年11月27日(2008.11.27)

【国際特許分類】

【出願番号】特願2007−134460(P2007−134460)

【出願日】平成19年5月21日(2007.5.21)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成20年11月27日(2008.11.27)

【国際特許分類】

【出願日】平成19年5月21日(2007.5.21)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]