半導体装置

【課題】配線の断線を防止することができる半導体装置を提供する。

【解決手段】フィルム基板に実装されたインターポーザ基板と、インターポーザ基板に実装された半導体素子とを備え、インターポーザ基板は、複数個の第1基板金属バンプと、複数個の第1基板パッドメタル23と、複数本の基板配線24とを有し、半導体素子は、第1基板金属バンプとそれぞれ熱圧着により接合した複数個の素子金属バンプと、複数個の素子パッドメタル13と、複数本の素子配線14とを有する半導体装置であって、第1基板パッドメタル23および素子パッドメタル13は、各角が外側に向かって突き出る多角形状をしており、基板配線24は、それぞれ対応する第1基板パッドメタル23の角の頂点から間隔を空けた位置に接続され、素子配線14は、それぞれ対応する素子パッドメタル13の角の頂点から間隔を空けた位置に接続されている。

【解決手段】フィルム基板に実装されたインターポーザ基板と、インターポーザ基板に実装された半導体素子とを備え、インターポーザ基板は、複数個の第1基板金属バンプと、複数個の第1基板パッドメタル23と、複数本の基板配線24とを有し、半導体素子は、第1基板金属バンプとそれぞれ熱圧着により接合した複数個の素子金属バンプと、複数個の素子パッドメタル13と、複数本の素子配線14とを有する半導体装置であって、第1基板パッドメタル23および素子パッドメタル13は、各角が外側に向かって突き出る多角形状をしており、基板配線24は、それぞれ対応する第1基板パッドメタル23の角の頂点から間隔を空けた位置に接続され、素子配線14は、それぞれ対応する素子パッドメタル13の角の頂点から間隔を空けた位置に接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、金属バンプを用いたチップ複合型パッケージの半導体装置に関するものである。

【背景技術】

【0002】

半導体装置として、半導体素子を種々の実装形態で構成するチップ複合型パッケージがある。このような半導体装置では、半導体素子が、信号の入出力が可能なようにフィルム基板に実装されている。半導体装置の品質および信頼性を低下させないためには、実装に起因する不具合を防止する必要がある。

【0003】

例えば、TCP(Tape Carrier Package)やCOF(Chip on Film)の半導体装置における構成を説明する。半導体素子には、フィルム基板に実装させる面に、フィルム基板との接合部分に配置された素子外部接続電極、および、素子外部接続電極と素子内部とを接続するように引き回された素子配線が形成され、素子外部接続電極上に金からなる金属バンプが形成される。フィルム基板には、半導体素子を実装する面に、半導体素子の素子外部接続電極と相対する位置に配置された錫メッキした銅からなるインナーリード、および、インナーリードから基板外部に接続可能なように引き回された基板配線が形成される。

【0004】

これらの構成において、熱および圧力を加えながら金属バンプをインナーリードに押し付け、金−錫共晶で接合することにより、半導体素子をフィルム基板に実装することができる。なお、この接合方法はILB(Inner Lead Bonding)と呼ばれている。

【0005】

ここで、素子外部接続電極と素子配線とは同一の金属にてパターン形成されるが、その一方で性能を向上させるために、複数の金属配線層を重ねたものを素子配線に使用する場合がある。この場合、素子外部接続電極と素子配線とは異なる材料となるので、別個に形成して接続させる必要がある。

【0006】

例えば、特許文献1には、図9に示すように、外部接続金属配線部201に内部金属配線205と接続させるための突出部202を設け、突出部202に内部金属配線205を重ねて接続させる構成が記載されている。外部接続金属配線部201は、導電接続部分となる開口窓203および開口窓204以外の部分が絶縁保護膜により被覆されている。しかし、特に、突出部202の基端部X(外部に対して張る角度が90度の部分)に内部金属配線205が重なると、両者材料の熱膨張率などの差異から応力が加わり、絶縁保護膜にひずみおよび割れが生じやすい。そこで特許文献1では、内部金属配線205を基端部Xから間隔をおいた部位に布線させることにより、絶縁保護膜のひずみおよび割れを防止している。

【特許文献1】特開昭62−232940号公報(1987年10月13日公開)

【発明の開示】

【発明が解決しようとする課題】

【0007】

ところで、上述したパッケージの半導体装置では、金属バンプとインナーリードとを接合させる構成であったが、フィルム基板と半導体素子との間に、シリコン基板などからなるインターポーザ基板を介した構成を有する半導体装置もある。この半導体装置では、インターポーザ基板には、半導体素子を実装する面に、半導体素子の素子外部接続電極と相対する位置に配置された基板外部接続電極、および、基板外部接続電極から基板外部に接続可能なように引き回された基板配線が形成され、基板外部接続電極上に金からなる金属バンプが形成される。図10に、金属バンプを形成する前の、従来の一般的な外部接続電極101(素子外部接続電極、基板外部接続電極)および配線102(素子配線、基板配線)のパターン例を示す。

【0008】

半導体素子は、金属バンプ同士の接合によりインターポーザ基板に実装される。金属バンプとインナーリードとを接合させる場合、金−錫共晶させて接合するため、熱圧着の接合圧力は低く、接合圧力が不良を起こす原因とはなり難い。しかしながら、金属バンプ同士を接合させる場合、例えば金を金属バンプの材料として用いると、共晶しない金と金とを接合させるために、熱圧着の接合圧力を高める必要がある。このため、高い接合圧力により、各金属バンプ下の素子外部接続電極および基板外部接続電極にダメージ(ヒビや割れなどの損傷)が生じるという問題がある。また、半導体素子とインターポーザ基板とを接合後、両者材料の熱膨張率などの差異から、素子外部接続電極および基板外部接続電極に応力がそれぞれ加わりダメージが生じる場合もある。

【0009】

ダメージが生じたときの一例として、外部接続電極101にヒビが生じたときの状態を図11に示す。応力は金属バンプの根元に集中し易いので、外部接続電極101にも応力が加えられる。ヒビは、起点から、円弧を描きながら外側に向かって抜けようとする。このため、外部接続電極101に生じたヒビが、配線102が設けられている方向に伝達すると、配線102の断線という重大な問題が発生する。それゆえ、半導体装置の品質および信頼性を高く維持することはできない。

【0010】

また、接合圧力が高い場合に限らず、発生確率は低くなるが、接合圧力が低い金属バンプとインナーリードとを接合させる場合であっても、素子外部接続電極にダメージが生じる場合がある。例えば、金属バンプ全てがインナーリードに確実に接触するように、比較的強く押さえつけるため、金属バンプの高さのバラツキなどにより、最も高い金属バンプに応力集中が発生する場合である。

【0011】

本発明は、上記従来の問題点に鑑みなされたものであって、その目的は、配線の断線を防止することができる半導体装置を提供することにある。

【課題を解決するための手段】

【0012】

本発明の半導体装置は、上記課題を解決するために、基板に実装されたインターポーザ基板と、前記インターポーザ基板に実装された半導体素子とを備え、前記インターポーザ基板は、前記半導体素子が実装される位置に形成された複数個の基板金属部と、前記各基板金属部の上にそれぞれ形成された複数個の基板突起電極と、前記各基板金属部にそれぞれ接続された複数本の基板配線とを有し、前記半導体素子は、前記各基板突起電極とそれぞれ熱圧着により接合した複数個の素子突起電極と、前記各素子突起電極の下にそれぞれ形成された複数個の素子金属部と、前記各素子金属部にそれぞれ接続された複数本の素子配線とを有する半導体装置であって、前記各基板金属部および前記各素子金属部は、各角が外側に向かって突き出る多角形状をしており、前記各基板配線は、それぞれ対応する基板金属部の角の頂点から間隔を空けた位置に接続され、前記各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されていることを特徴としている。

【0013】

従来では、熱圧着時の接合圧力が高いほど、基板突起電極の下にある基板金属部、および、素子突起電極の下にある素子金属部にダメージ(ヒビや割れなどの損傷)が生じやすかった。このダメージは、基板配線および素子配線の断線という事態につながる。また、ダメージは、応力が集中し易い角を終点として入り易い。

【0014】

これに対し、上記の構成によれば、各基板配線は、それぞれ対応する基板金属部の角の頂点から間隔を空けた位置に接続され、各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されている。これにより、基板金属部素子および素子金属部に、例えばヒビが生じても、該ヒビによって基板配線および素子配線までヒビが伝達し断線することを防止することが可能となる。

【0015】

また、上記半導体素子をインターポーザ基板に実装したとき、各基板突起電極と各素子突起電極とが好適に熱圧着により接合するために、本発明の半導体装置は、前記各基板突起電極および前記各素子突起電極は、電気抵抗が3×10−8(Ω・m)以下の金属バンプによって構成されていることが望ましい。または、本発明の半導体装置は、前記各基板突起電極および前記各素子突起電極は、引っ張り強さが1.0×108(Pa)以上の金属バンプによって構成されているものに適用することが望ましい。

【0016】

また、本発明の半導体装置は、前記各基板突起電極および前記各素子突起電極は、直方体の形状を有しており、前記各素子配線は、それぞれ対応する素子突起電極における素子金属部に接する面の短辺側に配置されていることが好ましい。

【0017】

各基板突起電極および各素子突起電極が直方体の形状を有する場合、熱圧着によって、素子突起電極における素子金属部に接する面では、長辺方向への拡がりは小さく、短辺方向への拡がりは大きい。このため、素子金属部は、上記長辺方向へ拡がるように加わる力は小さいので寸断されにくいが、上記短辺方向へ拡がるように加わる力は大きいため、上記長辺方向に寸断されやすい。

【0018】

それゆえ、上記の構成によれば、各素子配線は、それぞれ対応する素子突起電極における素子金属部に接する面の短辺側に配置されていることにより、基板突起電極、素子突起電極、素子金属部、および素子配線とつながる経路におけるオープンの発生を防止することが可能となる。

【0019】

また、本発明の半導体装置は、前記各基板突起電極および前記各素子突起電極は、直方体の形状を有しており、前記各基板配線は、それぞれ対応する基板突起電極における基板金属部に接する面の短辺側に配置されていることが好ましい。

【0020】

各基板突起電極および各素子突起電極が直方体の形状を有する場合、熱圧着によって、基板突起電極における基板金属部に接する面では、長辺方向への拡がりは小さく、短辺方向への拡がりは大きい。このため、基板金属部は、上記長辺方向へ拡がるように加わる力は小さいので寸断されにくいが、上記短辺方向へ拡がるように加わる力は大きいため、上記長辺方向に寸断されやすい。

【0021】

それゆえ、上記の構成によれば、各基板配線は、それぞれ対応する基板突起電極における基板金属部に接する面の短辺側に配置されていることにより、素子突起電極、基板突起電極、基板金属部、および基板配線とつながる経路におけるオープンの発生を防止することが可能となる。

【0022】

また、半導体素子とインターポーザ基板との熱膨張率の差により、半導体素子とインターポーザ基板との変形量に差が生じる。このため、半導体素子における各素子突起電極が形成されている面の中心付近から離れるほど、半導体素子とインターポーザ基板との変形量の差が大きくなる。もし、この熱膨張による力により、上記短辺方向に寸断されてしまった場合、上記経路にオープンが発生する虞がある。

【0023】

それゆえ、熱膨張による上記短辺方向の寸断の発生を防止するために、本発明の半導体装置は、前記各素子突起電極は、それぞれ対応する素子金属部に接する面の長辺が、前記半導体素子における前記各素子突起電極が形成されている面の長辺と垂直になるように配置されていることが望ましい。また、本発明の半導体装置は、前記各基板突起電極は、それぞれ対応する基板金属部に接する面の長辺が、前記インターポーザ基板における前記各基板突起電極が形成されている面の長辺と垂直になるように配置されていることが望ましい。

【0024】

また、本発明の半導体装置は、上記課題を解決するために、フィルム基板と、前記フィルム基板に実装された半導体素子とを備え、前記フィルム基板は、前記半導体素子が実装される位置に形成された複数個の基板金属部と、前記各基板金属部にそれぞれ接続された複数本の基板配線とを有し、前記半導体素子は、前記各基板金属部とそれぞれ熱圧着により接合した複数個の素子突起電極と、前記各素子突起電極の下にそれぞれ形成された複数個の素子金属部と、前記各素子金属部にそれぞれ接続された複数本の素子配線とを有する半導体装置であって、前記各素子金属部は、各角が外側に向かって突き出る多角形状をしており、前記各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されていることを特徴としている。

【0025】

従来では、素子突起電極の高さのばらつきにより熱圧着時に応力集中が生じると、その応力が大きいほど、素子突起電極の下にある素子金属部にダメージ(ヒビや割れなどの損傷)が生じやすかった。このダメージは素子配線の断線という事態につながる。また、ダメージは応力が集中し易い角を終点として入り易い。

【0026】

これに対し、上記の構成によれば、各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されている。これにより、素子金属部に、例えばヒビが生じても、該ヒビによって素子配線までヒビが伝達し断線することを防止することが可能となる。

【0027】

また、上記半導体素子をフィルム基板に実装したとき、各基板金属部と各素子突起電極とが好適に熱圧着により接合するために、本発明の半導体装置は、前記各素子突起電極は、電気抵抗が3×10−8(Ω・m)以下の金属バンプによって構成されていることが望ましい。

【発明の効果】

【0028】

以上のように、本発明の半導体装置は、各基板金属部および各素子金属部は、各角が外側に向かって突き出る多角形状をしており、各基板配線は、それぞれ対応する基板金属部の角の頂点から間隔を空けた位置に接続され、各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されているので、基板金属部素子および素子金属部にヒビなどが生じても、該ヒビによって基板配線および素子配線までヒビが伝達し断線することを防止することができるという効果を奏する。

【0029】

また、本発明の半導体装置は、各素子金属部は、各角が外側に向かって突き出る多角形状をしており、各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されているので、素子金属部にヒビなどが生じても、該ヒビによって素子配線までヒビが伝達し断線することを防止することができるという効果を奏する。

【発明を実施するための最良の形態】

【0030】

〔実施の形態1〕

本発明の一実施形態について図面に基づいて説明すれば、以下の通りである。

【0031】

図1は、本実施の形態の半導体装置1の一構成例を示す側面断面図である。

【0032】

半導体装置1は、図1に示すように、種々の機能を有するように構成された半導体素子11、半導体素子11が実装されたインターポーザ基板21、および、インターポーザ基板21が実装されたフィルム基板31を備えている。半導体装置1は、TCPにおいて、チップ・オン・チップ(Chip on Chip)と呼ばれるパッケージ構造を有する半導体装置である。

【0033】

半導体素子11は、シリコン等の半導体材料を主材料とし、薄いチップ形状を有している。半導体素子11の厚みは725〜500μmである。半導体素子11における、インターポーザ基板21に実装される側の表面(実装面)は、長方形となっている。半導体素子11の実装面には、インターポーザ基板21との接合要素となる素子金属バンプ12(素子突起電極)、素子金属バンプ12の土台である素子パッドメタル13(素子金属部)、および、素子パッドメタル13と素子内部とを接続するように引き回された素子配線14が形成されている。

【0034】

半導体素子11の実装面の一構成例を、図2(a)に示す。なお、図2(a)では、素子金属バンプ12および素子配線14を省略して図示している。

【0035】

素子パッドメタル13は、図2(a)に示すように、インターポーザ基板21との接合箇所に応じて、半導体素子11の実装面の4つの辺縁に沿って複数配置されている。詳細には、素子パッドメタル13は、図2(a)における、上辺側であって長辺方向の左端から右端に沿って等間隔に3列、中央から下辺側であって左辺側および右辺側に等間隔に3列ずつ、および、最下辺の中央付近に等間隔に1列、配置されている。なお、図2(a)は一例を示しているだけであり、素子パッドメタル13はインターポーザ基板21との接合箇所に応じて適宜配置すればよい。

【0036】

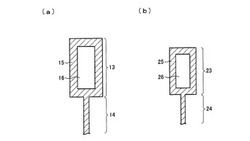

素子パッドメタル13の詳細な構成を図3(a)に示す。素子パッドメタル13は、半導体素子11の実装面に垂直な方向から見たとき、長方形の形状を有している。また、素子パッドメタル13の短辺の直線部分であって、かつ、角の頂点から間隔を空けた位置から、素子配線14が細く延びるように配設されている。素子パッドメタル13および素子配線14は、例えば銅により一体化してパターン形成され、その表面が、開口部を形成するように絶縁保護膜15により被覆されている。開口部により銅が露出した部分は、導電接続を行う導電部16となる。図3(a)では、導電部16は長方形の形状を有しているが、これに限るものではない。

【0037】

素子金属バンプ12は、素子パッドメタル13、詳細には絶縁保護膜15および導電部16の上に形成されている。素子金属バンプ12は、金からなり、直方体の形状を有している。素子金属バンプ12の厚みは8μmである。但し、素子金属バンプ12は、この形状に限らず、少なくとも導電部16を被覆し、かつ、インターポーザ基板21との実装強度を十分に確保するような形状であればよく、例えば、立方体やボール状でもよい。また、素子金属バンプ12は、金に限らず、電気抵抗が3×10−8(Ω・m)以下の金属、または、引っ張り強さが1.0×108(Pa)以上の金属によって構成されていればよい。

【0038】

インターポーザ基板21は、シリコンや化合物半導体、ガラス等からなる薄いチップ状の基板である。インターポーザ基板21の厚みは725〜500μmである。インターポーザ基板21における、半導体素子11を実装する側の表面(実装面)は、長方形となっている。インターポーザ基板21の実装面には、半導体素子11との接合要素となる第1基板金属バンプ22(基板突起電極)、第1基板金属バンプ22の土台である第1基板パッドメタル23(基板金属部)、フィルム基板31との接合要素となる第2基板金属バンプ27、第2基板金属バンプ27の土台である第2基板パッドメタル28、および、第1基板パッドメタル23と第2基板パッドメタル28とを接続するように引き回された基板配線24が形成されている。

【0039】

インターポーザ基板21の実装面の一構成例を、図2(b)に示す。なお、図2(b)では、第1基板金属バンプ22、第2基板金属バンプ27および基板配線24を省略して図示している。インターポーザ基板21の実装面において1点鎖線で示される領域が、半導体素子11が実装される領域である。第1基板パッドメタル23は上記領域内に設けられたものであり、第2基板パッドメタル28は上記領域外に設けられたものである。

【0040】

第1基板パッドメタル23は、図2(b)に示すように、インターポーザ基板21の実装面に半導体素子11の実装面を向かい合わせて実装させたとき、半導体素子11の素子パッドメタル13が形成されている位置に相対するような位置に、複数配置されている。

【0041】

第1基板パッドメタル23の詳細な構成を図3(b)に示す。第1基板パッドメタル23は、インターポーザ基板21の実装面に垂直な方向から見たとき、素子パッドメタル13のサイズよりも小さい長方形の形状を有している。また、第1基板パッドメタル23の短辺の直線部分であって、かつ、角の頂点から間隔を空けた位置から、基板配線24が細く延びるように配設されている。第1基板パッドメタル23および基板配線24は、例えばアルミニウムまたは銅により一体化してパターン形成され、その表面が、開口部を形成するように絶縁保護膜25により被覆されている。開口部によりアルミニウムまたは銅が露出した部分は、導電接続を行う導電部26となる。図3(b)では、導電部26は長方形の形状を有しているが、これに限るものではない。

【0042】

第1基板金属バンプ22は、第1基板パッドメタル23、詳細には絶縁保護膜25および導電部26の上に形成されている。第1基板金属バンプ22は、金からなり、直方体の形状を有している。第1基板金属バンプ22の厚みは15μmである。但し、第1基板金属バンプ22は、この形状に限らず、少なくとも導電部26を被覆し、かつ、半導体素子11との実装強度を十分に確保するような形状であればよく、例えば、角柱やボール状でもよい。また、第1基板金属バンプ22は、金に限らず、電気抵抗が3×10−8(Ω・m)以下の金属、または、引っ張り強さが1.0×108(Pa)以上の金属によって構成されていればよい。第1基板金属バンプ22と素子金属バンプ12とは、熱圧着によりそれぞれ接合されている。

【0043】

第2基板パッドメタル28は、図2(b)に示すように、フィルム基板31との接合箇所に応じて、インターポーザ基板21の実装面の4つの辺縁に沿って複数配置されている。詳細には、第2基板パッドメタル28は、4つの辺縁それぞれに、等間隔で1列ずつ配設されている。なお、図2(b)は一例を示しているだけであり、第2基板パッドメタル28はフィルム基板31との接合箇所に応じて適宜配置すればよい。

【0044】

第2基板パッドメタル28は、インターポーザ基板21の実装面に垂直な方向から見たとき、第1基板パッドメタル23と同様の長方形の形状を有している。また、第2基板パッドメタル28の短辺の直線部分であって、かつ、角の頂点から間隔を空けた位置から、基板配線24が細く延びるように配設されている。第2基板パッドメタル28も、第1基板パッドメタル23および基板配線24と同時に、例えばアルミニウムまたは銅により一体化してパターン形成される。第2基板パッドメタル28の表面は、開口部を形成するように絶縁保護膜により被覆されている。開口部によりアルミニウムまたは銅が露出した部分は、導電接続を行う導電部となる。

【0045】

第2基板金属バンプ27は、第2基板パッドメタル28、詳細には絶縁保護膜および導電部の上に形成されている。第2基板金属バンプ27は、金からなり、直方体の形状を有している。第2基板金属バンプ27の厚みは15μmである。但し、第2基板金属バンプ27は、この形状に限らず、少なくとも導電部を被覆し、かつ、フィルム基板31との実装強度を十分に確保するような形状であればよい。

【0046】

フィルム基板31は、ポリイミドなどからなる薄膜フィルムの絶縁基材に、銅からなる配線32を形成して作製された基板である。配線32のうち、インナーリードとしてインターポーザ基板21と接合される部分、およびアウターリードとして外部と接合される部分以外は、絶縁保護膜33により被覆されている。

【0047】

配線32のうちインナーリードは、フィルム基板31のインナーリードが形成されている面にインターポーザ基板21の実装面を向かい合わせて実装させたとき、インターポーザ基板21の第2基板パッドメタル28が形成されている位置に相対するような位置に、複数配置されている。第2基板パッドメタル28とインナーリードとは、ILBによりそれぞれ接合されている。

【0048】

また、フィルム基板31は、長方形の孔34を有している。孔34は、フィルム基板31にインターポーザ基板21を実装させたとき、インターポーザ基板21に実装された半導体素子11がフィルム基板31に干渉しないようなサイズおよび位置にて設けられている。インターポーザ基板21とフィルム基板31との隙間、半導体素子11とインターポーザ基板21との隙間、および半導体素子11とフィルム基板31との隙間は、アンダーフィル材35により充填されている。

【0049】

次いで、上記構成を有する半導体装置1の製造方法について説明する。

【0050】

まず、従来ある種々の作製方法により、半導体素子11、インターポーザ基板21、およびフィルム基板31に、次に記す構成要素をそれぞれ形成する。すなわち、半導体素子11には、素子金属バンプ12、素子パッドメタル13、および素子配線14を形成する。インターポーザ基板21には、第1基板金属バンプ22、第1基板パッドメタル23、第2基板金属バンプ27、第2基板パッドメタル28、および基板配線24を形成する。フィルム基板31には、配線32、絶縁保護膜33、および孔34を形成する。

【0051】

続いて、図4(a)〜(d)を参照しながら、半導体素子11、インターポーザ基板21、およびフィルム基板31の実装方法について詳細に説明する。

【0052】

図4(a)〜(d)は、半導体装置1の実装フローを示す図である。

【0053】

図4(a)に示すように、フィルム基板31を実装装置(図示せず)に設置する。このとき、フィルム基板31は、配線32が形成されていない位置にて押えられ固定される。

【0054】

続いて、図4(b)に示すように、インターポーザ基板21の実装面をフィルム基板31のインナーリードが形成されている面に向かい合わせ、熱および圧力を加えながら、インターポーザ基板21の第2基板金属バンプ27をフィルム基板31のインナーリードに圧着し(押し付け)、金−錫共晶で接合する。つまりは、ILBによりインターポーザ基板21をフィルム基板31に実装する。このとき、金−錫共晶させて接合するため、熱圧着時において高い接合圧力は必要ない。

【0055】

続いて、図4(c)に示すように、半導体素子11をフィルム基板31の孔34の中に通す。そして、半導体素子11の実装面をインターポーザ基板21の実装面に向かい合わせ、熱および圧力を加えながら、半導体素子11の素子金属バンプ12をインターポーザ基板21の第1基板金属バンプ22に圧着し接合する。このとき、金同士を接合するため、熱圧着時には高い接合圧力を加える。なお、インターポーザ基板21の実装面と反対側の面は押えられている。

【0056】

続いて、図4(d)に示すように、インターポーザ基板21とフィルム基板31との隙間、半導体素子11とインターポーザ基板21との隙間、および半導体素子11とフィルム基板31との隙間に、アンダーフィル材35を注入して充填する。これにより、半導体装置1が完成する。

【0057】

以上のように、半導体装置1では、半導体素子11をインターポーザ基板21に実装する際、金からなる素子金属バンプ12と金からなる第1基板金属バンプ22とを接合させるために、高い接合圧力が与えられている。これは、金を含む引っ張り強さが強い金属(1.0×108(Pa)以上の金属)は、弱い圧力を加えても塑性変形が起こらず、弱い圧力での接合は難しい材料であるためである。

【0058】

それゆえ、このような材料は強い圧力をかけて接合を行う必要があるので、素子パッドメタル13および第1基板パッドメタル23へのダメージ(ヒビや割れなどの損傷)がより起こりやすい。よって、従来では、図11に示したように、高い接合圧力により、各金属バンプの下にある外部接続電極101にヒビが生じるという問題があった。このヒビは、配線102の断線という事態につながる重大な問題となる。

【0059】

そこで、本発明の発明者は上記問題に対して検証した。その結果、金属バンプの下にある外部接続電極101にヒビが生じる場合、該ヒビは、応力が集中し易い角を終点として入り易いことを見出した。つまり、ヒビは、外部接続電極101の角がある位置に向かって、伝達エネルギーが抜けるように発生することがわかった。

【0060】

これを受けて、半導体装置1は、半導体素子11では、動作に寄与しないダミー配線等を除く、断線が発生してはならない素子配線14が、素子金属バンプ12の下にある素子パッドメタル13の角の頂点から間隔を空けた位置に配設され、かつ、インターポーザ基板21では、動作に寄与しないダミー配線等を除く、断線が発生してはならない基板配線24が、第1基板金属バンプ22の下にある第1基板パッドメタル23の角の頂点から間隔を空けた位置に配設されている、という構成を有している。これにより、素子パッドメタル13および第1基板パッドメタル23にヒビが生じても、該ヒビによって素子配線14や基板配線24までヒビが伝達し断線することを防止することが可能となっている。

【0061】

なお、上述した半導体装置1において、フィルム基板31には、インターポーザ基板21を実装する部分以外の領域に、他のチップコンデンサなどが適宜実装されていてもよい。また、素子金属バンプ12および素子パッドメタル13と、第1基板金属バンプ22および第1基板パッドメタル23と、第2基板金属バンプ27および第2基板パッドメタル28とには、信号の入出力を行わないダミーを設けてもよい。

【0062】

また、半導体装置1では、半導体素子11における素子パッドメタル13、並びに、インターポーザ基板21における第1基板パッドメタル23および第2基板パッドメタル28は、上述した形状に限るわけではなく、各角が外側に向かって突き出る多角形状であればよい。但し、外形形状の直線部分は、素子配線14や基板配線24の幅よりも大きいことが望ましい。一例を図5(a)(b)に示す。

【0063】

図5(a)は、正六角形のパッドメタル51aの一構成例を示す図である。配線52aは、パッドメタル51aの直線部分であって、かつ、角の頂点から間隔を空けた位置から細く延びるように配設される。図5(b)は、八角形のパッドメタル51bの一構成例を示す図である。配線52bは、パッドメタル51bの直線部分であって、かつ、角の頂点から間隔を空けた位置から細く延びるように配設される。図5(a)(b)の何れの構成においても、その表面は、適切な形状の開口部を形成するように絶縁保護膜により被覆される。

【0064】

ここで、半導体素子11における素子金属バンプ12、および、インターポーザ基板21における第1基板金属バンプ22が、直方体の形状を有する場合、素子金属バンプ12における素子パッドメタル13に接する面(以下、素子バンプ底面と略記する)の短辺側に素子配線14を配置し、第1基板金属バンプ22における第1基板パッドメタル23に接する面(以下、基板バンプ底面と略記する)の短辺側に基板配線24を配置させることが、オープンの発生を防止する上でより好ましい。

【0065】

図6は、素子金属バンプ12および第1基板金属バンプ22の熱圧着時の、各実装面における拡がりを示す図である。図6では、素子金属バンプ12および第1基板金属バンプ22を、まとめてバンプと表記している。また、X1方向およびY1方向は、素子バンプ底面および基板バンプ底面における短辺方向および長辺方向をそれぞれ示している。

【0066】

素子金属バンプ12と第1基板金属バンプ22とを熱圧着する際、図6に示すように、各金属バンプは、その圧力により実装面に平行な方向(横方向:X1方向およびY1方向)に拡がる。それゆえ、素子金属バンプ12の横方向の拡がりに伴い、素子金属バンプ12を固定している素子パッドメタル13にも同じ横方向に拡がる力が加わる。このとき、素子パッドメタル13に加わる力が大きいと、素子パッドメタル13が寸断されオープンが起きる。また、第1基板金属バンプ22の横方向の拡がりに伴い、第1基板パッドメタル23にも同様の現象が起こる。

【0067】

そこで、素子金属バンプ12および第1基板金属バンプ22が直方体の形状を有する場合、素子バンプ底面および基板バンプ底面において、長辺の中点と短辺の中点との微小領域に加わる横方向に拡がる力を考える。

【0068】

このとき、長辺の中点では、Y1方向への拡がりは、隣接する微小領域の金属バンプにより支えられるため小さくなる。なお、もし長辺の長さが無限大であるとすれば、Y1方向への拡がりはゼロであり、熱圧着による金属バンプの厚みの減少分と等量の体積の金属がX1方向に拡がる。

【0069】

一方、短辺の中点では、X1方向への拡がりは、隣接する微小領域により支えられる力が弱いため大きくなる。そして、X1方向でも拡がりが起きるため、力は分散され、Y1方向の拡がりは比較的小さくなる。なお、もし短辺の長さがゼロに近いとすれば、短辺の中点における拡がりは「Y1方向≒X1方向」となる。

【0070】

よって、Y1方向のパッドメタルは寸断されにくいが、X1方向のパッドメタルは寸断されやすい。すなわち、素子パッドメタル13および第1基板パッドメタル23は、素子バンプ底面および基板バンプ底面の長辺方向へ拡がるように加わる力は小さいので寸断されにくいが、素子バンプ底面および基板バンプ底面の短辺方向へ拡がるように加わる力は大きいため、素子バンプ底面および基板バンプ底面の長辺方向に寸断されやすい。

【0071】

発生したヒビはパッドメタルの角がある位置に向かって伝達するので、パッドメタルの角と角とをつなぐようにヒビが生じパッドメタルが寸断された場合、分離された部分は孤立状態となる。よって、分離された部分に配線が接続されているとオープンになってしまう。上記分離された部分は、素子バンプ底面および基板バンプ底面の長辺側にあるときが多くなる。

【0072】

したがって、素子バンプ底面および基板バンプ底面の短辺側から、素子配線14および基板配線24を出すことが望ましい。これにより、例え、素子パッドメタル13および第1基板パッドメタル23が、素子バンプ底面および基板バンプ底面の長辺方向に寸断してしまった場合であっても、素子配線14、素子パッドメタル13、素子金属バンプ12、第1基板金属バンプ22、第1基板パッドメタル23、および基板配線24とつながる経路におけるオープンの発生を防止することが可能となる。

【0073】

また、半導体素子11とインターポーザ基板21との熱膨張率の差により、半導体素子11とインターポーザ基板21との変形量に差が生じる。例えば、半導体素子11の熱膨張率が大きく、インターポーザ基板21の熱膨張率が小さいとする。このときの各部材の変形量を図7に示す。半導体素子11の実装面およびインターポーザ基板21の実装面が長方形の場合、半導体素子11およびインターポーザ基板21は、実装面の中央付近を中心にして長辺方向および短辺方向に変形する。

【0074】

このため、図7に記す矢印の長さで示すように、実装面の中心から離れるほど、半導体素子11とインターポーザ基板21との変形量の差が大きくなる。変形量の差が大きいほど、素子パッドメタル13および第1基板パッドメタル23に加わる力が比例して大きくなる。また、素子パッドメタル13および第1基板パッドメタル23は、実装面の長辺方向の端側に配置されたものほど加えられる力が大きくなる。

【0075】

それゆえ、上記力が大きくなると、図11に示したように、素子パッドメタル13および第1基板パッドメタル23が寸断されてしまう。もし、素子バンプ底面および基板バンプ底面の短辺方向における角と角とをつなぐようにヒビが入ってしまった場合、上述した経路にオープンが発生する虞がある。

【0076】

よって、素子金属バンプ12および第1基板金属バンプ22が直方体の形状を有し、かつ、素子バンプ底面および基板バンプ底面の短辺側から、素子配線14および基板配線24が配設されている構成の場合、半導体素子11の実装面の長辺と素子金属バンプ12の素子バンプ底面の長辺とが垂直になるように、素子金属バンプ12を配置させ、インターポーザ基板21の実装面の長辺と第1基板金属バンプ22の基板バンプ底面の長辺とが垂直になるように、第1基板金属バンプ22を配置させることが望ましい。図2(a)(b)は、この構成を図示している。

【0077】

これにより、熱膨張によって、素子パッドメタル13および第1基板パッドメタル23に、素子バンプ底面および基板バンプ底面の短辺方向における角と角とをつなぐようにヒビが生じることを防止することが可能となる。それゆえ、上述した経路におけるオープンの発生を防止することが可能となる。

【0078】

〔実施の形態2〕

本発明の他の実施の形態について図面に基づいて説明すれば、以下の通りである。なお、本実施の形態において説明すること以外の構成は、前記実施の形態1と同じである。また、説明の便宜上、前記の実施の形態1の図面に示した部材と同一の機能を有する部材については、同一の符号を付し、その説明を省略する。

【0079】

図8は、本実施の形態の半導体装置40の一構成例を示す側面断面図である。

【0080】

半導体装置40は、図8に示すように、半導体素子11、および半導体素子11が実装されたフィルム基板41を備えている。半導体装置40は、COFなどと呼ばれるパッケージ構造を有する半導体装置であり、例えば、液晶パネルのソースドライバとして用いられる。

【0081】

フィルム基板41は、ポリイミドなどからなる薄膜フィルムの絶縁基材に、銅からなる配線42を形成して作製された基板である。配線42にうち、インナーリードとして半導体素子11と接合される部分、およびアウターリードとして外部と接合される部分以外は、絶縁保護膜43により被覆されている。

【0082】

配線42のうちインナーリードは、フィルム基板41のインナーリードが形成されている面に半導体素子11の実装面を向かい合わせて実装させたとき、半導体素子11の素子金属バンプ12が形成されている位置に相対するような位置に、複数配置されている。素子金属バンプ12とインナーリードとは、ILBによりそれぞれ接合されている。また、半導体素子11とフィルム基板41との隙間は、アンダーフィル材45により充填されている。

【0083】

上記構成を有する半導体装置40では、半導体素子11をフィルム基板41に実装する際、金からなる素子金属バンプ12と錫メッキされたインナーリードとを共晶させて接合するため、熱圧着の接合圧力は低い。

【0084】

しかし、素子金属バンプ12全てがインナーリードに確実に接触するように、比較的強く押さえつけるため、素子金属バンプ12の高さのバラツキなどにより、最も高い素子金属バンプ12に応力集中が発生する場合がある。発生した応力が大きい場合、応力集中が起きた素子金属バンプ12の下にある素子パッドメタル13にダメージが生じてしまう。ヒビは、素子パッドメタル13の角がある位置に向かって、伝達するエネルギーが抜けるように発生しやすい。

【0085】

よって、半導体装置40は、半導体素子11における素子配線14の全てを、素子金属バンプ12の下にある素子パッドメタル13の角の頂点から間隔を空けた位置に配設させる、という構成を有している。これにより、素子パッドメタル13にヒビが生じても、該ヒビによって素子配線14までヒビが伝達し断線することを防止することが可能となっている。

【0086】

本発明は上述した各実施形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能であり、異なる実施形態にそれぞれ開示された技術的手段を適宜組み合わせて得られる実施形態についても本発明の技術的範囲に含まれる。

【産業上の利用可能性】

【0087】

本発明は、金属バンプの接合応力により発生したダメージによる配線の断線の防止が望まれる半導体装置に関する分野に好適に用いることができるだけでなく、半導体装置の製造に関する分野、例えば、配線パターンの形成に関する分野に好適に用いることができ、さらには、半導体装置を備える機器の分野にも広く用いることができる。

【図面の簡単な説明】

【0088】

【図1】本発明における半導体装置の実施の一形態を示す断面側面図である。

【図2】(a)は上記半導体装置に設けられた半導体素子の実装面の構成を示す平面図であり、(b)は上記半導体装置に設けられたインターポーザ基板の実装面の構成を示す平面図である。

【図3】(a)は、上記半導体素子の実装面における素子パッドメタルおよび素子配線の構成を示す平面図であり、(b)は、上記インターポーザ基板における第1基板パッドメタルおよび基板配線の構成を示す平面図である。

【図4】(a)〜(d)は、上記半導体装置の実装工程を示す断面側面図である。

【図5】(a)および(b)は、パッドメタルおよび配線の他の構成を示す平面図である。

【図6】熱圧着時の金属バンプの拡がりを示す図である。

【図7】上記半導体装置における半導体素子およびインターポーザ基板の熱膨張時の変形を概念的に示す図である。

【図8】本発明における半導体装置の他の実施の形態を示す断面側面図である。

【図9】従来の半導体装置における外部接続金属配線部および内部金属配線の構成を示す平面図である。

【図10】従来の半導体装置における外部接続電極および配線のパターン例を示す平面図である。

【図11】上記外部接続電極にヒビが生じたときの状態を示す平面図である。

【符号の説明】

【0089】

1 半導体装置

11 半導体素子

12 素子金属バンプ(素子突起電極)

13 素子パッドメタル(素子金属部)

14 素子配線

15 絶縁保護膜

16 導電部

21 インターポーザ基板

22 第1基板金属バンプ(基板突起電極)

23 第1基板パッドメタル(基板金属部)

24 基板配線

25 絶縁保護膜

26 導電部

27 第2基板金属バンプ

28 第2基板パッドメタル

31 フィルム基板(基板)

32 配線

33,43 絶縁保護膜

34 孔

35,45 アンダーフィル材

40 半導体装置

41 フィルム基板

42 配線(基板金属部、基板配線)

【技術分野】

【0001】

本発明は、金属バンプを用いたチップ複合型パッケージの半導体装置に関するものである。

【背景技術】

【0002】

半導体装置として、半導体素子を種々の実装形態で構成するチップ複合型パッケージがある。このような半導体装置では、半導体素子が、信号の入出力が可能なようにフィルム基板に実装されている。半導体装置の品質および信頼性を低下させないためには、実装に起因する不具合を防止する必要がある。

【0003】

例えば、TCP(Tape Carrier Package)やCOF(Chip on Film)の半導体装置における構成を説明する。半導体素子には、フィルム基板に実装させる面に、フィルム基板との接合部分に配置された素子外部接続電極、および、素子外部接続電極と素子内部とを接続するように引き回された素子配線が形成され、素子外部接続電極上に金からなる金属バンプが形成される。フィルム基板には、半導体素子を実装する面に、半導体素子の素子外部接続電極と相対する位置に配置された錫メッキした銅からなるインナーリード、および、インナーリードから基板外部に接続可能なように引き回された基板配線が形成される。

【0004】

これらの構成において、熱および圧力を加えながら金属バンプをインナーリードに押し付け、金−錫共晶で接合することにより、半導体素子をフィルム基板に実装することができる。なお、この接合方法はILB(Inner Lead Bonding)と呼ばれている。

【0005】

ここで、素子外部接続電極と素子配線とは同一の金属にてパターン形成されるが、その一方で性能を向上させるために、複数の金属配線層を重ねたものを素子配線に使用する場合がある。この場合、素子外部接続電極と素子配線とは異なる材料となるので、別個に形成して接続させる必要がある。

【0006】

例えば、特許文献1には、図9に示すように、外部接続金属配線部201に内部金属配線205と接続させるための突出部202を設け、突出部202に内部金属配線205を重ねて接続させる構成が記載されている。外部接続金属配線部201は、導電接続部分となる開口窓203および開口窓204以外の部分が絶縁保護膜により被覆されている。しかし、特に、突出部202の基端部X(外部に対して張る角度が90度の部分)に内部金属配線205が重なると、両者材料の熱膨張率などの差異から応力が加わり、絶縁保護膜にひずみおよび割れが生じやすい。そこで特許文献1では、内部金属配線205を基端部Xから間隔をおいた部位に布線させることにより、絶縁保護膜のひずみおよび割れを防止している。

【特許文献1】特開昭62−232940号公報(1987年10月13日公開)

【発明の開示】

【発明が解決しようとする課題】

【0007】

ところで、上述したパッケージの半導体装置では、金属バンプとインナーリードとを接合させる構成であったが、フィルム基板と半導体素子との間に、シリコン基板などからなるインターポーザ基板を介した構成を有する半導体装置もある。この半導体装置では、インターポーザ基板には、半導体素子を実装する面に、半導体素子の素子外部接続電極と相対する位置に配置された基板外部接続電極、および、基板外部接続電極から基板外部に接続可能なように引き回された基板配線が形成され、基板外部接続電極上に金からなる金属バンプが形成される。図10に、金属バンプを形成する前の、従来の一般的な外部接続電極101(素子外部接続電極、基板外部接続電極)および配線102(素子配線、基板配線)のパターン例を示す。

【0008】

半導体素子は、金属バンプ同士の接合によりインターポーザ基板に実装される。金属バンプとインナーリードとを接合させる場合、金−錫共晶させて接合するため、熱圧着の接合圧力は低く、接合圧力が不良を起こす原因とはなり難い。しかしながら、金属バンプ同士を接合させる場合、例えば金を金属バンプの材料として用いると、共晶しない金と金とを接合させるために、熱圧着の接合圧力を高める必要がある。このため、高い接合圧力により、各金属バンプ下の素子外部接続電極および基板外部接続電極にダメージ(ヒビや割れなどの損傷)が生じるという問題がある。また、半導体素子とインターポーザ基板とを接合後、両者材料の熱膨張率などの差異から、素子外部接続電極および基板外部接続電極に応力がそれぞれ加わりダメージが生じる場合もある。

【0009】

ダメージが生じたときの一例として、外部接続電極101にヒビが生じたときの状態を図11に示す。応力は金属バンプの根元に集中し易いので、外部接続電極101にも応力が加えられる。ヒビは、起点から、円弧を描きながら外側に向かって抜けようとする。このため、外部接続電極101に生じたヒビが、配線102が設けられている方向に伝達すると、配線102の断線という重大な問題が発生する。それゆえ、半導体装置の品質および信頼性を高く維持することはできない。

【0010】

また、接合圧力が高い場合に限らず、発生確率は低くなるが、接合圧力が低い金属バンプとインナーリードとを接合させる場合であっても、素子外部接続電極にダメージが生じる場合がある。例えば、金属バンプ全てがインナーリードに確実に接触するように、比較的強く押さえつけるため、金属バンプの高さのバラツキなどにより、最も高い金属バンプに応力集中が発生する場合である。

【0011】

本発明は、上記従来の問題点に鑑みなされたものであって、その目的は、配線の断線を防止することができる半導体装置を提供することにある。

【課題を解決するための手段】

【0012】

本発明の半導体装置は、上記課題を解決するために、基板に実装されたインターポーザ基板と、前記インターポーザ基板に実装された半導体素子とを備え、前記インターポーザ基板は、前記半導体素子が実装される位置に形成された複数個の基板金属部と、前記各基板金属部の上にそれぞれ形成された複数個の基板突起電極と、前記各基板金属部にそれぞれ接続された複数本の基板配線とを有し、前記半導体素子は、前記各基板突起電極とそれぞれ熱圧着により接合した複数個の素子突起電極と、前記各素子突起電極の下にそれぞれ形成された複数個の素子金属部と、前記各素子金属部にそれぞれ接続された複数本の素子配線とを有する半導体装置であって、前記各基板金属部および前記各素子金属部は、各角が外側に向かって突き出る多角形状をしており、前記各基板配線は、それぞれ対応する基板金属部の角の頂点から間隔を空けた位置に接続され、前記各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されていることを特徴としている。

【0013】

従来では、熱圧着時の接合圧力が高いほど、基板突起電極の下にある基板金属部、および、素子突起電極の下にある素子金属部にダメージ(ヒビや割れなどの損傷)が生じやすかった。このダメージは、基板配線および素子配線の断線という事態につながる。また、ダメージは、応力が集中し易い角を終点として入り易い。

【0014】

これに対し、上記の構成によれば、各基板配線は、それぞれ対応する基板金属部の角の頂点から間隔を空けた位置に接続され、各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されている。これにより、基板金属部素子および素子金属部に、例えばヒビが生じても、該ヒビによって基板配線および素子配線までヒビが伝達し断線することを防止することが可能となる。

【0015】

また、上記半導体素子をインターポーザ基板に実装したとき、各基板突起電極と各素子突起電極とが好適に熱圧着により接合するために、本発明の半導体装置は、前記各基板突起電極および前記各素子突起電極は、電気抵抗が3×10−8(Ω・m)以下の金属バンプによって構成されていることが望ましい。または、本発明の半導体装置は、前記各基板突起電極および前記各素子突起電極は、引っ張り強さが1.0×108(Pa)以上の金属バンプによって構成されているものに適用することが望ましい。

【0016】

また、本発明の半導体装置は、前記各基板突起電極および前記各素子突起電極は、直方体の形状を有しており、前記各素子配線は、それぞれ対応する素子突起電極における素子金属部に接する面の短辺側に配置されていることが好ましい。

【0017】

各基板突起電極および各素子突起電極が直方体の形状を有する場合、熱圧着によって、素子突起電極における素子金属部に接する面では、長辺方向への拡がりは小さく、短辺方向への拡がりは大きい。このため、素子金属部は、上記長辺方向へ拡がるように加わる力は小さいので寸断されにくいが、上記短辺方向へ拡がるように加わる力は大きいため、上記長辺方向に寸断されやすい。

【0018】

それゆえ、上記の構成によれば、各素子配線は、それぞれ対応する素子突起電極における素子金属部に接する面の短辺側に配置されていることにより、基板突起電極、素子突起電極、素子金属部、および素子配線とつながる経路におけるオープンの発生を防止することが可能となる。

【0019】

また、本発明の半導体装置は、前記各基板突起電極および前記各素子突起電極は、直方体の形状を有しており、前記各基板配線は、それぞれ対応する基板突起電極における基板金属部に接する面の短辺側に配置されていることが好ましい。

【0020】

各基板突起電極および各素子突起電極が直方体の形状を有する場合、熱圧着によって、基板突起電極における基板金属部に接する面では、長辺方向への拡がりは小さく、短辺方向への拡がりは大きい。このため、基板金属部は、上記長辺方向へ拡がるように加わる力は小さいので寸断されにくいが、上記短辺方向へ拡がるように加わる力は大きいため、上記長辺方向に寸断されやすい。

【0021】

それゆえ、上記の構成によれば、各基板配線は、それぞれ対応する基板突起電極における基板金属部に接する面の短辺側に配置されていることにより、素子突起電極、基板突起電極、基板金属部、および基板配線とつながる経路におけるオープンの発生を防止することが可能となる。

【0022】

また、半導体素子とインターポーザ基板との熱膨張率の差により、半導体素子とインターポーザ基板との変形量に差が生じる。このため、半導体素子における各素子突起電極が形成されている面の中心付近から離れるほど、半導体素子とインターポーザ基板との変形量の差が大きくなる。もし、この熱膨張による力により、上記短辺方向に寸断されてしまった場合、上記経路にオープンが発生する虞がある。

【0023】

それゆえ、熱膨張による上記短辺方向の寸断の発生を防止するために、本発明の半導体装置は、前記各素子突起電極は、それぞれ対応する素子金属部に接する面の長辺が、前記半導体素子における前記各素子突起電極が形成されている面の長辺と垂直になるように配置されていることが望ましい。また、本発明の半導体装置は、前記各基板突起電極は、それぞれ対応する基板金属部に接する面の長辺が、前記インターポーザ基板における前記各基板突起電極が形成されている面の長辺と垂直になるように配置されていることが望ましい。

【0024】

また、本発明の半導体装置は、上記課題を解決するために、フィルム基板と、前記フィルム基板に実装された半導体素子とを備え、前記フィルム基板は、前記半導体素子が実装される位置に形成された複数個の基板金属部と、前記各基板金属部にそれぞれ接続された複数本の基板配線とを有し、前記半導体素子は、前記各基板金属部とそれぞれ熱圧着により接合した複数個の素子突起電極と、前記各素子突起電極の下にそれぞれ形成された複数個の素子金属部と、前記各素子金属部にそれぞれ接続された複数本の素子配線とを有する半導体装置であって、前記各素子金属部は、各角が外側に向かって突き出る多角形状をしており、前記各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されていることを特徴としている。

【0025】

従来では、素子突起電極の高さのばらつきにより熱圧着時に応力集中が生じると、その応力が大きいほど、素子突起電極の下にある素子金属部にダメージ(ヒビや割れなどの損傷)が生じやすかった。このダメージは素子配線の断線という事態につながる。また、ダメージは応力が集中し易い角を終点として入り易い。

【0026】

これに対し、上記の構成によれば、各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されている。これにより、素子金属部に、例えばヒビが生じても、該ヒビによって素子配線までヒビが伝達し断線することを防止することが可能となる。

【0027】

また、上記半導体素子をフィルム基板に実装したとき、各基板金属部と各素子突起電極とが好適に熱圧着により接合するために、本発明の半導体装置は、前記各素子突起電極は、電気抵抗が3×10−8(Ω・m)以下の金属バンプによって構成されていることが望ましい。

【発明の効果】

【0028】

以上のように、本発明の半導体装置は、各基板金属部および各素子金属部は、各角が外側に向かって突き出る多角形状をしており、各基板配線は、それぞれ対応する基板金属部の角の頂点から間隔を空けた位置に接続され、各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されているので、基板金属部素子および素子金属部にヒビなどが生じても、該ヒビによって基板配線および素子配線までヒビが伝達し断線することを防止することができるという効果を奏する。

【0029】

また、本発明の半導体装置は、各素子金属部は、各角が外側に向かって突き出る多角形状をしており、各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されているので、素子金属部にヒビなどが生じても、該ヒビによって素子配線までヒビが伝達し断線することを防止することができるという効果を奏する。

【発明を実施するための最良の形態】

【0030】

〔実施の形態1〕

本発明の一実施形態について図面に基づいて説明すれば、以下の通りである。

【0031】

図1は、本実施の形態の半導体装置1の一構成例を示す側面断面図である。

【0032】

半導体装置1は、図1に示すように、種々の機能を有するように構成された半導体素子11、半導体素子11が実装されたインターポーザ基板21、および、インターポーザ基板21が実装されたフィルム基板31を備えている。半導体装置1は、TCPにおいて、チップ・オン・チップ(Chip on Chip)と呼ばれるパッケージ構造を有する半導体装置である。

【0033】

半導体素子11は、シリコン等の半導体材料を主材料とし、薄いチップ形状を有している。半導体素子11の厚みは725〜500μmである。半導体素子11における、インターポーザ基板21に実装される側の表面(実装面)は、長方形となっている。半導体素子11の実装面には、インターポーザ基板21との接合要素となる素子金属バンプ12(素子突起電極)、素子金属バンプ12の土台である素子パッドメタル13(素子金属部)、および、素子パッドメタル13と素子内部とを接続するように引き回された素子配線14が形成されている。

【0034】

半導体素子11の実装面の一構成例を、図2(a)に示す。なお、図2(a)では、素子金属バンプ12および素子配線14を省略して図示している。

【0035】

素子パッドメタル13は、図2(a)に示すように、インターポーザ基板21との接合箇所に応じて、半導体素子11の実装面の4つの辺縁に沿って複数配置されている。詳細には、素子パッドメタル13は、図2(a)における、上辺側であって長辺方向の左端から右端に沿って等間隔に3列、中央から下辺側であって左辺側および右辺側に等間隔に3列ずつ、および、最下辺の中央付近に等間隔に1列、配置されている。なお、図2(a)は一例を示しているだけであり、素子パッドメタル13はインターポーザ基板21との接合箇所に応じて適宜配置すればよい。

【0036】

素子パッドメタル13の詳細な構成を図3(a)に示す。素子パッドメタル13は、半導体素子11の実装面に垂直な方向から見たとき、長方形の形状を有している。また、素子パッドメタル13の短辺の直線部分であって、かつ、角の頂点から間隔を空けた位置から、素子配線14が細く延びるように配設されている。素子パッドメタル13および素子配線14は、例えば銅により一体化してパターン形成され、その表面が、開口部を形成するように絶縁保護膜15により被覆されている。開口部により銅が露出した部分は、導電接続を行う導電部16となる。図3(a)では、導電部16は長方形の形状を有しているが、これに限るものではない。

【0037】

素子金属バンプ12は、素子パッドメタル13、詳細には絶縁保護膜15および導電部16の上に形成されている。素子金属バンプ12は、金からなり、直方体の形状を有している。素子金属バンプ12の厚みは8μmである。但し、素子金属バンプ12は、この形状に限らず、少なくとも導電部16を被覆し、かつ、インターポーザ基板21との実装強度を十分に確保するような形状であればよく、例えば、立方体やボール状でもよい。また、素子金属バンプ12は、金に限らず、電気抵抗が3×10−8(Ω・m)以下の金属、または、引っ張り強さが1.0×108(Pa)以上の金属によって構成されていればよい。

【0038】

インターポーザ基板21は、シリコンや化合物半導体、ガラス等からなる薄いチップ状の基板である。インターポーザ基板21の厚みは725〜500μmである。インターポーザ基板21における、半導体素子11を実装する側の表面(実装面)は、長方形となっている。インターポーザ基板21の実装面には、半導体素子11との接合要素となる第1基板金属バンプ22(基板突起電極)、第1基板金属バンプ22の土台である第1基板パッドメタル23(基板金属部)、フィルム基板31との接合要素となる第2基板金属バンプ27、第2基板金属バンプ27の土台である第2基板パッドメタル28、および、第1基板パッドメタル23と第2基板パッドメタル28とを接続するように引き回された基板配線24が形成されている。

【0039】

インターポーザ基板21の実装面の一構成例を、図2(b)に示す。なお、図2(b)では、第1基板金属バンプ22、第2基板金属バンプ27および基板配線24を省略して図示している。インターポーザ基板21の実装面において1点鎖線で示される領域が、半導体素子11が実装される領域である。第1基板パッドメタル23は上記領域内に設けられたものであり、第2基板パッドメタル28は上記領域外に設けられたものである。

【0040】

第1基板パッドメタル23は、図2(b)に示すように、インターポーザ基板21の実装面に半導体素子11の実装面を向かい合わせて実装させたとき、半導体素子11の素子パッドメタル13が形成されている位置に相対するような位置に、複数配置されている。

【0041】

第1基板パッドメタル23の詳細な構成を図3(b)に示す。第1基板パッドメタル23は、インターポーザ基板21の実装面に垂直な方向から見たとき、素子パッドメタル13のサイズよりも小さい長方形の形状を有している。また、第1基板パッドメタル23の短辺の直線部分であって、かつ、角の頂点から間隔を空けた位置から、基板配線24が細く延びるように配設されている。第1基板パッドメタル23および基板配線24は、例えばアルミニウムまたは銅により一体化してパターン形成され、その表面が、開口部を形成するように絶縁保護膜25により被覆されている。開口部によりアルミニウムまたは銅が露出した部分は、導電接続を行う導電部26となる。図3(b)では、導電部26は長方形の形状を有しているが、これに限るものではない。

【0042】

第1基板金属バンプ22は、第1基板パッドメタル23、詳細には絶縁保護膜25および導電部26の上に形成されている。第1基板金属バンプ22は、金からなり、直方体の形状を有している。第1基板金属バンプ22の厚みは15μmである。但し、第1基板金属バンプ22は、この形状に限らず、少なくとも導電部26を被覆し、かつ、半導体素子11との実装強度を十分に確保するような形状であればよく、例えば、角柱やボール状でもよい。また、第1基板金属バンプ22は、金に限らず、電気抵抗が3×10−8(Ω・m)以下の金属、または、引っ張り強さが1.0×108(Pa)以上の金属によって構成されていればよい。第1基板金属バンプ22と素子金属バンプ12とは、熱圧着によりそれぞれ接合されている。

【0043】

第2基板パッドメタル28は、図2(b)に示すように、フィルム基板31との接合箇所に応じて、インターポーザ基板21の実装面の4つの辺縁に沿って複数配置されている。詳細には、第2基板パッドメタル28は、4つの辺縁それぞれに、等間隔で1列ずつ配設されている。なお、図2(b)は一例を示しているだけであり、第2基板パッドメタル28はフィルム基板31との接合箇所に応じて適宜配置すればよい。

【0044】

第2基板パッドメタル28は、インターポーザ基板21の実装面に垂直な方向から見たとき、第1基板パッドメタル23と同様の長方形の形状を有している。また、第2基板パッドメタル28の短辺の直線部分であって、かつ、角の頂点から間隔を空けた位置から、基板配線24が細く延びるように配設されている。第2基板パッドメタル28も、第1基板パッドメタル23および基板配線24と同時に、例えばアルミニウムまたは銅により一体化してパターン形成される。第2基板パッドメタル28の表面は、開口部を形成するように絶縁保護膜により被覆されている。開口部によりアルミニウムまたは銅が露出した部分は、導電接続を行う導電部となる。

【0045】

第2基板金属バンプ27は、第2基板パッドメタル28、詳細には絶縁保護膜および導電部の上に形成されている。第2基板金属バンプ27は、金からなり、直方体の形状を有している。第2基板金属バンプ27の厚みは15μmである。但し、第2基板金属バンプ27は、この形状に限らず、少なくとも導電部を被覆し、かつ、フィルム基板31との実装強度を十分に確保するような形状であればよい。

【0046】

フィルム基板31は、ポリイミドなどからなる薄膜フィルムの絶縁基材に、銅からなる配線32を形成して作製された基板である。配線32のうち、インナーリードとしてインターポーザ基板21と接合される部分、およびアウターリードとして外部と接合される部分以外は、絶縁保護膜33により被覆されている。

【0047】

配線32のうちインナーリードは、フィルム基板31のインナーリードが形成されている面にインターポーザ基板21の実装面を向かい合わせて実装させたとき、インターポーザ基板21の第2基板パッドメタル28が形成されている位置に相対するような位置に、複数配置されている。第2基板パッドメタル28とインナーリードとは、ILBによりそれぞれ接合されている。

【0048】

また、フィルム基板31は、長方形の孔34を有している。孔34は、フィルム基板31にインターポーザ基板21を実装させたとき、インターポーザ基板21に実装された半導体素子11がフィルム基板31に干渉しないようなサイズおよび位置にて設けられている。インターポーザ基板21とフィルム基板31との隙間、半導体素子11とインターポーザ基板21との隙間、および半導体素子11とフィルム基板31との隙間は、アンダーフィル材35により充填されている。

【0049】

次いで、上記構成を有する半導体装置1の製造方法について説明する。

【0050】

まず、従来ある種々の作製方法により、半導体素子11、インターポーザ基板21、およびフィルム基板31に、次に記す構成要素をそれぞれ形成する。すなわち、半導体素子11には、素子金属バンプ12、素子パッドメタル13、および素子配線14を形成する。インターポーザ基板21には、第1基板金属バンプ22、第1基板パッドメタル23、第2基板金属バンプ27、第2基板パッドメタル28、および基板配線24を形成する。フィルム基板31には、配線32、絶縁保護膜33、および孔34を形成する。

【0051】

続いて、図4(a)〜(d)を参照しながら、半導体素子11、インターポーザ基板21、およびフィルム基板31の実装方法について詳細に説明する。

【0052】

図4(a)〜(d)は、半導体装置1の実装フローを示す図である。

【0053】

図4(a)に示すように、フィルム基板31を実装装置(図示せず)に設置する。このとき、フィルム基板31は、配線32が形成されていない位置にて押えられ固定される。

【0054】

続いて、図4(b)に示すように、インターポーザ基板21の実装面をフィルム基板31のインナーリードが形成されている面に向かい合わせ、熱および圧力を加えながら、インターポーザ基板21の第2基板金属バンプ27をフィルム基板31のインナーリードに圧着し(押し付け)、金−錫共晶で接合する。つまりは、ILBによりインターポーザ基板21をフィルム基板31に実装する。このとき、金−錫共晶させて接合するため、熱圧着時において高い接合圧力は必要ない。

【0055】

続いて、図4(c)に示すように、半導体素子11をフィルム基板31の孔34の中に通す。そして、半導体素子11の実装面をインターポーザ基板21の実装面に向かい合わせ、熱および圧力を加えながら、半導体素子11の素子金属バンプ12をインターポーザ基板21の第1基板金属バンプ22に圧着し接合する。このとき、金同士を接合するため、熱圧着時には高い接合圧力を加える。なお、インターポーザ基板21の実装面と反対側の面は押えられている。

【0056】

続いて、図4(d)に示すように、インターポーザ基板21とフィルム基板31との隙間、半導体素子11とインターポーザ基板21との隙間、および半導体素子11とフィルム基板31との隙間に、アンダーフィル材35を注入して充填する。これにより、半導体装置1が完成する。

【0057】

以上のように、半導体装置1では、半導体素子11をインターポーザ基板21に実装する際、金からなる素子金属バンプ12と金からなる第1基板金属バンプ22とを接合させるために、高い接合圧力が与えられている。これは、金を含む引っ張り強さが強い金属(1.0×108(Pa)以上の金属)は、弱い圧力を加えても塑性変形が起こらず、弱い圧力での接合は難しい材料であるためである。

【0058】

それゆえ、このような材料は強い圧力をかけて接合を行う必要があるので、素子パッドメタル13および第1基板パッドメタル23へのダメージ(ヒビや割れなどの損傷)がより起こりやすい。よって、従来では、図11に示したように、高い接合圧力により、各金属バンプの下にある外部接続電極101にヒビが生じるという問題があった。このヒビは、配線102の断線という事態につながる重大な問題となる。

【0059】

そこで、本発明の発明者は上記問題に対して検証した。その結果、金属バンプの下にある外部接続電極101にヒビが生じる場合、該ヒビは、応力が集中し易い角を終点として入り易いことを見出した。つまり、ヒビは、外部接続電極101の角がある位置に向かって、伝達エネルギーが抜けるように発生することがわかった。

【0060】

これを受けて、半導体装置1は、半導体素子11では、動作に寄与しないダミー配線等を除く、断線が発生してはならない素子配線14が、素子金属バンプ12の下にある素子パッドメタル13の角の頂点から間隔を空けた位置に配設され、かつ、インターポーザ基板21では、動作に寄与しないダミー配線等を除く、断線が発生してはならない基板配線24が、第1基板金属バンプ22の下にある第1基板パッドメタル23の角の頂点から間隔を空けた位置に配設されている、という構成を有している。これにより、素子パッドメタル13および第1基板パッドメタル23にヒビが生じても、該ヒビによって素子配線14や基板配線24までヒビが伝達し断線することを防止することが可能となっている。

【0061】

なお、上述した半導体装置1において、フィルム基板31には、インターポーザ基板21を実装する部分以外の領域に、他のチップコンデンサなどが適宜実装されていてもよい。また、素子金属バンプ12および素子パッドメタル13と、第1基板金属バンプ22および第1基板パッドメタル23と、第2基板金属バンプ27および第2基板パッドメタル28とには、信号の入出力を行わないダミーを設けてもよい。

【0062】

また、半導体装置1では、半導体素子11における素子パッドメタル13、並びに、インターポーザ基板21における第1基板パッドメタル23および第2基板パッドメタル28は、上述した形状に限るわけではなく、各角が外側に向かって突き出る多角形状であればよい。但し、外形形状の直線部分は、素子配線14や基板配線24の幅よりも大きいことが望ましい。一例を図5(a)(b)に示す。

【0063】

図5(a)は、正六角形のパッドメタル51aの一構成例を示す図である。配線52aは、パッドメタル51aの直線部分であって、かつ、角の頂点から間隔を空けた位置から細く延びるように配設される。図5(b)は、八角形のパッドメタル51bの一構成例を示す図である。配線52bは、パッドメタル51bの直線部分であって、かつ、角の頂点から間隔を空けた位置から細く延びるように配設される。図5(a)(b)の何れの構成においても、その表面は、適切な形状の開口部を形成するように絶縁保護膜により被覆される。

【0064】

ここで、半導体素子11における素子金属バンプ12、および、インターポーザ基板21における第1基板金属バンプ22が、直方体の形状を有する場合、素子金属バンプ12における素子パッドメタル13に接する面(以下、素子バンプ底面と略記する)の短辺側に素子配線14を配置し、第1基板金属バンプ22における第1基板パッドメタル23に接する面(以下、基板バンプ底面と略記する)の短辺側に基板配線24を配置させることが、オープンの発生を防止する上でより好ましい。

【0065】

図6は、素子金属バンプ12および第1基板金属バンプ22の熱圧着時の、各実装面における拡がりを示す図である。図6では、素子金属バンプ12および第1基板金属バンプ22を、まとめてバンプと表記している。また、X1方向およびY1方向は、素子バンプ底面および基板バンプ底面における短辺方向および長辺方向をそれぞれ示している。

【0066】

素子金属バンプ12と第1基板金属バンプ22とを熱圧着する際、図6に示すように、各金属バンプは、その圧力により実装面に平行な方向(横方向:X1方向およびY1方向)に拡がる。それゆえ、素子金属バンプ12の横方向の拡がりに伴い、素子金属バンプ12を固定している素子パッドメタル13にも同じ横方向に拡がる力が加わる。このとき、素子パッドメタル13に加わる力が大きいと、素子パッドメタル13が寸断されオープンが起きる。また、第1基板金属バンプ22の横方向の拡がりに伴い、第1基板パッドメタル23にも同様の現象が起こる。

【0067】

そこで、素子金属バンプ12および第1基板金属バンプ22が直方体の形状を有する場合、素子バンプ底面および基板バンプ底面において、長辺の中点と短辺の中点との微小領域に加わる横方向に拡がる力を考える。

【0068】

このとき、長辺の中点では、Y1方向への拡がりは、隣接する微小領域の金属バンプにより支えられるため小さくなる。なお、もし長辺の長さが無限大であるとすれば、Y1方向への拡がりはゼロであり、熱圧着による金属バンプの厚みの減少分と等量の体積の金属がX1方向に拡がる。

【0069】

一方、短辺の中点では、X1方向への拡がりは、隣接する微小領域により支えられる力が弱いため大きくなる。そして、X1方向でも拡がりが起きるため、力は分散され、Y1方向の拡がりは比較的小さくなる。なお、もし短辺の長さがゼロに近いとすれば、短辺の中点における拡がりは「Y1方向≒X1方向」となる。

【0070】

よって、Y1方向のパッドメタルは寸断されにくいが、X1方向のパッドメタルは寸断されやすい。すなわち、素子パッドメタル13および第1基板パッドメタル23は、素子バンプ底面および基板バンプ底面の長辺方向へ拡がるように加わる力は小さいので寸断されにくいが、素子バンプ底面および基板バンプ底面の短辺方向へ拡がるように加わる力は大きいため、素子バンプ底面および基板バンプ底面の長辺方向に寸断されやすい。

【0071】

発生したヒビはパッドメタルの角がある位置に向かって伝達するので、パッドメタルの角と角とをつなぐようにヒビが生じパッドメタルが寸断された場合、分離された部分は孤立状態となる。よって、分離された部分に配線が接続されているとオープンになってしまう。上記分離された部分は、素子バンプ底面および基板バンプ底面の長辺側にあるときが多くなる。

【0072】

したがって、素子バンプ底面および基板バンプ底面の短辺側から、素子配線14および基板配線24を出すことが望ましい。これにより、例え、素子パッドメタル13および第1基板パッドメタル23が、素子バンプ底面および基板バンプ底面の長辺方向に寸断してしまった場合であっても、素子配線14、素子パッドメタル13、素子金属バンプ12、第1基板金属バンプ22、第1基板パッドメタル23、および基板配線24とつながる経路におけるオープンの発生を防止することが可能となる。

【0073】

また、半導体素子11とインターポーザ基板21との熱膨張率の差により、半導体素子11とインターポーザ基板21との変形量に差が生じる。例えば、半導体素子11の熱膨張率が大きく、インターポーザ基板21の熱膨張率が小さいとする。このときの各部材の変形量を図7に示す。半導体素子11の実装面およびインターポーザ基板21の実装面が長方形の場合、半導体素子11およびインターポーザ基板21は、実装面の中央付近を中心にして長辺方向および短辺方向に変形する。

【0074】

このため、図7に記す矢印の長さで示すように、実装面の中心から離れるほど、半導体素子11とインターポーザ基板21との変形量の差が大きくなる。変形量の差が大きいほど、素子パッドメタル13および第1基板パッドメタル23に加わる力が比例して大きくなる。また、素子パッドメタル13および第1基板パッドメタル23は、実装面の長辺方向の端側に配置されたものほど加えられる力が大きくなる。

【0075】

それゆえ、上記力が大きくなると、図11に示したように、素子パッドメタル13および第1基板パッドメタル23が寸断されてしまう。もし、素子バンプ底面および基板バンプ底面の短辺方向における角と角とをつなぐようにヒビが入ってしまった場合、上述した経路にオープンが発生する虞がある。

【0076】

よって、素子金属バンプ12および第1基板金属バンプ22が直方体の形状を有し、かつ、素子バンプ底面および基板バンプ底面の短辺側から、素子配線14および基板配線24が配設されている構成の場合、半導体素子11の実装面の長辺と素子金属バンプ12の素子バンプ底面の長辺とが垂直になるように、素子金属バンプ12を配置させ、インターポーザ基板21の実装面の長辺と第1基板金属バンプ22の基板バンプ底面の長辺とが垂直になるように、第1基板金属バンプ22を配置させることが望ましい。図2(a)(b)は、この構成を図示している。

【0077】

これにより、熱膨張によって、素子パッドメタル13および第1基板パッドメタル23に、素子バンプ底面および基板バンプ底面の短辺方向における角と角とをつなぐようにヒビが生じることを防止することが可能となる。それゆえ、上述した経路におけるオープンの発生を防止することが可能となる。

【0078】

〔実施の形態2〕

本発明の他の実施の形態について図面に基づいて説明すれば、以下の通りである。なお、本実施の形態において説明すること以外の構成は、前記実施の形態1と同じである。また、説明の便宜上、前記の実施の形態1の図面に示した部材と同一の機能を有する部材については、同一の符号を付し、その説明を省略する。

【0079】

図8は、本実施の形態の半導体装置40の一構成例を示す側面断面図である。

【0080】

半導体装置40は、図8に示すように、半導体素子11、および半導体素子11が実装されたフィルム基板41を備えている。半導体装置40は、COFなどと呼ばれるパッケージ構造を有する半導体装置であり、例えば、液晶パネルのソースドライバとして用いられる。

【0081】

フィルム基板41は、ポリイミドなどからなる薄膜フィルムの絶縁基材に、銅からなる配線42を形成して作製された基板である。配線42にうち、インナーリードとして半導体素子11と接合される部分、およびアウターリードとして外部と接合される部分以外は、絶縁保護膜43により被覆されている。

【0082】

配線42のうちインナーリードは、フィルム基板41のインナーリードが形成されている面に半導体素子11の実装面を向かい合わせて実装させたとき、半導体素子11の素子金属バンプ12が形成されている位置に相対するような位置に、複数配置されている。素子金属バンプ12とインナーリードとは、ILBによりそれぞれ接合されている。また、半導体素子11とフィルム基板41との隙間は、アンダーフィル材45により充填されている。

【0083】

上記構成を有する半導体装置40では、半導体素子11をフィルム基板41に実装する際、金からなる素子金属バンプ12と錫メッキされたインナーリードとを共晶させて接合するため、熱圧着の接合圧力は低い。

【0084】

しかし、素子金属バンプ12全てがインナーリードに確実に接触するように、比較的強く押さえつけるため、素子金属バンプ12の高さのバラツキなどにより、最も高い素子金属バンプ12に応力集中が発生する場合がある。発生した応力が大きい場合、応力集中が起きた素子金属バンプ12の下にある素子パッドメタル13にダメージが生じてしまう。ヒビは、素子パッドメタル13の角がある位置に向かって、伝達するエネルギーが抜けるように発生しやすい。

【0085】

よって、半導体装置40は、半導体素子11における素子配線14の全てを、素子金属バンプ12の下にある素子パッドメタル13の角の頂点から間隔を空けた位置に配設させる、という構成を有している。これにより、素子パッドメタル13にヒビが生じても、該ヒビによって素子配線14までヒビが伝達し断線することを防止することが可能となっている。

【0086】

本発明は上述した各実施形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能であり、異なる実施形態にそれぞれ開示された技術的手段を適宜組み合わせて得られる実施形態についても本発明の技術的範囲に含まれる。

【産業上の利用可能性】

【0087】

本発明は、金属バンプの接合応力により発生したダメージによる配線の断線の防止が望まれる半導体装置に関する分野に好適に用いることができるだけでなく、半導体装置の製造に関する分野、例えば、配線パターンの形成に関する分野に好適に用いることができ、さらには、半導体装置を備える機器の分野にも広く用いることができる。

【図面の簡単な説明】

【0088】

【図1】本発明における半導体装置の実施の一形態を示す断面側面図である。

【図2】(a)は上記半導体装置に設けられた半導体素子の実装面の構成を示す平面図であり、(b)は上記半導体装置に設けられたインターポーザ基板の実装面の構成を示す平面図である。

【図3】(a)は、上記半導体素子の実装面における素子パッドメタルおよび素子配線の構成を示す平面図であり、(b)は、上記インターポーザ基板における第1基板パッドメタルおよび基板配線の構成を示す平面図である。

【図4】(a)〜(d)は、上記半導体装置の実装工程を示す断面側面図である。

【図5】(a)および(b)は、パッドメタルおよび配線の他の構成を示す平面図である。

【図6】熱圧着時の金属バンプの拡がりを示す図である。

【図7】上記半導体装置における半導体素子およびインターポーザ基板の熱膨張時の変形を概念的に示す図である。

【図8】本発明における半導体装置の他の実施の形態を示す断面側面図である。

【図9】従来の半導体装置における外部接続金属配線部および内部金属配線の構成を示す平面図である。

【図10】従来の半導体装置における外部接続電極および配線のパターン例を示す平面図である。

【図11】上記外部接続電極にヒビが生じたときの状態を示す平面図である。

【符号の説明】

【0089】

1 半導体装置

11 半導体素子

12 素子金属バンプ(素子突起電極)

13 素子パッドメタル(素子金属部)

14 素子配線

15 絶縁保護膜

16 導電部

21 インターポーザ基板

22 第1基板金属バンプ(基板突起電極)

23 第1基板パッドメタル(基板金属部)

24 基板配線

25 絶縁保護膜

26 導電部

27 第2基板金属バンプ

28 第2基板パッドメタル

31 フィルム基板(基板)

32 配線

33,43 絶縁保護膜

34 孔

35,45 アンダーフィル材

40 半導体装置

41 フィルム基板

42 配線(基板金属部、基板配線)

【特許請求の範囲】

【請求項1】

基板に実装されたインターポーザ基板と、前記インターポーザ基板に実装された半導体素子とを備え、前記インターポーザ基板は、前記半導体素子が実装される位置に形成された複数個の基板金属部と、前記各基板金属部の上にそれぞれ形成された複数個の基板突起電極と、前記各基板金属部にそれぞれ接続された複数本の基板配線とを有し、前記半導体素子は、前記各基板突起電極とそれぞれ熱圧着により接合した複数個の素子突起電極と、前記各素子突起電極の下にそれぞれ形成された複数個の素子金属部と、前記各素子金属部にそれぞれ接続された複数本の素子配線とを有する半導体装置であって、

前記各基板金属部および前記各素子金属部は、各角が外側に向かって突き出る多角形状をしており、

前記各基板配線は、それぞれ対応する基板金属部の角の頂点から間隔を空けた位置に接続され、前記各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されていることを特徴とする半導体装置。

【請求項2】

前記各基板突起電極および前記各素子突起電極は、電気抵抗が3×10−8(Ω・m)以下の金属バンプによって構成されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記各基板突起電極および前記各素子突起電極は、引っ張り強さが1.0×108(Pa)以上の金属バンプによって構成されていることを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記各基板突起電極および前記各素子突起電極は、直方体の形状を有しており、

前記各素子配線は、それぞれ対応する素子突起電極における素子金属部に接する面の短辺側に配置されていることを特徴とする請求項1に記載の半導体装置。

【請求項5】

前記各基板突起電極および前記各素子突起電極は、直方体の形状を有しており、

前記各基板配線は、それぞれ対応する基板突起電極における基板金属部に接する面の短辺側に配置されていることを特徴とする請求項1に記載の半導体装置。

【請求項6】

前記各素子突起電極は、それぞれ対応する素子金属部に接する面の長辺が、前記半導体素子における前記各素子突起電極が形成されている面の長辺と垂直になるように配置されていることを特徴とする請求項4に記載の半導体装置。

【請求項7】

前記各基板突起電極は、それぞれ対応する基板金属部に接する面の長辺が、前記インターポーザ基板における前記各基板突起電極が形成されている面の長辺と垂直になるように配置されていることを特徴とする請求項5に記載の半導体装置。

【請求項8】

フィルム基板と、前記フィルム基板に実装された半導体素子とを備え、前記フィルム基板は、前記半導体素子が実装される位置に形成された複数個の基板金属部と、前記各基板金属部にそれぞれ接続された複数本の基板配線とを有し、前記半導体素子は、前記各基板金属部とそれぞれ熱圧着により接合した複数個の素子突起電極と、前記各素子突起電極の下にそれぞれ形成された複数個の素子金属部と、前記各素子金属部にそれぞれ接続された複数本の素子配線とを有する半導体装置であって、

前記各素子金属部は、各角が外側に向かって突き出る多角形状をしており、

前記各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されていることを特徴とする半導体装置。

【請求項9】

前記各素子突起電極は、電気抵抗が3×10−8(Ω・m)以下の金属バンプによって構成されていることを特徴とする請求項8に記載の半導体装置。

【請求項1】

基板に実装されたインターポーザ基板と、前記インターポーザ基板に実装された半導体素子とを備え、前記インターポーザ基板は、前記半導体素子が実装される位置に形成された複数個の基板金属部と、前記各基板金属部の上にそれぞれ形成された複数個の基板突起電極と、前記各基板金属部にそれぞれ接続された複数本の基板配線とを有し、前記半導体素子は、前記各基板突起電極とそれぞれ熱圧着により接合した複数個の素子突起電極と、前記各素子突起電極の下にそれぞれ形成された複数個の素子金属部と、前記各素子金属部にそれぞれ接続された複数本の素子配線とを有する半導体装置であって、

前記各基板金属部および前記各素子金属部は、各角が外側に向かって突き出る多角形状をしており、

前記各基板配線は、それぞれ対応する基板金属部の角の頂点から間隔を空けた位置に接続され、前記各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されていることを特徴とする半導体装置。

【請求項2】

前記各基板突起電極および前記各素子突起電極は、電気抵抗が3×10−8(Ω・m)以下の金属バンプによって構成されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記各基板突起電極および前記各素子突起電極は、引っ張り強さが1.0×108(Pa)以上の金属バンプによって構成されていることを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記各基板突起電極および前記各素子突起電極は、直方体の形状を有しており、

前記各素子配線は、それぞれ対応する素子突起電極における素子金属部に接する面の短辺側に配置されていることを特徴とする請求項1に記載の半導体装置。

【請求項5】

前記各基板突起電極および前記各素子突起電極は、直方体の形状を有しており、

前記各基板配線は、それぞれ対応する基板突起電極における基板金属部に接する面の短辺側に配置されていることを特徴とする請求項1に記載の半導体装置。

【請求項6】

前記各素子突起電極は、それぞれ対応する素子金属部に接する面の長辺が、前記半導体素子における前記各素子突起電極が形成されている面の長辺と垂直になるように配置されていることを特徴とする請求項4に記載の半導体装置。

【請求項7】

前記各基板突起電極は、それぞれ対応する基板金属部に接する面の長辺が、前記インターポーザ基板における前記各基板突起電極が形成されている面の長辺と垂直になるように配置されていることを特徴とする請求項5に記載の半導体装置。

【請求項8】

フィルム基板と、前記フィルム基板に実装された半導体素子とを備え、前記フィルム基板は、前記半導体素子が実装される位置に形成された複数個の基板金属部と、前記各基板金属部にそれぞれ接続された複数本の基板配線とを有し、前記半導体素子は、前記各基板金属部とそれぞれ熱圧着により接合した複数個の素子突起電極と、前記各素子突起電極の下にそれぞれ形成された複数個の素子金属部と、前記各素子金属部にそれぞれ接続された複数本の素子配線とを有する半導体装置であって、

前記各素子金属部は、各角が外側に向かって突き出る多角形状をしており、

前記各素子配線は、それぞれ対応する素子金属部の角の頂点から間隔を空けた位置に接続されていることを特徴とする半導体装置。

【請求項9】

前記各素子突起電極は、電気抵抗が3×10−8(Ω・m)以下の金属バンプによって構成されていることを特徴とする請求項8に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2009−147167(P2009−147167A)

【公開日】平成21年7月2日(2009.7.2)

【国際特許分類】

【出願番号】特願2007−323764(P2007−323764)

【出願日】平成19年12月14日(2007.12.14)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成21年7月2日(2009.7.2)

【国際特許分類】

【出願日】平成19年12月14日(2007.12.14)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]