半導体装置

【課題】排他処理に伴って抑止されるべきアクセス要求を調停前に排除することができ、調停によって受理されるべきアクセス要求を早く確定することができる半導体装置を提供する。

【解決手段】排他的アクセスの対象となるアドレス情報などを排他情報バッファ(81)に保持し、イニシエータ(60,61,62)が出力するアドレス情報と前記保持されたアドレス情報を比較する。これにより、排他的アクセスの対象であるアドレスを対象とするピンポイントの排他処理を実現する。調停処理に先立って排他処理に伴うアクセス要求の排除を行う。このため、排他処理に伴って抑止されるべきアクセス要求が調停処理されることを防止し、イニシエータがアクセス要求を行ってからアクセス要求が受理されるまでの時間を短くすることが出来る。

【解決手段】排他的アクセスの対象となるアドレス情報などを排他情報バッファ(81)に保持し、イニシエータ(60,61,62)が出力するアドレス情報と前記保持されたアドレス情報を比較する。これにより、排他的アクセスの対象であるアドレスを対象とするピンポイントの排他処理を実現する。調停処理に先立って排他処理に伴うアクセス要求の排除を行う。このため、排他処理に伴って抑止されるべきアクセス要求が調停処理されることを防止し、イニシエータがアクセス要求を行ってからアクセス要求が受理されるまでの時間を短くすることが出来る。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、バスインタフェースにおける、共有リソースに対するアクセスの排他処理に関し、例えば半導体集積回路化されたマイクロコンピュータ、システム・オン・チップ(SOC)化されたデータプロセッシングデバイス、チップセット、マルチチップを用いてシステム・イン・パッケージ化されたデータ処理モジュールなどの半導体装置におけるスプリットトランザクションによるパケット交換方式のバスインタフェースに適用して有効な技術に関する。

【背景技術】

【0002】

バスインタフェースには、バスアクセスのリクエスト中は他のリクエストを受け付けないというインターロック方式のほかに、スプリットトランザクションによるパケット交換方式がある。この方式は、アクセスを要求する回路が、アクセス要求の内容を含むリクエストパケットを、アクセス要求に応答する回路に送信し、アクセス要求に応答する回路は応答内容を含むレスポンスパケットを、アクセスを要求した回路に送信する、という処理を行なうものである。リクエストパケットとレスポンスパケットを含む一連の処理をトランザクションと称し、1つのトランザクションをパケットの転送毎に分離して、バスアクセス効率を向上させることができる。アクセスを要求する回路をイニシエータ、アクセス要求に答える回路をターゲットと呼ぶ。回路の種類によってはイニシエータとターゲットの双方の機能を備えるものもある。イニシエータとターゲットはリクエストパケットとレスポンスパケットの中継を行うパケットルータがある。パケットルータは、一つのターゲットに対して複数のイニシエータがアクセスを要求したときの調停、共有リソースなどに対する排他制御のために後のアクセス要求を無効化する制御などを行う。リソース単位で排他処理を行なう場合、排他処理中には、排他処理要求が受理されたイニシエータ以外のイニシエータによる、排他的アクセスの実行対象であるターゲットへのアクセスを抑止するという、プロトコルが従来から採用さてれている。例えば、ターゲットがメモリコントローラであれば,排他処理中はメモリに対する他イニシエータのアクセスが全て抑止される。

【0003】

特許文献1には、マルチCPUのシステムにおいて共有リソースに対するアクセスの排他処理について記載がある。これによれば、CPU単位の排他制御ではなく、CPUが排他処理を要求したとき、当該CPUのアクセス対象領域について他のCPUからのアクセス要求を排他する制御を行う。

【0004】

【特許文献1】特開平5−225117号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

今後普及が見込まれるマルチコアSOC(一つのチップに複数のCPUを搭載するSOC)では、シングルコアSOC(一つのチップに単一のCPUを搭載するSOC)に比して排他処理が多用されることが考えられるため、ターゲット単位の排他処理では、排他処理に伴う転送性能(バスアクセス性能)の低下が大きいため、排他処理単位の縮小が必要であると考えられる。特許文献1ではその点が考慮され、アドレス領域単位の排他制御を行う。

【0006】

しかしながら、特許文献1に記載の技術ではアクセス要求に対して先に優先度やアクセス要求の競合状態に基づいてバス調停部で許可候補信号を生成し、許可候補のアクセス要求に係るアドレス情報をセレクタで選択し、選択したアドレス情報が、先に受理された排他制御対象のアドレス領域に重なるかが判別され、重なる場合には、先に許可候補としたCPUにバス使用不許可を返す、という制御を行う。要するに、アクセス要求が排他処理によって抑止されるべきものか否かが、調停処理の後に判明する。このため、特許文献1に記載の技術では、排他処理に伴って抑止されるべきアクセス要求を調停前に排除できず、調停によって受理されるべきアクセス要求を早く確定することができない。このため、アクセス要求に対する処理効率が低く、この点においてデータ処理の高速化を阻む結果となる。

【0007】

また、スプリットトランザクションによるパケット交換方式のバスインタフェースでは、排他処理を伴うアクセス要求が一時的に抑止される場合でもイニシエータは単に待たされるだけであるが、特許文献1に記載の技術をそれに適用する場合を想定すると、アクセス要求が受理されないCPUなどのイニシエータにはバス使用不許可の信号が返されることになり、イニシエータは単に待つだけでは済まされず、再度アクセス要求を行うなどの処理が必要になり、イニシエータの実装が通常よりも複雑になる。

【0008】

本発明の目的は、排他処理に伴って抑止されるべきアクセス要求を調停前に排除することができ、調停によって受理されるべきアクセス要求を早く確定することができる半導体装置を提供することにある。

【0009】

本発明の別の目的は、アクセス要求に対する処理効率が高く、この点においてデータ処理の高速化に寄与することができる半導体装置を提供することにある。

【0010】

本発明の更に別の目的は、排他処理を伴うアクセス要求が一時的に抑止される場合でもイニシエータは単に待つだけで済まされ、イニシエータの実装が容易な半導体装置を提供することにある。

【0011】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0012】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0013】

すなわち、排他的アクセスの対象となるアドレス情報などを保持し、イニシエータが出力するアドレス情報と前記保持されたアドレス情報を比較する。これにより、排他的アクセスの対象であるアドレスを対象とするピンポイントの排他処理を実現する。

【0014】

そして、調停処理に先立って排他処理に伴うアクセス要求の排除を行う。このため、排他処理に伴って抑止されるべきアクセス要求が調停処理されることを防止し、イニシエータがアクセス要求を行ってからアクセス要求が受理されるまでの時間を短くすることが出来る。

【0015】

また、本発明では,階層的インターコネクトを構成する複数のパケットルータの全てに上記排他処理のための回路を搭載する。これにより、ハングアップ(アクセス要求が処理できなくなる状態に陥ること)を発生させることなく、ピンポイントで排他処理を行うことができ、しかもこのピンポイントの排他処理に伴って排他処理によって抑止されないアクセス要求を排他的処理を必要とするアクセス要求の完了まで抑止することがない。

【0016】

また、本発明では、排他的アクセスに対して不正なアクセスがなされたことを検出して割り込みを発生する。これにより、ソフトウエアやハードウエアのデバッグが容易になる。

【発明の効果】

【0017】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0018】

すなわち、排他処理に伴って抑止されるべきアクセス要求を調停前に排除することができ、調停によって受理されるべきアクセス要求を早く確定することができる。

【0019】

アクセス要求に対する処理効率が高く、この点においてデータ処理の高速化に寄与することができる。

【0020】

排他処理を伴うアクセス要求が一時的に抑止される場合でもイニシエータは単に待つだけで済まされ、イニシエータの実装が容易である。

【発明を実施するための最良の形態】

【0021】

1.実施の形態の概要

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

【0022】

〔1〕《アドレス比較による排他制御》

本発明に係る半導体装置は、アクセスを要求することが可能な複数のイニシエータと、アクセスに応答することが可能な複数のターゲットと、アクセスを要求するイニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行うリクエストリソース及びアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースを備えたパケットルータとを有する。前記パケットルータのリクエストリソース(80)は、排他情報バッファ(81)、比較回路(90,91,92)、アクセス要求無効化回路(100,101,102)、及び調停回路(80)を有する。排他情報バッファは、排他処理要求を含むリクエストパケット(REQPCKT)を受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する。比較回路は、前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する。アクセス要求無効化回路は、前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化する。調停回路は、前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う。

【0023】

上記によれば、排他的アクセスの対象となるアドレス情報などのアクセス情報を保持し、イニシエータが出力するアクセス情報と前記保持されたアクセス情報を比較し、アクセス対象アドレスが重なる範囲を最大限として他のアクセス要求を無効化するから、ターゲット単位よりも細かなアドレスを対象とするピンポイントの排他処理を実現することができる。

【0024】

そして、調停回路の処理に先立って排他処理要求を伴うアクセス要求に対する選択的な無効化の処理を行うから、排他的な制御により抑止されるべきアクセス要求が調停回路による調停処理の対象にはされず、この点において、イニシエータがアクセス要求を行ってからアクセス要求が受理されるまでの時間を短縮するのに寄与する。

【0025】

〔2〕《調停回路によるグラント信号の処理》

項1の半導体装置において、例えば前記調停回路は、前記イニシエータ毎にグラント信号(GNT)を出力し、前記イニシエータからアクセス要求を入力した場合、前記アクセス要求無効化回路によりそのアクセス要求が有効とされ、かつ、調停によって前記イニシエータからのアクセス要求を受理した場合に前記グラント信号をアサート状態とし、前記アクセス要求無効化回路によりそのアクセス要求が無効とされた場合や、調停によって前記イニシエータからのアクセス要求を受理しない場合には、前記グラント信号をディアサート状態とする。

【0026】

調停回路は、アクセス要求の無効化に関わらず、イニシエータからのアクセス要求を受理したときにのみグラント信号をアサートするから、これを受けるイニシエータは、アクセス要求の後、これが受理されたか無効化されたかを感知することなく、グラント信号のアサートを待てばよい。

【0027】

したがって、スプリットトランザクションによるパケット交換方式のバスインタフェースでは、排他処理を伴うアクセス要求が一時的に抑止される場合でもイニシエータは単に待てばよく、再度アクセス要求を行うなどの処理は不要であり、ピンポイントの無効化を採用してもイニシエータの実装は容易である。

【0028】

〔3〕《イニシエータによるグラント信号の把握》

項2の半導体装置において、前記イニシエータは、例えばアクセスを要求した場合、入力されるグラント信号がディアサート状態であることによってアクセス要求が受理されていないと判定し、入力されるグラント信号がアサート状態であることにより、アクセス要求が受理されたと判定する。

【0029】

〔4〕《アドレス比較による排他制御》

項1の半導体装置において、前記排他情報バッファが保持するアクセス情報は例えばアクセス対象アドレス情報であり、この場合、前記アクセス要求無効化回路は、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるイニシエータからの新たなアクセス要求を無効化する(図5)。

【0030】

〔5〕《プロセスIDの比較による排他制御》

項1の半導体装置において、前記排他情報バッファが保持するアクセス情報は、例えばアクセス対象アドレス情報とそのアクセス対象アドレス情報を用いるプロセスのプロセスID情報であり、この場合、前記アクセス要求無効化回路は、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とはプロセスIDが異なるアクセス要求を無効化する。同じイニシエータによる排他的アクセス要求に対してプロセスIDを考慮してアクセス要求の無効化に対処することができる。

【0031】

〔6〕《排他情報バッファのエントリ数》

項5の半導体装置において、前記排他情報バッファは、前記調停回路が並列的に受理可能な排他処理要求を伴うアクセス要求毎のアクセス情報を格納可能な記憶容量を有する。要するに、前記排他情報バッファが保持するアクセス情報には例えばアクセス対象アドレス情報とそのアクセス対象アドレス情報を用いるプロセスのプロセスID情報を含む。この場合、前記アクセス要求無効化回路は、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とはプロセスIDが異なるアクセス要求を無効化する。1つのイニシエータが複数の排他処理要求を伴うアクセスを要求して並列的に受理される場合にもアクセス要求の無効化に対処することができる。

【0032】

〔7〕《アドレス情報及びバイトイネーブル比較による排他制御》

項1の半導体装置において、前記排他情報バッファが保持するアクセス情報は、例えば複数バイトのアクセス対象の先頭を示すアクセス対象アドレス情報と、複数バイトのアクセス対象範囲内の有効性をバイト単位で示すバイトイネーブル情報(BE)である。このとき、前記アクセス要求無効化回路は、アクセス対象アドレス情報のアドレスを先頭とする複数バイトのアクセス対象範囲内においてバイトイネーブル情報で有効性とされるアドレスと重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化する。これにより、アクセスアドレスを先頭アドレスとバイトイネーブルによって特定する場合にもアクセス要求の無効化に対処することができる(図6)。

【0033】

〔8〕《プロセスIDの比較による排他制御》

項1の半導体装置において、前記排他情報バッファが保持するアクセス情報は、例えば、複数バイトのアクセス対象の先頭を示すアクセス対象アドレス情報と、複数バイトのアクセス対象範囲内の有効性をバイト単位で示すバイトイネーブル情報と、アクセス対象のアドレス情報を用いるプロセスのプロセスID情報である。このとき、前記アクセス要求無効化回路は、アクセス対象アドレス情報のアドレスを先頭とする複数バイトのアクセス対象範囲内においてバイトイネーブル情報で有効性とされるアドレスと重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とはプロセスIDが異なるアクセス要求を無効化する。これにより、アクセスアドレスを先頭アドレスとバイトイネーブルによって特定する場合を考慮し、且つ、同じイニシエータによる排他的アクセス要求に対してプロセスIDを考慮して、アクセス要求の無効化に対処することができる。

【0034】

〔9〕《排他情報バッファのエントリ数》

項8の半導体装置において、前記排他情報バッファは、前記調停回路が並列的に受理可能な排他処理要求を伴うアクセス要求毎のアクセス情報を格納可能な記憶容量を有する。要するに、前記排他情報バッファが保持するアクセス情報には例えばアクセス対象先頭アドレス、バイトイネーブル情報及びそのアクセス要求に係るプロセスのプロセスID情報を含む。この場合、前記アクセス要求無効化回路は、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とはプロセスIDが異なるアクセス要求を無効化する。1つのイニシエータが複数の排他的処理のアクセスを要求して並列的に受理される場合にもアクセス要求の無効化に対処することができる。

【0035】

〔10〕《排他制御レジスタ》

項1の半導体装置において、排他制御の対象とするアクセスの属性を保持する排他制御レジスタ(27)を更に有する。前記アクセス要求無効化回路は、前記比較回路による比較結果と前記排他制御レジスタに保持されたアクセスの属性情報と基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化する。アクセス要求の無効化条件を排他制御レジスタにプログラマブルに設定することが可能になる(図7)。

【0036】

〔11〕《排他制御レジスタに設定されるアクセス属性》

項10の半導体装置において、前記排他制御レジスタには、アクセス属性として、例えばアクセス方向が設定される。前記アクセス要求無効化回路は、前記比較回路による比較結果と前記排他制御レジスタに保持されたアクセスの属性情報と基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なり且つ前記排他制御レジスタに設定されたアクセス方向へのアクセス要求を無効化する。特定のアクセス方向に対してアクセス要求を無効化することができる。

【0037】

〔12〕《排他制御レジスタに設定されるアクセス属性》

項10の半導体装置において、前記排他制御レジスタには、アクセス属性として、例えばイニシエータの識別情報が設定される。前記アクセス要求無効化回路は、前記比較回路による比較結果と前記排他制御レジスタに保持されたアクセスの属性情報と基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異り且つ前記排他制御レジスタに設定されたイニシエータからのアクセス要求を無効化する。特定のイニシエータに限ってアクセス要求を無効化することができる。

【0038】

〔13〕《排他処理に競合するアクセスに関するデバッグ支援》

項1の半導体装置は、前記イニシエータとして機能し得る複数のCPUと、前記ターゲットとして機能し得るメモリ及び割り込みコントローラを備える。前記メモリは前記複数のCPUの共有メモリである。前記パケットルータは、一のCPUから前記共有メモリに対する排他的な処理の要求を伴うリクエストパケットを受理した場合、そのアクセス対象アドレスと重なる範囲で、受理されている排他処理要求を伴うアクセス要求とは異なるライトアクセス要求があったことを、前記割り込みコントローラに通知する。CPUによる排他処理に競合するライトアクセスのあったことを割込みを通じてデバッグ支援のための装置に通知することができる。

【0039】

〔14〕《排他処理に競合するアクセスに関するデバッグ支援》

項1の半導体装置は、前記ターゲットとして機能し得るメモリ及び割り込みコントローラを備える。前記メモリは複数のイニシエータの共有メモリである。前記パケットルータは、一のイニシエータから前記共有メモリに対する排他処理要求を伴うリクエストパケットを受理した場合、そのアクセス対象アドレスと重なる範囲で、受理されている排他処理要求を伴うアクセス要求とは異なるライトアクセス要求があったことを前記割り込みコントローラに通知する。一のイニシエータによる排他処理に競合するライトアクセスのあったことを割込みを通じてデバッグ支援のための装置に通知することができる。

【0040】

〔15〕《ターゲット単位の排他制御の併用》

別の観点による半導体装置は、アクセスを要求することが可能な複数のイニシエータと、アクセスに応答することが可能な複数のターゲットと、アクセスを要求するイニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行う第1のリクエストリソース(131)及び第2のリクエストリソース(132)並びにアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースを備えたパケットルータとを有する。前記第1のリクエストリソースには特定の一のターゲットを対象とするリクエストパケットだけが振り分けられる。前記第2のリクエストリソースは他の複数のターゲットを対象とするリクエストパケットが振り分けられる。前記第1及び第2のリクエストリソースは、排他処理要求を含むリクエストパケットを受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する排他情報バッファと、前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する比較回路と、前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するアクセス要求無効化回路と、前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う調停回路と、を有する。

【0041】

前記第1のリクエストリソースには特定の一のターゲットを対象とするリクエストパケットだけが振り分けられるから、ターゲット単位の排他制御にはアドレス比較を要せず、一のターゲットを対象として他のイニシエータが発行した排他処理要求が既に受理されているか否か判定すればよい。

【0042】

〔16〕《階層化ルータの排他処理》

別の観点による半導体装置は、アクセスを要求することが可能な複数のイニシエータと、アクセスに応答することが可能な複数のターゲットと、前記イニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行うリクエストリソース及びアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースを備えた複数のパケットルータと、を備える。前記複数のパケットルータが中継回路を介して複数階層に直列接続されているとき、前記夫々のパケットルータのリクエストリソースは、イニシエータから所要のターゲットに対するアクセス要求に伴う排他処理要求を受理する排他処理機能を備える(図10)。

【0043】

階層的インターコネクトを構成する複数のパケットルータのうち、アクセス要求の上流(イニシエータに近い側)のパケットルータに排他処理機構を持たない場合、上流側パケットルータに接続された一のイニシエータからの排他処理要求を伴うアクセスに続いて同じ階層のパケットルータに接続された別のイニシエータが前記アクセス要求と同じアドレスに対してアクセス要求を送信したときに、ハングアップが発生する。これは、パケットルータ間の中継回路(キューイングバッファ)が前記一のイニシエータのリクエストパケットをパケットルータに送信したときに下位階層のパケットルータが排他処理によって前記別のイニシエータのアクセス要求を抑止するために、当該一のイニシエータが排他処理停止要求を通知するアクセス要求が中継回路を通れずに下流のパケットルータに送信できないからである。

【0044】

また、アクセス要求の下流のパケットルータに排他処理機能を持たない場合は、排他処理機能を有する上流のパケットルータに接続するイニシエータからの排他処理要求を下流のパケットルータが受理しないため、排他性を保証することができない。

【0045】

〔17〕

項16の半導体装置において、前記排他処理機能を備えるパケットルータのリクエストリソースは、排他処理要求を含むリクエストパケットを受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する排他情報バッファと、前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する比較回路と、前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するアクセス要求無効化回路と、前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う調停回路と、を有する。

【0046】

〔18〕《階層化ルータの排他処理》

別の観点による半導体装置は、アクセスを要求することが可能な複数のイニシエータと、アクセスに応答することが可能な複数のターゲットと、前記イニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行うリクエストリソース及びアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースを備えた複数のパケットルータと、を備える。前記複数のパケットルータが中継回路を介して複数階層に直列接続されているとき、前記夫々のパケットルータのリクエストリソースは、イニシエータから所要のターゲットに対する排他的な処理要求を受理する排他処理機能を備える。排他処理要求を伴うアクセスを要求するイニシエータは、同一階層のパケットルータに集約して結合される(図11、図12)。

【0047】

排他処理要求を行なうイニシエータを、排他処理要求を行なわないイニシエータに混在させて上流及び下流のパケットルータに分散配置した場合、上流及び下流のイニシエータがそれと同一アドレスについて排他的なアクセスを要求したときには、上流側で排他処理を要求しないイニシエータからのアクセス要求は、それが前記排他的なアクセス要求によって抑止されるべきものか否かにかかわらず、抑止される。これは、中継回路において、先に上流側のイニシエータから下流側のパケットルータに転送されるべき排他処理要求のアクセス要求が、下流側のイニシエータの排他的アクセス終了まで、下流側への伝達が抑止されるためである。

【0048】

〔19〕

項18の半導体装置において、前記排他処理機能を備えるパケットルータのリクエストリソースは、排他処理要求を含むリクエストパケットを受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する排他情報バッファと、前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する比較回路と、前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するアクセス要求無効化回路と、前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う調停回路と、を有する。

【0049】

2.実施の形態の詳細

実施の形態について更に詳述する。

【0050】

《スプリットトランザクションによるパケット交換》

図2にはスプリットトランザクションによるパケット交換方式のシステムの概念が例示される。このシステムでは、マスタとしてのイニシエータ(INIT)1がアクセス要求としてのリクエストパケット(REQPCKT)をスレーブとしてのターゲット(TGET)2に送信し、ターゲットがイニシエータにアクセス応答としてのレスポンスパケット(RESPCKT)を送信することで転送が行われる。パケットルータ(PCKTRT)3は、同時に転送されるリクエストパケットやレスポンスパケットの調停を行う。パケットルータ3は、アクセスを要求するイニシエータ1から与えられるリクエストパケットをアクセス要求に応答するターゲット2に与える制御を行うリクエストリソース(REQRSC)3A及びアクセス要求に応答するターゲット2から与えられるレスポンスパケットをアクセス要求元のイニシエータ1に返す制御を行うレスポンスリソース(RESRSC)3Bを備える。実際のシステムではイニシエータ1とターゲット2は適宜の数だけ配置される。また、イニシエータ1とターゲット2は必ずしも別々の回路であることを要せず、システム動作上、ある局面ではイニシエータ1となり、別の局面ではターゲット2とされる場合もあり、例えばDMAC(ダイレクト・メモリ・アクセス・コントローラ)はCPUによってデータ転送条件が設定されるときはターゲット2、設定された転送条件に従ってDMA転送を行うときはイニシエータ1となる。

【0051】

リクエストパケットREQPCKTは、例えば、リクエストREQ、グラントGNT、エンドオブパケットEOP,ロックLCK、アドレスADD、オペコードOPC、データDATA、バイトイネーブルBE、ソースSRCの各信号から成る。

【0052】

リクエストREQは、イニシエータがイニシエータポートのリクエストパケット転送に使用される信号のうち、LCK、ADD、OPC、DATA、BE、SRCなどに有効な値を出力していることを示す。本信号とGNTが共にアサート状態であるときに、リクエストパケットがイニシエータからパケットルータに向けて転送される。本信号が非アサート状態のとき、パケットルータは上記各信号を無視する。イニシエータはGNTの状態に関わらず本信号をアサートできるが、ひとたび本信号をアサートしたら、GNTがアサートされてリクエストパケットの最初のセルの転送が完了するまで、アサート状態に保持しなければならない。

【0053】

グラント信号GNTは、対応するターゲットがリクエストパケットのセルを受信可能であることを示す。REQと本信号が共にアサート状態であるときに、リクエストパケットのセルが、イニシエータからパケットルータに転送される。パケットルータはREQの状態とは無関係に本信号をアサート、ディアサートすることができる。

【0054】

エンドオブパケットEOPは、イニシエータがリクエストパケットの最終セルをイニシエータポートに出力していることを示す。ターゲットは、転送されたセルの数ではなく、本信号がアサート状態にあることを、リクエストパケット終端の検出条件としなければならない。イニシエータは、セルの転送を開始してからそのセルの転送が完了するまで、本信号を一定値に保持しなければならない。

【0055】

ロックLCKは、排他的にトランザクション(リクエストパケットの転送からレスポンスパケットを受領するまでの一連の処理)を実行するために、システムをロックすることを要求する信号である。イニシエータは、リクエストパケット送信時において、ターゲットを排他的にアクセスするときに本信号をアサート状態とし、排他的アクセス要求を解除するときは本信号を非アサート(ネゲート)状態とする。排他的トランザクション実行をサポートするパケットルータは、本信号がアサート状態であるリクエストパケットをターゲットに転送してから、同じイニシエータからの本信号が非アサート状態であるリクエストパケットを転送するまでの間は、他のイニシエータからのリクエストパケットをターゲットに転送してはならない。

【0056】

アドレス信号ADDはトランザクションのターゲットアドレスを示す。本信号によるアドレス指定の最小単位は8バイトである。

【0057】

オペコードOPCはロード、ストア等のトランザクションの種類と転送サイズを示す信号である。イニシエータは、リクエストパケットの転送を開始してからそのリクエストパケットの転送が完了するまで、REQがアサート状態にある間は、本信号を一定値に保持する。

【0058】

データDATAはイニシエータからターゲットに転送されるデータである。

【0059】

バイトイネーブルBEはターゲットが処理を行うべきバイトを指定する8ビットのデータである。バイトイネーブルとアドレスの関係は、例えばバイトアドレス0+8n、…、7+8nに対して、バイトイネーブルビットBE_0、…、BE_7が対応される。

【0060】

ソースSRCはパケットルータがレスポンスパケットを中継するときに、レスポンスパケットの送信先のイニシエータを特定できるようにするために、イニシエータが出力する識別子である。ターゲットは、リクエストパケット受信時に本信号の値を保存し、対応するレスポンスパケットを送信する際に後述するR_SRCとして出力する。そして、パケットルータは、R_SRCによってレスポンスパケットの送信先を決定する。したがって、イニシエータVCは、必ずレスポンスパケットが自らに返るように、本信号を出力しなければならない。

【0061】

レスポンスパケットRESPCKTは、例えば、レスポンスバリッドR_VLD(レスポンスリクエストR_REQ)、レスポンスグラントR_GNT、レスポンスエンドオブパケットR_EOP、レスポンスロックR_LCK、レスポンスオペコードR_OPC、レスポンスデータR_DATA、レスポンスソースR_SRCの各信号から成る。

【0062】

レスポンスリクエストR_REQは、ターゲットが出力するR_RCK、R_OPC、R_DATA、R_SRCなどの有効性を示す。ターゲットは、R_GNTの値に関わらず本信号をアサートできる。ただし、ひとたび本信号をアサートしたら、R_GNTがアサートされてレスポンスパケットの最初のセルの転送が完了するまでは、本信号をアサート状態に保持しなければならない。

【0063】

レスポンスバリッドR_VLDは、レスポンスパケットの有効性を示す信号であり、R_EOP、R_LCK、R_OPC、R_DATAなどが有効であることをイニシエータに示すための信号である。

【0064】

レスポンスエンドオブパケットR_EOPはレスポンスパケットの最終セルをイニシエータに出力していることを示す。

【0065】

レスポンスロックR_LCKは イニシエータで受信されたレスポンスパケットが排他的に送信されたものであるか否かを示す。レスポンスパケットの転送を開始してからそのレスポンスパケットの転送が完了するまで、R_VLDがアサート状態にある間は、レスポンスロックR_LCKは一定値に保持されなければならない。排他的トランザクション実行をサポートするパケットルータは、本信号がアサート状態であるレスポンスパケットを転送してから、同じターゲットからの本信号が非アサート状態であるレスポンスパケットを転送するまでの間は、他のターゲットからのレスポンスパケットをイニシエータに転送してはならない。

【0066】

レスポンスオペコードR_OPCは、ロードやストア等のトランザクションの結果を示すレスポンスオペコードである。

【0067】

レスポンスデータR_DATAはイニシエータに転送されるデータである。

【0068】

レスポンスソースR_SRCは対応するリクエストパケットの送信時にイニシエータが出力したソースSRCと同じ値の信号であり、レスポンスパケットの転送を開始してからそのレスポンスパケットの転送が完了するまで、R_VLDがアサート状態にある間は、一定値に保持される。本信号は、パケットルータがレスポンスパケットをルーティングする際に、レスポンスパケットの送信先(イニシエータ)を特定できるようにするための識別子である。ターゲットは、リクエストパケット受信時にSRCの値を保存し、対応するレスポンスパケットを送信する際にR_SRCとして出力する。パケットルータは、R_SRCによってレスポンスパケットの送信先を決定する。

【0069】

レスポンスググラントR_GNTはレスポンスパケットを受信可能であることを示す。

【0070】

《マイクロコンピュータとチップセット》

図3にはスプリットトランザクションによるパケット交換を適用したマイクロコンピュータ及びその周辺機能の拡張に用いる拡張デバイスからなるチップセットのブロック図が示される。チップセットはモジュール化されていてもいし、マザーボード上に単なるマルチチップとして実装されていてもよい。

【0071】

マイクロコンピュータ10及び拡張デバイス11はそれぞれ異なる半導体チップに形成され、デュアルチップでチップセットを構成する。

【0072】

マイクロコンピュータ10はスプリットトランザクションによるパケット交換によってデータなどの転送を行うために、階層化されたパケットルータ12、13を有し、パケットルータ12、13の間には中継回路としてキューイングバッファ(QUEBUF)14が配置される。ここでは、拡張デバイス11にもスプリットトランザクションによるパケット交換方式が採用され、パケットルータ15が設けられている。特に制限されないが、マイクロコンピュータ10と拡張デバイス11はシリアル入出力回路(SIO)30と40によって接続される。

【0073】

パケットルータ12には中央処理装置(CPU)20〜23、割り込みコントローラ(INTC)24、ROMアクセスコントローラ(ROMC)25、周辺制御部(PRPHC)26、及びルーティングコントローラレジスタ(RCREG)27が接続される。ROMC25には例えばROM50が外付けされる。

【0074】

パケットルータ13には表示制御部(DISPC)31、ハードディスク制御部(HDDC)32、ダイレクト・メモリ・アクセス・コントローラ(DMAC)33、フラッシュメモリコントローラ(FMRYC)34、シンクロナスDRAMコントローラ(DMRYC)35、周辺制御部(PRPHC)36、及びSIO30が接続される。HDDC32にはハードディスク(HDD)51が外付けされ、DISPC31にはディスプレイ(DISP)52が外付けされ、FMRYC34にはフラッシュメモリ(FMRY)51が外付けされ、DMRYC35にはシンクロナスDRAM(DMRY)54が外付けされる。

【0075】

パケットルータ15には周辺制御部(PRPHC)41〜44、及びルーティングコントローラレジスタ(RCREG)45が接続される。

【0076】

ルーティングコントロールレジスタ27はパケットルータ12,13に対する制御データが例えばCPU20によってプログラマブルに設定され、設定された制御データはパケットルータ12,13に供給される。同様に、ルーティングコントロールレジスタ45はパケットルータ15に対する制御データが例えばCPU20によってプログラマブルに設定され、設定された制御データはパケットルータ45に供給される。ルーティングコントロールレジスタ27は、後述するリクエストリソースによる排他制御の対象とするアクセスの属性を保持する排他制御レジスタとして機能される。

【0077】

キューイングバッファ14はパケットルータ12で受理されたリクエストパケットをFIFO形態一時的に保持する。キューイングバッファ14が現に最初に保持するリクエストパケットはパケットルータ13に出力され、パケットルータ13がこれを受理することによって、キューイングバッファ14は当該リクエストパケットのリードが完了されたと認識する。また、キューイングバッファ14はパケットルータ13で受理されたレスポンスパケットをFIFO形態一時的に保持する。キューイングバッファ14が現に最初に保持するレスポンスパケットはパケットルータ12に出力され、パケットルータ12がこれを受理することによって、キューイングバッファ14は当該レスポンスパケットのリードが完了されたと認識する。

【0078】

マイクロコンピュータ10においてパケットルータ12,13は2階層で階層化される。パケットリクエストを基点とするトランザクションに対してパケットルータ12が上位階層、パケットルータ13が下位階層をなす。チップセットにおいては、パケットルータ15はパケットルータ13のさらに下位階層をなす。

【0079】

ここで、図3のチップセットを構成する各回路モジュールにおいて、どれがイニシエータで、どれがターゲットから、そのバスマスタ機能とバススレーブ機能によって決まり、例えば、前述の如くDMAC33はその動作形態によってイニシエータとなったり、ターゲットになったりし、また、RCREG27はターゲットだけとして機能される。

【0080】

図3のチップセットにおいて、パケットルータ12,13,15は一つのターゲットに対して複数のイニシエータがアクセスを要求したときの調停、そして共有リソースなどに対する排他制御のために後のアクセス要求を無効化する制御などを行う。例えば、マイクロコンピュータ10のCPUは、TAS(Test And Set)命令実行時にセマフォに対してリード・モディファイ・ライトを行う。CPUはイニシエータとしてTAS命令によるセマフォのリードアクセスを行うときにパケットルータに排他処理を要求し、TAS命令の後半のライトアクセスを行うときにパケットルータに排他処理終了を通知する。リソース単位で排他処理を行なう場合に、排他処理要求が受理されたイニシエータ以外のイニシエータによる排他的アクセス対象へのアクセスをターゲット単位で抑止する、というプロトコルは従来から採用さてれている。マイクロコンピュータ10のような、マルチコアSOC(一つのチップに複数のCPUを搭載するSOC)では、シングルコアSOC(一つのチップに単一のCPUを搭載するSOC)に比して排他処理が多用されることが考えられる。ターゲット単位の排他処理では、排他処理に伴う転送性能(バスアクセス性能)の低下が大きいから、図3のチップセットにおいては、排他処理単位を縮小するために、少なくともアドレス領域単位の排他制御を行うようになっている。以下、排他処理を中心にパケットルータの具体例を説明する。

【0081】

《アドレス比較を行うリクエストリソース》

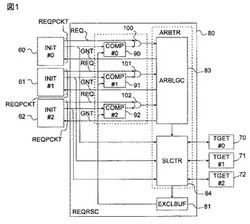

図1にはパケットルータ12、13、15のリクエストリソース(REQRSC)80について原理的構成が具体的に例示される。リクエストリソース80はリクエストリソース3Aの一例である。ここでは、説明を解り易くするために、リクエストリソース80には3個のイニシエータ60,61,62と3個のターゲット70、71、72が接続される例を示す。

【0082】

リクエストリソース80は、排他情報バッファ(EXCLBUF)81、比較回路(COMP)90,91,92、アクセス要求無効化回路(DSABL)100,101,102、及び調停回路(ARBTR)82を有する。調停回路82は調停ロジック(ARBLGC)83とセレクタ(SLCTR)84から成る。

【0083】

排他情報バッファ81は、たとえば図4に例示されるように、排他処理要求としてのロックLCKがアサートされたリクエストパケットを受理したとき当該要求元としてのイニシエータ番号INITIDに対応して、排他処理要求の有無を示す排他情報EXCL、当該リクエストパケットに含まれるアドレス情報ADD、アクセスデータサイズDSZ、及びバイトイネーブルBEを保持する。図4に示される対象イニシエータ番号TGINITと、リード又はライトのようなアクセス方向R/Wの情報とは排他制御レジスタ27が保持する。アクセスデータサイズDSZは、アドレス範囲の全てをアドレス情報で指定しない場合に、先頭アドレスとアクセスデータサイズによって指定する場合に用いるデータである。対象イニシエータ番号TGINITと、アクセス方向R/Wに応ずる情報はそもそもリクエストパケットで指定される情報ではなく、CPUが排他制御レジスタ27に指定するデータである。イニシエータID#0の対象イニシエータ番号TGINITは“#1=1/0,#2=1/0”となり、1は排他処理の対象、0は排他処理の非対象を意味する。例えばイニシエータID#0の対象イニシエータ番号TGINITは“11”すなわち“#1=1,#2=1”であり、イニシエータ#0が出力する排他処理要求に対しては、イニシエータID#1、#2の何れからのアクセス要求に対しても排他処理の対象とする。イニシエータID#1の対象イニシエータ番号TGINITは“#0=1/0,#2=1/0”となり、例えばイニシエータID#1の対象イニシエータ番号TGINITは“01”すなわち“#0=0,#2=1”であり、イニシエータ#1が出力する排他処理要求に対しては、イニシエータID#0からのアクセス要求に対しては排他処理の対象とはせず、イニシエータID#2からのアクセス要求に対しては排他処理の対象とする。

【0084】

例えば比較回路90、91、92は、前記排他情報バッファ81等に格納された情報と対応するイニシエータ60、61、62から与えられるリクエストパケットに含まれるアドレス情報とを比較して、その比較結果を出力する。例えば比較回路90は、前記排他情報バッファ81が保持しイニシエータIDが#1、#2のエントリデータと、イニシエータ60が出力するリクエストパケットに含まれていてそのエントリデータに対応するデータとを比較する。比較回路91は、前記排他情報バッファ81が保持しイニシエータIDが#0、#2のエントリデータと、イニシエータ60が出力するリクエストパケットに含まれていてそのエントリデータに対応するデータとを比較する。比較回路92は、前記排他情報バッファ81が保持しイニシエータIDが#0、#1のエントリデータと、イニシエータ60が出力するリクエストパケットに含まれていてそのエントリデータに対応するデータとを比較する。ここでは、夫々の比較回路90,91,92は、夫々の比較項目で排他条件に一致しなければハイレベル(“H”)を出力する。

【0085】

アクセス要求無効化回路(DSABL)100,101,102は、対応する比較回路90,91,92の出力が“L”のとき、対応するアクセス要求を無効化する。即ち、アクセス要求無効化回路100は、比較回路90の出力とイニシエータ69からのリクエストREQとの論理積を採り、当該リクエストREQのハイレベルによってアクセスが要求されているとき、比較回路90の出力が“H”でなければ対応するリクエストREQによるアクセス理要求を無効化する。アクセス要求無効化回路101は、比較回路91の出力とリクエストREQとの論理積を採り、当該リクエストREQのハイレベルによってアクセスが要求されているとき、比較回路91の出力が“H”でなければ対応するリクエストREQによるアクセス要求を無効化する。アクセス要求無効化回路102は、比較回路92の出力とリクエストREQとの論理積を採り、当該リクエストREQのハイレベルによってアクセスが要求されているとき、比較回路92の出力が“H”でなければ対応するリクエストREQによるアクセス要求を無効化する。要するに、アクセス要求無効化回路100,101,102は、アクセス対象アドレスに着目すれば、比較回路による比較結果に基づいて、既に受理されている排他処理要求とアクセス対象アドレスが重なる範囲を最大限として、既に受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するものである。アクセス対象アドレスが重なる範囲とは、同一のイニシエータ上でアクセスアドレスが重なることを意味する。

【0086】

調停ロジック83は、前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理する。セレクタ84は、調停ロジック83が受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う。更にセレクタ84は、排他処理要求を伴って受理されたアクセス要求のリクエストパケットの情報によって排他情報バッファ81の対応するエントリの情報を更新する。

【0087】

尚、図1ではリクエストパケットREQPCKTの中のリクエストREQとグラントGNTの所在を明示しているが、その他の信号はそれとは別の信号線に含まれる。

【0088】

上記によれば、排他的アクセスの対象となるアドレス情報などのアクセス情報を保持し、イニシエータが出力するアクセス情報と前記保持されたアクセス情報を比較し、アクセス対象アドレスが重なる範囲を最大限として他のアクセス要求を無効化するから、ターゲット単位よりも細かなアドレスを対象とするピンポイントの排他処理を実現することができる。

【0089】

そして、調停回路の処理に先立って排他処理要求を伴うアクセス要求に対する選択的な無効化の処理を行うから、排他的な制御により抑止されるべきアクセス要求が調停回路による調停処理の対象にはされず、この点において、イニシエータがアクセス要求を行ってからアクセス要求が受理されるまでの時間を短縮するのに寄与する。

【0090】

図1において、前記調停ロジック83は、前記イニシエータ毎にグラントGNTを出力し、前記イニシエータからリクエストREQによりアクセス要求を入力した場合、前記アクセス要求無効化回路100によりそのアクセス要求が有効とされ、かつ、調停によって前記イニシエータからのアクセス要求が無効とされた場合や、調停によって前記イニシエータからのアクセス要求を受理しない場合には、グラントGNTをディアサート状態とする。調停ロジック83は、アクセス要求の無効化に関わらず、イニシエータからのアクセス要求を受理したときにのみグラントGNTをアサートするから、これを受けるイニシエータは、アクセス要求の後、これが受理されたか無効化されたかを感知することなく、グラントGNTのアサートを待てばよい。したがって、スプリットトランザクションによるパケット交換方式のバスインタフェースでは、排他処理を伴うアクセス要求が一時的に抑止される場合でもイニシエータは単に待てばよく、再度アクセス要求を行うなどの処理は不要であり、ピンポイントの無効化を採用してもイニシエータの実装は容易である。

【0091】

図1において、前記イニシエータは、例えばアクセスを要求した場合、入力されるグラントGNTのディアサート状態によってアクセス要求が受理されていないと判定し、入力されるグラントGNTがアサート状態であることにより、アクセス要求が受理されたと判定する。

【0092】

図5には比較回路(COMP#0)90の一例としてアドレス比較と排他要求比較を行なう例が示される。110は、排他情報バッファ81におけるイニシエータID#1のエントリのアドレス情報ADDと、イニシエータID#0のイニシエータ60から出力されるアドレスADDとを比較するアドレス比較器であり、比較一致によって“H”を出力する。111は、排他情報バッファ81におけるイニシエータID#2のエントリのアドレス情報ADDと、イニシエータID#0のイニシエータ60から出力されるアドレスADDとを比較するアドレス比較器であり、比較一致によって“H”を出力する。アンドゲート112は排他情報バッファ81におけるイニシエータID#1のエントリの排他情報EXCLと、アドレス比較器110の比較結果を2入力として論理積を採る。アンドゲート113は排他情報バッファ81におけるイニシエータID#2のエントリの排他情報EXCLと、アドレス比較器111の比較結果を2入力として論理積を採る。エントリの排他情報EXCLは対応するイニシエータが排他処理を要求していれば“H”とされる。負論理和ゲート(ノアゲート)114はアンドゲート112、113の出力を2入力として、負論理和を採る。アクセス要求無効化回路100はイニシエータID#0が出力するリクエストREQとナンドゲート114の出力を2入力とするアンドゲートによって構成される。したがって、イニシエータ#1が排他処理を要求しており(INT1,EXCL(EXCLBUF)=“H”)且つアドレス比較器110による比較が一致であるときアンドゲート112の出力が“H”、また、イニシエータ#2が排他処理を要求しており(INT2,EXCL(EXCLBUF)=“H”)且つアドレス比較器111による比較が一致であるときアンドゲート113の出力が“H”となるから、その何れの場合においても、イニシエータ#0からのアクセス要求は無効化される。他の比較回路の場合も上記と同様である。

【0093】

このように、アドレス比較と排他要求比較を行なう比較回路を採用する場合、一つのイニシエータからアクセス要求があったとき、それによるアクセスアドレスと重なるアドレスについて既に別のイニシエータからの排他処理要求が受理されている場合に、当該一つのイニシエータからのアクセス要求を無効化する。

【0094】

図6には比較回路(COMP#0)90の一例としてアドレス比較、排他要求比較及びバイトイネーブル比較を行なう例が示される。120は図5の比較器110と同じであり、121は図5の比較器111と同じである。比較器125は排他情報バッファ81におけるイニシエータID#1のエントリのバイトイネーブルBEと、イニシエータID#0のイニシエータ60から出力されるバイトイネーブルBEとを比較するアドレス比較器であり、比較一致によって“H”を出力する。126は、排他情報バッファ81におけるイニシエータID#2のエントリのバイトイネーブルBEと、イニシエータID#0のイニシエータ60から出力されるバイトイネーブルBEとを比較するアドレス比較器であり、比較一致によって“H”を出力する。アンドゲート122は排他情報バッファ81におけるイニシエータID#1のエントリの排他情報EXCL、アドレス比較器120の比較結果、及びアドレス比較器125の比較結果を3入力として論理積を採る。アンドゲート123は排他情報バッファ81におけるイニシエータID#2のエントリの排他情報EXCL、アドレス比較器111の比較結果、及びアドレス比較器111の比較結果を3入力として論理積を採る。エントリの排他情報EXCLは対応するイニシエータが排他処理を要求していれば“H”とされる。負論理和ゲート(ノアゲート)124はアンドゲート122、123の出力を2入力として、負論理和を採る。アクセス要求無効化回路100はイニシエータID#0が出力するリクエストREQとナンドゲート124の出力を2入力とするアンドゲートによって構成される。したがって、イニシエータ#1が排他処理を要求しており(INT1,EXCL(EXCLBUF)=“H”)且つアドレス比較器120による比較及びアドレス比較器125による比較が夫々一致であるときアンドゲート122の出力が“H”、また、イニシエータ#2が排他処理を要求しており(INT2,EXCL(EXCLBUF)=“H”)且つアドレス比較器121による比較及びアドレス比較器126による比較が一致であるときアンドゲート123の出力が“H”となるから、その何れの場合においても、イニシエータ#0からのアクセス要求は無効化される。他の比較回路の場合も上記と同様である。

【0095】

このように、アドレス比較、排他要求比較及びバイトイネーブル比較を行なう比較回路を採用する場合、一つのイニシエータからアクセス要求があったとき、それによる指定アクセスアドレスと重なり、バイトイネーブルによるアクセス対象バイトが重なっている、既に別のイニシエータからの排他処理要求が受理されている場合に、当該一つのイニシエータからのアクセス要求を無効化する。

【0096】

図7には図6に対して更に対象イニシエータ番号TGINITも比較対象にした比較回路(COMP#0)90の一例が示される。図6との相違点は122,123のアンドゲートを4入力とし、INITID#1に関するアンドゲート132には排他情報バッファ81におけるINITID#1のエントリが保有する対象イニシエータ番号TGINITのINIT#0に対応する値を入力し、INITID#2に関するアンドゲート133には排他情報バッファ81におけるINITID#2のエントリが保有する対象イニシエータ番号TGINITのINIT#0に対応する値を入力する。図4の例に従えば、INITID#1のエントリにおいて、対象イニシエータ番号TGINITは“#0、#2”=“01”であるから、INIT#1,TGINIT(INIT#0)=0がアンドゲート132に、INITID#2のエントリにおいて、対象イニシエータ番号TGINITは“#0、#1”=“10”であるから、INIT#2,TGINIT(INIT#0)=0がアンドゲート133に供給される。これにより、イニシエータ60(INITID#0)からのアクセス要求は、イニシエータ61(INITID#1)による排他処理要求がすでに受理されていてもそれによって排除されず、イニシエータ62(INITID#2)による排他処理要求がすでに受理されていていればそれによって排除される。

【0097】

このように対象イニシエータ番号TGINITも比較対象にしてアドレス比較などを行えば、レジスタ27の設定内容で特定される一部のイニシエータからのアクセス要求に限って無効化することができるようになる。

【0098】

上記比較回路の具体例は図1に例示されるように3個のイニシエータ60,61,62の場合を例としており、イニシエータの数に応じてアンドゲート122,123(132,133)に係る構成を増やせばよい。

【0099】

《ターゲットを最小単位とする排他制御用のリクエストリソースの併用》

上記説明では、アクセス対象ターゲットが既に受理された排他処理の対象ターゲットと同じであるかはアドレス比較を用いた。ターゲット単位でアクセスの無効化を行う場合には、図8に例示されるように、ターゲットへの接続を変えたリクエストリソース(REQRSC)130、131を設け、リクエストリソース130,131へのリクエストパケットの振り分けを行う振り分け回路(PCKTSRT)132を用いればよい。すなわち、リクエストリソース130にはターゲットTGT70,71を接続し、リクエストリソース131には1個のターゲットTGT72を接続する。振り分け回路132はリクエストリソースに含まれるアクセスアドレスADDからアクセス対象ターゲットを判別し、ターゲット70又は71をアクセス対象とするリクエストパケットをリクエストリソース130に供給し、ターゲット72をアクセス対象とするリクエストパケットをリクエストリソース131に供給する。リクエストリソース130は接続されるターゲットが相違される点を除いて図1で説明したリクエストリソース80と同じ構成を備えるから、その詳細な説明は省略する。リクエストリソース131はターゲットを最小単位として排他処理要求に対する制御を行う点が図1のリクエストリソース80と相違される。即ち、リクエストリソース131の比較回路140は、図9に例示される。図9には比較回路(COMP#0)140の一例が示される。同図に示される比較回路140は、排他情報バッファ81におけるイニシエータID#1のエントリの排他情報EXCLと、排他情報バッファ81におけるイニシエータID#2のエントリの排他情報EXCLとが直接負論理和ゲート(ノアゲート)114に供給される。イニシエータ#1が排他処理を要求している状態(INT1,EXCL(EXCLBUF)=“H”)、又はイニシエータ#2が排他処理を要求している状態(INT2,EXCL(EXCLBUF)=“H”)の場合に、イニシエータ#0からのターゲット72へのアクセス要求は無効化される。

【0100】

リクエストリソース131には特定の一のターゲット70を対象とするリクエストパケットだけが振り分けられるから、ターゲット単位の排他制御にはアドレス比較を要せず、一のターゲット70を対象として他のイニシエータが発行した排他処理要求が既に受理されているか否か判定すれば、一のターゲット70に対してはこれを最小単位とする排他制御を行うことができる。

【0101】

《イニシエータを単位とする排他制御》

排他制御を要求したイニシエータがCPUであれば、パケットルータが、排他制御期間内に別のイニシエータによる別のアドレスへのアクセスを許可しても問題はない。一方,イニシエータの中には、他のイニシエータを排除して自己のアクセス頻度を高めることを目的として、排他的アクセスを要求するものがある。例えばDMAC等である。このようなイニシエータによる排他処理要求に対しては、アドレス等によるピンポイントの排他処理ではなく、ターゲットに対する全アクセスを対象とする排他処理が有効である。このため、排他処理を要求するイニシエータを単位として、全アクセスで排他制御を行う回路と、ピンポイントで排他制御を行う回路を混在させるのがよい。

【0102】

具体的には,イニシエータがCPUであれば図1で説明したように、アドレスを限定した排他処理を行い、イニシエータがCPU以外であれば、アドレスを限定しない排他処理を行う。パケットルータに直接イニシエータが接続されている場合、イニシエータがCPUであるかCPU以外であるかはSOCや半導体装置の開発段階で決まるため、イニシエータのタイプがCPUかCPU以外かを識別する回路を特別に設けることは不要である。パケットルータに、イニシエータが接続されている場合、リクエストパケットに含まれる属性の一つであるイニシエータ識別情報(シースSRC)に基づいてイニシエータタイプの判定を行えばよい。

【0103】

《排他情報バッファのエントリ数》

排他情報バッファのオーバーフローにより、排他処理が正常に行われないことがあってはならない。このため,排他情報バッファ81のエントリ数は、イニシエータが同時に実行できる排他的アクセスの合計値以上とする。例えば図4の例では一つのイニシエータIDが格納するアクセス情報は一つである。階層インターコネクトのように、パケットルータにパケットルータが接続されている場合、排他情報バッファのエントリ数はパケットルータに接続された全てのイニシエータが同時に実行できる排他的アクセスの合計数となる。

【0104】

一つのCPUが同時に実行できる排他的アクセス数が複数ある場合に、その識別をプロセスIDを用いて行ってもよい。この場合には、前記排他情報バッファが保持するアクセス情報には、アクセス対象アドレス情報と共に、そのアクセス対象アドレス情報を用いるプロセスのプロセスID情報を含める。この場合、前記アクセス要求無効化回路は、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とはプロセスIDが異なるアクセス要求を無効化する。同じイニシエータによる排他的アクセス要求に対してプロセスIDを考慮してアクセス要求の無効化に対処することができる。

【0105】

《排他処理に競合するアクセスに関するデバッグ支援》

セマフォを実現するために排他処理を使う場合、通常はCPUが排他的アクセスを要求中のアドレスに対して以下の事象が発生することはなく、発生した場合、その原因はソフトウエアやハードウエアの不具合である可能性が高い。その事象とは、排他処理を要求しているイニシエータ(CPU)以外のCPUからのライトアクセス、CPU以外のイニシエータからの任意のアクセス、があることである。図3に例示されるように、パケットルータ12,13は、上記事象を検出したときに、割込みコントローラ24に割込み要求信号IRQ1,IRQ2を出力し、CPU23に割り込み信号をINT出力する。これにより、ソフトウエアやハードウエアの不具合の早期発見に資することができる。

【0106】

《階層化ルータの排他処理》

図10には複数のパケットルータを階層的に組み合わせてオンチップインターコネクトを構築した例が示される。パケットルータ150,151の間には中継回路として例えばキューイングバッファ(QUEBUF)152は配置される。パケットルータ150にはイニシエータ160,161が接続され、パケットルータ151にはイニシエータ162,163が接続される。代表的に示されたターゲット164はパケットルータ151に接続される。このように、複数のパケットルータ150,151がキューイングバッファ152を介して複数階層に直列接続されているとき、夫々のパケットルータ150,151のリクエストリソースは、イニシエータから所要のターゲットに対するアクセス要求に伴う排他処理要求を受理する排他処理機能を備える。例えばリクエストリソースは図1で説明したように構成される。この場合、パケットルータ150のセレクタ84の出力は例えばワイヤード・オアでキューイングバッファ152の上流側ポートに接続される。キューイングバッファ152の下流側ポートは、一つのイニシエータとしてパケットルータ151のリクエストリソースに接続されればよい。

【0107】

階層的インターコネクトを構成する複数のパケットルータ150,151のうち、アクセス要求の上流(イニシエータに近い側)のパケットルータ150に排他処理機構を持たない場合、上流側パケットルータ150に接続された一のイニシエータ160からの排他処理要求を伴うアクセスに続いて同じ階層のパケットルータ150に接続された別のイニシエータ161が前記アクセス要求と同じアドレスに対してアクセス要求を送信したときに、ハングアップが発生する。これは、パケットルータ間の中継回路(キューイングバッファ)152が前記一のイニシエータ160のリクエストパケットをパケットルータに送信したときに下位階層のパケットルータ151が排他処理によって前記別のイニシエータ161のアクセス要求を抑止するために、当該一のイニシエータ160が排他処理停止要求を通知するアクセス要求が中継回路152を通れずに下流のパケットルータ151に送信できないからである。

【0108】

また、アクセス要求の下流のパケットルータ151に排他処理機能を持たない場合は、排他処理機能を有する上流のパケットルータ150に接続するイニシエータ160,161からの排他処理要求を下流のパケットルータ151が受理しないため、排他性を保証することができない。

【0109】

図11と図12には複数のパケットルータを階層的に組み合わせてオンチップインターコネクトを構築したとき、排他処理を要求するイニシエータを同一階層のパケットルータに集約して接続した例が示される。図11及び図12においてパケットルータ150、151及びキューイングバッファ152は図10と同じであり、パケットルータ150、151は共に排他制御機能を備える。図11及び図12ではイニシエータ170,171は排他処理を要求するイニシエータとされ、イニシエータ172,173は排他処理を要求しないイニシエータとされる。このように、排他処理要求を伴うアクセスを要求するイニシエータは、同一階層のパケットルータに集約して結合される。

【0110】

図13に例示されるように、排他処理要求を行なうイニシエータ170,171を、排他処理要求を行なわないイニシエータ172,173に混在させて上流及び下流のパケットルータ150,151に分散配置した場合、上流及び下流のイニシエータ170,171がそれと同一アドレスについて排他的なアクセスを要求したときには、上流側で排他処理を要求しないイニシエータ172からのアクセス要求は、それが前記排他的なアクセス要求によって抑止されるべきものか否かにかかわらず、抑止される。これは、中継回路152において、先に上流側のイニシエータ170から下流側のパケットルータ151に転送されるべき排他処理要求のアクセス要求が、下流側のイニシエータ171の排他的アクセス終了まで、下流側への伝達が抑止されるためである。

【0111】

以上説明した実施の形態によれば以下の作用効果がある。

【0112】

(1)排他処理対象アドレスを対象とした、ピンポイントの排他処理ができる。このため,排他処理に伴う転送性能を向上させることができる。本発明では排他情報保持バッファに排他処理対象アドレスを保持し,アクセス要求が排他処理対象アドレスに該当するか否かを判定し,該当するアクセス要求だけを排除するからである。

【0113】

(2)排他処理対象アドレスに限定した排他処理と、(スループット向上を目的とした)排他処理対象アドレスを限定しない排他処理を、一つのSOC若しくはチップに混在できる。本発明ではアクセス要求先のアドレスを振り分け回路で判定してリクエストパケットを所定のリクエストリソースに簡単に振り分けることができるからである。

【0114】

(3)単一のイニシエータによる複数の排他的アクセスを同時に処理できる。排他情報保持バッファに、プロセス識別情報(プロセスID)を記憶させ、アクセス要求が排他処理対象プロセスIDに該当するか否かを判定し、該当するアクセス要求だけを排除するからである。

【0115】

(4)排他処理に伴って抑止されるアクセス要求を調停前に排除するので、排他処理に伴って抑止されるアクセス要求が調停処理によって受理されることがない。結果として有効な(排他処理に伴って排除されない)アクセスが早く受理され、高いデータ転送性能を得る。イニシエータと調停回路の間にイニシエータ毎に比較回路を配置するから、調停前に排他処理によって抑止すべきアクセス要求を抑止し、調停回路が排他処理によって抑止されないアクセス要求だけを調停対象とするからである。

【0116】

(5)階層インターコネクトにおいて、排他処理によるハングアップを回避できる。複数のパケットルータを用いて階層的に構成されたインターコネクトにおいて、上流(イニシエータに近い側)のパケットルータが、排他処理によって抑止されるべきアクセス要求を抑止するためである。この抑止動作により、下流(ターゲットに近い側)のパケットルータによる排他処理によって抑止されるリクエストパケットが中継回路に滞留しないようにするためである。下流のパケットルータによる排他処理によって抑止されるアクセス要求が中継回路に滞留すると、下流のパケットルータに排他的アクセスの終了を通知するアクセス要求を転送できなくなり、これによってハングアップ状態に陥る。

【0117】

(6)階層インターコネクトにおいて、排他処理に伴って、排他処理によって排除されないアクセスが排他処理完了まで抑止され続けることがない。排他制御を要求するイニシエータを異なるパケットルータに接続しないため、排他制御によって抑止されるべきアクセス要求が、排他制御によって抑止されないアクセス要求の処理を阻害しないからである。

【0118】

(7)排他的処理の対象となっているアドレスに対する不正なアクセスを検出することにより、ソフトウエアやハードウエアの不具合の早期発見を容易にする。CPUによる排他処理の対象となるアドレスに対して、前記CPU以外のCPUがライトアクセスを実行したり、前記CPU以外の非CPUであるイニシエータがアクセスしたりすることは、通常意図的に発生しない事象であり、不具合である可能性が高い。排他処理の対象となるアドレスに対する前記CPU以外のCPUによるライトアクセスと、前記CPU以外の非CPUであるイニシエータによるアクセスを検出し、これによって割り込み信号をアサートできるからである。

【0119】

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【図面の簡単な説明】

【0120】

【図1】図1はパケットルータのリクエストリソースについて原理的構成を具体的に例示するブロック図である。

【図2】図2はスプリットトランザクションによるパケット交換方式のシステムの概念を例示するブロック図である。

【図3】図3はスプリットトランザクションによるパケット交換を適用したマイクロコンピュータ及び拡張デバイスからなるチップセットのブロック図である。

【図4】図4は排他情報バッファが保有する排他情報と排他制御レジスタが保有する制御情報を例示する説明図である。

【図5】図5は比較回路90の一例としてアドレス比較と排他要求比較を行なう構成を例示する論理回路図である。

【図6】図6は比較回路90の一例としてアドレス比較、排他要求比較及びバイトイネーブル比較を行なう構成を例示する論理回路図である。

【図7】図7は図6に対して更に対象イニシエータ番号TGINITも比較対象にした比較回路90の一例を例示する論理回路図である。

【図8】図8はターゲット単位でアクセスの無効化を行うために振り分け回路を採用したリクエストリソースを例示するブロック図である。

【図9】図9はターゲットを最小単位として排他処理要求に対する制御を行うための比較回路を例示する論理回路図である。

【図10】図10は複数のパケットルータを階層的に組み合わせてオンチップインターコネクトを構築するときのパケットルータの排他処理機能に着目した説明図である。

【図11】図11は複数のパケットルータを階層的に組み合わせてオンチップインターコネクトを構築するときの排他処理を要求するイニシエータの集約配置に着目した説明図である。

【図12】図12は複数のパケットルータを階層的に組み合わせてオンチップインターコネクトを構築するときの排他処理を要求するイニシエータの別の集約配置に着目した説明図である。

【図13】図13は排他処理を要求するイニシエータを分散配置したときの問題点に着目した説明図である。

【符号の説明】

【0121】

1 イニシエータ(INIT)

2 ターゲット(TGET)

3 パケットルータ(PCKTRT)

3A リクエストリソース(REQRSC)

3B レスポンスリソース(RESRSC)

REQPCKT リクエストパケット

REQ リクエスト

GNT グラント

ADD アドレス

BE バイトイネーブル

LCK ロック

RESPCKT レスポンスパケット

10 マイクロコンピュータ

11 拡張デバイス

12,13パケットルータ

14 キューイングバッファ(QUEBUF)

15 パケットルータ

20〜23 中央処理装置(CPU)

24 割り込みコントローラ(INTC)

25 ROMアクセスコントローラ(ROMC)

26 周辺制御部(PRPHC)

27 ルーティングコントローラレジスタ(RCREG)

31 表示制御部(DISPC)

32 ハードディスク制御部(HDDC)

33 ダイレクト・メモリ・アクセス・コントローラ(DMAC)

34 フラッシュメモリコントローラ(FMRYC)

35 シンクロナスDRAMコントローラ(DMRYC)

36 周辺制御部(PRPHC)

80 リクエストリソース(REQRSC)

60,61,62 イニシエータ

70、71、72 ターゲット

81 排他情報バッファ(EXCLBUF)

90,91,92 比較回路(COMP)

100,101,102 アクセス要求無効化回路(DSABL)

82 調停回路(ARBTR)

83 調停ロジック(ARBLGC)

84 セレクタ(SLCTR)

130、131 リクエストリソース(REQRSC)

150,151 パケットルータ

152 キューイングバッファ(QUEBUF)

160,161、162,163 イニシエータ

170,171,172,173 イニシエータ

【技術分野】

【0001】

本発明は、バスインタフェースにおける、共有リソースに対するアクセスの排他処理に関し、例えば半導体集積回路化されたマイクロコンピュータ、システム・オン・チップ(SOC)化されたデータプロセッシングデバイス、チップセット、マルチチップを用いてシステム・イン・パッケージ化されたデータ処理モジュールなどの半導体装置におけるスプリットトランザクションによるパケット交換方式のバスインタフェースに適用して有効な技術に関する。

【背景技術】

【0002】

バスインタフェースには、バスアクセスのリクエスト中は他のリクエストを受け付けないというインターロック方式のほかに、スプリットトランザクションによるパケット交換方式がある。この方式は、アクセスを要求する回路が、アクセス要求の内容を含むリクエストパケットを、アクセス要求に応答する回路に送信し、アクセス要求に応答する回路は応答内容を含むレスポンスパケットを、アクセスを要求した回路に送信する、という処理を行なうものである。リクエストパケットとレスポンスパケットを含む一連の処理をトランザクションと称し、1つのトランザクションをパケットの転送毎に分離して、バスアクセス効率を向上させることができる。アクセスを要求する回路をイニシエータ、アクセス要求に答える回路をターゲットと呼ぶ。回路の種類によってはイニシエータとターゲットの双方の機能を備えるものもある。イニシエータとターゲットはリクエストパケットとレスポンスパケットの中継を行うパケットルータがある。パケットルータは、一つのターゲットに対して複数のイニシエータがアクセスを要求したときの調停、共有リソースなどに対する排他制御のために後のアクセス要求を無効化する制御などを行う。リソース単位で排他処理を行なう場合、排他処理中には、排他処理要求が受理されたイニシエータ以外のイニシエータによる、排他的アクセスの実行対象であるターゲットへのアクセスを抑止するという、プロトコルが従来から採用さてれている。例えば、ターゲットがメモリコントローラであれば,排他処理中はメモリに対する他イニシエータのアクセスが全て抑止される。

【0003】

特許文献1には、マルチCPUのシステムにおいて共有リソースに対するアクセスの排他処理について記載がある。これによれば、CPU単位の排他制御ではなく、CPUが排他処理を要求したとき、当該CPUのアクセス対象領域について他のCPUからのアクセス要求を排他する制御を行う。

【0004】

【特許文献1】特開平5−225117号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

今後普及が見込まれるマルチコアSOC(一つのチップに複数のCPUを搭載するSOC)では、シングルコアSOC(一つのチップに単一のCPUを搭載するSOC)に比して排他処理が多用されることが考えられるため、ターゲット単位の排他処理では、排他処理に伴う転送性能(バスアクセス性能)の低下が大きいため、排他処理単位の縮小が必要であると考えられる。特許文献1ではその点が考慮され、アドレス領域単位の排他制御を行う。

【0006】

しかしながら、特許文献1に記載の技術ではアクセス要求に対して先に優先度やアクセス要求の競合状態に基づいてバス調停部で許可候補信号を生成し、許可候補のアクセス要求に係るアドレス情報をセレクタで選択し、選択したアドレス情報が、先に受理された排他制御対象のアドレス領域に重なるかが判別され、重なる場合には、先に許可候補としたCPUにバス使用不許可を返す、という制御を行う。要するに、アクセス要求が排他処理によって抑止されるべきものか否かが、調停処理の後に判明する。このため、特許文献1に記載の技術では、排他処理に伴って抑止されるべきアクセス要求を調停前に排除できず、調停によって受理されるべきアクセス要求を早く確定することができない。このため、アクセス要求に対する処理効率が低く、この点においてデータ処理の高速化を阻む結果となる。

【0007】

また、スプリットトランザクションによるパケット交換方式のバスインタフェースでは、排他処理を伴うアクセス要求が一時的に抑止される場合でもイニシエータは単に待たされるだけであるが、特許文献1に記載の技術をそれに適用する場合を想定すると、アクセス要求が受理されないCPUなどのイニシエータにはバス使用不許可の信号が返されることになり、イニシエータは単に待つだけでは済まされず、再度アクセス要求を行うなどの処理が必要になり、イニシエータの実装が通常よりも複雑になる。

【0008】

本発明の目的は、排他処理に伴って抑止されるべきアクセス要求を調停前に排除することができ、調停によって受理されるべきアクセス要求を早く確定することができる半導体装置を提供することにある。

【0009】

本発明の別の目的は、アクセス要求に対する処理効率が高く、この点においてデータ処理の高速化に寄与することができる半導体装置を提供することにある。

【0010】

本発明の更に別の目的は、排他処理を伴うアクセス要求が一時的に抑止される場合でもイニシエータは単に待つだけで済まされ、イニシエータの実装が容易な半導体装置を提供することにある。

【0011】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0012】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0013】

すなわち、排他的アクセスの対象となるアドレス情報などを保持し、イニシエータが出力するアドレス情報と前記保持されたアドレス情報を比較する。これにより、排他的アクセスの対象であるアドレスを対象とするピンポイントの排他処理を実現する。

【0014】

そして、調停処理に先立って排他処理に伴うアクセス要求の排除を行う。このため、排他処理に伴って抑止されるべきアクセス要求が調停処理されることを防止し、イニシエータがアクセス要求を行ってからアクセス要求が受理されるまでの時間を短くすることが出来る。

【0015】

また、本発明では,階層的インターコネクトを構成する複数のパケットルータの全てに上記排他処理のための回路を搭載する。これにより、ハングアップ(アクセス要求が処理できなくなる状態に陥ること)を発生させることなく、ピンポイントで排他処理を行うことができ、しかもこのピンポイントの排他処理に伴って排他処理によって抑止されないアクセス要求を排他的処理を必要とするアクセス要求の完了まで抑止することがない。

【0016】

また、本発明では、排他的アクセスに対して不正なアクセスがなされたことを検出して割り込みを発生する。これにより、ソフトウエアやハードウエアのデバッグが容易になる。

【発明の効果】

【0017】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0018】

すなわち、排他処理に伴って抑止されるべきアクセス要求を調停前に排除することができ、調停によって受理されるべきアクセス要求を早く確定することができる。

【0019】

アクセス要求に対する処理効率が高く、この点においてデータ処理の高速化に寄与することができる。

【0020】

排他処理を伴うアクセス要求が一時的に抑止される場合でもイニシエータは単に待つだけで済まされ、イニシエータの実装が容易である。

【発明を実施するための最良の形態】

【0021】

1.実施の形態の概要

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

【0022】

〔1〕《アドレス比較による排他制御》

本発明に係る半導体装置は、アクセスを要求することが可能な複数のイニシエータと、アクセスに応答することが可能な複数のターゲットと、アクセスを要求するイニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行うリクエストリソース及びアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースを備えたパケットルータとを有する。前記パケットルータのリクエストリソース(80)は、排他情報バッファ(81)、比較回路(90,91,92)、アクセス要求無効化回路(100,101,102)、及び調停回路(80)を有する。排他情報バッファは、排他処理要求を含むリクエストパケット(REQPCKT)を受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する。比較回路は、前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する。アクセス要求無効化回路は、前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化する。調停回路は、前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う。

【0023】

上記によれば、排他的アクセスの対象となるアドレス情報などのアクセス情報を保持し、イニシエータが出力するアクセス情報と前記保持されたアクセス情報を比較し、アクセス対象アドレスが重なる範囲を最大限として他のアクセス要求を無効化するから、ターゲット単位よりも細かなアドレスを対象とするピンポイントの排他処理を実現することができる。

【0024】

そして、調停回路の処理に先立って排他処理要求を伴うアクセス要求に対する選択的な無効化の処理を行うから、排他的な制御により抑止されるべきアクセス要求が調停回路による調停処理の対象にはされず、この点において、イニシエータがアクセス要求を行ってからアクセス要求が受理されるまでの時間を短縮するのに寄与する。

【0025】

〔2〕《調停回路によるグラント信号の処理》

項1の半導体装置において、例えば前記調停回路は、前記イニシエータ毎にグラント信号(GNT)を出力し、前記イニシエータからアクセス要求を入力した場合、前記アクセス要求無効化回路によりそのアクセス要求が有効とされ、かつ、調停によって前記イニシエータからのアクセス要求を受理した場合に前記グラント信号をアサート状態とし、前記アクセス要求無効化回路によりそのアクセス要求が無効とされた場合や、調停によって前記イニシエータからのアクセス要求を受理しない場合には、前記グラント信号をディアサート状態とする。

【0026】

調停回路は、アクセス要求の無効化に関わらず、イニシエータからのアクセス要求を受理したときにのみグラント信号をアサートするから、これを受けるイニシエータは、アクセス要求の後、これが受理されたか無効化されたかを感知することなく、グラント信号のアサートを待てばよい。

【0027】

したがって、スプリットトランザクションによるパケット交換方式のバスインタフェースでは、排他処理を伴うアクセス要求が一時的に抑止される場合でもイニシエータは単に待てばよく、再度アクセス要求を行うなどの処理は不要であり、ピンポイントの無効化を採用してもイニシエータの実装は容易である。

【0028】

〔3〕《イニシエータによるグラント信号の把握》

項2の半導体装置において、前記イニシエータは、例えばアクセスを要求した場合、入力されるグラント信号がディアサート状態であることによってアクセス要求が受理されていないと判定し、入力されるグラント信号がアサート状態であることにより、アクセス要求が受理されたと判定する。

【0029】

〔4〕《アドレス比較による排他制御》

項1の半導体装置において、前記排他情報バッファが保持するアクセス情報は例えばアクセス対象アドレス情報であり、この場合、前記アクセス要求無効化回路は、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるイニシエータからの新たなアクセス要求を無効化する(図5)。

【0030】

〔5〕《プロセスIDの比較による排他制御》

項1の半導体装置において、前記排他情報バッファが保持するアクセス情報は、例えばアクセス対象アドレス情報とそのアクセス対象アドレス情報を用いるプロセスのプロセスID情報であり、この場合、前記アクセス要求無効化回路は、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とはプロセスIDが異なるアクセス要求を無効化する。同じイニシエータによる排他的アクセス要求に対してプロセスIDを考慮してアクセス要求の無効化に対処することができる。

【0031】

〔6〕《排他情報バッファのエントリ数》

項5の半導体装置において、前記排他情報バッファは、前記調停回路が並列的に受理可能な排他処理要求を伴うアクセス要求毎のアクセス情報を格納可能な記憶容量を有する。要するに、前記排他情報バッファが保持するアクセス情報には例えばアクセス対象アドレス情報とそのアクセス対象アドレス情報を用いるプロセスのプロセスID情報を含む。この場合、前記アクセス要求無効化回路は、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とはプロセスIDが異なるアクセス要求を無効化する。1つのイニシエータが複数の排他処理要求を伴うアクセスを要求して並列的に受理される場合にもアクセス要求の無効化に対処することができる。

【0032】

〔7〕《アドレス情報及びバイトイネーブル比較による排他制御》

項1の半導体装置において、前記排他情報バッファが保持するアクセス情報は、例えば複数バイトのアクセス対象の先頭を示すアクセス対象アドレス情報と、複数バイトのアクセス対象範囲内の有効性をバイト単位で示すバイトイネーブル情報(BE)である。このとき、前記アクセス要求無効化回路は、アクセス対象アドレス情報のアドレスを先頭とする複数バイトのアクセス対象範囲内においてバイトイネーブル情報で有効性とされるアドレスと重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化する。これにより、アクセスアドレスを先頭アドレスとバイトイネーブルによって特定する場合にもアクセス要求の無効化に対処することができる(図6)。

【0033】

〔8〕《プロセスIDの比較による排他制御》

項1の半導体装置において、前記排他情報バッファが保持するアクセス情報は、例えば、複数バイトのアクセス対象の先頭を示すアクセス対象アドレス情報と、複数バイトのアクセス対象範囲内の有効性をバイト単位で示すバイトイネーブル情報と、アクセス対象のアドレス情報を用いるプロセスのプロセスID情報である。このとき、前記アクセス要求無効化回路は、アクセス対象アドレス情報のアドレスを先頭とする複数バイトのアクセス対象範囲内においてバイトイネーブル情報で有効性とされるアドレスと重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とはプロセスIDが異なるアクセス要求を無効化する。これにより、アクセスアドレスを先頭アドレスとバイトイネーブルによって特定する場合を考慮し、且つ、同じイニシエータによる排他的アクセス要求に対してプロセスIDを考慮して、アクセス要求の無効化に対処することができる。

【0034】

〔9〕《排他情報バッファのエントリ数》

項8の半導体装置において、前記排他情報バッファは、前記調停回路が並列的に受理可能な排他処理要求を伴うアクセス要求毎のアクセス情報を格納可能な記憶容量を有する。要するに、前記排他情報バッファが保持するアクセス情報には例えばアクセス対象先頭アドレス、バイトイネーブル情報及びそのアクセス要求に係るプロセスのプロセスID情報を含む。この場合、前記アクセス要求無効化回路は、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とはプロセスIDが異なるアクセス要求を無効化する。1つのイニシエータが複数の排他的処理のアクセスを要求して並列的に受理される場合にもアクセス要求の無効化に対処することができる。

【0035】

〔10〕《排他制御レジスタ》

項1の半導体装置において、排他制御の対象とするアクセスの属性を保持する排他制御レジスタ(27)を更に有する。前記アクセス要求無効化回路は、前記比較回路による比較結果と前記排他制御レジスタに保持されたアクセスの属性情報と基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化する。アクセス要求の無効化条件を排他制御レジスタにプログラマブルに設定することが可能になる(図7)。

【0036】

〔11〕《排他制御レジスタに設定されるアクセス属性》

項10の半導体装置において、前記排他制御レジスタには、アクセス属性として、例えばアクセス方向が設定される。前記アクセス要求無効化回路は、前記比較回路による比較結果と前記排他制御レジスタに保持されたアクセスの属性情報と基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なり且つ前記排他制御レジスタに設定されたアクセス方向へのアクセス要求を無効化する。特定のアクセス方向に対してアクセス要求を無効化することができる。

【0037】

〔12〕《排他制御レジスタに設定されるアクセス属性》

項10の半導体装置において、前記排他制御レジスタには、アクセス属性として、例えばイニシエータの識別情報が設定される。前記アクセス要求無効化回路は、前記比較回路による比較結果と前記排他制御レジスタに保持されたアクセスの属性情報と基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異り且つ前記排他制御レジスタに設定されたイニシエータからのアクセス要求を無効化する。特定のイニシエータに限ってアクセス要求を無効化することができる。

【0038】

〔13〕《排他処理に競合するアクセスに関するデバッグ支援》

項1の半導体装置は、前記イニシエータとして機能し得る複数のCPUと、前記ターゲットとして機能し得るメモリ及び割り込みコントローラを備える。前記メモリは前記複数のCPUの共有メモリである。前記パケットルータは、一のCPUから前記共有メモリに対する排他的な処理の要求を伴うリクエストパケットを受理した場合、そのアクセス対象アドレスと重なる範囲で、受理されている排他処理要求を伴うアクセス要求とは異なるライトアクセス要求があったことを、前記割り込みコントローラに通知する。CPUによる排他処理に競合するライトアクセスのあったことを割込みを通じてデバッグ支援のための装置に通知することができる。

【0039】

〔14〕《排他処理に競合するアクセスに関するデバッグ支援》

項1の半導体装置は、前記ターゲットとして機能し得るメモリ及び割り込みコントローラを備える。前記メモリは複数のイニシエータの共有メモリである。前記パケットルータは、一のイニシエータから前記共有メモリに対する排他処理要求を伴うリクエストパケットを受理した場合、そのアクセス対象アドレスと重なる範囲で、受理されている排他処理要求を伴うアクセス要求とは異なるライトアクセス要求があったことを前記割り込みコントローラに通知する。一のイニシエータによる排他処理に競合するライトアクセスのあったことを割込みを通じてデバッグ支援のための装置に通知することができる。

【0040】

〔15〕《ターゲット単位の排他制御の併用》

別の観点による半導体装置は、アクセスを要求することが可能な複数のイニシエータと、アクセスに応答することが可能な複数のターゲットと、アクセスを要求するイニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行う第1のリクエストリソース(131)及び第2のリクエストリソース(132)並びにアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースを備えたパケットルータとを有する。前記第1のリクエストリソースには特定の一のターゲットを対象とするリクエストパケットだけが振り分けられる。前記第2のリクエストリソースは他の複数のターゲットを対象とするリクエストパケットが振り分けられる。前記第1及び第2のリクエストリソースは、排他処理要求を含むリクエストパケットを受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する排他情報バッファと、前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する比較回路と、前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するアクセス要求無効化回路と、前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う調停回路と、を有する。

【0041】

前記第1のリクエストリソースには特定の一のターゲットを対象とするリクエストパケットだけが振り分けられるから、ターゲット単位の排他制御にはアドレス比較を要せず、一のターゲットを対象として他のイニシエータが発行した排他処理要求が既に受理されているか否か判定すればよい。

【0042】

〔16〕《階層化ルータの排他処理》

別の観点による半導体装置は、アクセスを要求することが可能な複数のイニシエータと、アクセスに応答することが可能な複数のターゲットと、前記イニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行うリクエストリソース及びアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースを備えた複数のパケットルータと、を備える。前記複数のパケットルータが中継回路を介して複数階層に直列接続されているとき、前記夫々のパケットルータのリクエストリソースは、イニシエータから所要のターゲットに対するアクセス要求に伴う排他処理要求を受理する排他処理機能を備える(図10)。

【0043】

階層的インターコネクトを構成する複数のパケットルータのうち、アクセス要求の上流(イニシエータに近い側)のパケットルータに排他処理機構を持たない場合、上流側パケットルータに接続された一のイニシエータからの排他処理要求を伴うアクセスに続いて同じ階層のパケットルータに接続された別のイニシエータが前記アクセス要求と同じアドレスに対してアクセス要求を送信したときに、ハングアップが発生する。これは、パケットルータ間の中継回路(キューイングバッファ)が前記一のイニシエータのリクエストパケットをパケットルータに送信したときに下位階層のパケットルータが排他処理によって前記別のイニシエータのアクセス要求を抑止するために、当該一のイニシエータが排他処理停止要求を通知するアクセス要求が中継回路を通れずに下流のパケットルータに送信できないからである。

【0044】

また、アクセス要求の下流のパケットルータに排他処理機能を持たない場合は、排他処理機能を有する上流のパケットルータに接続するイニシエータからの排他処理要求を下流のパケットルータが受理しないため、排他性を保証することができない。

【0045】

〔17〕

項16の半導体装置において、前記排他処理機能を備えるパケットルータのリクエストリソースは、排他処理要求を含むリクエストパケットを受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する排他情報バッファと、前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する比較回路と、前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するアクセス要求無効化回路と、前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う調停回路と、を有する。

【0046】

〔18〕《階層化ルータの排他処理》

別の観点による半導体装置は、アクセスを要求することが可能な複数のイニシエータと、アクセスに応答することが可能な複数のターゲットと、前記イニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行うリクエストリソース及びアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースを備えた複数のパケットルータと、を備える。前記複数のパケットルータが中継回路を介して複数階層に直列接続されているとき、前記夫々のパケットルータのリクエストリソースは、イニシエータから所要のターゲットに対する排他的な処理要求を受理する排他処理機能を備える。排他処理要求を伴うアクセスを要求するイニシエータは、同一階層のパケットルータに集約して結合される(図11、図12)。

【0047】

排他処理要求を行なうイニシエータを、排他処理要求を行なわないイニシエータに混在させて上流及び下流のパケットルータに分散配置した場合、上流及び下流のイニシエータがそれと同一アドレスについて排他的なアクセスを要求したときには、上流側で排他処理を要求しないイニシエータからのアクセス要求は、それが前記排他的なアクセス要求によって抑止されるべきものか否かにかかわらず、抑止される。これは、中継回路において、先に上流側のイニシエータから下流側のパケットルータに転送されるべき排他処理要求のアクセス要求が、下流側のイニシエータの排他的アクセス終了まで、下流側への伝達が抑止されるためである。

【0048】

〔19〕

項18の半導体装置において、前記排他処理機能を備えるパケットルータのリクエストリソースは、排他処理要求を含むリクエストパケットを受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する排他情報バッファと、前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する比較回路と、前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するアクセス要求無効化回路と、前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う調停回路と、を有する。

【0049】

2.実施の形態の詳細

実施の形態について更に詳述する。

【0050】

《スプリットトランザクションによるパケット交換》

図2にはスプリットトランザクションによるパケット交換方式のシステムの概念が例示される。このシステムでは、マスタとしてのイニシエータ(INIT)1がアクセス要求としてのリクエストパケット(REQPCKT)をスレーブとしてのターゲット(TGET)2に送信し、ターゲットがイニシエータにアクセス応答としてのレスポンスパケット(RESPCKT)を送信することで転送が行われる。パケットルータ(PCKTRT)3は、同時に転送されるリクエストパケットやレスポンスパケットの調停を行う。パケットルータ3は、アクセスを要求するイニシエータ1から与えられるリクエストパケットをアクセス要求に応答するターゲット2に与える制御を行うリクエストリソース(REQRSC)3A及びアクセス要求に応答するターゲット2から与えられるレスポンスパケットをアクセス要求元のイニシエータ1に返す制御を行うレスポンスリソース(RESRSC)3Bを備える。実際のシステムではイニシエータ1とターゲット2は適宜の数だけ配置される。また、イニシエータ1とターゲット2は必ずしも別々の回路であることを要せず、システム動作上、ある局面ではイニシエータ1となり、別の局面ではターゲット2とされる場合もあり、例えばDMAC(ダイレクト・メモリ・アクセス・コントローラ)はCPUによってデータ転送条件が設定されるときはターゲット2、設定された転送条件に従ってDMA転送を行うときはイニシエータ1となる。

【0051】

リクエストパケットREQPCKTは、例えば、リクエストREQ、グラントGNT、エンドオブパケットEOP,ロックLCK、アドレスADD、オペコードOPC、データDATA、バイトイネーブルBE、ソースSRCの各信号から成る。

【0052】

リクエストREQは、イニシエータがイニシエータポートのリクエストパケット転送に使用される信号のうち、LCK、ADD、OPC、DATA、BE、SRCなどに有効な値を出力していることを示す。本信号とGNTが共にアサート状態であるときに、リクエストパケットがイニシエータからパケットルータに向けて転送される。本信号が非アサート状態のとき、パケットルータは上記各信号を無視する。イニシエータはGNTの状態に関わらず本信号をアサートできるが、ひとたび本信号をアサートしたら、GNTがアサートされてリクエストパケットの最初のセルの転送が完了するまで、アサート状態に保持しなければならない。

【0053】

グラント信号GNTは、対応するターゲットがリクエストパケットのセルを受信可能であることを示す。REQと本信号が共にアサート状態であるときに、リクエストパケットのセルが、イニシエータからパケットルータに転送される。パケットルータはREQの状態とは無関係に本信号をアサート、ディアサートすることができる。

【0054】

エンドオブパケットEOPは、イニシエータがリクエストパケットの最終セルをイニシエータポートに出力していることを示す。ターゲットは、転送されたセルの数ではなく、本信号がアサート状態にあることを、リクエストパケット終端の検出条件としなければならない。イニシエータは、セルの転送を開始してからそのセルの転送が完了するまで、本信号を一定値に保持しなければならない。

【0055】

ロックLCKは、排他的にトランザクション(リクエストパケットの転送からレスポンスパケットを受領するまでの一連の処理)を実行するために、システムをロックすることを要求する信号である。イニシエータは、リクエストパケット送信時において、ターゲットを排他的にアクセスするときに本信号をアサート状態とし、排他的アクセス要求を解除するときは本信号を非アサート(ネゲート)状態とする。排他的トランザクション実行をサポートするパケットルータは、本信号がアサート状態であるリクエストパケットをターゲットに転送してから、同じイニシエータからの本信号が非アサート状態であるリクエストパケットを転送するまでの間は、他のイニシエータからのリクエストパケットをターゲットに転送してはならない。

【0056】

アドレス信号ADDはトランザクションのターゲットアドレスを示す。本信号によるアドレス指定の最小単位は8バイトである。

【0057】

オペコードOPCはロード、ストア等のトランザクションの種類と転送サイズを示す信号である。イニシエータは、リクエストパケットの転送を開始してからそのリクエストパケットの転送が完了するまで、REQがアサート状態にある間は、本信号を一定値に保持する。

【0058】

データDATAはイニシエータからターゲットに転送されるデータである。

【0059】

バイトイネーブルBEはターゲットが処理を行うべきバイトを指定する8ビットのデータである。バイトイネーブルとアドレスの関係は、例えばバイトアドレス0+8n、…、7+8nに対して、バイトイネーブルビットBE_0、…、BE_7が対応される。

【0060】

ソースSRCはパケットルータがレスポンスパケットを中継するときに、レスポンスパケットの送信先のイニシエータを特定できるようにするために、イニシエータが出力する識別子である。ターゲットは、リクエストパケット受信時に本信号の値を保存し、対応するレスポンスパケットを送信する際に後述するR_SRCとして出力する。そして、パケットルータは、R_SRCによってレスポンスパケットの送信先を決定する。したがって、イニシエータVCは、必ずレスポンスパケットが自らに返るように、本信号を出力しなければならない。

【0061】

レスポンスパケットRESPCKTは、例えば、レスポンスバリッドR_VLD(レスポンスリクエストR_REQ)、レスポンスグラントR_GNT、レスポンスエンドオブパケットR_EOP、レスポンスロックR_LCK、レスポンスオペコードR_OPC、レスポンスデータR_DATA、レスポンスソースR_SRCの各信号から成る。

【0062】

レスポンスリクエストR_REQは、ターゲットが出力するR_RCK、R_OPC、R_DATA、R_SRCなどの有効性を示す。ターゲットは、R_GNTの値に関わらず本信号をアサートできる。ただし、ひとたび本信号をアサートしたら、R_GNTがアサートされてレスポンスパケットの最初のセルの転送が完了するまでは、本信号をアサート状態に保持しなければならない。

【0063】

レスポンスバリッドR_VLDは、レスポンスパケットの有効性を示す信号であり、R_EOP、R_LCK、R_OPC、R_DATAなどが有効であることをイニシエータに示すための信号である。

【0064】

レスポンスエンドオブパケットR_EOPはレスポンスパケットの最終セルをイニシエータに出力していることを示す。

【0065】

レスポンスロックR_LCKは イニシエータで受信されたレスポンスパケットが排他的に送信されたものであるか否かを示す。レスポンスパケットの転送を開始してからそのレスポンスパケットの転送が完了するまで、R_VLDがアサート状態にある間は、レスポンスロックR_LCKは一定値に保持されなければならない。排他的トランザクション実行をサポートするパケットルータは、本信号がアサート状態であるレスポンスパケットを転送してから、同じターゲットからの本信号が非アサート状態であるレスポンスパケットを転送するまでの間は、他のターゲットからのレスポンスパケットをイニシエータに転送してはならない。

【0066】

レスポンスオペコードR_OPCは、ロードやストア等のトランザクションの結果を示すレスポンスオペコードである。

【0067】

レスポンスデータR_DATAはイニシエータに転送されるデータである。

【0068】

レスポンスソースR_SRCは対応するリクエストパケットの送信時にイニシエータが出力したソースSRCと同じ値の信号であり、レスポンスパケットの転送を開始してからそのレスポンスパケットの転送が完了するまで、R_VLDがアサート状態にある間は、一定値に保持される。本信号は、パケットルータがレスポンスパケットをルーティングする際に、レスポンスパケットの送信先(イニシエータ)を特定できるようにするための識別子である。ターゲットは、リクエストパケット受信時にSRCの値を保存し、対応するレスポンスパケットを送信する際にR_SRCとして出力する。パケットルータは、R_SRCによってレスポンスパケットの送信先を決定する。

【0069】

レスポンスググラントR_GNTはレスポンスパケットを受信可能であることを示す。

【0070】

《マイクロコンピュータとチップセット》

図3にはスプリットトランザクションによるパケット交換を適用したマイクロコンピュータ及びその周辺機能の拡張に用いる拡張デバイスからなるチップセットのブロック図が示される。チップセットはモジュール化されていてもいし、マザーボード上に単なるマルチチップとして実装されていてもよい。

【0071】

マイクロコンピュータ10及び拡張デバイス11はそれぞれ異なる半導体チップに形成され、デュアルチップでチップセットを構成する。

【0072】

マイクロコンピュータ10はスプリットトランザクションによるパケット交換によってデータなどの転送を行うために、階層化されたパケットルータ12、13を有し、パケットルータ12、13の間には中継回路としてキューイングバッファ(QUEBUF)14が配置される。ここでは、拡張デバイス11にもスプリットトランザクションによるパケット交換方式が採用され、パケットルータ15が設けられている。特に制限されないが、マイクロコンピュータ10と拡張デバイス11はシリアル入出力回路(SIO)30と40によって接続される。

【0073】

パケットルータ12には中央処理装置(CPU)20〜23、割り込みコントローラ(INTC)24、ROMアクセスコントローラ(ROMC)25、周辺制御部(PRPHC)26、及びルーティングコントローラレジスタ(RCREG)27が接続される。ROMC25には例えばROM50が外付けされる。

【0074】

パケットルータ13には表示制御部(DISPC)31、ハードディスク制御部(HDDC)32、ダイレクト・メモリ・アクセス・コントローラ(DMAC)33、フラッシュメモリコントローラ(FMRYC)34、シンクロナスDRAMコントローラ(DMRYC)35、周辺制御部(PRPHC)36、及びSIO30が接続される。HDDC32にはハードディスク(HDD)51が外付けされ、DISPC31にはディスプレイ(DISP)52が外付けされ、FMRYC34にはフラッシュメモリ(FMRY)51が外付けされ、DMRYC35にはシンクロナスDRAM(DMRY)54が外付けされる。

【0075】

パケットルータ15には周辺制御部(PRPHC)41〜44、及びルーティングコントローラレジスタ(RCREG)45が接続される。

【0076】

ルーティングコントロールレジスタ27はパケットルータ12,13に対する制御データが例えばCPU20によってプログラマブルに設定され、設定された制御データはパケットルータ12,13に供給される。同様に、ルーティングコントロールレジスタ45はパケットルータ15に対する制御データが例えばCPU20によってプログラマブルに設定され、設定された制御データはパケットルータ45に供給される。ルーティングコントロールレジスタ27は、後述するリクエストリソースによる排他制御の対象とするアクセスの属性を保持する排他制御レジスタとして機能される。

【0077】

キューイングバッファ14はパケットルータ12で受理されたリクエストパケットをFIFO形態一時的に保持する。キューイングバッファ14が現に最初に保持するリクエストパケットはパケットルータ13に出力され、パケットルータ13がこれを受理することによって、キューイングバッファ14は当該リクエストパケットのリードが完了されたと認識する。また、キューイングバッファ14はパケットルータ13で受理されたレスポンスパケットをFIFO形態一時的に保持する。キューイングバッファ14が現に最初に保持するレスポンスパケットはパケットルータ12に出力され、パケットルータ12がこれを受理することによって、キューイングバッファ14は当該レスポンスパケットのリードが完了されたと認識する。

【0078】

マイクロコンピュータ10においてパケットルータ12,13は2階層で階層化される。パケットリクエストを基点とするトランザクションに対してパケットルータ12が上位階層、パケットルータ13が下位階層をなす。チップセットにおいては、パケットルータ15はパケットルータ13のさらに下位階層をなす。

【0079】

ここで、図3のチップセットを構成する各回路モジュールにおいて、どれがイニシエータで、どれがターゲットから、そのバスマスタ機能とバススレーブ機能によって決まり、例えば、前述の如くDMAC33はその動作形態によってイニシエータとなったり、ターゲットになったりし、また、RCREG27はターゲットだけとして機能される。

【0080】

図3のチップセットにおいて、パケットルータ12,13,15は一つのターゲットに対して複数のイニシエータがアクセスを要求したときの調停、そして共有リソースなどに対する排他制御のために後のアクセス要求を無効化する制御などを行う。例えば、マイクロコンピュータ10のCPUは、TAS(Test And Set)命令実行時にセマフォに対してリード・モディファイ・ライトを行う。CPUはイニシエータとしてTAS命令によるセマフォのリードアクセスを行うときにパケットルータに排他処理を要求し、TAS命令の後半のライトアクセスを行うときにパケットルータに排他処理終了を通知する。リソース単位で排他処理を行なう場合に、排他処理要求が受理されたイニシエータ以外のイニシエータによる排他的アクセス対象へのアクセスをターゲット単位で抑止する、というプロトコルは従来から採用さてれている。マイクロコンピュータ10のような、マルチコアSOC(一つのチップに複数のCPUを搭載するSOC)では、シングルコアSOC(一つのチップに単一のCPUを搭載するSOC)に比して排他処理が多用されることが考えられる。ターゲット単位の排他処理では、排他処理に伴う転送性能(バスアクセス性能)の低下が大きいから、図3のチップセットにおいては、排他処理単位を縮小するために、少なくともアドレス領域単位の排他制御を行うようになっている。以下、排他処理を中心にパケットルータの具体例を説明する。

【0081】

《アドレス比較を行うリクエストリソース》

図1にはパケットルータ12、13、15のリクエストリソース(REQRSC)80について原理的構成が具体的に例示される。リクエストリソース80はリクエストリソース3Aの一例である。ここでは、説明を解り易くするために、リクエストリソース80には3個のイニシエータ60,61,62と3個のターゲット70、71、72が接続される例を示す。

【0082】

リクエストリソース80は、排他情報バッファ(EXCLBUF)81、比較回路(COMP)90,91,92、アクセス要求無効化回路(DSABL)100,101,102、及び調停回路(ARBTR)82を有する。調停回路82は調停ロジック(ARBLGC)83とセレクタ(SLCTR)84から成る。

【0083】

排他情報バッファ81は、たとえば図4に例示されるように、排他処理要求としてのロックLCKがアサートされたリクエストパケットを受理したとき当該要求元としてのイニシエータ番号INITIDに対応して、排他処理要求の有無を示す排他情報EXCL、当該リクエストパケットに含まれるアドレス情報ADD、アクセスデータサイズDSZ、及びバイトイネーブルBEを保持する。図4に示される対象イニシエータ番号TGINITと、リード又はライトのようなアクセス方向R/Wの情報とは排他制御レジスタ27が保持する。アクセスデータサイズDSZは、アドレス範囲の全てをアドレス情報で指定しない場合に、先頭アドレスとアクセスデータサイズによって指定する場合に用いるデータである。対象イニシエータ番号TGINITと、アクセス方向R/Wに応ずる情報はそもそもリクエストパケットで指定される情報ではなく、CPUが排他制御レジスタ27に指定するデータである。イニシエータID#0の対象イニシエータ番号TGINITは“#1=1/0,#2=1/0”となり、1は排他処理の対象、0は排他処理の非対象を意味する。例えばイニシエータID#0の対象イニシエータ番号TGINITは“11”すなわち“#1=1,#2=1”であり、イニシエータ#0が出力する排他処理要求に対しては、イニシエータID#1、#2の何れからのアクセス要求に対しても排他処理の対象とする。イニシエータID#1の対象イニシエータ番号TGINITは“#0=1/0,#2=1/0”となり、例えばイニシエータID#1の対象イニシエータ番号TGINITは“01”すなわち“#0=0,#2=1”であり、イニシエータ#1が出力する排他処理要求に対しては、イニシエータID#0からのアクセス要求に対しては排他処理の対象とはせず、イニシエータID#2からのアクセス要求に対しては排他処理の対象とする。

【0084】

例えば比較回路90、91、92は、前記排他情報バッファ81等に格納された情報と対応するイニシエータ60、61、62から与えられるリクエストパケットに含まれるアドレス情報とを比較して、その比較結果を出力する。例えば比較回路90は、前記排他情報バッファ81が保持しイニシエータIDが#1、#2のエントリデータと、イニシエータ60が出力するリクエストパケットに含まれていてそのエントリデータに対応するデータとを比較する。比較回路91は、前記排他情報バッファ81が保持しイニシエータIDが#0、#2のエントリデータと、イニシエータ60が出力するリクエストパケットに含まれていてそのエントリデータに対応するデータとを比較する。比較回路92は、前記排他情報バッファ81が保持しイニシエータIDが#0、#1のエントリデータと、イニシエータ60が出力するリクエストパケットに含まれていてそのエントリデータに対応するデータとを比較する。ここでは、夫々の比較回路90,91,92は、夫々の比較項目で排他条件に一致しなければハイレベル(“H”)を出力する。

【0085】

アクセス要求無効化回路(DSABL)100,101,102は、対応する比較回路90,91,92の出力が“L”のとき、対応するアクセス要求を無効化する。即ち、アクセス要求無効化回路100は、比較回路90の出力とイニシエータ69からのリクエストREQとの論理積を採り、当該リクエストREQのハイレベルによってアクセスが要求されているとき、比較回路90の出力が“H”でなければ対応するリクエストREQによるアクセス理要求を無効化する。アクセス要求無効化回路101は、比較回路91の出力とリクエストREQとの論理積を採り、当該リクエストREQのハイレベルによってアクセスが要求されているとき、比較回路91の出力が“H”でなければ対応するリクエストREQによるアクセス要求を無効化する。アクセス要求無効化回路102は、比較回路92の出力とリクエストREQとの論理積を採り、当該リクエストREQのハイレベルによってアクセスが要求されているとき、比較回路92の出力が“H”でなければ対応するリクエストREQによるアクセス要求を無効化する。要するに、アクセス要求無効化回路100,101,102は、アクセス対象アドレスに着目すれば、比較回路による比較結果に基づいて、既に受理されている排他処理要求とアクセス対象アドレスが重なる範囲を最大限として、既に受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するものである。アクセス対象アドレスが重なる範囲とは、同一のイニシエータ上でアクセスアドレスが重なることを意味する。

【0086】

調停ロジック83は、前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理する。セレクタ84は、調停ロジック83が受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う。更にセレクタ84は、排他処理要求を伴って受理されたアクセス要求のリクエストパケットの情報によって排他情報バッファ81の対応するエントリの情報を更新する。

【0087】

尚、図1ではリクエストパケットREQPCKTの中のリクエストREQとグラントGNTの所在を明示しているが、その他の信号はそれとは別の信号線に含まれる。

【0088】

上記によれば、排他的アクセスの対象となるアドレス情報などのアクセス情報を保持し、イニシエータが出力するアクセス情報と前記保持されたアクセス情報を比較し、アクセス対象アドレスが重なる範囲を最大限として他のアクセス要求を無効化するから、ターゲット単位よりも細かなアドレスを対象とするピンポイントの排他処理を実現することができる。

【0089】

そして、調停回路の処理に先立って排他処理要求を伴うアクセス要求に対する選択的な無効化の処理を行うから、排他的な制御により抑止されるべきアクセス要求が調停回路による調停処理の対象にはされず、この点において、イニシエータがアクセス要求を行ってからアクセス要求が受理されるまでの時間を短縮するのに寄与する。

【0090】

図1において、前記調停ロジック83は、前記イニシエータ毎にグラントGNTを出力し、前記イニシエータからリクエストREQによりアクセス要求を入力した場合、前記アクセス要求無効化回路100によりそのアクセス要求が有効とされ、かつ、調停によって前記イニシエータからのアクセス要求が無効とされた場合や、調停によって前記イニシエータからのアクセス要求を受理しない場合には、グラントGNTをディアサート状態とする。調停ロジック83は、アクセス要求の無効化に関わらず、イニシエータからのアクセス要求を受理したときにのみグラントGNTをアサートするから、これを受けるイニシエータは、アクセス要求の後、これが受理されたか無効化されたかを感知することなく、グラントGNTのアサートを待てばよい。したがって、スプリットトランザクションによるパケット交換方式のバスインタフェースでは、排他処理を伴うアクセス要求が一時的に抑止される場合でもイニシエータは単に待てばよく、再度アクセス要求を行うなどの処理は不要であり、ピンポイントの無効化を採用してもイニシエータの実装は容易である。

【0091】

図1において、前記イニシエータは、例えばアクセスを要求した場合、入力されるグラントGNTのディアサート状態によってアクセス要求が受理されていないと判定し、入力されるグラントGNTがアサート状態であることにより、アクセス要求が受理されたと判定する。

【0092】

図5には比較回路(COMP#0)90の一例としてアドレス比較と排他要求比較を行なう例が示される。110は、排他情報バッファ81におけるイニシエータID#1のエントリのアドレス情報ADDと、イニシエータID#0のイニシエータ60から出力されるアドレスADDとを比較するアドレス比較器であり、比較一致によって“H”を出力する。111は、排他情報バッファ81におけるイニシエータID#2のエントリのアドレス情報ADDと、イニシエータID#0のイニシエータ60から出力されるアドレスADDとを比較するアドレス比較器であり、比較一致によって“H”を出力する。アンドゲート112は排他情報バッファ81におけるイニシエータID#1のエントリの排他情報EXCLと、アドレス比較器110の比較結果を2入力として論理積を採る。アンドゲート113は排他情報バッファ81におけるイニシエータID#2のエントリの排他情報EXCLと、アドレス比較器111の比較結果を2入力として論理積を採る。エントリの排他情報EXCLは対応するイニシエータが排他処理を要求していれば“H”とされる。負論理和ゲート(ノアゲート)114はアンドゲート112、113の出力を2入力として、負論理和を採る。アクセス要求無効化回路100はイニシエータID#0が出力するリクエストREQとナンドゲート114の出力を2入力とするアンドゲートによって構成される。したがって、イニシエータ#1が排他処理を要求しており(INT1,EXCL(EXCLBUF)=“H”)且つアドレス比較器110による比較が一致であるときアンドゲート112の出力が“H”、また、イニシエータ#2が排他処理を要求しており(INT2,EXCL(EXCLBUF)=“H”)且つアドレス比較器111による比較が一致であるときアンドゲート113の出力が“H”となるから、その何れの場合においても、イニシエータ#0からのアクセス要求は無効化される。他の比較回路の場合も上記と同様である。

【0093】

このように、アドレス比較と排他要求比較を行なう比較回路を採用する場合、一つのイニシエータからアクセス要求があったとき、それによるアクセスアドレスと重なるアドレスについて既に別のイニシエータからの排他処理要求が受理されている場合に、当該一つのイニシエータからのアクセス要求を無効化する。

【0094】

図6には比較回路(COMP#0)90の一例としてアドレス比較、排他要求比較及びバイトイネーブル比較を行なう例が示される。120は図5の比較器110と同じであり、121は図5の比較器111と同じである。比較器125は排他情報バッファ81におけるイニシエータID#1のエントリのバイトイネーブルBEと、イニシエータID#0のイニシエータ60から出力されるバイトイネーブルBEとを比較するアドレス比較器であり、比較一致によって“H”を出力する。126は、排他情報バッファ81におけるイニシエータID#2のエントリのバイトイネーブルBEと、イニシエータID#0のイニシエータ60から出力されるバイトイネーブルBEとを比較するアドレス比較器であり、比較一致によって“H”を出力する。アンドゲート122は排他情報バッファ81におけるイニシエータID#1のエントリの排他情報EXCL、アドレス比較器120の比較結果、及びアドレス比較器125の比較結果を3入力として論理積を採る。アンドゲート123は排他情報バッファ81におけるイニシエータID#2のエントリの排他情報EXCL、アドレス比較器111の比較結果、及びアドレス比較器111の比較結果を3入力として論理積を採る。エントリの排他情報EXCLは対応するイニシエータが排他処理を要求していれば“H”とされる。負論理和ゲート(ノアゲート)124はアンドゲート122、123の出力を2入力として、負論理和を採る。アクセス要求無効化回路100はイニシエータID#0が出力するリクエストREQとナンドゲート124の出力を2入力とするアンドゲートによって構成される。したがって、イニシエータ#1が排他処理を要求しており(INT1,EXCL(EXCLBUF)=“H”)且つアドレス比較器120による比較及びアドレス比較器125による比較が夫々一致であるときアンドゲート122の出力が“H”、また、イニシエータ#2が排他処理を要求しており(INT2,EXCL(EXCLBUF)=“H”)且つアドレス比較器121による比較及びアドレス比較器126による比較が一致であるときアンドゲート123の出力が“H”となるから、その何れの場合においても、イニシエータ#0からのアクセス要求は無効化される。他の比較回路の場合も上記と同様である。

【0095】

このように、アドレス比較、排他要求比較及びバイトイネーブル比較を行なう比較回路を採用する場合、一つのイニシエータからアクセス要求があったとき、それによる指定アクセスアドレスと重なり、バイトイネーブルによるアクセス対象バイトが重なっている、既に別のイニシエータからの排他処理要求が受理されている場合に、当該一つのイニシエータからのアクセス要求を無効化する。

【0096】

図7には図6に対して更に対象イニシエータ番号TGINITも比較対象にした比較回路(COMP#0)90の一例が示される。図6との相違点は122,123のアンドゲートを4入力とし、INITID#1に関するアンドゲート132には排他情報バッファ81におけるINITID#1のエントリが保有する対象イニシエータ番号TGINITのINIT#0に対応する値を入力し、INITID#2に関するアンドゲート133には排他情報バッファ81におけるINITID#2のエントリが保有する対象イニシエータ番号TGINITのINIT#0に対応する値を入力する。図4の例に従えば、INITID#1のエントリにおいて、対象イニシエータ番号TGINITは“#0、#2”=“01”であるから、INIT#1,TGINIT(INIT#0)=0がアンドゲート132に、INITID#2のエントリにおいて、対象イニシエータ番号TGINITは“#0、#1”=“10”であるから、INIT#2,TGINIT(INIT#0)=0がアンドゲート133に供給される。これにより、イニシエータ60(INITID#0)からのアクセス要求は、イニシエータ61(INITID#1)による排他処理要求がすでに受理されていてもそれによって排除されず、イニシエータ62(INITID#2)による排他処理要求がすでに受理されていていればそれによって排除される。

【0097】

このように対象イニシエータ番号TGINITも比較対象にしてアドレス比較などを行えば、レジスタ27の設定内容で特定される一部のイニシエータからのアクセス要求に限って無効化することができるようになる。

【0098】

上記比較回路の具体例は図1に例示されるように3個のイニシエータ60,61,62の場合を例としており、イニシエータの数に応じてアンドゲート122,123(132,133)に係る構成を増やせばよい。

【0099】

《ターゲットを最小単位とする排他制御用のリクエストリソースの併用》

上記説明では、アクセス対象ターゲットが既に受理された排他処理の対象ターゲットと同じであるかはアドレス比較を用いた。ターゲット単位でアクセスの無効化を行う場合には、図8に例示されるように、ターゲットへの接続を変えたリクエストリソース(REQRSC)130、131を設け、リクエストリソース130,131へのリクエストパケットの振り分けを行う振り分け回路(PCKTSRT)132を用いればよい。すなわち、リクエストリソース130にはターゲットTGT70,71を接続し、リクエストリソース131には1個のターゲットTGT72を接続する。振り分け回路132はリクエストリソースに含まれるアクセスアドレスADDからアクセス対象ターゲットを判別し、ターゲット70又は71をアクセス対象とするリクエストパケットをリクエストリソース130に供給し、ターゲット72をアクセス対象とするリクエストパケットをリクエストリソース131に供給する。リクエストリソース130は接続されるターゲットが相違される点を除いて図1で説明したリクエストリソース80と同じ構成を備えるから、その詳細な説明は省略する。リクエストリソース131はターゲットを最小単位として排他処理要求に対する制御を行う点が図1のリクエストリソース80と相違される。即ち、リクエストリソース131の比較回路140は、図9に例示される。図9には比較回路(COMP#0)140の一例が示される。同図に示される比較回路140は、排他情報バッファ81におけるイニシエータID#1のエントリの排他情報EXCLと、排他情報バッファ81におけるイニシエータID#2のエントリの排他情報EXCLとが直接負論理和ゲート(ノアゲート)114に供給される。イニシエータ#1が排他処理を要求している状態(INT1,EXCL(EXCLBUF)=“H”)、又はイニシエータ#2が排他処理を要求している状態(INT2,EXCL(EXCLBUF)=“H”)の場合に、イニシエータ#0からのターゲット72へのアクセス要求は無効化される。

【0100】

リクエストリソース131には特定の一のターゲット70を対象とするリクエストパケットだけが振り分けられるから、ターゲット単位の排他制御にはアドレス比較を要せず、一のターゲット70を対象として他のイニシエータが発行した排他処理要求が既に受理されているか否か判定すれば、一のターゲット70に対してはこれを最小単位とする排他制御を行うことができる。

【0101】

《イニシエータを単位とする排他制御》

排他制御を要求したイニシエータがCPUであれば、パケットルータが、排他制御期間内に別のイニシエータによる別のアドレスへのアクセスを許可しても問題はない。一方,イニシエータの中には、他のイニシエータを排除して自己のアクセス頻度を高めることを目的として、排他的アクセスを要求するものがある。例えばDMAC等である。このようなイニシエータによる排他処理要求に対しては、アドレス等によるピンポイントの排他処理ではなく、ターゲットに対する全アクセスを対象とする排他処理が有効である。このため、排他処理を要求するイニシエータを単位として、全アクセスで排他制御を行う回路と、ピンポイントで排他制御を行う回路を混在させるのがよい。

【0102】

具体的には,イニシエータがCPUであれば図1で説明したように、アドレスを限定した排他処理を行い、イニシエータがCPU以外であれば、アドレスを限定しない排他処理を行う。パケットルータに直接イニシエータが接続されている場合、イニシエータがCPUであるかCPU以外であるかはSOCや半導体装置の開発段階で決まるため、イニシエータのタイプがCPUかCPU以外かを識別する回路を特別に設けることは不要である。パケットルータに、イニシエータが接続されている場合、リクエストパケットに含まれる属性の一つであるイニシエータ識別情報(シースSRC)に基づいてイニシエータタイプの判定を行えばよい。

【0103】

《排他情報バッファのエントリ数》

排他情報バッファのオーバーフローにより、排他処理が正常に行われないことがあってはならない。このため,排他情報バッファ81のエントリ数は、イニシエータが同時に実行できる排他的アクセスの合計値以上とする。例えば図4の例では一つのイニシエータIDが格納するアクセス情報は一つである。階層インターコネクトのように、パケットルータにパケットルータが接続されている場合、排他情報バッファのエントリ数はパケットルータに接続された全てのイニシエータが同時に実行できる排他的アクセスの合計数となる。

【0104】

一つのCPUが同時に実行できる排他的アクセス数が複数ある場合に、その識別をプロセスIDを用いて行ってもよい。この場合には、前記排他情報バッファが保持するアクセス情報には、アクセス対象アドレス情報と共に、そのアクセス対象アドレス情報を用いるプロセスのプロセスID情報を含める。この場合、前記アクセス要求無効化回路は、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とはプロセスIDが異なるアクセス要求を無効化する。同じイニシエータによる排他的アクセス要求に対してプロセスIDを考慮してアクセス要求の無効化に対処することができる。

【0105】

《排他処理に競合するアクセスに関するデバッグ支援》

セマフォを実現するために排他処理を使う場合、通常はCPUが排他的アクセスを要求中のアドレスに対して以下の事象が発生することはなく、発生した場合、その原因はソフトウエアやハードウエアの不具合である可能性が高い。その事象とは、排他処理を要求しているイニシエータ(CPU)以外のCPUからのライトアクセス、CPU以外のイニシエータからの任意のアクセス、があることである。図3に例示されるように、パケットルータ12,13は、上記事象を検出したときに、割込みコントローラ24に割込み要求信号IRQ1,IRQ2を出力し、CPU23に割り込み信号をINT出力する。これにより、ソフトウエアやハードウエアの不具合の早期発見に資することができる。

【0106】

《階層化ルータの排他処理》

図10には複数のパケットルータを階層的に組み合わせてオンチップインターコネクトを構築した例が示される。パケットルータ150,151の間には中継回路として例えばキューイングバッファ(QUEBUF)152は配置される。パケットルータ150にはイニシエータ160,161が接続され、パケットルータ151にはイニシエータ162,163が接続される。代表的に示されたターゲット164はパケットルータ151に接続される。このように、複数のパケットルータ150,151がキューイングバッファ152を介して複数階層に直列接続されているとき、夫々のパケットルータ150,151のリクエストリソースは、イニシエータから所要のターゲットに対するアクセス要求に伴う排他処理要求を受理する排他処理機能を備える。例えばリクエストリソースは図1で説明したように構成される。この場合、パケットルータ150のセレクタ84の出力は例えばワイヤード・オアでキューイングバッファ152の上流側ポートに接続される。キューイングバッファ152の下流側ポートは、一つのイニシエータとしてパケットルータ151のリクエストリソースに接続されればよい。

【0107】

階層的インターコネクトを構成する複数のパケットルータ150,151のうち、アクセス要求の上流(イニシエータに近い側)のパケットルータ150に排他処理機構を持たない場合、上流側パケットルータ150に接続された一のイニシエータ160からの排他処理要求を伴うアクセスに続いて同じ階層のパケットルータ150に接続された別のイニシエータ161が前記アクセス要求と同じアドレスに対してアクセス要求を送信したときに、ハングアップが発生する。これは、パケットルータ間の中継回路(キューイングバッファ)152が前記一のイニシエータ160のリクエストパケットをパケットルータに送信したときに下位階層のパケットルータ151が排他処理によって前記別のイニシエータ161のアクセス要求を抑止するために、当該一のイニシエータ160が排他処理停止要求を通知するアクセス要求が中継回路152を通れずに下流のパケットルータ151に送信できないからである。

【0108】

また、アクセス要求の下流のパケットルータ151に排他処理機能を持たない場合は、排他処理機能を有する上流のパケットルータ150に接続するイニシエータ160,161からの排他処理要求を下流のパケットルータ151が受理しないため、排他性を保証することができない。

【0109】

図11と図12には複数のパケットルータを階層的に組み合わせてオンチップインターコネクトを構築したとき、排他処理を要求するイニシエータを同一階層のパケットルータに集約して接続した例が示される。図11及び図12においてパケットルータ150、151及びキューイングバッファ152は図10と同じであり、パケットルータ150、151は共に排他制御機能を備える。図11及び図12ではイニシエータ170,171は排他処理を要求するイニシエータとされ、イニシエータ172,173は排他処理を要求しないイニシエータとされる。このように、排他処理要求を伴うアクセスを要求するイニシエータは、同一階層のパケットルータに集約して結合される。

【0110】

図13に例示されるように、排他処理要求を行なうイニシエータ170,171を、排他処理要求を行なわないイニシエータ172,173に混在させて上流及び下流のパケットルータ150,151に分散配置した場合、上流及び下流のイニシエータ170,171がそれと同一アドレスについて排他的なアクセスを要求したときには、上流側で排他処理を要求しないイニシエータ172からのアクセス要求は、それが前記排他的なアクセス要求によって抑止されるべきものか否かにかかわらず、抑止される。これは、中継回路152において、先に上流側のイニシエータ170から下流側のパケットルータ151に転送されるべき排他処理要求のアクセス要求が、下流側のイニシエータ171の排他的アクセス終了まで、下流側への伝達が抑止されるためである。

【0111】

以上説明した実施の形態によれば以下の作用効果がある。

【0112】

(1)排他処理対象アドレスを対象とした、ピンポイントの排他処理ができる。このため,排他処理に伴う転送性能を向上させることができる。本発明では排他情報保持バッファに排他処理対象アドレスを保持し,アクセス要求が排他処理対象アドレスに該当するか否かを判定し,該当するアクセス要求だけを排除するからである。

【0113】

(2)排他処理対象アドレスに限定した排他処理と、(スループット向上を目的とした)排他処理対象アドレスを限定しない排他処理を、一つのSOC若しくはチップに混在できる。本発明ではアクセス要求先のアドレスを振り分け回路で判定してリクエストパケットを所定のリクエストリソースに簡単に振り分けることができるからである。

【0114】

(3)単一のイニシエータによる複数の排他的アクセスを同時に処理できる。排他情報保持バッファに、プロセス識別情報(プロセスID)を記憶させ、アクセス要求が排他処理対象プロセスIDに該当するか否かを判定し、該当するアクセス要求だけを排除するからである。

【0115】

(4)排他処理に伴って抑止されるアクセス要求を調停前に排除するので、排他処理に伴って抑止されるアクセス要求が調停処理によって受理されることがない。結果として有効な(排他処理に伴って排除されない)アクセスが早く受理され、高いデータ転送性能を得る。イニシエータと調停回路の間にイニシエータ毎に比較回路を配置するから、調停前に排他処理によって抑止すべきアクセス要求を抑止し、調停回路が排他処理によって抑止されないアクセス要求だけを調停対象とするからである。

【0116】

(5)階層インターコネクトにおいて、排他処理によるハングアップを回避できる。複数のパケットルータを用いて階層的に構成されたインターコネクトにおいて、上流(イニシエータに近い側)のパケットルータが、排他処理によって抑止されるべきアクセス要求を抑止するためである。この抑止動作により、下流(ターゲットに近い側)のパケットルータによる排他処理によって抑止されるリクエストパケットが中継回路に滞留しないようにするためである。下流のパケットルータによる排他処理によって抑止されるアクセス要求が中継回路に滞留すると、下流のパケットルータに排他的アクセスの終了を通知するアクセス要求を転送できなくなり、これによってハングアップ状態に陥る。

【0117】

(6)階層インターコネクトにおいて、排他処理に伴って、排他処理によって排除されないアクセスが排他処理完了まで抑止され続けることがない。排他制御を要求するイニシエータを異なるパケットルータに接続しないため、排他制御によって抑止されるべきアクセス要求が、排他制御によって抑止されないアクセス要求の処理を阻害しないからである。

【0118】

(7)排他的処理の対象となっているアドレスに対する不正なアクセスを検出することにより、ソフトウエアやハードウエアの不具合の早期発見を容易にする。CPUによる排他処理の対象となるアドレスに対して、前記CPU以外のCPUがライトアクセスを実行したり、前記CPU以外の非CPUであるイニシエータがアクセスしたりすることは、通常意図的に発生しない事象であり、不具合である可能性が高い。排他処理の対象となるアドレスに対する前記CPU以外のCPUによるライトアクセスと、前記CPU以外の非CPUであるイニシエータによるアクセスを検出し、これによって割り込み信号をアサートできるからである。

【0119】

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【図面の簡単な説明】

【0120】

【図1】図1はパケットルータのリクエストリソースについて原理的構成を具体的に例示するブロック図である。

【図2】図2はスプリットトランザクションによるパケット交換方式のシステムの概念を例示するブロック図である。

【図3】図3はスプリットトランザクションによるパケット交換を適用したマイクロコンピュータ及び拡張デバイスからなるチップセットのブロック図である。

【図4】図4は排他情報バッファが保有する排他情報と排他制御レジスタが保有する制御情報を例示する説明図である。

【図5】図5は比較回路90の一例としてアドレス比較と排他要求比較を行なう構成を例示する論理回路図である。

【図6】図6は比較回路90の一例としてアドレス比較、排他要求比較及びバイトイネーブル比較を行なう構成を例示する論理回路図である。

【図7】図7は図6に対して更に対象イニシエータ番号TGINITも比較対象にした比較回路90の一例を例示する論理回路図である。

【図8】図8はターゲット単位でアクセスの無効化を行うために振り分け回路を採用したリクエストリソースを例示するブロック図である。

【図9】図9はターゲットを最小単位として排他処理要求に対する制御を行うための比較回路を例示する論理回路図である。

【図10】図10は複数のパケットルータを階層的に組み合わせてオンチップインターコネクトを構築するときのパケットルータの排他処理機能に着目した説明図である。

【図11】図11は複数のパケットルータを階層的に組み合わせてオンチップインターコネクトを構築するときの排他処理を要求するイニシエータの集約配置に着目した説明図である。

【図12】図12は複数のパケットルータを階層的に組み合わせてオンチップインターコネクトを構築するときの排他処理を要求するイニシエータの別の集約配置に着目した説明図である。

【図13】図13は排他処理を要求するイニシエータを分散配置したときの問題点に着目した説明図である。

【符号の説明】

【0121】

1 イニシエータ(INIT)

2 ターゲット(TGET)

3 パケットルータ(PCKTRT)

3A リクエストリソース(REQRSC)

3B レスポンスリソース(RESRSC)

REQPCKT リクエストパケット

REQ リクエスト

GNT グラント

ADD アドレス

BE バイトイネーブル

LCK ロック

RESPCKT レスポンスパケット

10 マイクロコンピュータ

11 拡張デバイス

12,13パケットルータ

14 キューイングバッファ(QUEBUF)

15 パケットルータ

20〜23 中央処理装置(CPU)

24 割り込みコントローラ(INTC)

25 ROMアクセスコントローラ(ROMC)

26 周辺制御部(PRPHC)

27 ルーティングコントローラレジスタ(RCREG)

31 表示制御部(DISPC)

32 ハードディスク制御部(HDDC)

33 ダイレクト・メモリ・アクセス・コントローラ(DMAC)

34 フラッシュメモリコントローラ(FMRYC)

35 シンクロナスDRAMコントローラ(DMRYC)

36 周辺制御部(PRPHC)

80 リクエストリソース(REQRSC)

60,61,62 イニシエータ

70、71、72 ターゲット

81 排他情報バッファ(EXCLBUF)

90,91,92 比較回路(COMP)

100,101,102 アクセス要求無効化回路(DSABL)

82 調停回路(ARBTR)

83 調停ロジック(ARBLGC)

84 セレクタ(SLCTR)

130、131 リクエストリソース(REQRSC)

150,151 パケットルータ

152 キューイングバッファ(QUEBUF)

160,161、162,163 イニシエータ

170,171,172,173 イニシエータ

【特許請求の範囲】

【請求項1】

アクセスを要求することが可能な複数のイニシエータと、アクセスに応答することが可能な複数のターゲットと、アクセスを要求するイニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行うリクエストリソース及びアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースを備えたパケットルータとを有し、

前記リクエストリソースは、排他処理要求を含むリクエストパケットを受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する排他情報バッファと、

前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する比較回路と、

前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するアクセス要求無効化回路と、

前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う調停回路と、を有する半導体装置。

【請求項2】

前記調停回路は、前記イニシエータ毎にグラント信号を出力し、前記イニシエータからアクセス要求を入力した場合、アクセス要求元のイニシエータに対応するグラント信号を一旦アサートした後は、前記アクセス要求無効化回路によりそのアクセス要求が有効とされた場合も無効とされた場合も、前記グラント信号のアサート状態を、当該アクセス要求に伴うリクエストパケットを応答先のターゲットに転送開始するまで維持する、請求項1記載の半導体装置。

【請求項3】

前記イニシエータは、アクセスを要求した場合、入力されるグラント信号のディアサート状態によってアクセス要求が受理されていないと判定し、入力されるグラント信号がアサート状態であることにより、アクセス要求が受理されたと判定する、請求項1記載の半導体装置。

【請求項4】

前記排他情報バッファが保持するアクセス情報はアクセス対象アドレス情報であり、

前記アクセス要求無効化回路は、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるイニシエータからのアクセス要求を無効化する、請求項1記載の半導体装置。

【請求項5】

前記排他情報バッファが保持するアクセス情報は、アクセス対象アドレス情報とそのアクセス対象アドレス情報を用いるプロセスのプロセスID情報であり、

前記アクセス要求無効化回路は、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とはプロセスIDが異なるアクセス要求を無効化する、請求項1記載の半導体装置。

【請求項6】

前記排他情報バッファは、前記調停回路が並列的に受理可能な排他処理要求を伴うアクセス要求毎のアクセス情報を格納可能な記憶容量を有する、請求項5記載の半導体装置。

【請求項7】

前記排他情報バッファが保持するアクセス情報は、複数バイトのアクセス対象の先頭を示すアクセス対象アドレス情報と、複数バイトのアクセス対象範囲内の有効性をバイト単位で示すバイトイネーブル情報であり、

前記アクセス要求無効化回路は、アクセス対象アドレス情報のアドレスを先頭とする複数バイトのアクセス対象範囲内においてバイトイネーブル情報で有効性とされるアドレスと重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化する、請求項1記載の半導体装置。

【請求項8】

前記排他情報バッファが保持するアクセス情報は、複数バイトのアクセス対象の先頭を示すアクセス対象アドレス情報と、複数バイトのアクセス対象範囲内の有効性をバイト単位で示すバイトイネーブル情報と、アクセス対象のアドレス情報を用いるプロセスのプロセスID情報であり、

前記アクセス要求無効化回路は、アクセス対象アドレス情報のアドレスを先頭とする複数バイトのアクセス対象範囲内においてバイトイネーブル情報で有効性とされるアドレスと重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とはプロセスIDが異なるアクセス要求を無効化する、請求項1記載の半導体装置。

【請求項9】

前記排他情報バッファは、前記調停回路が並列的に受理可能な排他処理要求を伴うアクセス要求毎のアクセス情報を格納可能な記憶容量を有する、請求項8記載の半導体装置。

【請求項10】

排他制御の対象とするアクセスの属性を保持する排他制御レジスタを更に有し、

前記アクセス要求無効化回路は、前記比較回路による比較結果と前記排他制御レジスタに保持されたアクセスの属性情報と基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化する、請求項1記載の半導体装置。

【請求項11】

前記排他制御レジスタには、アクセス属性として、アクセス方向が設定され、

前記アクセス要求無効化回路は、前記比較回路による比較結果と前記排他制御レジスタに保持されたアクセスの属性情報と基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異り且つ前記排他制御レジスタに設定されたアクセス方向へのアクセス要求を無効化する、請求項10記載の半導体装置。

【請求項12】

前記排他制御レジスタには、アクセス属性として、イニシエータの識別情報が設定され、

前記アクセス要求無効化回路は、前記比較回路による比較結果と前記排他制御レジスタに保持されたアクセスの属性情報と基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異り且つ前記排他制御レジスタに設定されたイニシエータからのアクセス要求を無効化する、請求項10記載の半導体装置。

【請求項13】

前記イニシエータとして機能し得る複数のCPUと、前記ターゲットとして機能し得るメモリ及び割り込みコントローラを備え、

前記メモリは前記複数のCPUの共有メモリであり、

前記パケットルータは、一のCPUから前記共有メモリに対する排他的な処理の要求を伴うリクエストパケットを受理した場合、そのアクセス対象アドレスと重なる範囲で、受理されている排他処理要求を伴うアクセス要求とは異なるライトアクセス要求があったことを、前記割り込みコントローラに通知する、請求項1記載の半導体装置。

【請求項14】

前記ターゲットとして機能し得るメモリ及び割り込みコントローラを備え、

前記メモリは複数のイニシエータの共有メモリであり、

前記パケットルータは、一のイニシエータから前記共有メモリに対する排他処理要求を伴うリクエストパケットを受理した場合、そのアクセス対象アドレスと重なる範囲で、受理されている排他処理要求を伴うアクセス要求とは異なるライトアクセス要求があったことを、前記割り込みコントローラに通知する、請求項1記載の半導体装置。

【請求項15】

アクセスを要求することが可能な複数のイニシエータと、アクセスに応答することが可能な複数のターゲットと、アクセスを要求するイニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行う第1のリクエストリソース及び第2のリクエストリソース並びにアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースを備えたパケットルータとを有し、

前記第1のリクエストリソースは特定の一のターゲットを対象とするリクエストパケットに対する制御を行い、

前記第2のリクエストリソースは他の複数のターゲットを対象とするリクエストパケットに対する制御を行い、

前記第1及びs第2のリクエストリソースは、排他処理要求を含むリクエストパケットを受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する排他情報バッファと、

前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する比較回路と、

前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するアクセス要求無効化回路と、

前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う調停回路と、を有する半導体装置。

【請求項16】

アクセスを要求することが可能な複数のイニシエータと、

アクセスに応答することが可能な複数のターゲットと、

前記イニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行うリクエストリソース及びアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースを備えた複数のパケットルータと、を備え、

前記複数のパケットルータが中継回路を介して複数階層に直列接続されているとき、前記夫々のパケットルータのリクエストリソースは、イニシエータから所要のターゲットに対するアクセス要求に伴う排他処理要求を受理する排他処理機能を備える、半導体装置。

【請求項17】

前記排他処理機能を備えるリクエストリソースは、

排他処理要求を含むリクエストパケットを受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する排他情報バッファと、

前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する比較回路と、

前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するアクセス要求無効化回路と、

前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う調停回路と、を有する請求項16記載の半導体装置。

【請求項18】

アクセスを要求することが可能な複数のイニシエータと、

アクセスに応答することが可能な複数のターゲットと、

前記イニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行うリクエストリソース及びアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースと備えた複数のパケットルータと、を備え、

前記複数のパケットルータが中継回路を介して複数階層に直列接続されているとき、前記夫々のパケットルータのリクエストリソースは、イニシエータから所要のターゲットに対する排他的な処理要求を受理する排他処理機能を備え、

排他処理要求を伴うアクセスを要求するイニシエータは、同一階層のパケットルータに集約して結合される、半導体装置。

【請求項19】

前記排他処理機能を備えるリクエストリソースは、

排他処理要求を含むリクエストパケットを受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する排他情報バッファと、

前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する比較回路と、

前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するアクセス要求無効化回路と、

前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う調停回路と、を有する請求項18記載の半導体装置。

【請求項1】

アクセスを要求することが可能な複数のイニシエータと、アクセスに応答することが可能な複数のターゲットと、アクセスを要求するイニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行うリクエストリソース及びアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースを備えたパケットルータとを有し、

前記リクエストリソースは、排他処理要求を含むリクエストパケットを受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する排他情報バッファと、

前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する比較回路と、

前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するアクセス要求無効化回路と、

前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う調停回路と、を有する半導体装置。

【請求項2】

前記調停回路は、前記イニシエータ毎にグラント信号を出力し、前記イニシエータからアクセス要求を入力した場合、アクセス要求元のイニシエータに対応するグラント信号を一旦アサートした後は、前記アクセス要求無効化回路によりそのアクセス要求が有効とされた場合も無効とされた場合も、前記グラント信号のアサート状態を、当該アクセス要求に伴うリクエストパケットを応答先のターゲットに転送開始するまで維持する、請求項1記載の半導体装置。

【請求項3】

前記イニシエータは、アクセスを要求した場合、入力されるグラント信号のディアサート状態によってアクセス要求が受理されていないと判定し、入力されるグラント信号がアサート状態であることにより、アクセス要求が受理されたと判定する、請求項1記載の半導体装置。

【請求項4】

前記排他情報バッファが保持するアクセス情報はアクセス対象アドレス情報であり、

前記アクセス要求無効化回路は、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるイニシエータからのアクセス要求を無効化する、請求項1記載の半導体装置。

【請求項5】

前記排他情報バッファが保持するアクセス情報は、アクセス対象アドレス情報とそのアクセス対象アドレス情報を用いるプロセスのプロセスID情報であり、

前記アクセス要求無効化回路は、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とはプロセスIDが異なるアクセス要求を無効化する、請求項1記載の半導体装置。

【請求項6】

前記排他情報バッファは、前記調停回路が並列的に受理可能な排他処理要求を伴うアクセス要求毎のアクセス情報を格納可能な記憶容量を有する、請求項5記載の半導体装置。

【請求項7】

前記排他情報バッファが保持するアクセス情報は、複数バイトのアクセス対象の先頭を示すアクセス対象アドレス情報と、複数バイトのアクセス対象範囲内の有効性をバイト単位で示すバイトイネーブル情報であり、

前記アクセス要求無効化回路は、アクセス対象アドレス情報のアドレスを先頭とする複数バイトのアクセス対象範囲内においてバイトイネーブル情報で有効性とされるアドレスと重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化する、請求項1記載の半導体装置。

【請求項8】

前記排他情報バッファが保持するアクセス情報は、複数バイトのアクセス対象の先頭を示すアクセス対象アドレス情報と、複数バイトのアクセス対象範囲内の有効性をバイト単位で示すバイトイネーブル情報と、アクセス対象のアドレス情報を用いるプロセスのプロセスID情報であり、

前記アクセス要求無効化回路は、アクセス対象アドレス情報のアドレスを先頭とする複数バイトのアクセス対象範囲内においてバイトイネーブル情報で有効性とされるアドレスと重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とはプロセスIDが異なるアクセス要求を無効化する、請求項1記載の半導体装置。

【請求項9】

前記排他情報バッファは、前記調停回路が並列的に受理可能な排他処理要求を伴うアクセス要求毎のアクセス情報を格納可能な記憶容量を有する、請求項8記載の半導体装置。

【請求項10】

排他制御の対象とするアクセスの属性を保持する排他制御レジスタを更に有し、

前記アクセス要求無効化回路は、前記比較回路による比較結果と前記排他制御レジスタに保持されたアクセスの属性情報と基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化する、請求項1記載の半導体装置。

【請求項11】

前記排他制御レジスタには、アクセス属性として、アクセス方向が設定され、

前記アクセス要求無効化回路は、前記比較回路による比較結果と前記排他制御レジスタに保持されたアクセスの属性情報と基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異り且つ前記排他制御レジスタに設定されたアクセス方向へのアクセス要求を無効化する、請求項10記載の半導体装置。

【請求項12】

前記排他制御レジスタには、アクセス属性として、イニシエータの識別情報が設定され、

前記アクセス要求無効化回路は、前記比較回路による比較結果と前記排他制御レジスタに保持されたアクセスの属性情報と基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異り且つ前記排他制御レジスタに設定されたイニシエータからのアクセス要求を無効化する、請求項10記載の半導体装置。

【請求項13】

前記イニシエータとして機能し得る複数のCPUと、前記ターゲットとして機能し得るメモリ及び割り込みコントローラを備え、

前記メモリは前記複数のCPUの共有メモリであり、

前記パケットルータは、一のCPUから前記共有メモリに対する排他的な処理の要求を伴うリクエストパケットを受理した場合、そのアクセス対象アドレスと重なる範囲で、受理されている排他処理要求を伴うアクセス要求とは異なるライトアクセス要求があったことを、前記割り込みコントローラに通知する、請求項1記載の半導体装置。

【請求項14】

前記ターゲットとして機能し得るメモリ及び割り込みコントローラを備え、

前記メモリは複数のイニシエータの共有メモリであり、

前記パケットルータは、一のイニシエータから前記共有メモリに対する排他処理要求を伴うリクエストパケットを受理した場合、そのアクセス対象アドレスと重なる範囲で、受理されている排他処理要求を伴うアクセス要求とは異なるライトアクセス要求があったことを、前記割り込みコントローラに通知する、請求項1記載の半導体装置。

【請求項15】

アクセスを要求することが可能な複数のイニシエータと、アクセスに応答することが可能な複数のターゲットと、アクセスを要求するイニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行う第1のリクエストリソース及び第2のリクエストリソース並びにアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースを備えたパケットルータとを有し、

前記第1のリクエストリソースは特定の一のターゲットを対象とするリクエストパケットに対する制御を行い、

前記第2のリクエストリソースは他の複数のターゲットを対象とするリクエストパケットに対する制御を行い、

前記第1及びs第2のリクエストリソースは、排他処理要求を含むリクエストパケットを受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する排他情報バッファと、

前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する比較回路と、

前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するアクセス要求無効化回路と、

前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う調停回路と、を有する半導体装置。

【請求項16】

アクセスを要求することが可能な複数のイニシエータと、

アクセスに応答することが可能な複数のターゲットと、

前記イニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行うリクエストリソース及びアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースを備えた複数のパケットルータと、を備え、

前記複数のパケットルータが中継回路を介して複数階層に直列接続されているとき、前記夫々のパケットルータのリクエストリソースは、イニシエータから所要のターゲットに対するアクセス要求に伴う排他処理要求を受理する排他処理機能を備える、半導体装置。

【請求項17】

前記排他処理機能を備えるリクエストリソースは、

排他処理要求を含むリクエストパケットを受理したとき当該要求元から排他処理要求があったことを示す排他情報と当該リクエストパケットに含まれるアクセス情報を保持する排他情報バッファと、

前記排他情報バッファに格納された情報とイニシエータから与えられるリクエストパケットに含まれるアクセス情報とを比較して、その比較結果を出力する比較回路と、

前記比較回路による比較結果に基づいて、アクセス対象アドレスが重なる範囲を最大限として、受理されている排他処理要求を伴うアクセス要求とは異なるアクセス要求を無効化するアクセス要求無効化回路と、

前記アクセス要求無効化回路により有効とされたアクセス要求を入力し、競合するアクセス要求に対して調停を行って、一つのアクセス要求を受理し、受理したアクセス要求に対応されるリクエストパケットをターゲットに与えるための制御を行う調停回路と、を有する請求項16記載の半導体装置。

【請求項18】

アクセスを要求することが可能な複数のイニシエータと、

アクセスに応答することが可能な複数のターゲットと、

前記イニシエータから与えられるリクエストパケットをアクセス要求に応答するターゲットに与える制御を行うリクエストリソース及びアクセス要求に応答するターゲットから与えられるレスポンスパケットをアクセス要求元のイニシエータに返す制御を行うレスポンスリソースと備えた複数のパケットルータと、を備え、

前記複数のパケットルータが中継回路を介して複数階層に直列接続されているとき、前記夫々のパケットルータのリクエストリソースは、イニシエータから所要のターゲットに対する排他的な処理要求を受理する排他処理機能を備え、

排他処理要求を伴うアクセスを要求するイニシエータは、同一階層のパケットルータに集約して結合される、半導体装置。