半導体装置

【課題】デザインルールに従いつつ、セル面積に対するキャパシタ面積の割合の増大を図ることができる、半導体装置を提供する。

【解決手段】アクティブ領域3は、列方向に延びる直線領域3Aおよび直線領域3Aの列方向の中央において直線領域3Aと直交する直交領域3Bを有する平面視T字状をなしている。直線領域3Aの両端部に形成されたドレイン領域6と強誘電体キャパシタ12の下部電極13とは、容量コンタクトプラグ18を介して接続されている。。直交領域3Bの端部に形成されたソース領域7とビットラインBL1,BL2,・・・とは、ビットコンタクトプラグ27を介して接続されている。ビットコンタクトプラグ27は、列方向に隣り合う2つのアクティブ領域3に形成されている4つのドレイン領域6に接続された容量コンタクトプラグ18を頂点とする四角形の中心に配置されている。

【解決手段】アクティブ領域3は、列方向に延びる直線領域3Aおよび直線領域3Aの列方向の中央において直線領域3Aと直交する直交領域3Bを有する平面視T字状をなしている。直線領域3Aの両端部に形成されたドレイン領域6と強誘電体キャパシタ12の下部電極13とは、容量コンタクトプラグ18を介して接続されている。。直交領域3Bの端部に形成されたソース領域7とビットラインBL1,BL2,・・・とは、ビットコンタクトプラグ27を介して接続されている。ビットコンタクトプラグ27は、列方向に隣り合う2つのアクティブ領域3に形成されている4つのドレイン領域6に接続された容量コンタクトプラグ18を頂点とする四角形の中心に配置されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、キャパシタを備える半導体装置に関する。

【背景技術】

【0002】

不揮発性メモリの一種として、強誘電体のヒステリシス(履歴現象)を利用してデータを保持するFeRAM(Ferroelectric Random Access Memory:強誘電体メモリ)が知られている。

【0003】

FeRAMには、セル構造の相違から大きき分類して2種類がある。1つは、メモリセル選択用の電界効果トランジスタと強誘電体キャパシタとを備える1T1C型セル構造を有するものであり、他の1つは、ゲート絶縁膜が強誘電体からなる電界効果トランジスタを備える1T型セル構造を有するものである。

【0004】

図4は、従来の1T1C型セル構造を有するFeRAMの図解的な平面図である。

【0005】

FeRAMは、P型のシリコン基板(図示せず)を備えている。シリコン基板の表面には、素子分離部(たとえば、LOCOS酸化膜)が選択的に形成されており、この素子分離部から複数の平面視長方形状のアクティブ領域101が露出している。アクティブ領域101は、その長手方向および長手方向と直交する方向に整列するマトリクス状に配置されている。

【0006】

アクティブ領域101には、2つのメモリセルが形成されている。各メモリセルは、1T1C型セル構造を有している。

【0007】

アクティブ領域101の長手方向の両端部および中央部には、シリコン基板の表層部に、N型の不純物領域が互いに間隔を空けて形成されている。アクティブ領域101の一端部の不純物領域は、一方のメモリセルに備えられる電界効果トランジスタのドレイン領域をなす。アクティブ領域101の他端部の不純物領域は、他方のメモリセルに備えられる電界効果トランジスタのドレイン領域をなす。アクティブ領域101の中央部の不純物領域は、2つのメモリセルに備えられる電界効果トランジスタに共通のソース領域をなす。

【0008】

シリコン基板上には、ソース領域と各ドレイン領域との間の各チャネル領域に対向する位置に、ゲート電極102が設けられている。アクティブ領域101の長手方向と直交する方向に配列される電界効果トランジスタのゲート電極102は、一体化され、1本のワードラインWLを構成している。

【0009】

シリコン基板上には、層間絶縁膜が積層されている。層間絶縁膜上には、各メモリセルのドレイン領域と対向する位置(アクティブ領域101の長手方向の一端部および他端部の上方)に、強誘電体キャパシタ103が設けられている。強誘電体キャパシタ103は、下部電極104と上部電極105との間に強誘電体膜を介在させた積層構造を有している。

【0010】

下部電極104は、平面視略正方形状をなしている。下部電極104の中央部とドレイン領域との間には、第1コンタクトプラグ106が層間絶縁膜を貫通して設けられている。下部電極104は、第1コンタクトプラグ106を介して、ドレイン領域と電気的に接続されている。

【0011】

上部電極105は、下部電極104よりも小さな平面視略正方形状をなしている。上部電極105の中央部の上方において、プレートラインPLがアクティブ領域101の長手方向と直交する方向に延びている。プレートラインPLは、上部電極105と電気的に接続されている。

【0012】

また、アクティブ領域101の上方において、ビットラインBLがアクティブ領域101の長手方向に延びている。ビットラインBLは、第2コンタクトプラグ107を介して、アクティブ領域101の中央部のソース領域と電気的に接続されている。

【0013】

ワードラインWLへの電圧の印加により電界効果トランジスタがオンされた状態で、プレートラインPLとビットラインBLとの間に電圧が印加されると、強誘電体キャパシタ103の強誘電体膜に自発分極が生じる。これにより、データの書き込みが達成され、その分極状態が維持されることにより、データが保持される。データの読み出し時には、ワードラインWLへの電圧の印加により電界効果トランジスタがオンされた状態で、プレートラインPLとビットラインBLとの間にパルス電圧が印加される。このパルス電圧の印加により強誘電体膜の分極方向が変わると、プレートラインPLとビットラインBLとの間に電流が流れるので、その電流の有無により、論理信号「1」または「0」を得ることができる。

【特許文献1】特開2004−95915号公報

【発明の開示】

【発明が解決しようとする課題】

【0014】

FeRAMには、デザインルールがある。このデザインルールでは、ゲート電極102と第1コンタクトプラグ106との間の最小距離、下部電極104の周端縁と第1コンタクトプラグ106との間の最小距離、第1コンタクトプラグ106と第2コンタクトプラグ107との間の最小距離などが定められている。デザインルールに従いつつ、メモリセルの面積(セル面積)に対する強誘電体キャパシタの面積(キャパシタ面積)の割合を増やすには、FeRAMの各部のレイアウトに工夫が必要である。セル面積に対するキャパシタ面積の割合が大きいほど、FeRAMの動作マージン(動作安定性)が向上する。

【0015】

そこで、本発明の目的は、デザインルールに従いつつ、セル面積に対するキャパシタ面積の割合の増大を図ることができる、半導体装置を提供することである。

【課題を解決するための手段】

【0016】

前記の目的を達成するための請求項1記載の発明は、第1導電型の半導体層と、前記半導体層の表面に選択的に形成され、複数のアクティブ領域を互いに分離する素子分離部と、各アクティブ領域において、前記半導体層の表層部に形成された第2導電型の第1不純物領域と、各アクティブ領域において、前記半導体層の表層部に前記第1不純物領域と間隔を空けて形成された第2導電型の第2不純物領域と、前記半導体層上に形成され、前記第1不純物領域と前記第2不純物領域との間の領域に対向するゲート電極と、前記第1不純物領域の上方に形成された下部電極と、前記下部電極上に形成された上部電極と、上端が前記下部電極に接続され、下端が前記第1不純物領域に接続された容量コンタクトプラグと、前記第2不純物領域の上方に形成されたビットラインと、下端が前記第2不純物領域に接続され、前記ビットラインと電気的に接続されたビットコンタクトプラグとを含み、前記アクティブ領域は、所定方向に延びる直線領域および前記直線領域の前記所定方向の中央において前記直線領域と直交する直交領域を有する平面視T字状をなし、前記所定方向と直交する方向に複数並べて形成され、前記第1不純物領域は、各アクティブ領域の前記直線領域の両端部にそれぞれ形成され、前記第2不純物領域は、各アクティブ領域の前記直交領域の端部に形成され、前記ビットコンタクトプラグは、前記所定方向と直交する方向に隣り合う2つのアクティブ領域に形成されている4つの前記第1不純物領域に接続された前記容量コンタクトプラグを頂点とする四角形の中心に配置されている、半導体装置である。

【0017】

この半導体装置では、第1導電型の半導体層の表面に、複数のアクティブ領域を互いに分離する素子分離部が選択的に形成されている。各アクティブ領域は、所定方向に延びる直線領域および直線領域の所定方向の中央において直線領域と直交する直交領域を有する平面視T字状をなしている。そして、アクティブ領域は、所定方向と直交する方向に複数並べて形成されている。直線領域の両端部には、半導体層の表層部に、第2導電型の第1不純物領域が形成されている。直交領域の端部には、半導体層の表層部に、第2導電型の第2不純物領域が形成されている。半導体層上には、ゲート電極が設けられている。ゲート電極は、第1不純物領域と第2不純物領域との間の領域に対向している。また、第1不純物領域の上方には、下部電極および上部電極を備えるキャパシタが形成されている。第1不純物領域と下部電極とは、容量コンタクトプラグを介して、電気的に接続されている。また、第2不純物領域の上方には、ビットラインが形成されている。第2不純物領域とビットラインとは、ビットコンタクトプラグを介して、電気的に接続されている。

【0018】

そして、ビットコンタクトプラグは、所定方向と直交する方向に隣り合う2つのアクティブ領域に形成されている4つの第1不純物領域に接続された容量コンタクトプラグを頂点とする四角形の中心に配置されている。これにより、容量コンタクトプラグとビットコンタクトプラグとの間にデザインルールで定められた最小距離を確保しつつ、所定方向に並ぶ2つの容量コンタクトプラグの間の距離を小さくすることができる。その結果、セル面積を縮小することができる。また、平面視におけるビットコンタクトプラグと下部電極との間にデザインルールで定められた最小距離を確保しつつ、キャパシタの面積を所定方向に拡大することができる。その結果、キャパシタ面積を増大することができる。よって、デザインルールに従いつつ、セル面積に対するキャパシタ面積の割合の増大を図ることができる。

【0019】

請求項2に記載のように、半導体装置は、上部電極の上方に形成されたプレートラインと、下端が上部電極に接続され、上端がプレートラインに接続されたプレートビアとをさらに備えていてもよい。

【0020】

この場合、請求項3に記載のように、容量コンタクトプラグおよびプレートビアが平面視で重なっていてもよい。このレイアウトにより、容量コンタクトプラグの形成時のフォトリソグラフィ工程およびプレートビアの形成時のフォトリソグラフィ工程に、同一のフォトマスク(レチクル)を用いることができる。

【0021】

また、請求項4に記載のように、半導体装置は、下部電極と上部電極との間に介在された強誘電体膜をさらに備えていてもよい。すなわち、半導体装置は、下部電極、上部電極およびこれらの間に介在される強誘電体膜からなる強誘電体キャパシタを備えていてもよい。

【発明を実施するための最良の形態】

【0022】

以下では、本発明の実施の形態を、添付図面を参照して詳細に説明する。

【0023】

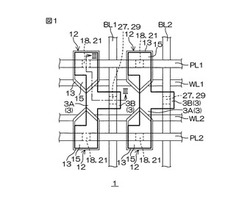

図1は、本発明の第1実施形態に係るFeRAMの図解的な平面図である。図2は、図1に示すFeRAMの回路図である。図3は、図1に示すFeRAMの切断線III−IIIにおける模式的な断面図である。

【0024】

FeRAM1は、複数のメモリセルを備えている。各メモリセルは、1T1C型セル構造を有している。なお、図1,2には、FeRAM1の一部が示されている。また、図2において、1つのメモリセルが破線で囲まれている。

【0025】

FeRAM1は、図3に示すように、P型の半導体層2を備えている。半導体層2は、Si(シリコン)基板またはSiC(炭化珪素)基板などの半導体基板であってもよいし、エピタキシャル成長またはCVD法により形成されるSi層またはSiC層などであってもよい。

【0026】

半導体層2の表面には、複数のアクティブ領域3を避けて、素子分離部4が選択的に形成されている。素子分離部4は、たとえば、半導体層2の表面から比較的浅く掘り下がった溝に絶縁体が埋設されたSTI(Shallow Trench Isolation)構造を有するものであってもよいし、LOCOS(Local Oxidation of Silicon)法により半導体層2の表面に選択的に形成されたシリコン酸化膜であってもよい。

【0027】

図1には、アクティブ領域3の輪郭が太線で示されている。アクティブ領域3は、行方向および列方向にそれぞれ一定の間隔を空けて、行方向および列方向に整列するマトリクス状に配列されている。各アクティブ領域3は、列方向に延びる直線領域3Aおよび直線領域3Aの列方向の中央において直線領域3Aと直交する直交領域3Bを有する平面視T字状をなしている。各アクティブ領域3の直線領域3Aは、その直交領域3Bに対して行方向の一方側に配置されている。

【0028】

各アクティブ領域3には、図3に示すように、半導体層2の表層部に、2つのNチャネルMOSFET(Negative-channel Metal Oxide Semiconductor Field Effect Transistor:以下「NMOS」という。)5のための不純物領域6,7が形成されている。不純物領域6は、直線領域3Aの両端部に形成され、2つのNMOS5の各ドレイン領域をなす。不純物領域7は、アクティブ領域3の直交領域3Bの端部に形成され、2つのNMOS5に共通のソース領域をなす。

【0029】

半導体層2上には、ドレイン領域6とソース領域7との間の領域(NMOS5のチャネル領域)に対向する位置に、ゲート絶縁膜8が形成されている。ゲート絶縁膜8は、たとえば、SiO2(酸化シリコン)からなる。ゲート絶縁膜8上には、ゲート電極9が形成されている。ゲート電極9は、たとえば、ドープトポリシリコン(たとえば、N型不純物が高濃度にドーピングされたポリシリコン)からなる。ゲート電極9の周囲には、サイドウォール10が形成されている。サイドウォール10によって、ゲート絶縁膜8およびゲート電極9の側面の全周が覆われている。サイドウォール10は、たとえば、SiN(窒化シリコン)またはSiO2からなる。

【0030】

図1,2に示すように、行方向に並ぶNMOS5のゲート電極9は、一体化されて、ワードラインWL1,WL2,・・・を構成している。ワードラインWL1,WL2,・・・は、アクティブ領域3の直交領域3Bに対する列方向の両側において、直線領域3Aにおけるドレイン領域6以外の領域と平面視で直交し、行方向に延びる直線状に形成されている。

【0031】

図3に示すように、半導体層2上には、第1層間絶縁膜11が積層されている。第1層間絶縁膜11は、たとえば、SiO2からなる。

【0032】

第1層間絶縁膜11上には、各ドレイン領域6と対向する位置に、強誘電体キャパシタ12が配置されている。強誘電体キャパシタ12は、下部電極13、強誘電体膜14および上部電極15を第1層間絶縁膜11上にこの順に積層した構造を有している。言い換えれば、強誘電体キャパシタ12は、下部電極13と上部電極15との間に強誘電体膜14が介在された構造を有している。強誘電体キャパシタ12は、その形成時におけるエッチング困難性のために、上方が窄まった断面台形状をなしている。

【0033】

下部電極13は、平面視で矩形状部分と略二等辺三角形状部分とを結合した五角形状(ホームベース形状)をなしている。下部電極13は、Irなどの貴金属を含む導電材料からなる。

【0034】

強誘電体膜14は、たとえば、PZT(Pb(Zr,Ti)O3:チタン酸ジルコン酸鉛)からなる。

【0035】

上部電極15は、下部電極13と相似かつ下部電極13よりも小さい平面視五角形状なしている。上部電極15は、たとえば、IrO2(酸化イリジウム)膜、Ir(イリジウム)膜およびIrTa(イリジウムタンタル)合金膜を強誘電体膜14上にこの順に積層した構造を有している。IrTa合金膜は、水素バリア性を有している。

【0036】

第1層間絶縁膜11および強誘電体キャパシタ12の各表面は、強誘電体膜14の水素還元による特性劣化を防止するための水素バリア膜16により被覆されている。水素バリア膜16は、たとえば、Al2O3(アルミナ)からなる。

【0037】

水素バリア膜16上には、第2層間絶縁膜17が積層されている。第2層間絶縁膜17は、たとえば、SiO2からなる。

【0038】

図1,2に示すように、FeRAM1は、プレートラインPL1,PL2,・・・およびビットラインBL1,BL2,・・・をさらに備えている。プレートラインPL1,PL2,・・・およびビットラインBL1,BL2,・・・は、たとえば、第2層間絶縁膜17よりも上方において、層間絶縁膜(図示せず)により互いに絶縁される別の配線層に形成されている。

【0039】

プレートラインPL1,PL2,・・・は、行方向に整列する各強誘電体キャパシタ12の上部電極15の中心上を経由する略直線状に延びている。プレートラインPL1,PL2,・・・は、たとえば、Al(アルミニウム)からなる。

【0040】

ビットラインBL1,BL2,・・・は、列方向に並ぶ各アクティブ領域3に形成されたソース領域7上を経由する直線状に延びている。ビットラインBL1,BL2,・・・は、たとえば、Alからなる。

【0041】

図3に示すように、第1層間絶縁膜11には、各ドレイン領域6とこれに対向する強誘電体キャパシタ12の下部電極13との間に、容量コンタクトプラグ18が埋設されている。図1に示すように、各アクティブ領域3の2つのドレイン領域6上の容量コンタクトプラグ18は、アクティブ領域3の直線領域3Aの列方向の中央に対して対称をなす位置に配置されている。

【0042】

各容量コンタクトプラグ18は、図3に示すように、第1層間絶縁膜11を貫通する容量コンタクトホール19にバリアメタル20を介して埋設されている。バリアメタル20は、容量コンタクトホール19の側面およびドレイン領域6における容量コンタクトホール19に臨む部分を被覆している。これにより、容量コンタクトプラグ18の下端は、バリアメタル20を介して、ドレイン領域6に接続され、その上端は、下部電極13におけるその中心からワードラインWL1,WL2,・・・側と反対側(直線領域3Aの両端部の対向方向の外側)にずれた位置に接続されている。容量コンタクトプラグ18は、たとえば、W(タングステン)からなる。バリアメタル20は、たとえば、TiN(窒化チタン)からなる。

【0043】

また、第2層間絶縁膜17には、各強誘電体キャパシタ12の上部電極15とこれに対向するプレートラインPL1,PL2,・・・との間に、プレートビア21が埋設されている。具体的には、第2層間絶縁膜17には、平面視で容量コンタクトホール19と重なる位置に、プレートビアホール22が形成されている。プレートビアホール22は、第2層間絶縁膜17を貫通し、水素バリア膜16をさらに貫通して、その下端が上部電極15に達している。プレートビアホール22の側面ならびに上部電極15および水素バリア膜16におけるプレートビアホール22に臨む部分上には、バリアメタル23が形成されている。バリアメタル23は、たとえば、TiNからなる。プレートビア21は、バリアメタル23を介して、プレートビアホール22に埋設されている。これにより、プレートビア21の下端は、バリアメタル23を介して、上部電極15におけるその中心からワードラインWL1,WL2,・・・側と反対側にずれた位置に接続され、その上端は、プレートラインPL1,PL2,・・・に接続されている。

【0044】

また、各ソース領域7の上方には、第1層間絶縁膜11を貫通するビットコンタクトホール24と、水素バリア膜16および第2層間絶縁膜17を連続して貫通するビットビアホール25とが互いに連通して形成されている。ビットコンタクトホール24の側面およびソース領域7におけるビットコンタクトホール24に臨む部分上には、バリアメタル20と同じ材料からなるバリアメタル26が形成されている。そして、バリアメタル26の内側には、容量コンタクトプラグ18と同じ材料からなるビットコンタクトプラグ27が埋設されている。これにより、ビットコンタクトプラグ27の下端は、バリアメタル26を介して、ソース領域7に接続されている。一方、ビットビアホール25の側面ならびに水素バリア膜16およびビットコンタクトプラグ27におけるビットビアホール25に臨む部分上には、バリアメタル23と同じ材料からなるバリアメタル28が形成されている。バリアメタル28の内側には、プレートビア21と同じ材料からなるビットビア29が埋設されている。ビットコンタクトプラグ27は、バリアメタル28およびビットビア29を介して、ビットラインBL1,BL2,・・・と電気的に接続されている。

【0045】

そして、アクティブ領域3の行方向の位置は、行方向に隣り合う2つのアクティブ領域3に形成されている4つのドレイン領域6に接続された容量コンタクトプラグ18を頂点とする四角形の中心に、ビットコンタクトプラグ27が配置されるように設定されている。

【0046】

ワードラインWL1,WL2,・・・への電圧の印加によりNMOS5がオンされた状態で、プレートラインPL1,PL2,・・・とビットラインBL1,BL2,・・・との間に電圧が印加されると、強誘電体キャパシタ12の強誘電体膜14に自発分極が生じる。これにより、データの書き込みが達成され、その分極状態が維持されることにより、データが保持される。データの読み出し時には、ワードラインWL1,WL2,・・・への電圧の印加によりNMOS5がオンされた状態で、プレートラインPL1,PL2,・・・とビットラインBL1,BL2,・・・との間にパルス電圧が印加される。このパルス電圧の印加により強誘電体膜14の分極方向が変わると、プレートラインPL1,PL2,・・・とビットラインBL1,BL2,・・・との間に電流が流れるので、その電流の有無により、論理信号「1」または「0」を得ることができる。

【0047】

以上のように、FeRAM1では、複数のアクティブ領域3が行方向に複数並べて形成されている。各アクティブ領域3は、列方向に延びる直線領域3Aおよび直線領域3Aの列方向の中央において直線領域3Aと直交する直交領域3Bを有する平面視T字状をなしている。直線領域3Aの両端部には、P型の半導体層2の表層部に、N型のドレイン領域6が形成されている。直交領域3Bの端部には、半導体層2の表層部に、N型のソース領域7が形成されている。半導体層2上には、ゲート電極9が設けられている。ゲート電極9は、ドレイン領域6とソース領域7との間の領域に対向している。また、ドレイン領域6の上方には、下部電極13、強誘電体膜14および上部電極15を備える強誘電体キャパシタ12が形成されている。ドレイン領域6と下部電極13とは、容量コンタクトプラグ18を介して、電気的に接続されている。また、ソース領域7の上方には、ビットラインBL1,BL2,・・・が形成されている。ソース領域7とビットラインBL1,BL2,・・・とは、ビットコンタクトプラグ27を介して、電気的に接続されている。

【0048】

そして、ビットコンタクトプラグ27は、行方向に隣り合う2つのアクティブ領域3に形成されている4つのドレイン領域6に接続された容量コンタクトプラグ18を頂点とする四角形の中心に配置されている。これにより、容量コンタクトプラグ18とビットコンタクトプラグ27との間にデザインルールで定められた最小距離を確保しつつ、列方向に並ぶ2つの容量コンタクトプラグ18の間の距離を小さくすることができる。その結果、セル面積を縮小することができる。また、平面視におけるビットコンタクトプラグ27と下部電極との間にデザインルールで定められた最小距離を確保しつつ、強誘電体キャパシタ12の面積を列方向に拡大することができる。その結果、キャパシタ面積を増大することができる。よって、デザインルールに従いつつ、セル面積に対するキャパシタ面積の割合の増大を図ることができる。

【0049】

また、容量コンタクトプラグ18およびプレートビア21が平面視で重なる位置に形成されるので、容量コンタクトプラグ18の形成時のフォトリソグラフィ工程およびプレートビア21の形成時のフォトリソグラフィ工程に、同一のフォトマスク(レチクル)を用いることができる。

【0050】

以上、本発明の一実施形態について説明したが、その実施形態には、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

【0051】

たとえば、本発明は、FeRAMに限らず、常誘電体キャパシタを備えるDRAM(Dynamic Random Access Memory)に適用することもできる。

【図面の簡単な説明】

【0052】

【図1】図1は、本発明の第1実施形態に係るFeRAMの図解的な平面図である。

【図2】図2は、図1に示すFeRAMの回路図である。

【図3】図3は、図1に示すFeRAMの切断線III−IIIにおける模式的な断面図である。

【図4】図4は、従来のFeRAMの図解的な平面図である。

【符号の説明】

【0053】

1 FeRAM

2 半導体層

3 アクティブ領域

3A 直線領域

3B 直交領域

4 素子分離部

6 ドレイン領域

7 ソース領域

9 ゲート電極

12 強誘電体キャパシタ

13 下部電極

14 強誘電体膜

15 上部電極

18 容量コンタクトプラグ

21 プレートビア

27 ビットコンタクトプラグ

BL1,BL2 ビットライン

PL1,PL2 プレートライン

WL1,WL2 ワードライン

【技術分野】

【0001】

本発明は、キャパシタを備える半導体装置に関する。

【背景技術】

【0002】

不揮発性メモリの一種として、強誘電体のヒステリシス(履歴現象)を利用してデータを保持するFeRAM(Ferroelectric Random Access Memory:強誘電体メモリ)が知られている。

【0003】

FeRAMには、セル構造の相違から大きき分類して2種類がある。1つは、メモリセル選択用の電界効果トランジスタと強誘電体キャパシタとを備える1T1C型セル構造を有するものであり、他の1つは、ゲート絶縁膜が強誘電体からなる電界効果トランジスタを備える1T型セル構造を有するものである。

【0004】

図4は、従来の1T1C型セル構造を有するFeRAMの図解的な平面図である。

【0005】

FeRAMは、P型のシリコン基板(図示せず)を備えている。シリコン基板の表面には、素子分離部(たとえば、LOCOS酸化膜)が選択的に形成されており、この素子分離部から複数の平面視長方形状のアクティブ領域101が露出している。アクティブ領域101は、その長手方向および長手方向と直交する方向に整列するマトリクス状に配置されている。

【0006】

アクティブ領域101には、2つのメモリセルが形成されている。各メモリセルは、1T1C型セル構造を有している。

【0007】

アクティブ領域101の長手方向の両端部および中央部には、シリコン基板の表層部に、N型の不純物領域が互いに間隔を空けて形成されている。アクティブ領域101の一端部の不純物領域は、一方のメモリセルに備えられる電界効果トランジスタのドレイン領域をなす。アクティブ領域101の他端部の不純物領域は、他方のメモリセルに備えられる電界効果トランジスタのドレイン領域をなす。アクティブ領域101の中央部の不純物領域は、2つのメモリセルに備えられる電界効果トランジスタに共通のソース領域をなす。

【0008】

シリコン基板上には、ソース領域と各ドレイン領域との間の各チャネル領域に対向する位置に、ゲート電極102が設けられている。アクティブ領域101の長手方向と直交する方向に配列される電界効果トランジスタのゲート電極102は、一体化され、1本のワードラインWLを構成している。

【0009】

シリコン基板上には、層間絶縁膜が積層されている。層間絶縁膜上には、各メモリセルのドレイン領域と対向する位置(アクティブ領域101の長手方向の一端部および他端部の上方)に、強誘電体キャパシタ103が設けられている。強誘電体キャパシタ103は、下部電極104と上部電極105との間に強誘電体膜を介在させた積層構造を有している。

【0010】

下部電極104は、平面視略正方形状をなしている。下部電極104の中央部とドレイン領域との間には、第1コンタクトプラグ106が層間絶縁膜を貫通して設けられている。下部電極104は、第1コンタクトプラグ106を介して、ドレイン領域と電気的に接続されている。

【0011】

上部電極105は、下部電極104よりも小さな平面視略正方形状をなしている。上部電極105の中央部の上方において、プレートラインPLがアクティブ領域101の長手方向と直交する方向に延びている。プレートラインPLは、上部電極105と電気的に接続されている。

【0012】

また、アクティブ領域101の上方において、ビットラインBLがアクティブ領域101の長手方向に延びている。ビットラインBLは、第2コンタクトプラグ107を介して、アクティブ領域101の中央部のソース領域と電気的に接続されている。

【0013】

ワードラインWLへの電圧の印加により電界効果トランジスタがオンされた状態で、プレートラインPLとビットラインBLとの間に電圧が印加されると、強誘電体キャパシタ103の強誘電体膜に自発分極が生じる。これにより、データの書き込みが達成され、その分極状態が維持されることにより、データが保持される。データの読み出し時には、ワードラインWLへの電圧の印加により電界効果トランジスタがオンされた状態で、プレートラインPLとビットラインBLとの間にパルス電圧が印加される。このパルス電圧の印加により強誘電体膜の分極方向が変わると、プレートラインPLとビットラインBLとの間に電流が流れるので、その電流の有無により、論理信号「1」または「0」を得ることができる。

【特許文献1】特開2004−95915号公報

【発明の開示】

【発明が解決しようとする課題】

【0014】

FeRAMには、デザインルールがある。このデザインルールでは、ゲート電極102と第1コンタクトプラグ106との間の最小距離、下部電極104の周端縁と第1コンタクトプラグ106との間の最小距離、第1コンタクトプラグ106と第2コンタクトプラグ107との間の最小距離などが定められている。デザインルールに従いつつ、メモリセルの面積(セル面積)に対する強誘電体キャパシタの面積(キャパシタ面積)の割合を増やすには、FeRAMの各部のレイアウトに工夫が必要である。セル面積に対するキャパシタ面積の割合が大きいほど、FeRAMの動作マージン(動作安定性)が向上する。

【0015】

そこで、本発明の目的は、デザインルールに従いつつ、セル面積に対するキャパシタ面積の割合の増大を図ることができる、半導体装置を提供することである。

【課題を解決するための手段】

【0016】

前記の目的を達成するための請求項1記載の発明は、第1導電型の半導体層と、前記半導体層の表面に選択的に形成され、複数のアクティブ領域を互いに分離する素子分離部と、各アクティブ領域において、前記半導体層の表層部に形成された第2導電型の第1不純物領域と、各アクティブ領域において、前記半導体層の表層部に前記第1不純物領域と間隔を空けて形成された第2導電型の第2不純物領域と、前記半導体層上に形成され、前記第1不純物領域と前記第2不純物領域との間の領域に対向するゲート電極と、前記第1不純物領域の上方に形成された下部電極と、前記下部電極上に形成された上部電極と、上端が前記下部電極に接続され、下端が前記第1不純物領域に接続された容量コンタクトプラグと、前記第2不純物領域の上方に形成されたビットラインと、下端が前記第2不純物領域に接続され、前記ビットラインと電気的に接続されたビットコンタクトプラグとを含み、前記アクティブ領域は、所定方向に延びる直線領域および前記直線領域の前記所定方向の中央において前記直線領域と直交する直交領域を有する平面視T字状をなし、前記所定方向と直交する方向に複数並べて形成され、前記第1不純物領域は、各アクティブ領域の前記直線領域の両端部にそれぞれ形成され、前記第2不純物領域は、各アクティブ領域の前記直交領域の端部に形成され、前記ビットコンタクトプラグは、前記所定方向と直交する方向に隣り合う2つのアクティブ領域に形成されている4つの前記第1不純物領域に接続された前記容量コンタクトプラグを頂点とする四角形の中心に配置されている、半導体装置である。

【0017】

この半導体装置では、第1導電型の半導体層の表面に、複数のアクティブ領域を互いに分離する素子分離部が選択的に形成されている。各アクティブ領域は、所定方向に延びる直線領域および直線領域の所定方向の中央において直線領域と直交する直交領域を有する平面視T字状をなしている。そして、アクティブ領域は、所定方向と直交する方向に複数並べて形成されている。直線領域の両端部には、半導体層の表層部に、第2導電型の第1不純物領域が形成されている。直交領域の端部には、半導体層の表層部に、第2導電型の第2不純物領域が形成されている。半導体層上には、ゲート電極が設けられている。ゲート電極は、第1不純物領域と第2不純物領域との間の領域に対向している。また、第1不純物領域の上方には、下部電極および上部電極を備えるキャパシタが形成されている。第1不純物領域と下部電極とは、容量コンタクトプラグを介して、電気的に接続されている。また、第2不純物領域の上方には、ビットラインが形成されている。第2不純物領域とビットラインとは、ビットコンタクトプラグを介して、電気的に接続されている。

【0018】

そして、ビットコンタクトプラグは、所定方向と直交する方向に隣り合う2つのアクティブ領域に形成されている4つの第1不純物領域に接続された容量コンタクトプラグを頂点とする四角形の中心に配置されている。これにより、容量コンタクトプラグとビットコンタクトプラグとの間にデザインルールで定められた最小距離を確保しつつ、所定方向に並ぶ2つの容量コンタクトプラグの間の距離を小さくすることができる。その結果、セル面積を縮小することができる。また、平面視におけるビットコンタクトプラグと下部電極との間にデザインルールで定められた最小距離を確保しつつ、キャパシタの面積を所定方向に拡大することができる。その結果、キャパシタ面積を増大することができる。よって、デザインルールに従いつつ、セル面積に対するキャパシタ面積の割合の増大を図ることができる。

【0019】

請求項2に記載のように、半導体装置は、上部電極の上方に形成されたプレートラインと、下端が上部電極に接続され、上端がプレートラインに接続されたプレートビアとをさらに備えていてもよい。

【0020】

この場合、請求項3に記載のように、容量コンタクトプラグおよびプレートビアが平面視で重なっていてもよい。このレイアウトにより、容量コンタクトプラグの形成時のフォトリソグラフィ工程およびプレートビアの形成時のフォトリソグラフィ工程に、同一のフォトマスク(レチクル)を用いることができる。

【0021】

また、請求項4に記載のように、半導体装置は、下部電極と上部電極との間に介在された強誘電体膜をさらに備えていてもよい。すなわち、半導体装置は、下部電極、上部電極およびこれらの間に介在される強誘電体膜からなる強誘電体キャパシタを備えていてもよい。

【発明を実施するための最良の形態】

【0022】

以下では、本発明の実施の形態を、添付図面を参照して詳細に説明する。

【0023】

図1は、本発明の第1実施形態に係るFeRAMの図解的な平面図である。図2は、図1に示すFeRAMの回路図である。図3は、図1に示すFeRAMの切断線III−IIIにおける模式的な断面図である。

【0024】

FeRAM1は、複数のメモリセルを備えている。各メモリセルは、1T1C型セル構造を有している。なお、図1,2には、FeRAM1の一部が示されている。また、図2において、1つのメモリセルが破線で囲まれている。

【0025】

FeRAM1は、図3に示すように、P型の半導体層2を備えている。半導体層2は、Si(シリコン)基板またはSiC(炭化珪素)基板などの半導体基板であってもよいし、エピタキシャル成長またはCVD法により形成されるSi層またはSiC層などであってもよい。

【0026】

半導体層2の表面には、複数のアクティブ領域3を避けて、素子分離部4が選択的に形成されている。素子分離部4は、たとえば、半導体層2の表面から比較的浅く掘り下がった溝に絶縁体が埋設されたSTI(Shallow Trench Isolation)構造を有するものであってもよいし、LOCOS(Local Oxidation of Silicon)法により半導体層2の表面に選択的に形成されたシリコン酸化膜であってもよい。

【0027】

図1には、アクティブ領域3の輪郭が太線で示されている。アクティブ領域3は、行方向および列方向にそれぞれ一定の間隔を空けて、行方向および列方向に整列するマトリクス状に配列されている。各アクティブ領域3は、列方向に延びる直線領域3Aおよび直線領域3Aの列方向の中央において直線領域3Aと直交する直交領域3Bを有する平面視T字状をなしている。各アクティブ領域3の直線領域3Aは、その直交領域3Bに対して行方向の一方側に配置されている。

【0028】

各アクティブ領域3には、図3に示すように、半導体層2の表層部に、2つのNチャネルMOSFET(Negative-channel Metal Oxide Semiconductor Field Effect Transistor:以下「NMOS」という。)5のための不純物領域6,7が形成されている。不純物領域6は、直線領域3Aの両端部に形成され、2つのNMOS5の各ドレイン領域をなす。不純物領域7は、アクティブ領域3の直交領域3Bの端部に形成され、2つのNMOS5に共通のソース領域をなす。

【0029】

半導体層2上には、ドレイン領域6とソース領域7との間の領域(NMOS5のチャネル領域)に対向する位置に、ゲート絶縁膜8が形成されている。ゲート絶縁膜8は、たとえば、SiO2(酸化シリコン)からなる。ゲート絶縁膜8上には、ゲート電極9が形成されている。ゲート電極9は、たとえば、ドープトポリシリコン(たとえば、N型不純物が高濃度にドーピングされたポリシリコン)からなる。ゲート電極9の周囲には、サイドウォール10が形成されている。サイドウォール10によって、ゲート絶縁膜8およびゲート電極9の側面の全周が覆われている。サイドウォール10は、たとえば、SiN(窒化シリコン)またはSiO2からなる。

【0030】

図1,2に示すように、行方向に並ぶNMOS5のゲート電極9は、一体化されて、ワードラインWL1,WL2,・・・を構成している。ワードラインWL1,WL2,・・・は、アクティブ領域3の直交領域3Bに対する列方向の両側において、直線領域3Aにおけるドレイン領域6以外の領域と平面視で直交し、行方向に延びる直線状に形成されている。

【0031】

図3に示すように、半導体層2上には、第1層間絶縁膜11が積層されている。第1層間絶縁膜11は、たとえば、SiO2からなる。

【0032】

第1層間絶縁膜11上には、各ドレイン領域6と対向する位置に、強誘電体キャパシタ12が配置されている。強誘電体キャパシタ12は、下部電極13、強誘電体膜14および上部電極15を第1層間絶縁膜11上にこの順に積層した構造を有している。言い換えれば、強誘電体キャパシタ12は、下部電極13と上部電極15との間に強誘電体膜14が介在された構造を有している。強誘電体キャパシタ12は、その形成時におけるエッチング困難性のために、上方が窄まった断面台形状をなしている。

【0033】

下部電極13は、平面視で矩形状部分と略二等辺三角形状部分とを結合した五角形状(ホームベース形状)をなしている。下部電極13は、Irなどの貴金属を含む導電材料からなる。

【0034】

強誘電体膜14は、たとえば、PZT(Pb(Zr,Ti)O3:チタン酸ジルコン酸鉛)からなる。

【0035】

上部電極15は、下部電極13と相似かつ下部電極13よりも小さい平面視五角形状なしている。上部電極15は、たとえば、IrO2(酸化イリジウム)膜、Ir(イリジウム)膜およびIrTa(イリジウムタンタル)合金膜を強誘電体膜14上にこの順に積層した構造を有している。IrTa合金膜は、水素バリア性を有している。

【0036】

第1層間絶縁膜11および強誘電体キャパシタ12の各表面は、強誘電体膜14の水素還元による特性劣化を防止するための水素バリア膜16により被覆されている。水素バリア膜16は、たとえば、Al2O3(アルミナ)からなる。

【0037】

水素バリア膜16上には、第2層間絶縁膜17が積層されている。第2層間絶縁膜17は、たとえば、SiO2からなる。

【0038】

図1,2に示すように、FeRAM1は、プレートラインPL1,PL2,・・・およびビットラインBL1,BL2,・・・をさらに備えている。プレートラインPL1,PL2,・・・およびビットラインBL1,BL2,・・・は、たとえば、第2層間絶縁膜17よりも上方において、層間絶縁膜(図示せず)により互いに絶縁される別の配線層に形成されている。

【0039】

プレートラインPL1,PL2,・・・は、行方向に整列する各強誘電体キャパシタ12の上部電極15の中心上を経由する略直線状に延びている。プレートラインPL1,PL2,・・・は、たとえば、Al(アルミニウム)からなる。

【0040】

ビットラインBL1,BL2,・・・は、列方向に並ぶ各アクティブ領域3に形成されたソース領域7上を経由する直線状に延びている。ビットラインBL1,BL2,・・・は、たとえば、Alからなる。

【0041】

図3に示すように、第1層間絶縁膜11には、各ドレイン領域6とこれに対向する強誘電体キャパシタ12の下部電極13との間に、容量コンタクトプラグ18が埋設されている。図1に示すように、各アクティブ領域3の2つのドレイン領域6上の容量コンタクトプラグ18は、アクティブ領域3の直線領域3Aの列方向の中央に対して対称をなす位置に配置されている。

【0042】

各容量コンタクトプラグ18は、図3に示すように、第1層間絶縁膜11を貫通する容量コンタクトホール19にバリアメタル20を介して埋設されている。バリアメタル20は、容量コンタクトホール19の側面およびドレイン領域6における容量コンタクトホール19に臨む部分を被覆している。これにより、容量コンタクトプラグ18の下端は、バリアメタル20を介して、ドレイン領域6に接続され、その上端は、下部電極13におけるその中心からワードラインWL1,WL2,・・・側と反対側(直線領域3Aの両端部の対向方向の外側)にずれた位置に接続されている。容量コンタクトプラグ18は、たとえば、W(タングステン)からなる。バリアメタル20は、たとえば、TiN(窒化チタン)からなる。

【0043】

また、第2層間絶縁膜17には、各強誘電体キャパシタ12の上部電極15とこれに対向するプレートラインPL1,PL2,・・・との間に、プレートビア21が埋設されている。具体的には、第2層間絶縁膜17には、平面視で容量コンタクトホール19と重なる位置に、プレートビアホール22が形成されている。プレートビアホール22は、第2層間絶縁膜17を貫通し、水素バリア膜16をさらに貫通して、その下端が上部電極15に達している。プレートビアホール22の側面ならびに上部電極15および水素バリア膜16におけるプレートビアホール22に臨む部分上には、バリアメタル23が形成されている。バリアメタル23は、たとえば、TiNからなる。プレートビア21は、バリアメタル23を介して、プレートビアホール22に埋設されている。これにより、プレートビア21の下端は、バリアメタル23を介して、上部電極15におけるその中心からワードラインWL1,WL2,・・・側と反対側にずれた位置に接続され、その上端は、プレートラインPL1,PL2,・・・に接続されている。

【0044】

また、各ソース領域7の上方には、第1層間絶縁膜11を貫通するビットコンタクトホール24と、水素バリア膜16および第2層間絶縁膜17を連続して貫通するビットビアホール25とが互いに連通して形成されている。ビットコンタクトホール24の側面およびソース領域7におけるビットコンタクトホール24に臨む部分上には、バリアメタル20と同じ材料からなるバリアメタル26が形成されている。そして、バリアメタル26の内側には、容量コンタクトプラグ18と同じ材料からなるビットコンタクトプラグ27が埋設されている。これにより、ビットコンタクトプラグ27の下端は、バリアメタル26を介して、ソース領域7に接続されている。一方、ビットビアホール25の側面ならびに水素バリア膜16およびビットコンタクトプラグ27におけるビットビアホール25に臨む部分上には、バリアメタル23と同じ材料からなるバリアメタル28が形成されている。バリアメタル28の内側には、プレートビア21と同じ材料からなるビットビア29が埋設されている。ビットコンタクトプラグ27は、バリアメタル28およびビットビア29を介して、ビットラインBL1,BL2,・・・と電気的に接続されている。

【0045】

そして、アクティブ領域3の行方向の位置は、行方向に隣り合う2つのアクティブ領域3に形成されている4つのドレイン領域6に接続された容量コンタクトプラグ18を頂点とする四角形の中心に、ビットコンタクトプラグ27が配置されるように設定されている。

【0046】

ワードラインWL1,WL2,・・・への電圧の印加によりNMOS5がオンされた状態で、プレートラインPL1,PL2,・・・とビットラインBL1,BL2,・・・との間に電圧が印加されると、強誘電体キャパシタ12の強誘電体膜14に自発分極が生じる。これにより、データの書き込みが達成され、その分極状態が維持されることにより、データが保持される。データの読み出し時には、ワードラインWL1,WL2,・・・への電圧の印加によりNMOS5がオンされた状態で、プレートラインPL1,PL2,・・・とビットラインBL1,BL2,・・・との間にパルス電圧が印加される。このパルス電圧の印加により強誘電体膜14の分極方向が変わると、プレートラインPL1,PL2,・・・とビットラインBL1,BL2,・・・との間に電流が流れるので、その電流の有無により、論理信号「1」または「0」を得ることができる。

【0047】

以上のように、FeRAM1では、複数のアクティブ領域3が行方向に複数並べて形成されている。各アクティブ領域3は、列方向に延びる直線領域3Aおよび直線領域3Aの列方向の中央において直線領域3Aと直交する直交領域3Bを有する平面視T字状をなしている。直線領域3Aの両端部には、P型の半導体層2の表層部に、N型のドレイン領域6が形成されている。直交領域3Bの端部には、半導体層2の表層部に、N型のソース領域7が形成されている。半導体層2上には、ゲート電極9が設けられている。ゲート電極9は、ドレイン領域6とソース領域7との間の領域に対向している。また、ドレイン領域6の上方には、下部電極13、強誘電体膜14および上部電極15を備える強誘電体キャパシタ12が形成されている。ドレイン領域6と下部電極13とは、容量コンタクトプラグ18を介して、電気的に接続されている。また、ソース領域7の上方には、ビットラインBL1,BL2,・・・が形成されている。ソース領域7とビットラインBL1,BL2,・・・とは、ビットコンタクトプラグ27を介して、電気的に接続されている。

【0048】

そして、ビットコンタクトプラグ27は、行方向に隣り合う2つのアクティブ領域3に形成されている4つのドレイン領域6に接続された容量コンタクトプラグ18を頂点とする四角形の中心に配置されている。これにより、容量コンタクトプラグ18とビットコンタクトプラグ27との間にデザインルールで定められた最小距離を確保しつつ、列方向に並ぶ2つの容量コンタクトプラグ18の間の距離を小さくすることができる。その結果、セル面積を縮小することができる。また、平面視におけるビットコンタクトプラグ27と下部電極との間にデザインルールで定められた最小距離を確保しつつ、強誘電体キャパシタ12の面積を列方向に拡大することができる。その結果、キャパシタ面積を増大することができる。よって、デザインルールに従いつつ、セル面積に対するキャパシタ面積の割合の増大を図ることができる。

【0049】

また、容量コンタクトプラグ18およびプレートビア21が平面視で重なる位置に形成されるので、容量コンタクトプラグ18の形成時のフォトリソグラフィ工程およびプレートビア21の形成時のフォトリソグラフィ工程に、同一のフォトマスク(レチクル)を用いることができる。

【0050】

以上、本発明の一実施形態について説明したが、その実施形態には、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

【0051】

たとえば、本発明は、FeRAMに限らず、常誘電体キャパシタを備えるDRAM(Dynamic Random Access Memory)に適用することもできる。

【図面の簡単な説明】

【0052】

【図1】図1は、本発明の第1実施形態に係るFeRAMの図解的な平面図である。

【図2】図2は、図1に示すFeRAMの回路図である。

【図3】図3は、図1に示すFeRAMの切断線III−IIIにおける模式的な断面図である。

【図4】図4は、従来のFeRAMの図解的な平面図である。

【符号の説明】

【0053】

1 FeRAM

2 半導体層

3 アクティブ領域

3A 直線領域

3B 直交領域

4 素子分離部

6 ドレイン領域

7 ソース領域

9 ゲート電極

12 強誘電体キャパシタ

13 下部電極

14 強誘電体膜

15 上部電極

18 容量コンタクトプラグ

21 プレートビア

27 ビットコンタクトプラグ

BL1,BL2 ビットライン

PL1,PL2 プレートライン

WL1,WL2 ワードライン

【特許請求の範囲】

【請求項1】

第1導電型の半導体層と、

前記半導体層の表面に選択的に形成され、複数のアクティブ領域を互いに分離する素子分離部と、

各アクティブ領域において、前記半導体層の表層部に形成された第2導電型の第1不純物領域と、

各アクティブ領域において、前記半導体層の表層部に前記第1不純物領域と間隔を空けて形成された第2導電型の第2不純物領域と、

前記半導体層上に形成され、前記第1不純物領域と前記第2不純物領域との間の領域に対向するゲート電極と、

前記第1不純物領域の上方に形成された下部電極と、

前記下部電極上に形成された上部電極と、

上端が前記下部電極に接続され、下端が前記第1不純物領域に接続された容量コンタクトプラグと、

前記第2不純物領域の上方に形成されたビットラインと、

下端が前記第2不純物領域に接続され、前記ビットラインと電気的に接続されたビットコンタクトプラグとを含み、

前記アクティブ領域は、所定方向に延びる直線領域および前記直線領域の前記所定方向の中央において前記直線領域と直交する直交領域を有する平面視T字状をなし、前記所定方向と直交する方向に複数並べて形成され、

前記第1不純物領域は、各アクティブ領域の前記直線領域の両端部にそれぞれ形成され、

前記第2不純物領域は、各アクティブ領域の前記直交領域の端部に形成され、

前記ビットコンタクトプラグは、前記所定方向と直交する方向に隣り合う2つのアクティブ領域に形成されている4つの前記第1不純物領域に接続された前記容量コンタクトプラグを頂点とする四角形の中心に配置されている、半導体装置。

【請求項2】

前記上部電極の上方に形成されたプレートラインと、

下端が前記上部電極に接続され、上端が前記プレートラインに接続されたプレートビアとをさらに含む、請求項1に記載の半導体装置。

【請求項3】

前記容量コンタクトプラグおよび前記プレートビアが、平面視で重なっている、請求項2に記載の半導体装置。

【請求項4】

前記下部電極と前記上部電極との間に介在された強誘電体膜をさらに含む、請求項1〜3のいずれか一項に記載の半導体装置。

【請求項1】

第1導電型の半導体層と、

前記半導体層の表面に選択的に形成され、複数のアクティブ領域を互いに分離する素子分離部と、

各アクティブ領域において、前記半導体層の表層部に形成された第2導電型の第1不純物領域と、

各アクティブ領域において、前記半導体層の表層部に前記第1不純物領域と間隔を空けて形成された第2導電型の第2不純物領域と、

前記半導体層上に形成され、前記第1不純物領域と前記第2不純物領域との間の領域に対向するゲート電極と、

前記第1不純物領域の上方に形成された下部電極と、

前記下部電極上に形成された上部電極と、

上端が前記下部電極に接続され、下端が前記第1不純物領域に接続された容量コンタクトプラグと、

前記第2不純物領域の上方に形成されたビットラインと、

下端が前記第2不純物領域に接続され、前記ビットラインと電気的に接続されたビットコンタクトプラグとを含み、

前記アクティブ領域は、所定方向に延びる直線領域および前記直線領域の前記所定方向の中央において前記直線領域と直交する直交領域を有する平面視T字状をなし、前記所定方向と直交する方向に複数並べて形成され、

前記第1不純物領域は、各アクティブ領域の前記直線領域の両端部にそれぞれ形成され、

前記第2不純物領域は、各アクティブ領域の前記直交領域の端部に形成され、

前記ビットコンタクトプラグは、前記所定方向と直交する方向に隣り合う2つのアクティブ領域に形成されている4つの前記第1不純物領域に接続された前記容量コンタクトプラグを頂点とする四角形の中心に配置されている、半導体装置。

【請求項2】

前記上部電極の上方に形成されたプレートラインと、

下端が前記上部電極に接続され、上端が前記プレートラインに接続されたプレートビアとをさらに含む、請求項1に記載の半導体装置。

【請求項3】

前記容量コンタクトプラグおよび前記プレートビアが、平面視で重なっている、請求項2に記載の半導体装置。

【請求項4】

前記下部電極と前記上部電極との間に介在された強誘電体膜をさらに含む、請求項1〜3のいずれか一項に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2010−147301(P2010−147301A)

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願番号】特願2008−323911(P2008−323911)

【出願日】平成20年12月19日(2008.12.19)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願日】平成20年12月19日(2008.12.19)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]